Page 1

The Worlds Leading Cellular

Telephone Man ufact urer

Service Manual

DCS StarTac

Cellular Subsciber Group

68P09304A85

Page 2

DCS1800 StarTAC PERSONAL

CELLULAR TELEPHONE

Module Level

Repair Manual

68P09304A85-O

Page 3

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85-0 AGen1

19/07/97

PERFORMANCE SPECIFICATIONS -DCS 1800 StarTAC

GENERAL

TRANSMITTER

RECEIVER

SPEECH CODING

Specificat ions are subject to change without notice

CAUTION

Do not jump start vehicle or use an automotive battery charger while the vehicle adapter

option and the portable ra diotelephone are connec ted to the ve hicle el ectrical s ystem as thi s

may cause serious damage to the radio. Disconnect the radio by removi ng the cable kit fuses.

Frequency Range 1710-1785 MHz Tx

1805-1880MHz Rx

Channel Spacing 200 kHz

Number of Chann els 375 carriers w ith 8 channels per carr ier

Modulation GMSK at BT = 0.3

Transmitter Ph a se Accu rac y 5 Degrees RMS, 20 Degre es peak

Duplex Spaci ng 95MHz

Frequency Stability +/- 0.1 ppm of the downlink frequency (Rx)

Voltage Operation +3V to +5.1V dc (Battery) and +4.4V to +6.5V (External connector

Transmit Current <260 mA at 1 Watt

Stand-by Cu rrent 15mA nominal

Dimensions 98.3 mm (L) x 57.3 mm(W) x 23 mm(D)

Size (Volume) 100 cubic cm

Weight Approximately 98.5g; w it h Light Lithium I on 350mAh battery a nd antenna

Temperature Range -20°C to +55°×C

RF Power Output 30 dBm nomina l

Output Impedance 50 ohms (nominal)

Spurious Emi ssions -36 dBm up to 1 GHz, (<-30 dBm > 1 GHz)

Rx Bit Error Rate (100kbit s) <2% @ -100 dBm

Channel Hop Time 500 microseco nds

Time to Camp Approximately 10 seconds

Speech Coding Type Regular Pul se Excita tion / Lin ear Predi ctive Codi ng with Lo ng Term Pred ictio n. (RPE

LPC with LTP.

Bit Rate 13.0 kbps

Frame Duration 20 ms

Block Length 260 bits

Classes Class 1 bits = 182 bits. Class 2 bits = 78 bits

Bit Rate with FEC Encoding

22.8 kbps

COMPUTER SOFTWARE COPYRIGHTS

The Motorola products described in this instru ction manual may include copyr ighted Mot or ola computer programs stor ed in semiconducto r memories

or other media. Laws in the United States and other countries preserve for Motorola certain exclusive rights for copyrighted computer programs,

including the exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any copyrighted Motorola computer

programs contained in t he Motorola products desc ribed in this instruction manual may not be copied or reproduced i n any manner without the express

written permission of Motorola. Furthermore, the purchase of Motorola products shall not be deemed to grant either directly or by implicat ion, estopp el ,

or otherwise, any license und er the copyrights, patents or patent applications of Mot or ola, except for the normal non-excl us ive, royalty free license to

use that arises by operation of law in the sale of a product.

© Motorola Lt d. 1997

All Rights Reserve d

Printed in U.K.

Page 4

Customer Services Publishing

Easter Inch, Bathgate, West Lothian,

EH48 2EH, United Kingdom

AGen1

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

CONTENTS LIST

19/07/97

Cellular Subscriber Group

SECTION 1 - GENERAL PAGE NUMBER

FOREWORD ix

MOTOROLA SERVICE POLICY ix

GENERAL SAFETY INFORMATION x

SECTION 2 - DESCRIPTION

SYSTEM DESCRIPTION 1

DCS SYSTEM OVERVIEW 1

TELEPHONE DESCRIPTION 5

FEATURE LIST 7

SECTION 3 - LABELLING & SIM CARDS

TRANSCEIVER LABELLING 9

INTRODUCTION 9

TITLE EXPLANATIONS 9

SIM CARD S 11

INTRODUCTION 11

SIM CARD INSERTION/REMOVAL 11

SECURITY INFORMATION 11

SECTION 4 - MANUAL - TEST MODE & VERIFICATION

MANUAL-TEST MODE 13

INTRODUCTION 13

TEST SIM INSERTION/REMOVAL 13

ACCESSING THE MANUAL-TEST MODE 13

VERIFICATION 15

INTRODUCTION 15

EQUIPMENT CONFIGURATION 15

TESTING PROCEDURE 16

iii

Page 5

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85-0 AGen1

19/07/97

SECTION 5 - TROUBLESHOOTING

TROUBLESHOOTING 17

INTRODUCTION 17

TROUBLESHOOTING AND REPAIR 17

TESTING AFTER REPAIR 17

PIN OUT CONNECTIONS 18

TROUBLESHOOTING AND REPAIR CHART 19/21

SECTION 6 - PERSONALITY TRANSFER

PERSONALITY TRANSFER 23

INTRODUCTION 23

NORMAL TRANSFER 23

MASTER TRANSFER 24

MASTER SIM CARD CREATION 24

SECTION 7 - DISASSEMBLY

DISASSEMBLY INSTRUCTIONS 25

INTRODUCTION 25

RECOMMENDED TOOLS 25

DISASSEMBLY PROCEDURE 25

ASSEMBLY PROCEDURE 25

STEP BY STEP DISASSEMBLY 26/35

EXPLODED DIAGRAM AND PART NUMBERS 36/37

SECTION 8 - ACCESSORIES

RECHARGEABLE BATTERY PACKS 39

INTRODUCTION 39

RECHARGING 40

EXPERT PERFORMANCE BATTERIES AND CHARGERS 40

BUILT IN E.P BATTERY FAST CHARGER 40

iv

Page 6

CONTENTS

AGen1 68P09304A85-O

19/07/97

SECTION 8 - ACCESSORIES (cont) PAGE NUMBER

NI-MH BATTERY PACKS 41

LITHIUM ION BATTERY PACKS 43

AUXILIARY BATTERY PACK 45

RAPID E.P BATTERY CHARGER 47

RAPID BATTERY CHARGER TRANSFORMER 49

CIGARETTE LIGHTER ADAPTOR/CHARGER 51

CAR KITS 53

INTRODUCTION 53

INSTALLATION INTRODUCTION 54

CAR KIT CONNECTION DIAGRAM 55

INSTALLATION PLANNING 56

COMPONENT LOCATION 56

ELECTRICAL SYSTEM POLARITY 56

USING FUSE LOOPS 56

MINIMIZING ELECTRICAL NOISE 56

CONVENIENCE ON/OFF FEATURE 56

CABLE ROUTING 57

POSSIBLE INTERFERENCE WITH ABS SYSTEMS 57

INSTALLATION 57

MOUNTING THE SMART HANDSET CRADLE 57

DHFA (ADAPTER BOX) 57

StarTAC CRADLE 58

ELECTRICAL CONNECTIONS 58

ENTERTAINMENT MUTE/AUX ALERT 59

MICROPHONE INSTALLATION 59

EXTERNAL SPEAKER INSTALLATION 59

EXTERNAL ANTENNA INSTALLATION 59

PERFORMANCE CHECKS 60

CHECKING ANTENNA PERFORMANCE 60

CHECKING ANTI SKID BRAKING SYSTEMS 61

SECTION 9 - FEED BACK FORM

FEED BACK FORM

v

Page 7

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85-0 AGen1

19/07/97

TYPICAL MODEL COMPLEMENT FOR DCS 1800 StarTAC

Motorola DCS StarTAC S5993ABB

Motorola/One2One DCS StarTAC S5990ABB

Motorola/E-Plus DCS StarTAC S6220ABF

Motorola/Orange DCS StarTAC S5991ABB

Motorola/Bougues DCS StarTAC S5992ABE

Note: In addition to the above, VIP versions are availa ble for the Motorola/E-Pl us and the Motorola kits. Both feature the

addition of a Desktop Cha rger (SPN4325) and an auxiliary Battery (SNN4598).

Model Description

Quantity

Supplied

SUG1120A

SUG1120A

Transceiver

One2One Transceiver

1

1

SNN4667 Standard Battery

1

SPN4278+SYN4656 Travel Charger + UK plug

1

SYN5378 Belt holster

User manual in local language

1

1

Model Description

Quantity

Supplied

SUG1043A Transceiver

1

SNN4667 Standard Battery

1

SPN4278+SYN4655 Travel Charger + Euro plug

1

SYN5378 Belt holster

User manual in local language

1

1

Model Description

Quantity

Supplied

SUG1043A Orange Transceiver

1

SNN4667 Standard Battery

1

SPN4278+SYN4656 Travel Charger + UK plug

1

SYN5378 Belt holster

User manual in local language

1

1

Model Description

Quantity

Supplied

SWF2210A Transceiver

1

SNN4667

SNN4598

Standard Battery

Auxiliary Battery

1

1

SPN4278+SYN4656 Travel Charger + UK plug

1

SYN5378 Belt holster

User manual in local language

1

1

viii

Page 8

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85-0 AGen1

19/07/97

1. SCOPE OF MANUAL

This manual is intende d for use by experie nced technic ians fami liar with si milar ty pes of eq uipment. It contains all servi ce information

required for the equipment described and is current as of the printing date. Major changes which occur after the printing date are

incorporated by C ellula r Ma nual Re visi ons (CMR ). The se CMR ’s are ad ded to t he manuals as t he engi ne ering c hang e is incorpor at ed

into the equipment.

2. MODEL AND KIT IDENTIFICATION

Motor ola equ ipm ents are spec ifica lly ide ntif ied by an ove rall m odel n umbe r on t he na meplat e. In most ca ses, as sem blies a nd ki ts

which make up the equipment also have kit model numbers stamped on t hem. When a produ ction or engi neering change is incorporat ed,

the applicable schematic diagrams are updated.

MOTOROLA SERVICE POLICY (DCS 1800) StarTAC

Warranty:

Product will be sol d with the standard 12 months warranty terms and conditions.

Accidental damage, misus e, and re ta ilers ex tended warranti es wi ll not be s upporte d under wa rranty. Non warran ty repa irs

will be available at agreed fixed repair prices. Proof of purchase will be required to validate warranty claims.

Core Product

:

Motorola only branded product will be supported under a Low tier DCS Loaner program or alternative low cost service

strategy (To be agreed with the Eur opean Cust omer Servi ce Mana gers) . The cust omers ori ginal te le phone wil l be repa ired

but not refurbish ed as s tandard.

Appointed Motorol a Service hubs may p erform both Warranty and Non Warranty field service for Level 2 (m odule repair)

and 3 (Limited compone nt). The Motorola HTC’s will perform f ull Level 4 (full pcb component lev el) repairs.

Customer support (End User)

:

This will be available through the operator own dedicated Call Centres and In Country Help Desks. Operators will be

supported as required by the local Motorola Country Service Manager.

Product Service training should be arrange d through the local Motorola National Support Centre.

REPLACEMENT PARTS ORDERING

Only centres authorized by Motorola to carry out repairs will be able to purchase spare parts. Orders for spare parts from

HUB’s, Motorola National Support Centres and Hi-Tech Centres, should be placed with the appropriate Motorola Parts

Distributi on Centre.

BOARD REPAIRS

All centres au thorize d to ca rry out module lev el r epairs, must return fa ulty boa rds to t he appropr ia te HUB or Motorola HiTech Centre for repair to component level.

FOREWORD

ORDERING INFORMATION

ix

Page 9

CONTENTS

AGen1 68P09304A85-O

19/07/97

GENERAL SAFETY INFORMATION

PORTABLE OPERATION:

DO NOT hold the radio so that the aerial is very close to, or t ouching, exposed parts of the body, especially the

face or eyes whilst transmitting. The radio wi ll perform best if it is held in the same manner as you would hold

a ‘land’ telephone handset, with the aerial angled up and over your shoulder.

DO NOT operate the portable phone in an aircraft. Switch off your telephone. The use of a cellular telephone

in an aircraft may be dangerous to the operation of the aircraft, disrupt the Cellular Network, and is illegal.

Failure to observe this instruction m ay lead to a suspension or denial of Cellular Telephone Service to the

offender, or legal action, or both.

MOBILE/PORTABLE OPERATION - Telephone use in Vehicles

:

All equipment must be properly grounded according to installation instructions for safe operation.

Users are advised to turn off their equipment when at a refuelling point.

Safety is every drivers busines s. Cellular telephones should only be used in situations in which the driver

considers it saf e to do so.

GENERAL

:

DO NOT allow children to play with any radio equipment containing a transmitter.

DO NOT operate this equipment near electrical blasting caps or in an explosive atmosphere. Mobile telephones

are, under certain conditions, capable of interfering with blasting operations. When you are in the vicinity of such

work, look out for and observe signs cautioning against mobile radio transmission. If transmission is prohibited,

you must turn off your mobile telephone to prevent any transmission.

In standby mode the mobile telephone will automatically transmit to acknowledge a call if it is not turned off

.

Refer to the appropriate section of the product user manual for additional pertinent safety information

All equipment should be serviced only by a qualified technician.

x

Page 10

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

BDesc2

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

DESCRIPTION

GENERAL

68P09304A85

19/07/97

1

Cellular Subscriber Group

SYSTEM DESCRIPTION

1. D.C.S. SYSTEM OVERVIEW

1.1 GENERAL CELLULAR CONCEPT

The cellular systems are used to provide radiotelephone

service in the frequency range 1710-1880MHz. A cellular

system provides higher call handling capacity and system

availability than would be possible with conventional

radiotelephone systems (those which require total system

area coverage on every operating channel) by dividing the

system coverage area into several adjoining sub-areas or

cells.

Each cell contains a base station (cell site) which provides

transm itti ng and receiv ing facilit ies, fo r an a llocat ed set of

duplex frequency pairs (channels). Since each cell is a

relatively smal l area, both the ce ll site and the radio telephone

that it supports can ope rate at lower power lev els than would

be used in conventional systems. Using this technique,

radiation on a given channe l is virt ually contai ned in the cell

operating on that channel and, to some extent, those cells

directly adjacent to that cell.

Since the coverage ar ea of a cell on a given channel is limited

to a small area (r elative to the total system coverage area), a

channel may be reused in another cell outside the coverage

area of the first. By this means, several subscribers may

operate within the same geographic area, without

interference with each other, on a single channel.

The following description is intended only as a

preliminary general introduction to the Digital

Communications System (D.C.S) cellular

network. Thi s desc ription is grea tly sim plifie d and

does not illustrate the full operating capabilities,

techniques, or technology incorporated in the

NOTE

1.2 G.S.M. DESCRIPTION

Unlike previous cellular systems, D.C.S. uses digital radio

techniques. The D.C.S.syste m has the following advantages

over previous analogue systems:-

• International Roaming - Due to international

harmonization a nd standa rdi zatio n, it wi ll be pos sibl e

to make and receive calls in any country which

supports a D.C.S. system.

• Digital Air Interface - The D.C.S. phone will pr ovide

an entirely digital link between the telephone and th e

base statio n, whic h i s, i n tu rn, dig it ally l ink ed into th e

switching subsystems and on into the PSTN.

• ISDN Compatibility - ISDN is a digital

communications standard that many countries are

committed to implementing. It is designed to carry

digital voice and data over existing copper telephone

cables. The D.C.S. phone wil l be able to offer similar

features to the ISDN telephone.

• Security and Confidentiality - Telephone calls on

analogue systems c an very eas ily be o verhea rd by th e

use of a suitable radio receiver. D.C.S. offers vastly

improved confidenti ality because of the way in which

data is digitally encrypted and transmitted.

• Better Call Quality - Co-channel interference,

handover breaks, and fading will be dealt with more

effec tively in the digi tal syste m. The ca ll quali ty is

also enh anc ed b y er r or c or re ct ion, whic h r eco n stru cts

lost information.

• Efficiency - The D.C.S. system will be able to use

spectral resources in a much more efficient way than

previous analogue sys tems.

Page 11

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 BDesc2

2 19/07/97

Refer to Figure 1. In the figure, the area bounded by bold

lines represents the total coverage area of a hypothetical

system. This area is divided into several cells, each

containing a cell site (base station) operating on a given set

of channels which interfaces radiotelephone subscribers to

the telephone switching system.

The radiotele phones themselves are capable of operation on

any channel in the system, allowing them to operate in any

cell. Du e to th e low po wer requ irements for c ommunica tions

between radiotel ephone s in a partic ular cel l and th e cel l sit e,

operating channel s may be repeated in cells which are out side

the coverage area of each other.

For example, presume that cell A operates on channels

arbitrarily num bered 1 through 8, cel l B operates on channe ls

9 through 16, cell C operate s on channel s 17 through 24 an d

cell D operate s on channe ls 1 th rough 8 (r epeat ing the usage

of those channels used by ce ll A). In this system, subscribers

in cell A and subscribers in cell D could simultaneously

operate on channels 1 through 8. The implementation of

frequency re-use incre ases the call ha ndling capabil ity of the

system, without i ncreasing t he number of availa ble channels.

When re-using identical frequencies in a small area, cochannel interference can be a problem. The D.C.S. system

can tolerate higher levels of co-channel interference than

analogue systems, by incorporating digital modulation,

forward error correction and equalization. This means that

cells using identical frequencies can be physically closer,

than similar cells in analogue systems. Therefore the

advantage of frequency re-use can be further enhanced in a

D.C.S. system, allowing greater traffic handling in high use

areas.

CHANNELS

CHANNELS

CHANNELS

A

B

C

CHANNELS

D

CHANNELS

E

CHANNELS

F

By incorporating Time Division Multiple Access (TDMA)

several calls can share the same carrier. The carrier is divided

into a continuous stream of TDMA frames, each frame is

split into eigh t time slots. When a connect ion is req uired the

system allo cate s t he su bs cribe r a d edi cate d ti me s lot with in

each TDMA f rame. User da ta (spe ech/d ata) f or tr ansmis sio n

is digitized and sectioned into blocks. The user data blocks

are sen t as inf ormation burst s in the al located time sl ot of

each TDMA frame, see Figure 2. The data blocks are

modulated onto the carrier using Gaussian Minimum Shift

Keying (GMSK), a very efficient method of phase

modulation.

Each time an information burst is transmitted, it may be

transmitted on a different frequency. This process is known

as frequency hopping. Fr equency hopping reduces the effe cts

of fading, and enhances the security and confidentiality of

the link. A D.C.S. ra diotele phone is onl y requi red to t ransmit

for one burst in eac h frame, and not continual ly, thus enabling

the uni t to be m o re pow er ef f i ci en t .

Each radiotelephone must be able to move from one cell to

another, with minimal inconve nience to the user. The mobile

itself carries out signal strength measurements on adjacent

cells, and the quality of the traffic channel is measured by

both the mobile and the base station. The handover criteria

can thus be much more accurately determined, and the

handover made before the c ha nnel q ualit y de terio rat es t o the

point that the subsc r iber notices.

When a radiotelephone is well within a cell, the signal

strength measure d will be high. As the radio telephone moves

towards the edge of the cell, the signal strength and quality

measurement decreases. Signal information provides an

indication of the subscriber’s distance from the bas e station.

As the radiotelephone moves from cell to cell, its control is

handed from one base statio n to another in the new cell . This

change is handled by the radiotelephone and base stations,

and is completely transparent to the user.

01234567012 345670123456701234567

FRAME 0 FRAME 3FRAME 2FRAM E 1

USER DATA SECTIONED INTO BLOCKS

INFORMATION BURSTS SENT IN ALLOCATED TIME SLOTS

Figure 1. Hypothetical Cell System Figure 2. Time Divisio n Multiple Access Transmission

Page 12

DESCRIPTION

BDesc2 68P09304A85

19/07/97 3

1.3 SERVICE AREA

The area within whic h calls can b e placed a nd received is

defined by the system operators. (Because this is a radio

system, there is no exact boundary that can be drawn on a

map.) If the telephone is outside a coverage area, the (no

service) indicator will illuminate and calls will be unable to

be placed or received. If this happens durin g a conv ersation,

the call will be lost. There may also be small areas within a

particular service area where communications may be lost.

The radiotelephon e’s identi ty i nformat ion is held by its local

D.C.S. system in its Home Location Register (HLR) and

Visitor Lo catio n Reg iste r ( VLR ). T he VL R co nta ins id ent it y

information on all local active radiotelephones. Should you

roam to another area, system or country the radiotelephones

identity information is sent to the VLR in the new system.

The new system will then check the radiotelephones details

with your home system for authenticity. If everything is in

order it will be possible to initiate and receive calls whilst in

the new ar ea .

Page 13

DESCRIPTION

BDesc2 68P09304A85

19/07/97 5

1. CELLULAR PERSONAL

TELEPHONE DES CRIPTION

1.1 GENERAL

The DCS StarTac personal cell ular telephone (sh own on next

page, in Fi gure 3) is a micro processor controll ed, full dupl ex,

synthesized FM radiotelephone using digital modulation

techniques, for use in compatible 1800 MHz cellular

radiotelephone systems. When operated properly, the

equipment will provide the user with land-linked telephone

service through individual cell site base stations, all linked

to a central control office. The StarTac has a 1.0 Watt

maximum output power capability.

1.2 PHYSICAL PACKAGING

The transceiver circuitry is contained in a water resistant

polycarbonate plastic housing measuring 98.3 mm (L) x

57.3 mm (W) x 22.5 mm (D); with a capacity of less than

100cc at a weight of approximately 99.5g; including Slim

LiIon battery pack and antenna.

The main internal electronic circuitry is contained on two

multi-layer boards, the RF/Logic board, and the keyboard

assembl y.

The keypad boa rd assembly inc orporates t he display, ke ypad

contacts and LEDs. Electrical connections between the two

boards are provided by connectors at the lower end of each

board.

The RF/Logic board houses the RF and Audio/Logic

circuitry on separate sides in addition to SIM contacts, the

alert, a 16 position ZIF connector, the microphone, and an

external connector.

The accessory connector, situated at the base of the phone

on the main board, allows connections to the audio/logic

circuitry and antenna for accessory applications such as a

mobile adaptor and chargers. When the accessory RF

connector is used (ie terminated with a resistance of

approximately 10 Kohms or less to groun d) the RF to th e top

antenna is disconnected.

Operating power for the perso nal tel ephone can be obt ained

from various methods including the following:-

Standard NiMH Battery pack

Standard Slim LiIon Battery pack

Standard XT LiIon Battery pack

Auxilliary NiMH Battery

The Au x illia r y LiIon B a t tery

Rapid Charging Power Supplies

Cigarette Light er Adaptors

The battery charger plugs into the accessory connector

socket, situ ated at the base of the telephone, and a vehicle’s

cigar lighter socket. As well as providing a battery charging

function, the adaptor provides power directly to the phone

whilst it is in use even with a ‘dead’ battery.

1/. Vehicle Adaptor Kits.

There will be a DHFA available whi ch supports Hands Free

Operation, battery charging, automatic answering, ignition

sense, entertainment mute and auxilliary alert. The kit will

be compatible with ETACS StarTac but a separate hangup

cup will be necessary. It will accomodate an external

microphone and s peaker, option al handset and the analogue

3 watt booster capability. The auxiliary battery cannot be

used with the DHFA. The vibra- alert is inactive when

phone is in use with the DHFA.

NOTE: T he StarTac may have various battery options as

standard depending on the particular market requirements.

Page 14

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 BDesc2

6 19/07/97

EARPIECE

ANTENNA

KEYPAD

MICROPHONE

Figure 3. DCS StarTAC Personal Cellular Telephone.

Page 15

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

BDesc2

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

PRODUCT DESCRIPTION

FEATURE LIST

Cellular Subscriber Group

68P09304A85

19/07/97

7

An ‘X’ indicates that the feature is present in the StarTAC Personal Phone

FEATURE LIST PRESENT

VISUAL/AUDIO FEATURES

Display 32 X 96 Pixel

Graphics Display

Number Capacity (per location) 20

Name Capacity (per location) 16

Language Selection 14

Automatic Language Selection based on SIM X

Silence Ringer w/Visual X

Silence Keypad Tones X

Adjustable earpiece volume X

Adjustable ringer volume X

Silence Scratchpad X

Call in Absence Indicator X

Display Signal Strength - continuous X

Display Battery Le vel - continuous X

Audible Low Battery Warning X

Status Review X

Microphone Mute X

Illumina ted Dis pl ay X

Backlight Display X

Dedicated Control Keys 7

Operator Definable Wake Up Graphics X

Smart Button Operation X

Real Time Clock X

CALL PLACEMENT FEATURES

VibraCall Alert, Including Vibrate then Ring. X

Selectable Ri nger Tones X

Selectable Keypad Tones X

Short, Extended and Pers onalised Menu List X

Auto Redial X

Clear Last Digit/All X

Mute Control X

International Acces s Key Sequence X

User Call Rejection X

Pre-origination Dialling X

FEATURE LIST PRESENT

Memories:

Numbered 100

SIM Card - Dependent on SIM X

Last 10 Numb er s Di al ed X

Last 10 Numbers Received (if using CLI) X

Notepad (Last Number Entered) X

Turbo Dialling (9 Numbers 1 Touch Dial)

from Phone and SIM X

Alpha Name Storage X

Recall by Name or Location X

Memory Linking/Pause X

Memory Auto Load X

Memory Scroll X

Alpha Name Scrolling X

Memory Capacity X

DTMF Signalling:

Long Tone DTMF X

DTMF from Memory X

Postscripting X

Menu Op er at i on X

Silent Alert X

Call Diverting/Barring (Via the Menu) X

Calling Line Identification (Present and Restrict) X

Call Waitin g X

Call Hold X

Master Clear X

Master Reset X

DTX (Discontinuous Transmission) X

112 Emergency Call Ori g ination X

COST CONTROL FEATURES

Electronic Lock X

Automatic Lock X

Programmable Unlock Code X

Display Unlock Code X

Page 16

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 BDesc2

8 19/07/97

An ‘X’ indicates that the feature is pres en t in th e DCS 1800 StarTAC Personal Phone

FEATURE LIST PRESENT

COST CONTROL FEATURES (cont.)

Display Call Timers and/or Charge Meters:

Last Call X

Total X

Home X

Roam X

Programmable Audible Call Timer

One Time X

Repeatable (User Defined) X

Automatic Timer Display:

Charge (units/currency) X

Minutes X

Store Charge Rate:

Home Rate X

Roam Rate X

Call Restriction Levels:

Restrict Keypad Dialing X

Variable Memory Recall Restriction X

Restrict Incoming Calls X

Restrict Phone Number Le ngth (Vari) X

Full Service-No Restrictions X

PIN Entry X

PIN Enable/Disable X

PIN Change X

PIN Unblocking X

NETWORK RELATED

Service S election:

Auto PLMN Selection X

PLMN Select from Scan List X

Scan List Display (auto and manual) X

FEATURE LIST PRESENT

Change Preferred List X

Rearrange Order of Preferred List X

Full Size SIM card X

Display Own Phone Number X

MESSAGING AND DATA

SMS:

Mobile Originated X

Create/send/store/edit/view/delete X

Mobile Termin ated Point to Point X

Cell Broadcast X

Data Calls X

VEHICULAR FEATURES

On Hook Call Processing X

Volume Adj-Speaker X

Safety Timer X

Full Duplex Hands Free Operation X

Ignition Sense (Auto Turn On) X

Entertainment Mute X

Auto Answer X

OTHER FEATURES

Status Indicators X

Easy Battery Removal X

Internal Charger X

Dead Battery Operati on with Chargers X

Desktop Charger X

Cigarette Lighter Adaptor (Option) X

Auxiliary Battery X

Page 17

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

CLbl3

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 StarTAC

CELLULAR TELEPHONE

LABELLING AND SIM CARDS

TRANSCEIVER LABELLING

68P09304A85

19/07/97

9

Cellular Subscriber Group

TRANSCEIVER LABELLING

1. INTRODUCTION

Each Motorola DCS StarTAC transceiver will be labelled

with various number configurations. The following

information shows and explains the common labelling titles.

2. TITLE EXPLANATIONS

2.1 MSN

The Mechanical Serial Number (MSN) is an individual

number, uniquely identifying t he unit. The MSN will remain

the same throughout the units life, even if the main board is

replaced. Because the MSN is unique to the whole phone, it

is often used for logging and tracking purposes by Motorola

National Service Centres on EPPRS. The MSN is divided

into the sections shown in Figure1.

2.2 CEPT DCS

This is the International Mobile Station Equipment Identity

(IMEI) number. The IMEI is held in th e logic circuitry.

3 digits 1 digit 2 digits 4 digits

Model

Code

Origin

Code

Date

Code

Serial

Number

MSN 10 digit s

Figure 1. MSN Confi guration

MC

OC

DC SNR

If the main boa rd is re placed th en the uni ts IMEI will change,

therefore the units labelling should be updated with the new

IMEI. An IMEI uniquely identifies a mobile station

equipment to the system, and is divided into the sections

shown in Figure 2.

2.3 REV S/H

This configuration consists of two blocks of two digits, and

denotes the software and hardware versions within the unit.

The first two digits correspond to the software version, and

the last two digits correspond to the hardware version. If a

version update is carried out on the unit, the corresponding

change information should be made apparent on the

labelling.

2.4 MODEL

The model number d efines t he type of pr oduc t. Ea ch produc t

type is issued a common model number.

2.5 PACKAGE

The package number is used to determine the type of

equipment, the mode in which it was sold, and the language

with which it was shipped.

6 digits 2 digits 6 digits 1 digit

TAC FAC

SNR

SP

Type

Approval

Code

Final

Assembly

Code

Serial

Number

Spare

IMEI 15 digits

Figure 2. IMEI Configuration

Page 18

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85 CLbl3

10 19/07/97

*

PAGE INTENTIONALLY BLANK

Page 19

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

CLbl3

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

LABELLING AND SIM CARDS

Cellular Subscriber Group

68P09304A85

19/07/97

11

SIM CARDS

1. INTRODUCTION

The Motorola DCS StarTAC personal cellular telephones

are designed to work with the full size Subscriber Identity

Module (SIM). The SIM card contains all the personal data

required to access DCS services. Data held by the SIM card

includes:-

• International Mobile Subscriber Identity

• Temporary Mobile Subscriber Identity

• Home system

• Services subscri b ed to

• PIN and unblocking codes

• Call barring codes

The SIM card may also be capable of storing phone

numbers, names, and messages.

2. SIM CARD INSERTION/REMOVAL

The SIM card must be inserted into the unit correctly so that

the card can be read, and the data checked for validity,

before operation on the system will be enabled. The card

contains all of the user’s personal identification numbers

and details of the sy stem the phone operates on.

The whol e SI M car d sh o ul d slide comp let ely into the sl ot at

the base of the ph one. Ensure that the co ntacts of th e card

face towards the front of the phone i.e. towards the keypad .

INTERFACE

CONTACTS

TEST SIM CARD

SIM CARD SLOT

Figure 1. Inserti ng the Test SIM ca rd

The slid ing, card re lease button will move up wards as th e

SIM card is inser ted. Whe n the bu tton reach es the top of its

recess an d th e car d is f lush with the bas e of th e ph one, it is

inserted co rrectly. To remove the SIM card from the unit,

push the sliding SIM card release button downwards. The

card will then be pushed out far enough to allow complete

removal. The User Guide contains full information about

inserting and removing the SIM card.

3. SECURITY INFORMATION

To stop unauthorized personnel using your SIM card, the

option of using a Personal Identity Number (PIN) is

available. When enabled the option requires (on power up) a

verification number to be entered via the unit’s keypad,

before the card can be used. Three attempts to enter the

corr ect P IN m ay b e m a de . If a ft er t he t h re e en tr ie s th e c orr ec t

PIN has not been entered, the card becomes blocked. To

unblock the card an unblocking/super PIN code must be

entere d. Te n attemp ts to e nter th e corr ect unbl ocking code

are permitt ed, if after ten att empts the correct co de has not

been entered, the SIM card is corrupted and becomes useless.

Another option available for the SIM card is call barring. If

subscribed to, the call barring of incoming and/or outgoing

calls may be accomplished by entering a special key

sequence. The key sequence includes a “barring code”,

which de termin es th e type of res trictio n inco rpo rated, an d a

password to validate the request. The initial password is

provided when you sub scribe to the s ervice. The pa ssword

can be changed by ente ring a set key sequence.

A valid st andard sized SIM card can be used in any working

DCS tran sceiver, regardless of the manufact urer, which is

compatib le with the stand ard size SIM car d. To pro tect the

actual unit from unauthorized use, a lock function on the

hardwa re is avai lable. When ena bled, thi s fun ctio n requ ires

that a three or four digit unlock code be entered, via the unit’s

keypad, before normal operation of the transceiver can take

place. The lo ck code can be chang ed by entering a se t key

sequence.

Note: Further information on set key sequences can be

derived from the unit’s user guide.

Page 20

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85 CLbl3

12 19/07/97

*

PAGE INTENTIONALLY BLANK

Page 21

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

DTest4

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

MANUAL-TEST MODE & VERIFICATION

MANUAL-TEST MODE

68P09304A85

19/07/97

13

Cellular Subscriber Group

MANUAL-TEST MODE

1. INTRODUCTION

The Motorola DCS 1800 StarTAC personal cellular

telephones are equipped with a manual-tes t mode capabi lity.

This capability allows service personnel to take control of

the telephone, and by entering certain keypad sequences,

make the telephone perform desired functions. To enter the

manual-test mode, a Test SIM card (Part No 8102316T01)

is required.

2. TEST SIM CARD INSERTION

REMOVAL

The Test SI M ca rd mu st be in serte d i nto the uni t c orre ctl y t o

access manual-test mode. The whole SIM card should slide

completely and securely into the slot at the base of the

phone. Ensure that the contacts of the card face towards the

front of the phone i.e. towards the keypad.

Figure 1. Inserting the Test SIM card

INTERFACE

CONTACTS

TEST SIM CARD

SIM CARD SLOT

The sliding, card release button will move upwards as the

SIM card is inserted. When the button reaches the top of its

recess and the card is flush with the base of the phone, it is

inserted correctly. To remove the SIM card from the unit,

push the sliding SIM card release button downwards. The

card will then be pushed out far enough to allow complete

removal.

The User Guide contains full information about inserting

and removing the SIM card.

3. ACCESSING THE MA NUAL-TE ST MODE

When the Test SIM c ard is in pla ce, p ower up the te lephon e.

Once the initial automatic ‘wake up’ sequence has taken

place correctly, depress the # key (on the units keypad) for

three seconds. Afte r three seconds ‘TEST’ should appear in

the display , indic at ing that t he u nit is now i n the manua l- test

mode. Table 1 below shows the available manual-test

commands and their corresponding results.

Note:

* Please use this command with caution as any customer

information stored in the unit will be lost

** If a custome r shoul d fo rget th e se curity code i n th eir uni t,

it can only be read or changed by using a Test SIM card.

Command Result

01# Exit manual-test mode

19# Display call processor s/w version

20# Display modem s/w version

22# Display speech coder s/w version

57# * Initialize non-volatile memory

58# ** Display security code

58xxxxxx# ** Change security code

59# Display lock code

59xxx# Change lock code

60# Display International Mobile station

Equipm e n t I de ntity ( I. M .E.I.)

Table 1

Page 22

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85 DTest4

14 19/07/97

*

PAGE INTENTIONALLY BLANK

Page 23

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

DTest4

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

MANUAL-TEST MODE & VERIFICATION

Cellular Subscriber Group

68P09304A85

19/07/97

15

1

7

VERIFICATION

1. INTRODUCTION

To test a DCS 1800 StarTAC cellular telephone, to verify

whether or not the unit is functioning correctly, the

following equipment will be required:-

• D.C.S. compatible communications analyser.

• Cable/connector s (SKN4779A) .

• Test SIM card (8102316T01).

• Charged battery pack.

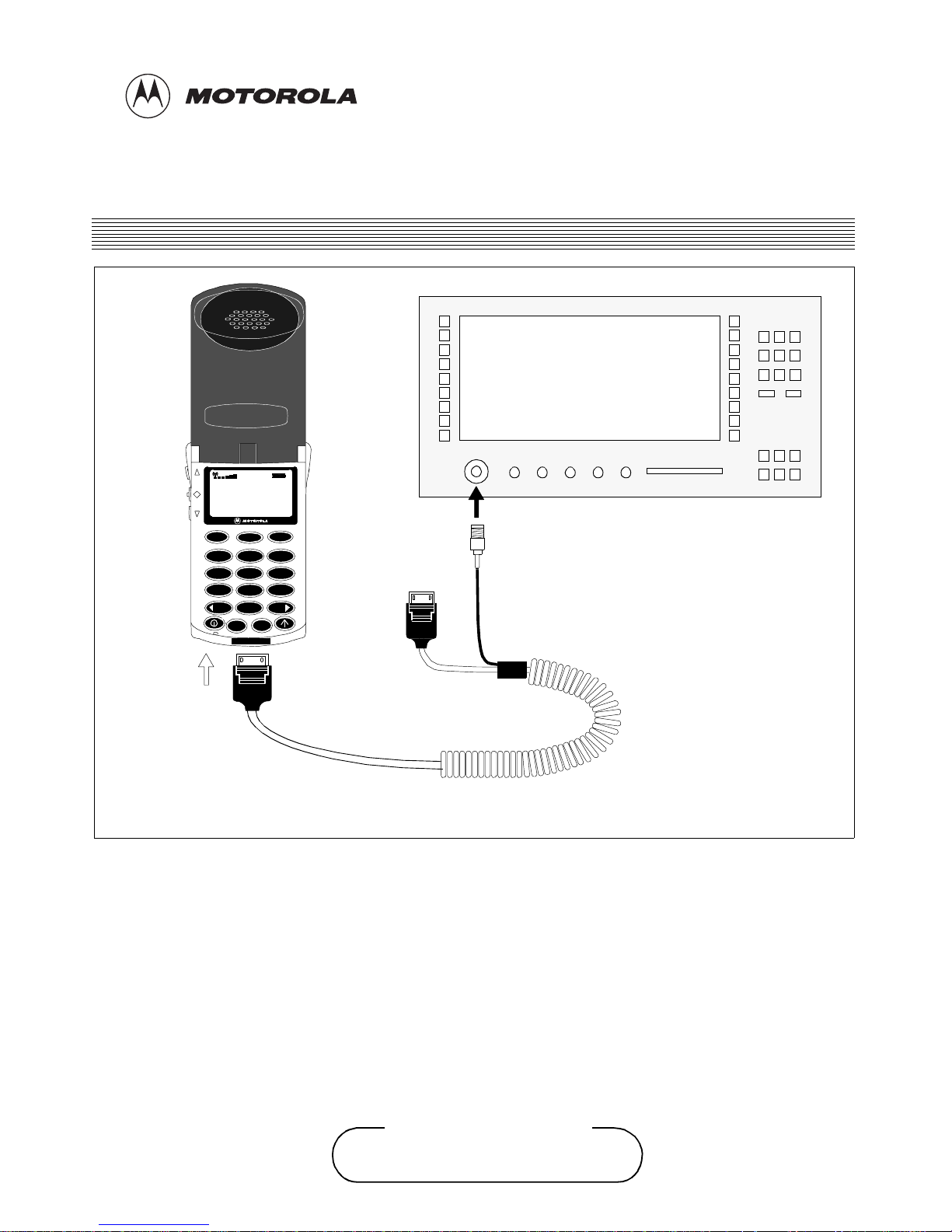

2. EQUIPMENT CONFIGURATION

Initiall y insert th e test SI M card into the slot at the rear of the

personal cellular telephone. If required, further information

on SIM card insertion is available on page 13. Attach the

antenna adapto r t o th e ant enna conne ctor o f th e p hone. Sl ide

a charged battery on to the back of the personal telephone,

so that the telephone can be powered up. Finally, connect a

cable from the test adaptor to the RF in/out port of the

communications analyser, and power both the analyser and

personal telephone on. The equipment set up shown in

Figure 1 should now be in place.

Figure 1: Testing Configuration

D.C..S . COMPATIBLE

COMMUNICATIONS ANALYSER

RF IN/OUT

PORT

32

4 6

5

98

0

c

MR

M+

StarTAC

SMA Plug

OK

MENU

SKN4779A

CABLE

12:00

DEF

MNO

*

#

ABC

JKL

GHI

PQRS

TUV

WXYZ

+

Page 24

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85 DTest4

16 19/07/97

3. TESTING PROCEDURE

All information requ ired to perform the desired t ests and measure ments should be obtained from the communicat ion analyser ’s

user manual.

Ensure that the unit being tested is capable of both initiating a call to the analyser, and receiving a call from the analyser.

Confirm that the displayed Temporary Mobile Subscriber Identity (TMSI), International Mobile Equipment Identity (IMEI),

and dialled number are correct. When a call is in progress th e following tests should be carried out on channels 512, 700

and 885. The record ed results must be within the acceptable stat ed limits, i f t h e un it being te sted passes all the tests it should

be taken as functioning c orrectly. If the unit being tested fai ls to conform with any of the expected measurements, it should be

taken as faulty and repaired accordingly. The following table states the required tests and tolera nces.

TEST TO BE PERFORMED LOWER LIMIT UPPER LIMIT

Transmit average phase error (RMS) at peak power 5

Transmit average phase error (Peak) at peak power 20

Transmit average frequency error at peak power -180 Hz +180 Hz

Transmit power error at level 0 (30 dBm)on CH700 -2 dB +2 dB

Transmit power error at le vel 5 (20 dBm)on CH 700 -3 dB +3 dB

Transmit power error at level 10 (10 dBm)on CH 700 -4 dB +4 dB

Transmit power error at max and min powe r on CH 512 -3 dB +3 dB

Transmit power error at max and min powe r on CH 885 -3 dB +3 dB

Transmit burst mask at max and min power Within DCS specif ication envelope

Receive Bit Error Test for Class II Residual (at -102 dBm)

4

2%

Receiv e Fr ame Erasure Rat e f o r RES II (at -1 02 d Bm )

4

0.12%

Receive level (Rx_LEV) indication at -100 dBm -104 dB -96 dB

Receive level (Rx_LEV) indication at -45 dBm -49dB -41 dB

Receive Quality (Rx_ QUAL) indication for Rx_LEV tests not above 2

Note: 1. The transmit average test values should be derived from 10 separate readings.

2. The receive signal strength for transmit measurements should be -85 dBm.

3. The receive test values should be deri ved from the receptio n of 20K bits of data.

Allow for the loss b etween t he ant enna po rt an d t he RF S MA co nnector on the tes t adapt or . The te st

specifications are written for the power levels at the antenna

Page 25

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

ETrbl5

© Motorola Ltd. 1997All

Rights Reserved

Printed in U.K.

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

TROUBLESHOOTING

ASSEMBLY REPLACEMENT LEVEL

68P09304A85

19/07/97

17

Cellular Subscriber Group

TROUBLESHOOTING

1. INTRODUCTION

Assembly replacement level troubleshooting and repair of

the DCS 1800 StarTAC personal telephone is limited to

isolation and rep lacement of t he following mai n items only: -

• Antenna

• Battery

• Logic/RF Assembly

• Keypad/Display Board

• Front/Rear Housings

• Keypad Membrane

• Flip Assembly

It is recommended that known good replacement parts and

assemblies be available to be used for troubleshooting by

substitution, and for replacement of parts/assemblies found

to be defective.

If at any time the unit is disassembled, whether repaired or

not, it is rec ommended that a simple t est of maki ng a call an d

checking signal strength and transmit and receive audio

quality is c arried out. Appropr iate action sho uld then be taken

on the outcome of the test.

2. TROUBLESHOOTING AND REPAIR

The troubleshooting information in Table 1 shows some

typical malfunction symptoms and the corresponding

verificatio n and repair procedures. Refer to the disassembly

instruction s located in the disassembly se ction of thi s manual

for instructions on removing and replacing parts/assemblies

from the personal telephone. If the Logic/RF assembly is

replaced a persona lity tran sfer will be necess ary, see page 2 3

for more information.

3. TESTING AFTER REPAIR

After any repair work has been carried out, the unit should

be thoroughly tested to ensure that its operates correctly. This

is especi ally import ant if the Logic/RF assembly is replace d.

For general repairs whi ch do not include repla cing the Logic/

RF assembly, simply placing a call and checking signal

strength, and transmit and receive audio quality is normally

sufficient.

When the Logic/RF assembly is replaced, the unit must have

a comprehensive tes t on a DCScompatible communica tions

analyser. See ‘Testing Procedure’ on page 16 for further

details. The simple test of placing a call on air is usually

carried out on completion of this Test to finalise the testing

procedure.

Additionally, a further audio test “Buzz Test” should be

carried out to eliminate the possibility of transmitter

inter fe r en ce to the au d io path. Ref er to tab le A.

Table A

Command Function

08# Unmute RX audio Path

10# Unmute TX audio path

36# Initiate Acoustic Loopback

434# Change audio Path

477

# Set volume level to 7 max

11700#

Set LO to CH700

1200# Set power level to max

310# Initiate PRS (Starts TX)

01# To terminate test

If any distortion or buzz ing is heard through the earpiec e after

entering the above sequence, refer to the DISASSEMBLY

instructions in this manual and ensure that the earpiece and

microphone are seated correctly and that there is no visible

damage to the display PCB/front housing connector. If no

fault found and symptoms persist replace Logic/RF board

(Table 1, symptom 1c).

Defective Logic/RF assemblies must be replaced

with pre-tested, pre-phased assembl ies.

NOTE

Page 26

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85 ETrbl5

18 19/07/97

1- RF Ground

2- RF In/Out

3- RF Ground

4- Battery Feedback

5- Manual Test Lin e

6- RS232 Tx (Charger & External comms)

7- RS232 Rx (Charger & External comms)

8- Audio In

9- Audio Out / On-Off

10- Battery Ground

11- Uplink

12- Downlink

13- DSC _EN_B

14- External B+

15- Ground

1

15

ThermistorDataB- B+

Figure 1: Main Battery Contacts Figure 2: Auxiliary Battery Contacts

Figure 3: J3 Pin Out

The J3 Butt Pl ug connector has pin outs as listed below. Note th at the pin numbe ring is from ri ght to left a s viewed

from the front of the phone; see above figure.

StarTAC

ThermistorData B- B+

Page 27

TROUBLESHOOTING

ETrbl5 68P09304A85

19/07/97 19

Table 1. DCS 1800 StarTAC Cellular Telephone Troublesh ooting and Repair Chart (Assembly Replacement Le vel).

SYMPTOM PROBABLE CAUSE VERIFICATION AND REMEDY

1. Personal telephone will not turn on

or stay on .

a) Batte ry pack ei ther disc harged

or defec t iv e.

Measure battery voltage across a 50 ohm (>1 Watt) load. If the battery

voltage is <3.25 V dc, recharge the battery using the appropriate battery

charger. If the batte ry will not re c harg e, re pl ace th e ba ttery . If b atte ry is

not at fault, proceed to b.

b) Battery connectors open or

misaligned.

Visually inspect the battery connectors on both the battery assembly and

the portable telephone. Re-align and, if necessary, replace either the

battery or the bat tery connect or assembly. Removing the batte ry connector

assembly has to be don e w ith extre m e c are to a void dam agi ng th e PCB.

If battery con nectors are not at fault, proceed to c

c) Logic/RF Board Assembly

defective.

Remove the Logic/RF Assembly. Substitute a known good assembly and

temporaril y reasse mble th e unit. Depress the PWR button; if un it turns

on and stays on, disconnect the dc power source and reassemble the

telephone wit h the new Lo gic/RF Bo ard assemb ly. Verify that the fault

has been cleared. If the fault has not been cleared then proceed to d.

d) Keypad/Display circuit board

failure.

Replace the Keypad/Display board. Temporarily connect a +3.6 V dc

supply to the battery connectors;(refer to pinouts in the diagram on

previous page). Depress the PWR button; if unit turns on and stays on,

disconnect the dc power source and reassemble the telephone with the

new Ke yp a d/Display boa r d.

2. Personal telephone exhibits poor

reception and/or erratic operation

(such as calls frequently dropping,

weak and/or distorted audio, etc.).

a) An tenna is defective. Check to m ake sure tha t the anten na pin is pro perly conn ected to t he Logic/

RF assembly. If OK, substitute a known good antenna . If the fault is still

present, proceed to b.

b) Logic/RF Board Assembly

defective.

Replace Logic/RF Assembly (refer to symptom 1c). Verify that the fault

has been cleared and re-assemble the unit with the ne w PCB.

3. Display is erratic, or provides

partial or n o disp lay.

a) Mating connections to/from

Keypa d/Display boa r d faulty.

Gain access to Keypad/Display / main board as described in the

DISASSEM BLY instru ctions i n this manual. If con nections a re faul ty

then replace the RF/Lo gic assembly a nd/or the Keyp ad/Display board as

necessary . If connectio ns ar e not at fault, r eplace the original boards a nd

proceed to b.

b) Keypad/Display board is

defective.

Substitute a known good Keypad/Display circuit board, if the fault is not

cleared, re-install the original Keypad/ D isplay PCB and proceed to c.

c) Logic/RF Board Assembly

defective.

Replace Logic/RF Assembly (refer to symptom 1c). Verify that the fault

has been cleared and re-assemble the unit with the ne w PCB.

Repair Chart

Page 28

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85 ETrbl5

20 19/07/97

Table 1. DCS 1800 StarTAC Cellular Te lephone Troublesho oting and Repair Chart (Ass embly Replacement Leve l).

SYMPTOM PROBABLE CAUSE VERIFICATION AND REMEDY

4. Incoming call alert transducer au dio

disto r te d or vo l u m e is too low.

a) Connections to/from Keypad/

Display cir cuit board faulty.

Gain access to Keyp ad/Display board as described in the DISASSEMB LY

instructions in this manual. Check connection to alert transducer. If

connection is not at fault, proceed to b.

b) Alert transducer defective. Gain access to alert speaker (located on the Keypad/Display board) as

described in th e DISAS SEMB LY ins tructio ns in this manual . Unsold er

the alert speake r an d so lder on a known good alert speaker. Place call to

personal tele pho ne from la ndli ne or ot he r mobile /per sona l teleph one and

verify alert signal volume and clarity. If good, re-assemble portable with

new alert speaker. If alert speaker not at fault, re-install original alert

speaker and proceed to c.

c) Logic/RF Board Assembly

defective.

Replace Logic/RF Board Assembly (refer to symptom 1c). Verify that the

fault has been cleared and re-assemble the unit with the new PC B .

5. Personal telephone transmit audio

is weak, (usua lly indicat ed by called

parties complaining of difficulty in

hearing voice from personal phone).

a) Microphone connections to

Keypad/Display board defective.

Gain access to the Microphone as described in the DISASSEMBLY

instructi ons in this manual. Check connect ions and if OK, proceed to b.

b) Microphone defective. Gain access to microphone (located on keypad membrane). Disconnect

and substitute a known good Microphone. Place a call and verify

improvemen t in portable tran smit signa l as heard by called party. If good,

re-assembl e portabl e with new Mic rophone. If Micropho ne is not at fa ult,

re-instal l original Microphone and proceed t o c.

c) Logic/RF Board Assembly

defective.

Replace Logic/RF Board Assembly (refer to symptom 1c). Verify that the

fault has been cleared and re-assemble the unit with the new PC B .

6. Personal teleph one r eceiv e aud io is

weak and/or distorted.

a) Connections to/from Logic/RF

circuit boa rd def ective.

Gain access to Logic/RF board as described in the DISASSEMBLY

instructions in this manual. Check connection and th e f lexistrip from the

earpiece to the Logic/RF circuit board. If connection is not at fault,

proceed to b.

b) Earpiece Speaker defective. Gain access to the earpiece spe aker as described in the DISASSEMBLY

instructions in this manual. Substitute a known good earpiece speaker.

Place a call and verify improvement in earpiece audio. If better,

reassemble the phone with the good earpiece speaker. If it was no better

then re-install the ori gin al com p one nt and proceed to c.

c) Antenna assembly is defective. Attempt a re-phasing of the unit and recheck symptom. If symptom the

same but unit re -phases correc tly, check to make sure th e two antenna

connectors are soldered to the main board correctly and that the antenne

is making good contact with them. If ok, substitute a known good antenna

assembly. If this does not cure the fault , re-install the original assembly

then proceed to d.

d) Logic/RF Board Assembly

defective.

Replace Logic/RF Board Assembly (refer to symptom 1c). Verify that the

fault has been cleared and re-assemble the unit with the new PC B .

Page 29

TROUBLESHOOTING

ETrbl5 68P09304A85

19/07/97 21

Table 1. DCS 1800 StarTAC Cellular Te lephone Troublesho oting and Repair Chart (Ass embly Replacement Leve l).

SYMPTOM PROBABLE CAUSE VERIFICATION AND REMEDY

7. Personal telephone will not

recogniz e/accept SIM card

a) SIM card defective Initially check that t he contacts o n the card a re not dirty ; clean if ne cessary,

and check if fault has been eliminated. If the contacts are clean, insert a

known good SIM card int o the po rtab le telep hon e. Po wer up th e unit and

confirm whet her or not the car d has been accepted . If the fault no longer

exists, the defec tive SIM card should be replaced. If the SIM card is not

at fault, proceed to b.

b) SIM card not being re ad. En su re th at the S IM card is pushed fully h ome in to it ’s recess . If all o k ,

proceed to c.

c) Logic/RF Board Assembly

defective.

Replace Logic/RF Board Assembly (refer to symptom 1c). Verify that the

fault has been cleared and re-assemble the unit with the new PC B .

8. Phone does not sense when flip is

opened or clos ed (usually i ndicated by

inability to a n sw er in c omi ng ca lls by

opening the flip, or ina bility to make

outgoing calls).

a) Magnet in flip defective. Replace fl ip assembl y with known good one (r efer to t he DISASSEM BLY

instructions in this manual. Place call to portable phone and verify ability

to answer by opening flip. If fault still present, replace original flip

assembly and proceed to b.

b) Reed switch defective. Gain acce ss to Keypad/Displ ay board as described in th e DISASSEMBLY

instructions in this manual. Unsolder the reed switch and replace with a

known good one. Re assemble unit. Place cal l to po rtable ph one and verify

ability to answe r by o pening fl ip. If faul t still present , repl ace ori ginal re ed

switch and proceed to c.

c) Keypad/Display board is

defective.

Replace the K eypad/Display board with a known good one. Place call to

portable ph one and v erify t hat the fau lt has be en elimi nated. If not at fa ult,

proceed to d.

d) Logic/RF Board Assembly

defective.

Replace Logic/RF Board Assembly (refer to symptom 1c). Verify that the

fault has been cleared and re-assemble the unit with the new PC B .

9. Vibrator feature not functioning. a) Vibrator motor defective. Replace vibrator motor. If fault still present, replace original vibrator

motor and proceed to b.

b) Logic/RF Board Assembly

defective.

Replace Logic/RF Board Assembly (refer to symptom 1c). Verify that the

fault has been cleared and re-assemble the unit with the new PC B .

10. Internal Charger not wo rking. c) Faulty charger ci rcuit on main

board.

Test a sel ection of batteries in the rear pocket of the desktop cha rger. Che ck

LED display for the charging indications. If these are charging ok, then

the internal charger is at fault. Replace main PCB.

11. Real Time Clock resetti ng when

standard battery is removed.

Lithium button cell in the Flip may

be depleted.

Replace Flip to check. If ok, replace original Flip and replace button

battery.

Page 30

DCS 1800 StarTAC CELLULAR TELEPHONE

68P09304A85 ETrbl5

22 19/07/97

*

PAGE INTENTIONALLY BLANK

Page 31

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

FPers6

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 starTAC PORTABLE

CELLULAR TELEPHONE

PERSONALITY TRANSFER

68P09304A85-O

19/07/97

23

Cellular Subscriber Group

PERSONALITY TRANSFER

4. INTRODUCTION

Personality Transfers are required when a phone is Express

Exchanged or when the main board is replaced. The

different variations (languages, features) of the DCS

starTAC personal cellular telephones requires that each

main board must be configured correctly to ensure that the

unit takes on the correct personality required. Therefore,

when a main board is replaced its personality must be

transferred into the new board, so that it functions correctly

in the customers unit. There are two possible methods of

transfer.

• Normal Transfer, an d;

• Mas ter Transf er

If the defective unit powers up, then the Normal Transfer

method should be followed. If the faul ty unit will not power

up, then a Master transfer will be required to configure the

replacement board, once installed.

5. NORMAL TRANSFER

This method allows the personality, selected features and

stored phone numbers of a defe ctive radio, to be transfe rred

into a repair ed radio. Data is transferr ed from the donor unit

into the recipient unit using a Transfer card (Part No

5104025D01). The instruction steps should be followed in

order.

Step 1. Insert the Transfer card into the slot located on

the back of the donor unit. Turn the donor unit

on, the display should show ‘Clone’.

Step 2. The donor unit is now in the cloning mode, and

ready to transfer the first block of data.

Step 3. E nter 021# via t he unit’s keypa d. This comman d

will cause the first block of information to be

uploaded into the Transfer card.

Step 4. While data transfer is taking place between the

unit and the card, ‘Please Wait’ will be

displayed. After a short period of time, if the

data transfer has been completed correctly,

‘Clone’ will re-appear in the donor unit’s

display.

Step 5. When the first data block has been successfully

uploaded, remove the card from the donor.

Step 6. Insert the Transfer card into the slot located on

the back of the recipient unit. Turn the recipient

unit on, the display should show ‘Clone’.

Step 7. The recipient unit is now in the cloning mode,

and ready to receive th e first block of data.

Step 8. Enter 03# via the unit’s keypad. This command

will cause th e recipient unit to download the first

data block from the Transfer card.

Step 9. While data transfer is taking place between the

card and the unit, ‘Please Wait’ will be

displayed. After a short period of time, if the

data transfer has been completed correctly,

‘Clone’ will re-appear in the recipient unit’s

display.

Step 10. The second data bloc k m ust now be transferred.

Repeat steps 1 to 9, but enter 022# to program

the second data block into the Transfer ca rd.

Step 11. The third data block must now be transferred.

Repeat steps 1 to 9, but enter 025# to program

the third data block into the Transfer ca rd.

Step 12. When the third block of data has been

transferred successfully, remove the Transfer

card and check the repaired radio functions

correctly. See page 19 for further informati on.

Page 32

68P09304A82-O FPers6

24 1/9/97

68P09304A85-O FPers6

24 19/07/97

DCS 1800 starTAC CELLULAR TELEPHONE

6. MASTER TRANSFER

This method of transfer should only be followed when the

defective unit will not power up, or complete a Normal

Transfer. As mentioned earlier, there may be different

variations (OEM looks for example) of the Motorola DCS

starTAC cellular telephone, each model requiring the main

board to be configured differently for correct operation.

When carrying out a Master Transfer it is not possible to

transfer the customers selected features or stored phone

numbers, only the model personality can be programmed

into the repaired unit.

Each different version of the DCS starTAC cellular

telephone, requires its own Master Transfer card which

contains essential set up information. Master SIM cards may

be ordered pre-programmed, or created from a Normal

Transfer card. The instruction steps should be followed in

order.

Step 1. Select the requi red M a st er SI M car d .

Step 2. Insert the Master Transfer card into the slot

located on the back of the repaired unit . Turn the

unit on, the display should show ‘Clone’.

Step 3. Enter 03# via the unit’s keypad. This command

will cause the configuration data to be

downloaded from the Maste r Transfer card.

Step 4. While data transfer is taking place between the

card and the unit ‘Please Wait’ will be

displayed. After a short period of time, if the

data transfer has been completed correctly,

‘Clone’ will re-appear in the recipient unit’s

display.

Step 5. When the data block has been transferred

succes sfully, remove t he Master Trans fer card

and check the radio functions correctly. See

page 19 for details.

At no point should either 021#, 022# or 025# be entered

while a Master Transfer card is in the radio. If either of the

stated co mmands are entered, the master information on the

card will be erased. To pr event the above happening the car d

can be locked by entering 06# via the unit’ s keypad, with the

card inserted. Unlock the card by entering 07#.

Note: If during ei ther transfer process a pr oblem arises, an

error message will be displayed. If the Transfer card

is removed before the data transfer is completed

‘Bad Data on Card’ will appear in the display. If

either situation arises, the process should be

repeated.

7. MASTER SIM CARD CREATION

When required a Master SIM card can be created by:-

Step 1. Insert a Transfer card into a unit which is

already configured in the desired way. Turn the

unit on, the display should show ‘Clone’.

Step 2. E nter 024# via t he unit’s keypa d. This comman d

copies the personality information in the unit

onto the Transfer card to create a Master

Transfer card.

Step 3. While data transfer is taking place between the

unit and the card ‘Please Wait’ will be

displayed. After a short period of time, if the

data transfer has been completed correctly,

‘Clone’ will re-appear in the recipient unit’s

display.

Step 4. A Master Transfer card has now been crea ted.

Lock th e c ar d to p r ev e nt acciden t al in f o rm at i on

erasure (see previous section). Remove the card

from the unit, and stor e until required.

Page 33

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH 48 2 EH, United Kingdom

GDis7

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

DISASSEMBLY

68P09304A85

19/07/97

25

Cellular Subscriber Group

DISASSEMBLY INSTRUCTIONS

1. INTRODUCTION

The DCS 1800 StarTAC cellular telephone is assembled

using a simple slide and press fit between front and back

housings followed by positioning of two fixing screws. The

antenna does not have to be removed before disassembly is

started, the antenna can be removed when the back panel is

free. Reaso nable care should be taken duri ng the di sassembly

and reassembly of the unit in order to avoid damaging or

stressing the housing and internal components. Ensure that a

properly grounded high impedance conductive wrist st rap is

used while performi ng these procedures on elec tronic units.

2. RECOMMENDED TOOLS

The following tools are recommended for use during the

assembly/disassembly of the personal telephone.

• Anti-Static Mat Kit 0180386A82; includes:

— Anti-Static Mat 66- 80387A95

— Ground Cord 66-80334B36

— Wrist Band 42-80385A59

• Plastic Bladed Tool (SLN7223A

Many of the inte grated circuit devi ces used in this

equipment are vulnerable to damage from static

charges. E nsure t hat adequa te st atic pr ote ction is

in place when handling, shipping, and servicing

CAUTION

•Τ6 Torx Screw Driver

• Antenna Removal Tool (SYN5179)

• A small flat bladed screw driver,

3. DISASSEMBLY PROCEDURE

3.1 DISASSEMBLY PROCEDURE

The following information describes the procedure for

removing and accessing various parts of the DCS1800

StarTAC.

4. ASSEMBLY PROCEDURE

Once the unit is disassembled and the repair is carried out it

then becomes obvious that to assemble the unit, the

procedure is the reverse of that previously completed for

disassembly. Note that the housings must be securely held

together and the screws torqued appropriately for assembly.

Failure to secure the housings properly could result in

possible damage.

Refer to the mechanical exploded view on

page 38, as necessary, while performing the

disassembl y/assembly procedures.

NOTE

Page 34

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 GDis7

26 19/07/97

Carefully unscrew both Torx Screws with a

size 6 dr i v er.

1

Push Rear housing from the bottom upwards towards the antenn a; when

the housi ng slides free, allow the a ntenna to remain in the rear housing

2

Page 35

DISASSEMBLY

GDis7 68P09304A85

19/07/97 27

2

The two housings simpl y come apart and t he antenna can remain in th e

back housing or you can carefully extract it from the retaining clips.

3

Unclip the flexistrip retaining bar with either a

plastic tool or a fine scredriver.

4

Page 36

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 GDis7

28 19/07/97

Withdraw the Flexistrip cable from the main PCB.

Pry the c ircuit bo ard asse m b ly ou t w ith the P la stic tool

or small screwdriver until it comes away completely.

6

5

Page 37

DISASSEMBLY

GDis7 68P09304A85

19/07/97 29

The Display / Keypad board just pulls away from

the Main board assembly.

7

Unclip the antenna guide from two gold retaining clips and gently ease

towards you, making sure that the tube is still attatched to the foil.

8

Page 38

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 GDis7

30 19/07/97

Pull the f oi l s trip to war ds y ou a nd force it al l th e wa y ov er unt ill you can see

the black adhesive str ip which covers t he reverse sid e of the board.

9

Turn the c ir cuit bo ar d o ver a nd pul l t he blac k a hes iv e st ri p off

completely, leaving the foil strip attatched.

10

Page 39

DISASSEMBLY

GDis7 68P09304A85

19/07/97 31

You now have access to both si des of the circuit board ; this is the

Audio/Di gital side.

11

This side is mostly RF.

12

Page 40

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 GDis7

32 19/07/97

Take up the Flip and remove the Keypad

Membrane.

13

Prize off the adhesive backed cover plate with the

small screwdriver or plastic tool.

14

Page 41

DISASSEMBLY

GDis7 68P09304A85

19/07/97 33

With a small screwdriver or a pair of tweezers, ease the tab

of the central Flexistrip guard out and over the clam shell .

15

With a small screwdriver , locate the recess on the right hand

side of the clam shell and slide the locking pin to the left.

16

Page 42

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 GDis7

34 19/07/97

Then ease the complete cl am shell off of the display/

keypad housing.

17

18

Remove the flip cover by pushing the retaining

pins and lifting the cove r.

Page 43

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 GDis7

35 19/07/97

19

Lifti ng the c ove r away g ives acces s to th e spe aker,

batery and vibrator.

Page 44

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 GDis7

36 19/07/97

6

1

16

7

23

2

22

20

19

18

3

15

14

8

24

9

12

25

5

?

10

17

13

Page 45

DISASSEMBLY

GDis7 68P09304A85

19/07/97 37

REPLACEMENT PARTS LIST

Reference No. PART No DESCRIPTION

1 0309333C01 SC REW TRILOB E W/CAP WASHER

2 0509220D01 GROMMET MIC

3 0509221D01 GROMMET ALERT

4 1109155J01 ADHESIVE DCA COVER (not shown)

5 1509237S01 HSNG FLEX COVER

6 2609231D02 SHIELD LOGIC

7 3709262J01 TUBE ANTENNA

8 3809105S01 ACTR KYPD 19 KEY

3809170E01 ACTR KYPD 17 KEY

9 4709050R01 SHAFT DCS RIGHT

10 5009536H15 MIC LEADED W/PINS

11 5409150R01 LABEL FLEX

12 5509242E01 HINGE DCS

13 7509165R01 PAD SHOCK

14 8509173J01 ANT DIRECT CONN 1800MHZ

15 4009106S01 SW KYPD METAL DOME 19 POS

4009293D01 SW KYPD METAL DOME 17 POS

16 7209185S01 19 KEY DISPLAY BOARD

(complete apart from keypad domes)

7209147D01 17 KEY DISPLAY BOARD (complete apart from keypad domes)

17 2809454C02 32 PIN CONNECTOR (MAIN)

18 4009060E01 SW TACTILE SMD

19 5009473S01 ALERT EM 5V SMD

20 0909449B01 15 Pin Accessory Connector

21 4009169E01 SIM card contact s (not s hown)

22 0 109194S01 F RONT HOUSING 19 KEY

0109212D01 FRONT HOUSING 17 KEY

23 0109284S01 REAR HOUSING

24 0109322D03 ASSY LENS “Motorola”

25 0109485D01 ASSY HSNG MAIN FLIP BLK (Blank Escutcheon)

3309284K01 “Motorola” metal escutcheon (outside of flip)

5409184R55 “StarTAC” vi nyl escutcheon

5409184R79 “EPlus” vinyl escutcheon

5409184R81 “Bouyges” vinyl escutcheon

REPLACEMENT PARTS LIST FOR DCS 1800 Star TAC

Page 46

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 GDis7

38 19/07/97

*

PAGE INTENTIONALLY BLANK

Page 47

Customer Services Publishing

Easter Inch, Bathgate, Wes t Lothian

EH48 2EH, United Kingdom

HAcc8

© Motorola Ltd. 1997

All Rights Reserved

Printed in U.K.

68P09304A85

19/07/97

39

Cellular Subscriber Group

DCS 1800 StarTAC PERSONAL

CELLULAR TELEPHONE

ACCESSORIES

RECHARGABLE BATTERY PACKS

(GENERAL)

1. INTRODUCTION

The DCS StarTAC normal ly opera tes from a 3.6V d c batt ery

pack. There are a number of battery packs, with various

options offered as standard, depending on the market

requirements;

(i) The Slim Lithium E•P Battery (SNN4667).

(ii) The Light LiIon E•P Battery (SNN4785).

(iii) The Slim NiMH E•P Batte ry (SNN4669).

(iv) The Extra Capacity LiIon E•P Battery

(SNN4668).

(v) The Slim LiIon E•P Batt ery (SNN4867)

Full specifications are given in the table below.

* NOTE: For Auxi liary Ba tter ies, t he wei ghts and volum es give n are

for the batteries only. The Talk and Standby times are in addition

to any main ba tte ry fitted .

Each battery pack is housed in a polycarbonate case, which

provides superior impact resistance. Removal of the battery

pack is accomplished through a quick-release latch. If

required, the User Guide contains information on removing

and replacing the battery packs.

2. RECHARGING

The DCS StarTAC has a built in rapid charger. The internal

charger can be powered by either the Travel Charger or the

Cigarette Lighter Adaptor. Both these accessories can power

the phone for a telephone call or

fast-charge a discharged

battery (but not both simultaneously).

Batteries can also be charged directly by the Desktop Rapid

Intellicharge.

Table 1: Battery Specifications

Battery

Information

Main(Primary ) Batteries Auxilliary Battery

Battery Slim LiIon Light LiIon Slim NiMH Extra Capacity

LiIon

Slim LiIon Auxi lliary

Weight (grams)

(phone plus battery)

110 98.5 125 126.5 130

Volume (cc) (phone

plus batt e r y)

100 100 135 109.4 145

Talktime (mins)

(approx.)

100 - 140 60 - 90 100/120 180 - 280 170 - 260

Stand-by time

(hours) (approx.)

30 - 40 20 - 25 30/40 60 - 75 55 - 70

Capacity (mA/Hours) 500 350 500 900 900

Charge Time (Hour s ) 2.5 2.5 1.0 2.5 2.5

Page 48

DCS 1800 StarTAC PERSONAL CELLULAR TELEPHONE

68P09304A85 HAc c8

40 19/07/97

1. (“EXPERT PERFORMANCE”)

BATTERIES AND CHARGERS

E•P batteries are marked with th e new E•P logo and cont ain

an EPROM which provides data to E

•P telephones or E•P