MITSUBISHI PS22052 Technical data

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS22052

TRANSFER-MOLD TYPE

TRANSFER-MOLD TYPE

INSULATED TYPE

INSULATED TYPE

PS22052

INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

• For upper-leg IGBTS :Drive circuit, High voltage high-speed level shifting, Control supply under-voltage (UV) protection.

• For lower-leg IGBT

• Fault signaling : Corresponding to an SC fault (Lower-side IGBT) or a UV fault (Lower-side supply).

• Input interface : 5V line CMOS/TTL compatible (High active logic).

S : Drive circuit, Control supply under-voltage protection (UV), Short circuit protection (SC).

INTEGRATED POWER FUNCTIONS

1200V/5A low-loss 4th generation IGBT inverter bridge for

3 phase DC-to-AC power conversion

PS22052

APPLICATION

AC400V 0.2kW~0.4kW inverter drive for small power motor control.

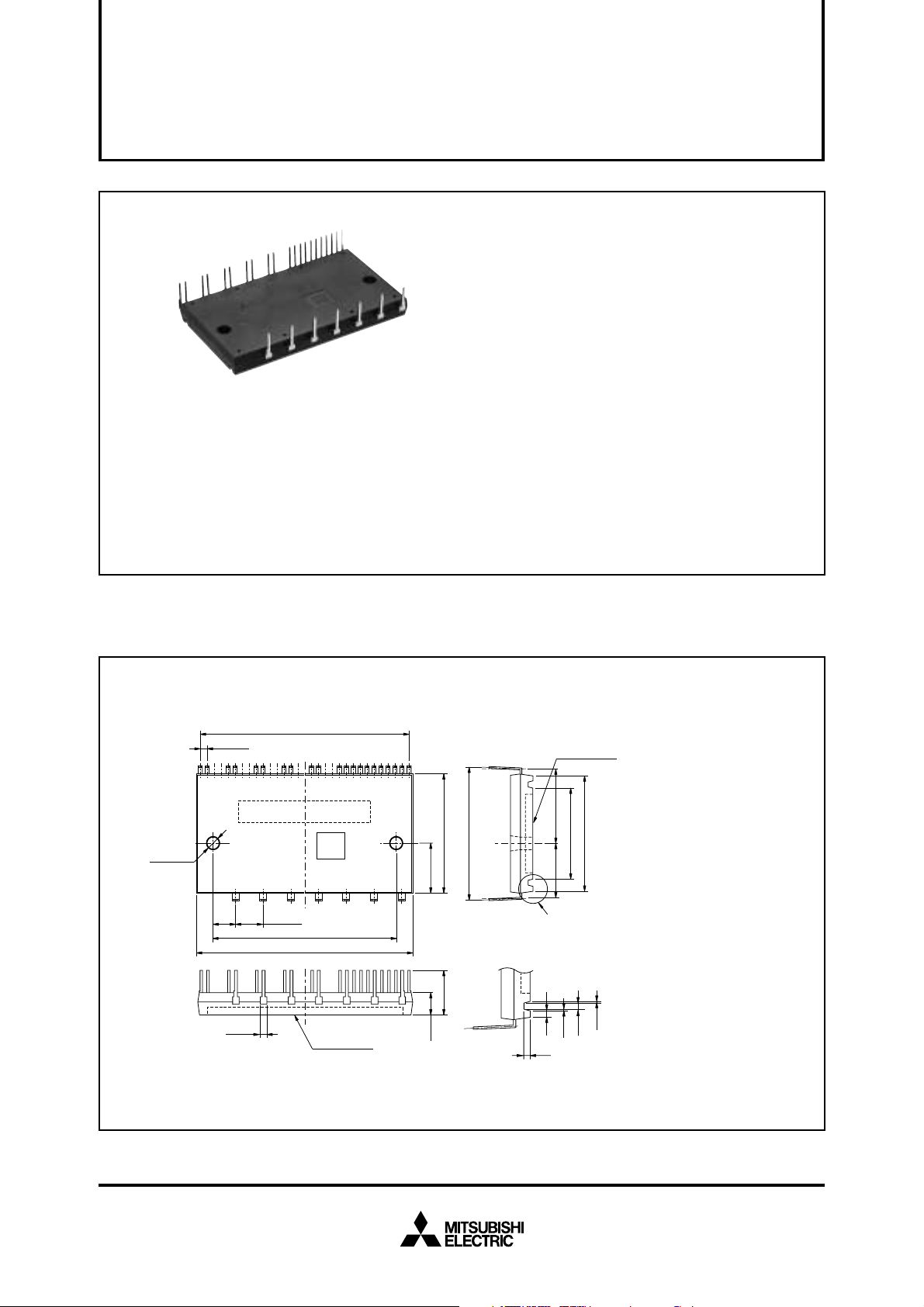

Fig. 1 PACKAGE OUTLINES

30✕2.54(=76.2)

±

0.3

2.54

12 34 56 78 9

10 11 12 13 14 15 16 17 18 19 20 21

Type name , Lot No.

QR

±

0.3

±

67

±

79

Code

0.3

0.5

Heat sink side

0.5

±

18.5

0.5

±

8.2

±

0.2

2-φ4.5

22 23 24 25 26 27 28

±

0.3

8

All external terminals are treated with lead free solder (ingredient : Sn-Cu) plating.

10.16

(2.5)

0.5

±

44

0.3

±

16.1

0.6

±

48.6

Detail : A

Heat sink side

0.5

±

27.4

0.5

±

20.4

A

(2)

(0.3)

(2)

0.5

0.5

±

±

34

42.6

(0.3)

(1.7)

1. VUFS

2. VUFB

3. VP1

4. UP

5. VVFS

6. VVFB

7. VP1

8. VP

9. VWFS

10. VWFB

11. VP1

12. VPC

13. WP

14. VN1

15. VNC

16. CIN

17. CFO

18. FO

19. UN

20. VN

21. WN

Dimensions in mm

22. P

23. U

24. V

25. W

26. NU

27. NV

28. NW

May 2005

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

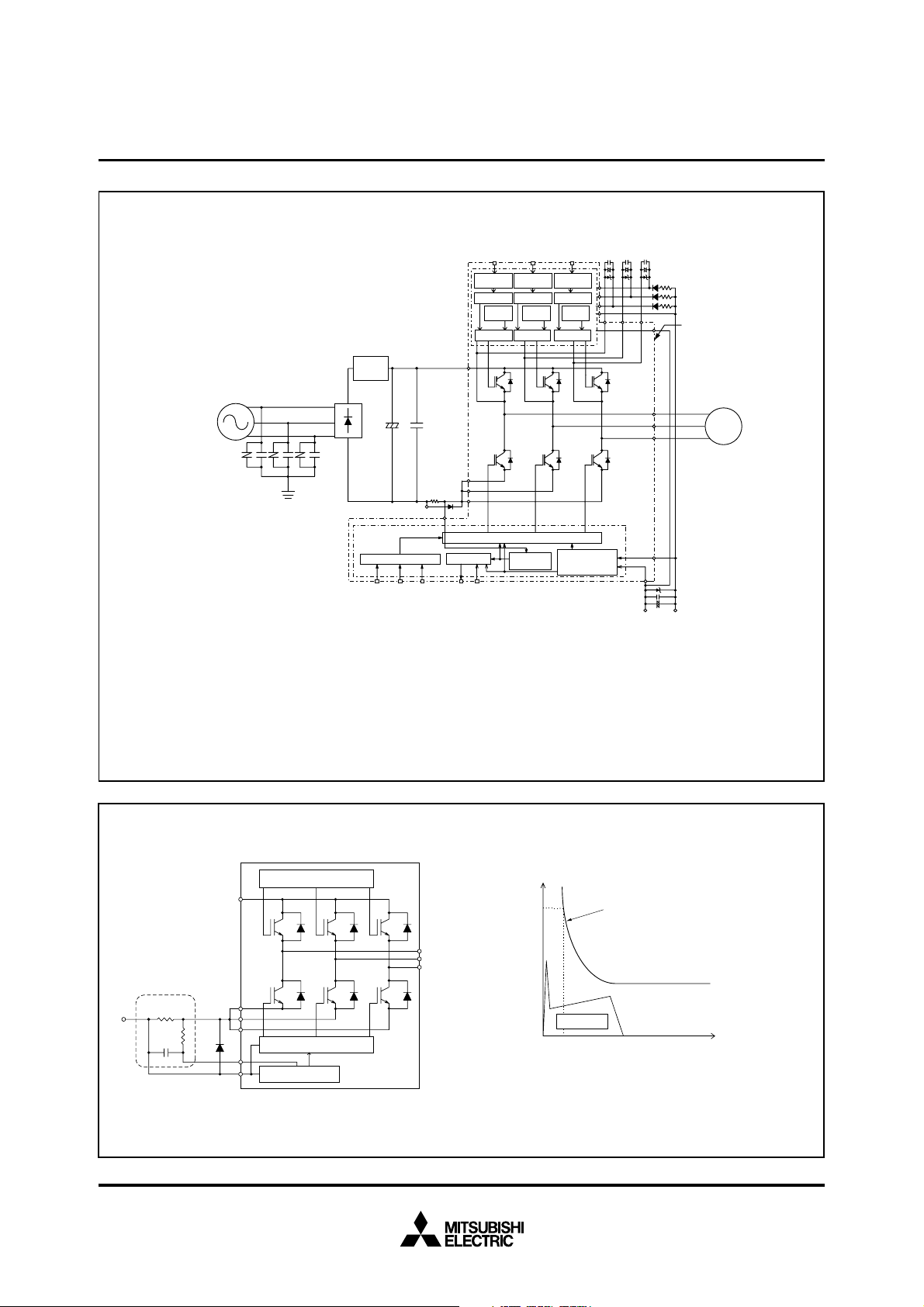

Fig. 2 INTERNAL FUNCTIONS BLOCK DIAGRAM (TYPICAL APPLICATION EXAMPLE)

CBV+

CBU–

CBV–

C1 : Tight tolerance, temp-compensated electrolytic type

(Note : The capacitance depends on the PWM control

scheme used in the applied system.)

C2 : 0.22~2µF R-category ceramic capacitor for noise filtering

Inrush current

limiter circuit

High-side input (PWM)

(5V line) (Note 1,2)

Input signal

conditioning

Level shifter

Protection

circuit (UV)

Drive circuit

P

Input signal

Input signal

conditioning

conditioning

Level shifter Level shifter

Drive circuit Drive circuit

Protection

circuit (UV)

Protection

circuit (UV)

CBU+

PS22052

TRANSFER-MOLD TYPE

INSULATED TYPE

CBW+

CBW–

C2

C1

(Note 6)

DIP-IPM

AC line input

(Note 4)

C

Z

N

1

V

NC

Z : ZNR (Surge absorber)

C : AC filter (Ceramic capacitor 2.2~6.5nF)

(Protection against common-mode noise)

Note1: To prevent input signals oscillation, an RC coupling at each input terminal is recommended.

2: By virtue of integrating HVIC inside the module, direct coupling to MCU terminals without any opto-coupler or transformer isolation is possible.

3: Fo output is open drain type. The signal line should be pulled up to the positive side of a 5V supply with an approximate 10kΩ resistor.

4: The wiring between the power DC-link capacitor and the P/N1 terminals should be as short as possible to protect DIP-IPM against catastrophic high

surge voltage. For extra precaution, a small film type snubber capacitor (0.1~0.22µF, high voltage type) is recommended to mount closely to the

P and N1 terminals.

5: Fo output pulse width (t

FO

=22nF)

at C

6: High voltage (1200V or more) and fast recovery type (less than 100ns) diodes should be used for the bootstrap circuit.

7: It is recommended to insert a Zener diode (24V/1W) between each pair of control supply terminals to prevent surge destruction.

8: To prevent LVIC from surge destruction, it is recommended to mount a fast recovery type diode between V

FO

) should be determined by connecting external capacitor between CFO and VNC terminals. (Example : tFO=2.4ms(typ.)

Input signal conditioning

Low-side input (PWM)

(5V line) (Note 1, 2)

NU

NV

(Note 8)

NW

CIN

Fo logic

FOCFO

Fault output (5V line)

(Note 3, 5)

Drive circuit

Fig. 3 EXTERNAL PART OF THE DIP-IPM PROTECTION CIRCUIT

Protection

circuit

Control supply

Under-Voltage

protection (UV)

H-side IGBT

S

U

V

W

L-side IGBT

S

(Note 7)

V

D

V

NC

(15V line)

NC

and NU, NV, NW terminals.

M

AC line output

DIP-IPM

P

H-side IGBT

A

B

C

(Note 2)

CIN

V

L-side IGBT

NU

NV

NW

NC

External protection circuit

Shunt

resistor

N1

(Note 1)

R

C

Note1: In the recommended external protection circuit, please select the RC time

constant in the range 1.5~2.0µs.

2: To prevent erroneous protection operation, the wiring of A, B, C should be

as short as possible.

Drive circuit

S

S

Drive circuit

Protection circuit

IC (A)

SC protection

trip level

U

V

W

Collector current

waveform

0

2

Short Circuit Protective Function (SC) :

SC protection is achieved by sensing the L-side DC-Bus current (through the external

shunt resistor) with a suitable filtering time (defined by the RC circuit).

When the sensed shunt voltage exceeds the SC trip-level, all the L-side IGBTs are turned

OFF and a fault signal (Fo) is output.

Since the SC fault may be repetitive, it is recommended to stop the system and check the fault,

when the Fo signal is received.

w

(µs)

t

May 2005

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS22052

TRANSFER-MOLD TYPE

INSULATED TYPE

MAXIMUM RATINGS (Tj = 25°C, unless otherwise noted)

INVERTER PART

ConditionSymbol Parameter Ratings Unit

CC

V

VCC(surge)

VCES

±IC

±ICP

PC

Tj

Supply voltage

Supply voltage (surge)

Collector-emitter voltage

Each IGBT collector current

Each IGBT collector current (peak)

Collector dissipation

Junction temperature

Applied between P-NU, NV, NW

Applied between P-NU, NV, NW

C = 25°C

T

T

C = 25°C, less than 1ms

C = 25°C, per 1 chip

T

(Note 1)

900

1000

1200

5

10

38.3

–20~+125

Note 1 : The maximum junction temperature rating of the power chips integrated within the DIP-IPM is 150°C (@ TC ≤ 100°C) however, to en-

sure safe operation of the DIP-IPM, the average junction temperature should be limited to T

j(ave) ≤ 125°C (@ TC ≤ 100°C).

CONTROL (PROTECTION) PART

D

V

VDB

VIN

VFO

IFO

VSC

Parameter

Control supply voltage

Control supply voltage

Input voltage

Fault output supply voltage

Fault output current

Current sensing input voltage

ConditionSymbol

Applied between V

P1-VPC, VN1-VNC

Applied between VUFB-VUFS, VVFB-VVFS,

WFB-VWFS

V

Applied between UP, VP, WP-VPC,

N, VN, WN-VNC

U

Applied between FO-VNC

Sink current at FO terminal

Applied between CIN-V

NC

Ratings Unit

20

20

–0.5~VD+0.5

–0.5~V

D+0.5

1

D+0.5

–0.5~V

V

V

V

A

A

W

°C

V

V

V

V

mA

V

TOTAL SYSTEM

Symbol Ratings Unit

CC(PROT)

V

TC

Tstg

Viso

Self protection supply voltage limit

(short circuit protection capability)

Module case operation temperature

Storage temperature

Isolation voltage

Parameter

D = 13.5~16.5V, Inverter part

V

T

j = 125°C, non-repetitive, less than 2 µs

60Hz, Sinusoidal, AC 1 minute, connection

pins to heat-sink plate

Condition

(Note 2)

800

–20~+100

–40~+125

2500

Note 2 : TC MEASUREMENT POINT

Control terminals

Heat sink boundary

Power terminals

Heat-sink

T

C

T

C

V

°C

°C

rms

V

May 2005

Loading...

Loading...