Mitsubishi M35045-XXXSP, M35045-XXXFP Datasheet

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

DESCRIPTION

The M35045-XXXSP/FP is a TV screen display control IC. It uses a

silicon gate CMOS process and is housed in a 20-pin shrink DIP

package (M35045-XXXSP) or a 20-pin shrink SOP package

(M35045-XXXFP).

For M35045-001SP/FP that is a standard ROM version of M35045XXXSP/FP respectively, the character pattern is also mentioned.

FEATURES

Screen composition ....................................24 columns × 12 lines

•

Number of characters displayed ...................................288 (Max.)

•

Character composition ...................................... 12 × 18 dot matrix

•

Characters available .............................................. 256 characters

•

Character sizes available..................... 4 (horizontal) × 4 (vertical)

•

Display locations available

•

Horizontal direction.............................................. 1000 locations

Vertical direction.................................................. 1023 locations

Blinking..................................................................Character units

•

Cycle : division of vertical synchronization signal into 64 or 32

Duty : 25%, 50%, or 75%

Data input.................................. By the 16-bit serial input function

•

Coloring

•

Character color..................................................... Character unit

Background coloring.............................................Character unit

Matrix-outline (shadow) coloring .............. 8 colors (RGB output)

Specified by register

Border coloring ......................................... 8 colors (RGB output)

Specified by register

Raster coloring .........................................8 colors (RGB output)

Specified by register

Blanking Blanking off

•

Output ports

•

4 shared output ports (toggled between RGB output)

4 dedicated output ports

Display RAM erase function

•

Display input frequency range ...................F

•

Character size blanking

Border size blanking

Matrix-outline blanking

All blanking (all raster area)

OSC

= 30MHz-80MHz

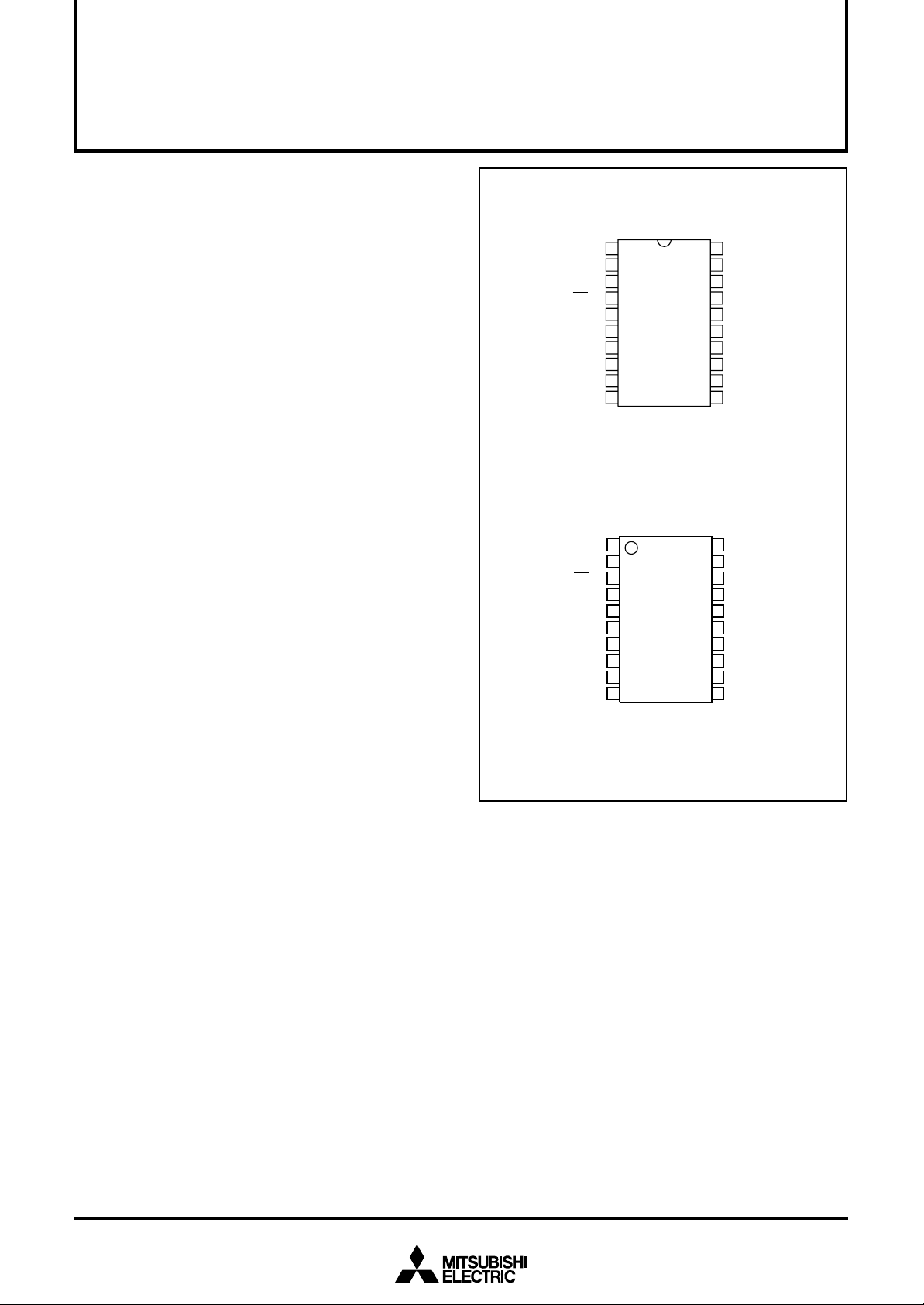

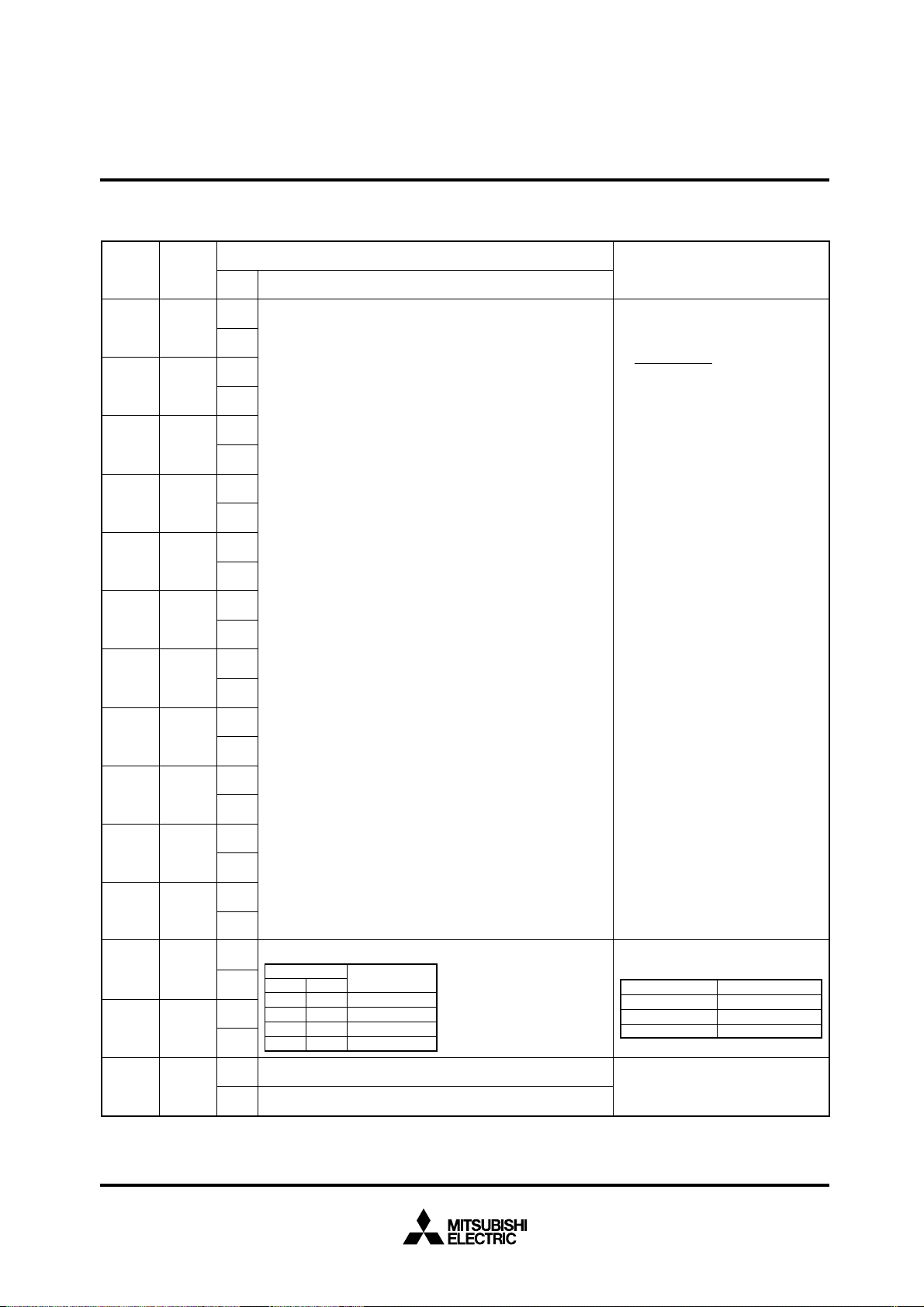

PIN CONFIGURATION (TOP VIEW)

←

VIR

AC

CS

SCK

SIN

TCK

DD1

V

P6

P7

1

2

→

3

→

4

→

5

→

6

→

7

8

←

9

←

10

M35045 - XXXSP

20

19

18

17

16

15

14

13

12

11

V

DD2

←

VERT

←

HOR

→

P5/B

→

P4

→

P3/G

→

P2

→

P1/R

→

P0/BLNK0

SS

V

CPOUT

Outline 20P4B

←

VIR

AC

CS

SCK

SIN

TCK

DD1

V

P6

P7

1

2

→

3

→

4

→

5

→

6

→

7

8

←

9

←

10

CPOUT

M35045 - XXXFP

20

19

18

17

16

15

14

13

12

11

V

DD2

←

VERT

←

HOR

→

P5/B

→

P4

→

P3/G

→

P2

→

P1/R

→

P0/BLNK0

V

SS

Outline 20P2Q-A

APPLICATION

Monitor

Rev.1.1

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

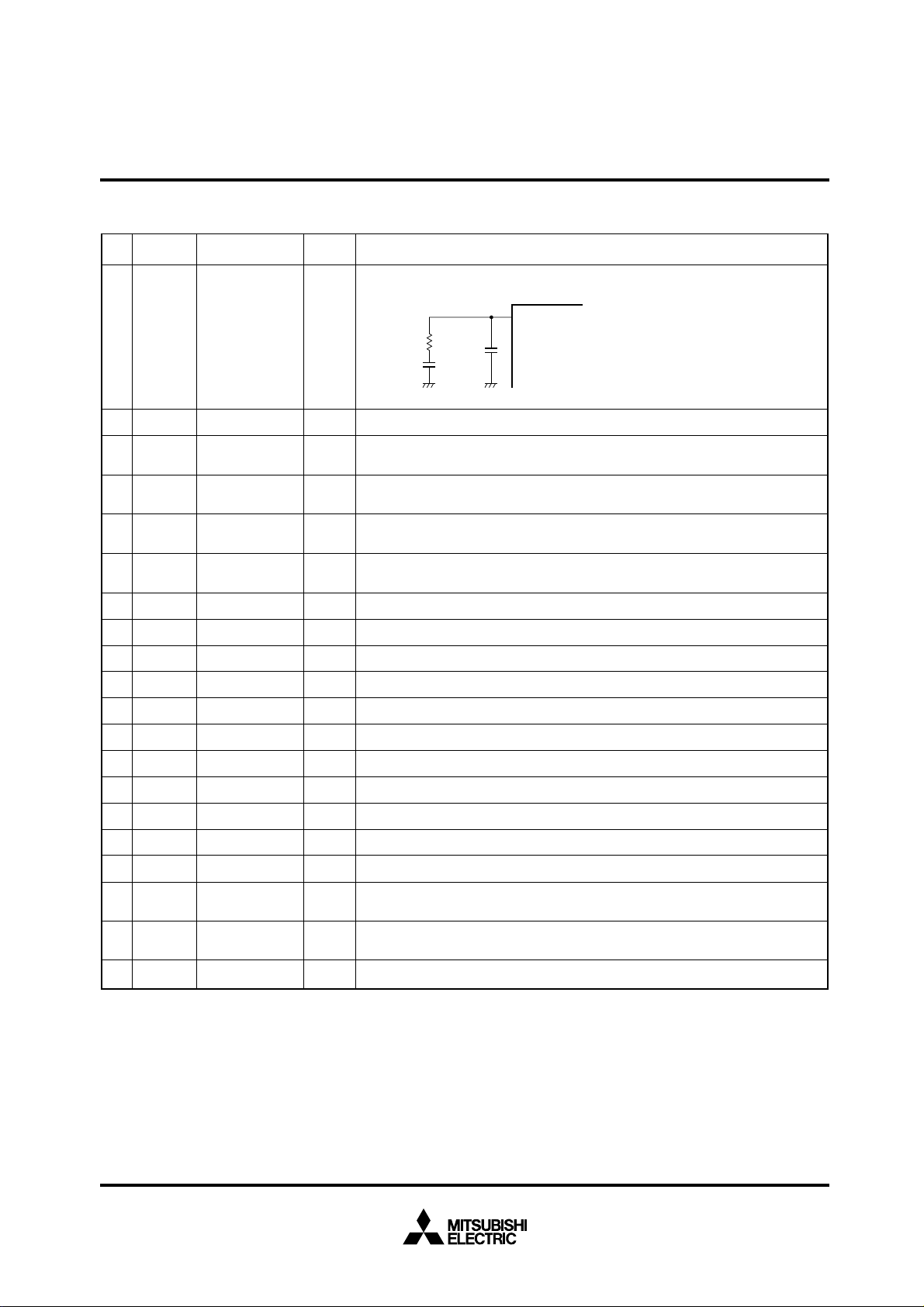

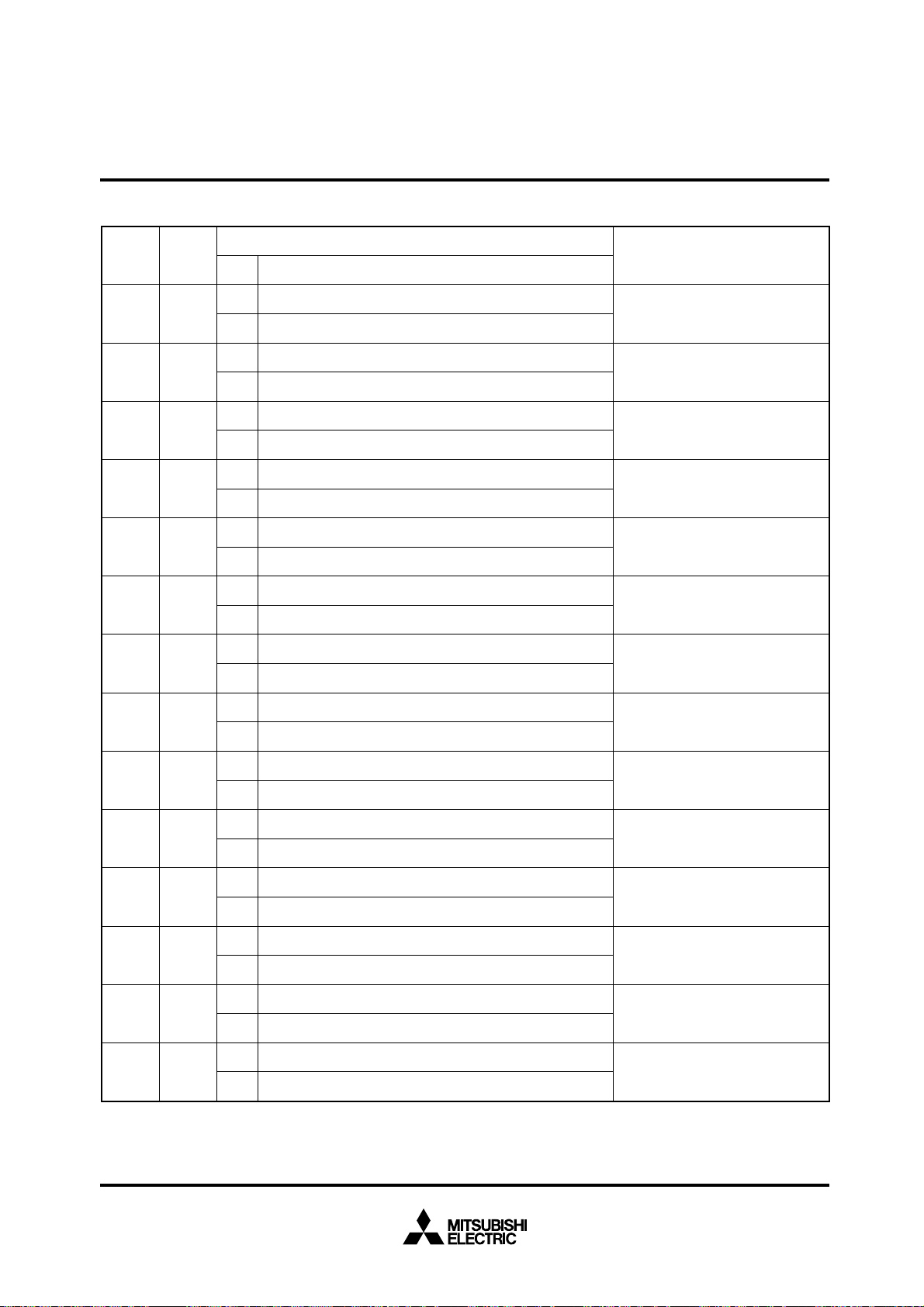

PIN DESCRIPTION

Pin

Number

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

Symbol

CPOUT

VIR

__

AC

__

CS

SCK

SIN

TCK

DD1

V

P6

P7

VSS

P0/BLNK0

P1/R

P2

P3/G

P4

P5/B

HOR

VERT

V

DD2

Pin name

Phase difference

Frequency control

Auto-clear input

Chip select input

Serial clock input

Serial data input

Test clock

Power pin

Port P6 output

Port P7 output

Earthing pin

Port P0 output

Port P1 output

Port P2 output

Port P3 output

Port P4 output

Port P5 output

Horizontal synchro-

nization signal input

Vertical synchroni-

zation signal input

Power pin

Input/

Output

Output

–

Input

Input

Input

Input

Input

–

Output

Output

–

Output

Output

Output

Output

Output

Output

Input

Input

–

Function

Connect loop filter to this pin.

2.4kΩ∗1

0.1µF

1pin

4700pF

2

∗

2

∗

CPOUT

1 Use at 1% precision

∗

2 Use at 10% precision

∗

Connect to GND.

When “L”, this pin resets the internal IC circuit. Hysteresis input. Includes built-in pull-up

resistor.

This is the chip select pin, and when serial data transmission is being carried out, it goes

to “L”. Hysteresis input. Includes built-in pull-up resistor.

__

When CS pin is “L”, SIN serial data is taken in when SCK rises. Hysteresis input. Built-in

pull-up resistor is included.

This is the pin for serial input of data and addresses for the display control register and

the display data memory. Hysteresis input. Includes built-in pull-up resistor.

Input for test. Please connect to GND using circuit earthing pin.

Please connect to +5V with the power pin.

This is the output port. Port data is set by PTD6.

This is the output port. Port data is set by PTD7.

Please connect to GND using circuit earthing pin.

This pin can be toggled between port pin output and BLNK0 signal output.

This pin can be toggled between port pin output and R signal output.

This is the output port. Port data is set by PTD2.

This pin can be toggled between port pin output and G signal output.

This is the output port. Port data is set by PTD4.

This pin can be toggled between port pin output and B signal output.

This pin inputs the horizontal synchronization signal. Hysteresis input.

This pin inputs the vertical synchronization signal. Hysteresis input.

Please connect to +5V with the power pin.

2

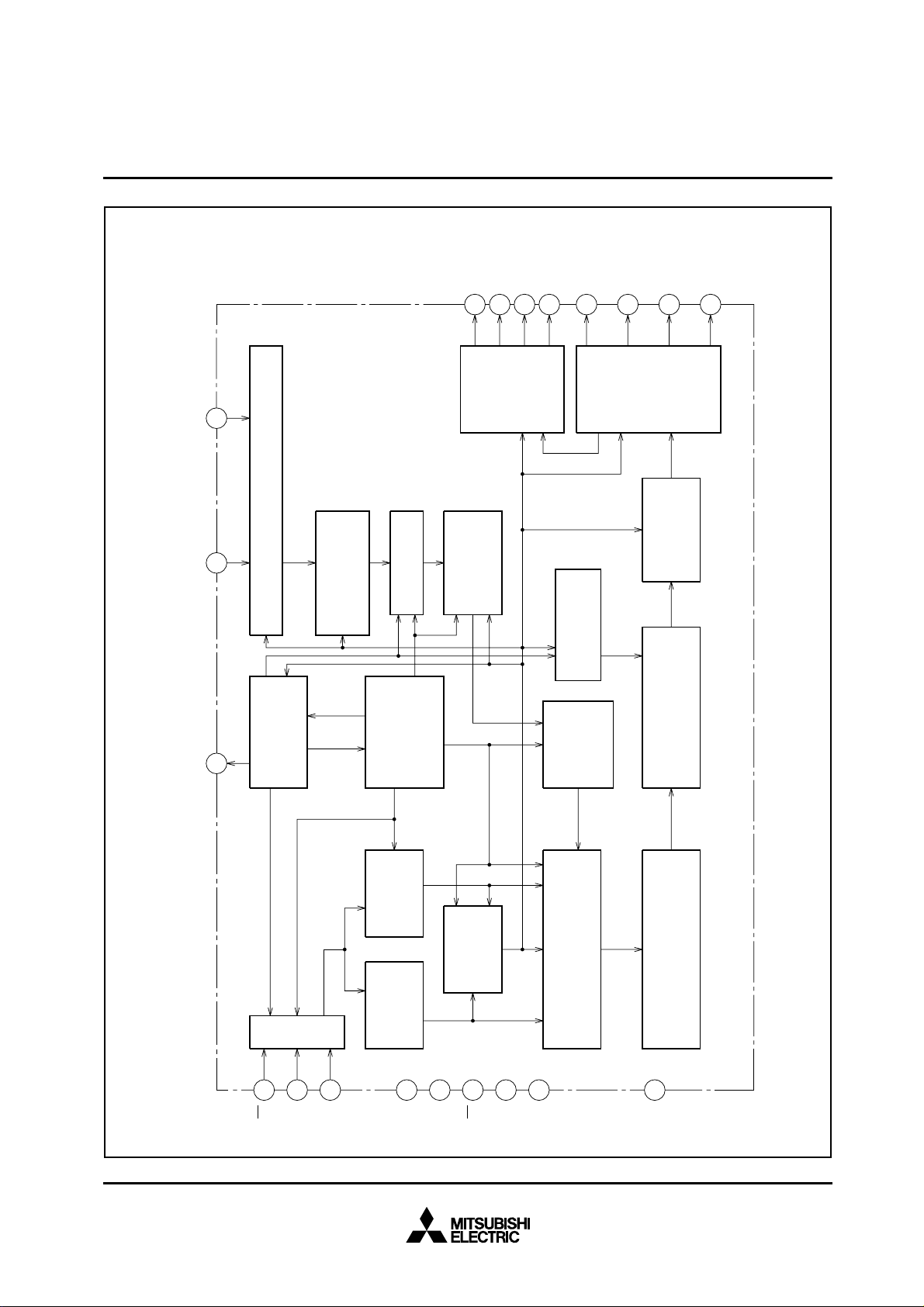

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

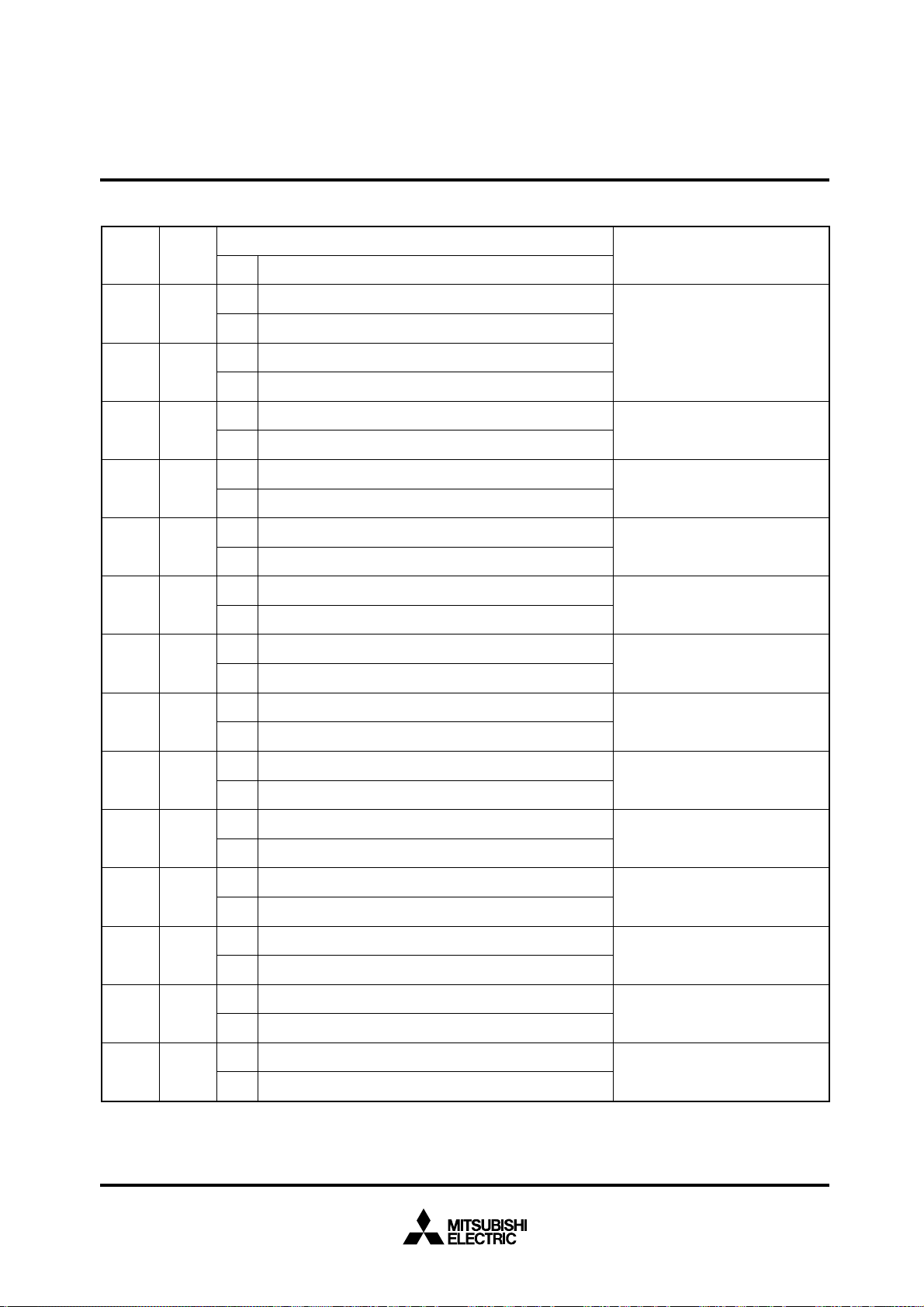

P0/BLNK0

16 P4

Port output

9P6

control circuit

10 P7

VERT

12

13 P1/R

15 P3/G

17 P5/B

14 P2

circuti

Polarity

19

switching

18

HOR

CPOUT

Polarity switching circuit

Clock oscillation

circuit for display

Input control circuit

H counter

switching circuit

Synchronous signal

Timing generator

circuit

Address control

circuit

Data control

detection circuit

Display location

register

Display control

Blinking circuit

control circuit

Reading address

Display RAM

circuit

Display control

Display character ROM Shift register

BLOCK DIAGRAM

415

CS

SCK

6

SIN

8

20

DD1VDD2

V

3

AC

2

11

SS

VIR

V

7

TCK

3

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

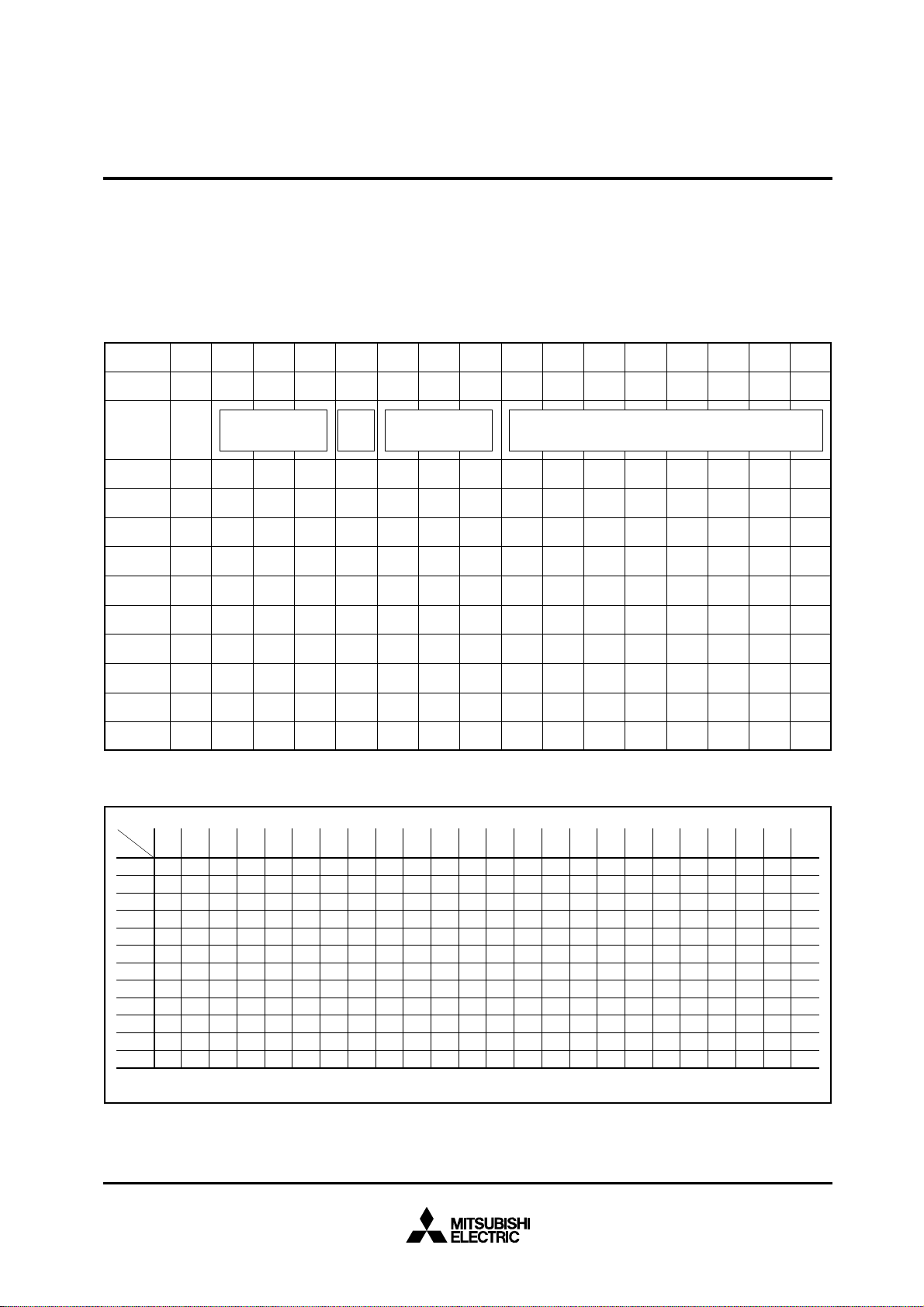

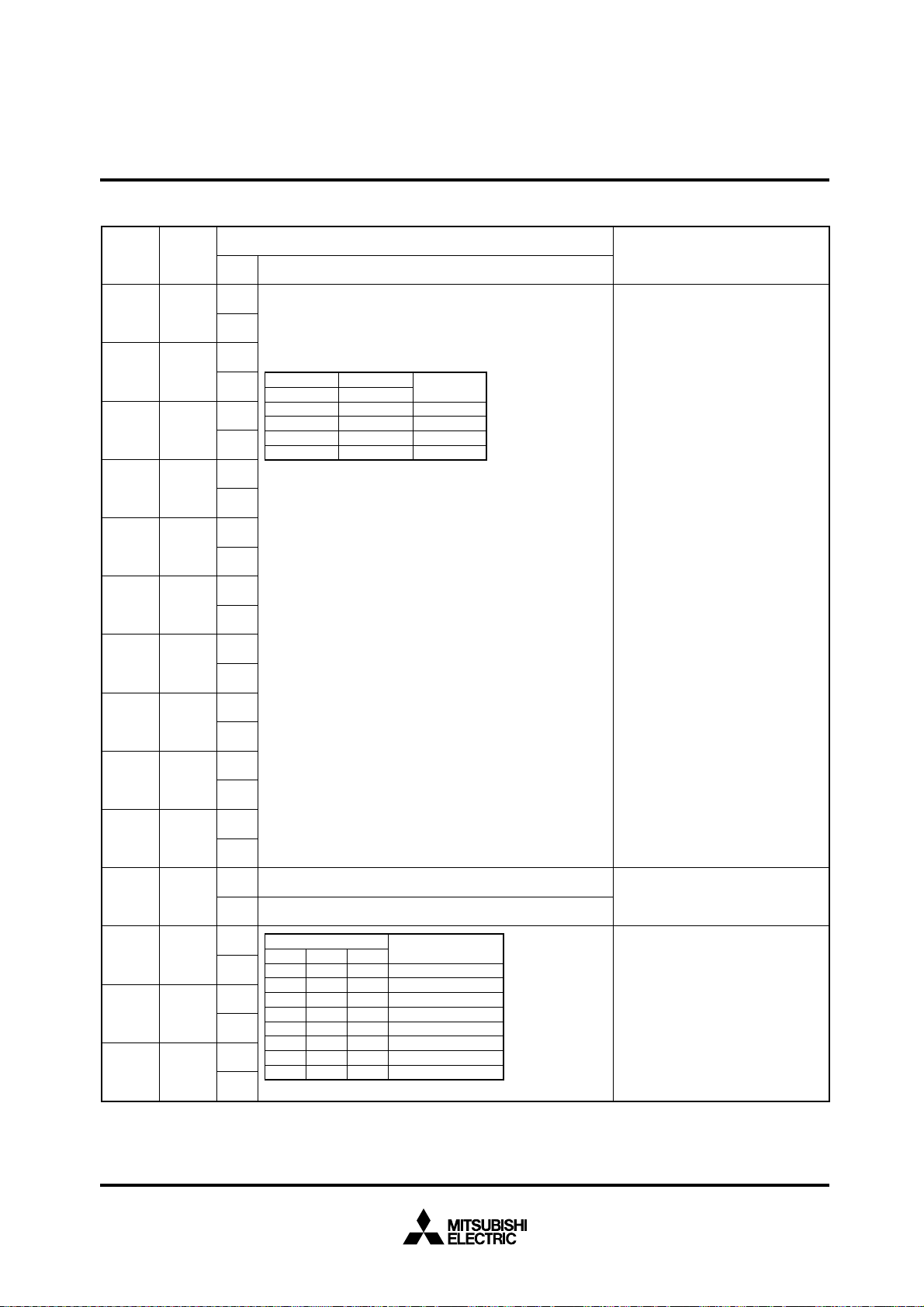

MEMORY CONSTITUTION

Address 00016 to 11F16 are assigned to the display RAM, address

120

16 to 12816 are assigned to the display control registers. The in-

ternal circuit is reset and all display control registers (address 120

to 12816) are set to “0” and display RAM (address 00016 to 11F16)

are set to “FF16” when the AC pin level is “L”.

Memory constitution is shown in Figure 1.

DAF DAE DAD DAC DAB DAA DA9 DA8 DA7 DA6 DA5 DA4 DA3 DA2 DA1 DA0

000

………

11F16

12016

12116

12216

12316

12416

12516

0 BB BG BR BLINK B G R C7 C6 C5 C4 C3 C2 C1 C0

16

………

0 BB BG BR BLINK B G R C7 C6 C5 C4 C3 C2 C1 C0

0 0 DIVS2 DIVS1 DIVS0 DIV10 DIV9 DIV8 DIV7 DIV6 DIV5 DIV4 DIV3 DIV2 DIV1 DIV0

0 0 PTD7 PTD6 PTD5 PTD4 PTD3 PTD2 PTD1 PTD0 PTC5 PTC4 PTC3 PTC2 PTC1 PTC0

00

0 0 TEST3 TEST2 TEST1 TEST0 VP9 VP8 VP7 VP6 VP5 VP4 VP3 VP2 VP1 VP0

0 0 TEST5 TEST4 DSP11 DSP10 DSP9 DSP8 DSP7 DSP6 DSP5 DSP4 DSP3 DSP2 DSP1 DSP0

00

__

Background

coloring

SPACE2 SPACE1 SPACE0

Blinking

TEST9 HP9 HP8 HP7 HP6 HP5 HP4 HP3 HP2 HP1 HP0

VSZ1H1 VSZ1H0 VSZ1L1 VSZ1L0

Character color

V1SZ1 V1SZ0 LIN9 LIN8 LIN7 LIN6 LIN5 LIN4 LIN3 LIN2

SCREEN CONSTITUTION

The screen lines and rows are determined from each address of the

display RAM. The screen constitution is shown in Figure 2.

16

Character code

12616

12716

12816

00

0 0 HSZ21 HSZ20 HSZ11 HSZ10

00

Fig. 1 Memory constitution

Row

Line

123456789101112131415161718192021222324

1

0001600116002160031600416005160061600716008160091600A1600B1600C1600D1600E1600F1601016011160121601316014160151601616017

018160191601A1601B1601C1601D1601E1601F160201602116022160231602416025160261602716028160291602A1602B1602C1602D1602E1602F

2

0301603116032160331603416035160361603716038160391603A1603B1603C1603D1603E1603F1604016041160421604316044160451604616047

3

048160491604A1604B1604C1604D1604E1604F160501605116052160531605416055160561605716058160591605A1605B1605C1605D1605E1605F

4

0601606116062160631606416065160661606716068160691606A1606B1606C1606D1606E1606F1607016071160721607316074160751607616077

5

078160791607A1607B1607C1607D1607E1607F160801608116082160831608416085160861608716088160891608A1608B1608C1608D1608E1608F

6

0901609116092160931609416095160961609716098160991609A1609B1609C1609D1609E1609F160A0160A1160A2160A3160A4160A5160A6160A7

7

0A8160A9160AA160AB160AC160AD160AE160AF160B0160B1160B2160B3160B4160B5160B6160B7160B8160B9160BA160BB160BC160BD160BE160BF

8

0C0160C1160C2160C3160C4160C5160C6160C7160C8160C9160CA160CB160CC160CD160CE160CF160D0160D1160D2160D3160D4160D5160D6160D7

9

10

0D8160D9160DA160DB160DC160DD160DE160DF160E0160E1160E2160E3160E4160E5160E6160E7160E8160E9160EA160EB160EC160ED160EE160EF

11

0F0160F1160F2160F3160F4160F5160F6160F7160F8160F9160FA160FB160FC160FD160FE160FF1610016101161021610316104161051610616107

108161091610A1610B1610C1610D1610E1610F161101611116112161131611416115161161611716118161191611A1611B1611C1611D1611E1611F

12

* The hexadecimal numbers in the boxes show the display RAM address.

Fig. 2 Screen constitution

VSZ2H1 VSZ2H0 VSZ2L1 VSZ2L0 V18SZ1 V18SZ0

BETA14

TEST8 TEST7 TEST6 FB FG FR RB RG RR

BLINK2 BLINK1 BLINK0 DSPON

STOP

RAMERS

LIN17 LIN16 LIN15 LIN14 LIN13 LIN12 LIN11 LIN10

SYAD BLK1 BLK0 POLH POLV

VMASK__B/F BCOL

16

16

16

16

16

16

16

16

16

16

16

16

4

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

REGISTERS DESCRIPTION

(1) Address 12016

RegisterDA

Status

0

0

DIV0

Set multiply value (frequency value) of horizontal synchronous frequency.

Function

Display frequency is computed as

shown below.

Remarks

1

FOSC = fH × N1

Contents

1

DIV1

1

0

2

DIV2

1

0

10

N1 = (DIVn × 2

Σ

n = 0

N1: frequency value

n

)

0

3

DIV3

1

F

OSC [MHz] : Display frequency

H [kHz] : Horizontal synchronous

f

signal frequency to HOR

pin.

N1 : Shown left

Set display frequency F

OSC to within

30MHz to 80MHz range.

When display frequency F

OSC, set fre-

quency value N2 in association with

DIVS0 and DIVS1.

0

4

DIV4

1

0

5

DIV5

1

0

6

DIV6

1

7

DIV7

1

0

0

8

DIV8

1

0

9

DIV9

1

0

A

DIV10

1

0

B

DIVS0

C

DIVS1

D

DIVS2

Set frequency value N2

1

0

1

0

1

DIVS Frequency

1

0

0

1

1

It should be fixed to “0”.

Can not be used.

0

0

1

0

1

value N2

Division into 2

Division into 3

Division into 4

Do not set

__

Note: The mark ⁄ around the status value means the reset status by the “L” level is input to AC pin.

Set frequency value N2 in association

with display frequency range.

Display frequency

55 ~ 80

40 ~ 55

30 ~ 40

Frequency value N2

Division into 2

Division into 3

Division into 4

5

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

(2) Address 121

RegisterDA

0

PTC0

1

PTC1

2

PTC2

3

PTC3

4

PTC4

5

PTC5

6

16

PTD0

Contents

Status

0

P0 output (port P0). Port data is set by PTD0.

1

BLNK0 output. Polarity is set by PTD0.

0

P1 output (port P1). Port data is set by PTD1.

1

R signal output. Polarity is set by PTD1.

0

P2 output (port P2). Port data is set by PTD2.

1

Do not set.

0

P3 output (port P3). Port data is set by PTD3.

1

G signal output. Polarity is set by PTD3.

0

P4 output (port P4). Port data is set by PTD4.

1

Do not set.

0

P5 output (port P5). Port data is set by PTD5.

1

B signal output. Polarity is set by PTD5.

0

“L” output (P0 output) or negative polarity output (BLNK0 output).

1

“H” output (P0 output) or positive polarity output (BLNK0 output).

Function

Remarks

BLNK0 outputs blanking signal.

Blanking status is determined by BLK0,

BLK1, and DSP0 to DSP11 settings.

P0 pin data control.

0

7

PTD1

8

PTD2

9

PTD3

A

PTD4

B

PTD5

C

PTD6

D

PTD7

“L” output (P1 output) or negative polarity output (R signal output).

1

“H” output (P1 output) or positive polarity output (R signal output).

0

“L” output (P2 output).

1

“H” output (P2 output).

0

“L” output (P3 output) or negative polarity output (G signal output).

1

“H” output (P3 output) or positive polarity output (G signal output).

0

“L” output (P2 output).

1

“H” output (P2 output).

0

“L” output (P5 output) or negative polarity output (B signal output).

1

“H” output (P5 output) or positive polarity output (B signal output).

0

“L” output (P6 output).

1

“H” output (P6 output).

0

“L” output (P7 output).

1

“H” output (P7 output).

P1 pin data control.

P2 pin exclusive port output state control.

P3 pin data control.

P4 pin exclusive port output state control.

P5 pin data control.

P6 pin exclusive port output state control.

P7 pin exclusive port output state control.

6

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

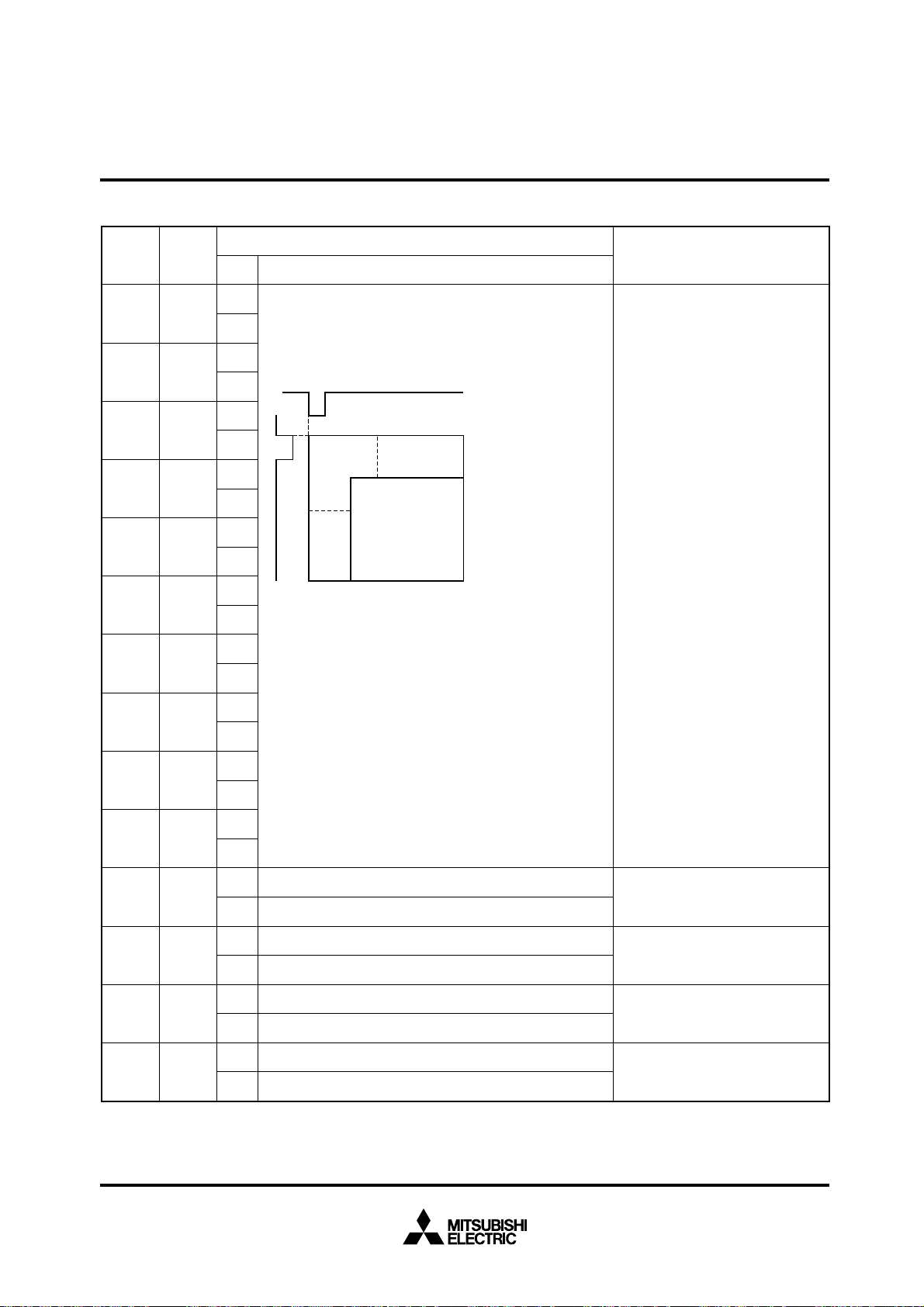

(3) Address 12216

Register

Status

0

0

1

2

3

HP0

(LSB)

HP1

HP2

HP3

If HS is the horizontal display start location,

9

1

HS = T × (

0

1

HSZ11

HSZ21

0

1

1000 settings are possible.

0

n

2

HPn + N).

Σ

n = 0

T: The cycle of display frequency

HSZ10

0

0

1

1

HSZ20

Function

Horizontal display start location is

specified using the 10 bits from HP9

to HP0.

Note: HP9 to 0 = (0000000000

(0000010111

N

0

1

0

1

6

7

8

9

RemarksDA

2) and

2) setting is forbidden

1

0

Contents

4

HP4

1

0

5

HP5

1

0

6

HP6

1

7

HP7

1

0

0

8

HP8

1

9

A

B

C

D

HP9

(MSB)

TEST9

SPACE0

SPACE1

SPACE2

0

1

0

It should be fixed to “0”.

1

Can not be used.

0

1

0

1

0

1

SPACE

2

0

0

0

0

1

1

1

1

0

1

0

0

1

0

0

1

1

1

0

0

1

0

0

1

1

1

Í represents one line worth of spaces.

Number of Lines and Space

(Í represents space)

12

1 Í 10 Í 1

2 Í 8 Í 2

3 Í 6 Í 3

4 Í 4 Í 4

5 Í 2 Í 5

6 Í 6

6 Í Í 6

Leave one line worth of space in the vertical direction.

For example, 6 Í 6 indicates two sets

of 6 lines with a line of spaces between

lines 6 and 7.

A line is 18 × N horizontal scan lines.

N is determined by the character size in

the vertical direction as follows:

×1 N = 1 ×2 N = 2

×3 N = 3 ×4 N = 4

7

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

(4) Address 12316

Contents

RegisterDA

Status

0

0

1

VP0

(LSB)

VP1

If VS is the vertical display start location,

9

1

VS = H × (

0

H: Cycle with the horizontal synchronizing pulse

2

Σ

n = 0

n

VPn).

1023 settings are possible.

Function

The vertical start location is specified

using the 10 bits from VP9 to VP0.

VP9 to VP0 = (0000000000

forbidden.

Note 1: In case of B/F register is “0”.

Remarks

2) setting is

_

1

0

HOR

2

VP2

1

VP

0

3

4

VP3

VP4

0

VERT

HP

Character

displaying area

1

1

0

5

VP5

1

0

6

VP6

1

7

VP7

1

0

0

8

VP8

1

9

A

B

C

D

VP9

(MSB)

TEST0

TEST1

TEST2

TEST3

0

1

0

It should be fixed to “0”.

1

Can not be used.

0

It should be fixed to “0”.

1

Can not be used.

0

It should be fixed to “0”.

1

Can not be used.

0

It should be fixed to “0”.

1

Can not be used.

8

MITSUBISHI MICROCOMPUTERS

M35045-XXXSP/FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

(5) Address 124

RegisterDA

0

DSP0

1

DSP1

2

DSP2

3

DSP3

4

DSP4

5

DSP5

6

DSP6

16

Contents

Status

0

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

1

Blanking is in the display mode specified by except BLK0 and BLK1.

0

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

1

Blanking is in the display mode specified by except BLK0 and BLK1.

0

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

1

Blanking is in the display mode specified by except BLK0 and BLK1.

0

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

1

Blanking is in the display mode specified by except BLK0 and BLK1.

0

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

1

Blanking is in the display mode specified by except BLK0 and BLK1.

0

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

1

Blanking is in the display mode specified by except BLK0 and BLK1.

0

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

1

Blanking is in the display mode specified by except BLK0 and BLK1.

Function

Sets the display mode of line 1.

Sets the display mode of line 2.

Sets the display mode of line 3.

Sets the display mode of line 4.

Sets the display mode of line 5.

Sets the display mode of line 6.

Sets the display mode of line 7.

Remarks

7

DSP7

8

DSP8

9

DSP9

A

DSP10

B

DSP11

C

TEST4

D

TEST5

Note: Refer to DISPLAY FORM1.

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

Blanking is in the display mode specified by except BLK0 and BLK1.

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

Blanking is in the display mode specified by except BLK0 and BLK1.

Blanking is in the display mode specified by BLK0 and BLK1. (Note)

Blanking is in the display mode specified by except BLK0 and BLK1.

Blanking is in the display mode specified by BLK0 and BLK1.

Blanking is in the display mode specified by except BLK0 and BLK1.

Blanking is in the display mode specified by BLK0 and BLK1.

Blanking is in the display mode specified by except BLK0 and BLK1.

It should be fixed to “0”.

Can not be used.

It should be fixed to “0”.

Can not be used.

Sets the display mode of line 8.

Sets the display mode of line 9.

Sets the display mode of line 10.

Sets the display mode of line 11.

Sets the display mode of line 12.

9

Loading...

Loading...