Mitsubishi M34514M8-XXXFP, M34514M6-XXXFP, M34514E8FP, M34513M8-XXXFP, M34513M6-XXXFP Datasheet

...

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

DESCRIPTION

The 4513/4514 Group is a 4-bit single-chip microcomputer designed with CMOS technology. Its CPU is that of the 4500 series

using a simple, high-speed instruction set. The computer is

equipped with serial I/O, four 8-bit timers (each timer has a reload

register), and 10-bit A-D converter.

The various microcomputers in the 4513/4514 Group include variations of the built-in memory type and package as shown in the

table below.

FEATURES

●Minimum instruction execution time ................................ 0.75 µs

(at 4.0 MHz oscillation frequency, in high-speed mode, VDD = 4.0

V to 5.5 V)

●Supply voltage

• Middle-speed mode

...... 2.5 V to 5.5 V (at 4.2 MHz oscillation frequency, for Mask

ROM version and One Time PROM version)

...... 2.0 V to 5.5 V (at 3.0 MHz oscillation frequency, for Mask

ROM version)

(Operation voltage of A-D conversion: 2.7 V to 5.5 V)

• High-speed mode

...... 4.0 V to 5.5 V (at 4.2 MHz oscillation frequency, for Mask

ROM version and One Time PROM version)

...... 2.5 V to 5.5 V (at 2.0 MHz oscillation frequency, for Mask

ROM version and One Time PROM version)

...... 2.0 V to 5.5 V (at 1.5 MHz oscillation frequency, for Mask

ROM version)

(Operation voltage of A-D conversion: 2.7 V to 5.5 V)

●Timers

Timer 1...................................... 8-bit timer with a reload register

Timer 2...................................... 8-bit timer with a reload register

Timer 3...................................... 8-bit timer with a reload register

Timer 4...................................... 8-bit timer with a reload register

●Interrupt ........................................................................ 8 sources

●Serial I/O....................................................................... 8 bit-wide

●A-D converter .................. 10-bit successive comparison method

●Voltage comparator........................................................2 circuits

●Watchdog timer ................................................................. 16 bits

●Voltage drop detection circuit

●Clock generating circuit (ceramic resonator)

●LED drive directly enabled (port D)

APPLICATION

Electrical household appliance, consumer electronic products, office automation equipment, etc.

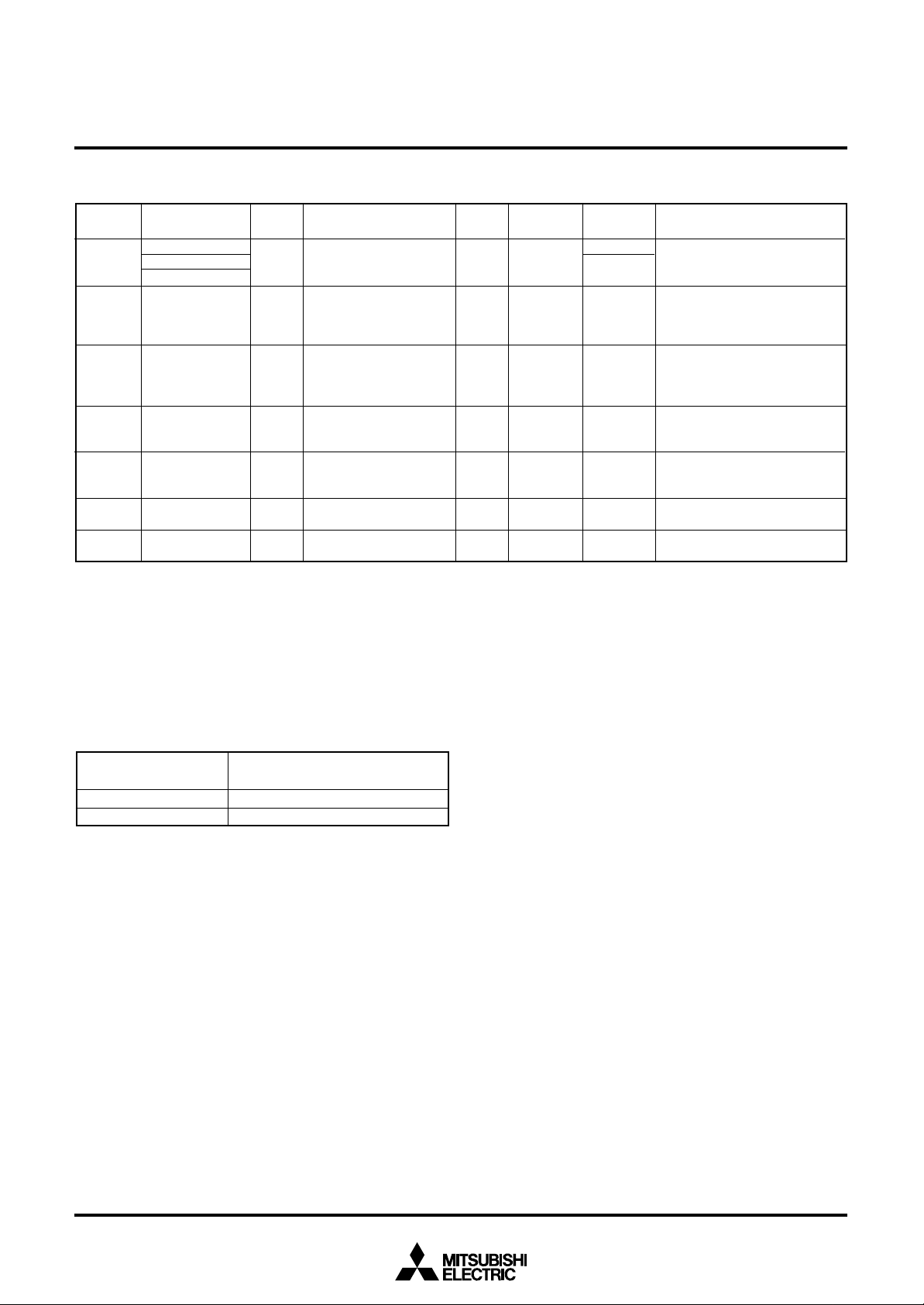

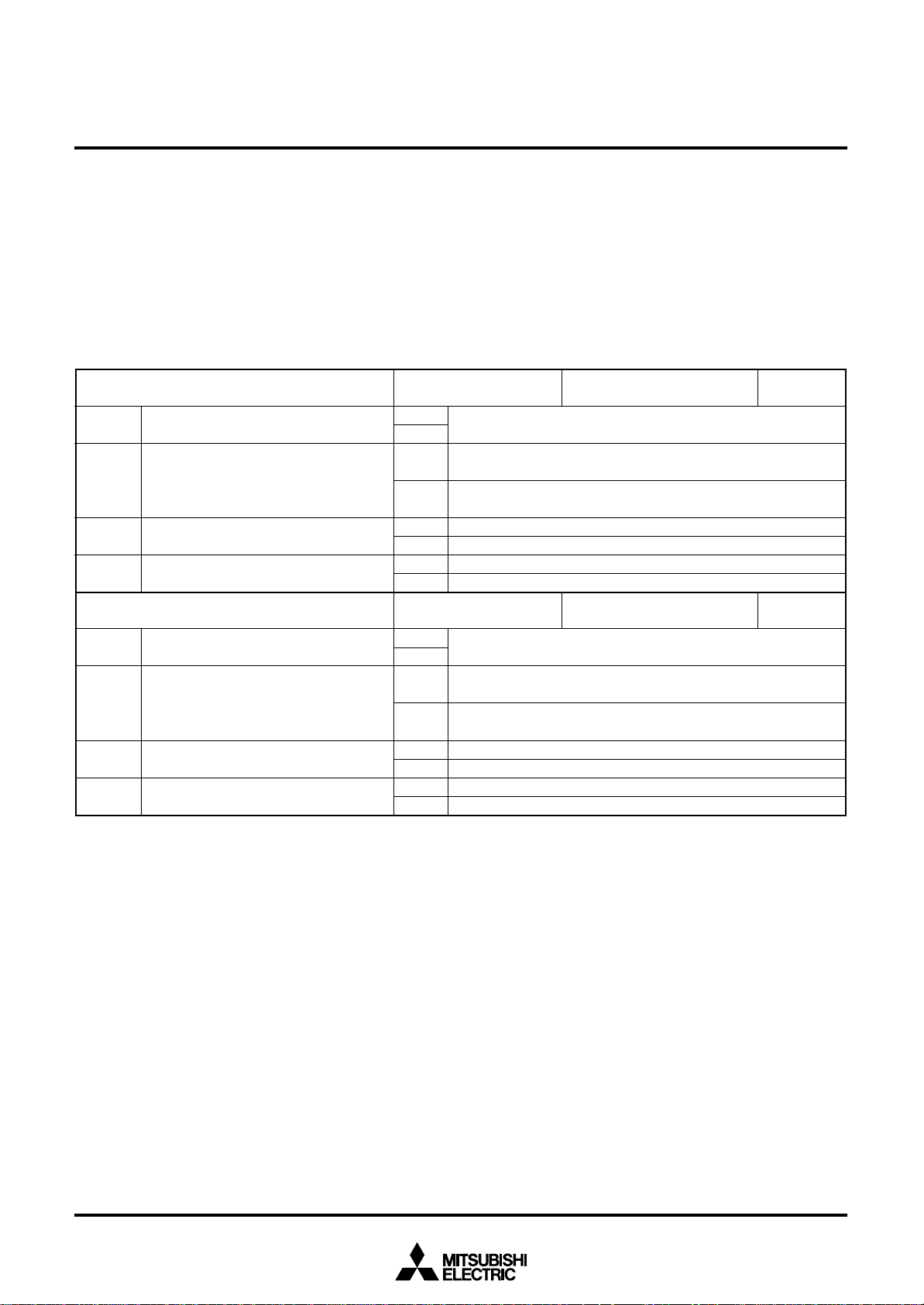

Product

M34513M2-XXXSP/FP

M34513M4-XXXSP/FP

M34513E4SP/FP (Note)

M34513M6-XXXFP

M34513M8-XXXFP

M34513E8FP (Note)

M34514M6-XXXFP

M34514M8-XXXFP

M34514E8FP (Note)

Note: shipped in blank

ROM (PROM) size

(✕ 10 bits)

2048 words

4096 words

4096 words

6144 words

8192 words

8192 words

6144 words

8192 words

8192 words

RAM size

(✕ 4 bits)

128 words

256 words

256 words

384 words

384 words

384 words

384 words

384 words

384 words

Package

SP: 32P4B FP: 32P6U-A

SP: 32P4B FP: 32P6U-A

SP: 32P4B FP: 32P6U-A

32P6U-A

32P6U-A

32P6U-A

42P2R-A

42P2R-A

42P2R-A

ROM type

Mask ROM

Mask ROM

One Time PROM

Mask ROM

Mask ROM

One Time PROM

Mask ROM

Mask ROM

One Time PROM

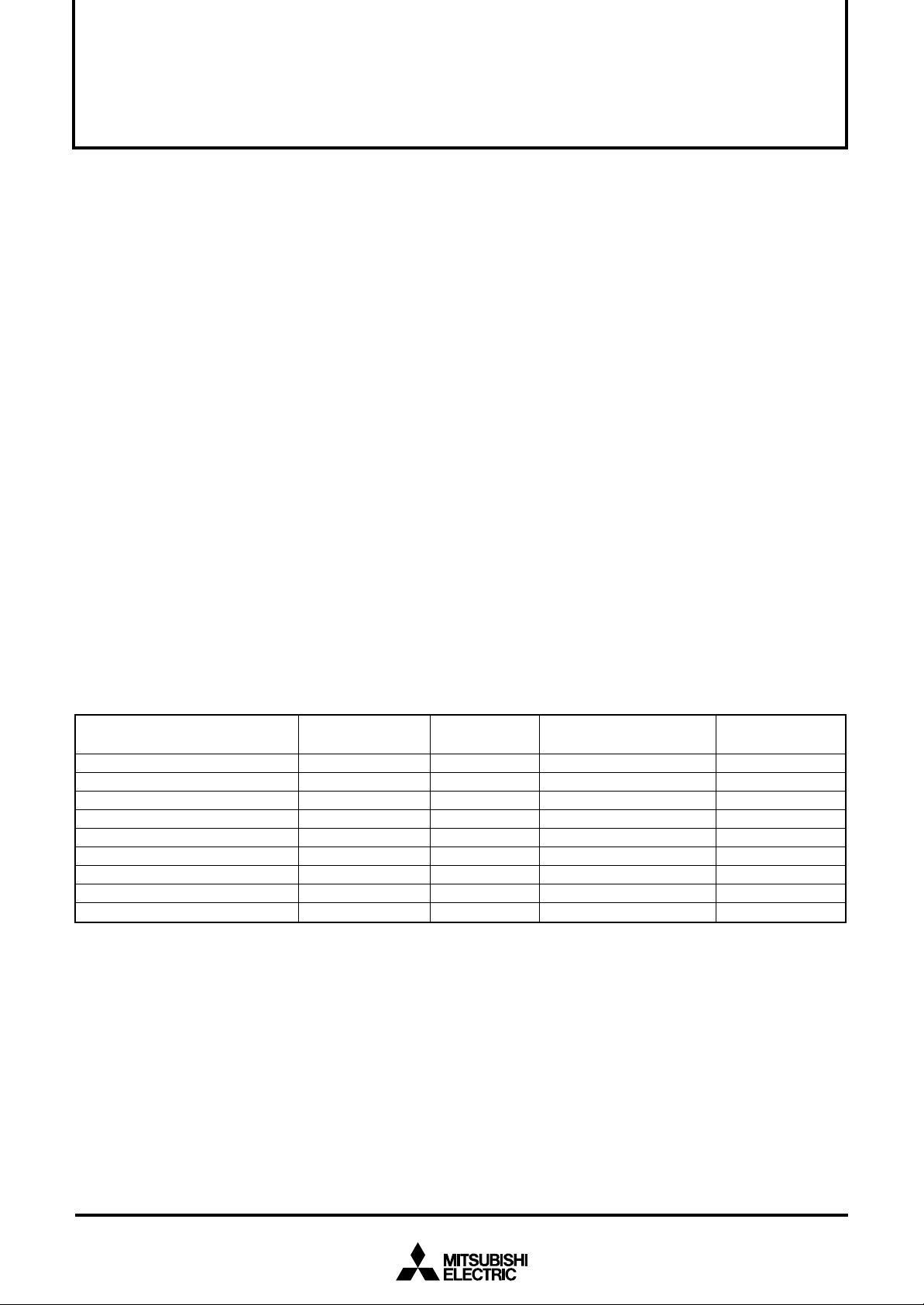

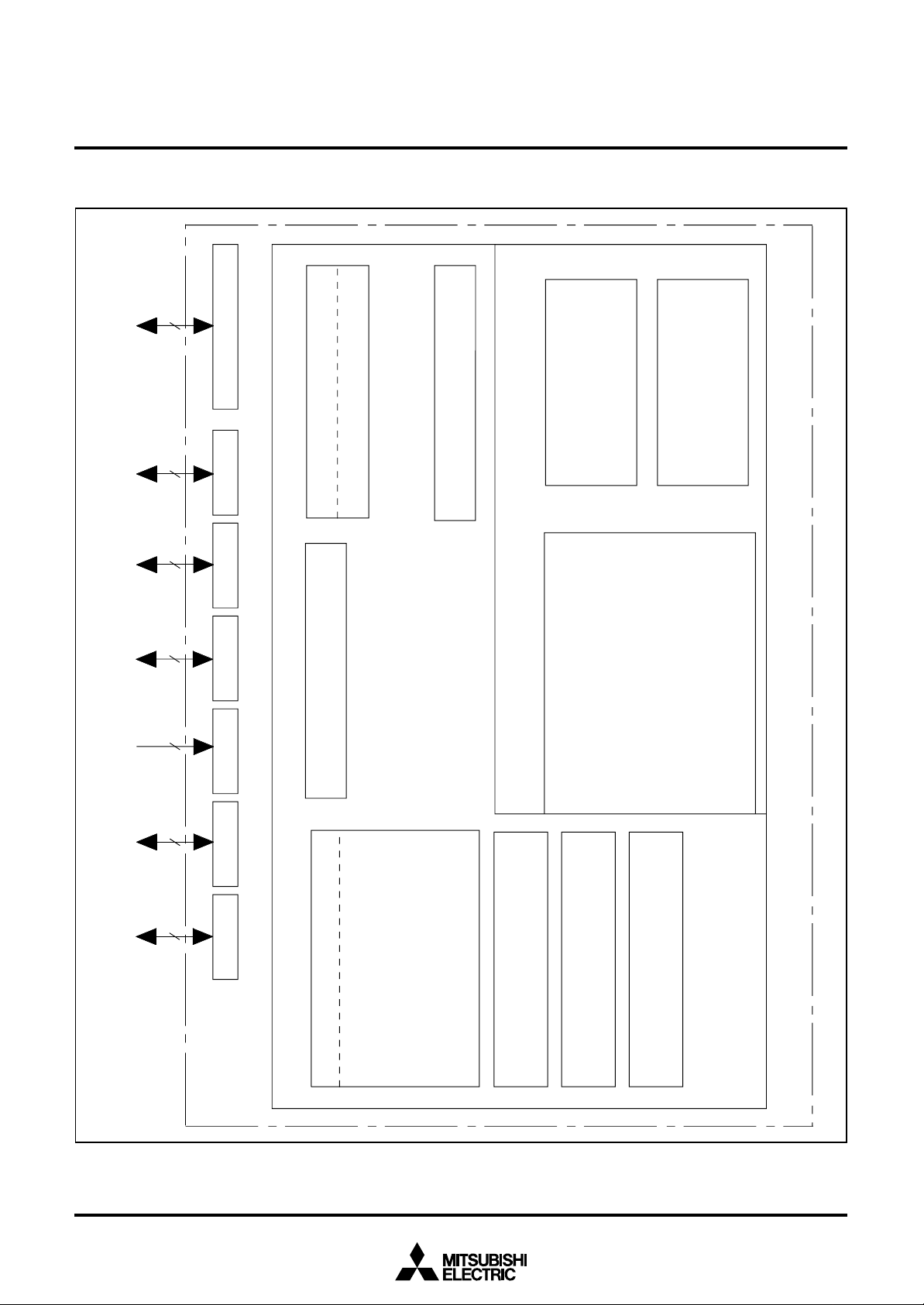

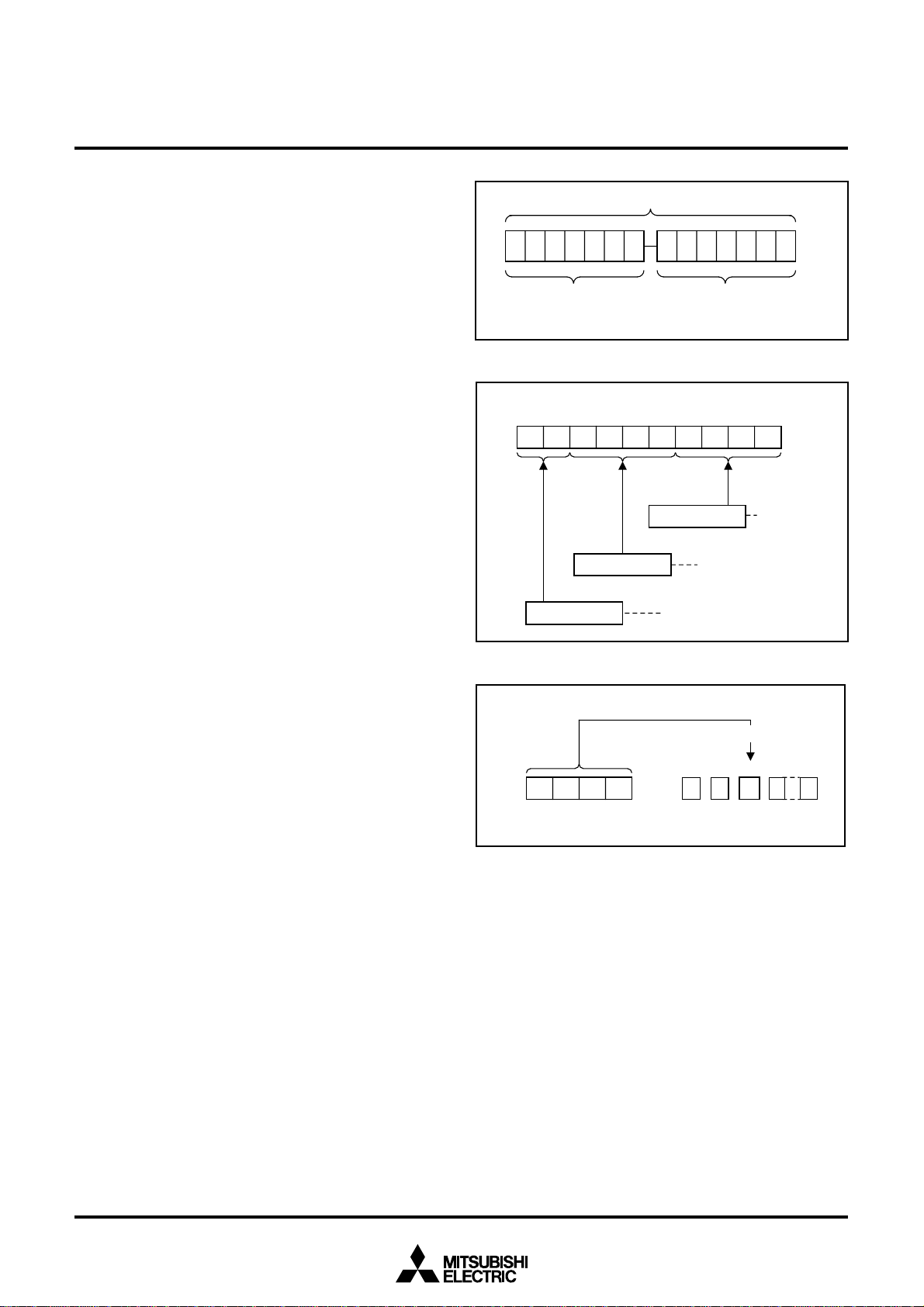

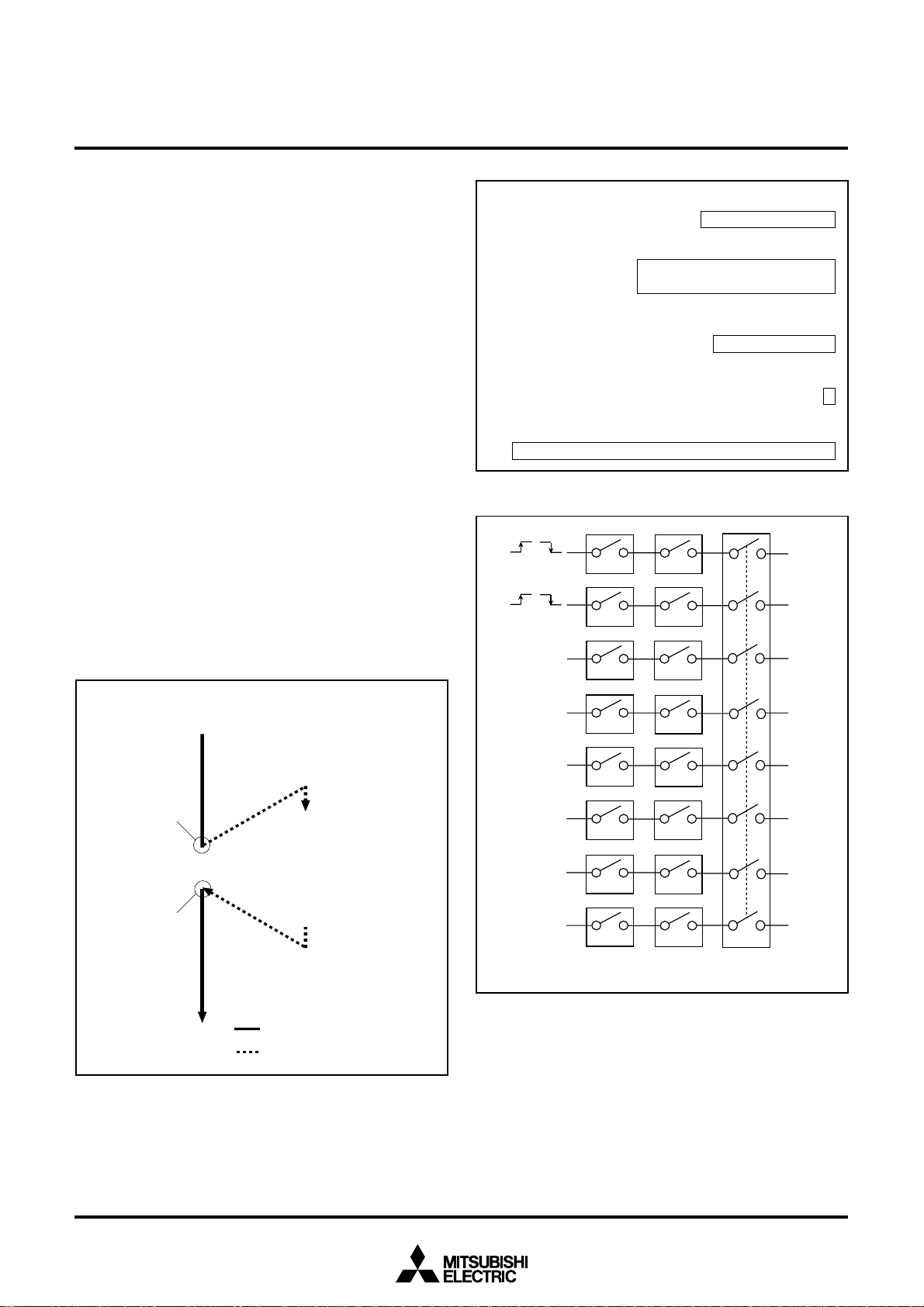

PIN CONFIGURATION (TOP VIEW) 4513 Group

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

D

D

D

D

D

D

D6/ C N T R 0

D

7

/ C N T R 1

P 2

0

/ S

C K

P 21/ S

O U T

P22/S

IN

R E S E T

C N V

S S

X

O U T

X

I N

V

S S

1

0

2

1

3

2

M

M

4

3

5

4

6

5

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

3 4 5 1 3 E 4 S

P

3 4 5 1 3 M x - X X X S

P

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

P1

3

P1

2

P1

1

P1

0

P0

3

P0

2

P0

1

P0

0

A

IN3

/CMP1+

A

IN2

/CMP1-

A

IN1

/CMP0+

A

IN0

/CMP0P31/INT1

P30/INT0

VDCE

DD

V

O u t l i n e 3 2 P 4 B

D6/ C N T R

D7/ C N T R

P 20/ S

P 21/ S

O U T

P22/S

3

2

1

0

1

P

D

D

V

1

P

62

51

E

V

D C

I N T

3

0

P

5

24

P 0

2

23

P 0

1

22

P 0

0

21

A

I N 3

/ C M P 1 +

20

A

I N 2

/ C M P 1 -

19

A

I N 1

/ C M P 0 +

18

A

I N 0

/ C M P 0 -

17

P 3

1

/ I N T 1

6

0

/

0

3

P

1

T

O

X

92

82

21

31

N

I

X

1

P

S

S

V

72

41

D2D1D0P

3

23

13

02

1

D

3

2

D

4

3

D

5

M 3 4 5 1 3 M x - X X X F P

4

0

5

C K

1

6

7

8

IN

M 3 4 5 1 3 E x F P

9

1

01

11

T

S

S

V

U

R

E S E

C

N

O u t l i n e 3 2 P 6 U - A

2

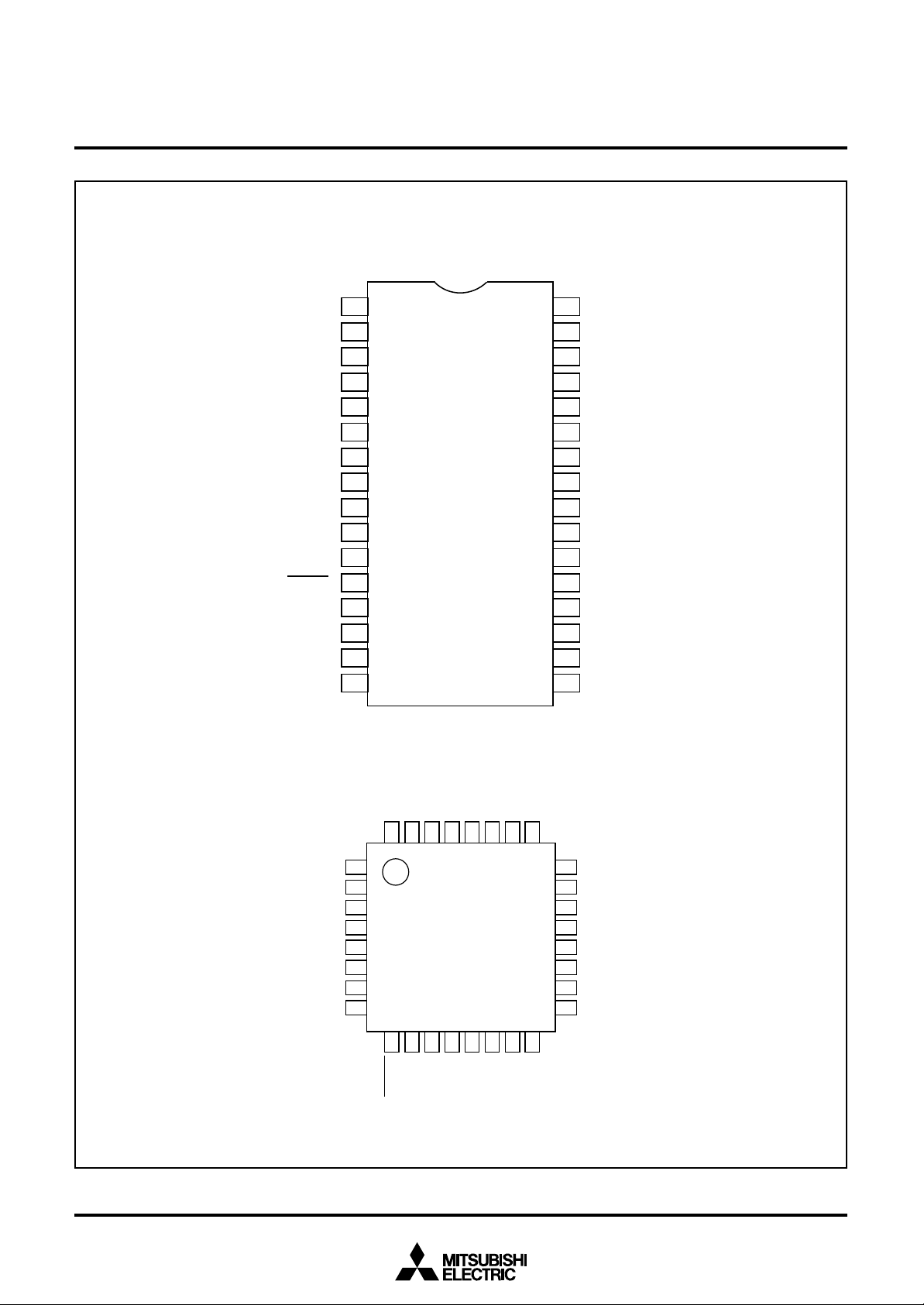

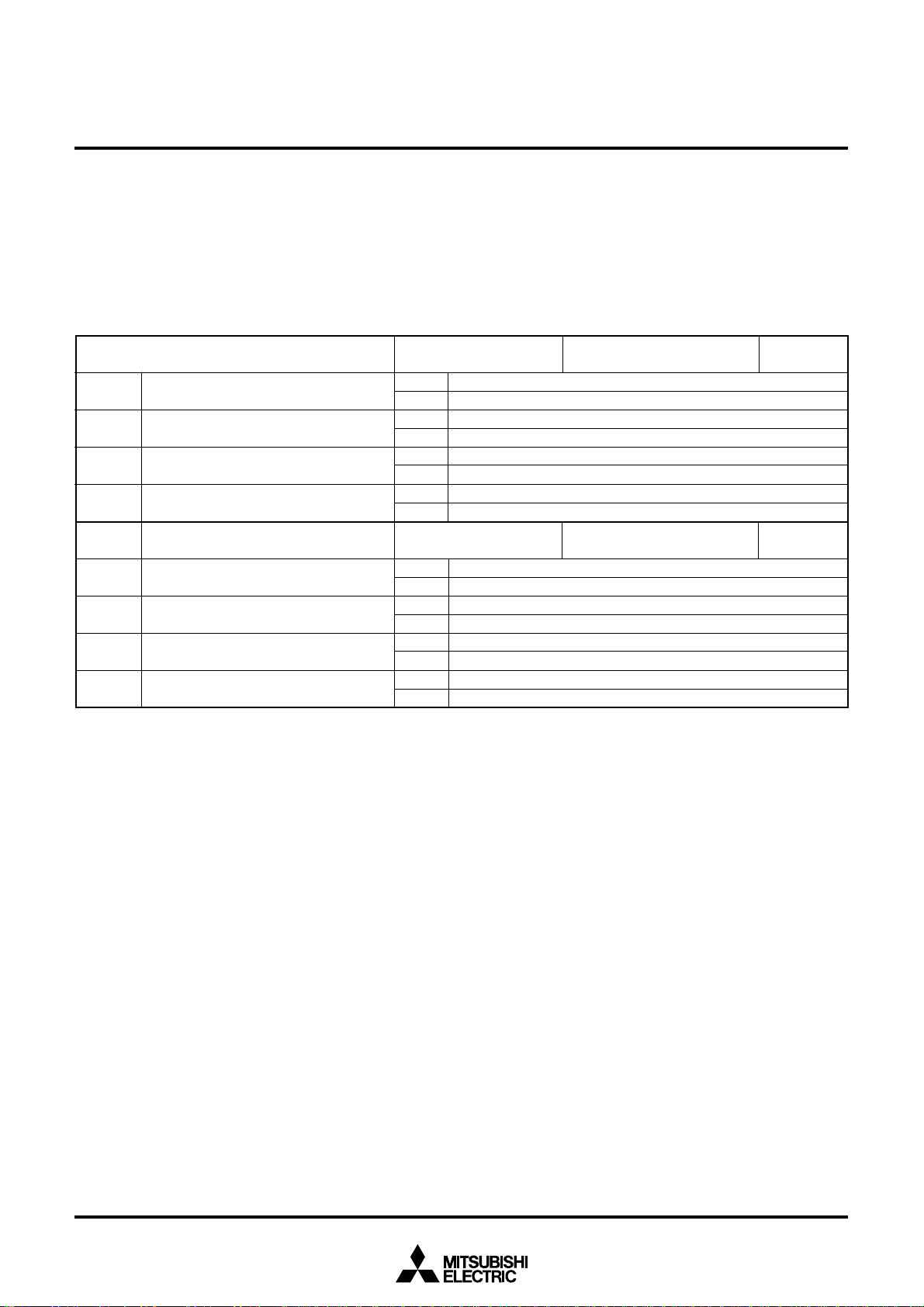

PIN CONFIGURATION (TOP VIEW) 4514 Group

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

P1

D

D

D

D

D

D

D6/CNTR0

7

/CNTR1

D

P5

P5

P5

P5

P20/S

CK

1/SOUT

P2

P22/S

IN

RESET

CNV

SS

X

OUT

X

IN

V

SS

1

3

2

0

3

1

4

2

5

3

6

4

7

5

8

9

10

0

11

1

12

2

13

3

14

15

16

17

18

19

20

21

M34514E8FP

M34514Mx-XXXFP

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

P1

2

P1

1

P1

0

P0

3

P0

2

P0

1

P0

0

P43/A

P42/A

P41/A

P40/A

A

IN3

A

IN2

A

IN1

A

IN0

P3

3

P3

2

P3

1

/INT1

P3

0

/INT0

VDCE

DD

V

IN7

IN6

IN5

IN4

/CMP1+

/CMP1/CMP0+

/CMP0-

Outline 42P2R-A

3

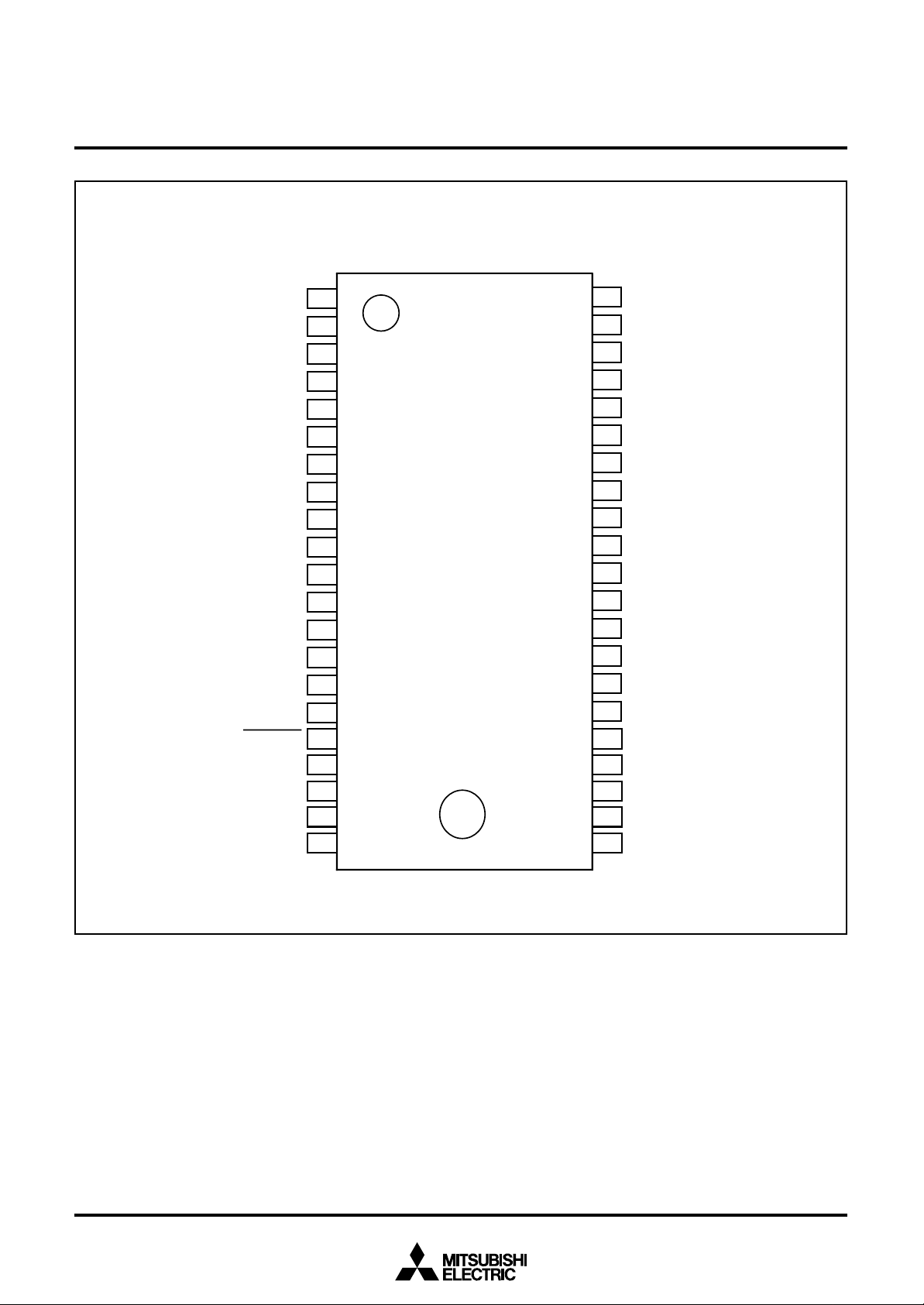

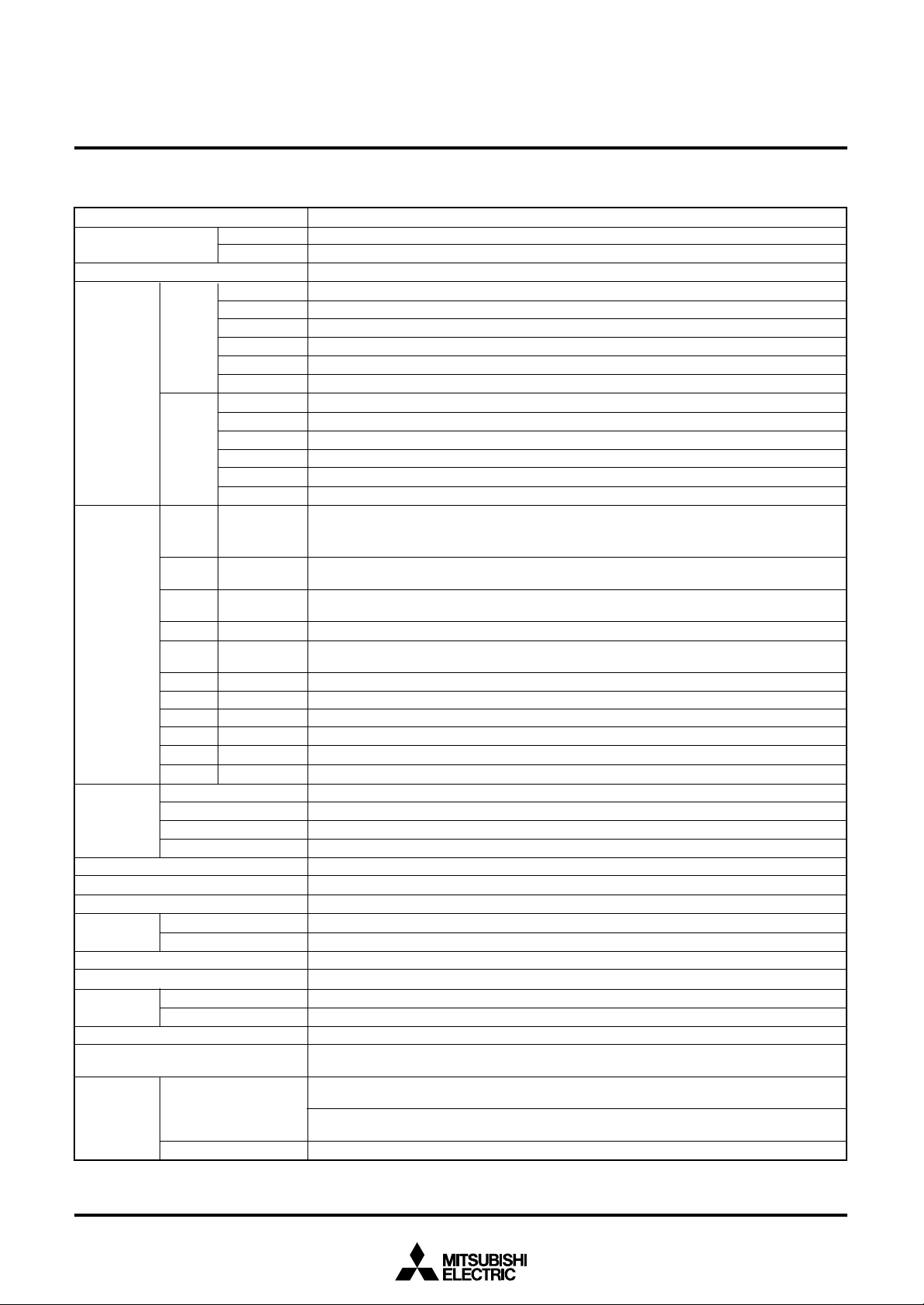

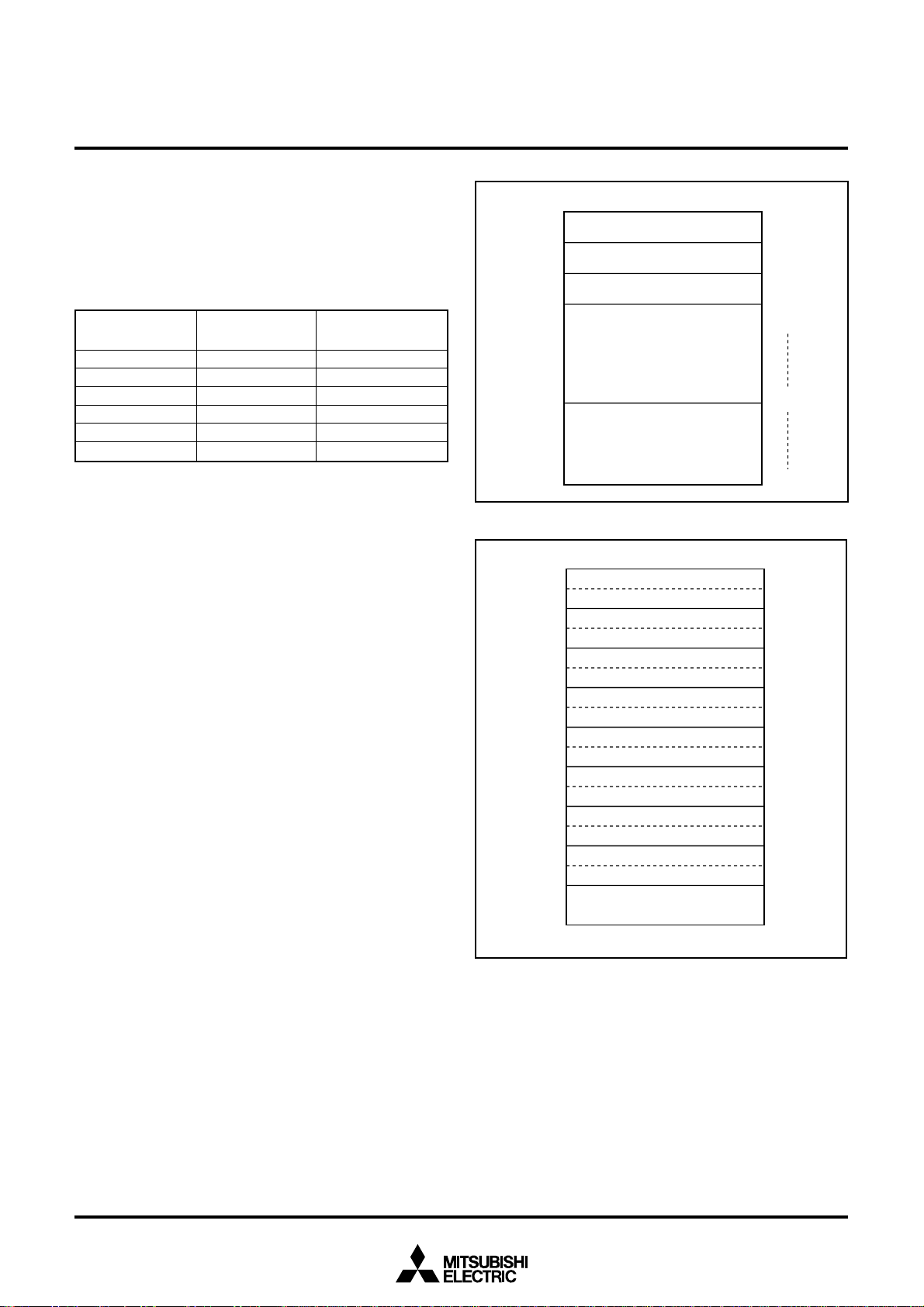

BLOCK DIAGRAM (4513 Group)

V

o l t a g e d r o p d e t e c t i o n c i r c u i

t

S

e r i a l I /

O

(

8 b i t s

✕

1

)

o

l

t

a

g

e

c

o

m

p

a

r

a

t

o

r

(

2 c i r c u i t s

)

X

I

N

—

X

O

U

T

I

/ O p o r

t

n

t

e

r

n

a

l

p

e

r

i

p

h

e

r

a

l

f

u

n

c

t

i

o

n

s

T

i m e

r

S

y s t e m c l o c k g e n e r a t i n g c i r c u i

t

W

a t c h d o g t i m e

r

(

1 6 b i t s

)

e

m

o

r

y

R

O

M

2

0 4 8 , 4 0 9 6 , 6 1 4 4 , 8 1 9

2

w

o r d s

✕

1 0 b i t

s

R

A

M

1

2 8 , 2 5 6 , 3 8 4 w o r d s

✕

4 b i t

s

4

5 0 0 S e r i e s

C

P U c o r

e

A

L U ( 4 b i t s

)

R

e g i s t e r A ( 4 b i t s ) R e g i s t e r B ( 4 b i t s

)

R

e g i s t e r D ( 3 b i t s ) R e g i s t e r E ( 8 b i t s

)

S

t a c k r e g i s t e r S K ( 8 l e v e l s

)

I

n t e r r u p t s t a c k r e g i s t e r S D P ( 1 l e v e l

)

T

i m e r 1 ( 8 b i t s

)

T

i m e r 2 ( 8 b i t s

)

T

i m e r 3 ( 8 b i t s

)

T

i m e r 4 ( 8 b i t s

)

A

- D c o n v e r t e

r

(

1

0

b

i

t

s

✕

4 c h

)

P

o r t

D

P

o r t P

3

P

o r t P

2

P

o r t P

1

P

o r t P

0

4

4

2

8

3

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

4

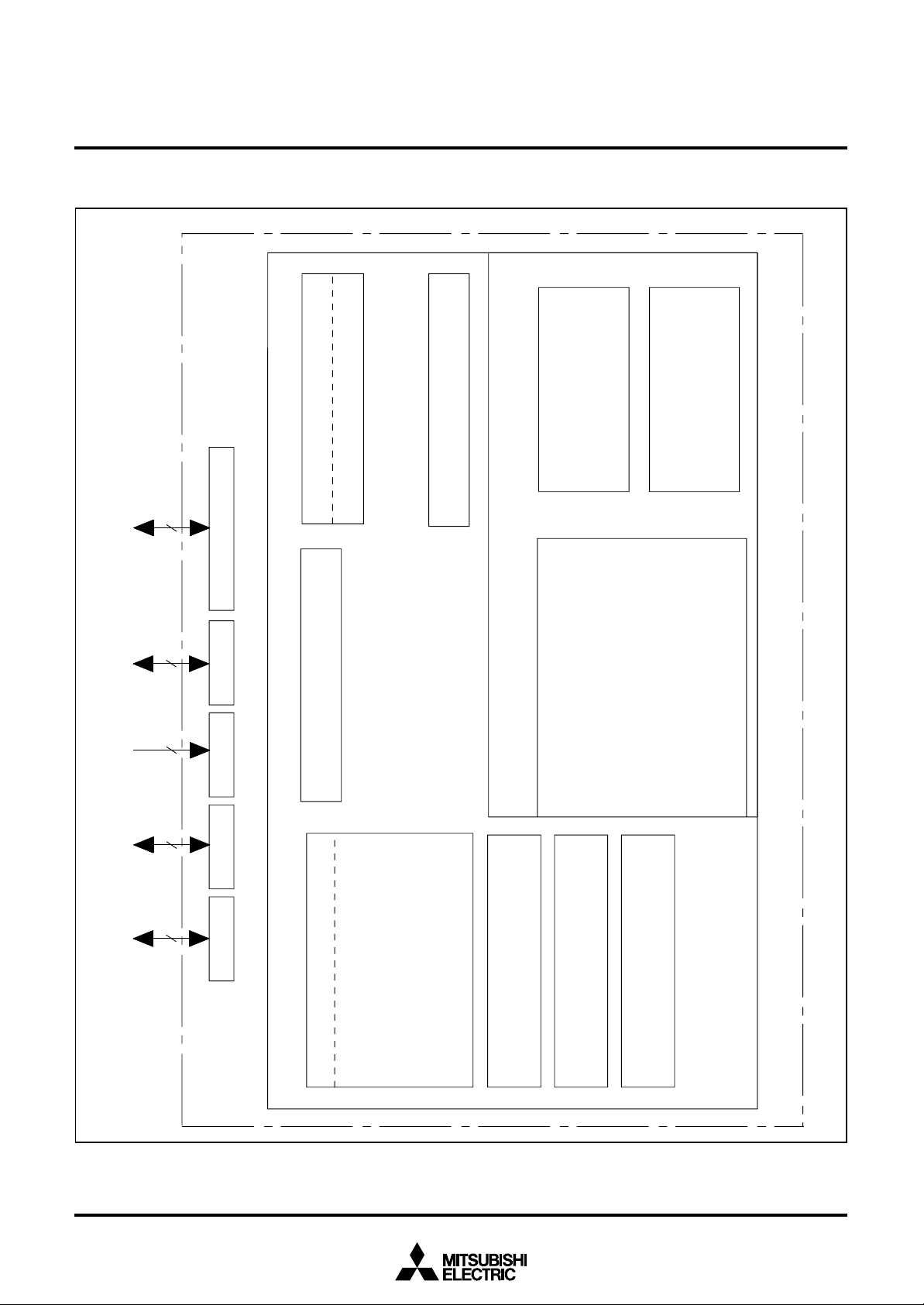

BLOCK DIAGRAM (4514 Group)

o

l

t

a

g

e

d

r

o

p

d

e

t

e

c

t

i

o

n

c

i

r

c

u

i

t

S

e r i a l I /

O

(

8 b i t s

✕

1

)

o

l

t

a

g

e

c

o

m

p

a

r

a

t

o

r

(

2 c i r c u i t s

)

X

I

N

—

X

O

U

T

I

/ O p o r

t

I

n t e r n a l p e r i p h e r a l f u n c t i o n

s

T

i m e

r

y

s

t

e

m

c

l

o

c

k

g

e

n

e

r

a

t

i

n

g

c

i

r

c

u

i

t

W

a t c h d o g t i m e

r

(

1 6 b i t s

)

M

e m o r

y

R

O

M

6

1

4

4

,

8

1

9

2

w

o

r

d

s

✕

1

0

b

i

t

s

R

A

M

3

8 4 w o r d s

✕

4 b i t

s

4

5 0 0 S e r i e s

C

P U c o r

e

A

L U ( 4 b i t s

)

R

e g i s t e r A ( 4 b i t s ) R e g i s t e r B ( 4 b i t s

)

R

e g i s t e r D ( 3 b i t s ) R e g i s t e r E ( 8 b i t s

)

S

t a c k r e g i s t e r S K ( 8 l e v e l s

)

I

n t e r r u p t s t a c k r e g i s t e r S D P ( 1 l e v e l

)

T

i m e r 1 ( 8 b i t s

)

T

i m e r 2 ( 8 b i t s

)

T

i m e r 3 ( 8 b i t s

)

T

i m e r 4 ( 8 b i t s

)

A

- D c o n v e r t e

r

(

1

0

b

i

t

s

✕

8 c h

)

o

r

t

D

P

o r t P

3

o

r

t

P

2

o

r

t

P

1

o

r

t

P

0

o

r

t

P

5

o

r

t

P

4

4

4

4

4

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

5

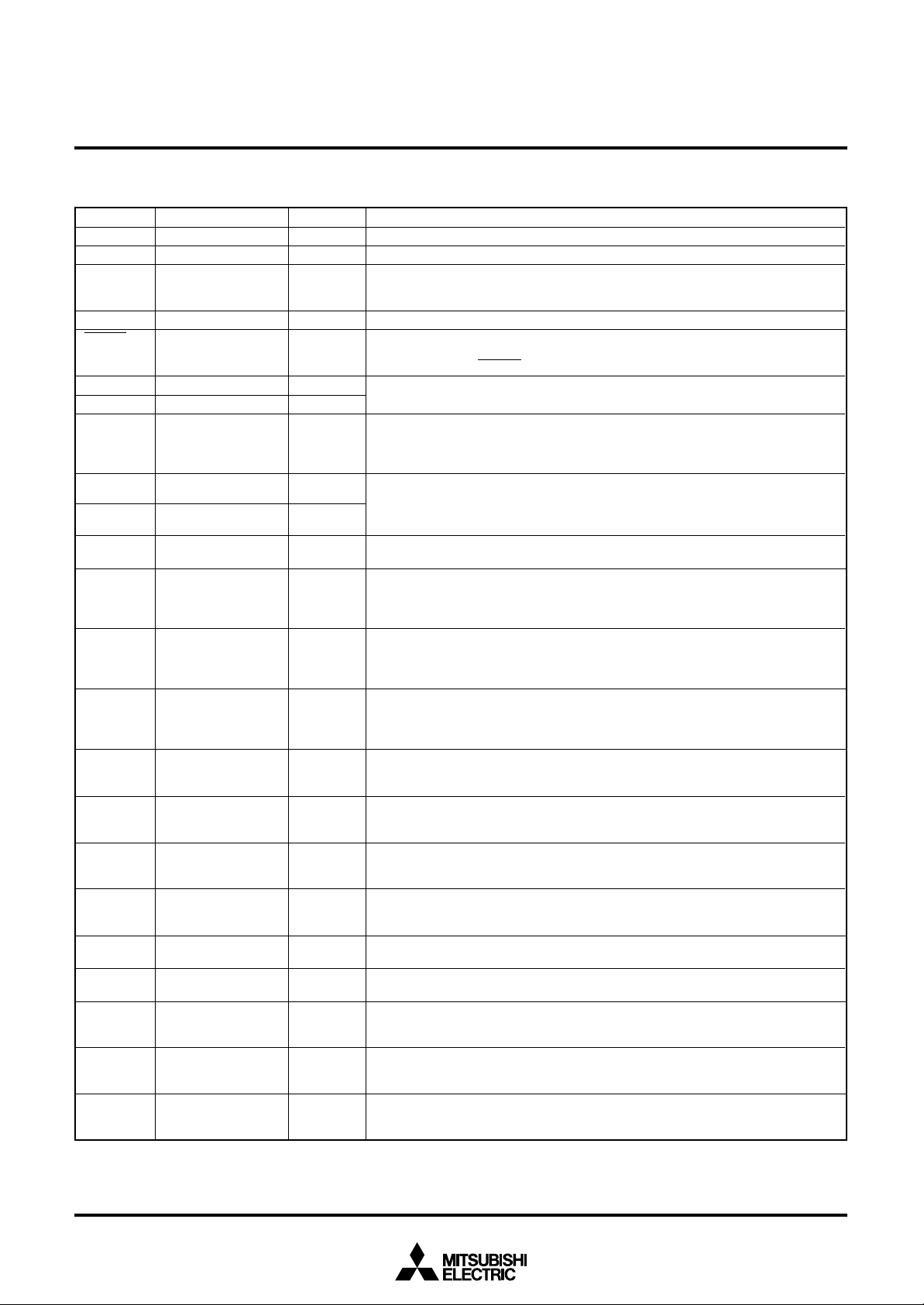

PERFORMANCE OVERVIEW

Parameter

Number of

basic instructions

Minimum instruction execution time

Memory sizes

Input/Output

ports

Timers

A-D converter

Voltage comparator

Serial I/O

Interrupt

Subroutine nesting

Device structure

Package

Operating temperature range

Supply voltage

Power

dissipation

(typical value)

ROM

RAM

D

0–D7

P00–P03

P10–P13

P20–P22

P30–P33

P40–P43

P50–P53

CNTR0

CNTR1

INT0

INT1

Timer 1

Timer 2

Timer 3

Timer 4

Sources

Nesting

4513 Group

4514 Group

Active mode

RAM back-up mode

4513 Group

4514 Group

M34513M2

M34513M4/E4

M34513M6

M34513M8/E8

M34514M6

M34514M8/E8

M34513M2

M34513M4/E4

M34513M6

M34513M8/E8

M34514M6

M34514M8/E8

I/O (Input is

examined by

skip decision)

I/O

I/O

Input

I/O

I/O

I/O

I/O

I/O

Input

Input

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Function

123

128

0.75

µ

s (at 4.0 MHz oscillation frequency, in high-speed mode)

2048 words ✕ 10 bits

4096 words ✕ 10 bits

6144 words ✕ 10 bits

8192 words ✕ 10 bits

6144 words ✕ 10 bits

8192 words ✕ 10 bits

128 words ✕ 4 bits

256 words ✕ 4 bits

384 words ✕ 4 bits

384 words ✕ 4 bits

384 words ✕ 4 bits

384 words ✕ 4 bits

Eight independent I/O ports;

ports D6 and D7 are also used as CNTR0 and CNTR1, respectively.

4-bit I/O port; each pin is equipped with a pull-up function and a key-on wakeup function. Both

functions can be switched by software.

4-bit I/O port; each pin is equipped with a pull-up function and a key-on wakeup function. Both

functions can be switched by software.

3-bit input port; ports P20, P21 and P22 are also used as SCK, SOUT and SIN, respectively.

4-bit I/O port (2-bit I/O port for the 4513 Group); ports P30 and P31 are also used as INT0 and

INT1, respectively. The 4513 Group does not have ports P32, P33.

4-bit I/O port; The 4513 Group does not have this port.

4-bit I/O port with a direction register; The 4513 Group does not have this port.

1-bit I/O; CNTR0 pin is also used as port D6.

1-bit I/O; CNTR1 pin is also used as port D7.

1-bit input; INT0 pin is also used as port P30 and equipped with a key-on wakeup function.

1-bit input; INT1 pin is also used as port P31 and equipped with a key-on wakeup function.

8-bit programmable timer with a reload register.

8-bit programmable timer with a reload register is also used as an event counter.

8-bit programmable timer with a reload register.

8-bit programmable timer with a reload register is also used as an event counter.

10-bit wide, This is equipped with an 8-bit comparator function.

2 circuits (CMP0, CMP1)

8-bit ✕ 1

8 (two for external, four for timer, one for A-D, and one for serial I/O)

1 level

8 levels

CMOS silicon gate

32-pin plastic molded SDIP (32P4B)/LQFP(32P6U-A)

42-pin plastic molded SSOP (42P2R-A)

–20 °C to 85 °C

2.0 V to 5.5 V for Mask ROM version, 2.5 V to 5.5 V for One Time PROM version (Refer to the

electrical characteristics because the supply voltage depends on the oscillation frequency.)

1.8 mA (at VDD = 5.0 V, 4.0 MHz oscillation frequency, in middle- speed mode, output transis-

3.0 mA (at VDD = 5.0 V, 4.0 MHz oscillation frequency, in high-speed mode, output transistors

0.1 µA (at room temperature, VDD = 5 V, output transistors in the cut-off state)

tors in the cut-off state)

in the cut-off state)

6

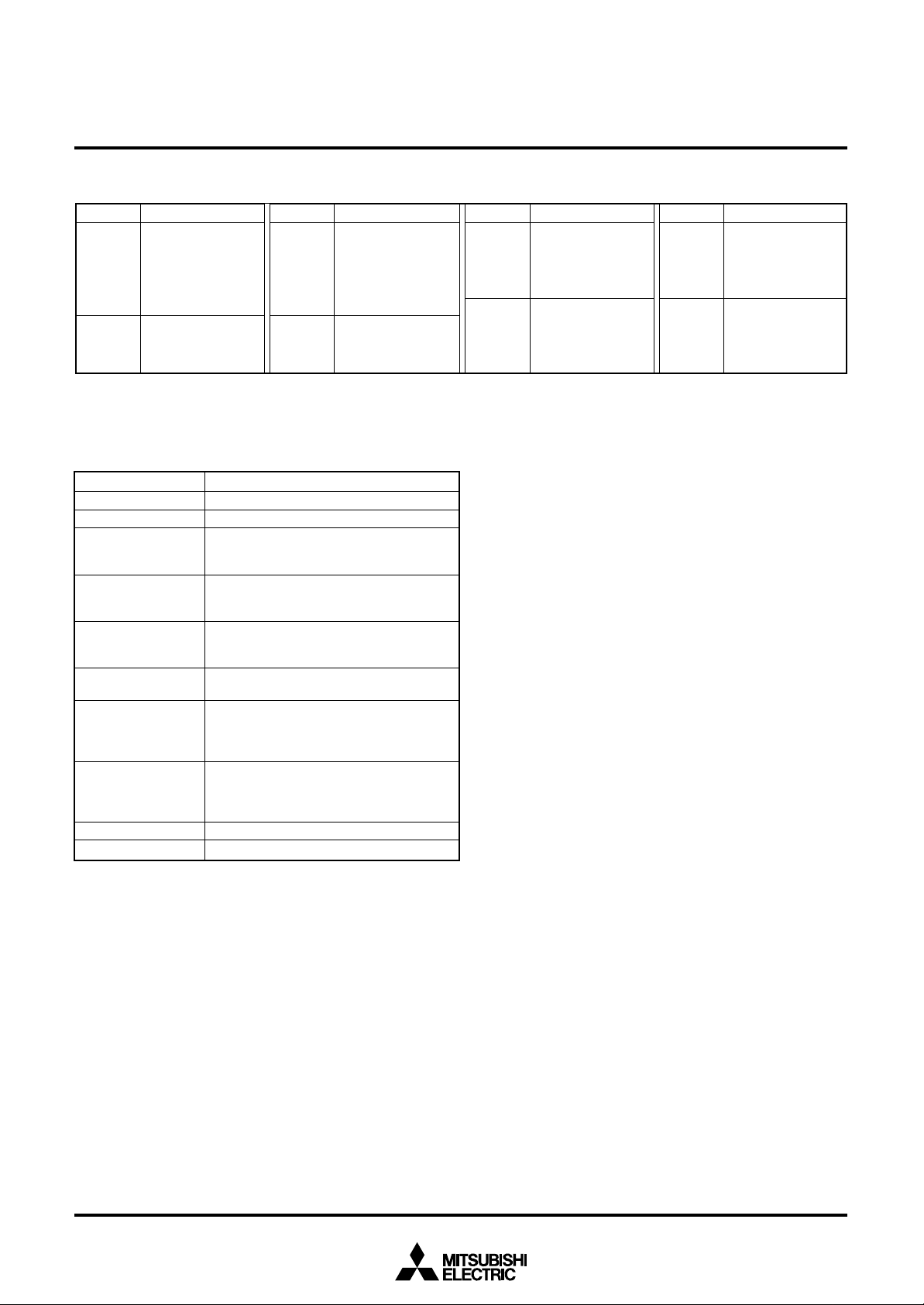

PIN DESCRIPTION

Pin

DD

V

VSS

VDCE

CNVSS

RESET

XIN

XOUT

D0–D7

P00–P03

P10–P13

P20–P22

P30–P33

P40–P43

P50–P53

AIN0–AIN7

CNTR0

CNTR1

INT0, INT1

SIN

SOUT

SCK

CMP0CMP0+

CMP1CMP1+

Name

Power supply

Ground

Voltage drop detec-

tion circuit enable

SS

CNV

Reset input

System clock input

System clock output

I/O port D

(Input is examined

by skip decision.)

I/O port P0

I/O port P1

Input port P2

I/O port P3

I/O port P4

I/O port P5

Analog input

Timer input/output

Timer input/output

Interrupt input

Serial data input

Serial data output

Serial I/O clock

input/output

Voltage comparator

input

Voltage comparator

input

Input/Output

—

—

Input

—

I/O

Input

Output

I/O

I/O

I/O

Input

I/O

I/O

I/O

Input

I/O

I/O

Input

Input

Output

I/O

Input

Input

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Function

Connected to a plus power supply.

Connected to a 0 V power supply.

VDCE pin is used to control the operation/stop of the voltage drop detection circuit.

When “H” level is input to this pin, the circuit is operating. When “L” level is inpu to

this pin, the circuit is stopped.

Connect CNVSS to VSS and apply “L” (0V) to CNVSS certainly.

An N-channel open-drain I/O pin for a system reset. When the watchdog timer

causes the system to be reset or system reset is performed by the voltage drop detection circuit, the RESET pin outputs “L” level.

I/O pins of the system clock generating circuit. XIN and XOUT can be connected to

ceramic resonator. A feedback resistor is built-in between them.

Each pin of port D has an independent 1-bit wide I/O function. Each pin has an output latch. For input use, set the latch of the specified bit to “1.” The output structure

is N-channel open-drain.

Ports D6 and D7 are also used as CNTR0 and CNTR1, respectively.

Each of ports P0 and P1 serves as a 4-bit I/O port, and it can be used as inputs

when the output latch is set to “1.” The output structure is N-channel open-drain.

Every pin of the ports has a key-on wakeup function and a pull-up function. Both

functions can be switched by software.

3-bit input port. Ports P20, P21 and P22 are also used as SCK, SOUT and SIN, respectively.

4-bit I/O port (2-bit I/O port for the 4513 Group). For input use, set the latch of the

specified bit to “1.” The output structure is N-channel open-drain. Ports P30 and

P31 are also used as INT0 and INT1, respectively.

The 4513 Group does not have ports P32, P33.

4-bit I/O port. For input use, set the latch of the specified bit to “1.” The output

structure is N-channel open-drain. Ports P40–P43 are also used as analog input

pins AIN4–AIN7, respectively.

The 4513 Group does not have port P4.

4-bit I/O port. Each pin has a direction register and an independent 1-bit wide I/O

function. For input use, set the direction register to “0.” For output use, set the direction regiser to “1.” The output structure is CMOS.

The 4513 Group does not have port P5.

Analog input pins for A-D converter. AIN0–AIN3 are also used as voltage comparator input pins and AIN4–AIN7 are also used as port P4.

The 4513 Group does not have AIN4–AIN7.

CNTR0 pin has the function to input the clock for the timer 2 event counter, and to

output the timer 1 underflow signal divided by 2.

CNTR0 pin is also used as port D6.

CNTR1 pin has the function to input the clock for the timer 4 event counter, and to

output the timer 3 underflow signal divided by 2.

CNTR1 pin is also used as port D7.

INT0, INT1 pins accept external interrupts. They also accept the input signal to return the system from the RAM back-up state.

INT0, INT1 pins are also used as ports P30 and P31, respectively.

SIN pin is used to input serial data signals by software.

SIN pin is also used as port P22.

SOUT pin is used to output serial data signals by software.

SOUT pin is also used as port P21.

SCK pin is used to input and output synchronous clock signals for serial data transfer by software.

SCK pin is also used as port P20.

CMP0-, CMP0+ pins are used as the voltage comparator input pin when the voltage comparator function is selected by software.

CMP0-, CMP0+ pins are also used as AIN0 and AIN1.

CMP1-, CMP1+ pins are used as the voltage comparator input pin when the voltage comparator function is selected by software.

CMP1-, CMP1+ pins are also used as AIN2 and AIN3.

7

MULTIFUNCTION

Pin

D6

D7

P20

P21

P22

P30

P31

Notes 1: Pins except above have just single function.

2: The input of D

S

3: The 4513 Group does not have P4

Multifunction

CNTR0

CNTR1

SCK

SOUT

SIN

INT0

INT1

6, D7, P20–P22, CMP0-, CMP0+, CMP1-, CMP1+ and the input/output of P30, P31, P40–P43 can be used even when CNTR0, CNTR1,

CK, SOUT, SIN, INT0, INT1, and AIN0–AIN7 are selected.

Pin

CNTR0

CNTR1

SCK

SOUT

SIN

INT0

INT1

0/AIN4–P43/AIN7.

CONNECTIONS OF UNUSED PINS

Pin

XOUT

VDCE

D0–D5

D6/CNTR0

D7/CNTR1

P20/SCK

P21/SOUT

P22/SIN

P30/INT0

P31/INT1

P32, P33

P40/AIN4–P43/AIN7

P50–P53 (Note 1)

AIN0/CMP0AIN1/CMP0+

AIN2/CMP1AIN3/CMP1+

P00–P03

P10–P13

Open (when using an external clock).

Connect to VSS.

Connect to VSS, or set the output latch to

“0” and open.

Connect to VSS.

Connect to VSS, or set the output latch to

“0” and open.

Connect to VSS, or set the output latch to

“0” and open.

When the input mode is selected by software, pull-up to VDD through a resistor or

pull-down to VDD.

When selecting the output mode, open.

Connect to VSS.

Open or connect to VSS (Note 2)

Open or connect to VSS (Note 2)

Connection

Multifunction

D6

D7

P20

P21

P22

P30

P31

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Pin

AIN0

AIN1

AIN2

AIN3

P40

P41

P42

P43

Notes 1: After system is released from reset, port P5 is in an input mode (di-

2: When the P0

(Note when the output latch is set to “0” and pins are open)

● After system is released from reset, port is in a high-impedance state un-

til it is set the output latch to “0” by software. Accordingly, the voltage

level of pins is undefined and the excess of the supply current may occur

while the port is in a high-impedance state.

● To set the output latch periodically by software is recommended because

value of output latch may change by noise or a program run away

(caused by noise).

(Note when connecting to V

● Connect the unused pins to V

shortest distance against noise.

Multifunction

CMP0CMP0+

CMP1CMP1+

AIN4

AIN5

AIN6

AIN7

rection register FR0 = 0000

0–P03 and P10–P13 are connected to VSS, turn off

their pull-up transistors (register PU0i=“0”) and also invalidate the

key-on wakeup functions (register K0i=“0”) by software. When

these pins are connected to V

tions are left valid, the system fails to return from RAM back-up

state. When these pins are open, turn on their pull-up transistors

(register PU0i=“1”) by software, or set the output latch to “0.”

Be sure to select the key-on wakeup functions and the pull-up

functions with every two pins. If only one of the two pins for the

key-on wakeup function is used, turn on their pull-up transistors by

software and also disconnect the other pin. (i = 0, 1, 2, or 3.)

SS and VDD)

Pin

CMP0CMP0+

CMP1CMP1+

AIN4

AIN5

AIN6

AIN7

2)

SS while the key-on wakeup func-

SS and VDD using the thickest wire at the

Multifunction

AIN0

AIN1

AIN2

AIN3

P40

P41

P42

P43

8

PORT FUNCTION

Port

Port D

Port P0

Port P1

Port P2

Port P3

(Note 1)

Port P4

(Note 2)

Port P5

(Note 2)

Notes 1: The 4513 Group does not have P32 and P33.

2: The 4513 Group does not have these ports.

Pin

D0–D5

D6/CNTR0

D7/CNTR1

P00–P03

P10–P13

P20/SCK

P21/SOUT

P22/SIN

P30/INT0

P31/INT1

P32, P33

P40/AIN4

–P43/AIN7

P50–P53

Input

Output

I/O

(8)

I/O

(4)

I/O

(4)

Input

(3)

I/O

(4)

I/O

(4)

I/O

(4)

N-channel open-drain

N-channel open-drain

N-channel open-drain

N-channel open-drain

N-channel open-drain

CMOS

Output structure

I/O

unit

1

4

4

3

4

4

4

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Control

instructions

SD, RD

SZD

CLD

OP0A

IAP0

OP1A

IAP1

IAP2

OP3A

IAP3

OP4A

IAP4

OP5A

IAP5

Control

registers

W6

PU0, K0

PU0, K0

J1

I1, I2

Q2

FR0

Remark

Built-in programmable pull-up

functions

Key-on wakeup functions

(programmable)

Built-in programmable pull-up

functions

Key-on wakeup functions

(programmable)

Built-in key-on wakeup

function

(P30/INT0, P31/INT1)

DEFINITION OF CLOCK AND CYCLE

● System clock

The system clock is the basic clock for controlling this product.

The system clock is selected by the bit 3 of the clock control register MR.

Table Selection of system clock

Register MR

MR3

0

1

Note: f(XIN)/2 is selected after system is released from reset.

● Instruction clock

The instruction clock is a signal derived by dividing the system

clock by 3. The one instruction clock cycle generates the one

machine cycle.

● Machine cycle

The machine cycle is the standard cycle required to execute the

instruction.

System clock

f(XIN)

f(XIN)/2

9

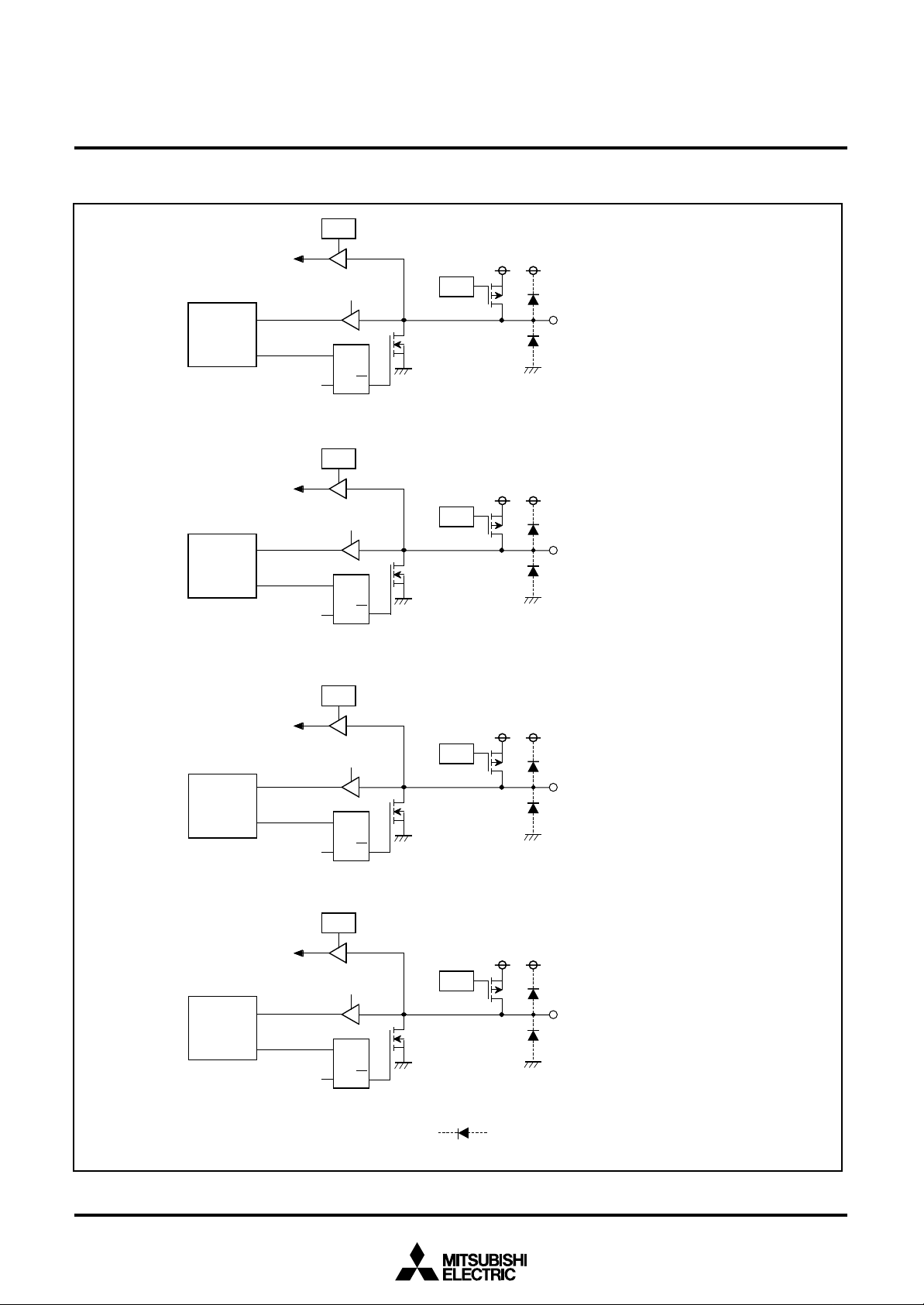

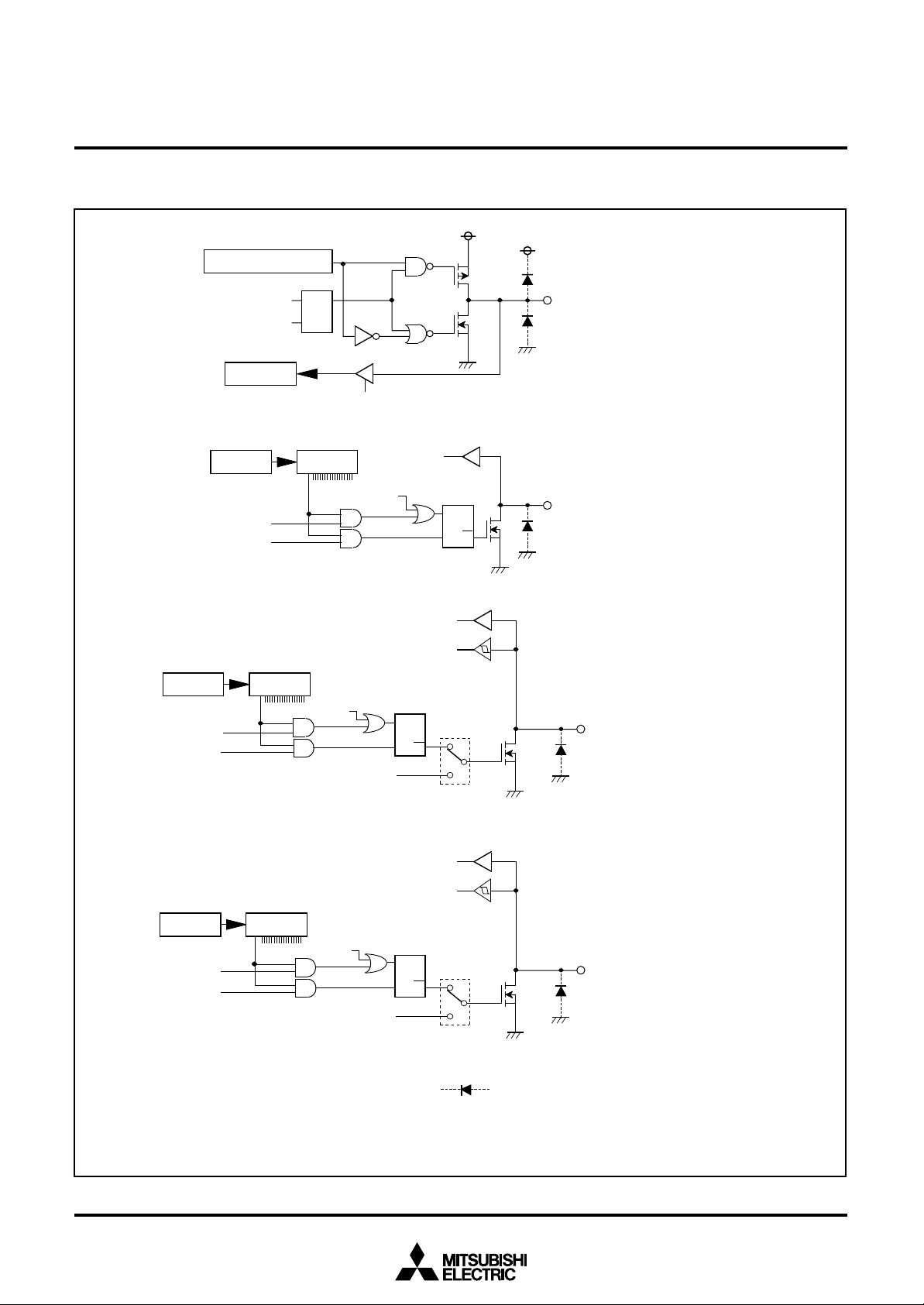

PORT BLOCK DIAGRAMS

0

2

3

A

A

Key-on wakeup input

K 0

0

I A P 0 i n s t r u c t i o n

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

P u l l - u p t r a n s i s t o r

PU0

R e g i s t e r A

A i

O P 0 A i n s t r u c t i o n

K e y - o n w a k e u p i n p u t

R e g i s t e r A

Ai

O P 0 A i n s t r u c t i o n

Key-on wakeup input

R e g i s t e r

D

T

Q

K 0

1

IAP0 instruction

D

Q

T

K 0

2

I A P 1 i n s t r u c t i o n

P u l l - u p t r a n s i s t o r

PU0

1

Pull-up transistor

PU0

P 00, P 0

P 02, P 0

P 10, P 1

1

3

1

10

A i

O P 1 A i n s t r u c t i o n

K e y - o n w a k e u p i n p u t

R e g i s t e r

A i

O P 1 A i n s t r u c t i o n

D

T

Q

K0

3

IAP1 instruction

D

T

Q

Pull-up transistor

PU0

•

i r e p r e s e n t s 0 , 1 , 2 , o r 3 .

•

T h i s s y m b o l r e p r e s e n t s a p a r a s i t i c d i o d e o n t h e p o r t .

P12,P1

3

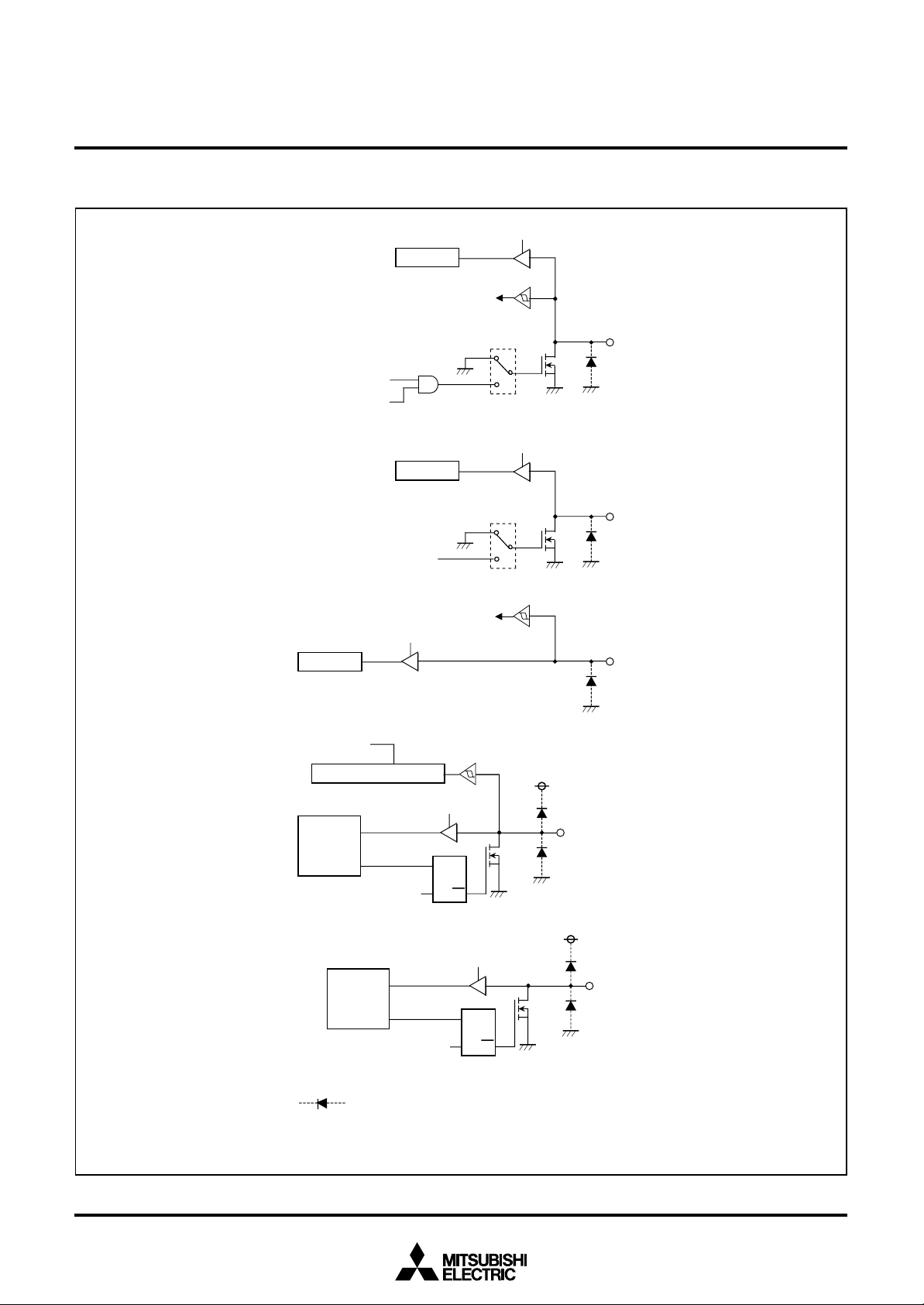

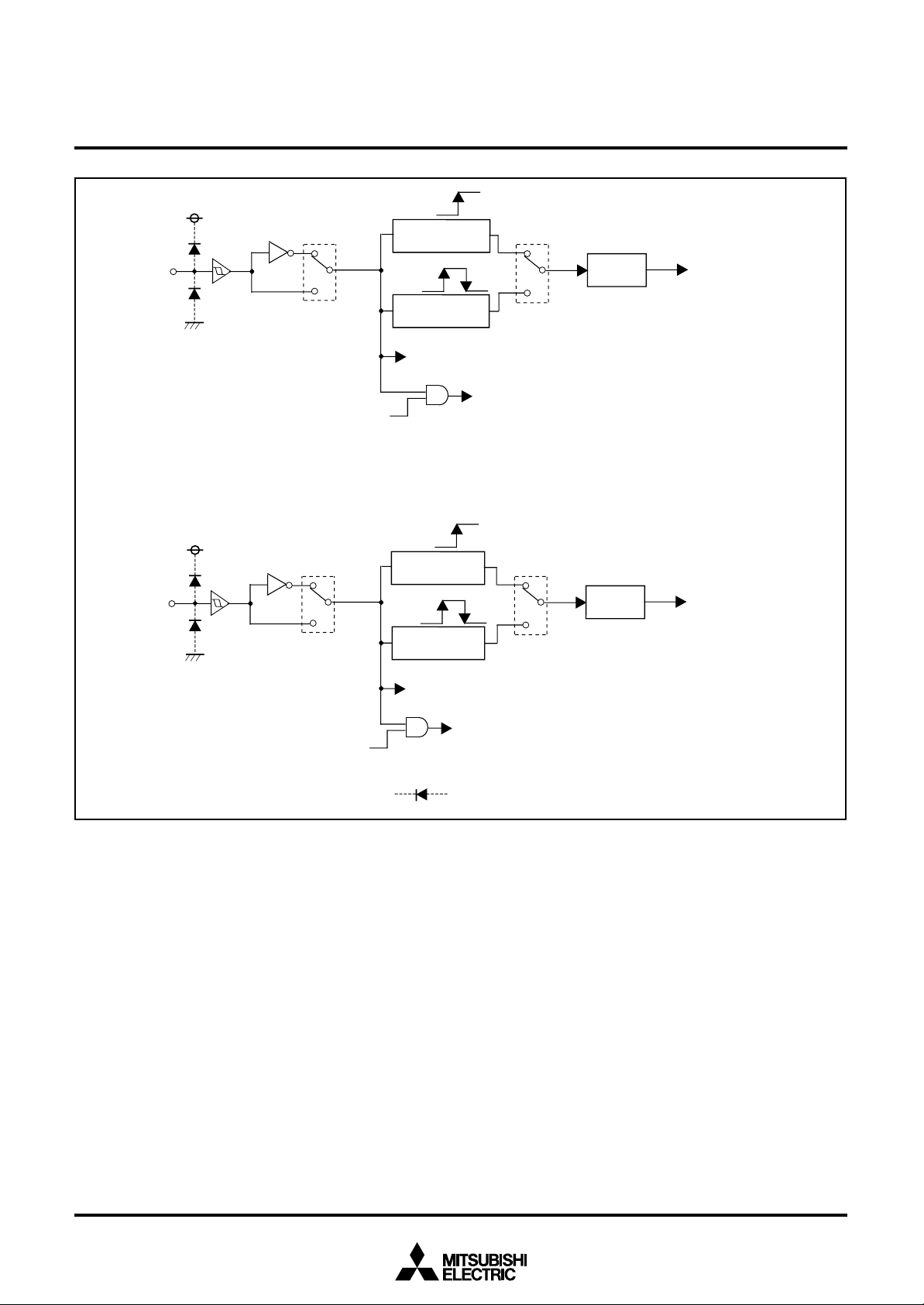

PORT BLOCK DIAGRAMS (continued)

Synchronous clock input for serial transfer

Synchronous clock output for serial transfer

J1

Register A

0

Register A

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

IAP2 instruction

J1

1

0

1

IAP2 instruction

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

P20/S

CK

Serial data output

Register A

Key-on wakeup input

External interrupt circuit

Register A

Ai

OP3A instruction

Register A

Serial data input

IAP2 instruction

IAP3 instruction

D

T

IAP3 instruction

1

J1

0

1

P21/S

P22/S

OUT

IN

P30/INT0,P31/INT1

Q

P32,P3

3

11

Ai

OP3A instruction

•

• Applied potential to ports P2

• i represents 0, 1, 2, or 3.

• The 4513 Group does not have ports P3

This symbol represents a parasitic diode on the port.

D

T

Q

0

—P22 must be VDD.

2

, P33.

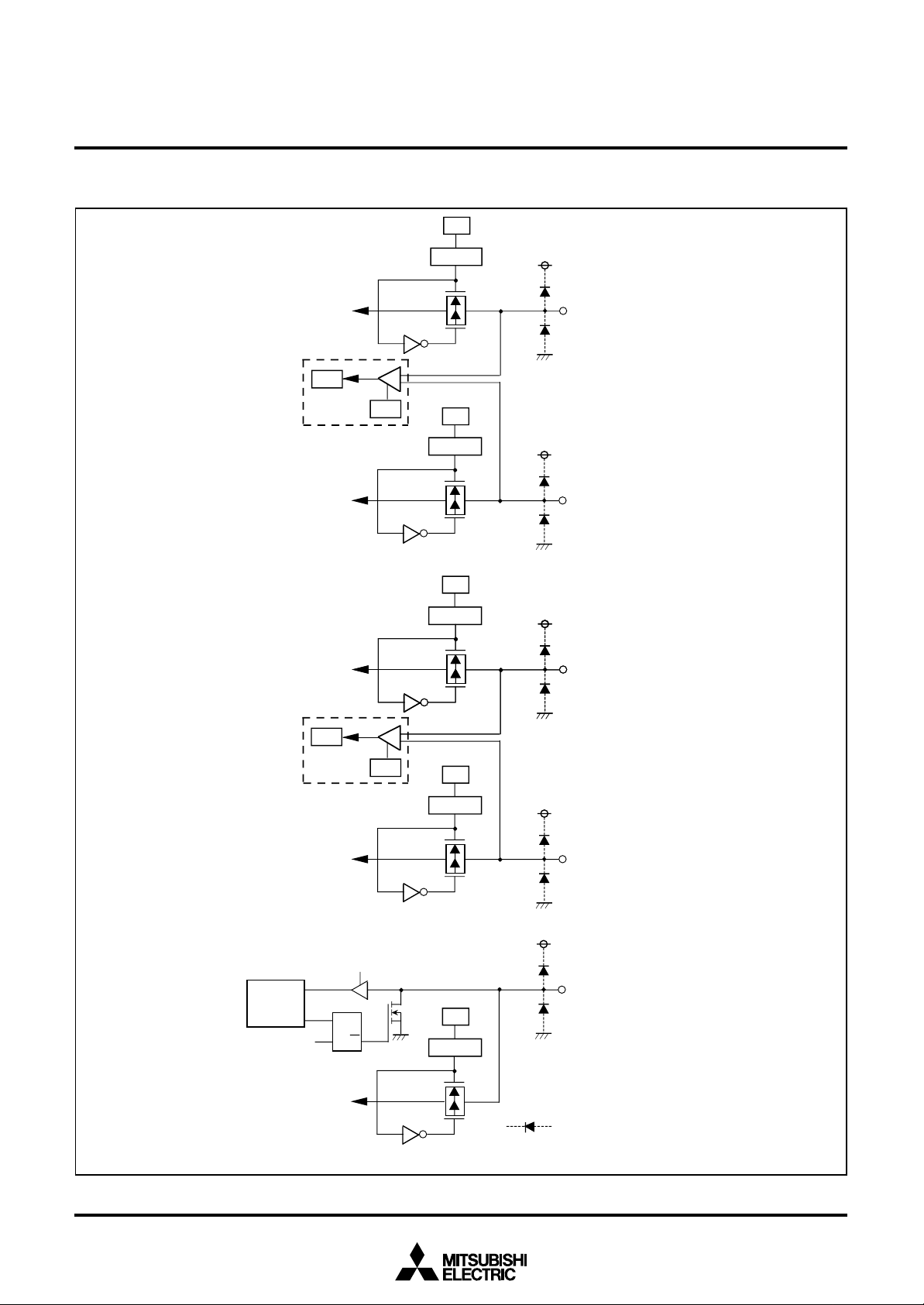

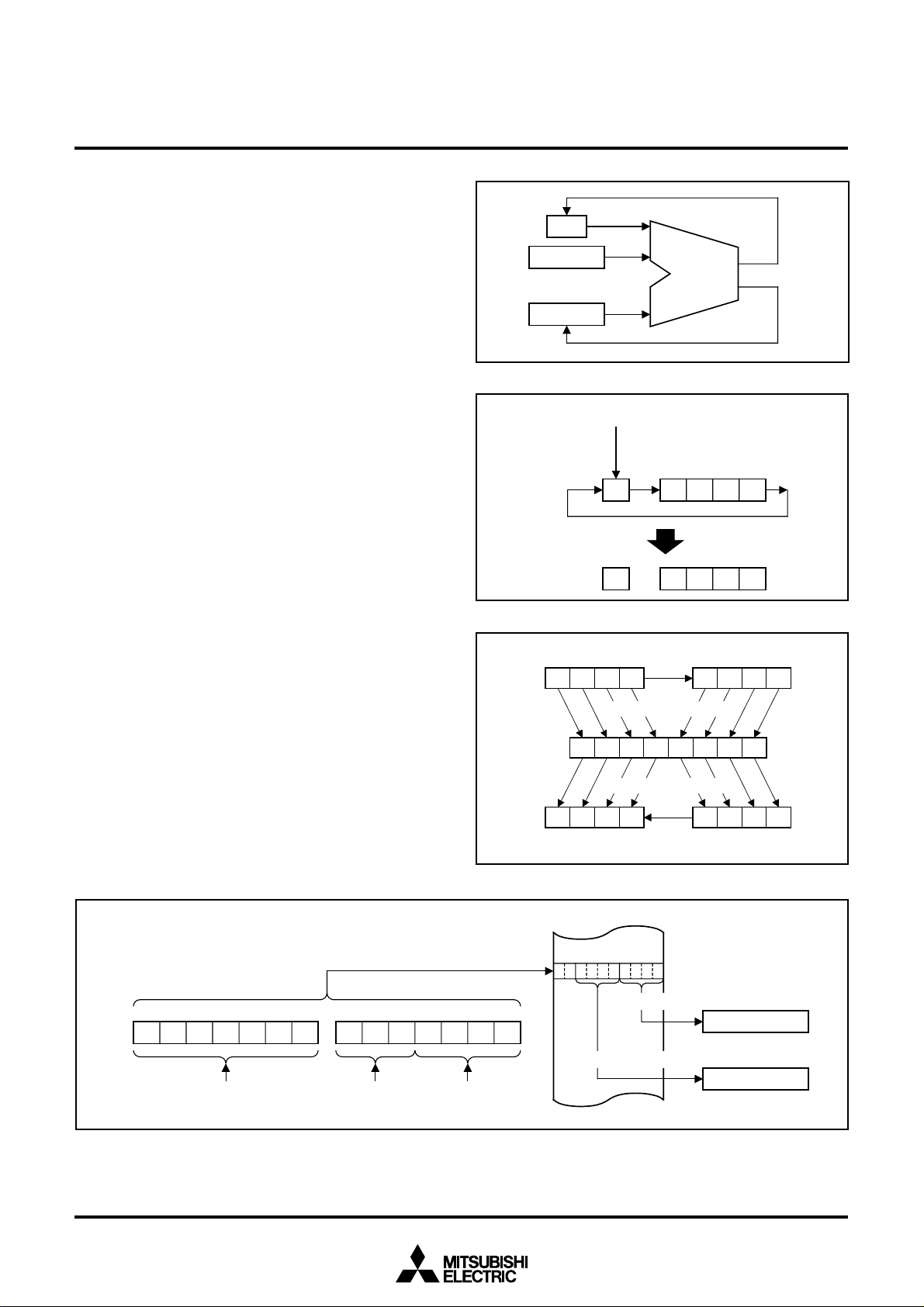

PORT BLOCK DIAGRAMS (continued)

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Q1

Decoder

Analog input

Q3

0

CMP0

Analog input

Analog input

Q3

1

Q3

A

IN0

/CMP0-

-

+

2

Q1

Decoder

A

IN1

/CMP0+

Q1

Decoder

A

IN2

/CMP1-

-

+

Analog input

Register A

Ai

OP4A instruction

Analog input

CMP1

IAP4 instruction

D

T

Q

Q3

3

Q1

Decoder

A

IN3

/CMP1+

P40/A

IN4

–P43/A

IN7

Q1

Decoder

•

• i represents 0, 1, 2, or 3.

• The 4513 Group does not have port P4.

This symbol represents a parasitic diode on the port.

12

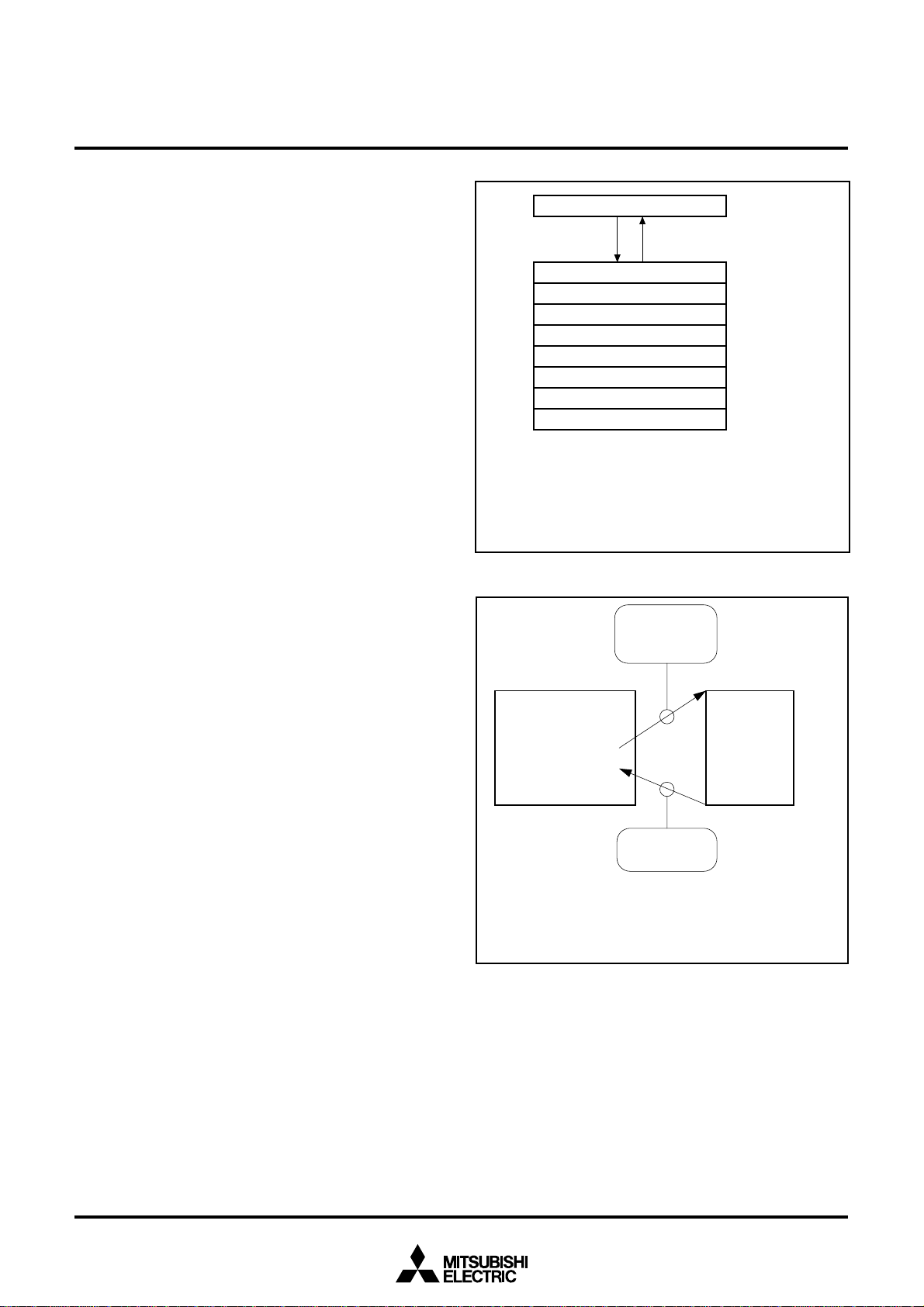

PORT BLOCK DIAGRAMS (continued)

DTQ

A i

S

R

Q

S

R

Q

W

S

R

Q

W

D i r e c t i o n r e g i s t e r F R 0 i

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

O P 5 A i n s t r u c t i o n

R e g i s t e r A

I A P 5 i n s t r u c t i o n

R e g i s t e r Y

D e c o d e r

C L D i n s t r u c t i o n

S D i n s t r u c t i o n

RD instruction

S k i p d e c i s i o n

C l o c k i n p u t f o r t i m e r 2 e v e n t c o u n t

D e c o d e rR e g i s t e r Y

CLD instruction

S D i n s t r u c t i o n

R D i n s t r u c t i o n

T i m e r 1 u n d e r f l o w s i g n a l d i v i d e d b y 2 o r

s i g n a l o f A N D o p e r a t i o n b e t w e e n

t i m e r 1 u n d e r f l o w s i g n a l d i v i d e d b y 2 a n d

t i m e r 2 u n d e r f l o w s i g n a l d i v i d e d b y 2

S k i p d e c i s i o n

(SZD instruction)

( S Z D i n s t r u c t i o n )

P 50– P 5

D0– D

0

6

0

1

3

5

D6/CNTR0

S k i p d e c i s i o n

(SZD instruction)

C l o c k i n p u t f o r t i m e r 4 e v e n t c o u n t

D e c o d e rR e g i s t e r Y

C L D i n s t r u c t i o n

SD instruction

R D i n s t r u c t i o n

T i m e r 3 u n d e r f l o w s i g n a l d i v i d e d b y 2 o r

2

0

1

D7/CNTR1

6

s i g n a l o f A N D o p e r a t i o n b e t w e e n

t i m e r 3 u n d e r f l o w s i g n a l d i v i d e d b y 2 a n d

t i m e r 4 u n d e r f l o w s i g n a l d i v i d e d b y 2

•

• A p p l i e d p o t e n t i a l t o p o r t s D

T h i s s y m b o l r e p r e s e n t s a p a r a s i t i c d i o d e o n t h e p o r t .

0

– D7 m u s t b e 1 2 V .

• i r e p r e s e n t s 0 , 1 , 2 , o r 3 .

• T h e 4 5 1 3 G r o u p d o e s n o t h a v e p o r t P 5 .

13

P3

0

/INT0

I1

2

Falling

Rising

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

One-sided edge

0

1

detection circuit

Both edges

detection circuit

Wakeup

SNZI0

Skip

I1

1

0

EXF0

1

External 0

interrupt

P3

1

/INT1

External interrupt circuit structure

I2

2

Falling

Rising

0

1

SNZI1

One-sided edge

detection circuit

Both edges

detection circuit

Wakeup

Skip

This symbol represents a parasitic diode on the port.

I2

1

0

EXF1

1

External 1

interrupt

14

FUNCTION BLOCK OPERATIONS

CPU

(1) Arithmetic logic unit (ALU)

The arithmetic logic unit ALU performs 4-bit arithmetic such as 4bit data addition, comparison, AND operation, OR operation, and

bit manipulation.

(2) Register A and carry flag

Register A is a 4-bit register used for arithmetic, transfer, exchange, and I/O operation.

Carry flag CY is a 1-bit flag that is set to “1” when there is a carry

with the AMC instruction (Figure 1).

It is unchanged with both A n instruction and AM instruction. The

value of A0 is stored in carry flag CY with the RAR instruction (Figure 2).

Carry flag CY can be set to “1” with the SC instruction and cleared

to “0” with the RC instruction.

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

<Carry>

(CY)

(M(DP))

Addition

(A)

Fig. 1 AMC instruction execution example

<Set>

SC instruction

RC instruction

CY A3A2A1A

ALU

<Result>

<Clear>

0

(3) Registers B and E

Register B is a 4-bit register used for temporary storage of 4-bit

data, and for 8-bit data transfer together with register A.

Register E is an 8-bit register. It can be used for 8-bit data transfer

with register B used as the high-order 4 bits and register A as the

low-order 4 bits (Figure 3).

(4) Register D

Register D is a 3-bit register.

It is used to store a 7-bit ROM address together with register A and

is used as a pointer within the specified page when the TABP p,

BLA p, or BMLA p instruction is executed (Figure 4).

TABP p instruction

Specifying address

RAR instruction

A

0

Fig. 2 RAR instruction execution example

Register B Register A

B3B2B1B

Register E

Fig. 3 Registers A, B and register E

E7E6E5E4E3E2E1E

B3B2B1B

Register B Register A

CY A3A2A

TAB instruction

0

TEAB instruction

TABE instruction

0

TBA instruction

A3A2A1A

A3A2A1A

ROM

840

<Rotation>

1

0

0

0

PC

H

p6p5p4p3p2p1p

Immediate field

value p

Fig. 4 TABP p instruction execution example

15

0

DR2DR1DR

The contents of

register D

PC

L

A3A2A1A

0

The contents of

register A

Low-order 4bits

0

Register A (4)

Middle-order 4 bits

Register B (4)

MITSUBISHI MICROCOMPUTERS

n

M

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(5) Stack registers (SKS) and stack pointer (SP)

Stack registers (SKs) are used to temporarily store the contents of

program counter (PC) just before branching until returning to the

original routine when;

• branching to an interrupt service routine (referred to as an interrupt service routine),

• performing a subroutine call, or

• executing the table reference instruction (TABP p).

Stack registers (SKs) are eight identical registers, so that subroutines can be nested up to 8 levels. However, one of stack registers

is used respectively when using an interrupt service routine and

when executing a table reference instruction. Accordingly, be careful not to over the stack when performing these operations

together. The contents of registers SKs are destroyed when 8 levels are exceeded.

The register SK nesting level is pointed automatically by 3-bit

stack pointer (SP). The contents of the stack pointer (SP) can be

transferred to register A with the TASP instruction.

Figure 5 shows the stack registers (SKs) structure.

Figure 6 shows the example of operation at subroutine call.

(6) Interrupt stack register (SDP)

Interrupt stack register (SDP) is a 1-stage register. When an interrupt occurs, this register (SDP) is used to temporarily store the

contents of data pointer, carry flag, skip flag, register A, and register B just before an interrupt until returning to the original routine.

Unlike the stack registers (SKs), this register (SDP) is not used

when executing the subroutine call instruction and the table reference instruction.

(7) Skip flag

Skip flag controls skip decision for the conditional skip instructions

and continuous described skip instructions. When an interrupt occurs, the contents of skip flag is stored automatically in the interrupt

stack register (SDP) and the skip condition is retained.

Program counter (PC)

SK

SK

SK

SK

SK

SK

SK

SK

0

1

2

3

4

5

6

7

Executing RT

instruction

Executing BM

instruction

Stack pointer (SP) points “7” at reset or

returning from RAM back-up mode. It points “0”

by executing the first BM instruction, and the

contents of program counter is stored in SK

When the BM instruction is executed after eight

stack registers are used ((SP) = 7), (SP) = 0

and the contents of SK

Fig. 5 Stack registers (SKs) structure

0

is destroyed.

(SP) ← 0

0

) ← 0001

(SK

(PC) ← SUB1

16

Main program

Address

16

NOP

0000

16

BM SUB1

0001

000216 NOP

(SP) = 0

(SP) = 1

(SP) = 2

(SP) = 3

(SP) = 4

(SP) = 5

(SP) = 6

(SP) = 7

Subroutine

SUB1 :

NOP

RT

0

.

·

·

·

16

(PC) ← (SK0)

(SP) ← 7

Returning to the BM instruction executio

Note :

address with the RT instruction, and the B

instruction becomes the NOP instruction.

Fig. 6 Example of operation at subroutine call

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(8) Program counter (PC)

Program counter (PC) is used to specify a ROM address (page and

address). It determines a sequence in which instructions stored in

ROM are read. It is a binary counter that increments the number of

instruction bytes each time an instruction is executed. However,

the value changes to a specified address when branch instructions,

subroutine call instructions, return instructions, or the table reference instruction (TABP p) is executed.

Program counter consists of PCH (most significant bit to bit 7)

which specifies to a ROM page and PCL (bits 6 to 0) which specifies an address within a page. After it reaches the last address

(address 127) of a page, it specifies address 0 of the next page

(Figure 7).

Make sure that the PCH does not specify after the last page of the

built-in ROM.

(9) Data pointer (DP)

Data pointer (DP) is used to specify a RAM address and consists

of registers Z, X, and Y. Register Z specifies a RAM file group, register X specifies a file, and register Y specifies a RAM digit (Figure

8).

Register Y is also used to specify the port D bit position.

When using port D, set the port D bit position to register Y certainly

and execute the SD, RD, or SZD instruction (Figure 9).

Program counter

p5p4p3p2p1p0a6a5a4a3a2a1a

p

6

PC

Specifying page

Fig. 7 Program counter (PC) structure

H

Specifying address

Data pointer (DP)

Z1Z0X3X2X1X0Y3Y2Y1Y

Register Y (4)

Register X (4)

Register Z (2)

Specifying RAM file group

0

PC

L

0

Specifying

RAM digit

Specifying RAM file

Fig. 8 Data pointer (DP) structure

Specifying bit position

D

7

0101 1

Register Y (4)

Fig. 9 SD instruction execution example

Port D output latch

Set

D

5

D

6

D4D

0

17

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

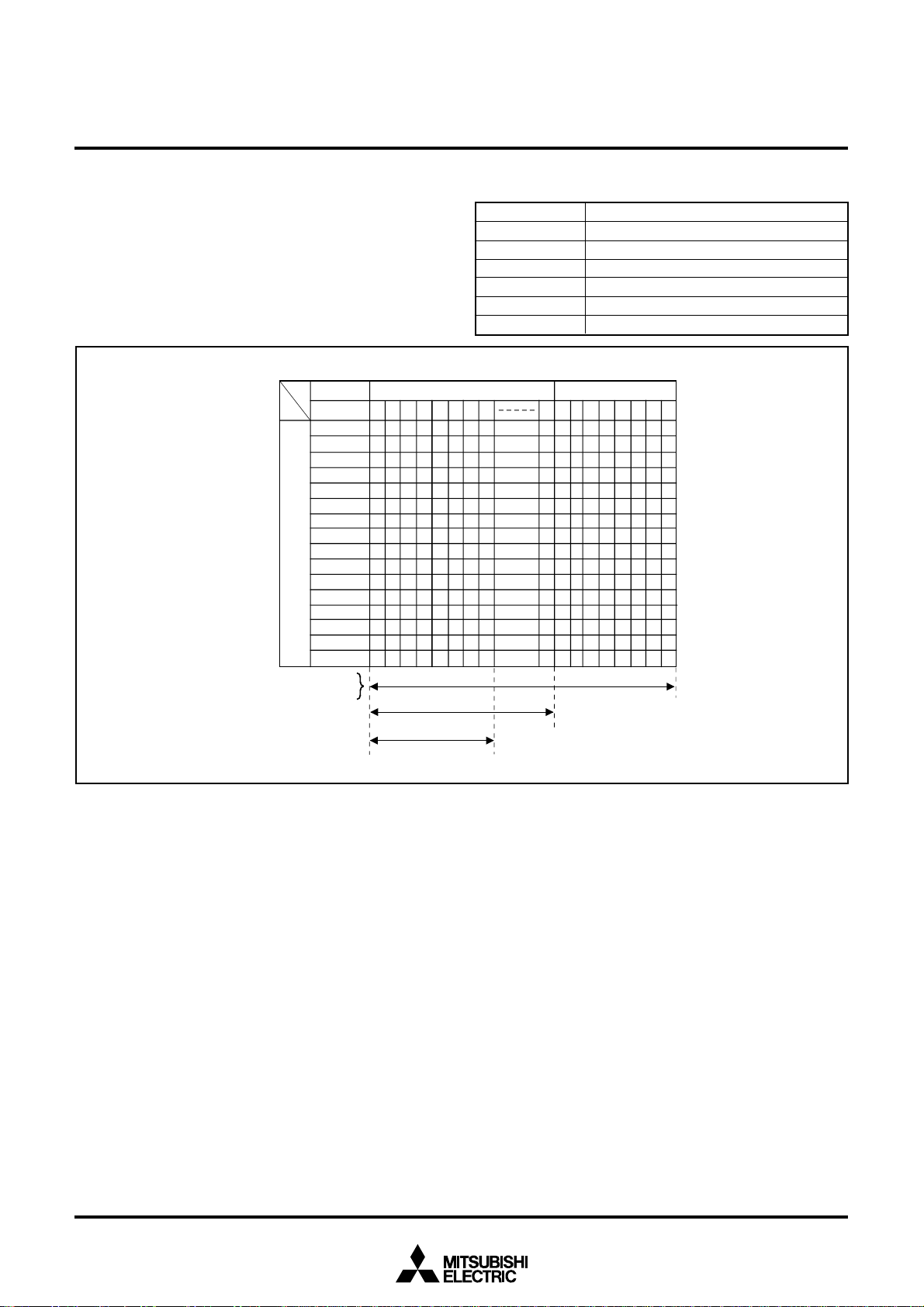

PROGRAM MEMOY (ROM)

The program memory is a mask ROM. 1 word of ROM is composed

of 10 bits. ROM is separated every 128 words by the unit of page

(addresses 0 to 127). Table 1 shows the ROM size and pages. Figure 10 shows the ROM map of M34514M8/E8.

Table 1 ROM size and pages

Product

M34513M2

M34513M4/E4

M34513M6

M34513M8/E8

M34514M6

M34514M8/E8

A part of page 1 (addresses 008016 to 00FF16) is reserved for interrupt addresses (Figure 11). When an interrupt occurs, the

address (interrupt address) corresponding to each interrupt is set

in the program counter, and the instruction at the interrupt address

is executed. When using an interrupt service routine, write the instruction generating the branch to that routine at an interrupt

address.

Page 2 (addresses 010016 to 017F16) is the special page for subroutine calls. Subroutines written in this page can be called from

any page with the 1-word instruction (BM). Subroutines extending

from page 2 to another page can also be called with the BM instruction when it starts on page 2.

ROM pattern (bits 7 to 0) of all addresses can be used as data areas with the TABP p instruction.

ROM size

(✕ 10 bits)

2048 words

4096 words

6144 words

8192 words

6144 words

8192 words

Pages

16 (0 to 15)

32 (0 to 31)

48 (0 to 47)

64 (0 to 63)

48 (0 to 47)

64 (0 to 63)

9

16

0000

007

F

16

0080

16

00

FF

0100

017

0180

0

FFF

1

FFF

F

Interrupt address page

16

16

Subroutine special page

16

16

16

16

Fig. 10 ROM map of M34514M8/E8

9087654321

16

0080

0082

0084

0086

0088

External 0 interrupt address

External 1 interrupt address

16

Timer 1 interrupt address

16

16

Timer 2 interrupt address

Timer 3 interrupt address

16

087654321

Page 0

Page 1

Page 2

Page 3

Page 31

Page 63

008A

16

Timer 4 interrupt address

16

008C

008E

16

00FF

16

Fig. 11 Page 1 (addresses 008016 to 00FF16) structure

A-D interrupt address

Serial I/O interrupt address

18

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

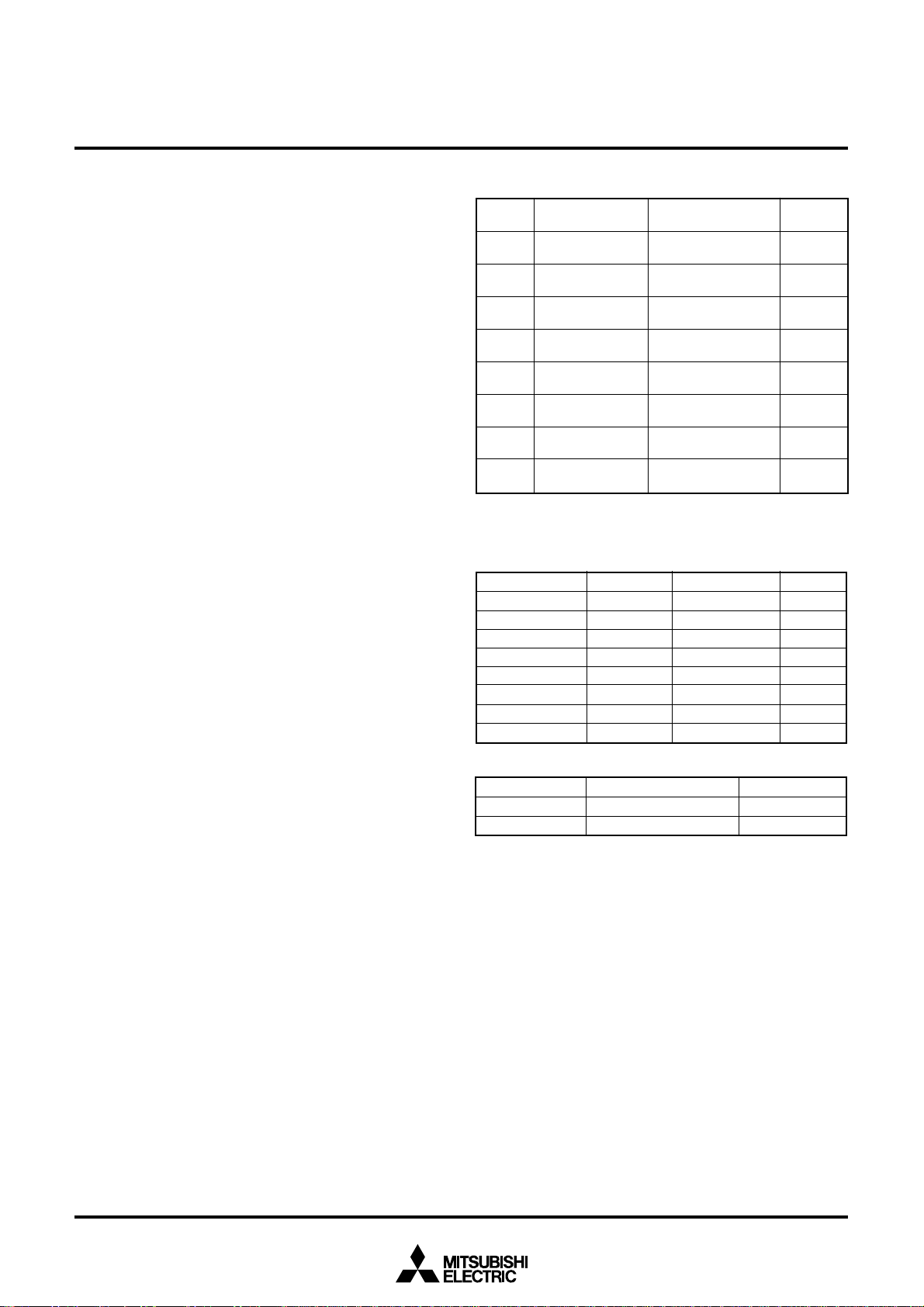

DATA MEMORY (RAM)

1 word of RAM is composed of 4 bits, but 1-bit manipulation (with

the SB j, RB j, and SZB j instructions) is enabled for the entire

memory area. A RAM address is specified by a data pointer. The

data pointer consists of registers Z, X, and Y. Set a value to the

data pointer certainly when executing an instruction to access

RAM.

Table 2 shows the RAM size. Figure 12 shows the RAM map.

RAM 384 words ✕ 4 bits (1536 bits)

Register Z

01 7

23 6 015

M34513M6

M34513M8/E8

M34514M6

M34514M8/E8

M34513M4/E4

Register X

0

1

2

3

4

5

6

7

8

9

Register Y

10

11

12

13

14

15

Z=0, X=0 to 15

Z=1, X=0 to 7

Z=0, X=0 to 15

Table 2 RAM size

M34513M2

M34513M4/E4

M34513M6

M34513M8/E8

M34514M6

M34514M8/E8

0

45

Product

128 words ✕ 4 bits (512 bits)

256 words ✕ 4 bits (1024 bits)

384 words ✕ 4 bits (1536 bits)

384 words ✕ 4 bits (1536 bits)

384 words ✕ 4 bits (1536 bits)

384 words ✕ 4 bits (1536 bits)

1

1723 6

256 words

45

384 words

RAM size

Fig. 12 RAM map

M34513M2

Z=0, X=0 to 7

128 words

19

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

INTERRUPT FUNCTION

The interrupt type is a vectored interrupt branching to an individual

address (interrupt address) according to each interrupt source. An

interrupt occurs when the following 3 conditions are satisfied.

• An interrupt activated condition is satisfied (request flag = “1”)

• Interrupt enable bit is enabled (“1”)

• Interrupt enable flag is enabled (INTE = “1”)

Table 3 shows interrupt sources. (Refer to each interrupt request

flag for details of activated conditions.)

(1) Interrupt enable flag (INTE)

The interrupt enable flag (INTE) controls whether the every interrupt enable/disable. Interrupts are enabled when INTE flag is set to

“1” with the EI instruction and disabled when INTE flag is cleared to

“0” with the DI instruction. When any interrupt occurs, the INTE flag

is automatically cleared to “0,” so that other interrupts are disabled

until the EI instruction is executed.

(2) Interrupt enable bit

Use an interrupt enable bit of interrupt control registers V1 and V2

to select the corresponding interrupt or skip instruction.

Table 4 shows the interrupt request flag, interrupt enable bit and

skip instruction.

Table 5 shows the interrupt enable bit function.

(3) Interrupt request flag

When the activated condition for each interrupt is satisfied, the corresponding interrupt request flag is set to “1.” Each interrupt

request flag is cleared to “0” when either;

• an interrupt occurs, or

• the next instruction is skipped with a skip instruction.

Each interrupt request flag is set when the activated condition is

satisfied even if the interrupt is disabled by the INTE flag or its interrupt enable bit. Once set, the interrupt request flag retains set

until a clear condition is satisfied.

Accordingly, an interrupt occurs when the interrupt disable state is

released while the interrupt request flag is set.

If more than one interrupt request flag is set when the interrupt disable state is released, the interrupt priority level is as follows

shown in Table 3.

Table 3 Interrupt sources

Priority

level

1

2

3

4

5

6

7

8

Table 4 Interrupt request flag, interrupt enable bit and skip in-

Interrupt name

External 0 interrupt

External 1 interrupt

Timer 1 interrupt

Timer 2 interrupt

Timer 3 interrupt

Timer 4 interrupt

A-D interrupt

Serial I/O interrupt

Table 5 Interrupt enable bit function

Interrupt enable bit

Interrupt name

External 0 interrupt

External 1 interrupt

Timer 1 interrupt

Timer 2 interrupt

Timer 3 interrupt

Timer 4 interrupt

A-D interrupt

Serial I/O interrupt

struction

Request flag

Occurrence of interrupt

1

0

Activated condition

Level change of

INT0 pin

Level change of

INT1 pin

Timer 1 underflow

Timer 2 underflow

Timer 3 underflow

Timer 4 underflow

Completion of

A-D conversion

Completion of

serial I/O transfer

EXF0

EXF1

T1F

T2F

T3F

T4F

ADF

SIOF

Enabled

Disabled

Skip instruction

SNZ0

SNZ1

SNZT1

SNZT2

SNZT3

SNZT4

SNZAD

SNZSI

Interrupt

address

Address 0

in page 1

Address 2

in page 1

Address 4

in page 1

Address 6

in page 1

Address 8

in page 1

Address A

in page 1

Address C

in page 1

Address E

in page 1

Enable bit

V10

V11

V12

V13

V20

V21

V22

V23

Skip instruction

Invalid

Valid

20

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(4) Internal state during an interrupt

The internal state of the microcomputer during an interrupt is as

follows (Figure 14).

• Program counter (PC)

An interrupt address is set in program counter. The address to be

executed when returning to the main routine is automatically

stored in the stack register (SK).

• Interrupt enable flag (INTE)

INTE flag is cleared to “0” so that interrupts are disabled.

• Interrupt request flag

Only the request flag for the current interrupt source is cleared to

“0.”

• Data pointer, carry flag, skip flag, registers A and B

The contents of these registers and flags are stored automatically in the interrupt stack register (SDP).

(5) Interrupt processing

When an interrupt occurs, a program at an interrupt address is executed after branching a data store sequence to stack register.

Write the branch instruction to an interrupt service routine at an interrupt address.

Use the RTI instruction to return from an interrupt service routine.

Interrupt enabled by executing the EI instruction is performed after

executing 1 instruction (just after the next instruction is executed).

Accordingly, when the EI instruction is executed just before the RTI

instruction, interrupts are enabled after returning the main routine.

(Refer to Figure 13)

• Program counter (PC)

............................................................... Each interrupt address

• Stack register (SK)

....................................................................................................

The address of main routine to be

executed when returning

• Interrupt enable flag (INTE)

.................................................................. 0 (Interrupt disabled)

• Interrupt request flag (only the flag for the current interrupt

source)................................................................................... 0

• Data pointer, carry flag, registers A and B, skip flag

........ Stored in the interrupt stack register (SDP) automatically

Fig. 14 Internal state when interrupt occurs

INT0 pin

(L→H or

H→L input)

INT1 pin

(L→H or

H→L input)

Timer 1

underflow

EXF0

EXF1 V1

T1F V1

V1

0

1

2

Address 0

in page 1

Address 2

in page 1

Address 4

in page 1

Main

routine

Interrupt

service routine

Interrupt

occurs

•

•

•

•

EI

RTI

Interrupt is

enabled

: Interrupt enabled state

: Interrupt disabled state

Fig. 13 Program example of interrupt processing

Timer 2

underflow

Timer 3

underflow

Timer 4

underflow

Completion of

A-D conversion

Completion of

serial I/O transfer

Activated

condition

T2F V1

T3F V2

T4F V2

ADF V2

SIOF V2

Request flag

(state retained)

Fig. 15 Interrupt system diagram

3

0

1

2

3

Enable

bit

INTE

Enable

flag

Address 6

in page 1

Address 8

in page 1

Address A

in page 1

Address C

in page 1

Address E

in page 1

21

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(6) Interrupt control registers

• Interrupt control register V1

Interrupt enable bits of external 0, external 1, timer 1 and timer 2

are assigned to register V1. Set the contents of this register

through register A with the TV1A instruction. The TAV1 instruction

can be used to transfer the contents of register V1 to register A.

Table 6 Interrupt control registers

Interrupt control register V1

V13

V12

V11

V10

V23

V22

V21

V20

Note: “R” represents read enabled, and “W” represents write enabled.

Timer 2 interrupt enable bit

Timer 1 interrupt enable bit

External 1 interrupt enable bit

External 0 interrupt enable bit

Interrupt control register V2

Serial I/O interrupt enable bit

A-D interrupt enable bit

Timer 4 interrupt enable bit

Timer 3 interrupt enable bit

• Interrupt control register V2

Interrupt enable bits of timer 3, timer 4, A-D and serial I/O are assigned to register V2. Set the contents of this register through

register A with the TV2A instruction. The TAV2 instruction can be

used to transfer the contents of register V2 to register A.

0

Interrupt disabled (SNZT2 instruction is valid)

1

Interrupt enabled (SNZT2 instruction is invalid)

0

Interrupt disabled (SNZT1 instruction is valid)

1

Interrupt enabled (SNZT1 instruction is invalid)

0

Interrupt disabled (SNZ1 instruction is valid)

1

Interrupt enabled (SNZ1 instruction is invalid)

0

Interrupt disabled (SNZ0 instruction is valid)

1

Interrupt enabled (SNZ0 instruction is invalid)

at reset : 00002

0

Interrupt disabled (SNZSI instruction is valid)

1

Interrupt enabled (SNZSI instruction is invalid)

0

Interrupt disabled (SNZAD instruction is valid)

1

Interrupt enabled (SNZAD instruction is invalid)

0

Interrupt disabled (SNZT4 instruction is valid)

1

Interrupt enabled (SNZT4 instruction is invalid)

0

Interrupt disabled (SNZT3 instruction is valid)

1

Interrupt enabled (SNZT3 instruction is invalid)

at RAM back-up : 00002

R/Wat RAM back-up : 00002at reset : 00002 R/Wat RAM back-up : 00002at reset : 00002

R/W

22

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

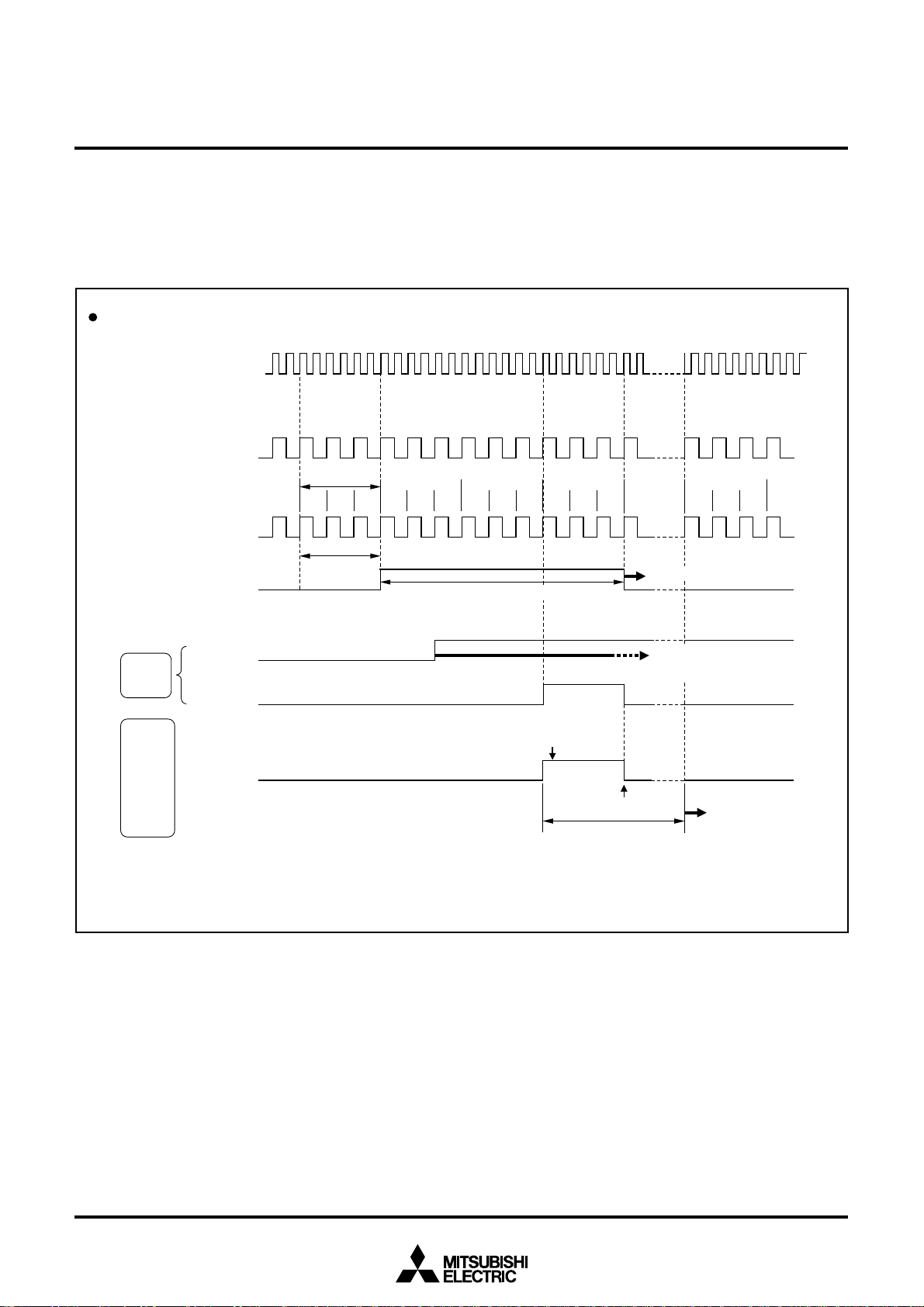

(7) Interrupt sequence

Interrupts only occur when the respective INTE flag, interrupt enable bits (V10–V13 and V20–V23), and interrupt request flag are

“1.” The interrupt actually occurs 2 to 3 machine cycles after the

cycle in which all three conditions are satisfied. The interrupt oc-

When an interrupt request flag is set after its interrupt is enabled (Note 1)

f (XIN) (middle-speed mode)

f (XIN) (high-speed mode)

1 machine cycle

System clock

Interrupt enable

flag (INTE)

T2 T3

T1

EI instruction

execution cycle

T2 T3

T1

curs after 3 machine cycles only when the three interrupt conditions are satisfied on execution of other than one-cycle instructions

(Refer to Figure 16).

T2 T3

T1

Interrupt enabled state

T2 T3

T1

Interrupt disabled state

T2 T3

T1

INT0, INT1

External

interrupt

EXF0, EXF1

Timer 1,

Timer 2,

Timer 3,

Timer 4,

A-D, and

Serial I/O

interrupts

Notes 1: The 4513/4514 Group operates in the middle-speed mode after system is released from reset.

T1F, T2F, T3F,

T4F, ADF,SIOF

2: The address is stacked to the last cycle.

3: This interval of cycles depends on the executed instruction at the time when each interrupt activated condition is satisfied.

Fig. 16 Interrupt sequence

Interrupt activated

condition is satisfied.

2 to 3 machine cycles

(Notes 2, 3)

Retaining level of system

clock for 4 periods or more

is necessary.

Flag cleared

The program starts from

the interrupt address.

23

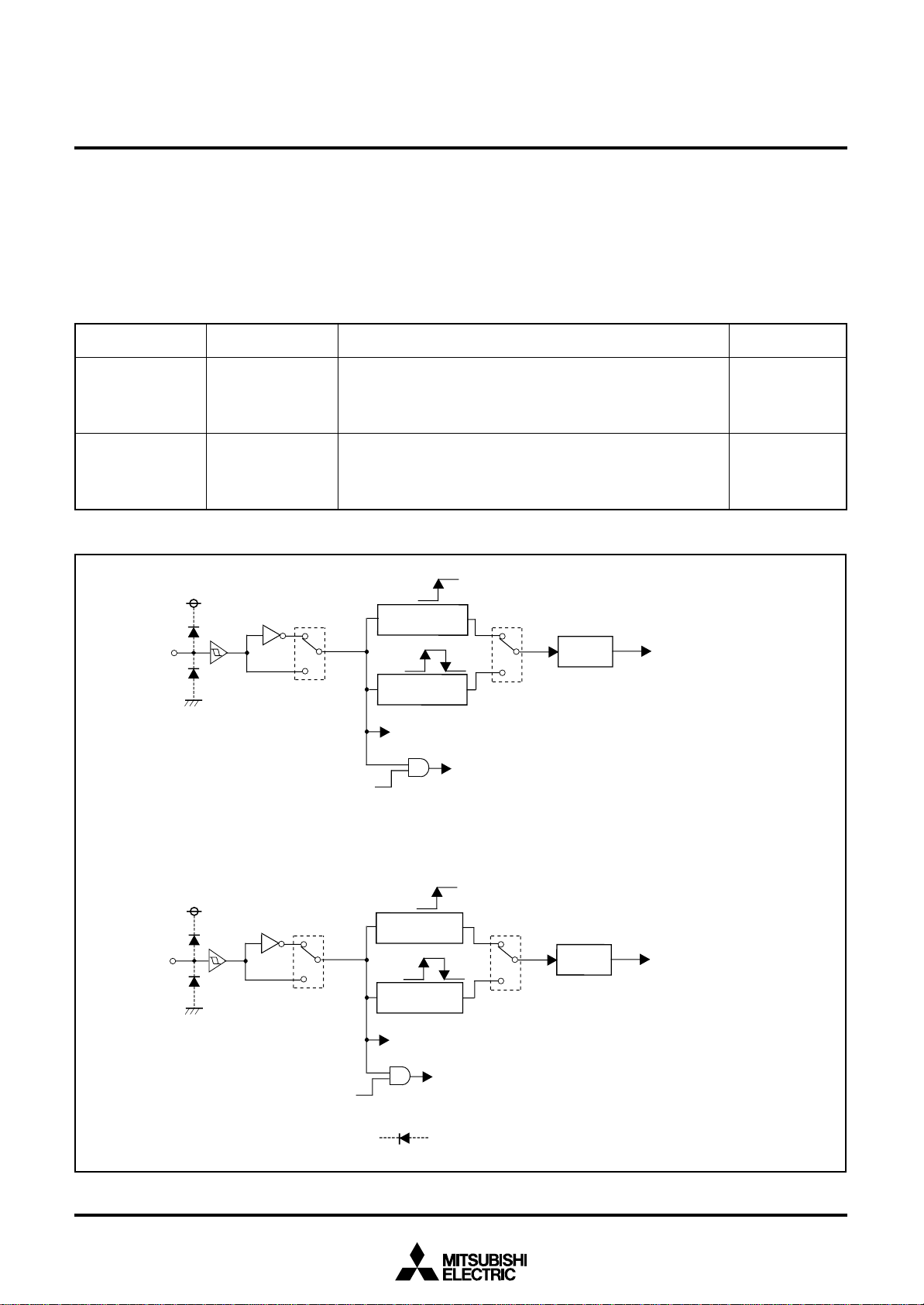

EXTERNAL INTERRUPTS

The 4513/4514 Group has two external interrupts (external 0 and

external 1). An external interrupt request occurs when a valid

waveform is input to an interrupt input pin (edge detection).

The external interrupts can be controlled with the interrupt control

registers I1 and I2.

Table 7 External interrupt activated conditions

Name

External 0 interrupt

External 1 interrupt

Input pin

P30/INT0

P31/INT1

When the next waveform is input to P30/INT0 pin

• Falling waveform (“H”→“L”)

• Rising waveform (“L”→“H”)

• Both rising and falling waveforms

When the next waveform is input to P31/INT1 pin

• Falling waveform (“H”→“L”)

• Rising waveform (“L”→“H”)

• Both rising and falling waveforms

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Activated condition

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

Valid waveform

selection bit

I11

I12

I21

I22

P3

P3

0

/INT0

1

/INT1

I1

2

Falling

Rising

I2

2

Falling

Rising

One-sided edge

0

1

0

1

detection circuit

Both edges

detection circuit

Wakeup

SNZI0

One-sided edge

detection circuit

Both edges

detection circuit

Wakeup

Skip

I1

1

0

1

I2

1

0

1

EXF0

EXF1

External 0

interrupt

External 1

interrupt

Fig. 17 External interrupt circuit structure

24

Skip

SNZI1

This symbol represents a parasitic diode on the port.

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(1) External 0 interrupt request flag (EXF0)

External 0 interrupt request flag (EXF0) is set to “1” when a valid

waveform is input to P30/INT0 pin.

The valid waveforms causing the interrupt must be retained at their

level for 4 clock cycles or more of the system clock (Refer to Figure

16).

The state of EXF0 flag can be examined with the skip instruction

(SNZ0). Use the interrupt control register V1 to select the interrupt

or the skip instruction. The EXF0 flag is cleared to “0” when an interrupt occurs or when the next instruction is skipped with the skip

instruction.

The P30/INT0 pin need not be selected the external interrupt input

INT0 function or the normal I/O port P30 function. However, the

EXF0 flag is set to “1” when a valid waveform is input even if it is

used as an I/O port P30.

• External 0 interrupt activated condition

External 0 interrupt activated condition is satisfied when a valid

waveform is input to P30/INT0 pin.

The valid waveform can be selected from rising waveform, falling

waveform or both rising and falling waveforms. An example of

how to use the external 0 interrupt is as follows.

➀ Select the valid waveform with the bits 1 and 2 of register I1.

➁ Clear the EXF0 flag to “0” with the SNZ0 instruction.

➂ Set the NOP instruction for the case when a skip is performed

with the SNZ0 instruction.

➃ Set both the external 0 interrupt enable bit (V10) and the INTE

flag to “1.”

(2) External 1 interrupt request flag (EXF1)

External 1 interrupt request flag (EXF1) is set to “1” when a valid

waveform is input to P31/INT1 pin.

The valid waveforms causing the interrupt must be retained at their

level for 4 clock cycles or more of the system clock (Refer to Figure

16).

The state of EXF1 flag can be examined with the skip instruction

(SNZ1). Use the interrupt control register V1 to select the interrupt

or the skip instruction. The EXF1 flag is cleared to “0” when an interrupt occurs or when the next instruction is skipped with the skip

instruction.

The P31/INT1 pin need not be selected the external interrupt input

INT1 function or the normal I/O port P31 function. However, the

EXF1 flag is set to “1” when a valid waveform is input even if it is

used as an I/O port P31.

• External 1 interrupt activated condition

External 1 interrupt activated condition is satisfied when a valid

waveform is input to P31/INT1 pin.

The valid waveform can be selected from rising waveform, falling

waveform or both rising and falling waveforms. An example of

how to use the external 1 interrupt is as follows.

➀ Select the valid waveform with the bits 1 and 2 of register I2.

➁ Clear the EXF1 flag to “0” with the SNZ1 instruction.

➂ Set the NOP instruction for the case when a skip is performed

with the SNZ1 instruction.

➃ Set both the external 1 interrupt enable bit (V11) and the INTE

flag to “1.”

The external 0 interrupt is now enabled. Now when a valid waveform is input to the P30/INT0 pin, the EXF0 flag is set to “1” and the

external 0 interrupt occurs.

The external 1 interrupt is now enabled. Now when a valid waveform is input to the P31/INT1 pin, the EXF1 flag is set to “1” and the

external 1 interrupt occurs.

25

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(3) External interrupt control registers

• Interrupt control register I1

Register I1 controls the valid waveform for the external 0 interrupt. Set the contents of this register through register A with the

TI1A instruction. The TAI1 instruction can be used to transfer the

contents of register I1 to register A.

Table 8 External interrupt control registers

Interrupt control register I1 R/Wat RAM back-up : state retained

I13

I12

I11

I10

I23

I22

I21

I20

Notes 1: “R” represents read enabled, and “W” represents write enabled.

Not used

Interrupt valid waveform for INT0 pin/

return level selection bit (Note 2)

INT0 pin edge detection circuit control bit

INT0 pin

timer 1 control enable bit

Interrupt control register I2 R/Wat RAM back-up : state retainedat reset : 00002

Not used

Interrupt valid waveform for INT1 pin/

return level selection bit (Note 3)

INT1 pin edge detection circuit control bit

INT1 pin

timer 3 control enable bit

2: When the contents of I1

3: When the contents of I2

2 is changed, the external interrupt request flag EXF0 may be set. Accordingly, clear EXF0 flag with the SNZ0 instruction.

2 is changed, the external interrupt request flag EXF1 may be set. Accordingly, clear EXF1 flag with the SNZ1 instruction.

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

• Interrupt control register I2

Register I2 controls the valid waveform for the external 1 interrupt. Set the contents of this register through register A with the

TI2A instruction. The TAI2 instruction can be used to transfer the

contents of register I2 to register A.

at reset : 00002

This bit has no function, but read/write is enabled.

Falling waveform (“L” level of INT0 pin is recognized with the SNZI0

instruction)/“L” level

Rising waveform (“H” level of INT0 pin is recognized with the SNZI0

instruction)/“H” level

One-sided edge detected

Both edges detected

Disabled

Enabled

This bit has no function, but read/write is enabled.

Falling waveform (“L” level of INT1 pin is recognized with the SNZI1

instruction)/“L” level

Rising waveform (“H” level of INT1 pin is recognized with the SNZI1

instruction)/“H” level

One-sided edge detected

Both edges detected

Disabled

Enabled

26

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

TIMERS

The 4513/4514 Group has the programmable timers.

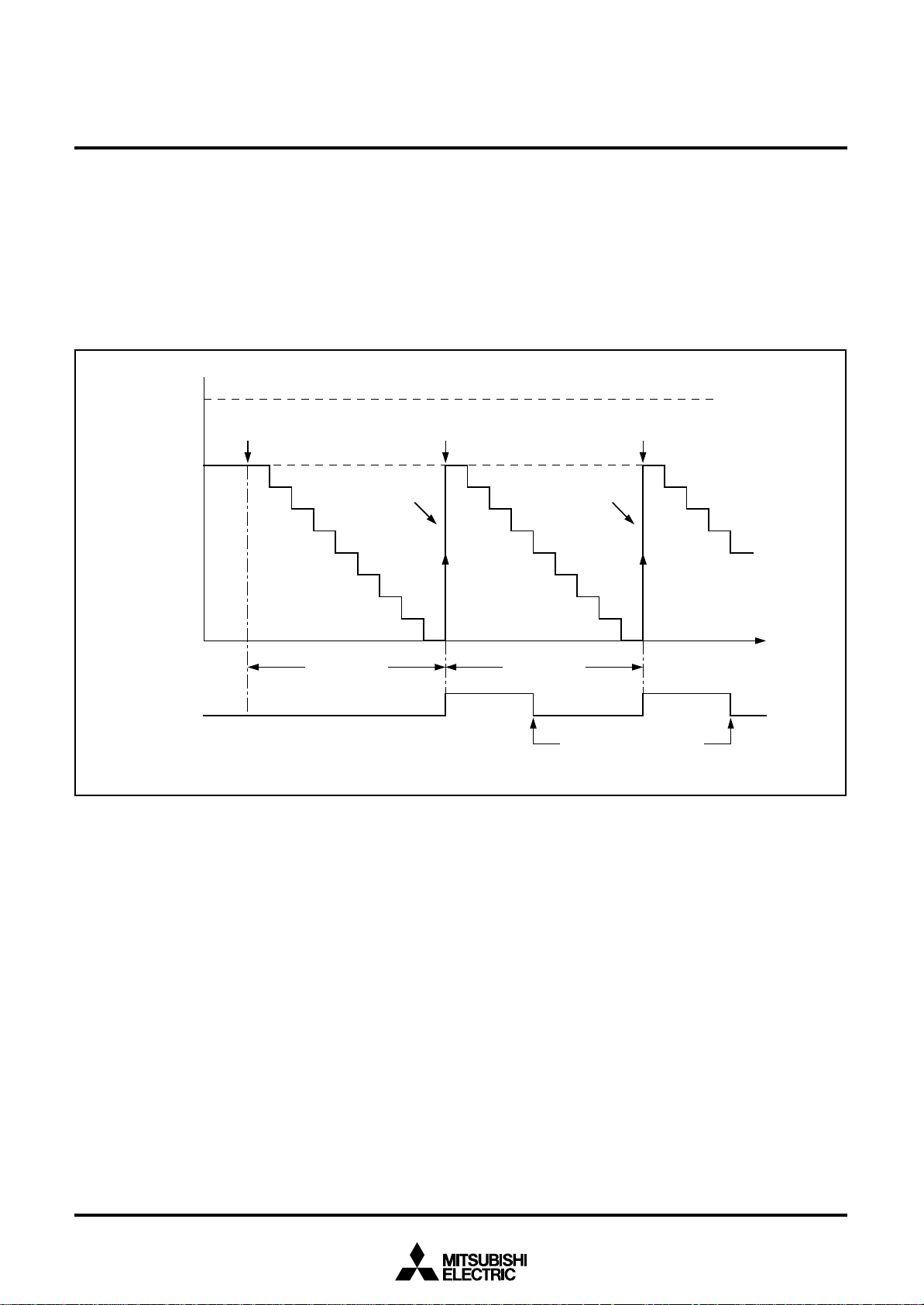

• Programmable timer

The programmable timer has a reload register and enables the

frequency dividing ratio to be set. It is decremented from a setting

value n. When it underflows (count to n + 1), a timer interrupt request flag is set to “1,” new data is loaded from the reload

register, and count continues (auto-reload function).

FF

16

n : Counter initial value

Count starts

n

1st underflow 2nd underflow

The contents of counter

16

00

n+1 count n+1 count

• Fixed dividing frequency timer

The fixed dividing frequency timer has the fixed frequency dividing ratio (n). An interrupt request flag is set to “1” after every n

count of a count pulse.

Reload Reload

Time

Timer interrupt

request flag

Fig. 18 Auto-reload function

“1”

“0”

An interrupt occurs or

a skip instruction is executed.

27

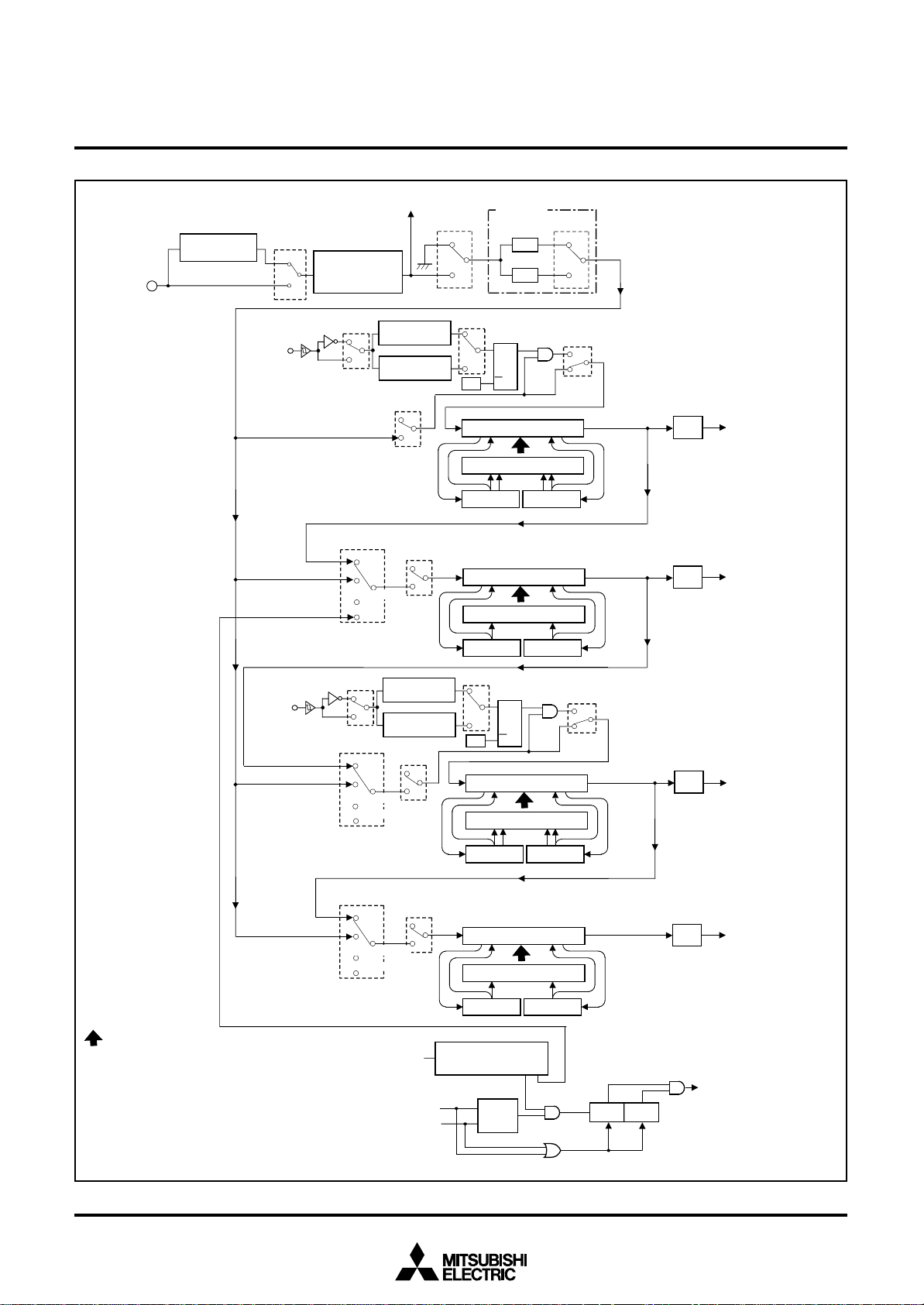

The 4513/4514 Group timer consists of the following circuits.

• Prescaler : frequency divider

• Timer 1 : 8-bit programmable timer

• Timer 2 : 8-bit programmable timer

• Timer 3 : 8-bit programmable timer

• Timer 4 : 8-bit programmable timer

(Timers 1 to 4 have the interrupt function, respectively)

• 16-bit timer

Prescaler and timers 1 to 4 can be controlled with the timer control

registers W1 to W6. The 16-bit timer is a free counter which is not

controlled with the control register.

Each function is described below.

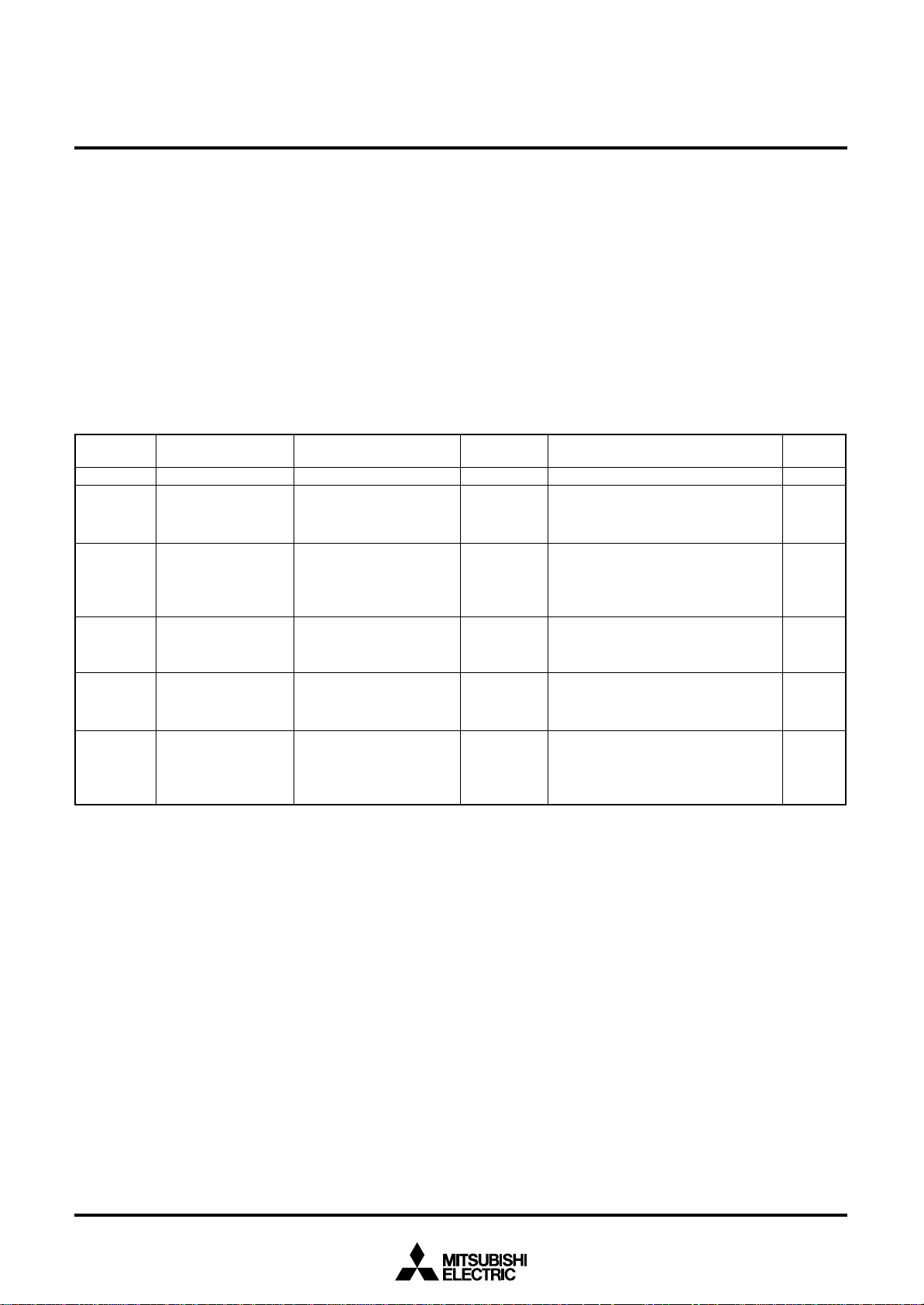

Table 9 Function related timers

Circuit

Prescaler

Timer 1

Timer 2

Timer 3

Timer 4

16-bit timer

Structure

Frequency divider

8-bit programmable

binary down counter

(link to P30/INT0 input)

8-bit programmable

binary down counter

8-bit programmable

binary down counter

(link to P31/INT1 input)

8-bit programmable

binary down counter

16-bit fixed dividing

frequency

Count source

• Instruction clock

• Prescaler output (ORCLK)

• Timer 1 underflow

• Prescaler output (ORCLK)

• CNTR0 input

• 16-bit timer underflow

• Timer 2 underflow

• Prescaler output (ORCLK)

• Timer 3 underflow

• Prescaler output (ORCLK)

• CNTR1 input

• Instruction clock

Frequency

dividing ratio

4, 16

1 to 256

1 to 256

1 to 256

1 to 256

65536

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Use of output signal

• Timer 1, 2, 3 and 4 count sources

• Timer 2 count source

• CNTR0 output

• Timer 1 interrupt

• Timer 3 count source

• Timer 2 interrupt

• CNTR0 output

• Timer 4 count source

• Timer 3 interrupt

• CNTR1 output

• Timer 4 interrupt

• CNTR1 output

• Watchdog timer

(The 15th bit is counted twice)

• Timer 2 count source

(16-bit timer underflow)

Control

register

W1

W1

W6

W2

W6

W3

W6

W4

W6

28

MITSUBISHI MICROCOMPUTERS

4513/4514 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Instruction clock

W1

Divistion circuit

(divided by 2)

X

IN

P30/INT0

MR

3

1

0

Internal clock

generating circuit

(divided by 3)

I1

2

One-sided edge

Falling

detection circuit

0

1

Both edges

detection circuit

Rising

1

(Note 3)W1

0

1

3

0

1

I1

I1

1

0

(Note 1)

1

0

Timer 1 (8)

Prescaler

1/4

1/16

Q

S

R

W1

ORCLK

W1

2

0

1

0

1

0

T1F

Timer 1

interrupt

Reload register R1 (8)

T1AB

Register A

Register A

Timer 2 underflow signal

W3

2

1

0

T3AB

Register A

T2F

T3F

Timer 2

interrupt

Timer 3

interrupt

P31/INT1

W21,W2

00

01

Not available

10

11

I2

2

Falling

0

1

Rising

W31,W3

00

01

Not available

10

11

Not available

(TAB1)

0

W23(Note 3)

0

1

(TAB2)

One-sided edge

detection circuit

Both edges

detection circuit

0

W33(Note 3)

0

1

(TAB3)

T1AB

(TR1AB)

Register B

Timer 1 underflow signal

Timer 2 (8)

Reload register R2 (8)

(T2AB)

Register B

I2

1

0

(Note 2)

Q

S

1

I2

0

R

Timer 3 (8)

Reload register R3 (8)

T3AB

(TR3AB)

Register B

Data is set automatically from each reload

register when timer 1, 2, 3, or 4 underflows

(auto-reload function)

Notes 1: Timer 1 count start synchronous circuit is set

by the valid edge of P3

bits 1 (I1

1

) and 2 (I12) of register I1.

0

/INT0 pin selected by

2: Timer 3 count start synchronous circuit is set

by the valid edge of P3

bits 1 (I2

1

) and 2 (I22) of register I2.

1

/INT1 pin selected by

3: Count source is stopped by clearing to “0.”

Fig. 19 Timers structure

29

W41,W4

0

00

01

Not available

10

Not available

11

W43(Note 3)

(TAB4)

Instruction clock

WRST instruction

Reset signal

Timer 3 underflow signal

0

1

Reload register R4 (8)

Register B

16-bit timer (WDT)

1 - - - - - - - - - - - 15 16

S

WEF

R

Timer 4 (8)

(T4AB)

Register A

Q

WDF1 WDF2

T4F

System reset

Timer 4

interrupt

Loading...

Loading...