Page 1

查询M30201供应商

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi microcomputers

M30201 Group

Description

Description

The M30201 group of single-chip microcomputers are built using the high-performance silicon gate CMOS

process using a M16C/60 Series CPU core. M30201 group is packaged in a 52-pin plastic molded SDIP, or

56-pin plastic molded QFP. These single-chip microcomputers operate using sophisticated instructions

featuring a high level of instruction efficiency. With 1M bytes of address space, they are capable of executing instructions at high speed.

The M30201 group includes a wide range of products with different internal memory types and sizes and

various package types.

Features

• Basic machine instructions ..................Compatible with the M16C/60 series

• Memory capacity..................................ROM/RAM (See figure 1.4. ROM expansion.)

• Shortest instruction execution time......

• Supply voltage .....................................4.0 to 5.5V (f(XIN)=10MHz) :mask ROM version

• Interrupts..............................................9 internal and 3 external interrupt sources, 4 software

• Multifunction 16-bit timer......................Timer A x 1, timer B x 2, timer X x 3

• Clock output

• Serial I/O..............................................1 channel

• A-D converter.......................................10 bits X 8 channels (Expandable up to 13 channels)

• Watchdog timer....................................1 line

• Programmable I/O ...............................43 lines

• LED drive ports ....................................8 ports

• Clock generating circuit .......................2 built-in clock generation circuits

100ns (f(XIN)=10MHz)

2.7 to 5.5V (f(XIN)=7MHz with software one-wait):mask ROM

version

4.0 to 5.5V (f(XIN)=10MHz) :flash memory version

(including key input interrupt)

for UART or clock synchronous, 1 for UART

(built-in feedback resistor, and external ceramic or quartz oscillator)

Applications

Home appliances, Audio, office equipment, Automobiles

------Table of Contents------

Central Processing Unit (CPU) .....................12

Reset.............................................................15

Clock Generating Circuit ............................... 19

Protection......................................................26

Interrupts.......................................................27

Watchdog Timer............................................35

Specifications written in this manual are believed to

be accurate, but are not guaranteed to be entirely

free of error.

Specifications in this manual may be changed for

functional or performance improvements. Please

make sure your manual is the latest edition.

Timer.............................................................37

Serial I/O ....................................................... 64

A-D Converter ............................................... 78

Programmable I/O Ports ...............................88

Electric Characteristics ................................. 95

Flash Memory version.................................126

1

Page 2

Under

development

Description

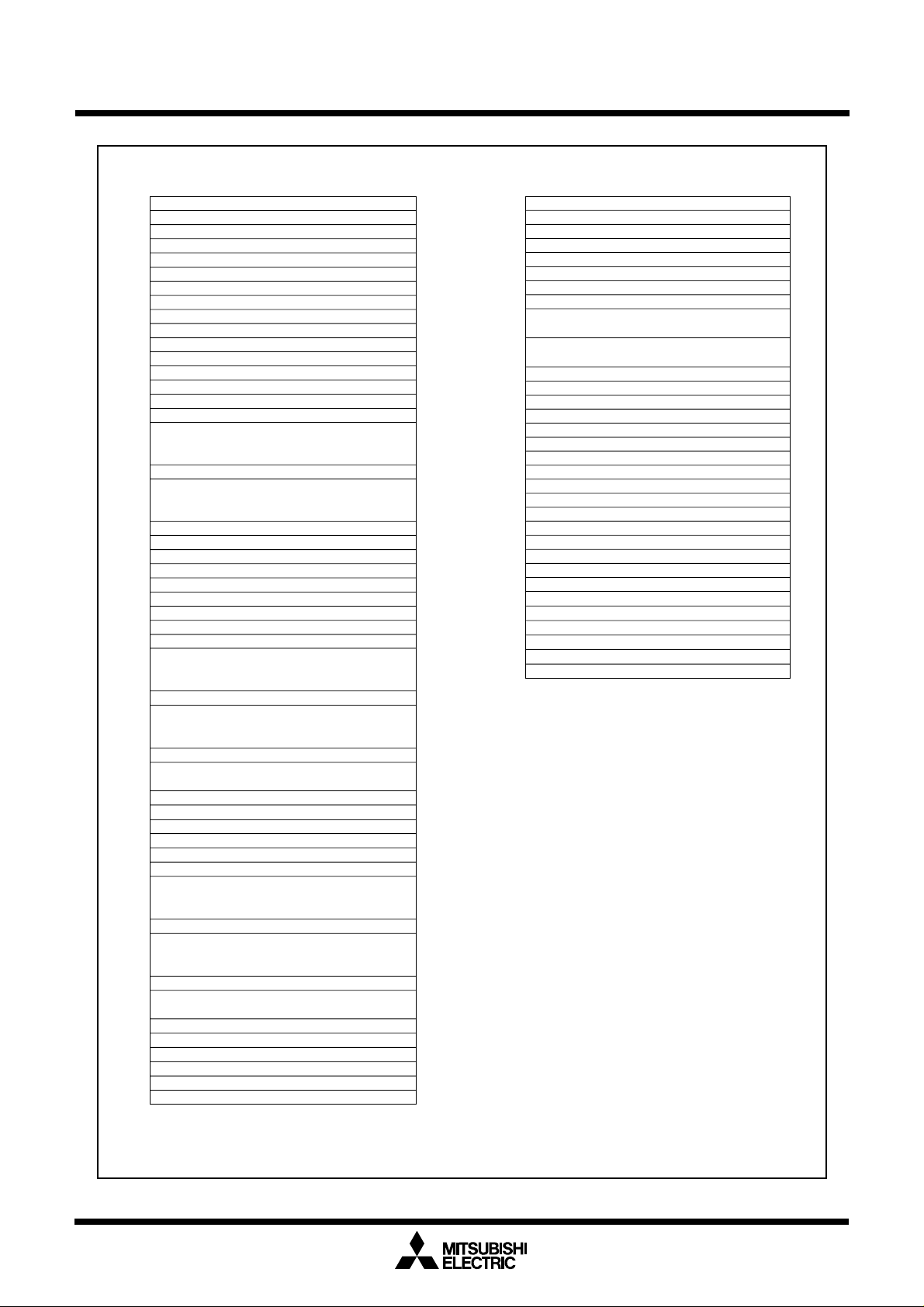

Pin Configuration

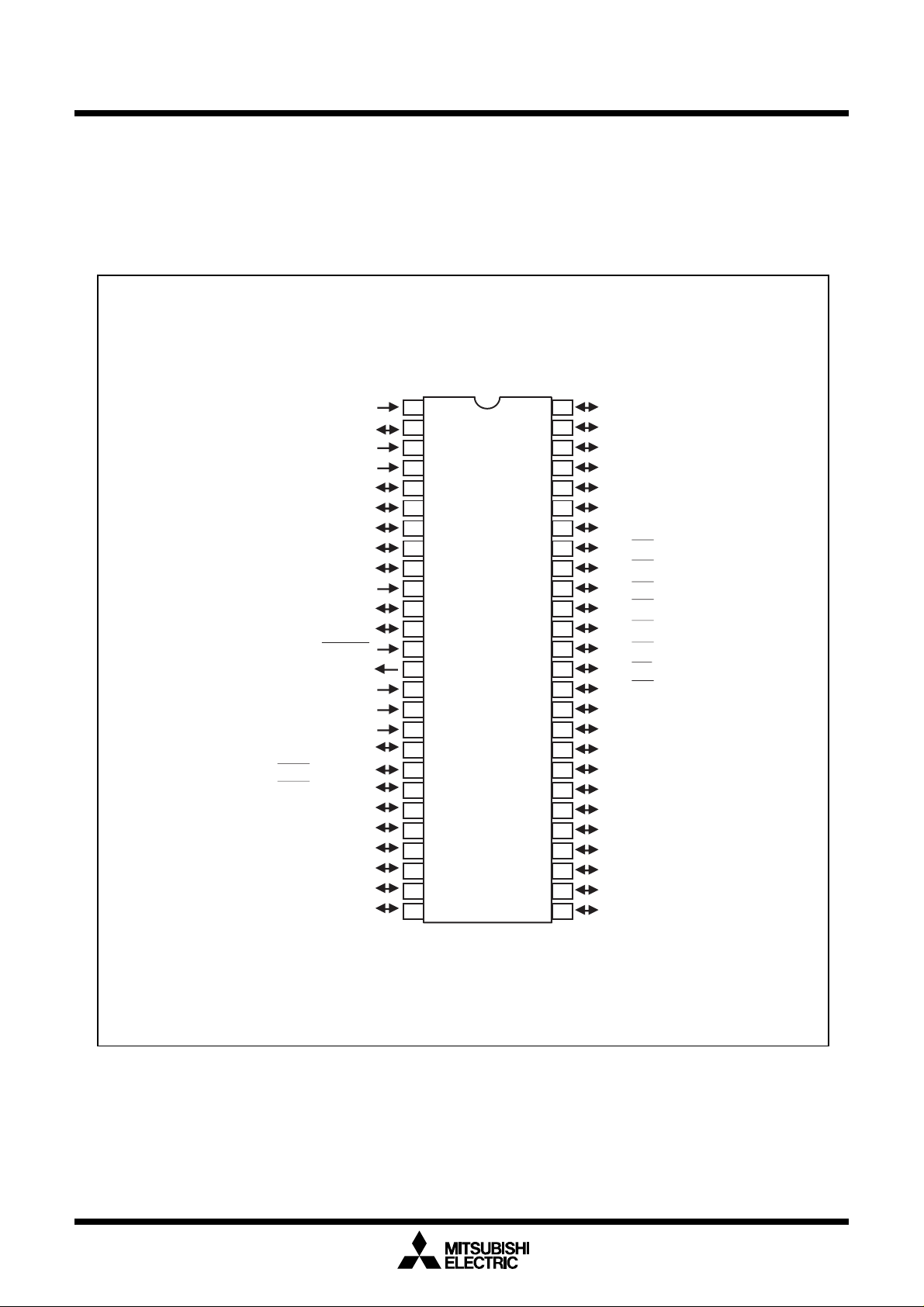

Figures 1.1 to 1.2 show the pin configurations (top view).

PIN CONFIGURATION (top view)

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

P60/AN

P54/CK

OUT

P53/CLKS/AN

P52/CLK0/AN

P51/RXD0/AN

P50/TXD0/AN

P71/TB1IN/X

P70/TB0IN/X

RESET

P45/TX2

P44/INT1/TX1

P43/INT0/TX0

P42/RXD

P41/TA0

P40/TA0IN/TXD

AV

V

AV

/AN

CNV

COUT

X

INOUT

INOUT

INOUT

REF

CIN

OUT

V

X

V

OUT

P3

P3

P3

SS

CC

54

53

52

51

SS

SS

CC

1

0

2

3

4

5

6

7

M30201F6TSP

M30201F6SP

8

50

9

M30201MXT-XXXSP

10

11

12

13

14

15

16

IN

17

18

19

20

1

21

22

1

23

24

5

4

25

3

26

52

51

50

49

48

47

46

M30201MX-XXXSP

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

P61/AN

P62/AN

P63/AN

P64/AN

P65/AN

P66/AN

P67/AN

P00/KI

P01/KI

P02/KI

P03/KI

P04/KI

P05/KI

P06/KI

P07/KI

P3

P3

P3

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

P10(LED0)

P1

1

(LED1)

P1

2

(LED2)

3

(LED3)

P1

P1

4

(LED4)

5

(LED5)

P1

P1

6

(LED6)

P1

7

(LED7)

0

1

2

Package: 52P4B

Figure 1.1. Pin configuration for the M30201 group (shrink DIP product) (top view)

2

Page 3

Under

development

Description

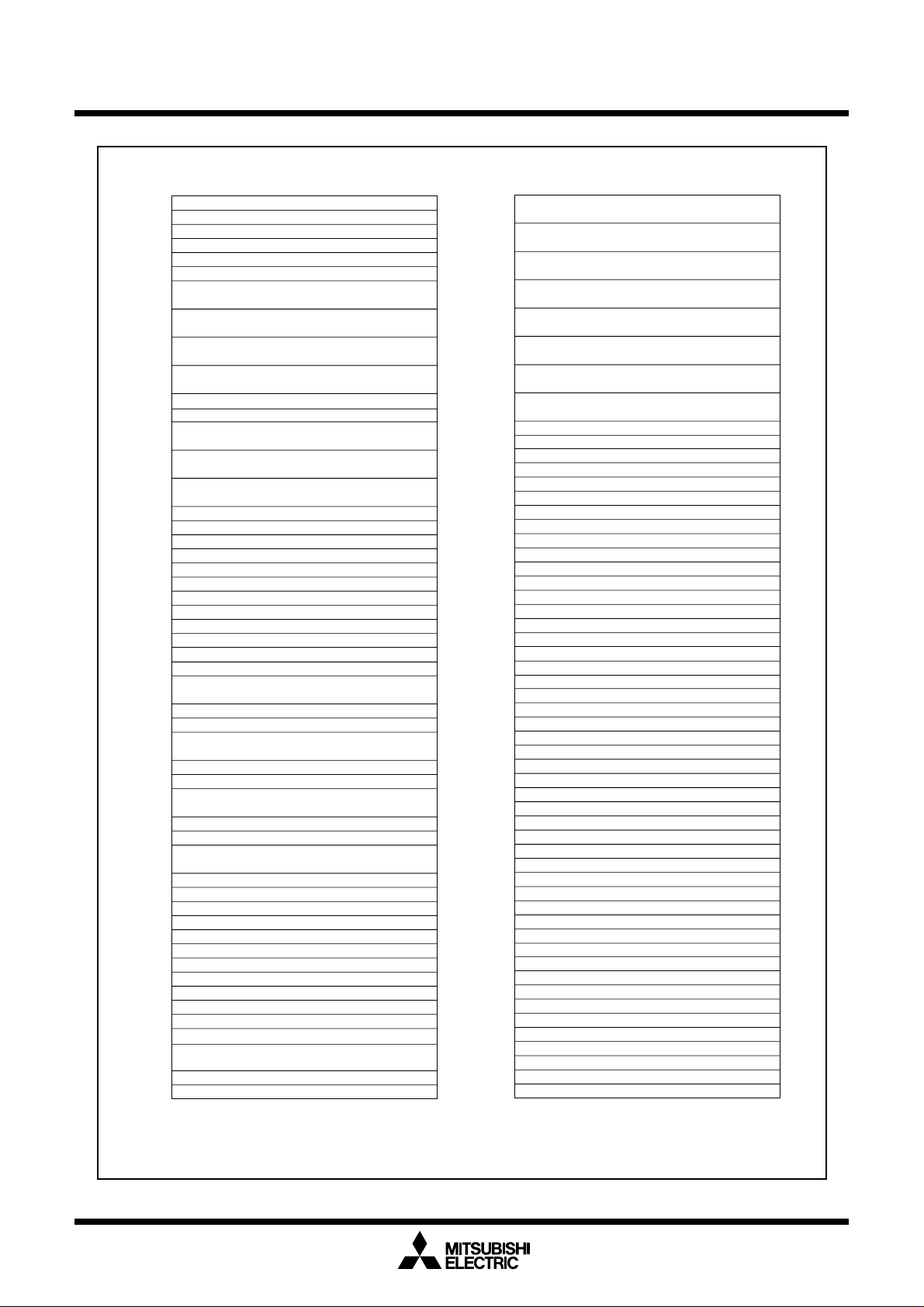

PIN CONFIGURATION (top view)

53

52

/AN

0

/CLK

/CLKS/AN

2

3

P5

P5

54

/AN

OUT

/CK

4

P5

N.C.

CC

AV

REF

V

0

/AN

0

P6

SS

AV

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

6

4

2

3

1

/AN

1

P6

/AN

2

P6

/AN

3

P6

/AN

4

P6

5

/AN

5

P6

/AN

6

P6

P51/RXD0/AN

P50/TXD0/AN

P71/TB1IN/X

P70/TB0IN/X

RESET

P45/TX2

P44/INT1/TX1

P43/INT0/TX0

CNV

COUT

N.C.

X

INOUT

INOUT

INOUT

OUT

V

X

V

51

50

SS

CIN

SS

CC

56

55

54

53

52

51

50

49

48

1

2

3

4

5

6

7

8

9

10

IN

M30201MX-XXXFP

M30201MXT-XXXFP

M30201F6FP

M30201F6TFP

11

12

13

14

16

OUT

/TA0

1

P4

17

1

D

X

/T

IN

/TA0

0

18

N.C.

5

P3

19

20

4

P3

21

3

P3

22

2

P3

23

1

P3

15

1

D

X

/R

2

P4

47

24

0

P3

46

25

)

7

(LED

7

P1

45

26

)

6

(LED

6

P1

44

27

)

5

(LED

5

P1

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

)

4

(LED

4

P1

P67/AN

7

N.C.

P00/KI

0

P01/KI

1

P02/KI

2

P03/KI

3

P04/KI

4

P05/KI

5

P06/KI

6

P07/KI

7

P10(LED0)

P11(LED1)

2

(LED2)

P1

P1

3

(LED3)

43

P4

Package: 56P6S-A

Figure 1.2. Pin configuration for the M30201 group (QFP product) (top view)

3

Page 4

Under

A

A

A

development

Description

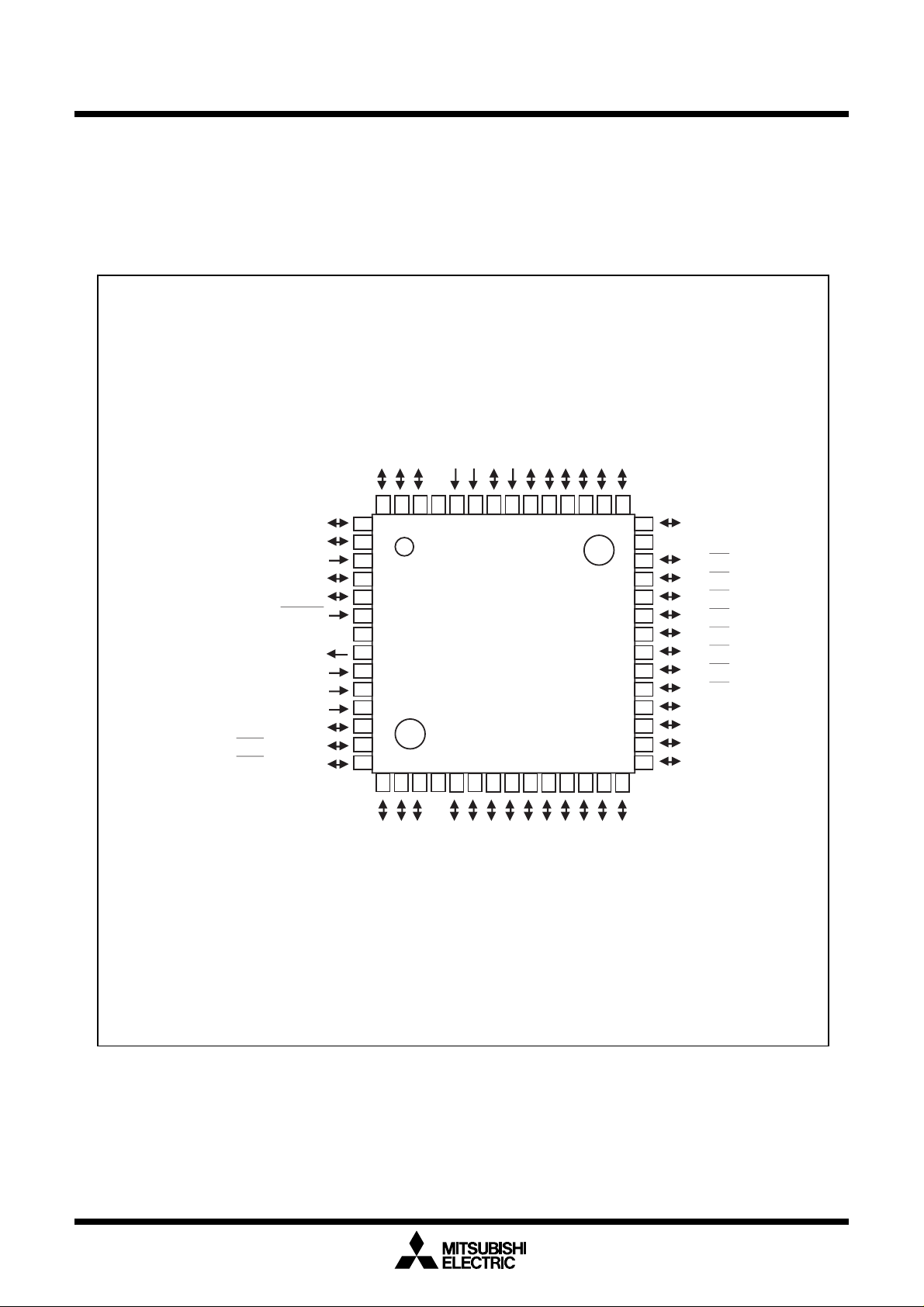

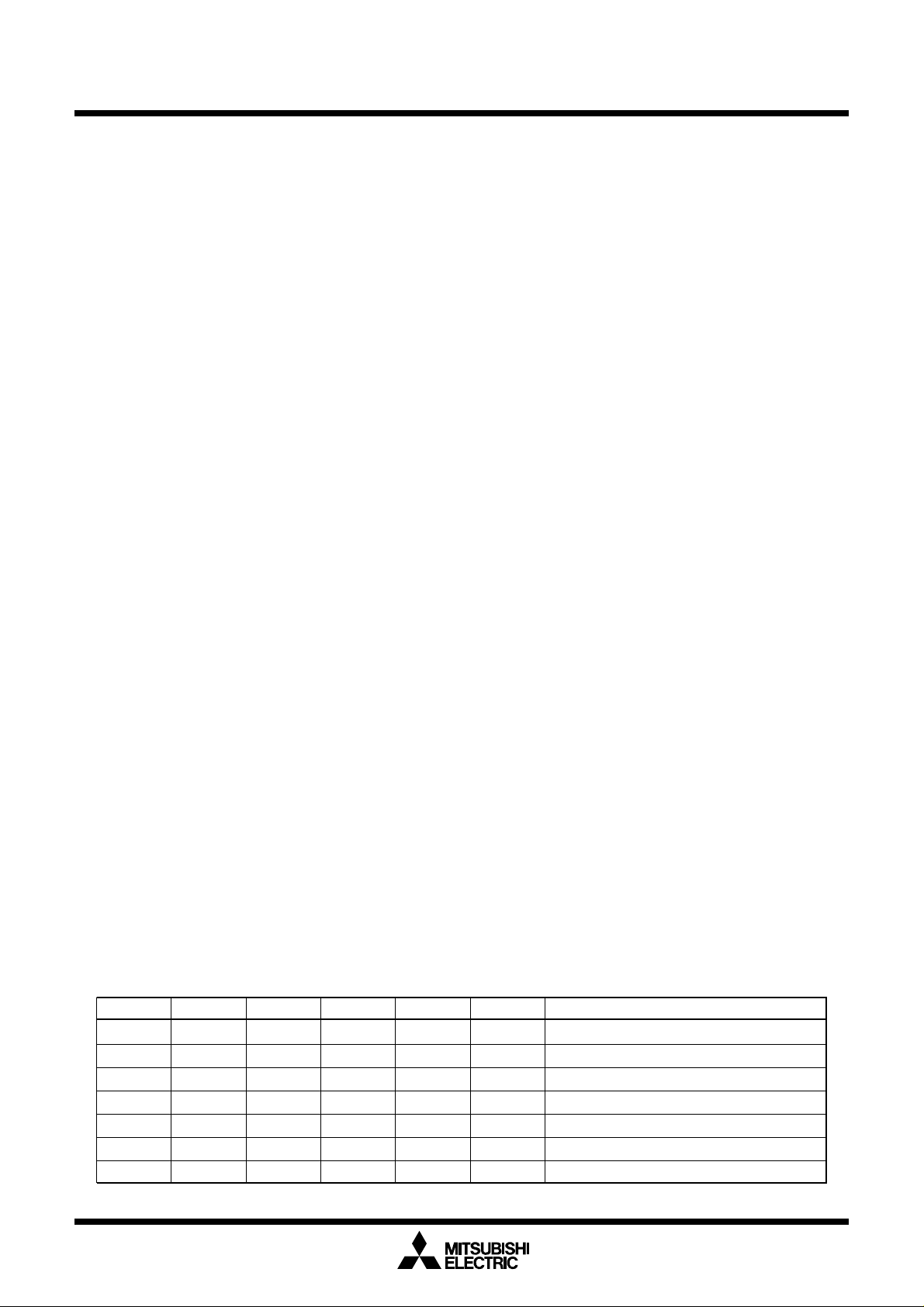

Block Diagram

Figure 1.3 is a block diagram of the M30201 group.

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

I/O ports

Internal peripheral functions

Timer TA0 (16 bits)

Timer TB0 (16 bits)

Timer TB1 (16 bits)

Timer TX0 (16 bits)

Timer TX1 (16 bits)

Timer TX2 (16 bits)

Watchdog timer

Port P08Port P1

Timer

(15 bits)

8

Port P36Port P46Port P55Port P6

A-D converter

(10 bits X 8 channels

Expandable up to 13 channels)

UART/clock synchronous SI/O

(8 bits X 1 channel)

UART

(8 bits X 1 channel)

M16C/60 series16-bit CPU core

Registers

R0LR0H

R1H R1L

R0LR0H

R1H R1L

R2

R2

R3

R3

A0

A0

A1

A1

FB

FB

SB FLG

Program counter

PC

Vector table

INTB

Stack pointer

ISP

USP

8

System clock generator

IN-XOUT

X

XCIN-XCOUT

Memory

AAAAA

AAAAA

ROM

(Note 1)

RAM

(Note 2)

AAAAA

Multiplier

2

Port P7

Note 1: ROM size depends on MCU type.

Note 2: RAM size depends on MCU type.

Figure 1.3. Block diagram for the M30201 group

4

Page 5

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Description

Performance Outline

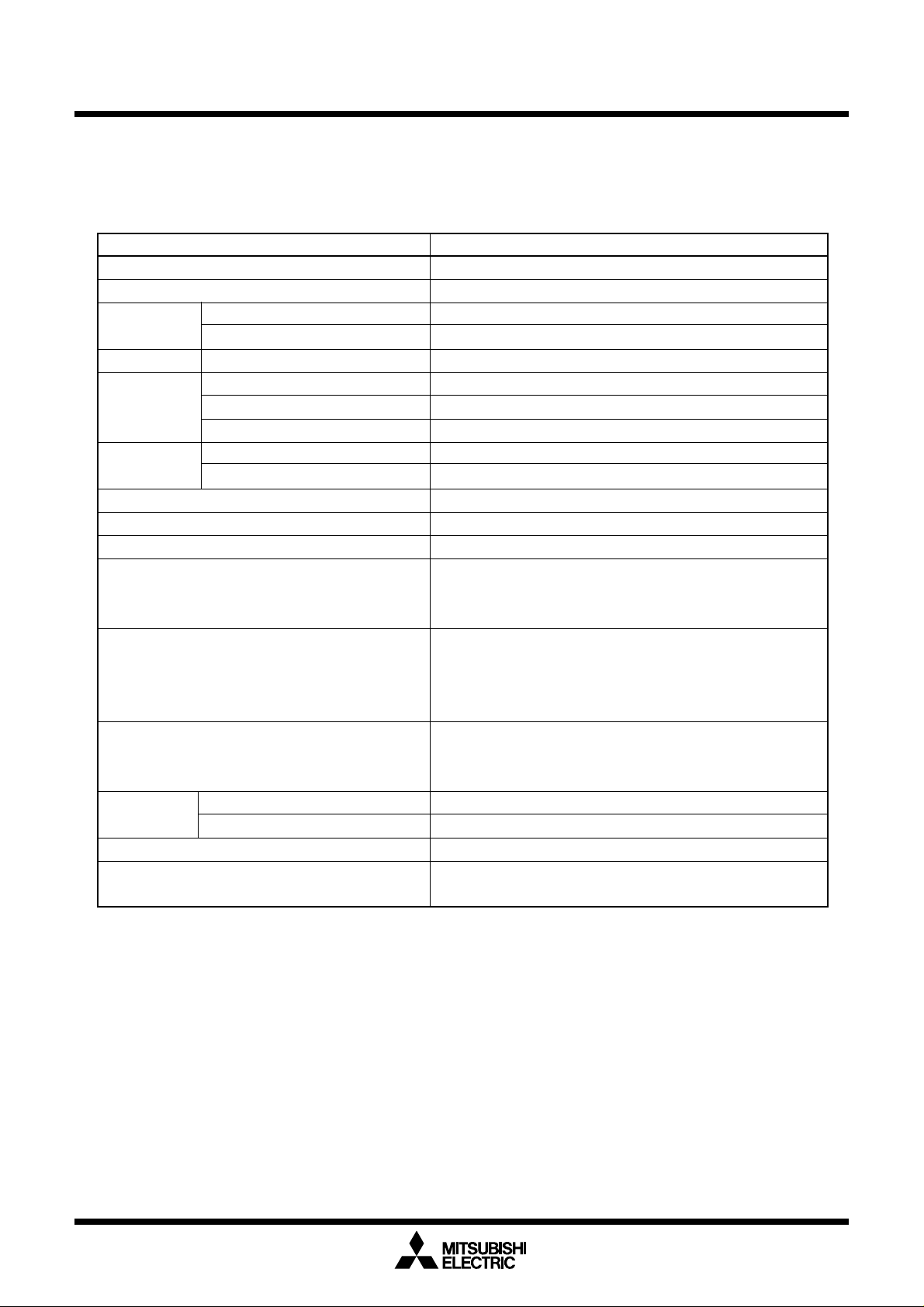

Table 1.1 is performance outline of M30201 group.

Table 1.1. Performance outline of M30201 group

Item Performance

Number of basic instructions 91 instructions

Shortest instruction execution time 100ns (f(XIN)=10MHz

Memory ROM (See figure 4. ROM expansion.)

capacity RAM (See figure 4. ROM expansion.)

I/O port P0 to P7 43 lines

Multifunction TA0 16 bits x 1

timer TB0, TB1 16 bits x 2

TX0, TX1, TX2 16 bits x 3

Serial I/O UART0 (UART or clock synchronous) x 1

UART1 UART x 1

A-D converter 10 bits x 8 channels (Expandable up to 13 channels)

Watchdog timer 15 bits x 1 (with prescaler)

Interrupt 9 internal and 3 external sources, 4 software sources

Clock generating circuit 2 built-in clock generation circuits

(built-in feedback resistor, and external ceramic or

quartz oscillator)

Supply voltage 4.0 to 5.5V (f(XIN)=10MHz) :mask ROM version

2.7 to 5.5V (f(XIN)=7MHz with software one-wait) :mask

ROM version

4.0 to 5.5V (f(XIN)=10MHz) :flash memory version

Power consumption 18mW (f(XIN)=7MHz with software one-wait, Vcc=3V)

:mask ROM version

95mW (f(XIN)=10MHz no wait, Vcc=5V) :flash memory version

I/O I/O withstand voltage 5V

characteristics Output current 5mA (15mA:LED drive port)

Device configuration CMOS silicon gate

Package 52-pin plastic mold SDIP

56-pin plastic mold QFP

5

Page 6

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Description

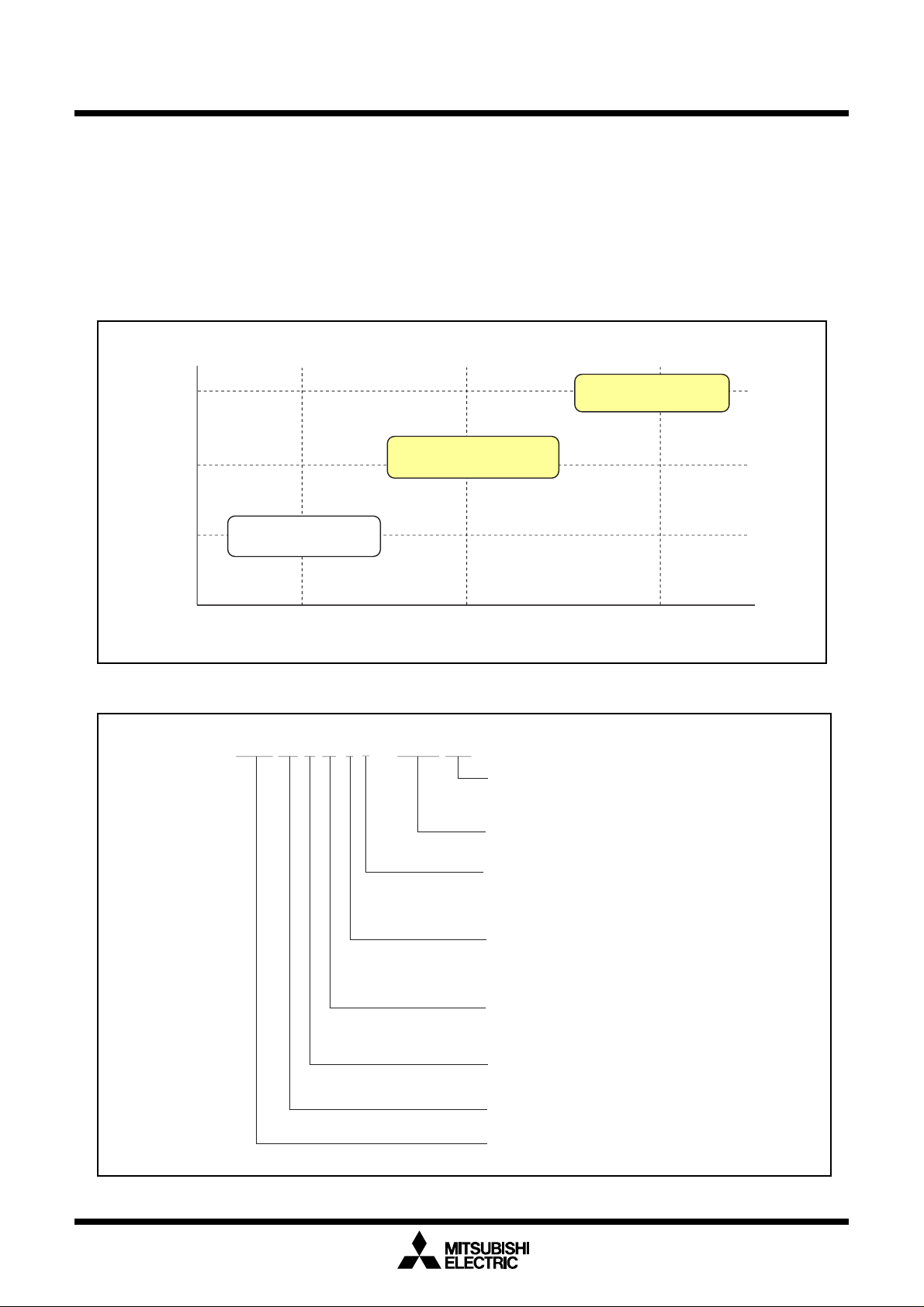

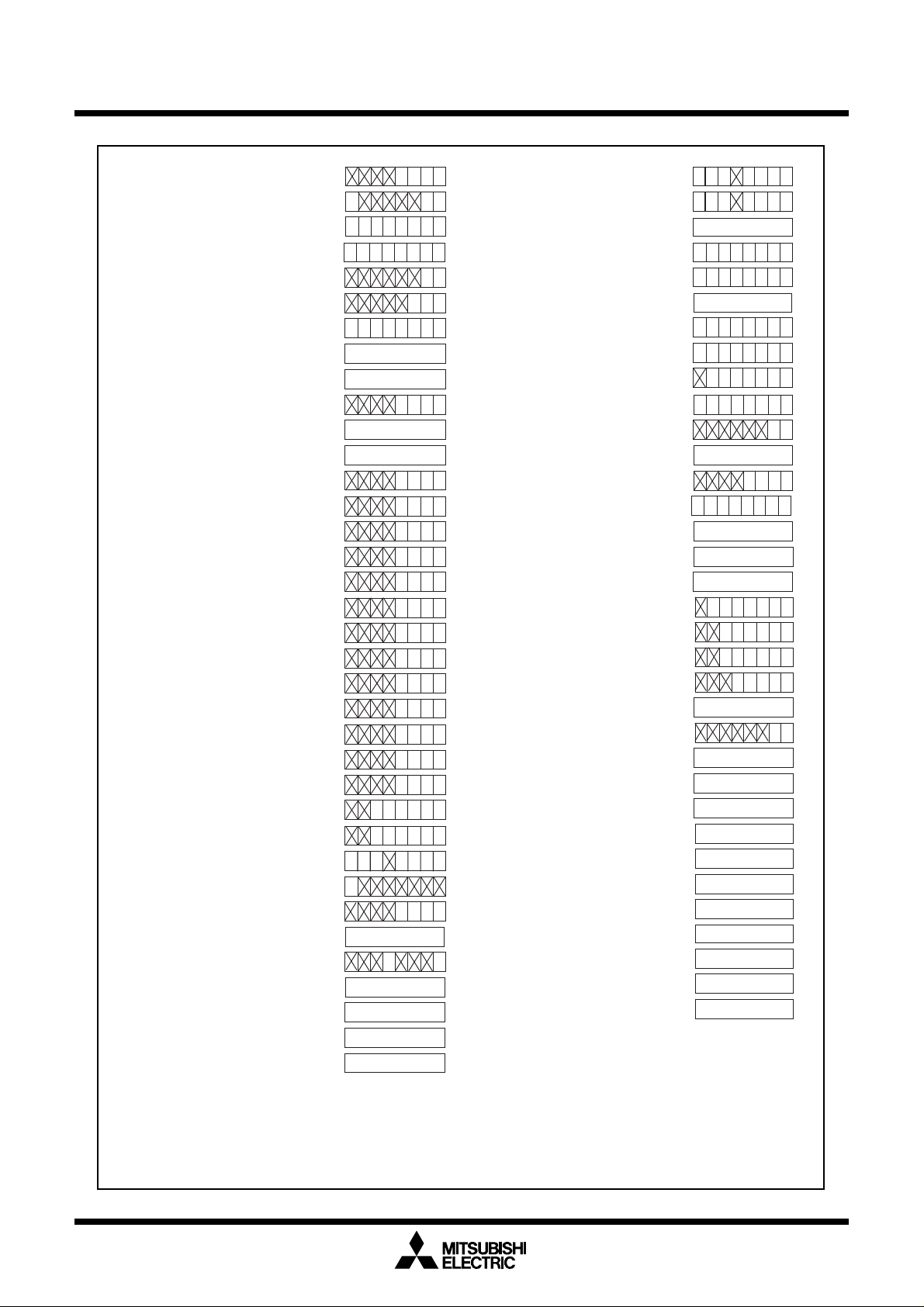

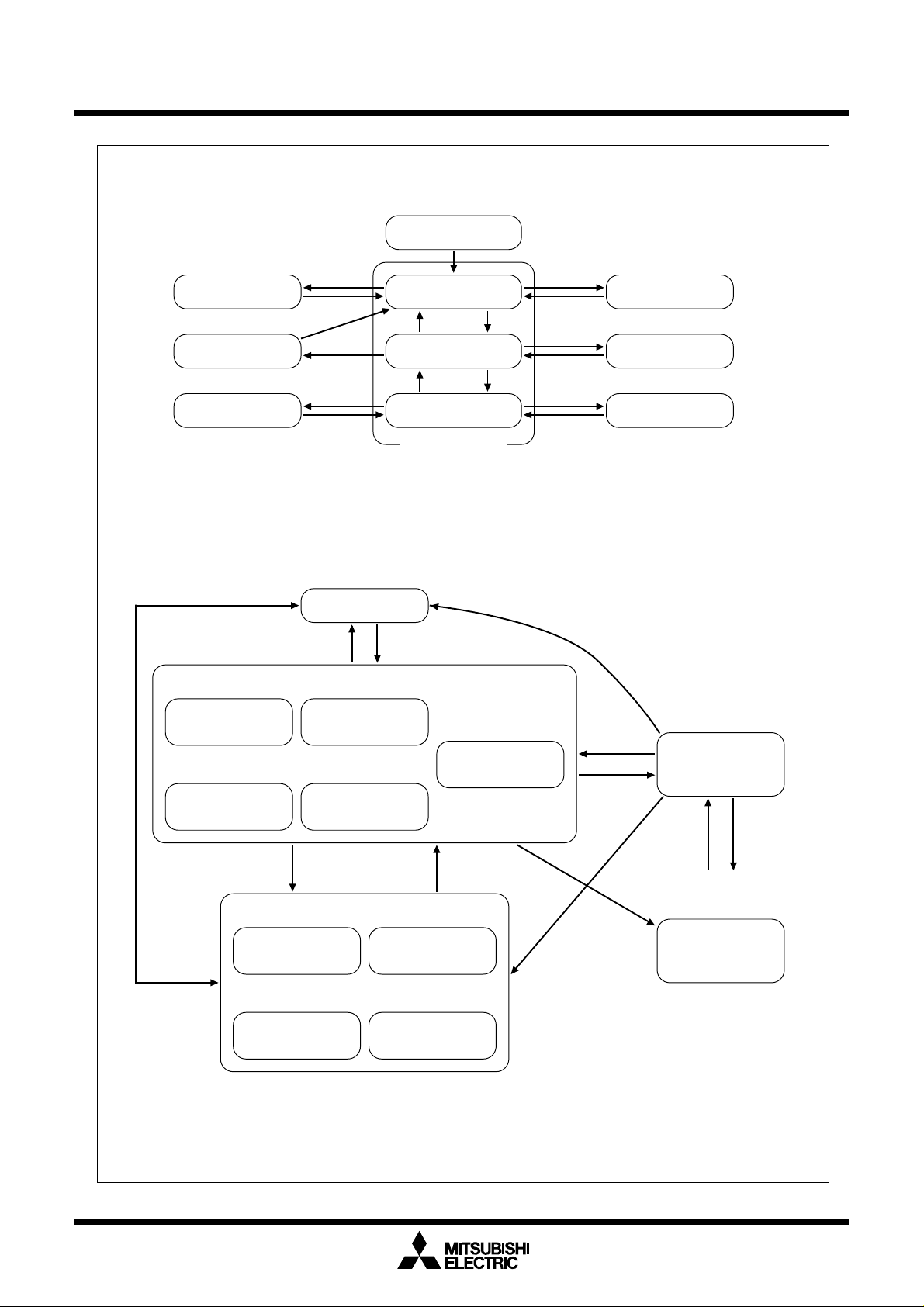

Mitsubishi plans to release the following products in the M30201 group:

(1) Support for mask ROM version and flash memory version

(2) ROM capacity

(3) Package

52P4B : Plastic molded SDIP (mask ROM version and flash memory version)

56P6S-A : Plastic molded QFP (mask ROM version and flash memory version)

RAM Size

(Byte)

2K

M30201M4-XXXSP/FP

1K

M30201M4T-XXXSP/FP

Under development

Mitsubishi microcomputers

M30201 Group

July 1998

M30201F6SP/FP

M30201F6TSP/FP

Under development

512

M30201M2-XXXSP/FP

M30201M2T-XXXSP/FP

Figure 1.4. ROM expansion

Type No. M 3 0 2 0 1 M 4 T – X X X S P

Under planning

16K

32K

Package type:

SP : Package 52P4B

FP : Package 56P6S-A

ROM No.

Omitted for flash memory version

Shows difference of characteristics

and usage etc:

Nothing : Common

T : Automobiles

ROM capacity:

2 : 16K bytes

4 : 32K bytes

6 : 48K bytes

Memory type:

M : Mask ROM version

F : Flash memory version

Shows pin count, etc

(The value itself has no specific meaning)

48K

ROM Size

(Byte)

Figure 1.5. Type No., memory size, and package

6

M16C/20 Group

M16C Family

Page 7

Under

development

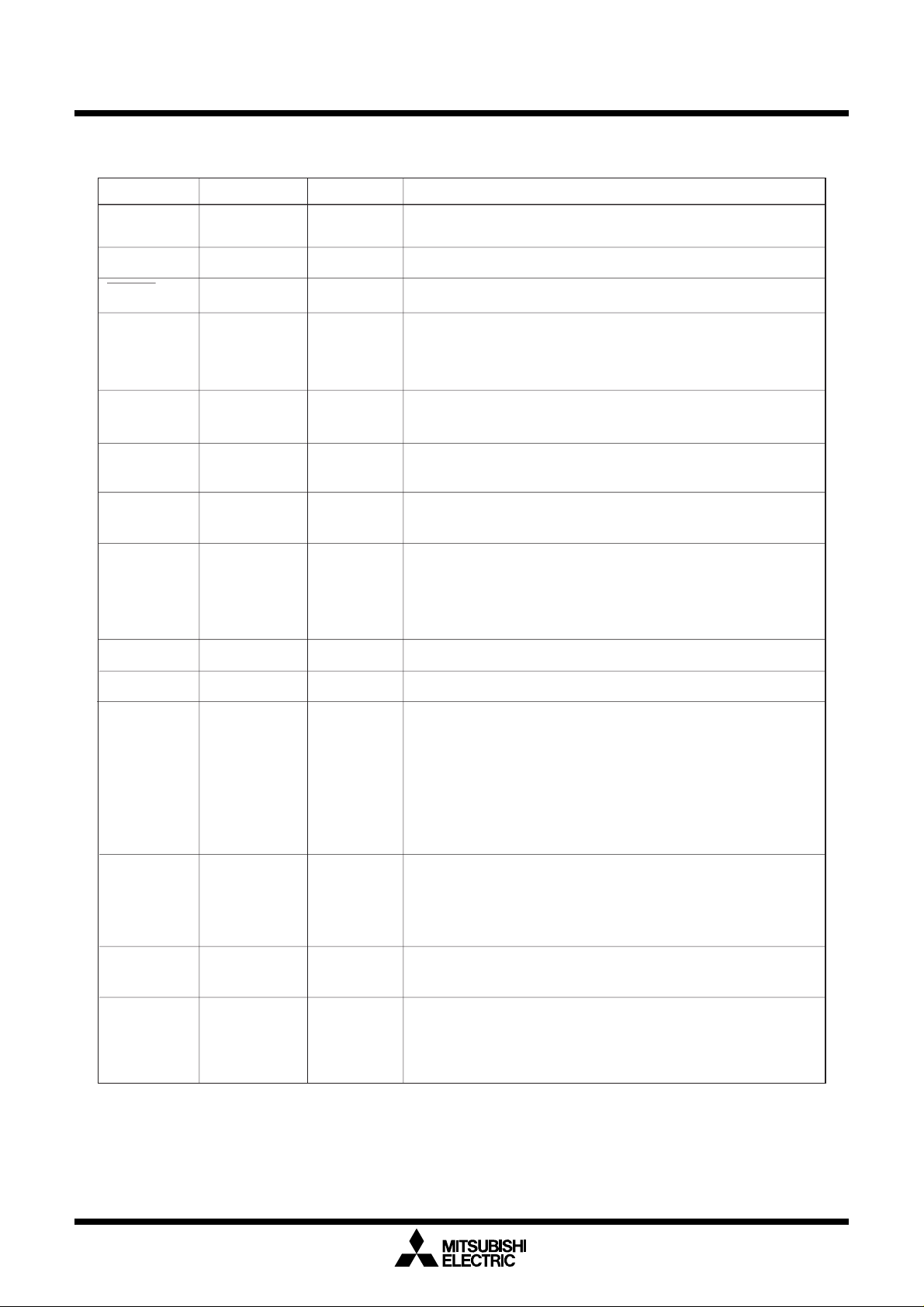

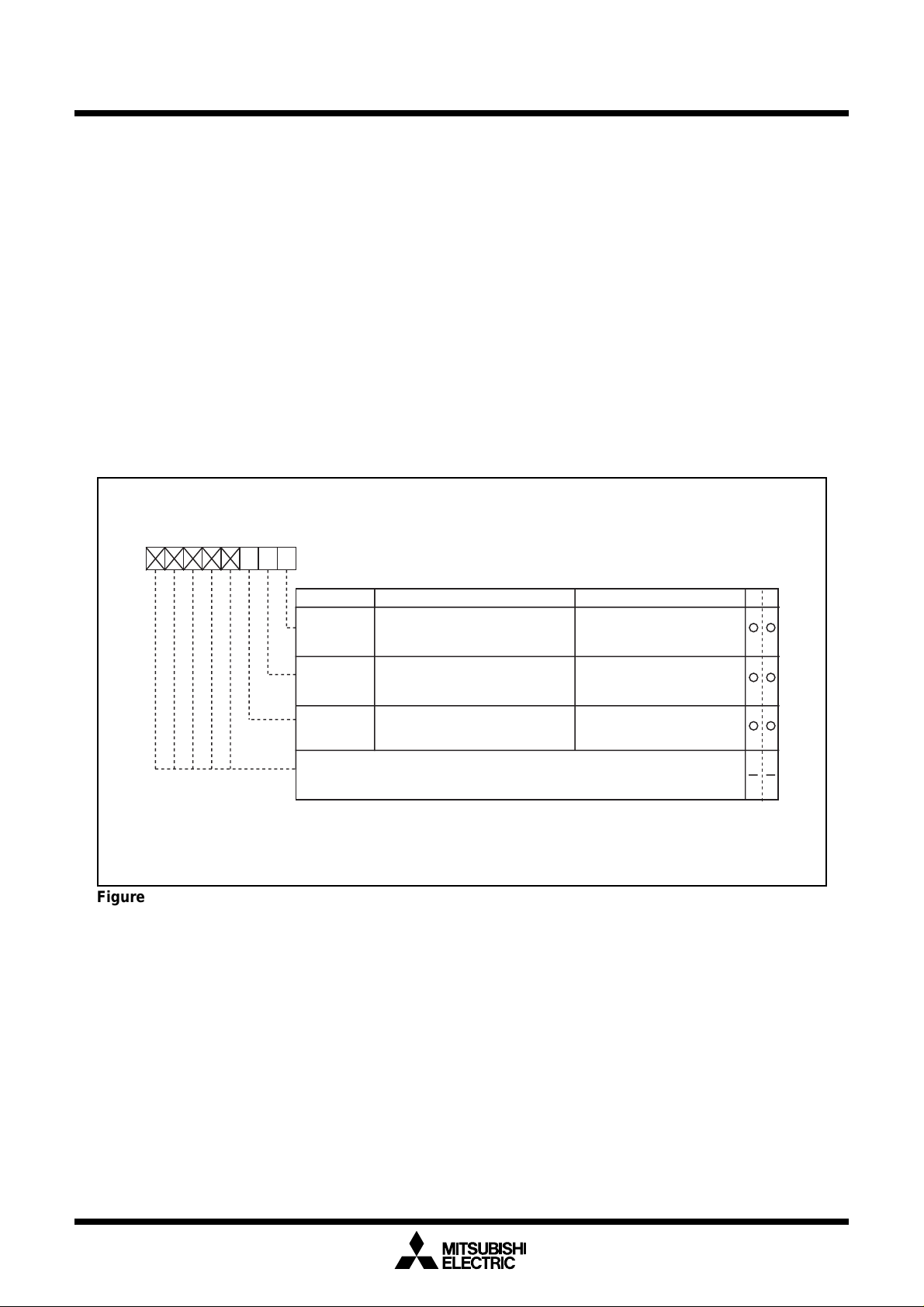

Pin Description

Pin Description

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Pin name

VCC, V

SS

CNV

SS

RESET

X

IN

X

OUT

AV

CC

AV

SS

V

REF

P00 to P0

7

Signal name

Power supply

input

CNV

SS

Reset input

Clock input

Clock output

Analog power

supply input

Analog power

supply input

Reference

voltage input

I/O port P0

I/O type

Input

Input

Input

Output

Input

Input/output

Function

CC

Supply 2.7 to 5.5 V to the V

Connect it to the V

SS

pin.

pin. Supply 0 V to the VSS pin.

A “L” on this input resets the microcomputer.

These pins are provided for the main clock generating circuit.

Connect a ceramic resonator or crystal between the X

X

OUT

pins. To use an externally derived clock, input it to the

IN

pin and leave the X

X

OUT

pin open.

IN

and the

This pin is a power supply input for the A-D converter. Connect

it to V

CC

.

This pin is a power supply input for the A-D converter. Connect

it to V

SS

.

This pin is a reference voltage input for the A-D converter.

This is an 8-bit CMOS I/O port. It has an input/output port

direction register that allows the user to set each pin for input or

output individually. When set for input, the user can specify in

units of four bits via software whether or not they are tied to a

pull-up resistor.

P10 to P1

P30 to P3

P40 to P4

P50 to P5

P60 to P6

P70 to P71

I/O port P1

7

I/O port P3

5

I/O port P4

5

I/O port P5 Input/output

4

I/O port P6

7

I/O port P7

Input/output

Input/output

Input/output

Input/output

Input/output

This is an 8-bit I/O port equivalent to P0.

This is a 6-bit I/O port equivalent to P0.

This is a 6-bit I/O port equivalent to P0. The P4

with timer A0 input and serial I/O output TxD1. The P4

2

shared with timer A0 output. The P4

I/O input RxD1. The P4

3

pin is shared with external interrupt

INT0 and timer X0 input/output TX0

pin is shared with serial

INOUT

0

pin is shared

1

pin is

. The P44 pin is

shared with external interrupt INT1 and timer X1 input/output

TX1

INOUT

. The P45 pin is shared with timer X2 input/output

TX2

INOUT

.

0

This is a 5-bit I/O port equivalent to P0. The P5

P5

3

pins are shared with serial I/O pins TxD0, RxD0, CLK0,

4

and CLKS. The P5

pin is shared with clock output CLK

Also, these pins are shared with analog input pins AN

through AN

54

.

, P51, P52, and

OUT

.

50

This is an 8-bit I/O port equivalent to P0. These pins are shared

with analog input pins AN

0

through AN7.

This is a 2-bit I/O port equivalent to P0 . These pins are used

for input/output to and from the oscillator circuit for the clock.

Connect a crystal oscillator between the X

CIN

and the X

COUT

pins.

7

Page 8

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Memory

Operation of Functional Blocks

The M30201 accommodates certain units in a single chip. These units include ROM and RAM to store

instructions and data and the central processing unit (CPU) to execute arithmetic/logic operations. Also

included are peripheral units such as timers, serial I/O, A-D converter, and I/O ports.

The following explains each unit.

Memory

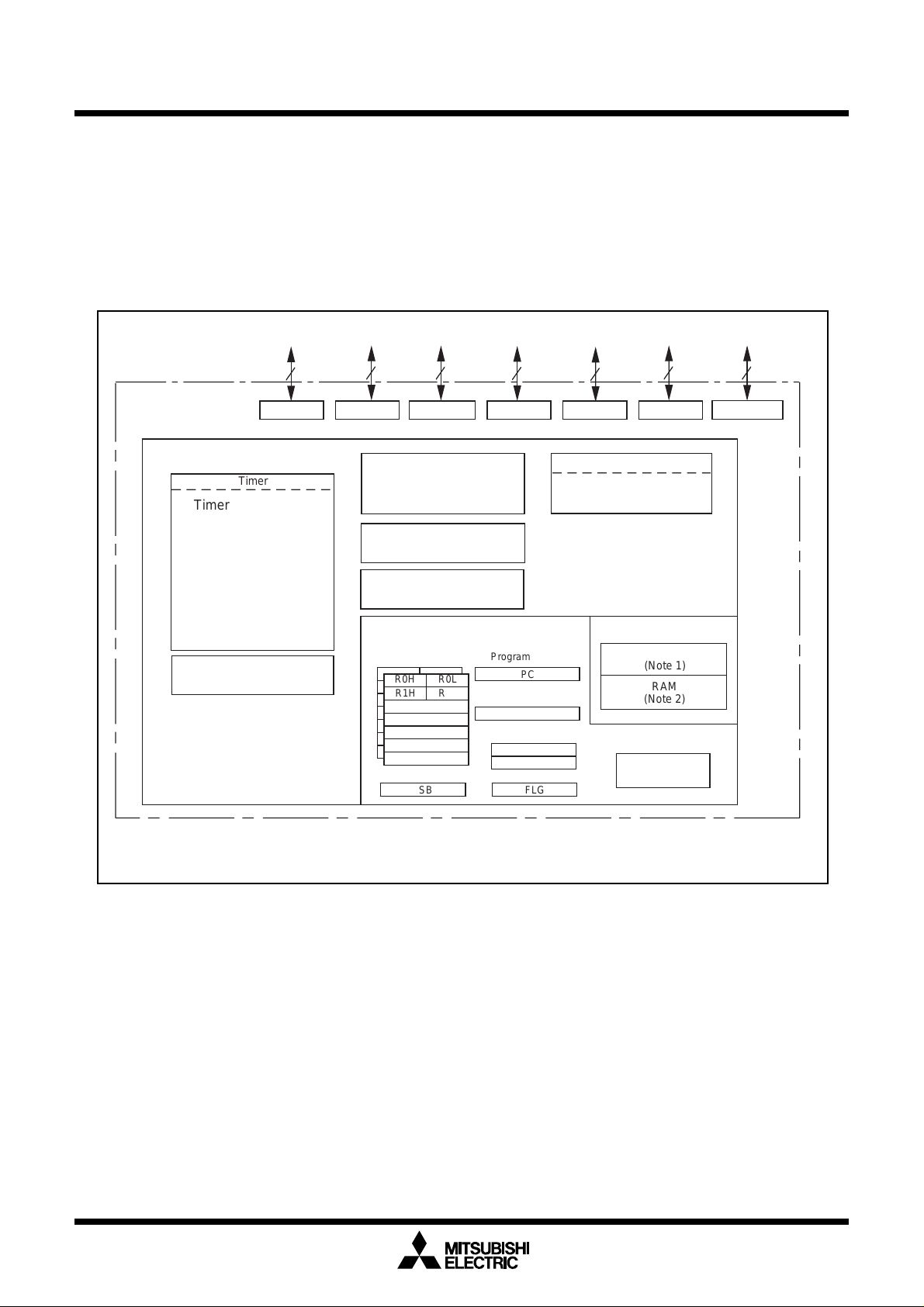

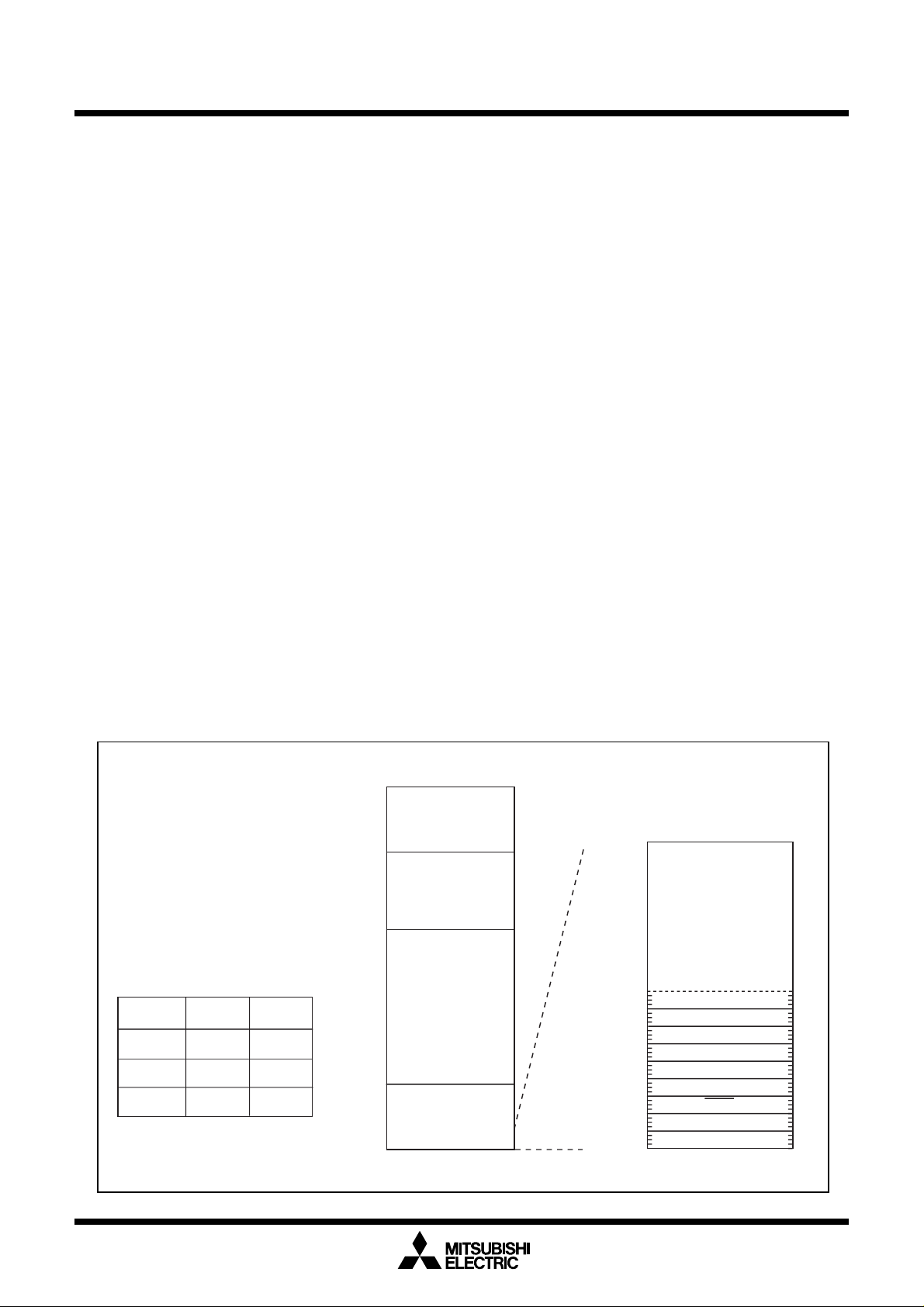

Figure 1.6 is a memory map of the M30201. The address space extends the 1M bytes from address

0000016 to FFFFF16. From FFFFF16 down is ROM. For example, in the M30201M4-XXXFP, there is 32K

bytes of internal ROM from F800016 to FFFFF16. The vector table for fixed interrupts such as the reset are

mapped to FFFDC16 to FFFFF16. The starting address of the interrupt routine is stored here. The address

of the vector table for timer interrupts, etc., can be set as desired using the internal register (INTB). See the

section on interrupts for details.

From 0040016 up is RAM. For example, in the M30201M4-XXXFP, there is 1K byte of internal RAM from

0040016 to 007FF16. In addition to storing data, the RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SFR area is mapped to 0000016 to 003FF16. This area accommodates the control registers for peripheral devices such as I/O ports, A-D converter, serial I/O, and timers, etc. Any part of the SFR area that is not

occupied is reserved and cannot be used for other purposes.

The special page vector table is mapped to FFE0016 to FFFDB16. If the starting addresses of subroutines

or the destination addresses of jumps are stored here, subroutine call instructions and jump instructions

can be used as 2-byte instructions, reducing the number of program steps.

Type No.

M30201M4

M30201M2

M30201F6

Address

XXXXX

F8000

FC000

F4000

Address

YYYYY

16

007FF

16

005FF

16

00BFF

16

Figure 1.6. Memory map

00000

16

SFR area

For details, see

00400

Figures 1.7 to 1.8

16

FFE00

16

Internal RAM area

Special page

YYYYY

16

FFFDC

16

16

16

16

XXXXX

16

16

FFFFF

Internal ROM area

16

FFFFF

16

vector table

Undefined instruction

Overflow

BRK instruction

Address match

Single step

Watchdog timer

DBC

Reset

8

Page 9

Under

development

Memory

0000

0001

0002

0003

0004

0005

0006

0007

0008

0009

000A

000B

000C

000D

000E

000F

0010

0011

0012

0013

0014

0015

0016

0017

0018

0019

001A

001B

001C

001D

001E

001F

0020

0021

0022

0023

0024

0025

0026

0027

0028

0029

002A

002B

002C

002D

002E

002F

0030

0031

0032

0033

0034

0035

0036

0037

0038

0039

003A

003B

003C

003D

003E

003F

16

16

16

16

Processor mode register 0 (PM0)

16

16

Processor mode register 1(PM1)

16

System clock control register 0 (CM0)

16

System clock control register 1 (CM1)

16

Address match interrupt enable register (AIER)

16

Protect register (PRCR)

16

16

16

16

Watchdog timer start register (WDTS)

16

Watchdog timer control register (WDC)

16

16

16

Address match interrupt register 0 (RMAD0)

16

16

16

Address match interrupt register 1 (RMAD1)

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

0040

16

0041

16

0042

16

0043

16

0044

16

0045

16

0046

16

0047

16

0048

16

0049

16

004A

16

004B

16

004C

16

Key input interrupt control register (KUPIC)

004D

16

A-D conversion interrupt control register (ADIC)

004E

16

004F

16

0050

16

UART0 transmit interrupt control register (S0TIC)

0051

16

UART0 receive interrupt control register (S0RIC)

0052

16

UART1 transmit interrupt control register (S1TIC)

0053

16

UART1 receive interrupt control register (S1RIC)

0054

16

Timer A0 interrupt control register (TA0IC)

0055

16

Timer X0 interrupt control register (TX0IC)

0056

16

Timer X1 interrupt control register (TX1IC)

0057

16

Timer X2 interrupt control register (TX2IC)

0058

16

0059

16

Timer B0 interrupt control register (TB0IC)

005A

16

Timer B1 interrupt control register (TB1IC)

005B

16

005C

16

INT0 interrupt control register (INT0IC)

005D

16

INT1 interrupt control register (INT1IC)

005E

16

005F

16

Mitsubishi microcomputers

M30201 Group

Figure 1.7. Location of peripheral unit control registers (1)

9

Page 10

Under

g

development

Memory

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

038016

Count start flag (TABSR)

038116

Clock prescaler reset flag (CPSRF)

038216

One-shot start flag (ONSF)

038316

Trigger select register (TRGSR)

038416

Up-down flag (UDF)

038516

038616

Timer A0 (TA0)

038716

038816

Timer X0 (TX0)

038916

038A16

Timer X1 (TX1)

038B16

038C16

Timer X2 (TX2)

038D16

038E16

Clock divided counter (CDC)

038F16

039016

Timer B0 (TB0)

039116

039216

Timer B1 (TB1)

039316

039416

039516

039616

Timer A0 mode register (TA0MR)

039716

Timer X0 mode register (TX0MR)

039816

Timer X1 mode register (TX1MR)

039916

Timer X2 mode register (TX2MR)

039A16

039B16

Timer B0 mode register (TB0MR)

039C16

Timer B1 mode register (TB1MR)

039D16

039E16

039F16

03A016

UART0 transmit/receive mode register (U0MR)

03A116

UART0 bit rate generator (U0BRG)

03A216

UART0 transmit buffer register (U0TB)

03A316

03A416

UART0 transmit/receive control register 0 (U0C0)

03A516

UART0 transmit/receive control register 1 (U0C1)

03A616

UART0 receive buffer register (U0RB)

03A716

03A816

UART1 transmit/receive mode register (U1MR)

03A916

UART1 bit rate generator (U1BRG)

03AA16

UART1 transmit buffer register (U1TB)

03AB16

03AC16

UART1 transmit/receive control register 0 (U1C0)

03AD16

UART1 transmit/receive control register 1 (U1C1)

03AE16

UART1 receive buffer register (U1RB)

03AF16

03B016

UART transmit/receive control register 2 (UCON)

03B116

03B216

03B316

03B416

Flash memory control register 0 (FCON0) (Note)

03B516

Flash memory control register 1 (FCON1) (Note)

03B616

Flash command register (FCMD) (Note)

03B716

03B816

03B916

03BA16

03BB16

03BC16

03BD16

03BE16

03BF16

Note: This re

ister is only exist in flash memory version.

03C016

A-D register 0 (AD0)

03C116

03C216

A-D register 1 (AD1)

03C316

03C416

A-D register 2 (AD2)

03C516

03C616

A-D register 3 (AD3)

03C716

03C816

A-D register 4 (AD4)

03C916

03CA16

A-D register 5 (AD5)

03CB16

03CC16

A-D register 6 (AD6)

03CD16

03CE16

A-D register 7 (AD7)

03CF16

03D016

03D116

03D216

03D316

03D416

A-D control register 2 (ADCON2)

03D516

03D616

A-D control register 0 (ADCON0)

03D716

A-D control register 1 (ADCON1)

03D816

03D916

03DA16

03DB16

03DC16

03DD16

03DE16

03DF16

03E016

Port P0 (P0)

03E116

Port P1 (P1)

03E216

Port P0 direction register (PD0)

03E316

Port P1 direction register (PD1)

03E416

Port P2 (P2) (Reserved)

03E516

Port P3 (P3)

03E616

Port P2 direction register (PD2) (Reserved)

03E716

Port P3 direction register (PD3)

03E816

Port P4 (P4)

03E916

Port P5 (P5)

03EA16

Port P4 direction register (PD4)

03EB16

Port P5 direction register (PD5)

03EC16

Port P6 (P6)

03ED16

Port P7 (P7)

03EE16

Port P6 direction register (PD6)

03EF16

Port P7 direction register (PD7)

03F016

03F116

03F216

03F316

03F416

03F516

03F616

03F716

03F816

03F916

03FA16

03FB16

03FC16

Pull-up control register 0 (PUR0)

03FD16

Pull-up control register 1 (PUR1)

03FE16

Port P1 drive control register (DRR)

03FF16

Figure 1.8. Location of peripheral unit control registers (2)

10

Page 11

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

CPU

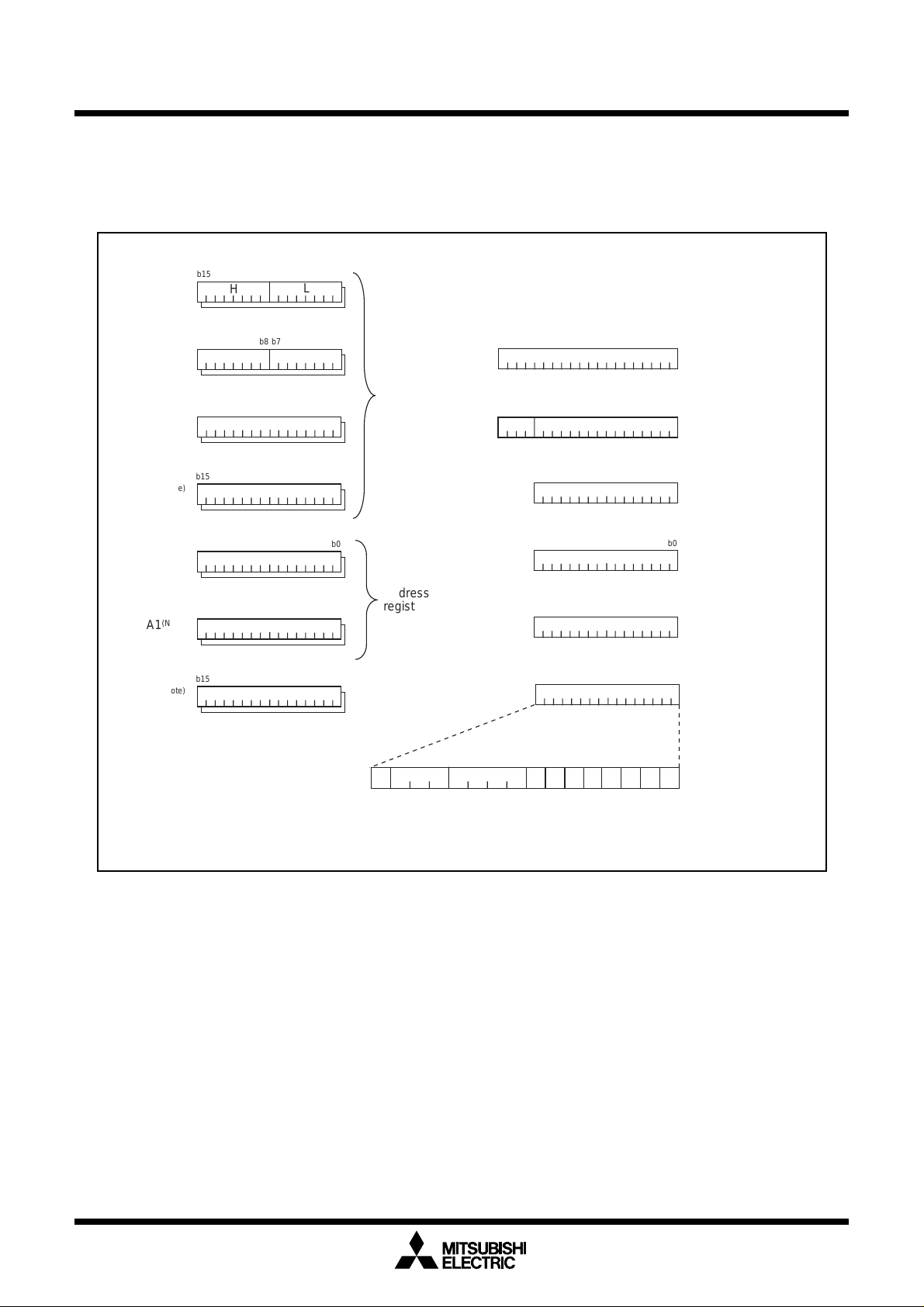

Central Processing Unit (CPU)

The CPU has a total of 13 registers shown in Figure 1.9. Seven of these registers (R0, R1, R2, R3, A0, A1,

and FB) come in two sets; therefore, these have two register banks.

R0

R1

R2

R3

A0

A1

FB

(Note)

(Note)

(Note)

(Note)

(Note)

(Note)

(Note)

b15

b15

b15

b15

b15

b15

b15

b8 b7 b0

H

b8 b7 b0

H

L

b19

L

PC

b0

Program counter

Data

b0

b0

b0

registers

INTB

b19

H

USP

ISP

b15

b15

b0

L

Interrupt table

register

b0

User stack pointer

b0

Interrupt stack

pointer

Address

b0

b0

registers

Frame base

registers

SB

FLG

b15

b15

b0

Static base

register

b0

Flag register

IPL

CDZSBOIU

Note: These registers consist of two register banks.

Figure 1.9. Central processing unit register

(1) Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, and R3)

Data registers (R0, R1, R2, and R3) are configured with 16 bits, and are used primarily for transfer and

arithmetic/logic operations.

Registers R0 and R1 each can be used as separate 8-bit data registers, high-order bits as (R0H, R1H),

and low-order bits as (R0L, R1L). In some instructions, registers R2 and R0, as well as R3 and R1 can

use as 32-bit data registers (R2R0, R3R1).

(2) Address registers (A0 and A1)

Address registers (A0 and A1) are configured with 16 bits, and have functions equivalent to those of data

registers. These registers can also be used for address register indirect addressing and address register

relative addressing.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

11

Page 12

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

CPU

(3) Frame base register (FB)

Frame base register (FB) is configured with 16 bits, and is used for FB relative addressing.

(4) Program counter (PC)

Program counter (PC) is configured with 20 bits, indicating the address of an instruction to be executed.

(5) Interrupt table register (INTB)

Interrupt table register (INTB) is configured with 20 bits, indicating the start address of an interrupt vector

table.

(6) Stack pointer (USP/ISP)

Stack pointer comes in two types: user stack pointer (USP) and interrupt stack pointer (ISP), each configured with 16 bits.

Your desired type of stack pointer (USP or ISP) can be selected by a stack pointer select flag (U flag).

This flag is located at the position of bit 7 in the flag register (FLG).

(7) Static base register (SB)

Static base register (SB) is configured with 16 bits, and is used for SB relative addressing.

(8) Flag register (FLG)

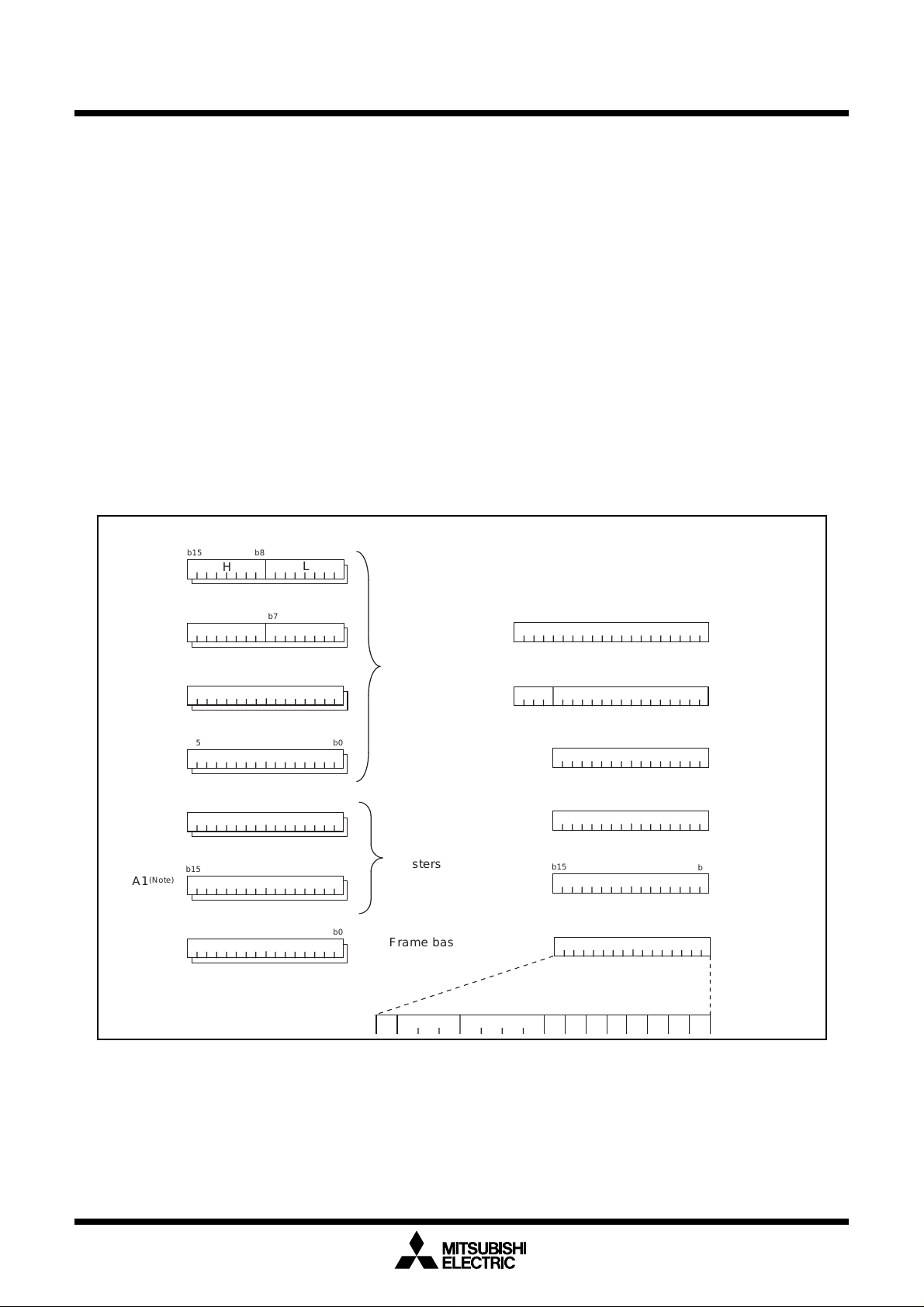

Flag register (FLG) is configured with 11 bits, each bit is used as a flag. Figure 1.10 shows the flag

register (FLG). The following explains the function of each flag:

• Bit 0: Carry flag (C flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

• Bit 1: Debug flag (D flag)

This flag enables a single-step interrupt.

When this flag is “1”, a single-step interrupt is generated after instruction execution. This flag is

cleared to “0” when the interrupt is acknowledged.

• Bit 2: Zero flag (Z flag)

This flag is set to “1” when an arithmetic operation resulted in 0; otherwise, cleared to “0”.

• Bit 3: Sign flag (S flag)

This flag is set to “1” when an arithmetic operation resulted in a negative value; otherwise, cleared to

“0”.

• Bit 4: Register bank select flag (B flag)

This flag chooses a register bank. Register bank 0 is selected when this flag is “0” ; register bank 1 is

selected when this flag is “1”.

• Bit 5: Overflow flag (O flag)

This flag is set to “1” when an arithmetic operation resulted in overflow; otherwise, cleared to “0”.

• Bit 6: Interrupt enable flag (I flag)

This flag enables a maskable interrupt.

An interrupt is disabled when this flag is “0”, and is enabled when this flag is “1”. This flag is cleared to

“0” when the interrupt is acknowledged.

12

Page 13

Mitsubishi microcomputers

n

e

o

k

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

CPU

• Bit 7: Stack pointer select flag (U flag)

Interrupt stack pointer (ISP) is selected when this flag is “0” ; user stack pointer (USP) is selected

when this flag is “1”.

This flag is cleared to “0” when a hardware interrupt is acknowledged or an INT instruction of software

interrupt Nos. 0 to 31 is executed.

• Bits 8 to 11: Reserved area

• Bits 12 to 14: Processor interrupt priority level (IPL)

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight

processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt

is enabled.

• Bit 15: Reserved area

The C, Z, S, and O flags are changed when instructions are executed. See the software manual for

details.

R0

R1

R2

R3

A0

A1

FB

(Note)

(Note)

(Note)

(Note)

(Note)

(Note)

(Note)

b15

b15

b15

b15

b15

b15

b15

b8 b7 b0

H

b8 b7 b0

H

L

L

b19

PC

b0

Program cou

Data

b0

b0

b0

registers

INTB

b19

H

USP

ISP

b15

b15

b0

L

Interrupt tabl

register

b0

User stack p

b0

Interrupt stac

pointer

Address

b0

registers

SB

b15

b0

Static base

register

b0

Frame base

registers

b15

FLG

b0

Flag register

Figure 1.10. Flag register (FLG)

IPL

CDZSBOIU

13

Page 14

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Reset

Reset

There are two kinds of resets; hardware and software. In both cases, operation is the same after the reset.

(See “Software Reset” for details of software resets.) This section explains on hardware resets.

When the supply voltage is in the range where operation is guaranteed, a reset is effected by holding the

reset pin level “L” (0.2VCC max.) for at least 20 cycles. When the reset pin level is then returned to the “H”

level while main clock is stable, the reset status is cancelled and program execution resumes from the

address in the reset vector table.

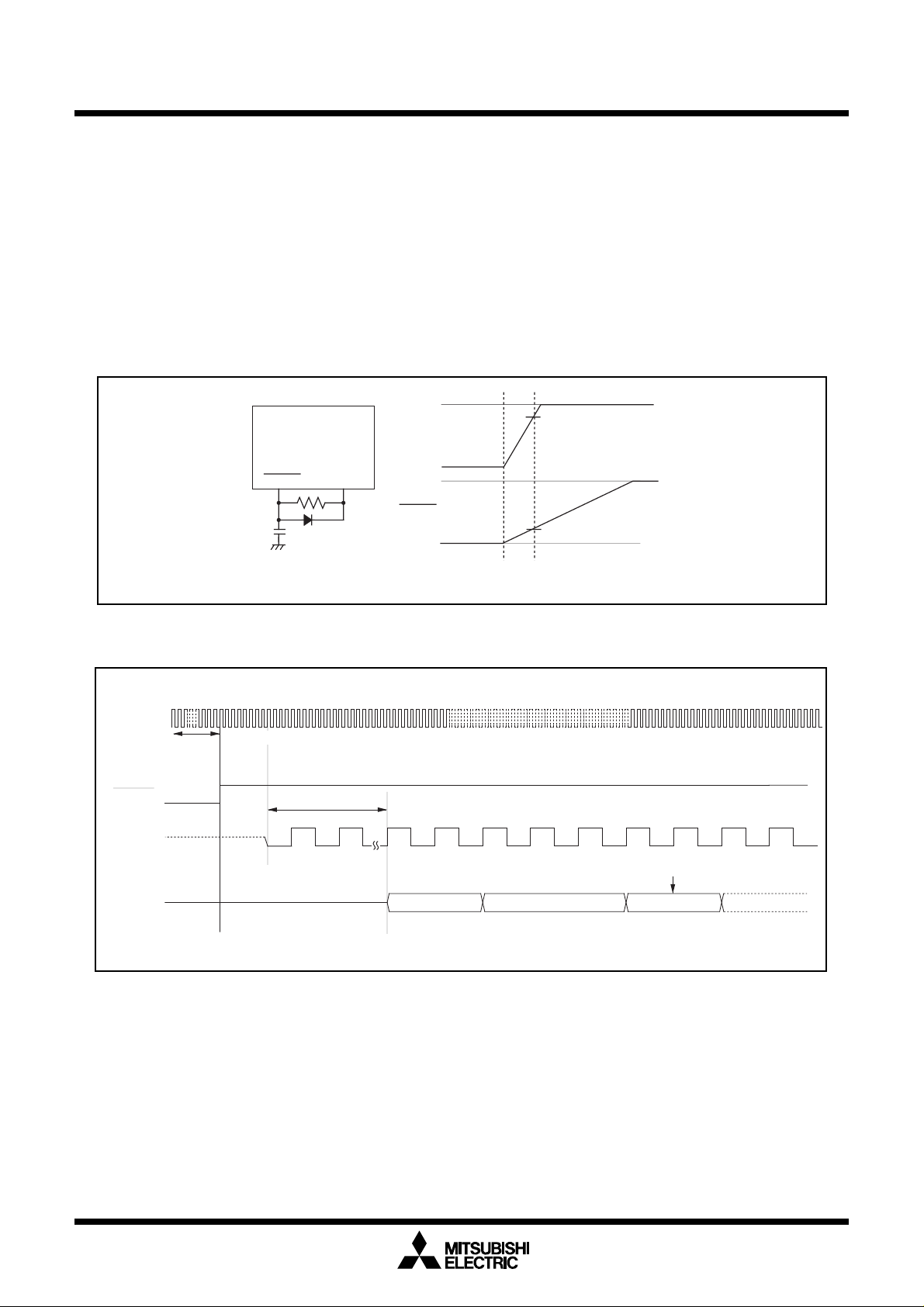

Figure 1.11 shows the example reset circuit. Figure 1.12 shows the reset sequence.

RESET

Example when V

V

CC

Figure 1.11. Example reset circuit

X

IN

More than 20 cycles are needed

RESET

BCLK

(Internal clock)

BCLK 24cycles

CC

= 5V

5V

V

CC

0V

5V

RESET

0V

4.0V

0.8V

.

Content of reset vector

Address

(Internal address

signal)

Figure 1.12. Reset sequence

14

FFFFC

16

FFFFE

16

Page 15

Under

development

Reset

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

(11)

(12)

(13)

(14)

(15)

(16)

(17)

(18)

(19)

(20)

(21)

(22)

(23)

(24)

(25)

(26)

(27)

(28)

(29)

(30)

(31)

(32)

Processor mode register 0

Processor mode register 1

System clock control register 0

System clock control register 1

Address match interrupt

enable register

Protect register

Watchdog timer control register

Address match interrupt

register 0

Address match interrupt

register 1

Key input interrupt control register

A-D conversion interrupt

control register

UART0 transmit interrupt control

register

UART0 receive interrupt control

register

UART1 transmit interrupt control

register

UART1 receive interrupt control

register

Timer A0 interrupt control register

Timer X0 interrupt control register

Timer X1 interrupt control register

Timer X2 interrupt control register

Timer B0 interrupt control register

Timer B1 interrupt control register

INT0 interrupt control register

INT1 interrupt control register

Count start flag

One-shot start flag

Trigger select flag

Up-down flag

Timer A0 mode register

Timer X0 mode register

Timer X1 mode register

Timer X2 mode register

(0004

(0005

(0006

(0007

(0009

(000A

(000F

(0010

(0011

(0012

(0014

(0015

(0016

(004D

(004E

(0051

(0052

(0053

(0054

(0055

(0056

(0057

(0058

(005A

(005B

(005D

(005E

(0380

(0381

(0382

(0383

(0384

(0396

(0397

(0398

(0399

16)···

16)···

16)···

01001000

16)···

16)···

16)···

16)···

000?????

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···Clock prescaler reset flag

16)···

16)···

16)···

16)···

16)···

16)···

16)···

0016

0016

0016

0016

00 000?

00 000?

0000000

0

0016

00

0016

0016

0016

0016

0000

0

000 00001

00

000

0000

0000

000?

000?

000?

000?

000?

000?

000?

000?

000?

000?

000?

000?

0000

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Timer B0 mode register

(33)

Timer B1 mode register

(34)

00

UART0 transmit/receive mode

(35)

register

UART0 transmit/receive control

(36)

register 0

UART0 transmit/receive control

(37)

register 1

UART1 transmit/receive mode

(38)

register

UART1 transmit/receive control

(39)

register 0

UART1 transmit/receive control

(40)

register 1

UART transmit/receive control

(41)

register 2

Flash memory control register 0

(42)

(Note )

Flash memory control register 1

(43)

(Note)

Flash command register

(44)

A-D control register 2

(45)

A-D control register 0

(46)

A-D control register 1

(47)

Port P0 direction register

(48)

Port P1 direction register

(49)

Port P2 direction register

(50)

Port P3 direction register

(51)

Port P4 direction register

(52)

Port P5 direction register

(53)

Port P6 direction register

(54)

Port P7 direction register

(55)

Pull-up control register 0

(56)

Pull-up control register 1

(57)

Port P1 drive capacity control

(58)

register

Data registers (R0/R1/R2/R3)

(59)

Address registers (A0/A1)

(60)

Frame base register (FB)

(61)

Interrupt table register (INTB)

(62)

User stack pointer (USP)

(63)

Interrupt stack pointer (ISP)

(64)

Static base register (SB)

(65)

Flag register (FLG)

(66)

(039B

(039C

(03A0

(03A4

(03A5

(03A8

(03AC

(03AD

(03B0

(03B4

(03B5

(03B6

(03D4

(03D6

(03D7

(03E2

(03E3

(03E6

(03E7

(03EA

(03EB

(03EE

(03EF

(03FC

(03FD

(03FE

16)···

00 0000?

16)···

00 0000?

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

16)···

0016

00010000

00000100

0016

00010000

00000100

0000000

0100

0016

00000???

0016

0016

0016

0000000

000000

000000

00000

0016

0016

0016

0016

000016

000016

000016

0000016

000016

000016

000016

000016

0000

00

0

000

00

x : Nothing is mapped to this bit

? : Undefined

The content of other registers and RAM is undefined when the microcomputer is reset. The initial values

must therefore be set.

Note: This register is only exist in flash memory version.

Figure 1.13. Device's internal status after a reset is cleared

15

Page 16

Mitsubishi microcomputers

Under

development

Software Reset

Bus Control

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Software Reset

Writing “1” to bit 3 of the processor mode register 0 (address 000416) applies a (software) reset to the

microcomputer. A software reset has almost the same effect as a hardware reset. The contents of internal

RAM are preserved.

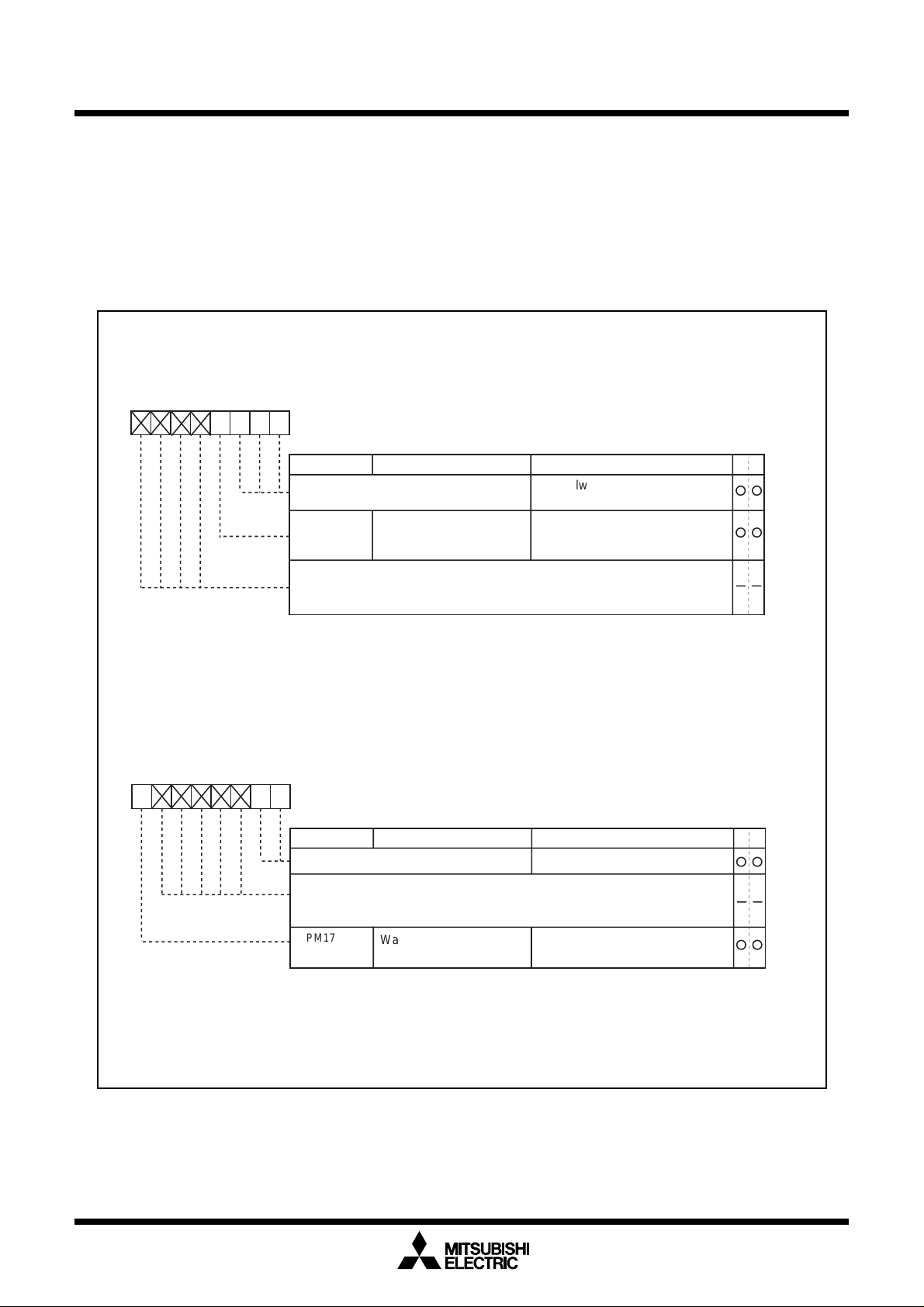

Figure 1.14 shows the processor mode register 0 and 1.

Processor mode register 0 (Note)

b7 b6 b5 b4 b3 b2 b1 b0

Symbol Address When reset

PM0 0004

0000

16

XXXX0000

2

Reserved bit

PM03

Nothing is assigned.

When write, set "0". When read, their contents are indeterminate.

Note: Set bit 1 of the protect register (address 000A

values to this register.

Processor mode register 1 (Note)

b7 b6 b5 b4 b3 b2 b1 b0

0

0

Symbol Address When reset

PM1 0005

0

Reserved bit

Nothing is assigned.

When write, set "0". When read, their contents are indeterminate.

Bit name FunctionBit symbol

Software reset bit

16

Bit name FunctionBit symbol

Must always be set to “0”

The device is reset when this bit

is set to “1”. The value of this bit

is “0” when read.

16

) to “1” when writing new

00XXXXX0

2

Must always be set to “0”

WR

WR

PM17

Note: Set bit 1 of the protect register (address 000A

to this register.

Wait bit 0 : No wait state

Figure 1.14. Processor mode register 0 and 1.

16

1 : Wait state inserted

16

) to “1” when writing new values

Page 17

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Software Wait

Software wait

The wait bit (bit 7) of the processor mode register 1 (address 000516)(note) allows you to insert software

wait states for the internal ROM/RAM areas. If this bit is 0, the bus cycle is executed in one BCLK (internal

clock) period; if the bit is 1, the bus cycle is executed in two BCLK periods. This bit is cleared to 0 after a

reset.

The SFR area is unaffected by this control bit; it is always accessed in two BCLK periods.

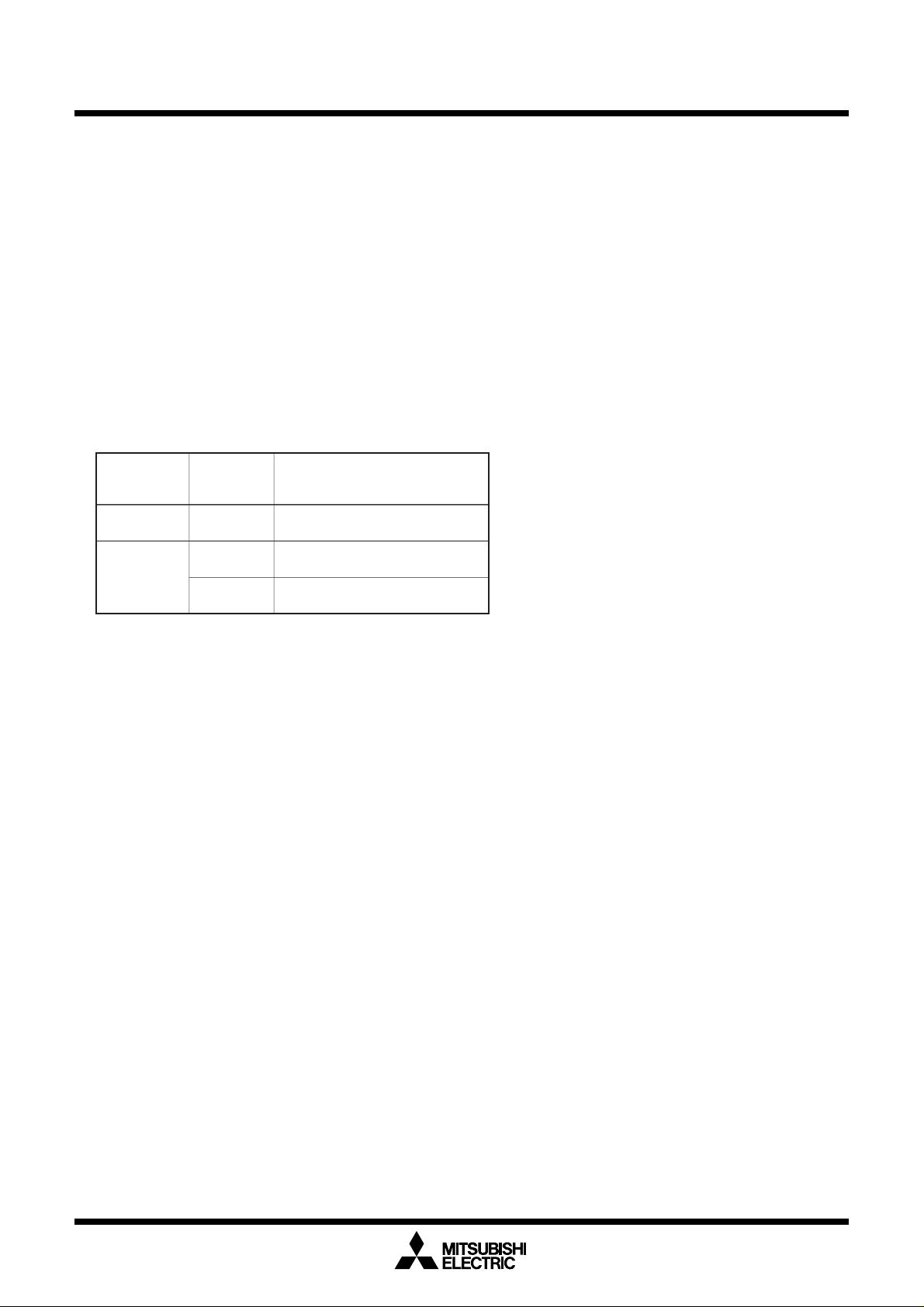

Table 1.2 shows the relationship between software wait states and bus cycles.

Note: Before attempting to change the contents of the processor mode register 1, set bit 1 of the protect

register (address 000A16) to “1”.

Table 1.2. Software waits and bus cycles

Area Wait bit

SFR

Internal

ROM/RAM

Bus cycle

Invalid 2 BCLK cycles

0 1 BCLK cycle

1 2 BCLK cycles

17

Page 18

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Clock Generating Circuit

Clock Generating Circuit

The clock generating circuit contains two oscillator circuits that supply the operating clock sources to the

CPU and internal peripheral units.

Table 1.3. Main clock and sub-clock generating circuits

Main clock generating circuit Sub clock generating circuit

Use of clock • CPU’s operating clock source • CPU’s operating clock source

• Internal peripheral units’ • Timer A/B/X’s count clock

operating clock source source

Usable oscillator Ceramic or crystal oscillator Crystal oscillator

Pins to connect oscillator XIN, XOUT XCIN, XCOUT

Oscillation stop/restart function Available Available

Oscillator status immediately after reset

Oscillating Stopped

Other Externally derived clock can be input

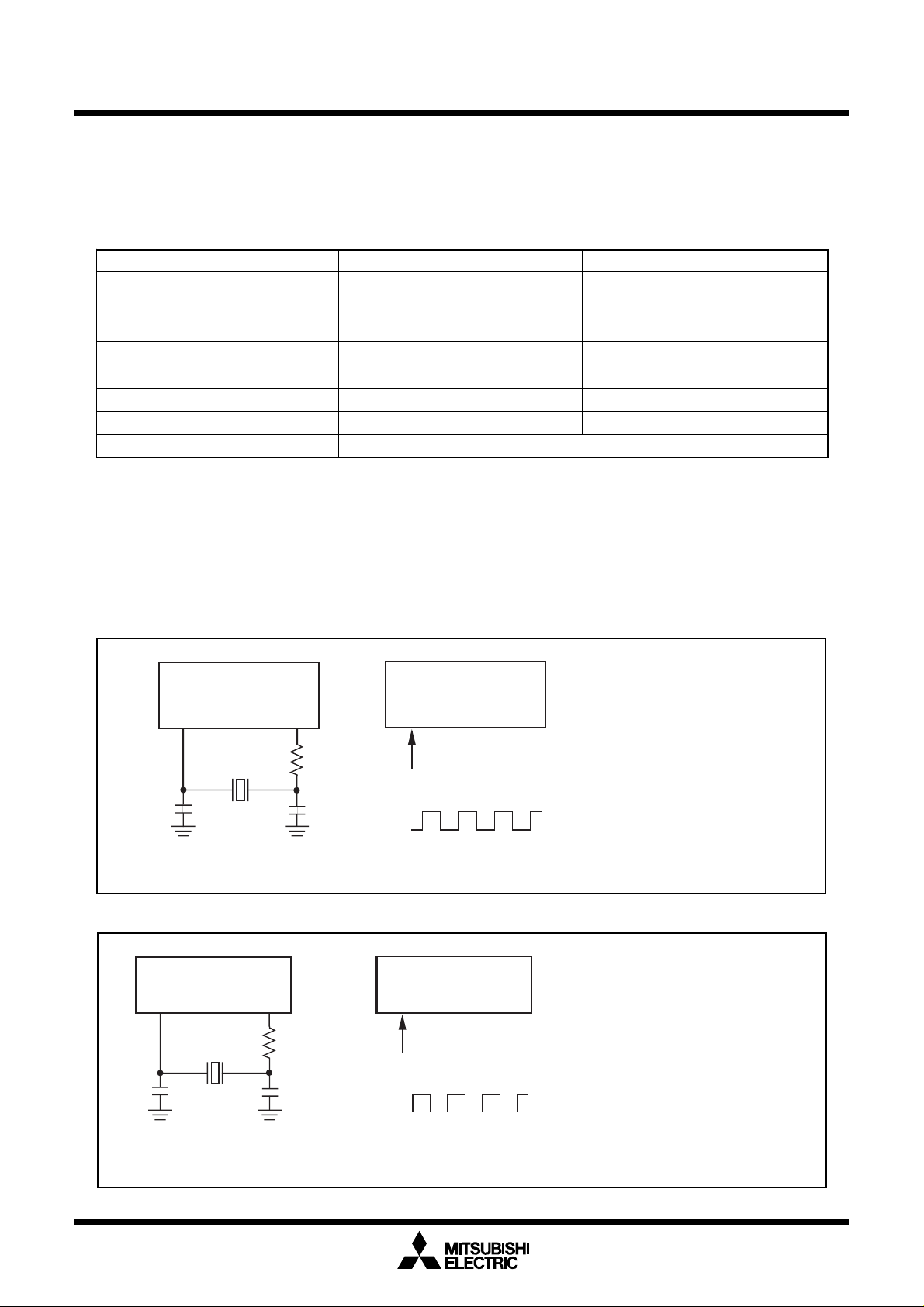

Example of oscillator circuit

Figure 1.15 shows some examples of the main clock circuit, one using an oscillator connected to the circuit,

and the other one using an externally derived clock for input. Figure 1.16 shows some examples of subclock circuits, one using an oscillator connected to the circuit, and the other one using an externally derived

clock for input. Circuit constants in Figures 15 and 16 vary with each oscillator used. Use the values

recommended by the manufacturer of your oscillator.

M30201

(Built-in feedback resistor)

X

IN

C

IN

X

OUT

(Note)

R

d

C

OUT

Figure 1.15. Examples of main clock

M30201

(Built-in feedback resistor)

XCIN XCOUT

(Note)

RCd

CCIN CCOUT

M30201

(Built-in feedback resistor)

X

IN

Externally derived clock

Vcc

Vss

M30201

(Built-in feedback resistor)

XCIN XCOUT

Externally derived clock

Vcc

Vss

X

Open

Open

OUT

Note: Insert a damping resistor if

required. The resistance will

vary depending on the

oscillator and the oscillation

drive capacity setting. Use the

value recommended by the

maker of the oscillator.

When the oscillation drive

capacity is set to low, check

that oscillation is stable. Also,

if the oscillator manufacturer's

data sheet specifies that a

feedback resistor be added

external to the chip, insert a

feedback resistor between X

OUT

and X

instruction.

Note: Insert a damping resistor if

required. The resistance will

vary depending on the oscillator

and the oscillation drive

capacity setting. Use the value

recommended by the maker of

the oscillator.

When the oscillation drive

capacity is set to low, check that

oscillation is stable. Also,

if the oscillator manufacturer's

data sheet specifies that a

feedback resistor be added

external to the chip, insert a

feedback resistor between

X

instruction.

following the

CIN and XCOUT following the

IN

Figure 1.16. Examples of sub-clock

18

Page 19

Under

development

Clock Generating Circuit

Clock Control

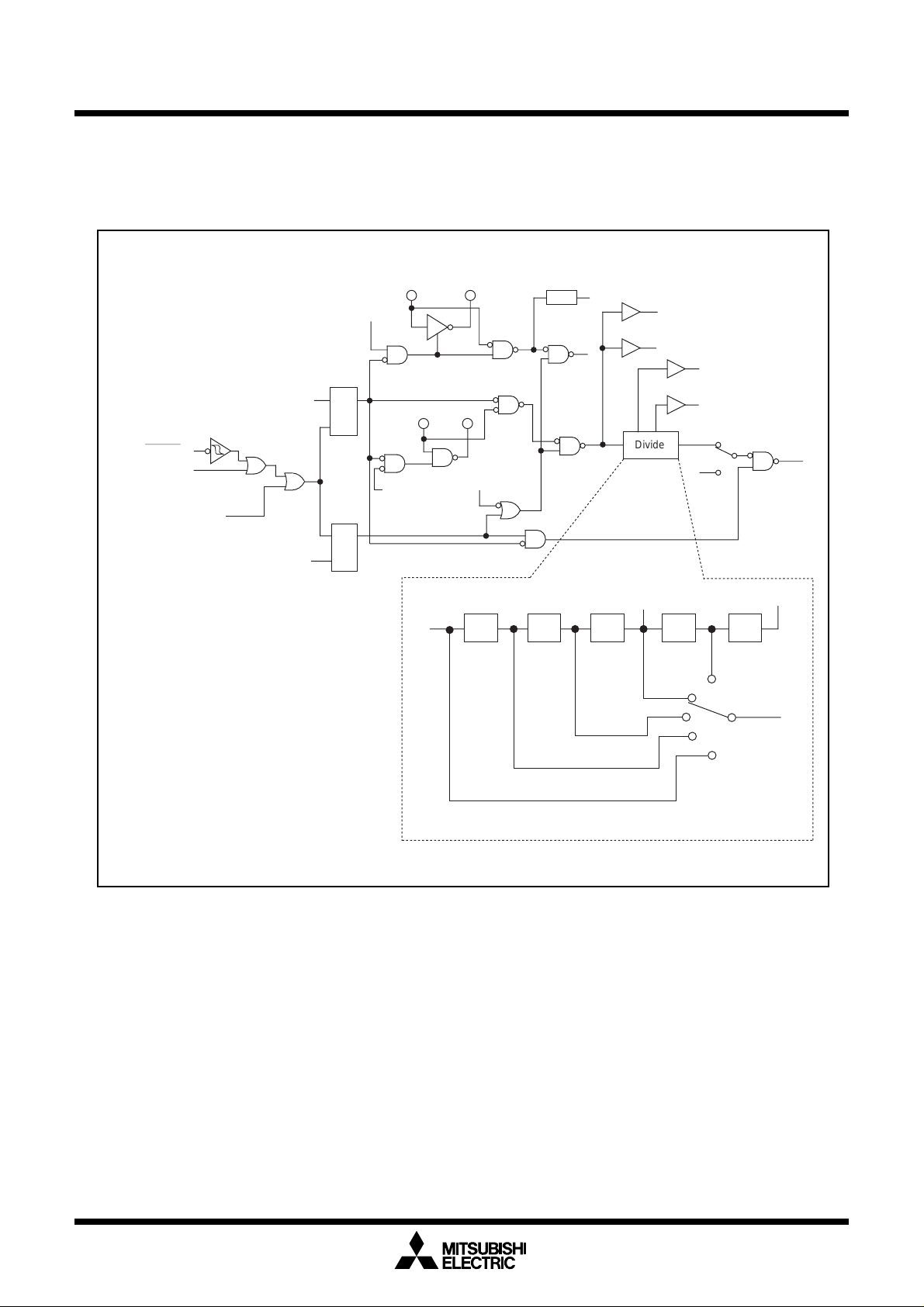

Figure 1.17 shows the block diagram of the clock generating circuit.

X

CIN

CM04

X

COUT

Sub clock

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

C32

f

1/32

f

C

f

1

f

AD

f

8

RESET

Software reset

Interrupt request

level judgment output

CM10 “1”

Write signal

WAIT instruction

CM0i : Bit i at address 0006

CM1i : Bit i at address 0007

WDCi : Bit i at address 000F

S

R

R

f

c

CM06=1

32

d

f

C

CM07=1

CM07=0

BCLK

c

1/2

CM06=0

CM17,CM16=11

d

Q

QS

CM05

X

IN

Main clock

X

OUT

CM02

b

a

Divider

b

a

16

16

16

1/2 1/2 1/2 1/2

CM06=0

CM17,CM16=10

CM06=0

CM17,CM16=01

CM06=0

CM17,CM16=00

Details of divider

Figure 1.17. Clock generating circuit

19

Page 20

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Clock Generating Circuit

The following paragraphs describes the clocks generated by the clock generating circuit.

(1) Main clock

The main clock is generated by the main clock oscillation circuit. After a reset, the clock is divided by 8 to

BCLK. The clock can be stopped using the main clock stop bit (bit 5 at address 000616). Stopping the

clock, after switching the operating clock source of CPU to the sub-clock, reduces the power dissipation.

After the oscillation of the main clock oscillation circuit has stabilized, the drive capacity of the main clock

oscillation circuit can be reduced using the XIN-XOUT drive capacity select bit (bit 5 at address 000716).

Reducing the drive capacity of the main clock oscillation circuit reduces the power dissipation. This bit

changes to “1” when shifting from high-speed/medium-speed mode to stop mode and at a reset. When

shifting from low-speed/low power dissipation mode to stop mode, the value before stop mode is retained.

(2) Sub-clock

The sub-clock is generated by the sub-clock oscillation circuit. No sub-clock is generated after a reset.

After oscillation is started using the port Xc select bit (bit 4 at address 000616), the sub-clock can be

selected as BCLK by using the system clock select bit (bit 7 at address 000616). However, be sure that the

sub-clock oscillation has fully stabilized before switching.

After the oscillation of the sub-clock oscillation circuit has stabilized, the drive capacity of the sub-clock

oscillation circuit can be reduced using the XCIN-XCOUT drive capacity select bit (bit 3 at address 000616).

Reducing the drive capacity of the sub-clock oscillation circuit reduces the power dissipation. This bit

changes to “1” when shifting to stop mode and at a reset.

(3) BCLK

The BCLK is the clock that drives the CPU, and is fc or the clock is derived by dividing the main clock by

1, 2, 4, 8, or 16. The BCLK is derived by dividing the main clock by 8 after a reset.

The main clock division select bit 0(bit 6 at address 000616) changes to “1” when shifting from highspeed/medium-speed to stop mode and at reset. When shifting from low-speed/low power dissipation

mode to stop mode, the value before stop mode is retained.

(4) Peripheral function clock (f1, f8, f32, fAD)

The clock for the peripheral devices is derived from the main clock or by dividing it by 8 or 32. The

peripheral function clock is stopped by stopping the main clock or by setting the WAIT peripheral

function clock stop bit (bit 2 at 000616) to “1” and then executing a WAIT instruction.

(5) fC32

This clock is derived by dividing the sub-clock by 32. It is used for the timer A, timer B and timer X counts.

(6) fC

This clock has the same frequency as the sub-clock. It is used for BCLK and for the watchdog timer.

20

Page 21

Under

development

Clock Generating Circuit

Figure 1.18 shows the system clock control registers 0 and 1.

System clock control register 0 (Note 1)

b7 b6 b5 b4 b3 b2 b1 b0

Symbol Address When reset

CM0 0006

16

48

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

16

Bit name FunctionBit symbol

CM00

CM01

CM02

CM03

CM04

CM05

CM06

CM07

Note 1: Set bit 0 of the protect register (address 000A16) to “1” before writing to this register.

Note 2: Changes to “1” when shifting to stop mode and at a reset.

Note 3: This bit is used to stop the main clock when placing the device in a low-power mode. If you want to operate with X

after exiting from the stop mode, set this bit to “0”. When operating with a self-excited oscillator, set the system clock

select bit (CM07) to “1” before setting this bit to “1”.

Note 4: When inputting external clock, only clock oscillation buffer is stopped and clock input is acceptable.

Note 5: If this bit is set to “1”, X

Note 6: Set port Xc select bit (CM04) to “1” and stabilize the sub-clock oscillating before setting to this bit from “0” to “1”.

Note 7: This bit changes to “1” when shifting from high-speed/medium-speed mode to stop mode and at a reset. When shifting

Note 8: f

OUT

(“H”) via the feedback resistor.

X

Do not write to both bits at the same time. And also, set the main clock stop bit (CM05) to “0” and stabilize the main clock

oscillating before setting this bit from “1” to “0”.

from low-speed/low power dissipation mode to stop mode, the value before stop mode is retained.

C32

is not included.

OUT

Clock output function

select bit

WAIT peripheral function

clock stop bit

X

CIN-XCOUT

select bit (Note 2)

Port XC select bit 0 : I/O port

Main clock (XIN-X

stop bit (Note 3,4,5)

Main clock division select

bit 0 (Note 7)

System clock select bit

(Note 6)

turns “H”. The built-in feedback resistor remains being connected, so XIN turns pulled up to

drive capacity

OUT

b1 b0

0 0 : I/O port P5

0 1 : fC output

8

output

1 0 : f

1 1 : Clock divide counter output

0 : Do not stop peripheral function clock in wait mode

1 : Stop peripheral function clock in wait mode (Note 8)

0 : LOW

1 : HIGH

CIN-XCOUT

1 : X

)

0 : On

1 : Off

0 : CM16 and CM17 valid

1 : Division by 8 mode

0 : XIN, X

1 : X

CIN

OUT

, X

4

generation

COUT

IN

WR

System clock control register 1 (Note 1)

b7 b6 b5 b4 b3 b2 b1 b0

Note 1: Set bit 0 of the protect register (address 000A16) to “1” before writing to this register.

Note 2: This bit changes to “1” when shifting from high-speed/medium-speed mode to stop mode and at a reset. When shifting

from low-speed/low power dissipation mode to stop mode, the value before stop mode is retained.

Note 3: Can be selected when bit 6 of the system clock control register 0 (address 000616) is “0”. If “1”, division mode is fixed at 8.

Note 4: If this bit is set to “1”, X

00

00

Symbol Address When reset

CM1 0007

16

20

16

Bit name FunctionBit symbol

CM10

Reserved bit

Reserved bit

Reserved bit

Reserved bit

CM15

CM16

CM17

OUT

turns “H”, and the built-in feedback resistor is cut off. X

All clock stop control bit

(Note 4)

IN-XOUT

drive capacity

X

select bit (Note 2)

Main clock division

select bit 1 (Note 3)

0 : Clock on

1 : All clocks off (stop mode)

Always set to

Always set to

Always set to

Always set to

0 : LOW

1 : HIGH

b7 b6

0 0 : No division mode

0 1 : Division by 2 mode

1 0 : Division by 4 mode

1 1 : Division by 16 mode

“0”

“0”

“0”

“0”

CIN

and X

COUT

turn high-impedance state.

Figure 1.18. Clock control registers 0 and 1

WR

21

Page 22

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Clock Generating Circuit

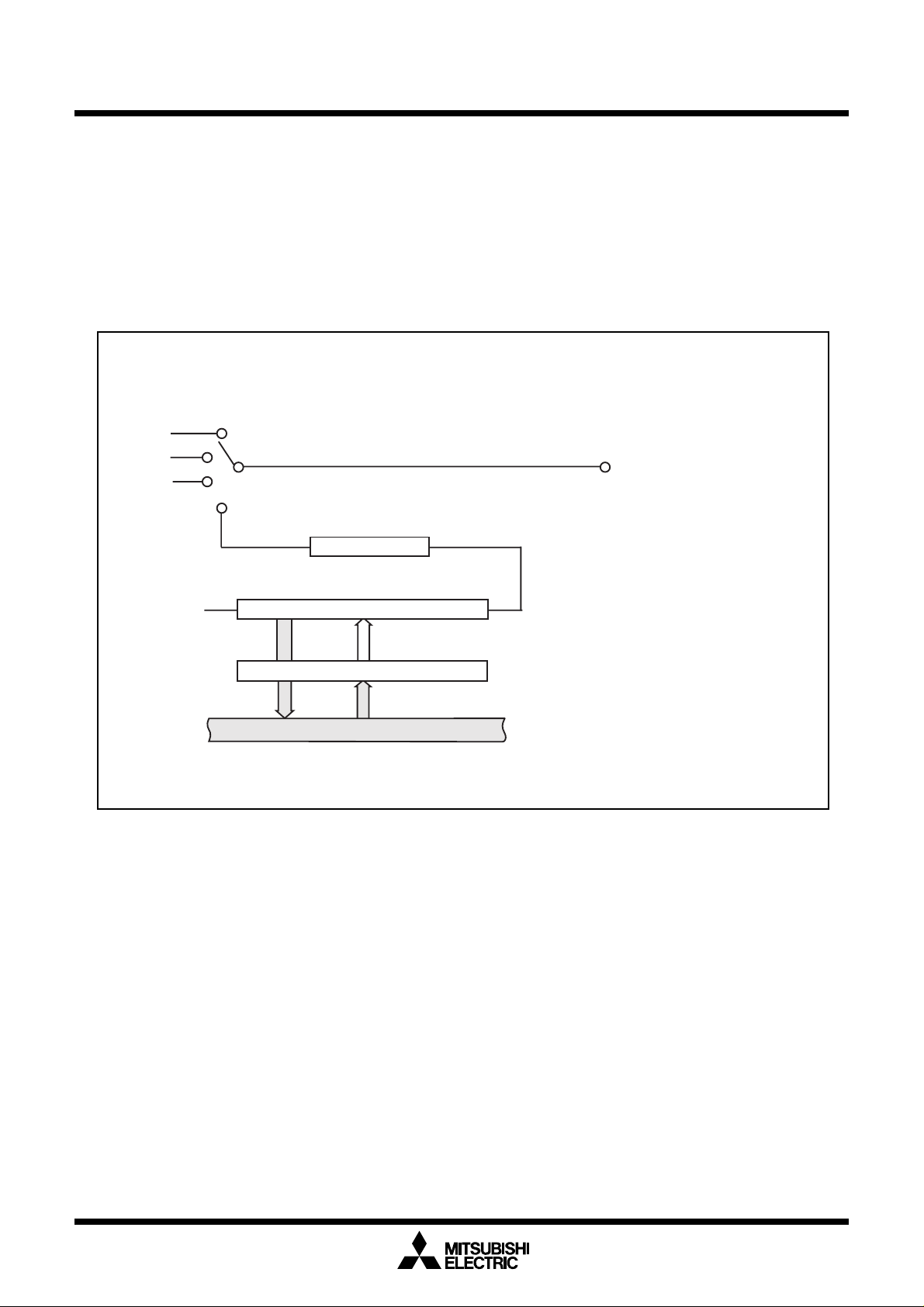

Clock Output

The clock output function select bit allows you to choose the clock from f8, fc, or a divide-by-n clock that is

output from the P54/CKOUT pin. The clock divide counter is an 8-bit counter whose count source is f32, and

its divide ratio can be set in the range of 0016 to FF16. Figure 1.19 shows a block diagram of clock output.

Clock source

selection

P5

4

f

8

f

C

P54/CK

OUT

1/2

f

32

Clock divided couter (8)

Division n+1 n=0016 to FF

Reload register (8)

Low-order 8 bits

Data bus low-order bits

Figure 1.19. Block diagram of clock output

16

Address 038E

16

Example:

When f(X

n=07

16 :

n=26

16 :

n=4D

16 :

n=9B

16 :

IN

)=10MHz

approx. 16.5kHz

approx. 4.0kHz

approx. 2.0kHz

approx. 1.0kHz

22

Page 23

Mitsubishi microcomputers

Under

development

Clock Generating Circuit

Wait Mode

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Stop Mode

Writing “1” to the all-clock stop control bit (bit 0 at address 000716) stops all oscillation and the microcomputer enters stop mode. In stop mode, the content of the internal RAM is retained provided that VCC remains

above 2V.

Because the oscillation of BCLK, f1 to f32, fc, fc32, and fAD stops in stop mode, peripheral functions such as

the A-D converter and watchdog timer do not function. However, timer A, timer B and timer X operate

provided that the event counter mode is set to an external pulse, and UART0 functions provided an external

clock is selected. Table 1.4 shows the status of the ports in stop mode.

Stop mode is cancelled by a hardware reset or an interrupt. If an interrupt is to be used to cancel stop mode,

that interrupt must first have been enabled. If returning by an interrupt, that interrupt routine is executed.

When shifting from high-speed/medium-speed mode to stop mode and at a reset, the main clock division

select bit 0 (bit 6 at address 000616) is set to “1”. When shifting from low-speed/low power dissipation mode

to stop mode, the value before stop mode is retained.

Table 1.4. Port status during stop mode

Pin States

Port Retains status before stop mode

CLKOUT When fC selected “H”

When f8, clock devided Retains status before stop mode

counter output selected

Wait Mode

When a WAIT instruction is executed, BCLK stops and the microcomputer enters the wait mode. In this

mode, oscillation continues but BCLK and watchdog timer stop. Writing “1” to the WAIT peripheral function

clock stop bit and executing a WAIT instruction stops the clock being supplied to the internal peripheral

functions, allowing power dissipation to be reduced. Table 1.5 shows the status of the ports in wait mode.

Wait mode is cancelled by a hardware reset or interrupt. If an interrupt is used to cancel wait mode, the

microcomputer restarts from the interrupt routine using as BCLK, the clock that had been selected when the

WAIT instruction was executed.

Table 1.5. Port status during wait mode

Pin States

Port

CLKOUT When fC selected Does not stop

Retains status before wait mode

When f8, clock devided Does not stop when the WAIT

counter output selected peripheral function clock stop bit is “0”.

When the WAIT peripheralfunction

clock stop bit is “1”,the status immediately prior to entering wait mode is

maintained.

23

Page 24

Mitsubishi microcomputers

Under

development

Clock Generating Circuit

Status Transition of BCLK

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Status Transition of BCLK

Power dissipation can be reduced and low-voltage operation achieved by changing the count source for

BCLK. Table 1.6 shows the operating modes corresponding to the settings of system clock control registers 0 and 1.

When reset, the device starts in division by 8 mode. The main clock division select bit 0(bit 6 at address

000616) changes to “1” when shifting from high-speed/medium-speed to stop mode and at a reset. When

shifting from low-speed/low power dissipation mode to stop mode, the value before stop mode is retained.

The following shows the operational modes of BCLK.

(1) Division by 2 mode

The main clock is divided by 2 to obtain the BCLK.

(2) Division by 4 mode

The main clock is divided by 4 to obtain the BCLK.

(3) Division by 8 mode

The main clock is divided by 8 to obtain the BCLK. When reset, the device starts operating from this

mode. Before the user can go from this mode to no division mode, division by 2 mode, or division by 4

mode, the main clock must be oscillating stably. When going to low-speed or lower power consumption

mode, make sure the sub-clock is oscillating stably.

(4) Division by 16 mode

The main clock is divided by 16 to obtain the BCLK.

(5) No-division mode

The main clock is divided by 1 to obtain the BCLK.

(6) Low-speed mode

fC is used as BCLK. Note that oscillation of both the main and sub-clocks must have stabilized before

transferring from this mode to another or vice versa. At least 2 to 3 seconds are required after the subclock starts. Therefore, the program must be written to wait until this clock has stabilized immediately

after powering up and after stop mode is cancelled.

(7) Low power dissipation mode

fC is the BCLK and the main clock is stopped.

Note : Before the count source for BCLK can be changed from XIN to XCIN or vice versa, the clock to which

the count source is going to be switched must be oscillating stably. Allow a wait time in software for

the oscillation to stabilize before switching over the clock.

Table 1.6. Operating modes dictated by settings of system clock control registers 0 and 1

CM17 CM16 CM07 CM06 CM05 CM04 Operating mode of BCLK

0 1 0 0 0 Invalid Division by 2 mode

1 0 0 0 0 Invalid Division by 4 mode

Invalid Invalid 0 1 0 Invalid Division by 8 mode

1 1 0 0 0 Invalid Division by 16 mode

0 0 0 0 0 Invalid No-division mode

Invalid Invalid 1 Invalid 0 1 Low-speed mode

Invalid Invalid 1 Invalid 1 1 Low power dissipation mode

24

Page 25

Under

development

Power Saving

Clock Generating Circuit

Power Saving

There are three power save modes.

(1) Normal operating mode

• High-speed mode

In this mode, one main clock cycle forms BCLK. The CPU operates on the BCLK. The peripheral

functions operate on the clocks specified for each respective function.

• Medium-speed mode

In this mode, the main clock is divided into 2, 4, 8, or 16 to form BCLK. The CPU operates on the

BCLK. The peripheral functions operated on the clocks specified for each respective function.

• Low-speed mode

In this mode, fc forms BCLK. The CPU operates on the fc clock. fc is the clock supplied by the

subclock. The peripheral functions operate on the clocks specified for each respective function.

• Low power-dissipation mode

This mode is selected when the main clock is stopped from low-speed mode. The CPU operates on

the fc clock. fc is the clock supplied by the subclock. Only the peripheral functions for which the

subclock was selected as the count source continue to run.

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

(2) Wait mode

CPU operation is halted in this mode. The oscillator continues to run.

(3) Stop mode

All oscillators stop in this mode. The CPU and internal peripheral functions all stop. Of all 3 power saving

modes, power savings are greatest in this mode.

Figure 1.20 shows the transition between each of the three modes, (1), (2), and (3).

25

Page 26

Under

development

Clock Generating Circuit

Power Saving

Transition of stop mode, wait mode

Mitsubishi microcomputers

M30201 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Reset

All oscillators stopped

Stop mode

All oscillators stopped

Interrupt

Stop mode

All oscillators stopped

Stop mode

Transition of normal mode

Main clock is oscillating

Medium-speed mode

CM06 = “1”

Main clock is oscillating

Sub clock is oscillating

High-speed mode

BCLK : f(XIN)

CM07 = “0” CM06 = “0”

CM17 = “0” CM16 = “0”

Medium-speed mode

(divided-by-4 mode)

BCLK : f(XIN)/4

CM07 = “0” CM06 = “0”

CM17 = “1” CM16 = “0”

CM04 = “0”

Medium-speed mode

Medium-speed mode

(divided-by-16 mode)

CM10 = “1”

Interrupt

CM10 = “1”

CM10 = “1”

Interrupt

Medium-speed mode

(divided-by-8 mode)

High-speed/medium-

Low-speed/low power

Sub clock is stopped

(divided-by-8 mode)

BCLK : f(XIN)/8

CM07 = “0” CM06 = “1”

CM04 = “1”

(Notes 1, 3)

(divided-by-2 mode)

BCLK : f(XIN)/2

CM07 = “0” CM06 = “0”

CM17 = “0” CM16 = “1”

BCLK : f(XIN)/16

CM07 = “0” CM06 = “0”

CM17 = “1” CM16 = “1”

CPU operation stopped

Wait mode

CPU operation stopped

Wait mode

CPU operation stopped

Wait mode

speed mode

dissipation mode

WAIT

instruction

Interrupt

WAIT

instruction

Interrupt

WAIT

instruction

Interrupt

Normal mode

(Refer to the following for the transition of normal mode.)

CM07 = “0” (Note 1)

CM06 = “1”

CM04 = “0”

Main clock is oscillating

Medium-speed mode

(divided-by-8 mode)

BCLK : f(XIN)/8

CM07 = “0”

CM06 = “1”

CM07 = “0”

(Note 1, 3)

CM07 = “1”

(Note 2)

Sub clock is oscillating

Low-speed mode

BCLK : f(X

CM07 = “1”

CM05 = “0” CM05 = “1”

CIN)

CM04 = “0” CM04 = “1”

High-speed mode

CM07 = “0” CM06 = “0”

CM17 = “0” CM16 = “0”

CM06 = “0”

(Notes 1,3)

Medium-speed mode

(divided-by-4 mode)

CM07 = “0” CM06 = “0”

CM17 = “1” CM16 = “0”

Note 1: Switch clock after oscillation of main clock is sufficiently stable.

Note 2: Switch clock after oscillation of sub clock is sufficiently stable.

Note 3: Change CM06 after changing CM17 and CM16.

Note 4: Transit in accordance with arrow.

Figure 1.20. Clock transition

26

Main clock is oscillating

Sub clock is stopped

BCLK : f(XIN)

BCLK : f(XIN)/4

Medium-speed mode

(divided-by-2 mode)

BCLK : f(XIN)/2

CM07 = “0” CM06 = “0”

CM17 = “0” CM16 = “1”

Medium-speed mode

(divided-by-16 mode)

BCLK : f(XIN)/16

CM07 = “0” CM06 = “0”

CM17 = “1” CM16 = “1”

CM07 = “1” (Note 2)

CM05 = “1”

CM07 = “0” (Note 1)

CM06 = “0” (Note 3)

CM04 = “1”

Main clock is stopped

Sub clock is oscillating

Low power dissipation mode

BCLK : f(XCIN)

CM07 = “1”

Page 27

Mitsubishi microcomputers

Under

development

Clock Generating Circuit

Protection

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Protection

The protection function is provided so that the values in important registers cannot be changed in the event

that the program runs out of control. Figure 1.21 shows the protect register. The values in the processor

mode register 0 (address 000416), processor mode register 1 (address 000516), system clock control register 0 (address 000616), system clock control register 1 (address 000716) and port P4 direction register

(address 03EA16) can only be changed when the respective bit in the protect register is set to “1”. Therefore, important outputs can be allocated to port P4.

If, after “1” (write-enabled) has been written to the port P4 direction register write-enable bit (bit 2 at address

000A16), a value is written to any address, the bit automatically reverts to “0” (write-inhibited). However, the

system clock control registers 0 and 1 write-enable bit (bit 0 at 000A16) and processor mode register 0 and

1 write-enable bit (bit 1 at 000A16) do not automatically return to “0” after a value has been written to an

address. The program must therefore be written to return these bits to “0”.

Protect register

b7 b6 b5 b4 b3 b2 b1 b0

Figure 1.21. Protect register

Symbol Address When reset

16

PRCR 000A

XXXXX000

Bit nameBit symbol

16

) (Note

PRC0

PRC1

PRC2

Nothing is assigned.

These bits can neither be set nor reset. When read, their contents are

indeterminate.

Enables writing to system clock

control registers 0 and 1 (addresses

0006

16

and 0007

Enables writing to processor mode

registers 0 and 1 (addresses 0004

and 0005

Enables writing to port P4 direction

register (address 03EA

16

)

16

)

2

0 : Write-inhibited

1 : Write-enabled

0 : Write-inhibited

16

1 : Write-enabled

0 : Write-inhibited

1 : Write-enabled

)

Function

Note: Writing a value to an address after “1” is written to this bit returns the bit

to “0” . Other bits do not automatically return to “0” and they must therefore

be reset by the program.

WR

27

Page 28

Under

development

Interrupts

Overview of Interrupt

Type of Interrupts

Figure 1.22 lists the types of interrupts.

Software

Interrupt

Hardware

Special

Peripheral I/O

Mitsubishi microcomputers

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Undefined instruction (UND instruction)

Overflow (INTO instruction)

BRK instruction

INT instruction

Reset

________

DBC

Watchdog timer

Single step

Address matched

*1

M30201 Group

*1

Peripheral I/O interrupts are generated by the peripheral functions built into the microcomputer system.

Figure 1.22. Classification of interrupts

• Maskable interrupt : An interrupt which can be enabled (disabled) by the interrupt enable flag (I

flag) or whose interrupt priority can be changed by priority level.

• Non-maskable interrupt : An interrupt which cannot be enabled (disabled) by the interrupt enable flag

(I flag) or whose interrupt priority cannot be changed by priority level.

28

Page 29

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Interrupts

Software Interrupts

A software interrupt occurs when executing certain instructions. Software interrupts are non-maskable

interrupts.

• Undefined instruction interrupt

An undefined instruction interrupt occurs when executing the UND instruction.

• Overflow interrupt

An overflow interrupt occurs when executing the INTO instruction with the overflow flag (O flag) set to “1”.

The following are instructions whose O flag changes by arithmetic:

ABS, ADC, ADCF, ADD, CMP, DIV, DIVU, DIVX, NEG, RMPA, SBB, SHA, SUB

• BRK interrupt

A BRK interrupt occurs when executing the BRK instruction.

• INT interrupt

An INT interrupt occurs when assigning one of software interrupt numbers 0 through 63 and executing the

INT instruction. Software interrupt numbers 0 through 31 are assigned to peripheral I/O interrupts, so

executing the INT instruction allows executing the same interrupt routine that a peripheral I/O interrupt

does.

The stack pointer (SP) used for the INT interrupt is dependent on which software interrupt number is

involved.

So far as software interrupt numbers 0 through 31 are concerned, the microcomputer saves the stack

pointer assignment flag (U flag) when it accepts an interrupt request. If change the U flag to “0” and select

the interrupt stack pointer (ISP), and then execute an interrupt sequence. When returning from the

interrupt routine, the U flag is returned to the state it was before the acceptance of interrupt request. So

far as software numbers 32 through 63 are concerned, the stack pointer does not make a shift.

29

Page 30

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Interrupts

Hardware Interrupts

Hardware interrupts are classified into two types — special interrupts and peripheral I/O interrupts.

(1) Special interrupts

Special interrupts are non-maskable interrupts.

• Reset

Reset occurs if an “L” is input to the RESET pin.

• DBC interrupt

This interrupt is exclusively for the debugger, do not use it in other circumstances.

• Watchdog timer interrupt

Generated by the watchdog timer.

• Single-step interrupt

This interrupt is exclusively for the debugger, do not use it in other circumstances. With the debug flag

(D flag) set to “1”, a single-step interrupt occurs after one instruction is executed.

• Address match interrupt

An address match interrupt occurs immediately before the instruction held in the address indicated by

the address match interrupt register is executed with the address match interrupt enable bit set to “1”.

If an address other than the first address of the instruction in the address match interrupt register is

set, no address match interrupt occurs.

M30201 Group

(2) Peripheral I/O interrupts

A peripheral I/O interrupt is generated by one of built-in peripheral functions. The interrupt vector table is

the same as the one for software interrupt numbers 0 through 31 the INT instruction uses. Peripheral I/O

interrupts are maskable interrupts.

• Key-input interrupt

A key-input interrupt occurs if an “L” is input to the KI pin.

• A-D conversion interrupt

This is an interrupt that the A-D converter generates.

• UART0 and UART1 transmission interrupt

These are interrupts that the serial I/O transmission generates.

• UART0 and UART1 reception interrupt

These are interrupts that the serial I/O reception generates.

• Timer A0 interrupt

This is an interrupts that timer A0 generates.

• Timer B0 and timer B2 interrupt

These are interrupts that timer B generates.

• Timer X0 to timer X2 interrupt

These are interrupts that timer X generates.

________ ________

• INT0 and INT1 interrupt

______ ______

An INT interrupt occurs if either a rising edge or a falling edge is input to the INT pin.

___

30

Page 31

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Interrupts

Interrupts and Interrupt Vector Tables

If an interrupt request is accepted, a program branches to the interrupt routine set in the interrupt vector

table. Set the first address of the interrupt routine in each vector table. Figure 1.23 shows format for

specifying interrupt vector addresses.

Two types of interrupt vector tables are available — fixed vector table in which addresses are fixed and

variable vector table in which addresses can be varied by the setting.

MSB

Vector address + 0

Vector address + 1

Vector address + 2

Vector address + 3

Figure 1.23. Format for specifying interrupt vector addresses

Low address

Mid address

0 0 0 0 High address

0 0 0 0 0 0 0 0

LSB

• Fixed vector tables

The fixed vector table is a table in which addresses are fixed. The vector tables are located in an area

extending from FFFDC16 to FFFFF16. One vector table comprises four bytes. Set the first address of

interrupt routine in each vector table. Table 1.7 shows the interrupts assigned to the fixed vector tables

and addresses of vector tables.

Table 1.7. Interrupt and fixed vector address

Interrupt source Vector table addresses Remarks

Address (L) to address (H)

Undefined instruction FFFDC16 to FFFDF16 Interrupt on UND instruction

Overflow FFFE016 to FFFE316 Interrupt on INTO instruction

BRK instruction FFFE416 to FFFE716

Address match FFFE816 to FFFEB16 There is an address-matching interrupt enable bit

Single step (Note) FFFEC16 to FFFEF16 Do not use

Watchdog timer FFFF016 to FFFF316

________

DBC (Note) FFFF416 to FFFF716 Do not use

- FFFF816 to FFFFB16 Reset FFFFC16 to FFFFF16

Note: Interrupts used for debugging purposes only.

If the vector is filled with FF16, program execution starts from

the address shown by the vector in the variable vector table

31

Page 32

Mitsubishi microcomputers

Under

development

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

M30201 Group

Interrupts

• Variable vector tables

The addresses in the variable vector table can be modified, according to the user’s settings. Indicate the

first address using the interrupt table register (INTB). The 256-byte area subsequent to the address the

INTB indicates becomes the area for the variable vector tables. One vector table comprises four bytes.

Set the first address of the interrupt routine in each vector table. Table 1.8 shows the interrupts assigned

to the variable vector tables and addresses of vector tables.

Table 1.8. Interrupt causes (variable interrupt vector addresses)

Software interrupt number Interrupt source

Vector table address

Address (L) to address (H)

+44 to +47 (Note) Software interrupt number 11

+48 to +51 (Note)Software interrupt number 12