MITEL VP2612 Datasheet

VP2612

Video Multiplexer

Supersedes version in June 1995 Digital Video & DSP IC Handbook, HB3923-2 DS3511 - 3.0 June 1996

FEATURES

■ Fully integrated H261 video multiplexer

■ Inputs data direct from VP2611 source coder

■ Output to X21 line buffers

■ Line rates from 64kbits/s up to 2Mbits/s

■ 100 Pin Quad Flatpack

ASSOCIATED PRODUCTS

■ VP2611 H.261 Encoder

■ VP2615 H.261 Decoder

■ VP2614 Video Demultiplexer

■ VP520S CIF/QCIF Converter

■ VP510 Colour Space Converter

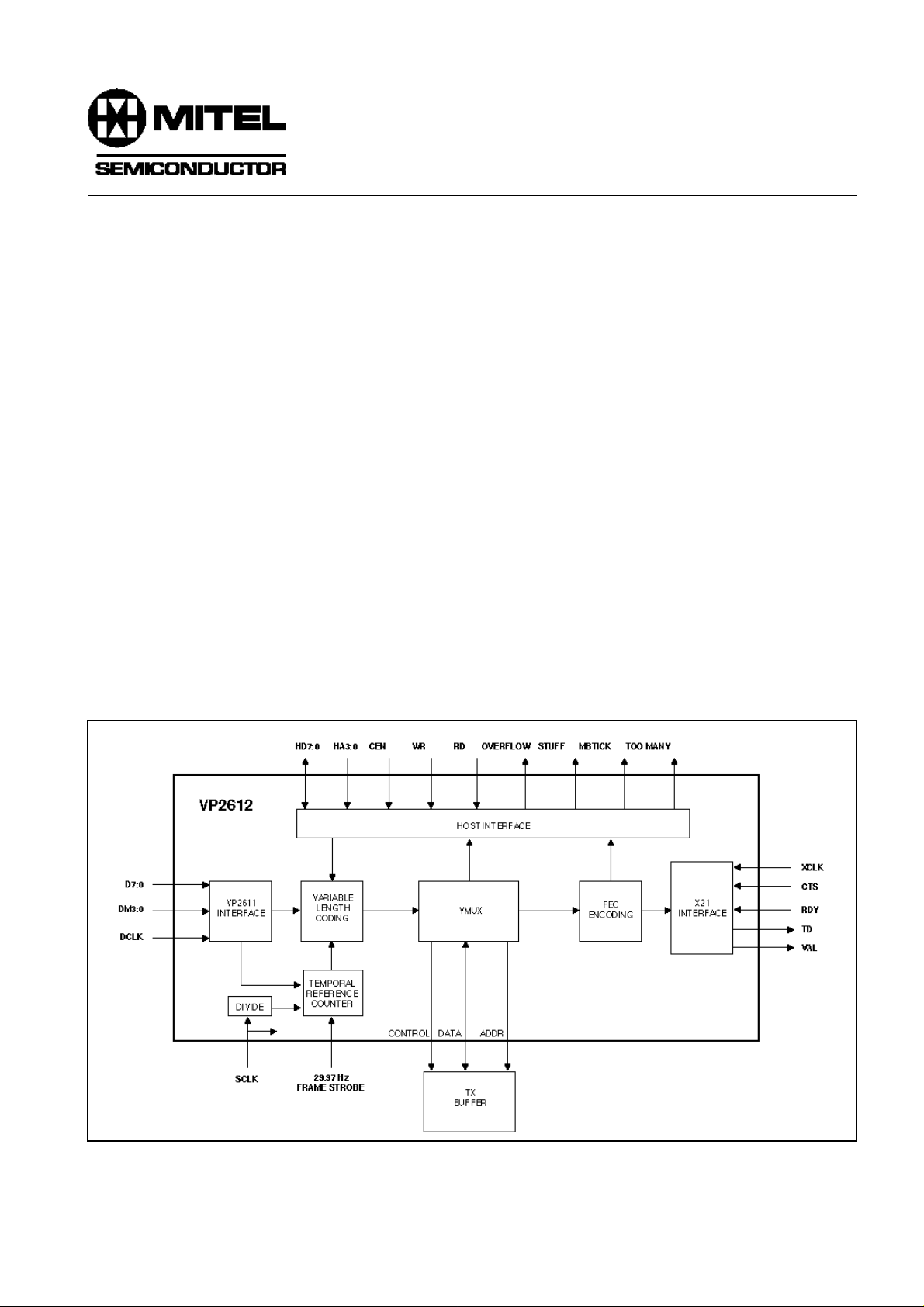

The VP2612 Video Multiplexer forms part of the Mitel

Semiconductor chip-set for video conferencing, video

telephony, and multimedia applications. This chip set

implements the H261 standard for video compression for line

rates of between 64K and 2M bits per second. With a 27MHz

clock rate full CIF resolution images can be coded at a frame

rate of up to 30Hz.

The device contains all the elements necessary to

convert the run length coded data from the VP2611 source

coder into an H261 compatible bit stream. It also calculates

the differential motion vectors and macroblock addresses

from the absolute values received from the VP2611. These

values are variable length coded, and bit packed for temporary

storage in the transmission buffer. The size of this buffer can

be either 256Kbits or 512Kbits. Data from the transmission

buffer is output through an X21 compatible serial interface,

and consists of frames containing framing bits, data, and the

BCH (511,493) forward error correction code.

The system processor interface is used to write data for

PTYPE, PSPARE, GSPARE, and to select the source of

temporal reference. The interface can also be used to monitor

the pointers into the transmission buffer, so that the buffer

fullness can be controlled using proprietary software

algorithms. In addition to the bus interface, flags are supplied

which indicate the start of each macroblock, each FEC stuffed

frame, the number of bits per picture is reaching the allowable

maximum, and impending buffer overflow.

Fig. 1. VP2612 Video Multiplexer

VP2612

PIN DESCRIPTIONS

DBUS7:0 The input data bus from VP2611. The data type is

defined by the value present on DMODE3:0

DMODE3:0These inputs define the data type present on the

data bus D7:0. Polarities are given in Table 1.

DCLK A strobe for DM3:0 and DBUS7:0.The high

going edge latches data into the VMUX.

HD7:0 A bidirectional tri-state data bus connecting the

VMUX to the system processor.

HA3:0 Four system processor address bits used to

address internal registers.

WR An active low write strobe from the system

processor.

RD An active low read strobe from the system

processor.

CEN An active low chip select input from the system

processor.

OVR An active high output which signals impending

buffer overflow.

STUFF An active high output that signals that FEC stuffing

is occuring.

MTICK An output which pulses high for every macroblock

received.

TOOM This active high output indicates that the picture is

likely to exceed the allowable number of bits per

picture.

VAL This line is taken low to indicate that the VMUX is

ready to transmit valid data. The C line in an

X21 system.

TD This is the serial data output from the VMUX.

CTS Indicates that the receiver can accept data. The I

line in an X21 system.

RDY Indicates that the receiver can accept data. The

R line in an X21 system.

XCLK X21 line clock input. 0 to 2.048MHz.

SCLK System clock input. Only the high going edge is

used internally, apart from TXWE generation.

FS A 29.97 Hz frame strobe for the temporal reference

counter. Must be high for at least 4 SCLK periods.

If a 256kBit buffer is being used this Chip Enable

should be used.

TXE2 Active low chip enable for the Transmission buffer.

This is used for the optional second memory chip,

if a 512kBit buffer is being used.

TXWE Active low write enable for the Transmission buffer.

TXOE Active low O/P enable for the Transmission buffer.

TCK Test clock for JTAG.

TMS Test mode select.

TDI Test data I/P.

TDO Test data O/P.

TRST JTAG reset.

TOE When low ALL O/P pins are high impedance.

NOTE: "Barred" active low signals do not appear with a

bar in the main body of the text.

OPERATIONS OF MAJOR BLOCKS

Variable Length Coding

This block is responsible for ordering the data from the

VP2611 Encoder into the correct sequence for the H261 bit

stream, and for performing the variable length coding. It also

uses data supplied by the system controller and the Temporal

Reference Counter.

Data for PTYPE, PSPARE, GSPARE is only obtained

from the system controller, and only 8 bits of PSPARE and

GSPARE information can be transmitted per picture or GOB

respectively. The temporal reference can either be obtained

from an internal counter, from the VP2611 outputs, or can be

written by the system controller. The actual source is

determined by bits in a control register as described later. The

internal counter is clocked from either a frame clock with a

maximum frequency of 29.97Hz, or a 29.97Hz clock derived

from the 27MHz system clock, or it simply counts H.261

frames from the encoder.

There is no support provided for macroblock stuffing,

however FEC stuffing is implemented, and can be used to

provide bit stuffing.

This block is also responsible for converting the absolute

values that are output from the V2611 into the relative values

that are required in parts of the H261 bitstream. The VMUX

has been designed so that it can accept ±15 motion vectors,

rather than the +7/-8 motion vectors produced by the VP2611.

Thus it will be compatible with any future upgrades to the

VP2611 that increase the size of the motion estimator search

window.

VMUX Block

RES Active low reset signal. Must be low for at least 16

SCLK periods.

TXA14:0 Address output to Transmission buffer.

TXD7:0 Bidirectional data interface to Transmission buffer.

TXE1 Active low chip enable for the Transmission buffer.

2

The VMUX section performs the bit packing on the data

coming from the variable length coder. This data is in the form

of a delimiter and a variable number of valid bits. The VMUX

section packs these variable length fields into bytes for

storage in the transmission buffer.

The transmission buffer is controlled by this block. It thus

generates read and write pointers, and performs the

arbitration between read and write operations. Buffer level

VP2612

monitoring is, however, done by the FEC block as described

later.

The two address pointers can be read by the system

processor, thus allowing the level of the buffer to be monitored.

These are provided as 16 bit words with no truncation, and thus

require two bytes. The 16 bit value is internally frozen when the

most significant byte is requested by the system processor, and

for accuracy the write pointer should be read first. There is also

a control register bit which selects a buffer size of either 256kbits

or 512kbits.

FEC Block

The FEC section performs the framing, and adds the error

correction parity bits. If sufficient data for a frame is not available

in the transmission buffer, then the frame will be stuffed

automatically. There is no absolute threshold at which the FEC

will start to stuff, as the buffer level monitor in the FEC only works

to a resolution of ±128bits. FEC stuffing can also be forced by

setting the "Force FEC stuffing" bit in the VMUX/FEC control

register.

If the buffer level reaches a threshold, internally set to 512

short of the buffer being full, the OVERFLOW output is asserted.

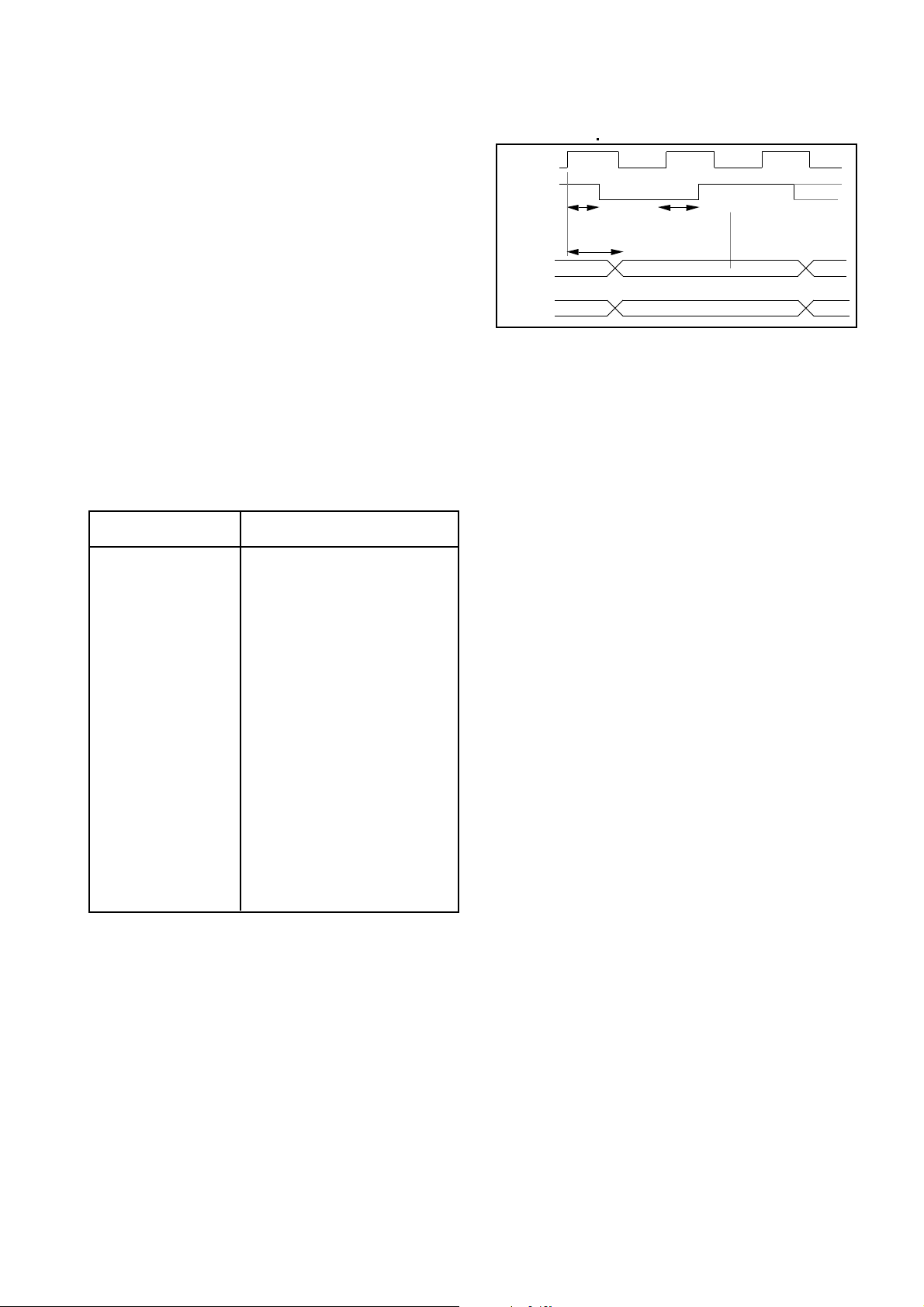

DMODE3:0 FUNCTION

0000 GOB Number

0001 MB Number

0010 Control Decisions

0011 Quant Value

0100 Horizontal MV

0101 Vertical MV

0110 Coded Blk Pattern

0111 Sub-Block No.

1000 Zero Run Count

1001 RLC Coefficient

1010 Not Used

1011 Not Used

1100 Not Used

1101 Not Used

1110 Not Used

1111 Wait State

Table 1

This is to warn the system processor that drastic action is

needed to avert a buffer overflow, which will result in corruption

and loss of data. Since the buffer level monitor only works to

resolution of ±128bits, then the overflow detection can only be

accurate to ±128bits.

VP2611 Interface

The VMUX has been designed to interface directly to

the VP2611 encoder, with no buffering. The interface consists

of two buses DBUS7:0 and DMODE3:0, and a strobe signal

DCLK. The value on DMODE3:0 identifies the data type on

DBUS7:0 during the same period (see Table 1).

The output of the VP2611 is structured such that the

data on DBUS7:0 and DMODE3:0 is always valid for at

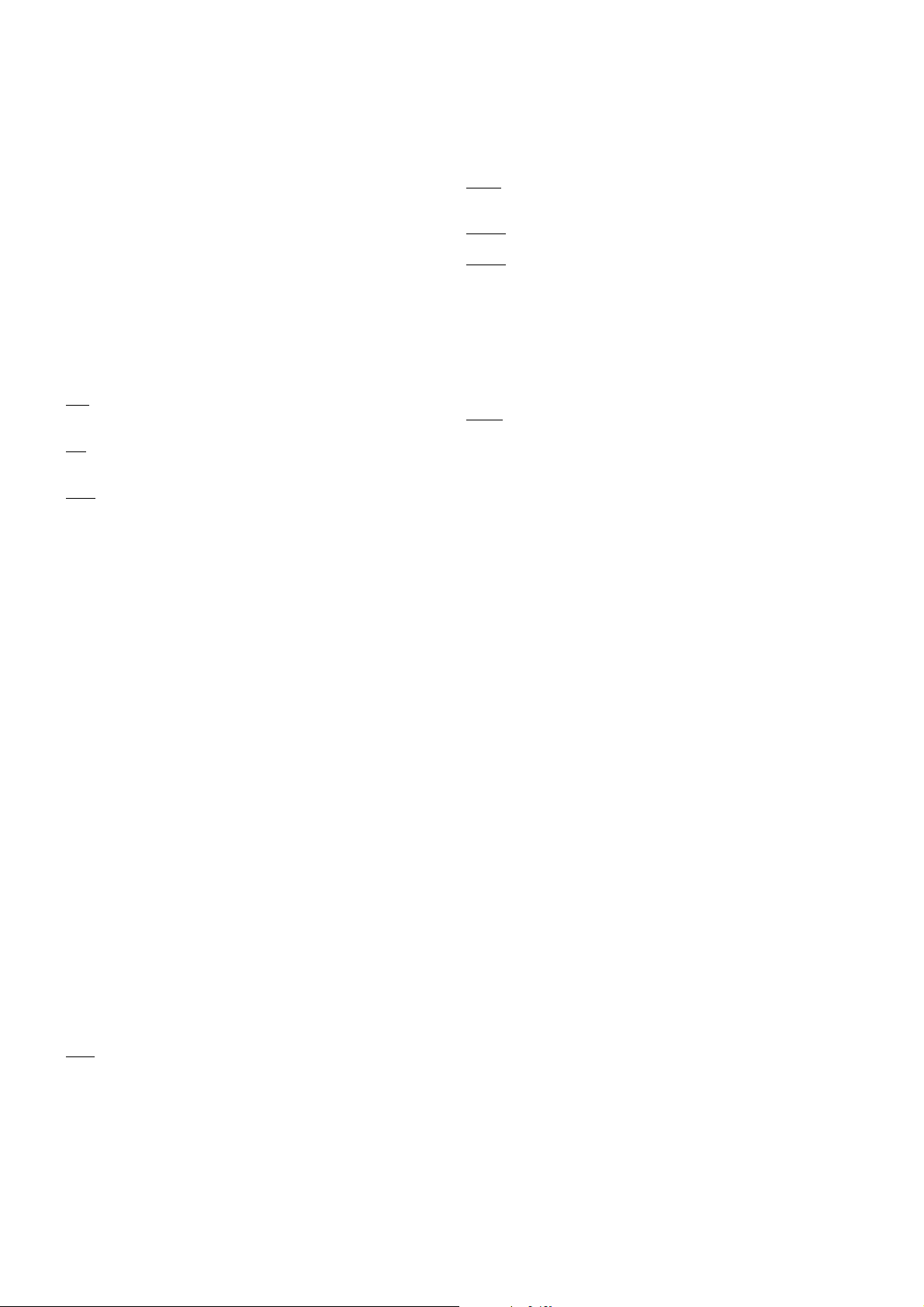

SCLK

DCLK

DATA FROM

VP2611

DMODE

3:0

25ns max

25ns max

20ns max

DATA VALID

DATA VALID

Figure 2. DBUS Timing

least two cycles, and DCLK is high for minimum of one

cycle. The rising DCLK edge occurs one cycle after

DBUS7:0 and DMODE3:0 are valid, as shown in Figure 2.

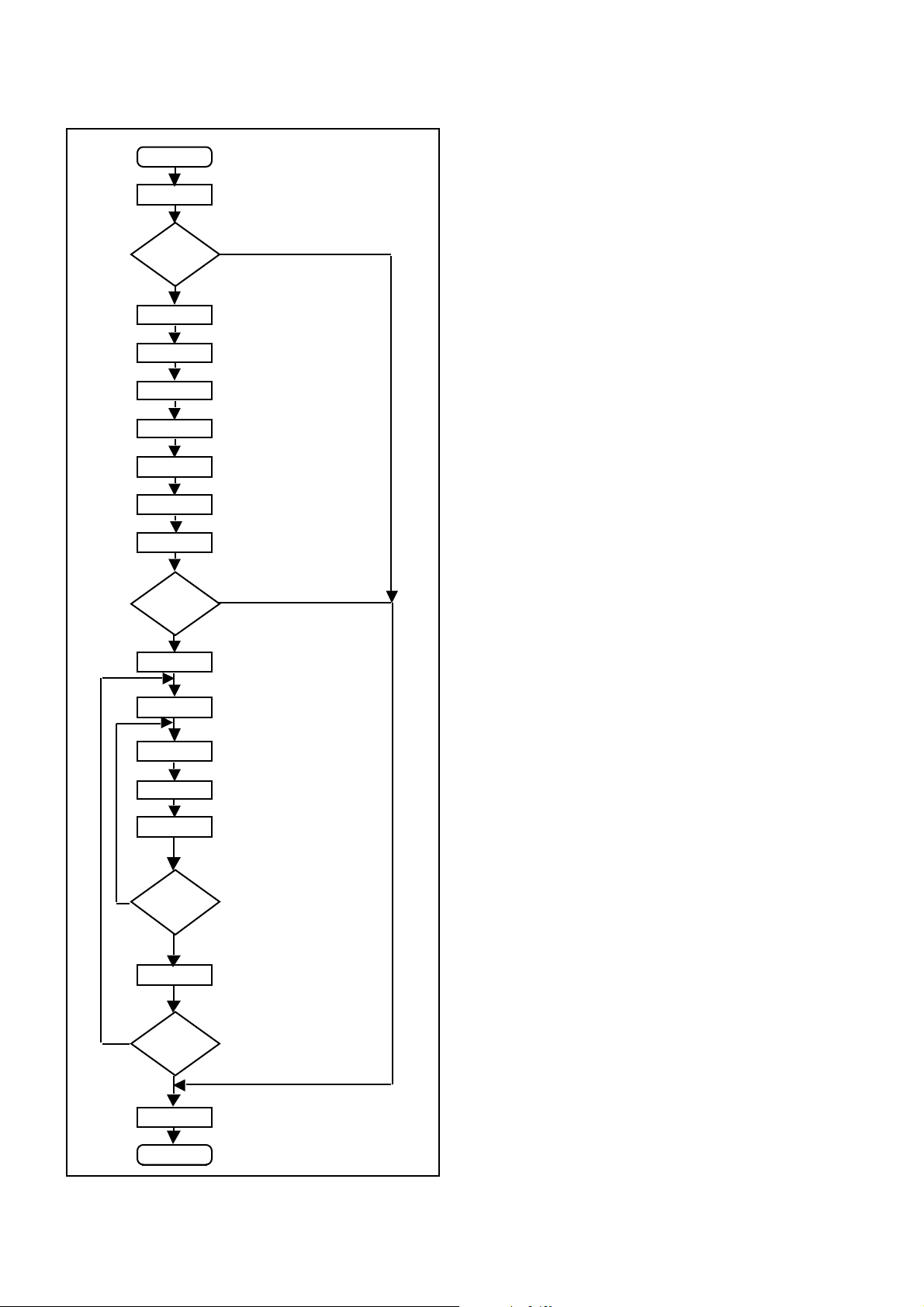

The sequence of events, and the duration of each

event, is shown in Figure 3. These duration times have

been chosen to satisfy the internal requirements of the

VP2612, and Wait States are inserted such that the time

to transfer a macroblock is always 2064 SCLK periods.

The parameters used by the VP2612 are described

in more detail below;

GOB Number : The current GOB Number is provided on

DBUS3:0 after the Control Decisions byte. (DBUS3 is

MSB).

MB Number : After the GOB Number, the macroblock

Number is provided on DBUS5:0 (DBUS5 is MSB).

Control Decisions : This byte shows which control decisions

have been taken for the forthcoming macroblock, and is

the first in the sequence. DBUS0 will be high if a Fixed

Macroblock (FIX MB) was enforced i.e. no new data will

be transmitted this macroblock. DBUS1 indicates

whether Inter (high) or Intra (low) coding was used for the

macroblock. DBUS2 will be high if the macroblock was

filtered, and DBUS3 will be high if motion compensation

was used. DBUS5 will be high if the current frame is being

coded in FAST UPDATE mode. In this mode the complete frame will be intra coded. DBUS6 will be high if the

current frame is a SKIP FRAME i.e. not being coded - so

no coefficients will be transmitted. DBUS4 and DBUS7

are not used.

Quant Value :The quantisation value used in processing the

current macroblock is provided on DBUS4:0 (DBUS4 is

MSB). This represents an actual quantisation level between 2 and 62, in steps of 2 and as defined in H.261.

Horizontal MV : If motion compensation was used the hori-

zontal component of the motion vector will be provided on

DBUS4:0 (DBUS4 is MSB). (This 5 bit value represents

a two's complement number in the range (-15 to +15)

(although only vectors in the range +7/-8 are currently

possible with the VP2611). If motion compensation was

not used this is a don't care value.

3

VP2612

START MB

WAIT

IS IT

A DUMMY

BLOCK?

no

CONTROL (2 cycles)

GOB (2 cycles)

MB

CBP (2 cycles)

QUANT (2 cycles)

HORZ MV (2 cycles)

VERT MV

ARE

ANY BLOCKS

CODED?

yes

WAIT (32 cycles)

SUB BLK NO (15 cycles)

RUN LENGTH

(2 cycles)

yes

(2 cycles)

(2 cycles)

no

(2 cycles)

Vertical MV : If motion compensation was used the vertical

component of the motion vector will be provided on

DBUS4:0 (DBUS4 is MSB). (This 5 bit value represents a

two's complement number in the range ±15 ( although only

vectors in the range (±7) are currently possible with the

VP2611). If motion compensation was not used this is a

don't care value.

Coded Block Pattern : This byte contains a 6 bit linear code

that indicates which of the sub-blocks actually contain

coded data. DBUS6 will be high if sub-block 1 contains

coded data, through to DBUS1 being high if sub-block 6

contains coded data. DBUS7 and DBUS0 are not used.

Sub-block Number : An identifier for the run length coded

coefficients which are about to be made available.

DBUS2:0 contain the coded sub-block number from 1 to 6.

All zero sub-blocks will not be produced, and their corresponding numbers will not appear.

Zero Run Count : The number of zero valued coefficents

preceding the next non zero coefficient is provided on

DBUS5:0 (DBUS5 is MSB). Normally, DBUS7:6 are low,

except to signify the end of a Sub-block, when they will

both be high. Zero Run Count is always followed by a

coefficient, even at the end of a sub-block.

RLC Coefficient : This byte contains the 8 bit coefficient value.

It will always be a non-zero value, except when the

previous Zero Run Count signalled the end of sub-Block.

A zero value is then possible since, as stated above, the

run count is always followed by a coefficient byte, which

may be zero if the last coefficient is zero.

Wait State : This indicates that no valid data is being output

from the DBUS port during this cycle. No DCLK is produced for this state.

MAGNITUDE

WAIT

(2 cycles)

(1 cycle)

SYSTEM PROCESSOR INTERFACE

The system processor interface is a memory

mapped microprocessor compatible interface. It has been

designed for use with any system processor, and consists

of the following buses and signals:

ARE

ALL COEFFS

no

O/P?

yes

HD7:0 Processor Data Bus

HA3:0 LSBs of address bus

WR Active Low Write strobe

RD Active Low Read strobe

WAIT

(wait variable time to make total

time since start of sub-block up

to 335 cycles)

CEN Decoded Active Low chip select

Detailed interface timing is shown in Figure 4. Since there

are several internal pipeline registers which are clocked by

no

ALL BLOCKS

yes

END MB

ARE

O/P?

WAIT

(variable cycles)

SCLK, then access times and strobe widths are dependent

on the period of SCLK.

Table 2 shows the addresses used for each of the user

accessible registers, and the function of each register is

described in detail below.

Figure 3. DBUS Port Flow Chart

4

Loading...

Loading...