The JUPITER circuit is designed for use in dual band and dual

mode mobile phones (CDMA/AMPS) and meets the requirements

for IS-95 when used with other chips from Mitel that form the

Planet chipset. JUPITER is an active filter incorporating circuits

for receiving both CDMA and FM (AMPS).

FEATURES

■ Low Power and Low Voltage Operation with a

Sleep Mode

■ Integrated CDMA and FM Filter with Wide

Dynamic Range

■ Low Inband Gain Ripple Performance and Good

I/Q Matching for the Filter

ABSOLUTE MAXIMUM RATINGS

Supply voltage, V

Operating temperature, T

Storage temperature, T

Junction temperature

CMOS input logic high, V

CMOS input logic low, V

Maximum input voltage at all pins

CC MAX

OP

(ambient)

STG

IH

IL

(at pins)

ORDERING INFORMATION

JUPITER-1/KG/NP1S

20·6V to V

20·7V to 15·3V

230°C to170°C

240°C to 1150°C

230°C to 1125°C

V

10·6V (Max.)

CC

20·6V (Min.)

10·6V

CC MAX

JUPITER

CDMA and FM (AMPS) I/Q Filter

Preliminary Information

DS4724 - 3.1 May 1998

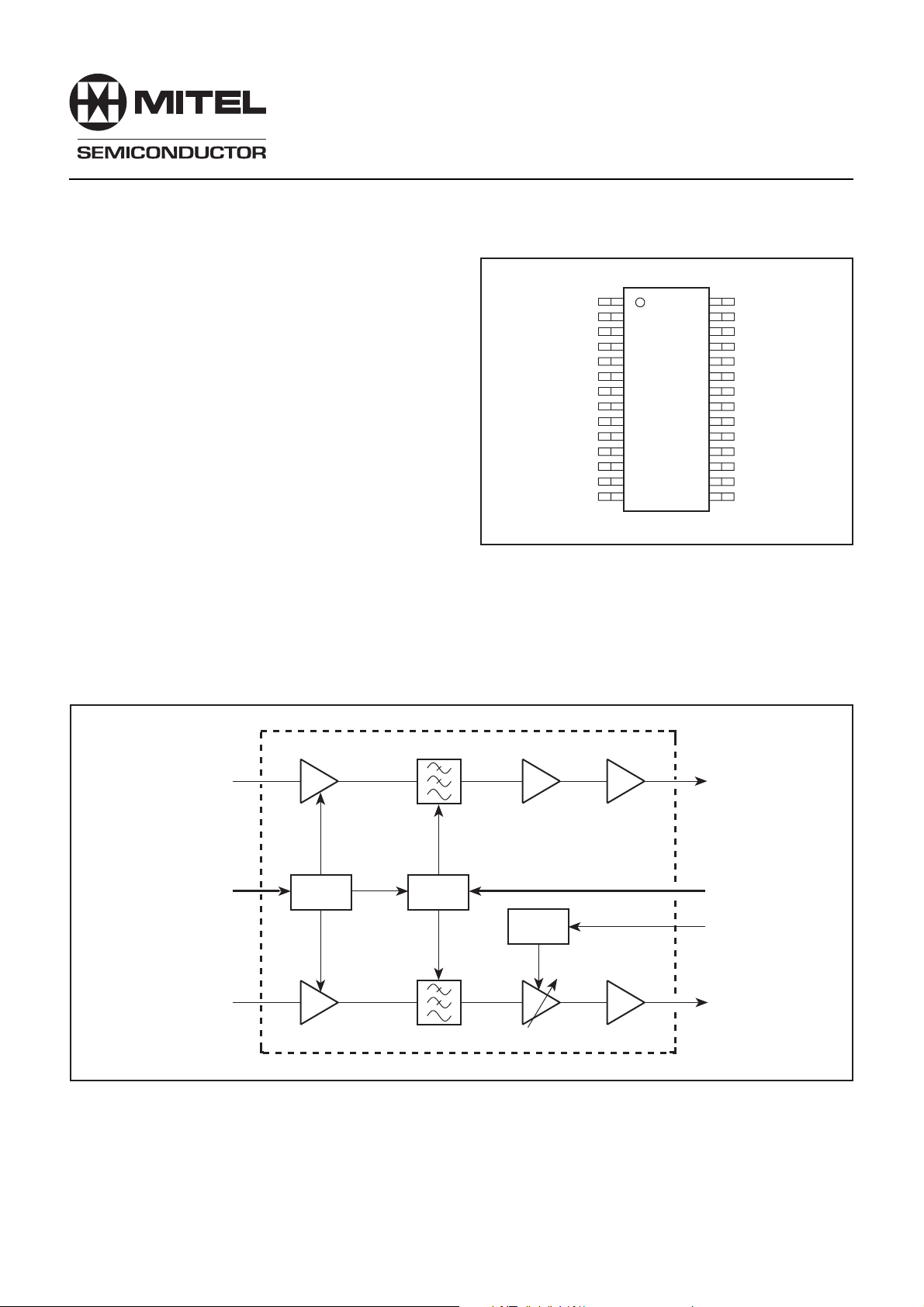

Q_OC_TEST

Q_OC_TESTB

QIN

QINB

Q_OFFSET

Q_OFFSETB

V

TEST

RTUNE

ITUNE

QTUNE

QBAL

QOUT

QOUTB

V

CC

1

2

3

4

5

6

7

JUPITER

8

9

10

11

12

13

14

Fig. 1 Pin connections - top view

ESD PROTECTION

All pins are protected against electrostatic discharge to both

supplies. At least 2kV protection is provided to MIL-STD-883D

Method 3015.7 (human body model).

28

27

26

25

24

23

22

21

20

19

18

17

16

15

I_OC_TEST

I_OC_TESTB

IIN

IINB

I_OFFSET

I_OFFSETB

V

EE

MODE_CDMA

ENABLE

ENTEST

V

REF

IOUT

IOUTB

2

V

EE

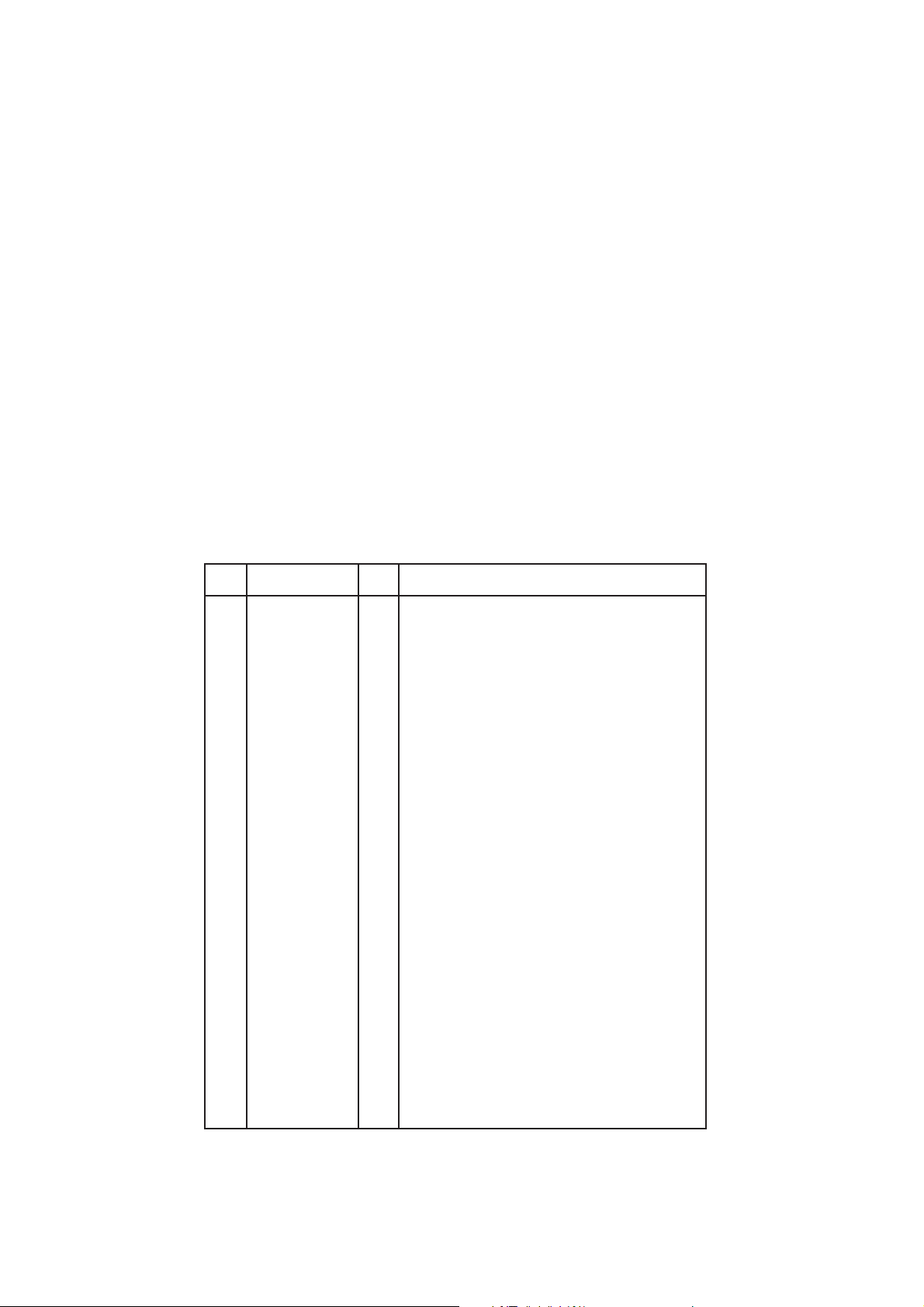

NP28

IIN

MODE

SELECT

INPUTS

QIN

MODE

CONTROL

I CHANNEL

FILTER

CONTROL

GAIN

CONTROL

Q CHANNEL

Fig. 2 Simplified block diagram

IOUT

TUNE

CONTROLS

V

GC

QBAL

QOUT

JUPITER

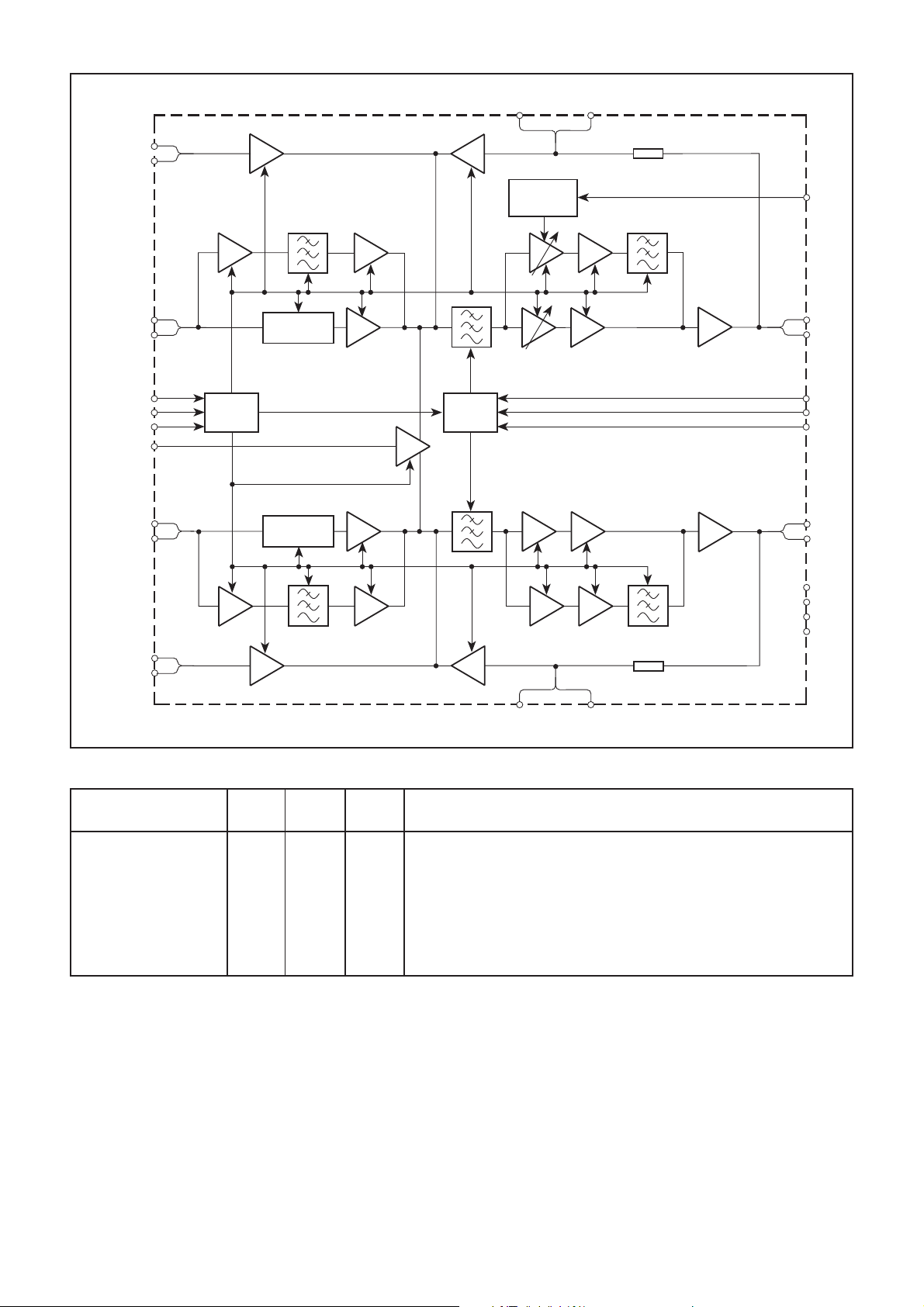

CIRCUIT DESCRIPTION

The block diagram of the JUPITER filter is shown in

Fig. 3. Two tunable active low-pass gyrator filters are designed

with balanced I/Q inputs and outputs.

CDMA MODE

In CDMA mode the filter (F1 on Fig. 3) is a 7th order 0.1dB

ripple continuously tunable elliptic type with the corner frequency

tuned to 690kHz for best stop band attenuation and minimal

phase error (in the overall system). Variable gain stages after the

filter provide the gain control capability. Overall, each of the

CDMA I/Q channels has 45dB nominal voltage gain with the Q

channel having ±2dB gain adjustment range. Separate I/Q

frequency tuning functions are built into the device.

FM MODE

In FM mode the same filter is used; however, the biasing is

designed such that the current density in the transconductor cells

is reduced by a factor of 46, changing the filter’s cutoff frequency

to 15kHz. The filter characteristic of the main channel filter

(gyrator filter) remains the same, i.e. a 0.1dB 7th order elliptic. In

FM mode additional 2nd order Sallen and Key 0.1dB ripple

Chebeyshev filters (F2) are included in the signal path prior to the

gyrators. These improve the out-of-band blocking of the overall

filter. Different amplifiers are used in FM mode to those used in

CDMA mode to enable optimization of the gain distribution in FM

mode for current consumption and dynamic range.

OPERATION

Signal inputs are DC coupled in both CDMA and FM modes.

The device modes are selected by CMOS compatible logic

signals as shown in Table 2. An external resistor should be

connected between RTUNE and ground to set internal currents;

a resistor with a tolerance of 65% and a temperature coefficient

of less than 100ppm is recommended. V

(pin 18) should be

REF

decoupled to VCC to give optimum supply rejection.

A test mode is provided for filter calibration. In this mode, a test

signal is applied to the V

input (pin 7) with ENTEST held high.

TEST

The test mode is designed to interface with the PLUTO baseband

processor, which can provide the test signal and I/QTUNE

voltages and calibrates the filters using an internal auto calibration

algorithm. The algorithm generates two test frequencies and

calibrates the filters to give the correct attenuation at the upper

frequency. The calibration is normally carried out in CDMA

mode: the FM filter performance is scaled accordingly.

Pins are provided for DC offset control for I and Q channels

(I_OFFSET, I_OFFSETB, Q_OFFSET and Q_OFFSETB). In

typical operation, the I_OFFSET/Q_OFFSET pins would be

controlled by a voltage derived from the baseband processor.

However, it is also possible to minimise the DC offset using

external components; this is primarily intended for test purposes.

These feedback components between IOUT/QOUT and

I_OFFSET/Q_OFFSET are shown in Fig. 4 but would not be

used in the normal application

In test mode, these offset controls are disabled and the offsets

are controlled using on-chip feedback. The loop filter for this

feedback uses external 10nF capacitors on pins I_OC_TEST/B

and Q_OC_TEST/B as shown in Fig. 4.

Pin

Q_OC_TEST

1

Q_OC_TESTB

2

QIN

3

QINB

4

Q_OFFSET

5

Q_OFFSETB

6

V

7

8

RTUNE

9

ITUNE

10

QTUNE

11

QBAL

12

QOUT

13

QOUTB

14

V

15

VEE2

16

IOUTB

17

IOUT

18

V

19

ENTEST

20

ENABLE

21

MODE_CDMA

22

V

23

I_OFFSETB

24

I_OFFSET

25

IINB

26

IIN

27

I_OC_TESTB

28

I_OC_TEST

TEST

CC

REF

EE

Name

I/O

Q channel offset control in test mode

I

Q channel offset control in test mode (balanced)

I

Q channel CDMA/FM input.

I

Q channel CDMA/FM input (balanced)

I

Q channel offset control

I

Q channel offset control (high gain mode)

I

Test mode signal input for tuning operation

I

Description

Precision resistor for current definition (18k)

I filter tuning control

I

Q filter tuning control

I

Q channel gain adjust voltage, VGC

I

Q channel CDMA/FM output

O

Q channel CDMA/FM output (balanced)

O

Supply

P

Ground

P

I channel CDMA (balanced)

O

I channel CDMA

O

Reference voltage decouple

Mode control (see Table 2)

I

Mode control (see Table 2)

I

Mode control (see Table 2)

I

Ground (substrate)

P

I channel offset control (high gain mode)

I

I channel offset control

I

I channel CDMA (balanced)

I

I channel CDMA

I

I channel offset control in test mode (balanced)

I

I channel offset control in test mode

I

Table 1 Pin descriptions

2

Q_OFFSET

Q_OFFSETB

JUPITER

Q_OC_TESTBQ_OC_TEST

12

5

6

-0·1

dB

gm

gm

Q CHANNEL

± 2dB

F2

gm

50k

F3

V

GC

11

QBAL

QIN

QINB

ENTEST

ENABLE

MODE_CDMA

V

TEST

IIN

IINB

I_OFFSET

I_OFFSETB

3

-0·1

dB

ATTENUATOR

ATTENUATOR

F2

gm

4

19

20

21

7

26

25

24

23

MODE

CONTROL

gm

gm

gm

gm

F1

FILTER

CONTROL

F1

gm

F3

50k

28 27

I_OC_TESTBI_OC_TEST

X1

X1

12

13

10

8

9

17

16

15

22

14

18

QOUT

QOUTB

QTUNE

RTUNE

ITUNE

IOUT

IOUTB

VEE2

V

EE

V

CC

V

REF

Description ENTEST

ENABLE

Sleep mode

CDMA mode

FM mode

CDMA filter testmode

FM filter test mode

Disallowed mode

MODE_

CDMA

0

1

1

1

1

0

X

1

0

1

0

X

Fig. 3 Block diagram

All circuits powered down

1

Biasing and CDMA signal path on

0

Biasing and FM signal path on

0

Biasing, CDMA test and CDMA signal path on, excluding input amplifier

1

Biasing, FM test and FM signal path on, excluding input amplifier.

1

This is functionally the same as sleep mode but has higher I

0

In sleep mode PLUTO applies a logic high to ENTEST

Table 2 Truth table for mode control lines

Comments

CC

.

3

Loading...

Loading...