Microsoft Xbox 360 Schematics Xenon

PAGE

CONTENTS

[1] COVER PAGE

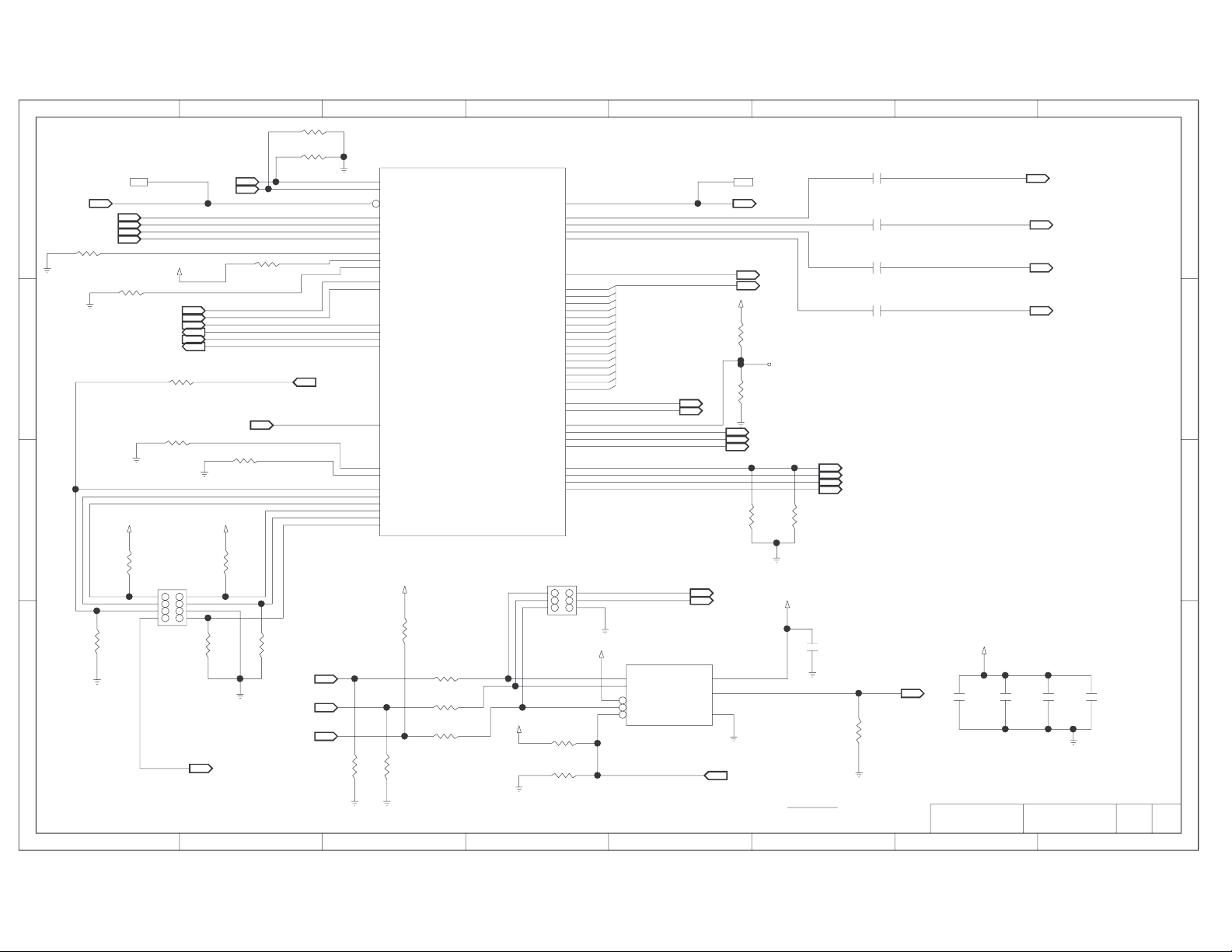

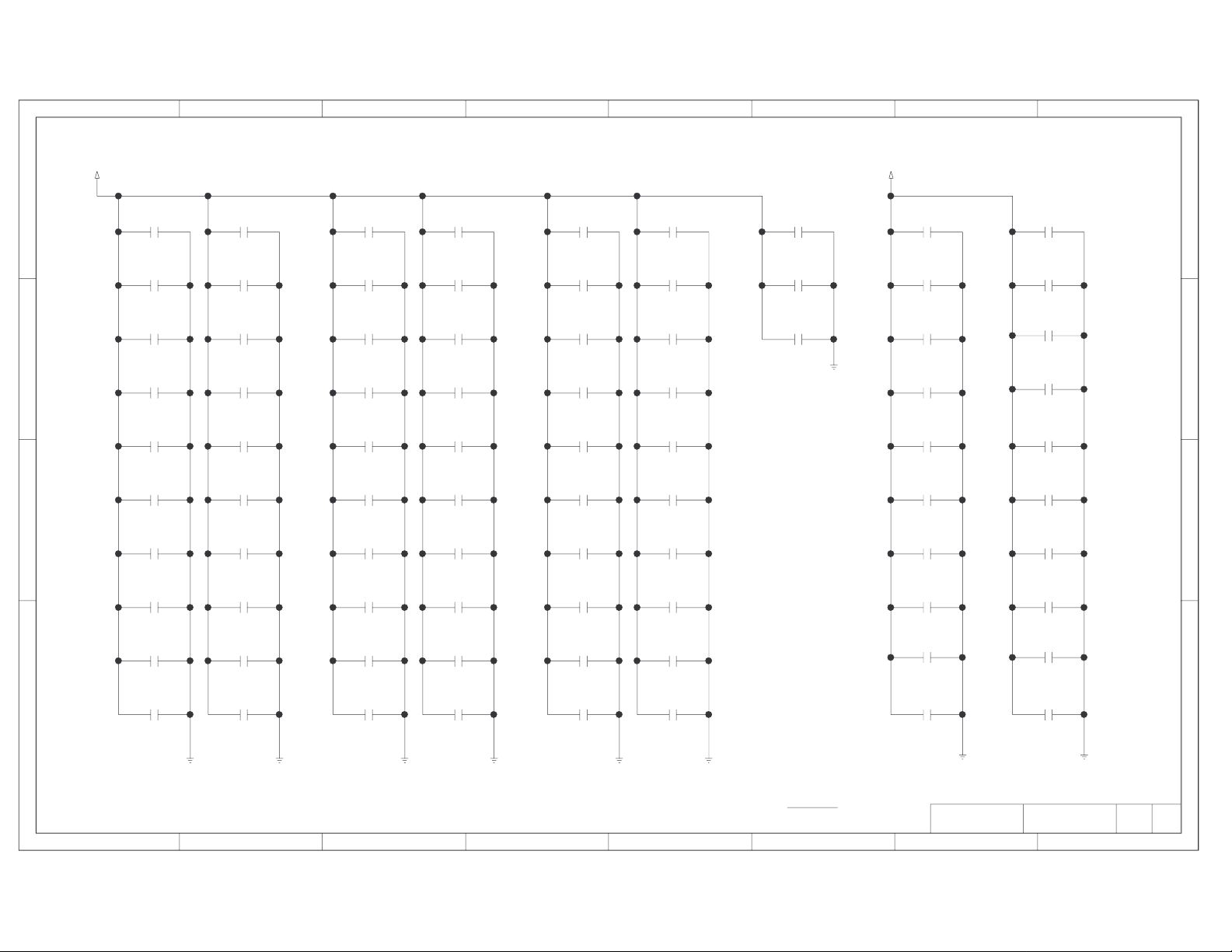

[2] CLOCK DIAGRAM

[3] RESET/ENABLE DIAGRAM

[4] CPU, CLOCKS + EEPRO M + STRAPPING

[5] CPU, FSB

[6] CPU, FSB POWER + PLL POWER

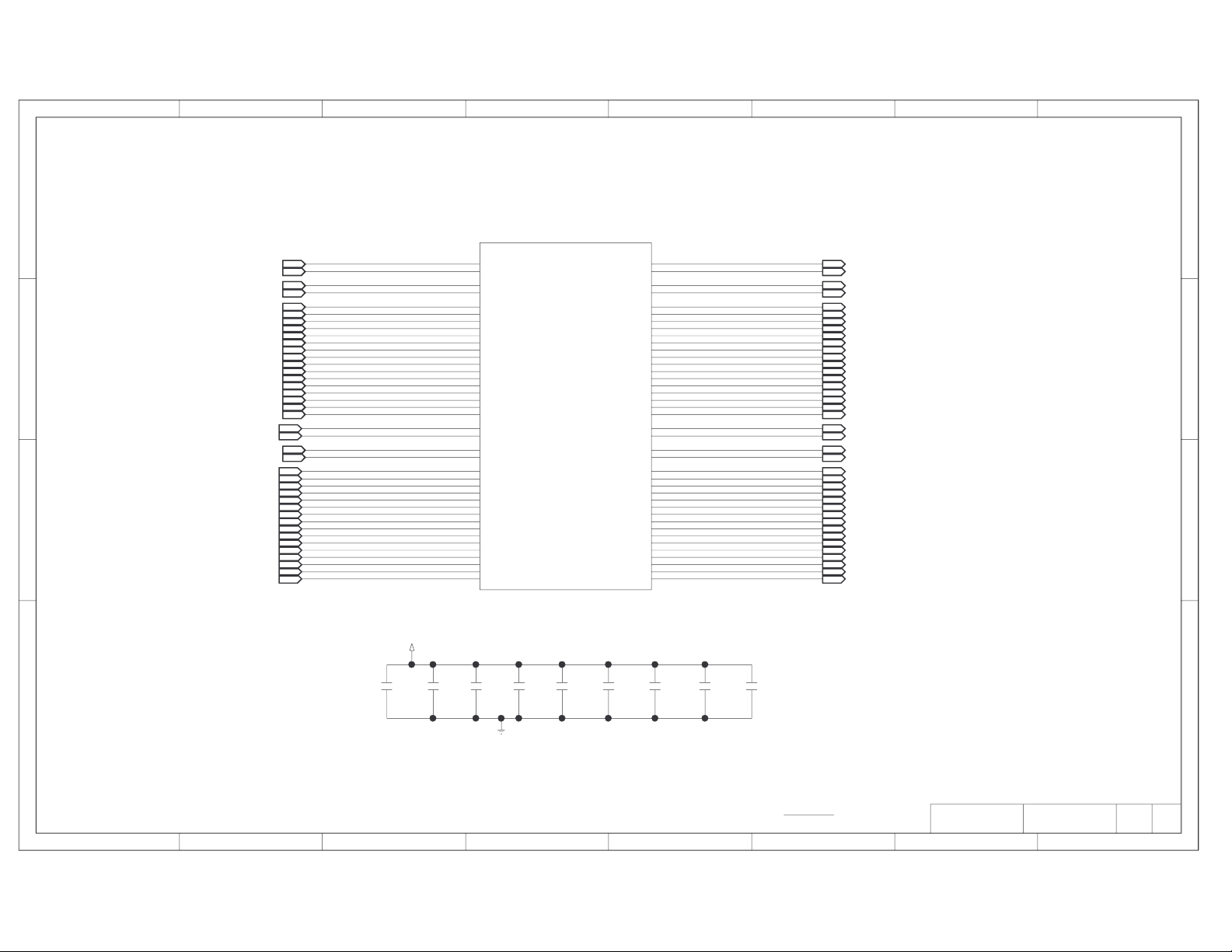

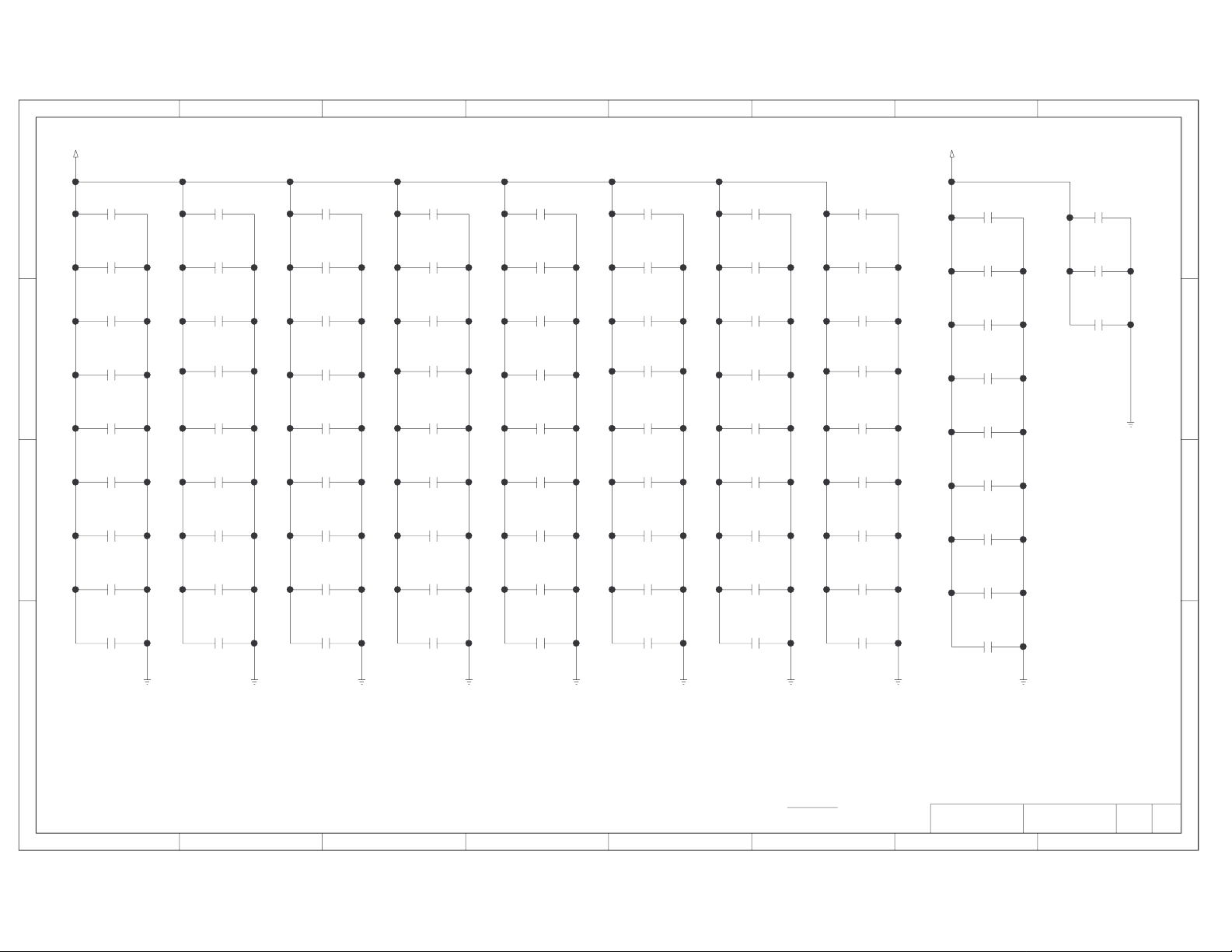

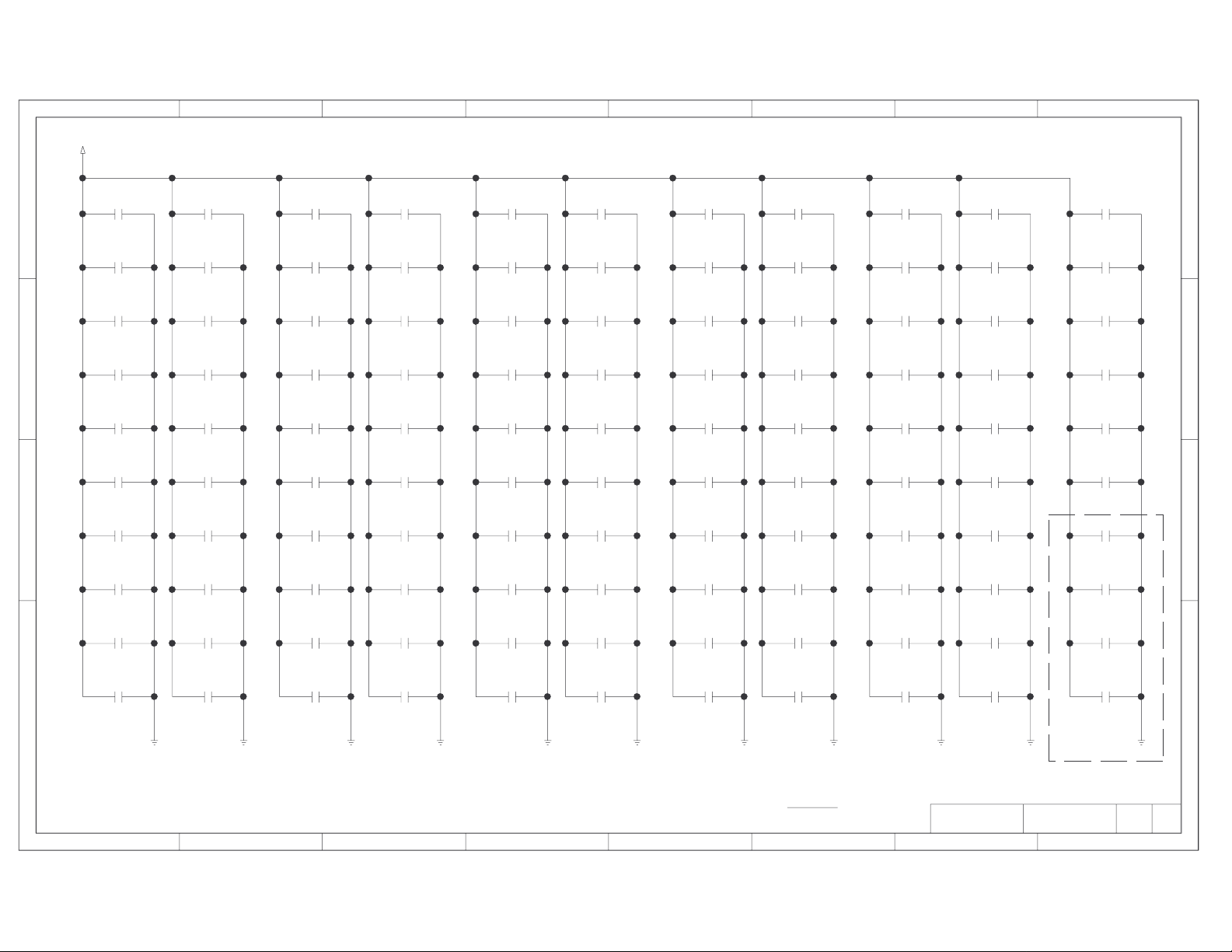

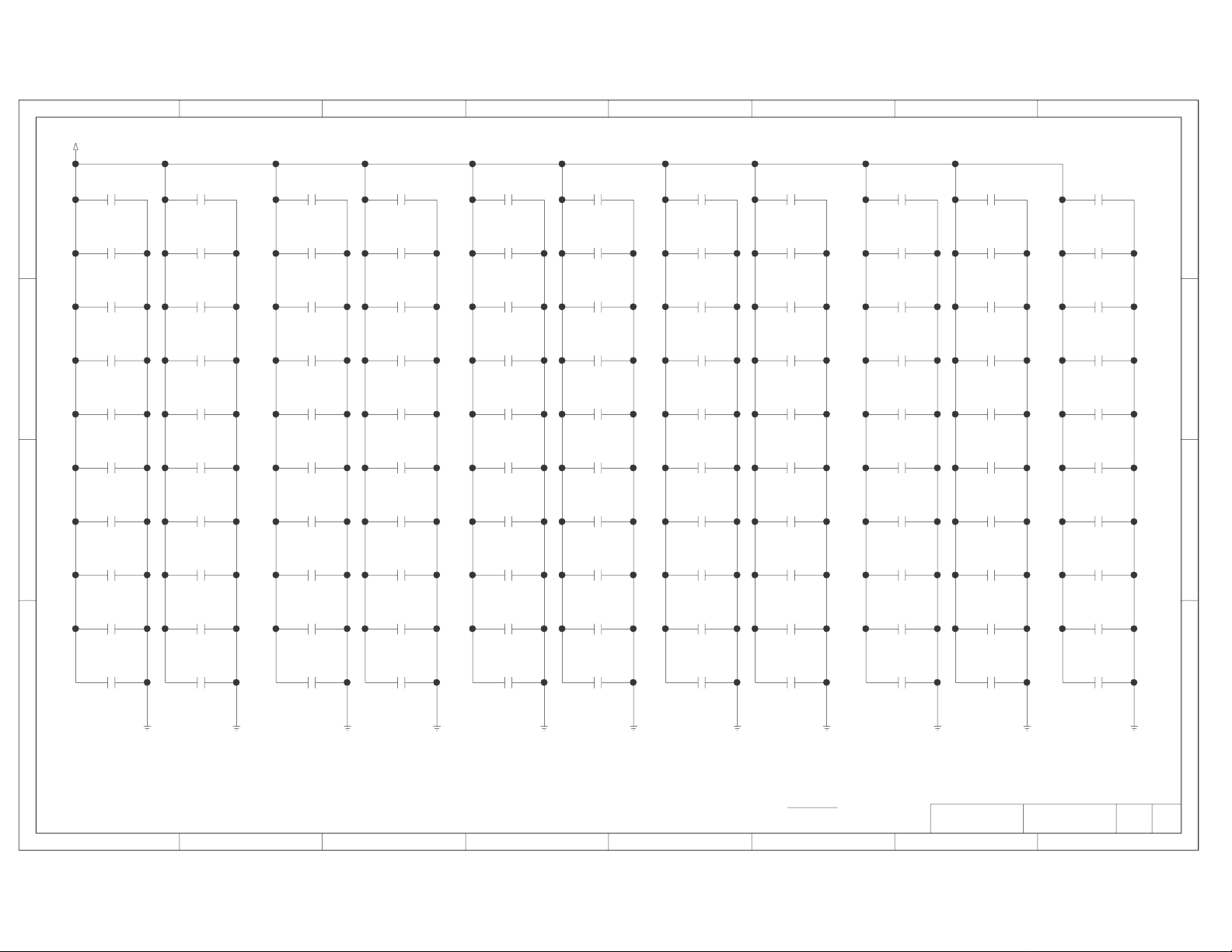

[7] CPU, CORE POWER

[8] CPU, POWER

[9] CPU, DECOUPLING

[10] CPU, DECOUPLING

[11] CPU, DECOUPLING

[12] GPU, FSB

[13] GPU, VIDEO + PCIEX + EEPROM

[14] GPU, MEMORY CONTROLLER A + B

[15] GPU, MEMORY CONTROLLER C + D

[16] GPU, PLL POWER + FSB POWER

[17] GPU, CORE POWER + MEM POWER

[18] GPU, DECOUPLING

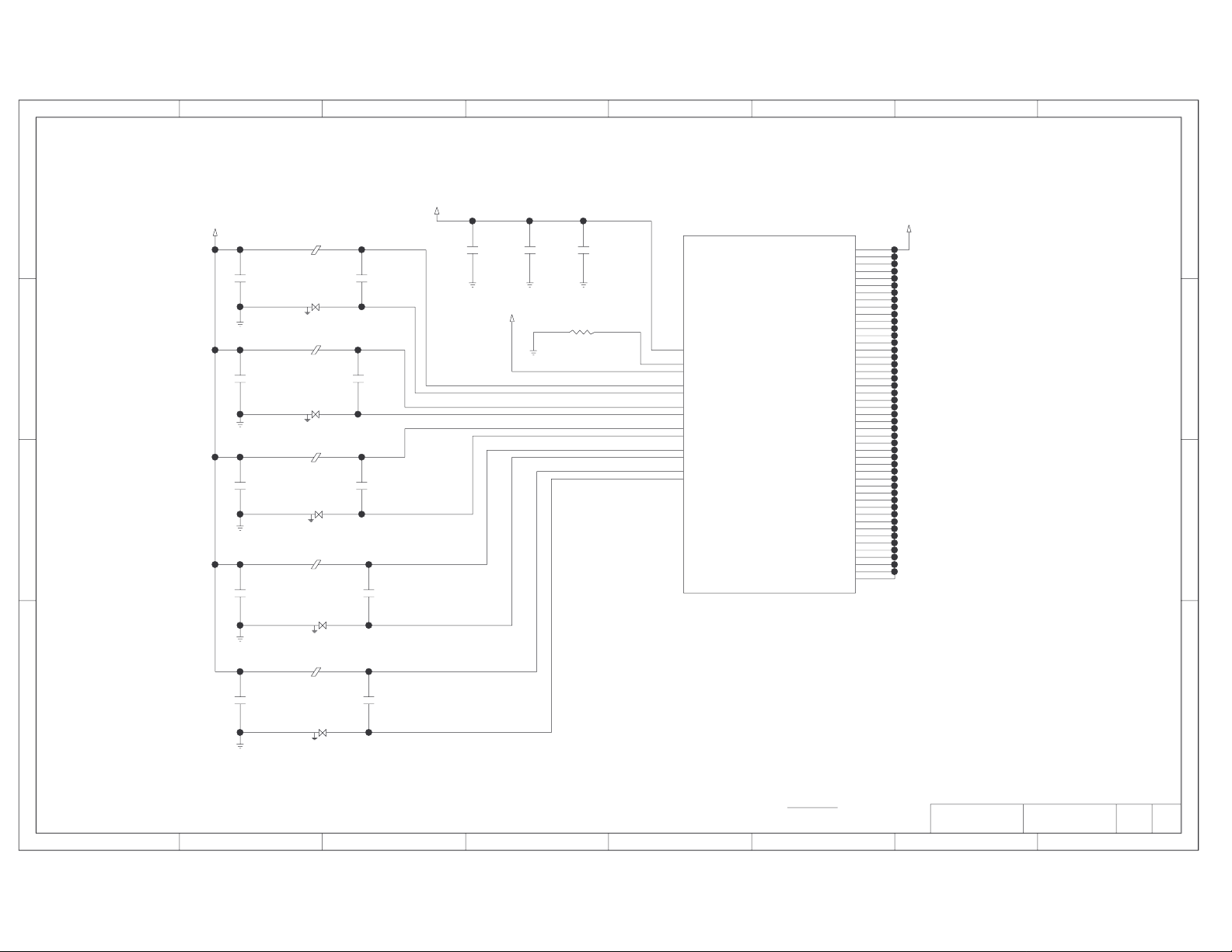

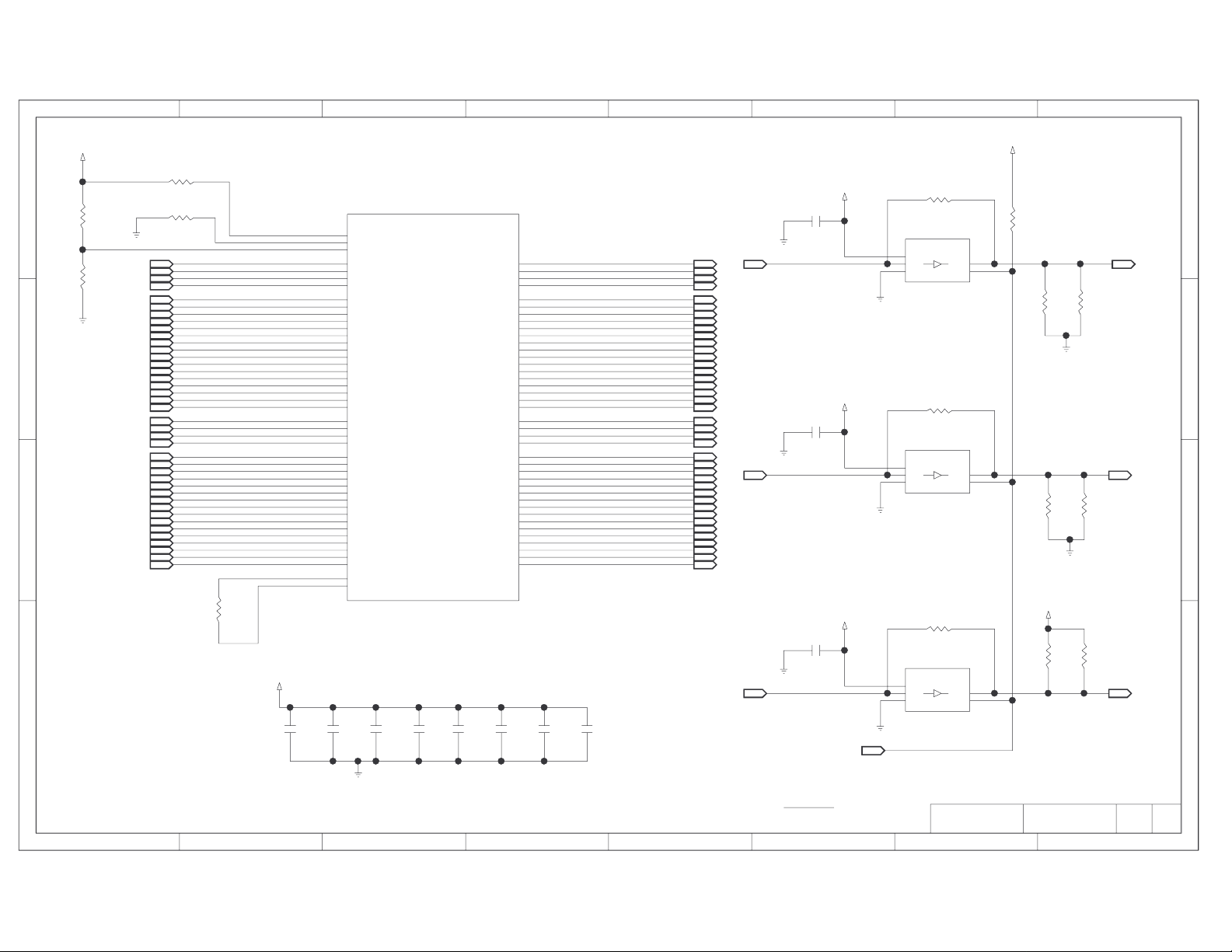

[19] DUAL ETHERNET PHY

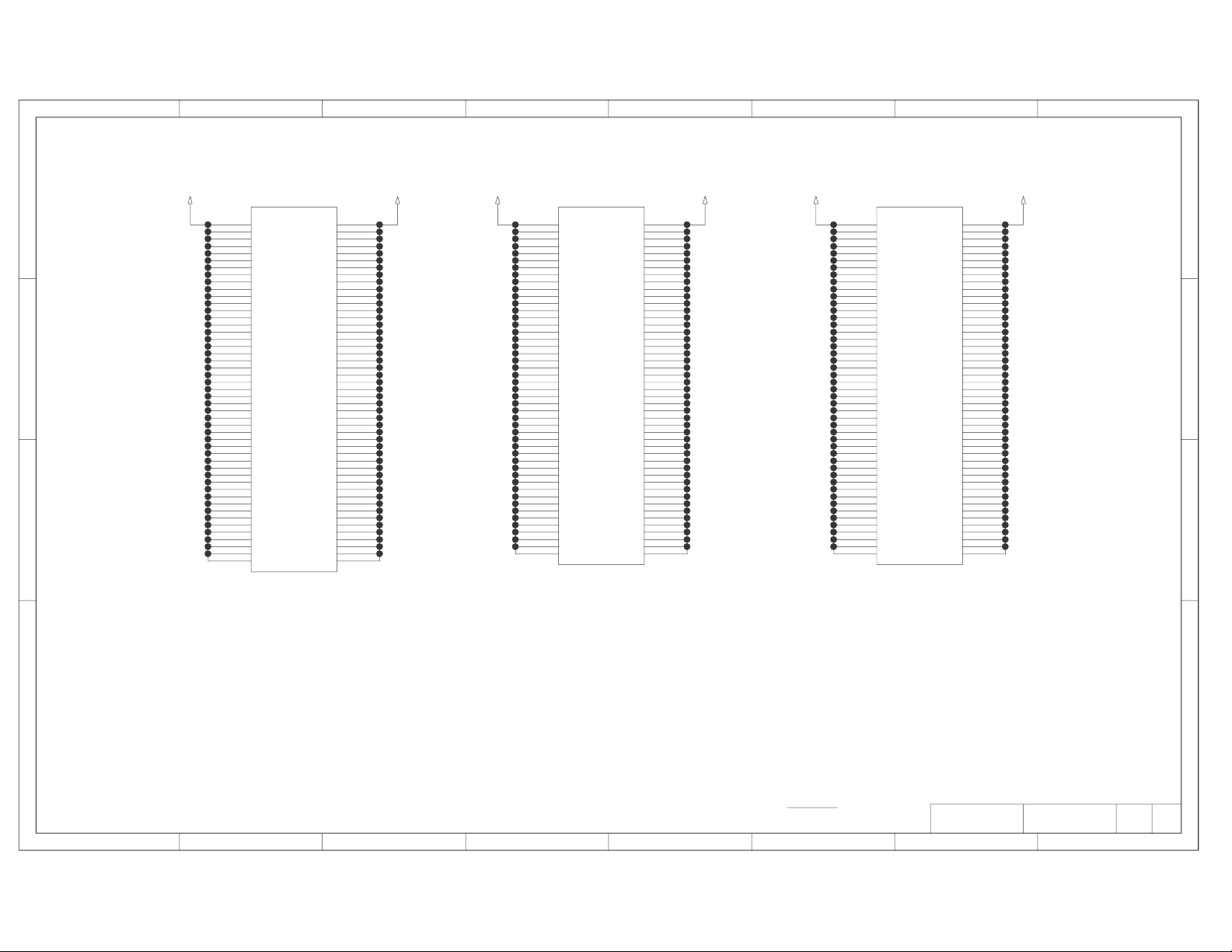

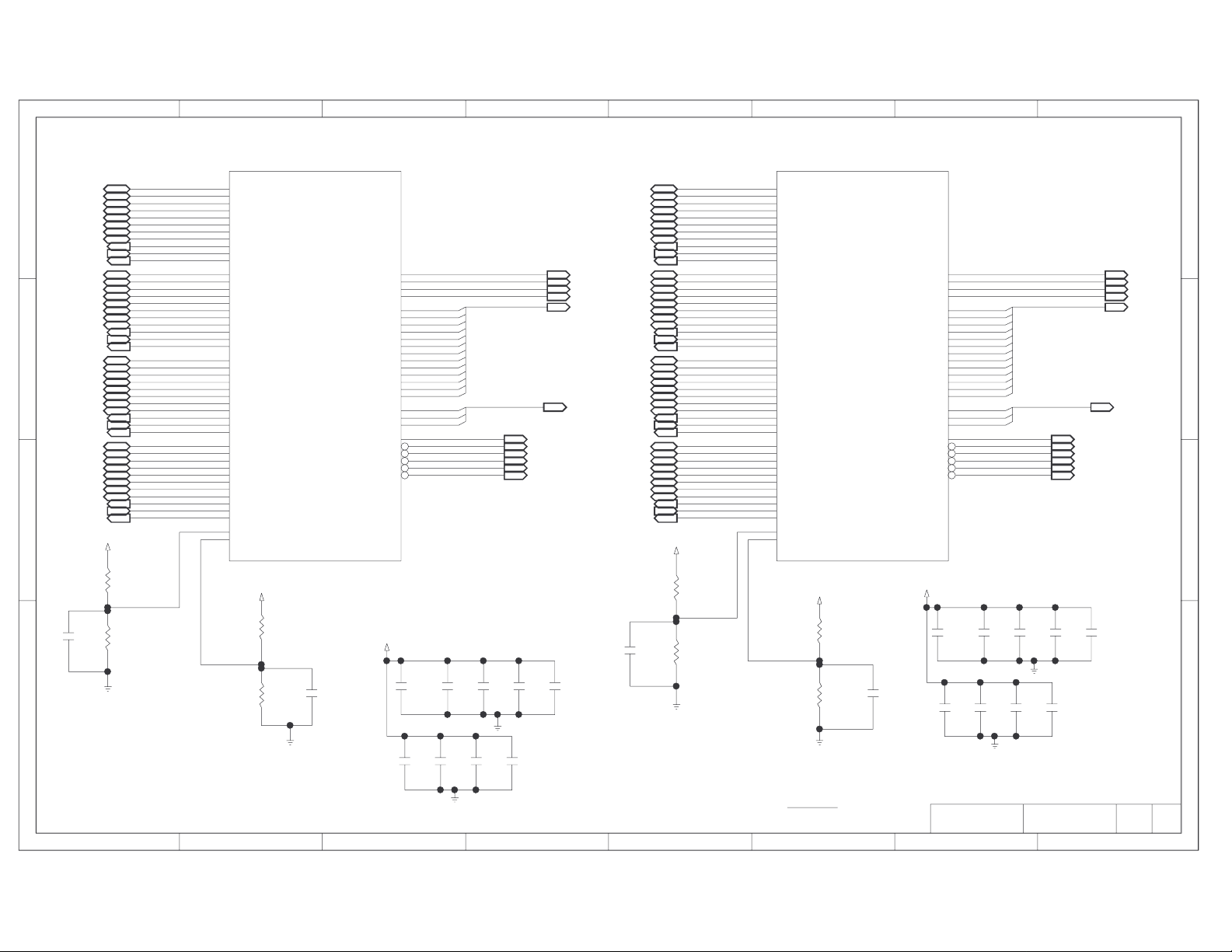

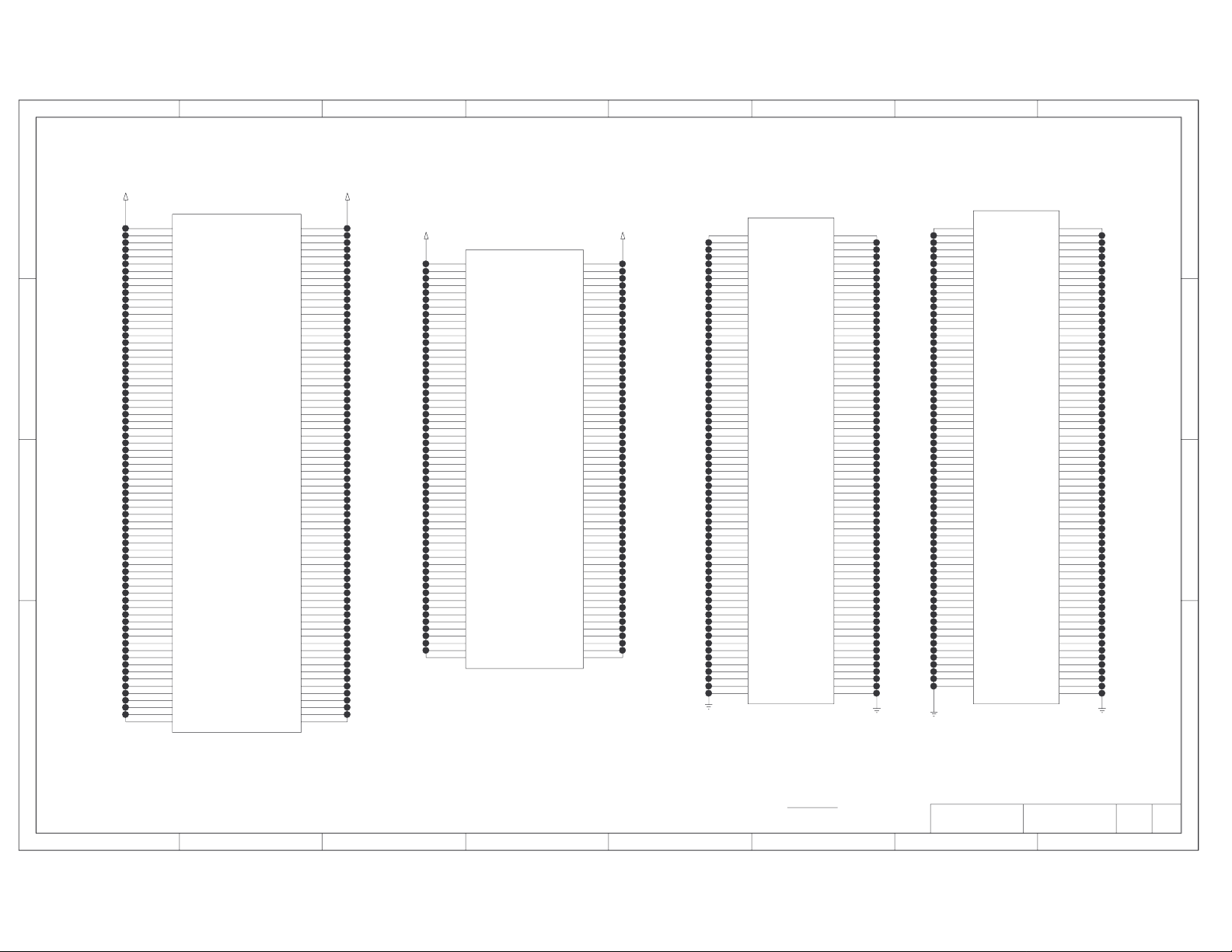

[20] MEMORY, A (TOP)

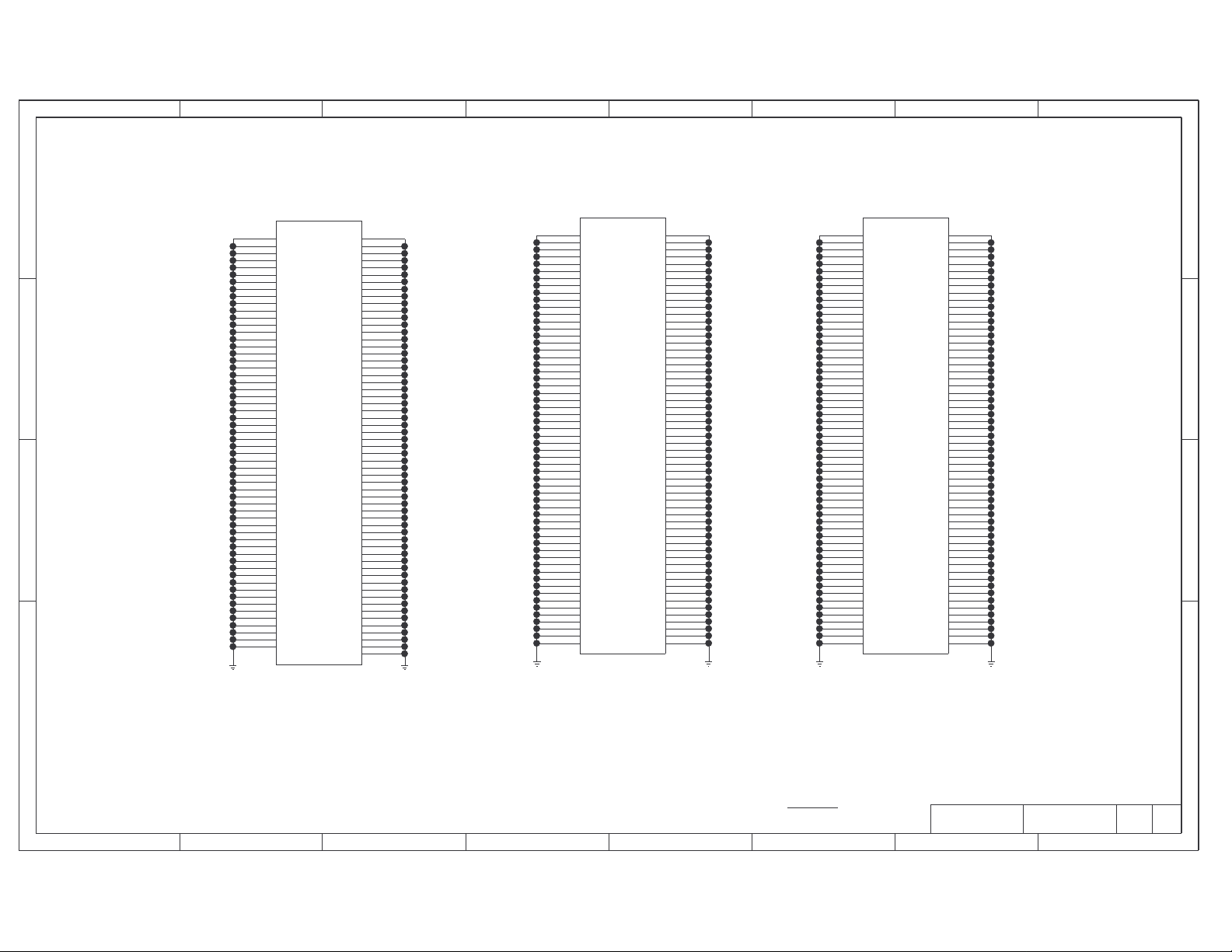

[21] MEMORY, A MIRRORED (BOTTOM)

[22] MEMORY, B (TOP)

[23] MEMORY, B MIRRORED (BOTTOM)

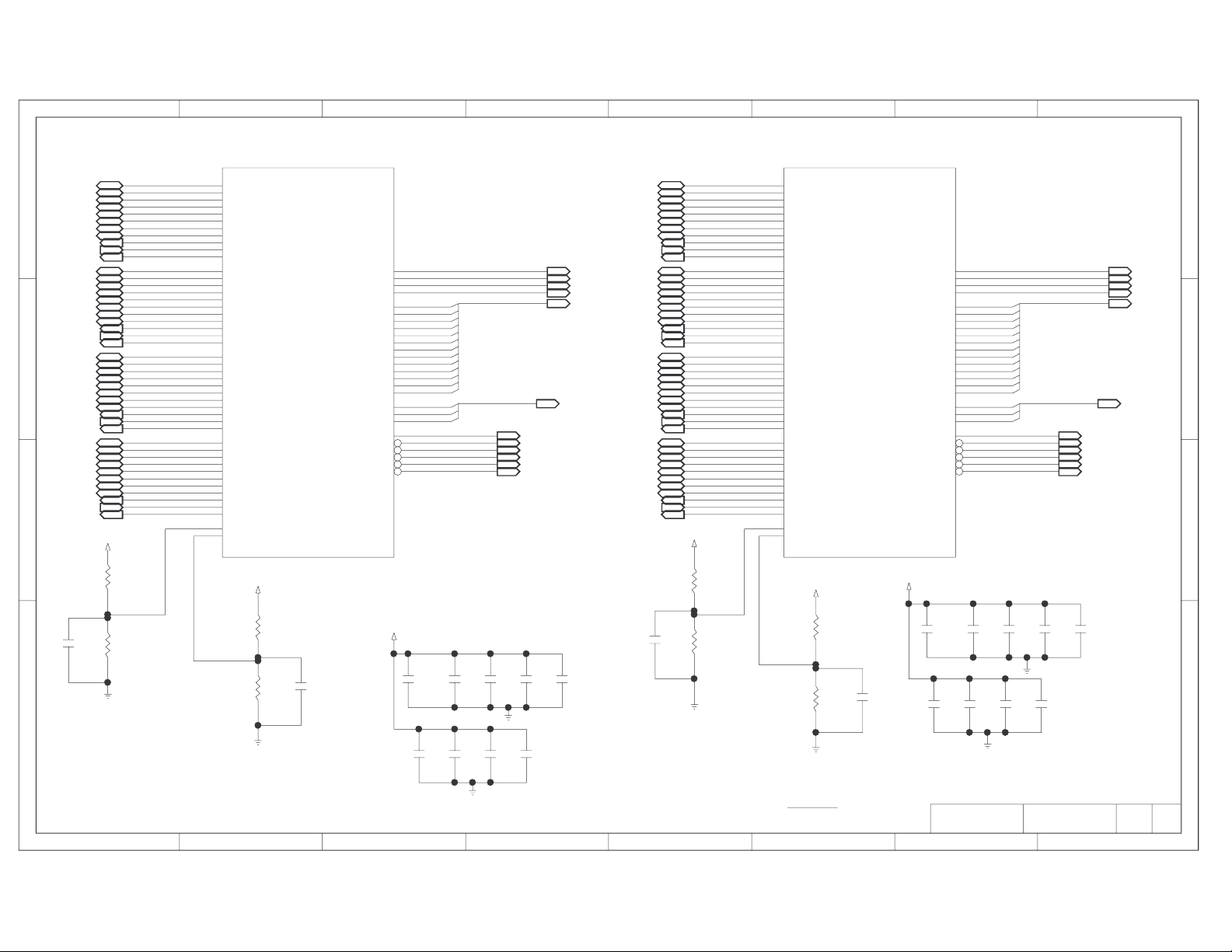

[24] MEMORY, C (TOP)

[25] MEMORY, C MIRRORED (BOTTOM)

[26] MEMORY, D (TOP)

[27] MEMORY, D MIRRORED (BOTTOM)

[28] ANA, CLOCKS + STRAPPING

[29] ANA, VIDEO + FAN + JTAG

[30] ANA, POWER + DECOUPLING

[31] DEBUG MAPPING, WN DBG VS WN XDK

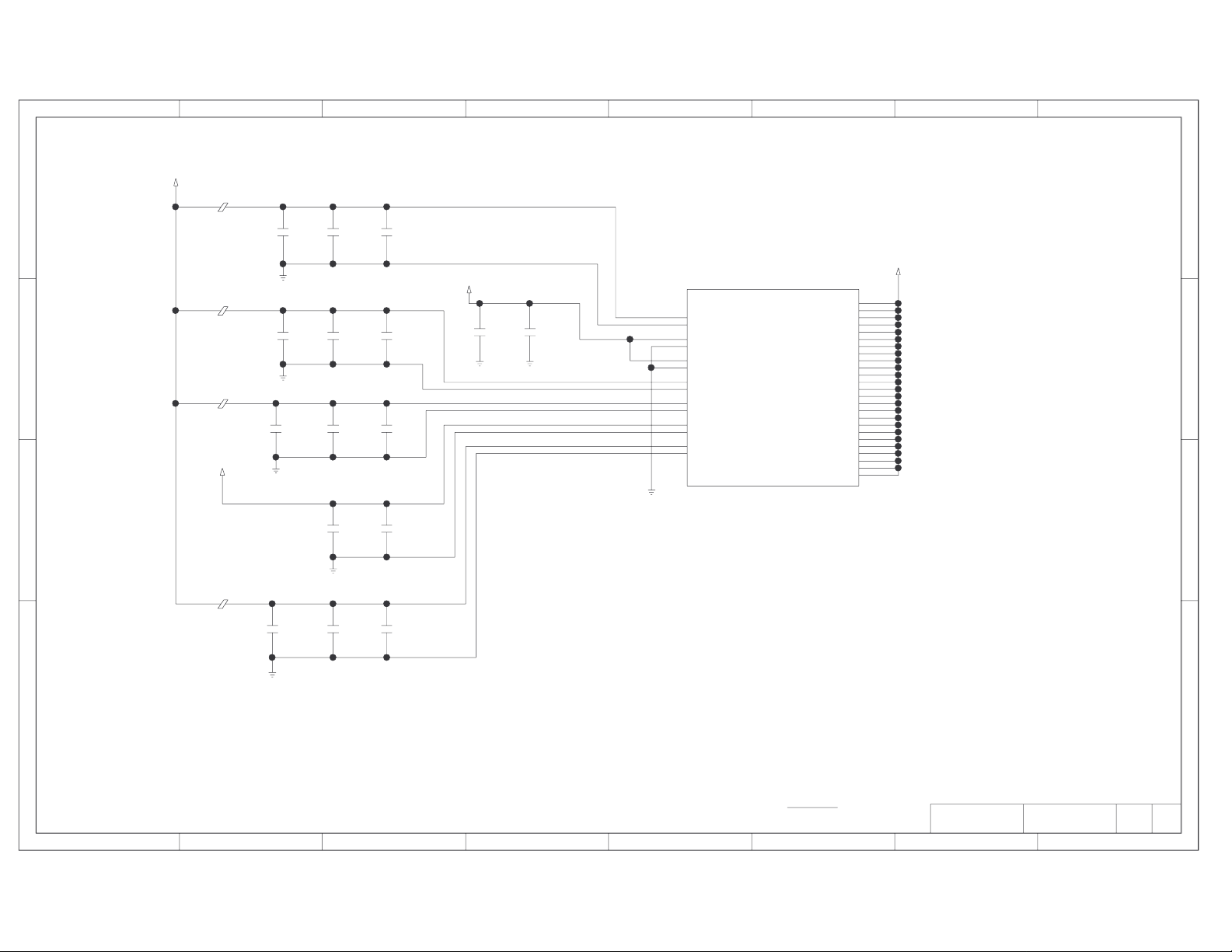

[32] POWER TRACE EMI CAPS

SCHEMA TI C REV PB N U M BER VER BOM RELEASE DATE

PAGE

CONTENTS

K7 X803600-011 RETAIL XX/XX/XX

[33] SB, PCIEX + SMM GPIO + JTAG

[34] SB, SMC

[35] SB, FLASH + USB + SPI

[36] SB, ETHERNET + AUDIO + SATA

[37] SB, STANDBY POWER + DECOUPLE

[38] SB, MAIN POWER + DECOUPLE

[39] SB OUT, ETHERNET

[40] SB OUT, AUDIO

[41] SB O U T, FLASH

[42] SB OUT, FAN + INFRARED + BUTTONS

[43] CONN, AVIP

[44] CONN, RJ45 + USB COMBO

[45] CONN, GAME PORTS + MEMORY PORTS

[46] BACKUP CLOCK + V_5P0 DUAL

[47] CONN, ODD AND HDD

[48] CONN, ARGON + POWER

[49] VREGS, INPUT + OUTPUT FILTERS

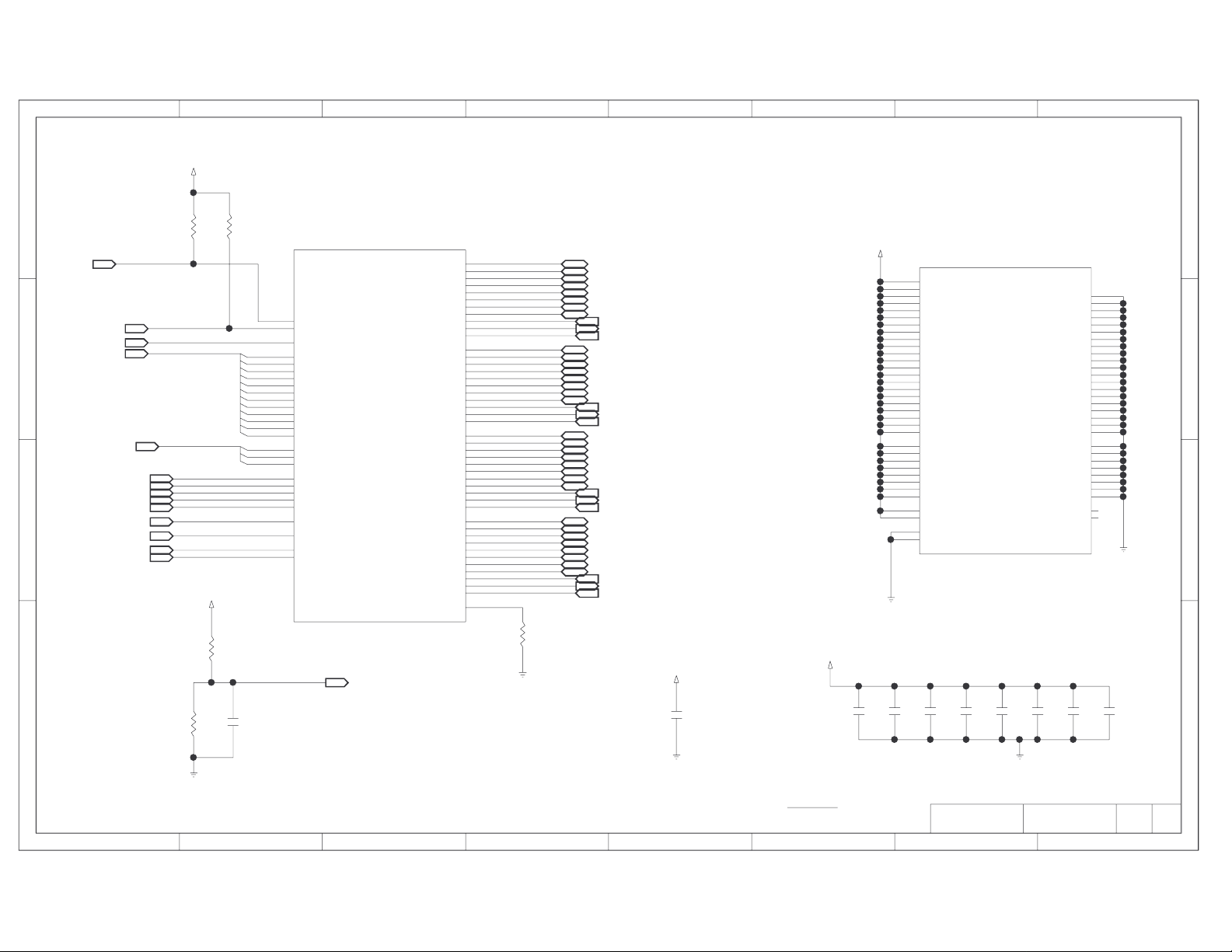

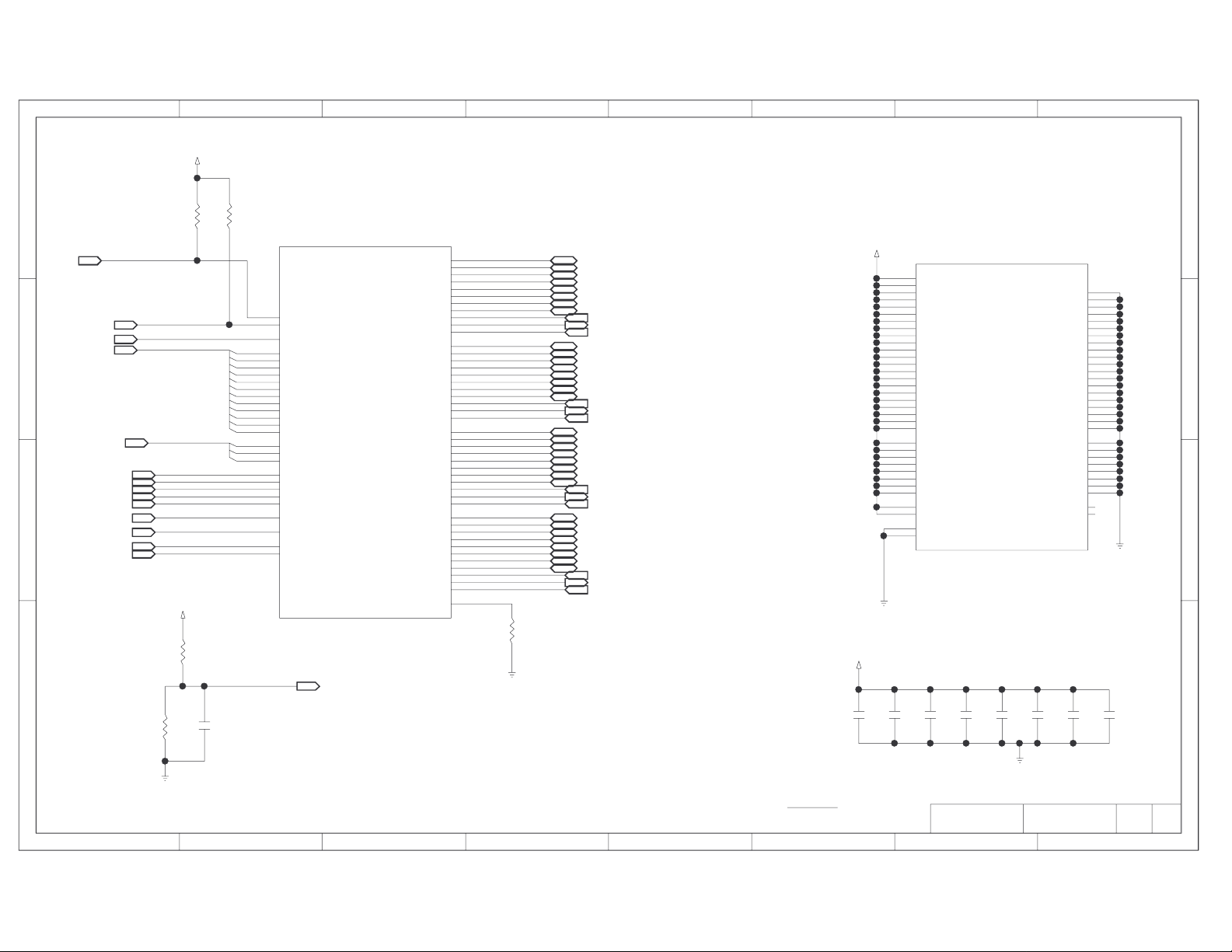

[50] VREGS, CPU CONTROLLER

[51] VREGS, GPU OUTPUT PHASE 1,2,3

[52] VREGS, GPU CONTROLLER

[53] VREGS, GPU OUTPUT PHASE 1,2

[54] VREGS, SWITCHED 1.8, 5.0V

[55] VREGS, LINEAR REGULATORS

[56] XDK, DEBUG CONN

[57] DEBUG BOARD, CPU + GPU BREAKO U T

[58] DEBUG BOARD, CPU CONN

[59] DEBUG BOARD, CPU CONN + TERM

[60] DEBUG BOARD, CPU TERM

[61] DEBUG BOARD, TITAN + YETI CONN

[62] DEBUG BOARD, GPU CONN + TERM

[63] XDK, LEDS

[64] LABELS AND MOUNTING

XENON

RETAIL

REV K7

FAB K

RULES: (APPLIED WHEN POSSIBLE)

1.) MSB TO LSB IS TOP TO BOTTOM

2.) WHEN POSSIBLE: INPUTS ON LEFT, OUTPUTS ON RIGHT

3.) ORDER OF PAGES=CHIP INTERFACES, TERMINATION, POWER, DECOUPLING

4.) AVOID USING OFF PAGE CONNECTORS FOR ON PAGE CONNECTIONS

5.) LANED SIGNAL S ARE GROU PED ON SYMBOLS

6.) TRANSIMITTER NAME USED AS PREFIX WITH RX A ND TX CONNECTIONS

7.) SUFFIX V_ IS USED FOR VOLTAGE RAIL SIGNAL NAMES

8.) SUFFIX _DP AND _DN ARE USED FOR DIFFERIENTAL PAIRS

9.) UNNAMED NETS ARE NAMED WITH /2 TEXT SIZE

10.) SUFFIX _N FOR ACTIVE LOW OR N JUNCTION

12.) SUFFIX _P FOR P JUNCTION

13.) SUFFIX _EN FOR ENABLE

14.) 'CLK' FOR CLOCKS, 'RST' FOR RESETS

15.) PWRGD FOR POWER GOOD

[PAGE_TITLE=COVER PAGE]

DRAWING

XENON_FABK

Wed Aug 24 09:41:55 2005

BOM RELEASE DATE

SIGNATURE

DRN BY

CHK BY

ENGR

APVD

APVD

APVD

XENON

PLEASE REFER TO THE XENON DESI GN SPEC

PB NUMBER

XX/XX/XX

DATE

MICROSOFT XBOX

TITLE

MICROSOFT

CONFIDENTIAL

X803600-011

SCH, PBA, XENON

PROJECT NAME

XENON_RETAIL

PAGE

1/73

REV

K7

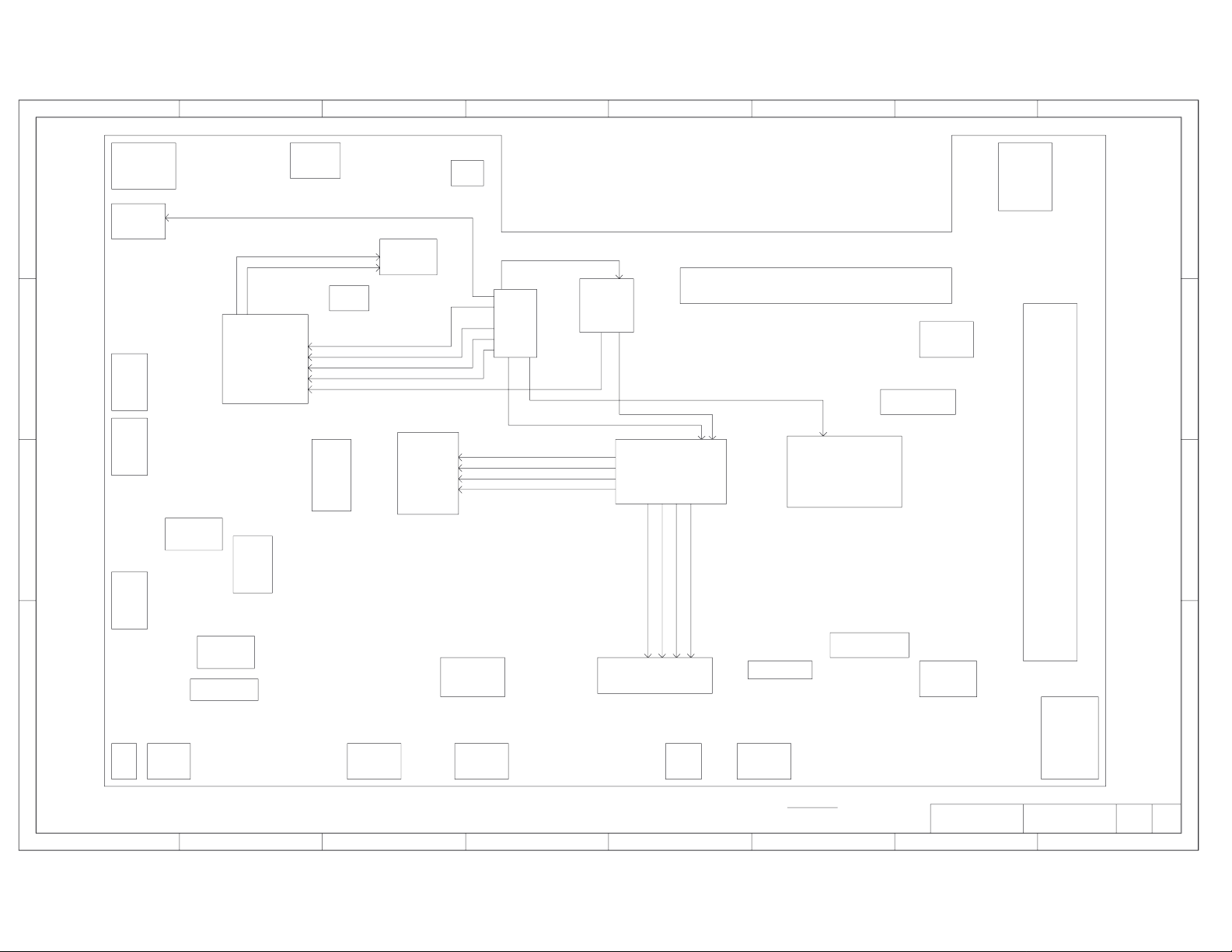

RJ45/USB

CONN

AVIP

CONN POWER

FAN

CONN

CONN

ENET

PHY

DVD

SATA

CONN

DVD

PWR

CONN

HDD

CONN

ENET_CLK(25MHZ)

1P8 VR

3P3 VR

MPORT VR

I2S_MCLK(12.288MHZ)

I2S_BCLK(3.072MHZ)

SB

FLSH

AUDIO

DAC

DEBUG

CONN

STBY_CLK(48MH Z)

SATA_CLK_REF(25MHZ)

SATA_CLK_DP/DN(100MHZ)

PCIEX_CLK_DP/DN(100MHZ)

AUD_CLK(24.576MHZ)

ANA

BCKUP

CLAM C+D

MEM

ANA_XTAL_IN(27MHZ)

ANA

BCKUP

GPU_CLK_DP/DN (100MHZ)

MC_CLK1_DP/DN(800MHZ)

MC_CLK0_DP/DN(800MHZ)

MD_CLK1_DP/DN(800MHZ)

MD_CLK0_DP/DN(800MHZ)

VMEM VR

5P0 VR

CLOCK DIAGRAM

GPU VR

ANA

CPU_CLK_DP/DN(100MHZ)

PIX_CLK_OUT_DP/DN(100MHZ)

GPU

MA_CLK0_DP/DN(800MHZ)

MA_CLK1_DP/DN(800MHZ)

MEM

CLAM A+B

MB_CLK0_DP/DN(800MHZ)

MB_CLK1_DP/DN(800MHZ)

EFUSE V R

CPU

TITAN JTAG

CONN

RISCWATCH

CONN

GPU VR

CNTL

CPU V R

CNTL

CPU

VR

EJECT

IR

SW

<PAGE_TITLE=CLOCK DIAGR AM>

MEM MEM

CONN

CONN SW

BIND

ARGON

CONN

DRAWING

XENON_FABK

MICROSOFT

CONFIDENTIAL

GAME

CONN

PROJECT NAME

XENON_RETAILWed Jul 27 21:53:30 2005

PAGE

2/73

REV

K7

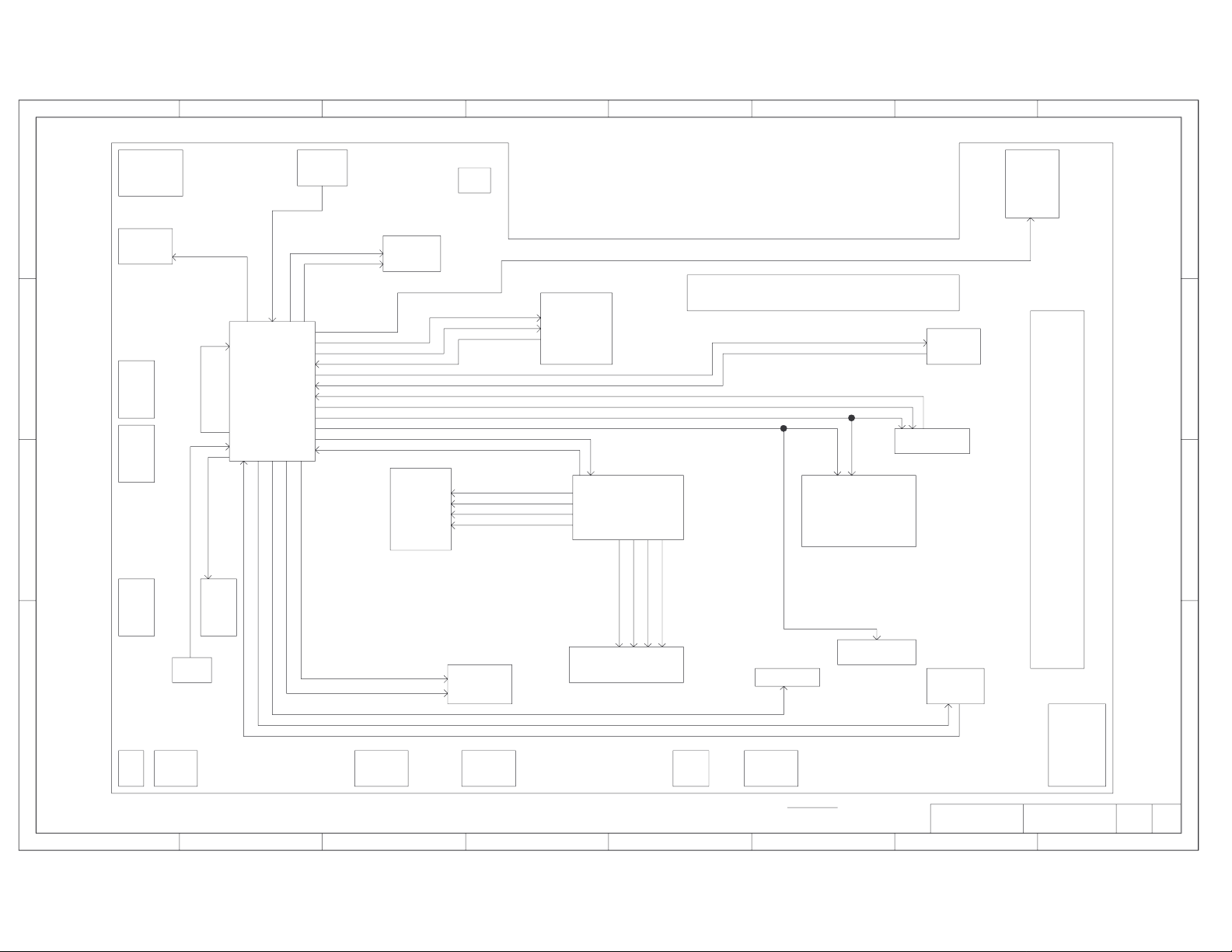

RJ45/USB

CONN

ENET

PHY

ENET_RST_N

AVIP

CONN

AUD_CLAMP

AUD_RST_N

AUDIO

DAC

FAN

CONN

RESET/ENABLE DIAGRAM

PSU_V12P0_EN

POWER

CONN

DVD

SATA

CONN

DVD

PWR

CONN

HDD

CONN

IR

DEBUG

CONN

EJECT

SW

CPU_PWRGD

EFUSE V R

GPU VR

VREG_GPU_EN_N

CPU_CHECKSTOP_N

CPU

TITAN JTAG

CONN

VREG_CPU_EN

GPU VR

CNTL

RISCWATCH

CONN

CPU V R

CNTL

CPU

VR

GAME

CONN

EXT_PWR_ON_N

SMC_RST_N

SB

VREG_GPU_PWRGD

EXT_PWR_ON_ N

SB_RST_N

GPU_RST_DONE

MEM

SMC_DBG_EN

VREG_3P3_EN

VREG_CPU_PWRGD

3P3

VR

CLAM C+D

VREG_1P8_EN_N

VREG_5P0_EN_N

MEM

ANA_CLK_OE

ANA_RST_N

GPU_RST_N

MEM_RST

MEM_SCAN_EN

MEM_SCAN_TOP_EN

MEM_SCAN_BOT_EN

VMEM VR

5P0 VR

MEM

CONN

ANA

GPU

MEM_RST

MEM_SCAN_EN

MEM

CLAM A+B

MEM_SCAN_BOT_EN

MEM_SCAN_TOP_EN

CPU_RST_N

CPU_PWRGD

VREG_EFUSE_EN

BIND

SWCONN

ARGON

CONN

[PAGE_TITLE=RESET/ENABLE DIAGRAM]

DRAWING

XENON_FABK

MICROSOFT

CONFIDENTIAL

PROJECT NAME

XENON_RETAILWed Jul 27 21:53:44 2005

PAGE

3/73

REV

K7

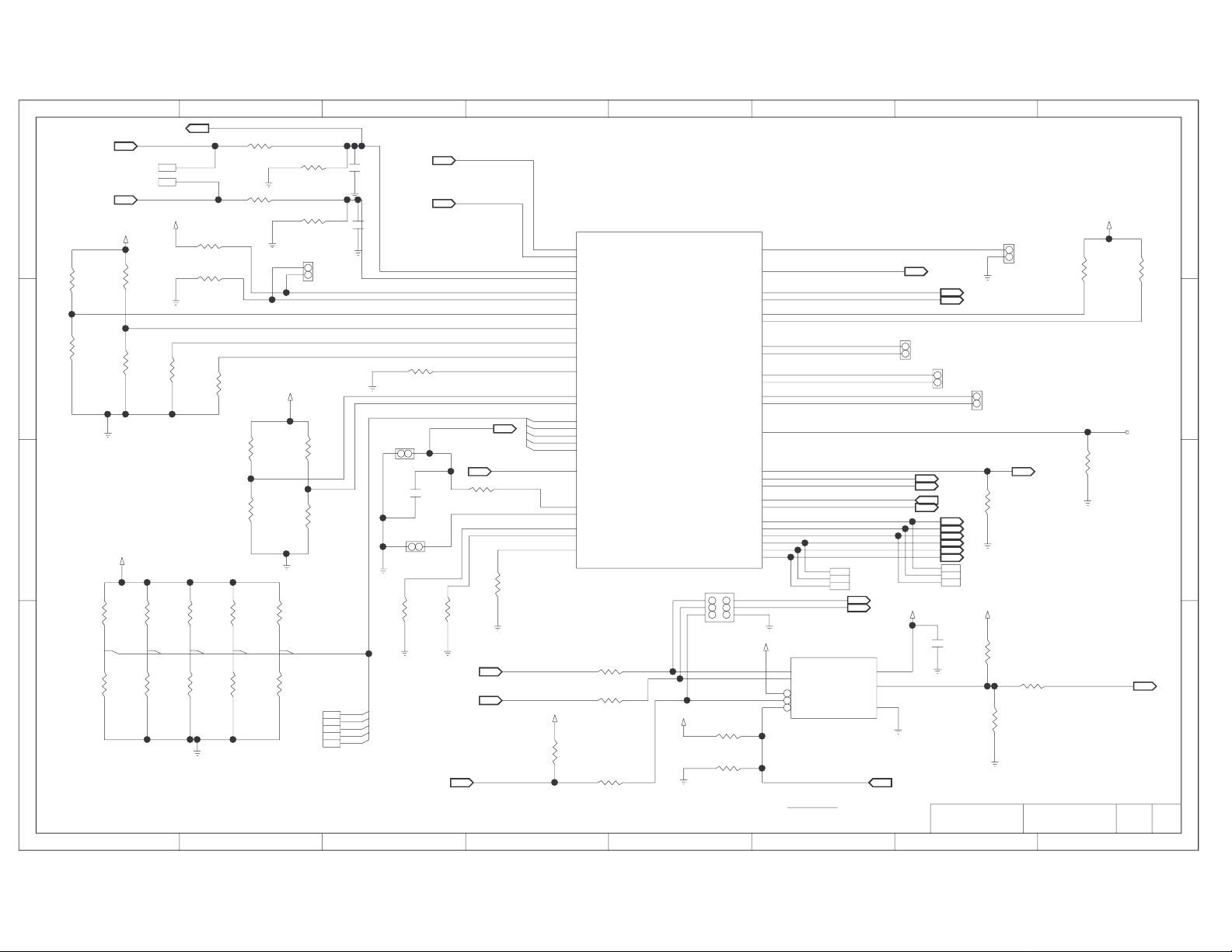

R6R4

R6R5

R7R13

10K

5%

CH

402

R7R3

10K

5%

EMPTY

402

CPU_RST_V1P1_N

1

3.92K

402

1

3.92K

402

1

5%

CH

1

5%

CH

1

R7D1

10K

5%

CH

402

2

1

R7R22

10K

5%

CH

402

2

3

1

R7R19

10K

5%

EMPTY

402

2

R7R4

R7R10

V_GPUCORE

1

R7R15

10K

5%

EMPTY

402

2

1

R7R6

10K

5%

CH

402

2

2

1%

CH

2

1%

CH

1

2

1

2

R7R16

1

6.19K

402

CPU_PWRGD_ V1P 1_N

R7R11

1

6.19K

402

TP6D1

PROBE

1

2

SMT

1

2

1

2

R7R23

10K

5%

CH

402

4

R7R18

10K

5%

EMPTY

402

FT7R4

FT7R6

FT7R2

FT7R1

FT7R5

R7R8

10K

5%

EMPTY

402

R7R7

10K

5%

CH

402

1%

CH

1%

CH

FTP

FTP

FTP

FTP

FTP

1

C7R112

2

360PF

10%

50V

2

NPO

603

1

2

2

FSB_CLK_DP

FSB_CLK_DN

1

4

1

3

1

2

1

1

1

0

C7R113

360PF

10%

50V

NPO

603

CPU_PULSE_LIMIT_BYPASS

R7R24

1

402

CPU_POS T_IN< 0.. 4>

TP6R1

PROBE

1

SMT

1

2

TP6R2

PROBE

1

SMT

1

R7R1

0

5%

EMPTY

402

2

CPU, CLOCKS + EEPROM + STRAPPING

CPU_CLK_DP

46

IN

CPU_CLK_DN

46

IN

CPU_FSB_CLK_SEL

CPU_EXT_CLK_EN

CPU_PLL_BYPASS

2

CPU_TRI GGER_I N

5%10K

CH

CPU_SYS_CONF I G0

CPU_SYS_CONF I G1

OUT

CPU_ANL_1

2

CPU_SPI_SI

4

IN

R6R10

2

1

5.11K

R7R2

0

5%

EMPTY

402

IN

CPU_A NL_1_R

1%

EMPTY402

CPU_ANL_2

CPU_SPARE0

CPU_SPARE1

CPU_TE ST_EN

1

R7R14

10K

5%

CH

402

2

4

IN

4

IN

CPU_SPI_EN

CPU_SPI_CLK

CPU_SPI_SO

C6R46

10UF

10%

6.3V

EMPTY

1206

2

1

2

4

IN

IN

FT2P11

FT2P12

CPU_RST_N

FTP

FTP

CPU_PWRGD

34

34

V_GPUCORE

V_GPUCORE

R6R9

10K

5%

CH

402

R6R8

10K

5%

EMPTY

402

1

R6R6

10K

5%

EMPTY

402

2

1

2

R6R7

10K

5%

CH

402

1

2

1

2

1

2

LAYOUT: MUST BE ACCESSIBLE

V_GPUCORE

1

1

2

1

2

R7R21

10K

5%

CH

402

0

R7R20

10K

5%

EMPTY

402

R7R12

10K

5%

CH

402

2

1

1

R7R5

10K

5%

EMPTY

402

2

56

R7R17

10K

5%

CH

402

OUT

1

1

2

1K

402

2

1K

402

1

2

2

1

2

[PAGE_TITLE=CPU, CLOCKS + EEPROM + STRAPPING]

0

1

2

3

4

V_MEM

AH25

AF16

AK23

AK22

AG18

AF18

AH16

AJ16

AG16

AH10

AJ10

AK10

AK11

AG24

AF24

1

2

AJ2

AK3

AH1

AK9

AK1

AJ1

AH4

B3

R7U3

10K

5%

CH

402

N: STUFF C?,C? WITH ZERO OHM R'S FOR WN

N: STUFF C?,C? WITH .01UF CAPS FOR SHIVA

U7D1

CORE_CLK_DP

CORE_CLK_DN

HARD_RESET_B

POWER_GOOD

FSB_CLK_DP

FSB_CLK_DN

FSB_CLK_SEL

EXT_CLK_EN

PLL_BYPASS

PULSE_LIMIT_BYPASS

TRIGGER_IN

SYS_CONFIG0

SYS_CONFIG1

POST_IN0

POST_IN1

POST_IN2

POST_IN3

POST_IN4

SPI_SI

ANL_1

ANL_2

SPARE0

SPARE1

TE

X02046-002

1OF10

CPU VERSION 20

FSB_HF_CLKOUT_DP

FSB_HF_CLKOUT_DN

FSB_IMPED_CAL_DP

FSB_IMPED_CAL_DN

CORE_IF_BGR_PLL

EFU_POWERON

RESISTOR0_DP

RESISTOR0_DN

VDDS0_DP

VDDS0_DN

VDDS1_DP

VDDS1_DN

PSRO0_OUT

SPI_CLK

SPI_EN

SPI_SO

TEMP_ P

TEMP_ N

J7F1

2X3HDR

1

3

VID0

VID1

VID2

VID3

VID4

VID5

EMPTY

R6E2

1K

402

R7E7

1K

402

R7F2

1K 5%

402

5%

CH

5%

CH

CH

V_MEM

CPU_S P I_CLK_R

CPU_SP I_SO _R

CPU_SP I_EN_ R

2

10K

402

2

10K

402

R7E8

R7F1

5%

CH

5%

EMPTY

IC

CPU_CORE_IF_BGR_PLL

AK17AJ25

VREG_EFUSE_EN

C6

CPU_FSB_HF_CLKOUT_DP

AH22

CPU_FSB_HF_CLKOUT_DN

AJ22

CPU_FSB_IMPED_CAL_DP

AK25

CPU_FSB_IMPED_CAL_DN

AK24

CPU_RES0_DP

AK14

CPU_RES0_DN

AK15

CPU_VDDS0_DP

AH13

CPU_VDDS0_DN

AK12

CPU_VDDS1_DP

AJ4

CPU_VDDS1_DN

AK5

CPU_PSRO0_OUT

AK16

CPU_SPI_CLK

A2

CPU_SPI_EN

B2

CPU_SPI_SO

A3

CPU_TEMP_P

AK20

CPU_TEMP_N

AK21

CPU_VREG_APS0

C4

CPU_VREG_APS1

B5

CPU_VREG_APS2

A4

CPU_VREG_APS3

B4

CPU_VREG_APS4

A5

CPU_VREG_APS5

C5

CPU_SPI_SI

2

CPU_SPI_WP_N

4

65

V_MEM

U7E1

AT25020A

6

SCK

5

SDI

7

HOLD_N*

1

CS_N*

3

WP_N*

X800552-001

1

1

CPU_SPI_WP_N

DRAWING

XENON_FABK

Wed Aug 24 09:27:00 2005

V_GPUCORE

TP7R1

PROBE

1

2

1

2

TP7R2

PROBE

SMT

49

49

49

49

49

49

FT7T5

FT7T4

FT7T3

2

1

V_MEM

1

2

R6E1

10K

5%

CH

402

R7F3

10K

5%

EMPTY

402

1

2

SMT

R7F4

100

5%

CH

402

OUT

R7F7

2

1K

402

PROJECT NAME

XENON_RETAIL

55

OUT

OUT

OUT

TP7R3

PROBE

1

2

TP7R4

SMT

PROBE

1

2

SMT

4

OUT

4

OUT

29

IN

29

OUT

OUT

OUT

OUT

OUT

OUT

OUT

V_MEM

8

CPU_SPI_SI_R

2

4

4

1

FTP

1

FTP

1

FTP

1

C6F1

.1UF

10%

6.3V

2

X5R

402

1

FTP

FT7T2

1

FTP

FT7T1

1

FT7T7

FTP

4

OUT

4

OUT

IC

VCC

SDO

GND

IN

MICROSOFT

CONFIDENTIAL

4

5%

CH

1

2

R6D1

931

1%

CH

402

1

1

R7R9

10K

5%

CH

402

2

CPU_SPI_SI

1

R6D2

1.07K

1%

CH

402

2

DB7R1

TP

1

4

OUT

PAGE

REV

K7

4/73

CPU, FSB

U7D1

FSB_GP_CP0_CLK_DP

12

IN

FSB_GP_CP0_CLK_DN

12

IN

FSB_GP_CP0_FLAG_DP

12

IN

FSB_GP_CP0_FLAG_DN

12

IN

FSB_GP_CP0_DATA0_DP

12

IN

FSB_GP_CP0_DATA0_DN

12

IN

FSB_GP_CP0_DATA1_DP

12

IN

FSB_GP_CP0_DATA1_DN FSB_CP_GP0_DATA1_DN

12 12

IN

FSB_GP_CP0_DATA2_DP

12

IN

FSB_GP_CP0_DATA2_DN FSB_CP_GP0_DATA2_DN

12 12

IN

FSB_GP_CP0_DATA3_DP

12

IN

FSB_GP_CP0_DATA3_DN

12

IN

FSB_GP_CP0_DATA4_DP

12

IN

FSB_GP_CP0_DATA4_DN

12

IN

FSB_GP_CP0_DATA5_DP

12

IN

FSB_GP_CP0_DATA5_DN

12

IN

FSB_GP_CP0_DATA6_DP

12

IN

FSB_GP_CP0_DATA6_DN

12

IN

FSB_GP_CP0_DATA7_DP

12

IN

FSB_GP_CP0_DATA7_DN

12

IN

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

FSB_GP_CP1_CLK_DP

IN

FSB_GP_CP1_CLK_DN

IN

FSB_GP_CP1_FLAG_DP

12

IN

FSB_GP_CP1_FLAG_DN

12

IN

FSB_GP_CP1_DATA0_DP

IN

FSB_GP_CP1_DATA0_DN

IN

FSB_GP_CP1_DATA1_DP

IN

FSB_GP_CP1_DATA1_DN

IN

FSB_GP_CP1_DATA2_DP FSB_CP_GP1_DATA2_DP

IN

FSB_GP_CP1_DATA2_DN

IN

FSB_GP_CP1_DATA3_DP

IN

FSB_GP_CP1_DATA3_DN

IN

FSB_GP_CP1_DATA4_DP

IN

FSB_GP_CP1_DATA4_DN

IN

FSB_GP_CP1_DATA5_DP

IN

FSB_GP_CP1_DATA5_DN

IN

FSB_GP_CP1_DATA6_DP

IN

FSB_GP_CP1_DATA6_DN

IN

FSB_GP_CP1_DATA7_DP

IN

FSB_GP_CP1_DATA7_DN

IN

AD29

AD30

AA29

AA30

AB28

AB27

AB30

AB29

AC29

AC30

Y30

Y29

V28

V27

V30

V29

W29

W30

Y28

Y27

G30

G29

L28

L27

E28

E27

E30

E29

F29

F30

G28

G27

H29

H30

J28

J27

J30

J29

K29

K30

GP_CP0_CLK_DP

GP_CP0_CLK_DN

GP_CP0_FLAG_DP

GP_CP0_FLAG_DN

GP_CP0_DATA0_DP

GP_CP0_DATA0_DN

GP_CP0_DATA1_DP

GP_CP0_DATA1_DN

GP_CP0_DATA2_DP

GP_CP0_DATA2_DN

GP_CP0_DATA3_DP

GP_CP0_DATA3_DN

GP_CP0_DATA4_DP

GP_CP0_DATA4_DN

GP_CP0_DATA5_DP

GP_CP0_DATA5_DN

GP_CP0_DATA6_DP

GP_CP0_DATA6_DN

GP_CP0_DATA7_DP

GP_CP0_DATA7_DN

GP_CP1_CLK_DP

GP_CP1_CLK_DN

GP_CP1_FLAG_DP

GP_CP1_FLAG_DN

GP_CP1_DATA0_DP

GP_CP1_DATA0_DN

GP_CP1_DATA1_DP

GP_CP1_DATA1_DN

GP_CP1_DATA2_DP

GP_CP1_DATA2_DN

GP_CP1_DATA3_DP

GP_CP1_DATA3_DN

GP_CP1_DATA4_DP

GP_CP1_DATA4_DN

GP_CP1_DATA5_DP

GP_CP1_DATA5_DN

GP_CP1_DATA6_DP

GP_CP1_DATA6_DN

GP_CP1_DATA7_DP

GP_CP1_DATA7_DN

X02046-002

2OF10

CPU VERSION 20

CP_GP0_DATA0_DP

CP_GP0_DATA0_DN

CP_GP0_DATA1_DP

CP_GP0_DATA1_DN

CP_GP0_DATA2_DP

CP_GP0_DATA2_DN

CP_GP0_DATA3_DP

CP_GP0_DATA3_DN

CP_GP0_DATA4_DP

CP_GP0_DATA4_DN

CP_GP0_DATA5_DP

CP_GP0_DATA5_DN

CP_GP0_DATA6_DP

CP_GP0_DATA6_DN

CP_GP0_DATA7_DP

CP_GP0_DATA7_DN

CP_GP1_DATA0_DP

CP_GP1_DATA0_DN

CP_GP1_DATA1_DP

CP_GP1_DATA1_DN

CP_GP1_DATA2_DP

CP_GP1_DATA2_DN

CP_GP1_DATA3_DP

CP_GP1_DATA3_DN

CP_GP1_DATA4_DP

CP_GP1_DATA4_DN

CP_GP1_DATA5_DP

CP_GP1_DATA5_DN

CP_GP1_DATA6_DP

CP_GP1_DATA6_DN

CP_GP1_DATA7_DP

CP_GP1_DATA7_DN

CP_GP0_CLK_DP

CP_GP0_CLK_DN

CP_GP0_FLAG_DP

CP_GP0_FLAG_DN

CP_GP1_CLK_DP

CP_GP1_CLK_DN

CP_GP1_FLAG_DP

CP_GP1_FLAG_DN

IC

FSB_CP_GP0_CLK_DP

AG29

FSB_CP_GP0_CLK_DN

AG30

FSB_CP_GP0_FLAG_DP

AK27

FSB_CP_GP0_FLAG_DN

AK28

FSB_CP_GP0_DATA0_DP

AD28

FSB_CP_GP0_DATA0_DN

AD27

FSB_CP_GP0_DATA1_DP

AE29

AE30

FSB_CP_GP0_DATA2_DP

AF30

AF29

FSB_CP_GP0_DATA3_DP

AF27

FSB_CP_GP0_DATA3_DN

AF28

FSB_CP_GP0_DATA4_DP

AH30

FSB_CP_GP0_DATA4_DN

AH29

FSB_CP_GP0_DATA5_DP

AH27

FSB_CP_GP0_DATA5_DN

AH28

FSB_CP_GP0_DATA6_DP

AJ29

FSB_CP_GP0_DATA6_DN

AJ30

FSB_CP_GP0_DATA7_DP

AK30

FSB_CP_GP0_DATA7_DN

AK29

FSB_CP_GP1_CLK_DP

P30

FSB_CP_GP1_CLK_DN

P29

FSB_CP_GP1_FLAG_DP

U30

FSB_CP_GP1_FLAG_DN

U29

FSB_CP_GP1_DATA0_DP

L30

FSB_CP_GP1_DATA0_DN

L29

FSB_CP_GP1_DATA1_DP

M30

FSB_CP_GP1_DATA1_DN

M29

N27

FSB_CP_GP1_DATA2_DN

N28

FSB_CP_GP1_DATA3_DP

N30

FSB_CP_GP1_DATA3_DN

N29

FSB_CP_GP1_DATA4_DP

R27

FSB_CP_GP1_DATA4_DN

R28

FSB_CP_GP1_DATA5_DP

R30

FSB_CP_GP1_DATA5_DN

R29

FSB_CP_GP1_DATA6_DP

T30

FSB_CP_GP1_DATA6_DN

T29

FSB_CP_GP1_DATA7_DP

U27

FSB_CP_GP1_DATA7_DN

U28

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

V_GPUCORE

1

C6T33

.1UF

10%

6.3V

X5R

402

1

C6T32

.1UF

10%

6.3V

2

X5R

402

C6R6

.1UF

10%

6.3V

2

X5R

402

1

1

2

C6R14

.1UF

10%

6.3V

X5R

402

1

1

C6R25

.1UF

10%

6.3V

2

X5R

402

1

C6R37

C6T19

.1UF

.1UF

10%

10%

6.3V

6.3V

2

2

X5R

X5R

402

402

1

1

2

C6T7

.1UF

10%

6.3V

X5R

402

C6T27

.1UF

10%

6.3V

2

2

X5R

402

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

[PAGE_TITLE=CPU, FSB]

DRAWING

XENON_FABK

Wed Aug 24 09:27:01 2005

MICROSOFT

CONFIDENTIAL

PROJECT NAME

XENON_RETAIL

PAGE

5/73

REV

K7

V_CPUPLL

CPU, FSB POWER + PLL POWER

V_1P8

IC

V_GPUCORE

AA27

AB26

AC27

AD26

AE27

AF26

AG27

AH26

AJ27

AK26

B9

B12

B15

B18

B21

B24

B27

C8

C11

C14

C17

C20

C23

C26

D10

D13

D17

D21

D25

D27

D29

E26

F27

G26

H27

J26

K27

L26

M27

N26

P27

R26

T27

U26

V26

W27

Y26

AJ19

AH19

AK19

AK18

AF22

AG22

AF20

AG20

AK13

AJ13

AK6

A6

B6

U7D1

VDD_IO

VDDE

VDDE_SEC

CORE_HF_VDDA_PLL

CORE_HF_GNDA_PLL

CORE_IF_VDDA_PLL

CORE_IF_GNDA_PLL

FSB_HF_VDDA_PLL

FSB_HF_GNDA_PLL

FSB_IF_VDDA_PLL

FSB_IF_GNDA_PLL

VDDA_RNG

GNDA_RNG

X02046-002

FB7R1

2

1

1K

0.2AFB603

C7R1

.1UF

10%

6.3V

X5R

402

C6D1

.1UF

10%

6.3V

X5R

402

C6R2

.1UF

10%

6.3V

X5R

402

C6R3

.1UF

10%

6.3V

X5R

402

C7D1

1UF

10%

50V

EMPTY

603

0.7DCR

0.7DCR

0.7DCR

0.7DCR

0.7DCR

1

C7R7

2.2UF

10%

6.3V

2

X5R

ST7R1

1

SHORT

FB6D1

1

1K

0.2A

ST6D1

1

SHORT

FB6R1

1

1K

0.2A

ST6R1

1

SHORT

FB6R2

1

1K

0.2A

ST6R2

1

SHORT

FB7D1

1

1K

0.2A

ST7D1

1

SHORT

603

2

2

FB

603

1

C6D4

2.2UF

10%

6.3V

2

X5R

603

2

2

FB

603

1

C6R4

2.2UF

10%

6.3V

2

X5R

603

2

2

FB

603

1

C6R5

2.2UF

10%

6.3V

2

X5R

603

2

2

FB

603

1

C7D2

2.2UF

10%

6.3V

2

X5R

603

2

1

2

1

2

1

2

1

2

1

2

1

2

C7R115

.1UF

10%

6.3V

X5R

402

V_EFUSE

1

2

C7R116

.1UF

10%

6.3V

X5R

402

1

C7R114

.1UF

10%

6.3V

2

X5R

402

R7T2

2

1

5%

10K

CH

402

V_CPU_ CORE_HF _VDDA_ PLL

V_CPU_ CORE_HF _GNDA_ PLL

V_CPU_ CORE_I F_VDDA _PL L

V_CPU_ CORE_I F_GNDA _PL L

V_CPU_ FSB_ HF_VDDA _PL L

V_CPU_ FSB_ HF_GNDA _PL L

V_CPU_ FSB_ IF_ VDDA_P LL

V_CPU_ FSB_ IF_ GNDA_PL L

V_CPU_ VDDA_ RNG

V_CPU_ GNDA_RNG

CPU_VDDE

4of 10

CPU VERSION 20

VDD_FSB0

VDD_FSB1

VDD_FSB2

VDD_FSB3

VDD_FSB4

VDD_FSB5

VDD_FSB6

VDD_FSB7

VDD_FSB8

VDD_FSB9

VDD_FSB10

VDD_FSB11

VDD_FSB12

VDD_FSB13

VDD_FSB14

VDD_FSB15

VDD_FSB16

VDD_FSB17

VDD_FSB18

VDD_FSB19

VDD_FSB20

VDD_FSB21

VDD_FSB22

VDD_FSB23

VDD_FSB24

VDD_FSB25

VDD_FSB26

VDD_FSB27

VDD_FSB28

VDD_FSB29

VDD_FSB30

VDD_FSB31

VDD_FSB32

VDD_FSB33

VDD_FSB34

VDD_FSB35

VDD_FSB36

VDD_FSB37

VDD_FSB38

VDD_FSB39

VDD_FSB40

VDD_FSB41

VDD_FSB42

VDD_FSB43

VDD_FSB44

VDD_FSB45

VDD_FSB46

[PAGE_TITLE=CPU, FSB POWER + PLL POWER]

DRAWING

XENON_FABK

MICROSOFT

CONFIDENTIAL

PROJECT NAME

XENON_RETAILWed Aug 24 09:27:01 2005

PAGE

6/73

REV

K7

CPU, CORE POWER

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA24

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB25

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC24

AD11

AD13

AD15

AD17

AD19

AD21

AA2

AA4

AA6

AA8

AB1

AB3

AB5

AB7

AB9

AC2

AC4

AC6

AC8

AD1

AD3

AD5

AD7

AD9

U7D1

5of 10

CPU VERSION 20

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

X02046-002

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDD93

VDD94

VDD95

IC

AD23

AD25

AE2

AE4

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE22

AE24

AF1

AF3

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF23

AF25

AG2

AG4

AG6

AG8

AG10

AG12

AG14

AH3

AH6

AH9

AH12

AH15

AJ5

AJ8

AJ11

AJ14

B1

C2

D1

D3

D5

D7

D9

E2

E4

E6

E8

E10

F1

F3

F5

F7

F9

F11

G2

G4

G6

G8

G10

G12

G14

G16

G18

G20

G22

G24

H1

H3

H5

H7

H9

H11

H13

H15

H17

H19

H21

H23

H25

J2

J4

J6

J8

J10

J12

J14

J16

J18

U7D1

6of 10

CPU VERSION 20

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD134

VDD135

VDD136

VDD137

VDD138

VDD139

VDD140

VDD141

VDD142

X02046-002

VDD143

VDD144

VDD145

VDD146

VDD147

VDD148

VDD149

VDD150

VDD151

VDD152

VDD153

VDD154

VDD155

VDD156

VDD157

VDD158

VDD159

VDD160

VDD161

VDD162

VDD163

VDD164

VDD165

VDD166

VDD167

VDD168

VDD169

VDD170

VDD171

VDD172

VDD173

VDD174

VDD175

VDD176

VDD177

VDD178

VDD179

VDD180

VDD181

VDD182

VDD183

VDD184

VDD185

VDD186

VDD187

VDD188

VDD189

V_CPUCOREV_CPUCOREV_CPUCORE V_CPUCORE V_CPUCOREV_CPUCORE

IC

J20

J22

J24

K1

K3

K5

K7

K9

K11

K13

K15

K17

K19

K21

K23

K25

L2

L4

L6

L8

L10

L12

L14

L16

L18

L20

L22

L24

M1

M3

M5

M7

M9

M11

M13

M15

M17

M19

M21

M23

M25

N2

N4

N6

N8

N10

N12

N14

N16

N18

N20

N22

N24

P1

P3

P5

P7

P9

P11

P13

P15

P17

P19

P21

P23

P25

R2

R4

R6

R8

R10

R12

R14

R16

R18

R20

R22

R24

T1

T3

T5

T7

T9

T11

T13

T15

T17

T19

T21

T23

T25

U2

U4

U6

U7D1

7of 10

CPU VERSION 20

VDD190

VDD191

VDD192

VDD193

VDD194

VDD195

VDD196

VDD197

VDD198

VDD199

VDD200

VDD201

VDD202

VDD203

VDD204

VDD205

VDD206

VDD207

VDD208

VDD209

VDD210

VDD211

VDD212

VDD213

VDD214

VDD215

VDD216

VDD217

VDD218

VDD219

VDD220

VDD221

VDD222

VDD223

VDD224

VDD225

VDD226

VDD227

VDD228

VDD229

VDD230

VDD231

VDD232

VDD233

VDD234

VDD235

VDD236

X02046-002

VDD237

VDD238

VDD239

VDD240

VDD241

VDD242

VDD243

VDD244

VDD245

VDD246

VDD247

VDD248

VDD249

VDD250

VDD251

VDD252

VDD253

VDD254

VDD255

VDD256

VDD257

VDD258

VDD259

VDD260

VDD261

VDD262

VDD263

VDD264

VDD265

VDD266

VDD267

VDD268

VDD269

VDD270

VDD271

VDD272

VDD273

VDD274

VDD275

VDD276

VDD277

VDD278

VDD279

VDD280

VDD281

VDD282

VDD283

IC

U8

U10

U12

U14

U16

U18

U20

U22

U24

V1

V3

V5

V7

V9

V11

V13

V15

V17

V19

V21

V23

V25

W2

W4

W6

W8

W10

W12

W14

W16

W18

W20

W22

W24

Y1

Y3

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

Y21

Y23

Y25

[PAGE_TITLE=CPU, CORE POWER]

DRAWING

XENON_FABK

MICROSOFT

CONFIDENTIAL

PROJECT NAME

XENON_RETAILWed Aug 24 09:27:01 2005

PAGE

7/73

REV

K7

CPU, POWER

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AA25

AA26

AA28

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AB24

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AC25

AC26

AC28

AD10

AD12

AD14

AD16

AD18

AD20

AD22

AD24

AA1

AA3

AA5

AA7

AA9

AB2

AB4

AB6

AB8

AC1

AC3

AC5

AC7

AC9

AD2

AD4

AD6

AD8

AE1

AE3

AE5

AE7

U7D1

8of 10

CPU VERSION 20

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

X02046-002

VSS58VSS0

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

B14

B17

B20

B23

B26

B29

C1

C3

C9

C12

C15

C18

C21

C24

C27

D2

D4

D6

D8

D11

D15

D19

D23

D26

D28

D30

E1

E3

E5

E7

E9

F2

F4

F6

F8

F10

F12

F14

F16

F18

F20

F22

F24

F26

F28

G1

G3

G5

G7

G9

G11

G13

G15

G17

G19

G21

G23

G25

U7D1

9of 10

CPU VERSION 20

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

X02046-002

IC

AE9

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AE25

AE26

AE28

AF2

AF4

AF6

AF8

AF10

AF12

AF14

AG1

AG3

AG5

AG7

AG9

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AG25

AG26

AG28

AH2

AH5

AH8

AH11

AH14

AH17

AH18

AH20

AH21

AH23

AH24

AJ3

AJ6

AJ9

AJ12

AJ15

AJ17

AJ18

AJ20

AJ21

AJ23

AJ24

AJ26

AJ28

B8

B11

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

IC

H2

H4

H6

H8

H10

H12

H14

H16

H18

H20

H22

H24

H26

H28

J1

J3

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

J25

K2

K4

K6

K8

K10

K12

K14

K16

K18

K20

K22

K24

K26

K28

L1

L3

L5

L7

L9

L11

L13

L15

L17

L19

L21

L23

L25

M2

M4

M6

M8

M10

M12

M14

M16

M18

M20

M22

M24

M26

M28

N1

N3

N5

N7

N9

N11

N13

N15

N17

N19

N21

N23

N25

P2

P4

P6

P8

P10

P12

P14

P16

P18

P20

P22

P24

P26

P28

R1

R3

R5

R7

R9

R11

R13

R15

R17

R19

R21

R23

R25

T2

T4

T6

T8

T10

T12

T14

T16

U7D1

10 of 10

CPU VERSION 20

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS290

X02046-002

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS301

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS314

VSS315

VSS316

VSS317

VSS318

VSS319

VSS320

VSS321

VSS322

VSS323

VSS324

VSS325

VSS326

VSS327

VSS328

VSS329

VSS330

VSS331

VSS332

VSS333

VSS334

VSS335

VSS336

VSS337

VSS338

VSS339

VSS340

VSS341

VSS342

VSS343

VSS344

VSS345

VSS346

VSS347

VSS348

IC

T18

T20

T22

T24

T26

T28

U1

U3

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

U25

V2

V4

V6

V8

V10

V12

V14

V16

V18

V20

V22

V24

W1

W3

W5

W7

W9

W11

W13

W15

W17

W19

W21

W23

W25

W26

W28

Y2

Y4

Y6

Y8

Y10

Y12

Y14

Y16

Y18

Y20

Y22

Y24

[PAGE_TITLE=CPU, POWER]

DRAWING

XENON_FABK

MICROSOFT

CONFIDENTIAL

PROJECT NAME

XENON_RETAILWed Aug 24 09:27:02 2005

PAGE

8/73

REV

K7

V_CPUCORE

V_CPUCORE

CPU, DECOUPLING

C7D21

1

6.3V

X5R

805

C7T94

1

6.3V

X5R

805

C7T101

1

6.3V

X5R

805

C7T87

1

6.3V

X5R

805

C7R2

1

6.3V

X5R

805

C7E3

1

6.3V

X5R

805

C7T32

1

6.3V

X5R

805

C7R28

1

6.3V

X5R

805

C7D20

1

6.3V

X5R

805

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

C7R122

1

6.3V

X5R

805

C7E8

1

6.3V

X5R

805

C7E14

1

6.3V

X5R

805

C7T93

1

6.3V

X5R

805

C7D16

1

6.3V

X5R

805

C7E12

1

6.3V

X5R

805

C7E10

1

6.3V

X5R

805

C7E11

1

6.3V

X5R

805

C7T33

1

6.3V

X5R

805

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

C7T85

1

6.3V

X5R

805

C7E6

1

6.3V

X5R

805

C7D12

1

6.3V

X5R

805

C7D19

1

6.3V

X5R

805

C7T36

1

6.3V

X5R

805

C7R118

1

6.3V

X5R

805

C7E5

1

6.3V

X5R

805

C7D14

1

6.3V

X5R

805

C7R121

1

6.3V

X5R

805

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

C7R6

1

6.3V

X5R

805

C7R94

1

6.3V

X5R

805

C7E1

1

6.3V

X5R

805

C7R119

1

6.3V

X5R

805

C7E7

1

6.3V

X5R

805

C7D13

1

6.3V

X5R

805

C7T83

1

6.3V

X5R

805

C7D11

1

6.3V

X5R

805

C7T84

1

6.3V

X5R

805

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

C7D9

1

6.3V

C7R5

1

6.3V

C7T34

1

6.3V

C7R26

1

6.3V

C7R117

1

6.3V

C7T96

1

6.3V

C7R92

1

6.3V

C7D6

1

6.3V

C7D17

1

6.3V

2

10%4.7UF

X5R

805

2

10%4.7UF

X5R

805

2

10%4.7UF

X5R

805

2

10%4.7UF

X5R

805

2

10%4.7UF

X5R

805

2

10%4.7UF

X5R

805

2

10%4.7UF

X5R

805

2

10%4.7UF

X5R

805

2

10%4.7UF

X5R

805

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

C7R27

1

1

1

C7D18

1

1

C7E16

1

C7R91

1

C7R29

1

1

6.3V

X5R

805

C7D8

6.3V

X5R

805

C7D4

6.3V

X5R

805

6.3V

X5R

805

C7D7

6.3V

X5R

805

6.3V

X5R

805

6.3V

X5R

805

6.3V

X5R

805

C7E4

6.3V

X5R

805

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

4.7UF

C7D10

1

6.3V

X5R

805

C7R4

1

6.3V

X5R

805

C7T35

1

6.3V

X5R

805

C7D5

1

6.3V

X5R

805

C7R93

1

6.3V

X5R

805

C7T95

1

6.3V

X5R

805

C7D3

1

6.3V

X5R

805

C7R120

1

6.3V

X5R

805

C7D15

1

6.3V

X5R

805

10%

10%

10%

10%

10%

10%

10%

10%

10%

2

2

2

2

2

2

2

2

2

1

C7R30

1

C7R90

1

1

C7E15

1

1

C7T86

1

C7T97

1

C7D22

1

C7R3

6.3V

X5R

805

6.3V

X5R

805

6.3V

X5R

805

C7E2

6.3V

X5R

805

6.3V

X5R

805

C7E9

6.3V

X5R

805

6.3V

X5R

805

6.3V

X5R

805

6.3V

X5R

805

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

2

10%4.7UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

C7T79

1

C7T78

1

C7T77

1

C7T76

1

C7T88

1

C7R12

1

C7R10

1

C7R11

1

C7R13

1

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

.1UF

.1UF

.1UF

1

C7T45

1

C7R16

1

C7T1

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

2

10%

2

10%

2

10%

[PAGE_TITLE=CPU, DECOUPLING]

DRAWING

XENON_FABK

MICROSOFT

CONFIDENTIAL

PROJECT NAME

XENON_RETAILWed Aug 24 09:27:03 2005

PAGE

9/73

REV

K7

V_CPUCORE

CPU, DECOUPLING

C7R36

1

.1UF 10%

6.3V

X5R

402

C7R22

1

.1UF 10%

6.3V

X5R

402

C7R23

1

.1UF 10%

6.3V

X5R

402

C7R24

1

6.3V

X5R

402

C7R25

1

.1UF 10%

6.3V

X5R

402

C7R38

1

.1UF

6.3V

X5R

402

C7R37

1

.1UF

6.3V

X5R

402

C7R44

1

.1UF 10%

6.3V

X5R

402

C6R11

1

.1UF 10%

6.3V

X5R

402

C7R46

1

.1UF

6.3V

X5R

402

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

1

1

1

1

1

1

1

1

1

1

C7T20

6.3V

X5R

402

C7T22

6.3V

X5R

402

C7T27

6.3V

X5R

402

C7R48

6.3V

X5R

402

C6T4

6.3V

X5R

402

C7T37

6.3V

X5R

402

C7R89

6.3V

X5R

402

C6T25

6.3V

X5R

402

C7R99

6.3V

X5R

402

C6T23

6.3V

X5R

402

10%

10%

10%

10%

10%

10%

10%

10%

10%

10%

2

2

2

2

2

2

2

2

2

2

C6R44

1

.1UF

6.3V

C6T2

1

.1UF

6.3V

C6T1

1

.1UF

6.3V

C6R43

1

.1UF

6.3V

C7R102

1

.1UF

6.3V

C7R81

1

.1UF

6.3V

C6R36

1

.1UF

6.3V

C7T81

1

.1UF

6.3V

C7R100

1

.1UF

6.3V

C7R74

1

.1UF

6.3V

2

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

C6T10

1

.1UF 10%

6.3V

X5R

402

C7T19

1

10%

.1UF

6.3V

X5R

402

C7R66

1

10%

.1UF

6.3V

X5R

402

C7R111

1

.1UF 10%

6.3V

X5R

402

C7R110

1

10%

.1UF

6.3V

X5R

402

C7T2

1

.1UF 10%

6.3V

X5R

402

C6R35

1

10%

.1UF

6.3V

X5R

402

C7T10

1

.1UF

10%

6.3V

X5R

402

C6R39

1

.1UF 10%

6.3V

X5R

402

C6R18

1

.1UF 10%

6.3V

X5R

402

2

2

2

2

2

2

2

2

2

2

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

C7T21

1

C7T71

1

C6R42

1

C7R67

1

1

1

C7T82

1

C6R40

1

C6R38

1

C6R34

1

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

C7T3

6.3V

X5R

402

C7T5

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

2

2

2

10%.1UF

2

2

10%

2

10%

2

2

2

10%

C7R62

2

1

10% 10%

.1UF

6.3V

X5R

402

C7R78

2

1

10%

.1UF

6.3V

X5R

402

C7R70

2

1

.1UF

10%

6.3V

X5R

402

C7R53

2

1

10%

.1UF

6.3V

X5R

402

C7R47

2

1

10%

.1UF

6.3V

X5R

402

C7R63

2

1

.1UF

10%

6.3V

X5R

402

C7R79

2

1

10%

.1UF

6.3V

X5R

402

C7R77

2

1

.1UF

10%

6.3V

X5R

402

C6R17

2

1

10%

.1UF

6.3V

X5R

402

C7R45

2

1

10%

.1UF

6.3V

X5R

402

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

C7R49

1

C7R72

1

C6R29

1

C6R28

1

C6R27

1

C7R76

1

C7T15

1

C7R64

1

C7R71

1

C7R84

1

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

C7T9

1

.1UF 10%

6.3V

X5R

402

C7R55

1

.1UF 10%

6.3V

X5R

402

C7R35

1

.1UF

6.3V

X5R

402

C7R34

1

.1UF 10%

6.3V

X5R

402

C7R19

1

.1UF 10%

6.3V

X5R

402

C7R43

1

.1UF 10%

6.3V

X5R

402

C6R16

1

.1UF

6.3V

X5R

402

C6R19

1

.1UF 10%

6.3V

X5R

402

C7R61

1

.1UF 10%

6.3V

X5R

402

C7R54

1

.1UF

6.3V

X5R

402

2

2

2

10%

2

2

2

2

10%

2

2

2

10%

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

1

1

1

1

1

1

1

1

1

1

C7R80

6.3V

X5R

402

C6R32

6.3V

X5R

402

C6R31

6.3V

X5R

402

C6T5

6.3V

X5R

402

C7R68

6.3V

X5R

402

C7R69

6.3V

X5R

402

C7R57

6.3V

X5R

402

C6R20

6.3V

X5R

402

C6R21

6.3V

X5R

402

C6T26

6.3V

X5R

402

10%

10%

10%

10%

10%

10%

10%

10%

10%

10%

2

2

2

2

2

2

2

2

2

2

C7R52

1

.1UF

10%

6.3V

X5R

402

C7R51

1

.1UF 10%

6.3V

X5R

402

C7R50

1

.1UF 10%

6.3V

X5R

402

C6T6

1

10%.1UF

6.3V

X5R

402

C6R22

1

.1UF

10%

6.3V

X5R

402

C6R23

1

.1UF 10%

6.3V

X5R

402

C7R58

1

.1UF

10%

6.3V

X5R

402

C7R59

1

.1UF 10%

6.3V

X5R

402

C7R60

1

.1UF 10%

6.3V

X5R

402

C6R30

1

.1UF 10%

6.3V

X5R

402

2

2

2

2

2

2

2

2

2

2

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

C7T69

1

C7T70

1

C7T75

1

C7T74

1

C7T73

1

C7T72

1

C6R33

1

C7R88

1

C6R45

1

1

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

C7T8

6.3V

X5R

402

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

[PAGE_TITLE=CPU, DECOUPLING]

DRAWING

XENON_FABK

MICROSOFT

CONFIDENTIAL

N: EMPTY FOR

PROJECT NAME

XENON_RETAILWed Aug 24 09:27:03 2005

CPU SOCKET

PAGE

10/73

REV

K7

V_CPUCORE

CPU, DECOUPLING

C7R31

1

.1UF

6.3V

X5R

402

C7T12

1

.1UF 10%

6.3V

X5R

402

C7R82

1

.1UF 10%

6.3V

X5R

402

C7R56

1

.1UF 10%

6.3V

X5R

402

C6R26

1

.1UF 10%

6.3V

X5R

402

C6T9

1

.1UF 10%

6.3V

X5R

402

C6T3

1

.1UF

6.3V

X5R

402

C7R21

1

.1UF 10%

6.3V

X5R

402

C7R107

1

.1UF 10%

6.3V

X5R

402

C6R13

1

.1UF 10%

6.3V

X5R

402

2

10%

2

2

2

2

2

2

10%

2

2

2

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

C6T11

1

6.3V

C7R17

1

6.3V

C7R18

1

6.3V

C7R20

1

6.3V

C7R42

1

6.3V

C7R41

1

6.3V

C7R40

1

6.3V

C7R39

1

6.3V

C6T21

1

6.3V

C6R12

1

6.3V

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

C7T38

1

C7R65

1

C6T14

1

C7T28

1

C7T31

1

C6R10

1

1

C7R15

1

C7R33

1

C7R32

1

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

C7R8

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

6.3V

X5R

402

10%

10%

10%

10%

10%

10%

10%

10%

10%

10%

2

2

2

2

2

2

2

2

2

2

1

.1UF

1

.1UF

1

.1UF

1

.1UF

1

.1UF

1

.1UF

1

.1UF

1

.1UF

1

.1UF

1

.1UF

C7T58

6.3V

X5R

402

C6R24

6.3V

X5R

402

C7T56

6.3V

X5R

402

C7R98

6.3V

X5R

402

C6T8

6.3V

X5R

402

C7T17

6.3V

X5R

402

C7T41

6.3V

X5R

402

C6T12

6.3V

X5R

402

C6R15

6.3V

X5R

402

C6R41

6.3V

X5R

402

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

C7T30

2

1

10%.1UF

6.3V

X5R

402

C7T29

2

1

10%

.1UF .1UF

6.3V

X5R

402

C7T50

2

1

.1UF 10%

6.3V

X5R

402

C7R106

2

1

10%

.1UF

6.3V

X5R

402

C6T20

2

1

.1UF 10%

6.3V

X5R

402

C7T49

2

1

.1UF 10%

6.3V

X5R

402

C6T22

2

1

.1UF 10%

6.3V

X5R

402

C7T13

2

1

10%.1UF

6.3V

X5R

402

C7R14

2

1

10%.1UF

6.3V

X5R

402

C7R9

2

1

10%.1UF

6.3V

X5R

402

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

1

1

1

1

1

1

1

1

1

1

C7T54

6.3V

X5R

402

C6T24

6.3V

X5R

402

C7T53

6.3V

X5R

402

C7T52

6.3V

X5R

402

C6R9

6.3V

X5R

402

C6R7

6.3V

X5R

402

C7T61

6.3V

X5R

402

C7T60

6.3V

X5R

402

C7T59

6.3V

X5R

402

C7R86

6.3V

X5R

402

10%

10%

10%

10%

10%

10%

10%

10%

10%

10%

2

2

2

2

2

2

2

2

2

2

C6T13

1

.1UF

6.3V

C7T14

1

.1UF

6.3V

C7T80

1

.1UF

6.3V

C7T11

1

.1UF

6.3V

C7T40

1

.1UF

6.3V

C7R75

1

.1UF

6.3V

C7R85

1

.1UF

6.3V

C7R101

1

.1UF

6.3V

C6R8

1

.1UF

6.3V

C7R73

1

.1UF

6.3V

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

2

10%

X5R

402

C7R95

1

.1UF 10%

6.3V

X5R

402

C7R103

1

10%.1UF

6.3V

X5R

402

C7R104

1

.1UF 10%

6.3V

X5R

402

C7R96

1

.1UF 10%

6.3V

X5R

402

C7R108

1

.1UF 10%

6.3V

X5R

402

C7R109

1

.1UF 10%

6.3V

X5R

402

C7R105

1

.1UF 10%

6.3V

X5R

402

C7T4

1

.1UF 10%

6.3V

X5R

402

C6T18

1

.1UF 10%

6.3V

X5R

402

C7T16

1

.1UF 10%

6.3V

X5R

402

2

.1UF

2

2

.1UF

2

.1UF

2

.1UF

2

.1UF

2

.1UF

2

.1UF

2

.1UF

2

.1UF

C7T51

1

C7T47

1

C7T46

1

C7R97

1

C7T57

1

C7T55

1

C7T18

1

C7T39

1

C7T26

1

C7T48

1

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

2

10%

6.3V

X5R

402

C6T15

1

.1UF 10%

6.3V

X5R

402

C6T16

1

.1UF 10%

6.3V

X5R

402

C7T43

1

.1UF 10%

6.3V

X5R

402

C7T44

1

.1UF 10%

6.3V

X5R

402

C7T42

1

.1UF 10%

6.3V

X5R

402

C7R83

1

.1UF 10%

6.3V

X5R

402

C7T24

1

.1UF 10%

6.3V

X5R

402

C7T25

1

6.3V

X5R

402

C6T17

1

.1UF 10%

6.3V

X5R

402

C7T23

1

.1UF 10%

6.3V

X5R

402

2

2

2

2

2

2

2

2

2

2

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF.1UF 10%

.1UF

.1UF

1

1

1

1

1

1

1

1

1

1

C6T28

6.3V

X5R

402

C6T29

6.3V

X5R

402

C6T30

6.3V

X5R

402

C7T62

6.3V

X5R

402

C7T63

6.3V

X5R

402

C7T64

6.3V

X5R

402

C7T65

6.3V

X5R

402

C7T66

6.3V

X5R

402

C7T67

6.3V

X5R

402

C7T68

6.3V

X5R

402

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

2

10%

[PAGE_TITLE=CPU, DECOUPLING]

DRAWING

XENON_FABK

MICROSOFT

CONFIDENTIAL

PROJECT NAME

XENON_RETAILWed Aug 24 09:27:05 2005

PAGE

11/73

REV

K7

V_GPUCORE

1

R5R1

1K

5%

EMPTY

402

2

1

R5R2

1K

5%

CH

402

2

GPU, FSB

R5C12

2

1

5%1K

CH

402

R5C11

2

1

1K

5%

CH

402

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

FSB_CP_GP0_CLK_DP

IN

FSB_CP_GP0_CLK_DN

IN

FSB_CP_GP0_FLAG_DP

IN

FSB_CP_GP0_FLAG_DN

IN

FSB_CP_GP0_DATA0_DP

IN

FSB_CP_GP0_DATA0_DN

IN

FSB_CP_GP0_DATA1_DP

IN

FSB_CP_GP0_DATA1_DN

IN

FSB_CP_GP0_DATA2_DP

IN

FSB_CP_GP0_DATA2_DN

IN

FSB_CP_GP0_DATA3_DP

IN

FSB_CP_GP0_DATA3_DN

IN

FSB_CP_GP0_DATA4_DP

IN

FSB_CP_GP0_DATA4_DN

IN

FSB_CP_GP0_DATA5_DP

IN

FSB_CP_GP0_DATA5_DN

IN

FSB_CP_GP0_DATA6_DP

IN

FSB_CP_GP0_DATA6_DN

IN

FSB_CP_GP0_DATA7_DP

IN

FSB_CP_GP0_DATA7_DN

IN

FSB_CP_GP1_CLK_DP

IN

FSB_CP_GP1_CLK_DN

IN

FSB_CP_GP1_FLAG_DP

IN

FSB_CP_GP1_FLAG_DN

IN

FSB_CP_GP1_DATA0_DP

IN

FSB_CP_GP1_DATA0_DN

IN

FSB_CP_GP1_DATA1_DP

IN

FSB_CP_GP1_DATA1_DN

IN

FSB_CP_GP1_DATA2_DP

IN

FSB_CP_GP1_DATA2_DN

IN

FSB_CP_GP1_DATA3_DP

IN

FSB_CP_GP1_DATA3_DN

IN

FSB_CP_GP1_DATA4_DP

IN

FSB_CP_GP1_DATA4_DN

IN

FSB_CP_GP1_DATA5_DP

IN

FSB_CP_GP1_DATA5_DN

IN

FSB_CP_GP1_DATA6_DP

IN

FSB_CP_GP1_DATA6_DN

IN

FSB_CP_GP1_DATA7_DP

IN

FSB_CP_GP1_DATA7_DN

IN

FSB_BYPCLK_DP

FSB_BYPCLK_DN

FSB_BYPCLK_SEL

1

R5R3

4.87K

1%

CH

402

2

FSB_IMPED_CAL

FSB_IMPED_NCAL

AA31

AA32

AA28

B29

A29

D25

J34

J33

J30

J29

M29

M30

L32

L31

K33

K34

L30

L29

J31

J32

K30

K29

H34

H33

H31

H32

V33

V34

T33

T34

Y33

Y34

W30

W29

W33

W34

V29

V28

V31

V32

U33

U34

U30

U29

T28

U4D1

FSB_BYPCLK_DP

FSB_BYPCLK_DN

FSB_BYPCLK_SEL

CP_GP0_CLK_DP

CP_GP0_CLK_DN

CP_GP0_FLAG_DP

CP_GP0_FLAG_DN

CP_GP0_DATA0_DP

CP_GP0_DATA0_DN

CP_GP0_DATA1_DP

CP_GP0_DATA1_DN

CP_GP0_DATA2_DP

CP_GP0_DATA2_DN

CP_GP0_DATA3_DP

CP_GP0_DATA3_DN

CP_GP0_DATA4_DP

CP_GP0_DATA4_DN

CP_GP0_DATA5_DP

CP_GP0_DATA5_DN

CP_GP0_DATA6_DP

CP_GP0_DATA6_DN

CP_GP0_DATA7_DP

CP_GP0_DATA7_DN

CP_GP1_CLK_DP

CP_GP1_CLK_DN

CP_GP1_FLAG_DP

CP_GP1_FLAG_DN

CP_GP1_DATA0_DP

CP_GP1_DATA0_DN

CP_GP1_DATA1_DP

CP_GP1_DATA1_DN

CP_GP1_DATA2_DP

CP_GP1_DATA2_DN

CP_GP1_DATA3_DP

CP_GP1_DATA3_DN

CP_GP1_DATA4_DP

CP_GP1_DATA4_DN

CP_GP1_DATA5_DP

CP_GP1_DATA5_DN

CP_GP1_DATA6_DP

CP_GP1_DATA6_DN

CP_GP1_DATA7_DP

CP_GP1_DATA7_DN

FSB_IMPED_PCAL

FSB_IMPED_NCAL

X02056-010

V_GPUCORE

C4R27 C4R33 C4R45 C4T22 C5R18 C4R65 C4R60 C4T13

.1UF

.1UF

10%

10%

6.3V

6.3V

X5R

X5R

402

402

1OF8

GPU VERSION 57

FSB DECOUPLING

.1UF

.1UF

10%

10%

6.3V

6.3V

X5R

X5R

402

402

GP_CP0_CLK_DP

GP_CP0_CLK_DN

GP_CP0_FLAG_DP

GP_CP0_FLAG_DN

GP_CP0_DATA0_DP

GP_CP0_DATA0_DN

GP_CP0_DATA1_DP

GP_CP0_DATA1_DN

GP_CP0_DATA2_DP

GP_CP0_DATA2_DN

GP_CP0_DATA3_DP

GP_CP0_DATA3_DN

GP_CP0_DATA4_DP

GP_CP0_DATA4_DN

GP_CP0_DATA5_DP

GP_CP0_DATA5_DN

GP_CP0_DATA6_DP

GP_CP0_DATA6_DN

GP_CP0_DATA7_DP

GP_CP0_DATA7_DN

GP_CP1_CLK_DP

GP_CP1_CLK_DN

GP_CP1_FLAG_DP

GP_CP1_FLAG_DN

GP_CP1_DATA0_DP

GP_CP1_DATA0_DN

GP_CP1_DATA1_DP

GP_CP1_DATA1_DN

GP_CP1_DATA2_DP

GP_CP1_DATA2_DN

GP_CP1_DATA3_DP

GP_CP1_DATA3_DN

GP_CP1_DATA4_DP

GP_CP1_DATA4_DN

GP_CP1_DATA5_DP

GP_CP1_DATA5_DN

GP_CP1_DATA6_DP

GP_CP1_DATA6_DN

GP_CP1_DATA7_DP

GP_CP1_DATA7_DN

.1UF

10%

6.3V

X5R

402

.1UF

10%

6.3V

X5R

402

IC

P33

P34

L34

L33

T29

T30

T31

T32

R34

R33

R29

R30

N34

N33

P29

P30

N31

N32

M34

M33

AC33

AC34

Y29

Y30

AC28

AC29

AD29

AD30

AD34

AD33

AB29

AB30

AC32

AC31

AA29

AA30

AB33

AB34

AA34

AA33

.1UF

10%

6.3V

X5R

402

FSB_GP_CP0_CLK_DP

FSB_GP_CP0_CLK_DN

FSB_GP_CP0_FLAG_DP

FSB_GP_CP0_FLAG_DN

FSB_GP_CP0_DATA0_DP

FSB_GP_CP0_DATA0_DN

FSB_GP_CP0_DATA1_DP

FSB_GP_CP0_DATA1_DN

FSB_GP_CP0_DATA2_DP

FSB_GP_CP0_DATA2_DN

FSB_GP_CP0_DATA3_DP

FSB_GP_CP0_DATA3_DN

FSB_GP_CP0_DATA4_DP

FSB_GP_CP0_DATA4_DN

FSB_GP_CP0_DATA5_DP

FSB_GP_CP0_DATA5_DN

FSB_GP_CP0_DATA6_DP

FSB_GP_CP0_DATA6_DN

FSB_GP_CP0_DATA7_DP

FSB_GP_CP0_DATA7_DN

FSB_GP_CP1_CLK_DP

FSB_GP_CP1_CLK_DN

FSB_GP_CP1_FLAG_DP

FSB_GP_CP1_FLAG_DN

FSB_GP_CP1_DATA0_DP

FSB_GP_CP1_DATA0_DN

FSB_GP_CP1_DATA1_DP

FSB_GP_CP1_DATA1_DN

FSB_GP_CP1_DATA2_DP

FSB_GP_CP1_DATA2_DN

FSB_GP_CP1_DATA3_DP

FSB_GP_CP1_DATA3_DN

FSB_GP_CP1_DATA4_DP

FSB_GP_CP1_DATA4_DN

FSB_GP_CP1_DATA5_DP

FSB_GP_CP1_DATA5_DN

FSB_GP_CP1_DATA6_DP

FSB_GP_CP1_DATA6_DN

FSB_GP_CP1_DATA7_DP

FSB_GP_CP1_DATA7_DN

.1UF

10%

6.3V

X5R

402

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

MEM_SCAN_EN _BUFF

13

IN

MEM_SCAN_TOP_EN_BUFF

13

IN

MEM_SCAN_BOT_EN_BUFF

13 21

IN

1

.1UF

1

.1UF

1

.1UF

C2E4

6.3V

X5R

402

C2R12

6.3V

X5R

402

C2D5

6.3V

X5R

402

10%

10%

10%

V_MEM

2

V_MEM

2

V_MEM

2

R2E5

1

0

5%

402

CH

U2E2

EMPTY

SN74LVC1G125

5

VCC

2

IN

3

GND OE_N

X801565-001

R2D12

1

5%

0

402

CH

U2D1

EMPTY

SN74LVC1G125

5

VCC

2

IN

3

GND OE_N

X801565-001

R2R6

1

5%

0

CH

402

U2R1

EMPTY

SN74LVC1G125

5

VCC

2

IN

3

GND OE_N

X801565-001

13

GPU_SCAN_BUF F_EN_N

IN

V_MEM

2

OUT

1

R2R5

0

5%

CH

402

2

4

1

MEM_SCAN_EN

1

1

R4F8

1K

5%

CH

402

2

2

R2D11

1K

5%

CH

402

OUT

27

26

202122

23 24 25

2

MEM_SCAN_TOP_EN

4

OUT

1

1

1

R4F7

R2T2

1K

1K

5%

5%

CH

CH

402

2

402

2

OUT

20 22 24

26

V_MEM

2

1

1

R4U6

R2T1

1K

1K

5%

5%

CH

CH

402

402

2

4

OUT

1

MEM_SCAN_BOT_EN

2

23 25

OUT

27

[PAGE_TITLE=GPU, FSB]

DRAWING

XENON_FABK

Wed Aug 24 09:27:06 2005

MICROSOFT

CONFIDENTIAL

PROJECT NAME

XENON_RETAIL

PAGE

12/73

REV

K7

R4D3

2

1

49.9

1%

EMPTY

402

R4D4

2

1

1%

49.9

FT2P14

34 34

IN

33

33

33

33

R5D1

2

1

562

1%

402

CH

1

1.47K

402

1

GPU_RST_N GPU_RST_DONE

IN

IN

IN

IN

PEX_SB_GPU_L1_DP

PEX_SB_GPU_L1_DN

PEX_SB_GPU_L0_DP

PEX_SB_GPU_L0_DN

PEX_PCAL

V_GPUPCIE

R4R3

2