Page 1

5

Table of Contents

4

3

2

1

Page

01

D D

02

03

0

4

05

06

07

08

09

10

11

C C

12

13

Title

CHANGE HISTORY

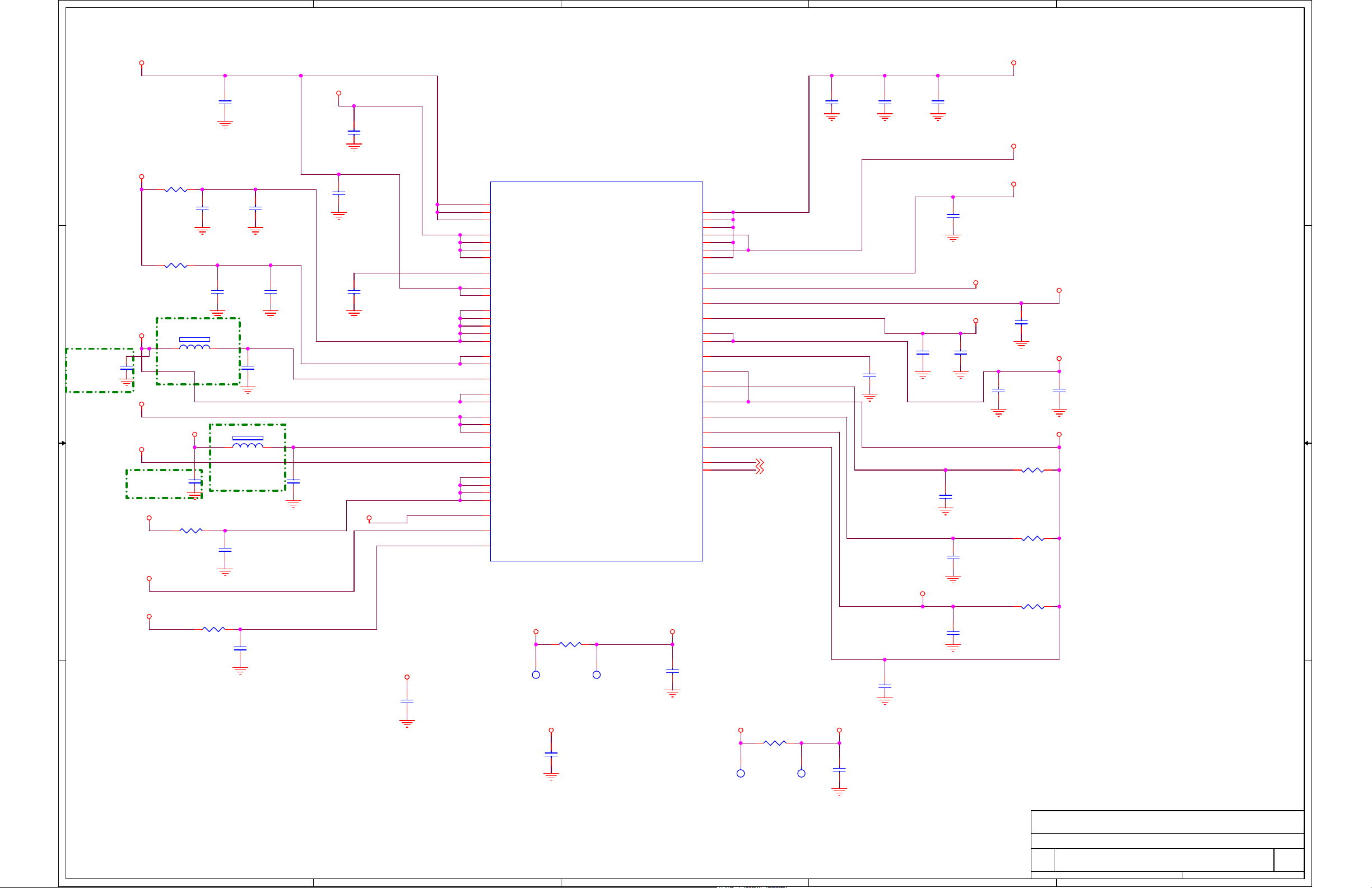

BLOCK DIAGRAM

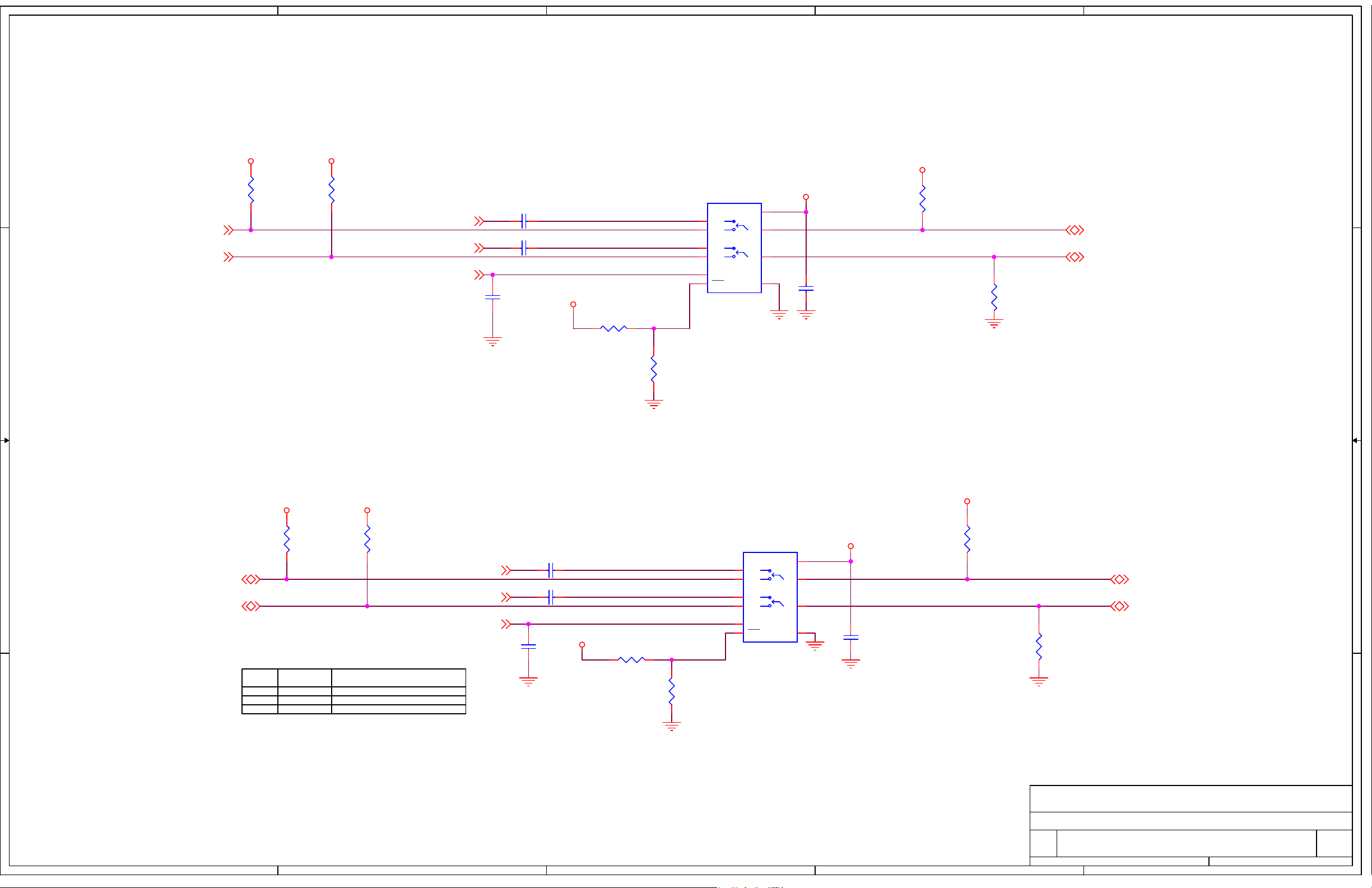

CLOCK DISTRIBUTION

SIGNAL & RESET MAP

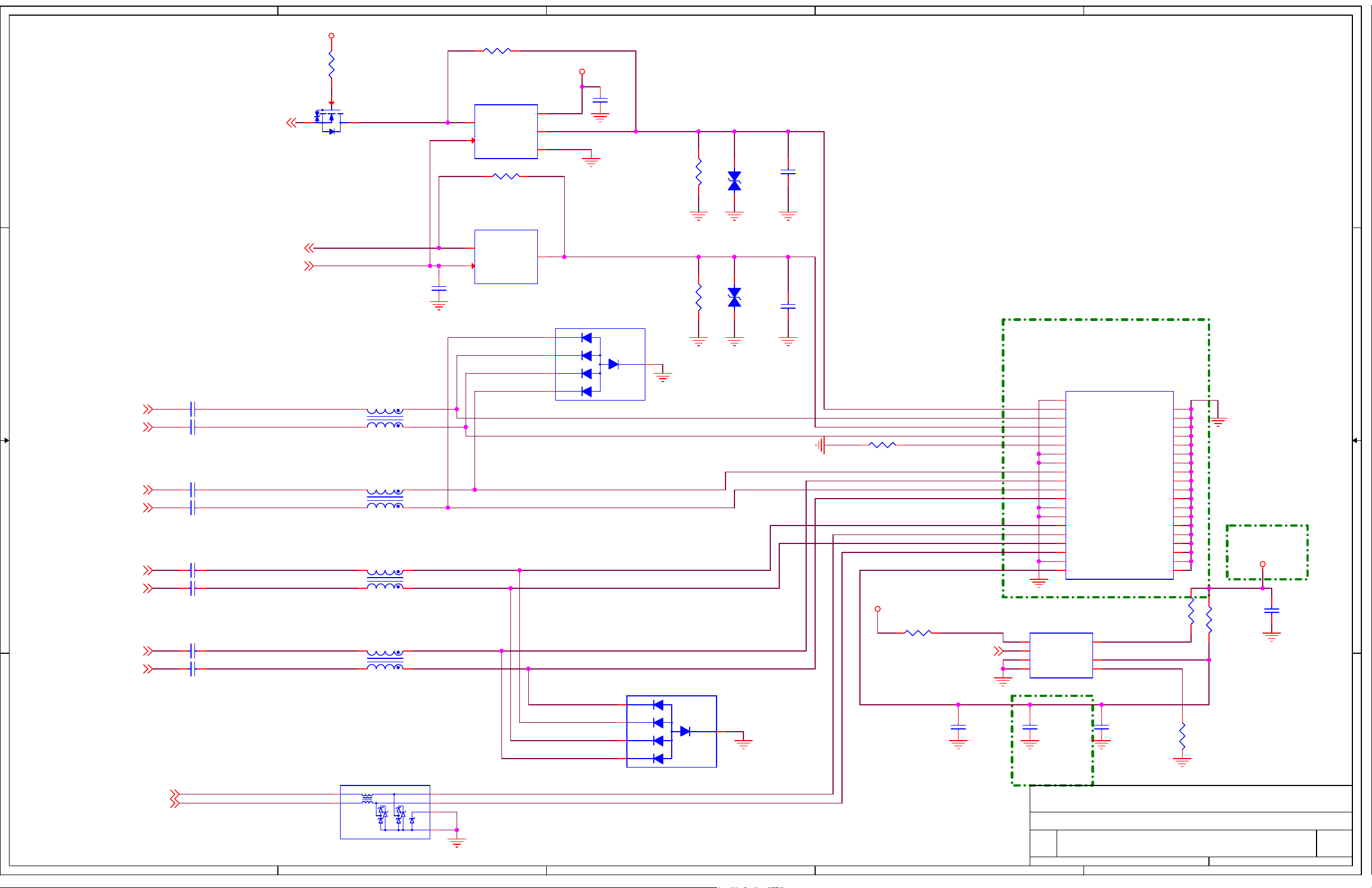

POWER FLOW

POWER DISTRIBUTION

POWER SEQUENCE

I2C MAP

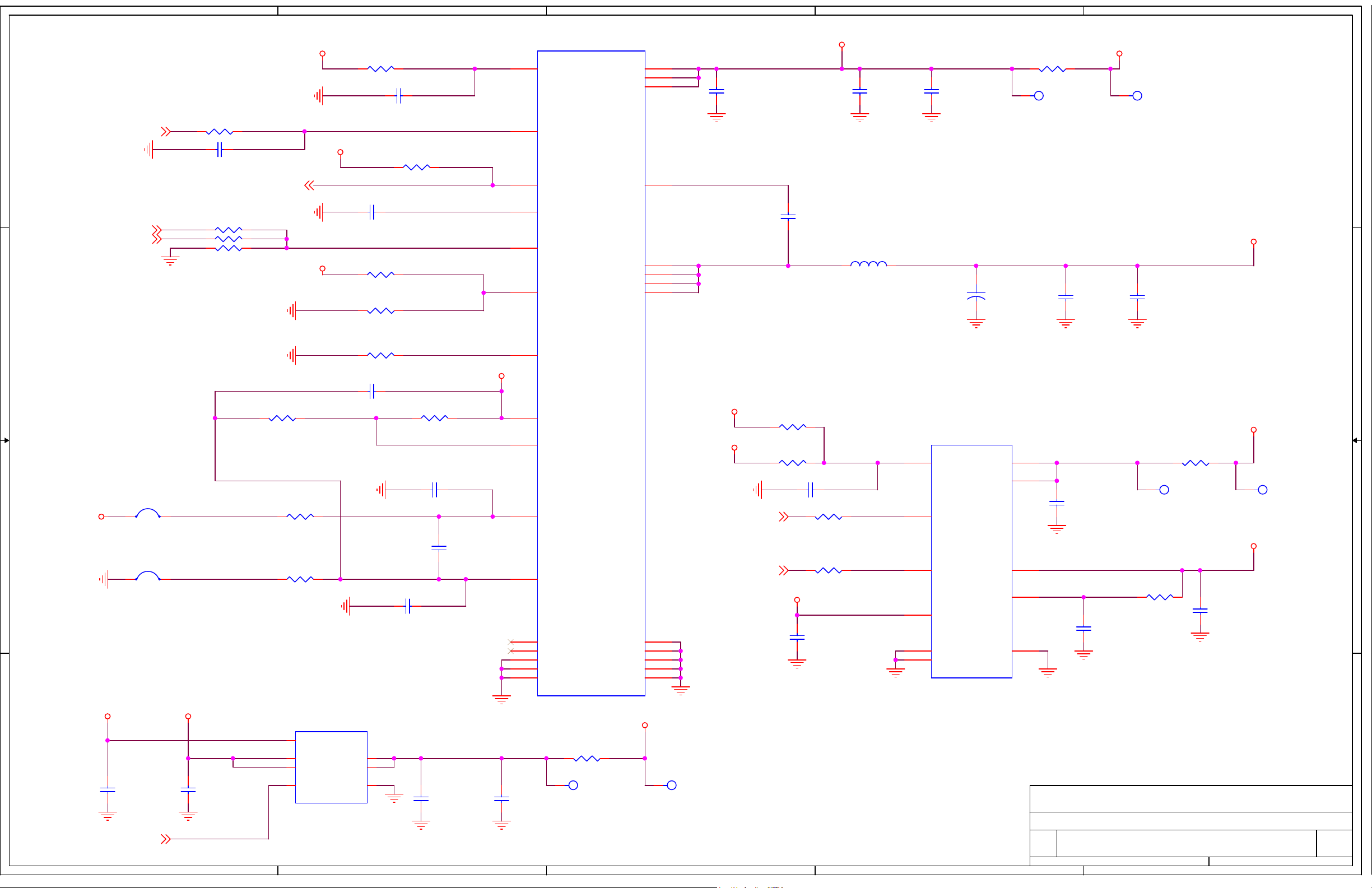

CPU(1)_MISC,JTAG,DDI.EDP

CPU(2)_LPDDR3

CPU(3)_SKL POWER1

CPU(4)_SKL_POWER2

Page

31

32

33

34

35

36

37

38

39

40

41

42

43

Title

Sensor-uC

On Board-Sensors

Debug Conn

Empty

SM BUS

EC-ITE 8528VG-1

EC-ITE 8528VG-2/SPI ROM

TPM

Temp Sensor/System Fan

REALTEK ALC298 CODEC

Audio Jack/Vol Button/Spkr

Microphones

M.2 SSD CONNECTOR

Page

61

62

63

64

65

66

67

68

69

70

71

72

73

Title

+1VSB

+1.8VSB & Load SW

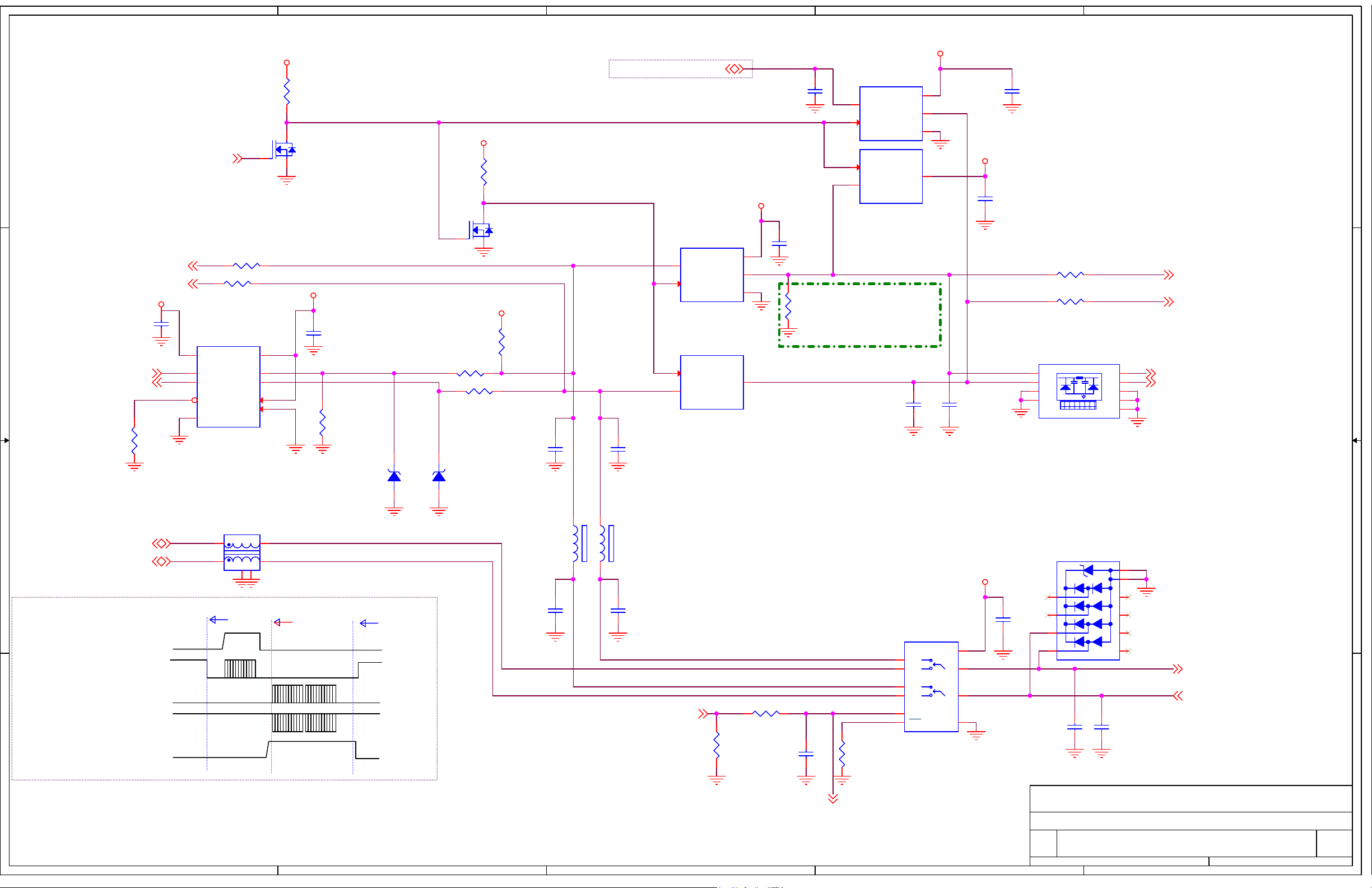

CHARGER

+5V Load SW

+3P3V Load SW

VCPU Controller

VCORE VCCSA

VCVGT

EMPTY (was GTX Reg)

SL1 PWR/ BATT CONN.

SL1 SIGNALS

+3P3V_HPD/LCD backlight/TB

BLADE PWR

14

15

16

17

18

19

20

B B

21

22

23

24

25

26

27

28

CPU(5)_GND

CPU(6)_CFG_RESERVED

LPDDR3(1)_MEMORY DOWN

LPDDR3(2)_MEMORY DOWN

XDP

LPDDR3(3)_CA/DQ Voltage

PCH(1)_SD,HDA,RTC, CLK

PCH(2)_CLK,SMB,LPC, SPI

PCH(3)_SYS PWR CONTR

PCH(4)_CCI, HWID

PCH(5)_PCIE,USB

PCH(6)_CPU,GPIO,MISC

PCH(7)_POWER

PCH(8)_empty

Power Monitor

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

Empty

USB3.0

DP Dongle Control

mDP

SDXC

Camera IR

Wi-Fi_BT

Components for ME/EMI

Camera Power

Camera Rear

Camera Front

3P3VA & BKL PWR

+VCCIO & 0P85VSB

eDP connector

+VCCEDRAM & +VCCEOPIO

74

75

76

BLADE

Power Protect

Test Points

29

30

A A

CAD Note:

Default component footprint is SMD 0201, X5R, 1% resistors.

Property: BUILD-OPT

DNP = Do Not Place

Empty

Touch Con & Key

5

59

60

+5VSB & +3P3VSB

+1P2V_DUAL&+VTT

4

S or DB = Replace after Debug

3

2

<Core Design>

<Core Design>

<Core Design>

Table of Contents

Table of Contents

Title:

Title:

Title:

Engineer:

Engineer:

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

Table of Contents

Surface

Surface

Surface

1 76Monday, May 11, 2015

1 76Monday, May 11, 2015

1

1 76Monday, May 11, 2015

1.90.2

1.90.2

1.90.2

Page 2

5

Schematics Change History

4

3

2

1

Rev.

0p9 28 Oct 2014 1. Starting with G_EV1_1021-1630.DSN

D D

0p10 3 Nov 2014 1. Changing to NVDC

0p12 11 Nov 2014 1. Model DDR connection from Intel SDS

0p13 18 Nov 2014

0p14

C C

0p15 26 Nov 2014

0p16 03 Dec 2014

Date

20 Nov 2014

2. Added SL schematic from page 72 ...\T\MB\DV_RELEASED\Schematic\CASTLE2_DV_2014_1021_1100.DSN

3. Added External USB3 schematic from ...\T\MB\DV_RELEASED\Schematic\CASTLE2_DV_2014_1021_1100.DSN

4. Added external DP ...\T\MB\DV_RELEASED\Schematic\CASTLE2_DV_2014_1021_1100.DSN

5. Added IR_CAMERA from Front Camera...put in page 49

6. Removed page 73 PCIe GPU

7. Added Blade from T

8. Removed P72 T2B Pwr Transistors

2. Replaced GTX with GT, kept bypass caps

3. Replaced Charger with BQ24770

1. Replace SKL-U with SKL-Y0p11 3 Nov 2014

1. Added FUB information to all components

2. Changed Decretes.. sizing caps

1. Added +5VA_SHA

2. Added T Cost Down/XCN's

3. Added SL +5V load Switch & Caps

4. Added Blade +5V load Switch & Caps

1. Removed Boost

2. Re-adjusted usb ports on CPU

3. Removed Audio DSP

1. changed +1VSB regulator

2. changed IR Camera/added diode

3. added power numbers from 0.91 PDG, Oct14

4. changed BLADE connector

5. cpu decoupling caps changed

6. changed +5V/+3V inductors (place holder)

Comments

1. swapped M_A_CAA with MA_CAB on U1601/U1602

2. added two SAR chips, P32

3. remove tp's from csi lines on (p23)

4. change from 10 ceramic to 3 tantalum-poly on usb3 typeA (p45)

5. remove the RSENSE from output of +VCCIO(p56)/+0p85VSB(p56)/+VCCEDRAM (p58)/+VCCEOPIO (p58)/+1VSB(p61)/+1P8VSB(p62)

0p17 05 Dec 2014

B B

A A

0p18

0p19

0p20 15 Dec 2014

0p21 16 Dec 2014

0p22 17 Dec 2014 1. Replaced SD connector with AY531465T

0p23

current

09 Dec 2014

12 Dec 2014

-

6. change RSENSE input to 0402 from 0603 for +VCCIO(p56)/+0p85VSB(p56)/+VCCEDRAM (p58)/+VCCEOPIO (p58)/+1VSB(p61)/+1P8VSB(p62) input regulator

7. change inductor for +VCCIO(p56)/+0p85VSB(p56)/+VCCEDRAM (p58) to HMLE20161B-1R0MDR-01

8. change RSENSE input to 0402 from 0603 for +5V_TS,+5V_SDXC,+5V_AUDIO,+5V, +5V_FAN(p64)

9. change RSENSE input to 0402 from 0603 for +3P3V_PANEL,+3P3V,+3P3V_SENSOR,+1P8V_DMIC (p65)

10. Replacing the SL connector with X908351-001

11. Replace PL5901 and PL5902 with CMLE042T-2R2MS-01

12. Replace 0402 1uf 6.3V with 0201 1uF 6.3V X5R

13. Replace L7201 with TOKO #A919CY-100M

14. Added VSYS -> BLADE FANG supply (p73)

1. Reduced sizes of parts for Cameras (Resistors/Caps/Regulators)

1. All 47uF caps become 0805/1mmZ

2. All 10uF caps become 0402...4V/6.3V

1. changed SAM flash to reduce size to 2x3 from 5x4

2. Shui Changes

3. more Shui Changes

1. changed SAM flash to reduce size to 2x3 from 5x5

2. changes from EV_schematic_issue_check_1216_JDM1.xlsx

3. changed name of +6_12 to +V_ALWAYS_ON

4. Removed 2 Mikes & Front Mike & added FPC conn

5. Added 2nd BLADE connector

2. changes from EV_schematic_issue_check_viola_1217_JDM1.xlsx

1. See apexUfixes_revXpXX.xlsx

CAD Note:

Default component footprint is SMD 0201, X5R, 1% resistors

Property: BUILD-OPT

DNP = Not Installed Part.

5

4

S = Short after design fixed

3

CHANGE HISTORY-1

CHANGE HISTORY-1

Title:

Title:

Title:

Engineer:

Engineer:

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

CHANGE HISTORY-1

Surface

Surface

Surface

2 76Monday, May 11, 2015

2 76Monday, May 11, 2015

1

2 76Monday, May 11, 2015

1.90.2

1.90.2

1.90.2

Page 3

5

4

3

2

1

LPDDR3 2GB/4GB/8GB

2 x32 @1600MHz

page 16

LPDDR3 2GB/4GB/8GB

2 x32 @1600MHz

D D

16MB UEFI EEPROM

page 17

W25Q128FVPIQ

page 37

CH A

CH B

QSPI

eDP

Display TCON

Connector

page 57

DP 4 Lane + AUX(B)

USB2.0(0) LPM + USB3.0(1)

USB2.0(0) LPM + USB3.0(1)

ANX2875

page 47

page 45

page 71

page 70

Power

DP Connector

USB3

TYPE A

Connector

SPI / I2C4

Intel Processor

SKL

DP 4 Lane

PCH UART(Debug)

page 71

AUX(C)

HPD/CONFIG1

EC Debug UART

2:1 MUX

page 71

AUX(C)/PCH UART

2:1 MUX

DP/ EC Debug UART

SAM Debug UART

page 71

SURF LINK

Connector

page 47,71

SAR

ADI / ADUX1050

SAR

ADI / ADUX1051

Touch Connector

page 30

page 32

I2C0

page 32

15W (BGA1168)

C C

Accelerometer+Gyro

Bosch / BMI160

page 32

Sensor

Aggregator

Microcontroller

256/512/

1024GB SSD

Full size

mSATA card

E-compass (Magnetometer)

MEMSIC / MMC34160PJ

page 32

I2C_SCL_MCU

ALS/Proximity-Sensor

Intersil / ISL29033

B B

page 32

SAM

MKL33Z256VMP4

OR

MKL17Z256VMP4

HOST_AUTH_RX/TX

SAM_SPI

page 31

LPDDR3 Thermal Sensor

STTS751-1DP3F

Surrend Thermal Sensor

SEN_HALL_INT

STTS751-1DP3F

Hall Effect Sensor IC

ROHM / BU52058GWZ-E2

page 32

M2 2280

B-M Type

Connector

page 43

PCIe x2

or SATA

Authentication

ATECC108

page 31

SAM reflash

image backup

EEPROM

MX25L4006EZNI-12G

page 39

page 31

SMBUS3

SMBUS3

PROCHOT#

page 20~28

SMBUS2 PECI

LPC BUS

24MHz

MIPI

MIPI

MIPI

PCIe

USB2.0(5)

480Mb/s

TPM

SLB9665TT

USB3 (only)

Front Webcam

Connector

5MP

Rear Webcam

Con

8MP

IR VGA CAMERA

Connector

HD Audio

page 38

page 54

nector

page 53

page 49

Marvell 8897

WLAN 802.11 /b/g/n/AC

Bluetooth 4.0

page 50

AUDIO CODEC

Realtek

ALC298

USB2 to SDXC

RTS5304-GR

page 48

WIFI ANT1

WIFI ANT2

MIMO

page 40

SPKR L/R

Audio+mic

SDIO

Speaker

L+/-, R+/-

AUDIO IN/OUT

DMIC1 Onboard

SDIO CONN

page 49

page 42

page 41

page 43

SEN_HALL_INT_EC

System EC

Battery Charge

A A

40Wh

Battery

page 70

+7.4V

Controller

BQ24770

SMBUS1 + CTRL

page 63

ITE 8528

page 36

PWM/TACH

SPI

EC_SAM_I2C

5

4

3

FAN Connector

page 39

EC EEPROM

page 37

2

BLOCK DIAGRAM

BLOCK DIAGRAM

Title:

Title:

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Title:

Engineer:

Engineer:

Engineer:

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

1

BLOCK DIAGRAM

Surface

Surface

Surface

3 76Monday, May 11, 2015

3 76Monday, May 11, 2015

3 76Monday, May 11, 2015

1.90.2

1.90.2

1.90.2

Page 4

5

4

3

2

1

HSW Buffer Through Mode for Pre-Silicon

D D

WIFI_32K_CLK

32 KHz

88W8897-XX-CBK2

M_CHA_CLK[0..1]/#

SUS_CLK

M_CHB_CLK[0..1]/#

DIMM2

DIMM1

CLKOUT_LPC_0

CK_24M_EC

24 MHz

ITE 8528VG/FX

32.768KHz

Intel

C C

SKL U/Y

CK_24M_DEBUG

24 MHz

CLKOUT_LPC_1

CLKOUT_ITXDP_N

CLKOUT_ITXDP_P

B B

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

CLK_XDP_N

CLK_XDP_P

PCIE_WIFI_RCLK_N

PCIE_WIFI_RCLK_P

CK_24M_TPM

24 MHz

XDP

100 MHz

WIFI

100 MHz

LPC DEBUG HEADER

TPM

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

HDA_BCLK

SPI_CLK

A A

PCIECLK_SL1_N

PCIECLK_SL1_P

100 MHz

AZ_BITCLK

24 MHz

SPI_CLK

50 MHz

SL1

AUDIO CODEC

SPI ROM

XTAL24_IN RTCX

<Core Design>

<Core Design>

<Core Design>

CLOCK DISTRIBUTION(TBD)

CLOCK DISTRIBUTION(TBD)

Title:

Title:

Title:

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

32.768KHz24MHz

5

4

3

2

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

Engineer:

Engineer:

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

CLOCK DISTRIBUTION(TBD)

Surface

Surface

Surface

4 76Monday, May 11, 2015

4 76Monday, May 11, 2015

1

4 76Monday, May 11, 2015

1.90.2

1.90.2

1.90.2

Page 5

5

Battery

VDD_

4

BATA_PACK

3

2

1

D D

SL1

PWR_SL1

PWR_SL1_F

CHG_BATDRV_R_ A

FET

SW

Switch

(Dio

USER_RESET

Charging

SL1_PWR_GOOD

EC_SL1_PWR_EN

C C

SW

EXT_DC_IN

circuit

& Switch

VCCDSW

POWER ON SEQUENCE (TBD)

STEP1Signal & Description

+6VA_12VA /TRANSLATE TO +3P3VAS,

+3P3V_EC /EC POWER

2

EC_RST# /EC INITIAL

3

+AC

4.

5.

6.

7.

8.

9.

10.

11.

B B

12

13.

14.

15.

16.

17.

18.

19.

20.

21.

22.

23.

24.

A A

_BAT_SYS /SYSTEM POWER READY

VCCDSW_EN /TURN ON DSW POWER for PCH

PCH_DPWROK /DEEP POWER GOOD TO PCH

SLP_SUS# /STANBY POWER REQUIRED

VSUS_ON/EC TURN ON STANBY POWER

ALL_SUS_PWRGD /STANDBY(SUS) POWER STABLE

RSMRST# /SUS POWER GOOD TO PCH

EC_SAM_INT_IN

PWRBTN# TO EC

SB_PWRBTN# /PASS PWRBTN SIGNAL TO PCH

PM_SUSC#(SLP_S4#) /EXIT S4 STATE, HIGH

SUSC_EC# /BYPASS SLP_S4#

PM_SUSB#(SLP_S3#) /EXIT S3 STATE, HIGH

SUSB_EC# /BYPASS SLP_S3#, MAIN PWR ON

ALL_SYS_PWRGD /SYSTEM POWER STABLE

VCCST_PWRGD/ INDICTOR TO CPU

VRM_PWRGN /POWER FOR CPU IS GOOD

PM_PCH_PWROK /PCH CORE POWER OK AT LEAST 5ms

SYS_PWROK /SYSTEM POWER STABLE

SVID /VR controller establish protocol to CPU

PLTRST# /ALL SET UP AND RESET TO INITIAL

+V_VDDQ_VTT

+1P2V_DUAL

+1P8V_DUAL

+VCCST_CPU

+AC_BAT_SYS

1-2

+VCCIO

+VCCSTG

+1P8V

+3P3V

+3P3V_SSD

+5V

de)

1-1

+V_ALWAYS_ON

VOLT REG.

MAX6443

3P3VA_EN

Step-Down

+3P3V_EC

5

VCCDSW_EN

+3P3VSB

+5VSB

+1P8VSB

+0P85VSB

+1VSB

+1VS

B is last one ramp up

+1P2V_DUAL_PW RGD

ALL_SUS_PWRGD

VRM_PWRGD

ALL_SYS_PWRGD

+VCCIO_PWRGD

+3P3VA, +1P8V A

+VCC_RTC

+5V_SHA

2

+3P3V_EC

Power

Button

11

SAM

EC_SAM_INT_IN

VSUS_ON

8

ALL_SUS_PWRGD

9

15

SUSC_EC#

17

SUSB_EC#

+VCCEDRAM

+VCCEOPIO

VCORE

VCCGT

VCCGTX

VCCSA

FORCE_OFF#

PWRBTN#_EC

PWRB

12

18

ALL_SYS_PWRGD

EN

20

VRDY

EC Reset

circuit

TN#

CPU_VRON

VRM_PWRGD

3

EC_RST#

WRST#

EC

IT8528

13

10

6

7

PM_PCH_PWROK

SYS_PWROK

VCCST_PWRGD

19

OD

STUFF

0 ohm

23

SVID

SB_PWRBTN#

RSMRST#

PCH_DPWROK

SLP_SUS#

21

22

PWRBTN#

RSMRST#

DSW_PWROK

SLP_SUS#

PCH_PWROK

SYS_PWROK

VCCST_PWRGD

Intel

SKL U

PM_SUSC#

14

PM_SUSB#

16

SLP_S3#

SLP_S4#

EC etc.

PLTRST#

24

PLTRST#

1V TO 3.3V

ER

SHIFT

Power On Sequence

1

24

TPM

<Core Design>

<Core Design>

<Core Design>

SIGNAL&RESET MAP

SIGNAL&RESET MAP

Title:

Title:

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Title:

Engineer:

Engineer:

Engineer:

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

1

SIGNAL&RESET MAP

Surface

Surface

Surface

1.90.2

1.90.2

5 76Monday, May 11, 2015

5 76Monday, May 11, 2015

5 76Monday, May 11, 2015

1.90.2

Page 6

5

12V

ADAPTER

+V_ALWAYS_ON

3A

0.45A

A B

Charger

PWR_SL1_F

D D

+AC_BAT_SYS

C C

B B

Switching

Linear

A A

Switch ON/OFF

0.564A

3.125A

5.16A

2.76A

1.7A

0.28A

4

0.075A

0.075A

+5VA_EN

3P3VAS_EN

NCP4623

TPS62175DQCR

Efficiency is about 90%

3P3VA_EN

NCP4623

TPS51624

Efficiency is about 80%

CPU_VR_EN

CSD87351Q5D

TPS51285

Efficiency is about 90%

CSD87351Q5D

TPS51285

Efficiency is about 90%

VSUS_ON

TPS51367

Efficiency is about 80%

SUSC_EC#

TPS51367

Efficiency is about 80%

SUSB_EC#

TPS62140

INT-MOS

Efficiency is about 80%

SUSC_EC#

3

3P3V_EC_EN

& 3P3VA_EN

VCCDSW_EN

3P3V_EC_EN

& 3P3VA_EN

SL1_3P3V_DIS

+3P3V_PANEL

RT9728

0.49A0.3A

BLADE_AUTH_PWR_EN

RST

32A

5.58A

0.7A

SUSB_EC#

0.9A

RTD3_CR_PWREN

1.07A

SUSB_EC#

0.9A

USB_PWREN

1.5A

SL1_5V_PWR_EN

0.5A

BLADE_5V_PWR_EN

0.0027A

4.51A

0.062A

2.013A

SUSB_EC#

0.0313A

0.0094A

RTD3_TPANEL_PWR

0.451A

EDP_VDD_EN

1.5A

WWAN_PWREN

0.007375A

SENSORS_PWR_EN

+3P3V_TS

SUSB_EC#

0.0033A

0.61A

RTD3_CAM_PWREN

06Dec14 jks: NEEDS UPDATE

6.8A

SUSC_EC#

0.0239A

DDR_PG_CTRL

MPHY_PWREN

SUSB_EC#

5.248A 1.148A

0.741A

NX3P1108UK

NX3P1108UK

ADP151

RT9728

P-MOS

SLG59M301

SLG59M301

SLG59M301

NCP380

NCP380

NCP380

G5244A31U

TPS22920

NX3P1108UK

NX3P1108UK

G5244A31U

TPS22920

NX3P1108UK

TPS22920

TPS51206

SLG5NT1477VTR

NX3P1108UK

2

0.023A

0.0012A

0.00368A

SN_AB_GPIO_6

0.122A

SN_A_GPIO_5

SN_B_GPIO_5

0.07A

SN_A_GPIO_6

0.07A

SN_B_GPIO_6

0.0882A

SN_AB_GPIO_6

+1P8V_AUDIO

+3P3V_CAM

+3P3V_CAM

CS_ENTRY#

+5V_AUDIO

SUSB_EC#

TPS62590DRVR

Efficiency is about 90%

RT9013-25GQW

RT9013-25GQW

RT9013-18GQW

RT9013-28GU5

RT9013-28GU5

RT9013-18GQW

RT9030-11GU5

+3P3V

SLG59M301

TPS79901

TPS79901

NCP380

0.625A0.232A

S0/S3/S5

S0/S3/S5

S0/S3/S5

S0/S3/S5

S0/S3/S5

S0/S3/S5

S0

S0

S0/S3/S5

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0/S3/S5

S0

S0

S0

S0

S0

S0

S0

S0

S0/S3/S5

S0/S3

S0

S0

S0

S0/S3

S0

S0

1

+5VA_SHA

+5V_SHA_CONN

Imax =0.075A

+3P3VA

Imax=0.18805A

+3P3V_EC

Imax =0.0375A

+VCCDSW

Imax =0.15A

+1P8V_EC

Imax=0.11A

+VCC_RTC

+3P3V_HPD

Imax=0.075A

+VCC_EDP_BKLT_IN

TDC= 0.3948A Imax = 0.564A

+VCORE

TDC =10A Imax = 32A

+5VSB

+5V

+5V_FAN

Imax = 0.7A

+5V_SDXC

TDC= 0.63A Imax =0.9A

+5V_AUDIO

TDC=0.735A Imax = 1.05A

DMIC_3P3V

Imax = 0.02A

+5V_USBPWR

TDC= 0.63A Imax =0.9A

+5V_SL1

Imax =1.5A

+5V_KB_CONN

Imax =0.5A

+5V_TS

Imax = 0.0027A

+3P3VSB

Imax = 0.062A

+3P3V

Imax = 0.31A

+3P3V_SSD

Imax = 1.2A

+1P5V

TDC= 0.003A Imax = 0.003A

DP_3P3V_PWR_FUSE

Imax=0.5A

+3P3V_AUDIO

Imax =0.0313A

+3P3V_TS

TDC= 0.0094A

+3P3V_PANEL

Imax = 0.451A

+3P3V_WWAN

TDC= 1.05A Imax = 1.5A

+3P3V_SENSOR

Imax = 0.007375A

+3P3V_MUX

Imax = 0.0033A

S0

+3P3V_CAM

Imax =0.006A

S0

+3P3V_USB_CAM

Imax = 0.017A

S0

+1P1V_CAM

Imax = 0.61A

S0

+1P1V_USB_CAM

Imax = 0.014A

S0

+1P1V_PLLD_CAM

Imax = 0.0016A

S0

+2P5V_CAM

Imax = 0.001A

S0

+2P5V_PLL_CAM

Imax = 0.000168A

S0

+2P5V_MIPI_CAM_A

Imax = 0.00184A

S0

+2P5V_MIPI_CAM_B

Imax = 0.00184A

S0

+1P8V_VDD_CAM_A

Imax = 0.061A

S0

+1P8V_VDD_CAM_B

Imax = 0.061A

S0

+2P8V_CAM_A

Imax = 0.07A

S0

+2P8V_CAM_B

Imax = 0.07A

S0

+1P8V_CAM_A

Imax = 0.0441A

S0

+1P8V_CAM_B

Imax = 0.0441A

+1P2V_DUAL

TDC=4A Imax =5.71A

+V_VDDQ_VTT

Imax = 1A

+1P05V

TDC = 2.387A Imax = 3.41A

+1P05V_MODPHY

TDC= 1.29A Imax = 1.838A

+1P8V_DUAL

TDC=0.5A Imax = 0.717A

+1P8V_AUDIO

Imax = 0.005A

+1P1V_AUDIO

Imax =0.0189A

<Core Des ign>

<Core Des ign>

<Core Des ign>

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

1

POWER FLOW

POWER FLOW

POWER FLOW

Surface

Surface

Surface

6 76Monday, May 11, 201 5

6 76Monday, May 11, 201 5

6 76Monday, May 11, 201 5

1.90.2

1.90.2

1.90.2

Page 7

5

4

3

2

1

CPU Haswell ULT

+VCORE

+1P05V

+DDR_V

(+1P2V_DUAL)

D D

+1P05V

+1P05V_MODPHY

+1P5V

+3P3V

+3P3VSB

+3P3VA

-> 32A

-> 0.6A

-> 2.5A

-> 2.81A

-> 1.838A

-> 0.003A

-> 0.200A

-> 0.062A

-> 0.099A

(+3P3V)

+5V_SDXC

+3P3V_WWAN

DMIC_+3P3V/+3P3V_AUDIO

+5V_FAN

LPDDR3

+1P8V_DUAL

+1P2V_DUAL

+VTT_DDQ_VTT(0.6V)

C C

+3P3V

06Dec14 jks: NEEDS UPDATE

+3P3V_EC

-> 0.717A

-> 3.210A

-> 1A

-> 1.2A

-> 0.012A

mSATA(SSD)

EC

+3P3V

VCC_EDP_BKLT_IN

+3P3V_PANEL

+3P3VA

EC ROM

+3P3V_EC

+3P3VA

-> 0.005A

-> 0.00025A

+3P3V_TS

+5V_TS

Temp sensor(STTS751)

+3P3V_EC

B B

+1P1V_CAM

+1P1V_PLLD_CAM

+1P1V_USB_CAM

+1P8V_CAM

+1P8V_VDD_CAM

+2P5V_CAM

+2P5V_PLL_CAM

+2P5V_MIPI_CAM

+2P8V_CAM

+3P3V_CAM

A A

+3P3V_USB_CAM

-> 0.00025A

-> 0.609A

-> 0.0016A

-> 0.0137A

-> 0.0882A

-> 0.122A

-> 0.001A

-> 0.000168A

-> 0.00368A

-> 0.14A

-> 0.006A

-> 0.0169A

Camera

+3P3V_AUDIO

+5V_AUDIO

+1P8V_AUDIO

+3P3V_AUDIO

+1P1V_AUDIO

TPM(Infineon SLB9665 ESS2) Sensor uC(ATUC256L3U-Z3UR)

-> 0.1A

-> 0.9A

+3P3VA+3P3V_TPM

SDXC

+3P3V_HPD

+5V_SL1

WiFi&BT

-> 0.061A

SL1

->0.075A

-> 1.5A

-> 1.5A

BLADE

DMIC

+5V_KB_CONN

-> 0.5A

-> 0.02A

Hall effect sensor(BU52058GWZ-E2)

->0.0028A

Compass(MMC3416XMA)

->0.0012A

Acceleromte&Gyro(LSM330TR)

-> 0.0061A

-> 0.7A

UEFI_SPI_BIOS_ROM

-> 0.04A

-> 0.564A

FAN

+3P3VA

+3P3V_SENSOR

Panel

+3P3V_SENSOR

-> 0.273A

Authentication IC

(ECC108)

-> 0.005A

Touch Interface

-> 0.0094A

-> 0.0027A

-> 0.005A

+3P3V_SENSOR

+3P3V_MUX

+3P3V

ALC3264 CODEC

+5VUSBPWR

ALS(ISL29033IROZ-T7) FPC CON

-> 0.000075A

MUX

-> 0.033A

mini DP

-> 0.5A

USB 3.0 connector

-> 0.9A

-> 1.05A

-> 0.005A

Transceiver SN74AVCT245

+1P8V_EC

DSP (ES320)

-> 0.11A

-> 0.0063A

-> 0.0189A

+V_ALWAYS_ON

Battery Charger BQ24735

-> 0.003A

<Core Design>

<Core Design>

<Core Design>

POWER DISTRIBUTION

POWER DISTRIBUTION

Title:

Title:

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Title:

Engineer:

Engineer:

Engineer:

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

POWER DISTRIBUTION

Surface

Surface

Surface

7 76Monday, May 1 1, 2015

7 76Monday, May 1 1, 2015

7 76Monday, May 1 1, 2015

1

1.90.2

1.90.2

1.90.2

Page 8

5

4

3

2

1

S5 to S0 Power Sequence

SLP_SUS#

D D

+5VSB / +3P3VSB

RSMRST#

10mS

200mS

SUSWARN#

SUS_ACK#

SLP_A#(NC)

5mS

SLP_LAN#(NC)

SLP_S5#(NC)

PM_SUSC#

PM_SUSB#

+6V_12V

C C

30uS

PSU: <=20mS

+3P3V

+1P2V_DUAL

=500mS

+1P05V_CPUIO

+1P8V_DUAL

H_PWRGD assertion

06Dec14 jks: NEEDS UPDATE

VCCSA_VID

H_PWRGD must be stable (low) at this time

Recommended that +0P85VSA ramp after +1P05V_CPUIO has ramped to ensure VCCSA_VID[0] is stable

+0V85VSA

<5mS

CPU_VRON(NC)

VIDSCLK / VIDSOUT

B B

VIDALERT#

CPU SVID buffers are Hi-Z once VCCIO is

stable and VRM_PWRGD = 0

CPU SVID buffers are Hi-Z once VCCIO is

stable and VRM_PWRGD = 0

MISC ACK0/1...

<600uS

Set VID

slow packet sta

ACK0/1...

VCCSA_VID[0] FINAL

Typ 60uS

Get Reg

tus packet

S

<1u

ACK0/1...

Pay

loa

+0P85VSA FINAL

d

>400uS

: 100ms~500ms

PM_PCH_PWROK

PSU

1mS

CLK_EXP

Min 10 CLK_EXP

PM_DRAM_PWRGD

H_PWRGD

+VCORE

>1mS

<5u

S

<2mS

5mS

VRM_PWRGD

<5mS

A A

PLTRST#

<Core Design>

<Core Design>

<Core Design>

Title:

Title:

Title:

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

Engineer:

Engineer:

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

1~100mS

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

Surface

Surface

Surface

8 76Monday, May 11, 2015

8 76Monday, May 11, 2015

1

8 76Monday, May 11, 2015

1.90.2

1.90.2

1.90.2

Page 9

5

4

3

2

1

I2C & SMBUS Map

SML1_PCH_DATA

SML1

_PCH_CLK

Q3501

Q3504

PCH_I2C1_SDA_3V3

D D

S

M

PCH_

I2C1_SCL_3V3

R3001

R3003

TS_A_I2C_SDA_CON

TS_A_I2C_SCL_CON

Touch Connector

CON3001

0x60

Surrend

TEMP Sensor

U3901

0x4B

PCH

U1001

M

C C

0x4D

SH_I2C_SDA

SH_I

2C_SCL

Debug Connector

CON3302

SML3_EC_DATA

SML3

_EC_CLK

M

Skin

TEMP Sensor

U3902

0x3B

Skin

TEMP Sensor

U3903

0x3A

Skin

TEMP Sensor

U3501

SML0_EC_DATA

SML0_EC_CLK

S

I2C_SDA_MCU_R

R3122

R3124

M

B B

SAM

U310

5

I2C_SCL_MCU_R

ADUX1050

U3206

0x2D

ADUX6

I2C_SDA_MCU

I2C_S

R3229

R3230

R3285

R3287

CL_MCU

R3266

R3267

TEMP Sensor

U3211

R3210

R3211

R3212

R3213

MAG2_X_SDA

MAG2_X_SCL

0x3A

SML1_EC_DATA

SML1_EC_CLK

Accel & Gyro

U3202

0x68

EC

S

U3601

0x4E

M

R7032/L7005

R7033/L7006

PR6309

PR6310

0 ohm

CHG_SDA_A

CHG_SCL_A

MAG2_SCL_3V3

A A

0x28

U3207

0x2C

ADUX1050

ADUX7

R3286

R3288

MAG2_SDA_3V3

Magnetometer

U3203

0x30

EC_SMCLK_BAT

EC_S

MDATA_BAT

U3904

Charger

U6301

Battery

Connector

CON7001

0x4A

0x12

0x16

09. I2C MAP

09. I2C MAP

Title:

Title:

Title:

Engineer:

Engineer:

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

Engineer:

09. I2C MAP

Surface

Surface

Surface

9 76Monday, May 11, 2015

9 76Monday, May 11, 2015

1

9 76Monday, May 11, 2015

1.90.2

1.90.2

1.90.2

Page 10

5

4

3

2

1

+VCCSTG

R1008

1K

RES_0201_12mil

TPS0P35

SAR_INDICATION_1[31]

SAR_INDICATION_2[31]

+VCCST_CPU

H_PECI_R[36]

XDP_TP1001TPS0P35

TS_IRQ_3V3_N[30]

XDP_TP1002

R1021 0

RES_0201_12mil

R1022 49.9

R1023 49.9

RES_0201_12mil

R1002 499

RES_0201_12mil

C1008 47pDNP,CPU

CAP_0201_14mil

R1035 0 RES_0201_12mil

R1024 49.9

RES_0201_12mil

RES_0201_12mil

D D

C C

H_PROCHOT#[63,66]

R1037

RES_0402_16mil

EC_PROCHOT[36]

Q1001

SOT-VMT3_1p2xp8xp5_p4mm

RUM002N02GT2L

100

G

D

S

+VCCST_CPU

R1025 49.9

RES_0201_12mil

DNP,CPU

R1016

49.9

RES_0201_12mil

PM_THRMTRIP#[10]

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

TP_CATERR#_R

H_PROCHOT#_R

XDP_BPM0[18]

XDP_BPM1[18]

PROC_DETECT#

GPP_E3

GPP_E7

U1001D

SKL_

ULT_1356BGA_R1

bga1356_47x30_42x24x1p27mm-SKL

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

REV = JKS

Source Package = SKL_ULT_1356BGA_R1

TBL1001,CPU

CPU MISC

TBL1001

CPU MSPN Inte l PN

SKL_ULT

4 OF 20

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

i3 X904344-001 SKLU22i3

R1020

1K

RES_0201_12mil

H_THERMTRIP#[75]

B B

DDI Port 1: base port

DDI Port 2: SL1

+VCCIO

R1006

24.9

RES_0201_12mil

A A

5

R1018 0

RES_0201_12mil

DDI1_DATA0_DN[47]

DDI1_DATA0_DP[47]

DDI1_DATA1_DN[47]

DDI1_DATA1_DP[47]

DDI1_DATA2_DN[47]

DDI1_DATA2_DP[47]

DDI1_DATA3_DN[47]

DDI1_DATA3_DP[47]

DDI2_DATA0_DN[71]

DDI2_DATA0_DP[71]

DDI2_DATA1_DN[71]

DDI2_DATA1_DP[71]

DDI2_DATA2_DN[71]

DDI2_DATA2_DP[71]

DDI2_DATA3_DN[71]

DDI2_DATA3_DP[71]

DDPB_CTRL_CLK[46]

DDPB_CTRL_DATA[46]

DDPC_CTRL_CLK[46]

DDPC_CTRL_DATA[46]

PCH_CODEC_IRQ[40]

RTD3_CR_PWREN[64]

EDP_COMP

PM_THRMTRIP# [10]

E55

F55

E58

F58

F53

G53

F56

G56

C50

D50

C52

D52

A50

B50

D51

C51

L13

L12

INT. PD

INT

INT. PD

. PD

4

N7

N8

N11

N12

E52

U1001A

SKL_

ULT_1356BGA_R1

bga1356_47x30_42x24x1p27mm-SKL

DDI1_TXN[0]

DDI1_TXP[0]

DDI1_TXN[1]

DDI1_TXP[1]

DDI1_TXN[2]

DDI1_TXP[2]

DDI1_TXN[3]

DDI1_TXP[3]

DDI2_TXN[0]

DDI2_TXP[0]

DDI2_TXN[1]

DDI2_TXP[1]

DDI2_TXN[2]

DDI2_TXP[2]

DDI2_TXN[3]

DDI2_TXP[3]

GPP_E18/DDPB_CTRLCLK

GPP_E19/DDPB_CTRLDATA

GPP_E20/DDPC_CTRLCLK

GPP_E21/DDPC_CTRLDATA

GPP_E22/DDPD_CTRLCLK

GPP_E23/DDPD_CTRLDATA

EDP_RCOMP

REV = JKS

Source Package = SKL_ULT_1356BGA_R1

TBL1001,CPU

SKL_ULT

DDI

DISPLAY SIDEBANDS

1 OF 20

i5 X904343-001 SKLU22i5

i7 X904345-001 SKLU22i7

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EDP

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

3

EDP_TX0_DN [57]

EDP_TX0_DP [57]

EDP_TX1_DN [57]

EDP_TX1_DP [57]

EDP_TX2_DN [57]

EDP_TX2_DP [57]

EDP_TX3_DN [57]

EDP_TX3_DP [57]

EDP_AUX_DN [57]

EDP_AUX_DP [57]

DDPB_AUX_DN [46]

DDPB_AUX_DP [46]

DDPC_AUX_DN [46]

DDPC_AUX_DP [46]

L_BKLTEN [72]

L_BKLT_CTRL_IN [57]

EDP_VDD_EN [65]

eDP x 4

EDP_DISP_UTIL

R1032 100K

MTP1012 SP_TP_SMDp58mm

MTP1013 SP_TP_SMDp58mm

MTP1014 SP_TP_SMDp58mm

MTP1015 SP_TP_SMDp58mm

MTP1016 SP_TP_SMDp58mm

DNP,CPU

RES_0201_12mil

RES_0201_12mil

RES_0201_12mil

R1028 49.9

R1039

10K

R1017 100K

R1005 49.9

RES_0201_12mil

R1026 49.9

RES_0201_12mil

RES_0201_12mil

RES_0201_12mil

+3VSUS_ORG

R1004 49.9

R1027 49.9

RES_0201_12mil

R1033 1M

RES_0201_12mil

2

PLACE TP's on BOTTOM,

XDP_TCK [18]

XDP_TDI [18]

XDP_TDO [18]

XDP_TMS [18]

XDP_TRST#_BUF [18]

PLACE TP's on BOTTOM,

+VCCSTG

DNP,CPU

R1030 1K

RES_0201_12mil

R1038

10K

RES_0201_12mil

DDPB_DP_HPD [47]

SL1_DP_HPD [71]

EXT_SMI# [36]

EXT_SCI# [36]

EDP_HPD [57]

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

MTP1004 SP_TP_SMDp58mm

MTP1001 SP_TP_SMDp58mm

MTP1005 SP_TP_SMDp58mm

MTP1003 SP_TP_SMDp58mm

MTP1000 SP_TP_SMDp58mm

MTP1002 SP_TP_SMDp58mm

PCH_JTAG_TCK [18]

PCH_JTAG_TDI [18]

PCH_JTAG_TDO [18]

PCH_JTAG_TMS [18]

XDP_TRST# [18]

PCH_JTAGX [18]

R1029

49.9

RES_0201_12mil

DNP,CPU

R1019

0

RES_0201_12mil

SMI and SCI can be set to HIGH in S5 in EC code

and they need to set LOW before go to deep sleep

CPU(1)_MISC,JTAG,DDI,EDP

CPU(1)_MISC,JTAG,DDI,EDP

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

CPU(1)_MISC,JTAG,DDI,EDP

Surface

Surface

Surface

1.90.2

1.90.2

1.90.2

10 76Monday, May 11, 2015

10 76Monday, May 11, 2015

1

10 76Monday, May 11, 2015

Page 11

5

U1001B

SKL_U

LT_1356BGA_R1

bga1356_47x30_42x24x1p27mm-SKL

M_A_D[7:0][16]

M_A_D[15:8][16]

D D

M_A_D[39:32][16]

M_A_D[47:40][16]

M_B_D[7:0][17]

M_B_D[15:8][17]

C C

M_B_D[39:32][17]

M_B_D[47:40][17]

M_A_D0

M_A_D1

M_A_D2

M_A_D3

M_A_D4

M_A_D5

M_A_D6

M_A_D7

M_A_D8

M_A_D9

M_A_D10

M_A_D11

M_A_D12

M_A_D13

M_A_D14

M_A_D15

M_A_D32

M_A_D33

M_A_D34

M_A_D35

M_A_D36

M_A_D37

M_A_D38

M_A_D39

M_A_D40

M_A_D41

M_A_D42

M_A_D43

M_A_D44

M_A_D45

M_A_D46

M_A_D47

M_B_D0

M_B_D1

M_B_D2

M_B_D3

M_B_D4

M_B_D5

M_B_D6

M_B_D7

M_B_D8

M_B_D9

M_B_D10

M_B_D11

M_B_D12

M_B_D13

M_B_D14

M_B_D15

M_B_D32

M_B_D33

M_B_D34

M_B_D35

M_B_D36

M_B_D37

M_B_D38

M_B_D39

M_B_D40

M_B_D41

M_B_D42

M_B_D43

M_B_D44

M_B_D45

M_B_D46

M_B_D47

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_ DQ[32]

AW65

DDR0_DQ[17]/DDR0_ DQ[33]

AW63

DDR0_DQ[18]/DDR0_ DQ[34]

AY63

DDR0_DQ[19]/DDR0_ DQ[35]

BA65

DDR0_DQ[20]/DDR0_ DQ[36]

AY65

DDR0_DQ[21]/DDR0_ DQ[37]

BA63

DDR0_DQ[22]/DDR0_ DQ[38]

BB63

DDR0_DQ[23]/DDR0_ DQ[39]

BA61

DDR0_DQ[24]/DDR0_ DQ[40]

AW61

DDR0_DQ[25]/DDR0_ DQ[41]

BB59

DDR0_DQ[26]/DDR0_ DQ[42]

AW59

DDR0_DQ[27]/DDR0_ DQ[43]

BB61

DDR0_DQ[28]/DDR0_ DQ[44]

AY61

DDR0_DQ[29]/DDR0_ DQ[45]

BA59

DDR0_DQ[30]/DDR0_ DQ[46]

AY59

DDR0_DQ[31]/DDR0_ DQ[47]

AY39

DDR0_DQ[32]/DDR1_ DQ[0]

AW39

DDR0_DQ[33]/DDR1_ DQ[1]

AY37

DDR0_DQ[34]/DDR1_ DQ[2]

AW37

DDR0_DQ[35]/DDR1_ DQ[3]

BB39

DDR0_DQ[36]/DDR1_ DQ[4]

BA39

DDR0_DQ[37]/DDR1_ DQ[5]

BA37

DDR0_DQ[38]/DDR1_ DQ[6]

BB37

DDR0_DQ[39]/DDR1_ DQ[7]

AY35

DDR0_DQ[40]/DDR1_ DQ[8]

AW35

DDR0_DQ[41]/DDR1_ DQ[9]

AY33

DDR0_DQ[42]/DDR1_ DQ[10]

AW33

DDR0_DQ[43]/DDR1_ DQ[11]

BB35

DDR0_DQ[44]/DDR1_ DQ[12]

BA35

DDR0_DQ[45]/DDR1_ DQ[13]

BA33

DDR0_DQ[46]/DDR1_ DQ[14]

BB33

DDR0_DQ[47]/DDR1_ DQ[15]

AY31

DDR0_DQ[48]/DDR1_ DQ[32]

AW31

DDR0_DQ[49]/DDR1_ DQ[33]

AY29

DDR0_DQ[50]/DDR1_ DQ[34]

AW29

DDR0_DQ[51]/DDR1_ DQ[35]

BB31

DDR0_DQ[52]/DDR1_ DQ[36]

BA31

DDR0_DQ[53]/DDR1_ DQ[37]

BA29

DDR0_DQ[54]/DDR1_ DQ[38]

BB29

DDR0_DQ[55]/DDR1_ DQ[39]

AY27

DDR0_DQ[56]/DDR1_ DQ[40]

AW27

DDR0_DQ[57]/DDR1_ DQ[41]

AY25

DDR0_DQ[58]/DDR1_ DQ[42]

AW25

DDR0_DQ[59]/DDR1_ DQ[43]

BB27

DDR0_DQ[60]/DDR1_ DQ[44]

BA27

DDR0_DQ[61]/DDR1_ DQ[45]

BA25

DDR0_DQ[62]/DDR1_ DQ[46]

BB25

DDR0_DQ[63]/DDR1_ DQ[47]

REV = JKS

Source Package = SKL_ULT_1356BGA_R1

BUILD-OPT = TBL1001,CPU

SKL_ULT

DDR0_MA[5]/DDR0 _CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0 _CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0 _CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0 _CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0 _CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_ CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR 0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR 0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR 0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR 0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR 0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CA B[1]/DDR0_MA[15]

DDR0_WE#/DDR0 _CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CA B[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_ CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0 _CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_ CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR 0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0 _CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0 _CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_ DQSN[4]

DDR0_DQSP[2]/DDR0_ DQSP[4]

DDR0_DQSN[3]/DDR0_ DQSN[5]

DDR0_DQSP[3]/DDR0_ DQSP[5]

DDR0_DQSN[4]/DDR1_ DQSN[0]

DDR0_DQSP[4]/DDR1_ DQSP[0]

DDR0_DQSN[5]/DDR1_ DQSN[1]

DDR0_DQSP[5]/DDR1_ DQSP[1]

DDR0_DQSN[6]/DDR1_ DQSN[4]

DDR0_DQSP[6]/DDR1_ DQSP[4]

DDR0_DQSN[7]/DDR1_ DQSN[5]

DDR0_DQSP[7]/DDR1_ DQSP[5]

DDR CH - A

2 OF 20

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR_VTT_CNTL

4

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

M_A_DIM0_CLK#0 [16]

M_A_DIM0_CLK0 [16]

M_A_DIM0_CLK#1 [16]

M_A_DIM0_CLK1 [16]

M_A_DIM0_CKE0 [16]

M_A_DIM0_CKE1 [16]

M_A_DIM0_CKE2 [16]

M_A_DIM0_CKE3 [16]

M_A_DIM0_CS#0 [16]

M_A_DIM0_CS#1 [16]

M_A_DIM0_ODT0 [16]

M_A_CAA0

M_A_CAA1

M_A_CAA2

M_A_CAA3

M_A_CAA4

M_A_CAA5

M_A_CAA6

M_A_CAA7

M_A_CAA8

M_A_CAA9

M_A_CAB0

M_A_CAB1

M_A_CAB2

M_A_CAB3

M_A_CAB4

M_A_CAB5

M_A_CAB6

M_A_CAB7

M_A_CAB8

M_A_CAB9

M_A_DQS#0 [16]

M_A_DQS0 [16]

M_A_DQS#1 [16]

M_A_DQS1 [16]

M_A_DQS#4 [16]

M_A_DQS4 [16]

M_A_DQS#5 [16]

M_A_DQS5 [16]

M_B_DQS#0 [17]

M_B_DQS#1 [17]

M_B_DQS1 [17]

M_B_DQS#4 [17]

M_B_DQS4 [17]

M_B_DQS#5 [17]

M_B_DQS5 [17]

DDR0_ALERT#

DIMM_VREF_CA [19]

DIMM0_VREF_DQ [19]

DIMM1_VREF_DQ [19]

M_A_CAA[9:0] [16]

M_A_CAB[9:0] [16]

R1135 0

RES_0201_12mil

M_A_D[23:16][16]

M_A_D[31:24][16]

M_A_D[55:48][16]

M_A_D[63:56][16]

M_B_D[23:16][17]

M_B_D[31:24][17]

M_B_D[55:48][17]

M_B_D[63:56][17]

3

M_A_D16

M_A_D17

M_A_D18

M_A_D19

M_A_D20

M_A_D21

M_A_D22

M_A_D23

M_A_D24

M_A_D25

M_A_D26

M_A_D27

M_A_D28

M_A_D29

M_A_D30

M_A_D31

M_A_D48

M_A_D49

M_A_D50

M_A_D51

M_A_D52

M_A_D53

M_A_D54

M_A_D55

M_A_D56

M_A_D57

M_A_D58

M_A_D59

M_A_D60

M_A_D61

M_A_D62

M_A_D63

M_B_D16

M_B_D17

M_B_D18

M_B_D19

M_B_D20

M_B_D21

M_B_D22

M_B_D23

M_B_D24

M_B_D25

M_B_D26

M_B_D27

M_B_D28

M_B_D29

M_B_D30

M_B_D31

M_B_D48

M_B_D49

M_B_D50

M_B_D51

M_B_D52

M_B_D53

M_B_D54

M_B_D55

M_B_D56

M_B_D57

M_B_D58

M_B_D59

M_B_D60

M_B_D61

M_B_D62

M_B_D63

U1001C

SKL_U

LT_1356BGA_R1

bga1356_47x30_42x24x1p27mm-SKL

AF65

DDR1_DQ[0]/DDR0_DQ[ 16]

AF64

DDR1_DQ[1]/DDR0_DQ[ 17]

AK65

DDR1_DQ[2]/DDR0_DQ[ 18]

AK64

DDR1_DQ[3]/DDR0_DQ[ 19]

AF66

DDR1_DQ[4]/DDR0_DQ[ 20]

AF67

DDR1_DQ[5]/DDR0_DQ[ 21]

AK67

DDR1_DQ[6]/DDR0_DQ[ 22]

AK66

DDR1_DQ[7]/DDR0_DQ[ 23]

AF70

DDR1_DQ[8]/DDR0_DQ[ 24]

AF68

DDR1_DQ[9]/DDR0_DQ[ 25]

AH71

DDR1_DQ[10]/DDR0_ DQ[26]

AH68

DDR1_DQ[11]/DDR0_ DQ[27]

AF71

DDR1_DQ[12]/DDR0_ DQ[28]

AF69

DDR1_DQ[13]/DDR0_ DQ[29]

AH70

DDR1_DQ[14]/DDR0_ DQ[30]

AH69

DDR1_DQ[15]/DDR0_ DQ[31]

AT66

DDR1_DQ[16]/DDR0_ DQ[48]

AU66

DDR1_DQ[17]/DDR0_ DQ[49]

AP65

DDR1_DQ[18]/DDR0_ DQ[50]

AN65

DDR1_DQ[19]/DDR0_ DQ[51]

AN66

DDR1_DQ[20]/DDR0_ DQ[52]

AP66

DDR1_DQ[21]/DDR0_ DQ[53]

AT65

DDR1_DQ[22]/DDR0_ DQ[54]

AU65

DDR1_DQ[23]/DDR0_ DQ[55]

AT61

DDR1_DQ[24]/DDR0_ DQ[56]

AU61

DDR1_DQ[25]/DDR0_ DQ[57]

AP60

DDR1_DQ[26]/DDR0_ DQ[58]

AN60

DDR1_DQ[27]/DDR0_ DQ[59]

AN61

DDR1_DQ[28]/DDR0_ DQ[60]

AP61

DDR1_DQ[29]/DDR0_ DQ[61]

AT60

DDR1_DQ[30]/DDR0_ DQ[62]

AU60

DDR1_DQ[31]/DDR0_ DQ[63]

AU40

DDR1_DQ[32]/DDR1_ DQ[16]

AT40

DDR1_DQ[33]/DDR1_ DQ[17]

AT37

DDR1_DQ[34]/DDR1_ DQ[18]

AU37

DDR1_DQ[35]/DDR1_ DQ[19]

AR40

DDR1_DQ[36]/DDR1_ DQ[20]

AP40

DDR1_DQ[37]/DDR1_ DQ[21]

AP37

DDR1_DQ[38]/DDR1_ DQ[22]

AR37

DDR1_DQ[39]/DDR1_ DQ[23]

AT33

DDR1_DQ[40]/DDR1_ DQ[24]

AU33

DDR1_DQ[41]/DDR1_ DQ[25]

AU30

DDR1_DQ[42]/DDR1_ DQ[26]

AT30

DDR1_DQ[43]/DDR1_ DQ[27]

AR33

DDR1_DQ[44]/DDR1_ DQ[28]

AP33

DDR1_DQ[45]/DDR1_ DQ[29]

AR30

DDR1_DQ[46]/DDR1_ DQ[30]

AP30

DDR1_DQ[47]/DDR1_ DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

REV = JKS

BUILD-OPT = TBL1001,CPU

e Package = SKL_ULT_1356BGA_R1

Sourc

SKL_ULT

DDR1_MA[5]/DDR1 _CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1 _CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1 _CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1 _CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1 _CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_ CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR 1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR 1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR 1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR 1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR 1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CA B[1]/DDR1_MA[15]

DDR1_WE#/DDR1 _CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CA B[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_ CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1 _CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_ CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR 1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1 _CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1 _CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_ DQSN[2]

DDR1_DQSP[0]/DDR0_ DQSP[2]

DDR1_DQSN[1]/DDR0_ DQSN[3]

DDR1_DQSP[1]/DDR0_ DQSP[3]

DDR1_DQSN[2]/DDR0_ DQSN[6]

DDR1_DQSP[2]/DDR0_ DQSP[6]

DDR1_DQSN[3]/DDR0_ DQSN[7]

DDR1_DQSP[3]/DDR0_ DQSP[7]

DDR1_DQSN[4]/DDR1_ DQSN[2]

DDR1_DQSP[4]/DDR1_ DQSP[2]

DDR1_DQSN[5]/DDR1_ DQSN[3]

DDR1_DQSP[5]/DDR1_ DQSP[3]

DRAM_RESET#

DDR_RCOMP[0]

DDR CH - B

3 OF 20

DDR_RCOMP[1]

DDR_RCOMP[2]

2

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_CAA0

M_B_CAA1

M_B_CAA2

M_B_CAA3

M_B_CAA4

M_B_CAA5

M_B_CAA6

M_B_CAA7

M_B_CAA8

M_B_CAA9

M_B_CAB0

M_B_CAB1

M_B_CAB2

M_B_CAB3

M_B_CAB4

M_B_CAB5

M_B_CAB6

M_B_CAB7

M_B_CAB8

M_B_CAB9

M_A_DQS#2 [16]

M_A_DQS2 [16]

M_A_DQS#3 [16]

M_A_DQS3 [16]

M_A_DQS#6 [16]

M_A_DQS6 [16]

M_A_DQS#7 [16]

M_A_DQS7 [16]

M_B_DQS#2 [17]

M_B_DQS2 [17]

M_B_DQS#3 [17]M_B_DQS0 [17]

M_B_DQS3 [17]

M_B_DQS#6 [17]

M_B_DQS6 [17]

M_B_DQS#7 [17]

M_B_DQS7 [17]

DDR1_ALERT#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

M_B_DIM0_CLK#0 [17]

M_B_DIM0_CLK#1 [17]

M_B_DIM0_CLK0 [17]

M_B_DIM0_CLK1 [17]

M_B_DIM0_CKE0 [17]

M_B_DIM0_CKE1 [17]

M_B_DIM0_CKE2 [17]

M_B_DIM0_CKE3 [17]

M_B_DIM0_CS#0 [17]

M_B_DIM0_CS#1 [17]

M_B_DIM0_ODT0 [17]

M_B_CAA[9:0] [17]

M_B_CAB[9:0] [17]

R1136 0

RES_0201_12mil

SM_DRAMRST#

R11112001% RES_0201_12mil

R113480.6 RES_0201_12MIL

R11121621%

RES_0402_16mil

1

DNP,CPU

R1118 1M

RES_0201_12mil

+1P2V_DUAL

+3P3VSB +3P3V+1P2V_DUAL

U1102

74AUP1G07GX

sot1226_p8xp8xp35_p48mm

B B

A A

DDR_PG_CTRL_S

DNP,CPU

R1117

10K

RES_0201_12mil

1

VCC

A2Y

NC

GND

5

4

3

C1101

0.1u

cap_0201_14mil

EV1.9

CHG MSPN

6.3V

DNP,CPU

R1114

220K

res_0201_12mil

DNP,CPU

R1113

2M

RES_0201_12mil

R1115

4.99K

RES_0201_12mil

DDR_PG_CTRL [60]

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

CPU(2)_LPDDR3

CPU(2)_LPDDR3

CPU(2)_LPDDR3

Surface

Surface

Surface

1

1.90.2

1.90.2

11 76Monday, May 11, 2015

11 76Monday, May 11, 2015

11 76Monday, May 11, 2015

1.90.2

Page 12

+1P2V_DUAL

5

4

3

2

1

4V

C13017 22u

D D

6.3V

C1241 10u

CAP_0402_28mil

R1201 0

RES_0402_16mil

C C

B B

4V

cap_0603_40mil

C13018 22u

6.3V

C1240 10u

CAP_0402_28mil

DNP,CPU

R1202 0

RES_0402_16mil

4V

cap_0603_40mil

cap_0603_40mil

C13019 22u

Place on secondary side,

underneath the package

6.3V

C1239 10u

C13020 10u

6.3V

C1238 10u

cap_0402_0p65mm

CAP_0402_28mil

6.3V

DNP,CPU

C1245 1u

CAP_0201_14mil

+VCCPLL_OC

Place on secondary side,

underneath the package

CAP_0402_28mil

4V

4V

DNP,CPU

C1237 10u

+VCCST_CPU

C1246

6.3V

1u

CAP_0402_22mil

4V

DNP,CPU

C1236 10u

cap_0402_0p65mm

6.3V

DNP,CPU

C1244 1u

cap_0402_0p65mm

from 1VSB, control SLP_S4 (S3 rail)

+VCCSTG

Place on secondary side,

6.3V

DNP,CPU

C1243 1u

CAP_0201_14mil

DNP,CPU

C1247 1u

underneath the package

6.3V

DNP,CPU

C1242 1u

CAP_0201_14mil

6.3V

CAP_0402_22mil

6.3V

DNP,CPU

C1232 1u

CAP_0201_14mil

C1248

1u

CAP_0402_22mil

CAP_0201_14mil

VDDQC

+VCCST_CPU

6.3V

C1249

1u

CAP_0402_22mil

+VCC_CORE

Place on secondary side,

underneath the package

+VCCEDRAM

C1228

10u

4V

cap_0402_0p65mm

A A

5

C1252

6.3V

1u

CAP_0201_14mil

C1254

6.3V

1u

CAP_0201_14mil

C1253

6.3V

1u

CAP_0201_14mil

C1255

6.3V

1u

CAP_0201_14mil

+VCCEOPIO

C1231

10u

4V

cap_0402_0p65mm

Place on secondary side,

rneath the package

unde

C1250

6.3V

1u

CAP_0201_14mil

C1256

6.3V

1u

CAP_0201_14mil

CAP_0201_14mil

C1230

10u

4V

cap_0402_0p65mm

C1251

6.3V

+1P8V

1u

VCCOPC_SENSE[58]

VCCOPIO_SENSE[58]

4

U1001N

Source Package = SKL_ULT_1356BGA_R1

BUILD-OPT = TBL1001,CPU

SKL_U

LT_1356BGA_R1

bga1356_47x30_42x24x1p27mm-SKL

AU23

VDDQ_AU23

AU28

VDDQ_AU28

AU35

VDDQ_AU35

AU42

VDDQ_AU42

BB23

VDDQ_BB23

BB32

VDDQ_BB32

BB41

VDDQ_BB41

BB47

VDDQ_BB47

BB51

VDDQ_BB51

AM40

VDDQC

A18

VCCST

A22

VCCSTG_A22

AL23

VCCPLL_OC

K20

VCCPLL_K20

K21

VCCPLL_K21

6.3V

REV = JKS

U1001L

SKL_U

bga13

A30

VCC_A30

A34

VCC_A34

A39

VCC_A39

A44

VCC_A44

AK33

VCC_AK33

AK35

VCC_AK35

AK37

VCC_AK37

AK38

VCC_AK38

AK40

VCC_AK40

AL33

VCC_AL33

AL37

VCC_AL37

AL40

VCC_AL40

AM32

VCC_AM32

AM33

VCC_AM33

AM35

VCC_AM35

AM37

VCC_AM37

AM38

VCC_AM38

G30

VCC_G30

K32

RSVD_K32

AK32

RSVD_AK32

AB62

VCCOPC_AB62

P62

VCCOPC_P62

V62

VCCOPC_V62

H63

VCC_OPC_1P8_H63

G61

VCC_OPC_1P8_G61

AC63

VCCOPC_SENSE

AE63

VSSOPC_SENSE

AE62

VCCEOPIO

AG62

VCCEOPIO

AL63

VCCEOPIO_SENSE

AJ62

VSSEOPIO_SENSE

REV = JKS

BUILD-OPT = TBL1001,CPU

Source Package = SKL_ULT_1356BGA_R1

SKL_ULT

CPU POWER 3 OF 4

14 OF 20

LT_1356BGA_R1

56_47x30_42x24x1p27mm-SKL

SKL_ULT

CPU POWER 1 OF 4

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

12 OF 20

3

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

Place on secondary side,

underneath the package

4V

DNP,CPU

C1262 10u

4V

DNP,CPU

C1261 10u

cap_0402_0p65mm

cap_0402_0p65mm

6.3V

DNP,CPU

C1259 1u

Place on secondary side, underneath the package

6.3V

C1273 1u

VCCIO_SENSE [56]

VSSSA_SENSE [66]

VCCSA_SENSE [66]

+VCC_CORE

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

6.3V

CAP_0201_14mil

C1274 1u

CAP_0201_14mil

C1275 1u

VCC_CORE_SENSE [66]

VSS_CORE_SENSE [66]

H_CPU_SVIDALERT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

+VCCSTG

+VCCSTG is control by SLP_S0,

but it can overwrite by XDP, that

means it need power for XDP intrafece

6.3V

CAP_0201_14mil

6.3V

DNP,CPU

C1258 1u

CAP_0201_14mil

6.3V

C1268 1u

CAP_0201_14mil

C1281

10u

cap_0402_0p65mm

EV1.9

was:

6.3V

DNP,CPU

CAP_0201_14mil

C1257 1u

6.3V

C1269 1u

CAP_0201_14mil

4V

6.3V

DNP,CPU

CAP_0201_14mil

C1260 1u

6.3V

C1267 1u

CAP_0201_14mil

C1282

10u

cap_0402_0p65mm

CAP_0201_14mil

C1265 1u

6.3V

C1271 1u

CAP_0201_14mil

4V

X867508-004

R1216 220 res_0201_12mil

R1209 0 RES_0201_12mil

R1207 0 RES_0201_12mil

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Date: Sheet of

Date: Sheet of

2

Dat

+VCCIO

6.3V

6.3V

C1266 1u

CAP_0402_22mil

C1283

10u

4V

cap_0402_0p65mm

Microsoft

Microsoft

Microsoft

B

B

B

e: Sheet of

6.3V

CAP_0402_22mil

C1263 1u

4V

C1272 10u

cap_0402_0p65mm

+VCCST_CPU

res_0201_12mil

R1215 56

U -- EV 1.90

U -- EV 1.90

U -- EV 1.90

6.3V

C1264 1u

CAP_0402_22mil

CAP_0402_22mil

4V

C1270 10u

C1284

10u

cap_0402_0p65mm

R1212 100

cap_0402_0p65mm

4V

RES_0201_12mil

Title:

Title:

Title:

Engineer:

Engineer:

Engineer:

C1277 10u

4V

4V

C1276 10u

cap_0402_0p65mm

C1286

10u

cap_0402_0p65mm

VIDALERT# [66]

VIDSCLK [66]

VIDSOUT [66]

CPU(3)_SKL POWER1

CPU(3)_SKL POWER1

CPU(3)_SKL POWER1

Surface

Surface

Surface

4V

C1278 10u

cap_0402_0p65mm

4V

1

cap_0402_0p65mm

+VCCSA

12 76Monday, May 11, 2015

12 76Monday, May 11, 2015

12 76Monday, May 11, 2015

+VCCSA

4V

C1279 10u

C1285

10u

cap_0402_0p65mm

4V

C1280 10u

cap_0402_0p65mm

4V

cap_0402_0p65mm

1.90.2

1.90.2

1.90.2

Page 13

5

U1001M

SKL_

ULT_1356BGA_R1

+VCCGT +VCCGT

D D

C C

VCCGT_SENSE[66]

VSSGT_SENSE[66]

+VCC_CORE

C1315

10u

cap_0402_0p65mm

C13179

10u

cap_0402_0p65mm

C13188

B B

10u

cap_0402_0p65mm

Place on secondary side, underneath the package

4V

4V

4V

C1314

10u

4V

cap_0402_0p65mm

C13182

10u

4V

cap_0402_0p65mm

C13191

10u

4V

cap_0402_0p65mm

C1317

10u

cap_0402_0p65mm

C13180

10u

cap_0402_0p65mm

C13189

10u

cap_0402_0p65mm

bga1356_47x30_42x24x1p27mm-SKL

SKL_ULT

CPU POWER 2 OF 4

A48

VCCGT

A53

VCCGT

A58

VCCGT

A62

VCCGT

A66

VCCGT

AA63

VCCGT

AA64

VCCGT

AA66

VCCGT

AA67

VCCGT

AA69

VCCGT

AA70

VCCGT

AA71

VCCGT

AC64

VCCGT

AC65

VCCGT

AC66

VCCGT

AC67

VCCGT

AC68

VCCGT

AC69

VCCGT

AC70

VCCGT

AC71

VCCGT

J43

VCCGT

J45

VCCGT

J46

VCCGT

J48

VCCGT

J50

VCCGT

J52

VCCGT

J53

VCCGT

J55

VCCGT

J56

VCCGT

J58

VCCGT

J60

VCCGT

K48

VCCGT

K50

VCCGT

K52

VCCGT

K53

VCCGT

K55

VCCGT

K56

VCCGT

K58

VCCGT

K60

VCCGT

L62

VCCGT

L63

VCCGT

L64

VCCGT

L65

VCCGT

L66

VCCGT

L67

VCCGT

L68

VCCGT

L69

VCCGT

L70

VCCGT

L71

VCCGT

M62

VCCGT

N63

VCCGT

N64

VCCGT

N66

VCCGT

N67

VCCGT

N69

VCCGT

J70

VCCGT_SENSE

J69

VSSGT_SENSE

REV = JKS

Source Package = SKL_ULT_1356BGA_R1

D-OPT = TBL1001,CPU

BUIL

C1316

10u

4V

4V

4V

4V

cap_0402_0p65mm

C13184

10u

4V

cap_0402_0p65mm

C13193

10u

4V

cap_0402_0p65mm

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

13 OF 20

C1310

10u

4V

cap_0402_0p65mm

C13178

10u

4V

cap_0402_0p65mm

C13187

10u

4V

cap_0402_0p65mm

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

C1311

10u

cap_0402_0p65mm

C13183

10u

cap_0402_0p65mm

C13192

10u

cap_0402_0p65mm

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

4V

4V

4V

4

+VCCGT

C1312

10u

4V

cap_0402_0p65mm

C13181

10u

4V

cap_0402_0p65mm

C13190

10u

4V

cap_0402_0p65mm

C1313

10u

4V

cap_0402_0p65mm

C13185

10u

4V

cap_0402_0p65mm

C13194

10u

4V

cap_0402_0p65mm

C1318

4V

10u

cap_0402_0p65mm

C13186

10u

4V

cap_0402_0p65mm

C13195

10u

4V

cap_0402_0p65mm

+VCCGT

3

+VCCGT

U23E,CPU

C1390

10u

cap_0402_0p65mm

U23

C13101

22u

cap_0603_40mil

C1355

10u

4V

cap_0402_0p65mm

C1361

6.3V

1u

CAP_0201_14mil

C1366

6.3V

1u

CAP_0201_14mil

4V

,CPU

DNP,CPU

DNP

C13124 10u

cap_0402_0p65mm

6.3V

DNP,CPU

DNP,CPU

C13144 1u

CAP_0201_14mil

C1371

47u

cap_0805_36mil

C1382

22u

cap_0603_38mil

2

THIS IS PLACE ON VCCGTX pins (they are connected to +VCCGT)

Place on secondary side, underneath the package

only for 23e

U23E,CPU

C1391

10u

4V

E,CPU

4V

4V

cap_0402_0p65mm

onl

y for 23e

E,CPU

U23

C1376

22u

4V

cap_0603_40mil

Place on secondary side, underneath the package

C1353

10u

4V

cap_0402_0p65mm

C1360

6.3V

1u

CAP_0201_14mil

C1367

6.3V

1u

CAP_0201_14mil

4V

4V

DNP,CPU

C13127 10u

C13126 10u

cap_0402_0p65mm

Place on secondary side, underneath the package

6.3V

6.3V

DNP,CPU

C13147 1u

C13146 1u

CAP_0201_14mil

C1373

47u

6.3V

cap_0805_36mil

C1381

22u

6.3V

cap_0603_38mil

C13125 10u

C13145 1u

6.3V

6.3V

4V

DNP,CPU

cap_0402_0p65mm

6.3V

DNP,CPU

CAP_0201_14mil

C1352

10u

4V

cap_0402_0p65mm

C1357

1u

CAP_0201_14mil

C1364

1u

CAP_0201_14mil

4V

DNP,CPU

C13128 10u

cap_0402_0p65mm

cap_0402_0p65mm

6.3V

DNP,CPU

C13148 1u

CAP_0201_14mil

CAP_0201_14mil

C1372

47u

cap_0805_36mil

C1384

22u

cap_0603_38mil

U23E,CPU

C1389

10u

4V

cap_0402_0p65mm

E,CPU

U23

C1397

22u

4V

cap_0603_40mil

C1351

10u

cap_0402_0p65mm

6.3V

6.3V

4V

DNP,CPU

DNP,CPU

C13129 10u

C13130 10u

cap_0402_0p65mm

6.3V

DNP,CPU

DNP,CPU

C13149 1u

C13177 1u

CAP_0201_14mil

6.3V

6.3V

U23E,CPU

C1393

10u

cap_0402_0p65mm

E,CPU

U23

C1398

22u

cap_0603_40mil

4V

C1359

6.3V

1u

CAP_0201_14mil

C1365

6.3V

1u

CAP_0201_14mil

4V

4V

DNP,CPU

C13131 10u

cap_0402_0p65mm

6.3V

6.3V

DNP,CPU

C13151 1u

CAP_0201_14mil

C1374

47u

6.3V

cap_0805_36mil

C1383

22u

6.3V

cap_0603_38mil

4V

4V

C1350

10u

cap_0402_0p65mm

4V

DNP,CPU

C13132 10u

cap_0402_0p65mm

6.3V

DNP,CPU

C13152 1u

CAP_0201_14mil

U23E,CPU

C1392

10u

4V

cap_0402_0p65mm

E,CPU

U23

C1399

22u

4V

cap_0603_40mil

4V

C1349

6.3V

1u

CAP_0201_14mil

C1363

6.3V

1u

CAP_0201_14mil

4V

DNP,CPU

C13133 10u

cap_0402_0p65mm

6.3V

DNP,CPU

C13153 1u

CAP_0201_14mil

C1375

47u

6.3V

cap_0805_36mil

C1377

22u

6.3V

cap_0603_38mil

C1358

10u

4V

cap_0402_0p65mm

DNP,CPU

C13134 10u

cap_0402_0p65mm

DNP,CPU

C13154 1u

CAP_0201_14mil

C1378

22u

cap_0603_38mil

U23E,CPU

C1394

10u

4V

cap_0402_0p65mm

E,CPU

U23

C1308

22u

4V

cap_0603_40mil

C1354

10u

4V

cap_0402_0p65mm

C1356

6.3V

1u

CAP_0201_14mil

C1362

6.3V

1u

CAP_0201_14mil

4V

4V

DNP,CPU

C13135 10u

cap_0402_0p65mm

cap_0402_0p65mm

6.3V

6.3V

DNP,CPU

C13155 1u

CAP_0201_14mil

CAP_0201_14mil

6.3V

DNP,CPU

DNP,CPU

U23E,CPU

C1395

10u

4V

cap_0402_0p65mm

E,CPU

U23

C13100

22u

4V

cap_0603_40mil

C1368

10u

cap_0402_0p65mm

C13196

6.3V

1u

CAP_0201_14mil

C13197

6.3V

1u

CAP_0201_14mil

4V

DNP,CPU

C13137 10u

C13136 10u

cap_0402_0p65mm

6.3V

DNP,CPU

C13156 1u

C13157 1u

CAP_0201_14mil

C1379

22u

6.3V

cap_0603_38mil

4V

4V

DNP,CPU

C13138 10u

cap_0402_0p65mm

6.3V

DNP,CPU

C13158 1u

CAP_0201_14mil

U23E,CPU

C1396

10u

4V

cap_0402_0p65mm

E,CPU

U23

C13102

22u

4V

cap_0603_40mil

C1369

10u

4V

cap_0402_0p65mm

4V

4V

DNP,CPU

C13139 10u

cap_0402_0p65mm

cap_0402_0p65mm

6.3V

6.3V

DNP,CPU

C13159 1u

CAP_0201_14mil

CAP_0201_14mil

EV19

: 0402

WAS

EV1.9

was:X867508-004

C1370

10u

4V

cap_0402_0p65mm

4V

4V

DNP,CPU

DNP,CPU

DNP,CPU

C13140 10u

cap_0402_0p65mm

6.3V

DNP,CPU

C13160 1u

CAP_0201_14mil

C13142 10u

C13141 10u

cap_0402_0p65mm

6.3V

DNP,CPU

DNP,CPU

C13161 1u

C13162 1u

CAP_0201_14mil

1

4V

DNP,CPU

cap_0402_0p65mm

6.3V

DNP,CPU

CAP_0201_14mil

EV1.9

was:X867508-004

C13122

10u

4V

cap_0402_0p65mm

4V

EV1.9

was:X867508-003

C13143 10u

cap_0402_0p65mm

6.3V

C13163 1u

CAP_0201_14mil

C13123

10u

4V

cap_0402_0p65mm

C1328

10u

4V

cap_0402_0p65mm

C1334

6.3V

1u

CAP_0201_14mil

C1306

6.3V

1u

CAP_0201_14mil

C13108

6.3V

1u

CAP_0201_14mil

C13115

6.3V

1u

CAP_0201_14mil

A A

C13121

6.3V

1u

CAP_0201_14mil

C1327

10u

4V C13165

cap_0402_0p65mm

C1335

6.3V

1u

CAP_0201_14mil

C1307

6.3V

1u

CAP_0201_14mil

C1322

6.3V

1u

CAP_0201_14mil

C13109

6.3V

1u

CAP_0201_14mil

C13116

6.3V

1u

CAP_0201_14mil

C1326

10u

4V

cap_0402_0p65mm

C1332

6.3V

1u

CAP_0201_14mil

C1304

6.3V

1u

CAP_0201_14mil

C13104

6.3V

1u

CAP_0201_14mil

C13111

6.3V

1u

CAP_0201_14mil

C13119

6.3V

1u

CAP_0201_14mil

C1325

10u

4V

cap_0402_0p65mm

C1333

6.3V

1u

CAP_0201_14mil

C1305

6.3V

1u

CAP_0201_14mil

C13103

6.3V

1u

CAP_0201_14mil

C13110

6.3V

1u

CAP_0201_14mil

C13117

6.3V

1u

CAP_0201_14mil

C1324

10u

4V

cap_0402_0p65mm

C1323

6.3V

1u

CAP_0201_14mil

C1302

6.3V

1u

CAP_0201_14mil

C13106

6.3V

1u

CAP_0201_14mil

C13113

6.3V

1u

CAP_0201_14mil

C13120

6.3V

1u

CAP_0201_14mil

C1331

10u

4V

cap_0402_0p65mm

C1330

6.3V

1u

CAP_0201_14mil

C1303

6.3V

1u

CAP_0201_14mil

C13105

6.3V

1u

CAP_0201_14mil

C13112

6.3V

1u

CAP_0201_14mil

C13118

6.3V

1u

CAP_0201_14mil

C1329

4V

10u

cap_0402_0p65mm

C1301

6.3V

1u

CAP_0201_14mil

C1309

6.3V

1u

CAP_0201_14mil

C13107

6.3V

1u

CAP_0201_14mil

C13114

6.3V

1u

CAP_0201_14mil

EV1.9

was:X867508-004

C1300

6.3V

1u

CAP_0201_14mil

+VCC_CORE

4V

,CPU

DNP

C13167 10u

C1338

10u

4V

cap_0402_0p65mm

C1341

47u

6.3V

cap_0603_40mil

47u

6.3V

cap_0805_36mil

C1380

22u

6.3V

cap_0603_38mil

4V

DNP,CPU

C13168 10u

cap_0402_0p65mm

C1337

10u

4V

cap_0402_0p65mm

C1342

47u

6.3V

cap_0603_40mil

DNP,CPU

cap_0402_0p65mm

C13166

47u

6.3V

cap_0805_36mil

C1385

22u

6.3V

cap_0603_38mil

4V

DNP,CPU

C13170 10u

C13169 10u

cap_0402_0p65mm

C1336

10u

4V

cap_0402_0p65mm

C1343

47u

6.3V

cap_0603_40mil

C13164

47u

cap_0805_36mil

C1386

22u

cap_0603_38mil

4V

DNP,CPU

cap_0402_0p65mm

C1320

10u

cap_0402_0p65mm

C1344

47u

cap_0603_40mil

C13171 10u

6.3V

6.3V

4V

4V

6.3V

cap_0402_0p65mm

C1387

22u

cap_0603_38mil

4V

DNP,CPU

C13172 10u

cap_0402_0p65mm

6.3V

4V

DNP,CPU

C13173 10u

cap_0402_0p65mm

C1321

10u

4V

cap_0402_0p65mm

C1345

47u

6.3V

cap_0603_40mil

C1388

22u

6.3V

cap_0603_38mil

4V

DNP,CPU

C13174 10u

cap_0402_0p65mm

C1319

10u

4V

cap_0402_0p65mm

C1346

47u

6.3V

cap_0603_40mil

EV19

WAS: 0402

4V

DNP,CPU

C13175 10u

cap_0402_0p65mm

4V

DNP,CPU

C13176 10u

cap_0402_0p65mm

C1339

10u

4V

cap_0402_0p65mm

C1347

47u

6.3V

cap_0603_40mil

C1340

10u

4V

cap_0402_0p65mm

C1348

47u

6.3V

cap_0603_40mil

EV1.9

was:X867508-002

EV1.9

was:X867508-001

EV1.9 was:0805

CPU(4)_SKL_POWER2

CPU(4)_SKL_POWER2

Microsoft

Microsoft

Microsoft

Size Project Name Rev

Size Project Name Rev