Page 1

Service Manual

Model : KP275/KP275c

Service Manual

KP275/KP275c

Date: November, 2008 / Issue 1.0

Internal Use Only

Page 2

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

- 3 -

1. INTRODUCTION ...............................5

1.1 Purpose .................................................. 5

1.2 Regulatory Information............................ 5

1.3 Abbreviations .......................................... 7

2. PERFORMANCE...............................8

2.1 Supporting Standard................................8

2.2 Main Parts: Solution.................................8

2.3 HW Feature..............................................9

2.4 HW Spec................................................11

3. TECHNICAL BRIEF ........................15

3.1 Functional Block Diagram......................15

3.2 Baseband Processor Introduction..........16

3.3 Power management IC ..........................28

3.4 Power ON/OFF ......................................35

3.5 SIM Interface..........................................36

3.6 MICRO SD connector ............................37

3.7 Memory..................................................38

3.8 LCD Display...........................................39

3.9 Keypad switching & scanning ................40

3.10 keypad back-light illumination..............41

3.11 LCD back-light illumination ..................43

3.12 Battery voltage monitor........................44

3.13 Audio....................................................45

3.14 BLUETOOTH.......................................48

3.15 FM Radio .............................................51

3.16 CAMERA connector.............................54

3.17 18PIN Interface connector ...................55

3.18 General Description .............................56

3.19 GSM Part .............................................59

3.20 WCDMA Part .......................................64

3.21 GSM Power Amplifier Module..............66

3.22 WCDMA Band1/5Power Amplifier

Module .................................................67

3.23 WCDMA Band1/5 Low Noise Amplifier68

3.24 WCDMA Band 1/5 Duplexer ................69

4. TROUBLE SHOOTING ...................70

4.1 Trouble shooting test setup....................70

4.2 Power on trouble....................................71

4.3 Charging Trouble ...................................74

4.4 UBS Trouble ..........................................77

4.5 SIM Detect Trouble................................79

4.6 Number Key Sense Trouble...................82

4.7 Multi Key sense Trouble ........................84

4.8 Keypad backlight Trouble ......................86

4.9 Micro SD Trouble...................................88

4.10 Audio Trouble.......................................90

4.11 Microphone Trouble.............................94

4.12 Camera Trouble...................................98

4.13 Main LCD Trouble..............................103

4.14 Bluetooth Trouble...............................105

4.15 FM Radio ...........................................108

4.16 RF Component...................................112

4.17 RF SIGNAL PATH .............................113

4.18 Trouble Shooting of GSM Part ..........114

4.19 Trouble Shooting of WCDMA Part.....122

5. DOWNLOAD.....................................128

5.1 USB Driver Installation to Download....128

5.2 Device Detection..................................130

5.3 USB Port Mapping ...............................131

5.4 Configuration to Download...................132

5.5 Nexus setting .......................................134

6. CIRCUIT DIAGRAM ......................135

7. BGM PIN MAP...............................143

8. PCB LAYOUT................................149

9. RF Calibration ..............................155

9.1 Test Equipment Setup .........................155

9.2 Calibration Step ...................................155

10. EXPLODED VIEW &

REPLACEMENT PART LIST ......161

10.1 Exploded View ...................................161

10.2 Replacement Parts ............................163

10.3 Accessory ..........................................184

Table Of Contents

Page 3

- 4 -

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Page 4

- 5 -

1. INTRODUCTION

1.1 Purpose

This manual provides the information necessary to repair, calibration, description and download the

features of the KP275C.

1.2 Regulatory Information

A. Security

Toll fraud, the unauthorized use of telecommunications system by an unauthorized part (for example,

persons other than your company’s employees, agents, subcontractors, or person working on your

company’s behalf) can result in substantial additional charges for your telecommunications services.

System users are responsible for the security of own system.

There are may be risks of toll fraud associated with your telecommunications system. System users

are responsible for programming and configuring the equipment to prevent unauthorized use. LGE

does not warrant that this product is immune from the above case but will prevent unauthorized use of

common carrier telecommunication service of facilities accessed through or connected to it. LGE will

not be responsible for any charges that result from such unauthorized use.

B. Incidence of Harm

If a telephone company determines that the equipment provided to customer is faulty and possibly

causing harm or interruption in service to the telephone network, it should disconnect telephone

service until repair can be done. A telephone company may temporarily disconnect service as long as

repair is not done.

C. Changes in Service

A local telephone company may make changes in its communications facilities or procedure. If these

changes could reasonably be expected to affect the use of the KP275C or compatibility with the net

work, the telephone company is required to give advanced written notice to the user, allowing the user

to take appropriate steps to maintain telephone service.

D. Maintenance Limitations

Maintenance limitations on the KP275C must be performed only by the LGE or its authorized agent.

The user may not make any changes and/or repairs expect as specifically noted in this manual.

Therefore,note that unauthorized alternations or repair may affect the regulatory status of the system

and may void any remaining warranty.

1. INTRODUCTION

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Page 5

- 6 -

1. INTRODUCTION

E. Notice of Radiated Emissions

This model complies with rules regarding radiation and radio frequency emission as defined by local

regulatory agencies. In accordance with these agencies, you may be required to provide information

such as the following to the end user.

F. Pictures

The pictures in this manual are for illustrative purposes only; your actual hardware may look slightly

different.

G. Interference and Attenuation

An KP275C may interfere with sensitive laboratory equipment, medical equipment, etc. Interference

from unsuppressed engines or electric motors may cause problems.

H. Electrostatic Sensitive Devices

ATTENTION

Boards, which contain Electrostatic Sensitive Device (ESD), are indicated by the Following

information is ESD handling:

• Service personnel should ground themselves by using a wrist strap when exchange system boards.

• When repairs are made to a system board, they should spread the floor with anti-static mat which is

also grounded.

• Use a suitable, grounded soldering iron.

• Keep sensitive parts in these protective packages until these are used.

• When returning system boards or parts like EEPROM to the factory, use the protective package as

described.

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Page 6

- 7 -

1. INTRODUCTION

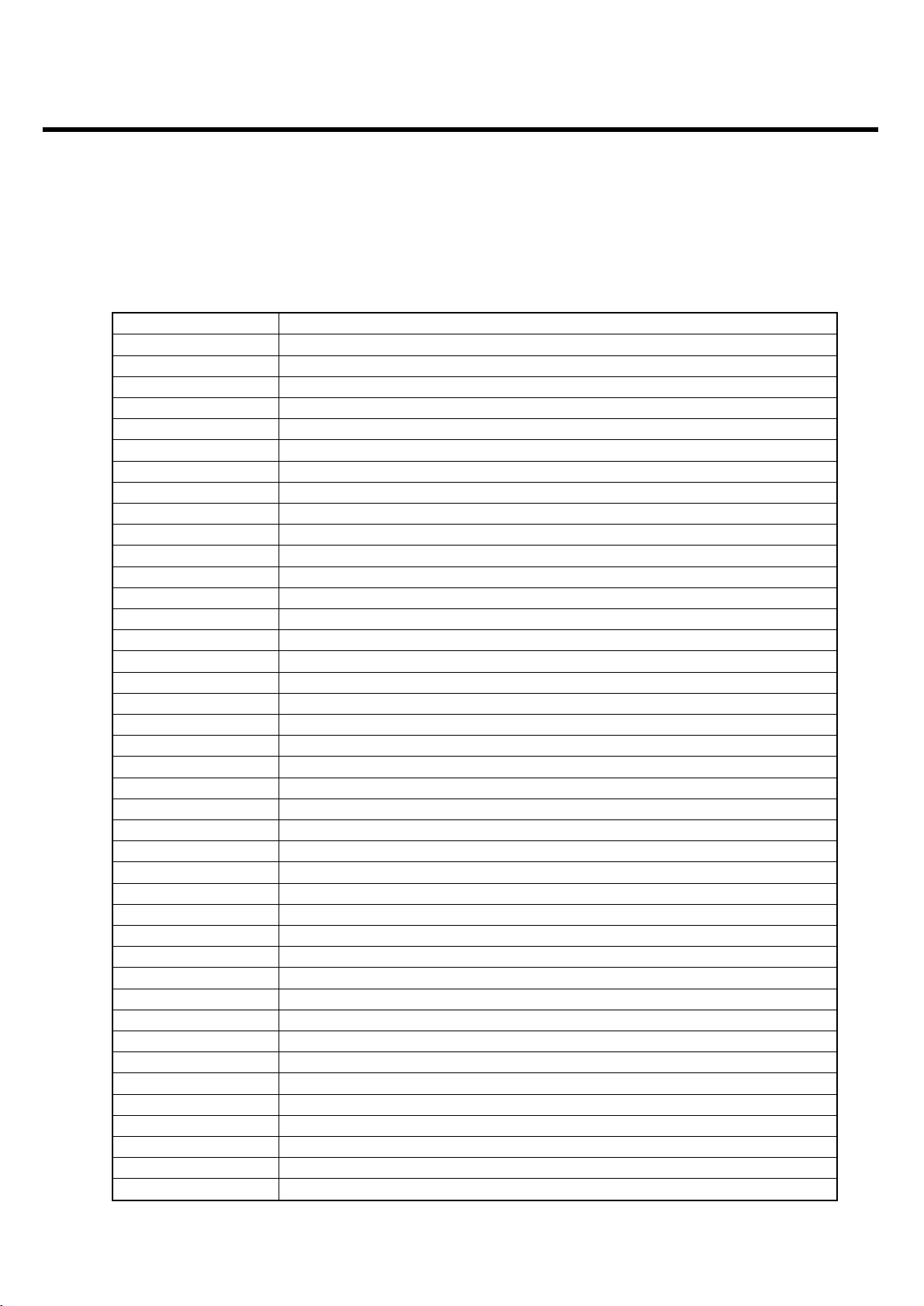

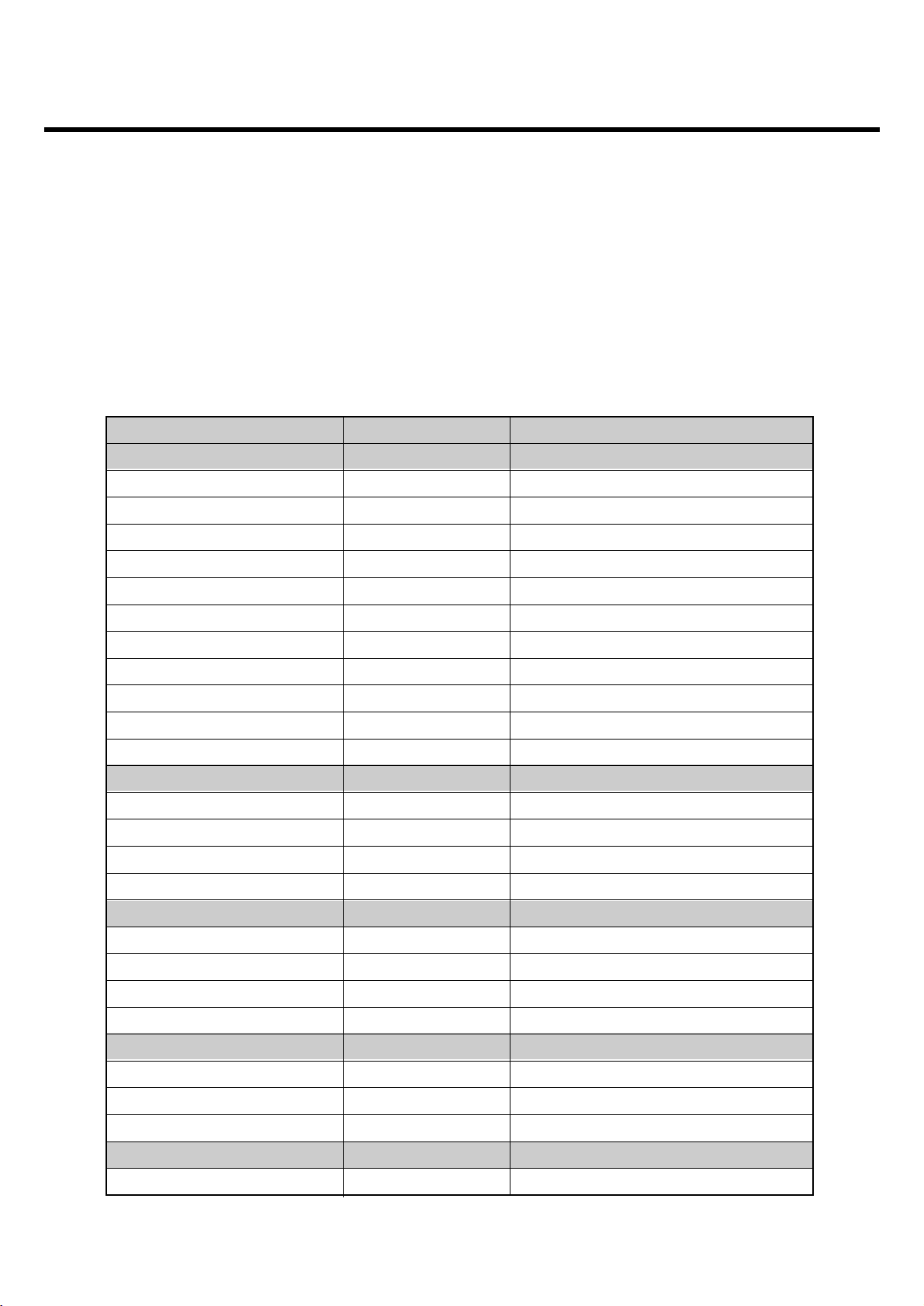

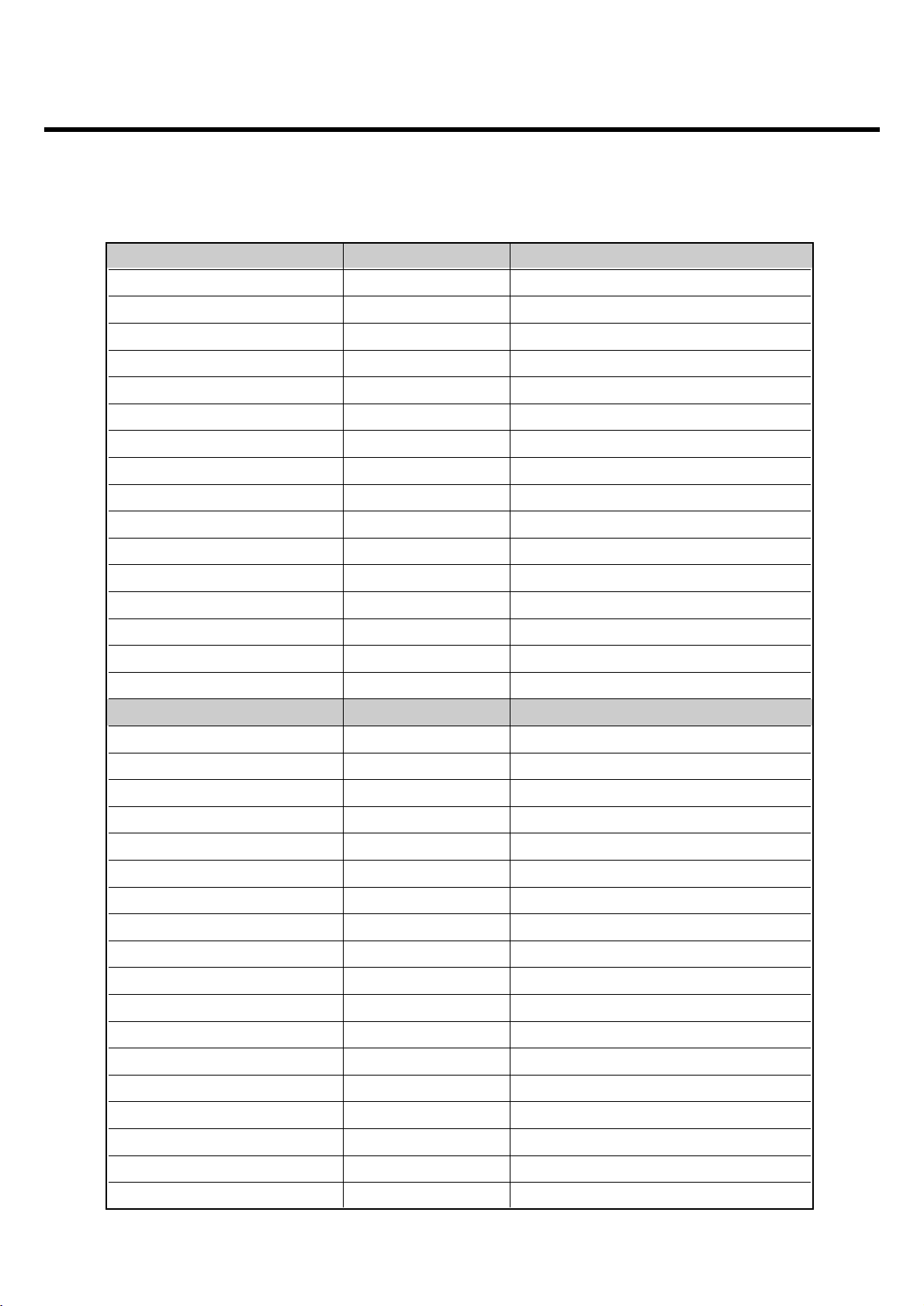

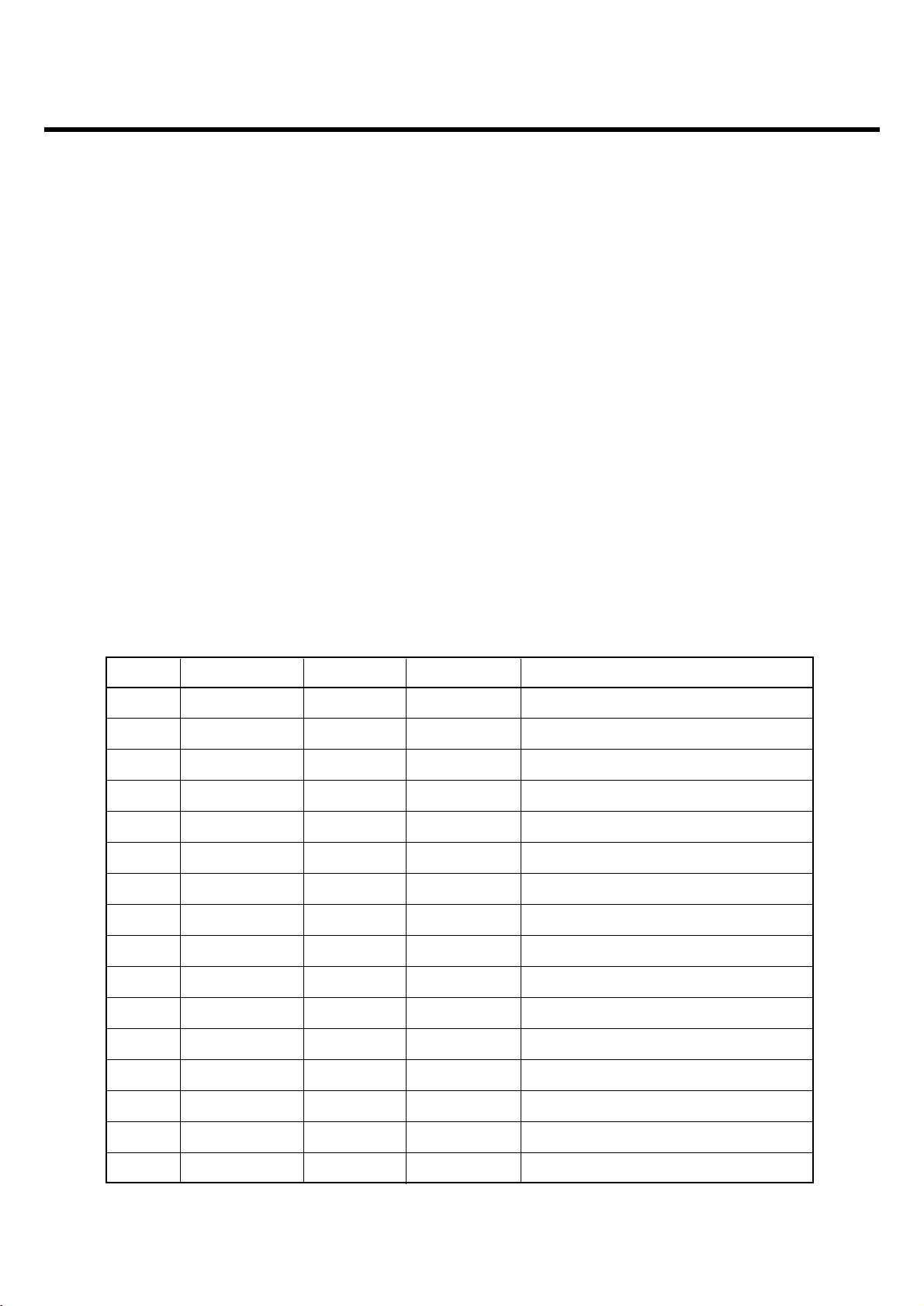

1.3 Abbreviations

For the purposes of this manual, following abbreviations apply:

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

APC Automatic Power Control

BB Baseband

BER Bit Error Ratio

CC-CV Constant Current - Constant Voltage

DAC Digital to Analog Converter

DCS Digital Communication System

dBm dB relative to 1 milliwatt

DSP Digital Signal Processing

EEPROM Electrical Erasable Programmable Read-Only Memory

EL Electroluminescence

ESD Electrostatic Discharge

FPCB Flexible Printed Circuit Board

GMSK Gaussian Minimum Shift Keying

GPIB General Purpose Interface Bus

GSM Global System for Mobile Communications

IPUI International Portable User Identity

IF Intermediate Frequency

LCD Liquid Crystal Display

LDO Low Drop Output

LED Light Emitting Diode

OPLL Offset Phase Locked Loop

PAM Power Amplifier Module

PCB Printed Circuit Board

PGA Programmable Gain Amplifier

PLL Phase Locked Loop

PSTN Public Switched Telephone Network

RF Radio Frequency

RLR Receiving Loudness Rating

RMS Root Mean Square

RTC Real Time Clock

FEM Front End Module

SIM Subscriber Identity Module

SLR Sending Loudness Rating

SRAM Static Random Access Memory

STMR Side Tone Masking Rating

TA Travel Adapter

TDD Time Division Duplex

TDMA Time Division Multiple Access

UART Universal Asynchronous Receiver/Transmitter

VCO Voltage Controlled Oscillator

VCTCXO Voltage Control Temperature Compensated Crystal Oscillator

WAP Wireless Application Protocol

Page 7

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

2. PERFORMANCE

- 8 -

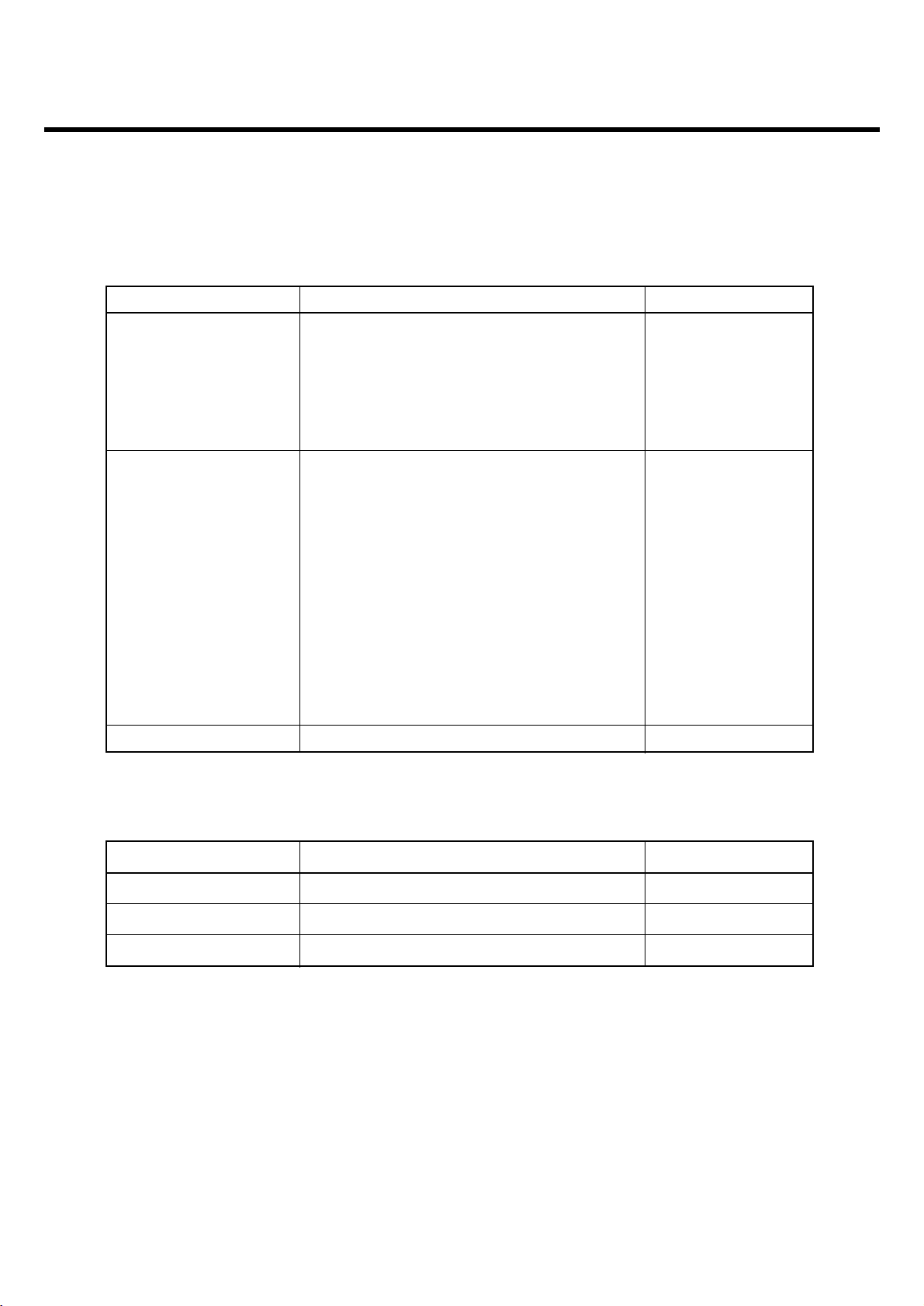

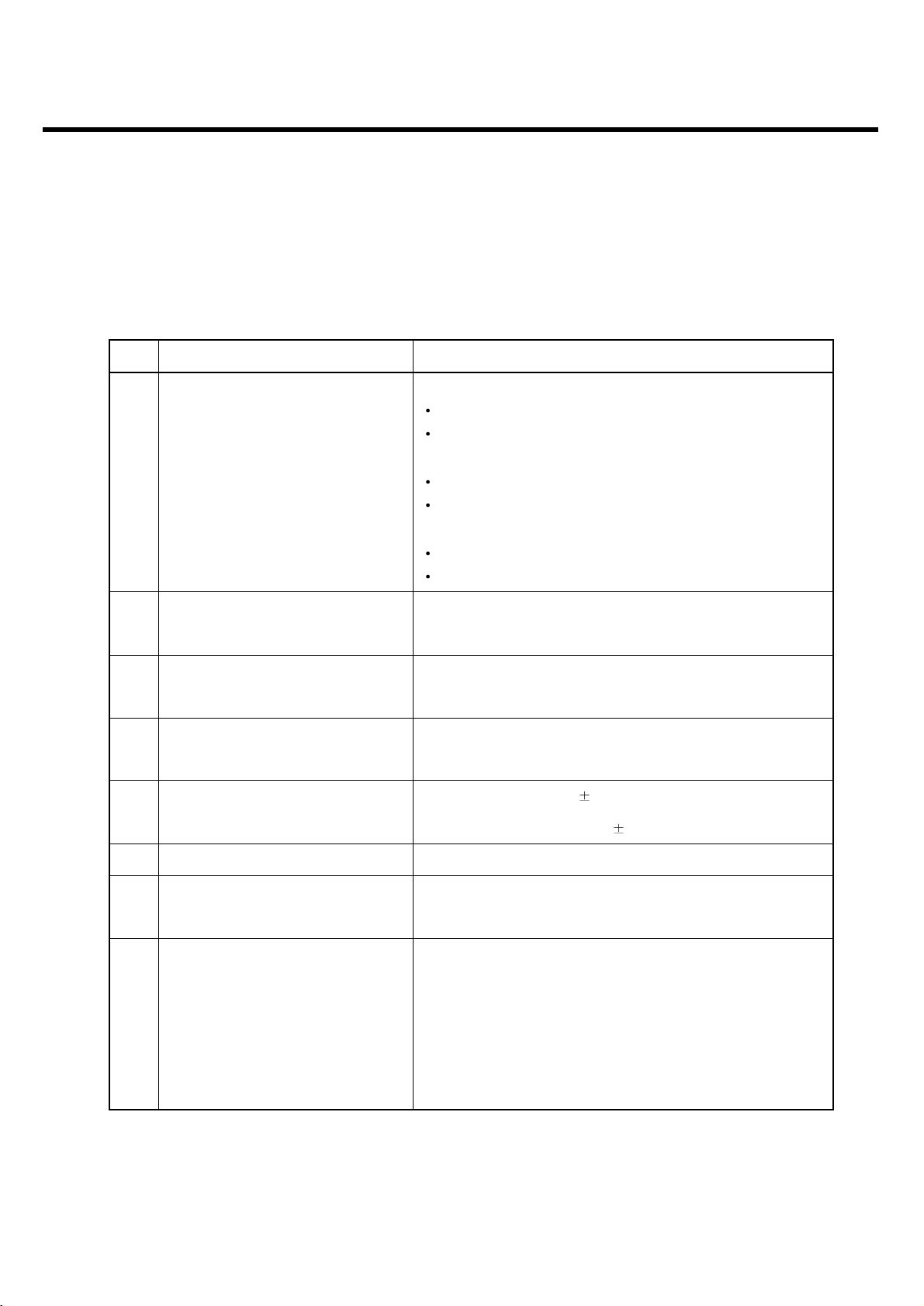

2.1 Supporting Standard

2.2 Main Parts: Solution

Item Feature Comment

Supporting Standard WCDMA850 / WCDMA 2100

EGSM900 / DCS1800 / PCS1900

seamless handover

Phase 2+(include AMR)

SIM Toolkit : Class 1, 2, 3, A-E

Frequency Range EGSM900 TX : 880 - 915MHz

EGSM900 RX : 925 - 960 MHz

DCS1800 TX : 1710 - 1785 MHz

DCS1800 RX : 1805 - 1880 MHz

PCS1900 TX : 1850 - 1910 MHz

PCS1900 RX : 1930 - 1990 MHz

WCDMA850 TX : 824 - 849MHz

WCDMA850 RX : 869 - 894MHz

WCDMA2100 TX : 1920 - 1980 MHz

WCDMA2100 RX : 2110 - 2170 MHz

Application Standard WAP 2.0, JAVA 2.0

Item Part name Comment

Digital Baseband PMB8868 (Infineon)

Analog Baseband PMB8868 (Infineon)

RF chip PMB6952 (Infineon)

Page 8

- 9 -

2. PERFORMANCE

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

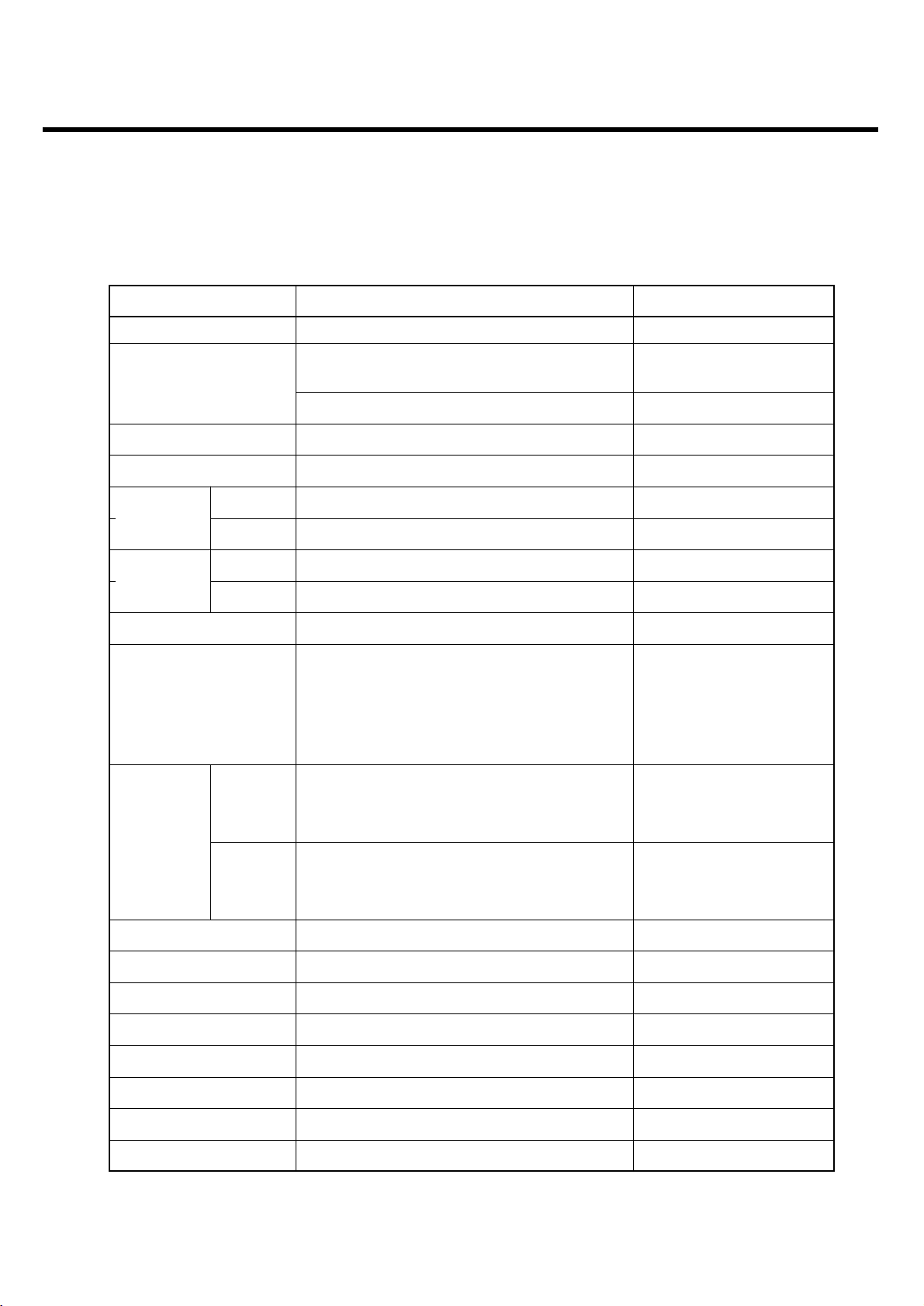

2.3 HW Feature

Item Feature Comment

Form Factor Slide type

Battery 1)Capacity

Standard : Li-Ion, 900mAh

2) Packaging Type : Soft Pack

Size 98 x 48 x 16.9 mm

Weight 98 g With Battery

GSM 280 hours @paging period 5

WCDMA 200hours @DRX=128frames

GSM 160min @ Power Level 7

WCDMA 160min @Tx=12dBm

Charging time 3 hours @power OFF/900mAh

RX sensitivity GSM850 : -105 dBm

DCS1800 : -105 dBm

PCS1900 : -105 dBm

WCDMA 850 : -106.7dBm

WCDMA2100 : -106.7 dBm

GSM850 : 33 dBm Class4 (EGSM900)

DCS1800 : 30 dBm Class1(DCS)

PCS1900 : 30 dBm Class1(PCS)

EGSM900 : 27 dBm E2 (EGSM900)

DCS1800 : 26 dBm E2 (DCS)

PCS1900 : 26 dBm E2 (PCS)

GPRS compatibility GPRS Class 12

EDGE compatibility EDGE Class 12

Display Main LCD(2”, 176 x 220)/TFT

Built-in Camera 1.3 Mega pixel, VT CAM(VGA)

ANT Main : Internal Fixed Type

System connector 18 Pin

Ear Phone Jack 18pin, 4 Pole, Stereo

PC synchronization Yes

TX output

power

GSM/

GPRS

EDGE

Stand-by

time

Talk time

Page 9

- 10 -

2. PERFORMANCE

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Item Feature Comment

Speech coding FR, EFR, HR, AMR

Vibrator Built in Vibrator

Blue Tooth V1.2, A2DP

Voice Recording Yes

Speaker Phone mode Yes

Support

Travel Adapter Yes

CDROM Yes

Stereo Headset Yes

Data Cable No

T-Flash Yes Not Equipped

Page 10

- 11 -

2. PERFORMANCE

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

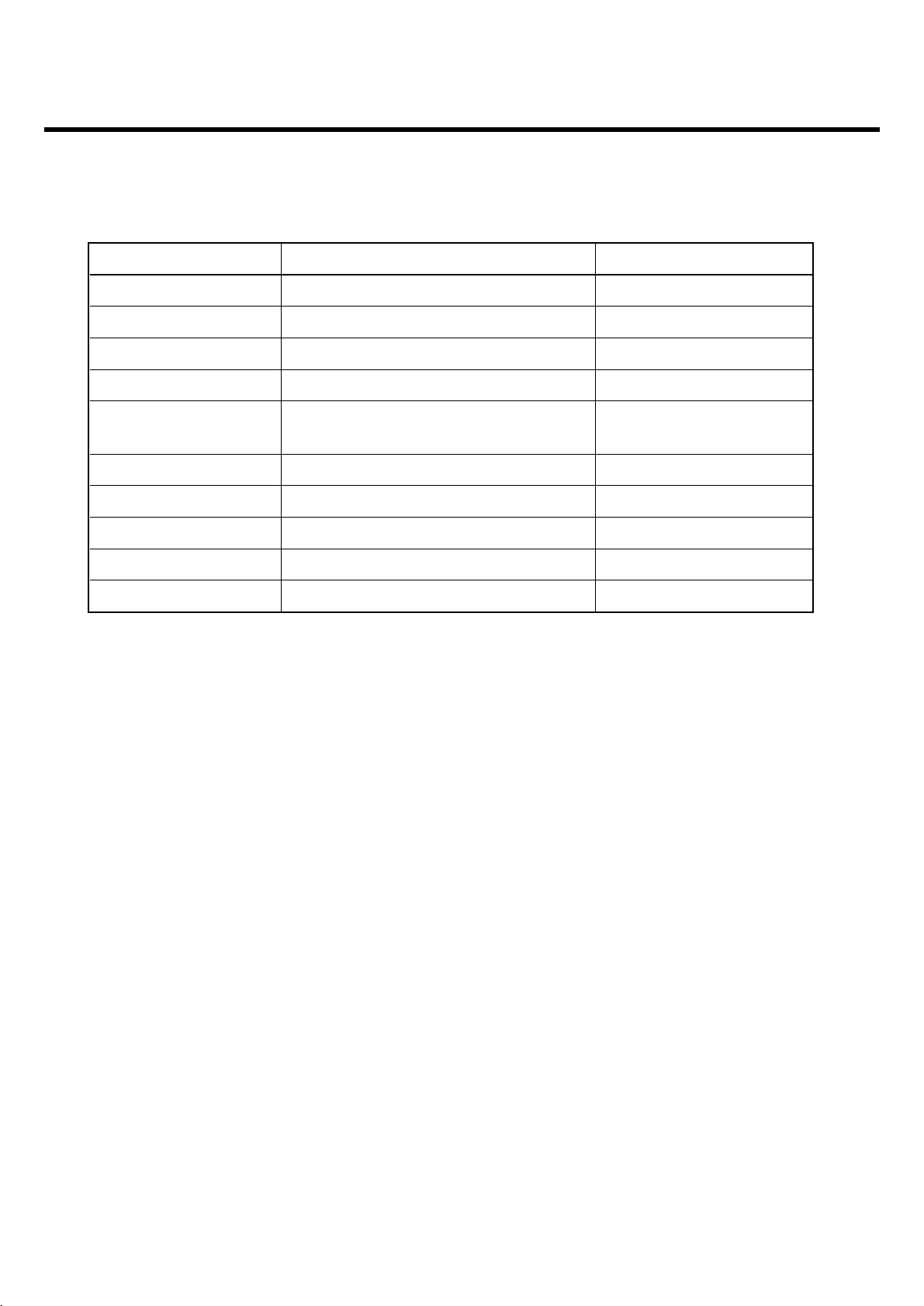

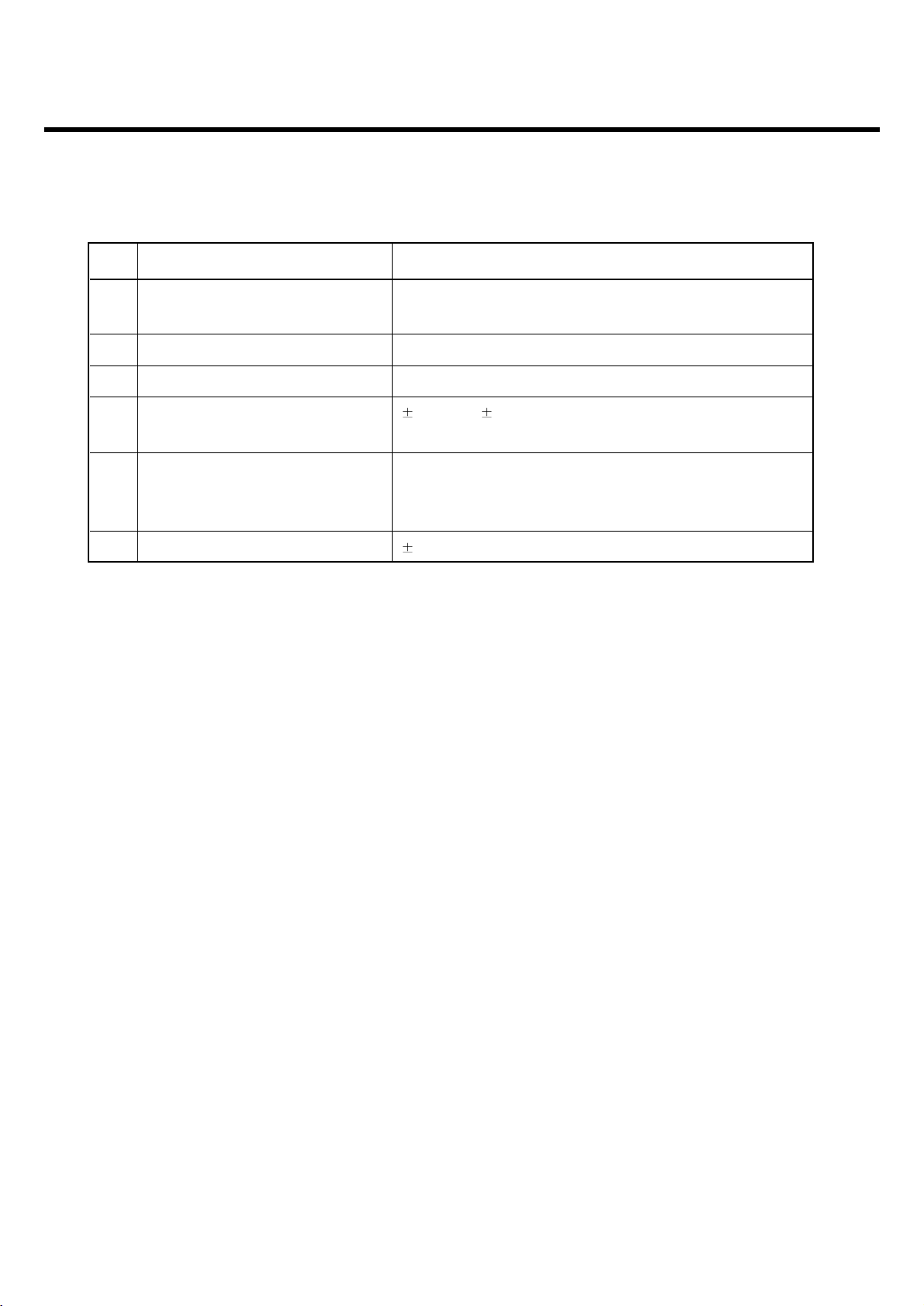

2.4 HW Spec.

2.4.1 GSM Transmitter/Receiver spec.

Item Specification

1Frequency Band EGSM900

TX : 880 - 915MHz

RX : 925 - 960 MHz

DCS1800

TX : 1710 - 1785 MHz

RX : 1805 - 1880 MHz

PCS1900

TX : 1850 - 1910 MHz

RX : 1930 - 1990 MHz

2 Phase Error Rms : 5°

Peak : 20°

3 Frequency Error GSM : 0.1 ppm

DCS/PCS : 0.1 ppm

4 EMC(Radiated Spurious GSM/DCS : < -28dBm

Emission Disturbance)

5 Transmitter Output power and GSM : 5dBm - 33dBm 3dB

Burst Timing DCS/PCS : 0dBm - 30dBm 3dB

6 Burst Timing < 3.69us

7 Spectrum due to modulation out 200kHz : -36dBm

to less than 1800kHz offset 600kHz : -51dBm/-56dBm

8 Spectrum due to modulation out GSM

to larger than 1800kHz offset to 1800-3000kHz :< -63dBc(-46dBm)

the edge of the transmit band 3000kHz-6000kHz : <-65dBc(-46dBm)

6000kHz < : < -71dBc(-46dBm)

DCS

1800-3000kHz :< -65dBc(-51dBm)

6000kHz < : < -73dBc(-51dBm)

Page 11

- 12 -

2. PERFORMANCE

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Item Specification

9 Spectrum due to switching 400kHz : -19dBm/-22dBm(5/0), -23dBm

transient 600kHz : -21dBm/-24dBm(5/0), -26dBm

10 Reference Sensitivity - TCH/FS Class II(RBER) : -105dBm(2.439%)

11 Usable receiver input level range 0.012(-15 - -40dBm)

12 Intermodulation rejection - 800kHz, 1600kHz : -98dBm / -96dBm (2.439%)

Speech channels

13 AM Suppression -98dBm/-96dBm (2.439%)

- GSM : -31dBm

- DCS : -29dBm

14 Timing Advance 0.5T

Page 12

- 13 -

2. PERFORMANCE

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2.4.2 WCDMA Transmitter spec.

Item Specification

1 Transmit Frequency WCDMA 850 : 824 MHz ~ 849 MHz

WCDMA 2100 : 1920 MHz ~ 1980 MHz

2 Maximum Output Power +24 dBm / 3.84 MHz, +1 / -3 dB

3 Frequency Error within 0.1 PPM

4 Open Loop Power Control Normal Conditions : within 9 dB,

Extreme Conditions : within 12 dB

5 Minimum Transmit Power < -50 dBm / 3.84 MHz

6 Occupied Bandwidth < 5 MHz at 3.84 Mcps (99% of power)

7 Adjacent Channel Leakage > 33 dB @ 5 MHz,

Power Ratio (ACLR) > 43 dB @ 10 MHz

8 Spurious Emissions < -36 dBm / 1 kHz RW @ 9 kHz ≤ f < 150 kHz

|f-fc| > 12.5 MHz < -36 dBm / 10 kHz RW @ 150 KHz ≤ f < 30 MHz

< -36 dBm / 100 kHz RW @ 30 MHz ≤ f < 1 GHz

< -30 dBm / 1 MHz RW @ 1 GHz ≤ f < 12.75 GHz

< -41 dBm / 300 kHz RW @ 1893.5 MHz < f < 1919.6 MHz

< -67 dBm / 100 kHz RW @ 925 MHz ≤ f ≤ 935 MHz

< -79 dBm / 100 kHz RW @ 935 MHz < f ≤ 960 GHz

< -71 dBm / 100 kHz RW @ 1805 MHz ≤ f ≤ 1880 MHz

9 Transmit Intermodulation < -31 dBc @ 5 MHz & < -41 dBc @ 10 MHz

when Interference CW Signal Level = -40 dBc

10 Error Vector Magnitude < 17.5 %, when Pout ≥ -20 dBm

11 Peak Code Domain Error < -15 dB at Pout ≥ -20 dBm

Page 13

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

2. PERFORMANCE

- 14 -

2.4.3 WCDMA Receiver spec.

Item Specification

1 Receive Frequency WCDMA 850 : 869 MHz ~ 894 MHz

WCDMA 2100 : 2110MHz ~ 2170 MHz

2 Reference Sensitivity Level WCDMA 850 :

BER < 0.001 when Îor = -104.7 dBm / 3.84 MHz

WCDMA 2100 :

BER < 0.001 when Îor = -106.7 dBm / 3.84 MHz

3 Maximum Input Level BER < 0.001 when Îor = -25 dBm / 3.84 MHz

4 Adjacent Channel Selectivity ACS > 33 dB where BER < 0.001 when Îor =

(ACS) -92.7 dBm / 3.84 MHz

& Ioac = -52 dBm / 3.84 MHz @ 5 MHz

5Blocking Characteristic BER < 0.001 when Îor = -103.7 dBm / 3.84 MHz

& Iblocking = -56 dBm / 3.84 MHz @ Fuw(offset)

= 10 MHz

or Iblocking = -44 dBm / 3.84 MHz @ Fuw(offset)

= 15 MHz

6 Spurious Response BER < 0.001 when Îor = -103.7 dBm / 3.84 MHz &

Iblocking = -44 dBm

7 Intermodulation BER < 0.001 when Îor= -103.7 dBm / 3.84 MHz

& Iouw1 = -46 dBm @ Fuw1(offset) = 10 MHz

& Iouw2 = -46 dBm / 3.84 MHz @ Fuw2(offset) =

20 MHz

8 Spurious Emissions < -57 dBm / 100 kHz BW @ 9 kHz ≤ f < 1 GHz

< -47 dBm / 1 MHz BW @ 1 GHz ≤ f ≤ 12.75 GHz

9 nner Loop Power control in uplink Adjust output(TPC command)

cmd 1dB 2dB 3dB

+1 +0.5/1.5 +1/3 +1.5/4

0 -0.5/+0.5 -0.5/+0.5 -0.5/+0.5

-1 -0.5/-1.5 -1/-3 -1.5/-4

group(10equal command group)

+1 +8/+12 +16/+24

Page 14

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

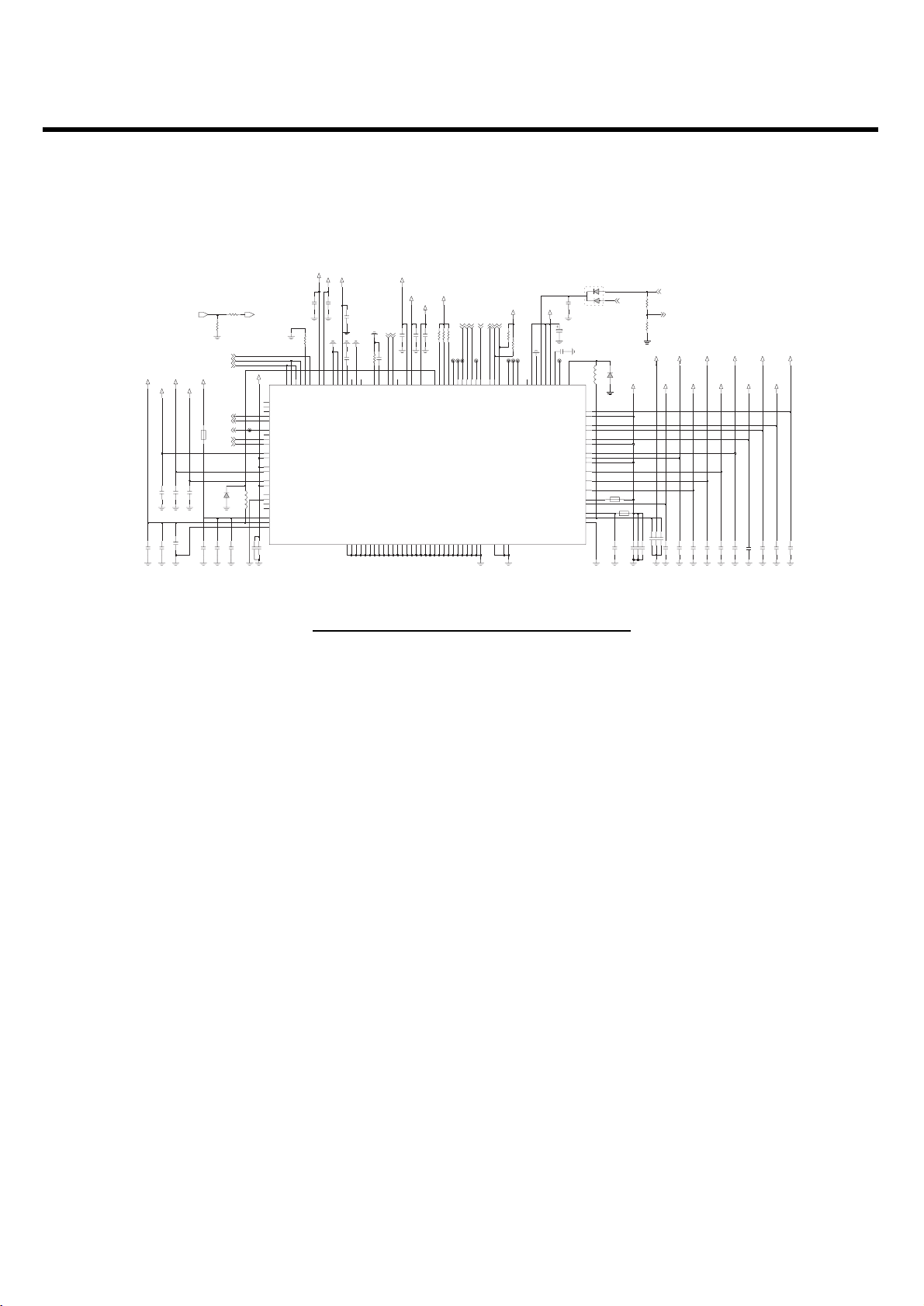

3. TECHNICAL BRIEF

- 15 -

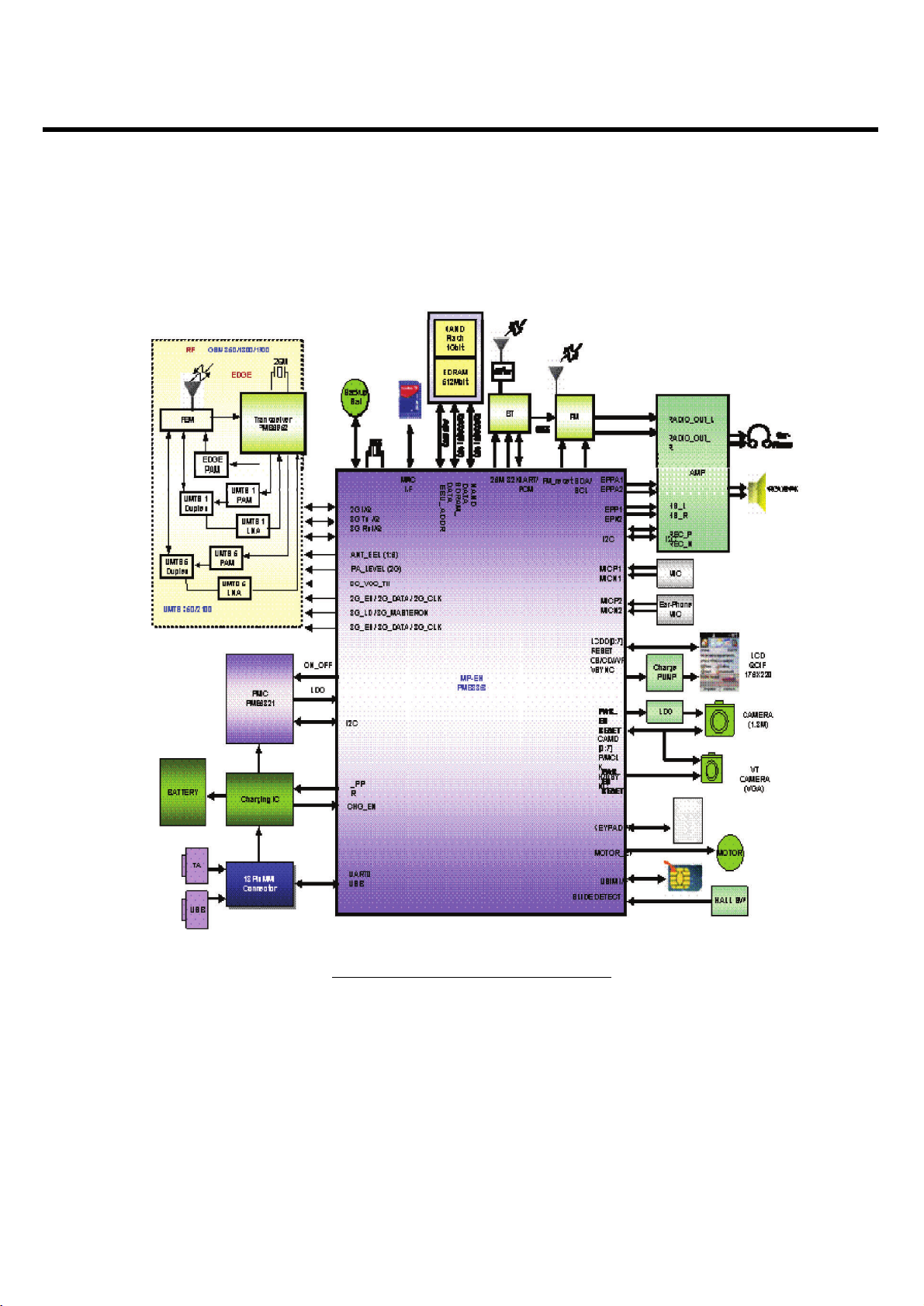

3.1 Functional Block Diagram

3. TECHNICAL BRIEF

[Figure 3.1] Functional Block Diagram

Page 15

- 16 -

3. TECHNICAL BRIEF

3.2 Baseband Processor Introduction

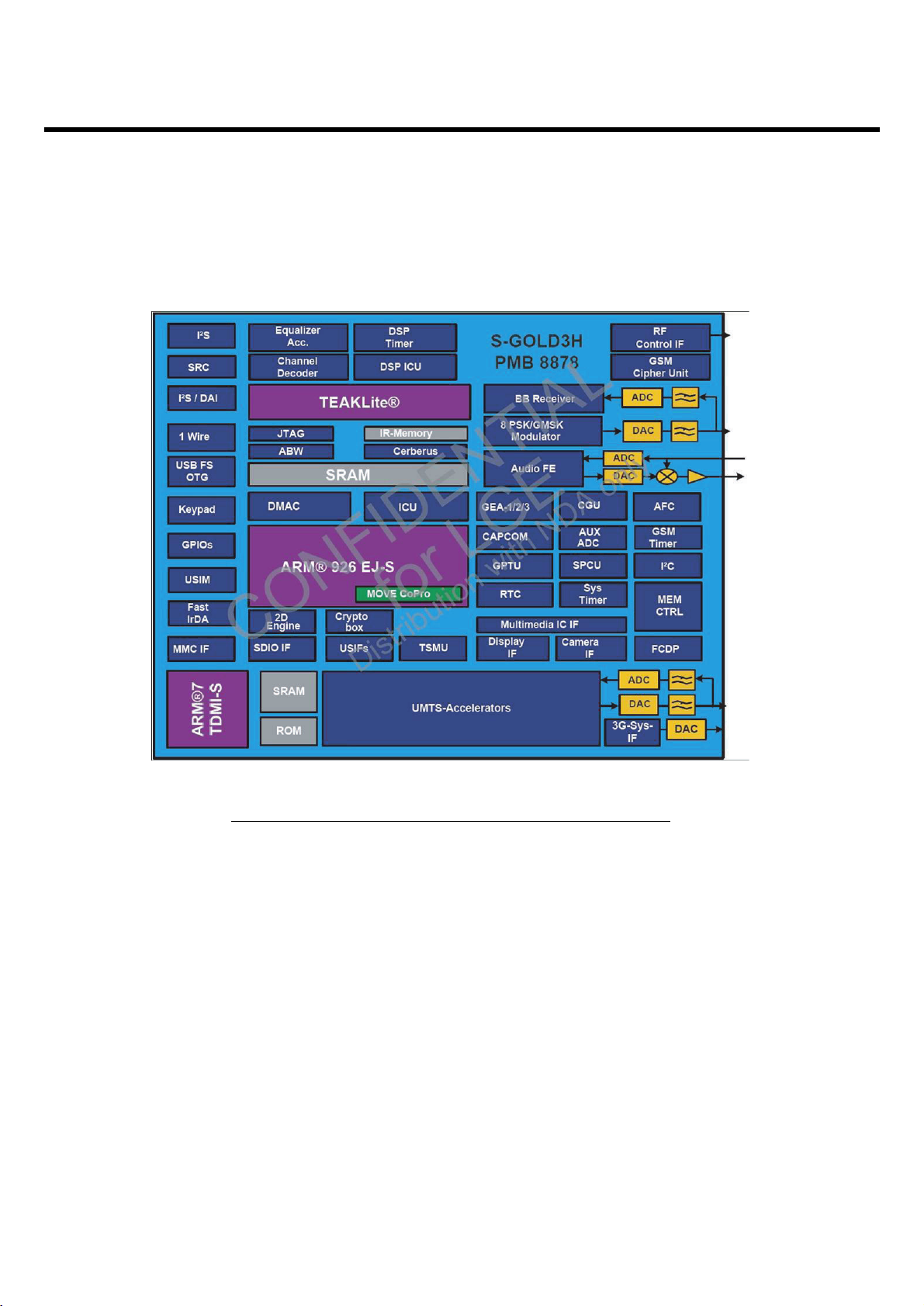

3.2.1 General description

S-GOLD3H-LC is a HSDPA/WCDMA/EDGE/GPRS/GSM system in package solution consisting of a

mixed signal baseband IC with a 3G coprocessor IC.

l Baseband IC containing all analog and digital functionality of a cellular radio. Additionally SGOLD3TM

Provides multimedia extensions such as camera, software MIDI, MP3 sound. It is designed as a single

chip solution, integrating the digital and mixed signal portions of the base band in 0.09um, 1.2V

technology.

The chip will support the FR, EFR, HR and AMR-NB vocoding.

S-GOLD3™ support multi-slot operation modes HSCSD (up to class 10), GPRS for high speed data

application (up to class 12), EGPRS (up to class 12) and DTM(class11) without additional external

hardware.

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.2] Top level block diagram of the MPEH(PMB8868)

Page 16

- 17 -

3. TECHNICAL BRIEF

3.2.2 Block Description

• Processing core

ARM926EJ-S 32 bit processor core for controller functions. The ARM926EJ-S includes an MMU,

and the Jazelle Java extension for Java acceleration.

- TEAKLite DSP core

• ARM-Memory

- 32k Byte Boot ROM on the AHB

- 128k Byte SRAM on the AHB, flexibly usable as program or data RAM

- 32k Byte Instruction Cache

- 32k Byte Data Cache

- 8k Byte Instruction Tightly coupled Memory(I-TCM)

- 8k Byte Data tightly coupled memory (D-TCM)

• DSP-Memory

- 120k x 16bit Program ROM

- 8k x 16bit Program RAM

- 72k x 16bit Data ROM

- 48k x 16bit Data XRAM

- 5k x 16bit Data YRAM

- Incremental Redundancy(IR) Memory of 35904 words of 16bit

• Shared Memory Block

1.5K x 32bit Shared RAM(dual ported) between controller system and TEAKLite.

• Controller Bus system

The processor cores and their peripherals are connected by powerful buses.

-Multi-layer AHB for connecting the ARM and the other master capable building blocks with

theinternal and external memories and with the peripheral buses.

-An FPI-Bus for connecting GSM peripherals, called hereafter FPI3 bus.

-A controller FPI bus for connecting the low performance controller peripherals such as keypad,

Called hereafter fPI2 bus.

-FPI2 and FPI3 are connected asynchronously to the AHB buses.

• Clock system

The clock system allows widely independent selection of frequencies for the essential parts of the

SGOLD3H-LC. Thus power consumption and performance can be optimized for each application.

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Page 17

- 18 -

3. TECHNICAL BRIEF

• Functional Hardware block

- CPU and DSP Timers

- MOVE coprocessor performing motion estimation for video encoding algorithms(H.263, MPEG-4)

- Programmable PLL with additional phase shifters for system clock generation

- GSM Timer Module that off-loads the CPU from radio channel timing

- GMSK / 8-PSK Modulator according to GSM-standard 05.04 (5/2000)

- GMSK Modulator: gauss-filter with B*T=0.3

- EDGE Modulator: 8PSK-modulation with linearized GMSK-Pulse-Filter

- Hardware accelerators for equalizer and channel decoding.

- Incremental Redundancy memory for EDGE class 12 support

- A5/1, A5/2, A5/3 Cipher unit

- GEA1, GEA2, GEA3 Cipher Unit to support GPRS data transmission

- Advanced static and dynamic power management features including TDMA-Frame synchronous

low power mode and enhanced CPU modes(idle and sleep modes)

3.2.3 RF Interface(T_OUT)

S-Gold3H-LC uses this interface to control RF IC and Peripherals.

[Table 3.2.3-1] RF Interface Spec.

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

T_OUT

Resource Interconnection Description

T_OUT0 TXON_PA PAM Power on

T_OUT1 T_OUT2 ANT_SEL1

T_OUT3

T_OUT4 FEM control

T_OUT5 FEM control

T_OUT6 PA_MODE PAM Mode select

T_OUT7 ANT_SEL2

T_OUT8 ANT_SEL3

T_OUT9

T_OUT10

Page 18

- 19 -

3. TECHNICAL BRIEF

3.2.4 ADC channel

ADC block is composed of 11 external ADC channel. This block operates charging process and other

related process by reading battery voltage and other analog values.

[Table 3.2.4-1] S-Gold3 ADC channel usage

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

ADC channel

Resource Interconnection Description

M0 BAT_ID Battery temperature measure

M1 RF_TEMP RF block temperature measure

kM2 N.C

M3 JACK_TYPE Accessory type detect

M4 N.C

M5 N.C

M6 N.C

M7 H/W VERSION H/W version detect

M8 VBAT Battery supply voltage measure

M9 N.C

M10 N.C

Page 19

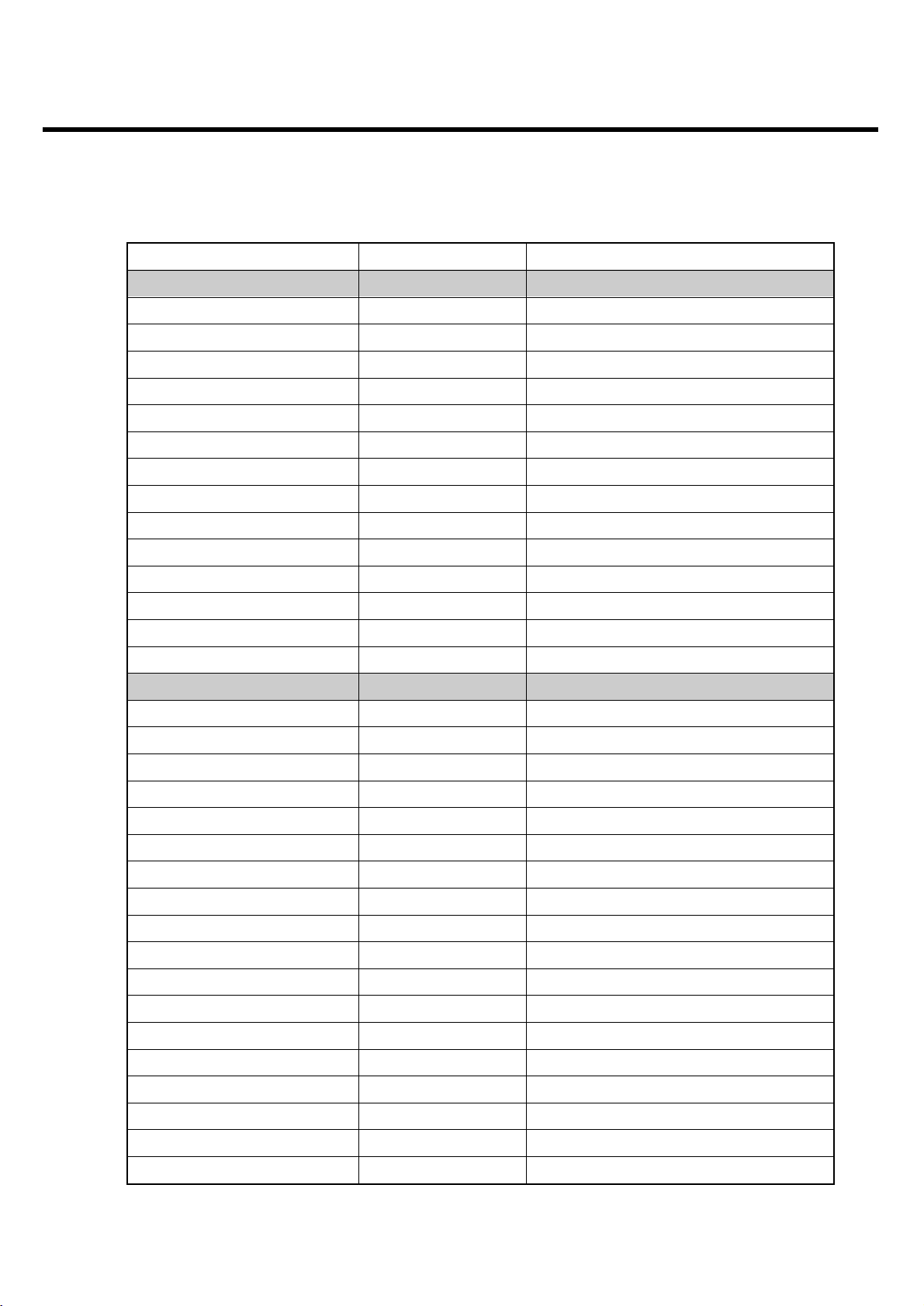

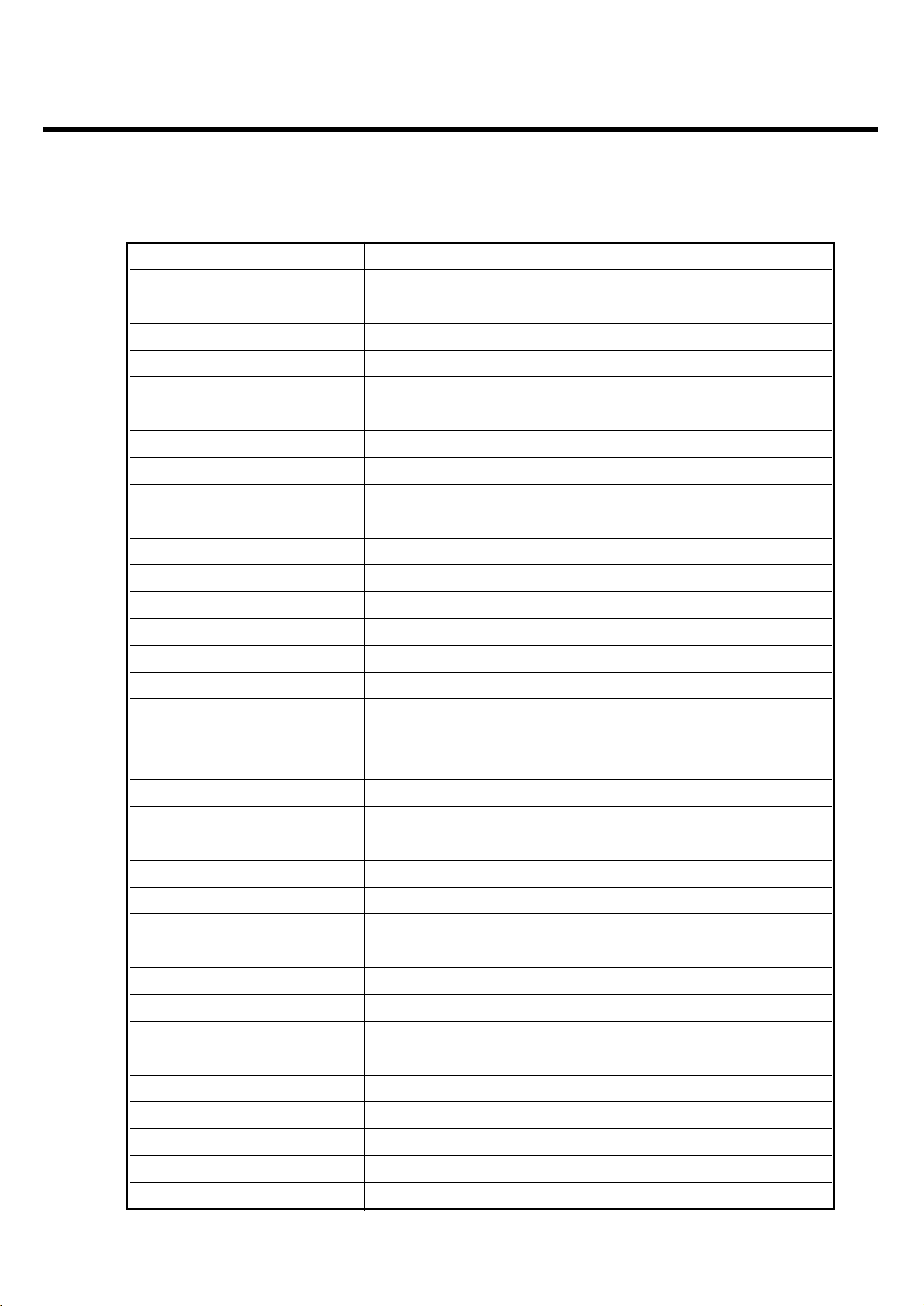

3.2.5 GPIO map

Over a hundred allowable resources, KP275C is using as follows except dedicated to SIM and

Memory.

KP275C GPIO(General Purpose Input/Output) Map, describing application, I/O state, and enable level,

is shown in below table

[Table 3.2.5-1] S-Gold3H-LC GPIO pin Map

- 20 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Port Function Net Name Description

KEY MATRIX

KP_IN0 KEYIN0

KP_IN1 KEYIN1

KP_IN2 KEYIN2

KP_IN3 KEYIN3

KP_IN4 KEYIN4

KP_IN5 KEYIN05

KP_IN6 KEYOUT5

KP_OUT0 KEYOUT0

KP_OUT1 KEYOUT1

KP_OUT2 KEYOUT2

KP_OUT3 KEYOUT3

USIF1

USIF1_RXD_MRST UART_RX UART Data

USIF1_TXD_MTSR UART_TX UART Data

USIF1_RTS_N USB_ DAT_VP USB Data

USIF1_CTS_N USB_SE0_VM USB Data

USIF2

USIF2 _RXD_MRST BT_UART_RX Bluetooth UART Data

USIF2 _TXD_MTSR BT_UART_TX Bluetooth UART Data

USIF2_RTS_N BT_UART_RTS Bluetooth RTS

USIF2_CTS_N BT_UART_CTS Bluetooth CTS

USIF3

GPIO_19 FM_RESET FM radio reset

USIF3 _TXD_MTSR

GPIO_21 VT_PWR_EN VT camera power enable

CLK

CLK32K CLK32k For FM Radio, BT CLK32K

Page 20

- 21 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

GPIO_22 Not used

CAMERA I/F

CIF_D0 CAM_D0 Camera DATA[0]

CIF_D1 CAM_D1 Camera DATA[1]

CIF_D2 CAM_D2 Camera DATA[2]

CIF_D3 CAM_D3 Camera DATA[3]

CIF_D4 CAM_D4 Camera DATA[4]

CIF_D5 CAM_D5 Camera DATA[5]

CIF_D6 CAM_D6 Camera DATA[6]

CIF_D7 CAM_D7 Camera DATA[7]

CIF_PCLK CAM_PCLK Camera pixel clock

CIF_HSYNC CAM_HSYNC Camera H sync

CIF_VSYNC CAM_VSYNC Camera V sync

CLKOUT2 CAM_MCLK Camera main clock

CIF_PD CAM_PWR_EN Camera power down(active high)

CIF_RESET CAM_RESET Camera reset

LCD I/F

DIF_D0 LCD_D0 LCD data[0]

DIF_D1 LCD_D1 LCD data[1]

DIF_D2 LCD_D2 LCD data[2]

DIF_D3 LCD_D3 LCD data[3]

DIF_D4 LCD_D4 LCD data[4]

DIF_D5 LCD_D5 LCD data[5]

DIF_D6 LCD_D6 LCD data[6]

DIF_D7 LCD_D7 LCD data[7]

DIF_D8 DIF_ID LCD data[8]

DIF_CS1 _LCD_CS1 MAIN LCD chip select

EINT4 FM_INT FM radio interrupt

DIF_CD LCD_CD Command Data switch

DIF_WR _LCD_WR LCD Write

GPIO_98 VT_CAM_RESET VT camera reset

DIF_HD LCD Reset

DIF_VD LCD_VSYNC LCD Vsync

DIF_RESET1 _LCD_RESET LCD Reset

DIF_RESET2 A_RESET 3G reset

Page 21

- 22 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

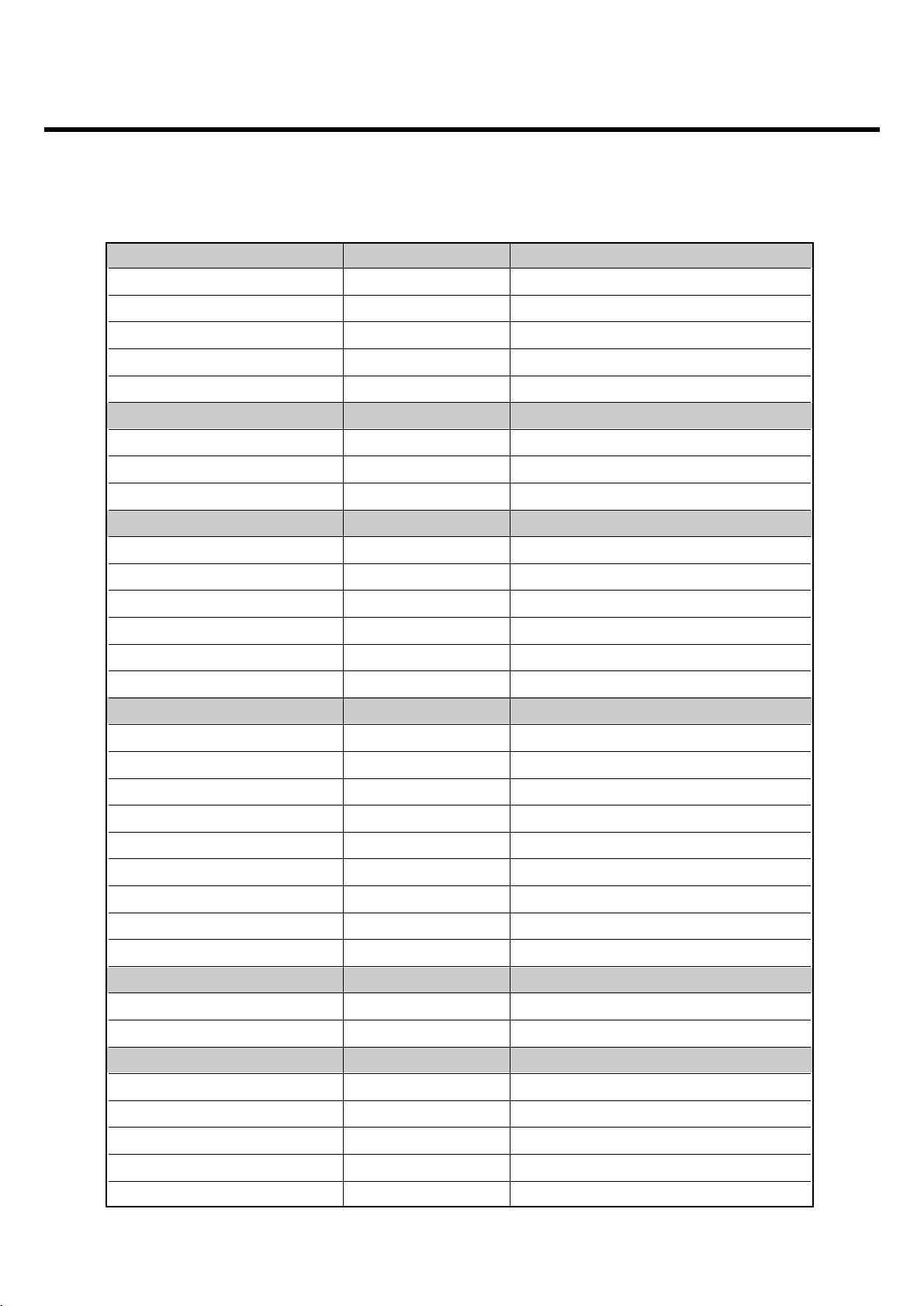

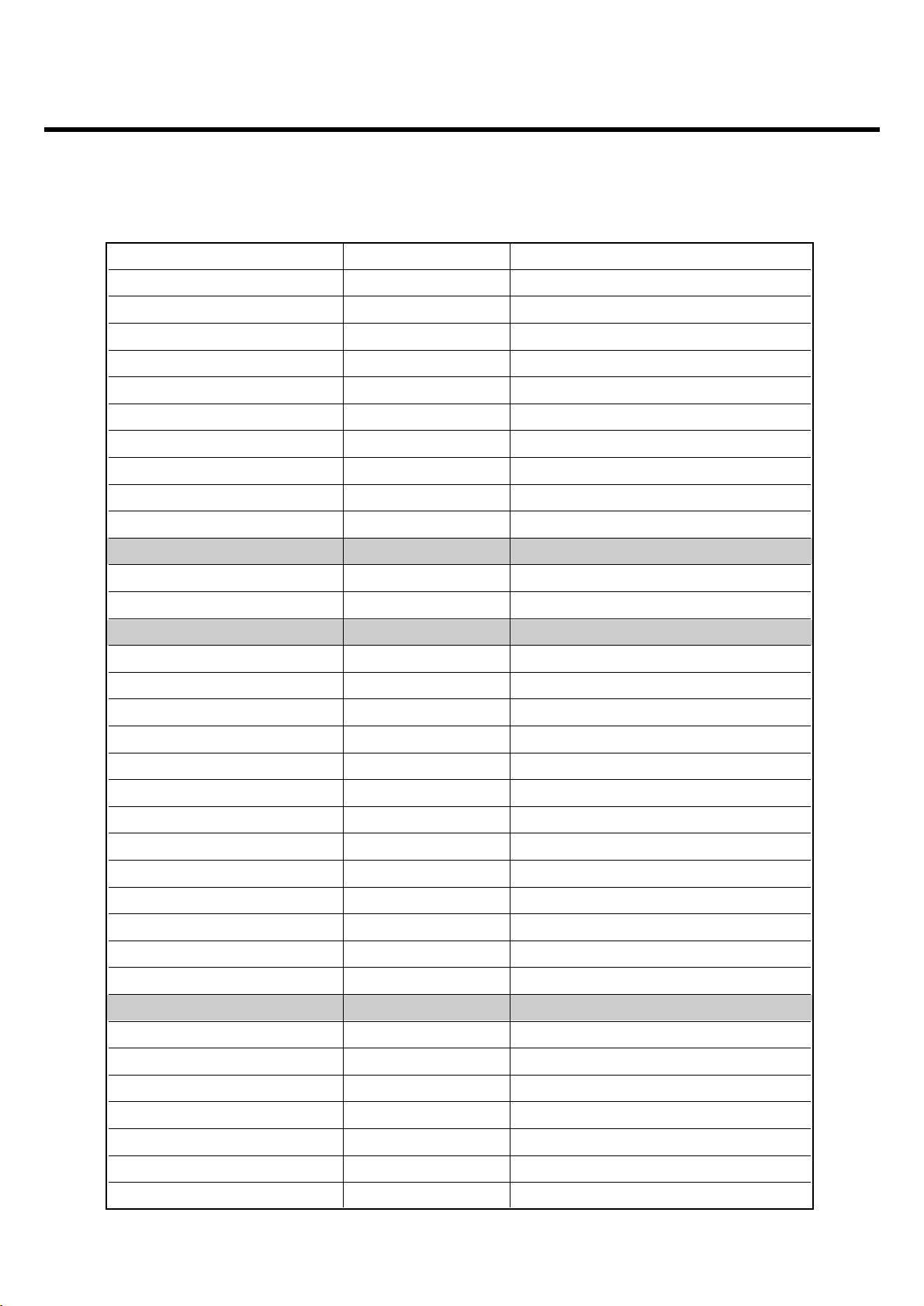

I2C

I2C1_SCL SCL_PMIC For PMIC

I2C1_SDA SDA_PMIC For PMIC

PM_INT (EINT) PM_INT For PMIC

I2C2_SCL SCL

I2C2_SDA SDA

SIM I/F

CC_IO SIM_DATA SIM CARD DATA

CC_CLK SIM_CLK SIM CARD CLOCK

CC_RST SIM_RST SIM CARD RESET

I2S2

GPIO_31 BT_RESETn Bluetooth reset

GPIO_102 DBB_BT_INT S-GOLD3H-LC to Bluetooth interrupt

GPIO_32 UPPER_KEY_LED Function key LED enable

CC0CC7IO BT_IN Bluetooth to S-GOLD3H-LC interrupt

GPIO_34 MAIN_KEY_EN Number key LED enable

GPIO_103 BT_LDO_EN Bluetooth LDO enable

External Memory

MMCI_CMD MMC_CMD T-flash command

MMCI_DAT[0] MMC_D0 T-flash data0

MMCI_CLK MMC_CLK T-flash clock

MMC1_DAT[1] MMC_D1 T-flash data1

MMC1_DAT[2] MMC_D2 T-flash data2

MMC1_DAT[3] MMC_D3 T-flash data3

MMC2_CMD

MMC2_DAT[0]

MMC2_CLK MOTOR_EN Vibrator enable

IrDA

GPIO_110 USB_OEn For USB

GPIO_111 SLIDE_DETECT Slide on/off detect

I2S1

I2S1_CLK0 BT_PCM_CLK For Bluetooth

I2S1_CLK1

I2S1_RX BT_PCM_RX For Bluetooth

I2S1_TX BT_PCM_TX For Bluetooth

I2S1_WA0 BT_PCM_SYNC For Bluetooth

Page 22

- 23 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

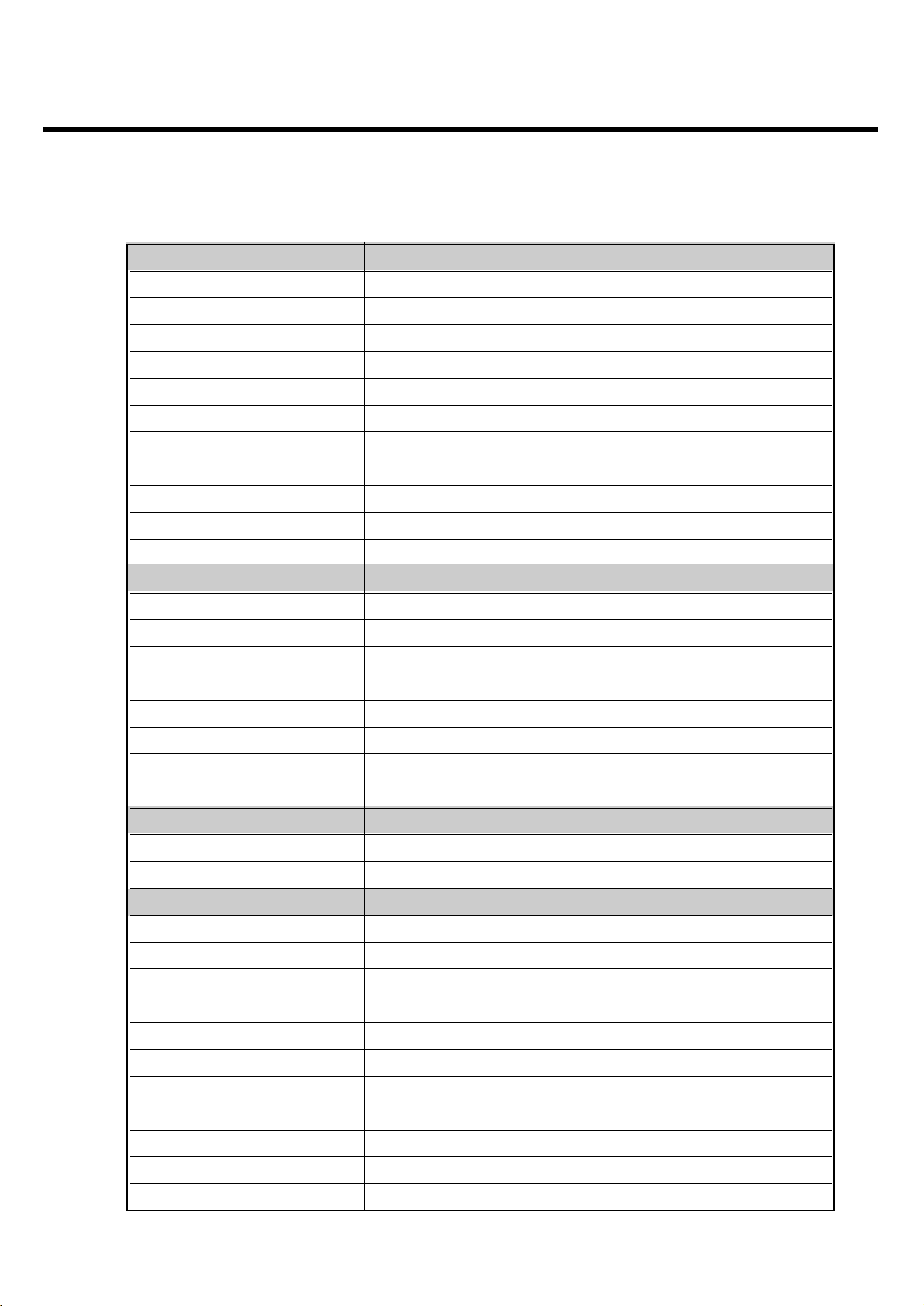

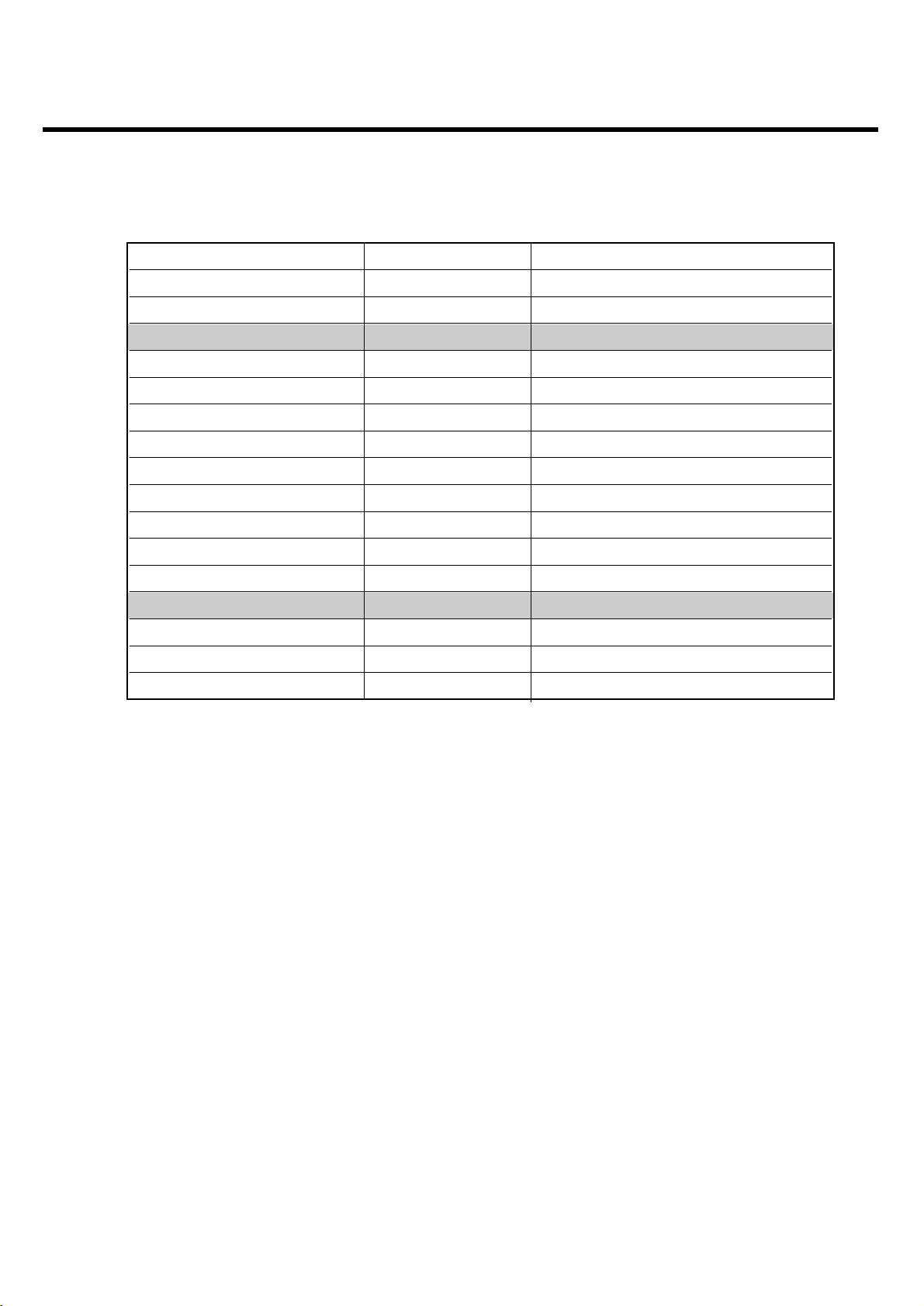

Audio I/F

EPN1 REC_N For Receiver

EPP1 REC_P For Receiver

EPPA1 HS_L For Headset

EPREF Reference

EPPA2 HS_R For Headset

MICN1 MAIN_MIC_N For Main Mic

MICP1 MAIN_MIC_P For Main Mic

MICN2 HS_MIC_N For Headset Mic

MICP2 HS_MIC_N For Headset Mic

VMICP VMIC_P Power for MIC

VMICN GND Ground for MIC

ADC

M0 BAT_ID Battery temperature measure

M1 RF_TEMP RF block temperature measure

M2

M3 JACK_TYPE Accessory type detect

M7 H/W VERSION H/W version detect

M8 VBAT Battery supply voltage measure

M9

M10

Reference

VREF VREFN

IREF GND with resistor

JTAG I/F

JTAG0_TDO

JTAG0_TDI

JTAG0_TMS

JTAG0_TCK

JTAG0_TRST_n

JTAG0_RTCK

JTAG1_TDO

JTAG1_TDI

JTAG1_TMS

JTAG1_rTCK

JTAG0_TRST_n

Page 23

- 24 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

ETM I/F

TRIG_IN

MON1 MON1 ETM

MON2 MON2 ETM

TRACESYNC

TRACECLK

PIPESTAT[2]

PIPESTAT[1]

PIPESTAT[0]

TRACEPKT[0]

TRACEPKT[1]

TRACEPKT[2]

TRACEPKT[3]

TRACEPKT[4]

TRACEPKT[5]

TRACEPKT[6]

TRACEPKT[7]

Memory

MEM_AD[0] DATA(0)

MEM _AD[1] DATA(1)

MEM _AD[2] DATA(2)

MEM _AD[3] DATA(3)

MEM _AD[4] DATA(4

MEM _AD[5] DATA(5)

MEM _AD[6] DATA(6)

MEM _AD[7] DATA(7)

MEM _AD[8] DATA(8)

MEM _AD[9] DATA(9)

MEM _AD[10] DATA(10)

MEM _AD[11] DATA(11)

MEM _AD[12] DATA(12)

MEM _AD[13] DATA(13)

MEM _AD[14] DATA(14)

MEM _AD[15] DATA(15)

MEM _WR_n _WR

MEM _RD_n _ RD

Page 24

- 25 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

MEM _BC0_n _BC0

MEM _BC1_n _BC1

MEM _BC2_n LDQS

MEM _BC3_n UDQS

MEM _A[0] ADD(0)

MEM _A[1] ADD(1)

MEM _A[2] ADD(2)

MEM _A[3] ADD(3)

MEM _A[4] ADD(4)

MEM _A[5] ADD(5)

MEM _A[6] ADD(6)

MEM _A[7] ADD(7)

MEM _A[8] ADD(8)

MEM _A[9] ADD(9)

MEM _A[10] ADD(10)

MEM _A[11] ADD(11)

MEM _A[12] ADD(12)

MEM _A[13] ADD(13)

MEM _A[14] ADD(14)

MEM _A[15] ADD(15)

MEM _A[16] ADD(16)

MEM _A[17] ADD(17)

MEM _A[18] ADD(18)

MEM _A[19] ADD(19)

MEM _A[20] ADD(20)

MEM _A[21] ADD(21

MEM _A[22] ADD(22)

MEM _A[23] ADD(23)

MEM _A[24] ADD(24)

MEM _A[25] ADD(25)

MEM _A[26] ADD(26)

MDM_SDA[11] ADD(27)

MDM_SDA[12] ADD(28)

MDM_SDA[13] ADD(29)

MDM_SDA[14] ADD(30)

MEM _CS0_n _ _NAND_CS INTEL NOR (64MB)

Page 25

- 26 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

MEM _CS1_n _RAM_CS INTEL SDRAM (64MB)

MEM _CS2_n

MEM _CS3_n _CS3

MEM _ADV_n ADV_A15

MEM _RAS_n _RAS

MEM _CAS_n _CAS

MEM _WAIT_n _WAIT

MEM _SDCLK0 SDCLKO For Burst mode

MEM _BFCLK01 BFCLKO For Burst mode

MEM _BFCLK02 SDCLK1 For Burst mode

MEM _CKE CKE

Memory

FCDP_RBn FCDP

GPIO_60 RPWRON_DBB

TDMA I/F

T_OUT0 TXON_PA PAM

T_OUT1

T_OUT2 ANT_SEL1

GPIO_46 MLED_CLDO_CTR Charge pump control

EINT6 _EOC Charging terminate signal

CC0CC2IO MMC_DETECT SD card detect

T_OUT6 PA_MODE PAM

T_OUT7 ANT_SEL2

T_OUT8 ANT_SEL3

GPIO_52 DSR

CC1CC7IO JACK_DETECT Jack detect

GPIO_54 TA_DETECT Charger detect

GPIO_55 CHG_EN Charging enable

RF I/F

RF_STR0 2G_EN

CC1CC5IO _PPR Charger detect

RF_DATA 2G_DATA

RF_CLK 2G_CLK

RF_LOCK_DET 3G_LD

MASTER_ON 3G_MASTER_ON

PA_MODE 3G_PA_MODE1

Page 26

- 27 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

FEM_CTRL[0] ANT_SEL4

FEM_CTRL[1] ANT_SEL5

FEM_CTRL[2] ANT_SEL6

System Port

AFC AFC

CLKOUT0 [<=26MHz] Not used

F26M 26MHZ 26M Main Clock

F32K to 32k crystal

OSC32K to 32k crystal

RESET_n _RESET

TRIG_OUT TRIG_OUT

RTC_OUT RTC_OUT

VCXO_EN VCXO_EN

DSP

DSPIN0 CLK32K

DSPOUT1 WDOG Navi key LED Backlight Control

DSPIN1

Page 27

- 28 -

3. TECHNICAL BRIEF

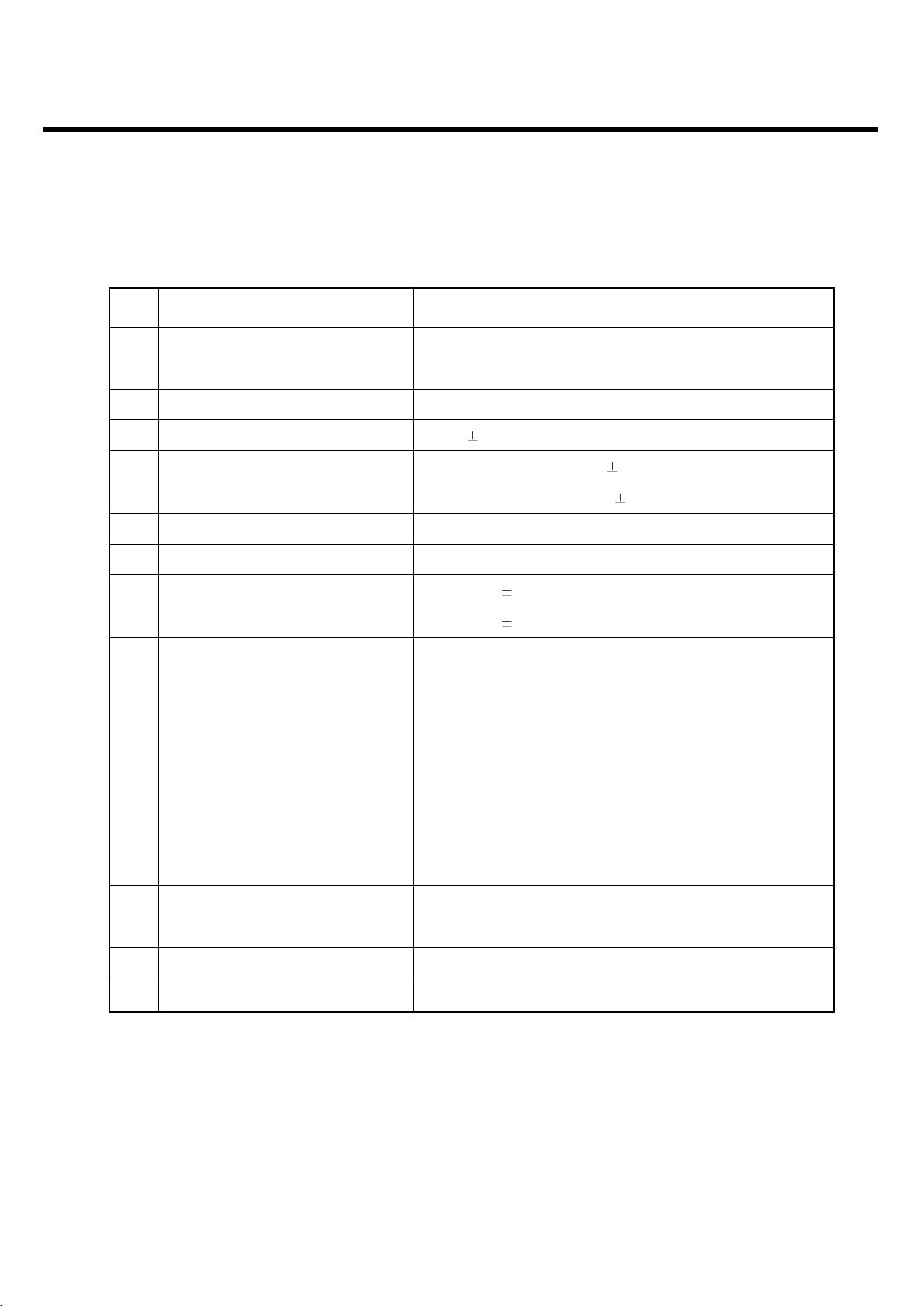

3.3 Power management IC

3.3.1 General Description

SM-POWER is a highly integrated Power and Battery Management IC for mobile handsets. It has

been specially designed for usage with S-Gold3. Although optimized for usage with the Infineon

SGOLD

baseband device it is suitable for the S-GOLD lite and the E-GOLD+ baseband devices as well. It also

supports the cellular RF devices like SMARTi-DC, SMARTi-DC+, SMARTi-SD and the Bluemoon

Single, Infineon’s single chip solution for Bluetooth. If used with S-GOLD3 it provides all power supply

functions (except for the RF PA) for a complete advanced GSM Edge smart phone minimizing external

device count.

Block Description

• Highly efficient step-down converter for main digital baseband supply including Core, DSP and

memory interface (External Bus Unit).

• Support of S-GOLD standby power-down concept

• Low-drop-out (LDO) regulators for Flash and mobile RAM memory devices

• Voltage independent switching of two SIM cards

• LDO regulators for baseband I/O supply

• LDO regulator for analog mixed-signal section of S-GOLD

• Low-noise LDO regulators for RF devices

• Supply for Bluemoon Single, Infineon°Øs single chip solution for Bluetooth

• Audio amplifier 8 Ohms for handsfree operation and ringing

• Charge Control for charging Li-Ion/Polymer batteries under software control

• Pre-charge current generator with selectable current level

• RTC regulator with ultra-low quiescent current

• USB interface support for peripheral and mini-host mode

• Backlight LEDs driver with current selection and PWM dimming function

• Two single LED driver outputs for signaling

• Vibrator driver with adjustable voltage

• Fully controlable by software via I2C - Bus

• Temperature and battery voltage sensors

• Interrupt channels for peripherals

• System debug mode

• VQFN 48 package with heat sink and non-protruding leads

• Compatible with the Infineon E-GOLD+ V2 and V3

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Page 28

- 29 -

3. TECHNICAL BRIEF

SM-POWER is a further step on the successful E-Power product line with enhanced and optimized

functionality.

SM-POWER features a baseband supply concept with a DC/DC step-down converter cascaded by

two linear regulators

• SM-POWER’s DC/DC converter makes up to 40 % reduction of battery current for smart phone

functions (e.g. organizer functions, games, MP3 decoding) possible.

• SDBB has high efficiency up to 95% and also a power save mode.

• Memory Interface is directly supported by the SDBB

• SDBB can also act as main supply voltage for E-GOLD+ or S-GOLDlite baseband devices.

• For S-GOLD two linear regulators for DSP and Core are cascaded after the SDBB.

SM-POWER supports the standby power-down concept of S-GOLD by temporarily switching off the

linear regulator for the DSP during mobile standby whenever this subsystem is not used. In this

phase the ARM controller and most peripherals including parts of the on-chip SRAM are kept

powered-up withpower being supplied by the other linear regulator.

SM-POWER includes a fully differential audio amplifier able to drive loads down to a nominal value

of 8 Ohm for usage in hands-free phones and for ringing

• 450 mW maximum output power

• adjustable gain

• mute switch SM-POWER also integrates a charging function for Li-Ion, Li-Polymer batteries

• click and pop -protection SM-POWER also integrates a charging function for Li-Ion, Li-Polymer

batteries

• Precharge current source with two current levels

• Constant current / constant voltage charging with 3 different termination voltages

• Programable charge current limitation for use with different batteries

• Freely programable pulse charging to reduce the thermal power dissipation in the constant voltage

charging phase

• Top-off charge current sensing SM-POWER completes the USB interface of S-GOLD

• Regulated voltage for S-GOLD USB interface including reverse current and overvoltage protection

• Switch to supply USB pull-up resistor

• Mini-host pull down resistor functionality

• Charge pump with internal switching capacitor for USB host VBUS supply voltage SM-POWER

fully supports LED and Vibra Motor functionality

• no external components needed

• driver for backlight LEDs adjustable in steps up to 140mA and with soft turn on and off by PWM

dimming

• two driver outputs for single LEDs for precharge indication and signaling with i.e. change of colour

• driver for Vibra Motor with adjustable voltages, soft startup / shutdown and current limitation

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Page 29

SMPOWER

offers several control functions

• Power-on Reset Generator with logic state machine

• I2C bus interface

• I2C bus configurable mode control logic with ON (push-button or RTC), VCXOEN and LRF3EN

(wake-up by Bluetooth) inputs

• Programable interrupt channels to handle peripherals like SIM, MMC and USB

• Monitoring of charging functions

• Undervoltage Shut-Down

• Errorflags (volatile or non-volatile) from many power-supply functions and thermal sensor in order

to debug system

• Overtemperature Shut-Down

• Overtemperature Warning

• Support of S-GOLD standby power-down concept

• Support of S-GOLD Power-Down Pad Tristate Function

[Table 3.3.1-1] LDO Output Table of SM-Power3

- 30 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LDO Net name Output Voltage Output Current Usage

SD1 1V35_Core 1.35V 600mA Core & for LDO

SD2 1V8_SD 1.8V 300mA Memory

VAUX 2V85_VFM 2.85V 100mA FM RADIO

VIO 2V62_VIO 2.62V 100mA Peripherals

VSIM 2V9_SIM 2.9V 70mA SIM card

VMME 2V9_VMME 2.9V 150mA u-SD

VUMTS 2V85_VCD 2.85V 110mA LCD

VAUDIOa 2V5_VAUDA 2.5V 200mA Stereo headset, Mono earpiece

VAUDIOb 2V5_VAUDB 2.5V 50mA Analog parts of S-Gold

VRF1 2V85_VRF 2.85V 150mA 2.85 V supply for SMARTi-PM RF transceiver

VRF2 1V5_VRF 1,53V 100mA 1.5 V supply for SMARTi-PM RF transceiver

VRF3 2V855_VBT 2.7V 150mA Bluetooth

VPLL 1V35_VPLL 1.35V 30mA S-GOLD3H PLL

VRTC 2V11_RTC 2.11V 4mA Real Time Clock

VAFC 2V7_VRF 2.65V 5mA Not used

VVIB 2V8_VAMP 2.8V 140mA AUDIO AMP

Page 30

- 31 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure3.3.1-1] SM-Power 3 Circuit Diagram

1V8_SD

2V5_VAUDA

C223

10u

PMIC

2V5_VAUDB

2.2u 2.2u

C224

10u

16081608

C215C214

C222

0.1u

RTC_OUT ON_OFF2

2V85_VFM

R209

27K

R212

DNI

USB_OEn

USB_DAT_VP

USB_SE0_VM

VBAT

FB201

PM_VCXO_EN

1608

BT_VCXO_EN

C216

1u

C219

4.7u

1608

RB521S-30

PMRSTn

D204

VBAT

USB+

USB-

PMRSTn

L202

10uH

2.2uC227

C225

C226

2.2u

0.1u

1608

VUSB

VBAT

VBAT

C203

2.2uC204

2.2u

1608

1608

R235

100K

0.1u

C210

B7

B5

A2

A4

B2

B3

C3

A3

C5

B6

C4

AC-

AC+

OE_N

VUSB

DAT_VP

SE0_VM

B1

RCV

C2

VPIN

D3

VMIN

C1

D+

D2

D-

E3

RESET_N

D1

RESET2_N

E2

SLEEP1_N

E1

SLEEP2_N

F2

VAUDIOA

F1

VDDAUDIOA

G2

VDDAUDIOB

G1

VAUDIOB

H2

VAUX

H1

VDDAUX

J1

SU1_GATE

J2

SU1_GND

H3

SU1_FB

J3

SU1_ISENSE

K1

VDDSD2

K2

SD2_FB

L2

SD2_FBL

4.7uC228

1608

SUSPEND

VDD_USB

MONO_INP

MONO_INN

VDD_MONO

A5

VREFEX_M

VSS1

C6

C201

0.1u

A7

C7

VSS_MONO

MONO_OUTP

VSS2

VSS3

D4

D5

1%

A6

MONO_OUTN

VSS4

VSS5

D6

D7

VSS6E4VSS7E5VSS8

D8

1V35_VPLL

VBAT

VBAT

2V62_VIO

MAIN_KEY_LED

MAIN_KEY_EN

1u

4.7KR215

4.7KR214

2.2u

2.2u

C209

C207

C208

C9

FLASH_ON

VSS11

E8

R213 4.7K

1608

TP202

TP203

L1

A11

A10

B4

B11

B9

K3

B10

TXONPA

VSS12

E9

A1

J4

VIO

VPLL

VSD2

PUMS2

PUMS3

PUMS1

OUTPORT

VDDPLLIO

U202

PMB6821

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22G6VSS23

VSS13

F3

F4

VSS24

VSS14

VSS15

VSS16

F7

F8

F9

F5

F6

G3

G4

G5

G7

G8

1u

100K

R219

C212

C8

B8

A9

VREF

RREF

FLASH_SHINK

VSS10

VSS9

E7

E6

WDOG

TP204

L3

WDOG

POWER_ON

VSS25

VSS26

H5

G9

PWRON

ON_OFF2

TP205

L4

L5

ON_OFF1K4ON_OFF2

VSS27

VSS28

H6

H7

RESOURCE_CTRL

J5

K5

ON_OFF_OUT

RESOURCE_CRTL

VSS29

VSS30

J6

SPOWER_INT

SDA_PMIC

SCL_PMIC

R216

4.7K

J7

K6

I2C_INT

I2C_CLK

I2C_DAT

D9

H8

2V62_VIO

TP206

L6

VSS_SD1

TP207

K7

BL1_PWM

VSS_SD2H4VSS_VREF

R217

4.7K

TP208

J8

BL2_PWM

BL3_PWM

L7

CH_CNTRL

L8

K8

CHARGE_UC

CH_SOURCE

VBAT

K9

L9

K10

SENSE_IN1

VDD_CHARGE

J9

VDD_REF

SENSE_IN2

C202

C205

33u

0.1uC211

TP209

L11

A8

VSD1

VLED

VDDMME

VDDRF2

VDDRF13_AFC

VDDSIMVIB

VDDUMTS

VDDSD1

SD1_FB

SD1_FBL

KDR331V

2

3

1

1u

D202

L201

10uH

D203

C11

VMME

C10

D10

D11

VRF2

E10

VRF3

E11

F10

VRF1

F11

VVIB

G11

G10

VSIM

H11

VAFC

H10

VRTC

FB202

H9

J11

VUMTS

K11

J10

L10

C220

4.7u

1608

SDB0530

FB203

OVP_VUSB

1608

OVP_VCHG

R233

47K

TA_DETECT

R234

47K

C233

1u

2V11_RTC

2V85_VRF

C235

2V9_VSIM

1V5_VRF

2V9_VMME

1V8_SD

2V85_VBT

C239

C237

C238

C236

2.2u2.2u

C240

C241

2.2u

2.2u

2.2u

2.2u

2.2u

2V7_VRF

C234

1u

1V35_CORE

2V8_AMP

2V85_VLCD

VBAT

1608

1608

1608

10uC218

10uC221

10u

1608

1608

1608

4.7uC231

C232

C217

1u

C230 4.7u

C229 2.2u

Page 31

- 32 -

3. TECHNICAL BRIEF

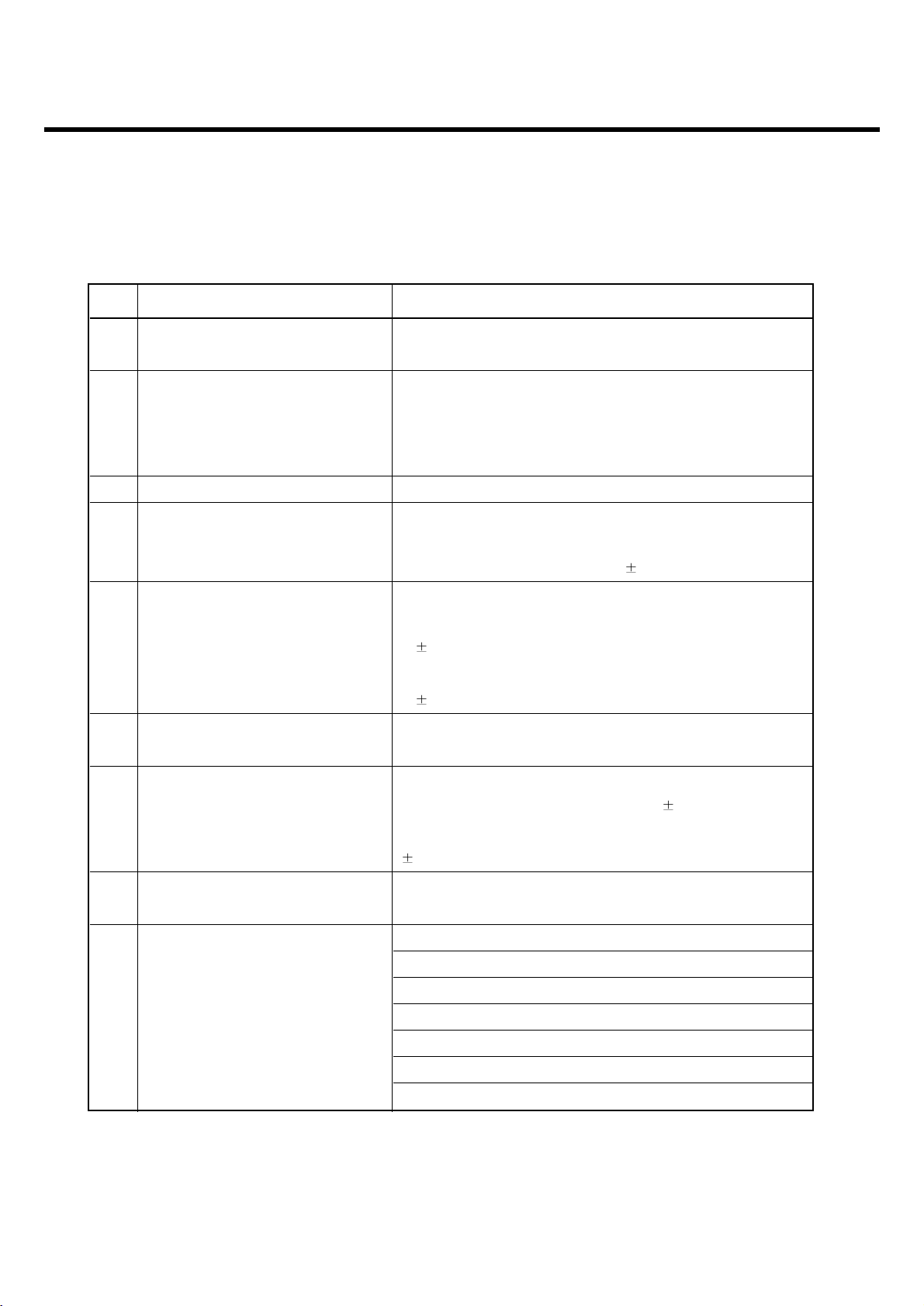

3.3.2 Charging control

• KP275C is use external charging IC

• Charging IC is ISL9221

1. Charging method : CC-CV

2. Charger output voltage : 5.1 V

3. Charging time : 2h 10m

4. Charging current : 600 mA

5. CV voltage : 4.2 V

6. Cutoff current : 117 mA

7. Full charge indication current (icon stop current) : 117 mA

8. Recharge voltage : 4.15 V

9. Low battery alarm

a. Idle : 3.45 V ~ 3.31 V

b. Dedicated : 3.45 V ~ 3.3 V

10. Low battery alarm interval

a. Idle : 3 min

b. Dedicated : 1 min

11. Switch-off voltage : 3.31 V

12. Charging temperature adc range

a. ~ -20°C : low charging voltage operation (3.6 V ~ 3.9 V) .

b. -20°C ~ 60°C : standard charging (up to 4.2 V)

c. 60°C~ : low charging voltage operation (3.6V ~ 3.9V)

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.3.2-1] Charging IC (ISL9221)

CHARGING IC

_EOC

CHG_EN

USB_VCHG

VCHG

2V62_VIO

R226

100K

_PPR

2V11_RTC

R227

100K

C242

U203

1

2

3

4

5

6

C243

1u

R228

1u

4.7K

1%

VDC

VUSB

_PPR

_CHG

_EN

IMIN

ISL9221

PGND

VDC_BYP

BAT

USB_BYP

IVDC

GND

IUSB

378mA 600mA117mA

13

12

11

10

9

8

7

R230

18K

1%

VBAT

OVP_VCHG

OVP_VUSB

R229

11.3K

1%

C244

1u

C245

1u

C246

1u

Page 32

- 33 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.3.2-1] Block diagram of Charging IC

[Table 3.3.2-1] PIN description of Charging IC

NAME PIN TYPE DESCRIPTION

VDC 1 AI Input pin from car adapter or AC/DC adapter

VUSB 2 AI Input pin from USB host device

VDC_LDO 12 AO Output pin of Linear Regulator

USB_SYP 10 AO Output pin from USB bypass circuitry

IVDC 9 AI Battery current setting pin for adapter power

IUSB 7 AI Current setting pin for USB power

IMIN 6 AI End-of-charge current setting pin

BAT 11 AO Output pin to battery

EN 5 DI Active low charge enable pin

PPR 3 OD Active low power present indicator pin

CIIC 4 OD Active low charging indication pin

GND 8 G Ground pad

Page 33

- 34 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.3.2-2] Charging Profile

Page 34

- 35 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.4 Power ON/OFF

KS360 series Power State : Defined 3cases as follow

Voltage level of PWRON pin is high before push the END_KEY button.

If push the END_KEY button, voltage level of PWRON pin is change from high to low.

ON_OFF1 is a power-on input for SM-POWER3 with active low levels.

[Figure 3.4-1] Remote power on and End-key power on circuit

2V11_RTC

Remote Power On

3.3M

RPWRON_EN

END_KEY

R207

C206

2.2u

END_KEY_IN

R223

10K

2

R225

100K

2

R210

3.3M

R220 10K

R221 DNI

3

Q203

KTC4075E

1

3

Q201

KTC4075E

1

R218

100K

R202

100K

3

2

1

END_KEY_IN

KEYIN0

KEYOUT0

R208 0

Q202

KTC4075E

PWRON

RPWRON_DBB

PWRON

WDOG

TP204

TP203

L3

K4

K3

L4

WDOG

ON_OFF1

POWER_ON

ON_OFF2

RESOURCE_CTRL

TP205

J5

L5

ON_OFF2

ON_OFF_OUT

RESOURCE_CRTL

Page 35

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.5 SIM Interface

KP275C supports 1.8V & 2.9V plug in SIM. SIM_IO, SIM_CLK, SIM_RST ports are used to

communicate with S-Gold3H-LC and the SIM power supply enabled by PMIC.

SIM Interface

SIM_CLK : SIM card reference clock

SIM_RST : SIM card Async /sync reset

SIM_IO : SIM card bidirectional reset

3. TECHNICAL BRIEF

- 36 -

[Figure 3.5-1] SIM Circuit

SIM CONNECTOR

SIM_DATA

2V9_VSIM

R317

10K

C323

22p

2V9_VSIM

J301

4

C5

5

C6

6

C7

10

GND4

9

C1

C2

C3

GND1

GND2GND3

1

2

3

7

8

2V9_VSIM

C322

0.1u

C324

22p

SIM_RST

SIM_CLK

C325

DNI

Page 36

- 37 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.6 MICRO SD connector

The Micro SD Memory Module has eight exposed contacts on one side.

The S-Gold3H-LC connected to the module using a dedicated eight-pin connector

[Figure 3.6-1] Micro SD Connector

MICRO SD Connector

2V62_VIO

56KR323

56KR324

2V9_VMME

56KR325

2V9_VMME

MMC_D1

MMC_D0

MMC_CLK

MMC_CMD

MMC_D3

MMC_D2

MMC_DETECT

C329

1u

R322 100K

C330

DNI

R327 56K

C331

DNI DNI

C332

C333

DNI

R326 56K

C334

C335

DNI

10p 1u

C336

DNI

C337

S301 AXA463062P

DAT1_2

DUMMY1

DAT0

VSS

CLK

VDD

CMD

CD_DAT3

DUMMY2

DAT2

DETECT_A

DETECT_B

DUMMY3

GND

Page 37

- 38 -

3. TECHNICAL BRIEF

3.7 Memory

1Gbit NAND Flash & 512Mbit DDR SDRAM employed on KP275C with 16 bit parallel data bus thru

ADD(0) ~ ADD(24). The 1Gbit Nand Flash memory with DDR SDRAM stacked device family offers

multiple high-performance solutions.

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.7-1] Memory circuit diagram

1G NAND(Large Block x16bit) +512M DDR SDRAM

C139

1V8_SD

ADD(16:28)

_RD

_NAND_CS

_RAM_CS

SDCLKI

SDCLKO

CKE

ADD(17)

ADD(16)

_WR

_CAS

_RAS

LDQS

UDQS

_BC1

_BC0

_WR

ADD(29)

ADD(30)

DATA(0:15)

1V8_SD

R108

10K

FCDP

IO10

IO11

IO12

IO13

IO14

IO15

IO16

NC46

NC47

NC48

NC49

NC50

NC51

NC52

NC53

NC54

NC55

NC56

NC57

NC58

NC59

NC60

NC61

NC62

NC63

NC64

NC65

NC66

NC67

NC68

NC69

NC70

NC71

_WP

RY__BY

_CLK

CLK

CKE

CLE

ALE

_WEN

_CAS

_RAS

LDQS

UDQS

UDQM

LDQM

_WED

BA0

BA1

TP102

ADD(16)

D4

A0

ADD(17)

E4

A1

ADD(18)

F4

A2

ADD(19)

G4

A3

ADD(20)

G8

A4

ADD(21)

F8

A5

ADD(22)

E8

A6

ADD(23)

D8

A7

ADD(24)

D9

A8

ADD(25)

G7

A9

ADD(26)

G5

A10

A11

A12

IO1

IO2

IO3

IO4

IO5

IO6

IO7

IO8

IO9

_RE

_CE

_CS

ADD(27)

F7

ADD(28)

E7

TP103

DATA(0)

P10

DATA(1)

N10

DATA(2)

M10

DATA(3)

L10

DATA(4)

F10

DATA(5)

E10

DATA(6)

D10

DATA(7)

C10

DATA(8)

N11

DATA(9)

M11

DATA(10)

L11

DATA(11)

K11

DATA(12)

G11

DATA(13)

F11

DATA(14)

E11

DATA(15)

D11

K2

K4

K5

K8

K9

K10

L2

M2

N2

P1

P2

P3

P11

P12

R1

R2

R3

R10

R11

R12

T1

T2

T3

T10

T11

T12

10KR106

N3

TP104

F3

TP105

G3

TP106

D5

E3

C6

C7

TP107

D7

TP108

K3

L3

TP109

M3

E6

F6

L6

L7

K7

K6

D6

E5

F5

ADD(0:15)

1V8_SD

C134

C133

0.1u

1V8_SD

C137

C138

0.1u

0.1u

C140

0.1u

0.1u

0.1u

ADD(0)

ADD(1)

ADD(2)

ADD(3)

ADD(4)

ADD(5)

ADD(6)

ADD(7)

ADD(8)

ADD(9)

ADD(10)

ADD(11)

ADD(12)

ADD(13)

ADD(14)

ADD(15)

C135

0.1u

1V8_SD

TP101

L4

M4

N4

L5

M5

N5

M6

N6

M7

N7

L8

M8

N8

L9

M9

N9

A1

A2

A3

A10

A11

A12

B1

B2

B3

B10

B11

B12

C1

C2

C3

C11

C12

D1

D2

D3

E2

E9

F2

F9

G6

G9

G10

H3

H4

H5

H6

H7

H8

H9

H11

J2

J3

J4

J5

J6

J7

J8

J9

J10

J11

C4

C8

P6

P4

P8

H2

C5

C9

G2

H10

P5

P7

P9

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC26

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC38

NC39

NC40

NC41

NC42

NC43

NC44

NC45

VCCD1

VCCD2

VCCD3

VCCQD1

VCCQD2

VCCN1

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

TY9000A000TMGFU102

Page 38

- 39 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.8 LCD Display

LCD module include:

- Main LCD: 2.0” 176x220 QCIF, 262K color TFT

- Backlight : 3 piece of white LED

[Figure3.8-1] LCD circuit diagram

LCD_D0

LCD_D1

LCD_D2

LCD_D3

LCD_D4

LCD_D5

LCD_D6

LCD_D7

LCD_VSYNC

_LCD_CS1

LCD_CD

_LCD_WR

2V8_AVDD

varistor

VA305

FL301

ICVE10184E150R101FR

1

INOUT_A1

2

INOUT_A2

3

INOUT_A3

4

INOUT_A4

FL304

ICVE10184E150R101FR

1

INOUT_A1

2

INOUT_A2

3

INOUT_A3

4

INOUT_A4

FL305

EVRC14S03Q030050R

1

INOUT_A1

2

INOUT_A2

3

INOUT_A3

4

INOUT_A4

1V8_CAMCORE

C316

0.1u

varistor

VA306

5

C317

0.1u

INOUT_B1

INOUT_B2

INOUT_B3

INOUT_B4

G15G2

10

INOUT_B1

INOUT_B2

INOUT_B3

INOUT_B4

G110G2

INOUT_B1

INOUT_B2

INOUT_B3

INOUT_B4

G15G2

10

9

8

7

6

9

8

7

6

9

8

7

6

SPK_RCV_N

SPK_RCV_P

C318

39p

KEYIN3

KEYIN4

KEYIN5

KEYOUT3

KEYOUT2

KEYOUT1

KEYOUT5

END_KEY

C319

39p

varistor

VA307

varistor

VA308

CN302

G1 G2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35 36

G3 G4

2V85_VLCD

FB308

1000

VBAT

C307

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

C308

18p

0.1u

LCD_ID

C311

22p

MOTOR_P

MLED

MLED1

MLED2

MLED3

UPPER_KEY_LED

CAM_DATA_OUT7

CAM_DATA_OUT6

CAM_DATA_OUT5

CAM_DATA_OUT4

CAM_DATA_OUT3

CAM_DATA_OUT2

CAM_DATA_OUT1

CAM_DATA_OUT0

CAM_VSYNC

CAM_HSYNC

SDA

SCL

CAM_MCLK_IN

CAM_PCLK_OUT

varistor

VA303

47R310

_LCD_RESET

varistor

VA304

VT_PWR_EN

VT_CAM_RESET

70 pin main connector

ATX570124

Page 39

3.9 Keypad switching & scanning

The keypad interface is a peripheral which can be used for scanning keypads up to 8 rows (outputs

from Port Control Logic) and 8 columns (inputs to PCL). The number of rows and columns depend on

settings of the PCL.

- 40 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.9-1] Number key circuit diagram [Figure 3.9-2]

Function key circuit diagram

KEY PAD

KEYIN3

VA801

EVLC5S0250

VA802

MENU

LEFT

SOFT802

CALL

EVLC5S0250

KEYIN4

DOWN

VA803

UP

OK

EVLC5S0250

KEYIN5

SOFT801

RIGHT

SOFT803

END_KEY

VA805

EVLC5S0250

VA806

EVLC5S0250

VA807

EVLC5S0250

VA808

EVLC5S0250

END

VA804

EVLC5S0250

VBAT

KEYOUT1

KEYOUT2

KEYOUT3

KEYOUT5

NUMBER KEY PAD

KEYIN0

KB_STAR

KEYIN1

301

4

304

7

307

*

21

302

5

8

308

0

310

KEYIN2

3

303

6

306305

9

309

#

KB301

KEYOUT1

KEYOUT2

KEYOUT3

KEYOUT5

Page 40

3.10 keypad back-light illumination

3.10.1 Number keypad back-light illumination

There are 2 snow white color LEDs on Key for keypad illumination. Keypad Back-light is controlled by

SMPower3 Flash LED port which has constant current control function. The whole configuration of the

SMPOWER3 Flash LED drivers is shown in below Figure.

- 41 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.10.1-1] LED driver in the SM-POWER3

[Figure 3.10.1-2] Number key back-light LED circuit diagram

KEY BACKLIGHT

MAIN_KEY_LED

R316

100ohm

100ohmR319

LD301

C

2

SSC-SWTS1007

LD302

C

2

SSC-SWTS1007

VBAT

A

1

A

1

C321

0.1u

Page 41

- 42 -

3. TECHNICAL BRIEF

3.10.2 Function KEY back-light illumination

S-GOLD3H-LC is control the Tr for Function KEY back-light illumination.

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.10.2-1] Function KEY back-light LED circuit diagram

VBAT

SUB KEY LED

C803

1u

UPPER_KEY_LED

R801

LD801

LEBB-S14E

EVLC5S02100

VA812

LD802

R802

150

LD803

LEBB-S14E

R803

150

1KR809

R810

10K

LD804

LEBB-S14E

R804

150150

Q801

KTC4075E

LD805

LEBB-S14E

R805

150

LEBB-S14E

EVLC5S02100

VA813

LD806

R806

150

LD807

LEBB-S14E

R807

150

LD808

LEBB-S14E

R808

150

C804

1u

LEBB-S14E

Page 42

3.11 LCD back-light illumination

SC624 is high efficiency charge pump LED driver using Semtech’s proprietary mAhXLife technology.

The load and supply conditions determine whether the charge pump operates 1X, 1.5X, or 2X mode.

SC624 also provides two low-drop out, low-noise linear regulators for powering a camera module or

other peripheral circuits.

- 43 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.11-1] LCD charge pump circuit diagram

BACKLIGHT CHARGE PUMP

VBAT

1V8_CAMIO

FB204

C248

4.7u

MLED1

MLED2

MLED3 MLED_CLDO_CTRL

C249

1u

1

2

3

4

5

C2PGND

NC1

BL1

BL2

C247

1u

20

21

THER_GND

U204

SC624ULTRT

6

19

C1-

BL3

7

VIN

BL4

18

C1+

AGND

8

17

9

16

C2+

VOUT

GREF

NC2

10

LDO1

LDO2

BYP

NC3

SWIF

15

14

13

12

11

C250

2.2u

MLED

C251

C259

22n

2V8_AVDD

FB206

1u

1V8_CAMCORE

FB205

FB207

C252

2.2u

2V62_VIO

R232

DNI

R231

DNI

Page 43

- 44 -

3. TECHNICAL BRIEF

3.12 Battery voltage monitor

S-Gold3H-LC is monitor battery capacity with ADC port.

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure3.12-1] Battery voltage monitor circuit diagram

VBAT

BAT_ID

RF_TEMP

R102

390K

(1%)

R103

100K

(1%)

JACK_TYPE

R131

PCB_VERSION

24000ohm

(1%)

PA_LEVEL

F3

G4

E2

D1

F4

E3

D3

E4

D2

D4

F5

P4

M8

M0

M1

M2

M3

M4

M5

M6

M7

M8

M9

M10

PAOUT1_1

PAOUT1_2

Page 44

- 45 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.13 Audio

KP275C Audio signal flow diagram as following diagram.

[ Figure 3.13-1] Audio signal flow diagram

AN

AN

FM RADIO

FM RADIO

RADIO_OUT_L

RADIO_OUT_L

RADIO_OUT_R

RADIO_OUT_R

HS_L

32

32

I2C

I2C

EPPA1

EPPA1

EPPA2

EPPA2

EPP1

EPP1

EPN2

EPN2

I2C

I2C

K

K

HS_L

HS_R

HS_R

REC_P

REC_P

REC_

REC_

I2C

I2C

T

T

AMP

AMP

N

N

Ear-Phone

Ear-Phone

RCV/SPK

RCV/SPK

S-Gold3H

S-Gold3H

Page 45

- 46 -

3. TECHNICAL BRIEF

3.13.1 Audio amplifier

MAX9877 combines a high efficiency Class D audio power amplifier with a stereo Class AB

capacitorless Direct Drive headphone amplifier.

MAX9877 del KP275C use external AMP(MAX9877).

ivers up to 725mV from a 3.7V supply into an 8ohm load with 87% efficiency to extend battery life.

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.13.1-1] Audio AMP circuit diagram

AUDIO AMP

RADIO_OUT_R

RADIO_OUT_L

HS_R

HS_L

C423

39p

REC_P

REC_N

C4301uC431

39p

C424

39p

39p

C416 1u

C420 1u

SDA

SCL

VBAT

C403

1uC407

A3

A4

1uC411

A5

1uC412

D1

1uC415

D2

C1

C2

B2

B3

C3

2.2R405

D4

2.2R406

B4

C429

1u

C1N

C1P

INA2

INA1

INB2

INB1

BIAS

SDA

SCL

RXIN+

RXIN-

VSS

U401

MAX9877AEWP_TG45

GND

D3

C404

4.7u

B1

C5

VDD

PVDD

PGND

C4

HPR

HPL

OUT+

OUT-

A1

A2

C417

D5

B5

C427 C428

39p

C418

39p39p

39p

HSO_R

HSO_L

SPK_RCV_P

SPK_RCV_N

Page 46

3.13.2 Microphone circuit

3.13.3 Headset circuit

- 47 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.13.2-1] Microphone circuit diagram

[Figure 3.13.3-1] Headset circuit diagram

MAIN MIC

MIC401

6

G4

5

PWR

4

G3

3

G2

2

G1

1

OUT

SPM0204LE5-QB

VMIC_P

100nH

L401

C421

39p

C408

10u

1608

C413

39p

C409

39p

C422

39p

C410

DNI

0.1uC414

VMIC_GND

MAIN_MIC_N

0.1uC419

MAIN_MIC_P

VMIC_GND

18PIN MULTIPORT RECEPTACEL

2V5_VAUDB

R307

1.5K

HS_MIC_N

HS_MIC_P

22nC309

R308 2.2K

22nC310

C312

39p

HSO_L

HSO_R

C313

10u

C314

39p

FB303 1800

C315

39p

1800FB301

PRSB6.8C

VA301

PRSB6.8C

VA302

JACK_TYPE

MULTI_PORT_0

MULTI_PORT_1

JACK_DETECT

RPWRON_EN

UART_TX

UART_RX

VBAT

USB_VCHG

FL302

100nH

C301

1u

GND1 GND2

IN OUT

NFM18PC104R1C3

24pC306

1800FB302

1800

1800FB306

1800FB307

2V62_VIO

10KR306

10K

100KR304

R303

L302

FB304 1800

DSR

FB305

VCHG

FL303

C302

1u

A_MON_TX

C303

C304

NFM18PC104R1C3

39p

1u

A_MON_RX

GND1 GND2

IN OUT

DNIR333

R334 DNI

FOR RADIO

L301

270nH

CN301

21

19

1

2

2 : Headset MIC

3

3 : Jack type

4 : HSO_L

4

5 : HSO_R

5

6 : USB+/Remote_INT/MON_TXD

6

7 : USB-/Remote_ADC/MON_RXD

7

8 : JACK_D

8

9

9,10 : BATT

10

11 : R/ON

11

12

12,13 : CHG

13

14 : DSR

14

15 : VUSB

15

16 : UART_TX

16

17 : UART_RX

17

18

20

22

C305

10p

FM_ANT

R305

DNI

Short = KP270

DNI = KP275 series

Page 47

3.14 BLUETOOTH

3.14.1 General Description

The Broadcom BCM2046 is a monolithic single-chip, Bluetooth 2.1-compliant, stand-alone baseband

processor with an integrated 2.4 GHz transceiver. It employs the highest level of integration and

eliminates all critical external components, thus minimizing the footprint and implementation cost of

Bluetooth solution.

The BCM2046 is the optimal solution for any voice and/or data application that that requires the

Bluetooth SIG standard HCI Controller interface (HCI) via USB, UART, or H5 and PCM audio interface

support . The BCM2046 radio transceiver provides enhanced radio performance to meet the most

stringent industrial temperature applications or the tightest intergration into mobile handsets and

portable devices. It is fully compatible with any of the standard TCXO frequencies and provides full

radio compatibility to operate simultaneously with GPS and cellular radios.

- 48 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.14.1-1] Bluetooth Circuit Diagram

BLUETOOTH_BC

ANT401

NC1

FEED

NC2

L402

NA

0R422

C446

DNI

CLK32K

FL403

IN OUT

GND1 GND2

LFB212G45SG8A166

R419 47K

R423

100K

BT_CLK

CLK_FM

BT_VCXO_EN

BT_INT

DBB_BT_INT

10pC445

C450 10p

R413 150K

1000pC449

TP408

TP409

1V8_SD

FB403

C440

0.1u

Close to VDDO

(1%)

J3

RES

C1

RFIOP

E1

RFION

D1

RFTUNE

470pC447

J2

VCTRIFP

J5

XTAL_P

J4

XTAL_N

A5

LPO_IN

A9

SCL_TX_PU_TDO_N

A8

SDA_TX_PU_TDO

H7

GPIO7_TX_PU_TDDN_TX_PU_TDO_USB

H8

PA_CTL_GPIO6_TX_PU_TDD_TX_PU_T

G9

XTAL_PD_GPIO5_TX_PU_TDO_TX_PU_

F9

RF_ACTIVE_GPIO4

E9

BT_PRIORITY_STATUS_GPIO3

A6

TX_CONFX_WLAN_ACTIVITY_GPIO2

B6

HOST_WAKE_USB_DETACH_GPIO_1

B5

BT_WAKE_GPIO_0

Close to VDDR3V

A7

B7

VDDC1

VDDC2

VSS1

C2

H9

VDDO1

VSS2

D2

2V85_VBT

C434

2.2u

J9

D5

FB401

Close to VREG1 Close to VDDVCO

BT_LDO_EN

TP402

DNIR409

G8

A4

H1

A3

A2

B3

VREG1

VDDO2

VDDR3V

VDDVCO

VREG_CTL

VDDO_USB

VREG2_VBAT

U403

BCM2046SB1

PCM_OUT_SPDIF_OUT_SD_OUT

VSS4

VSS5E2VSS6

E4

VSS7E6VSS8

E5

F1

VSS9

VSS10

F2

VSS3

D6

FB402

C435

2.2u

0R410

A1

J1

G1

G2

B1

H4

VDDIF

VDDTF

VDDLO

VDDXO

VDDIFP

VDDPLL

PCM_CLK_SCK

PCM_IN_SPDIF_IF_SD_IN

PCM_SYNC_TX_PU_TDO

UART_CTS_N

UART_RTS_N

VSS11

VSS12

VSS13

VSS14

VSS15

F4

F5

F6

H2

H3

C436

1u

B2

VDDRF

UART_RXD

UART_TXD

HUSB_DN

HUSB_DP

RST_N

TST1

C438

C437

2.2u

0.1u

Close to VDDIFP

BT_RESETn

0R417

0R420

1V8_SD

FB404

BT_PCM_CLK

BT_PCM_TX

BT_PCM_RX

BT_PCM_SYNC

BT_UART_RTS

BT_UART_CTS

BT_UART_TX

BT_UART_RX

C442

2.2u

Close to VDDTF

TP403

B4

H5

TM2

TM1

TM0

H6

J6

D4

F8

E8

D9

D8

C8

C9

B9

B8

J8

J7

(256KHz)

R418 0

R421 0

TP404

TP405

TP406

TP407

Page 48

- 49 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

FEATURES

-Bluetooth 2.1 compliant with enhanced data rate support

-class 1 capable with built-in PA

-Programmable output power control meets Class1, Class2, or Class3 requirements

-Use supply voltages up to 5.5V

-Internal OR gate TCXO control

-Fractional-N synthesizer supports frequency references form 12MHz to 40 MHz

-Lower Power consumption

-Standard PCB and module package types available

-ARM7TDMI-S- Based microprocessor with intergrated ROM and RAM.

-supports mobile and PC applications without external memory

APPLICATIONS

-Mobile handsets and smart phones

-Personal digital assistants

-Desktop and Laptop personal computers

-Automotive telematic systems

-Computer peripheral devices (PCMCIA cards, CF cards, and USB dongles)

Page 49

- 50 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

[Figure 3.14.1-2] Bluetooth Block Diagram

XMM6070

XMM6070

I2S1ís

I2S1ís

USIF2ís

USIF2ís

BT_INT

BT_INT

DBB_BT_INT

DBB_BT_INT

KT22M- ECW29A- 26.000

KT22M- ECW29A- 26.000

BT_CLK

BT_CLK

BT_CLK

VC- TCXO

VC- TCXO

(26MHz_BT)

(26MHz_BT)

MC- 146

MC- 146

X- TAL

X- TAL

(32. 768KHz)

(32. 768KHz)

BT_CLK

CLK32K

CLK32K

PCM

PCM

UART

UART

BCM2046SB1

BCM2046SB1

BT_PCM_TX

BT_PCM_TX

BT_PCM_RX

BT_PCM_RX

BT_PCM_SYNC

BT_PCM_SYNC

BT_PCM_CLK

BT_PCM_CLK

BT_UART_TX

BT_UART_TX

BT_UART_RX

BT_UART_RX

BT_UART_RTS

BT_UART_RTS

BT_UART_CTS

BT_UART_CTS

HOST_WAKE_GPIO_1

HOST_WAKE_GPIO_1

BT_WAKE_GPIO_0

BT_WAKE_GPIO_0

XTAL_P

XTAL_P

LPQ_IN

LPQ_IN

XTAL_PD_GPIO5

XTAL_PD_GPIO5

LFB212G45SG8A

LFB212G45SG8A

BPF

BPF

2V85_VBT

2V85_VBT

1V8_SD

1V8_SD

BT ANT

BT ANT

PMB6821

PMB6821

BT_VCXO_EN

BT_VCXO_EN

PMB6952

PMB6952

BT_VCXO_EN

BT_VCXO_EN

Chip

Chip

Antenna

Antenna

Page 50

- 51 -

3. TECHNICAL BRIEF

LGE Internal Use Only

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

3.15 FM Radio

3.15.1 General Description

The Si4702 integrates the complete tuner function from antenna input to stereo audio output for FM

broadcast radio reception.

FM RADIO

FM_ANT

FM_RESET

AUDIO AMP

RADIO_OUT_R

RADIO_OUT_L

HS_R

HS_L

REC_P

REC_N

C423

39p

C430

39p

C441 100p

C424

39p

C431

39p

CLK_FM

C416 1u

C420 1u

SDA

SCL

SCL

SDA

1uC412

1uC415

2.2R405

C429

FM_INT

TP401

19

18

17

20

21

NC2

PGND

GPIO1

GPIO2

U402

_SEN

SCLK

SDIO

6

7

8

9

VBAT

C403

1u

B1

A3

VSS

VDD

U401

MAX9877AEWP_TG45

GND

D3

GPIO3

RCLK

1

NC1

2

FMIP

3

RFGND

4

GND1

5

_RST

SI4702-C19-GM

R414

10K

1uC407

A4

C1N

1uC411

A5

C1P

D1

INA2

D2

INA1

C1

INB2

C2

INB1

B2

BIAS

B3

SDA

C3

SCL

D4

RXIN+

2.2R406

B4

RXIN-

1u

C4

16

VA

VIO

10

C5

PGND

GND3

LOUT

ROUT

GND2

PVDD

2V62_VIO

2V62_VIO

C439

1u

15

14

13

12

11

VD

1V8_SD

C448

0.1u

C404

4.7u

A1

HPR

A2

HPL

D5

OUT+

B5

OUT-

C443

22n

C417

C427 C428

39p

RADIO_OUT_L

RADIO_OUT_R

HSO_R

HSO_L

C418

39p39p

SPK_RCV_P

SPK_RCV_N

39p