LG KP199 Service Manual

1

2

3

4

5

H7

Screw Hole

VDD

R101

10K_5%

FM_RESET_N[8]

LCM_ID[7]

I2C_SCL[7, 8]

I2C_SDA[7,8]

26MHZ[10]

BBWAKEUP[4]

High driving BPI port: 4mA/8mA

High driving BPI port: 4mA/8mA

High driving BPI port: 4mA/8mA

RF 3-wire interface chip select 0

RF 3-wire interface data output

RF 3-wire interface clock output

SIM card reset output

SIM card clock output

SIM card supply power control

SIM card data input/output

3

2

TP0.5-T

TP0.5-T

TP0.5-T

TP0.5-T

TP0.5-T

TP0.5-T

TP0.5-T

1 4

H5

Position Hole

H9

Position Hole

(30 mils)

TP102

TP103

TP104

TP105

TP106

TP107

TP108

C102

22pF_5%

X101

32.768KHZ

C101

22pF_5%

H1

MARK POINT

D D

C C

B B

H3

MARK POINT

H2

MARK POINT

H4

MARK POINT

H6

Position Hole

1

1

R103

10M_5%

BANDSW_DCS[10]

H10

Position Hole

/JTRST

JTCK

JTDI

JTMS

JTDO

JRTCK

/SYSRST

BT_PWR_EN[9]

BT_32K[9]

RFVCOEN[10]

SIMDATA[4]

1

1

CAMERA_PWR_EN[7]

HB_TX[10]

LB_TX[10]

PCS_RX[1 0]

PAEN[10]

LE[10]

SDATA[10]

SCLK[10]

SIMRST[4]

SIMCLK[4]

SIMVCC[4]

1

EINT0_HEADSET[5]

EINT1_HOOK_KEY[5]

EINT2_CHARGER[4]

USB_DM[5]

USB_DP[5]

/WATCHDOG[3]

R102

10K_5%

R107 100K_5%

/JTRST

JTCK

JTDI

JTMS

JTDO

JRTCK

H8

Screw Hole

1

EINT3_BT[9]

RS MMC serial clock

SD_CLK[6]

RS MMC detect input

SD_CD[6]

SD_DAT3[6]

SD_DAT2[6]

SD_DAT1[6]

SD_DAT0[6]

SD_CMD[6]

/WATCHDOG

U2

GPIO0/DSP_GPO3

M19

GPIO1/DICK

L15

GPIO2/DID

L16

GPIO3/DIMS

C17

GPIO4/DSP_CLK/DSPLCK/TRASD4

A19

GPIO5/AHB_CLK/DSPLD3/TRASD3

B18

GPIO6/ARM_CLK/DSPLD2/TRASD2

B17

GPIO7/SLOW_CLK/DSPLD1/TRASD1

A18

GPIO8/DSPLD0/TRASD0

A17

GPIO9

A2

SYSCLK

B1

XOUT

C2

XIN

C1

BBWAKEUP

D3

TESTMODE

E4

/JTRST

E3

JTCK

E2

JTDI

E1

JTMS

F5

JTDO

F4

JRTCK

F3

BPI_BUS0[HIGH DRIVING]

F2

BPI_BUS1[HIGH DRIVING]

G5

BPI_BUS2[HIGH DRIVING]

G4

BPI_BUS3

G3

BPI_BUS4

G2

BPI_BUS5

G1

BPI_BUS6/GPIO10

H5

BPI_BUS7/GPIO11

H4

BPI_BUS8/GPIO12

H3

BPI_BUS9/GPIO13/BSI_CS1

H1

BSI_CS0

J5

BSI_DATA

J4

BSI_CLK

L18

SIMRST

L17

SIMCLK

K15

SIMVCC

K16

SIMSEL/GPIO32

K17

SIMDATA

R18

/WATCHDOG

Baseband sigma-Delta Clock, 13MHz test point

ED11

ED12

ED10

ED14

ED1

ED2

ED0

ED5

ED3

ED4

P16

P19

N19

M16

M18

N15

N16

N17

N18

V2

P17

USB_DP

USB_DM

M17

MCDA0

MCDA1

MCDA2

MCDA3

MCCM0

MCCK/MCINS

MCINS/MCWP

MCPWRON/MCCK

MCWP/MCPWRON

R16

R17

R5

D15

ED0

EINT0V1EINT1U3EINT2W1EINT3

MFIQ/GPIO42

MIRQ/GPIO41

NC/ESDM_CK

U101A

MT6226/6226M/6227

R15

T19

T17

U19

U18

ED1

ED2

ED3

ED4

ED13

ED6

ED7

ED8

ED9

W17

T16

W16

T15

V18

W19

U17

V17

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

DAIPCMOUT/GPIO44/TDMA_D1/TRASYNC

U15

FM_32KHZ [8]

ESDM_13MHZ

ED[0..15] [3]

ED15

V15

K4

R3

R2

J1

J2

J3

K3

T4

ED14

ED15

LSCE0B/GPIO19

LSCK/GPIO16/TBTXEN

LSCE1B/GPIO20/LPCE2B

NRNB/GPIO25/DSP_TID1/MCU_TID1

NCLE/GPIO26/DSP_TID2/MCU_TID2

NALE/GPIO27/DSP_TID3/MCU_TID3

NWEB/GPIO28/DSP_TID4/MCU_DID

NREB/GPIO29/DSP_TID5/MCU_DFS

NCEB/GPIO30/DSP_TID6/MCU_DCK

IRDA_TXD/GPIO38/URTS2

IRDA_RXD/GPIO37/UCTS2

DAICLK/GPIO43/TDMA_CK/TRA_CLK

DAIPCMIN/GPIO45/TDMA_D0/TRASD7

DAIRST/GPIO47/TDMA_FS/TRASD6

DAISYNC/GPIO46/BFEPRBO/TRASD5

KROW0

KROW1

KROW2

LSDA/GPIO18

KROW3

PWM1/GPIO21

KROW4

KROW5

KCOL0

LSA0/GPIO17/TDTIRQ

KCOL1

PWM2/GPIO22/DSP_GPO

KCOL2

KCOL3

ALERTER/GPIO23/DSP_GPO

KCOL4

KCOL5

KCOL6

IRDA_PDN/GPIO39

UTXD2/GPIO36/URTS3

URXD2/GPIO35/UCTS3

URXD3/GPIO33

UTXD3/GPIO34

URTS1

UCTS1

UTXD1

URXD1

IBOOT(XAB)

NLD7

NLD6

NLD5

NLD4

NLD3

NLD2

NLD1

NLD0

TP101

TP0.5-T

FM_/SEN [8]

LSCE0B [4]

LSCK [4]

PWM_LCD_EN [7]

D19

D16

E18

E17

E16

F19

F18

F17

F16

F15

G19

G18

G17

M5

M4

M3

N5

N4

N3

N2

N1

P5

P4

P3

P2

P1

R4

G16

G15

H17

J19

J18

H15

H16

J17

J16

K19

K18

E5

D17

D18

C19

C18

B19

LSDA [4]

Nand flash data port 7

Nand flash data port 6

Nand flash data port 5

Nand flash data port 4

Nand flash data port 3

Nand flash data port 2

Nand flash data port 1

Nand flash data port 0

NRNB

NCLE

NALE

NWEB

NREB

NCEB

DAI clock output

DAI pcm data output

DAI pcm data input

DAI reset signal input

UTXD1

URXD1

DAICLK

DAIPCMOUT

DAIPCMIN

DAIRST

DAISYNC

NLD7 [3,7]

NLD6 [3,7]

NLD5 [3,7]

NLD4 [3,7]

NLD3 [3,7]

NLD2 [3,7]

NLD1 [3,7]

NLD0 [3,7]

NRNB [3]

NCLE [3]

NALE [3]

NWEB [3]

NREB [3]

NCEB [3]

BT_RESET [9]

URXD3_BT [9]

UTXD3_BT [9]

DAICLK [9]

DAIPCMOUT [9]

DAIPCMIN [9]

DAISYNC [9]

KROW0 [6]

KROW1 [6]

KROW2 [6]

KROW3 [6]

KROW4 [6]

KROW5 [6]

KCOL0 [6]

KCOL1 [6]

KCOL2 [6]

KCOL3 [6]

KCOL6 [4]

TP0.5-T

TP114

TP0.5-T

TP115

UTXD1 [5]

URXD1 [5]

R104

100K_5%

0402R

/SYSRSTU1SRCLKENA/GPO0T1SRCLKENAN/GPO1

LPCE1B/GPIO24/DSP_TID0/MCU_TID0

SRCLKENAI/GPIO31

LPCE0BL5LRSTBL4LRDBL3LWRBL1LPA0

LWRB[7]

LPA0[7]

LRDB[7]

LRSTB[7]

LCM_MAIN_CS[7]

/SYSRST[3,4]

VCXOEN[4,10]

BT_SRCLKENA[9]

A A

1

2

L2

T3

T2

K2

W2

EA11

EA9

EA10

EA8

EA15

EA17

EA16

EA20

EA18

EA19

EA22

EA21

EA23

EA24

EA7

EA13

EA14

EA12

3

EA0

EA1

EA2

EA3

EA4T9EA5U9EA6V9EA7R8EA8T8EA9W8EA10R7EA11T7EA12U7EA13V7EA14R6EA15T6EA16U6EA17W6EA18T5EA19U5EA20V5EA21W5EA22V4EA23U4EA24W3EA25

T10

R10

U10

W10

EA1

EA2

EA3

EA4

EA6

EA5

/ECS0

/EWR

/ERD

/EUB

/ELB

/EPDN/GPO2

T14

T11

R13

U14

R14

W14

EA[1..24] [3]

/ECS1

T13

/EADV

ECLK

/ECS7/GPIO40

/ECS6/GPIO52

/ECS5/GPIO53

/ECS4/GPIO54

/ECS3

/ECS2

U13

EWAIT

T12

V11

V13

U11

U12

R12

R11

W12

/ECS1_PSRAM

/ECS0_FLASH

/EWR

/ERD

/EUB

/ELB

/ECS1_PSRAM [3]

/ECS0_FLASH [3]

/EWR [3]

/ERD [3]

/EUB [3]

/ELB [3]

4

DAICLK

DAIPCMOUT

DAIPCMIN

DAIRST

DAISYNC

TP109 TP0.5-T

TP110 TP0.5-T

TP0.5-T

TP111

TP112 TP0.5-T

TP113

TP0.5-T

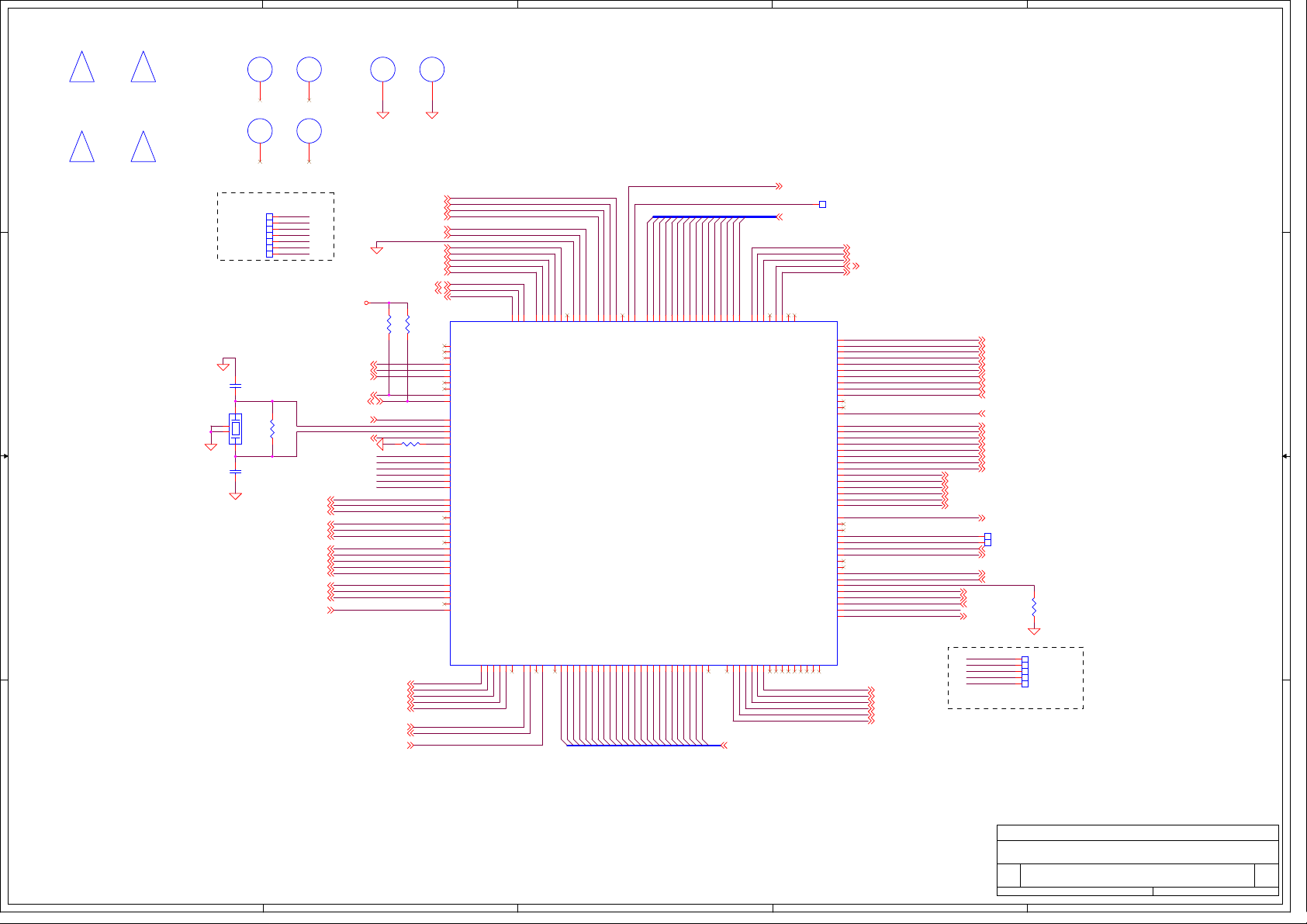

Title

MT6226-01

Size Document Number Rev

<Doc> 1A

A3

Date: Sheet

5

of

112Wednesday, June 04, 2008

5

D D

4

3

U101C

MT6226/6226M/6227

2

1

AFC_BYP

AFC

BUPAIP

BUPAIN

BUPAQN

BUPAQP

BDLAIP

BDLAIN

BDLAQN

BDLAQP

APC

AUXADIN0

AUXADIN1

AUXADIN2

AUXADIN3

AUXADIN4

AUXADIN5

AUXADIN6

A4

B4

B8

A8

C8

D8

B9

A9

C9

D9

B7

D6

C6

B6

A6

C5

B5

A5

D5

VCORE

VAFC [10]

I[10]

IB [10]

QB [10]

Q[10]

VAPC [10]

ADC0_I- [4]

ADC1_I+ [4]

ADC2_TBAT [4,6]

ADC3_VCHG [5]

ADC5_MIC [5]

ADC6_USB [5]

C218

C219

33pF_5%

33pF_5%

C220

1nF

C216

33pF/5%

U101D

MT6226/6226M/6227

L12

CMDAT0

CMDAT1

CMDAT2

CMDAT3

M9

CMDAT4

M8

CMDAT5

L8

CMDAT6

K8

CMDAT7

J8

CMDAT8

H8

CMDAT9

CMVREF

CMHREF

J12

CMRST

CMPDN

CMMCLK

H9

CMPCLK

B15

AU_MOUTL

A15

AU_MOUTR

C14

AU_M_BYPL

C13

AU_M_BYPR/AU_OUT1_N

D13

AU_RBIAS/AU_OUT1_P

B14

AU_FMINL

A14

AU_FMINR

B12

AU_OUT0_N

A12

AU_OUT0_P

C12

AU_MICBIAS_P

D12

AU_MICBIAS_N

C11

AU_VREF_N

B11

AU_VREF_P

D10

AU_VIN0_P

C10

AU_VIN0_N

B10

AU_VIN1_N

A10

AU_VIN1_P

C217

33pF/5%

NC/VDD33_ANA

NC/VDD33_ANA

NC/VSS33_ANA

VCORE/VDD33

NLD16/UPLL_OUT

NLD17/MPLL_OUT

PLL_OUT/VSS33_ANA

A1

NC

E6

E13

E7

E11

G6

F6

E12

VSS

J15

NC

K5

NC

R9

NC

J9

NLD8

J10

NLD9

J11

NLD10

K9

NLD11

K11

NLD12

L9

NLD13

L10

NLD14

L11

NLD15

MP3_OUTL[4,5]

MP3_OUTR[5]

U101B

VMEM

C204

100nF_10%

C C

VCORE

C206

100nF_10%

VUSB

VRTC

B B

MT6226/6226M/6227

W4

VDD33_EMI

W7

VDD33_EMI

W9

VDD33_EMI

W11

VDD33_EMI

W13

VDD33_EMI

W15

VDD33_EMI

W18

VDD33_EMI

T18

VDD33_EMI

V6

VSS33_EMI

U8

VSS33_EMI

V10

VSS33_EMI

V12

VSS33_EMI

V14

VSS33_EMI

U16

VSS33_EMI

V19

VSS33_EMI

R19

VSS33_EMI

C16

VDDK

D1

VDDK

M1

VDDK

H19

VDDK

V8

VDDK_EMI

V16

VDDK_EMI

A16

VSS33_ANA

E14

VSS33_ANA

A3

NC/VSS33_ANA

P15

VDD33_USB

B2

AVDD_RTC

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33_MC/NC

NC/VDD33_ANA

VDD33_IS

VSS33

VSS33

VSS33

VSS33

VSS33

VSS33

VSS33

AVDD_PLL

AVDD_MBUF

AVDD_BUF

AVDD_GSMRFTX

AVDD_RFE

AUX_REF

AVDD_AFE

AVSS_PLL

AVSS_MBUF

AVSS_BUF

AGND_AFE

AVSS_AFE

AGND_RFE

AVSS_GSMRFTX

AVSS_RFE

F1

K1

R1

L19

E19

M15

D4

E15

D2

H2

M2

V3

P18

H18

B16

B3

C15

B13

D7

A7

C4

D11

C3

D14

A13

A11

E10

E9

E8

C7

VDD

C205

100nF_10%

C208

100nF_10%

AVDD

C207

100nF_10%

B201

BLM18HD102SN1D

SPKN0[5]

SPKP0[5]

C211

33pF/5%

R208 51K/1%

C212

33pF/5%

MICBIASP

MICBIASN

VREFN

VREFP

MICP0[5]

MICN0[5]

MICN1[5]

MICP1[5]

C209 0.1uF/DNI

FM_INL[8]

FM_INR[8]

C214

33pF/5%

Raw bit

CMDATA2[7]

CMDATA3[7]

CMDATA4[7]

CMDATA5[7]

CMDATA6[7]

CMDATA7[7]

CMDATA8[7]

CMDATA9[7]

CMVREF[7]

CMHREF[7]

CMRST[7]

CMMCLK[7]

CMPCLK[7]

C210 0.1uF/DNI

C201 0.1uF

C202 0.1uF

C213 47nF/10%

C215

33pF/5%

M12

M11

M10

H12

H11

K12

H10

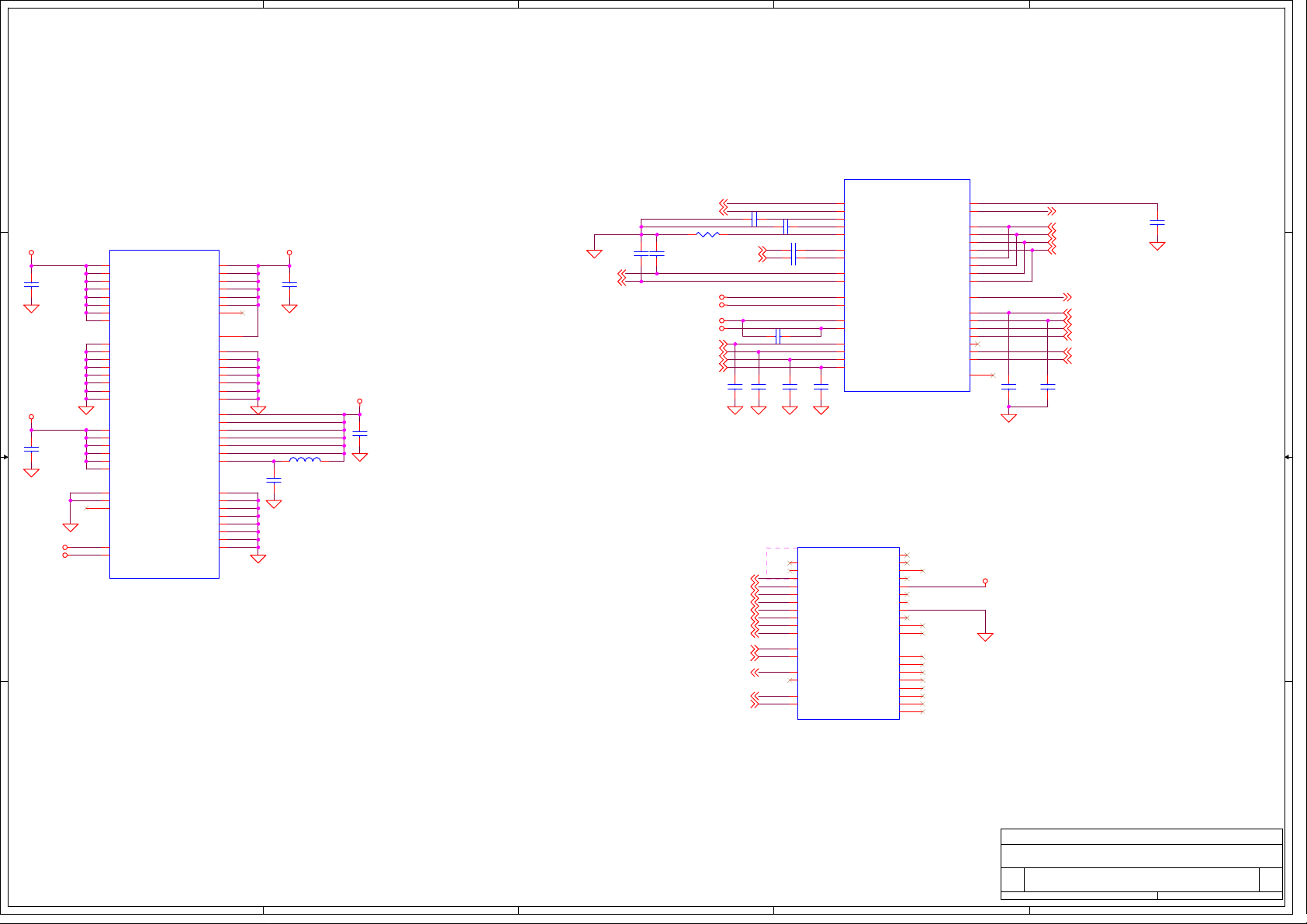

A A

Title

MT6226-02

Size Document Number Rev

<Doc> 1A

A3

5

4

3

2

Date: Sheet of

212Wednesday, June 04, 2008

1

5

4

3

2

1

D D

VMEM

C C

C301

100pF_5%

R301

47K_5%

R302

47K_5%C302

100nF_5%

NCEB

NCEB[1]

NRNB

NRNB[1]

B B

TOSHIBA MCP

TV00679002CAGD 128M+64M+512M

ED[0..15][1]

/SYSRST[1,4]

EA[1..24][1]

ED0

J3

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

NLD0

NLD0[1,7]

NLD1

NLD1[1,7]

NLD2

NLD2[1,7]

NLD3

NLD3[1,7]

NLD4

NLD4[1,7]

NLD5

NLD5[1,7]

NLD6

NLD6[1,7]

NLD7

NLD7[1,7]

NCLE

NCLE[1]

NALE

NALE[1]

NREB

NREB[1]

NWEB

NWEB[1]

/SYSRST

EA24

DQ0

G4

DQ1

K4

DQ2

H5

DQ3

H6

DQ4

K7

DQ5

G7

DQ6

J8

DQ7

K3

DQ8

H4

DQ9

J4

DQ10

K5

DQ11

J7

DQ12

H7

DQ13

K8

DQ14

H8

DQ15

L6

I/O1

L7

I/O2

L8

I/O3

L9

I/O4

K9

I/O5

K10

I/O6

J10

I/O7

H10

I/O8

F10

VCCn

F1

VCCn

H1

CLE

J1

ALE

E1

CEn

D1

REn

K1

WEn

K2

WPn

C1

RY/BYn

A1

NC

A2

NC

A9

NC

A10

NC

B2

NC

B3

NC

B4

NC

B5

NC

B6

NC

B7

NC

B8

NC

B9

NC

B10

NC

C2

NC

C9

NC

C10

NC

D10

NC

E10

NC

F5

NC

F6

NC

G5

NC

G6

NC

G8

NC

U301

TV00679002CAGD

TV00578002

CE1ps

CE2ps

WP/ACC

RY/BYf

RESET

VCCf

VCCps

VSS

VSS

VSS

VSS

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

CEf

WE

OE

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

LB

UB

G2

F2

E2

D2

F3

E3

D3

C3

C7

E7

F7

C8

D8

E8

F8

D9

G9

F4

E4

D7

E6

E9

F9

/ERD

H3

/ECS0_FLASH

H2

/ECS1_PSRAM

J2

D6

C6

C5

C4

D4

E5

D5

J5

J6

M10

M9

M2

M1

L10

L5

L4

L3

L2

L1

K6

H9

G1

G3

G10

J9

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

EA10

EA11

EA12

EA13

EA14

EA15

EA16

EA17

EA18

EA19

EA20

EA21

EA22

EA23

/WATCHDOG

C303

100nF_5%

EA[1..24] [1]

/EWR

/ELB

/EUB

/ERD [1]

/ECS0_FLASH [1]

/ECS1_PSRAM [1]

/EWR [1]

/ELB [1]

/EUB [1]

/WATCHDOG [1]

VMEM

A A

Title

MCP

Size Document Number Rev

<Doc> 1A

A3

5

4

3

2

Date: Sheet of

312Wednesday, June 04, 2008

1

5

MT6318

Vcore 1.8/1.2V

VIO 2.8V

VA 2.8V

VTCXO 2.8V

D D

VM 2.8/1.8V VMEM 2.8V

VSIM 1.8/3V

VRTC 1.5/1.2V

VSW_A 2.8/3.3V

VMC 2.8/3V

V_USB 3.3V

VIBR 3.2V/1.8V

C C

VDD

B B

VCHG

C4011u/16V/0603

A A

R401

4

G

D5D

Driving

200mA

100mA

150mA

20mA

150mA

20mA

0.6mA

50mA

250mA

20mA

200mA

KCOL6[1]

1

3

0R

2

3

S

K7K

6

Reserve LC if Charge

Pump used to supply

backlight power

D401

1 2

RB520S-30

2

GDRVAC

A1A

NTHD4P02FT1G

8

U402

ISENSE

MT6226

VCORE 1.8V

VDD 2.8V

AVDD 2.8V

VTCXO 2.8V

VSIM 1.8/3V

VRTC 1.5V

VBT 2.8V

VUSB 3.3V

VIB 3.2V

ADC2_TBAT[2,6]

VBAT

4.7u (0603 X5R 6.3V)

Remark

VD_SEL=1

VMSEL=1

RTC_SEL=1

VMCSEL=L

VIBSEL=1

R403 100k

C402

PWRKEY [5,6]

BBWAKEUP[1]

[PWR ON/OFF]

[END]

EINT2_CHARGER[1]

VBAT

LSCE0B[1]

LSCK[1]

LSDA[1]

SIMVCC[1]

SIMCLK[1]

SIMRST[1]

SIMDATA[1]

SIM_CLK[6]

SIM_RST[6]

SIM_IO[6]

TP401TP0.5-T

VCXOEN[1,10]

ADC0_I-[2]

ADC1_I+[2]

4

VCHG

GDRVAC

ISENSE

C403

2.2uF/10V (X5R)

VBAT

B10

D10

H10

K10

E1

D1

E2

D2

F2

F1

H2

G2

J1

J2

J3

D9

A8

B8

C8

A5

B5

C5

D5

K7

A9

G9

K4

B9

J4

H5

H3

C9

E9

F8

G8

J8

H9

K9

J7

J9

H8

100n/10V (X5R)

U401

AC

USB

GDRVAC

GDRVUSB

ISENSE

VBAT

SEL1

SEL2

BAT_ON

PWRIN1

PWRIN1

PWRIN1

PWRIN2

PWRIN2

PWRIN3

PWRIN3

PWRIN3

PWRIN4

PWRIN4

PWRIN4

PWRIN4

PWRKEY

PWRBB

SRCLKEN

VMSEL

INT

VB_OUT

Isense_OUT

SEL1_EN

RTC_SEL

VD_SEL

SPICS

SPICK

SPIDAT

SIMVCC

SIMCLK

SIMRST

SIMIO

SCLK

SRST

SIO

C405

BAT_BACKUP

A10

D6

R405 3.9K

C404 100n/10V (X5R)

J6

AUDN

MT6318

GND3D8GND3E8GND4C3GND4C4GND4C6GND4C7GND4D4GND4

GND3

F7

E7

2 step RTC

[2,5]

J5

MP3_OUTL

C406 100n/10V (X5R)

AUDP

[5]

SPK-

K6

SPK-

[5]

SPK+

K5

12

+

V

-

SPK+

GND2H4GND2G5GND2G6GND2H6GND2G7GND2H7GND3D7GND3

RSTCAP

BP/VREF

3

BLDRV

CS_BL

DC_OV

FB_BL

LEDKP

CS_KP

C2+

C1+

C1-

VO_R

VO_G

VO_B

RESET

VD

VIO

VA

VTCXO

VM

VSIM

VRTC

VSW_A

VMC

V_USB

VIBR

GND1

GND1

GND1

GND1

GND1

GND1

GND1

BAT401

XH414HGV01E

A7

B6

B4

A6

A1

B3

A2

A3

C410

A4

1uF/10V (X5R)

R415 0R/DNI

B2

R416 0R/DNI

B1

R417 0R/DNI

C2

F9

B7

K2

C412

1uF/10V (X5R)

J10

C10

K1

H1

G1

K8

G10

E10

K3

C1

F10

D3

E3

F3

G3

E4

F4

G4

C413 1uF/10V(X5R)

22n/10V (X5R)

C415 4.7u (0603 X5R 6.3V)

C414 10u (0805 X5R 6.3V)

C411

C423

4.7U/0603C

VCORE_EN

LEDKP [6]

CS_KP [6]

V_C2+ [7]

C409

4.7U (0603 X5R 6.3V)

R406 0R

R407 0R

R408 0R

R409 0R

C416 4.7u (0603 X5R 6.3V)

C417 2.2u (0603 X5R 6.3V)

100n/10V (X5R)C418

VBAT

R411

0R/0402R

LCM_LED1 [7]

LCM_LED2 [7]

LCM_LED3 [7]

VCORE_EN

C419 2.2u (0603 X5R 6.3V)

C421 2.2u/(0603 10V X5R)

C420 4.7u (0603 X5R 6.3V)

2

DC/DC converter to Vcore

C422 2.2u/(0603 10V X5R)

U404

1

Vin

2

GND

EN3FB

TPS62200

R413

100k

R414 0R/DNI

1 2

VDD

RB520S-30

AVDD

VMEM

VSIM

M401

DC VIBRATOR

SW

D402

R410

5

4

VRTC

VSW_A

VBT

VUSB

M

VCORE

0R /0603

10UH

L401

VIB

1 2

21

D403

RB520S-30

RB520S30T1

C425

100pF

/SYSRST [ 1,3]

C426

0.1uF

430K

160K

1

VCORE

R412

C424

10uF/0805C

R402

R404

0.1 (1% 0805 1/4W)

VBAT

5

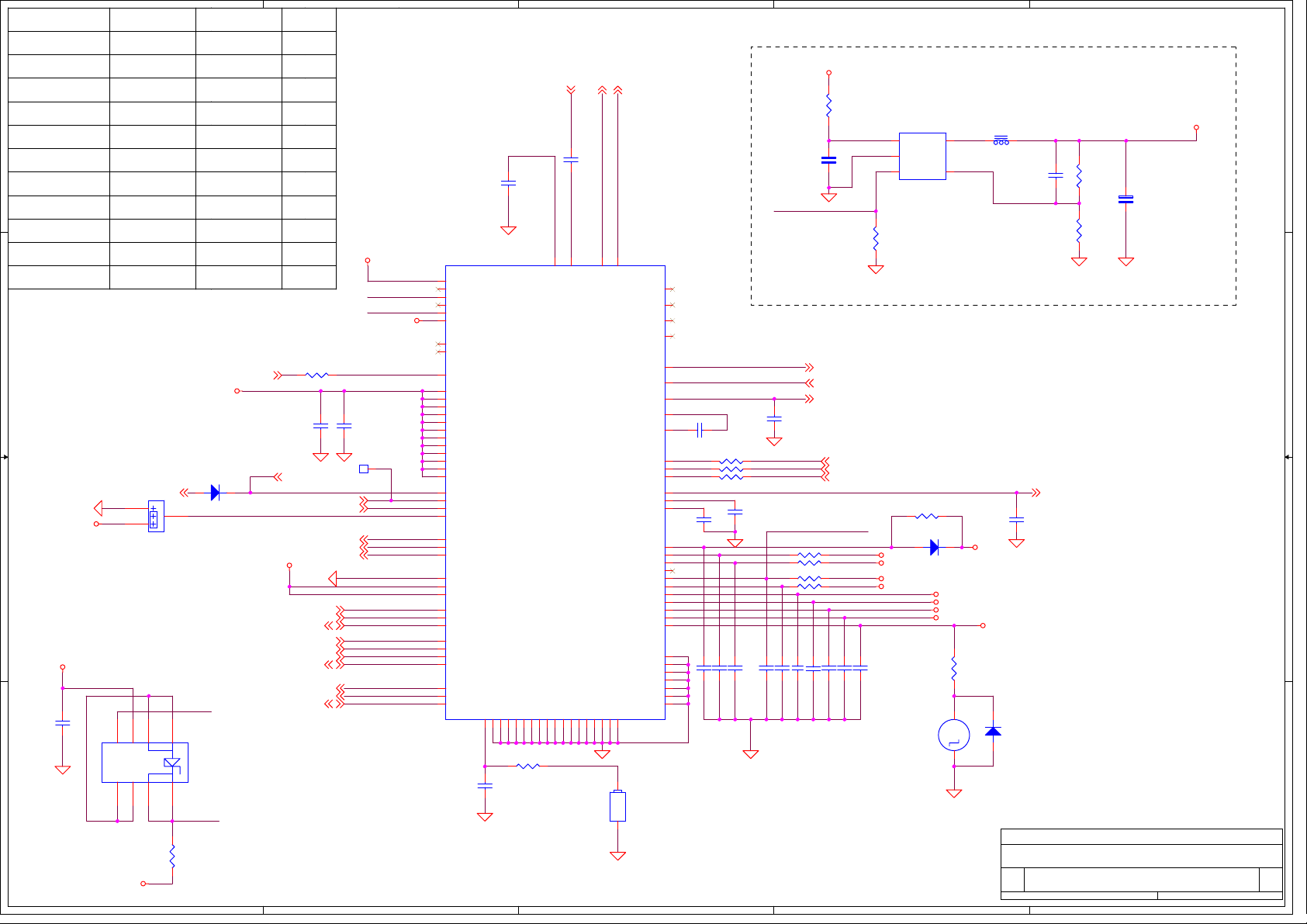

Title

PMIC

Size Document Number Rev

1A

A3

4

3

2

Date: Sheet

412Wednesday, June 04, 2008

1

1A

of

5

MICBIASP

R501

1K

4

3

2

1

UART1&PWR

TP501

TP502

TP503

TP504

TP505

> 2.0V :AC Charger

< 2.0v :USB

VBAT

PWRKEY[4,6]

UTXD1[1]

URXD1[1]

Normal MIC Input

D D

C501

MICP0[2]

100n/10V (X5R)

C502

10u (0805 X5R 6.3V)

C503

MICN0[2]

100n/10V (X5R)

C C

MICN1[2]

100n/10V (X5R)

C520

MICP1[2]

100n/10V (X5R)

B B

A A

ADC5_MIC[2]

SPK+[4]

SPK-[4]

R520 1k

5

MICBIASN

C516

100p

C517

33p

R502

1.5K

R503

1.5K

R504

1K

C521

C523

C518

33p

33p

C522

100pF

33p

MIC_H-

MIC_H+

MICBIASP

R514

1K

R515

1.5K

B504

MLG1608B47NJT

B505

MLG1608B47NJT

10u (0805 X5R 6.3V)

C515

EINT1_HOOK_KEY[1]

Use TVS

1

.

T514

.

2

1

.

.

T515

2

C504

100p

C505

C506

33p

33p

EINT0_HEADSET[1]

C508

0.1uF/DNI

E501

PAD2X3

1

E502

PAD2X3

1

Loudspeaker

C530

10p

R516

100k/DNI

12

4

VDD

1 2

C529

10p

VDD

R513

100K

U501

1

NCS2200SN2T1

OUT

VCC

VEE

V+3V-

1

.

T501

.

2

VCE(22p)

MP3_OUTL[2,4]

MP3_OUTR[2]

USB_DP[1]

USB_DM[1]

5

2

4

1

.

T502

.

2

VCE(22p)

1

2

MIC501

Microphone

Use TVS

R521 0R/0603R

SPKP0[2]

SPKN0[2]

C507

0.1uF

ADC6_USB[2]

R509 43R

R510 43R

L504 0R

L503 0R

VDD

VDD

12

C524

33p

C525

100p

C526

33p

R505

120K

VUSB

C510 47u (1210 X5R 6.3V)

C511 47u (1210 X5R 6.3V)

R517

1 2

R507

1 2

100k

22k

ADC3_VCHG[2]

3

D502

RB520S-30

1 2

R506

560K

R511 3 3 R

R512 3 3 R

VCHG

C527

10p

C528

10p

C513

33p

R518

100K/1%

R519

24K/ 1%

Use TVS

1

2

1

2

C512

C509

.

T516

.

T517

.

.

R508

1.5K

100p

C514

33pC519

F501 FUSE(1A 0603)

2.2U/0805C/(25V, X5R)

Receiver

SP502

+

_

SDRP0615FJ04-F6-G

VUSB

FM_ANT[8]

VBAT

PWRKEY[4,6]

UTXD1[1]

URXD1[1]

B501

MMZ1608S121AT

B502

MMZ1608S121AT

B503

MMZ1608S121AT

L502

L501

270nH/DNI

270nH

1

1

.

.

.

.

2

2

T505 6V_0.2pF

T504 6V_0.2pF

Use TVS Use TVS

2

Use TVS

Title

Size Document Number Rev

Date: Sheet of

1

.

T518

.

6V_0.2pF

2

1

1

1

.

.

.

.

2

2

2

T509 24V_3pF

T511 24V_3pF

T503 6V_0.2pF

ACOUSTIC

A3

.

.

1

1

.

.

.

.

2

2

T512

T513

Use TVS

T510

1

2

1

.

.

2

1

.

.

2

T508

Use TVS

J501

1

GND

2

EAR-MIC

3

TV-OUT

4

EAR-L / UART_CTS

5

EAR-R / UART_RTS

6

USB_D+

7

USB_D-

8

HS_DET

9

VBAT_OUT1

10

VBAT_OUT2

11

PWR_ON

12

VCHG

13

VCHG

14

UART_DSR

15

VUSB

16

UART_TX

17

UART_RX

18

GND

Accessery IO (18 PIN)

1

.

.

.

.

GND

GND

GND

GND

19

20

21

22

2

T507

T506

512Wednesday, June 04, 2008

1

1A

Loading...

Loading...