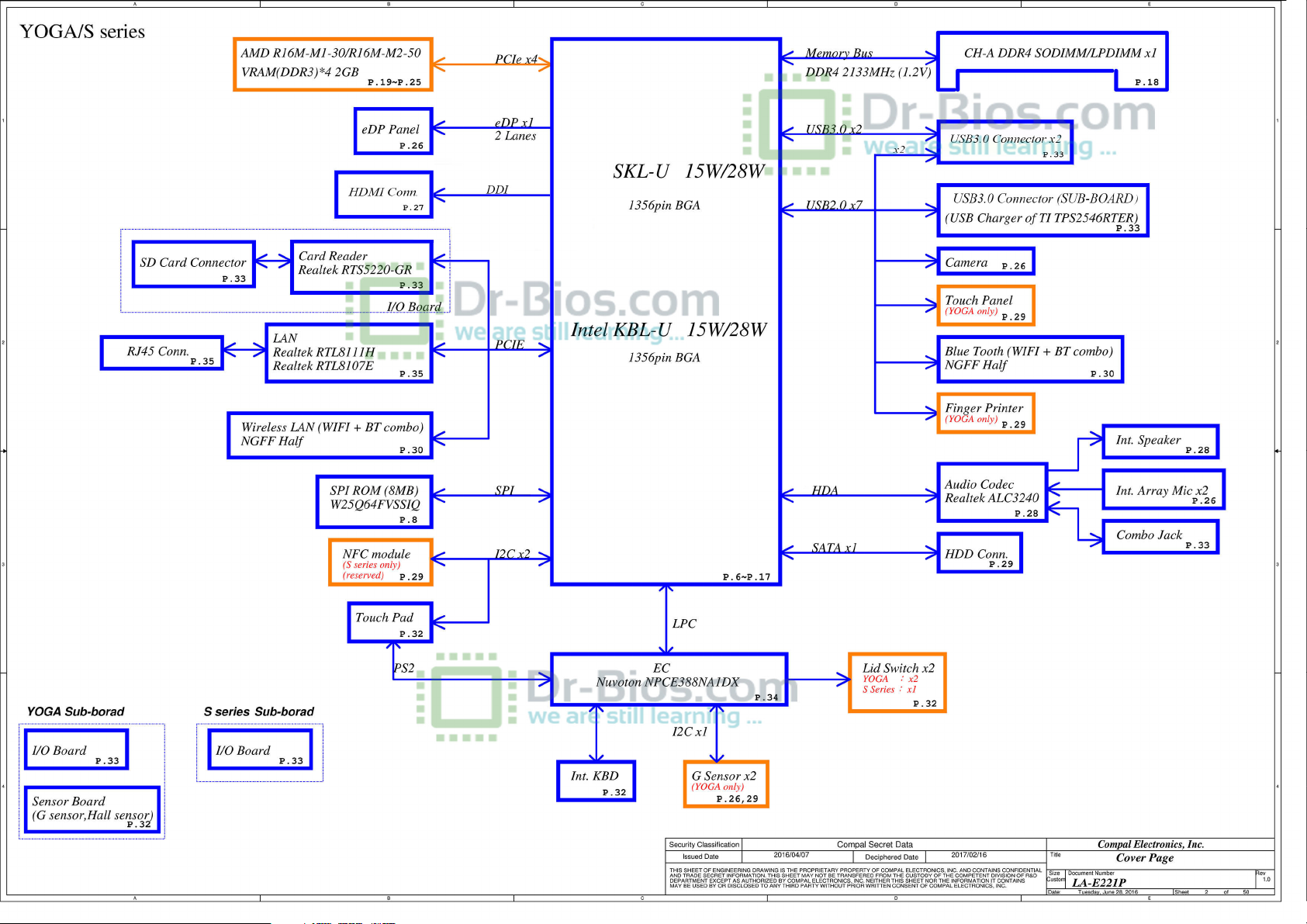

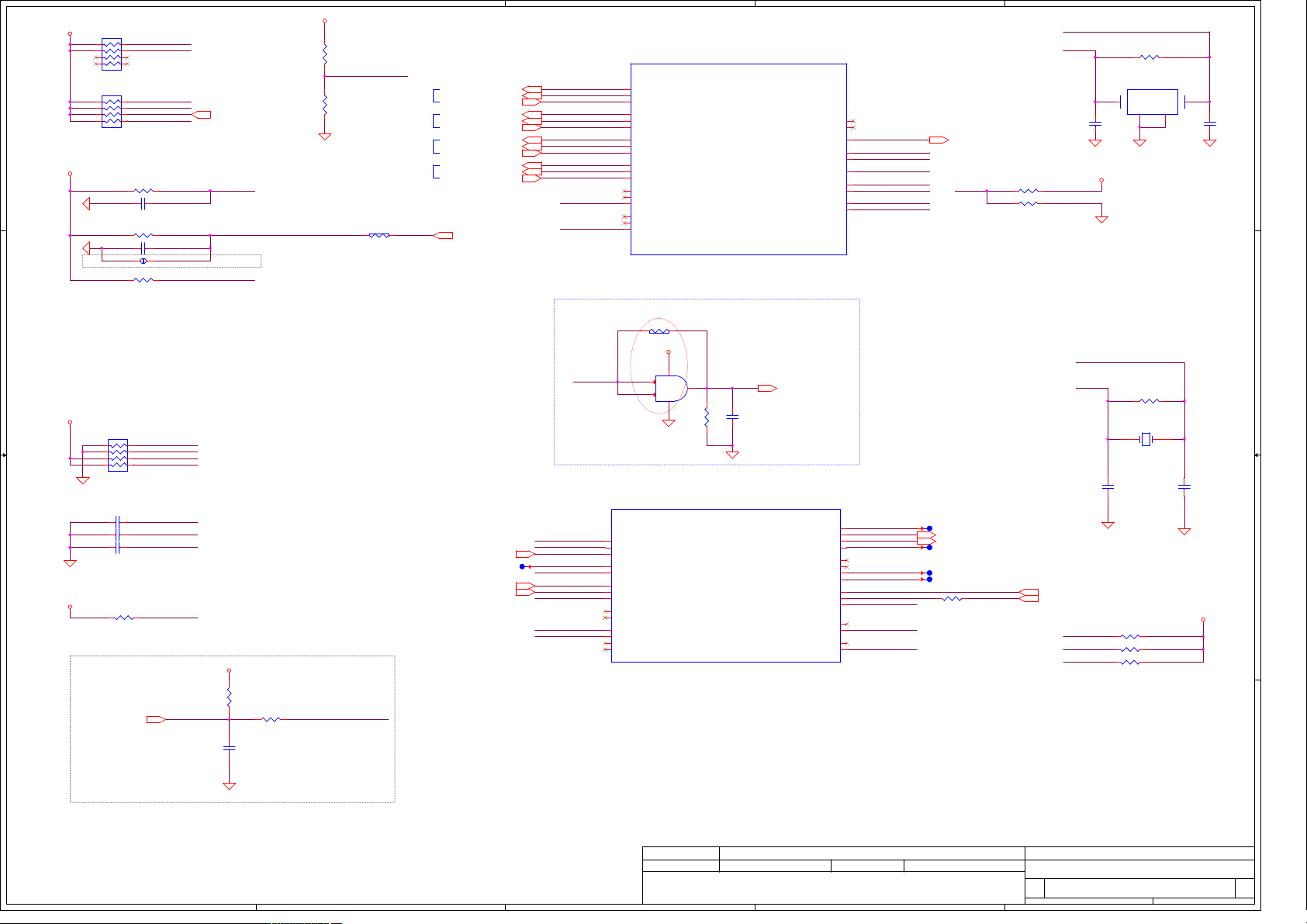

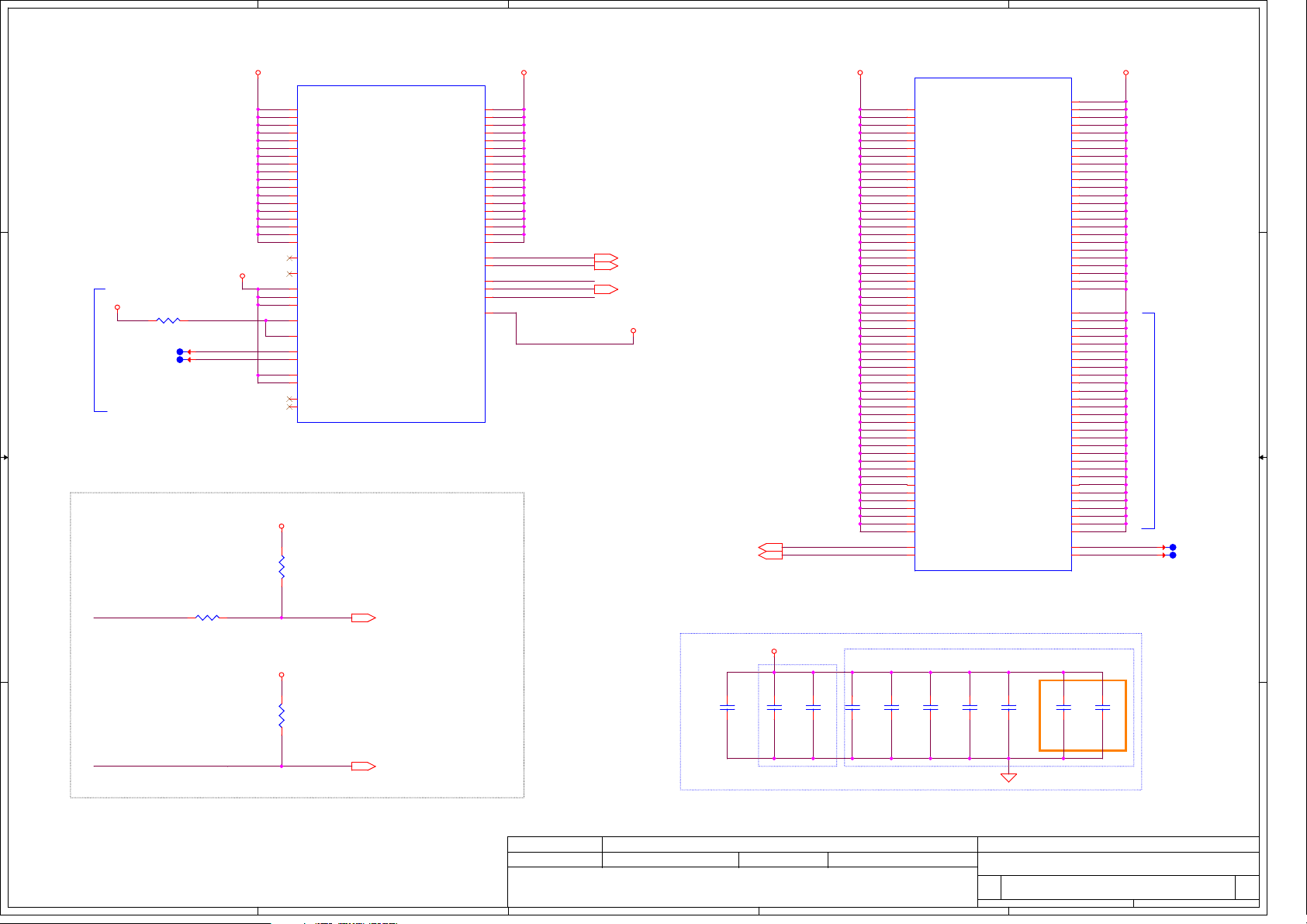

Lenovo Yoga 520 14IKB Schematic

A

1 1

B

C

D

E

Compal Confidential

BIUS4/S5 & CIUY0/Y1

2

DIS M/B Schematics Document

2

Intel KabyLake U Processor with DDR4

AMD R16M-M1-30/R16M-M2-50

3

2016-06-27

3

LA-E221P

REV

4

Security Classificati on

Security Classificati on

Security Classificati on

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

!

!

1.0

!!

Compal Secret Data

Compal Secret Data

2016/04/07 2017/02/16

2016/04/07 2017/02/16

2016/04/07 2017/02/16

C

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-E221P

LA-E221P

LA-E221P

1.0

1.0

1.0

of

150Tuesday, June 28, 2016

of

150Tuesday, June 28, 2016

of

150Tuesday, June 28, 2016

E

A B C D E

1

2

3

4

5

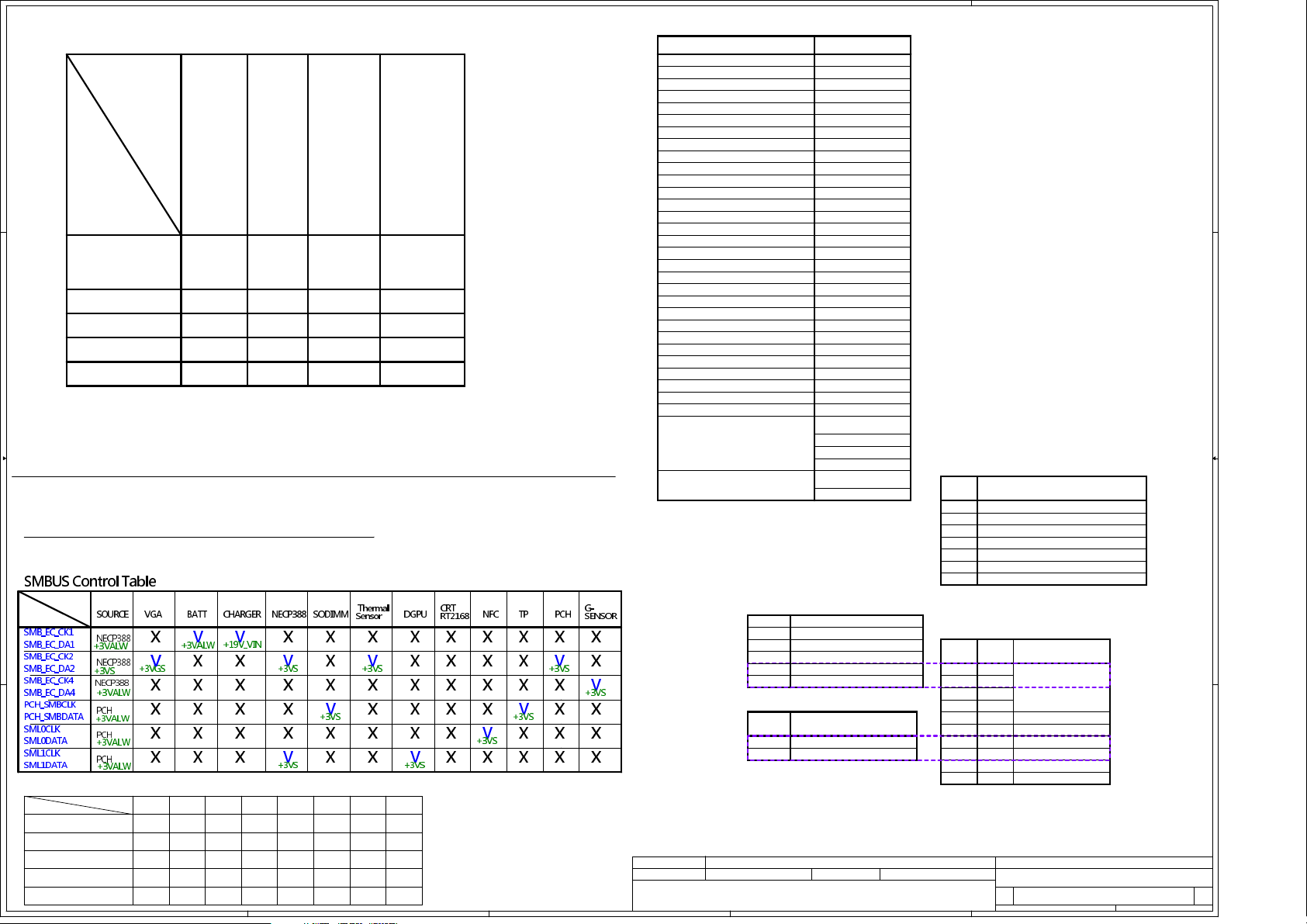

BOM Structure Table

Voltage Rails

+5VS

power

State

S0

S3

S5 S4/AC

plane

B+

O

O

O

O

+5VALW

+3VALW

O

O

O

X

+1.5V

OO

O

X

X

A A

B

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

+3VS

+1.35VS

+1.0VS_VCCOPC

+VCC_CORE

+VGA_CORE

+VCC_GFXCORE_AXG

+1.8VS

+0.75VS

+1.0VALW

X

XX

X

XXX

Item

LAN 10/100 Transformer

For Giga LAN Chip

For 10/100 LAN Chip

For DIS DIS@

For UMA UMA@

For GPU M1 Chip

For GPU M2 Chip

For Thermal Chip EX_THM@

For Keyboard backlight KBL@

For K/B 15 inch NUM LED

For VARM X76 GM_X76@

For Hynix Memory

For Samsung Memory

For Micron Memory

For EMI

For ESD

No EMI

No ESD

No RF

For RF

Connector ME@

For Test Point TP@

For 2+3E power 23E@

For YOGA series only

For 14 inch only

For 15 inch only

For 15 inch UMA_EXTRA

For SKL CPU Type

EC SM Bus1 address

Device

Smart Battery

Address

0001 011x 16h

PCH SM Bus address

DDR_JDIMM1

Touch Pad

C

AddressDevice

1010 000x A0h

EC SM Bus2 address

Device

NCT7718W NFC

Address

1001 100x 98h

EC SM Bus4 address

Device Address

BMA250E

0001 100X 18h

GPU SM Bus address

AddressDevice

Internal thermal sensor

1001 111x 9Eh

ME SM Bus address

AddressDevice

0010 1000 28h

For KBL CPU Type

Port

1

2

3

4

5

6

SATA Port Table

Port

0

1

D

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1#

LOW

HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW

LOWLOW

1

SLP_S4#SLP_S3# +V+VALWSLP_S5# Clock+VS

HIGH

HIGH

HIGH

LOWLOW

ONONON

ON

ON

ON

ON

ON

OFF

OFF

ON

OFF

OFF

OFF

HIGHHIGHHIGH

HIGH

ONON

LOW

OFF

OFF

OFF

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN C ONSENT OF COMPAL ELECTRON ICS, INC.

3

2016/04/07 2017/02/16

2016/04/07 2017/02/16

2016/04/07 2017/02/16

BOM Structure

100@

GIGA@LAN Giga Transformer

8111H@

8107E@

M1@

M2@

NFC@For NFC Option

NOKBL@No Keyboard backlight

15_NUM@

H2G@

S2G@

M2G@

EMI@

ESD@

@EMI@

@ESD@

@RF@

RF@

YOGA@

S14@

S15@

UMA_EXTRA@

6500U@

6200U@

6100U@

4405U@

KS@

JW@

USB 3.0 Port Table

USB2/3 MB(JUSB1)

USB2/3 MB(JUSB2)

HDD

Compal Secr et Data

Compal Secr et Data

Compal Secr et Data

Deciphered Date

Deciphered Date

Deciphered Date

4

*

CV194_RF@ only for DIS

USB 2.0 Port Table

Port

1

2

3

4

5

6

7

External

USB Port

Touch panel (for YOGA only)

USB2/3 MB(JUSB1)

USB2/3 MB(JUSB2)

USB2 IO Board(Charger)

Camera

NGFF WLAN+BT

PCIE Port Table

Port

Lane

1

1

2

3

4

5

6

7

8

9

10

GPU

2

3

4

LAN

NGFF WLAN+BT

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet of

Date: Sheet

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

LA-E221P

LA-E221P

LA-E221P

5

of

350Tuesday, June 28, 2016

350Tuesday, June 28, 2016

of

350Tuesday, June 28, 2016

1.0

1.0

1.0

B

C

D

5

4

3

2

1

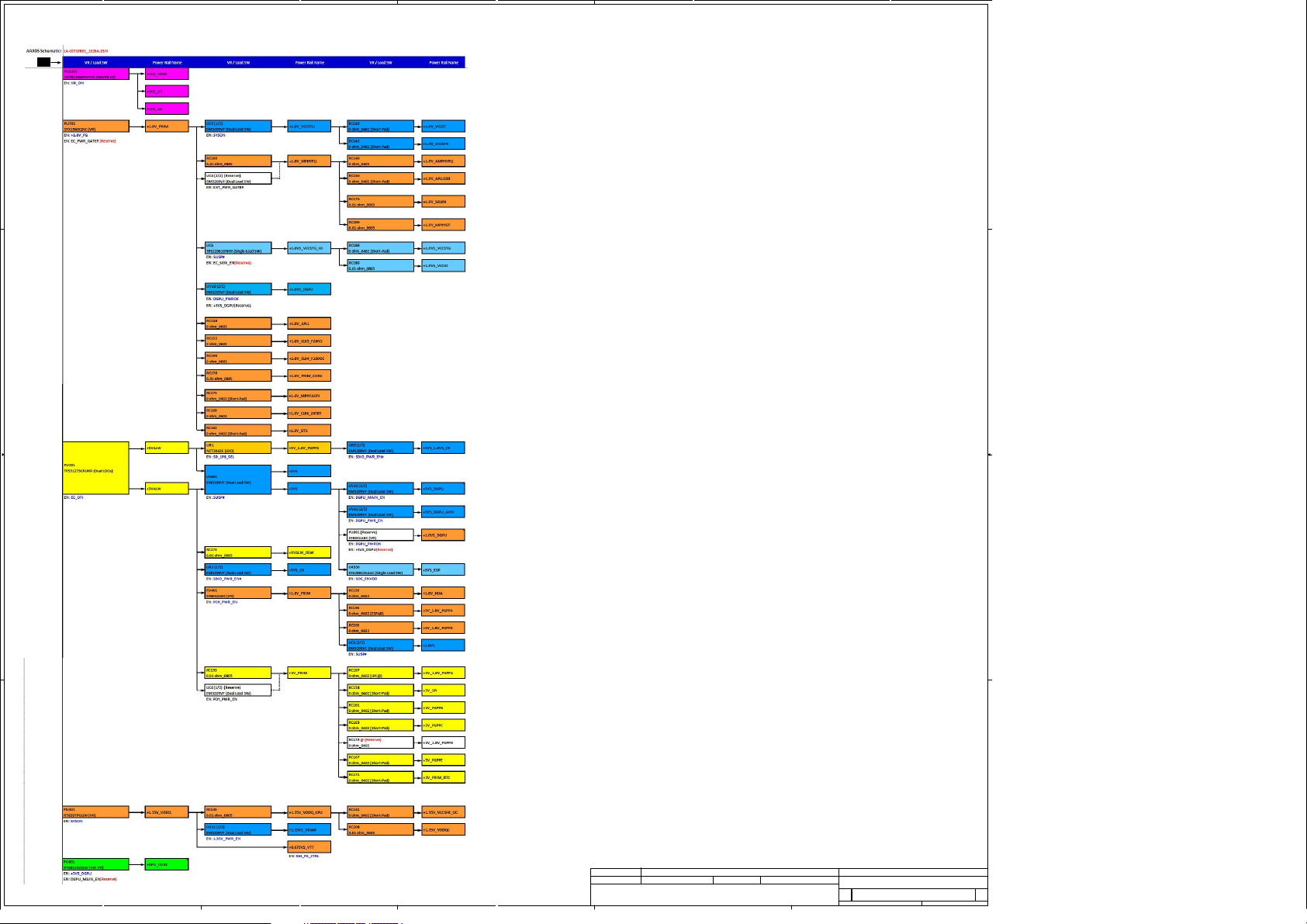

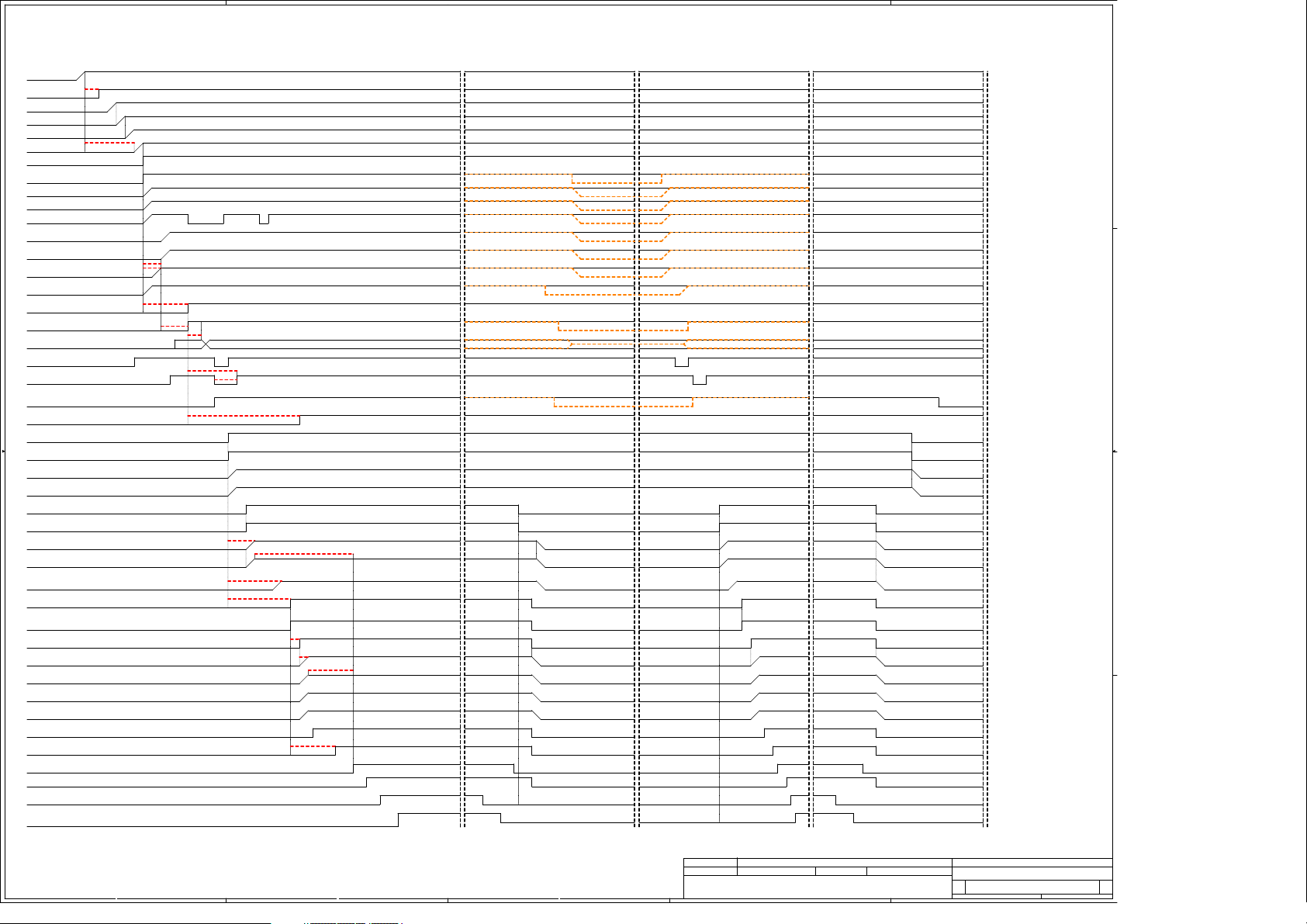

BIVS3/ VE3 -PowerMap_SKL-U22_DDR3L_Volume_NON CS]

B+

D D

C

B

C

B

A

Security Classification

Security Classification

Security Classification

Issued D ate

Issued D ate

Issued D ate

THIS S HEET OF ENGI NEE RING DRA WI NG IS THE P ROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS S HEET OF ENGI NEE RING DRA WI NG IS THE P ROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS S HEET OF ENGI NEE RING DRA WI NG IS THE P ROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE US ED BY OR DI S CLOS ED TO ANY THI RD PAR TY WI THOUT PRI OR W RI TTEN CONSE NT OF COMPA L ELE CTRONI CS , I NC.

MAY BE US ED BY OR DI S CLOS ED TO ANY THI RD PAR TY WI THOUT PRI OR W RI TTEN CONSE NT OF COMPA L ELE CTRONI CS , I NC.

5

4

3

MAY BE US ED BY OR DI S CLOS ED TO ANY THI RD PAR TY WI THOUT PRI OR W RI TTEN CONSE NT OF COMPA L ELE CTRONI CS , I NC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/04/07 2017/02/16

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power MAP

Power MAP

Power MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

1

450Tuesday, June 28, 2016

450Tuesday, June 28, 2016

450Tuesday, June 28, 2016

A

1.0

1.0

1.0

of

of

of

5

[AAX05-PWR Sequence_SKL-U22_DDR3L_Volume_NON CS]

4

3

2

1

G3->S0 S0->S3 ->S0

+3VL_RTC

SOC_RTCRST#

B+

D D

+3VLP/+5VLP

EC_ON

+5VALW/+3VALW/+3VALW_DSW

PM_BATLOW#

tPCH01_Min : 9 ms

tPCH04_Min : 9 ms

Pull-up to DS W well if not implemented.

/DS3 DS3S0/

PCH_PWR_EN (S LP_SUS#)

+3V_PRIM

+1.8V_PRIM

C

EXT_PWR_GATE#

+1.0V_MPHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

SUSACK#

PCH_DPWROK

EC_RSMRST#

AC_PRES ENT

ON/OFF

PBTN_OUT#

PM_SLP_S5#

ESPI_RST#

tPCH06_Min : 200 us

tPCH34_Max : 20 ms

tPCH02_Min : 10 ms

tPCH03_Min : 10 ms

tPLT02_Min : 0 ms Max : 90 ms

Minimum duration of PWRBTN# asser tion = 16mS . PWRBTN# can assert before or after RSMRST#

If EXT_PWR _GATE# Toffmin is too small, Pw r

gate may choose to completely ignore it

tPCH43_Min : 95 ms

tPCH18_Min : 90 us

PM_SLP_S4#

SYSON

+1.0V_VCCST/+1.0V_VCCSFR

+1.35V_VDDQ/+1.35V_VCCSFR_OC

PM_SLP_S3#

SUSP#

+1.0VS_VCCSTG

+1.0VS_VCCIO

B

+5VS/+3VS/+1.5VS/+1.05VS

EC_VCCST_PG

VR_ON

SM_PG_CTRL

+0.675VS_VTT

+VCC_SA

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

T <=10msec

T = 10msec

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

+VCC_CORE

+VCC_GT

VR_PWRGD

PCH_PWROK

tCPU16 Min : 0 ns

H_CPUPWRGD

SYS_PWROK

A

SUS_STAT#

SOC_PLTRST#

S0->S5

+3VL_RTC

SOC_RTCRST#

B+

+3VLP/+5VLP

EC_ON

+5VALW/+3VALW/+3VALW_DSW

PM_BATLOW#

PCH_PWR_EN (S LP_SUS#)

+3V_PRIM

+1.8V_PRIM

EXT_PWR_GATE#

+1.0V_MPHYPLL

+1.0V_PRIM_CORE

+1.0V_PRIM

SUSACK#

PCH_DPWROK

EC_RSMRST#

AC_PRES ENT

ON/OFF

PBTN_OUT#

PM_SLP_S5#

ESPI_RST#

PM_SLP_S4#

SYSON

+1.0V_VCCST/+1.0V_VCCSFR

+1.35V_VDDQ/+1.35V_VCCSFR_OC

PM_SLP_S3#

SUSP#

+1.0VS_VCCSTG

+1.0VS_VCCIO

+5VS/+3VS/+1.5VS/+1.05VS

EC_VCCST_PG

VR_ON

SM_PG_CTRL

+0.675VS_VTT

+VCC_SA

+VCC_CORE

+VCC_GT

VR_PWRGD

PCH_PWROK

H_CPUPWRGD

SYS_PWROK

SUS_STAT#

SOC_PLTRST#

C

B

A

Security Classificat ion

Security Classificat ion

Security Classificat ion

Issued Date

Issued Date

Issued Date

THIS SHEE T OF ENGI NEERING DRAWIN G IS THE PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEE T OF ENGI NEERING DRAWIN G IS THE PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEE T OF ENGI NEERING DRAWIN G IS THE PROPRI ETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DI SCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DI SCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DI SCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/04/07 2017/02/16

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electr onics, Inc.

Compal Electr onics, Inc.

Compal Electr onics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Power Seq uence

Power Seq uence

Power Seq uence

1

of

550Tuesday, June 2 8, 20 16

of

550Tuesday, June 2 8, 20 16

of

550Tuesday, June 2 8, 20 16

1.0

1.0

1.0

A

B

C

D

E

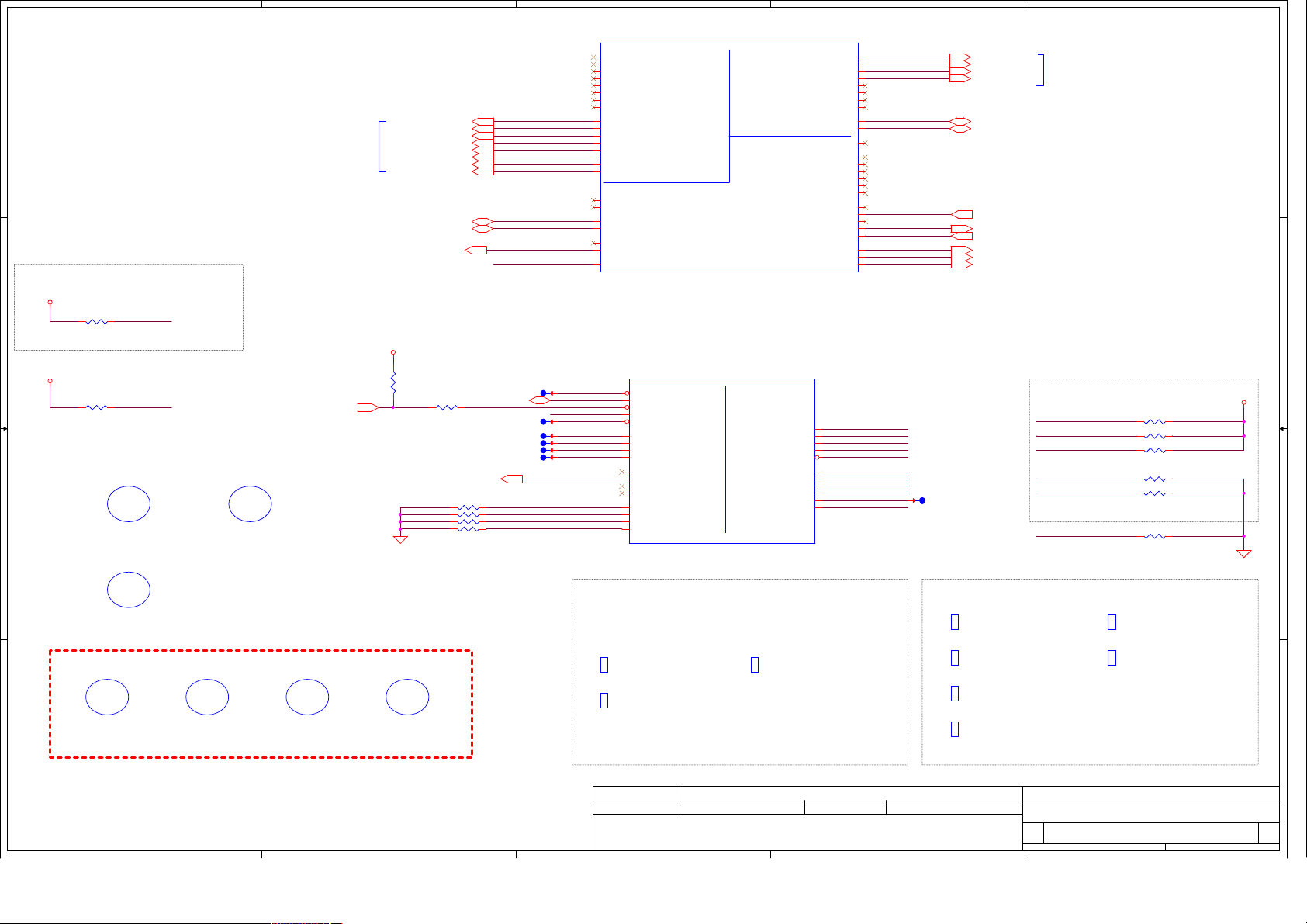

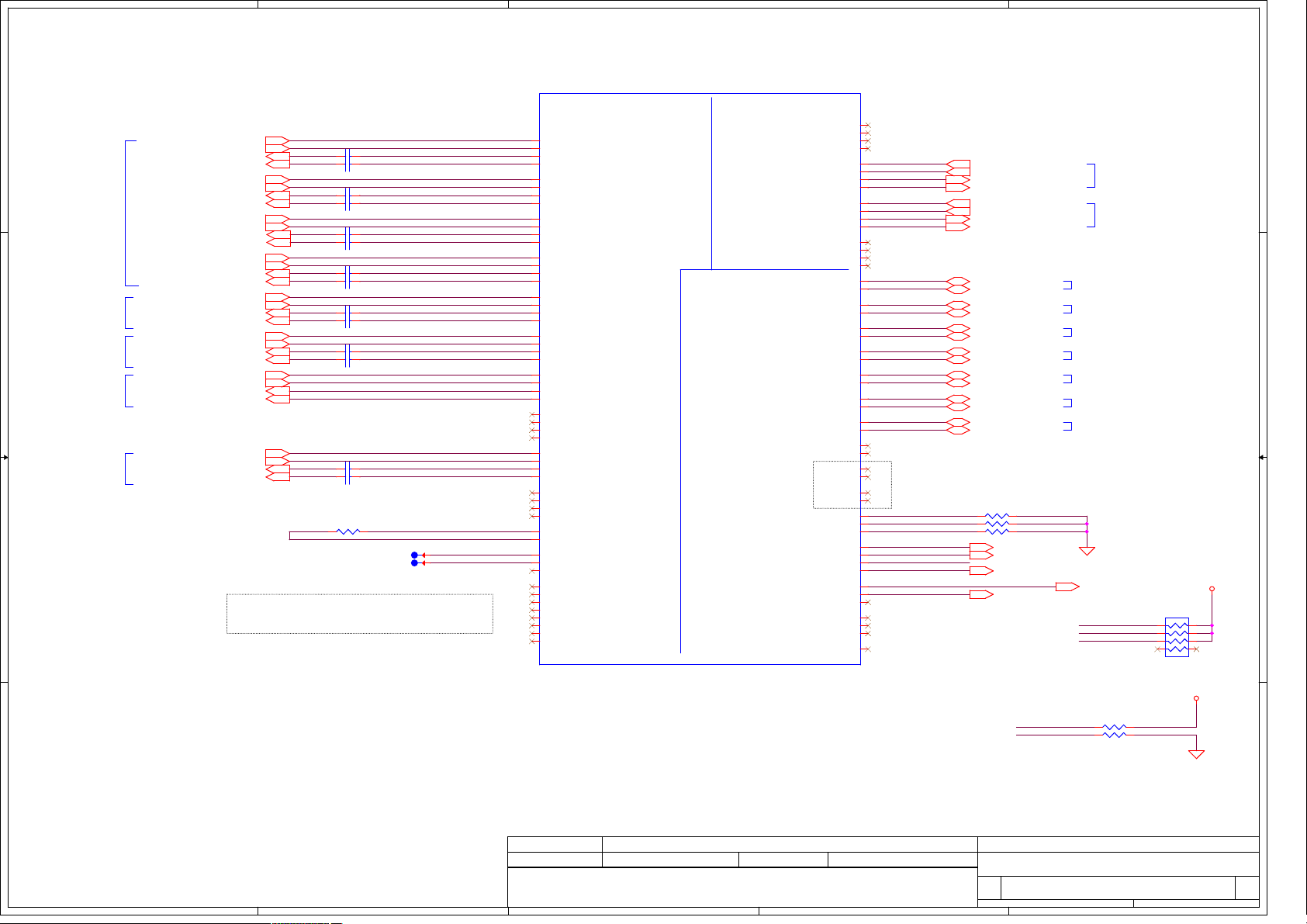

DDI

DISPLAY SI DEBANDS

SKL-U

1 OF 20

SKL-U

4 OF 20

EDP

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

Rev_1.0

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

Rev_1.0

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

JTAGX

RSVD

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

PCH_JTAG_TCK1

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

PCH_XDP_TRST#

CPU_XDP_TCK0

T116 TP@

EDP_TXN0 <26>

EDP_TXP0 <26>

EDP_TXN1 <26>

EDP_TXP1 <26>

EDP_AUXN <26>

EDP_AUXP <26>

TMDS_B_HPD <27>

EC_SCI# <10,34>

EDP_HPD <26>

ENBKL <26,34>

INVPWM <26>

PCH_ENVDD <26>

!'#(&

)*+,-"#$%

)*+,-'#(

-!-(FG(#-H+*-.$.-#'IJB-&

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

CPU_XDP_TCK0

PCH_JTAG_TCK1

SOC_XDP_TRST#

RC11 51_0402_5%@

RC12 51_0402_5%@

RC13 51_0402_5%@

RC14 51_0402_5%

RC15 51_0402_5%

RC23 51_0402_5%@

1

1

1 2

1

@

1

@

1

+1.0VS_VCCIO

2

2

2

2

2

UC1A

@

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

1 1

!"#$%&

"#$%-##.-/(+*0-.1

HDMI_TX2-_CK<27>

HDMI_TX2+_CK<27>

HDMI_TX1-_CK<27>

HDMI_TX1+_CK<27>

HDMI_TX0-_CK<27>

HDMI_TX0+_CK<27>

HDMI_CLK-_CK<27>

HDMI_CLK+_CK<27>

HDMICLK_NB<27>

HDMIDAT_NB<27>

TS_I2C_RST#<26>

EDP_COMP

!-.+,@'A=306+A-(F-)+*-'#(-&

+1.0VS_VCCIO

1

2

1

EDP_COMP

24.9_0402_1%

2

H_THERMTRIP#

ZZZ

S14@

DAZ1PR00101

ZZZ

S15@

H_PROCHOT#<34>

ZZZ

YOGA@

PCB CIUY0 LA-E221P LS-D452P/D453P 02

DAZ1R400100

+1.0VS_VCCIO

1

RC4

1K_0402_5%

2

RC6 499_0402_1%

%H-*+J0'7-$?>-(K.%-*'LJ6*'=-EM-,6<=-=@346AB-0+-+08'*-=6BA3<=

T99 TP@

1

2

RC7 49.9_0402_1%

2

RC8 49.9_0402_1%

2

RC9 49.9_0402_1%

RC10 49.9_0402_1%

H_PECI<34>

2

T100 TP@

T103 TP@

T105

TP@

T107 TP@

T109 TP@

TS_INT#<26>

1

1

1

12

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

2

RC3

2*34'-567089:;-,6<=>-?@346AB9:C,6<>-$3D-<'AB089E;;,6<=

+1.0V_VCCST

RC5 1K_0402_5%

3

PCB BIUS4 LA-E221P LS-D451P 02

C50

D50

C52

D52

A50

B50

D51

C51

L13

L12

N7

N8

N11

N12

E52

SOC_CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

SOC_OCC#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

DDI1_TXP[3]

DDI2_TXN[0]

DDI2_TXP[0]

DDI2_TXN[1]

DDI2_TXP[1]

DDI2_TXN[2]

DDI2_TXP[2]

DDI2_TXN[3]

DDI2_TXP[3]

GPP_E18/DDPB_CTRLCLK

GPP_E19/DDPB_CTRLDATA

GPP_E20/DDPC_CTRLCLK

GPP_E21/DDPC_CTRLDATA

GPP_E22

GPP_E23

EDP_RCOMP

SKL-U_BGA1356

UC1D

@

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKL-U_BGA1356

CPU MISC

2

3

?NOPF-.(FNQOPF-.(F

PCB BIUS5 LA-E221P LS-E221P 02

4

DAZ1PQ00201

ZZZ

UMA_EMC_FP@

Part Number = X4EA4C38L01

UMA_EMC with FP

ZZZ

DIS_EMC_FP@

Part Number = X4EA4C38L02

DIS_EMC with FP

ZZZ

UMA_EMC_NFP@

Part Number = X4EA4C38L03

UMA_EMC without FP

ZZZ

DIS_EMC_NFP@

Part Number = X4EA4C38L04

DIS_EMC without FP

UC1

SA0000A3870

S IC FJ8067702739738 SR2ZW H0 2.4G C38!

I3@

UC1

SA0000A3430

S IC FJ8067702739740 SR2ZV H0 2.7G C38!

I7@

UC1

SA0000A3730

S IC FJ8067702739739 SR2ZU H0 2.5G C38!

I5@

UC1

SA000094250

S IC FJ8066201930905 QJ8Q D0 2.1G C38

4405@

UC1

SA000092OA0

S IC FJ8066201930409 SR2EY D1 2.3G BGA

6200@

UC1

SA000092P80

S IC FJ8066201930408 SR2EZ D1 2.5G BGA

6500@

UC1

SA000092NA0

S IC FJ8066201931104 SR2EU D1 2.3G BGA

6100@

UC1

SA00009E620

S IC FJ8066202499000 QK2Z K1 3.3G C38

6567@

UC1

SA00009E510

S IC FJ8066202499000 QK2Z K1 3.3G C38

6267@

4

)+*-K$.-RSKT-QU$

Security Classifi cation

Security Classifi cation

Security Classifi cation

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

C

2016/04/07 2017/02/16

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Dat e

Deciphered Dat e

Deciphered Dat e

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SKL-U(1/12)DDI,EDP,MISC,CMC

SKL-U(1/12)DDI,EDP,MISC,CMC

SKL-U(1/12)DDI,EDP,MISC,CMC

LA-E221P

LA-E221P

LA-E221P

E

of

650Thursday, July 14, 2016

650Thursday, July 14, 2016

650Thursday, July 14, 2016

of

of

1.0

1.0

1.0

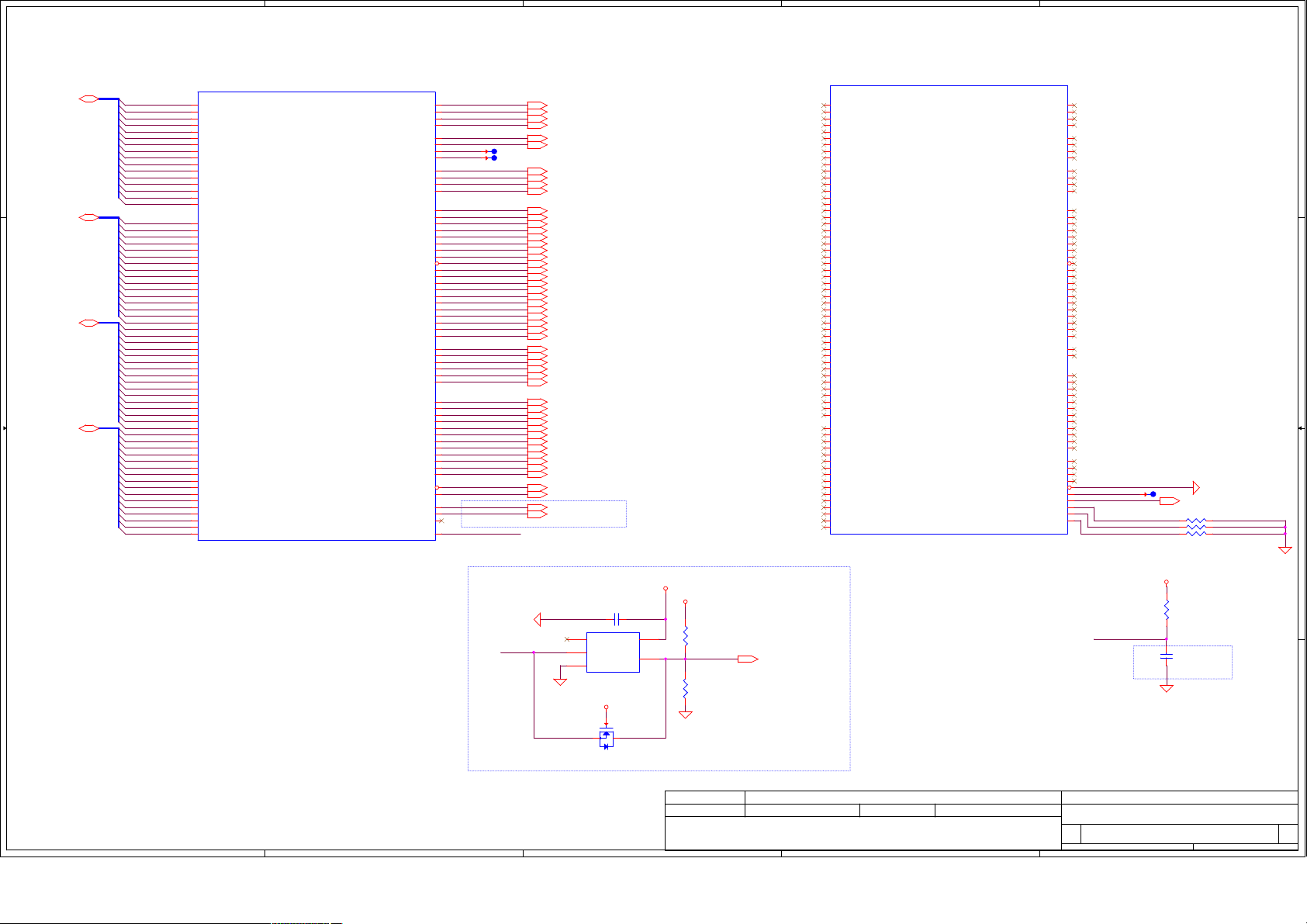

5

%A0'*<'3V'7-$',+*W

4

3

2

1

UC1C

UC1B

DDR_A_D[0..15]<18>

D D

DDR_A_D[16..31]<18>

DDR_A_D[32..47]<18>

C

DDR_A_D[48..63]<18>

B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

@

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

Interleave / Non-Interleaved

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR CH - A

2 OF 20

DDR3L / LPDDR3 / DDR4

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

Interleave / Non-Interleaved

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

Rev_1.0

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_MA5

DDR_A_MA9

DDR_A_MA6

DDR_A_MA8

DDR_A_MA7

DDR_A_BG0

DDR_A_MA12

DDR_A_MA11

DDR_A_MA13

DDR_A_MA15

DDR_A_MA14

DDR_A_MA16

DDR_A_BA0

DDR_A_MA2

DDR_A_BA1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

DDR_A_MA3

DDR_A_MA4

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_PG_CTRL

TP@

T119TP@

T118

DDR_A_CLK#0 < 18>

DDR_A_CLK0 <18>

DDR_A_CLK#1 < 18>

DDR_A_CLK1 <18>

DDR_A_CKE0 <18 >

DDR_A_CKE1 <18 >

DDR_A_CS#0 <18>

DDR_A_CS#1 <18>

DDR_A_ODT0 <18>

DDR_A_ODT1 <18>

DDR_A_MA5 <18>

DDR_A_MA9 <18>

DDR_A_MA6 <18>

DDR_A_MA8 <18>

DDR_A_MA7 <18>

DDR_A_BG0 <18>

DDR_A_MA12 <18>

DDR_A_MA11 <18>

M_A_ACT# <18>

DDR_A_BG1 <18>

DDR_A_MA13 <18>

DDR_A_MA15 <18>

DDR_A_MA14 <18>

DDR_A_MA16 <18>

DDR_A_BA0 <18>

DDR_A_MA2 <18>

DDR_A_BA1 <18>

DDR_A_MA10 <18>

DDR_A_MA1 <18>

DDR_A_MA0 <18>

DDR_A_MA3 <18>

DDR_A_MA4 <18>

DDR_A_DQS#0 < 18>

DDR_A_DQS0 <18>

DDR_A_DQS#1 < 18>

DDR_A_DQS1 <18>

DDR_A_DQS#2 < 18>

DDR_A_DQS2 <18>

DDR_A_DQS#3 < 18>

DDR_A_DQS3 <18>

DDR_A_DQS#4 < 18>

DDR_A_DQS4 <18>

DDR_A_DQS#5 < 18>

DDR_A_DQS5 <18>

DDR_A_DQS#6 < 18>

DDR_A_DQS6 <18>

DDR_A_DQS#7 < 18>

DDR_A_DQS7 <18>

DDR_A_ALERT# <18>

DDR_A_PARITY <18>

+0.6V_VREFCA <18>

+0.6V_A_VREFDQ <18>

2*34'-56708G?@346AB-&9-:;,6<=

@

Interleave / Non-Interleaved

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR CH - B

3 OF 20

DDR3L / LPDDR3 / DDR4

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

Interleave / Non-Interleaved

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

Rev_1.0

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

T123

TP@

DDR_DRAMRST# <18>

2

1

RC16 121_0402_1%

RC17 80.6_0402_1%

RC18 100_0402_1%

2

1

2

1

C

B

DDR_VTT_CNTL to DDR

VTT supplied ramped

<35uS

(tCPU18)

2

1

NC

DDR_PG_CTRL

A

5

4

Reserve for cost test.

2

A

3

GND

74AUP1G07GW_TSSOP5

SA00007WE00

+1.2V

G

2

3

S

Q2009

@

MESS138 W-G_S OT323-3

+1.2V

+3VS

1

CC1010.1U_0201_10V6K

UC7

VCC

Y

1

D

1

5

4

RC54

220K_0402_5%

2

2

RC19

@

2M_0402_5%

1

Security Cla ssification

Security Classi fication

Security Classi fication

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGI NEERING DRAWING I S THE PROPRIETARY PROPERTY OF CO MPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGI NEERING DRAWING I S THE PROPRIETARY PROPERTY OF CO MPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGI NEERING DRAWING I S THE PROPRIETARY PROPERTY OF CO MPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NO T BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

DDR_VTT_PG_CTRL <41>

Compal Secret Data

Compal Secret Data

2016/04/07 2017/02/16

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

DDR_DRAMRST#

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Tuesday, June 28, 2016

Date: Sheet

Tuesday, June 28, 2016

Date: Sheet

Tuesday, June 28, 2016

+1.2V

1

RC20

470_0402_5%

2

2

ESD@

CC96

100P_0402_50V8J

1

.<+='-0+-.(F

SKL-U(2/12)DDR3L

SKL-U(2/12)DDR3L

SKL-U(2/12)DDR3L

LA-E221P

LA-E221P

LA-E221P

1

A

1.0

1.0

1.0

50

50

50

7

of

7

of

7

5

4

3

2

1

SML0ALERT# (Internal Pull Down):

+3VS

1

1 2

1 2

1

2

2

RC112 10K_0402_5%

D D

+3VALW

RC21 1K_0402_5%@

RC22 1K_0402_5%@

RC24 1K_0402_5%@

From WW36 MOW for SKL-U ES sample

+1.8VS_3VS_PGPPA

1 2

RC25 8.2K_0402_5%

C

KB_RST#

SOC_SPI_IO2

SOC_SPI_IO3

SERIRQ

UC1E

@

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

KB_RST#<34>

SERIRQ<34>

KB_RST#

SERIRQ

AW3

AW2

AW13

AY11

AV2

AV3

AU4

AU3

AU2

AU1

M2

M3

J4

V1

V2

M1

G3

G2

G1

SKL-U

LPC

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

5 OF 20

Rev_1.0

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

PCH_SMB_CLK

PCH_SMB_DATA

SOC_SMBALERT#

SOC_SML0CLK

SOC_SML0DATA

SOC_SML0ALERT#

SOC_SML1ALERT#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_CLK0

RC26 22_0402_5%EMI@

PM_CLKRUN#

T124TP@

T125TP@

1 2

PCH_SMB_CLK <18,32>

PCH_SMB_DATA <18,32>

SOC_SML0CLK <29>

SOC_SML0DATA <29>

EC_SMB_CK2 <20,31,34>

EC_SMB_DA2 <20,31,34>

LPC_AD0 <34>

LPC_AD1 <34>

LPC_AD2 <34>

LPC_AD3 <34>

LPC_FRAME# <34>

eSPI or LPC

0 = LPC is selected for EC ==> Default

1 = eSPI is selected for EC

SMB

(Link to DDR,TP)

SML0

(Link to NFC)

SML1

(Link to EC,DGPU,Thermal Sensor)

CLK_LPC_EC <34>

+3VS

C

RPC1, RPC3 and RC30 are close to UC3

RPC1

SOC_SPI_SO

SOC_SPI_CLK

SOC_SPI_SI

)*+,-?U.

B

)*+,-K.

EC_SPI_CLK<34>

EC_SPI_MOSI<34>

EC_SPI_CS0#<34>

EC_SPI_MISO<34>

SOC_SPI_IO3

SOC_SPI_IO2

1 8

2 7

3 6

4

33_0804_8P4R_5%

EMI@

1

EMI@

RC30 33_0402_5%

RPC3

1

EC_SPICLK

2

EC_MOSI

3

EC_SPICS#

4 5

EC_MISO

33_0804_8P4R_5%

EMI@

SOC_SPI_SO_0_R

SOC_SPI_CLK_0_R

SOC_SPI_SI_0_R

5

SOC_SPI_IO3_0_R

2

SOC_SPI_IO2_0_R

8

SOC_SPI_CLK_0_R

7

SOC_SPI_SI_0_R

6

SOC_SPI_CS#0

SOC_SPI_SO_0_R

SOC_SML0CLK

SOC_SML0DATA

SOC_SML1ALERT#

PCH_SMB_CLK

PCH_SMB_DATA

EC_SMB_CK2

EC_SMB_DA2

PM_CLKRUN#

1

RC28 499_0402_1%

RC29 499_0402_1%

RC113 150K_0402_5%

RC31 8.2K_0402_5%

2

1

2

1 2

@

RPC2

1

8

2 7

3

6

4 5

1K_0804_8P4R_5%

1 2

@

+1.8VS_3VS_PGPPA

B

Follow 543016_SKL_U_Y_PDG_0_9

!-?(%-XU$-P-M$-&

UC3

5

1

/CS

2

DO(IO1)

3

/WP(IO2)

4

GND

W25Q128FVSIQ_SO8

/HOLD(IO3)

SOC_SPI_CS#0

SOC_SPI_SO_0_R

SOC_SPI_IO2_0_R

A

VCC

CLK

DI(IO0)

8

7

6

5

+3VALW

@

1 2

CC2 0.1U_0201_10V K X5R

SOC_SPI_IO3_0_R

SOC_SPI_CLK_0_R

SOC_SPI_SI_0_R

1

CC3

10P_0402_50V8J

2

@EMI@

4

Security Classification

Security Classification

Security Classification

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2016/04/07 2017/02/16

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

Date: Sheet

Compal Electronics, Inc.

SKL-U(3/12)SPI,SMB,LPC,ESPI

SKL-U(3/12)SPI,SMB,LPC,ESPI

SKL-U(3/12)SPI,SMB,LPC,ESPI

LA-E221P

LA-E221P

LA-E221P

1

of

850Tuesday, June 28, 2016

850Tuesday, June 28, 2016

850Tuesday, June 28, 2016

of

A

1.0

1.0

1.0

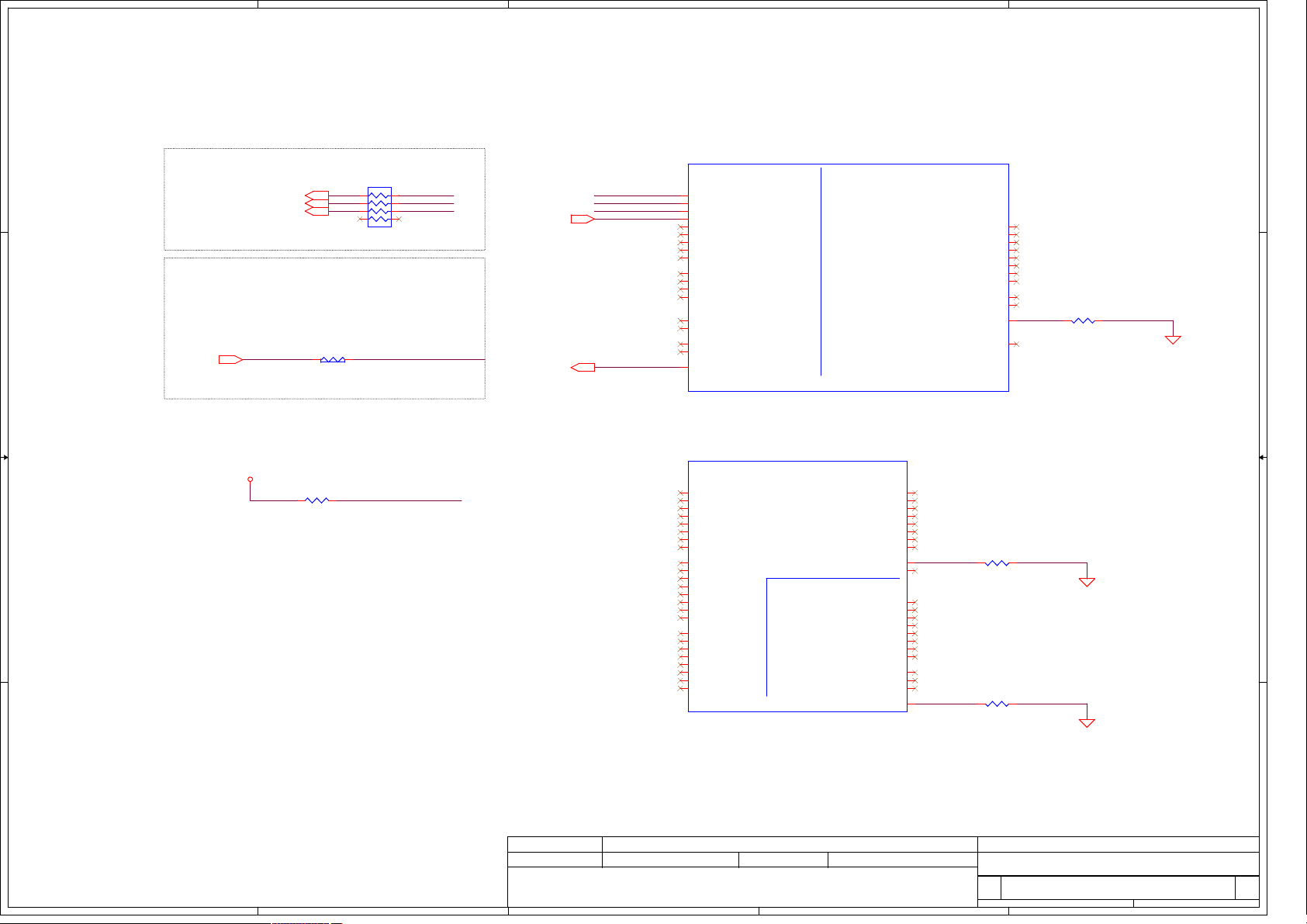

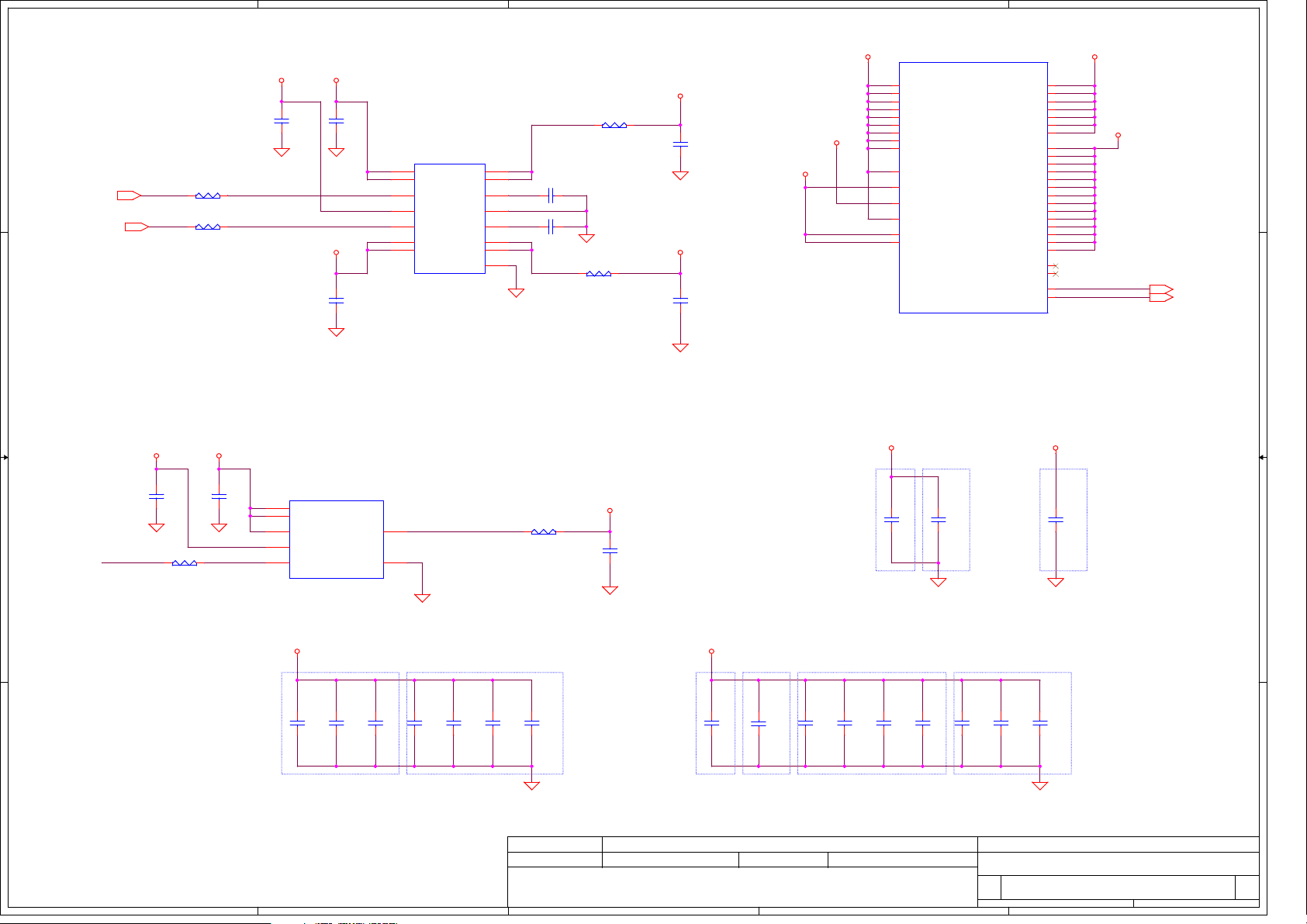

5

D D

4

3

2

1

SKL-U

9 OF 20

SKL-U

7 OF 20

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

SDIO / SDXC

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

SD_RCOMP

GPP_F23

Rev_1.0

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

1 2

RC80 100_0402_1%

1

RC129 200_0402_1%

Rev_1.0

@

@

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

2

1 2

@

RC76 200_0402_1%

C

B

UC1G

BA22

HDA_SYNC/I2S0_SFRM

AY22

HDA_BLK/I2S0_SCLK

BB22

HDA_SDO/I2S0_TXD

BA21

HDA_SDI0/I2S0_RXD

AY21

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

AY20

I2S1_SFRM

I2S1_TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

AK10

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

AW5

GPP_B14/SPKR

SKL-U_BGA1356

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_BGA1356

@

AUDIO

@

!-"#-YF#%U-&

RPC4

HDA_BITCLK_AUDIO<28>

HDA_SYNC_AUDIO<28>

HDA_SDOUT_AUDIO<28>

1 8

2

3 6

4

HDA_BIT_CLK

7

HDA_SYNC

HDA_SDOUT

5

33_0804_8P4R_5%

EMI@

HDA_SDIN0<28>

!-2+-KA3I<'-$K-UV'**67'-&

C

ME_EN<34>

RC116 0_0402_5%

+3VS

1

RC33 2.2K_0402_5%@

12

2

HDA_SDOUT

HDA_SPKR

HDA_SPKR<28>

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SPKR

AW22

AW20

SPKR (Internal Pull Down):

TOP Swap Override

B

0 = Disable TOP Swap mode. ==> Default

1 = Enable TOP Swap Mode.

A

Security Classification

Security Classification

Security Classification

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2016/04/07 2017/02/16

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

LA-E221P

LA-E221P

Tuesday, June 28, 2016

Tuesday, June 28, 2016

Tuesday, June 28, 2016

LA-E221P

9

9

of

9

of

1

of

A

1.0

1.0

1.0

50

50

50

5

@

+3VS

RPC5

1

8

7

5

10K_0804_8P4R_5%

7

D D

6

10K_0804_8P4R_5%

+3VL_RTC

CLKREQ_PCIE#4

2

CLKREQ_PCIE#5

36

4

RPC6

18

CR_CLKREQ#

2

WLANCLK_REQ#

3

45

LANCLK_REQ#

1 2

RC36 20K_0402_5%

1

2

CC6 1U_0402_6.3V6K

1

RC37 20K_0402_5%

CC7 1U_0402_6.3V6K

CLRP2 SHORT PADS

2

1 2

1

2

1 2

RC39 1M_0402_5%

EC_SCI# <6,34>

SOC_SRTCRST#

SOC_RTCRST#

CLR CMOS

SM_INTRUDER#

+3VS

2

UMA@

1

2

DIS@

1

4

RC134

10K_0402_5%

VGA_CLK REQ#

RC135

10K_0402_5%

DGPU

LAN

NGFF WL+BT(KEY E)

Card Reader RTS5220

2

1

RC38 0_0402_5%

CLK_PEG_VGA#<19>

CLK_PEG_VGA<19>

VGA_CLK REQ#<20>

CLK_PCIE_LAN#<35>

CLK_PCIE_LAN<35>

LANCLK_REQ#<35>

CLK_PCIE_WLAN#<30>

CLK_PCIE_WLAN<30>

WLANCLK_REQ#<30>

CLK_PCIE_CR#<33>

CLK_PCIE_CR<33>

CR_CLKREQ#<33>

EC_CLEAR_CMOS <34>

VGA_CLK REQ#

LANCLK_REQ#

WLANCLK_REQ#

CLKREQ_PCIE#4

CLKREQ_PCIE#5

3

UC1J

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356

2

SOC_XTAL24_IN

@

SKL-U

CLOCK SIGNALS

10 OF 20

Rev_1.0

CLKOUT_ITPXDP _N

CLKOUT_ITPXDP _P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

SUSCLK

SOC_XTAL24_IN

SOC_XTAL24_OUT

XCLK_B IASREF

SOC_RTCX1

SOC_RTCX2

SOC_SRTCRST#

SOC_RTCRST#

SUSCLK <30>

XCLK_B IASREF

1

RC35 2.7K_0402_1%

1 2

RC110 60.4_0402_1%

)+<<+5-CSZ[ZC\:;ES]]SM\?^W<3^'\$U]\X'V\E\;

SOC_XTAL24_OUT

+1.0V_CLK5_F24NS

2

@

1

1

RC34 1M_0402_5%

YC1

24MHZ_12PF_5YEA24000122IF40Q3

3

3

15P_0402_50V8J

GND

1

CC4

2

4

GND

2

1

1

2

15P_0402_50V8J

12

CC5

?0JHH-:_[^-+8,/X.`C1-(F-H+*-?^WO3^'PF

?0JHH-Z;_S-+8,/X.EE;1-(#-H+*-.3AA+AO3^'PF

!-(."-(O2X?2-QJHH'*-&

1

+3VS

1

B

2

A

@

@

SYSTEM POWER MANAGEMENT

2

5

UC4

P

4

Y

G

1

RC44

2

100K_0402_5%

SKL-U

11 OF 20

12

3

PCI_RST# <19,30,33,34,35>

CC8

100P_0402_50V8J

ESD@

GPP_B12/SLP_S0#

GPD9/SLP_WLAN#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPP_B11/EXT_PW R_GATE#

GPP_B2/VRALERT#

Rev_1.0

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD6/SLP_A#

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

PM_SLP_S0#

PM_SLP_S3#

PM_SLP_S4#

PM_SLP_S5#

SLP_WLAN#

PM_SLP_A#

PBTN_OUT#

AC_PRE SENT

PM_BATLOW#

SM_INTRUDER#

SOC_VRALERT#

1

RC103 0_0402_5%@

T130TP@

PM_SLP_S3# <3 4>

PM_SLP_S4# <3 4,39,41>

T131TP@

T133TP@

T134TP@

2

SOC_RTCX2

SOC_RTCX1

PBTN_OUT# <34>

VCIN1_AC _IN <20,34, 39>

PM_BATLOW#

RC46 8.2K_0402_5%

AC_PRE SENT

RC48 10K_0402_5%

SOC_VRALERT#

RC50 10K_0402_5%

2

1

RC41 10M_0402_5%

YC2

2

1

32.768KHZ 9PF 20PPM 9H03280012

1

CC9

6.8P_0402_50V8C

2

1

1

@

1 2

@

1

2

2

2

CC10

6.8P_0402_50V8C

+3VALW

C

B

RC42 0_0402_5%

C

SOC_PLTRST#

TC7SH08FUF_SSOP5

+3VALW

RPC7

8

1

PCH_PWROK

27

EC_RSMRST#

3

6

10K_0804_8P4R_5%

1 2

ESD@

CC97 100P_0402_50V8J

1 2

ESD@

CC94 100P_0402_50V8J

1

ESD@

CC95 100P_0402_50V8J

B

+3VALW

1

RC47 1K_0402_5%

)*+,-K.-/U@'AP#*36A1

VCCST_ PWRGD<34>

LAN_WAKE#

45

SYS_RESET#

SYS_RESET#

EC_RSMRST#

2

2

SYS_PWROK

WAKE#

+1.0V_VCCST

1

RC52

1K_0402_5%

2

1

RC53 60.4_0402_1%

CA47

100P_0402_50V8J

1

ESD@

2

Only For Power Sequence Debug

2

EC_VCCST_PG

EC_RSMRST#<34>

PCH_PWROK<34,44>

T132 TP@

SYS_PWROK<34,44>

SOC_PLTRST#

SYS_RESET#

EC_RSMRST#

H_CPUPWRGD

EC_VCCST_PG

SYS_PWROK

PCH_PWROK

EC_RSMRST#

WAKE#

LAN_WAKE#

SA007080100

UC1K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PW ROK

AR13

GPP_A13/SUSW ARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE #

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL-U_BGA1356

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL E LECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2016/04/07 2017/02/16

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SKL-U(5/12)CLK,PM,GPIO

SKL-U(5/12)CLK,PM,GPIO

SKL-U(5/12)CLK,PM,GPIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet

2

Date: Sheet

LA-E221P

LA-E221P

LA-E221P

1

10 50Tuesday, June 28, 2016

10 50Tuesday, June 28, 2016

of

of

10 50Tuesday, June 28, 2016

A

1.0

1.0

1.0

5

4

3

2

1

a?(%;\$U?%-/%A0'*A3<-(J<<-#+5A1b

c+-X'I++0

;-9-#6=3I<'-c+-X'I++0-,+7'_-99&-#'H3J<0

E-9-KA3I<'-c+-X'I++0-$+7'_-/(."-56<<-76=3I<'-08'-2.U-

D D

------26,'*-=W=0',-*'I++0-H'30J*'1_-286=-HJA406+A-6=-J='HJ<-

------58'A-*JAA6AB-%2(GR#(_

a?(%E\$U?%-/%A0'*A3<-(J<<-#+5A1b

Q++0-Q%U?-?0*3@-Q60

;-9-?(%-$+7'-99&-#'H3J<0

E-9-O(.-$+7'

+3VS

1 2

RC59 4.7K_0402_5%@

2

1

RC60 150K_0402_5%@

C

+3VS

+3VS

B

1

2

3

4 5

1 2

RC27 1K_0402_5%@

1

RC32 1K_0402_5%@

RPC10

8

7

6

49.9K_0804_8P4R_1%

2

GSPI0_MOSI

GSPI1_MOSI

UART0_RTS

UART0_CTS

UART0_RX

UART0_TX

I2C1_SDA_ TS

I2C1_SCL _TS

NFC_DWL<29>

GSPI0_MOSI

SENSOR_EC_INT<34>

NFC_RST<29>

WLBT_OFF#<30>

UART0_RX<30>

UART0_TX<30>

UART0_RTS<30>

UART0_CTS<30>

I2C0_SD A_SEN<34>

I2C0_SC L_SEN<34>

I2C1_SD A_TS<26>

I2C1_SC L_TS<26>

GSPI1_MOSI

UC1F

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKL-U_BGA1356

@

LPSS ISH

SKL-U

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

Sx_EXIT_HOLDOFF# / GPP_A12 / BM_BUSY# / ISH_GP6

6 OF 20

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

Rev_1.0

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

DGPU_PWR_EN

AC2

DGPU_HOLD_RST#

AC3

DGPU_PWROK

AB4

DGPU_PRSNT#

AY8

BA8

BB7

BA7

AY7

AW7

AP13

MB_ID

MB_ID

+3VS

1 2

2

1

S14@

RC146

10K_0402_5%

YOGA@

RC147

10K_0402_5%

DGPU_PWR_EN <21,34,48>

DGPU_HOLD_RST# <19>

DGPU_PWROK <48>

RC146S15@

SD028100280

S RES 1/16W 10K +-5% 0402

)JA406+A

#%?

F$Y-UA<W

+3VS

DGPU_PWR_EN

DGPU_HOLD_RST#

DGPU_PWROK

WLBT_OFF#

1 2

R73 10K_0402_5%UMA@

1

R74 10K_0402_5%DIS@

1 8

2 7

3 6

4 5

#a(F\(X?c2d

/a((\.EC1

;

E

2

+3VS

RPC8

10K_0804_8P4R_5%

DGPU_PRSNT#

C

B

A

Security Classifi cation

Security Classifi cation

Security Classifi cation

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2016/04/07 2017/02/16

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SKL-U(6/12)GPIO,I2C,GSPI

SKL-U(6/12)GPIO,I2C,GSPI

SKL-U(6/12)GPIO,I2C,GSPI

LA-E221P

LA-E221P

LA-E221P

11 50Tuesday, June 28, 20 16

11 50Tuesday, June 28, 20 16

11 50Tuesday, June 28, 20 16

of

1

of

A

1.0

1.0

1.0

5

4

3

2

1

UC1H

@

D D

PCIE_PRX_DTX_N1<19>

C

B

dGPU

LAN

NGFF WLAN+BT

HDD

Card Reader

PCIE_PRX_DTX_P1<19>

PCIE_PTX_C_DRX_N1<19>

PCIE_PTX_C_DRX_P1<19>

PCIE_PRX_DTX_N2<19>

PCIE_PRX_DTX_P2<19>

PCIE_PTX_C_DRX_N2<19>

PCIE_PTX_C_DRX_P2<19>

PCIE_PRX_DTX_N3<19>

PCIE_PRX_DTX_P3<19>

PCIE_PTX_C_DRX_N3<19>

PCIE_PTX_C_DRX_P3<19>

PCIE_PRX_DTX_N4<19>

PCIE_PRX_DTX_P4<19>

PCIE_PTX_C_DRX_N4<19>

PCIE_PTX_C_DRX_P4<19>

PCIE_PRX_DTX_N5<35>

PCIE_PRX_DTX_P5<35>

PCIE_PTX_C_DRX_N5<35>

PCIE_PTX_C_DRX_P5<35>

PCIE_PRX_DTX_N6<30>

PCIE_PRX_DTX_P6<30>

PCIE_PTX_C_DRX_N6<30>

PCIE_PTX_C_DRX_P6<30>

SATA_PRX_DTX_N0<29>

SATA_PRX_DTX_P0<29>

SATA_PTX_DRX_N0<29>

SATA_PTX_DRX_P0<29>

PCIE_PRX_DTX_N9<33>

PCIE_PRX_DTX_P9<33>

PCIE_PTX_C_DRX_N9<33>

PCIE_PTX_C_DRX_P9<33>

]8'A-(.%KMG?Y2YEY-6=-J='7-3=-?Y2Y-(+*0-E-/U##1>-08'A

(.%KEEG?Y2YEQ-/$_:-??#1-43AA+0-I'-J='7-3=-?Y2Y-(+*0-E_

1

DIS@

DIS@

1 2

1 2

1

1 2

1 2

1

1

1 2

1

1 2

1

1

1

1 2

2

2

2

2

2

2

2

2

0.1U_0201_10V K X5R

0.1U_0201_10V K X5R

0.1U_0201_10V K X5R

0.1U_0201_10V K X5R

0.1U_0201_10V K X5R

0.1U_0201_10V K X5R

T147 TP@

T148 TP@

CC11 0.22U_0402_6.3V6KDIS@

CC14 0.22U_0402_6.3V6KDIS@

CC15 0.22U_0402_6.3V6KDIS@

CC16 0.22U_0402_6.3V6KDIS@

CC12 0.22U_0402_6.3V6KDIS@

CC13 0.22U_0402_6.3V6K

CC17 0.22U_0402_6.3V6K

CC18 0.22U_0402_6.3V6KDIS@

CC19

CC20

CC102

CC103

CC104

CC105

RC71 100_0402_1%

PCIE_PTX_DRX_N1

PCIE_PTX_DRX_P1

PCIE_PTX_DRX_N2

PCIE_PTX_DRX_P2

PCIE_PTX_DRX_N3

PCIE_PTX_DRX_P3

PCIE_PTX_DRX_N4

PCIE_PTX_DRX_P4

PCIE_PTX_DRX_N5

PCIE_PTX_DRX_P5

PCIE_PTX_DRX_N6

PCIE_PTX_DRX_P6

PCIE_PTX_DRX_N9

PCIE_PTX_DRX_P9

PCIE_RCOMPN

PCIE_RCOMPP

XDP_PRDY#

XDP_PREQ#

PCIE / USB3 / SATA

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

SKL-U

8 OF 20

SSIC / USB3

USB3_2_RXN / SSIC_RXN

USB3_2_RXP / SSIC_RXP

USB3_2_TXN / SSIC_ TXN

USB3_2_TXP / SSIC_ TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

Rev_1.0

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_3_RXN

USB3_3_RXP

USB3_3_TXN

USB3_3_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB20_N1

USB20_P1

USB20_N2

USB20_P2

USB20_N3

USB20_P3

USB20_N4

USB20_P4

USB20_N5

USB20_P5

USB20_N6

USB20_P6

USB20_N7

USB20_P7

USB2_COMP

USB_OC2#

USB3_RX2_N <33>

USB3_RX2_P <33>

USB3_TX2_N <33>

USB3_TX2_P <33>

USB3_RX3_N <33>

USB3_RX3_P <33>

USB3_TX3_N <33>

USB3_TX3_P <33>

USB20_N1 <26>

USB20_P1 <26>

USB20_N2 <33>

USB20_P2 <33>

USB20_N3 <33>

USB20_P3 <33>

USB20_N4 <33>

USB20_P4 <33>

USB20_N5 <26>

USB20_P5 <26>

USB20_N6 <29>

USB20_P6 <29>

USB20_N7 <30>

USB20_P7 <30>

1 2

RC70 113_0402_1%

1 2

RC104 1K_0402_5%

RC105 1K_0402_5%

1

USB_OC0# <33>

USB_OC1# <33>

NFC_IRQ <29>

WL_OFF# <30>

2

USB2/3 MB(JUSB1)

USB2/3 MB(JUSB2)

Touch panel (for YOGA only)

USB2/3 MB(JUSB1)

USB2/3 MB(JUSB2)

USB2 IO Board(Charger)

Camera

Finger Printer

NGFF WLAN+BT

NFC_RST_KBL <29>

USB_OC0#

USB_OC1#

USB_OC2#

+3VALW

RPC9

1

8

7

2

3

6

4

5

10K_0804_8P4R_5%

+3VS

C

B

WL_OFF#

NFC_IRQ

A

Security Classification

Security Classification

Security Classification

2016/04/07 2017/02/16

2016/04/07 2017/02/16

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2016/04/07 2017/02/16

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet of

Compal Electronics, Inc.

SKL-U(7/12)PCIE,USB,SATA

SKL-U(7/12)PCIE,USB,SATA

SKL-U(7/12)PCIE,USB,SATA

1 2

RC139 10K_0402_5%@

1

RC138 100K_0402_5%@

LA-E221P

LA-E221P

LA-E221P

2

A

1.0

1.0

1.0

of

12 50Tuesday, June 28, 2016

of

12 50Tuesday, June 28, 2016