Page 1

User Guide

COMe-cP2020

Doc. ID: 1055-5562, Rev. 1.0

Date: September 17, 2013

www.kontron.com

Page 2

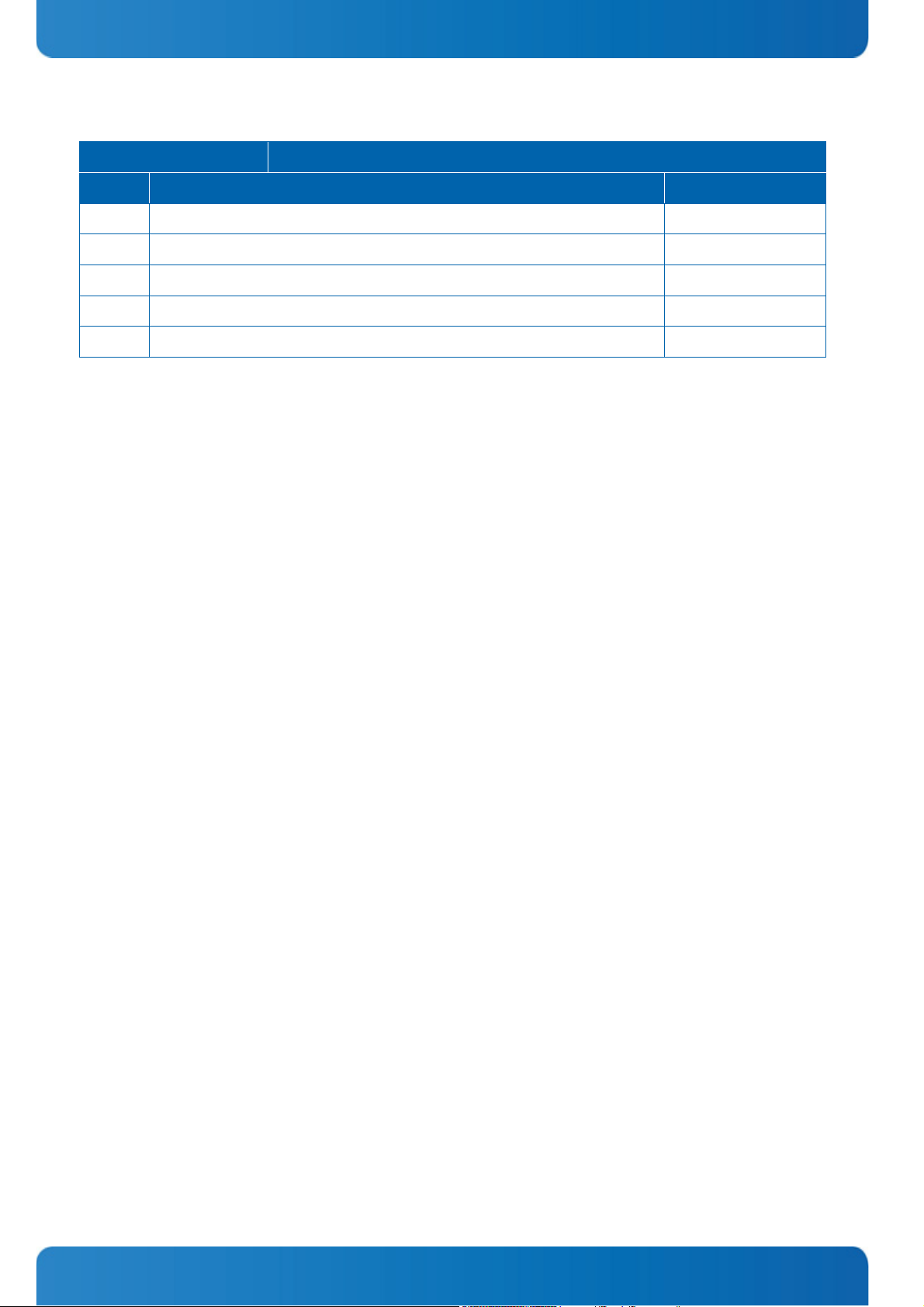

Revision History

Publication Title: COMe-P2020 User Guide

Rev. Brief Description of Changes Date of Issue

0.5 Initial Issue 18 February 2013

1.0 Chapter 3 updated 17 September 2013

Imprint

Kontron Europe GmbH may be contacted via the following:

COMe-P2020 User Guide

MAILING ADDRESS TELEPHONE AND E-MAIL

Kontron Europe GmbH +49 (0) 800-SALESKONTRON

Sudetenstraße 7 sales@kontron.com

D - 87600 Kaufbeuren Germany

For further information about other Kontron products, please visit our Internet web site: www.kontron.com.

Disclaimer

Copyright © 2013 Kontron AG. All rights reserved. All data is for information purposes only and not guaranteed for legal purposes. Information has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Kontron and

the Kontron logo and all other trademarks or registered trademarks are the property of their respective owners and are recognized. Specifications are subject to change without notice.

2

www.kontron.com

Page 3

COMe-P2020 User Guide

Contents

Revision History .................................................................................................................2

Imprint.............................................................................................................................2

Disclaimer .........................................................................................................................2

Proprietary Note.................................................................................................................9

Trademarks........................................................................................................................9

Environmental Protection Statement ......................................................................................9

General Instructions on Usage...............................................................................................9

Two Year Warranty...............................................................................................................9

1 Introduction ............................................................................................................. 11

1.1 COMe-cP2020 Overview ...................................................................................... 11

1.2 Board Diagrams ................................................................................................ 12

1.3 Technical Specifications ..................................................................................... 14

1.4 Standards....................................................................................................... 17

1.5 Related Publications.......................................................................................... 18

2 Functional Description ................................................................................................ 19

2.1 Processor ........................................................................................................ 19

2.2 Memory........................................................................................................... 19

2.2.1 DDR3 ......................................................................................................... 19

2.2.2 Flash Memory .............................................................................................. 19

2.2.3 System/User Data EEPROMs ............................................................................ 20

2.3 Timer.............................................................................................................. 20

2.4 Watchdog Timer................................................................................................ 20

2.5 Connectors ...................................................................................................... 21

2.5.1 COM Express Connectors ................................................................................ 21

2.5.2 Signal Descriptions COM Express Connectors ...................................................... 33

2.5.3 JTAG/Debug Interface ................................................................................... 36

3 Configuration ............................................................................................................ 38

3.1 DIP Switch Configuration.................................................................................... 38

3.2 Board Memory Map............................................................................................ 39

3.3 I/O Address Map ............................................................................................... 40

3.4 Board Control and Status Registers....................................................................... 43

4 Power Considerations.................................................................................................. 74

4.1 Electrical Specifications ..................................................................................... 74

4.1.1 Supply Voltage............................................................................................. 74

4.2 Power Supply Rise Time ...................................................................................... 74

3

www.kontron.com

Page 4

COMe-P2020 User Guide

4.3 Supply Voltage Ripple ........................................................................................ 74

4.4 Power Consumption........................................................................................... 74

5 Thermal.................................................................................................................... 76

5.1 Cooling Solution COMe-cP2020c .......................................................................... 76

5.2 Cooling Solution COMe-cP2020i ........................................................................... 77

6 U-Boot..................................................................................................................... 78

6.1 Introduction to U-Boot ...................................................................................... 78

6.2 Standard U-Boot Commands ............................................................................... 78

6.3 Kontron-Specific Commands ............................................................................... 81

6.4 U-Boot Access and Startup.................................................................................. 90

6.5 Working with U-Boot ......................................................................................... 90

6.5.1 General Operation ........................................................................................ 90

6.5.2 Using the sconf Command .............................................................................. 90

6.5.3 Examples of sconf Command Usage .................................................................. 91

6.5.4 Using the Network ........................................................................................ 94

6.5.5 Using SD Cards............................................................................................. 95

6.5.6 Using USB Devices ........................................................................................ 95

6.5.7 Using the Onboard NAND Flash........................................................................ 96

6.5.8 Using the SPI Flash for OS .............................................................................. 97

6.5.9 Booting an OS.............................................................................................. 97

6.6 Getting Help .................................................................................................... 99

6.7 Update ........................................................................................................... 99

6.8 Recovery Mechanism ........................................................................................ 100

6.9 Copyrights and Licensing................................................................................... 100

6.10 Obtaining Source Code...................................................................................... 104

7 Installation.............................................................................................................. 105

7.1 Safety............................................................................................................ 105

7.2 General Instructions on Usage ............................................................................ 105

7.3 COM Express Module-to-Carrier Assembly Considerations ......................................... 105

4

www.kontron.com

Page 5

COMe-P2020 User Guide

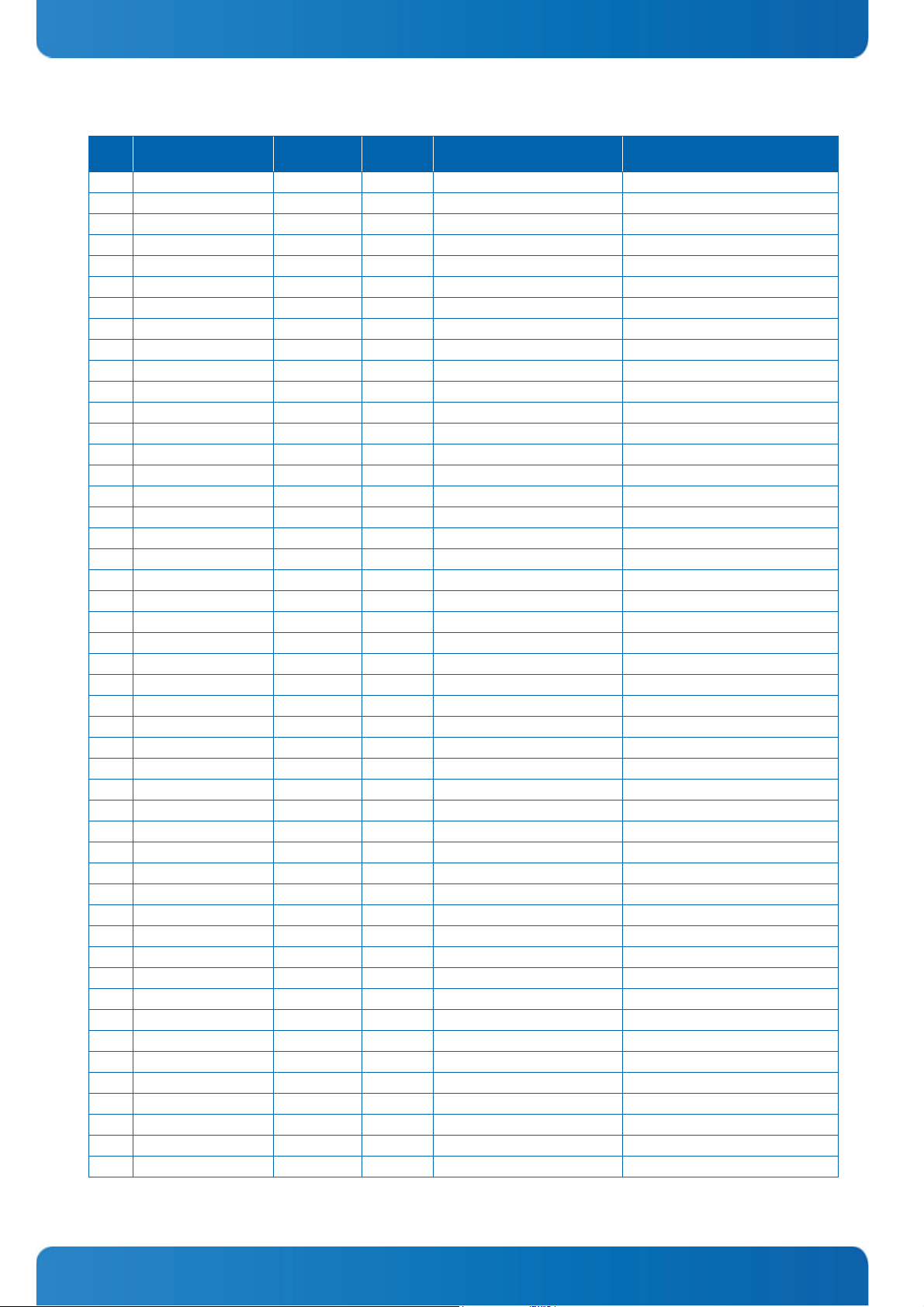

List of Tables

Table 1-1: COMe-cP2020 Main Specifications ..................................................................... 14

Table 1-2: Standards..................................................................................................... 17

Table 1-3: Related Publications....................................................................................... 18

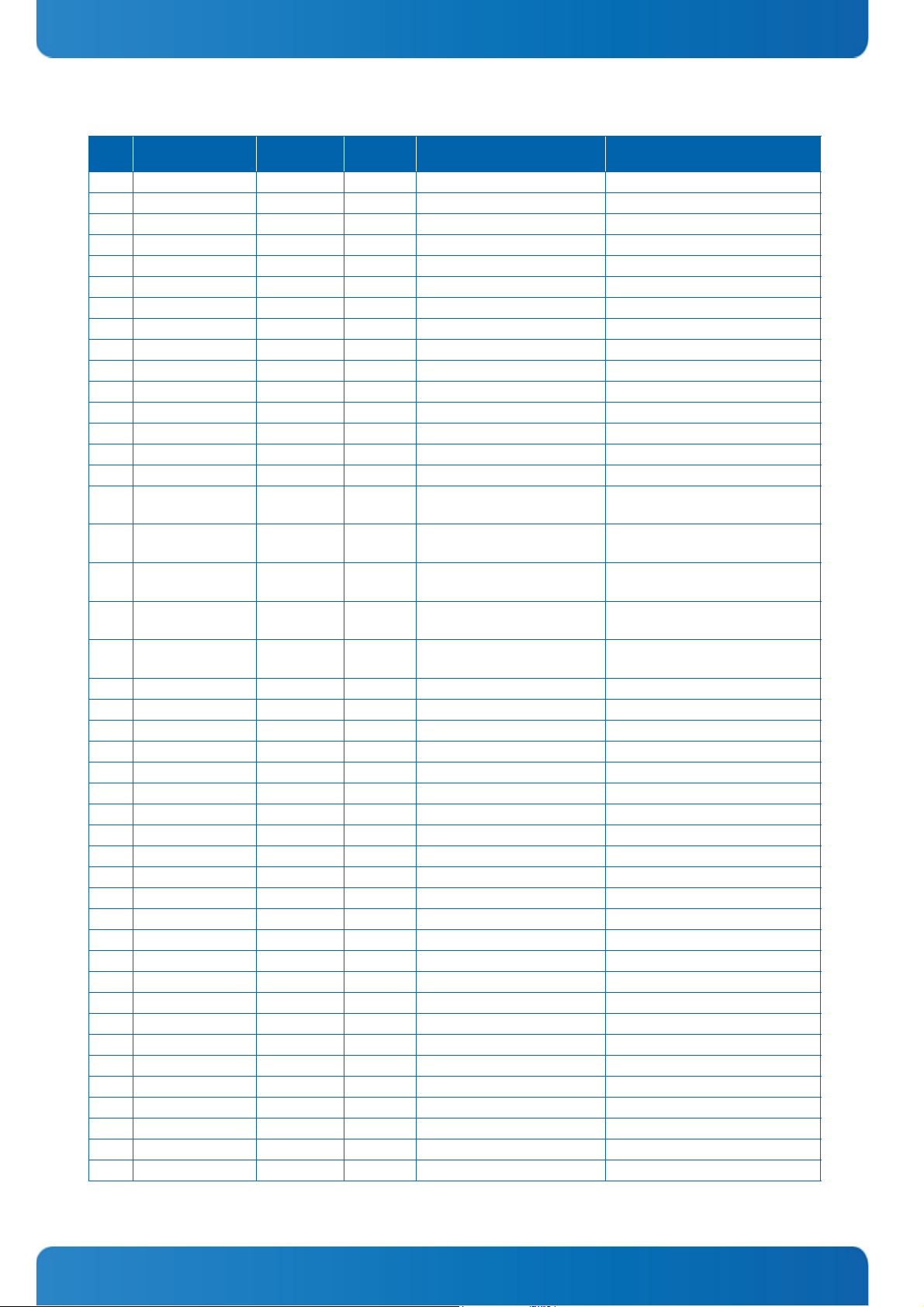

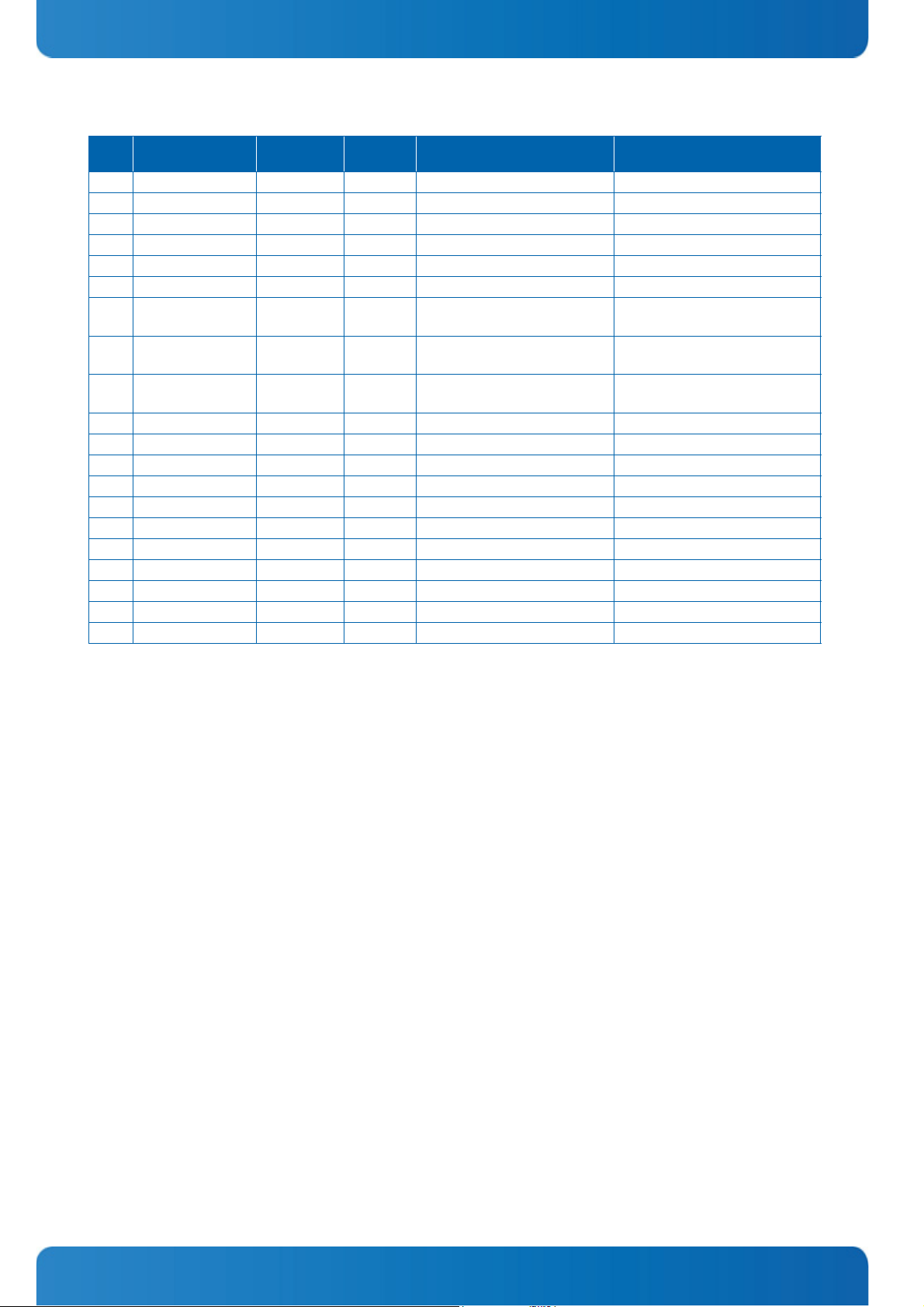

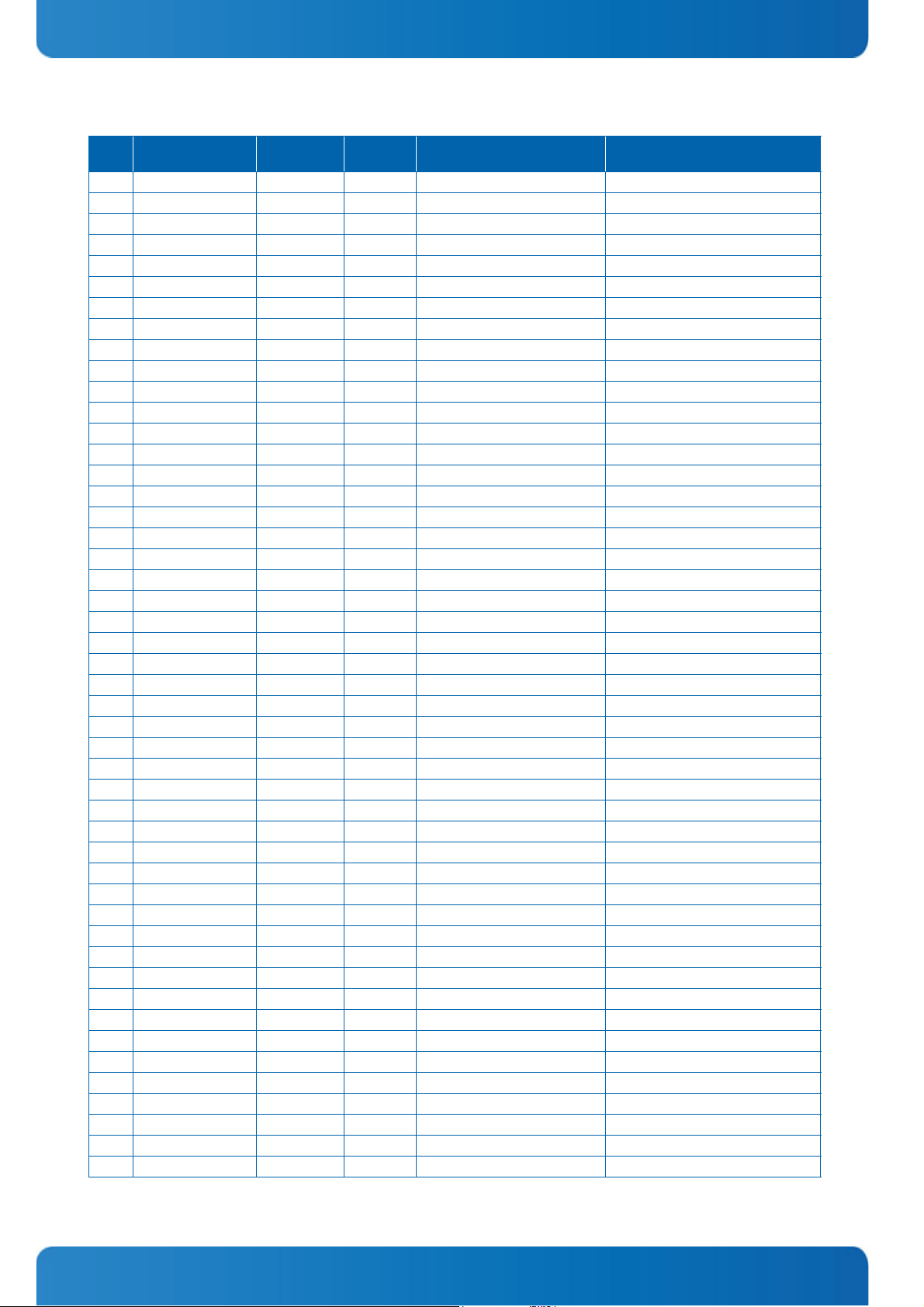

Table 2-1: Connector J1 Row A Pinout .............................................................................. 21

Table 2-2: Connector J1 Row B Pinout .............................................................................. 24

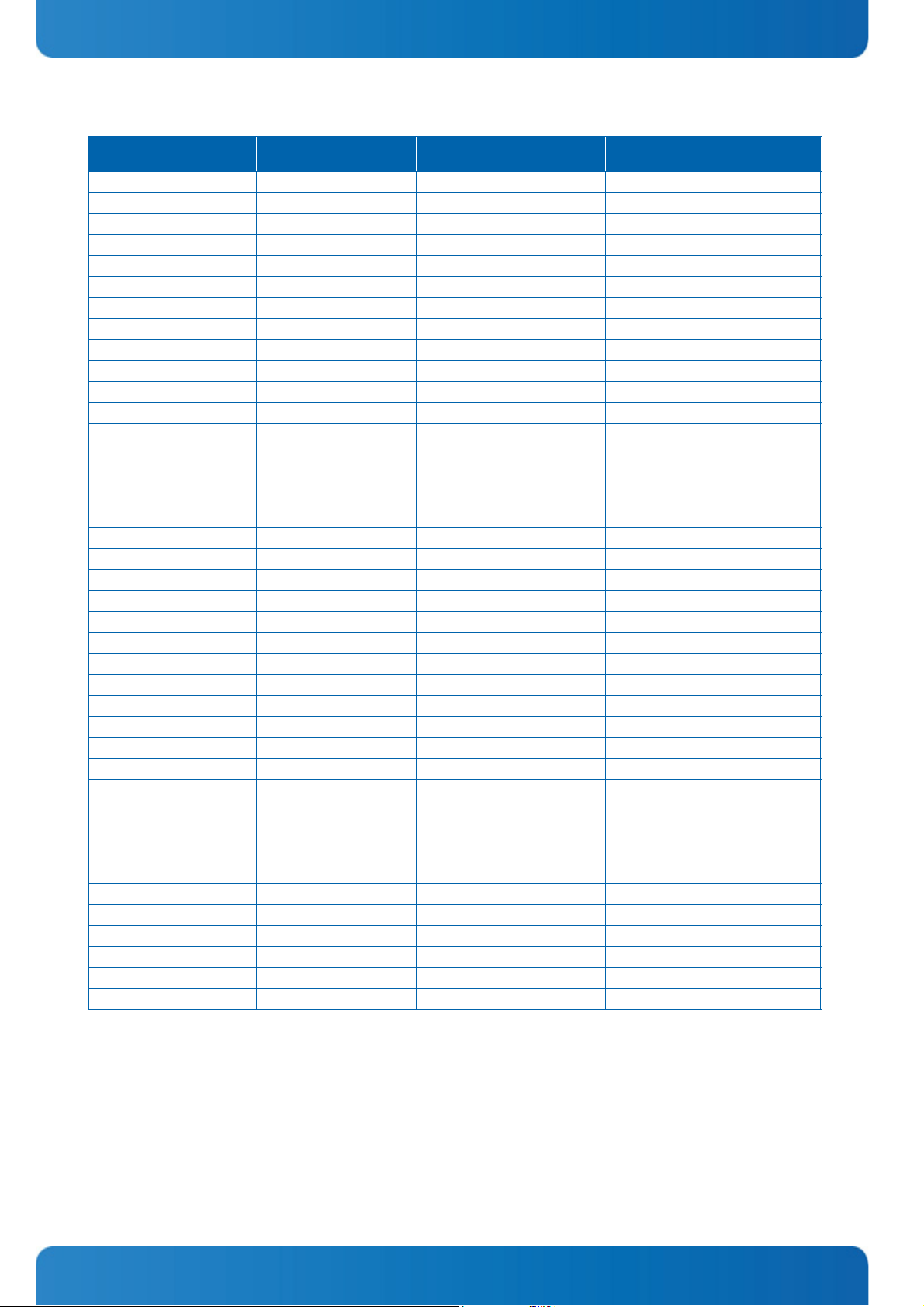

Table 2-3: Connector J2 Row C Pinout............................................................................... 27

Table 2-4: Connector J2 Row D Pinout .............................................................................. 30

Table 2-5: General Signal Description............................................................................... 32

Table 2-6: P2020 SerDes Lane Routing.............................................................................. 33

Table 2-7: SerDes Protocol Mapping ................................................................................. 34

Table 2-8: SPI Signal Configurations ................................................................................ 35

Table 2-9: On-Board Device Resource ............................................................................... 35

Table 2-10: JTAG/Debug Connector J4 Pinout ...................................................................... 37

Table 3-1: DIP Switch SW1 Configuration........................................................................... 38

Table 3-2: COMe-bP2020 Virtual and Physical Memory Address Map ........................................ 39

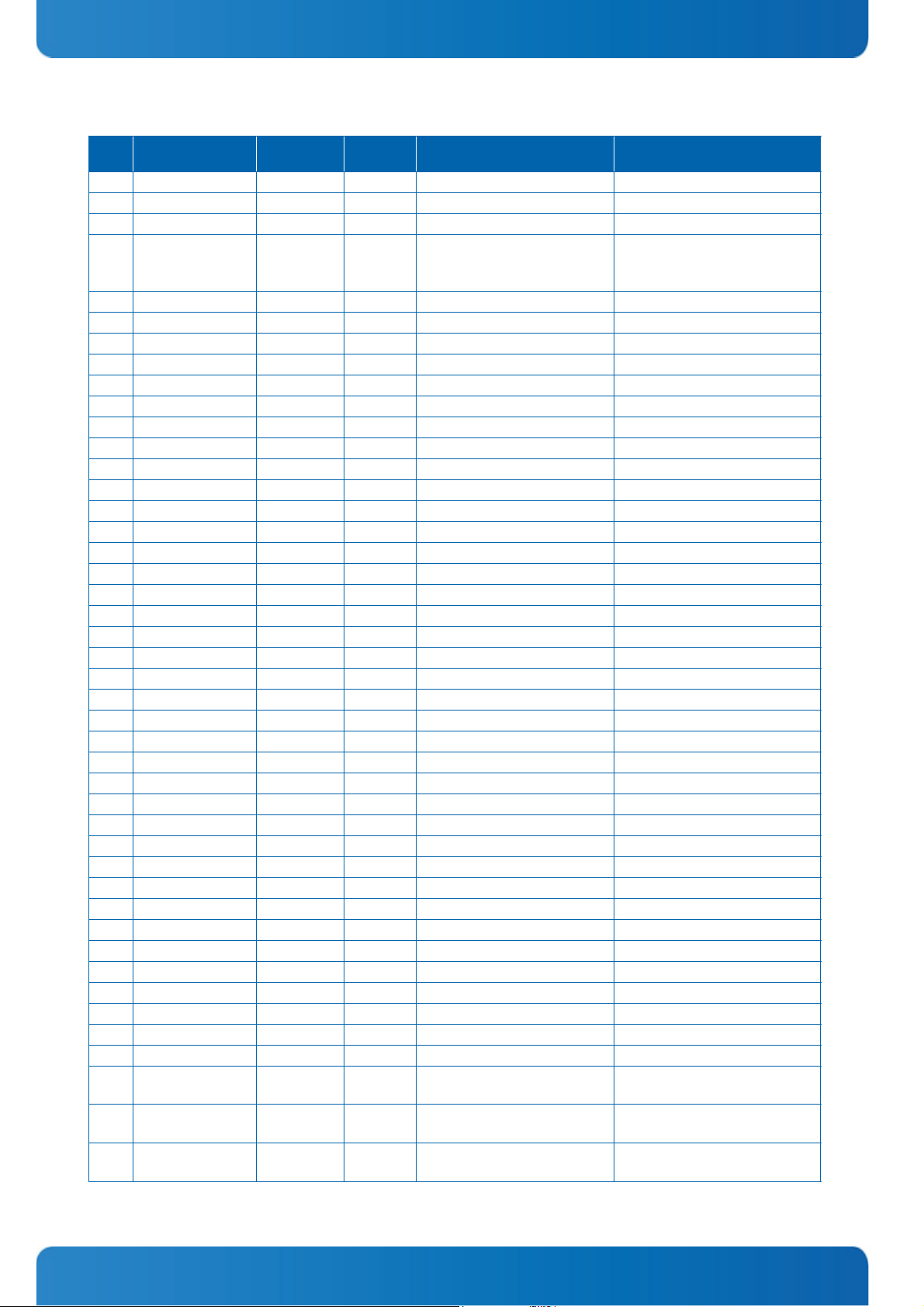

Table 3-3: I/O Address Map ............................................................................................ 40

Table 3-4: 0x000: User Boot ROM Location Configuration Register ......................................... 43

Table 3-5: 0x001: User Host/Agent Configuration Register ................................................... 44

Table 3-6: 0x002: User I/O Port Selection Register.............................................................. 45

Table 3-7: 0x003: User Boot Configuration Register ............................................................ 46

Table 3-8: 0x004: User Boot Sequencer Configuration Register.............................................. 46

Table 3-9: 0x005: User SerDes Reference Clock Configuration Register.................................... 46

Table 3-10: 0x006: User eTSEC2 SGMII Mode Configuration Register......................................... 47

Table 3-11: 0x007: User eTSEC3 SGMII Mode Configuration Register......................................... 47

Table 3-12: 0x008: User eTSEC1 Width Configuration Register................................................. 47

Table 3-13: 0x009: User eTSEC2 Protocol Configuration Register ............................................. 48

Table 3-14: 0x00A: User eTSEC3 Protocol Configuration Register ............................................. 48

Table 3-15: 0x00B: User RapidIO Device ID Register .............................................................. 49

Table 3-16: 0x00C: User RapidIO System Size Register ........................................................... 49

Table 3-17: 0x00D: User Core0 Speed Register ..................................................................... 49

Table 3-18: 0x00E: User Core1 Speed Register ..................................................................... 50

Table 3-19: 0x00F: User SerDes OLL Time-out Enable Register ................................................. 50

Table 3-20: 0x010: Serdes Multiplexer Control Register ......................................................... 51

5

www.kontron.com

Page 6

COMe-P2020 User Guide

Table 3-21: 0x011: User Checksum Register......................................................................... 51

Table 3-22: 0x012: UFM Erase Control Register .................................................................... 51

Table 3-23: 0x013: UFM/CPU Control and Status Register....................................................... 52

Table 3-24: 0x080: POST Code Low Byte Register .................................................................. 52

Table 3-25: 0x081: POST Code High Byte Register ................................................................. 52

Table 3-26: 0x084: Debug Low Byte Register ....................................................................... 52

Table 3-27: 0x085: Debug High Byte Register ...................................................................... 53

Table 3-28: 0x280: Status Register 0.................................................................................. 53

Table 3-29: 0x282: Control Register 0 ................................................................................ 53

Table 3-30: 0x284: Device Protection Register ..................................................................... 54

Table 3-31: 0x285: Reset Status Register ............................................................................ 54

Table 3-32: 0x286: Board Interrupt Configuration Register (not implemented!) ......................... 54

Table 3-33: 0x288: Board ID High Byte Register ................................................................... 55

Table 3-34: 0x289: Board and PLD Revision Register ............................................................. 55

Table 3-35: 0x28C: Watchdog Timer Register ....................................................................... 56

Table 3-36: 0x28D: Board ID Low Byte Register .................................................................... 56

Table 3-37: 0x290: LED Configuration Register .................................................................... 57

Table 3-38: 0x291: LED Control Register ............................................................................. 57

Table 3-39: 0x300: Default Boot ROM Location Configuration Register...................................... 58

Table 3-40: 0x301: Default Host/Agent Configuration Register ............................................... 58

Table 3-41: 0x302: Default I/O Selection Register ................................................................ 59

Table 3-42: 0x303: Default Boot Configuration Register......................................................... 60

Table 3-43: 0x304: Default Boot ROM Location Configuration Register...................................... 60

Table 3-44: 0x305: Default SerDes Reference Clock Configuration Register ................................ 60

Table 3-45: 0x306: Default eTSEC2 SGMII Mode Configuration Register ..................................... 61

Table 3-46: 0x307: Default eTSEC3 SGMII Mode Configuration Register ..................................... 61

Table 3-47: 0x308: Default eTSEC1 Width Configuration Register ............................................. 61

Table 3-48: 0x309: Default eTSEC2 Protocol Configuration Register (Reserved, See note!) ............ 62

Table 3-49: 0x30A: Default eTSEC3 Protocol Configuration Register (Reserved, See note!) ............ 62

Table 3-50: 0x30B: Default RapidIO Device ID Register .......................................................... 63

Table 3-51: 0x30C: Default RapidIO System Size Register ....................................................... 63

Table 3-52: 0x30D: Default Core0 Speed Register ................................................................. 63

Table 3-53: 0x30E: Default Core1 Speed Register (Reserved, see note!).................................... 64

Table 3-54: 0x30F: Default SerDes PLL Time-out Enable Register.............................................. 64

Table 3-55: 0x320-0x321: Scratchpad Registers #0-#1 .......................................................... 64

6

www.kontron.com

Page 7

COMe-P2020 User Guide

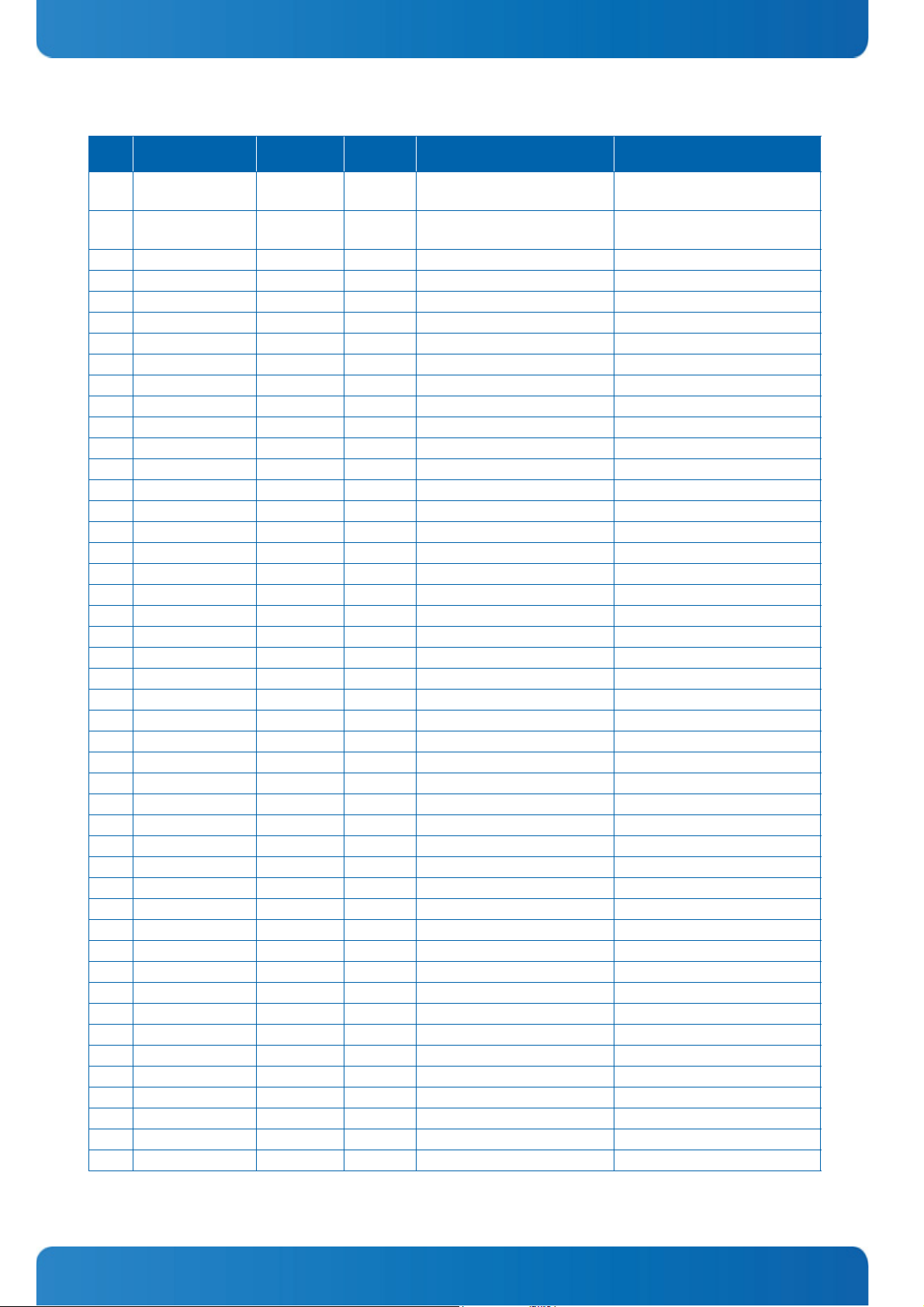

Table 3-56: 0x322-0x327: Scratchpad Registers #2-#7 (Not implemented) ................................ 65

Table 3-57: 0x330: Power Status Register ........................................................................... 65

Table 3-58: 0x338: CPU Status Register .............................................................................. 65

Table 3-59: 0x339: CPU Control Register............................................................................. 66

Table 3-60: 0x33A: Board Variant Register .......................................................................... 66

Table 3-61: 0x350: PCIe Status Register ............................................................................. 66

Table 3-62: 0x351: PCIe Control/Status Register .................................................................. 67

Table 3-63: 0x370: Carrier Interrupt Direction Register.......................................................... 67

Table 3-64: 0x374: Carrier Interrupt Mode 1 Register ............................................................ 68

Table 3-65: 0x375: Carrier Interrupt Mode 2 Register ............................................................ 68

Table 3-66: 0x376: Board Interrupt Pending Register 1.......................................................... 69

Table 3-67: 0x377: Board Interrupt Pending Register 2.......................................................... 69

Table 3-68: 0x378: Board Interrupt Pending Register 3.......................................................... 70

Table 3-69: 0x379: Board Interrupt Pending Register 4.......................................................... 70

Table 3-70: 0x37A: Board Interrupt Enable Register 1 ........................................................... 70

Table 3-71: 0x37B: Board Interrupt Enable Register 2 ........................................................... 71

Table 3-72: 0x37C: Board Interrupt Enable Register 3............................................................ 71

Table 3-73: 0x37D: Board Interrupt Enable Register 4 ........................................................... 72

Table 3-74: 0x380: Interrupt Multiplexer Register 1 .............................................................. 72

Table 3-75: 0x381: Interrupt Multiplexer Register 2 .............................................................. 72

Table 3-76: 0x390: Carrier Control Register ......................................................................... 73

Table 4-1: Supply Voltages ............................................................................................. 74

Table 4-2: Workload Dependency..................................................................................... 74

Table 4-3: Power Consumption vs. Ambient Temperature (Standard Board Variant).................... 74

Table 4-4: Power Consumption vs. Ambient Temperature (Extended Temperature Board Variant).. 75

Table 6-1: Standard U-Boot Commands Configured for the COMe-cP2020................................. 78

Table 6-2: Kontron-Specific Commands............................................................................. 81

Table 6-3: flsw Command ............................................................................................... 82

Table 6-4: kboardinfo Command...................................................................................... 83

Table 6-5: md5sum Command ......................................................................................... 84

Table 6-6: sconf Command ............................................................................................. 85

Table 6-7: tlbdbg Command............................................................................................ 88

Table 6-8: vpd Command................................................................................................ 89

Table 6-9: Naming Conventions....................................................................................... 98

7

www.kontron.com

Page 8

COMe-P2020 User Guide

List of Figures

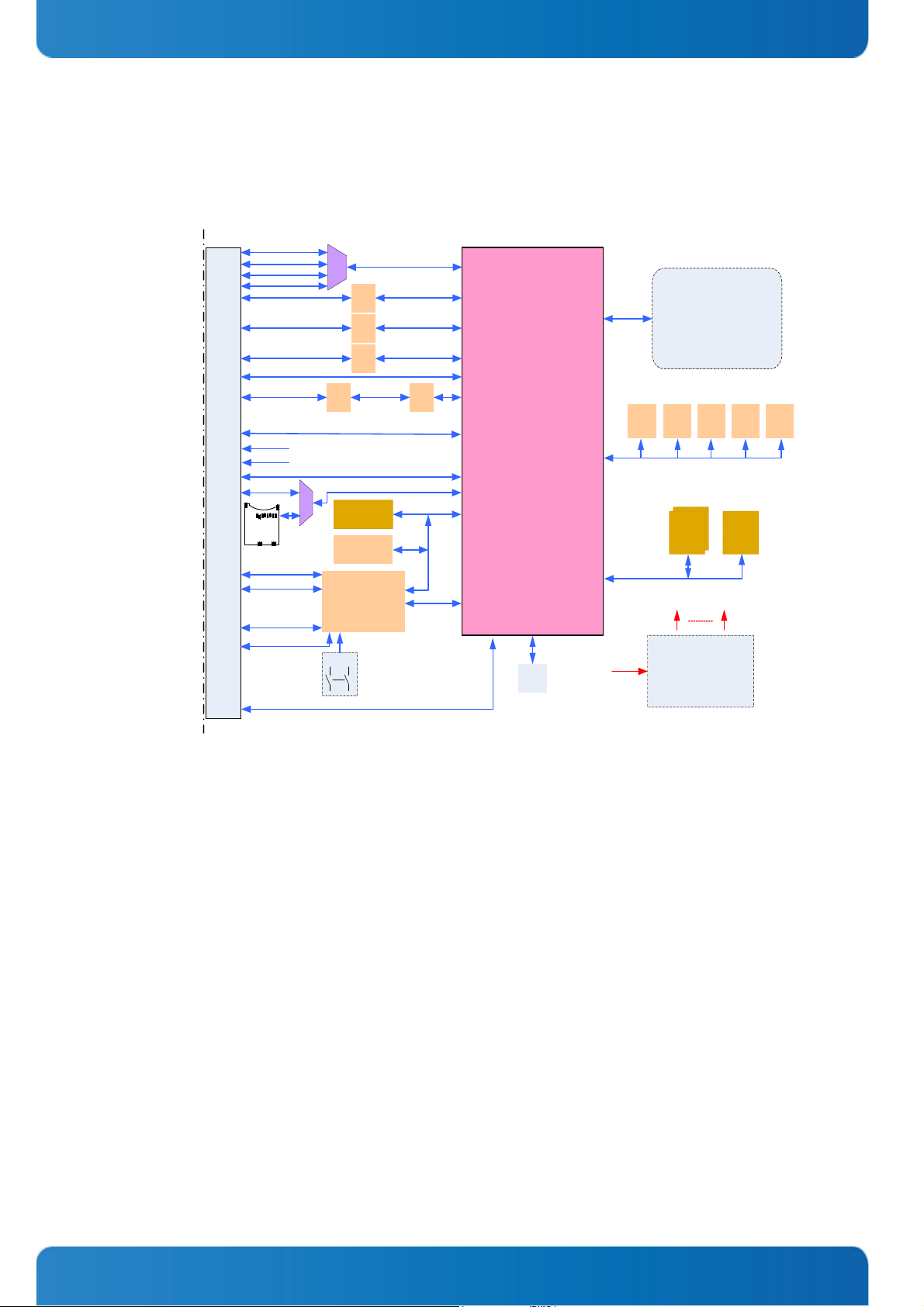

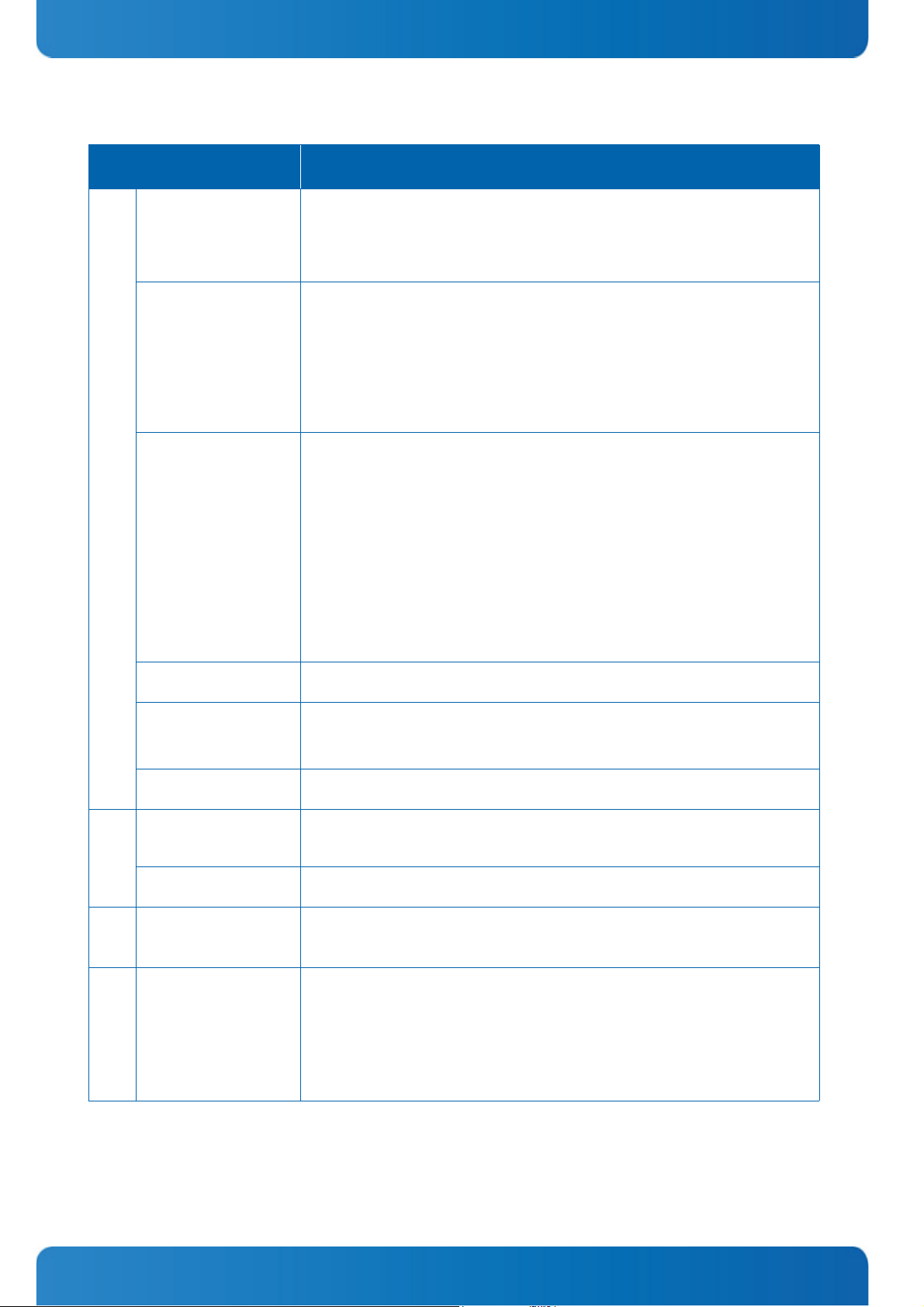

Figure 1-1: COMe-cP2020 Block Diagram ................................................................................. 12

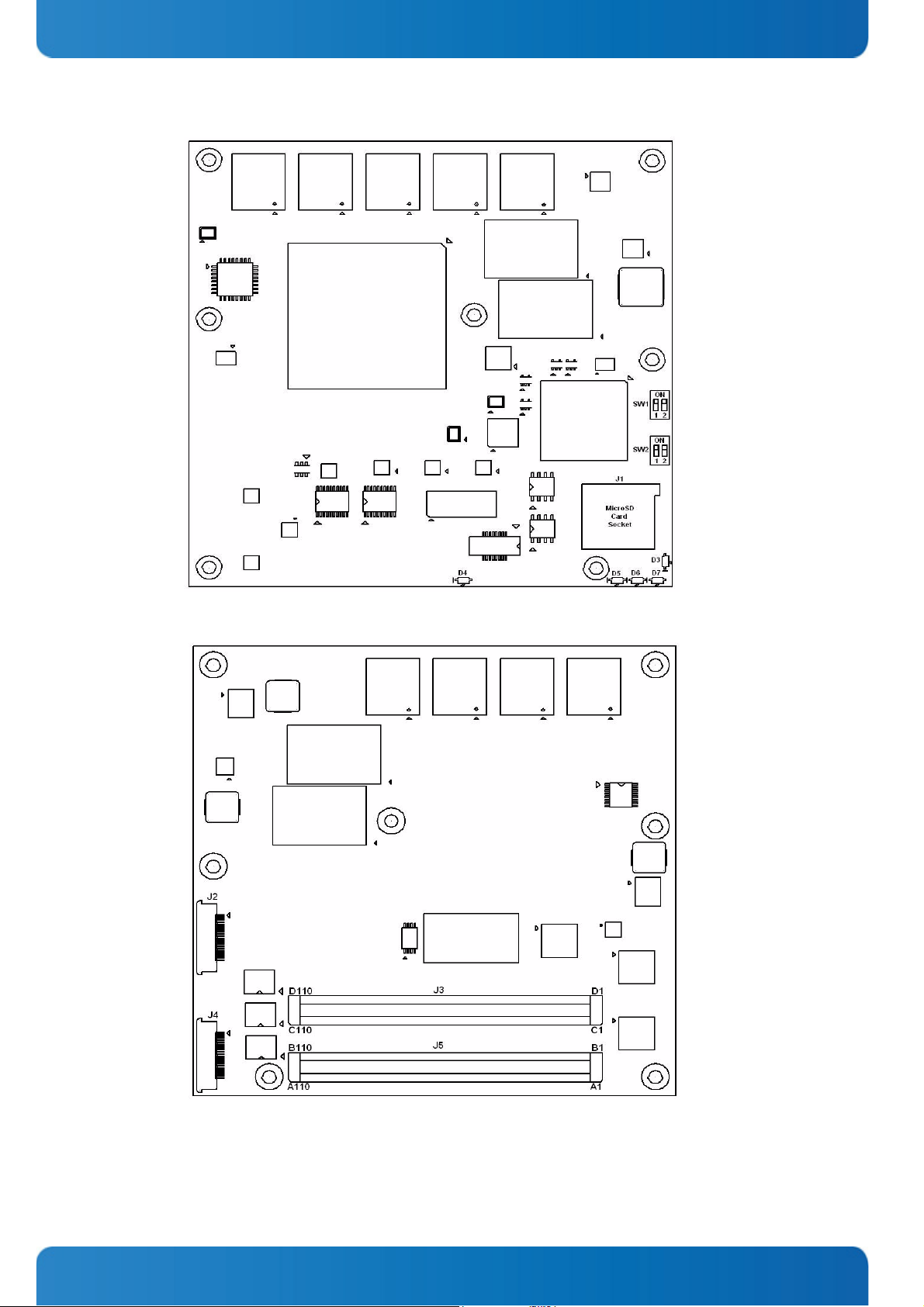

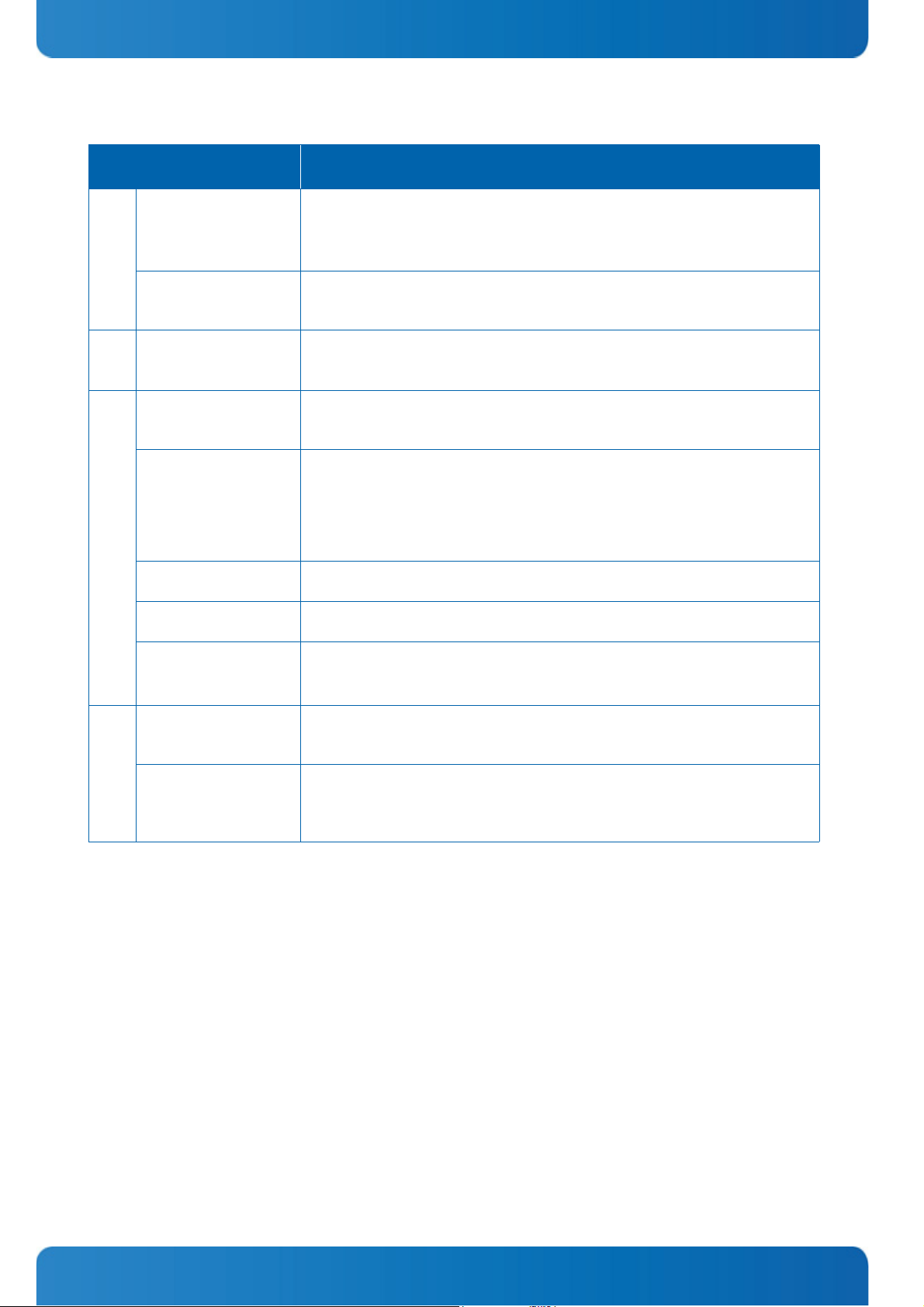

Figure 1-2: COMe-cP2020 Board Layout Top View ...................................................................... 13

Figure 1-3: COMe-cP2020 Board Layout Bottom View ................................................................. 13

Figure 2-1: IRQ Routing Scheme ............................................................................................ 36

Figure 5-1: Cooling Solution COMe-cP2020c............................................................................. 76

Figure 5-2: Cooling Solution COMe-cP2020i ............................................................................. 77

8

www.kontron.com

Page 9

COMe-P2020 User Guide

Proprietary Note

This document contains information proprietary to Kontron. It may not be copied or transmitted by any means, disclosed to

others, or stored in any retrieval system or media without the prior written consent of Kontron or one of its authorized

agents.

The information contained in this document is, to the best of our knowledge, entirely correct. However, Kontron cannot

accept liability for any inaccuracies or the consequences thereof, or for any liability arising from the use or application of

any circuit, product, or example shown in this document.

Kontron reserves the right to change, modify, or improve this document or the product described herein, as seen fit by Kontron without further notice.

Trademarks

Kontron and the Kontron logo are trade marks owned by Kontron AG, Germany. In addition, this document may include

names, company logos and trademarks, which are registered trademarks and, therefore, proprietary to their respective

owners.

Environmental Protection Statement

This product has been manufactured to satisfy environmental protection requirements where possible. Many of the com-

ponents used (structural parts, printed circuit boards, connectors, batteries, etc.) are capable of being recycled.

Final disposition of this product after its service life must be accomplished in accordance with applicable country, state, or

local la

ws or regulations.

General Instructions on Usage

In order to maintain Kontron’s product warranty, this product must not be altered or modified in any way. Changes or mod-

ifications to the device, which are not explicitly approved by Kontron and described in this manual or received from Kontron’s Technical Support as a special handling instruction, will void your warranty.

This device should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This applies also to the operational temperature range of the specific system version, which must not be

exceeded. If batteries are present their temperature restrictions must be taken into account.

In performing all necessary installation and application operations, please follow only the instructions supplied by the

present manual.

Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store or ship the system, please re-pack it as nearly as possible in the manner in which it was delivered.

Special care is necessary when handling or unpacking the product. Please consult the special handling and unpacking

instruction on the previous page of this manual.

Two Year Warranty

Kontron grants the original purchaser of Kontron’s products a TWO YEAR LIMITED HARDWARE WARRANTY as described in the following. However, no other warranties that may be granted or implied by anyone on behalf of Kontron are valid unless the consumer has the express written consent of Kontron.

Kontron warrants their own products, excluding software, to be free from manufacturing and material defects for a period

of 24 consecutive months from the date of purchase. This warranty is not transferable nor extendible to cover any other

users or long-term storage of the product. It does not cover products which have been modified, altered or repaired by any

other party than Kontron or their authorized agents. Furthermore, any product which has been, or is suspected of being

damaged as a result of negligence, improper use, incorrect handling, servicing or maintenance, or which has been damaged as a result of excessive current/voltage or temperature, or which has had its serial number(s), any other markings or

parts thereof altered, defaced or removed will also be excluded from this warranty.

If the customer’s eligibility for warranty has not been voided, in the event of any claim, he may return the product at the

earliest possible convenience to the original place of purchase, together with a copy of the original document of purchase,

a full description of the application the product is used on and a description of the defect. Pack the product in such a way as

to ensure safe transportation (see our safety instructions).

9

www.kontron.com

Page 10

COMe-P2020 User Guide

Kontron provides for repair or replacement of any part, assembly or sub-assembly at their own discretion, or to refund the

original cost of purchase, if appropriate. In the event of repair, refunding or replacement of any part, the ownership of the

removed or replaced parts reverts to Kontron, and the remaining part of the original guarantee, or any new guarantee to

cover the repaired or replaced items, will be transferred to cover the new or repaired items. Any extensions to the original

guarantee are considered gestures of goodwill, and will be defined in the “Repair Report” issued by Kontron with the

repaired or replaced item.

Kontron will not accept liability for any further claims resulting directly or indirectly from any warranty claim, other than

the above specified repair, replacement or refunding. In particular, all claims for damage to any system or process in which

the product was employed, or any loss incurred as a result of the product not functioning at any given time, are excluded.

The extent of Kontron liability to the customer shall not exceed the original purchase price of the item for which the claim

exists.

Kontron issues no warranty or representation, either explicit or implicit, with respect to its products’ reliability, fitness,

quality, marketability or ability to fulfil any particular application or purpose. As a result, the products are sold “as is,” and

the responsibility to ensure their suitability for any given task remains that of the purchaser. In no event will Kontron be

liable for direct, indirect or consequential damages resulting from the use of our hardware or software products, or documentation, even if Kontron were advised of the possibility of such claims prior to the purchase of the product or during any

period since the date of its purchase.

Please remember that no Kontron employee, dealer or agent is authorized to make any modification or addition to the

above specified terms, either verbally or in any other form, written or electronically transmitted, without the company’s

consent.

10

www.kontron.com

Page 11

COMe-P2020 User Guide

1Introduction

1.1 COMe-cP2020 Overview

The COMe-cP2020 is a COM Express® form factor compliant Power Architecture® processor module based on Freescale's

QorIQ™ 32-bit P2020 processor.

Designed in the COM Express® basic (95 mm x 95 mm) form factor the module incorporates the Freescale QorIQ P2020 dualcore Power Architecture® processor operating up to 1.2 GHz - other processor versions (P2010, P1020 and P1011) and

operating speeds are available on request. Featuring 32-bit technology, it integrates up to 4 GByte of soldered DDR3

SDRAM at 667 MHz and ECC support. 512 KBytes of shared second level cache facilitate core-to-core communications to

minimize accesses to main memory.

Up to 2 GByte of NAND Flash as well as a socket for MicroSD card offer reliable storage space for application data. In terms

of I/Os, the module interfaces the QorIQ-specific I/Os to the carrier board. In addition to USB 2.0 ports there are also UART

(TxD, RxD, RTC and CTS) and Gigabit Ethernet interfaces.

Flexible interface support is guaranteed by 4 SERDES lanes, which can be configured according to application-specific

needs. A comprehensive range of different combinations, for example as PCIe x4, sRIO x4 and Serial Gigabit Media Independent Interface (SGMII) is available.

The COMe-cP2020 targets high-bandwidth telecommunication and data processing applications. With its long-term availability of more than 10 years, it is also a good fit to be used in long life cycle network applications in the medical, military

and transportation markets.

Kontron offers two modules in standard and extended temperature range:

• COMe-cP2020c

• P2020NSN2MFC 1200 MHZ

• 2 GByte 667 MHz DDR3 Memory

•1 GByte NAND

• 0°C - 60 °C Ambient Temperature

• Standard COMe Heatspreader

• COMe-cP2020i

• P2020NXN2KFC 1000 MHZ

• 2 GByte 667 MHz DDR3 Memory

•1 GByte NAND

• -40°C - 85 °C Ambient Temperature

• Extended 95x95 mm Forced Air Cooling Heatsink

11

www.kontron.com

Page 12

1.2 Board Diagrams

SPI- NOR

FLASH

2x 8 Mb

DDR3 SDRAM

1/2/4 GB w ECC

9x DDR3 x8

1 bank solder ed

COM eP2020:COM Expressm odulebasedonQorIQP2020

Rev. 0.1

CPLD

Board Control

WDog, glue, etc.

COP/

JTAG

Debug

Freescale

Qor I Q P20 20

Dual-Core

32-bit PowerPC

up to 1.2 GHz

DDR3

RTC

RGMII

NAND FLASH

up to 2 GB

Sys

EEP

64kb

SPI

COP

Local Bus

I2C_1

SDHC

Micr oSD -Ca rd

Socket

Uboot Fl ash

redundant

SPI- NOR

Flash

64 Mb

GbE

PHY

Therm.

Sensor

User

EEP

64kb

72-bit ,

667 MHz

SPD

EEP

2kb

eTSEC 3

SPI- NOR

FLASH

16 Mb

OS Boot

ROM

2x Module Connector 0.5 mm pitch 220 pin 4H Receptacle A1-A110/B1-B110/C1-C110/D1-D110

SPI

SERDES 0- 3

SERDES 2

MDI

1x SDHC

ULPI

LAD Bus

4 DIP-SW

I2C#1

eLBC

OUT: 5V / 3.3V / 2.5V

1.5V / 1.2V / 1.05V / 0.75V

DC/DC

IN :12V

Up to 2x sRIO x1, x4

or 3x PCIe x1, x2, x4

or 2x GbE (SGMII)

GbE

USB 2.0

USB

Hub

4x USB 2.0

4x USB Hos t

2x RxD/ TxD/RTS/ CTS

1x SD-Card I/F

GPIO

ETH_Mngt 1

Local Bus

MRAM

512 KB

DUART

2x Serial

I2C_2

2x I2C

opt.

strictly confidential

SPI

SPI

MUX

SERDES 1

I2C#1

I2C#2

MDIO/MDC

ETH_Mngt 1

JTAG

JTAG

IEEE1588

IEEE1588

IEEE1588

MISC

EXP Card

EXP Card

MUX

opt.

USB

PHY

RGMII

GbE

PHY

eTSEC 2

MDI

GbE

RGMII

GbE

PHY

eTSEC 1

MDI

GbE

SERDES 3

SERDES 0,1 ,2,3

Figure 1-1: COMe-cP2020 Block Diagram

COMe-P2020 User Guide

12

www.kontron.com

Page 13

Figure 1-2: COMe-cP2020 Board Layout Top View

COMe-P2020 User Guide

Figure 1-3: COMe-cP2020 Board Layout Bottom View

13

www.kontron.com

Page 14

1.3 Technical Specifications

Table 1-1: COMe-cP2020 Main Specifications

COMe-cP2020 SPECIFICATIONS

CPU The COMe-cP2020 supports the following microprocessor:

• Freescale™ QorIQ™ P2020 processor, 1.2 GHz, 667 MHz platform frequency

standard temperature range

• Freescale™ QorIQ™ P2020 processor, 1.0 GHz, 667 MHz platform frequency extended temperature range

COMe-P2020 User Guide

PROCESSOR

available on request)

Integrated Controllers Controllers integrated in the CPU and utilized by the COMe-cP2020 are:

• eSDHC, eLBC, DUART, eTSEC, PCIe, sRIO, SPI, I²C

Memory Main memory:

• Up to 4 GB, dual-channel DDR3 SDRAM memory with ECC running at 667 MHz

(800 MHz version is available on request)

Cache structure:

• 32 kB instruction cache for each e500 core

• 32 kB data cache for each e500 core

• 512 kB shared L2 cache

Flash memory:

• Two SPI boot flashes (2 x 2 MB) for U-Boot selectable via the DIP switch

(Other operating speeds and processor variants (P2010, P1020 and P1011) are

MEMORY

• One 8 MB SPI flash for operating system or application

Mass storage device:

• Up to 2 GB NAND flash via an integrated/embedded NAND flash controller

• Up to 32 GB microSDHC flash via an integrated SDHC controller

MRAM memory:

• 512 kB of non-volatile memory

Two serial EEPROMs with 64 kbit:

• One for system data storage

14

• One free for user data storage

www.kontron.com

Page 15

Table 1-1: COMe-cP2020 Main Specifications (Continued)

COMe-cP2020 SPECIFICATIONS

Gigabit Ethernet Up to five Gigabit Ethernet ports:

• Three Gigabit Ethernet port through COMe MDI interface

• Up to two Gigabit Ethernet ports through SGMII interface

COMe-P2020 User Guide

SRIO

Serial RapidIO interfaces operate in host or agent configuration in various

speeds: 1.25 GHz, 2.5 GHz or 3.125GHz, depending on configuration

•One interface x1

•One interface x4

•Two interfaces x1

PCI Express

PCI Express interface operates in host or agent at 2.5 GHz (PCIe GEN1), depending on configuration

•One interface x1

•One interface x2

INTERCONNECTION

•One interface x4

•Two interfaces x1

•Two interfaces x2

• Three interfaces x1, x1, x2

Debug Interface One debug port

Serial Interface Up to two serial ports:

• 2x 4-wire UART interfaces (RxD, TxD, RTS, CTS)

GPIO/Interrupts Five GPIOs are shared with Interrupts. Function depends on configuration

Onboard Connectors

• Two 220-pin connectors for interfacing with a carrier board

• One JTAG/COP connector, J4, for debugging

microSD card Socket Standard microSD socket, J9, accepts microSD and microSDHC cards

Connectors

DIP Switch Two DIP switches for board configuration, SW1/SW2, consisting of two

Switch

Module Health Monitor

LEDs

LEDs

switches

CPLD HEALTY D4: indicates by blinking CPLD is active

LED0 D5:indicates U-Boot boot failure

LED1 D6: indicates CPU reset is asserted

LED2 D7: not used

LED3 D3: indicates Power-Good failure

15

www.kontron.com

Page 16

Table 1-1: COMe-cP2020 Main Specifications (Continued)

COMe-cP2020 SPECIFICATIONS

Watchdog Timer Software-configurable, two-stage Watchdog with programmable timeout

ranging from 125 ms to 4096 s in 16 steps

Serves for generating IRQ or hardware reset

TIMER

System Timer There are several timers implemented in the CPU. For further information

regarding these timers, refer to the CPU reference manual from Freescale.

Thermal Monitoring CPU and board temperature is provided by one onboard temperature sensor

for monitoring the board temperature

THERMAL

Power Consumption Refer to Chapter 5, “Power Considerations” for information related to the

power consumption of the COMe-cP2020.

COMe-P2020 User Guide

Temperature Range Operational:

• 0°C to +60°C (Standard Version)

• -40°C to +85°C (Extended Temperature Version)

Storage: -40°C to +70°C

GENERAL

Mechanical COM Express®compact

Dimensions 95 mm x 95 mm

Board Weight 99 grams (without heatspreader)

220 grams (with heatspreader)

Bootloader DENX U-Boot (Universal Boot Loader) with Kontron-specific modifications to

support the COMe-cP2020 requirements

Operating Systems The board is offered with various Board Support Packages including VxWorks

SOFTWARE

and Linux operating systems. For further information concerning the operating systems available for the COMe-cP2020, please contact Kontron.

16

www.kontron.com

Page 17

1.4 Standards

The COMe-cP2020 complies with the requirements of the following standards.

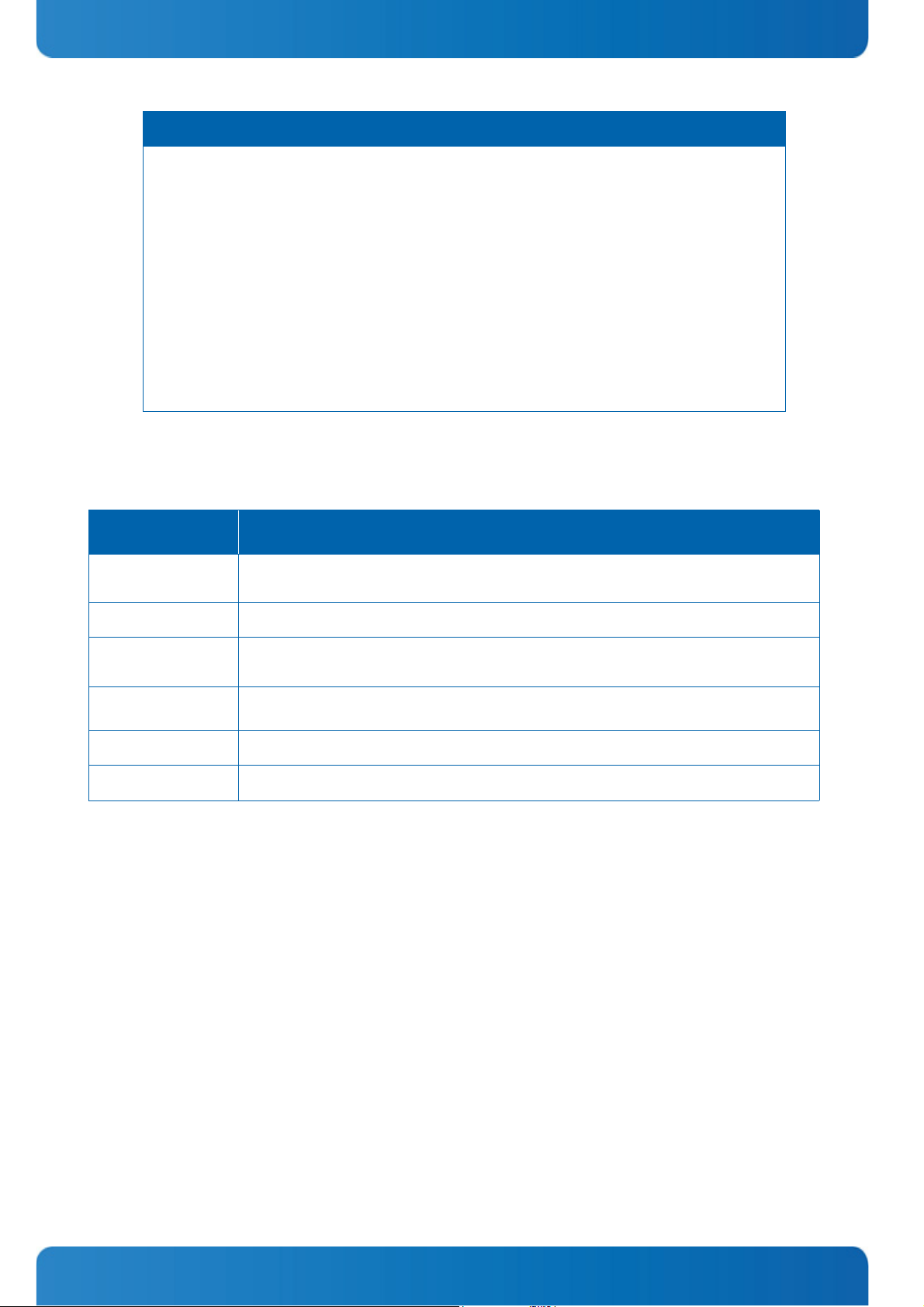

Table 1-2: Standards

COMPLIANCE TYPE STANDARD TEST LEVEL

COMe-P2020 User Guide

CE Emission EN55022

EN61000-6-3

Immission EN55024

EN61000-6-2

Electrical Safety EN60950-1 --

Railway Safety Electrical Safety EN50155 --

Mechanical Mechanical Dimensions COM Express® com-

pact

Environmental

and Health

Vibration

(sinusoidal, operating)

EN 50155

IEC 60068-2-6

Aspects

VITA 47

Shock (operating) EN 50155 Class 1B

Bump

Operating

IEC

60068-2-29

--

--

--

Class 1B

Frequency:10 - 300 Hz

Acceleration: 5 g

Class V1

5 to 100Hz

~2g RMS

Peak Accel.: 15 g

Shock Dur.: 11 ms half sine

Shock Count: 500

Climatic Humidity IEC60068-2-78 93% RH at 40°C, non-condensing

(see notice below)

WEEE Directive 2002/96/EC Waste electrical and electronic

equipment

RoHS-II Directive 2011/65/EC Restriction of the use of certain

hazardous substances in electrical and electronic equipment

17

www.kontron.com

Page 18

Kontron performs comprehensive environmental testing of its products in accordance with applicable standards.

Customers desiring to perform further environmental testing of Kontron products must contact

Kontron for assistance prior to performing any such testing. This is necessary, as it is possible

that environmental testing can be destructive when not performed in accordance with the applicable specifications.

In particular, for example, boards without conformal coating must not be exposed to a change of

temperature exceeding 1K/minute, averaged over a period of not more than five minutes. Otherwise, condensation may cause irreversible damage, especially when the board is powered up

again.

Kontron does not accept any responsibility for damage to products resulting from destructive

environmental testing.

1.5 Related Publications

COMe-P2020 User Guide

NOTICE

Table 1-3: Related Publications

SPECIFICATION /

ORGANIZATION

PUBLICATION

COM Express PICMG® COM.0, COM Express® Module Base Specification, Revision 2.0, August 8, 2010

Freescale, Kontron and Emerson Common Pinout Definition

PCI Express PCI Express Base Specification Revision 2.0, Dec. 20, 2006

Serial RapidIO

RapidIO

™ Interconnect Specification Part 6: LP-Serial Physical Layer Specification,

Rev. 2.0.1, March 2008

Ethernet IEEE802.3: Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD)

Access Method and Physical Layer Specification, Clause 22

Platform Firmware DENX “U-Boot” (Universal Boot Loader) online documentation at www.denx.de

Kontron Kontron’s Product Safety and Implementation Guide, ID 1021-9142

18

www.kontron.com

Page 19

COMe-P2020 User Guide

2 Functional Description

2.1 Processor

The COMe-cP2020 supports the high-performance, 32-bit, 45nm dual-core Freescale QorIQ P2020 processor with the following functions and features:

• Two e500v2 cores built on Power Architecture technology, running up to 1.2 GHz clock speed

• 512 Kbyte shared level two cache

• One 64-bit DDR3 SDRAM memory controllers with ECC and chip-select interleaving support

• Data path acceleration architecture incorporating acceleration for Packet-/Buffer- and Queue-Management

• Three 1 Gbps Ethernet controllers

• Up to three PCI Express 1.0a controllers/ports running at 2.5 Gbps

• Two serial RapidIO controllers/ports version 1.2 running at up to 3.125 Gbps

• One ULPI controller

• One SD/MMC controller

• One SPI controller

• Two I2C controllers

• Two DUARTs

• One enhanced local bus controller

• Multicore programmable interrupt controller

2.2 Memory

2.2.1 DDR3

The COMe-cP2020 supports a soldered, single-channel (72-bit), Double Data Rate (DDR3) memory with Error Checking and

Correcting (ECC) running at up to 800 MHz (memory error detection and reporting of 1-bit and 2-bit errors and correction

of 1-bit failures). The available memory configuration can be either 1 GB, 2 GB or 4 GB.

2.2.2 Flash Memory

2.2.2.1 SPI Boot Flash

The COMe-cP2020 provides two 2 MB SPI boot flashes for two separate U-Boot images, a standard SPI boot flash and a

recovery SPI boot flash. The fail-over mechanism for the U-Boot recovery can be controlled via the DIP switch SW1, switch

1. Refer to Chapter 6.10 for further information.

The SPI boot flashes include a hardware write protection option. If write protection is enabled, writing to the SPI boot

flashes is not possible.

N O T I C E

19

The U-Boot code and settings are stored in the SPI boot flashes. Changes made to the U-Boot settings are available only in the currently selected SPI boot flash. Thus, switching over to the other

SPI boot flash may result in operation with different U-Boot code and settings.

www.kontron.com

Page 20

COMe-P2020 User Guide

2.2.2.2 SPI OS/User Flash

The COMe-cP2020 supports 8 MB of soldered flash memory for the OS.

2.2.2.3 NAND Flash

The COMe-cP2020 supports up to 2 GB of soldered NAND flash memory, which is an SLC-based NAND flash. It is optimized for

embedded systems providing high performance, reliability and security.

2.2.2.4 MRAM Memory

The COMe-cP2020 supports 512 kB of MRAM memory (Magnetorestrictive Random Access Memory) for fast non-volatile

data storage (optional).

2.2.2.5 SDHC Socket

The COMe-cP2020 is provided with a microSDHC card socket, J1, which accepts microSD and microSDHC cards up to 32 GB. If

used, the card must be installed prior to installation of the COMe-cP2020 in a system.

If the SDHC interface is routed to the COM Express connector (via DIP switch SW1, switch [1]), the onboard socket J1 cannot

be used.

2.2.3 System/User Data EEPROMs

The COMe-cP2020 provides two 64-kBit EEPROMs, one for system data storage and one which is free for user data storage.

The user data EEPROM is accessible via the OS or an application. The system data EEPROM is reserved for system usage.

2.3 Timer

The COMe-cP2020 is equipped with the following timer:

• Real-Time Clock (RTC)

The COMe-cP2020 is equipped with an onboard high-precision real-time clock RV-8564-C3. The RV-8564-C3 RTC is registercompatible with the PCF8564A RTC from Philips/NXP. In addition, it provides a very tight frequency tolerance at low power

consumption. The COMe-cP2020 does not include a 3 V lithium battery or a GoldCap power source for RTC backup. Power for

the RTC is supplied by the carrier via the VCC_RTC pin.

2.4 Watchdog Timer

The COMe-cP2020 provides a Watchdog timer that is programmable for a timeout period ranging from 125 ms to 4096 s in

16 steps. Failure to trigger the Watchdog timer in time results in a interrupt or a system reset or both. In dual-stage mode,

it results in a combination of both interrupt and reset if the Watchdog is not serviced. A hardware status flag will be provided to determine if the Watchdog timer generated the reset. Refer to the Watchdog Timer Control Register (WTIM) in

Chapter 3 for further information.

There are four possible modes of operation involving the Watchdog timer:

• Timer only mode

• Reset mode

• Interrupt mode

• Dual stage mode

At power on the Watchdog is not enabled. If required, the bits of the Watchdog Timer Control Register must be set according

to the application requirements. To operate the Watchdog, the mode and time period required must first be set and then

the Watchdog enabled. Once enabled, the Watchdog can only be disabled or the mode changed by powering down and then

up again. To prevent a Watchdog timeout, the Watchdog must be retriggered before timing out. This is done by writing a ‘1’

to the WTR bit. In the event a Watchdog timeout does occur, the WTE bit is set to ‘1’. What transpires after this depends on

the mode selected.

20

www.kontron.com

Page 21

COMe-P2020 User Guide

The four operational Watchdog timer modes can be configured by the WMD[1:0] bits, and are described as follows:

Timer only mode - In this mode the Watchdog is enabled using the required timeout period. Normally, the Watchdog is

retriggered by writing a ‘1’ to the WTR bit. In the event a timeout occurs, the WTE bit is set to ‘1’. This bit can then be polled

by the application and handled accordingly. To continue using the Watchdog, write a ‘1’ to the WTE bit, and then retrigger

the Watchdog using WTR. The WTE bit retains its setting as long as no power down-up is done. Therefore, this bit may be

used to verify the status of the Watchdog.

Reset mode - This mode is used to force a hard reset in the event of a Watchdog timeout. In addition, the WTE bit is not reset

by the hard reset, which makes it available if necessary to determine the status of the Watchdog prior to the reset.

Interrupt mode - This mode causes the generation of an interrupt in the event of a Watchdog timeout. The interrupt handling is a function of the application. If required, the WTE bit can be used to determine if a Watchdog timeout has occurred.

Dual stage mode - This is a complex mode where in the event of a timeout two things occur: 1) an interrupt is generated,

and 2) the Watchdog is retriggered automatically. In the event a second timeout occurs following the first timeout, a hard

reset will be generated. The second timeout period is the same as the first. If the Watchdog is retriggered normally as specified above, operation continues. The interrupt generated at the first timeout is available to the application to handle the

first timeout if required. As with all of the other modes, the WTE bit is available for application use.

Pin B27 on the COM Express® J1 connector offers a signal that can be asserted when a Watchdog timer has not been triggered within time. It can be configured to any of the 2 stages. Deassertion of the signal is automatically done after reset. If

deassertion during runtime is necessary please contact Kontron for further assistance.

2.5 Connectors

2.5.1 COM Express Connectors

Table 2-1: Connector J1 Row A Pinout

PIN SIGNAL

A1 GND PWR GND

A2 GBE0_MDI3- GigE MDI DP-I/O eTSEC1_GBE0_MDI3-

A3 GBE0_MDI3+ GigE MDI DP-I/O eTSEC1_GBE0_MDI3+

A4 GBE0_LINK100# GigE MDI O-3.3 eTSEC1_GBE0_LINK100#

A5 GBE0_LINK1000# GigE MDI O-3.3 eTSEC1_GBE0_LINK1000#

A6 GBE0_MDI2- GigE MDI DP-I/O eTSEC1_GBE0_MDI2-

A7 GBE0_MDI2+ GigE MDI DP-I/O eTSEC1_GBE0_MDI2+

A8 GBE0_LINK# GigE MDI O-3.3 eTSEC1_GBE0_LINK#

A9 GBE0_MDI1- GigE MDI DP-I/O eTSEC1_GBE0_MDI1-

A10 GBE0_MDI1+ GigE MDI DP-I/O eTSEC1_GBE0_MDI1+

A11 GND PWR GND

A12 GBE0_MDI0- GigE MDI DP-I/O eTSEC1_GBE0_MDI0-

A13 GBE0_MDI0+ GigE MDI DP-I/O eTSEC1_GBE0_MDI0+

A14 GBE0_CTREF GigE MDI Not applicable

A15 SUS_S3# BOARD CTRL O-3.3 Undefined

A16 SATA0_TX+ SATA N/C

A17 SATA0_TX- SATA N/C

A18 SUS_S4# BOARD CTRL O-3.3 Undefined

A19 SATA0_RX+ SATA N/C

A20 SATA0_RX- SATA N/C

A21 GND PWR GND

A22 SATA2_TX+ SATA N/C

A23 SATA2_TX- SATA N/C

A24 SUS_S5# BOARD CTRL O-3.3 Undefined

A25 SATA2_RX+ SATA N/C

A26 SATA2_RX- SATA N/C

SIGNAL

GROUP

TYPE TERMINATION COMMENT

21

www.kontron.com

Page 22

COMe-P2020 User Guide

Table 2-1: Connector J1 Row A Pinout (Continued)

PIN SIGNAL

A27 BATLOW# BOARD CTRL I-3.3 Interrupt Source

A28 (S)ATA_ACT# SATA N/C

A29 AC/HAD_SYNC AUDIO N/C

A30 AC/HAD_RST# AUDIO N/C

A31 GND PWR GND

A32 AC/HAD_BITCLK AUDIO N/C

A33 AC/HAD_SDOUT AUDIO N/C

A34 BIOS_DIS0# BOARD CTRL I-3.3 N/C

A35 THERMTRIP# BOARD CTRL O-3.3 THERMTRIP#

A36 USB6- USB2.0 N/C

A37 USB6+ USB2.0 N/C

A38 USB_6_7_OC# USB2.0 N/C

A39 USB4- USB2.0 N/C

A40 USB4+ USB2.0 N/C

A41 GND PWR GND

A42 USB2- USB2.0/

A43 USB2+ USB2.0/

A44 USB_2_3_OC# USB2.0/

A45 USB0- USB2.0/

A46 USB0+ USB2.0/

A47 VCC_RTC PWR 3V VCC_RTC

A48 EXCD0_PERST# EXP CARD O-3.3 Undefined

A49 EXCD0_CPPE# EXP CARD I-3.3 Undefined

A50 RSVD Local Bus O-3.3 LA16

A51 GND PWR GND

A52 SERDES_TX5+ SERDES N/C

A53 SERDES_TX5- SERDES N/C

A54 GPIO/SD_DATA0 GPIO/SDIO I/O-3.3 SD_DATAO

A55 SERDES_TX4+ SERDES DP-O MUX_PCIE_TX1_P

A56 SERDES_TX4- SERDES DP-O MUX_PCIE_TX1_N

A57 GND PWR GND

A58 SERDES_TX3+ SERDES DP-O SERDES_TX3+

A59 SERDES_TX3- SERDES DP-O SERDES_TX3-

A60 GND PWR GND

A61 SERDES_TX2+ SERDES DP-O SERDES_TX2+

A62 SERDES_TX2- SERDES DP-O SERDES_TX2-

A63 GPI1/SD_DATA1 GPIO/SDIO I/O-3.3 SD_DATA1

A64 SERDES_TX1+ SERDES DP-O SERDES_TX1+

A65 SERDES_TX1- SERDES DP-O SERDES_TX1-

A66 GND PWR GND

A67 GPI2/SD_DATA2 GPIO/SDIO I/O-3.3 SD_DATA2

A68 SERDES_TX0+ SERDES DP-O SERDES_TX0+

A69 SERDES_TX0- SERDES DP-O SERDES_TX0-

A70 GND PWR GND

SIGNAL

GROUP

USB3.0

USB3.0

USB3.0

USB3.0

USB3.0

TYPE TERMINATION COMMENT

USB2-

USB2+

I-3.3 USB_2_3_OC#

DP-I/O USB0-

DP-I/O USB0+

22

www.kontron.com

Page 23

COMe-P2020 User Guide

Table 2-1: Connector J1 Row A Pinout (Continued)

PIN SIGNAL

A71 LVDS_A0+ LVDS RSVD

A72 LVDS_A0- LVDS RSVD

A73 LVDS_A1+ LVDS RSVD

A74 LVDS_A1- LVDS RSVD

A75 LVDS_A2+ LVDS RSVD

A76 LVDS_A2- LVDS RSVD

A77 LVDS_VDD_EN LVDS RSVD

A78 LVDS_A3+ LVDS RSVD

A79 LVDS_A3- LVDS RSVD

A80 GND PWR GND

A81 LVDS_A_CK+ LVDS RSVD

A82 LVDS_A_CK- LVDS RSVD

A83 LVDS_I2C_CK LVDS RSVD

A84 LVDS_I2C_DAT LVDS RSVD

A85 GPI3/SD_DATA3 GPIO/SDIO I/O-3.3 SD_DATA3

A86 RSVD19 Local Bus O-3.3 LA18

A87 RSVD19 Local Bus O-3.3 LA17

A88 SERDES_CK_REF1+ SERDES O-3.3 SERDES_CK_REF+

A89 SERDES_CK_REF1- SERDES O-3.3 SERDES_CK_REF-

A90 GND PWR GND

A91 SPI_POWER SPI O-3.3 3.3V Source for carrier SPI flash

A92 SPI_MISO SPI I-3.3 SPI_MISO

A93 GPO0/SD_CLK GPIO/SDIO O-3.3 SD_CLK

A94 SPI_CLK SPI SPI_CLK

A95 SPI_MOSI SPI O-3.3 SPI_MOSI

A96 TPM_PP BOARD CTRL GND

A97 TYPE10# TYPE Single 4K7 pull down, DNI

A98 SER0_TX UART O-3.3 U0_TXD

A99 SER0_RX UART I-3.3 U0_RXD

A100 GND PWR GND

A101 SER1_TX UART O-3.3 U1_TXD

A102 SER1_RX UART I-3.3 U1_RXD

A103 LID# BOARD CTRL N/C

A104 VCC_12V PWR VCC_12V

A105 VCC_12V PWR VCC_12V

A106 VCC_12V PWR VCC_12V

A107 VCC_12V PWR VCC_12V

A108 VCC_12V PWR VCC_12V

A109 VCC_12V PWR VCC_12V

A110 GND PWR GND

SIGNAL

GROUP

TYPE TERMINATION COMMENT

23

www.kontron.com

Page 24

COMe-P2020 User Guide

Table 2-2: Connector J1 Row B Pinout

PIN SIGNAL

B1 GND PWR

B2 GBE0_ACT# GigE MDI

B3 1588_CLK_OUT IEEE1588 O-3.3 1588_CLK_OUT

B4 1588_PULSE_OUT1 IEEE1588 O-3.3 1588_PULSE_OUT1

B5 1588_PULSE_OUT2 IEEE1588 O-3.3 1588_PULSE_OUT2

B6 1588_ALARM_OUT1 IEEE1588 O-3.3 1588_ALARM_OUT1

B7 1588_ALARM_OUT2 IEEE1588 O-3.3 1588_ALARM_OUT2

B8 1588_TRIG_IN1 IEEE1588 I-3.3 1588_TRIG_IN1

B9 1588_TRIG_IN2 IEEE1588 I-3.3 1588_TRIG_IN2

B10 1588_CLK_IN IEEE1588 I-3.3 1588_CLK_IN

B11 GND PWR GND

B12 PWRBTN# BOARD CTRL I-3.3 Undefined

B13 SMB_CK SMB I/O-3.3 SMB_CK

B14 SMB_DAT SMB I/O-3.3 SMB_DAT

B15 SMB_ALERT# SMB 3.3 Interrupt Source

B16 SATA1_TX+ SATA N/C

B17 SATA1_TX- SATA N/C

B18 SUS_STAT# BOARD CTRL O-3.3 N/C

B19 SATA1_RX+ SATA N/C

B20 SATA1_RX- SATA N/C

B21 GND PWR GND

B22 SATA3_TX+ SATA N/C

B23 SATA3_TX- SATA N/C

B24 PWR_OK BOARD CTRL I-3.3 PWR_OK

B25 SATA3_RX+ SATA N/C

B26 SATA3_RX- SATA N/C

B27 WDT BOARD CTRL WDT

B28 AC/HAD_SDIN2 AUDIO N/C

B29 AC/HAD_SIN1 AUDIO N/C

B30 AC/HAD_SIN0 AUDIO N/C

B31 GND PWR GND

B32 SPKR BOARD CTRL N/C

B33 I2C_CK I2C I/O-3.3 I2C_CK

B34 I2C_DAT I2C I/O-3.3 I2C_DAT

B35 THERM# BOARD CTRL I-3.3 Interrupt Source

B36 USB7- USB2.0 N/C

B37 USB7+ USB2.0 N/C

B38 USB_4_5_OC# USB2.0 N/C

B39 USB5- USB2.0 N/C

B40 USB5+ USB2.0 N/C

B41 GND PWR GND

B42 USB3- USB2.0/

B43 USB3+ USB2.0/

B44 USB_0_1_OC# USB2.0/

SIGNAL

GROUP

USB3.0

USB3.0

USB3.0

TYPE TERMINATION COMMENT

USB3-

USB3+

I-3.3 USB_0_1_OC#

24

www.kontron.com

Page 25

COMe-P2020 User Guide

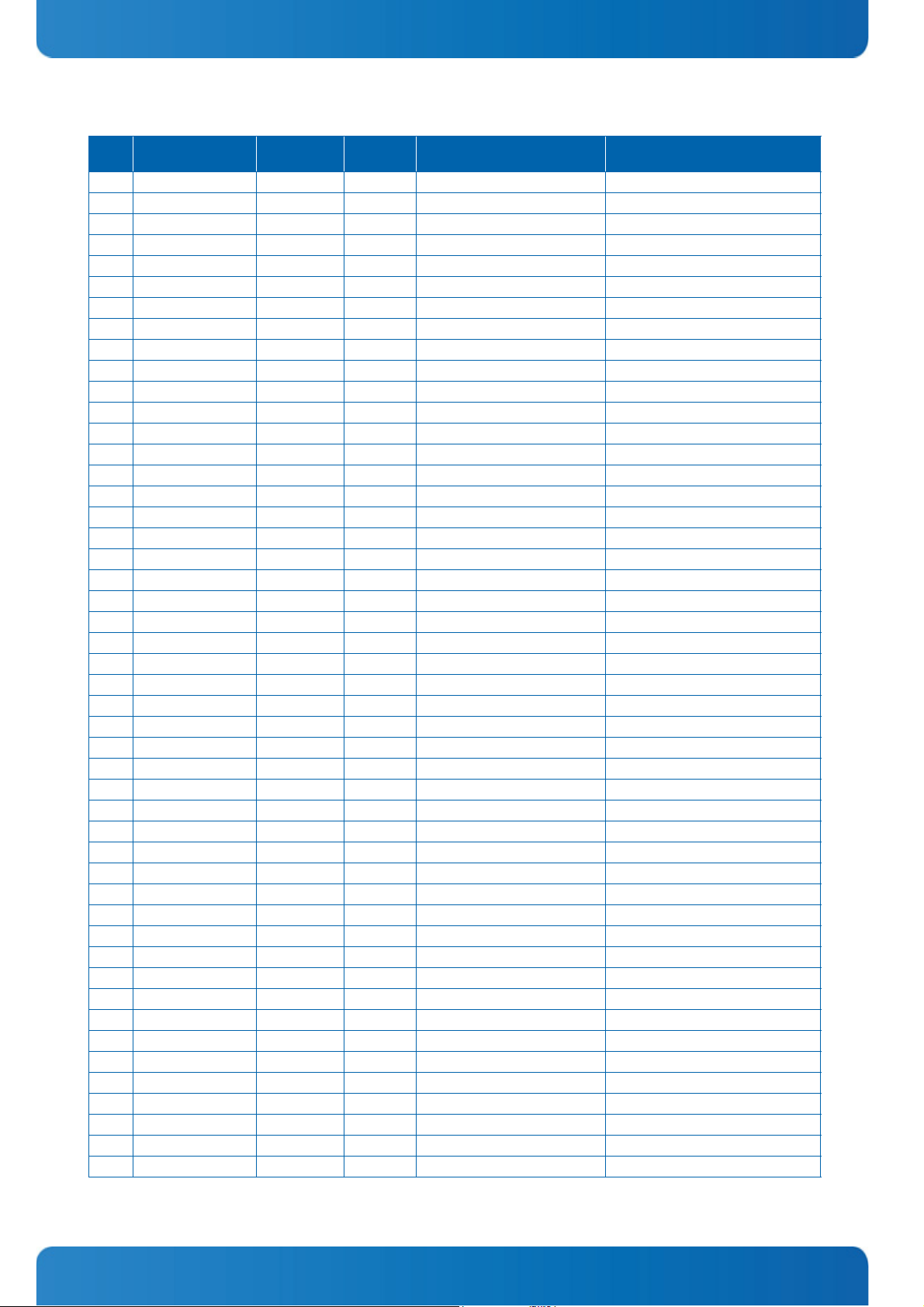

Table 2-2: Connector J1 Row B Pinout (Continued)

PIN SIGNAL

B45 USB1- USB2.0/

B46 USB1+ USB2.0/

B47 EXCD1_PERST# EXP CARD O-3.3 Undefined

B48 EXCD1_CPPE# EXP CARD I-3.3 Undefined

B49 SYS_RESET# BOARD CTRL I-3.3 SYS_RESET#

B50 CB_RESET# BOARD CTRL O-3.3 CB_RESET#

B51 GND PWR GND

B52 SERDES_RX5+ SERDES N/C

B53 SERDES_RX5- SERDES N/C

B54 GP01/SD_CMD GPIO/SDIO O-3.3 SD_CMD

B55 SERDES_RX4+ SERDES DP-I MUX_PCIE_RX1_P

B56 SERDES_RX4- SERDES DP-I MUX_PCIE_RX1_N

B57 GPO/SD_WP GPIO/SDIO 0-3.3 SD_WP

B58 SERDES_RX3+ SERDES DP-I PCIE_RX3+

B59 SERDES_RX3- SERDES DP-I PCIE_RX3-

B60 GND PWR GND

B61 SERDES_RX2+ SERDES DP-I PCIE_RX2+

B62 SERDES_RX2- SERDES DP-I PCIE_RX2-

B63 GPO3/SD_CD# GPIO/SDIO I-3.3 SD_CD#

B64 SERDES_RX1+ SERDES DP-I PCIE_RX1+

B65 SERDES_RX1- SERDES DP-I PCIE_RX1-

B66 WAKE0# BOARD CTRL I-3.3 N/C

B67 WAKE1# BOARD CTRL I-3.3 N/C

B68 SERDES_RX0+ SERDES DP-I PCIE_RX0+

B69 SERDES_RX0- SERDES DP-I PCIE_RX0-

B70 GND PWR GND

B71 LVDS_B0+ LVDS N/C

B72 LVDS_B0- LVDS N/C

B73 LVDS_B1+ LVDS N/C

B74 LVDS_B1- LVDS N/C

B75 LVDS_B2+ LVDS N/C

B76 LVDS_B2- LVDS N/C

B77 LVDS_B3+ LVDS N/C

B78 LVDS_B3- LVDS N/C

B79 LVDS_BKLT_EN LVDS N/C

B80 GND PWR GND

B81 LVDS_B_CK+ LVDS N/C

B82 LVDS_B_CK- LVDS N/C

B83 LVDS_BKLT_CTRL LVDS N/C

B84 VCC_5V_SBY PWR VCC_5V_SBY

B85 VCC_5V_SBY PWR VCC_5V_SBY

B86 VCC_5V_SBY PWR VCC_5V_SBY

B87 VCC_5V_SBY PWR VCC_5V_SBY

B88 BIOS_DIS1# SPI I-3.3 Undefined

B89 VGA_RED RSVD N/C

B90 GND PWR GND

SIGNAL

GROUP

USB3.0

USB3.0

TYPE TERMINATION COMMENT

USB1-

USB1+

25

www.kontron.com

Page 26

COMe-P2020 User Guide

Table 2-2: Connector J1 Row B Pinout (Continued)

PIN SIGNAL

B91 VGA_GRN RSVD N/C

B92 VGA_BLU RSVD N/C

B93 VGA_HSYNC RSVD N/C

B94 VGA_VSYNC RSVD N/C

B95 VGA_I2C_CK RSVD N/C

B96 VGA_I2C_DAT RSVD N/C

B97 SPI_CS# SPI O-3.3 SPI_CS0#/SPI_CS1#

B98 MDC (clause 45) GBE MDIO N/C

B99 MDIO (clause 45) GBE MDIO N/C

B100 GND PWR GND

B101 FAN_PWNOUT BOARD CTRL N/C

B102 FAN_TACHIN BOARD CTRL I-3.3 N/C

B103 SLEEP# BOARD CTRL I-3.3 N/C

B104 VCC_12V PWR VCC_12V

B105 VCC_12V PWR VCC_12V

B106 VCC_12V PWR VCC_12V

B107 VCC_12V PWR VCC_12V

B108 VCC_12V PWR VCC_12V

B109 VCC_12V PWR VCC_12V

B110 GND PWR GND

SIGNAL

GROUP

TYPE TERMINATION COMMENT

26

www.kontron.com

Page 27

COMe-P2020 User Guide

Table 2-3: Connector J2 Row C Pinout

PIN SIGNAL

C1 GND PWR GND

C2 GND PWR eTSEC2_GBE1_ACT#

C3 USB_SSRX0- USB3.0 eTSEC2_GBE1_MDI3-

C4 USB_SSRX0+ USB3.0 eTSEC2_GBE1_MDI3+

C5 GND PWR eTSEC2_GBE1_LINK100#

C6 USB_SSRX1- USB3.0 eTSEC2_GBE1_MDI2-

C7 USB_SSRX1+ USB3.0 eTSEC2_GBE2_MDI2+

C8 GND PWR eTSEC2_GBE1_LINK1000#

C9 USB_SSRX2- USB3.0 eTSEC2_GBE1_MDI1-

C10 USB_SSRX2+ USB3.0 eTSEC2_GBE1_MDI1+

C11 GND PWR GND

C12 USB_SSRX3- USB3.0 eTSEC2_GBE1_MDI0-

C13 USB_SSRX3+ USB3.0 eTSEC2_GBE2_MDI0+

C14 GND PWR eTSEC2_GBE1_LINK#

C15 DDI1_PAIR6+ DDI N/C

C16 DDI1_PAIR6- DDI N/C

C17 LOE# Local Bus O-3.3 LOE#

C18 LWE# Local Bus O-3.3 LWE#

C19 SERDES_RX6+ SERDES N/C

C20 SERDES_RX6- SERDES N/C

C21 GND PWR GND

C22 SERDES_RX7+ SERDES N/C

C23 SERDES_RX7- SERDES N/C

C24 DDI1_HPD DDI N/C

C25 DDI1_PAIR4+ DDI N/C

C26 DDI1_PAIR4- DDI N/C

C27 LAD0 Local Bus I/O-3.3 LAD0

C28 LAD1 Local Bus I/O-3.3 LAD1

C29 DDI1_PAIR5+ DDI N/C

C30 DDI1_PAIR5- DDI N/C

C31 GND PWR GND

C32 LAD2 Local Bus I/O-3.3 LAD2

C33 LAD3 Local Bus I/O-3.3 LAD3

C34 LAD4 Local Bus I/O-3.3 LAD4

C35 LAD5 Local Bus I/O-3.3 LAD5

C36 LAD6 Local Bus I/O-3.3 LAD6

C37 LAD7 Local Bus I/O-3.3 LAD7

C38 LAD8 Local Bus I/O-3.3 LAD8

C39 LAD9 Local Bus I/O-3.3 LAD9

C40 LAD10 Local Bus I/O-3.3 LAD10

C41 GND PWR GND

C42 LAD11 Local Bus I/O-3.3 LAD11

C43 LAD12 Local Bus I/O-3.3 LAD12

C44 LAD13 Local Bus I/O-3.3 LAD13

C45 LAD14 Local Bus I/O-3.3 LAD14

C46 LAD15 Local Bus I/O-3.3 LAD15

C47 MDC (clause 22) GBE MDIO O-2.5 MDC (clause 22)

C48 MDIO (clause 22) GBE MDIO I/O-2.5 MDIO (clause 22)

SIGNAL

GROUP

TYPE TERMINATION COMMENT

27

www.kontron.com

Page 28

COMe-P2020 User Guide

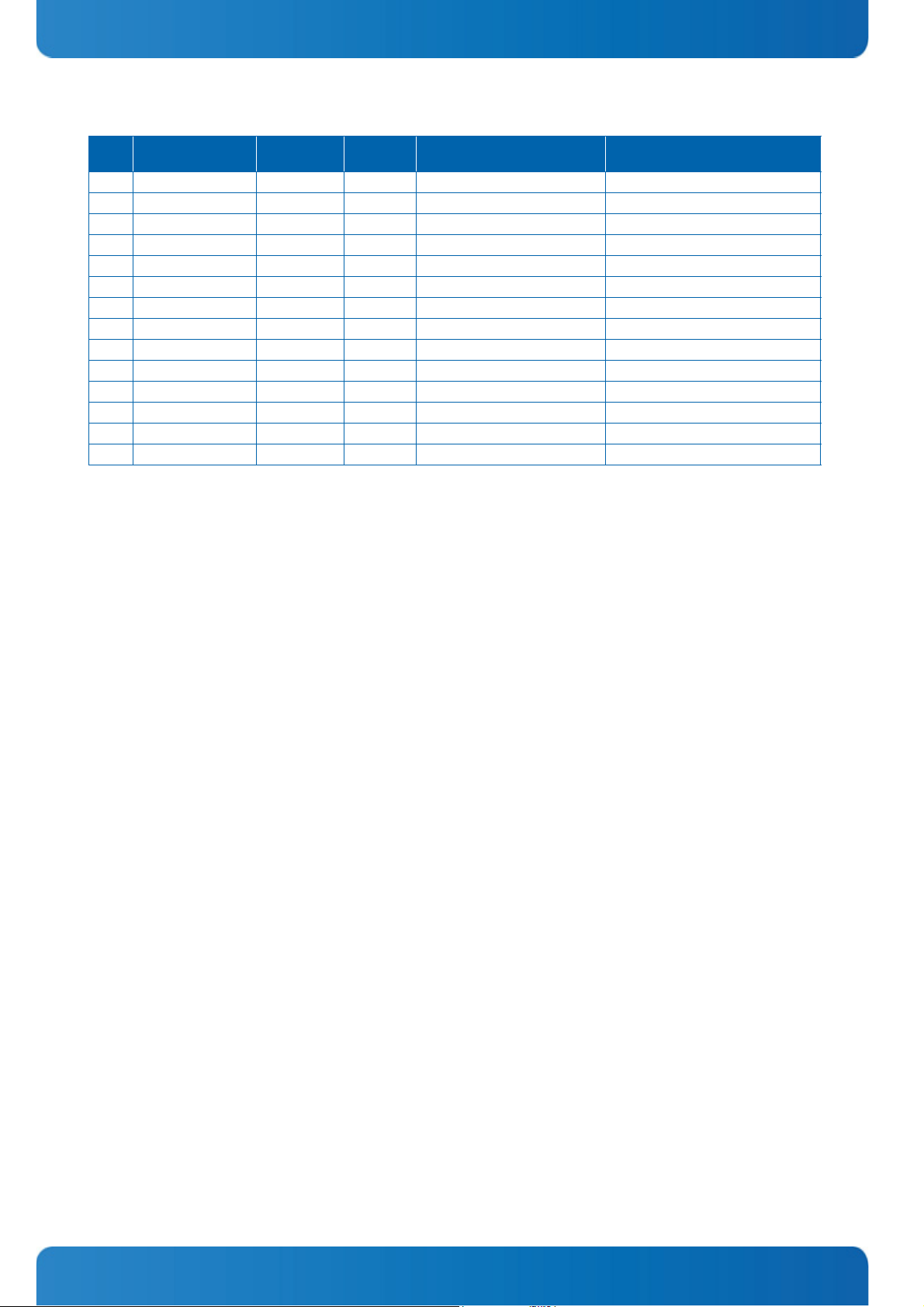

Table 2-3: Connector J2 Row C Pinout (Continued)

PIN SIGNAL

C49 IRQ1# IRQ Undefined

C50 IRQ2# IRQ Undefined

C51 GND PWR GND

C52 SERDES_RX8+ SERDES N/C

C53 SERDES_RX8- SERDES N/C

C54 TYPE0# TYPE Single 4K7 pull down, DNI

C55 SERDES_RX9+ SERDES N/C

C56 SERDES_RX9- SERDES N/C

C57 TYPE1# TYPE Single 4K7 pull down, DNI

C58 SERDES_RX10+ SERDES DP-I MUX_PCIE_RX2_P

C59 SERDES_RX10- SERDES DP-I MUX_PCIE_RX2_N

C60 GND PWR GND

C61 SERDES_RX11+ SERDES DP-I MUX_PCIE_RX3_P

C62 SERDES_RX11- SERDES DP-I MUX_PCIE_RX3_N

C63 RSVD19 Local Bus O-3.3 LA25

C64 RSVD19 Local Bus O-3.3 LA24

C65 SERDES_RX12+ SERDES N/C

C66 SERDES_RX12- SERDES N/C

C67 RSVD19 Local Bus O-3.3 LA23

C68 SERDES_RX13+ SERDES N/C

C69 SERDES_RX13- SERDES N/C

C70 GND PWR GND

C71 SERDES_RX14+ SERDES N/C

C72 SERDES_RX14- SERDES N/C

C73 GND PWR GND

C74 SERDES_RX15+ SERDES N/C

C75 SERDES_RX15- SERDES N/C

C76 GND PWR GND

C77 RSVD19 Local Bus O-3.3 LA22

C78 SERDES_RX16+ SERDES N/C

C79 SERDES_RX16- SERDES N/C

C80 GND PWR GND

C81 SERDES_RX17+ SERDES N/C

C82 SERDES_RX17- SERDES N/C

C83 RSVD19 Local Bus O-3.3 LA21

C84 GND PWR GND

C85 SERDES_RX18+ SERDES N/C

C86 SERDES_RX18- SERDES N/C

C87 GND PWR GND

C88 SERDES_RX19+ SERDES N/C

C89 SERDES_RX19- SERDES N/C

C90 GND PWR GND

C91 SERDES_RX20+ SERDES N/C

C92 SERDES_RX20- SERDES N/C

C93 GND PWR GND

C94 SERDES_RX21+ SERDES N/C

C95 SERDES_RX21- SERDES N/C

C96 GND PWR GND

SIGNAL

GROUP

TYPE TERMINATION COMMENT

28

www.kontron.com

Page 29

Table 2-3: Connector J2 Row C Pinout (Continued)

PIN SIGNAL

C97 RSVD19 Local Bus O-3.3 LA20

C98 SERDES_RX22+ SERDES N/C

C99 SERDES_RX22- SERDES N/C

C100 GND PWR GND

C101 SERDES_RX23+ SERDES N/C

C102 SERDES_RX23- SERDES N/C

C103 GND PWR GND

C104 VCC_12V PWR VCC_12V

C105 VCC_12V PWR VCC_12V

C106 VCC_12V PWR VCC_12V

C107 VCC_12V PWR VCC_12V

C108 VCC_12V PWR VCC_12V

C109 VCC_12V PWR VCC_12V

C110 GND PWR GND

SIGNAL

GROUP

TYPE TERMINATION COMMENT

COMe-P2020 User Guide

29

www.kontron.com

Page 30

COMe-P2020 User Guide

Table 2-4: Connector J2 Row D Pinout

PIN SIGNAL

D1 GND PWR GND

D2 GND PWR eTSEC3_GBE2_ACT#

D3 USB_SSTX0- USB3.0 eTSEC3_GBE2_MDI3-

D4 USB_SSTX0+ USB3.0 eTSEC3_GBE2_MDI3+

D5 GND PWR eTSEC3_GBE2_LINK100#

D6 USB_SSTX1- USB3.0 eTSEC3_GBE2_MDI2-

D7 USB_SSTX1+ USB3.0 eTSEC3_GBE2_MDI2+

D8 GND PWR eTSEC3_GBE2_LINK1000#

D9 USB_SSTX2- USB3.0 eTSEC3_GBE2_MDI1-

D10 USB_SSTX2+ USB3.0 eTSEC3_GBE2_MDI1+

D11 GND PWR GND

D12 USB_SSTX3- USB3.0 eTSEC3_GBE2_MDI0-

D13 USB_SSTX3+ USB3.0 eTSEC3_GBE2_MDI0+

D14 GND PWR eTSEC3_GBE2_LINK#

D15 DDI1_CTRLCLK_AUX+ DDI N/C

D16 DDI1_CTRLDATA_AUX- DDI N/C

D17 LCS0# Local Bus O-3.3 LCS0#

D18 LCS1# Local Bus O-3.3 LCS1#

D19 SERDES_TX6+ SERDES N/C

D20 SERDES_TX6- SERDES N/C

D21 GND PWR GND

D22 SERDES_TX7+ SERDES N/C

D23 SERDES_TX7- SERDES N/C

D24 LA17 Local Bus O-3.3 LA31

D25 LA16 Local Bus O-3.3 LA30

D26 DDI1_PAIR0+ DDI N/C

D27 DDI1_PAIR0- DDI N/C

D28 GND PWR GND

D29 DDI1_PAIR1+ DDI N/C

D30 DDI1_PAIR1- DDI N/C

D31 GND PWR GND

D32 DDI1_PAIR2+ DDI N/C

D33 DDI1_PAIR2- DDI N/C

D34 DDI1_DDC_AUX_SEL DDI N/C

D35 LALE Local Bus O-3.3 LALE

D36 DDI1_PAIR3+ DDI N/C

D37 DDI1_PAIR3- DDI N/C

D38 GND PWR GND

D39 SER1_CTS# UART I-3.3 U0_CTS

D40 SER1_RTS# UART O-3.3 U0_RTS

D41 GND PWR GND

D42 SER2_CTS# UART I-3.3 U1_CTS

D43 SER2_RTS# UART O-3.3 U1_RTS

D44 LBCTL Local Bus O-3.3 LBCTL

D45 LGTA# Local Bus O-3.3 LGTA#

D46 IRQ3# IRQ I-3.3 Undefined

D47 IRQ4# IRQ I-3.3 Undefined

D48 LA15 Local Bus O-3.3 LA29

SIGNAL

GROUP

TYPE TERMINATION COMMENT

30

www.kontron.com

Page 31

COMe-P2020 User Guide

Table 2-4: Connector J2 Row D Pinout (Continued)

PIN SIGNAL

D49 LA14 Local Bus O-3.3 LA28

D50 IRQ_OUT# IRQ O-3.3 Undefined

D51 GND PWR GND

D52 SERDES_TX8+ SERDES N/C

D53 SERDES_TX8- SERDES N/C

D54 PEG_LANE_RV# PCIE/SERDES I-3.3 Undefined

D55 SERDES_TX9+ SERDES N/C

D56 SERDES_TX9- SERDES N/C

D57 T YPE2# TYPE 0 Single 4K7 pull down, DNI

D58 SERDES_TX10+ SERDES DP-O MUX_PCIE_TX2_P

D59 SERDES_TX10- SERDES DP-O MUX_PCIE_TX2_N

D60 GND PWR GND

D61 SERDES_TX11+ SERDES DP-O MUX_PCIE_TX3_P

D62 SERDES_TX11- SERDES DP-O MUX_PCIE_TX3_N

D63 RSVD19 Local Bus O-3.3 LA27

D64 RSVD19 Local Bus O-3.3 LA26

D65 SERDES_TX12+ SERDES N/C

D66 SERDES_TX12- SERDES N/C

D67 GND PWR GND

D68 SERDES_TX13+ SERDES N/C

D69 SERDES_TX13- SERDES N/C

D70 GND PWR GND

D71 SERDES_TX14+ SERDES N/C

D72 SERDES_TX14- SERDES N/C

D73 GND PWR GND

D74 SERDES_TX15+ SERDES N/C

D75 SERDES_TX15- SERDES N/C

D76 GND PWR GND

D77 IRQ5# IRQ I-3.3 Undefined

D78 SERDES_TX16+ SERDES N/C

D79 SERDES_TX16- SERDES N/C

D80 GND PWR GND

D81 SERDES_TX17+ SERDES N/C

D82 SERDES_TX17- SERDES N/C

D83 TYPE3# TYPE 0 Single 4K7 pull down, DNI

D84 GND PWR GND

D85 SERDES_TX18+ SERDES N/C

D86 SERDES_TX18- SERDES N/C

D87 GND PWR GND

D88 SERDES_TX19+ SERDES N/C

D89 SERDES_TX19- SERDES N/C

D90 GND PWR GND

D91 SERDES_TX20+ SERDES N/C

D92 SERDES_TX20- SERDES N/C

D93 GND PWR GND

D94 SERDES_TX21+ SERDES N/C

D95 SERDES_TX21- SERDES N/C

D96 GND PWR GND

SIGNAL

GROUP

TYPE TERMINATION COMMENT

31

www.kontron.com

Page 32

Table 2-4: Connector J2 Row D Pinout (Continued)

PIN SIGNAL

D97 RSVD19 Local Bus O-3.3 LA19

D98 SERDES_TX22+ SERDES N/C

D99 SERDES_TX22- SERDES N/C

D100 GND PWR GND

D101 SERDES_TX23+ SERDES N/C

D102 SERDES_TX23- SERDES N/C

D103 GND PWR GND

D104 VCC_12V PWR VCC_12V

D105 VCC_12V PWR VCC_12V

D106 VCC_12V PWR VCC_12V

D107 VCC_12V PWR VCC_12V

D108 VCC_12V PWR VCC_12V

D109 VCC_12V PWR VCC_12V

D110 GND PWR GND

SIGNAL

GROUP

TYPE TERMINATION COMMENT

COMe-P2020 User Guide

Table 2-5: General Signal Description

TYPE DESCRIPTION

I/O-3.3 Bi-directional 3.3V IO-Signal

I-3.3 3.3V Input

O-3.3 3.3V Output

OD-3.3 Open-Drain Output

DP-I/O Differential Pair Input/Output

DP-I Differential Pair Input

DP-O Differential Pair Output

PDS Pulldown Strap

Straping Input during Power-Up (do

STRAP

PWR Power Connection

not connect any external Pullup or

Pulldown resistor)

32

www.kontron.com

Page 33

COMe-P2020 User Guide

2.5.2 Signal Descriptions COM Express Connectors

2.5.2.1 Ethernet (Group GigE MDI)

The COMe-cP2020 module provides three Gigabit Ethernet interface whose signals are already at copper Ethernet transmission voltage levels (physical levels / MDI) in accordance to the COM Express Base Specification. So the carrier board needs

to add only the galvanic isolation (magnetics) function and the appropriate transmission connector type.

Additionally, for monitoring and control purposes, LED functionality is provided to indicate activity (GBE[0..2]), Ethernet

link (GBE[0..2]_LINK#), Ethernet speed 100Mbit/s (GBE[0..2]_LINK100#) and Ethernet speed 1000Mbit/s

(GBE[0..2]_LINK1000#).

Reference voltage for carrier board Ethernet magnetics center tap is not required.

2.5.2.2 Ethernet Management (ETH MGT)

The management communication between the Ethernet MACs and the external connected Ethernet PHYs is realized by using

the signal group ETH MGT (EC_MDC, EC_MDIO).

2.5.2.3 IEEE 1588

The Freescale QorIQ CPUs provide support for the Ethernet Precision Time Protocol (PTP) defined in the IEEE 1588 specification. In order to utilize this functionality the CPUs provide additional IEEE 1588 time stamp signals. For a more detailed

description of those signals please refer to the CPU’s reference manual.

2.5.2.4 SerDes

The signal group SerDes reflects all the high speed low voltage differential signals provided by the CPU. The SerDes signals

are grouped into so called lanes and links.

A set of differential signal pairs, one pair for transmission and one pair for reception is called a lane. One or more lanes

together form a link which can support various logical protocols such as: PCIe, sRIO, SGMII.

The P2020 Processor provides 4 SerDes lanes (lane #0 to lane #3). SerDes lanes #1 to #3 are configurable. Each lane can be

switched via on-board multiplexer to different COMe connector SerDes Ports. The multiplexer are controlled by CPLD, see

chapter xxx User SerDes Multiplexer Control Register. The P2020 SerDes lane routing is shown in the following table.

Table 2-6: P2020 SerDes Lane Routing

P2020 SerDes COMe Connector Port

CPLD

Control Line

Lane #1 SERDES_TX/RX[1]+/- SERDES_TX/RX[4]+/-

Lane #2 SERDES_TX/RX[2]+/- SERDES_TX/RX[10]+/-

Lane #3 SERDES_TX/RX[3]+/- SERDES_TX/RX[11]+/-

The logical protocols which run on the SerDes lanes are specified by strapping options P2020 CPU read at system powerup.

To obtain a complete overview about all theoretical protocol combinations, please refer to the Freescale "P5020 QorIQ

Integrated Multicore Communication Processor Family Reference Manual", Chapter 3.5.11 "SerDes Lane Assignments and

Multiplexing".

To handle the SerDes configuration in a more comfortable way, Kontron provides the configuration tool “sconf”. “sconf”

provides a very easy way to configure the functionality of the SerDes lanes. Refer to Chapter 6, "U-Boot" for further information.

CPLD

Control Line#

33

www.kontron.com

Page 34

The following SerDes protocol combinations can be selected by using the “sconf” command:

Table 2-7: SerDes Protocol Mapping

COMe-CONNECTOR

COMe-P2020 User Guide

BASE

CON-

FIG.

SERDES_

TX/RX[0]+/-

SERDES_

TX/RX[1]+/-

SERDES_

TX/RX[2]+/-

SERDES_

TX/RX[3]+/-

SERDES_

TX/RX[4]+/-

SERDES_

TX/RX[10]+/-

SERDES_

TX/RX[11]+/-

1 off off off off off off off

2 PCIex1 off off off PCIex1 PCIex2

3PCIex2 offoffoff PCIex2

4 PCIex1 off off off PCIex1 SGMII SGMII

5PCIex2 offoffoffSGMIISGMII

6 PCIex1 off off off SRIOx1 SGMII SGMII

7 SRIOx1 off off off SRIOx1 SGMII SGMII

8 SRIOx4 off off off

2.5.2.5 Local Bus / GPIO

2.5.2.5.1 Local Bus

The COMe-cP2020 provides a local bus interface for connecting directly memory mapped parallel bus devices (SRAM-style).

The Local Bus implementation on the COMe-cP2020 supports 8-bit and 16-bit data signal paths depending on the Local Bus

chip select configuration and an 8Mbyte address range for each of the two Local Bus chip selects.

The Local Bus signals designated as LAD0..15 incorporate multipexed address and data information, whereby the Local Bus

signals LA16..31 are dedicated address lines. Please be aware that external address latches must be provided on the

LAD8..15 lines if an address range greater than 64kB is to be addressed.

The numbering scheme for the Local Bus LA/LAD pins is noted in Power Architecture style, meaning that LAD0 is the most

significant bit and LA31 is the least significant bit.

For a better understanding of the QorIQ P2020 Local Bus functionality and all the involved control signals please refer to

the CPU’s reference manual.

2.5.2.5.2 GPIO

The COMe-cP2020 provides the possibility to convert part of the Interrupt signals to GPIO functionality. There are 5 signals

on the COM Express connector which can be multiplexed between Interrupt functionality and GPIO functionality.

2.5.2.6 USB

The COMe-cP2020 supports four USB 2.0 high speed USB ports.

The USB ports USB0..3 at the COM Express connectors are provided using a 4-port USB hub with its Uplink-Port connected

via an external USB-PHY to the USB controller ULPIO-Interface on the QorIQ P2020.

2.5.2.7 SDHC (SDIO)

The Freescale QorIQ CPUs incorporate an enhanced Secure Digital Host Controller (eSDHC) which provides support for MultiMediaCards (MMC) and Secure Digital (SD) Cards.

The interfacing signals of the CPU are multiplexed between the on-board SD card socket and the dedicated SDIO signals on

the COM Express connectors. The selection between on-board socket and external interfacing is done via the DIP Switch

SW1, switch 1.

34

www.kontron.com

Page 35

COMe-P2020 User Guide

2.5.2.8 SPI

The Serial Peripheral Interface Bus or SPI bus is a synchronous serial data link standard developed by Motorola that operates in full duplex mode. Devices communicate in master/slave mode where the master device initiates the data frame. Multiple slave devices are allowed with individual slave select (chip select) lines. Sometimes SPI is called a "four wire" serial

bus, contrasting with three, two, and one wire serial buses.

For a detailed signal description, please refer to the COM Express base specification, chapter 4.3.12.

The COMe-cP2020 supports boot from an external SPI flash. Therefore it can be configured by pin B88 (BIOS_DIS1#) for the

following configurations:

Table 2-8: SPI Signal Configurations

BIOS_DIS1# FUNCTION SIGNAL ROUTING

Open

Boot from on-module

flashes

Pulled to GND Boot from external flash

P2020 eSPI chip select SPI_CS2# is available

on the carrier

P2020 eSPI chip select SPI_CS0# (boot chip

select) is available on the carrier

The BIOS_DIS0# signal defined in the COM-Express Base specification is not used on the COMe-cP2020.

2.5.2.9 Serial Interface

The COMe-cP2020 provides two UART interfaces which makes the following configuration possible:

• 2x 4-wire UARTs (manufacturer preset)

2.5.2.10 SMB / I2C

The COMe-cP2020 supports two I2C controllers with speeds up to 400 kHz for customer usage. The signals on the COM

Express connector labeled SMB_CK and SMB_DAT are connected to I2C controller IIC1 of the P2020. The resources occupied

for the on-board devices are as follows:

Table 2-9: On-Board Device Resource

DEVICE

I2C ADDRESS

(binary)

I2C ADDRESS

(hex)

User EEPROM 1010 110x 0xAC

System EEPROM 1010 111x 0xAE

RTC 1010 001x 0xA2

Thermal Sensor 1001 000x 0x90

SPD EEPROM 1010 000x 0xA0

The signals on the COM Express connector labeled I2C_CK and I2C_DAT are connected to I2C controller IIC2 of the P2020.

This controller is completely dedicated to user purposes.

35

www.kontron.com

Page 36

COMe-P2020 User Guide

Watchdog

Timer

IRQ1..5#

CPU_IRQ7..11#

Carrier

Interrupt

Mode

0x374

0x375

Interrupt

Enable

Board

Interrupt

Pending

0x376

0x377

0x378

0x379

0x37A

0x37B

0x37C

0x37D

Interrupt

Multiplexer

0x380

0x381

1

5

1

PWROK

BATLOW#

WAKE0#

WAKE1#

CARRIER COMe_cP2020

THERM#

SMB_ALERT#

0x28C

DIR

0x370

DIR

0x370

LM73_TEMP_ALERT#

RTC_INT#

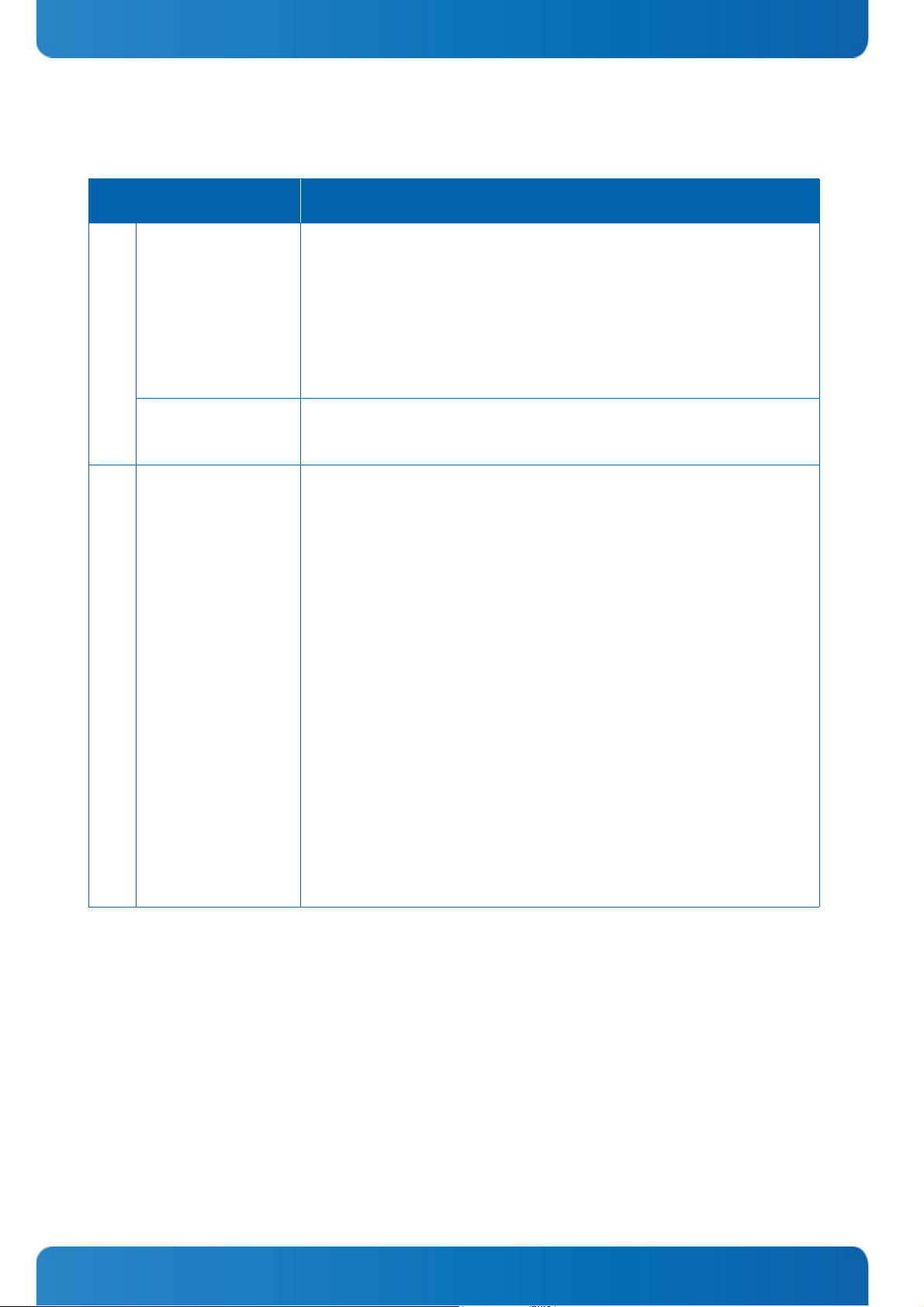

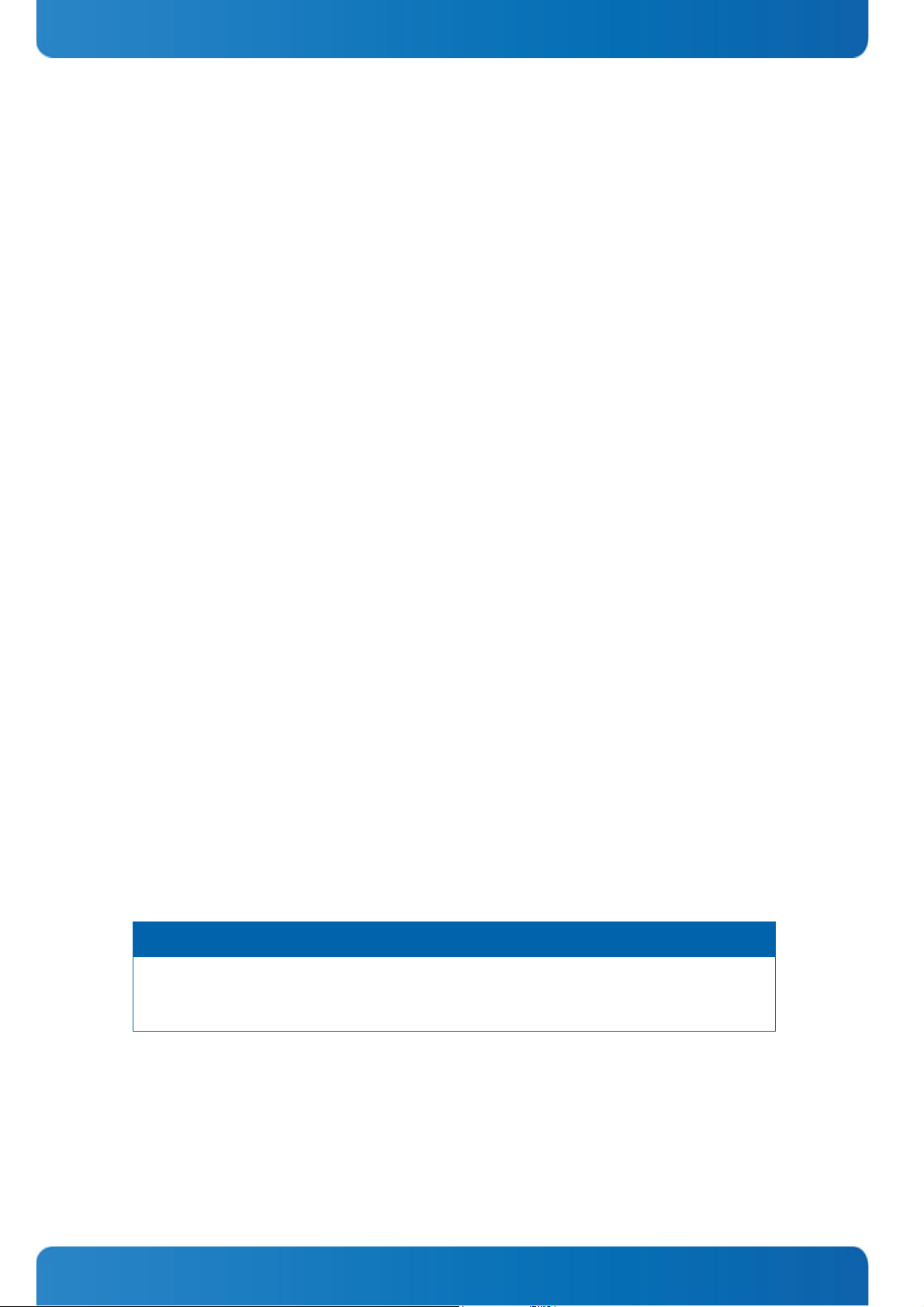

2.5.2.11 IRQs

The COMe-cP2020 provides five IRQ inputs which can be configured for edge/level, high and low active usage. The operational mode of the IRQs is programmed via the Carrier Interrupt Mode1 and Carrier Interrupt Mode2 registers. Refer to

Chapter 3 for further information.

The following figure demonstrates the IRQ routing of the COMe-cP2020.

Figure 2-1: IRQ Routing Scheme

2.5.2.12 Miscellaneous (MISC)

These signals are normally pre-defined for an X86 architecture board and have no defined functionality on Power Architecture CPUs. On the COMe-cP2020 these signals may be used as gerneral purpose output.

2.5.3 JTAG/Debug Interface

The COMe-cP2020 provides one JTAG/Debug connector, J4, to facilitate software debugging using an emulation probe. The

connector type is: 1x20_SAMTECH_ZF.

36

www.kontron.com

Page 37

The following table provides pinout information for the debug connector J4.

Table 2-10: JTAG/Debug Connector J4 Pinout

PIN SIGNAL FUNCTION I/O

1 TD0 JTAG data output 0

2NC Not connected -

3 TDI JTAG data input I

4COP_TRST JTAG test reset I

5NC Not connected --

6 COP_SENSE Analog, connected to 3V3 -

7TCK JTAG test clock I

8 COP_CKSTOP_IN# COP checkstop input I

9 TMS JTAG test mode select I

COMe-P2020 User Guide

10 NC Not connected -

11 COP_SOFT_RST COP soft reset I

12 GND Ground signal --

13 COP_HARD_RST# COP hard reset I

14 NC Not connected --

15 COP_CKSTOP_OUT# COP checkstop output 0

16 GND GND signal -

17 NC Not connected -

18 NC Not connected -

19 NC Not connected -

20 NC Not connected -

37

www.kontron.com

Page 38

COMe-P2020 User Guide

3 Configuration

3.1 DIP Switch Configuration

The COMe-cP2020 is equipped with one 4-bit DIP switch, SW1, used for board configuration.

Table 3-1: DIP Switch SW1 Configuration

SWITCH SETTING DESCRIPTION

1 OFF Boot from the standard SPI boot flash

ON Boot from the recovery SPI boot flash

2 OFF The SDHC interface is routed to the onboard MicroSD

ON The SDHC interface is routed to the COM Express connectorResaerved

3OFFReserved

ON