Page 1

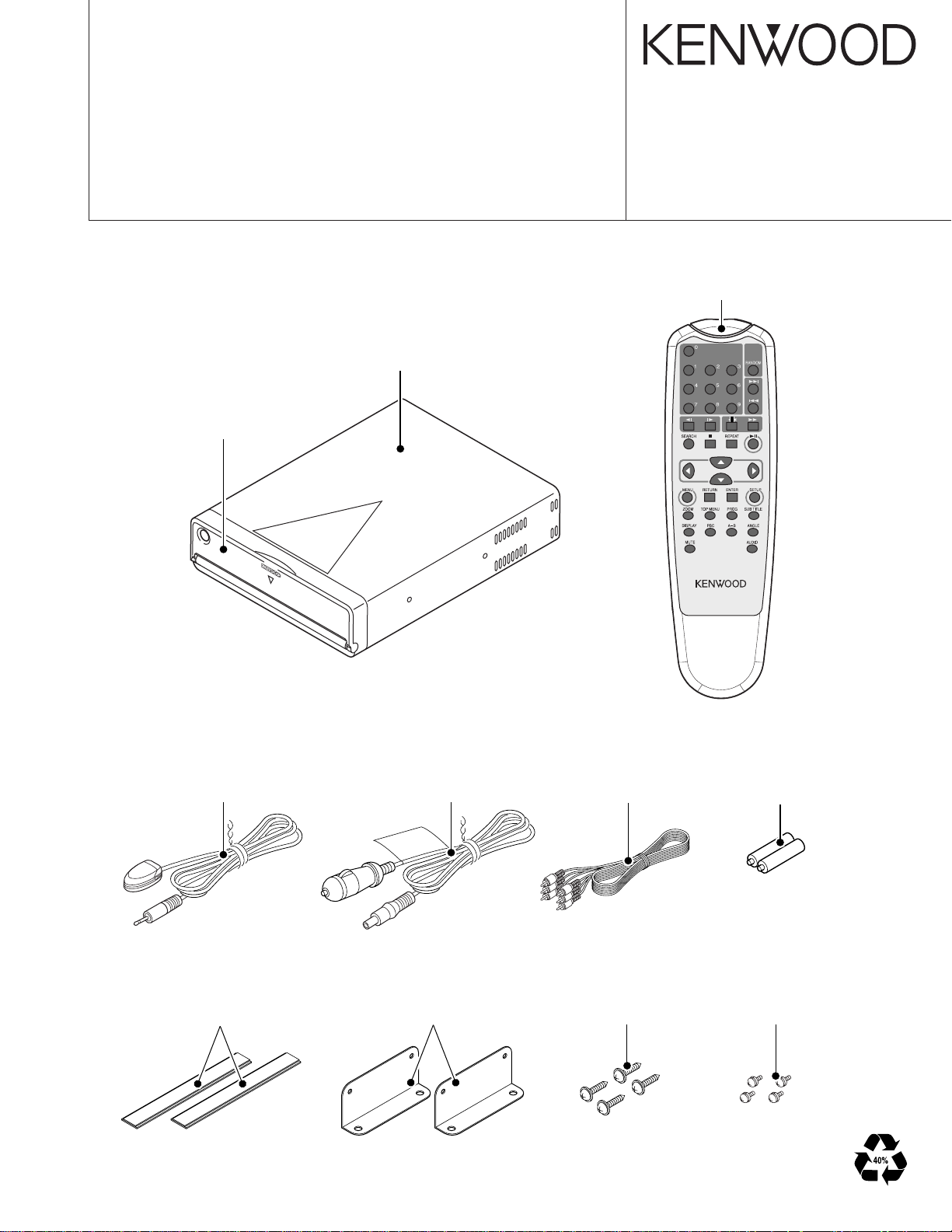

DVD PLAYER

KDV-S210P/S220P

/S230P/S240P

SERVICE MANUAL

Metallic cabinet

Panel assy

(A64-3526-08): KDV-S210P

(A64-3528-08): KDV-S220P

(A64-3529-08): KDV-S230P

(A64-3530-08): KDV-S240P

(A01-2845-08)

© 2004-5 PRINTED IN JAPAN

B53-0171-00 (N) 2703

Remote controller assy

(A70-2066-08)

Remote control sensor assy (6m)

(T95-0264-08)

Magic tape

(H30-0514-05)

x2

Cord with DC plug (2.4m)

(E03-0405-08)

Mounting hardware

(J22-0237-08)

x2

Cord with pinplug (3m)

(E30-6389-08)

Except KDV-S210P

Tapping screw

(N09-6274-08)

x4

RC-DV500

Size AAA battery

(Not supplied)

SEMS

(N09-6273-08)

x4

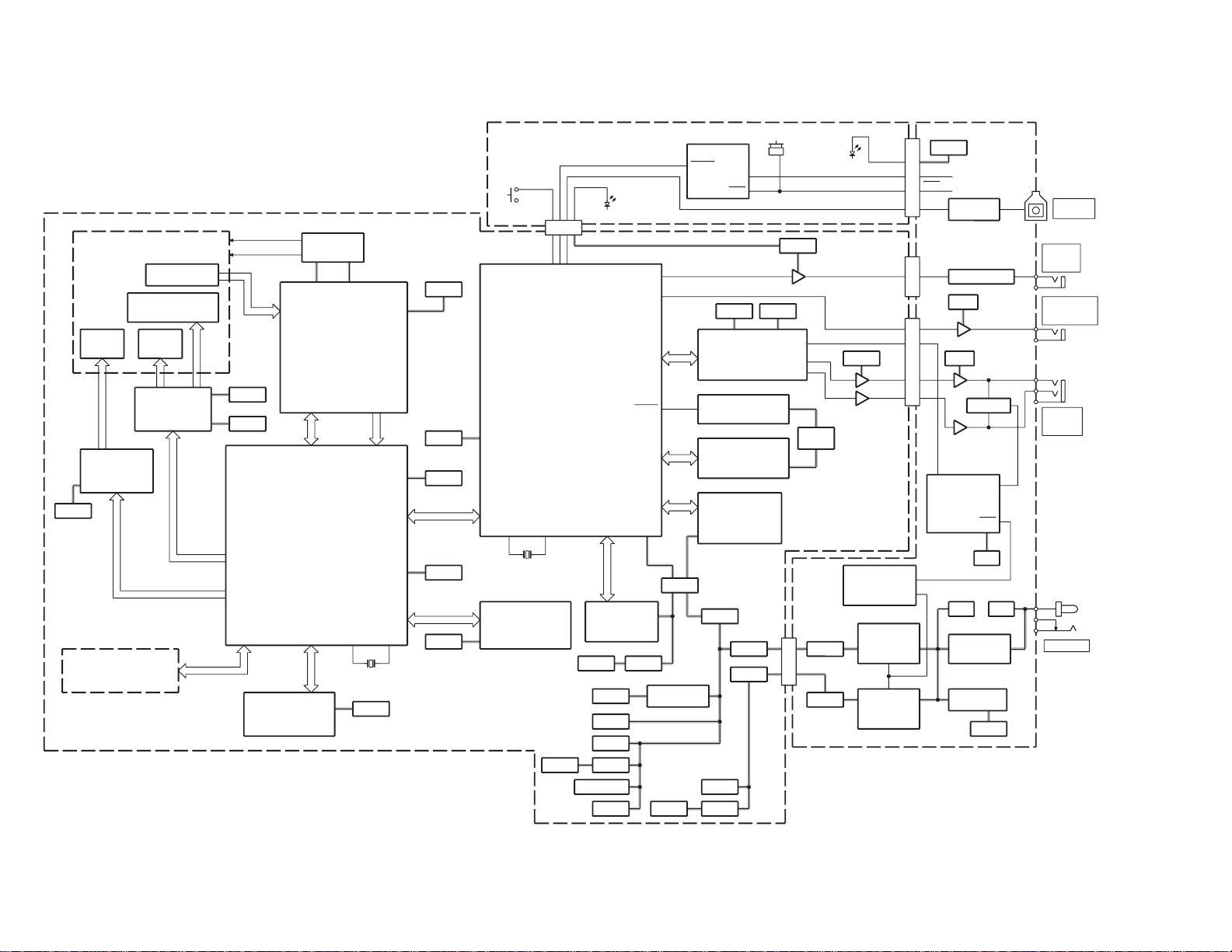

Page 2

2

PROCESSOR

-DIGITAL SERVO CONTROL

DVD/CD DATA DECODING

SU6

SU1

SU3

MOTOR DRIVER

PWM

SU2

BTL

MOTOR DRIVER

HEAD AMPLIFIER

-GENERATING SERVO

-AUTO GAIN CONTROLLING

S+7V

MMVC

MVCC

DECODING & CORRECTING

-F/E CONTROL uP

-DATA BUFFERING

SVCC

-F/E PROGRAMING

FLASH MEMORY

3.3V

RFVCC

3.3V

VCC27

RFVCC

-DATA BUFFERING

DVD MPEG DECODING PROCESSOR

-MPEG DECODING

-B/E & SYSTEM CONTROL uP

U1

SU7

-B/E FRAME

SDRAM

-DVD/CD DATA

U34

CIRCUIT

LASER DRIVE

SQ4,5

U3

-F/E FRAME BUFFER

SDRAM 1Mx16BITS

-WORKING MEMORY

ACTUATOR &

BRUSHLESS

SY1

-F/E SYSTEM CLOCK

33.8688MHz

CERAMIC RESONATOR

CODE STORED

128kx8

-B/E SYSTEM CLOCK

CRYSTAL RESONATOR

27MHz

Y1

VCC27

-INCLUDING OVER

2ch AUDIO DAC

U35

DIGITAL FILTER

SAMPLING

U9

-RESETING

RESET IC

for U1

STORED

-SETUP & RESUME

EEPROM

INFORMATION

U2

U28

CODE STORED

-B/E PROGRAMING

FLASH ROM

VCC33

Q1

MMVC

MVCC

SVCC

3.3V

RFVCC

VCC33 AVCC

AVCC

RESET VCC

VCCA

S+7V

U5

REGULATOR

3.3V FIXED

SQ3

+7V

S7V

VCC

VCC

+7V

U23-1

U23-2

BUFFER

U27

POST LPF

-2nd ORDER

ACTIVE LPFx2

3.3V

CB5 CBP5

CBP7CB7

CB502 CBP502

CB3

CBD3

1MBITx8

BUFFER

4Mx16BITS

SERVO SIGNAL

RF AMPLITUDE

ERROR SIGNALS

INSERTION

DISC

SLIT

INDICATOR

EJECT SW

UD3

NAND GATES

POWER SW

INDICATOR

POWER

CBD1 CBP1

VCC

S7V

UP1

REGULATOR

SWITCHING

REGULATOR

SWITCHING

UP2

+B1

REGULATOR

5V

QP30

REGULATOR

QP40

28V

CIRCUIT

BU VCC

-GENERATING

TIMING

ON/OFF SW

DELAY CIRCUIT

VCC

RESET

REDUCING +B1

CIRCUIT

MUTE

-SENDING

DRIVING

-MUTE TR

+B1

ACTIVE LPFx2

LPF

-2nd ORDER

UP3-2

UP3-1

S7V

MUTE TR

QP4,5

UP4

VCC

75 Ohm

VIDEO

DRIVER

TRP1

PULSE TRANS

BU VCC

EYE INPUT

REMOTE

DC INPUT

ANALOG

OUT

AUDIO

VIDEO

OUT

COMPOSITE

DIGITAL

OUT

AUDIO

REMOTE

EYE

SPINDLE

MOTOR

to

SLEDGE

MOTOR

to

PICKUP HEAD

from SENSOR of

ACTUATOR COIL of

PICKUP HEAD

to

to CD LD

to DVD LD

+B

ERROR SIGNAL

INPUT

RF & SERVO

I/O

VPA

VM

PVCC

VCC

INTERFACE

COMMAND

DSP

CDLD DVDLD

DSP COMMAND

INTERFACE SIGNAL INPUT

RF & SERVO

CONTROL

LOADING

MECHANISM

OUTPUT

SERVO DRIVE SIGNAL

INTERFACE

FLUSH MEMORY

INTERFACE

SDRAM

AVDD5

INTERFACE

ATAPI

VDD 3.3

INTERFACE

SDRAM

INTERFACE

ATAPI

FLUSH MEMORY

EEPROM

RESET

DIGITAL AUDIO

VC25

INTERFACE

INTERFACE

INTERFACE

SPDIF OUT

SPDIF

UDAC

VIDEO DAC OUT

VC33

VCC

OUTPUT

SIGNAL

ERROR

RF & SERVO

RESET

HARDWARE

for F/E

INCLUDING

AUX4

AUX2

AUX7

VCC

VDD

VOUTR

VAA

VOUTL

VDD

ZRR

VCC

VCC

VCC

LED

RED

P DWN

P ON

+B DWN

LED

GREEN

IR

VSW

EN

VIN

VSW

EN

VIN

P ON

ZERO MUTE

VCC

V+ V+

CH-R

CH-L

VCC

+B DWN

P ON

IR

ZERO MUTE

SLOT-IN

LOADING MECHANISM

DISPLAY PCB POWER & OUTPUT PCB

COMBO PCB

TRAVERSE MECHANISM

KDV-S210P/S220P

/S230P/S240P

BLOCK DIAGRAM

Page 3

KDV-S210P/S220P

/S230P/S240P

COMPONENTS DESCRIPTION

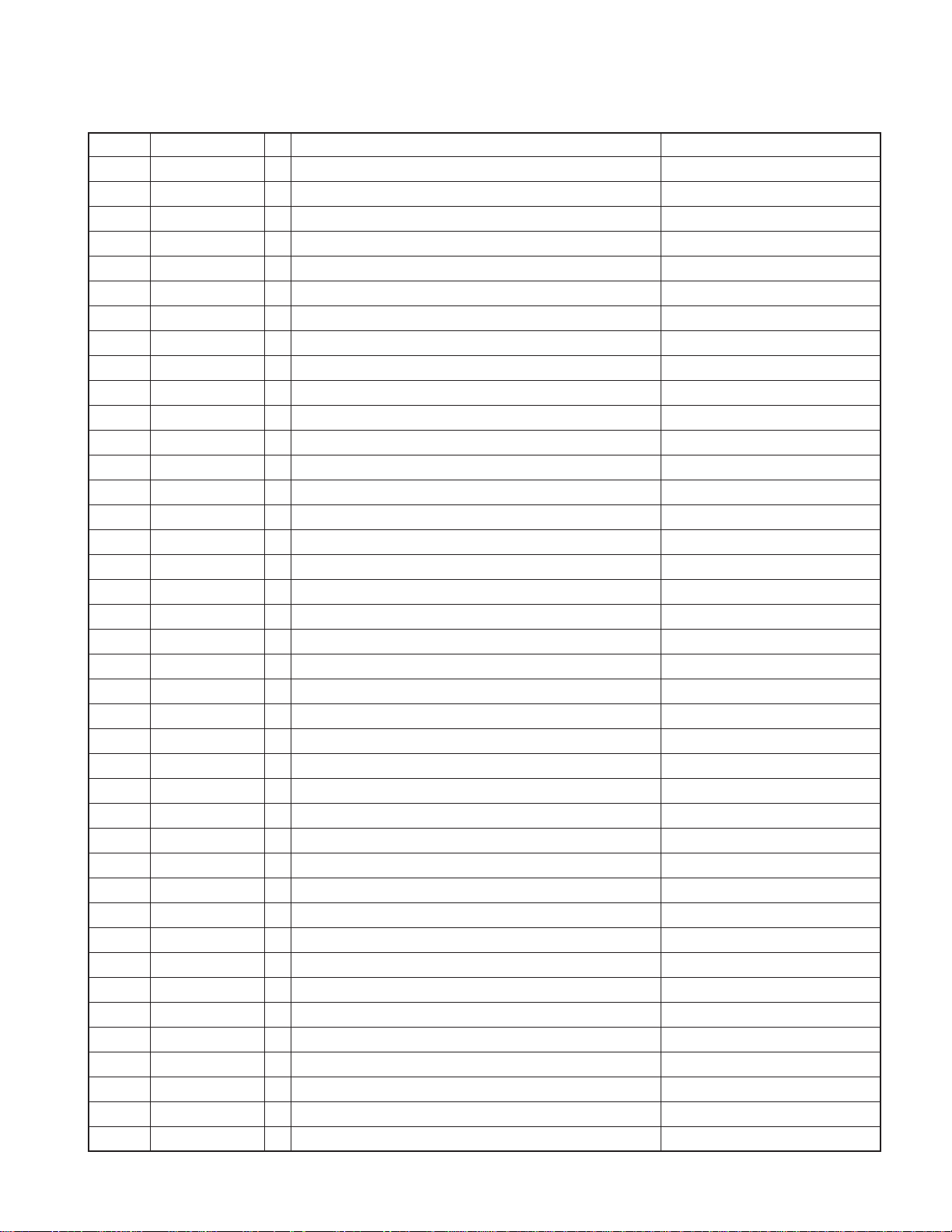

● COMBO PCB

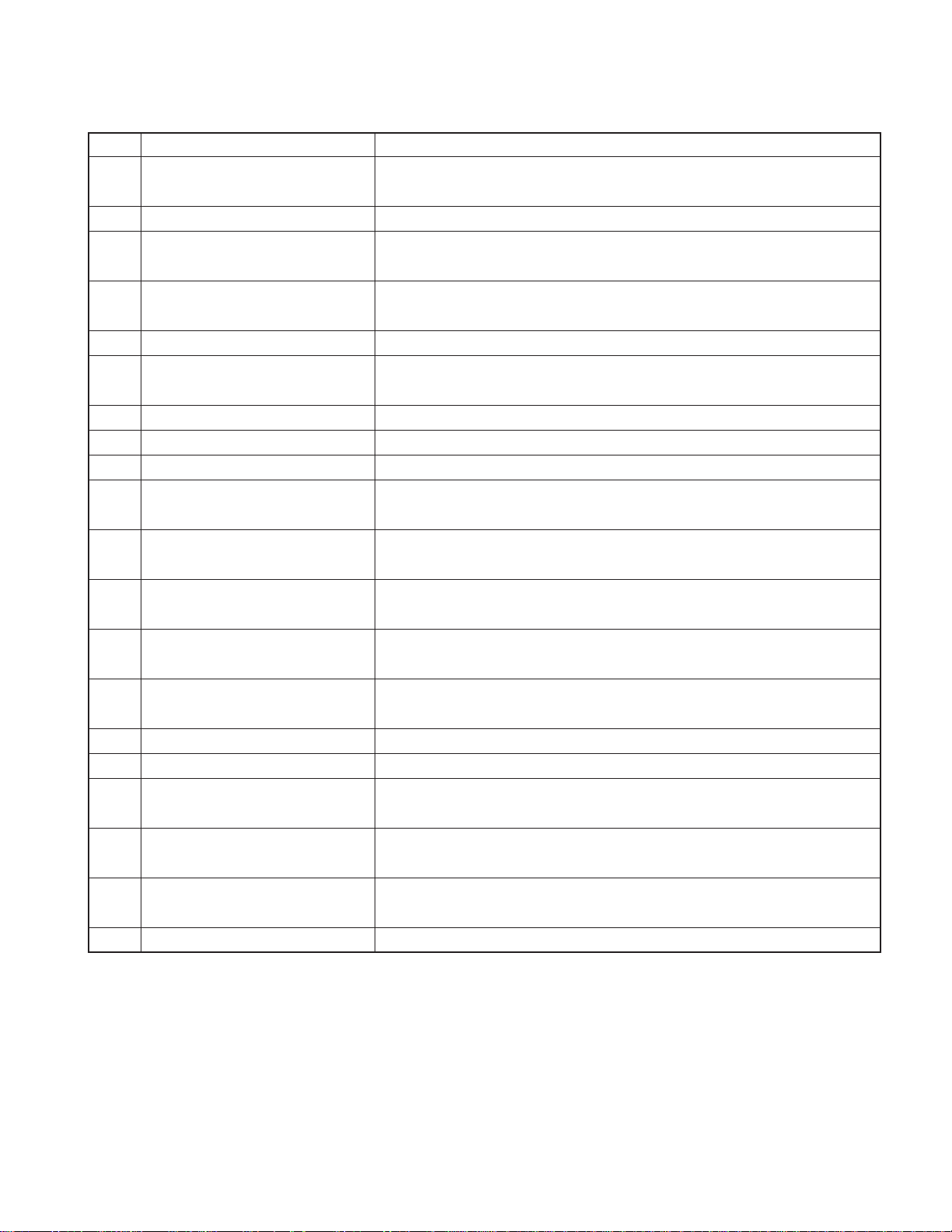

Ref. No. Application / Function Operation / Condition / Compatibility

MPEG decoding control DVD MPEG images are decoded.

Dolby digital decoding control Outputs of Dolby digital audio are decoded.

LPCM audio decoding control LPCM audio of CD and DVD are decoded.

DVD navigation control DVD navigation is controlled.

ATAPI communication control ATAPI communication is control in order to control F/E.

U1

U2

U3

U5 3.3V regulator From No. 3 pin, VCC (5V) is input and from No. 2 pin, VCC33 (3.3V) is output.

U9 System reset control

U23 For audio post LPF CH1-side is Rch and CH2-side Lch. Constitutes a multiple feedback-type active LPF.

U27 SPDIF output, Pulse transformer driver

U28 B/E program memory Flash memory for storing B/E program memory.

U34 Program memory Flash memory for storing programs.

U35 Digital audio 2ch DAC

SU1

SU2 Feed motor driver

Built-in microcomputer for controlling

system and B/E system

Built-in video DAC Video DAC is built-in to output current for composite video output from No. 106 pin.

Digital audio DAC control output

Controls for keys and remote control

EEPROM for storing system setting

information and resume information

Frame buffer memory Decoding data buffer memory.

Program memory Memory for program control.

DVD/CD digital servo control Built-in DVD/CD digital servo equalizer and various timing generation circuit.

DVD/CD data decoding control

F/E section built-in system control

microcomputer

ATAPI communication control ATAPI communication control with B/E.

Pickup actuator driver

Motor driver for slot loading mechanism

System as a whole and B/E are controlled. 32bit RISC microcomputer is built-in.

Audio signals are output from No. 32 (TWS), 33 (TSD0), 39 (MCLK), and 40 (TBCK) pins. Also,

DAC system control is conducted using No. 160 (AUX0), 161 (AUX1), and 168 (AUX6) pins.

No. 162 pin is input for EJECT key. When receiving input, it is in L. No. 166 pin is for

remote control input. When receiving input, there will be pulse input.

EEPROM for storing system setting information and resume information.

Rising/Falling of VCC (5V) is detected by No. 5 pin, and L-reset output is made from No. 4 pin.

Inverters are connected in 3-step parallel connection for increased current capacity and

output to the pulse transformer.

Digital audio signal is input from No. 3 (TWS), 2 (TSD0), 16 (MCLK), and 1 (TBCK) pins.

Also, signals for DAC system control are input from No. 15 (AUX0), 14 (AUX1), and 13 (AUX6) pins.

Output for Lch analog audio is made from No. 7 pin and that for Rch is made from No. 8 pin.

Data generation from RF of DVD/CD, error correction and control over scramble analysis

and release.

F/E section 8bit microcomputer for system control.

Control signals for focus and tracking actuator signals of the pickup are received by No. 1 and

No. 26 pins respectively and currents are output from No. 13 and14 and No. 15 and 16 pins.

Control signals for the feed motor is received at No.6 pin and currents are output from

No. 11 and 12 pins.

Control signals for slot loading mechanism motor is received at No. 23 pin and currents

are output from No. 18 and 17 pins.

3

Page 4

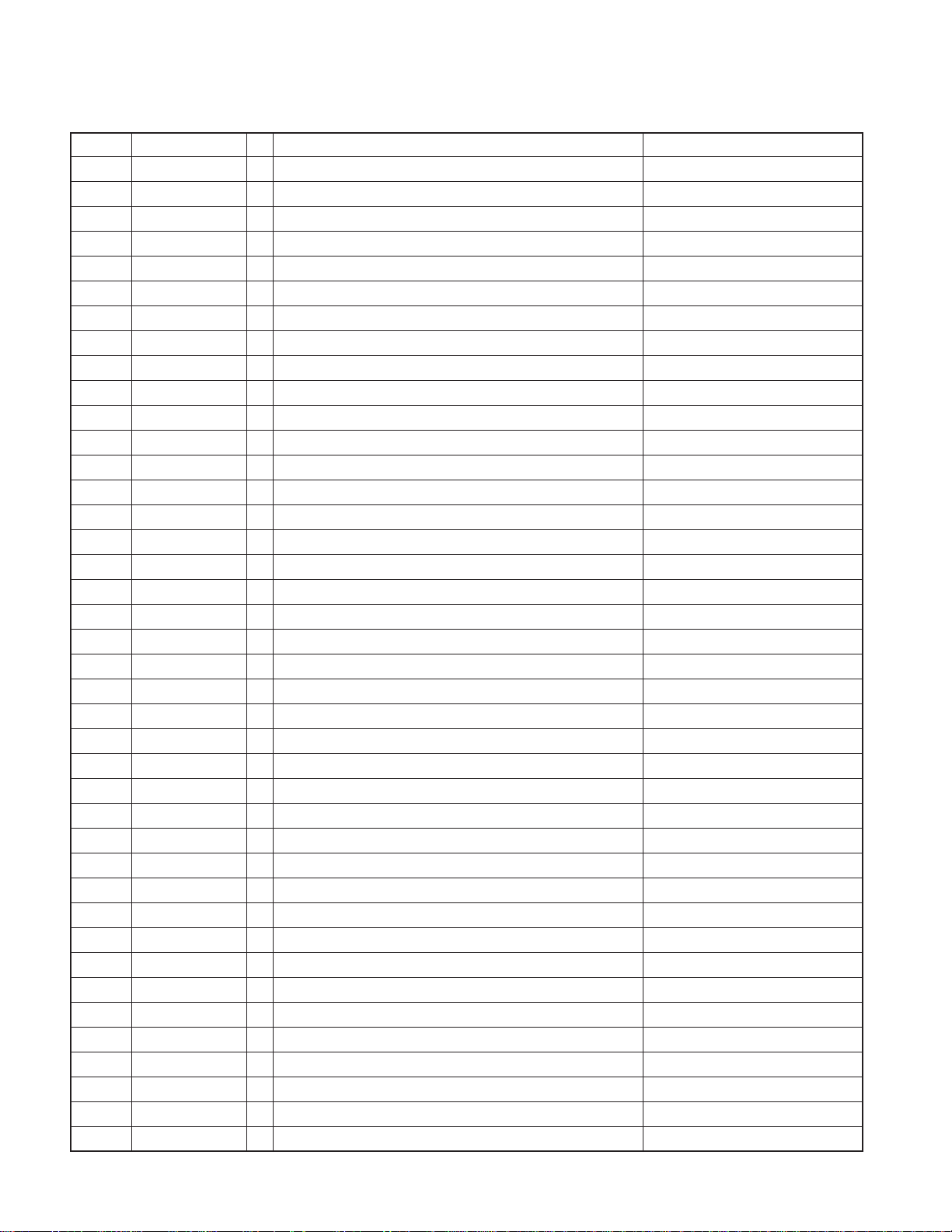

KDV-S210P/S220P

/S230P/S240P

COMPONENTS DESCRIPTION

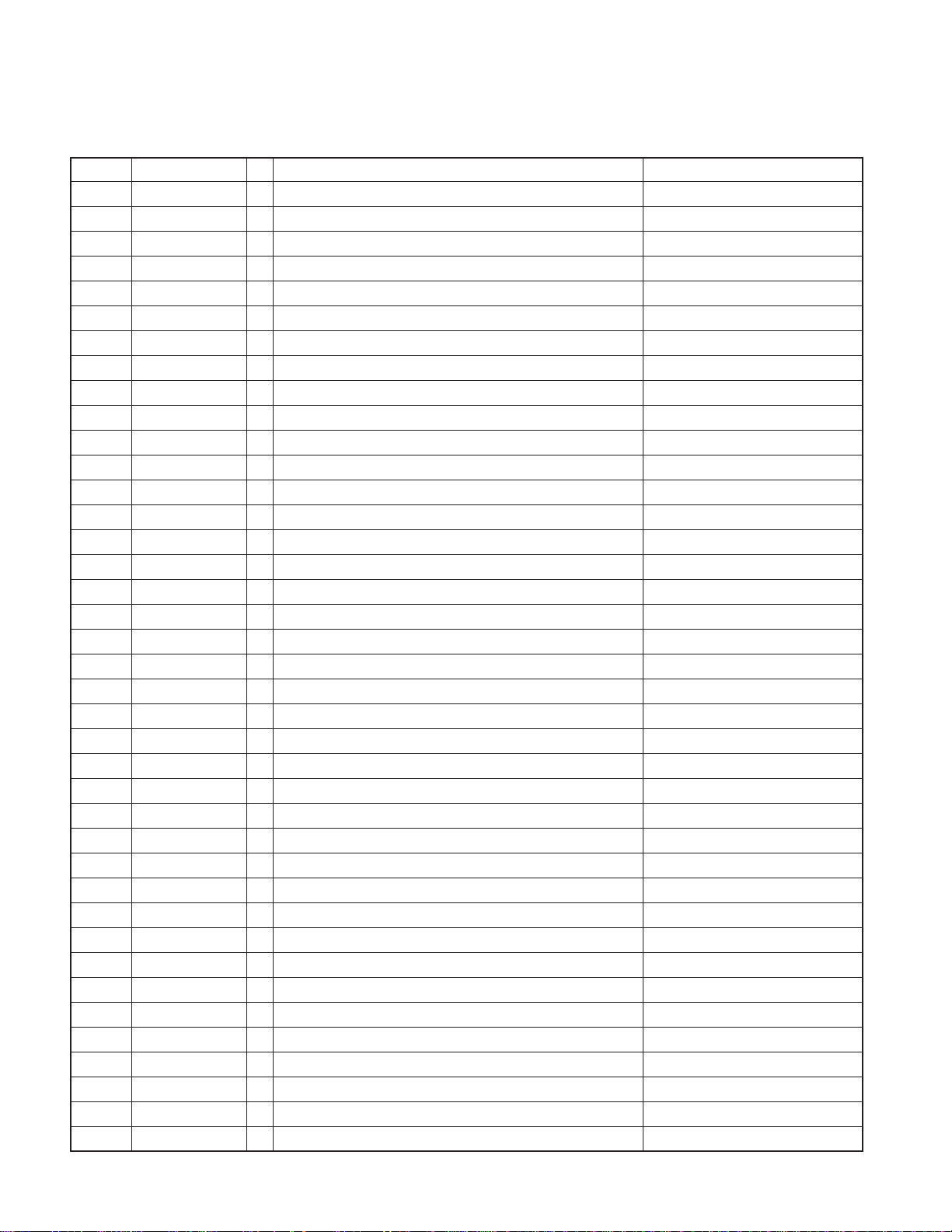

Ref. No. Application / Function Operation / Condition / Compatibility

SU3

SU6 amplifier control

SU7

SU8

SQ3 3.3V regulator VCC (5V) is input from No. 3 pin and 3.3V is output from No. 2 pin.

SQ4 Driver for LD-driving for CD

SQ5 Driver for LD-driving for DVD

Spindle motor driver

Spindle motor rotation detection Rotation FG output for controlling spindle motor is output from No. 27 pin.

DVD/CD servo error signal replay

Built-in DVD/CD laser APC circuit Built-in LD current control circuit for DVD/CD.

Frame buffer memory Memory for temporarily caching read data of DVD/CD.

System memory External microcomputer memory for F/E system control.

CH1-side CH1-side

Servo reference voltage generation Signal after dividing VC25 (2.5V) into 2.1V enters the positive phase and output from the

amplifier output terminal as buffer output.

CH2-side CH2-side

RFRP (mirror detection signal) RF bottom hold signal and its DC are input to reverse input and positive input respectively

generation amplifier for canceling DC fluctuation. These then can be used as mirror signals.

Timing is controlled by No. 18 pin control signal for the 3-phase brushless spindle motor, using

No. 1~6 pins Hall element input signals, while current outputs are made from No 20, 22 and 24 pins.

Generation of various servo signals from pick up signals.

CD’s LD current control signals output from SU6 are received at base and the current

amount for LD driving is controlled.

DVD’s LD current control signals output from SU6 are received at base and the current

amount for LD driving is controlled.

● THERMISTER PCB

Ref. No. Application / Function Operation / Condition / Compatibility

UT1 Inverter

UT2 Comparator

QT1 Switching TR

THT1

Temperature detection thermister for

thermal shutdown

Output from UT2 comparator is inverted. Input is made on No. 2 pin and output on No. 4

pin. Activ e L.

Signal from thermister is inverse input and reference voltage is input to positive-phase

input. Output from thermister is comparated and output from No . 4 pin. Active H.

UT1 output is received on the base and output is inverted when it is made. The output is

feedback into the positive-phase input at UT2 for containing the fluctuations in outputs.

Resistance value is low at low temperature and high at high temper ature.

● DISPLAY PCB

Ref. No. Application / Function Operation / Condition / Compatibility

UD3

Power supply ON/OFF delay circuit With +B_DWN of reduced voltage detection circuit and OR of /P_ON signal, /P_DWN

NOR gate IC signal is generated.

● POWER & OUTPUT PCB

Ref. No. Application / Function Operation / Condition / Compatibility

UP1

VCC (+5V) generation switching Power supply is input from No. 2 pin and switching output is made from No. 3 pin.

regulator IC Going via choke coil, it becomes VCC (+5V) power supply output.

4

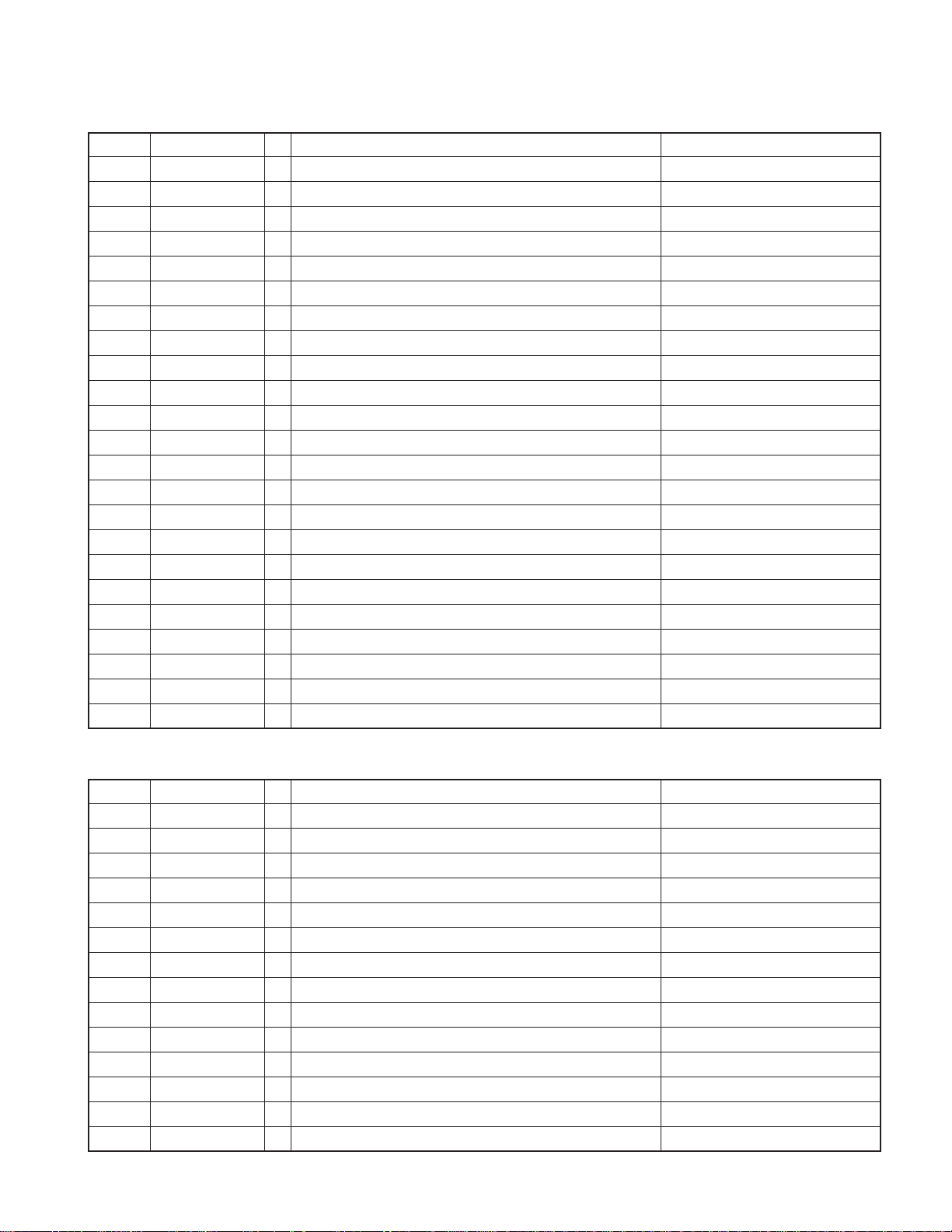

Page 5

KDV-S210P/S220P

/S230P/S240P

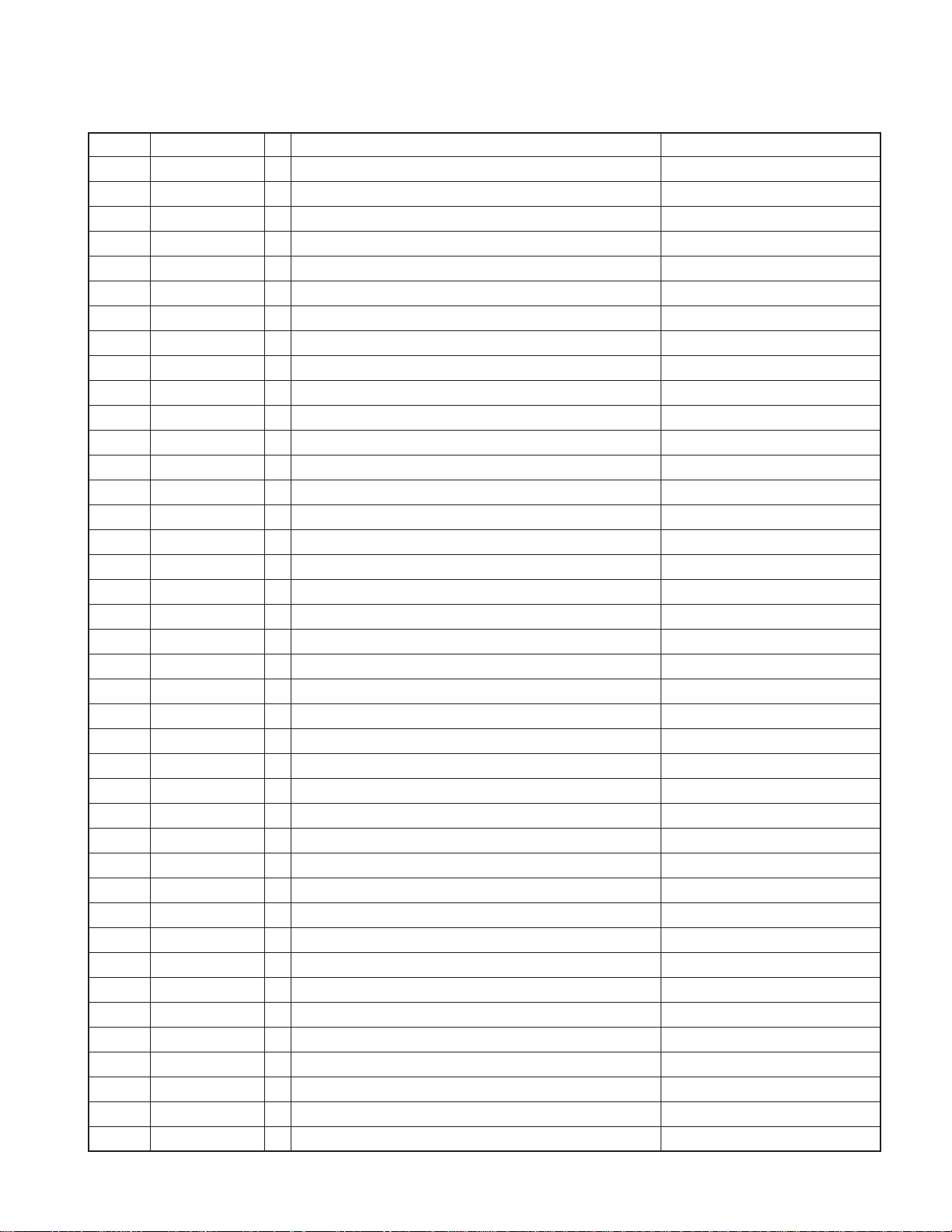

COMPONENTS DESCRIPTION

Ref. No. Application / Function Operation / Condition / Compatibility

UP2 S7V generation switching regulator IC

UP3 Analog audio output LPF amplifier CH1-side is Rch and CH2-side is Lch. Constitutes non-inverse active LPF composition.

UP4

QP1 Mute circuit driving TR

QP2 Mute circuit switching TR When this TR comes ON, muting is ON and when it comes OFF, muting is OFF.

QP3 Mute circuit switching TR

QP4 Rch mute TR When base is H, Rch is muted.

QP5 Lch mute TR When base is H, Lch is muted.

QP8 Composite video output buffer driver TR When the input signal comes in on the base, output is made from the emitter.

QP9

QP10 Mute circuit switching TR

QP11 Mute circuit switching TR

QP12

QP15

QP20

QP21

QP22

QP30 BU_VCC (+5V) regulator driving TR

QP40 28V regulator drive TR

QP41

Composite video output 75Ω driver

amplifier IC

Power supply ON/OFF delay circuit SW TR

Power supply ON/OFF delay circuit SW TR

Reduced voltage detection switching

TR for resume operation

Power supply ON/OFF delay circuit SW TR

Power supply ON/OFF delay circuit SW TR

Power supply ON/OFF delay circuit SW TR

TR for comprising Darlington connection

Power supply is input from No. 2 pin and switching output is made from No. 3 pin.

Going via choke coil, it becomes S7V power supply output.

Input is made on No. 3 pin and output is made from No 6 pin.

When QP2 is ON, input is made to the emitter. Mute circuit driving power supply is output

from the collector.

This is a TR for switching QP2. Therefore, the logic is inverted and when the TR comes

ON, muting is OFF, and when the TR comes OFF, the muting is ON.

When this TR is ON, base current of QP21 is shut off. QP21 is OFF and switching power

supply is ON.

When Z_MUTE signal in the base of this TR is active, (H on no signal), QP1 is turned ON

and the mute circuit is driven.

/P_ON in the base becomes L when the power switch comes ON. Therefore, it is H when

the power is OFF. When this happens, QP3 is forced to go OFF and muting is driven.

On the base of this TR, power switch triggered /P_ON signal comes in. When this is L, and QP22

is turned ON, base current of QP20 is shut off. When QP20 is OFF, switching power supply is ON.

At the time of reduced +B1, base current is shut off and the circuit goes OFF.

When this TR is ON, switching power supply is OFF.

When this TR is ON, switching power supply is OFF.

When this TR is ON, base current at QP20 is shut off. This means QP20 is OFF and

switching power supply is ON.

Receives batter power supply (+B1) by the collector and outputs regulation voltage 28V

(+B1) from the emitter.

Receives battery current (+B) with collector and outputs regulated voltage 28V (+B1) from the

emitter. This is used to counter the surge current, and it is normally about +B- +B1 =1.4V.

Along with QP40, constitutes Darlington connection and works to enhance compound hfe.

5

Page 6

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

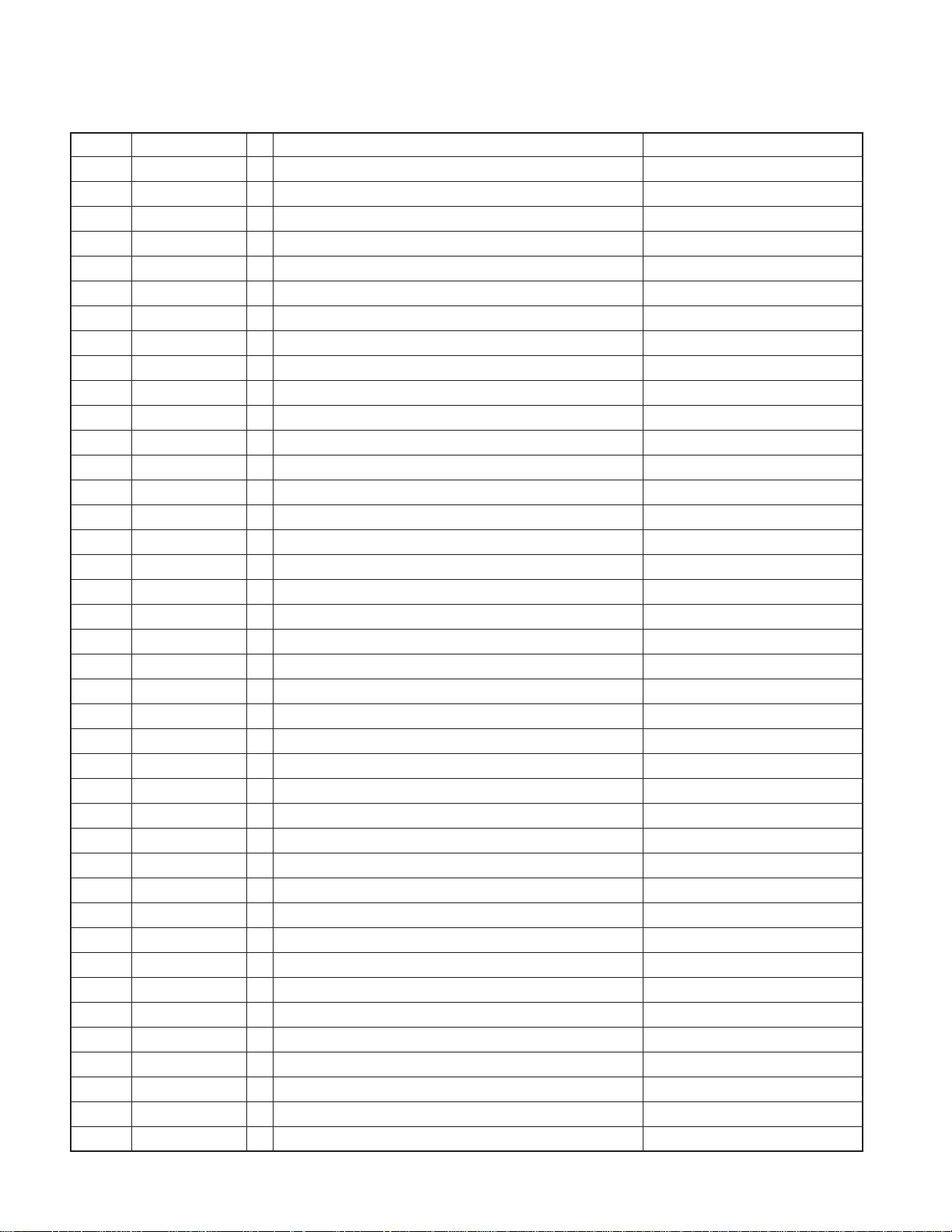

● B/E Microcomputer : ES6008 (COMBO PCB : U1)

Pin No. Pin Name I/O Application Processing Operation Description

1 VEE - I/O power supply (+3.3V) input

2~7 LA4~LA9 O Flash ROM address bus

8 VSS - Digital GND

9 VCC - Core power supply (+2.5V) input

10~16 LA10~LA16 O Flash ROM address bus

17 VSS - Digital GND

18 VEE - I/O power supply (+3.3V) input

19~21 LA17~LA19 O Flash ROM address bus

22,23 LA20,LA21 O Flash ROM address bus NC

24 /RESET I Chip reset input

25 TDMDX O NC

25 RSEL I ROM selection terminal Selected by 8bit ROM

26 VSS - Digital GND

27 VEE - I/O power supply (+3.3V) input

28 TDMDR I NC

29 TDMCLK I NC

30 TDMSF I NC

31 TDMTSC# O NC

32 TWS O Audio frame synchronization output

32 SEL_PLL2 I System and DSCK output clock selection [2] Selected by DCLK x 4

33 TSD0 O Audio serial data port 0

33 SEL_PLL0 I System and DSCK output clock selection [0] Selected by DCLK x 4

34 VSS - Digital GND

35 VCC - Core power supply (+2.5V) input

36 TSD1 O Audio serial data port 1 NC

36 SEL_PLL1 I System and DSCK output clock selection [1] Selected by DCLK x 4

37,38 TSD2,TSD3 O Audio serial data port 2,3 NC

39 MCLK O Audio master clock

40 TBCK O Audio bit clock output

41 SPDIF O SPDIF output

41 SEL_PLL3 I Clock source selection Selected by crystal oscillator

42 NC - NC

43 VSS - Digital GND

44 VCC - Core power supply (+2.5V) input

45 RSD I Audio input serial data NC

46 RWS I Audio input frame synch NC

47 RBCK I Audio input bit clock NC

48 NC - NC

49 XIN I Crystal input

6

Page 7

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

50 XOUT O Crystal output

51 AVEE - PLL analog power source (+3.3V) input

52 VSS - Digital GND

53~58 DMA0~DMA5 O DRAM address bus [0]~[5]

59 VEE - I/O power supply (+3.3V) input

60 VSS - Digital GND

61~66 DMA6~DMA11 O DRAM address bus [6]~[11]

67 VSS - Digital GND

68 VEE - I/O power supply (+3.3V) input

69 /DCAS O DRAM Column address strobe

70 /DOE O DRAM output enable Not used.

70 DSCK_EN O DRAM clock enable

71 /DWE O DRAM write enable

72 /DRAS O DRAM low address strobe

73,74 DMBS0,DMBS1 O SDRAM bank select 0,1

75 VEE - I/O power supply (+3.3V) input

76 VSS - Digital GND

77~82 DB0~DB5 I/O DRAM data bus [0]~[5]

83 VCC - Core power supply (+2.5V) input

84 VSS - Digital GND

85~90 DB6~DB11 I/O DRAM data bus [6]~[11]

91 VSS - Digital GND

92 VEE - I/O power supply (+3.3V) input

93~96 DB12~DB15 I/O DRAM data bus [12]~[15]

97 /DCS1 O SDRAM chip select [1] NC

98 VSS - Digital GND

99 VEE - I/O power supply (+3.3V) input

100 /DCS0 O SDRAM chip select [0]

101 DQM O DATA input/output mask

102 DSCS O SDRAM clock output

103 VSS - Digital GND

104 VEE - I/O power supply (+3.3V) input

105 DCLK I PLL 27MHz clock input NC

106 YUV0 O YUV0 pixel output data Not used.

106 CAMIN2 I Camera input 2 Not used.

106 UDAC O U video DAC output Output for composite video out

107 YUV1 O YUV1 pixel output data Not used.

107 VREF I Video DAC reference voltage input

108 YUV2 O YUV2 pixel output data NC

108 CDAC O Video DAC output NC

7

Page 8

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

109 YUV3 O YUV3 pixel output data Not used.

109 COMP I Compensation input

110 YUV4 O YUV4 pixel output data Not used.

110 RSET I DAC current adjust input

111 ADVEE - Video DAC analog power supply input

112 VSS - Digital GND

113 YUV5 O YUV5 pixel output data NC

113 YDAC O Y video DAC output NC

114 YUV6 O YUV6 pixel output data NC

114 VDAC O V video DAC output NC

115 YUV7 O YUV7 pixel output data NC

115 CAMIN3 I Camera YUV input 3 NC

116 PCLK2XSCN I/O 27MHz video output pixel clock NC

116 CAMIN4 I Camera YUV input 4 NC

117 PCLKQSCN O 13.5MHz video outout pixel clock NC

117 CAMIN5 I Camera YUV input 5 NC

118 /YSYNC I/O Vertical synchronization NC

118 CAMIN6 I Camera YUV input 6 NC

119 /HSYNC I/O Horizontal synchronization NC

119 CAMIN7 I Camera YUV input 7 NC

120 VSS - Digital GND

121 VCC - Core power supply (+2.5V) input

122 HD0 I/O Host data I/O [0] HD8

122 DCI [0] I/O DVD channel data I/O [0] Not used.

122 EAUX1 [0] I/O AUX1 data I/O [0] Not used.

123 HD1 I/O Host data I/O [1] HD9

123 DCI [1] I/O DVD channel data I/O [1] Not used.

123 EAUX1 [1] I/O AUX1 data I/O [1] Not used.

124 HD2 I/O Host data I/O [2] HD10

124 DCI [2] I/O DVD channel data I/O [2] Not used.

124 EAUX1 [2] I/O AUX1 data I/O [2] Not used.

125 HD3 I/O Host data I/O [3] HD11

125 DCI [3] I/O DVD channel data I/O [3] Not used.

125 EAUX1 [3] I/O AUX1 data I/O [3] Not used.

126 HD4 I/O Host data I/O [4] HD12

126 DCI [4] I/O DVD channel data I/O [4] Not used.

126 EAUX1 [4] I/O AUX1 data I/O [4] Not used.

127 HD5 I/O Host data I/O [5] HD13

127 DCI [5] I/O DVD channel data I/O [5] Not used.

127 EAUX1 [5] I/O AUX1 data I/O [5] Not used.

8

Page 9

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

128 HD6 I/O Host data I/O [6] HD14

128 DCI [6] I/O DVD channel data I/O [6] Not used.

128 EAUX1 [6] I/O AUX1 data I/O [6] Not used.

129 VSS - Digital GND

130 VEE - I/O power supply (+3.3V) input

131 HD7 I/O Host data I/O [7] HD15

131 DCI [7] I/O DVD channel data I/O [7] Not used.

131 EAUX1 [7] I/O AUX1 data I/O [7] Not used.

131 VFD_DIN I VFD data input Not used.

132 HD8 I/O Host data I/O [8] HD0

132 /DCI_FDS I/O DVD input sector start Not used.

132 EAUX2 [0] I/O AUX2 data I/O [0] Not used.

132 VFD_CLK I VFD clock input Not used.

133 HD9 I/O Host data I/O [9] HD1

133 EAUX2 [1] I/O AUX2 data I/O [1] Not used.

133 SQSQ I Sub code Q data Not used.

134 HD10 I/O Host data I/O [10] HD2

134 EAUX2 [2] I/O AUX2 data I/O [2] Not used.

134 SQSK I Sub code Q clock Not used.

135 HD11 I/O Host data I/O [11] HD3

135 EAUX2 [3] I/O AUX2 data I/O [3] Not used.

135 IRQ O IRQ output Not used.

136 HD12 I/O Host data I/O [12] HD4

136 EAUX2 [4] I/O AUX2 data I/O [4] Not used.

136 C2PO I C2PO error correction flag input from CD-ROM Not used.

137 HD13 I/O Host data I/O [13] HD5

137 EAUX2 [5] I/O AUX2 data I/O [5] Not used.

137 SP I 16550 UART serial port input Not used.

138 VSS - Digital GND

139 VCC - Core power supply (+2.5V) input

140 HD14 I/O Host data I/O [14] HD6

140 EAUX2 [6] I/O AUX2 data I/O [6] Not used.

140 SQSI I Sub code Q synch Not used.

141 HD15 I/O Host data I/O [15] HD7

141 EAUX2 [7] I/O AUX2 data I/O [7] Not used.

141 IR I IR remote control input Not used.

142 /HWRQ O Host write request NC

142 /DCI_REQ O DVD control interface request NC

142 EAUX4 [0] I/O AUX4 data I/O 5 NC

143 /HRRQ O Host read request NC

9

Page 10

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

143 EAUX4 [1] I/O AUX4 data I/O 4 NC

144 HIRQ I/O Host interrupt

144 /DCL_ERR I/O DVD channel data error Not used.

144 EAUX4 [0] I/O AUX4 data I/O 0 Not used.

145 /HRST O Host reset

145 EAUX3 [5] I/O AUX3 data I/O 5 Not used.

146 HIORDY I Host I/O ready

146 EAUX3 [3] I/O AUX3 data I/O 3 Not used.

147 VSS - Digital GND

148 VEE - I/O power supply (+3.3V) input

149 /HWR I/O Host write request

149 DCI_CLK I/O DVD channel data clock Not used.

149 EAUX4 [5] I/O AUX4 data I/O 5 Not used.

150 /HRD O Host read request

150 /DCI_ACK O DVD channel data valid Not used.

150 EAUX4 [6] I/O AUX4 data I/O 6 Not used.

151 /HIOCS16 I Device 16-bit data transfer

151 CAMCLK I Camera port pixel clock input Not used.

151 EAUX3 [4] I/O AUX3 data I/O 4 Not used.

152 /HCS1FX O Host select 1

152 EAUX3 [7] I/O AUX3 data I/O 7 Not used.

153 /HCS3FX O Host select 3

153 EAUX3 [6] I/O AUX3 data I/O 6 Not used.

154 HA0 I/O Host address bus 0

154 EAUX4 [2] I/O AUX4 data I/O 2 Not used.

155 HA1 I/O Host address bus 1

155 EAUX4 [3] I/O AUX4 data I/O 3 Not used.

156 VSS - Digital GND

157 VEE - I/O power supply (+3.3V) input

158 HA2 I/O Host address bus 2

158 EAUX4 [4] I/O AUX4 data I/O 4 Not used.

159 VEE - I/O power supply (+3.3V) input

160,161 AUX0,AUX1 I/O Accessory port 0,1 NC

162 AUX2 I Accessory port 2 EJECT key input

162 /IOW O I/O write strobe Not used.

163 VSS - Digital GND

164 VEE - I/O power supply (+3.3V) input

165 AUX3 I/O Accessory port 3 NC

165 /IOR O I/O read strobe NC

166 AUX4 I Accessory port 4 IR remote control input

10

Page 11

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

167,168 AUX5,AUX6 I/O Accessory port 5,6 NC

169 AUX7 I Accessory port 7 Power down detection

170 /LOE O Device output enable

171 VSS - Digital GND

172 VCC - Core power supply (+2.5V) input

173~175 /LCS0~/LCS2 O Chip select 0~2 NC

176 /LCS3 O Chip select 3

177 VSS - Digital GND

178~182 LD0~LD4 I/O Flash ROM device data bus [0]~[4]

183 VEE - I/O power supply (+3.3V) input

184 VSS - Digital GND

185~191 LD5~LD11 I/O Flash ROM device data bus [5]~[11]

192 VSS - Digital GND

193 VEE - I/O power supply (+3.3V) input

194~197 LD12~LD15 I/O Flash ROM device data bus [12]~[15]

198 /LWRLL O Device low bite write enable NC

199 /LWRHL O Device high bite write enable NC

200 VSS - Digital GND

201 VEE - I/O power supply (+3.3V) input

202 CAMIN0 I Camera YUV0 NC

203 CAMIN1 I Camera YUV1 NC

204~207 LA0~LA3 O Flash ROM address bus

208 VSS - Digital GND

● F/E Microcomputer : M5705 (COMBO PCB : SU1)

Pin No. Pin Name I/O Application Processing Operation Description

1AVSS_DS - Data slicer port analog ground 2 XSRFIN I Analog RF signal input after passing through equalizer 3 XSIPIN I Data slicer inverse input 4AVDD5_DS - Data slicer port analog +5V power supply 5 XSDSSLV O Slice level output 6 XSRSLINT I Analog data slicer reference current setting input 7 VDD - Digital +3.3V power supply input 8 XSAWRC O Control putout for widening VCO range 9 XSRFGC O Loading motor control signal L : Eject, H : Loading, Vref : Stop

10 XSEFGC O NC 11 XSFOCUS O Focus actuator control DA output 12 XSTRACK O Tracking actuator control DA output 13 XSSLEG O Feed motor control DA output 14 AVDD5_DA - DAC analog +5V power supply input -

11

Page 12

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

15 XSMOTOR O Disc motor control DA output 16 AVSS_DA - DAC analog ground 17 XSRFRPLP I NC 18 XSTELP I Tracking error signal AD input after passing through LPF 19 XSVREF2 I 2.1V reference voltage input 20 XSRFRPLP I Mirror signal AD input 21 XSTEXI I Tracking-zero cross signal AD input 22 AVSS_AD - ADC analog ground 23 XSTEI I Tracking error signal AD input 24 XSFEI I Focus error signal AD input 25 XSCEI I Center error signal AD input 26 AVDD5_AD - ADC analog +5V power supply input 27 XSSBAD - Sub-beam add (SBAD) signal AD input 28 GND - Digital ground 29 XSDFCT I Defect detection signal input 30 XSCSJ O Head amplifier control register chip selection output 31 XSCLK O Head amplifier control register communication clock output 32 XSDATA I/O Head amplifier control register communication data input/output 33 XSLDC O Actuator feed/loading driver mute output L : Driver mute

34 XSFGIN I Disc motor FG signal input 35 XSSPDON O Disc motor driver mute signal output L : Driver mute

36~39

40 XMP1_7 I SLOT_IN_DET sensor input DISC detection : H

41 XMP1_6 I HOMESW input

42 GND - Digital ground 43 NC - - 44 XMP1_4 I OUTSW sensor input Disc eject : L

45 XMP1_3 I INSW input Disc insert : L

46 XMFSCSJ I Flash memory chip selection output 47 XMP1_2 I LED lighting up output NC

48 XGPIO2 O SLDC (Laser SW) output L : Laser lights up.

49 XMP1_1 I EJECT SW input NC

50 XHRSTJ I ATAPI HRST input L : Reset

51 XGPIO1 O NC 52 XGPIO0 O Disc motor driver SB (short brake) control output NC

53 XCRSTJ I Chip reset input L : Reset

54 XMPSENJ O Flash memory program store enable output 55 VDD - Digital +3.3V power supply input 56 XMALE O NC 57 XMP1_0 O Flash memory address path output [16] -

XSFLAG3~XSFLAG0

O Servo control block monitor output -

Pick internal circumference detection : L

12

Page 13

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

58 VDD - Digital +3.3V power supply input 59 XOSC1 I Main clock inverter input 60 XOSC2 O Main clock inverter output 61 GND - Digital ground 62~69 XMD0~XMD7 I/O Flash memory data bus input/output [0]~[7] 70 XMCSJ I/O XMP3_1 NC

71 XMRDJ I/O XMP3_0 NC

72 XMWRJ O Flash memory write strobe output 73 XMINT1J I/O XMP3_7 NC

74,75 XMA11,XMA10 I/O Flash memory address bus input/output [11],[10] 76 VDD - Digital +3.3V power supply input 77~86 XMA9~XMA0 I/O Flash memory address bus input/output [9]~[0] 87 XMA12 I/O Flash memory address bus input/output [12] 88 GND - Digital ground 89~91 XMA13~XMA15 I/O Flash memory address bus input/output [13]~[15] -

92 XHDASPJ I F/E master/slave switching input

93 XHCS3J I ATA control block task file register control input 94 XHCS1J I ATA command block task file register control input 95 XHA2 I Host address input [2] 96 XHA0 I Host address input [0] 97 XHPDIAGJ I/O Passod Diagnostics signal input/output NC

98 XHA1 I Host address input [1] 99 XHCS16J O ATAPI 16bits data selection output 100 XHINT O ATAPI host interrupt request output 101 XHDACKJ I ATAPI DMA acknowledge input 102 XHIORDY O ATAPI I/O channel ready output 103 XHIORJ I ATAPI host I/O read input 104 XHIOWJ I ATAPI host I/O write input 105 XHDRQ O DMA request input 106 XHD15 I/O ATAPI host data bus input/output [15] 107 XHD0 I/O ATAPI host data bus input/output [0] 108 XHD14 I/O ATAPI host data bus input/output [14] 109 XHD1 I/O ATAPI host data bus input/output [1] 110 GND - Digital ground 111 XHD13 I/O ATAPI host data bus input/output [13] 112 XHD2 I/O ATAPI host data bus input/output [2] 113 XHD12 I/O ATAPI host data bus input/output [12] 114 XHD3 I/O ATAPI host data bus input/output [3] 115 VDD - Digital +3.3V power supply input -

This terminal is not referenced by the

firm. It is master-fixed at the firm.

13

Page 14

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

116 XHD11 I/O ATAPI host data bus input/output [11] 117 XHD4 I/O ATAPI host data bus input/output [4] 118 XHD10 I/O ATAPI host data bus input/output [10] 119 XHD5 I/O ATAPI host data bus input/output [5] 120 XHD9 I/O ATAPI host data bus input/output [9] 121 XHD6 I/O ATAPI host data bus input/output [6] 122,123 XHD8,XHD7 I/O ATAPI host data bus input/output [8],[7] 124 XRD15 I/O SDRAM data bus input/output [15] 125 XRD0 I/O SDRAM data bus input/output [0] 126 XRD14 I/O SDRAM data bus input/output [14] 127 XRD1 I/O SDRAM data bus input/output [1] 128 XRD13 I/O SDRAM data bus input/output [13] 129 XRD2 I/O SDRAM data bus input/output [2] 130 GND - Digital ground 131 XRD12 I/O SDRAM data bus input/output [12] 132 XRD3 I/O SDRAM data bus input/output [3] 133 XRD11 I/O SDRAM data bus input/output [11] 134 XRD4 I/O SDRAM data bus input/output [4] 135 XRD10 I/O SDRAM data bus input/output [10] 136 XRD5 I/O SDRAM data bus input/output [5] 137 XRD9 I/O SDRAM data bus input/output [9] 138 GND - Digital ground 139 XRD6 I/O SDRAM data bus input/output [6] 140,141 XRD8,XRD7 I/O SDRAM data bus input/output [8],[7] 142 XRWEJ O SDRAM write output 143 XRSDCLK O SDRAM clock output 144 XRRASJ O SDRAM RAW address output 145 XRCASJ O SDRAM COLUMN address output 146 VDD - Digital +3.3V power supply input 147 XROEJ - SDRAM memory output enable output 148,149 XRA9,XRA8 I/O SDRAM address bus input/output [9],[8] 150 VDD - Digital +3.3V power supply input 151,152 XRA11,XRA10 I/O SDRAM address bus input/output [11],[10] 153 XRA7 I/O SDRAM address bus input/output [7] 154 GND - Digital ground 155~157 XRA6~XRA4 I/O SDRAM address bus input/output [6]~[4] 158~161 XRA0~XRA3 I/O SDRAM address bus input/output [0]~[3] 162 VDD - Digital +3.3V power supply input 163 XTPLCK O PLCK test output NC

164 XTSLRF O SLRF (slice RF) test output -

14

Page 15

KDV-S210P/S220P

/S230P/S240P

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. Pin Name I/O Application Processing Operation Description

165 GND - Digital ground 166 XSPDIREF I PLL phase detector reference current generation input 167 XSFDIREF I PLL frequency detector reference current generation input 168 AVDD5_PL - Data PLL analog +5V input 169 XSPLLFTR2 I Data PLL loop filter pin #2 170 AVSS_PL - PLL analog GND 171 XSFDO O PLL frequency detector charged pump circuit output terminal 172 XSFTROPI I PLL loop filter OP circuit input terminal 173 XSVR_PLL I PLL reference voltage input 174 XSPDOFTR2 I PLL phase detector filter pin #1 175 XSVREFO O PLL reference voltage output 176 XSAWRCVCO I AWRC VCO input pin -

TEST MODE

In the test mode, it is possible to confirm on the controlling

firm ware version number on each of F/E (disc servo control

section) and B/E (system control and MPEG replay) systems.

■ How to use the Test Mode

Turn on power supply (Use the power switch) and immediately after turning power on, use the remote controller to input

the following, without inserting a disc.

RETURN

↓

PROGRAM

↓

RANDOM

Each time input is made, the screen shows a hand mark (which

means the input is not effective) b ut continue pressing the ke ys.

Then, the each firm’s version will be displa y on the bottom two

lines of the screen.

Line 1 : B/E firm version number

Line 2 : F/E firm version number

The display will soon disappear. During display, other operations can be conducted.

15

Page 16

A B C D E

B37

B36

B

KDV-S210P/S220P

/S230P/S240P

1

2

3

4

5

PC BOARD (COMPONENT SIDE VIEW)

SR86

SC59

SR83

SR87

SC60

SR84

SD1

SR44

SC33

SR41

SR37

SC31

SR39

SR35

SR33

STC13

STC14

SC41

SR78

COMBO PCB

B500

SL5

SL6

SD7SD8

SQ4SQ5

EBEB

SL7

SC44

STC1

SR4

SC7

SC554

SC11

SC12

SC14

SR9

SC13

SR10

SR12SC15

SR13SC17

SR11SC16

SR14SC22

SR15SC21

SR16SC20

SR17SC19

SR18SC18

SR97SC23

SR20

SC24

SR21

SR19

SR22

SR24

SR23

SR26

SC25

SR29

SC26

SC27

SD2

SR27

SBC6

FB501

STC12

B4

SR109

SC81

85

SR110

SU8

SR113

1

SC84

SR100

SR82

SR101

SC82

SR85

SR2

J3

SR3

SBC3

SR70

SR69

SR72

SR71

SR65

SC9

SR66

SR5

SR6

SR67

SR68

SC8

SR8

176 133

1

FB500

B1

SC83

SR112

SR108

SR111

SR114

SC72

SC71

SC54

SR103

SR92

SR25

SC67

SR91

SR90

SR89

SC74

SBC9

4

SC64

SC63

SC61

SU1

44

45 88

SR1

SR31

SL1

SC29

SC28

SR32

SY1

SC500

SD3

SC30

SR74

SR75

SR77

31

45

SC76

SU9

THERMISTER PCB

RT7

RT8

RT20

RT5

CT1

QT1

EB

RT9 RT2

54

13

THT1

CBT10

13

BCT1

UT1

SC46

RT6

54

UT2

13

CT3

RT4

SD5

SL2

SR46

SR48

STC6

SD6

SC42

SBC13

SBC14

SC34

SR42

SR40

SC32

SR36

SR34

STC8

SC45

STC5

SR47

SR49

SR43

1

CB5

STC15

STC16

SC77

SC80

SC79

SBC2

SC552

33

SU6

48

SC56 SC57 SC55

SC53 SBC1

SR88

STC2

STC4

SR102

SR106

132

89

SC553

4

SR104

SC52

SRN14

SC551

SR94

SR105

SR95

SC550

1732

6449

SR93

SR96

SC78

SC75

SC603

SC602

21

SJ2

SR98

SR99

1

CB7

G

R39

R38

O

B3

B2

I

B50

U5

F

D22

SC58

SC70

SC68

SC66

SC65

SC69

SC600

SC601

16

D21

SC62

1

SBC17

21

40

SRN10

SR117

SU4

SRN13

SRN3

SRN5

SBC5

SBC4

20

1

SRN12

SRN4

B61

SR73

B40

SRN11

R14

R32

B38B35

L501

28

B34

54

B12

U3

105

156

B45

85

27

1

R19

104

157

U2

6

SC100

SC102

SR201

SR50

SR54

SR55

SR200

7

SC39

SC38

STC101

SC37

SQ3

SC36

SR56

SC43

SBC12

SR58

SR57

11

SR38

SJ4 SJ3

OG I

STC100

SC50

SR120

SR121

SR51

SL3

SR52

SR53

43

SR79

STC11

SLED1

SBC30

SL4

SC47

SBC7

SC48

STC10

STC9

14

R4

R5

25

B30

R34

R219

R37

B39

C5

48

CB3

16

16

Page 17

JIHGF

9

KDV-S210P/S220P

/S230P/S240P

1

THERMISTER PCB

Ref. No. Address

UT1 2B

UT2 2B

QT1 2B

COMBO PCB

Ref. No. Address

U1 5F

U2 6E

U3 4E

U5 2F

U9 5G

U23 4H

U27 3F

U28 6F

U35 5H

SU1 5C

SU6 3D

SU8 3C

Q1 4F

SQ3 6C

SQ4 2B

SQ5 3B

2

3

4

5

C222

14

8

RN9

RN11

U1

B33

12

CB502

C512

B14

Q1

BE

53

B10

52

D4

CB600

B31

D500

BC651

BC650

R167

Q26

Q27

B62

R165

R174

FB3

R3R301

54

U9

13

C227

BE

BE

BE

R176

R353

Y1

R43

Q25

R173

R50

C59

R171R170

D2

D501

D7

C226

D6

D5

FB8

C268

BC750

BC653

BC701

C14

1

8

FB6

BC652

R511

U35

C267

C505

R28

C192

C190

Q13

C213

C188

R27

R510

R535

5

8

R24 C191 R20

16

9

C266

R29

U23

BE

C258

R152

R508

R45

R46

R162

BE

Q22

R156

C219

R159

R509

C504

4

C184

R534

1

R22

R21

C185

C259

8

U5

FB505

B50

1

U27

7

27

RN8

RN10

B36

B37

1

4

7 208

B32

CB10

136

24

1

R600

R33

R216

25

U28

48

CB4

FB7

1

C273

C274

6

1

14

U4

7

8

Refer to the schematic diagram for the values

7

of resistors and capacitors.

17

Page 18

K L M N O

B

B

0

KDV-S210P/S220P

/S230P/S240P

1

PC BOARD (FOIL SIDE VIEW)

COMBO PCB

C223 C216

R15

2

BC609

BC608

C230

R178

C232

R179

FB2

R523

B

RFOUT

B

24 1

F

D

A

C

E

PD

SCN2

C252

L19

R172

R166

R522

C251

R322

GNDD2

3

R524

C228

R312

R310

B16

B23

D/A

LA5

LA3

LA4

LA4

LA12

LA16

LA9

B28

LD1

LD3

LA11

R298

R9

FB5

B25

LD0

LD2

BYTE

R31

R40

R299

LD10

B41

R35

B22

B15

B24

B18

B7

FB1

B6

LOE#

R292

C247

B27

LCE#

R326

LD13

R307

R306

R295

C246

R308

R311

B11

R296

R423

R212

R213

LD11

R701

R700

R431

LD12

LD14

B59

CB601

R11

R10

26

SU7

C4

SRN6

50

SBC18

SBC8

SRN7

SRN8

SRN9

SRN2SRN1

SC4

SC5

SC6

SC3

21

1420

U34

29

30

1324

GNDD3

3-3V

R604

R603

R41C58

R313

R13

R149

R602

R601

4

R12

5

6

7

C15

C269

BC654

BC655

BC656

BC700

C250

FB4

R44

C248

C249

R6

R332

BC611

BC610

R304

R354

BC702

ZD700

L500

C63

R330

R331

LA8

SR550

L502

L503

R334

FB504

R7

R8

R42

RST#

R52

C2

D1

B13

C1

R335

R1 R2

B8

B26

B20

B19

B9

R36

R26

LA18

LA19

WR#

LD7

B29

B21

R503

LA6

LD9

LA5

LA7

LA17

LA15

B17

LD8

LA1

R381R382

LA2

LA6

LA10

LA13

LA14

13

SC1

SC2

5

RF

25

1

S

S

18

Page 19

B501

5

B503

SC49

BC613

BC612

THERMISTER PCB

CT2

RT3

RT1

COMBO PCB

Ref. No. Address

U34 6O

SU2 5R

SU3 6Q

SU7 4O

TSRQP

KDV-S210P/S220P

/S230P/S240P

1

2

GNDD2

RFVCC

SR107

SC73

B5

BCT2

3

RF 0

GNDD

PLLVCC

SBC11

GPIO1

SR7

SC10

MIRR1

SCEI

SB

SR60

SR300

SC101

XSPLLFTR2

SBC19

SBC15

SBC10

SBC16

XSFGIN

XSPDON

SLDC

HRSTJ

SR59

SR62

1

SBC20

SBC21

SC51

SR118

DGND

SR64

SR63

XTSLRF

XTPCLK

XSDFCT

XTEI

XFEI

SSBAD

SC40

SBC500

14

SR45

SFOCUS

STRACK

SSLEG

SMOTOR

SQ1

EB

BC606

BC607

S1

BC604

TR+

BC605

TR-

15

28

MRDJ1

PSEN1

SU2

SR81

SR80

FO-

SJ5

R100

14

1

FO+

BC602

BC603

4

5

6

MVCC

SR551

SBC100

SU3

SCN1

BC600

2815

BC601

FM+

FM-

115

Refer to the schematic diagram for the values

7

of resistors and capacitors.

19

Page 20

U V W X Y

KDV-S210P/S220P

/S230P/S240P

1

PC BOARD (COMPONENT SIDE VIEW)

POWER & OUTPUT PCB

DISPLAY PCB

DD2

DD1

ZDD1

BCD6

CD8

UD2

UD3

1

LD1

44

UD1

1

BCD1

RD2

BCD3

1

CD7

CD6 CD5

YD1

RD12

RD1

RD13

18

177

6

RD14

RD11

1

BCD4

14

RD5

DD4

DD3

BCD30

RD31

CD2

RD10

BCP4

RP51

BCP20

QP12QP22

RP17

FBP8

BCP8

RP53

BE

RP18

BE

EPP2

RP47

EPR1

JKP1

RP79

JKP2

RP90

ZDP7

RP52

CP70

RP67

DP10

RD6

CP30

CD3

QP14

QP13

RP49

FBP6

RP44

FBP12

RP48

RP69

RP70

BCP2

JKP3JKP4JKP5

CP10

DP11

BE

EB

ZDP20

FBP9

FBP3

BCP5

QP11

BEBE

RP7

ZDP3

DP4

BCP3

FP1

BPC40

8

CBD3

2

3

RD30

BCD2

28

2939

40

RD20

BCD5

8

5

UD4

1

4

4

5

6

1

7

8

5

CBD1

7

FBP7

RP20

CP11

ZDP4

FBP10

RP81

RP10

BE

CP3

CP2

QP3

QP41

RP76

RP74

RP12

EB

QP7

ZDP6

RP41

RP42

RP72

RP11

BCP6

BCP7

BCP44

RP16

RP15

DP7

FBP11

BCP49

BCP48

TRP1

EB

QP20

EB

QP21

EB

QP9

RP80

DP3

BCP51

BE

QP40

BCP30

CP71

RP27

BE BE

QP4 QP6

EB

QP5

RP23

DP8

ZDP21

DP6

BCP41

RP66

RP14

CP21

CP23

CBP502

DP2

CP9

RP71

RP28

RP65

QP30

CP20

UP3

CP15

BCP47

CP22

8

1

FBP20

DP1

BCP50

ZDP40

BCP42

CP19

RP31

CP41

4

5

CP40

RP24

UP4

5

CP7

RP4

CP8

UP2

BCP52

8

1

CP6

LP3

BE

RP39

BCP27

RP6

RP5

5

4

BCP53

UP1

1

8

1124

8

CP4

RP1

CP5

RP25

RP26

RP60

CP16

RP43

RP110

RP34

RP21

QP1

RP101

RP30

RP32

RP29

5

4

ZDP30

ZDP5

BCP22

RP22

RP100

RP36RP35

QP8

RP38

RP37

RP40

BE

BCP12

RP3

RP2

BCP32 RP91

RP61

BCP45

DISPLAY PCB

Ref. No. Address

UD3 6U

BCP17

CP18

RP33

BCP21

POWER &

OUTPUT PCB

BCP23

BCP20

Ref. No. Address

UP1 5X

UP2 5X

UP3 2X

CP17

EB

BCP26

RP13

CBP7

18

RP46

FBP15

BEBE

DP12

QP10

RP19

QP2

ZDP2

BCP25

RP9

RP8

UP4 3X

QP1 4X

QP2 4X

QP3 4W

QP4 2X

QP5 3X

QP8 3X

QP9 4X

QP10 4X

QP11 4W

QP12 4W

QP15 7X

QP20 4X

QP21 4X

LP2

QP22 4W

QP30 7X

QP40 6X

BCP13

14

BCP15

LP1

ZDP1

BCP9

RP45

EB

CBP1

QP15

15

RP50

BCP43

BCP31

CBP5

BCP11

DP5

QP41 6W

Refer to the schematic

diagram for the values of

resistors and capacitors.

20

Page 21

ADACABAAZ

KDV-S210P/S220P

/S230P/S240P

PC BOARD (FOIL SIDE VIEW)

POWER & OUTPUT PCB

EJECT SW

SWD2

1

DISPLAY PCB

2

3

LEDD2

4

5

6

POWER SW

SWD1

LEDD1

Refer to the schematic

diagram for the v alues of

resistors and capacitors.

7

21

Page 22

A B C D E

0

S

1

KDV-S210P/S220P

/S230P/S240P

1

(CHASISS GND)

SPNDLE

MOTOR

2

LOADING

MOTOR

DISC

3

SENSOR

SLOT

SENSOR

SCN1

FM+

H3+

H2+

H1+

LOAD+

LOAD-

DISC EJECT

INSW

GNDD

DISC IN

OUT SW

SLOT IN DET

GNDD

COMBO PCB

1

FM-

2

SW

3

4

SW

5

H+

6

H-

7

H3-

8

9

H2-

10

11

H1-

12

13

A1

14

A2

15

A3

SJ2

1

2

SJ3

1

2

3

4

SJ4

1

2

3

SR38

120

SR51

91

SR52

11

12

26

6

5

4

3

2

1

24

22

20

17

18

4.7K

SR57

5.1V

SR551

SR53

47K

3.3V

0

45

91

47K

SR58

44

40

SVCC

MOTOR DRIVER

SU3

1

2

3

4

5

6

SR62 0

5.1V

41

SR78 10K

SC100 0.1

SC101 0.1

SC41

SC40 0.1

0.1

SR60 0

5.1V

0.1

SBC500

49

SC37SC38

1000P

1000P1000P

SC39

STC100

29

10

12

13

14

+

100u16

H1+

2

H1-

3

H2+

4

H2-

5

H3+

6

H3-

7

GSW

FIN

8

GND

9

CP1

CP2

11

VG

CNF

SB

VCC

FG3

RNF1

RNF1

RNF2

ECR

281

27

FG

SR200

26

VH

25

VM

24

A1

23

22

A2

30

FIN

21

20

A3

SR201

10K 0.01

19

18

PS

EC

VM

35

17

15

16

15

0.1

SBC100

120

SR54 1

SR55 1

SC102

7.0V

STC101

7.0V

SC36

0.1

100u16

S+7V

MMVC

SC31 0.1

PICK DRIVER

MOTOR DRIVER

SU2

SR39

33

SR43

10K

13

14

SR34 33K

SC32 100P

SR40 12K

SR42 3.3K

SC34 4700P

5.1V

26

24

22

20

34

SR56

33

+

11

19

13

SR36 0

SR46 1

SR48 1

1

VINFC

2

CFCERR1

3

CFCERR2

4

VINSL+

5

VINSL-

6

VOSL

7

VNFFC

29

GND

8

VCC

9

PVCC1

10

PGND

11

VOSL-

11

12

VOSL+

12

13

VOFC-

14

VOFC+

STBY

BIAS

VINTK

CTKERR1

CTKERR2

VINLD

PREGND

GND

PVCC2

VNFTK

PGND

VOLD-

VOLD+

VOTK-

VOTK+

28

27

26

25

24

23

22

30

21

20

19

18

17

16

15

SBC1

0.1

SC552

4

STC12

10

SD7

10

SD8

22u16

STC13

SC59

STC14

100u16

SC60

+

SR86

5.1K

+

SR87

1K

100u16

1000P

1000P

+

24

SC603 10P

SC602 10P

SC601 10P

SC600

10P

11

12

13

22

14

15

16

SCN2

TR-

TR+

FO-

FO+

PD(MONITOR)

VCC

VR

GND

LD(DVD)

5

OPTICAL

PICKUP

6

LD(CD)

GND(NC)

GND

RFOUT

VCC

VS(VCC)

GND

VR

PD

C

B

A

D

F

E

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

16

15

13

14

21

SR99 1.2K

SR98 470

23

12

13

14

11

15

16

0.1

SC78

SC550

+

100u16

SC75

SR83

TP31

SQ4

5.1V

SL6

SR84

TP32

SQ5

SL7

+

0.1

SC551

100u16

SC58

680P

SC62 0.1

SC65 680P

SC66 680P

SC68 680P

SC69 680P

SC70 100P

SR93 1.2K

SR94 1.2K

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

SR95 11K

DVDFRP

DVDRFN

PD1

PD2

A2

B2

C2

D2

CP

CN

D

C

B

A

F

E

CDTE

181920

17

SR96 11K

SC52 0.1

64636261605958

ATOP

CDRF

CDRFDC

VC12NCVNB

21

SR105 0

SC55 0.1

ATON

DVDPD

DVDLD

22

SR104 0

22

21

5.1V

AIP

AIN

CDPD

232425

SR102 0

SR106 0

23

100u16

+

VPA

CDLD

24

DVD/CD SERVO

HEAD AMPLIFIER

LDON

SR103 1.5K

0

10K

SR85

SC54

680P

575655545352515049

SIGO

SU6

VC

26

+

SC80 0.1

SC79 0.1

STC15 47u16

SR101

0

SR108

8.2K

SR112

STC16 47u16

0.1

SC82

SC57 0.1

SR88 8.2K

BYP

VCI

27

+

SBC2 0.1

SU8

1

2

3

4

SC53 0.1

RX

DIN

VPB

282930

1OUT

1IN-

1IN+

GND

SC56 0.1

DIP

FNP

MIRRMPMB

31

SC77 1000P

SC76 4700P

VCC

2OUT

2IN-

2IN+

FNN

32

8

7

6

5

VNA

SDEN

SDATA

SCLK

MEVO

MLPF

FDCHG

5.1V

SC83

HOLD1

LCP

LCN

CE

FE

TE

MEI

MEV

TPH

DFT

PI

MIN

0.1

SC8

SR1

SR11

SC84

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

0.47

7

COMBO PCB (1/7)

22

Page 23

JIHGF

33V

144

76

VNA

V

KDV-S210P/S220P

/S230P/S240P

47u16

160

160

XRA2

SVCC

10K

SR3

SR2

3.3K

+

0.1

SC10

151

156

155

XRA5

155

XRA6

152

153

154

153

152

GND

XRA7

151

XRA10

150

XRA11

149

149

XRA8

VDD 3.3

148

148

147

XRA9

XROEJ

146

VDD 3.3

145

XRCASJ

159

159

158

XRA1

158

157

XRA0

157

156

XRA4

SU1

MVCC

RFVCC

5.1V

IVER

RIVER

STBY

BIAS

INTK

ERR1

ERR2

VINLD

EGND

GND

VCC2

NFTK

PGND

OLDOLD+

OTKOTK+

28

27

26

25

24

23

22

30

21

20

19

18

17

16

15

33K

SR33

SR35

SD2

22K

SR37

33K

SR41 SC33

0 100P

SR44 0

0.1

SBC14

18

17

SR47 1

SR49 1

0.1

SBC13

16

15

33

12

9

5.1V

5.1V

MEI

SC61 33P

SC63 33P

SC64 33P

SR89 33

48

SR90 33

47

SR91 33

46

SC67 0.047

45

44

43

CE

42

FE

41

TE

SR92 0

40

SC71 1000P

39

SC72 0.1

38

37

36

PI

35

34

SC74

33

160P

2

30

32

31

25

24

23

21

29

27

49

SDEN

SDATA

SCLK

MEV

MEVO

MLPF

HOLD1

LCP

LCN

TPH

DFT

MIN

5.1V

RFVCC

SC554

+

SBC16

100u16

TP4

SBC19 0.1

2

20

21

23

24

25

27

0.1

9

11

12

13

15

19

SC27 0.1

SR29 5.1K

0.1

SBC10

0.047

SC18

SR21

SR23 1.6K

TP7

33

TP8

SC19

SC24

PLLVCC

SR4

SC7

1.2K

0.047

SC9 560P

0.1

SC14SC13

0.1

0.1

SC12 47P

SR6 SR5

10K 5.1K

SC11

TP3

STC1

SR7

+

220u16

100K

SR8

SC8

56K

0.1

STC2

TP1

TP2

161

5.1V

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

4.7K

SR10

XSVREFO

XSVR PLL

XSPDOFTR1

XSAWRCVCO

1

3.3V

TP10

TP11

TP12

TP20

TP13

TP9

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

AVSS DS

XSRFIN

XSIPIN

AVDD5 DS

XSDSSLV

XSRSLINT

VDD

XSAWRC

XSRFGC

XSEFGC

XSFOCUS

XSTRACK

XSSLEG

AVDD5 DA

XSMOTOR

AVSS DA

XSRFRPLP

XSTELP

XSVREF2

XSRFRP

XSTEXI

AVSS AD

XSTEI

XSFEI

XSCEI

AVDD5 AD

XSSBAD

GND

XSDFCT

XSCSJ

XSCLK

XSDATA

XSLDC

XSFGIN

XSSPDON

XSFLAG3

XSFLAG2

XSFLAG1

XSFLAG0

XMP1-7

XMP1-6

GND

XMP1-5

XMP1-4

SC15 1000P

SR12 20K

SR13

SC17

51K

6800P

TP5

SR15 3.3K

TP6

SR16 3.3K

SR17 3.3K

SR18 10K

470P

470P

SC21

0.0470.1

SC20

SC23 0.1

SR20 47K

SR19 0

SR24 0

SR26 0SR25 4.7K

SC25

SC26

1000P

1000P

SR27 0

29

30

31

32

33

34

35

TP14 TP15

40

41

44

XSFTROPI

XSFDO

AVSS PL

XSPLLFTR2

AVDD5 PL

XSFDIREF

GND

VDD 3.3

XTSLRF

XTPLCK

XSPDIREF

DVD/CD DATA DECODING

XRA3

SC83

0.1

SC81 33P

SR109 56K

SR110 10K

SR113

470K

0.47

SC84

SR111

XMP1-3

XMFSCSJ

XMP1-2

XGPIO2

XMP1-1

XHRSTJ

XGPIO1

XGPIO0

XCRSTJ

XMPSENJ

VDD 3.3

XMALE

XMP1-0

VDD 3.3

51

SR31

SR1

10

10K

TP19

TP17

52

TP16

535455

10

SR300

46

3.3V

54

45

4647484950

45

49

48

0

20

48

TP18

565758

57

SC28

59

12P

XOSC1

SR32 100K

33.8688MHz

SY1

SC30

60

12P

XOCS2

GND

61

62

XMD0

XMD1

636465

62

XMD2

XMD3

6667686970

6563666968

64

XMD4

XMD5

67

XMD6

XMD7

XMCSJ

XMRDJ

71

XMWRJ

XMINT1J

72

737475

72

SBC21 0.1

XMA11

XMA10

75

74

COMBO PCB (2/7)

23

Page 24

K L M N O

.

7

148

72

KDV-S210P/S220P

/S230P/S240P

148

147

XRA9

XMWRJ

XMINT1J

737475

72

SBC21 0.1

XROEJ

146

VDD 3.3

XMA11

74

145

143

144

143

142

XRCASJ

XRRASJ

XRSDCLK

XMA10

VDD 3.3

XMA9

XMA8

7677787980

3.3V

78

75

77

SRN14

XRWEJ

XMA7

79

18

16

17

15

141

140

141

140

139

XRD8

XRD7

XMA6

XMA5

XMA4

81

82

838485

81

808283

139

138

XRD6

XMA3

137

GND

XMA2

137

136

XRD9

XMA1

868788

136

135

135

134

XRD5

XRD10

XRD3

XRD12

XRD2

XRD13

XRD1

XRD14

XRD0

XRD15

XHD7

XHD8

XHD6

XHD9

XHD5

XHD10

XHD4

XHD11

VDD 3.3

XHD3

XHD12

XHD2

XHD13

XHD1

XHD14

XHD0

XHD15

XHDRQJ

XHIOWJ

XHIORJ

XHIORDYJ

XHDACKJ

XHINTJ

XHCS16J

XHPDIAGJ

XHA0

XHA2

XHCS1J

XHCS3J

XHDASPJ

XMA15

XMA14

XMA13

XMA0

XMA12

868485

87

134

133

XRD4

GND

GND

XHA1

GND

SBC20

0.1

SC553

100u16

133

XRD11

+

VCC

SDRAM

SU7

1

VCC

2

DQ0

125

3

DQ1

127

4

VSSQ

5

DQ2

129

6

DQ3

132

7

VCCQ

8

134

DQ4

9

136

DQ5

10

VSSQ

11

139

DQ6

12

141

DQ7

13

VCCQ

14

132

132

131

131

130

129

129

128

128

127

127

126

126

125

125

124

124

123

123

122

122

121

121

120

120

119

119

118

118

117

117

116

116

115

3.3V

114

114

113

113

112

112

111

111

110

109

109

108

108

107

107

106

106

105

105

104

104

103

103

102

102

101

101

100

100

99

99

98

98

97

97

96

96

95

95

94

94

93

93

92

92

91

91

90

90

89

89

3.3V

15

16

17

18

151

152

158

159

160

161

SBC18 0.1

SBC17 0.1

109

108

107

106

123

122

121

120

119

118

117

116

114

113

112

111

15

16

17

18

19

20

21

22

23

24

25

SBC8 0.1

SRN10

100

SRN11

100

SRN12

100

SRN13

100

LDQM

WE

CAS

RAS

CS

A11

A10

A0

A1

A2

A3

VCC

VSS

DQ15

DQ14

VSSQ

DQ13

DQ12

VCCQ

DQ11

DQ10

VSSQ

DQ9

DQ8

VCCQ

UDQM

CLK

CKE

VSS

R431 0

50

49

48

47

46

45

44

43

42

41

40

39

38

37

NC

36

35

34

33

NC

32

A9

31

A8

30

A7

29

A6

28

A5

27

A4

26

SRN9

10K

133

128

132

131

SRN6

10K

141

122

140

123

SRN7

10K

137

124

136

125

SRN8

10K

135

126

134

127

3.3V

3.3V

124

126

128

131

133

135

137

140

143

SR117

0

SR73

2.2K

148

149

153

155

156

157

57

91

87

5

79

A7

6

80

A6

7

81

A5

8

82

A4

9

83

A3

10

84

A2

11

85

A1

12

86

A0

13

62

DQ0

0.1

SBC3

105

104

103

102

SC1

10P

SC2

100

98

96

95 158

10P

10P

SC6

SC5

SC4

SR118

SR121 0

432

1

A12

A15

A16

U34

FLASH MEMORY

128kx8

DQ1

DQ2

GND

15

1617181920

14

63

64

0.1

SBC4

92

SRN1

10K

SRN3

33

SRN5

10P

47

10P

10K

NC

SBC5

DQ3

65

101

94

93

0.1

323130

VDD

DQ4

DQ5

0.1

SBC6

10P

SC3

97

SVCC

RESETVCC

5.1V

72

NC

WE

29

90

A14

28

89

A13

27

78

A8

26

77

A9

25

74

A11

24

54

OE

23

75

A10

22

46

CE

21

SRN4

33

R423

10K

15199

152

153

SRN2

10K

149

150

146

144

155

154

69

DQ7

DQ6

686766

FB2

D22 D21

FB1

2.7uH

3.3V

2.6V

3.3V

2.6V

3.3V

VCC

2.7uH

C252 470P

2.6V

L19

2.7uH

C251 470P

B11 0.1

0.1

B6

R322 75

C247 0

R296 2

B12

10u25

122

123

124

125

126

127

128

131

132

133

134

135

136

137

140

141

144

146

149

150

151

152

153

154

155

158

B15

B59

B24

+

0.1

0.1

0.1

C246 0.1

COMBO PCB (3/7)

24

5.1V

Page 25

TSRQP

6V

Q

0

0

2

6

6

7

B6

KDV-S210P/S220P

/S230P/S240P

BC601

1000P

1000P

BC602

BC600

R322 75

C247 0.1

R296 270

B12

10u25

122

123

124

125

126

127

128

B15

131

132

133

134

135

136

137

0.1

B59

140

141

144

146

B24

149

150

151

152

153

154

155

158

3.3V

B22

104

VC33

105

CLK

106

YUVO/CAMYUV2

107

YUV1/VREF

C246 0.1

108

YUV2/CDAC

109

YUV3/COMP

110

YUV4/RSET

111

AVCC(VDAC)

+

112

AVSS(VDAC)

113

YUV5/YDAC

114

YUV6/VDAC

115

YUV7 CAMYUV3

116

PCLK2 XSCN/CAMYUV4

117

PCLK QSCN/CAMYUV5/AUX3(2)

118

VSSCN/CAMYUV6/EAUX3(1)

119

HSSCN/CAMYUV7/EAUX3(0)

120

VSS

121

VC25

122

HD0/DCI(0)/EAUX1(0)

123

HD1/DCI(1)/EAUX1(1)

124

HD2/DCI(2)/EAUX1(2)

125

HD3/DCI(3)/EAUX1(3)

126

HD4/DCI(4)/EAUX1(4)

127

HD5/DCI(5)/EAUX1(5)

128

HD6/DCI(6)/EAUX1(6)

129

VSS

0.1

130

VC33

131

HD7/DCI(7)/EAUX1(7)

132

HD8/DCI FDS/EAUX2(0)

133

HD9/EAUX2(1)

134

HD10/EAUX2(2)

135

HD11/EAUX2(3)

136

HD12/EAUX2(4)

137

HD13/EAUX2(5)

138

VSS

0.1

139

VC25

140

HD14/EAUX2(6)

141

HD15/EAUX2(7)

142

HWRQ/DCI REQ/EAUX4(1)

143

HRDQ/EAUX4(0)

144

HIRQ/DCI ERR/EAUX4(7)

145

HRST/EAUX3(5)

146

HIORDY/EAUX3(3)

147

VSS

0.1

148

VC33

149

HWR/DCI CLK/EAUX4(5)

150

HRD/DCI ACK/EAUX4(6)

151

HIOCS16/CAMPCLK/EAUX3(4)

152

HCS1FX/EAUX3(7)

153

HCS3FX/EAUX3(6)

154

HA0/EAUX4(2)

155

HA1/EAUX4(3)

156

VSS

B27 0.1

B18 0.1

71

72

73

69

RN11

33 10

69

DWE

DCAS

DRAS0

DSCK/DOE

DBANK0/DRAS1

B16

0.1

VSS

74

3.3V

R313 0

VC33

DBANK1/DRAS2

101

102

100

DB8

868788

DB7

85

DB6

VSS

2.6V

VC25

82

DB5

81

DB4

80

DB3

79

DB2

78

DB1

77

DB0

0

L501

R32 33

R292 33

33

R19

103

102

101

100999897969594939291908988878685848382818079787776757473727170

VSS

DQM

DSCK

DCS0

VC33

VSS

DCS1

96

DB15

959493

DB13

DB14

DB12

B280.1

0.1

VC33

VSS

90

DB11

89

DB10

DB9

U1

DVD MPEG DECODING PROSESSOR

VC33

HA2/EAUX4(4)

VC33

AUX0

AUX1

AUX2

VSS

VC33

AUX3

AUX4

AUX5

AUX6

AUX7

LOE

VSS

VC25

LCS0

LCS1

LCS2

LCS3

VSS

LD0

LD1

LD2

LD3

LD4

VC33

VSS

LD5

LD6

LD7

LD8

LD9

LD10

161

158

159

157

162

160

SDA

163

165

166

164

167

B25

0.1

162

165

SCL

SDA

SCL

166

171

168

169

168

172

170

173

175

176

174

B7

0.1

2.6V

170

169

176

181

182

178

179

180

183

185

186

188

189

177

178

179

180

184

B23

181

182

185

190

187

188

189

190

186

187

2.6V

L19

2.7uH

C251 470P

B11 0.1

1000P

1000P

1000P

0.1

VC33

193

VC33

194

BC604

VSS

LD12

195

194

LD13

196

195

1000P

BC605

656663

DMA11

DMA10

LD14

197

196

BC606

64

DMA9

LD15

R600

BC603

70

R295 33

6867666564636261605958

LD11

VSS

191

192

191

1000P

RN10

DMA8

LWRLL

198

0

198

BC607

LWRHL

199

1000P

62

DMA7

VSS

200

10u25

B21 0.10.1

1000P

BC608

61

DMA6

B32

+

RN9

10

VSS

1000P

BC609

VC33

VC33

201

3.3V

BC610

58

57

57

DAM5

DAM4

CAMYUV0

CAMYUV1

202

203

1000P

B29B17

LA0

204

204

0.1

BC611

1000P

BC612

3.3V

565554

SPDIF/SEL PLL3

TSD1/SEL PLL1

TSD0/SEL PLL0

TWS/SEL PLL2

TDMDX/RSEL

LA1

LA2

205

206

207

205

206

1000P

555653

DMA2

DAM3

AVSS(PLL)

AVCC(PLL)

NC/APLL

NC/CAMVS

TDMTSC

TDMCLK

LA3

VSS

208

207

1000P

BC613

54

53

DAM1

X OUT

X IN

RBCK

RWS

RSD

VC25

VSS

TBCK

MCLK

TSD3

TSD2

VC25

VSS

TDMFS

TDMDR

VC33

VSS

RESET

LA21

LA20

LA19

LA18

LA17

VC33

VSS

LA16

LA15

LA14

LA13

LA12

LA11

LA10

VC25

VSS

LA9

LA8

LA7

LA6

LA5

LA4

VC33

BC650

RN8

DMA0

B19 0.1

1000P

10

B10

10u25

1000P

BC655

2.

52

51

L5

50

0

49

48

R304

47

L5

46

0

45

44

43

42

4.7K

R299

41

40

R5

39

38

33

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

R2

21

R3

20

R3

19

18

17

R40

16

15

14

13

12

11

10

9

B9

8

7

6

5

4

3

2

1

+

2.

3.3V

COMBO PCB (4/7)

25

Page 26

U V W X Y

T

T

K

)

5

503

4

BCT

KDV-S210P/S220P

/S230P/S240P

BC650

RN8

LL)

LL)

UT

IN

LL

CK

S

SD

25

SS

VS

L3

CK

LK

D3

D2

LL1

25

SS

L0

L2

SC

FS

LK

DR

33

SS

EL

ET

21

20

19

18

17

33

SS

16

15

14

13

12

11

10

25

SS

A9

A8

A7

A6

A5

A4

33

B19 0.1

1000P

10

B10

10u25

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

+

1000P

BC655

2.6V

L502

0

L503

0

R299

R52

33

R26 4.7K

R36 4.7K

R37 4.7K

R40

B9

2.6V

R304

4.7K

Q1

100K

L500

2.7uH

33

19

4.7K

16

15

14

13

12

10

0.1

R9

0

B8

32

B26

21

20

11

7

6

5

4

3

2

C248

27P

Y1

C249

27P

2.6V

40

39

R3

4.7K

0.1

R1 4.7K

R6 4.7K

3.3V

0.1

R7 4.7K

27MHz

2.6V

B20

0.1

2.6V

3.3V

B30

+

100u16

2200P

R46 33

0.1

C266

B4

220u16

RT20 33

3.3V

3.3V5.1V

+

R524

+

0

B501

C216

7.0V

0.1

UT1 :

3

R172

BUFF

2200P

FB504

B500+B

U27

(2/6

47K

FB

220u16

5.1

:UT2

0.1

SC50

STC11

100u16

39

SDA

SCL

168

+

C267

10u16

FB501

+

FB500

B1

220u16

QT1 :

RT9 22K

UT1

RT6

5

10K

10K

RT7

2

4

3

RT5

CT1

RT1

4.7K

0.01

22

5

4

2

VCC

VCC33

RESETVCC