Page 1

SERVICE MANUAL

CD RECEIVER

4979320034

KD-LX555R

S

STDM

SOURCE

9

7

8

KD-LX555R

0

1

12

11

Area Suffix

E ------ Continental Europe

TABLE OF CONTENTS

1 Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Disassembly method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3 Adjustment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4 Description of major ICs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

COPYRIGHT © 2003 VICTOR COMPANY OF JAPAN, LTD.

No.49793

2003/5

Page 2

SECTION 4

Description of major ICs

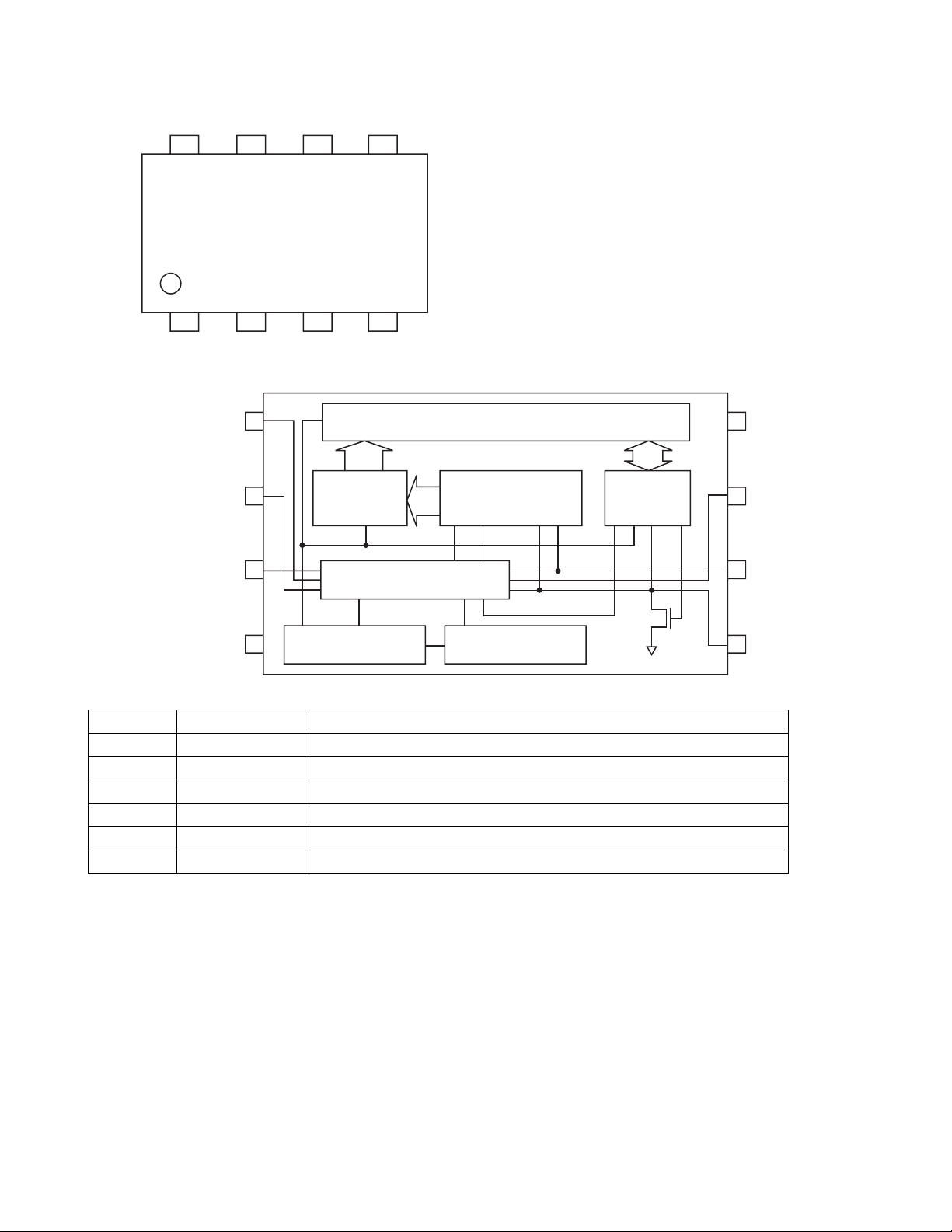

4.1 BA6956AN (IC830, IC831) : Reversible motor driver

• Block diagram

TSD

CONTROL LOGIC

1 2 3 4 5 6 7 8 9

REF

OUT2

RNF

VM

OUT1

Vcc

FIN

GND

RIN

• Pin function • Truth table

Pin No. Symbol Function

1 VREF Output high voltage level control terminal

2 OUT2 Output terminal for motor

3 RNF GND of driver division

4 OUT1 Output terminal for motor

FIN RIN OUT1 OUT2 MODE

H L H L Forward rotation mode

L H L H Reverse rotation mode

H H L L Break Mode

L L OPEN OPEN Stand-by mode

5 VM Power supply for driver division

6 Vcc Power supply for signal division

7 FIN Input terminal for control logic

8GNDGND

9 RIN Input terminal for control logic

1-32 (No.49793)

Page 3

4.2 BR24C01AFV-W-X (IC1502) : EEPROM

A

•Pin layout

Vcc WP SCL SDA

A0 A1 A2 GND

• Block diagram

A0

1

7bit

A1

2

A2

3

GND

• Pin function

Pin name I/O Description

Vcc - Power supply

GND - Ground (0v)

A0,A1,A2 IN Slave address set

SCL IN Serial clock input

SDA IN / OUT Slave and word addressserial data input serial data output *1

WP IN Write protect input

*1 An open drain output requires a pull-up resister.

4

ADDRESS

DECODER

CONTROL LOGIC

HIGH VOLTAGE GEN.

1kbit EEPROM ARRAY

SLAVE/WORD

7bit

ADDRESS REGISTER

START

STOP

Vcc LEVEL DETECT

ACK

8bit

DATA

REGISTER

Vcc

8

7

WP

6

SCL

5

SD

(No.49793)1-33

Page 4

4.3 BR24C32F (IC703) : EEPROM

A

• Pin Layout

VCC

BR24C32/F

• Pin function

SDASCLWP

• Pin layout & Block diagram

PIN NAME I/O Function

VCC - Power Supply

GND - Ground (0V)

A0-A2 I Slave Address Set

SCL I Serial Clock Input

SDA I/O Slave and Word Address.

Serial Data Input$ Serial Data Output *1

WP I Write Protect Input

GNDA2A1A0

1

A0

12bit

2

A1

3

A2

4

GND

4.4 HD74HC126FP (IC771) : Changer Control

OE1

A1

Y1

1

2

3

ADDRESS

DECODER

CONTROL LOGIC

HIGH VOLTAGE GEN.

14

13

12

32 Kbit EEPROM ARRAY

SLAVE WORD

12bit

ADDRESS REGISTER

START STOP

VCC LEVEL DETECT

Vcc

OE4

A4

DATA

REGISTER

ACK

8bit

8

7

6

5

Vcc

WP

SCL

SD

OE2

A2

Y2

Vss

1-34 (No.49793)

4

5

6

7

HD74HC126

11

10

9

8

Y4

OE3

A3

Y3

Page 5

4.5 BU1923F (IC51) : RDS decoder

A

•Pin layout

1

QUAL

RDATA

Vref

MUX

VDD1

VSS1

VSS3

CMP

2

3

4

5

6

7

8

16

15

14

13

12

11

10

• Block diagram

9

RCLK

N.C.

XO

XI

VDD2

VSS2

T1

T2

MUX

Vref

VDD1

VSS1

VDD2

VSS2

4

3

5

Power supply

6

12

Power supply

11

100k

120k

Analog

Digital

100k

+

anti-aliasing

filter

PLL

57kHz

RDS/ARI

Reference

clock

PLL

1187.5Hz

VSS3

8th Switched

capacitor filter

Bi-phase

decoder

7

CMP

Measurement

circuit

8

comparator

Differential

decoder

16

1

2

RCLK

QUAL

RDAT

13

Xl

14

X0

10 9

T1

T2

(No.49793)1-35

Page 6

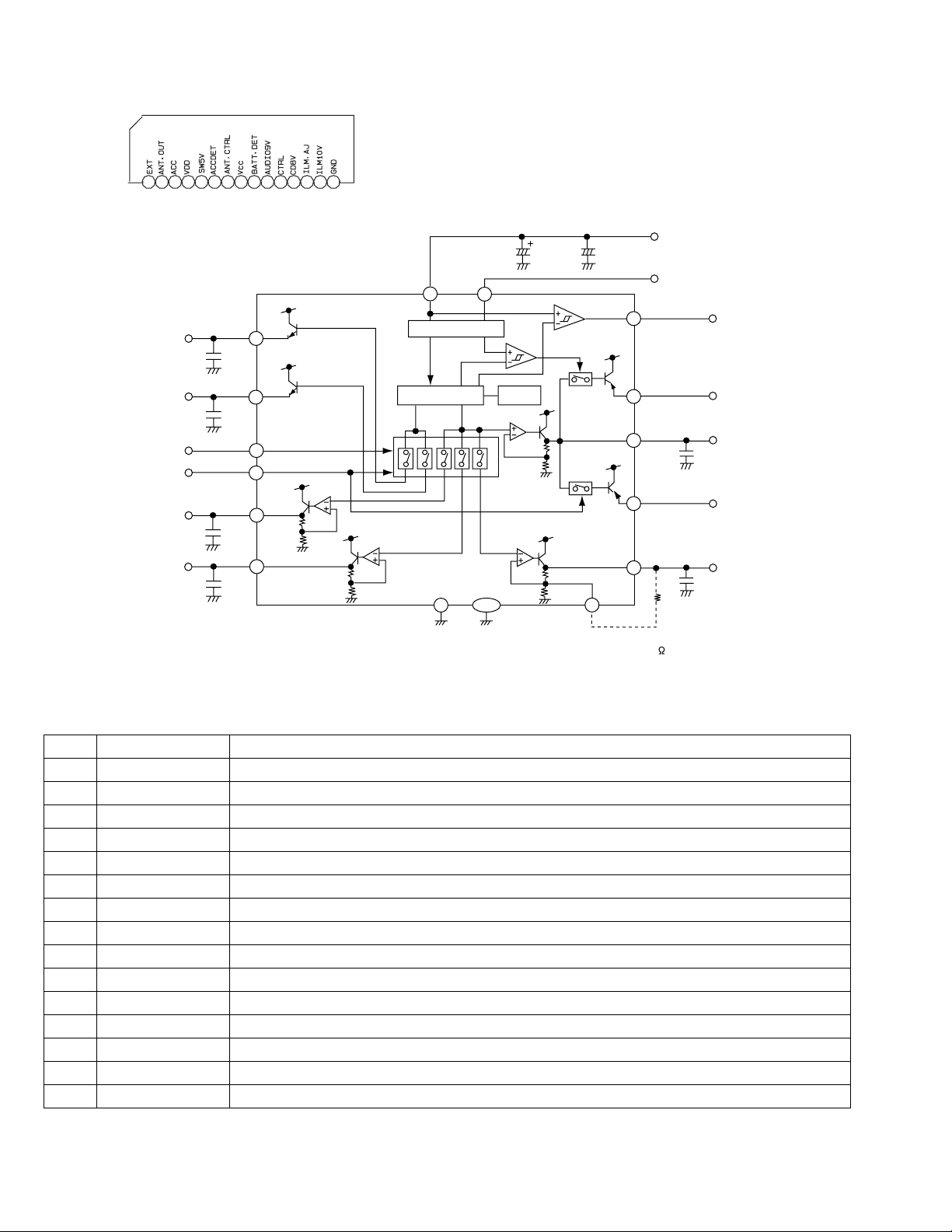

4.6 HA13164A (IC961) : Regulator

• Terminal layout

123456789101112131415

• Block diagram

ANT OUT

EXT OUT

ANT CTRL

CTRL

CD OUT

AUDIO OUT

C3

0.1u

C4

0.1u

C5

0.1u

C6

10u

2

1

7

11

12

10

VCC ACC

8

Surge Protector

BIAS TSD

15

3

TAB

C1

100u

C2

0.1u

13

ILM AJGND GND

+B

ACC

BATT.DET OUT

9

COMPOUT

6

VDD OUT

4

SW5VOUT

5

ILMOUT

14

R1

C7

0.1u

C8

0.1u

UNIT R:

C:F

note1) TAB (header of IC)

connected to GND

• Pin function

Pin No. Symbol Function

1 EXTOUT Output voltage is VCC-1 V when M or H level applied to CTRL pin.

2 ANTOUT Output voltage is VCC-1 V when M or H level to CTRL pin and H level to ANT-CTRL.

3 ACCIN Connected to ACC.

4 VDDOUT Regular 5.7V.

5 SW5VOUT Output voltage is 5V when M or H level applied to CTRL pin.

6 COMPOUT Output for ACC detector.

7 ANT CTRL L:ANT output OFF H:ANT output ON

8 VCC Connected to VCC.

9 BATT DET Low battery detect.

10 AUDIO OUT Output voltage is 9V when M or H level applied to CTRL pin.

11 CTRL L:BIAS OFF M:BIAS ON H:CD ON

12 CD OUT Output voltage is 8V when H level applied to CTRL pin.

13 ILM AJ Adjustment pin for ILM output voltage.

14 ILM OUT Output voltage is 10V when M or H level applied to CTRL pin.

15 GND Connected to GND.

1-36 (No.49793)

Page 7

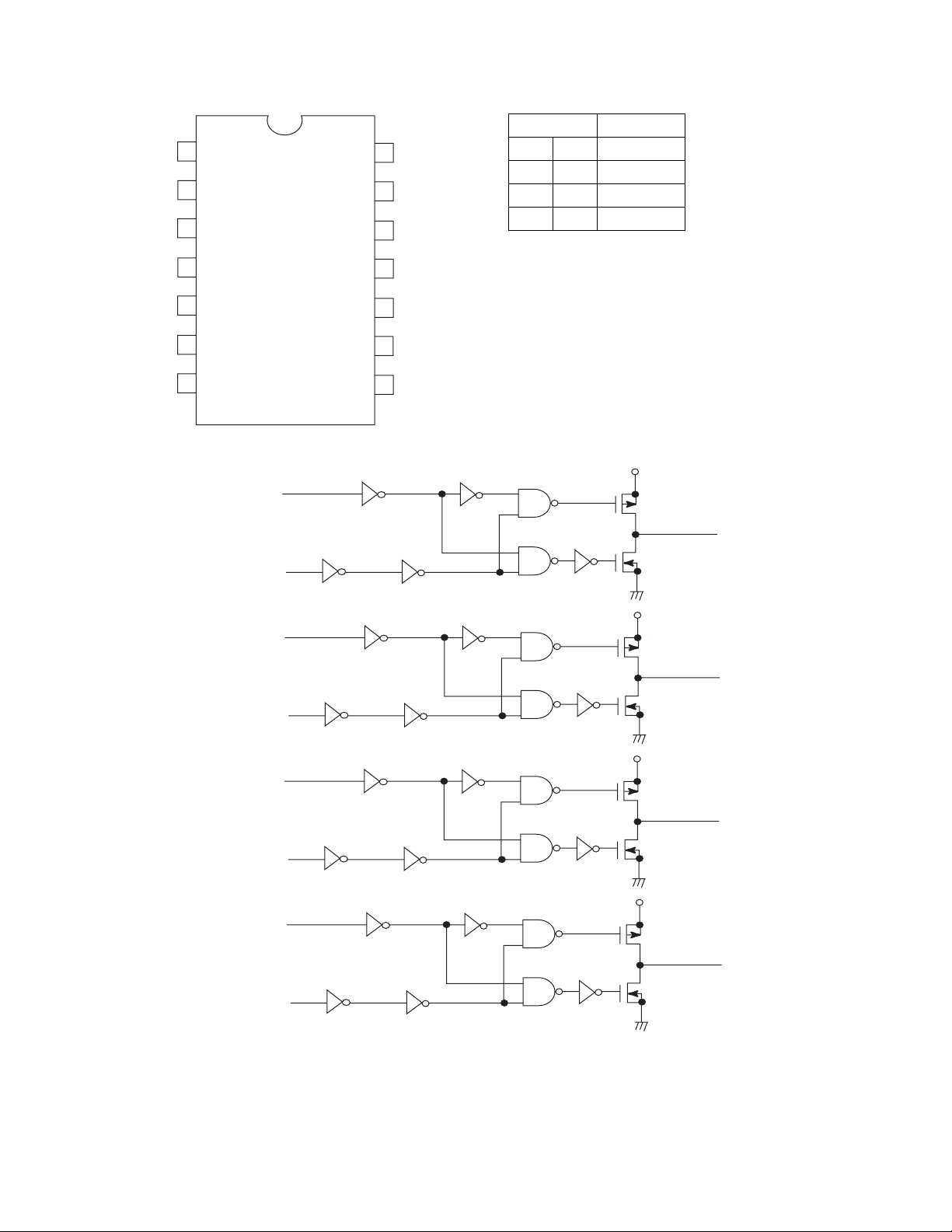

4.7 HD74HCT126T-X : (IC1500,IC1503) Buffer

• Pin arrangement • Pin function

Input Output

1C

1A

1Y

2C

2A

2Y

GND

• Block diagram

1

2

3

4

5

6

7

14

13

12

11

10

Vcc

4C

4A

4Y

3C

9

3A

8

3Y

CA Y

LX Z

HL L

HH H

H : High level

L : Low level

X : Irrelevant

Z : Off (Hhigh-impedance)state of a 3-stage output

1A

1C

2A

2C

3A

3C

4A

1Y

2Y

3Y

4Y

4C

(No.49793)1-37

Page 8

4.8 LA47505 (IC941) : Power amp.

• Terminal layout

206

11

1

12

4

10

Stand by

Switch

Ripple

Filter

Protective

circuit

Mute

circuit

9

7

8

5

3

2

22

15

25

13

14

16

Muting &

On Time Control

Circuit

protective

circuit

17

19

18

21

23

24

1-38 (No.49793)

Page 9

• Terminal layout

AC CONT1

GND1

OUTFR-

STBY

OUTFR+

Vcc1/2

OUTRR-

GND2

OUTRR+

VREF

INRR

INFR

SGND

INFL

INRL

ONTIME

OUTRL+

GND3

OUTRL-

Vcc3/4

OUTFL+

MUTE

OUTFL-

GND4

NC

• Pin function

Pin No. Symbol Function

1 AC CONT1 Header of IC

2 GND1 Power GND

3 OUTFR- Outpur(-) for front Rch

4 STBY Stand by input

5 OUTFR+ Output (+) for front Rch

6 Vcc1/2 Power input

7 OUTRR- Output (-) for rear Rch

8 GND2 Power GND

9 OUTRR+ Output (+) for rear Rch

10 VREF Ripple filter

11 INRR Rear Rch input

12 INFR Front Rch input

13 SGND Signal GND

14 INFL Front Lch input

15 INRL Rear Lch input

16 ONTIME Power on time control

17 OUTRL+ Output (+) for rear Lch

18 GND3 Power GND

19 OUTRL- Output (-) for rear Lch

20 Vcc3/4 Power input

21 OUTFL+ Output (+) for front

22 MUTE Muting control input

23 OUTFL- Output (-) for front

24 GND4 Power GND

25 NC No connection

(No.49793)1-39

Page 10

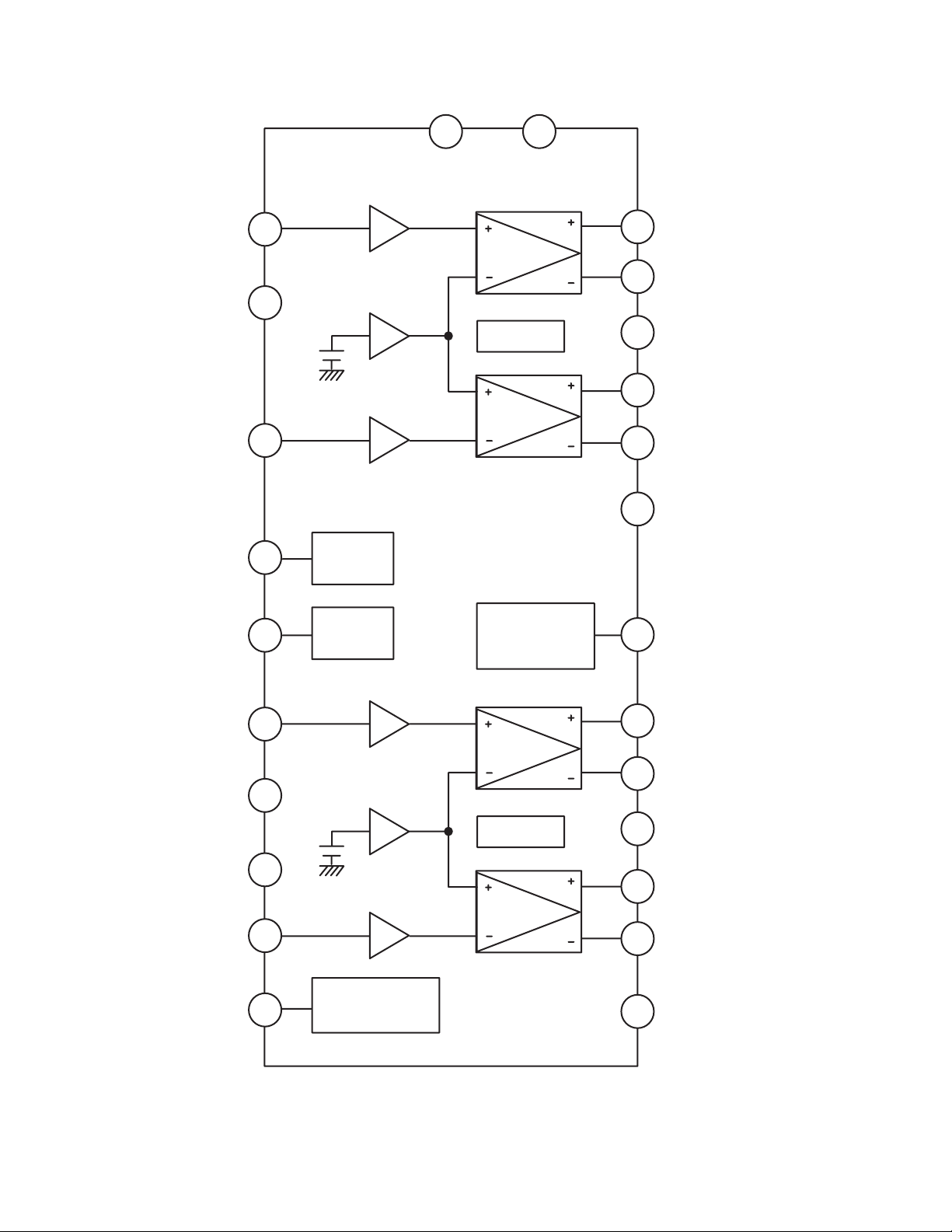

4.9 LA6579H-X (IC1681) : 4-Channel bridge driver

W

• Pin layout & Block diagram

VIN1-A

1

+

VIN1+A

VCCP1

2

3

VIN1_SW

[H]: OP-AMP_A

[L]: OP-AMP_B

[H]

[L]

28

VIN1

27

VIN1-B

-

+

26

VIN1+B

VO+

VO-

VO2+

VO2-

FR

VO3+

VO3-

VO4+

4

5

6

7

FR

8

9

10

Power system

GND

+

Level shift

Level shift

Level shift

Level shift

33k

11k

-

+

All outputs ON/OFF

H : ON

L : OFF

3.3VREG

(External:PTP Tr)

Signal system

power supply

MUTE

Power system GND

Signal system

power supply

+

-

25

24

23

22

FR

21

20

19

S-GND

VIN1-S

MUTE

VREFIN

FR

VCCS

3.3VREG

REGIN

VO4-

VCCP2

VIN4

VIN4G

1-40 (No.49793)

11

12

13

14

11k

33k

+

33k

33k

18

VIN2G

11k

-

17

VIN2

+

16

VIN3G

11k

-

15

VIN3

+

Page 11

• Pin function

Pin No. Symbol Function

1 VIN1-A CH1 input AMP_inverted input

2 VIN1+A CH1 input AMP_non-inverted input

3 VCCP1 CH1 and CH2 power stage power supply

4 VO1+ Output pin(+)for channel 1

5 VO1- CH1 output pin (-) for channel 1

6 VO2+ Output pin(+)for channel 2

7 VO2- Output pin(-)for channel 2

8 VO3+ Output pin(+)for channel 3

9 VO3- Output pin(-)for channel 3

10 VO4+ Output pin(+)for channel 4

11 VO4- Output pin(-)for channel 4

12 VCCP2 CH3 and CH4 power stage powr supply

13 VIN4 Input pin for channel 4

14 VIN4G Input pin for channel 4(for gain adjustment)

15 VIN3 Input pin for channel 3

16 VIN3G Input pin for channel 3(for gain adjustment)

17 VIN2 Input pin for channel 2

18 VIN2G Input pin for channel 2(for gain adjustment)

19 REGIN External PNP transistor base connection

20 3.3VREG 3.3VREG output pin external PNP transistor,collector connection

21 VCCS Signal system GND

22 VREFIN Reference voltage application pin

23 MUTE Output ON/OFF pin

24 VIN1_SW CH1 input OP AMP_changeover pin

25 S_GND Signal system GND

26 VIN1+B CH1 AMP_B non-inverted input pin

27 VIN1-B CH1 AMP_B inverted input pin

28 VIN1 CH1 input pin input OP_AMP output pin

(No.49793)1-41

Page 12

4.10 M61508FP (IC400) : E.volume

• Pin layout & Block diagram

VDD OUT 2

CLOCK

VDD

NonFadaer OUT 2

FRONT OUT 2

REAR OUT2

FADER IN 2

TONE OUT 2

VOL IN 2

SEL OUT 2

19

20

21

22

23

24

25

26

LOUDNESS

+

3BAND TONE

CONTROL

(BASS/MID/

TREBLE)

27

28

SOFT

SELECT

NON FADER

VOLUME

+ -

VOLUME 2

A

B

ZERO

CROSS

DETECTOR

VOLUME 1

I/F

TIMER

DETECTOR

NON FADER

VOLUME

A

B

ZERO DETECT

SELECT SWITCH

ZERO

CROSS

DETECTOR

GNDVDD

- +

LOUDNESS

+

3BAND TONE

CONTROL

(BASS/MID/

TREBLE)

18 VDD OUT 1

17

DATA

GND

16

15

NonFadaer OUT 1

FRONT OUT 1

14

REAR OUT1

13

FADER IN 1

12

11

TONE OUT 1

10

VOL IN 1

9

SEL OUT 1

1-42 (No.49793)

DEFN OUT 2

IND 2

INC 2

INB 2

INA 2

DEFN IN 2

DEFP IN 2

AVDD

29

30

31

32

33

34

35

36

50K

50K

50K

50K

+

VCC

+ -

51K

51K

- +

25.5K

REF

25.5K

+ -

30K 30K

+ -

- +

25.5K25.5K

51K

51K

-

+

50K

50K

50K

50K

8

DEFN OUT 1

IND 1

7

INC 1

6

5

INB 1

4

INA 1

3

DEFN IN 1

DEFP IN 1

2

1

REF

Page 13

• Pin function

Pin No. Symbol Function

1 REF IC signal GND

2 DEFP IN 1 Ope amp positive input

3 DEFN IN 1 Ope amp negative input

4 INA 1 Input selector ch1 input terminal

5 INB 1 Input selector ch1 input terminal

6 INC 1 Input selector ch1 input terminal

7 IND 1 Input selector ch1 input terminal

8 DEFN OUT 1 Operation outoutterminal (-)

9 SEL OUT 1 Input selector output terminal

10 VOL IN 1 Volume 1 input terminal

11 TONE OUT 1 Tone output terminal

12 FADER IN 1 Volume 2 input terminal

13 REAR OUT1 Fader volume (rear) output terminal

14 FRONT OUT 1 Fader volume (front) output terminal

15 NonFadaer OUT 1 Non fader volume output terminal

16 GND GND

17 DATA Control data input terminal

18 VDDOUT 1 Connect to GND with capacitor

19 VDDOUT 2 Connect to GND with capacitor

20 CLOCK Serial data clock input terminal

21 VDD VDD for digital

22 NonFadaer OUT 2 Non fader volume output terminal

23 FRONT OUT 2 Fader volume (front) output terminal

24 REAR OUT2 Fader volume (rear) output terminal

25 FADER IN 2 Volume 2 input terminal

26 TONE OUT 2 Tone output terminal

27 VOL IN 2 Volume 1 input terminal

28 SEL OUT 2 Input selector output terminal

29 DEFN OUT 2 Ope amp output terminal (-)

30 IND 2 Input selector switch ch2 input terminal

31 INC 2 Input selector switch ch2 input terminal

32 INB 2 Input selector switch ch2 input terminal

33 INA 2 Input selector switch ch2 input terminal

34 DEFN IN 2 Ope amp negative input terminal

35 IEFP IN 2 Ope amp positive input terminal

36 VCC VCC for analog

(No.49793)1-43

Page 14

4.11 LC75878W (IC601) : LCD driver

• Pin layout

100 ~ 76

1

75

• Block diagram

~

25

OSC

VLCD

VLCD0

VLCD1

VLCD2

VLCD3

VLCD4

VDD

VSS

26 ~ 50

P1

GENERAL

GENERATOR

CONTRAST

ADJUSTER

PORT

CLOCK

~

51

P4

COM1

COMMON

DRIVER

COM8

S75/COM9

S74/COM10

S73

SEGMENT DRIVER & LATCH

CONTROL

REGISTER

SHIFT REGISTER

CCB

INTERFACE

S1

DI

CL

• Pin function

INH

No. Symbol I/O Function

1~73 SEG1~SEG73 O Segment driver output pin.

74 SEG74 O Segment driver output pin.

75 SEG75 O Segment driver output pin.

76~83 COM8~COM1 O Common driver output pin.

84~87 P1~P4 O General-purpose output pin.

88 VDD - Logic block power supply pin.

89 VLCD - LCD driver power supply pin.

90 VLCD0 O LCD driver bias 4/4 voltage (H-level) power pin.

91 VLCD1 I LCD driver bias 3/4 voltage (intermediate level) power pin.

92 VLCD2 I LCD driver bias 2/4 voltage (intermediate level) power pin.

93 VLCD3 I LCD driver bias 1/4 voltage (intermediate level) power pin.

94 VLCD4 I LCD driver bias 0/4 voltage (L-level) power pin.

95 VSS - Power supply pin to connect to ground.

96 OSC I/O Oscillator pin.

97 LCD RESET I Display off general-purpose output port "L" fixed input pin.

98 CE I Chip enable

99 CL I Synchronization clock

100 DI I Transfer data

CE

1-44 (No.49793)

Page 15

4.12 NJM4565V-X (IC1572) : Dual ope amp

• Terminal layout & Pin function

1

8

A

2

+

-

7

B

3

+

-

4

4.13 NJU7241F25 (IC1651) : Regulator

• Pin Layout • Block Diagram

6

5

1

AOUTPUT

2

A-INPUT

3

A+INPUT

4

V

5

B+INPUT

6

B-INPUT

7

B OUTPUT

8

V

GND 1

VIN 2

VOUT 3

4.14 NJU7241F33 (IC1504) : Voltage regulator

PIN FUNCTION

1

2

3

5

4

1. GND

IN

2. V

3. VOUT

4. NC

5. STB

5 STB

4 NC

VIN 2

STB 5

GND 1

Short protect

3 VOUT

Vref

1 GND

(No.49793)1-45

Page 16

4.15 TA2157FN-X (IC1601):RF amp

• Terminal layout

24 ~ 13

1 ~ 12

• Block diagram

13

14

15

16

17

18

19

20

21

10pF

40k30k

20k 20k

20k

20k

15k

50 A

12k

12k

BOTTOM

PEAK

20k

20k

20k

PEAK

1.3V

40k

240k

15pF

240k

15pF

40k

50k

2k

20k

50k

14k

K

1

15k

x0.5

x2

x0.5

x2

1k

2k

1.75k

10pF

12

11

10

9

8

7

6

5

4

PIN

VCTRLPIN

1-46 (No.49793)

180k

40pF

22

23

24

SEL

(APC SW)

180k

40pF

3k

3k

TEB

(TE BAL)

60k

60k

(AGC Gian)

94k

RFGC

VCC APC ON -50% +12dB

HiZ APC ON 0% +6dB

GND

APC OFF

(LDO=H)

50% 0dB

94k

22k

22k

3

2

1

TEB

(TE BAL)

Normal mode

(0dB)

Normal mode

(0dB)

CD-RW mode

(+12dB)

Page 17

• Pin function

Pin No. Symbol I/O Function

1 VCC - 3.3V power supply pin

2 FNI I Main-beam amp input pin

3 FPI I Main-beam amp input pin

4 TPI I Sub-beam amp input pin

5 TNI I Sub-beam amp input pin

6 MDI I Monitor photo diode amp input pin

7 LDO O Laser diode amp output pin

8 SEL I APC circuit ON/OFF control signal, laser diode (LDO) control signal input

or bottom/peak detection frequency change pin.

SEL

GND

Hiz

VCC

9 TEB I Tracking error balance adjustment signal input pin

Adjusts TE signal balance by eliminating carrier component from PWM signal (3-state output,

PWM carrier = 88.2kHz) output from TC94A14F/FA

TEBC pin using RC-LPF and inputting DC.

TEBC input voltage:GND~VCC

10 TEN I Tracking error signal generation amp negative-phase input pin

11 TEO O Tracking error signal generation amp output pin.

Combining TEO signal RFRP signal with TC94A14F/FA configures tracking search system.

12 RFDC O RF signal peak detection output pin

13 GVSW I AGC/FE/TE amp gain change pin

APC

circuit

LDO

OFF Connected VCC through 1k resistor

ON

Control signal output

ON Control signal output

GVSW Mode

GND

Hiz

CD-RW

Normal

VCC

14 VRO O Reference voltage (VRO) output pin

*VRO=1/2VCC When VCC=3.3V

15 FEO O Focus error signal generation amp output pin

16 FEN I Focus error signal generation amp negative-phase input pin

17 RFRP O Signal amp output pin for track count

Combining RFRP signal and TEO signal with TC94A14F/FA configures tracking search system.

18

19

20

21 AGCIN I RF signal amplitude adjustment amp input pin

22 RFO O RF signal generation amp output pin

23 RFI I RF signal generation amp input pin

24 GND - GND pin

REIS

RFGO

RFGC

I

OIRF signal amplitude adjustment amp output pin

RF amplitude adjustment control signal input pin

Adjusts RF signal amplitude by eliminating carrier component from PWM signal (3-state output,

PWM carrier=88.2kHz)output fromTC94A14F/14FA *RFGC pin using RC-LPF and inputting DC.

*RFGC input voltage:GND~VCC

(No.49793)1-47

Page 18

4.16 TC94A14FA (IC1621) : DSP & DAC

• Terminal layout & block daiagram

48 47 46 45 44 43 42 41 40 39

38 37 36 35 34 33

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

LPF

generator

Microcontroller

interface

Clock

1-bit

DAC

Audio out

Correction

circuit

circuit

Address

circuit

16 k

RAM

Digital

output

PWM

Servo

control

ROM

RAM

CLV servo

Synchronous

guarantee

EFM

decoder

Sub code

decoder

Digital equalizer

automatic

adjustment circuit

A/D

Data

slicer

VCO

PLL

TMAX

D/A

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

64

17

161514131211101 2 3 4 5 6 7 8 9

• Pin function

Pin

Symbol I/O Descroption

No

1 BCK O Bit clock output pin.32fs48fsor 64fs selectable by command.

2 LRCK O L/R channel clock output pin."L" for L channel and "H" for R channel.

Output polarity can be inverted by command.

3 AOUT O Audio data output pin. MSB-first or LSB-first selectable by command.

4 DOUT O Digital data output pin.Outputs up to double-speed playback.

5 IPF O Correction flag output pin. When set to "H" AOUT output cannot be corrected by C2 correction processing.

6V

DD3

7V

SS3

- Digital 3.3V power supply voltage pin.

- Digital GND pin.

8 SBOK O Subcode Q data CRCC result output pin. "H" level when result is OK.

9 CLCK O Subcode P-W data read I/O pin. I/O polarity selectable by command.

10 DATA O Subcode P-W data output pin.

11 SFSY O Playback frame sync signal output pin.

12 SBSY O Subcode block sync signal output pin. "H" level at S1 when subcode sync is detected.

13 HSO

14 UHSO

15 PV

I/O General-purpose input / output pins.Input port at reset.

- PLL-only 3.3V power supply voltage pin.

DD3

16 PDO O EFM and PLCK phase difference signal output pin.

1-48 (No.49793)

Page 19

Pin

Symbol I/O Descroption

No

17 TMAX O TMAX detection result output pin.

TMAX Detection Result

Longer than fixed period

Within fixed period

Shorter than fixed period

TMAX Output

DD3"

"PV

"HiZ"

"AV

SS3"

18 LPFN I Inverted input pin for PLL LPF amp.

19 LPFO O Output pin for PLL LPF amp.

20 PVREF - PLL-only VREF pin.

21 VCOF O VCO filter pin.

22 AV

- Analog GND pin.

SS3

23 SLCO O DAC output pin for data slice level generation.

24 RFI I RF signal input pin. Zin selectable by command.

25 AV

- Analog 3.3V power supply voltage pin.

DD3

26 RFCT I RFRP signal center level input pin.

27 RFZI I RFRP signal zero-cross input pin.

28 RFRP I RF ripple signal input pin.

29 FEI I Focus error signal input pin.

30 SBAD I Sub-beam adder signal input pin.

31 TEI I Tracking error input pin. Inputs when tracking servo is on.

32 TEZI I Tracking error signal zero-cross input pin.

33 FOO O Focus equalizer output pin.

34 TRO O Tracking equalizer output pin.

35 VREF - Analog reference power supply voltage pin.

36 RFGC O RF amplitude adjustment control signal output pin.

37 TEBC O Tracking balance control signal output pin.

38 SEL O APC circuit ON/OFF signal output pin. At laser on, high impedance with UHS="L",

H output with UHS="H".

39 AV

- Analog 3.3V power supply voltage pin.

DD3

40 FMO O Feed equalizer output pin.

41 DMO O Disc equalizer output pin.

42 V

43 V

SS3

DD3

- Digital GND pin.

- Digital 3.3V power supply voltage pin.

44 TESIN I Test input pin. Normally, fixed to "L".

45 XV

- System clock oscillator GND pin.

SS3

46 XI I System clock oscillator input pin.

47 XO O System clock oscillator output pin.

48 XV

49 DV

SS3

- System clock oscillator 3.3V power supply voltage pin.

DD3

R - DA converter GND pin.

50 RO O R-channel data forward output pin.

51 DV

- DA converter 3.3V power supply pin.

DD3

52 DVR - Reference voltage pin.

53 LO O L-channel data forward output pin.

54 DV

L - DA converter GND pin.

SS3

55 ZDET O 1 bit DA converter zero detection flag output pin.

56 V

SS5

- Microcontroller interface GND pin.

57 BUS0

58 BUS1

I/O Microcontroller interface data I/O pins.59 BUS2

60 BUS3

61 BUCK I Microcontroller interface clock input pin.

62 /CCE I Microcontroller interface chip enable signal input pin.At "L", BUS0 to BUS3 are active.

63 /RST I Reset signal input pin. At reset, "L".

64 V

DD5

- Microcontroller interface 5V power supply pin.

(No.49793)1-49

Page 20

4.17 TC94A20F-011 (IC1652) : DAC/SRAM built in type D-ROM decoder+ MP3 decoder

• Pin layout

48 33

49

32

• Block diagram

64

17

116

32 31 30 29 28

33

34

35

36

General output

37

38

39

DIT

port

2sets

Address calc.

27

Bus

Switch

register

C-Pointer

register

Y-Pointer

register

X-Pointer

25

26

DAC DAC

24

22 21

23

ALU

20 19 18 17

A2A1A0 A3

16

15

14

13

12

11

Audio I/F

10

40

41

Flag

42

43

Timer

44

control

45

46

47

48

Interrupt

DRAM I/F

General

inputbport

ERAM

2k word

*7

CROM

4k word

Y-RAM

4k word

X-RAM

4k word

SRAM I/F

1Mbit

SRAM

I/F

SubCode

register

X0 X1 X2

PRAM

Y0 Y1 Y2

256word

MX AX AYMY MZ

Program

PROM

VCO

MAC

control

4k*3

=12k word

Timing

generator

round & limit round & limit

decoder

Instruction

Microcom. I/F

9

8

7

6

5

4

3

2

1

1-50 (No.49793)

51

52

5049

53

5857565554

6059

6261

64

63

Page 21

• Pin functions

Pin No Symbol I/O Functions

1 /RESET I Hard reset input H:normal L:reset

2 MiMD I Micon I/F mode select input

3 /MiCS I Micon I/F chip select input

4 /MiLP I Micon I/F latch palus input

5 MiDio I/O Micon I/F data input/output

6 /MiCK I Micon I/F clock input

7 MiACK O Micon I/F acknowledge output

8 VDDT - Power supply for digital (3.3V)

9 SDo O Data output

10 BCKo O Bit output

11 LRCKo O LR clock output

12 SDiO I Data input 0

13 BCKiA I Bit clock input A

14 LRCKiA I LR clock input A

15 SDiL I Data input terminal 1

16 BCKiB I Bit clock input terminal B

17 LRCKiB I LR clock input terminal B

18 VDD - Power supply for digital (2.5V)

19 STANBY I Standby mode control input H:STBY L:normal

20 VSS - GND for digital

21 VSSL - GND for DAC Lch

22 VRAL - Reference voltage for DAC Lch

23 LO O DAC Lch output

24,25 VDAL,VDAR - Power supply for DAC Lch/Power supply for DAC Rch (2.5V)

26 RO O DAC Rch output

27 VRAR - Reference voltage for DAC Rch

28 VSSR - GND for DAC R ch

29 TESTP I Test terminal H:test mode L:normal

30 TXO O SPDIF output

31~34 Po0~Po3 O General purpose output 0 ~ 3

35 VDDT - Power supply for digital (3.3V)

36~38 Po4~Po6 O General purpose output 4 ~ 6

39 REQ O REC terminal

40 VSS - GND for digital

41 IRO I/O External interrupt input

42 VDDM - Internal 1Mbit SRAM power supply (2.5V)

43,44 Fi0,Fi1 I Flug input 0,1

45 VSSM - GND for internal 1Mbit SRAM

46,47 Pi0,Pi1 I General ourpose input 01

48 VSS - GND for digital

49,50 Pi2,Pi3 I General purpose input 23

51 Pi4/CLCL I General purpose input 4/SUBQ I/F clock inputoutput

52 VDD - Power supply for digital (2.5V)

53 Pi5/DATA I General purpose input 5/SUBQ I/F data input

54 TSTiN/SFSY I Test terminal/SUBQ I/F flame sync input

55 Fi2/SBSY I Flug input 2/SUBQ I/F block sync input

56 VSSP - GND for VCO

57 Pdo O PLL phase error detection signal output

58 Vcoi I VCO control voltage input

59 VDDP - Power supply for VCO (2.5V)

60 CKo/CKi I/O External clock input/Clock output terminal

61 VDDX - Power supply for X'tal oscillator (2.5V)

62,63 Xi,Xo I,O Oscillator connection terminal for input/output

64 VSSX - GND for oscillator

(No.49793)1-51

Page 22

4.18 UPD784217AGC208 (IC962) : Main micon

• Pin Layout

100 ~ 76

1

~

25

26 ~ 50

• Pin functions

Pin No Symbol I/O Function

1NC-Not use

2NC-Not use

3NC-Not use

4NC-Not use

5NC-Not use

6NC-Not use

7 DIM_OUT O DIMMER pulse control output

8 ILLUM1 O POWER ON:H,FLAT PANEL:L

9VDD-5V

10 X2 11 X1 12 VSS - GND

13 XT2 14 XT1 15 RESET I Reset detection teaminal

16 CD_P.REQ I CD mechanical switch 1 detection signal input

17 BUS_NT I J-BUS int

18 PS2 I POWER SAVE2. Operating together with BACKUP.H input:STOP

19 H.REMOCON I Pulse signal for CRUISE input(only in 330R)

20 RDS_SCK I RDS clock input

21 RDS_ DA I RDS data input

22 REMOCON I Remocon input(111R:READY)

23 AVDD - 5V

24 AVREF0 - 5V

25 TEMP I Temperature detection input

26 KEY0 I Key input 0

27 KEY1 I Key input 1

28 KEY2 I Key input 2

29 LEVEL I Level meter input

30 MRC I MRC output voltage detection

31 SQ I S.QUALITY level input

32 SM I S.METER level input

33 AVSS - GND

34 NC - Not use

35 DOT_CNT O Dot matrix contrast adjustment analog output

36 AVREF - 5V

37 BUS_SI I J-BUS data input

38 BUS_SO O J-BUS data output

39 BUS_SCK I/O J-BUS clock input and output

40 NC - Not use

75

~

51

1-52 (No.49793)

Page 23

Pin No Symbol I/O Function

41 LCD_DA O Data output to LCD driver

42 LCD_SCK O Clock output to LCD driver

43 LCD-CE1 O Chip enable output 1 to LCD driver

44 BUZZER O Buzzer output

45 12C_DAI I 12C communication data input

46 12C_DAO O 12C communication data output

47 12C-CLK O 12C communication clock output

48 BUS-I/O O J-BUSI/O signal terminal

49 TMO O Tray motor negative signal output terminal

50 TM1 O Tray motor positive signal output terminal

51 DMO O Motor control signal output in door down

52 DM1 O Motor control signal output in door up

53 ST I Stereo signal input L:Stereo

54 NC - Not use

55 AFCK O AF check output AF check:L

56 C_SW1 I Chameleon machanical switch 1 detection signal input

57 C_SW2 I Chameleon machanical switch 2 detection signal input

58 C_SW3 I Chameleon machanical switch 3 detection signal input

59 C_SW4 I Chameleon machanical switch 4 detection signal input

60 C_SW5 I Chameleon machanical switch 5 detection signal input

61 VOL1 I Rotary volume signal 1 input

62 VOL2 I Rotary volume signal 2 input

63 SEEK/STP O Auto seek/stop selection output SEEK:L STOP:H

64 NC - Not use

65 FM/AM - FM/AM selection output FM:H AM:L

66 PLL_CE O IC control CE output

67 PLL_DO O IC control data output

68 PLL_CLK O IC control clock output

69 PLL_DI I IC control data input

70 TEL_MUTE I Telephone mute detection input

71 NC - Not use

72 VSS - GND

73 DIM_IN I Dimmer detection input L:dimmer ON

74 PS1 I Power save 1 Operating together with ACC.Power save :L Operating :H

75 POWER O Power ON/OFF selection output Power ON:H

76 CD_ON O CD power supply control signal output CD:H

77 MUTE O Mute output MUTEON:L

78 CD_RESET O Subwoofer cut off frequency control output 1

79 CD_MUTE O Subwoofer cut off frequency control output 2

80 NC - Not use

81 VDD - 5V

82 VOL_DA O data output terminal

83 VOL_CLK O clock signal output terminal

84 CF-SEL O FM band filter selection signal output

85 NC O Not use

86 LCD_RST O Reset signal output to LCD driver

87~93 NC - Not use

94 TEST - GND

95~100 NC - Not use

(No.49793)1-53

Page 24

4.19 UPD784225GK-629 (IC1501) : CPU

• Pin layout

60 ~ 41

61

40

~

80

1 ~ 20

~

21

• Pin function

Pin No. Symbol I/O Function

1 TEMP IN I Temp. detection input terminal

2,3 - - No use

4 AVSS - GND

5 ADCONT O Output H level during power on. During stop mode:L

6---

7 AVREF1 - 3.3V

8 EPROMDI I EEPROM data input terminal

9 EPROMDO O EEPROM data output terminal. Output H level during input

10 EPROMCK I/O EEPROM clock signal input/output terminal

11 LCD CE O Chip enable output for LCD driver

12 LCD DA O Data output for LCD driver

13 LCD CK O Clock output for LCD driver

14 BUS I/O O JVC BUS input/output control terminal (negative)

15 BUS I/O O JVC BUS input/output control terminal

16 BUS SI I JVC BUS data input terminal

17 BUS SO O JVC BUS data output terminal

18 BUS SCK I/O JVC BUS clock input/output terminal

19 BUSOUT O JVC BUS BUSOUT output terminal

20 CD ON O Power supply (3.3V) control for CD

21 CD REQ O CD mechanism power supply on request signal output terminal

22 CD MUTE O CD mute signal output terminal

23 - - -

24 DSP RESET O CD DSP reset signal output terminal

25 CCE O CD DSP chip enable output terminal

26 BUCK O CD DSP data clock output terminal

27 BUS3 I/O CD DSP data 3 input/output terminal

28 BUS2 I/O CD DSP data 2 input/output terminal

29 BUS1 I/O CD DSP data 1 input/output terminal

30 BUS0 I/O CD DSP data 0 input/output terminal

31 2X PLAY O RF frequency response select output of 2x speed playback

32 RW SEL O CD-RW select output terminal (RW:L)

33 VSS1 - GND

34 LD O Loading signal output terminal (L:loading, H:eject)

35 LD/FE O Loading/Feed select signal output terminal (H:LD, L:FE)

36 MP3 DI I CD MP3 data input terminal

37 MP3 DO O CD MP3 data output terminal

38 MP3 CK O Clock signal output terminal for CD MP3 data

1-54 (No.49793)

Page 25

Pin No. Symbol I/O Function

39 MP3 RESET O CD MP3 reset signal output terminal

40 MP3 STB O CD MP3 standby signal output terminal (H:Standby)

41~43 - - -

44 DAC ML O DAC mode control latch output terminal

45 DAC MC O DAC mode control BCK output terminal

46 DAC MD O DAC mode control data output terminal

47 DAC CS O DAC chip select output terminal

48~51 - - No use

52 DISC SEL I 8cm disc correspondence mode select terminal (correspondence:L)

53 DAC SEL I DAC select mode input terminal

54 - - -

55 TEST MODE I LCD/AD key/Remocon invalid select mode input terminal L:invalid

56 MP3 SEL I MP3 select mode input terminal

57 8V DET I CD mechanism power supply detection terminal (L:8V on)

58 REST I CD mechanism rest switch input terminal

59 SW2 I CD mechanism SW2 input terminal

60 RESET I Reset signal input terminal

61 SW1 I CD mechanism SW1 input terminal

62 B.DET I Backup power supply detection input terminal (H:Stop mode)

63 P.DET I Main power off detection input terminal (H:HALT mode)

64 BUS INT I JVC BUS communication start interrupt input terminal

65 MP3 REQ I CD MP3 request signal input terminal

66 - - -

67 VSS0 - GND

68 VDD1 - 3.3V

69 X2 O Oscillator (6MHz)

70 X1 I Oscillator (6MHz)

71 VPP - GND

72 XT2 O Open

73 XT1 I GND

74 VDD0 - 3.3V

75 AVDD - Connect to ADCONT (Power supply for A/D convertor)

76 IOP I Pickup IOP measurement input terminal

77 KEY0 I Key input 0 (8bit A/D input) terminal

78 KEY1 I Key input 1 (8bit A/D input) terminal

79 KEY2 I Key input 2 (8bit A/D input) terminal

80 KET3 I Key input 3 (8bit A/D input) terminal

(No.49793)1-55

Page 26

4.20 PCM1716E-X (IC1571) : D/A converter

O

• Pin layout

28 15

114

• Block diagram

BCK

LBCK

DATA

ML/llS

MC/DM1

MD/DM0

CS/WO

MODE

MUTE

RST

Serial

Input

I/F

Mode

Control

I/F

8X Oversampling

Digital Filter

with

Function Controller

SCK

BPZ-Cont

Crystal OSC

XTI XTO CLKO Vcc1 VccAGND1 DGND

• Pin function

Pin

Symbol I/O Function

No.

1 LRCK I LRCK clock input

2 DATA I Serial audio data input

3 BCK I Bit clock input for serial audio data

4 CLKO O Buffered output of system clock

5 XTI I Oscillator input / External clock input

6 XTO O Oscillator output

7 DGND - Digital ground

8 VDD - Digital power +5V

9 VDD2R - Analog power +5V

10 AGND2R - Analog ground

11 EXTR O Rch common pin of analog output amp

12 NC - Non connection

13 VOUTR O Rch analog voltage output of audio signal

14 AGND1 - Analog ground

15 Vcc1 - Analog power +5V

Mult-level

Delta-Sigma

Modulator

Pin

No.

Vcc2L

DAC

DAC

Power Supply

Symbol I/O Function

AGND2L

Open drain

Vcc2R

AGND2R

Low-pass

Filter

Low-pass

Filter

VoutL

EXTL

VoutR

EXTR

ZER

16 VOUTL O Lch analog voltage output of audio signal

17 NC - Non connection

18 EXTL O Lch common pin of analog output amp

19 AGND2L - Analog ground

20 Vcc2L - Analog power +5V

21 ZERO O Zero data flag

22 RST I Reset

23 CS/IWO I Chip select / Input format selection

24 MODE I Mode control select

25 MUTE I Mute control

26 MD/DM0 I Mode control, Data /

De-emphasis selection 1

27 MC/DM1 I Mode control, BCK /

De-emphasis selection 2

28 ML/IIS I Mode control, WDCK /

Input format selection

1-56 (No.49793)

Page 27

KD-LX555R

Block diagram

ANT

J1

REST

REST

A,B,E,F

MD,LD

SWITCH

5

SW1

SW2

LOAD/FEED+

LOAD/FEED-

SPINDLE+

SPINDLE-

REST

CN1601

SW1

SW2

LOAD/FEED

MOTOR

SPINDLE

MOTOR

SW1

SW2

4

PICKUP

FOCUS+

FOCUSTRACKING+

TRACKINGA,B,E,F

MD,LD

FOCUS+

FOCUSTRACKING+

TRACKINGSPINDLE+

SPINDLELOAD/FEED+

LOAD/FEED-

IC1601

CDRF

RFDC

TEO

TEN

TEB

SEL

IC1621

D.SERVO

DSP

TRO

FOO

IC1681

CD

RFGC

RFGO

RFRP

FEN

BCK,LRCK,AOUT

VREF

FMO

CMO

DRIVER

3

RWSEL

IOP

BUSO to BUS3

BUCK,CCF

DSPRESET

CLOCK

MUTE

LOAD

LD/FF

IC1571

D/A

CONVERTER

IC1652

MP3

DECODER

/RESET

MIDIO

/MCLK

REQ

DATA

IC1501

CPU

SDA

SCL

IC1502

EEPROM

VOUTL

VOUTR

LRCK

BCK

A0 to A16

WF,OF,CS1

I/O1 to I/O8

DACMI

DACMC

DACMD

DACCS

/BUSIO

BUSIO

BUSSI

BUSSO

BUSSCK

CDMUTTE

CDREQ

P.D E T

B.DET

CDREST

DISCSEL

RST

IC1572

CDLPF

IC1653

SRAM

DATA

BUSSI/SO

BUFFER

CDL-CH

CDR-CH

BUSCLK

IC1503

J-BUS

CN1501

CN501

AM_ANT

FM_ANT

CD_Lch,CD_Rch

P.D E T

CD_MUTE

CD_P.REQ

CD_RESET

BUSSI/SO

BUSCLIC

TU1

FM/AM

TUNER

MBC

SQ

SM

SD/ST

AFCK

SEEK/STOP

FM/AM

PLL_CE

PLL_DO

PLL_CLK

PLL_DI

CF_SEL

TU_Lch

TU_Rch

FM/AM_DET

RDS_SCK

RDS_DA

IC962

IC51

RDS

CPU

VOL_DA

VOL_CLK

IC703

EEPROM

BUSSCK

BUSIO

BUSSO

BUSSI

IC400

E.VOLUME

SDA

SCL

IC771

J.BUS

BUFFER

FRONTR

REARR

CH_Lch

CH_Rch

FRONTL

REARL

PREAMP

PREAMP

BUSSI

BUSSCK

IC461

IC361

FRONTR

REARR

FRONTL

REARL

IC941

POWER

AMP

OUTFL+

OUTFLOUTFR+

OUTFROUTRL+

OUTRLOUTRR+

OUTRR-

REMOTE

CHANGER

CN771

FRONTL

FRONTR

REARL

REARR

CD

LINE OUT

CN380

DC CONNECTOR

CN901

IC603

REMOCON

S1 to S74

COM1 to COM8

SENSOR

LCD1

LCDDA

LCDCL

2

LED

P1 to P4

DRIVER

IC601

LCD

LCDCE1

LCDRST

DRIVER

S631

to

S638

1

KEY0

REMOCON

ENCODER

PANEL

SENSOR

S639

to

S643

KEY1

ENC0

ENC1

CASW4

CASW5

LED

MATRIX

CN1601

CN701

CN1631

CN702

REMOCON,LCDRST,LCDCE1,

KEY2,RESETCASW4,CASW5,

LCDCL,LCDDA,VOL1,VOL2

KEY0

KEY1

H.REMOCON

DM0

DM1

DMK

TM1

TM0

TMK

C_SW1

C_SW2

C_SW3

IC830

MOTOR

DIRIVER

IC831

MOTOR

DRIVER

H.REMOCON

CN840

CN704

CN830 CN831

DOOR

MOTOR

TRAY

MOTOR

ABC DEFGH

2-1

Page 28

KD-LX555R

KD-LX555R

Standard schematic diagrams

Main amp section

R463 15K

R464 15K

R363 15K

R364 15K

1SS400

D980

CRS03

SI/SO

SCK

REMOTE

CH_Lch

GND

CH_Rch

VCC

GND

GND

GND

GND

GND

GND

131211 10 9 8 7 6 5 4 3 2 1

1

2

3

Q977

DTA114EUA

100/10

C978

D962

Q983

LINE[1-4]

R472

0

0

R471

R467

15K

V-

A+INPUT

IC461

5678

B-INPUT

B+INPUT

R468

15K

R367

15K

V-

A+INPUT

3

4

IC361

6

5

B-INPUT

B+INPUT

R368

R371

R372

DTA114EUA

R945

10K

D941

1SS400

R962

9.1K

4.7K

R963

0.1

C968

D967

CRS03

47K

47K

R987

R984

Q986

DTC114EUA

QRS

2SC4081

C982

22/16

H-REMOCON

NJM4565M-D

R466

3.3K

NJM4565M-D

R366

3.3K15K

0

0

Q948

R943

Q942

C962

2.2/50

R976

R986

D986

R985

4.7K

PRE AMP

R465

3.3K

A-INPUT

AOUTPUT

1234

V+

BOUTPUT

C464

0.001

R365

3.3K

A-INPUT

AOUTPUT

2

1

7

8

V+

BOUTPUT

C364

0.001

GND

6.8K

DTC114EUA

Q943

R941

27K

R979

1K

1/4W

2.2K

2012

1K

DAP202U

C987

C970

RR

AMP[1]

C463

0.001

AMP[4]

AMP[3]

C363

0.001

AMP[2]

C941

22/16

C944

2.2/50

C942

DTC114EUA

47/16

C943

0.1

C945

0.01

2012

2.2K

2012

R977

0.1

4.7K

R989

0.001

2012

R978

100K

LINE[2]

DAP202U

LINE[3]

FR

LINE[1]

FL

DAP202U

LINE[4]

RL

RL

RR

AMP[2]

AMP[1]

10K

10K

R369

R370

100K

R374

100K

R473

CQ

CQ

C370

C469

0.33

0.33

330P

C372

CH

330PC471

CH

P_GND

MUTE

VCC

20 22 24

P_GND

18

ON TIME C

16

IN_RL

LA47505

IN_RR

RF

10 12 14

IC941

P_GND

VCC

STBY

P_GND

2468

C961

D961

1N5404TU-15

*

Parts are safety assurance parts.

When replacing those parts make

sure to use the specified one.

TUNER SIGNAL

CD SIGNAL

TAPE SIGNAL

AUX IN SIGNAL

MAIN SIGNAL

R380

2.2K

D380

R480

2.2K

R381

2.2K

D381

R481

2.2K

AMP[1-4]

R373

R474

C371

C472

AC_CONT2

OUT_RLOUT_RL+

OUT_FL-

19 21 23 25

OUT_FL+

IN_FL

15 17

S_GND

IN_FR

11 13

OUT_FR+

OUT_FROUT_RR+

579

OUT_RRAC_CONT1

13

R944

SP[1]

SP[2]

SP[3]

SP[4]

SP[5]

SP[6]

SP[7]

SP[8]

L961

140uH

105 C

3300/16

GND

Note:NM=No Mount

330P

CH

330P

CH

100K

100K

C947

0.47/50

C946

0.47/50

AMP[3]

10K

R369

C369

NM

CN901

GND

ACC

REMOTE

NC

REAR RIGHT(+)

REAR RIGHT(-)

REAR LEFT(-)

REAR LEFT(-)

FRONT LEFT(+)

FRONT LEFT(-)

FRONT RIGHT(-)

FRONT RIGHT(+)

TEL

NC

ILLUMINATION

MEMORY

181716 151413 1211 10 9 8 7 6 5 4 3 2 1

Q380

2SD1048

Q480

2SD1048

Q381

2SD1048

Q481

2SD1048

FL

AMP[4]

CQ

0.33

FUSE 15A

R382

100

X678

X678

R482

100

R383

100

X678

X678

R483

100

FR

10K

R470

CQ

C470

0.33

POWER AMP

CH

C996

C995

100P

CH

C998

C997

100P

C940

NM

SP[1-8]

CH

C994

100P

CH

C991

100P

LINE OUT

NM

C380

NM

C480

NM

C481

NM

C481

CH

C993

100P

CH

C992

100P

1:GND

2:ACC

3:REMOTE

4:NC

5:REAR RIGHT(+)

6:REAR RIGHT(-)

7:REAR LEFT(-)

8:REAR LEFT(+)

TP59

TP60

TP61

TP64

TP63

TP62

0.1

CQ

C1002

CH

0.1

CQ

C1000

100P

CH

0.1

CQ

100P

C1000

0.1

CQ

C999

DC CONNECTOR

2345678

1

16

15A

STYLE PIN 32

STYLE PIN 32

STYLE PIN 32

GND

CN380

123456

SP[3]

SP[4]

SP[6]

SP[5]

SP[8]

SP[7]

SP[1]

SP[2]

9:FRONT LEFT(+)

10:FRONT LEFT(-)

11:FRONT RIGHT(-)

12:FRONT RIGHT(+)

13:TEL

14:NC

15:ILLUMINATION

16:MEMORY

9101112131415

FRONT_Lch

GND

FRONT_Rch

REAR_Lch

GND

REAR_Rch

1 2 3 4 5 6 7 8 9 10111213141516171819202122

ANT

_

GND1

AM

5

4

CD_Rch

AGND

AGND

CD_Lch

ON5V

(CD_SCK)

(CD_LRCK)

(CD_DATA)

(DISC_SEL)

CD_MUTE

CD_REQ

CD_RESET

B.DET

P.DET

BUS_SI/SO

BUS_CLK

3

2

1

VDD5V

CASW5

CASW4

LCDRST

LCDCE1

LCDCL

LCDDA

REMOCON

ACC5V

RESET

CASW1

CASW2

CASW3

DOOR_MOTOR

TRY_MOTOR

CD8V

CD8V

KEY0

KEY1

KEY2

VOL2

VOL1

GND

GND

GND

GND

GND

GND

GND

L1

J1

4.7uH

D1

DAN217U

GND

4.7

R10

4.7

R11

2SA1576A

47K

R14

Q11

2SB1197K

QR

R12

R12

47K

R13

4.7K

Q12

DTC114EUA

TP7

TP8

TP9

TP10

TP11

CN501

TKC-W22P-M1

12345678910111213141516171819202122

9V

TP12

TP13

TP16

TP17

TP18

TP14

BUS[2]

TP15

R800

0

0

R801

0.01

C804

L800

TP21

TP22

TP23

TP25

TP24

TP27

TP28

TP26

TP29

CN702

123456

10V

TP35

TP32

TP33

TP31

TP34

TP30

CN701

52559-1617

12345678910111213141516

9V

C756

INV

0.0022

NM

10V

TP41

TP43

TP42

TP44

TP40

TP65

TP67

TP66

CN704

CASW[3]

1234

S653

S652

TP68

IC830

123456789

TP46

TP45

CN830

12

TP47

TP48

12

CN831

123456789

123456789

IC831

0.047

C1

47uH

TP36

TP39

100/10

C13

Q13

QRS

D11

BUS[1]

0.01

C800

C830

VCC

_

AM

0.01

R15

TP19

Q800

TP37

TP38

CONT[5]

CONT[6]

CONT[7]

CONT[8]

CONT[9]

CONT[10]

CONT[11]

CONT[12]

CASW[2]

S651

47/16

C2

3.3K

TP20

DTC114EUA

CONT[1]

CONT[2]

CONT[3]

CONT[4]

VCC

_

FM

DAN202U

CASW[1]

BA6956AN

BA6956AN

ANT

_

GND6

FM

0.01

47/16

C9

C3

TU[4]

TU[9]

0.01

0.01

Q801

DTC114EUA

C801

C802

2SA1576A

Q701

987654321

MOTOR DRIVER

VSS

_

PLL

Q802

CONT[1-12]

Q702

QRS

R713

DTC114EUA

CASW[1-3]

R832

R833

_

_

TU[14]

C25

DTC114EUA

1K

3.3K

DTA114EUA

4.7K

TU1

L

VCC

_

LPF

MONITOR

BW

CF

10

0.047

100/10

B5

C5

C14

R27

R26

10K

470

Q23

QRS

2SC4081

0.47

Q803

DTC114EUA

47K

R726

Q832

R831

Q833

DTC114EUA

R25

TU[1-14]

MD[1]

Q804

DTC114EUA

MD[2]

MD[3]

3.3K

R830

DTA114EUA

4.7K

FAE372-E01

R

IND

_

SD/ST

TU[6]

TU[6]

R23

C24

0.1

Q22

QRS

2SC4081

10K

R24

C23

0.0047

DI

CL

CE

VDD

_

PLL

1.8uH

NM

NM

C6

C15

L7

TU[10]

R21

47K

10K

R28

47K

C22

0.01

39K

R22

2.2K

DO

TU[11]

TU[12]

TU[13]

Q34

DTA114EUA

Q24

CH

330P

DTC114EUA

C21

TU[5]

TU[14]

NM

C751

SENSOR

_

MRC

TU[3]

DTA114EUA

MOTOR[1-6]

39K

B1

Q5

TU[7]

S.METER

_

FM/AM

DTA114EUA

C8

TU[8]

VCC

_

DRIVE

_

MPX

MUTE

220/10

0.01

C7 0.1/50

C4

C11

R16

Q4

4.7K

C10

NM

Q3

NM

CPU

POWER

MD[1-3]

MD[3]

MD[1]

EVOL[1]

EVOL[2]

MOTOR[5]

MOTOR[6]

C712

C719

MOTOR[1]

MOTOR[2]

MOTOR[3]

MOTOR[4]

Q830

MOTOR[5]

Q831

MOTOR[6]

DTC114EUA

CD_ON

76

MUTE

77

CD_RESET

78

CD_MUTE

79

NC

80

R747

R748

R749

R728

R742

VDD

4.7K

81

VOL_DA

1K

82

VOL_CLK

1K

83

CF_SEL

2.2K

84

NC

85

LCD_RST

86

NC

87

DMK

88

TMK

89

0.47

NC

90

NC

91

220P

NC

92

NC

CH

93

10K

TEST

94

NC

95

NC

96

VPP

NC

TP6

97

NC

98

NC

99

NC

100

C750

0.47

1 2 3 4 5 6 7 8 9 10111213141516171819202122232425

NCNCNCNCNC

TP5

GND

DET

_

FM/AM

QRS

2SC4081

10K

R738

IN

_

PS1

DIM

47K

R739

VSSNCTEL

R702

15PC704

R213

4.7K

C203

C103

R113

4.7K

22

R51

TU[13]

TU[12]

2.2K

2.2K

R765

R764

MUTE

DI

CLK

_

_

_

_

PLL

PLL

IC uPD784217AGC-208-8EU

NC

OUT

_

ILLUMI

DIM

VDD

TP4

100

X701

12.5MHz

CH

15PC703

FM/AM

TUNER

C213

4.7/25

R200

4.7K

R100

4.7K

VDD

VDD

47/16

C53

CONT[3]

CONT[10]

100K

R718

SW5

_

VOL1

C

P.REQ

RESET

_

CD

TP3

RESET

CH

MD[2]

0.022

C56

MUX

OSCI

X51

4.332MHz

CH

12P

C52

CONT[4]

CASW[3]

SW4

SW3

_

_

C

C

INT

PS2

_

BUS

Q200

Q100

2.2/50

C57

VFEF

DATA

TCON

OSCO

10K

R53

CH

12P

C51

TU[7]

CASW[2]

CASW[1]

1K

R736

SW2

SW1

_

_

AFCK

C

C

DA

_

SCK

_

RDS

RDS

H.REMOCON

47K

47K

R704

R703

0.1

C757

QRS

2SC4081

QRS

2SC4081

RDS

161514131211109

NC

REMOCON

0.0022

C724

0.015

0.015

C113

4.7/25

C55

560P

CH

SCOUT

CIN

GND

87654321

IC51 BU1923F

GND

SYNC

MODE

0.01

C54

TU[9]

TU[8]

TU[11]

TU[10]

CONT[9]

2.2K

2.2K

10K

10K

100K

R719

R762

R737

R757

R763

DO

CE

_

NC

VOL2

FM/AM

PLL

PLL

SEEK/STP

IC962

X2

X1

XT2

XT1

VSS

VDD

R751

10M

47K

R701

X702

32.768KHz

CH

CH

27P

22P

C702

C701

R52

TU[6]

10K

R760

SD/ST

AVDD

LINE[4]

LINE[3]

LINE[2]

C966

Q966

QRS

10

56

2A

22K

R777

LINE[1]

680

680

680

680

R134

47K

47K

R462

R461

47K

47K

R362

R361

AJ

_

OUT

OUT

_

_

ILM

CD

ILM

15K

Q981

R975

DTA114EUA

47/16

22/16

Q982

C967

C971

R970

6.8K

39K

R971

R773

22K

100K

R782

L771

1.8uH

3Y

9

8

7

2Y

GND

100K

0.0022

R118

C116

NM

R234

R235

R135

C461

4.7/25

10K

10K R458

C462

R459

4.7/25

47/16

C467

C367

47/16

C361

4.7/25

C362

R358 10K 10KR359

4.7/25

Q979

DTA114EUA

22/16

UDZ11B

D978

GND

DTC114EUA

0.1

C937

C977

TH981

R981

18K

10K

3.3K

R988

D701

CRS03

BUS[1]

BUS[2]

47K

R772

TP49

TP52

TP50

TP51

CN771

100K

0.0022

R218

C216

CH

TP56

TP55

TP54

TP53

C840

C100P

CN840

TP57

TP58

E.VOLUME

C403

100/10

3.3K

R400

CDCH[2]

R401

C224

0.01

C223 470P

R223 12K

C123 470P

R123 12K

R301

R300

CDCH[1]

QUAL

CLK

2.2K

2.2K

R54

TU[2]

TU[1]

C400 4.7/25

C401

2.2K

C402

I2

_

47K

15K

DFP

VCC

36

35

R402

R403

2

1

15K

47K

I1

_

REF

DFP

R302

R303

C302

2.2K

C301

3.3K

C300

10/16

C303

0.22

C164

D430

CRS03

4.7/25

1/50

I2

_

DFN

INA2

INB2

INC2

32

31

33

30

34

6

5

3

4

7

I1

_

INA1

INB1

INC1

DFN

1/50

4.7/25

4.7/25

D161

C163

0.047

DAN217U

270K

R167

Q161

C162

CDCH[1-2]

IND2

IC400

IND1

QRS

2SC4081

R165

R166

22/16

C405

C404

2.2/50

2.2/50

02

02

_

DFN

29

8

01

_

DFN

R162

12K

390

1K

02

I2

I2

02

_

_

_

_

_

SEL

27

28

9

10

01

_

SEL

C304

2.2/50

R163

R164

VOL

M1508FP

I1

_

VOL

180K

22K

C161

1/50

TON

26

11 12

01

_

TON

C305

2.2/50

02

_

FAD

REA

FA

22

23

2425

15

13 14

I1

01

01

_

_

_

FR

FAD

REA

D111

DAN202U

47K

R161

1/50

C431

C406

0.047

C430

10/16

C407

4.7/25

EVOL[1-2]

4.7/25

4.7/25

C408

C307

C308

4.7/25

02

_

NF

01

_

NF

EVOL[2]

VDD

CLOCK

VDD02

21

20

19

17

16

18

GND

DATA

VDD01

EVOL[1]

1/50

C306

220K

R111

R211

220K

REGULAT OR

HA1364A

C720

0.047

A2A1A0

R761

R766

R731

R732

R733

R734

R735

MOTOR[1]

MOTOR[2]

NM

R767

NM

R768

DW1

DMO

51525354555657585960616263646566676869707172737475

TM1

50

TM0

49

BUS_I/O

48

I2C_CLK

47

I2C_DAO

46

I2C_DAI

45

BUZZER

44

LCD_CE1

43

LCD_SCK

42

LCD_DA

41

NC

40

BUS_SCK

39

BUS_SO

38

BUS_SI

37

AVREF

36

DOT_CNT

35

NC

34

AVSS

33

SM

32

SQ

31

MRC

30

LEVEL

29

KEY2

28

KEY1

27

KEY0

26

TEMP

AVREF0

R700

10K

10K

TH700

GND

47K

4321

47K

IC703 BR24C32D

5678

47K

47K

47K

47K

47K

MOTOR[4]

MOTOR[3]

NM

NM

R770

R769

0.0022

0.0022

C721

C722

SDA

TP1

SI

TP2

SO

R723

R722

R721

R720

R717

R716

R715

R714 10K

R727

R712

R711

R710

10/16

PST3433UL

C708

WP

C711

SCL

VCC

0.47

1K

R791

BZ791

0.1/50

270

270

PKM13EPY-4000

L701

Q791

R724

R725

DTC114EUA

1K

10K

10K

330

L719

1.8uH

1.8uH

L718

4.7K

4.7K

4.7K

10K

10K

10K

10K

4.7K

4.7K

4.7K

100PCH

R707

R708

R709

C723

47K

10K

1SS400

D711

R706

R705

VDDNC

VOUT

0.01

2

1

IC702

4

3

C707

VSS

47uH

C791

CONT[5]

CONT[6]

CONT[7]

TU[5]

TU[4]

TU[3]

CONT[8]

CONT[2]

CONT[1]

TU[2]

TU[1]

CONT[11]

CONT[12]

CH

1000/6.3

220/10

0.047

220P

C706

C705

C710

C713

22K

R841

R752

0

R840

1K

123456789101112131415

OUT

OUT

_

_

EXT

ANT

1SS400

22/16

C969

Q700

DTA114EUA

CDCH[1]

CDCH[2]

IC961

IN

_

OUT

OUT

_

_

ACC

VDD

SW5V

D963

0.01

220/10

C972

C964

OUT

_

COMP

0.047

C771

VCC

_

CTRL

_

ANT

Q965

DTC114EUA

R775

10K

VCC

4C4A4Y3C3A

13

14

IC771

2

1

1A

1C

100K

R776

DET

BATT

NM

R968

L772

CET

_

AUDIO

22/16

C965

R781

12

3

1Y

R779

CTRL

0.01

2SA1576A

BUS[1-2]

330

11

HD74HC126FP

4

2C

1.8uH

47K

J.BUS BUFFER

GND

ABC DEFGH

2-2

Page 29

KD-LX555R

CD servo control section

B[1]

CD RF

C1611

R1613

68P

CH

1K

R1610

R1611

R1614

MECHANISM

5

TP24

TP25

TP22

TP23

TP20

TP21

REST

C001

FOCUS

COIL

PICK UP

12345

0.1

1

GND

21212123

LOAD/FEEDLOAD/FEED+

SPINDLESPINDLE+

SW1

SW2

GND

A

123456789101112131415

VCC

F

GND

E

VREF

B

VR

MD

GND

LD

FOCUSFOCUS+

TRACKING+

TRACKING-

TRACKING

COIL

VR001

1K

FOCUS-

FOCUS+

TRACKING+

TRACKING-

VREF

A

VCC

F

GND

E

VREF

B

TP30

VR

MD

LD

FOCUS-

FOCUS+

TRACKING+

TRACKING-

SPINDLE+

SPINDLE-

REST

SW2

SW1

GND

LOAD/FEED+

1 2 3 4 5 6 7 8 9 10111213141516171819202122

1 2 3 4 5 6 7 8 9 1011121314 151617 181920 2122

LOAD/FEED-

CN1601

A

123456789101112131415

VCC

F

GND

E

B

VR

MD

GND

LD

REST SW

LOAD/FEED

MOTOR

SPINDLE

MOTOR

SW1

SW2

4

HDU-110

678910

3

1

C002

0.1

C003

TP26

C1613

C1612

TP31

TP34

TP35

TP38

TP36

TP37

R1615

TP32

TP33

TP27

C[1]

C[2]

C[3]

TP28

TP29

C[4]

C[5]

B[2]

C[6]

B[3]

B[4]

B[5]

C[7]

C[8]

TP41

TP40

TP39

C[1-8]

B[1-12]

15K

TP44

GND

0.01

0.01

R1601

R1602

R1603

R1604

150

C1614

0.01

E[1-5]

C1643

B[6]

B[7]

B[8]

B[9]

B[10]

B[11]

B[12]

4.7K

4.7K

4.7K

R1638

R1639

R1640

L1623

CD DRIVER

R1681

6.8K

VIN1-A

VIN1

1

28

VIN1+A

VIN1-B

2

27

VCCP1

2

1

C1688

C[7]

0.047

C[8]

C1687

C[5]

0.047

C[6]

C1686

C[4]

0.047

C[3]

C1685

C[2]

0.047

C[1]

0

R1687

22K

30K

NM

R1689

R1688

R1690

47/16

C1684

G[1]

VO1+

VO2+

VO3+

VO4+

VCCP2

VIN4G

VIN1+B

3

26

S-GND

4

25

VO1-

VIN1-SW

5

24

MUTE

6

23

VO2-

VREFIN

7

22

LA6579H

GND

GND

29

30

VCCS

8

21

IC1681

VO3-

3.3VREG

9

20

REGIN

10

19

VO4-

VIN2G

11

18

VIN2

12

17

VIN4

VIN3G

13

16

VIN3

14

15

R1686

8.2K

R1682

R1683

4.7K

R1684

15K

R1685

6.8K

C1681

33K

C1683

10K

100

2K

C1610

0.1

C1609

5P

GND

RFI

RFO

AGCI

24 23 22 21 20 19 18 17 16 15 14 13

IC1601

123456789101112

FPI

TPI

FNI

VCC

C1603

22

47/6.3

C1601

R1605

R1616

22

R1606

10K

Q1601

0.01

C1602

10/10

C1615

82K

330K

330K

R1612

82K

D.SERV O&DSP

CH

0.01

47/6.3

100P

C1642

C1641

C1640

L1622

47uH

XVDD3X0XI

47

48

DVSS3R

49

R0

50

4.7K

R1641

NM

10K

R1642

C1644

0.1

C1689

47/16

DVDD3

51

DVR

52

LO

53

DVSS3L

54

ZDET

55

VSS5

56

BUS0

57

BUS1

58

BUS2

59

BUS3

60

BUCK

61

CCE

62

RESET

63

VDD5

64

1

BCK

47

47/6.3

D1682

1SR154-400

0

3216

C1646

C1690

10/10

C1682

10/16

Q1681

0.01

QR

2SB1184F5

NM

D1681

R1621

0.33

C1645

R1691

0.01

47uH

E[3]

E[4]

E[5]

E[2]

E[1]

RFGC

TNI

2SB1132

C1604

1M

R1637

46

2

3

LRCK

AOUT

47

47

R1622

R1623

F[1]

F[2]

G[2]

D[1]

100/6.3

45

G[3]

D[2]

C1608

RFGO

RFRPIN

TA2157FN

MDI

LDO

0.01

C1647

NM

XVSS3

TESIN

VDD3

VSS3

4344

42

TC94A14FA

6

5

7

4

IPF

VSS3

VDD3

DOUT

0.01

C1621

F[3]

GNDA2A1

BR24CO1AFV-W

5678

SDA

R1502

0.1

41

IC1621

270

RF

TP43

E[5]

C1639

100

R1636

CMO

8

SBOK

IC1502

RFRP

SEL

40

SCL

E[4]

47/6.3

9

D[3]

100

R1635

FMO

CLCK

B[2]

TP42

VREF

56K

R1609

FEN

TEB

C1638

AVDD3

SEL

39

38

10

111213

DATA

SFSY

L1621

WPIN

TEBC

SBSY

47uH

C1508

FEO

TEN

R1607

A0

1234

VDD

82K

R1631

RFGC

HSO

D[4]

0.01

353637

14

C1606

E[3]

100

VREF

UHSO

0.01

VRO

TEO

E[2]

34

15

C1622

R1608

TRO

33

16

PVDD3

47/6.3

RFDC

820

E[1]

C1637

C1636

C1632

C1631

FOO

PDD

CN1506

RESET

GVSW

R1634

R1633

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

47/6.3

C1502

C1503

C1504

C1505

R1545

C1507

R1632

GND

GND

XTAL

VDD

C1607

R1630

TEZI

TEI

SBAD

FEI

RFRP

RFZI

RFCT

AVDD3

RFI

SLCO

AVSS3

VCOF

PVREF

LPFO

LPFN

TMAX

R1624

VPP

SO

0.0068

100

5.6K

CN1502

SI

0.01

C1605

0.047

0.047

470P

CH

470P

CH

0

0

0

R1629

10K

C1627

C1626

C1625

R1628

470K

R1626

R1625

0.01

0.01

100/6.3

CH

27P

22P

CH

10K

CH

470P

12345678

47K

D[5]

D[6]

D[7]

D[8]

C1648

47P

C1630

0.033

C1623

0.047

C1635

C1629

0.033

D[1-8]

D[1-8]

0.047

C1634

2.2M

CH

C1624

R1627

0.047

C1633

CH

470P

0.01

0.0022

TP51

TP50

TP49

TP48

TP47

TP46

TP45

0.01

H[2]

H[1]

X1501

D-A CONVERTOR

0.001

D[7]

D[6]

D[1]

D[8]

D[5]

D[4]

D[3]

D[2]

R1538

47K

R1537

47K

Q1501

47K

R1539

R1541

100

0

R1547

NM

100K

4.7K

12345678

G[1-3]

C1598

0.001

L1652

F[1-3]

NM

C1674

H[3]

B[5]

R1536

R1535

R1534

R1533

C1509

1K

B.DET

P.D E T

BUSINT

MP3REQ

1K

AVDD

TP56

TP55

TP54

TP53

R1501

TP52

8.2K

C1533

H[4]

B[4]

B[3]

47K

47K

1K

47K

R1531

R1530

47K

47K

0.01

RESET

SW2

REST

8VDET

MP3SEL

TESTMODENCDACSEL

61

62

63

64

65

66

67

68

X2

69

X1

70

71

72

uPD784225GK-629-9EU

73

74

75

76

77

78

79

80

1 2 3 4 5 6 7 8 9 1011121314151617181920

NC

GND

GND

AVSS

TEMP

ADCONT

10K

TH1501

VSS0

VDD1

VDD0

KEY0

KEY1

KEY2

KEY3

SW1

NC

VPP

XT2

XT1

IOP

NM

C1597

C1628

47/6.3

0.015

10K

DTA114EUA

R1540

R1542

R1543

6MHz

R1546

RN1547

CN1503

GND

KEY3

KEY2

KEY1

KEY0

LCDCK

LCDDA

LCDCE

L[2]

L[1]

ML/IIS

MC/DM1

1 2 3 4 5 6 7 8 9 10 11 12 13 14

DATA

LRCK

R1668

0

R1676

NM

470K

470K

470K

R1671

R1672

R1673

K[16]

K[15]

K[14]

C1663

K[13]

K[12]

K[11]

R1675

C1664

C1665

C1677

0.33

C1666

C1667

C1675

C1676

0.01

C1669

STB

47uH

5

IC1651

NJU7241F25

1

2

VIN

GND

H[5]

NM

NM

NM

100

47K

100K

R1526

R1529

R1528

R1527

R1567

R1532

DISCSELNCNCNCNC

DACCS

IC1501

/BUSIO

LCDCK

AVREF1

EPROMI

LCDDA/SI

EPROMCK

LCDCE/SO

EPROMDO

270

0.01

10K

R1503

C1501

R1504

DACMD

BUSIO

M[1]

L[3]

MD/DM0

BCK

470K

470K

R1669

R1670

330

0.022

0.0047

100P

0.01

NM

NM

C1668

NC

4

3

VOUT

C1651

DACMC

BUSSI

M[2]

47K

R1573

MUTE

CLKO

R1574

0.1

CH

47/6.3

47/6.3

RN1522

DACMLNCNC

BUSSO

BUSSCK

M[4]

M[3]

47K

R1572

MODE

IC1571

XTI

R1575

NM

47

X1571

16.9344MHz

C1571

R1674

330

R1677

1M

X1651

NM

L1651

C1652

C1510

100

NC

4142434445464748495051525354555657585960

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

CDON

BUSOUT

R1544

M[5]

G[2]

L[4]

CS/IWO

XTO

2.7K

R1576

CH

12P

C1662

R1680

47uH

47/6.3

0.01

C1653

0.001

1SS355

D1505

MPSSTB

MP3RESET

MP3CK

MP3DO

MP3DI

LD/FE

LOAD

VSS1

RWSEL

2XPLAY

BUS3

BUS2

BUS1

BUS0

BUCK

CCE

DSPRESET

NC

CDMUTE

CDREQ

1K

R1667

R1666

R1665

R1664

0

RST

DGND

100P

C1678

R1653

R1652

NM

C1670

1SS355

D1504

CPU

CH

0.1

PI4/CK

PI5/DT

TS/SY

FI2/SY

VDDP

VDDX

1SS355

D1503

ZERO

VDD

CH

12P

C1572

VSSP

CKO/I

VSSX

1SS355

D1502

C1580

PCM1716E

PI2

PI3

VDD

PDO

VCOI

XI

X0

R1651

100K

R1518

R1516

R1515

R1514

R1513

R1512

R1511

R1510

R1509

R1508

R1507

R1506

R1505

C1573

470K

470K

470K

R1679

VCC2L

VCC2R

0.1

NM

0

49

50