Page 1

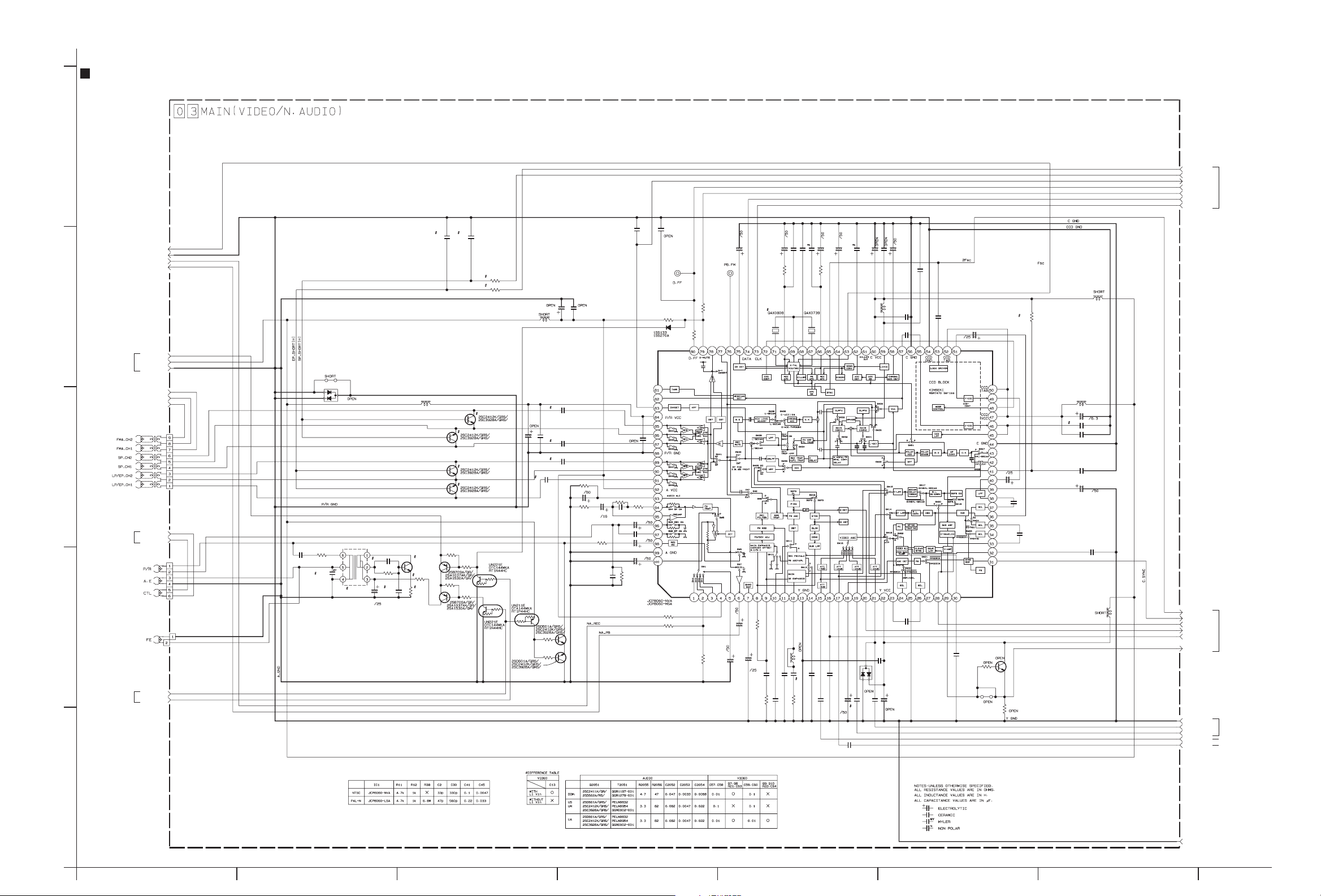

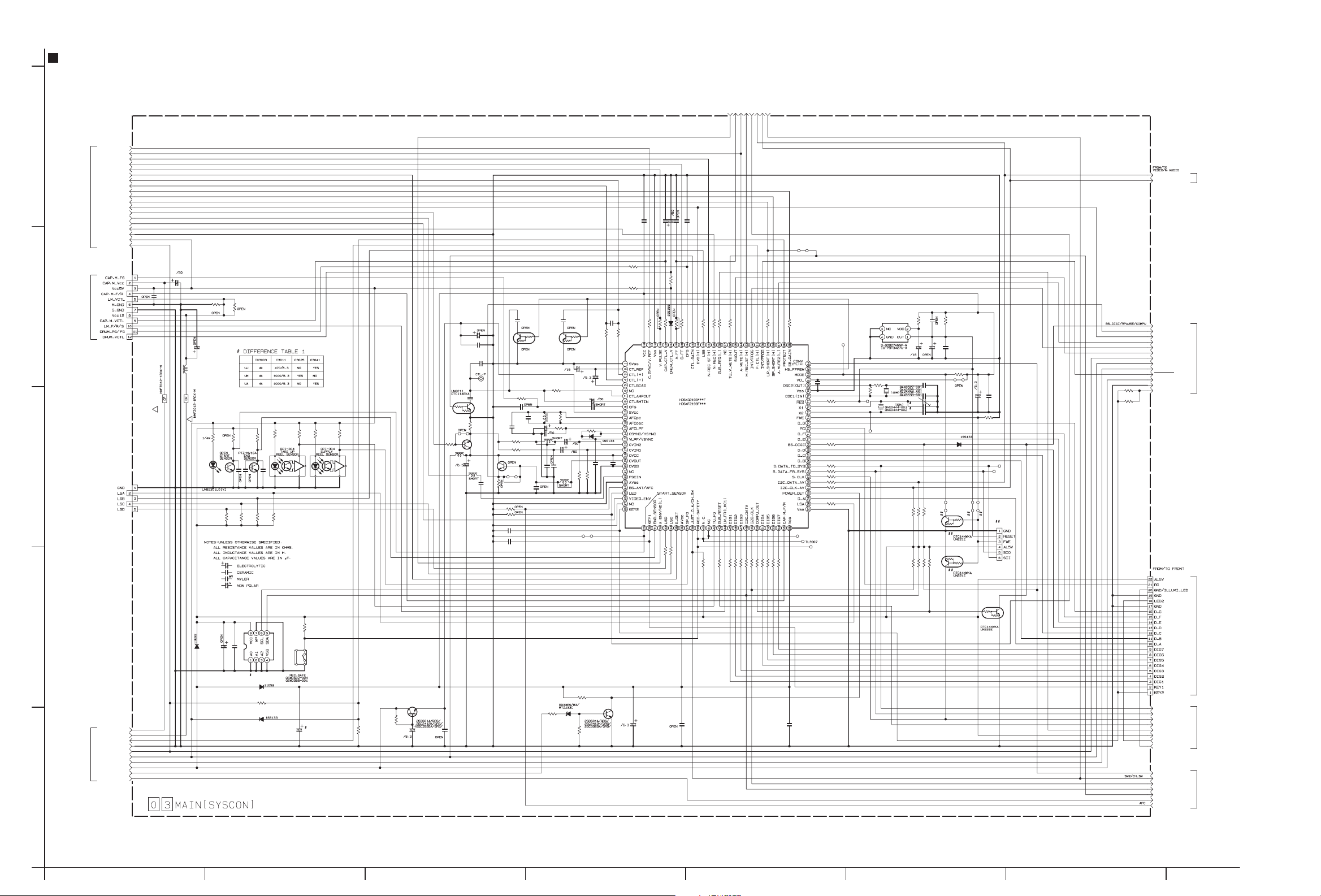

SCHEMATIC DIAGRAMS

DVD PLAYER & VIDEO CASSETTE RECORDER

HR-XVC27UA,HR-XVC27UM,

HR-XVC29UJ

CD-ROM No.SML200409

(UM, UJ model)

(UA model)

HR-XVC27UA, HR-XVC27UM, HR-XVC29UJ [D3PV0]

For disassembling and assembling of MECHANISM ASSEMBLY, refer to the SERVICE MANUAL No.86700 (MECHANISM ASSEMBLY).

Regarding service information other than these sections, refer to the service manual No. YD008 (HR-XVC27US).

Also, be sure to note important safety precautions provided in the service manual.

COPYRIGHT © 2004 Victor Company of Japan, Limited.

No.YD023SCH

2004/8

Page 2

CHARTS AND DIAGRAMS

MAIN(VIDEO/N.AUDIO) SCHEMATIC DIAGRAM

5

LP_SHORT[H]

SP_SHORT[H]

VIDEO_ENV

D.FF

A.MUTE[H]

I2C_DATA_A/V

I2C_CLK_A/V

TO SYSCON

SHEET 2

C63

C64

0.01

TO FMA/DEMOD

Fsc

GND

NA_REC

NA_PB

4

TO SYSCON

SHEET 2

SW12V

SW5V

TO FMA/DEMOD

FMA_CH1

FMA_COM

FMA_CH2

TO DRUM

GND

CN1

B10

D1

L10

3

TO SYSCON

SHEET 2

2

TO SYSCON

SHEET 2

CTL[+]

CTL[-]

CN2001

CN2002

N.REC[H]

N.REC_ST[H]

C2051

T2051

C2055

10

C2053

R2054

C2054

Q2051

R2056

12k

R2055

R2053

10k

330p

C2052

0.01

R21

2.2k

2.2k

R22

L2001

10

µ

R2057

R2059

47k

Q2052

47k

Q2054

Q8

Q9

Q10

R2058

R2060

Q7

Q2053

18k

18k

Q2055

Q2003

Q2002

C61

C78

0.1

C60

Q2001

R2018

4.7k

R2019

4.7k

C2004C2003

C57

C58

C59

R2021

33k

C2005

4.7

R2014

390k

R2015

270

C2006

C2007

0.0068

22

C2008

C2010

R2017

C2011

22k

C2012

C2009 R2016

0.001 33k

C55C56

0.1

TP111

R2022

10k

D2001

R37

10k

C62

R2013

12k

4.7

680p

4.7

4.7

IC1

R2024

10k

R2007

12k

12k

R2010

R2023

10k

TP106

1

C2002

C2001

C49

4.7

X1

4.7

R1

6.2k

C4

10

C1

150p

R2

C5

0.1

1.5k

C48

C47

0.022

0.47

R11

4.7k

L1

C6

0.1 0.1

C2

R3

8.2k

C45

C46

0.033

C44

X2

C7

C11

1

C41

C43

3.3

2.2

R12

1k

C8

1

C9

2.2

C12

1

C38

C36

C39

1

C37

4p

µ

L7

12

C40

C35

0.01

C17

0.1

C15

0.1

D5

C14 C10

1

C13

1

C34

0.1

0.01

C33

10

C19

R6

0.1

B1

R38

C26

10

C24

0.1

C22

0.1

Q2

R7

L6

10

µ

L5

C31

47

C30

0.1

C77

0.01

C27

C25

3.3

C20

0.1

L3

2Fsc

C.SYNC/V.REF

V.PULSE

S_DET

SB_GAIN

V_TO_OSD

GND

F_V

L_1_V

TU_VIDEO

DVD_V_IN

TO SYSCON

SHEET 2

TO TERMINAL

SHEET 4

TO TUNER

TO TERMINAL

SHEET 4

1

UJ

GND

p10661001a_rev1

SHEET 1

A

BCD EFG

2-1 2-2

Page 3

MAIN(SYSCON) SCHEMATIC DIAGRAM

TO

FMA/DEMOD

A.ENV/ND[L]

A.FF

A.MUTE[H]

H.REC_ST[H]

I2C_DATA_A/V

LED

I2C_CLK_A/V

JUST_CLK/SW2

5

VIDEO/N.AUDIO

4

3

SHEET 1

CAPSTAN MDA

C.SYNC/V.REF

A.MUTE[H]

N.REC_ST[H]

V.PULSE

S_DET

CTL[+]

CTL[-]

SB_GAIN

TO

SP_SHORT[H]

LP_SHORT[H]

DVD[H]

V_TO_OSD

VIDEO_ENV

N.REC[H]

SW12V

CN3001

TO

ROTARY ENCODER

JS3001

D.FF

2Fsc

SW5V

I2C_DATA_A/V

I2C_CLK_A/V

0.047

R4017

R4004

C3033

1k

R4001

4.7k

1k

560

R4009

GND

C3071

33

C3056

R3253

R3252

C4001

C4002

C4031

µ

1

L4001

!

CP3002

CP4002

!

R3206 R3207

R3205

180

TO

D3001

Q3001 Q3002

R3217

1Ok

C3046

18k

C3045

C3008

0.01

R3215R3216

R3214

10k

10k10k

R3208R3210

R3211 R3209

120120

18k 18k

PC3001PC3002

0.01

C4005

180p

TP4001

Q4001

C4010

0.022

R212

B202

470

R211

100

Q202

L202

µ

10

C209

47

L203

C213

10p

R207

R3240

R3242

C3047

C3048

R4007

1K

C4003

L201

C201

15

22p

C210

0.01

C203

1000p

300

R205

R210

0Ω

Q201

B201

0.01

0.01

C4017C4018

Q4002Q4003

C4004

22

R4005

5.6k

R201

µ

470

R202

C202

4.7

10k

R203

L204

C205

4.7

C207

4.7

680p

L205

C206

C211

C208

B3003

C4015

220p

R4003

560

C4006

47

1

C4008

C4009

10K

D201

C204

680p

C212

0.01

R204

R206

470K

470K

R4013

0.1

C4011

2.2k

R4012

4.7k

R3033

0.22

R4015

D4002

4.7k

R3034

C4012

22k

R4010

C4016

4.7k

R36

IC3001

100p

C4014

4.7k

R3101

2.2k

R3256

1k

R3099

1k

R3098

1k

R3043

0Ω

R3096

1k

R3045

1k

R3046

1k

R3047

330

R3048

330

R3049

330

R3050

0Ω

R3089

1k1k1k

R3051

R3052

R3053

1k

R3054

1.8k

R3085

B3004

TL3908

C3050

TL3906

R3077

R3069

R3065

R3064

R3063

R3062

R3061

R3058

IC3002

TL3904

R3080

TL3905

R3229

1M

TL3903

100

X3002

X3001

0.1

1k

1k

270

1k

1k

330

330

4.7K

C3037

C3025

C3041

C3024

3.3k

R3236

3.3k

R3223

R3246

3.3k

R3235

3.3k

R3224

10k

C3055

C3036

47k

R3234

33k

R3244

R3248

4.7k

C3053

C3054C3052

0.002210

1k

R3082

12p

B3001

0.047

B3903

D3008

Q3901

Q3902

B3901

47

C3030

B3902

R3074

C3031

10k

TL3901

TL3902

CN3901

18p

30p

18p

12p

3.3k

R3243

R3202

R3201

COMPU_IO

V_FROM_OSD

DVD[H]

A.MUTE2[L]

INT/PRG

S1OUT

SW12V

SW5V

SW3.3V

INT/PROG

AL5.8V

GND

P/EJ

39k

10k

CN3102

TO

VIDEO/N.AUDIO

SHEET 1

TO TERMINAL

SHEET 4

R3225

2

0.047

C3022

C3021

D3005

IC3003

D3004

R3212

470k

D3002

26V

AL12V

P.CTL[H]

GND

TO SW.REG

SHEET 3

SW12V

SW3.3V

AL5.8V

SW5V

48V

BT2

10k

S3001

C3011

R3213

330k

R3222

10k

R3220

100k

D3003

R3218

Q3005

C3012

47

C3013

4.7k

R3219

4.7k

Q3004

C3016

C3014

47

C3072

0.047

1

Q3007

K_B.DATA_TO_SYS

K_B.DATA_FR_SYS

K_B.CLK

RESET_IN

REQ[L]

AL5V

LED2

ILLUMI_LED

CONV.CTL[H]

JUST_CLK/SW2

I2C_CLK

I2C_DATA

TU_V_MUTE[H]

BT2

AFC/BS_ANT

TO DISPLAY

CN7003

TO SUB CPU

TO TUNER

p10660001a_rev0

SHEET 2

A

BCDEFG

2-3 2-4

Page 4

MAIN(SW.REG) SCHEMATIC DIAGRAM

5

!

!

!

CN5001

!

F5001

T2AL

4

3

R5106

0.27

GROUND POINT FOR

PRIMARY VOLTAGE

!

C5003

100p

2

LF5002

C5001

! !

0.068

R5103

68k

C5104

1

Q5101

R5110

220k

D5106

R5113

100k

C5002

0.022

R5101

220k

R5102

220k

C5108

0.1

C5105

0.018

Q5102

Q5103

C5004

0.0022

K5101

PC5101

!

C5107

0.1

C5109

0.018

!

D5001

R5104

C5214

0.15

C5201

0.15

68k

270p

C5006

82

R5107

R5109

680

C5106

330

K5102

D5101

D5102

D5103

R5112D5105

220

R5111

1k

R5108

2.2k

R5202

1k

IC5201

C5102

0.0047

C5101

100p

R5201

220

R5203

1k

R5205

12k

!

T5001

R5206

3.3k

R5204

3.3k

D5201

C5203

100

DANGEROUS VOLTAGE

D5204

R5390

1k

C5213

120

D5205

D5206

D5212

D5208

D5209

C5207

4.7

GROUND POINT FOR

SECONDARY VOLTAGE

D5213

L5201

33µ

C5205

390

D5301

L5203

33µ

C5202

1200

L5202

33µ

C5204 C5209

1200 100

R5317

47k

C5211

100

C5210

100

R5326

R5392 R5393

390 390

D5308

D5309

CP5302

!

CP5304

C5306

1

R5325

100

R5395R5394

390390

Q5307

Q5315

D5310

IC5302

Q5391

B5393

C5314

100

D5391

C5307

470p

Q5305

R5391

!

CP5301

CP5303

B5311

B5392

C5308

2.2

R5310

4.7k

R5311

C5309

100

10k

D5305

R5319

56

C5301

100

Q5306

Q5304

D5304

Q5310

D5306

Q5311

C5303

2.2

IC5301

D5393

B5394

C5304

100

C5305

100

C5302

47

R5316

180

R5320

R5321

15k

47k

C5310

100

L5301

SHORT

Q5309

R5313R5312

1.2k1k

D5392

R5314

27k

R5315

27k

C5311

100

B5301

CP3101 CP3102D5207

L5302

SHORT

L5303

22µ

B5303

Q5308

C5312

100

C5313

100

26V

AL12V

48V

SW12V

TO

VIDEO/N.AUDIO,SYSCON

TUNER

BT2

TO

SYSCON,TUNER

TO

FMA/DEMOD,SYSCON

AL5.8V

!

TO

VIDEO/N.AUDIO,

SYSCON,TUNER

SW5V

TO SYSCON

P.CTL[H]

TO

VIDEO/N.AUDIO,

FMA/DEMOD,

SYSCON,TERMINAL

GND

TO

SYSCON,TERMINAL

SW3.3V

SW2V

S3.3V

A5V

S5V

GND

M5V

TO TERMINAL

M9V

TO SYSCON

TO TERMINAL

GND

1

p20438001a_rev0

SHEET 3

A

BCD EFG

2-5 2-6

Page 5

MAIN(TERMINAL) SCHEMATIC DIAGRAM

TO SW/JACK

CN7191

CN7103

5

LED1

P/EJ

GND

TO SYSCON

SHEET 2

TO FMA/DEMOD

4

TO SUB CPU

3

TO SW.REG

SHEET 3

2

TO SYSCON

SHEET 2

1

SW5V

SW12V

AL5.8V

INT/PROG

F.AUDIO[L]

F.AUDIO[R]

A.IN1[L]

A.IN1[R]

FMA_OUT[L]

FMA_OUT[R]

DVD_OUT[L]

DVD_OUT[R]

TO DVD

CN7303

SCLK

U2SDT

S2UDT

CPURST

SMUTE

TO DVD(2/2)

CN503

CN7302

S3.3V

SW2V

TO DVD(2/2)

CN501

CN7301

A.MUTE2[L]

INT/PRG

S1OUT

COMPU_IO

SW3.3V

GND

GND

UCS

SCS

GND

A5V

M9V

M5V

GND

S5V

GND

C8001

22

C8002

22

C7141

R8001

4.7k

R8002

4.7k

180

R7183

2.2k

R7184

R8004

TO VIDEO/N.AUDIO

SHEET 1

L_1_V

F_V

DVD_V_IN

GND

L7103

C7130

C7131

C7132

C7133

22

C7134

C7135

C7136

10^

R7136

R7135

220

0.01

0.1

0.1

1

1

R7181

Q7116

C7126

R7137

220

IC7104

Q7113

R7138

C7128

C7129

0.1

C7118

10

R7182

K7501

B7501

R7501

C7117

10

10

R8019

R8020

Q7201

C7202

5p

R7201

100

R7203

L7201

560

6.8^

R7202

1k

C7201C7203

3p33p

R7204R7205

1.5k

D8001

Q8053Q8052

Q8001

R8017

10k

C8053

Q8002

R8018

10k

L7202

R7206

1k

Q7202

C7204C7205

82

C7138

180

R7175

R8008

3.3k

C8051

R8010

2.2k

R7176

3.9k

C8005

820p

R8007

3.3k

C7139

100

82

R7177

R8009

3.9k

C8052

R7178

C7140

R7179

R8052

5.6k

R8053

5.6k

R8051

R7180

C8007

22

C8008

22

R8013

27k

R8014

27k

R8015

C8010

R8016

R8055

47k

R8054

47k

820

C8009

820

180

2.2k

R7173

R7174

C7137

C8003

820p

R8005R8003

2.7k1k

IC8001

R8006

2.7k

1k

C8004

820p

C8006

820p

K7502

C7119

0.1

L7101

10^

TO SYSCON

SHEET 2

IC7102

C7502C7501

0.1

B7502

DVD[H]

V_FROM_OSD

IC7501

TO TUNER

RF_VIDEO

C7123

470

R7502

300

R7503

300

C7109

R7131

75

J7002

J7002

J7002

J7002

C7114

470

C7124

470

C7503

4.7

C7125

470

R7134

75

C7120

R7154

470

75

C7121

R7155

75

0.01

R7156

10k

C7122

R7157

470

75

R7164

75

R7165

75

R7166

75

R7167

R7168

75

R7170

75

R7172

75

K7503

R7507

100k

C7507 C7508

47 0.1

R7506

10k

R7193

100

33

C7505

R7169

10k

R7171

10k

L7501

1^

C7504R7504

150p82

R7505

L7502

1^

C7506

0.1

J7006

J7010

J7009

J7004

J7004J7004

J7005

J7005

J7008

p10662001a_rev1

SHEET 4

A

BCDEFG

2-7 2-8

Page 6

MAIN CIRCUIT BOARD

<03>MAIN

LPB10258-001B

ST1

ST2

R5317

Q5305

R5313

R5314

Q5308

B5301

CN7301

D5001

K5102

D5209

D5204

Q5304

R5310

C8002

L8301

C5207

D5304

CP5301

Q5311

Q5307

R5312

R5315

R8003

R8005

C5102

D5101

C8003

R3218

C5002

D5102

C5213

C5302

L5302

Q5309

R8004

R8002

R8001

D3003

D5206

D5208

C5313

R8052

C8005

R8015

C8007

CN8301

R5104

D5205

CP5303

R5319

C5301

L5303

C8001

R8010

R8007

R8009

C8009

R8013

W50

R8017

R3219

T5001

C5204

B5394

IC8001

Q8001

D5213

C5209

D5393

C5312

C5311

C8004

R8053

Q8053

W2

C5006

C5101

R5320

R5321

R8008

C8051

R8019

Q3004

L5202

C5310

C8006

R8018

C8053

IC5301

C5314

R8006

C8052

R8301

L5301

C8301

D5301

L5201

R8051

R8020

C8010

Q8002

D3004

LF5002

C5205

CP5302

C7139

R7177

R7178

C8008

C8303

K5101

D5309

Q8052

R5106

Q5101

R5111

R5326

R5316

D5308

R5325

Q5315

CP5304

C7138

W22

R8014

R8016

R8055

R8054

IC8301

CN5001

C5001

FC5002

R5101 R5102

D5106

R5110

C5109

C5106

PC5101

R5202

D5201

R5390

C5202

C5211

C5210

C5306

Q5306

C5304

D5310

D5305

R5311

C5303

C7140

R7179

R7180

W25

R7175

R7176

CN7303

C3011

D8001

C8302

C5105

R5109

D5207

D5212

R5203

C5203

ZZ4

C5308

W24

CN7302

D8303

F5001

R5103

Q5102

L5203

R5395

C7137

R3220

R5113

D5306

R7174

C7205

C3014

C5201

R5206

R7173

C5003

FC5001

C5104

C5107

D5105

R5112

R5108

D5103

R5201

C5214

CP3101

Q5310

C5305

IC5302

C5307

C5309

W23

R7183

L7202

ZZ7

D8301

D8302

R5204

R7184

C7141

C7204

Q5103

R5107

IC5201

R5205

B5311

CP3102

D3005

Q7202

R7206

Q8301

C5108

R5392

R5394

DANGEROUS VOLTAGE

J7010

R7507

C7508

Q3001

C8202

K7501

CP3002

R7203

C7201

C7203

X8201

R8215

W1

C7506

R7501

R7202

R8207

R8214

B7501

Q7201

R8208

B5392

R8206

K8301

C5004

R8205

D5391

R5393

R7205

W45

R5391

C3046

R8262

R8263

Q5391

R7204

C7507

L7502

L7201

C7202

R8260

ZZ1

B5393

R8259

C8201

C7505

R7506

J7009

K7503

R7505

C7504

C7502

C7501

B7502

K7502

C7128

C7130

C4031

L4001

CP4002

B5303

R7201

R8252

R8250

R8251

W18

R8216

L7501

R7504

C7129

C7131

C3071

R8201

R7502

R3253

R7503

IC7501

C7132

R3252

IC8201

C7503

IC7104

C7133

W15

R8217

Q3007

R3243

R8204

J7006

C7134

R3214

W26

R3206

R8221

C7135

CN3001

W16

R8227

R8222

R8223

C7136

C7126

C3056

W29

JS3001

R8202

R8203

R3215

R3216

R7169

R7136

R3234

R7171

R7138

L7103

W6

W48

R3217

W19

W9

R7181

R3033

R3034

CN2001

Q7113

R7137

IC8202

W5

D3008

R3202

R3201

Q7116

R7135

W10

C8203

R7168

R7172

C2051

PC3002

W13

R7170

C7123

Q201

L205

B201

C209

L203

R7167

Q202

R207

C208

R3211

ZZ8

WR7

C7124

R3222

R211

R3210

W8

R212

R205

R210

ZZ2

Q3005

C211

L202

W7

Q2003

L204

B202

R206

W20

J7005

C7125

C4002

C3012

C206

C207

C203

C204

C205

R204

W21

C3072

CN3102

R7166

W47

L3

L6

ZZ5

C202

R202

D201

C213

C4001

C210

C3013

L201

R203

TL3908

WR8

L2001

C10

L5

C4017

Q4002

R4007

C201

R3240

B3003

C3048

W12

R7165

R2019

C14

B1

R201

R3045

R3043

C12

C4005

C4009

R7164

R2018

R6

R38

C4004

C4003

R3242

R3046

Q2002

C9

D3001

Q4003

R3047

R2007

C2001

C13

Q2

C4008

C4006

C212

C3047

R3050

L1

D5

C20

C24

C34

C4018

R3048

R7156

C2

C11

R7

C27

W37

W36

C4010

Q4001

R3049

C7121

Q2001

C17

C25

C26

R3051

J7004

C7120

R3

C8

R4005

C4015

R3052

R3054

C2003

C15

C19

C22

C77

C44

R4003

R3053

C2004

C7

C30

C31

C47

R3205

C2002

C6

C5

W27

R4004

C3016

R3058

J7008

WR3

R2201

C6501

C6513

W32

R2214

R2209

ZZ3

R2221

R2223

C2219

C2215

D2001

S3001

R2222

C2234

C6515

C2216

R2220

R3207

R7193

R2224

C2235

C2055

C3021

WR10

IC2201

C6514

C6605

R2219

T2051

Q2052

L6005

L6006

R2218

C2053

R2054

R3224

R2217

R2216

C2218

Q2201

R2056

R2059

Q2055

R3223

W49

CN2002

C3022

C6012

L6050

L6001

B6022

B6021

B6020

R2211

R2213

R3225

IC3003

L6003

C6005

C6007

C6532

C2052

Q2203

Q2204

R2212

R2053

Q2054

R2060

ZZ6

R2210

Q2202

C6020

C6021

B6024

CF6031

Q2051

R2055

R6051

C6008

D6002

R6054

L6032

R6030

R6034

Q6031

Q3002

C3008

C3045

CN7103

C2054

CN3901

C6054

C6053

C6013

C6052

C6055

R6050

R6020

R6021

C6033

R6055

TU6001

C6006

B6025

R6031

Q6030

Q7

C2254

R2255

PC3001

R3085

B3903

C3054

IC3002

TL3902

W44

C2256

C2209

C2212

C7119

K2251

C2255

C2208

R2230

Q3902

C2262

C2261

C2230

C2231

R2231

R3213

C3031

J7002

C7109

D1

Q10

Q9

Q8

C2253

K2252

C2210

R3209

C3055

C3030

CN1

C2251

C2252

C6601

C2211

B3004

K2253

R3208

D3002

R7134

C2204

C2206

C2207

C2222

W31

R3212

Q3901

L7101

W41

W34

R6502

C7114

B10

C2203

C6602

ZZ9

B3902

C6502

C6503

R2207

R2208

R2206

C6504

C6517

C6516

R3235

C2205

C6508

C6505

WR5

C2202

R2205

C2220

C6509

R3256

R3074

R3236

R2203

R2204

WR2

B6601

TL3906

C2201

C2221

C6512

C6511

C2214

W30

R2057

R2058

R2202

R3244

Q2053

WR9

W43

W38

C40

R3063

C2012

R2017

L7

C4012

R4015

R36

C41

W33

X3002

X3001

TL3903

R3064

TP106

C2011

C2010

X2

D4002

C3041

R3062

R3061

R2016

IC1

C46

R12

R4001

C4016

C3050

R3065

C7122

C2009

C2006

C2008

C45

W35

R2022

C4014

R4010

R3229

W17

TP4001

C2007

R2014

C62

R4017

C3025

WR1

X1

C48

R11

R3101

C3037

R3080

C3024

R7182

TP111

R2013

R37

C55

C49

R3099

R3096

R3089

C3036

W14

TL3905

WR4

R2015

R2021

W40

R2023

C2257

C61

C56

C2259

B3001

W4

R7131

C7117

C7118

IC7102

C58

C78

W39

L2251

C3053

R3246

R3077

W11

C2005

L10

C64

C63

R22

R21

R3098

TL3904

W46

C60

C59

C57

R2252

R2257

R2251

D2251

R3248

C3052

TL3901

R3082

B3901

R7157

R7155

R7154

TP2253

R2024

C4

R2010

W42

R2

C1

R1

C33

C36

C39

C37

C35

C38

C43

W28

R4009

C3033

R4013

C4011

R4012

IC3001

W3

2-9 2-10

Page 7

COMPONENT PARTS LOCATION GUIDE <MAIN> LPB10258-001B

REF.NO. LOCATION REF.NO. LOCATION REF.NO. LOCATION REF.NO. LOCATION REF.NO. LOCATION REF.NO. LOCATION REF.NO. LOCATION

CAPACITOR

C1 B C 15L

C2 B C 14M

C4 A D 15M

C5 B C 14M

C6 B C 14M

C7 B C 14L

C8 B C 14L

C9 A D 13L

C10 A D 13L

C11 B C 14L

C12 B C 13L

C13 B C 13L

C14 B C 13L

C15 B C 14L

C17 B C 14L

C19 B C 14K

C20 B C 14K

C22 B C 14K

C24 B C 14K

C25 A D 14K

C26 A D 14J

C27 B C 14J

C30 B C 14J

C31 A D 15J

C33 A D 15J

C34 B C 14J

C35 B C 15J

C36 A D 15J

C37 B C 15J

C38 B C 15I

C39 A D 15J

C40 B C 15J

C41 B C 16J

C43 A D 15I

C44 A D 14I

C45 B C 16J

C46 B C 16J

C47 A D 15I

C48 B C 16J

C49 A D 17J

C55 B C 17J

C56 B C 17K

C57 B C 17L

C58 B C 17L

C59 B C 17L

C60 B C 17M

C61 A D 17L

C62 A D 16L

C63 B C 17K

C64 B C 17K

C77 B C 14J

C78 B C 17L

C201 B C 13E

C202 A D 13F

C203 B C 13E

C204 B C 12E

C205 A D 12E

C206 B C 12E

C207 A D 12E

C208 B C 12E

C209 A D 11D

C210 B C 13F

C211 B C 12E

C212 B C 13E

C213 B C 13D

C2001 A D 14M

C2002 A D 14M

C2003 A D 14M

C2004 B C 14M

C2005 A D 17M

C2006 B C 16M

C2007 A D 16M

C2008 A D 16L

C2009 B C 16M

C2010 B C 16M

C2011 A D 16M

C2012 A D 15M

C2051 B C 11M

C2052 A D 21I

C2053 B C 20D

C2054 B C 21D

C2055 A D 20C

C2201 A D 19M

C2202 A D 19M

C2203 A D 19L

C2204 A D 18L

C2205 A D 18K

C2206 A D 18K

C2207 B C 18K

C2208 B C 17J

C2209 A D 18G

C2210 A D 18G

C2211 A D 18H

C2212 A D 18G

C2214 A D 19G

C2215 A D 20G

C2216 A D 20G

C2218 A D 20H

C2219 A D 20H

C2220 A D 19I

C2221 B C 19I

C2222 B C 18H

C2230 B C 18I

C2231 B C 18I

C2234 B C 20J

C2235 B C 19J

C2251 B C 18K

C2252 B C 18K

C2253 B C 18K

C2254 A D 17J

C2255 B C 18J

C2256 B C 17K

C2257 B C 17I

C2259 A D 17J

C2261 B C 18J

C2262 B C 18K

C3008 B C 21H

C3011 A D 4C

C3012 A D 12F

C3013 B C 13F

C3014 A D 5C

C3016 B C 15C

C3021 A D 20A

C3022 B C 20A

C3024 B C 16C

C3025 A D 17C

C3030 A D 18C

C3031 B C 18C

C3033 B C 15F

C3036 B C 16C

C3037 B C 16D

C3041 B C 16C

C3045 B C 21H

C3046 B C 6H

C3047 B C 13D

C3048 B C 13D

C3050 B C 16D

C3052 A D 17C

C3053 B C 17C

C3054 B C 17C

C3055 A D 17C

C3056 B C 9J

C3071 A D 8J

C3072 B C 13C

C4001 A D 13F

C4002 B C 12F

C4003 B C 13E

C4004 A D 13F

C4005 B C 13F

C4006 A D 14F

C4008 A D 13F

C4009 B C 13E

C4010 B C 14F

C4011 B C 15F

C4012 A D 15E

C4014 B C 16E

C4015 B C 14E

C4016 B C 16E

C4017 A D 13F

C4018 B C 14F

C4031 A D 8J

C5001 A D 4P

C5002 A D 2P

C5003 A D 5P

C5004 A D 6L

C5006 A D 2N

C5101 A D 2M

C5102 A D 2N

C5104 A D 5N

C5105 A D 4M

C5106 B C 4L

C5107 A D 5M

C5108 B C 5M

C5109 B C 4M

C5201 A D 5K

C5202 A D 4I

C5203 A D 4J

C5204 A D 2I

C5205 A D 3I

C5207 A D 1I

C5209 A D 2H

C5210 A D 3H

C5211 A D 5I

C5213 A D 1J

C5214 B C 5K

C5301 A D 2G

C5302 A D 1H

C5303 A D 4G

C5304 A D 4G

C5305 A D 5G

C5306 B C 4G

C5307 B C 5G

C5308 B C 5F

C5309 A D 5F

C5310 A D 3G

C5311 A D 2E

C5312 A D 2F

C5313 A D 2E

C5314 A D 3F

C6005 A D 21M

C6006 B C 22M

C6007 A D 20L

C6008 B C 21M

C6012 A D 21O

C6013 B C 22O

C6020 B C 21N

C6021 B C 21N

C6033 B C 22J

C6052 B C 22O

C6053 B C 22O

C6054 B C 22O

C6055 B C 22O

C6501 B C 19K

C6502 A D 19M

C6503 A D 19K

C6504 B C 19H

C6505 A D 19G

C6508 B C 19H

C6509 B C 19H

C6511 B C 19H

C6512 B C 19H

C6513 A D 19H

C6514 B C 20I

C6515 A D 20I

C6516 A D 19G

C6517 B C 19H

C6532 B C 21K

C6601 A D 18H

C6602 A D 19H

C6605 A D 20I

C7109 A D 18O

C7114 A D 18O

C7117 A D 17O

C7118 A D 17O

C7119 B C 18O

C7120 A D 14O

C7121 B C 14O

C7122 A D 16P

C7123 A D 11O

C7124 A D 12O

C7125 A D 12O

C7126 B C 10K

C7128 A D 8M

C7129 B C 8M

C7130 B C 8L

C7131 B C 8L

C7132 B C 8L

C7133 A D 9L

C7134 B C 9L

C7135 B C 9K

C7136 B C 9L

C7137 B C 4E

C7138 B C 4D

C7139 B C 4E

C7140 B C 4E

C7141 B C 5E

C7201 B C 7E

C7202 B C 6E

C7203 B C 7E

C7204 B C 5D

C7205 A D 5D

C7501 A D 8O

C7502 B C 8O

C7503 A D 8O

C7504 B C 8O

C7505 B C 7P

C7506 B C 7O

C7507 A D 7O

C7508 B C 7P

C8001 A D 2D

C8002 A D 1D

C8003 B C 2C

C8004 B C 2D

C8005 B C 2C

C8006 B C 3D

C8007 A D 2C

C8008 A D 3D

C8009 B C 2C

C8010 B C 3C

C8051 A D 3D

C8052 A D 3C

C8053 B C 3C

C8201 A D 7B

C8202 B C 7B

C8203 B C 10B

C8301 A D 3B

C8302 B C 4A

C8303 B C 3A

CONNECTOR

CN1 A D 18K

CN2001 A D 11M

CN2002 A D 21J

CN3001 A D 9J

CN3102 A D 12A

CN3901 A D 22B

CN5001 A D 4P

CN7103 A D 22E

CN7301 A D 1E

CN7302 A D 4E

CN7303 A D 4C

CN8301 A D 2A

DIODE

D1 B C 18N

D5 B C 14L

D201 A D 13E

D2001 A D 20D

D2251 A D 17G

D3001 A D 14G

D3002 A D 18D

D3003 A D 2B

D3004 A D 3B

D3005 A D 5F

D3008 A D 10A

D4002 A D 16E

D5001 B C 1O

D5101 A D 2M

D5102 A D 2M

D5103 A D 5L

D5105 A D 5M

D5106 A D 5N

D5201 A D 4K

D5204 A D 1K

D5205 A D 2J

D5206 A D 2J

D5207 A D 4K

D5208 A D 2K

D5209 A D 1K

D5212 A D 4K

D5213 A D 2K

D5301 A D 3H

D5304 A D 2H

D5305 A D 4G

D5306 A D 5G

D5308 A D 3H

D5309 A D 3H

D5310 A D 4G

D5391 A D 6K

D5392 A D 3F

D5393 A D 2G

D6002 A D 21M

D8001 A D 4C

D8301 A D 5B

D8302 A D 5B

D8303 A D 4B

IC

IC1 B C 15K

IC2201 B C 18J

IC3001 B C 15D

IC3002 B C 17C

IC3003 B C 21A

IC5201 A D 5K

IC5301 A D 3G

IC5302 B C 5G

IC7102 B C 17O

IC7104 B C 9L

IC7501 B C 8N

IC8001 B C 2C

IC8201 B C 8B

IC8202 B C 10C

IC8301 A D 5B

COIL

L1 A D 14L

L3 A D 13L

L5 A D 13K

L6 A D 13J

L7 A D 16J

L10 A D 17K

L201 A D 13E

L202 A D 12D

L203 A D 11D

L204 A D 12F

L205 A D 11E

L2001 A D 12M

L2251 A D 17J

L4001 A D 8J

L5201 A D 3H

L5202 A D 2H

L5203 A D 4I

L5301 A D 3E

L5302 A D 2G

L5303 A D 2E

L6001 A D 21L

L6003 A D 21O

L6005 A D 21M

L6006 A D 20L

L6032 A D 22J

L6050 A D 21O

L7101 A D 19O

L7103 A D 10K

L7201 A D 7E

L7202 A D 5D

L7501 A D 8O

L7502 A D 7O

L8301 A D 1C

LF5002 A D 3O

TRANSISTOR

Q2 B C 14L

Q7 B C 17K

Q8 B C 18L

Q9 B C 18L

Q10 B C 18M

Q201 B C 12E

Q202 B C 12F

Q2001 B C 14N

Q2002 B C 14N

Q2003 B C 12M

Q2051 B C 21D

Q2052 B C 20C

Q2053 B C 20C

Q2054 B C 21C

Q2055 B C 20C

Q2201 B C 20F

Q2202 B C 21F

Q2203 B C 21G

Q2204 B C 20G

Q3001 A D 7H

Q3002 A D 21H

Q3004 B C 2B

Q3005 B C 12F

Q3007 B C 9H

Q3901 B C 19C

Q3902 B C 18B

Q4001 B C 14E

Q4002 B C 13E

Q4003 B C 13E

Q5101 A D 4M

Q5102 A D 5L

Q5103 B C 5N

Q5304 A D 2H

Q5305 B C 1H

Q5306 A D 4H

Q5307 B C 1G

Q5308 B C 1F

Q5309 B C 1F

Q5310 A D 5H

Q5311 A D 2G

Q5315 A D 4F

Q5391 B C 7L

Q6030 B C 22J

Q6031 B C 22I

Q7113 B C 10L

Q7116 B C 10K

Q7201 B C 7E

Q7202 B C 6E

Q8001 B C 2C

Q8002 B C 3C

Q8052 B C 3C

Q8053 B C 3B

Q8301 B C 5B

RESISTOR

R1 B C 15L

R2 B C 15M

R3 B C 14M

R6 B C 13K

R7 B C 14K

R11 B C 16J

R12 B C 16J

R21 B C 17J

R22 B C 17J

R36 B C 16E

R37 B C 16K

R38 B C 13K

R201 B C 13E

R202 B C 13F

R203 B C 13E

R204 B C 13E

R205 B C 12F

R206 B C 12E

R207 B C 12E

R210 B C 12E

R211 A D 12F

R212 B C 12E

R2007 B C 14M

R2010 B C 15M

R2013 B C 16M

R2014 B C 16M

R2015 B C 17M

R2016 B C 16M

R2017 B C 15M

R2018 B C 13N

R2019 B C 13N

R2021 B C 17M

R2022 B C 16H

R2023 A D 17I

R2024 B C 15M

R2053 B C 21D

R2054 B C 20C

R2055 B C 21D

R2056 A D 20C

R2057 B C 20C

R2058 B C 20C

R2059 B C 20C

R2060 B C 21B

R2201 B C 19K

R2202 B C 19K

R2203 B C 19K

R2204 B C 19K

R2205 B C 19K

R2206 B C 19K

R2207 B C 19K

R2208 B C 19K

R2209 A D 20F

R2210 B C 21F

R2211 B C 20H

R2212 B C 21G

R2213 B C 21F

R2214 A D 20F

R2216 B C 20H

R2217 B C 20H

R2218 B C 20G

R2219 B C 20H

R2220 B C 20F

R2221 B C 19K

R2222 B C 20K

R2223 B C 20K

R2224 B C 20K

R2230 B C 18H

R2231 B C 18H

R2251 B C 17I

R2252 B C 17J

R2255 B C 18I

R2257 B C 17J

R3033 A D 11E

R3034 A D 11E

R3043 B C 13C

R3045 B C 13C

R3046 B C 13C

R3047 B C 14C

R3048 B C 14C

R3049 B C 14C

R3050 B C 13C

R3051 B C 14C

R3052 B C 14C

R3053 B C 14C

R3054 B C 14C

R3058 B C 15C

R3061 A D 15B

R3062 A D 15C

R3063 B C 15B

R3064 B C 16B

R3065 B C 16B

R3069 A D 15B

R3074 B C 19C

R3077 B C 17C

R3080 B C 16D

R3082 B C 17D

R3085 B C 17D

R3089 B C 17D

R3096 B C 17E

R3098 B C 17E

R3099 B C 17E

R3101 B C 16E

R3201 B C 10A

R3202 B C 10A

R3205 A D 15G

R3206 B C 9E

R3207 A D 20E

R3208 B C 18D

R3209 B C 18D

R3210 B C 12D

R3211 B C 11D

R3212 A D 19D

R3213 B C 18D

R3214 B C 9F

R3215 B C 10F

R3216 B C 10F

R3217 B C 10F

R3218 B C 1B

R3219 B C 2B

R3220 A D 5C

R3222 B C 12F

R3223 B C 20B

R3224 B C 20B

R3225 B C 21B

R3229 B C 16D

R3234 A D 10B

R3235 A D 19B

R3236 A D 19B

R3240 B C 13D

R3242 B C 13D

R3243 A D 9G

R3244 B C 19E

R3246 B C 17C

R3248 B C 17C

R3252 B C 8J

R3253 B C 8J

R3256 B C 19E

R4001 B C 16E

R4003 B C 14E

R4004 B C 14E

R4005 B C 14E

R4007 B C 13E

R4009 B C 15F

R4010 B C 16E

R4012 B C 15E

R4013 B C 15E

R4015 B C 16E

R4017 B C 16E

R5101 A D 4N

R5102 A D 4N

R5103 A D 5N

R5104 A D 2M

R5106 A D 3N

R5107 A D 5M

R5108 B C 5L

R5109 B C 4M

R5110 B C 4M

R5111 B C 4L

R5112 B C 5L

R5113 B C 5N

R5201 A D 5K

R5202 B C 4K

R5203 B C 5J

R5204 B C 5J

R5205 B C 5J

R5206 B C 5J

R5310 B C 1H

R5311 B C 4G

R5312 B C 1G

R5313 B C 1G

R5314 B C 1G

R5315 B C 1G

R5316 A D 4H

R5317 B C 1J

R5319 B C 2G

R5320 B C 3G

R5321 B C 3G

R5325 B C 4F

R5326 A D 4H

R5390 A D 4J

R5391 B C 6K

R5392 A D 5H

R5393 A D 5H

R5394 A D 5G

R5395 A D 5H

R6020 B C 22N

R6021 B C 22M

R6030 B C 22J

R6031 B C 22K

R6034 B C 22I

R6050 B C 22O

R6051 A D 21O

R6054 B C 21O

R6055 B C 22P

R6502 B C 19H

R7131 B C 17P

R7134 B C 18O

R7135 B C 10K

R7136 B C 10L

R7137 B C 10L

R7138 A D 10L

R7154 A D 15O

R7155 B C 14O

R7156 B C 14O

R7157 A D 15P

R7164 A D 13O

R7165 A D 13O

R7166 A D 13O

R7167 B C 11P

R7168 B C 11P

R7169 B C 10P

R7170 B C 11P

R7171 B C 10P

R7172 B C 11O

R7173 B C 5E

R7174 B C 5E

R7175 B C 4D

R7176 B C 4D

R7177 B C 4E

R7178 B C 4E

R7179 B C 4E

R7180 B C 4E

R7181 B C 10K

R7182 A D 17O

R7183 B C 5E

R7184 B C 5E

R7193 B C 20O

R7201 A D 8E

R7202 B C 7E

R7203 B C 7E

R7204 B C 6E

R7205 B C 6E

R7206 B C 6D

R7501 B C 7O

R7502 B C 8O

R7503 B C 8O

R7504 B C 8O

R7505 B C 8O

R7506 B C 8P

R7507 B C 7O

R8001 B C 2D

R8002 B C 2D

R8003 B C 1C

R8004 B C 2D

R8005 B C 1C

R8006 B C 3D

R8007 B C 2C

R8008 B C 2D

R8009 B C 2C

R8010 B C 2D

R8013 B C 2C

R8014 B C 3D

R8015 B C 2C

R8016 B C 3D

R8017 B C 2C

R8018 B C 3C

R8019 B C 3C

R8020 B C 3C

R8051 A D 3D

R8052 B C 2D

R8053 B C 2C

R8054 B C 3C

R8055 B C 3C

R8201 B C 8B

R8202 B C 10B

R8203 B C 10B

R8204 B C 9B

R8205 B C 6B

R8206 B C 6B

R8207 B C 7D

R8208 B C 7B

R8214 B C 7A

R8215 B C 7A

R8216 B C 8A

R8217 B C 9B

R8221 B C 9B

R8222 B C 9B

R8223 B C 9B

R8227 B C 9B

R8250 B C 8D

R8251 B C 8D

R8252 B C 7D

R8259 B C 6C

R8260 B C 6C

R8262 B C 6B

R8263 B C 6B

R8301 A D 3B

OTHER

CF6031 A D 21J

CP3002 B C 8I

CP3101 B C 5H

CP3102 A D 5F

CP4002 B C 8J

CP5301 A D 2H

CP5302 A D 3F

CP5303 B C 2H

CP5304 B C 3F

F5001 A D 5O

FC5001 A D 5O

FC5002 A D 4O

J7002 A D 18P

J7004 A D 14P

J7005 A D 13P

J7006 A D 10P

J7008 A D 20P

J7009 A D 8P

J7010 A D 7P

JS3001 A D 10F

K2251 B C 18K

K2252 B C 18K

K2253 B C 18K

K5101 A D 4M

K5102 A D 1M

K7501 B C 7O

K7502 B C 8N

K7503 B C 8P

K8301 B C 6A

PC085 B C 21A

PC01343 B C 5H

PC02242 B C 2Q

PC02505 B C 22N

PC3001 A D 17E

PC3002 A D 11E

PC5101 A D 5L

S3001 A D 20B

T2051 A D 20D

T5001 A D 2L

TL3901 B C 17B

TL3902 B C 17B

TL3903 B C 16C

TL3904 B C 17D

TL3905 B C 17C

TL3906 B C 19B

TL3908 B C 13C

TP106 A D 16O

TP111 A D 16O

TP2253 A D 15O

TP4001 A D 16O

TU6001 A D 22P

WR11 A D 4H

X1 A D 16J

X2 A D 16J

X3001 A D 16C

X3002 A D 16C

X8201 A D 7B

VOLTAGE CHARTS

<MAIN>

MODE

REC PLAY

PIN NO.

IC1

1 0 0

2 0 0

3 0 0

4 0 4.4

5 2.0 2.0

6 2.5 2.5

7 2.8 0

8 0 1.4

9 1.8 1.3

10 2.3 1.9

11 2.6 3.0

12 0 0

13 0 0

14 2.7 2.4

15 1.2 2.8

16 0 0

17 2.8 2.8

18 1.9 0

19 2.8 2.8

20 0 0

21 2.8 0

22 5.0 5.1

23 2.3 2.3

24 0 0.2

25 0 0

26 3.0 2.8

27 0 0

28 0 0

29 0 2.4

30 2.7 0

31 0.4 0.3

32 2.3 2.7

33 2.0 2.1

34 1.7 1.7

35 3.0 3.0

36 0 2.3

37 3.0 3.0

38 2.1 2.1

39 1.4 1.4

40 2.1 2.0

41 2.6 0

42 1.9 1.9

43 2.1 0

44 0 0

45 3.1 3.1

46 3.1 3.1

47 5.0 0

48 5.0 0

49 3.2 3.2

50 5.0 5.1

51 2.1 2.1

52 5.0 5.1

53 0 2.6

54 0 0

55 2.0 2.1

56 0 0

57 0 2.1

58 2.3 0

59 5.0 5.1

60 5.0 0

61 0 0

62 2.3 0

63 2.2 0

64 2.9 3.0

65 2.2 2.2

66 2.9 3.0

67 0 2.2

68 1.2 0

69 0 1.9

70 2.7 1.3

71 0 0

72 5.0 5.0

73 4.7 4.7

74 4.7 4.7

75 0 0

76 0 2.2

77 2.8 2.8

78 0 0

79 0.5 2.5

80 2.5 2.5

81 0 0

82 0 0

83 0 3.7

84 5.0 5.0

85 2.4 0

86 2.3 2.3

87 2.4 0

88 0 0

89 0 0

90 0 0

91 0 0

92 4.9 5.1

93 1.5 0

94 2.5 0

95 2.5 2.5

96 2.5 0

MODE

REC PLAY

PIN NO.

97 0 0

98 2.3 0

99 0 0

100 2.5 2.5

IC2201

1 2.4 2.4

2 0 0

3 0 0

4 0 0

5 0 0

6 2.5 2.5

7 2.0 2.0

8 0 0.4

9 0 0

10 0 0

11 0 0

12 2.0 2.0

13 2.6 2.6

14 0 0

15 0 0

16 2.5 2.5

17 0.8 0.8

18 2.4 0

19 2.4 2.5

20 2.0 0

21 1.9 0

22 1.9 0.6

23 0 0

24 2.0 0.6

25 5.0 5.1

26 2.0 0

27 0 2.4

28 4.2 2.8

29 4.2 1.8

30 2.1 0.9

31 1.0 2.5

32 2.5 2.5

33 2.5 2.5

34 0.9 0.9

35 2.5 2.6

36 0 0

37 1.6 1.6

38 0 0

39 0 0

40 5.0 5.0

41 0 0

42 4.7 4.7

43 4.7 4.7

44 2.5 2.3

45 0 0

46 3.4 3.5

47 2.9 2.4

48 2.2 2.2

49 3.3 3.5

50 0 3.5

51 5.0 5.1

52 2.5 0

53 4.3 4.4

54 2.4 2.4

55 0 0

56 2.0 0

57 4.3 4.4

58 10.6 10.7

59 4.4 4.4

60 1.1 0

61 2.5 2.5

62 2.4 0

63 2.6 2.6

64 0.8 0.5

IC3001

1 0 0

2 2.3 2.4

3 2.9 2.4

4 1.8 2.4

5 2.4 2.4

6 0 0

7 2.5 2.4

8 2.4 2.4

9 2.2 2.2

10 4.9 0

11 1.8 1.9

12 1.8 1.8

13 2.3 2.4

14 0.4 0.4

15 0.9 0.8

16 2.9 3.0

17 2.4 2.4

18 5.0 5.1

19 2.4 2.5

20 0 0

21 0 0

22 2.5 2.5

23 0 0

24 2.1 2.0

25 - 0

26 0 0

27 0 0

MODE

REC PLAY

PIN NO.

28 4.9 0

29 0 0

30 4.9 4.9

31 4.3 4.3

32 4.2 2.8

33 4.9 4.9

34 0 0

35 0 0

36 4.9 4.9

37 5.0 5.0

38 0 4.8

39 4.8 4.9

40 0 4.9

41 4.9 4.8

42 - 43 0 4.8

44 2.5 2.6

45 4.5 4.5

46 0 4.4

47 4.5 4.5

48 0 0

49 0 4.8

50 0 0

51 4.5 4.4

52 4.5 4.5

53 0 4.4

54 0 4.2

55 0 0.0

56 4.9 4.9

57 0 0

58 0 0

59 2.7 3.4

60 0 0

61 4.7 4.7

62 0 4.6

63 4.6 0.1

64 0 0

65 4.6 4.6

66 3.4 3.4

67 4.1 4.1

68 2.0 3.4

69 0.5 0

70 2.7 2.8

71 0 0

72 4.8 4.8

73 1.4 0.7

74 0 0.1

75 0 1.5

76 1.4 1.4

77 4.9 4.9

78 0 0

79 0 0

80 2.4 2.4

81 3.3 3.1

82 4.9 4.9

83 4.9 4.9

84 4.8 4.9

85 0 3.3

86 4.2 4.3

87 4.9 4.9

88 0 0

89 0 4.9

90 4.8 4.8

91 4.8 4.8

92 0 0

93 4.8 0

94 0 0

95 0 0

96 0 0

97 4.8 4.9

98 2.9 3.4

99 4.8 0

100 4.9 0

101 4.9 4.9

102 0 0

103 4.8 4.8

104 1.3 1.3

105 2.4 0

106 0 2.4

107 2.4 2.4

108 2.7 2.7

109 0 0

110 0 0

111 0.3 0.4

112 4.9 4.9

IC3002

1 4.9 4.9

2 4.9 4.9

3 0 0

4 0 0

IC3003

1 0 0

2 0 0

3 0 0

4 0 0

5 4.0 4.7

6 4.1 0.1

MODE

REC PLAY

PIN NO.

7 0 0

8 4.9 4.9

IC5201

1 2.5 2.5

2 0 0

3 4.5 4.5

IC5301

1 2.3 2.5

2 0 0

3 4.0 3.9

IC5302

1 5.0 5.0

2 0 0

3 0 0

4 3.4 3.3

5 5.1 5.1

6 0 0

7 5.6 5.6

IC7102

1 0 0

2 3.6 3.7

3 10.5 10.8

4 3.4 3.4

5 0 0

6 3.5 3.6

IC7104

1 5.0 5.1

2 2.4 2.4

3 5.0 5.1

4 1.1 1.1

5 0 0

6 1.3 1.4

7 0 0

8 2.4 0

9 4.8 0

10 1.4 1.4

11 0 0

12 0 2.4

13 5.0 0

14 2.4 2.4

15 0 0

16 2.4 2.4

17 0 0

18 2.4 2.4

19 0 0

20 1.7 1.7

21 1.7 1.7

22 0 0

23 1.6 1.7

24 0 0

25 0 0

26 2.4 2.4

27 0 0

28 5.0 5.1

IC7501

1 0 0

2 0 0

3 0 0

4 0 0

5 0 0

6 0 0

7 0 0

8 1.6 1.6

9 3.3 3.3

10 1.6 1.6

11 1.6 1.6

12 1.6 0

13 3.3 3.3

14 3.3 3.3

IC8001

1 5.3 5.4

2 5.3 5.4

3 0 5.4

4 0 0

5 5.3 5.4

6 5.3 0

7 0 5.4

8 10.6 10.8

IC8201

1 0 0

2 0 0

3 0 0

4 0 0

5 0 0

6 4.9 4.9

7 4.9 4.9

8 2.4 2.4

9 2.4 2.3

10 0 0

11 0 0

12 4.8 4.9

13 0 0

14 4.7 4.7

15 0 0

16 4.6 4.7

17 4.4 4.4

18 4.7 4.9

MODE

REC PLAY

PIN NO.

19 0 4.9

20 0 0

21 4.9 0

22 0 0

23 4.4 4.4

24 4.4 0

25 0 0

26 0 0

27 3.0 3.4

28 4.9 4.9

29 0 0

30 0 0

31 0 0

32 0 0

33 0 0

34 0 0

35 0 0

36 0 0

37 0 0

38 0 0

39 0 0

40 0 0

41 0 0

42 0 0

43 0 0

44 0 0

45 0 0

46 0 0

47 0 0

48 0 0

49 0 0

50 0 0

51 0 0

52 0 0

53 0 0

54 0 0

55 0 0

56 0 0

57 0 0

58 0 0

59 0 0

60 3.4 3.5

61 0 0

62 0 0

63 0 0

64 0 0

IC8202

1 3.3 3.3

2 4.9 4.9

3 4.9 0

4 4.9 4.9

5 0 4.9

6 0 0

7 0 0

8 4.9 4.9

9 4.9 4.9

10 3.3 3.3

11 4.9 0

12 0 0

13 3.3 3.0

14 4.9 4.9

IC8301

1 0 0

2 0.6 0.5

3 0.7 0.7

4 0.3 0.1

5 0 0

6 0 0

7 9.3 9.4

8 9.2 9.4

9 0.7 0.7

10 0.4 0.5

Q202

E 1.7 1.7

C 5.0 5.1

B 2.4 2.4

Q2001

E -5.4 0

C 0 0

B -13.9 0.7

Q2002

E -5.4 0

C 0 0

B -13.7 0.7

Q2003

E 5.0 5.1

C -13.7 5.0

B 4.8 0

Q2051

E 0 0

C 7.1 0.1

B 0.4 0.1

Q2052

E 10.5 10.8

C 10.3 0.2

B 9.8 10.7

Q2053

MODE

REC PLAY

PIN NO.

E 0 0

C 0 10.7

B 4.9 0

Q2054

E 10.3 0.4

C 10.0 0.2

B 9.5 0.3

Q2055

E 0 0

C 0 0.4

B 4.7 0

Q2201

E 5.6 5.6

C -0.2 -0.1

B 5.6 5.6

Q2202

E 0 0

C 5.6 5.6

B 0 0

Q2203

E 0 0

C 0 0

B 0 -0.1

Q2204

E 0 0

C 0 0

B -0.1 -0.2

Q3002

E 0 0

C 4.1 4.4

Q3004

E 0 0

C 0 0

B 0.7 0.7

Q3005

E 4.9 4.9

C 5.6 5.6

B 5.5 5.5

Q3007

E 0 0

C 0 0

B 0.5 0.5

Q3901

E 0 0

C 4.9 4.9

B 0 0

Q3902

E 0 0

C 4.6 4.6

B 0 0

Q4001

E 0 0

C 0 0

B 4.8 0

Q5101

S 0 0

G 4.0 3.8

D 132.0 133.0

Q5102

E 0 0

C 4.0 3.8

B 0.2 0.1

Q5103

E 3.9 3.8

C 0 0

B 9.9 10.0

Q5306

E 10.6 10.7

C 11.4 11.3

B 11.2 11.4

Q5307

E 51.3 50.6

C 51.3 50.5

B 0 0

Q5309

E 0 0

C 0 0

B 4.8 4.8

Q5310

E 5.1 5.1

C 5.6 5.6

B 5.9 5.9

Q5311

E 3.3 3.3

C 3.6 3.6

B 4.0 4.0

Q5315

E 9.3 9.5

C 11.4 11.4

B 10.1 10.0

Q6030

E 2.2 2.2

C 0 0

B 1.5 1.5

Q7113

E 2.3 2.3

C 0 0

MODE

REC PLAY

PIN NO.

B 1.6 1.7

Q8001

E 0 0

C 0 0

B 0.6 0.6

Q8002

E 0 0

C 0 0

B 0.6 0.6

Q8052

E 0 0

C 0 0

B 0.6 0.6

Q8053

E 5.6 5.6

C 5.6 5.6

B 0 0

TU6001

27 0 0

28 4.8 4.8

29 5.0 5.0

30 4.8 4.9

31 3.6 3.7

33 1.8 1.8

34 0 0.1

35 0 0.1

36 4.1 4.7

37 4.1 4.7

38 2.2 2.0

39 2.8 2.8

40 2.4 2.4

41 31.9 32.2

42 0 0.1

43 1.6 1.5

CN1

1 0 0

2 0 0

3 0 0

4 2.3 2.3

5 2.4 2.3

6 2.3 2.3

7 1.9 0

8 1.9 0

9 1.9 0

CN2001

1 0 0

2 0 0

3 0 0

4 0 0

5 2.2 2.4

6 2.5 2.5

CN2002

1 0 0.1

2 0 0

CN3001

1 2.3 2.3

2 11.4 11.4

3 5.1 5.2

4 0 0

5 11.3 11.3

6 0 0

7 0 0

8 11.4 11.3

9 2.7 2.7

10 2.6 2.5

11 1.3 1.3

12 2.6 2.6

CN3102

1 4.9 4.9

2 4.9 4.9

3 4.8 4.8

4 4.8 4.8

5 4.8 4.8

6 4.8 4.8

7 4.8 4.8

8 4.8 4.8

9 4.7 4.8

10 2.7 2.8

11 3.4 3.4

12 3.4 2.7

13 2.7 3.4

14 2.7 3.4

15 2.0 2.0

16 2.0 1.4

17 0 0

18 0 0

19 0 0

20 0 0

21 4.8 4.9

22 4.8 0.0

CN3901

1 0 0

2 4.9 4.9

3 0 0

4 4.9 4.9

5 0 0

6 4.6 4.6

MODE

REC PLAY

PIN NO.

CN7103

1 0 0.1

2 0 0

3 0 0

4 0 0

5 0 0

6 0 0

7 0 0

8 0 0

9 3.4 3.4

10 4.8 4.7

CN7301

1 2.4 2.4

2 0 0

3 0 2.4

4 0 0

5 5.0 5.0

6 0 0

7 0 0

8 9.4 9.5

9 5.0 5.0

10 5.0 5.0

11 0 0

12 0 0

13 3.3 3.3

14 3.3 3.3

15 3.3 3.3

16 0 0

17 1.6 1.6

18 0 0

19 3.2 3.3

CN7302

1 0.3 0.4

2 0 0

3 0.5 0.5

4 0 0

5 0.2 0.2

6 0 0

7 0.9 0.8

8 0 0

9 0.3 0.4

10 3.2 3.2

11 0 0

12 3.3 3.3

13 2.8 0

14 3.3 3.3

15 3.3 3.3

16 2.8 2.9

17 2.8 2.8

CN8301

1 0.5 0.5

2 0.5 0.5

3 0 0

4 0 0

5 0 0

JS3001

1 0 0

2 0 0

3 4.9 4.8

4 0 0

5 4.8 4.9

2-11 2-12

Page 8

Victor Company of Japan, Limited

AV & MULTIMEDIA COMPANY VIDEO DISPLAY CATEGORY 12, 3-chome, Moriya-cho, kanagawa-ku, Yokohama, kanagawa-prefecture, 221-8528, Japan

(No.YD023)

Printed in Japan

WPC

Loading...

Loading...