JRC NJG1523KB2 Datasheet

NJG1523KB2

SPDT SWITCH GaAs MMIC

KB2 Type

Top view

nGENERAL DESCRIPTION nPACKAGE OUTLINE

NJG1523KB2 is a SPDT switch IC featured low insertion

loss, medium handling power and high isolation.

This device is suitable for switching of Tx/Rx signals at

sub-microwave applications.

This switch exhibits wide frequency range from 50MHz to

3.0GHz at low operating voltage of 2.5V, and is operated

up to 25dBm at 3.0V operating voltage.

The ultra small & ultra thin FLP6 package is applied.

nFEATURES

lSingle low voltage control +2.5~+6.5V

lLow insertion loss 0.4dB typ. @f=1GHz, Pin=23dBm

0.5dB typ. @f=2GHz, Pin=23dBm

lHigh isolation 29dB typ. @f=2GHz, Pin=23dBm

lHandling power 25dBm max. @f=2GHz, V

lLow current consumption 8uA typ. @f=0.05~2.5GHz, Pin=23dBm

lUltra small & ultra thin package FLP6-B2 (Mount Size: 2.1x2.0x0.75mm)

nPIN CONFIGURATION

NJG1523KB2

=3.0V

CTL

nTRUTH TABLE

PC – P1 ON OFF

PC – P2 OFF ON

V

V

CTL1

CTL2

Orientation Mark

Pin connection

1

6

1.P1

2.GND

2

5

3.P2

4.V

CTL2

5.PC

3

“H”=V

CTL (H)

4

, “L”=V

CTL (L)

6.V

CTL1

H L L H

L H L H

Insertion loss=17dB

P1 return Loss=2dB

Insertion loss=17dB

P2 return Loss=2dB

Insertion loss=18dB

P1 return Loss=2dB

Insertion loss=18dB

P2 return Loss=2dB

Note: The values of insertion losses and return losses are the typical values at 2GHz.

- 1 -

NJG1523KB2

nABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL CONDITIONS RATINGS UNITS

(Ta=25°C)

Input Power P

Control Voltage V

Power Dissipation P

Operating Temp. T

Storage Temp. T

in

CTL

D

opr

stg

V

V

=0V, V

CTL (L)

CTL (H)-VCTL (L)

=2.7V 32 dBm

CTL (H)

7.5 V

450 mW

-30~+85 °C

-55~+125 °C

nELECTRICAL CHARACTERISTICS

(V

CTL (L)

=0V, V

=2.7V, ZS=Zl=50Ω, C6=10pF, Ta=25°C)

CTL (H)

PARAMETERS SYMBOL CONDITIONS MIN TYP MAX UNITS

Operating voltage (LOW) V

Operating voltage (HIGH) V

Control current I

CTL (L)

CTL (H)

CTL

f=2.0GHz, Pin=23dBm - 8 14 uA

-0.2 0 0.2 V

2.5 2.7 6.5 V

Insertion loss 1 LOSS1 f=1GHz, Pin=23dBm - 0.4 0.7 dB

Insertion loss 2 LOSS2 f=2GHz, Pin=23dBm - 0.5 0.8 dB

Isolation 1

(PC-P1, PC-P2, P1-P2)

Isolation 2

(PC-P1, PC-P2, P1-P2)

Maximum input power 1* Pin1 V

ISL1 f=1GHz, Pin=23dBm 27 29 - dB

ISL2 f=2GHz, Pin=23dBm 26 29 - dB

=2.7V, f=2GHz - - 24.0 dBm

CTL (H)

Maximum input power 2* Pin2 V

Maximum input power 3* Pin3 V

Pin at 1dB

compression point

P

-1dB

f=2.0GHz 28 30.5 - dBm

=3.0V, f=2GHz - - 25.0 dBm

CTL (H)

=6.5V, f=2GHz - - 34.5 dBm

CTL (H)

VSWR (PC, P1, P2) VSWR f=0.05~2.2GHz, ON State - 1.4 1.6

Switching time T

* Maximum input power: This value is defined as maximum input power of linear operating region

or damage free operating region

SW

fin=0.05~2.5GHz - 20 - ns

- 2 -

NJG1523KB2

nTERMINAL INFORMATION

CTL(H)

CTL(L)

CTL (H)

CTL(L)

No. SYMBOL DESCRIPTION

1 P1

2 GND

3 P2

4 V

CTL2

5 PC

6 V

CTL1

RF port. This port is connected with PC port by controlling 6th pin (V

to 2.5~6.5V and 4th pin(V

) to -0.2~+0.2V. An external capacitor is

required to block the DC bias voltage of internal circuit. (50~100MHz:

0.01uF, 0.1~0.5GHz: 1000pF, 0.5~2.5GHz: 56pF)

Ground terminal. Please connect this terminal with ground plane as close

as possible for excellent RF performance.

RF port. This port is connected with PC port by controlling 4th pin (V

to 2.5~6.5V and 6th pin(V

) to -0.2~+0.2V. An external capacitor is

required to block the DC bias voltage of internal circuit. (50~100MHz:

0.01uF, 0.1~0.5GHz: 1000pF, 0.5~2.5GHz: 56pF)

Control port 2. The voltage of this port controls PC to P2 state. The ‘ON’

and ‘OFF’ state is toggled by controlling voltage of this terminal such as

high-state (2.5~6.5V) or low-state (-0.2~+0.2V). The voltage of 6th pin

have to be set to opposite state. The bypass capacitor has to be chosen

to reduce switching time delay from 10pF~1000pF range.

Common RF port. In order to block the DC bias voltage of internal circuit,

an external capacitor is required. (50~100MHz:0.01uF, 0.1~0.5GHz:

1000pF, 0.5~2.5GHz: 56pF)

Control port 1. The voltage of this port controls PC to P2 state. The ‘ON’

and ‘OFF’ state is toggled by controlling voltage of this terminal such as

high-state (2.5~6.5V) or low-state (-0.2~+0.2V). The voltage of 4th pin

have to be set to opposite state. The bypass capacitor has to be chosen

to reduce switching time delay from 10pF~1000pF range.

)

)

- 3 -

NJG1523KB2

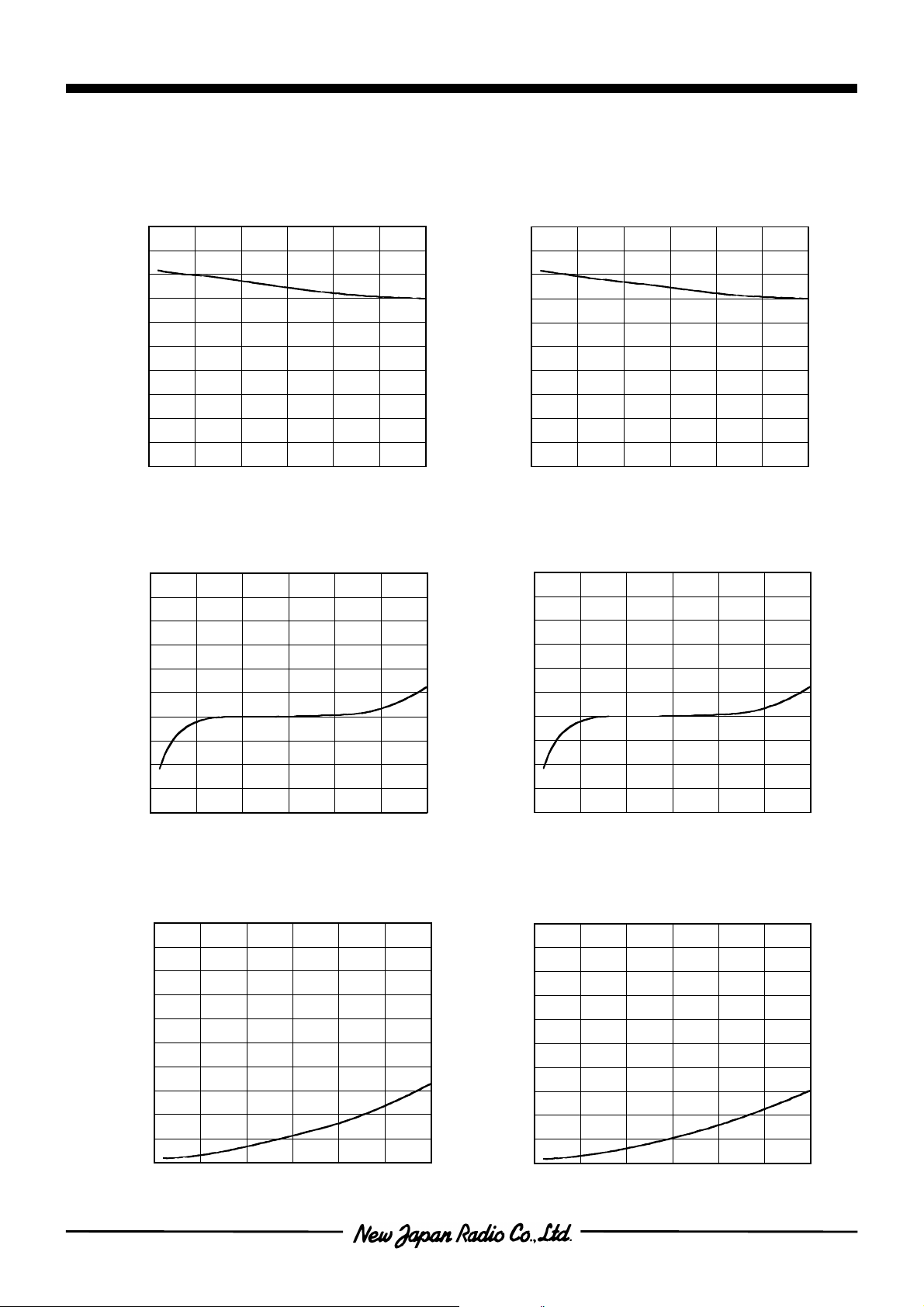

nELECTRICAL CHARACTERISTICS

(f=0.1~3.0GHz, with Application circuit, Losses of external circuit are excluded)

PC-P1 Insertion Loss vs. Frequency

(V

=2.7V,V

0

-0.4

-0.8

-1.2

Insertion Loss (dB)

-1.6

-2

0 0.5 1 1.5 2 2.5 3

CTL1

Frequency (GHz)

=0V,Pin=0dBm)

CTL2

PC-P1 Isolation vs. Frequency

(V

-10

=0V,V

0

CTL1

=2.7V,Pin=0dBm)

CTL2

PC-P2 Insertion Loss vs. Frequency

(V

=0V,V

0

-0.4

-0.8

-1.2

Insertion Loss (dB)

-1.6

-2

0 0.5 1 1.5 2 2.5 3

CTL1

=2.7V,Pin=0dBm)

CTL2

Frequency (GHz)

PC-P2 Isolation vs. Frequency

(V

-10

=2.7V,V

0

CTL1

=0V,Pin=0dBm)

CTL2

-20

-30

Isolation (dB)

-40

-50

0 0.5 1 1.5 2 2.5 3

Frequency (GHz)

PC-P1 VSWR vs. Frequency

(V

2.6

2.2

VSWR

1.8

1.4

=2.7V,V

3

CTL1

=0V,PC port)

CTL2

-20

-30

Isolation (dB)

-40

-50

0 0.5 1 1.5 2 2.5 3

Frequency (GHz)

P1-PC VSWR vs. Frequency

(V

2.6

2.2

VSWR

1.8

1.4

=2.7V,V

3

CTL1

=0V,P1 port)

CTL2

1

0 0.5 1 1.5 2 2.5 3

- 4 -

Frequency (GHz)

1

0 0.5 1 1.5 2 2.5 3

Frequency (GHz)

Loading...

Loading...