Page 1

查询STEL-2176供应商

STEL-2176

User Manual

STel-MAN-97709

STEL-2176

Digital Mod/Demod ASIC

16/64/256 QAM Receiver

with FEC

QPSK/16 QAM Transmitter

with FEC

R

Page 2

TRADEMARKS

Stanford Telecom and STEL are registered trademarks of Stanford Telecommunications, Incorporated.

STEL-2176 User Manual

Page 3

FOREWORD

The Telecom Component Products Division of Stanford Telecommunications, Inc., is pleased to provide its

customers with this copy of the STEL 2176 User Manual.

This User Manual contains product information for the STEL 2176 and is being provided to assist our customers in

understanding the advantages to be gained by integrating both the receiver and transmitter functions as an integral

portion of their cable modem chip.

Recipients of this User Manual should note that the content contained here-in is subject to change. The content of

this User Manual will be updated to reflect the latest technical data, without notice to the recipients of this

document.

User Manual STEL-2176

Page 4

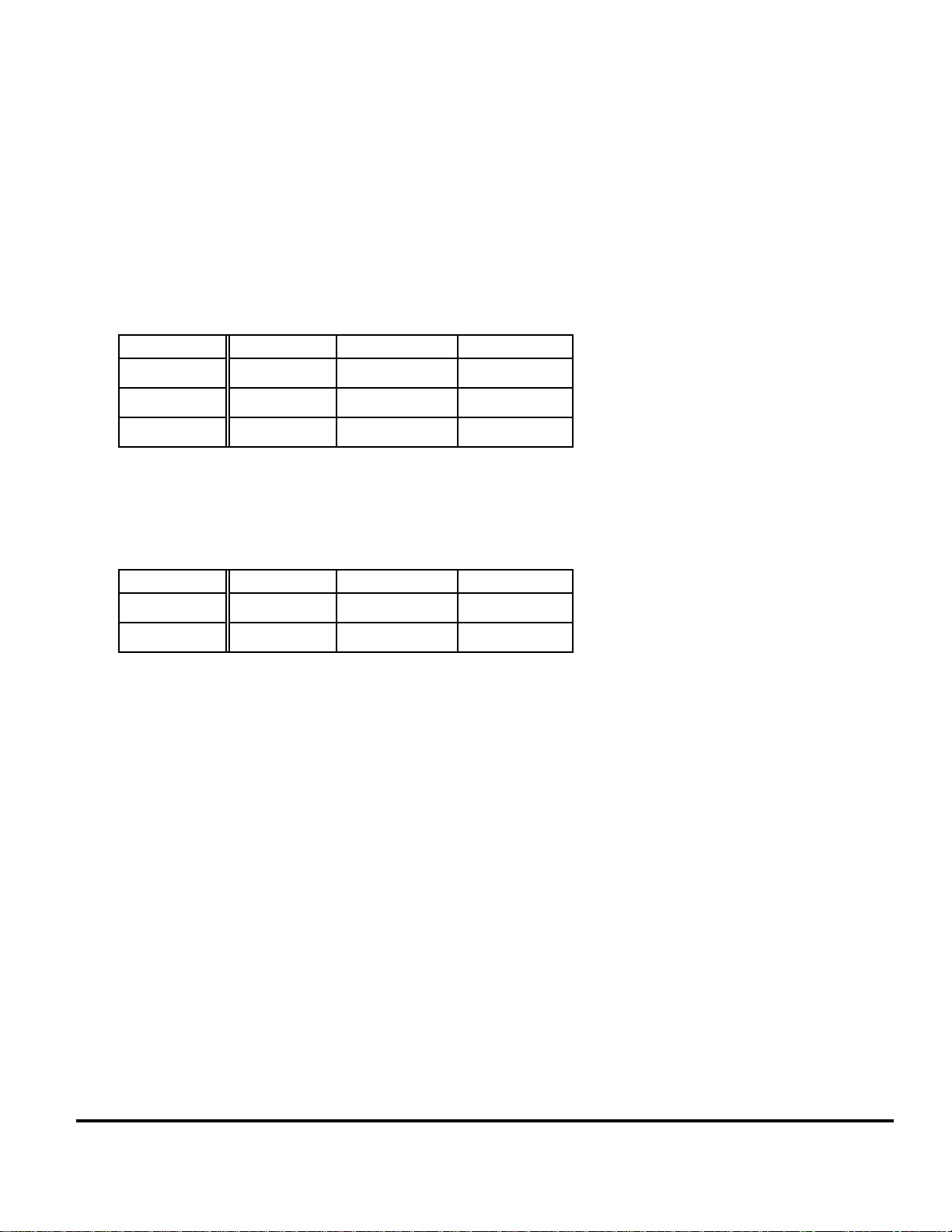

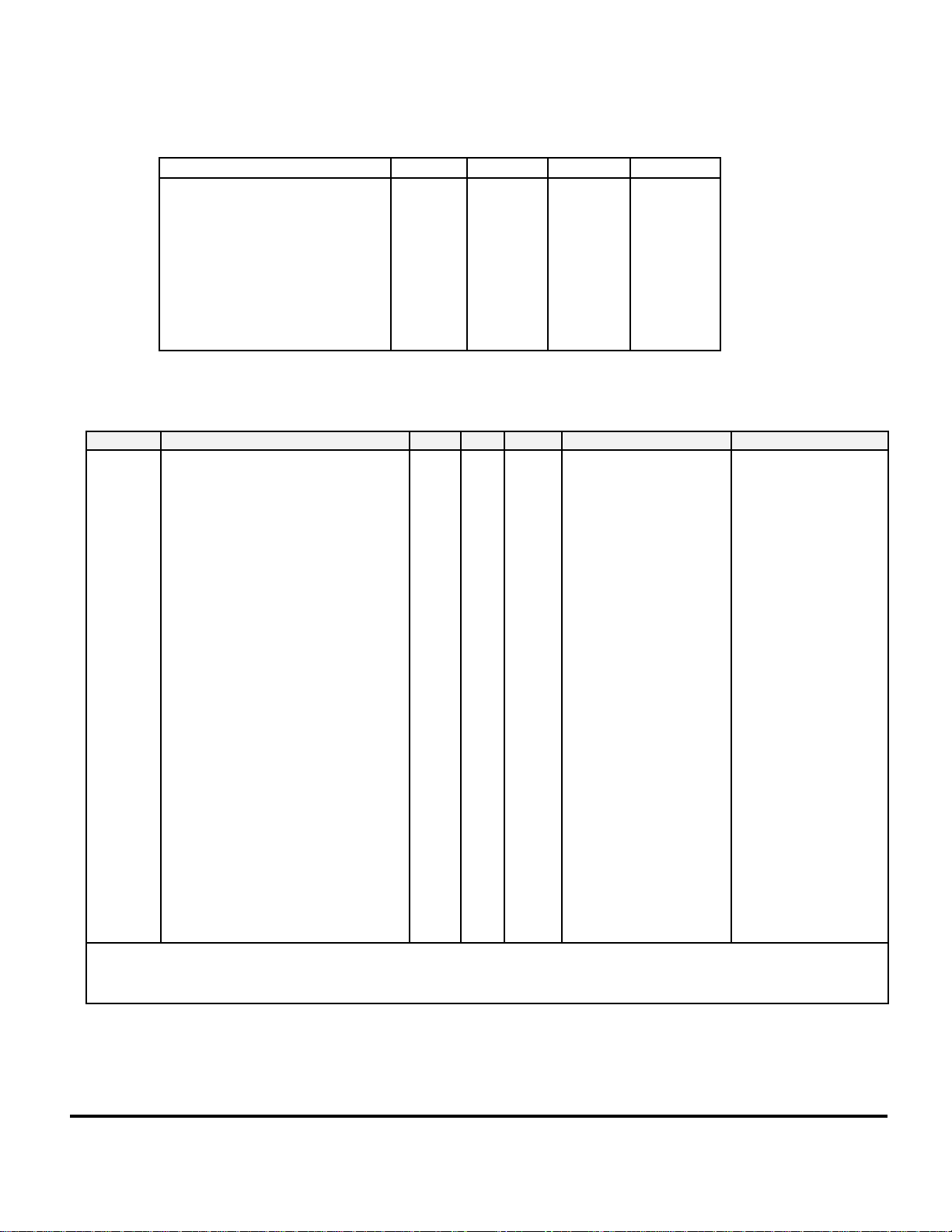

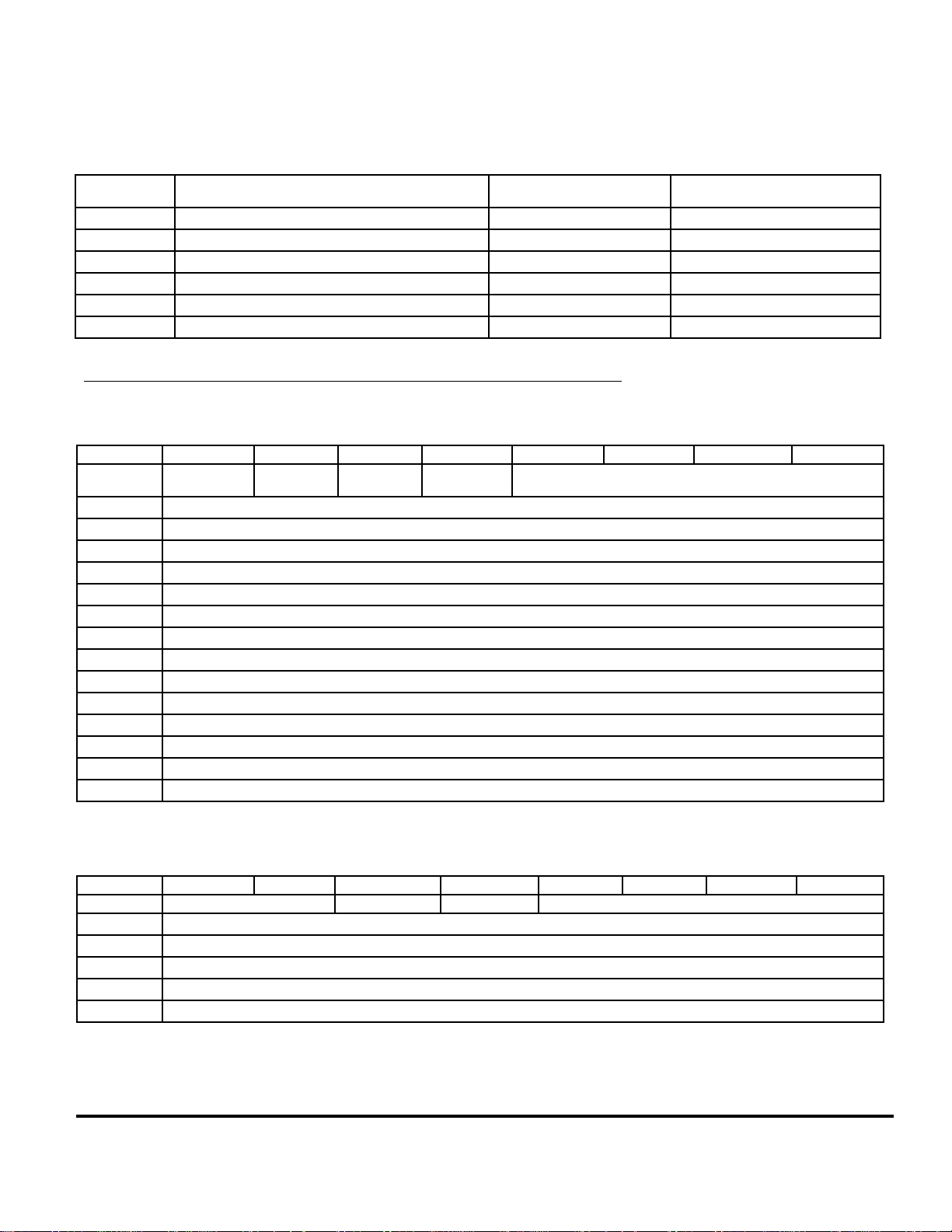

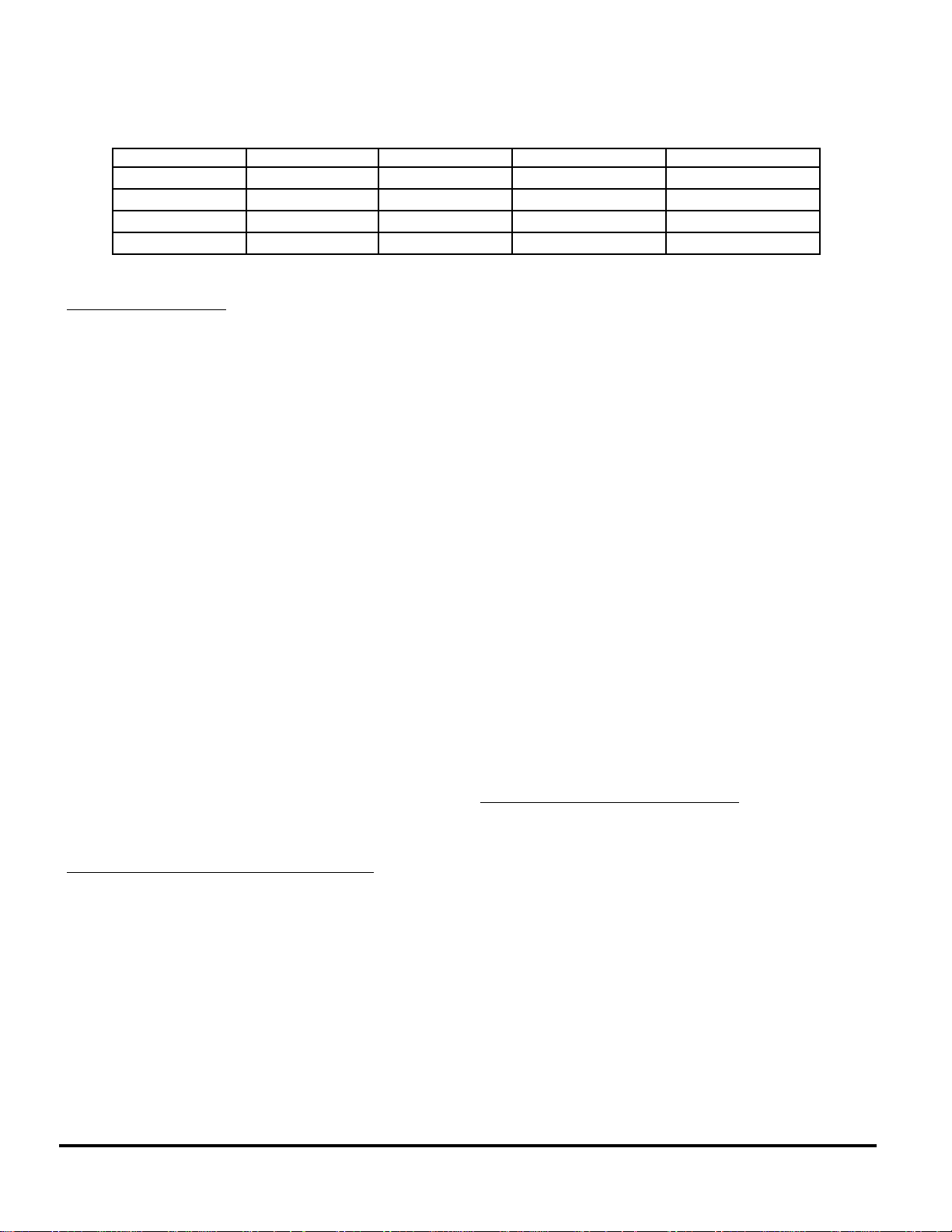

Supported Modes of Operation:

Downstream

FEC 16 QAM 64 QAM 256 QAM

Annex A X X

Annex B X X

Annex C X X

Upstream

STD BPSK QPSK 16 QAM

MCNS X X

ERRATA for STEL-2176

DAVIC X X

STEL-2176 User Manual

Page 5

TABLE OF C ON TENTS

PARAGRAPH PAGE

KEY FEATURES..................................................................................................................................... 1

RECEIVER........................................................................................................................................... 1

TRANSMITTER................................................................................................................................... 1

INTRODUCTION .................................................................................................................................. 2

RECEIVER OVERVIEW........................................................................................................................ 2

TRANSMITTER OVERVIEW................................................................................................................ 2

MECHANICAL SPECIFICATIONS ........................................................................................................ 3

208-PIN SQFP PACKAGE..................................................................................................................... 3

ELECTRICAL SPECIFICATIONS........................................................................................................ 8

RECEIVER ............................................................................................................................................. 10

OVERVIEW......................................................................................................................................... 10

FUNCTIONAL BLOCKS ...................................................................................................................... 11

ADC.............................................................................................................................................. 11

Microcontroller Interface................................................................................................................. 11

Master Receive Clock Generator...................................................................................................... 12

QAM Demodulator Blocks.............................................................................................................. 13

FEC Decoder Blocks ....................................................................................................................... 14

RECEIVE AND UNIVERSAL REGISTER DESCRIPTIONS .................................................................... 20

PROGRAMMING THE 2176 RECEIVE FUNCTIONS ............................................................................. 20

REGISTER DESCRIPTIONS.................................................................................................................. 20

Bank 0 - Universal Registers (Group 1)............................................................................................. 20

Bank 0 - QAM Demodulator Registers Universal Registers (Group 2) ................................................ 22

Bank 1 - FEC Registers (Group 3)..................................................................................................... 30

TIMING................................................................................................................................................. 35

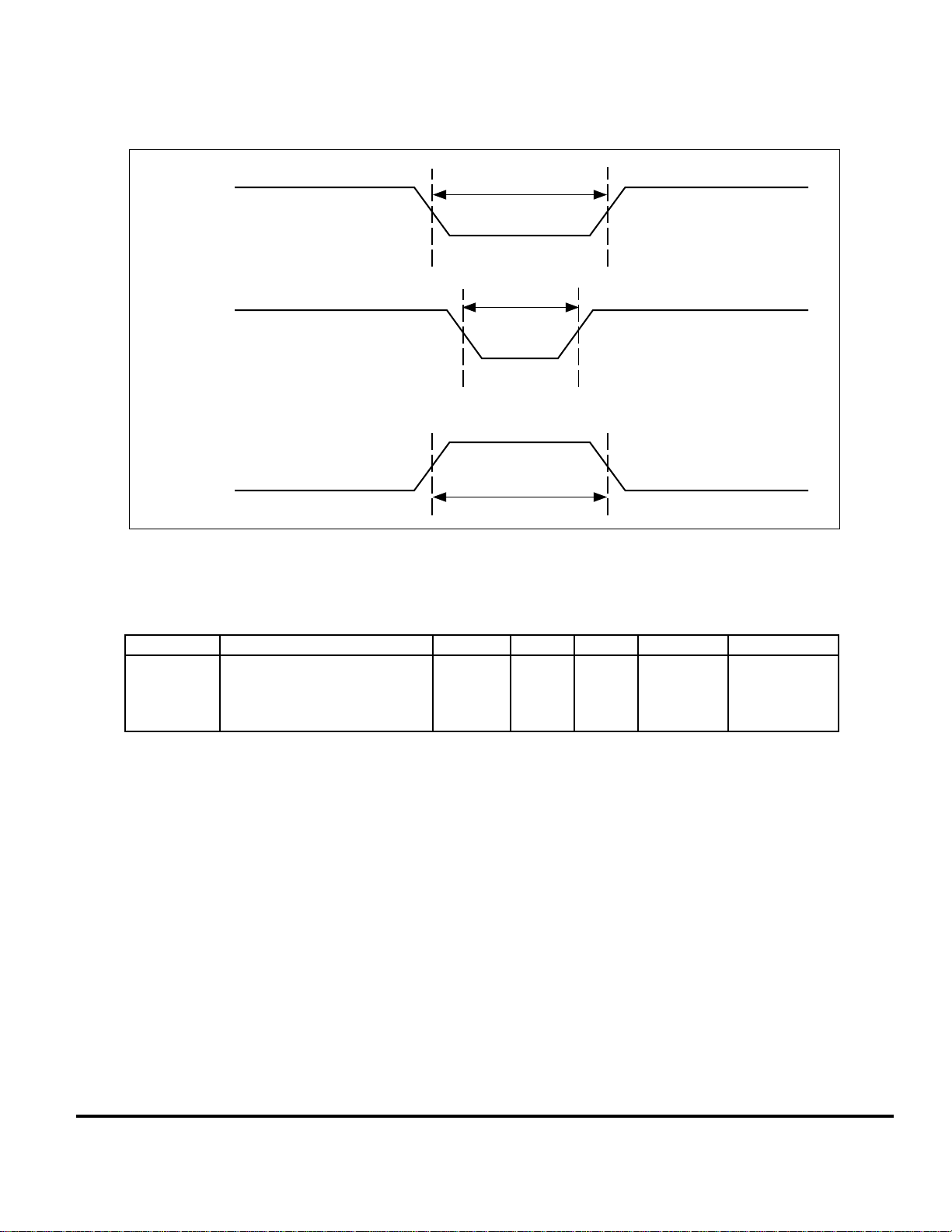

NO GAP, PARALLEL MODE ............................................................................................................... 35

NO GAP, SERIAL MODE..................................................................................................................... 35

GAPS, PARALLEL MODE.................................................................................................................... 35

GAPS, SERIAL MODE ......................................................................................................................... 35

TRANSMITTER..................................................................................................................................... 39

INTRODUCTION ................................................................................................................................39

FUNCTIONAL BLOCK DIAGRAM DESCRIPTIONS ............................................................................. 39

DATA PATH DESCRIPTION ............................................................................................................... 39

Bit SYNC Block .............................................................................................................................. 39

Bit Encoder Block ........................................................................................................................... 41

Symbol Mapper Block..................................................................................................................... 45

Nyquist FIR Filter........................................................................................................................... 50

Interpolating Filter ......................................................................................................................... 50

Modulator ..................................................................................................................................... 51

10-Bit DAC..................................................................................................................................... 52

User Manual i STEL-2176

Page 6

TABLE OF C ON TENTS

PARAGRAPH PAGE

CONTROL UNIT DESCRIPTION.......................................................................................................... 52

Bus Interface Unit ........................................................................................................................... 52

Master Transmit Clock Generator .................................................................................................... 52

Clock Generator ............................................................................................................................. 53

NCO.............................................................................................................................................. 53

TRANSMIT REGISTER DESCRIPTIONS................................................................................................ 54

Programming the 2176 Transmit and Receive Functions.................................................................... 54

Block 2, Upstream Registers (Group 4) ............................................................................................. 54

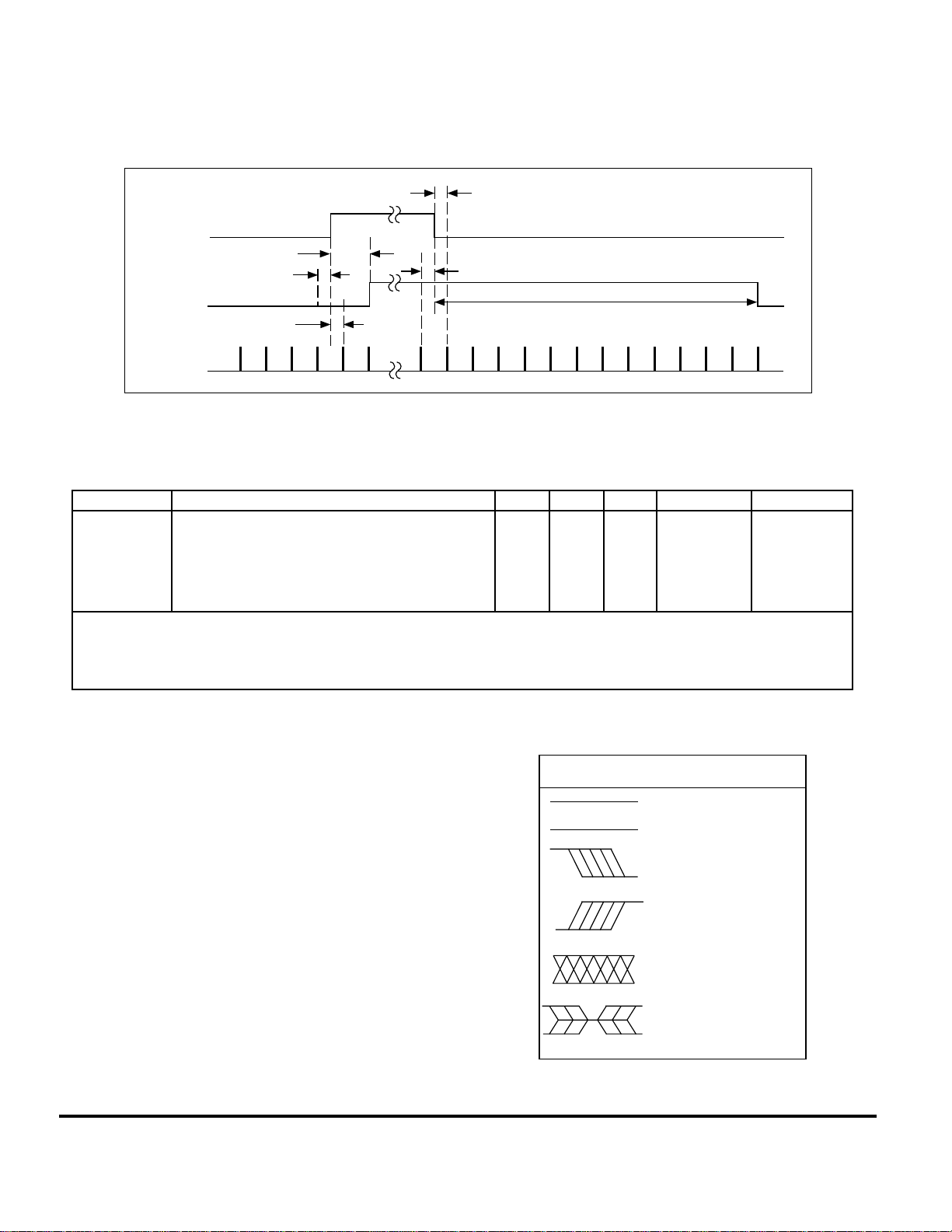

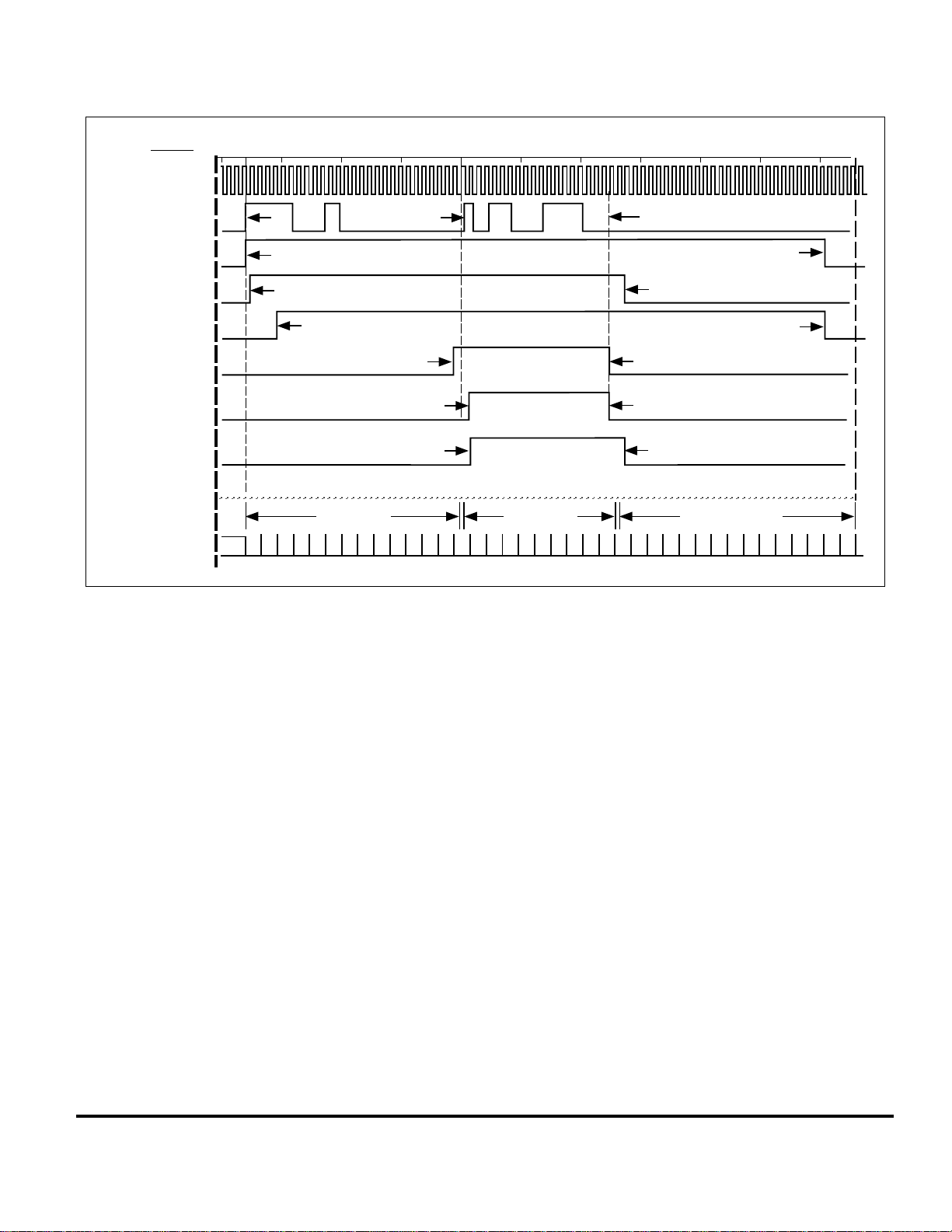

TIMING DIAGRAMS ............................................................................................................................ 57

BURST TIMING EXAMPLES ................................................................................................................. 65

RECOMMENDED INTERFACE CIRCUITS ............................................................................................ 70

STEL-2176 ii User Manual

Page 7

LIST OF FIGU RES

FIGURE PAGE

1 Reference A/D Wiring............................................................................................... 7

2 Example Output Load Schematic................................................................................ 7

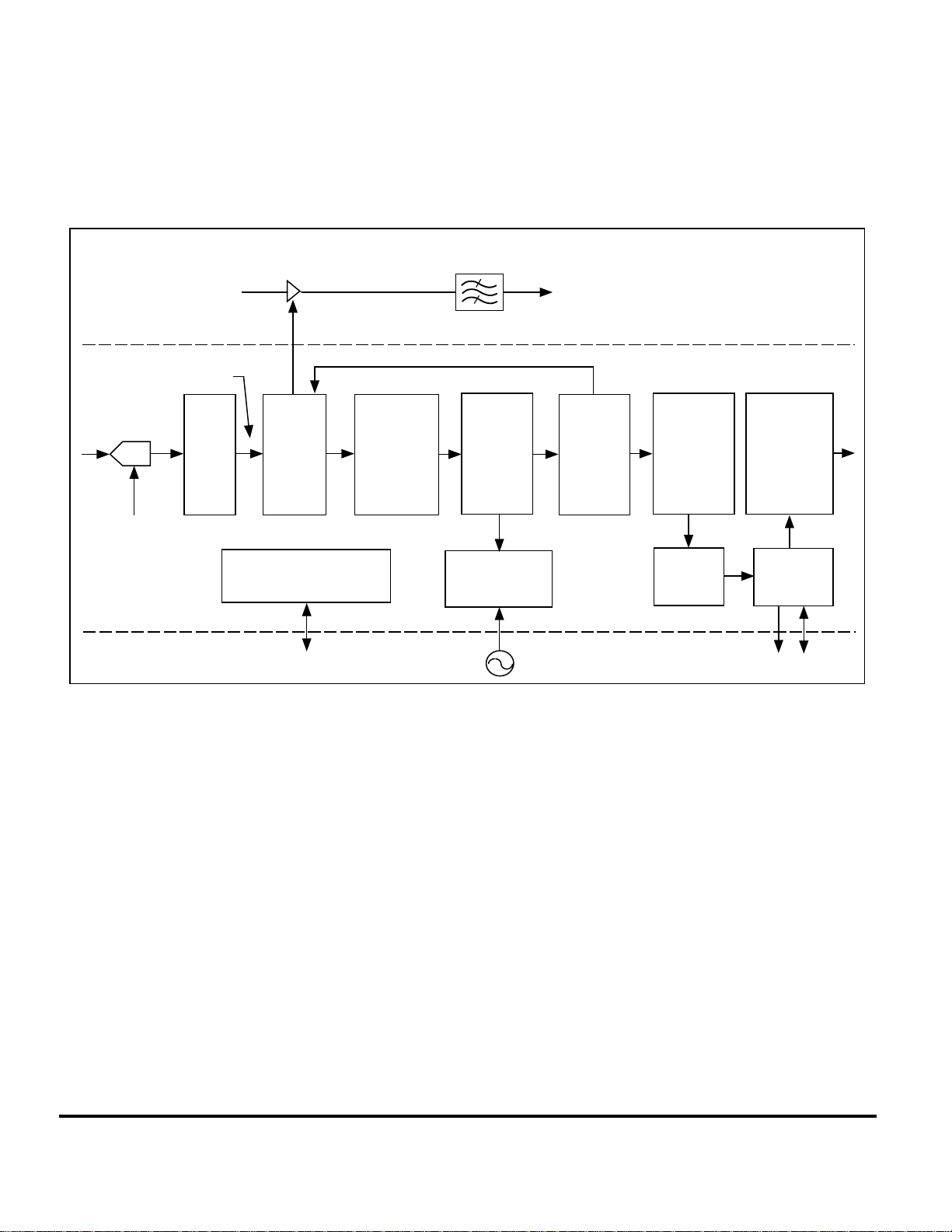

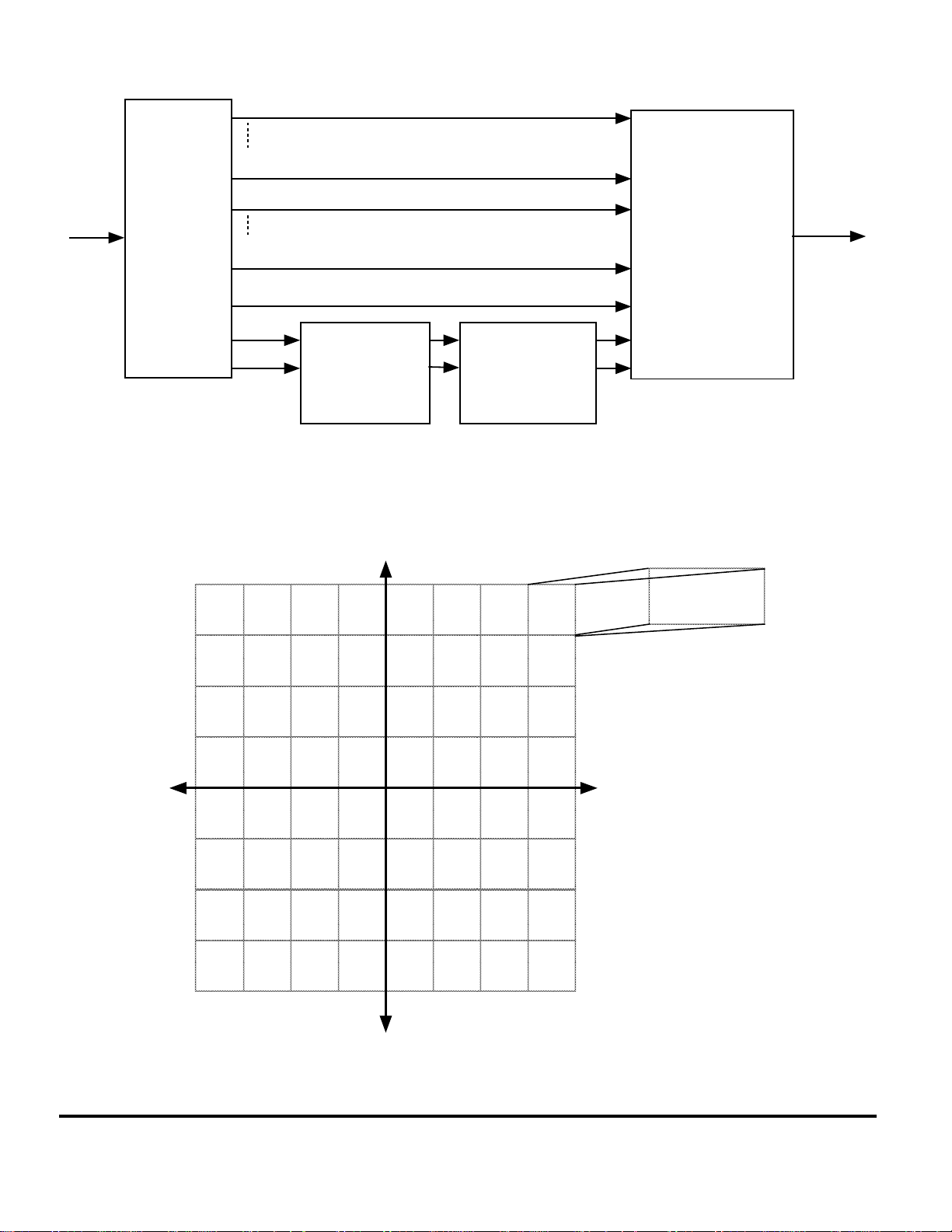

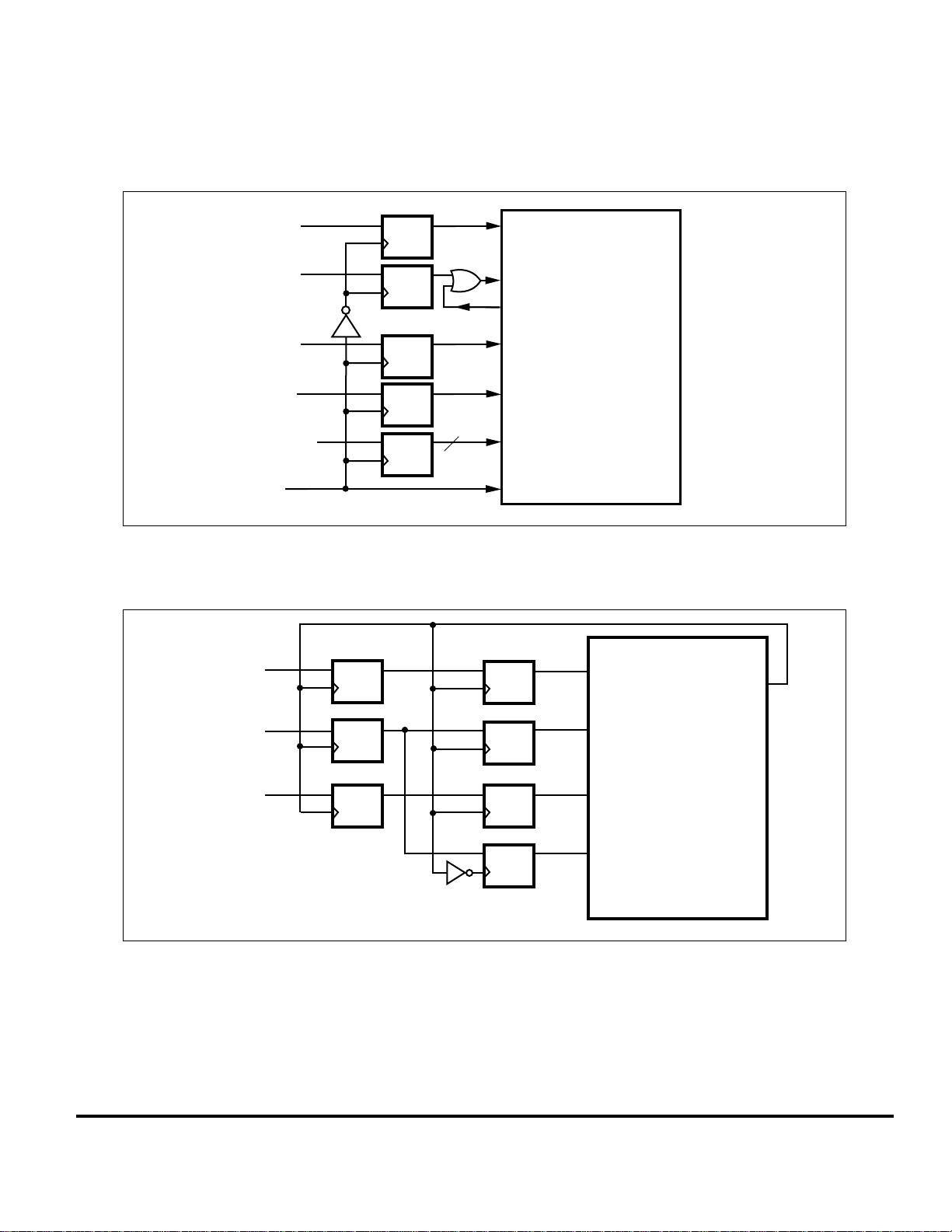

3 STEL-2176 Receiver Block Diagram ............................................................................ 11

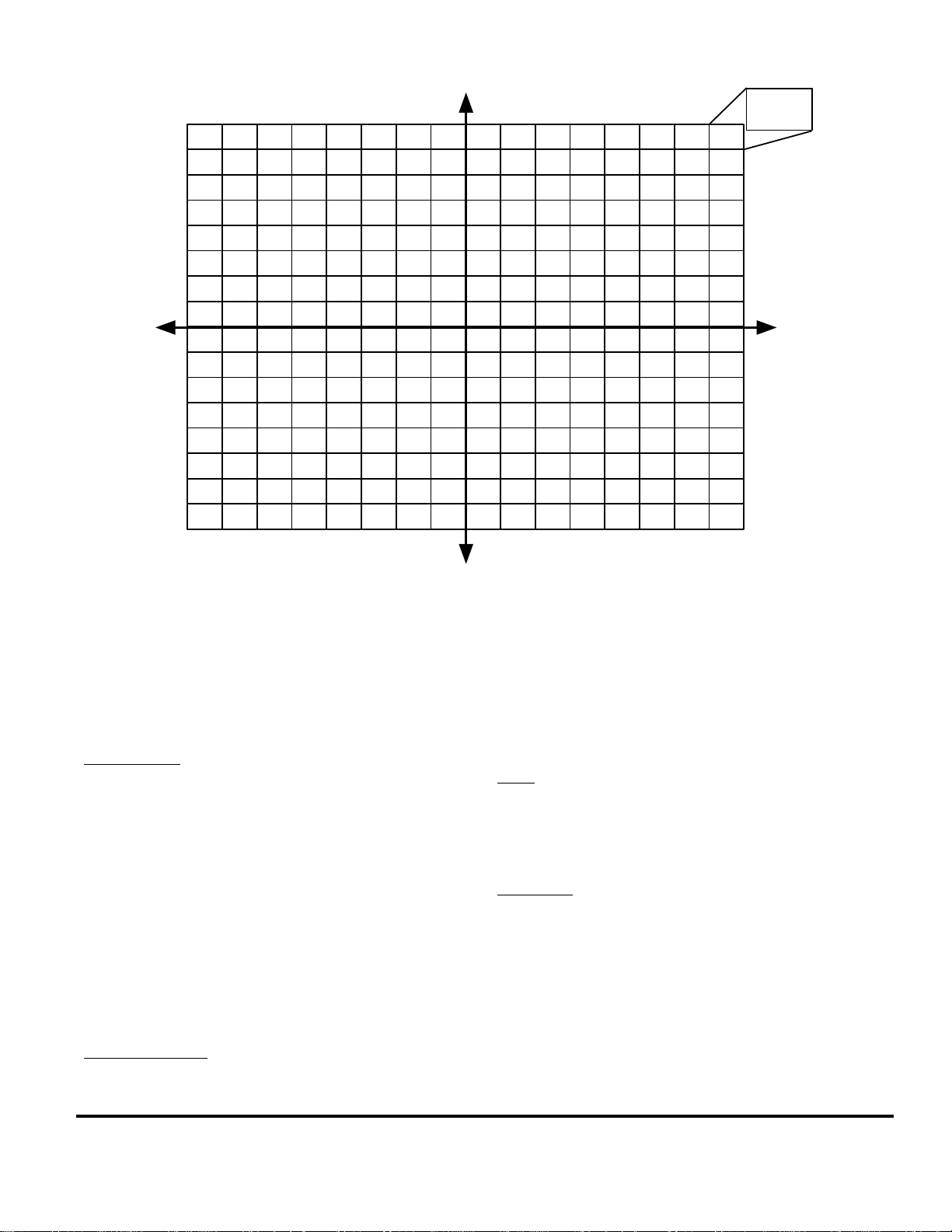

4 Master Receive Clock Generator................................................................................. 12

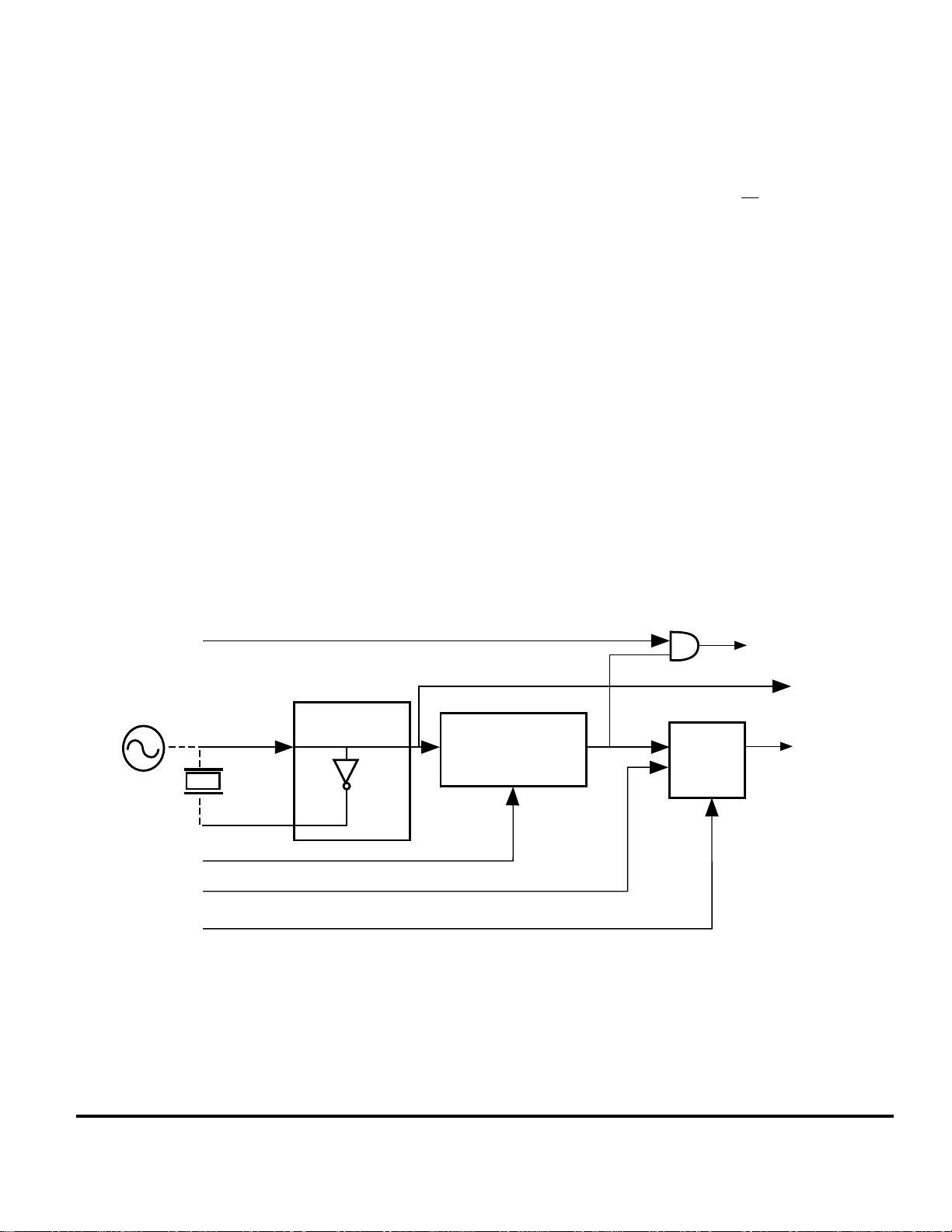

5 QAM Demodulator Blocks......................................................................................... 13

6 ITU-T (J.83) Annex A FEC Subsystem ......................................................................... 14

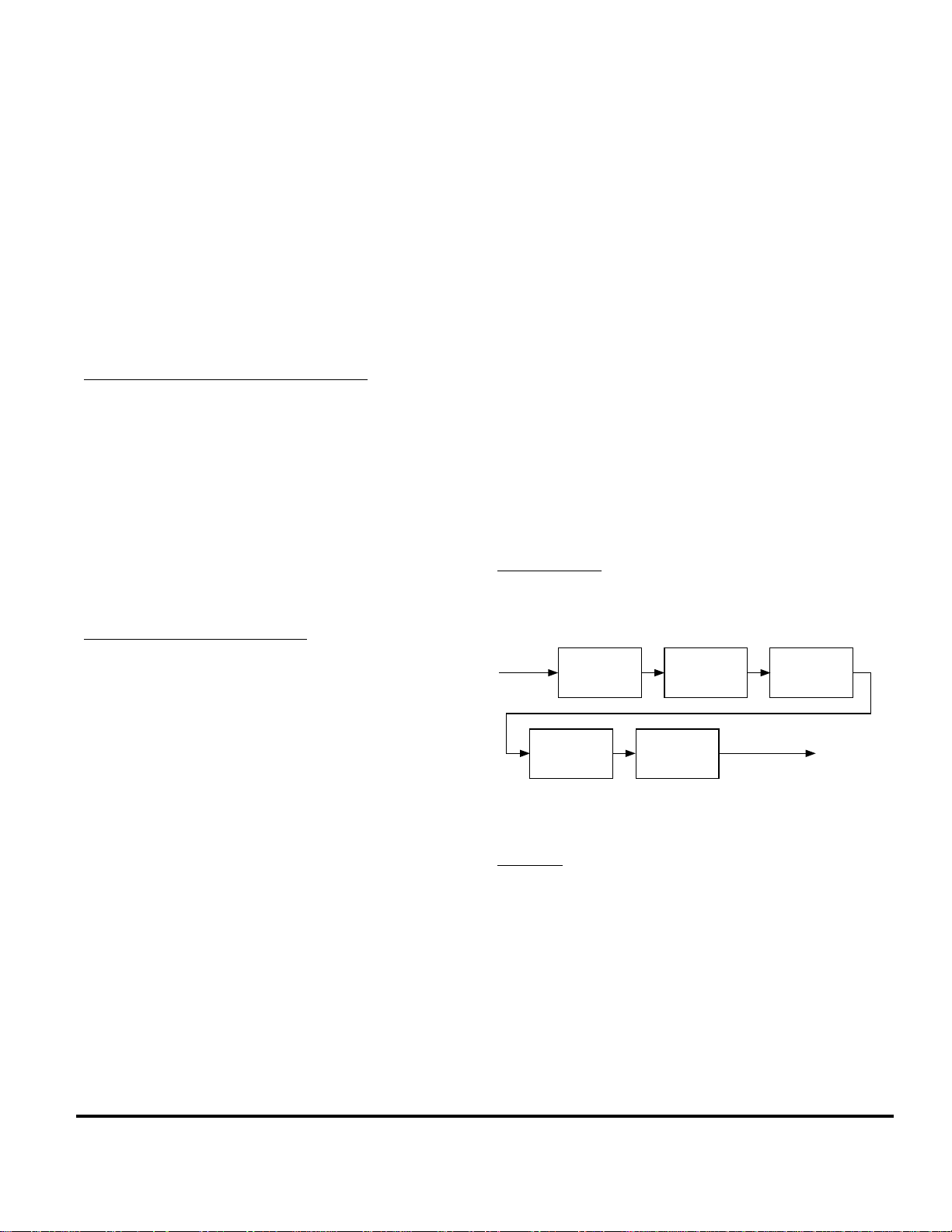

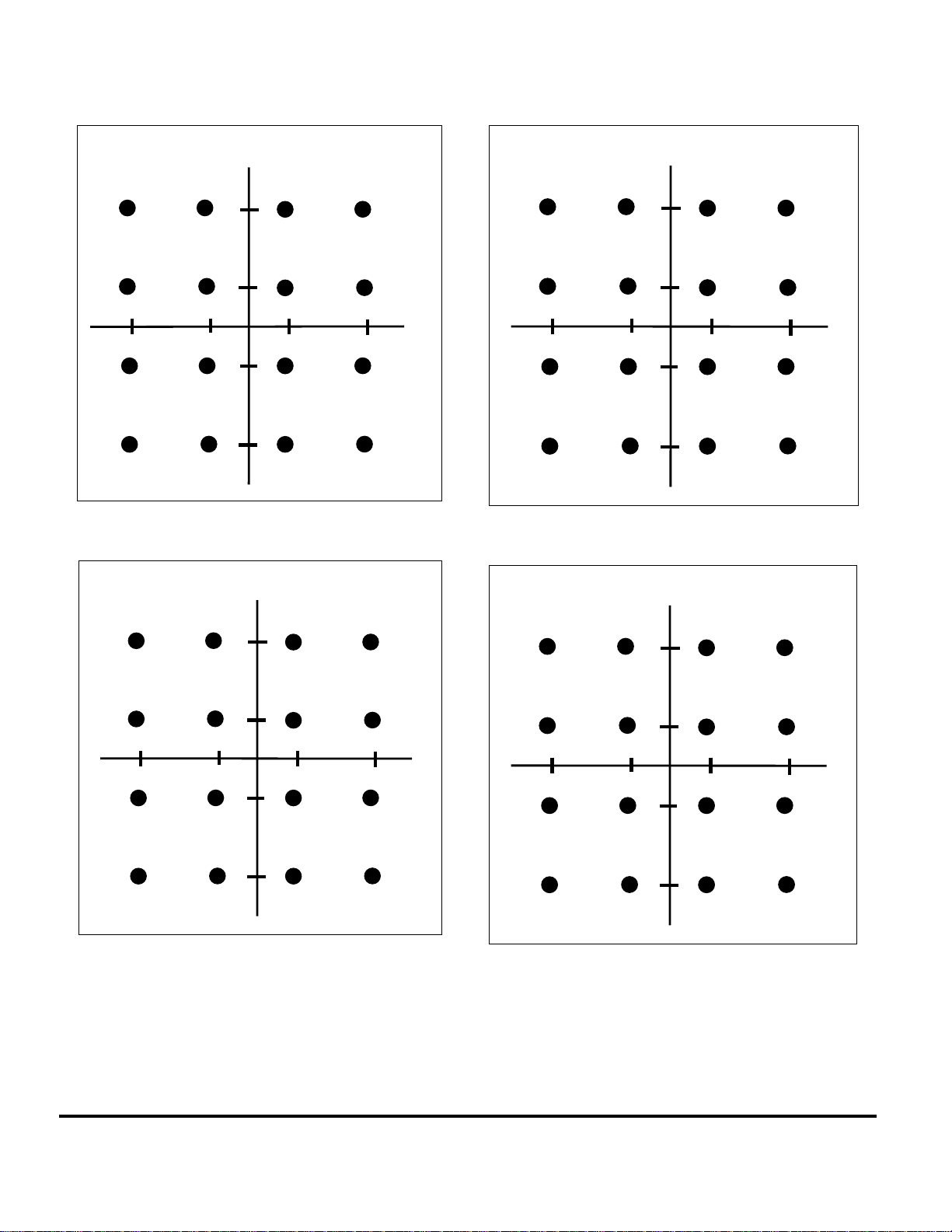

7 16 QAM Constellation ............................................................................................... 15

8 64 QAM Constellation ............................................................................................... 15

9 256 QAM Constellation (DAVIC)................................................................................ 15

10 256 QAM Constellation (DVB/IEEE 802.14) ................................................................ 15

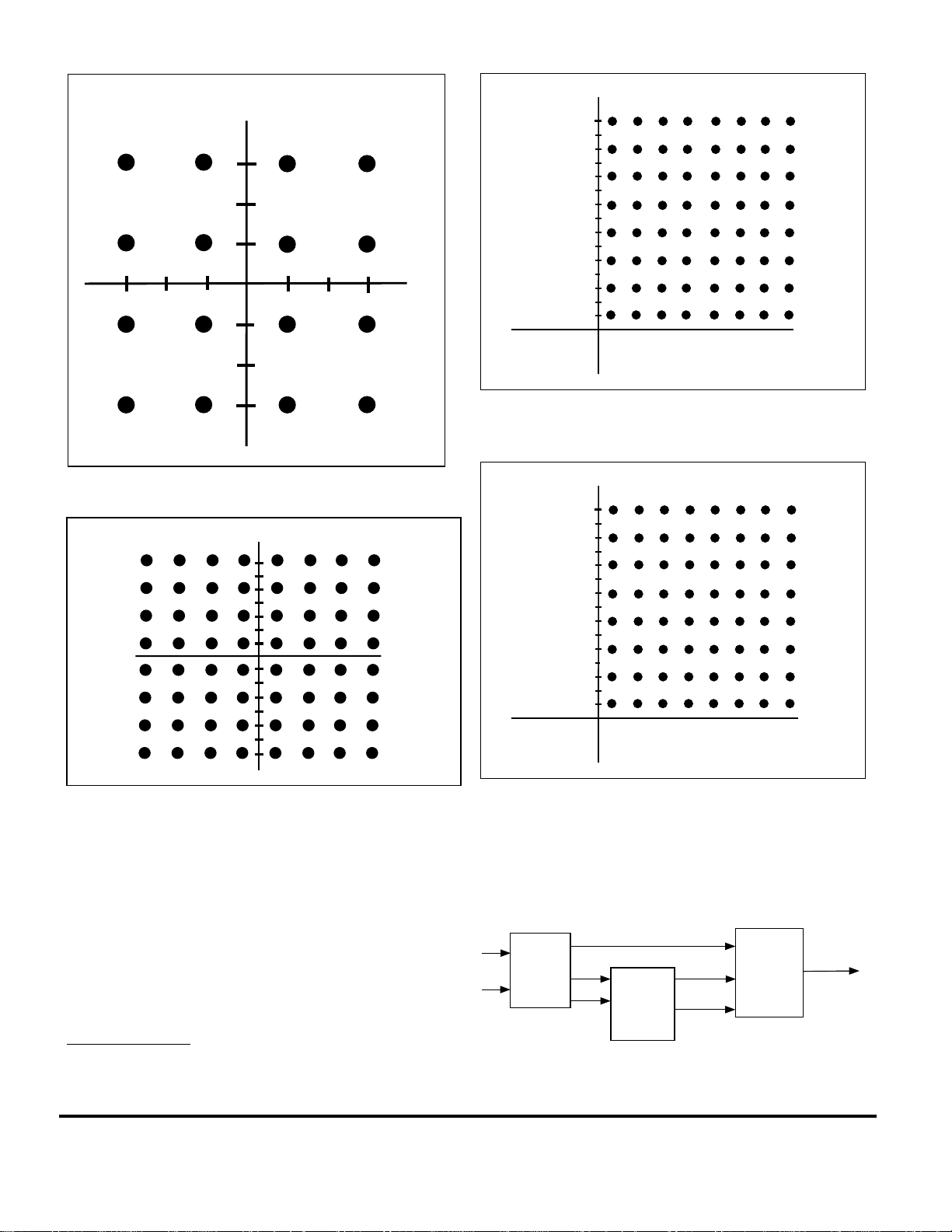

11 Demapper................................................................................................................. 15

12 De-Interleaver........................................................................................................... 16

13 ITU-T (J.83) Annex B FEC Subsystem.......................................................................... 16

14 Trellis Coded Demodulator........................................................................................ 17

15 64 QAM Mapping ..................................................................................................... 17

16 256 QAM Mapping.................................................................................................... 18

17 Derandomizer........................................................................................................... 19

18 De-Interleaver........................................................................................................... 19

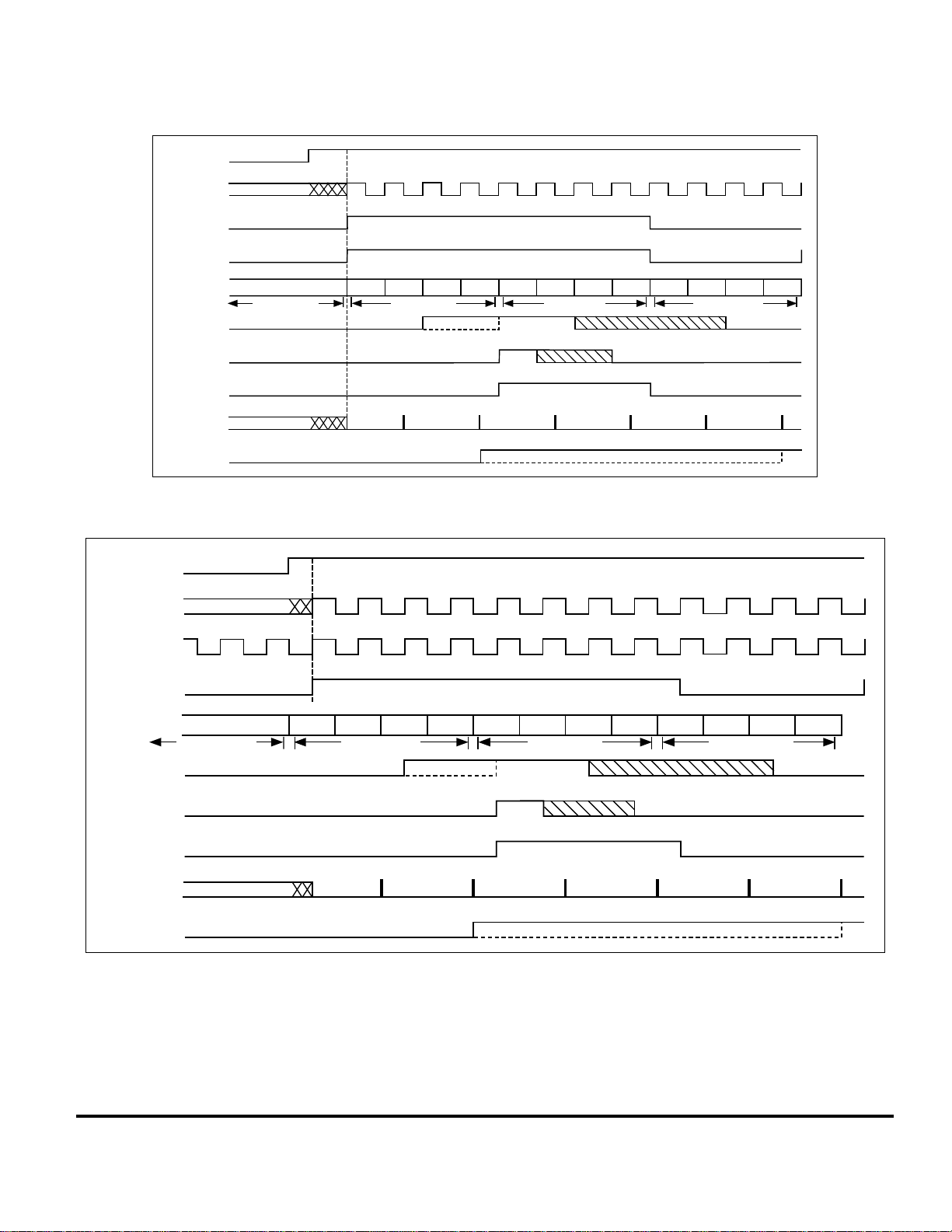

19. Downstream Output Timing (Parallel Data Output) .................................................... 36

20. Downstream Output Timing (Serial Output)............................................................... 36

21. Downstream Output Timing (Parallel Data Output) .................................................... 37

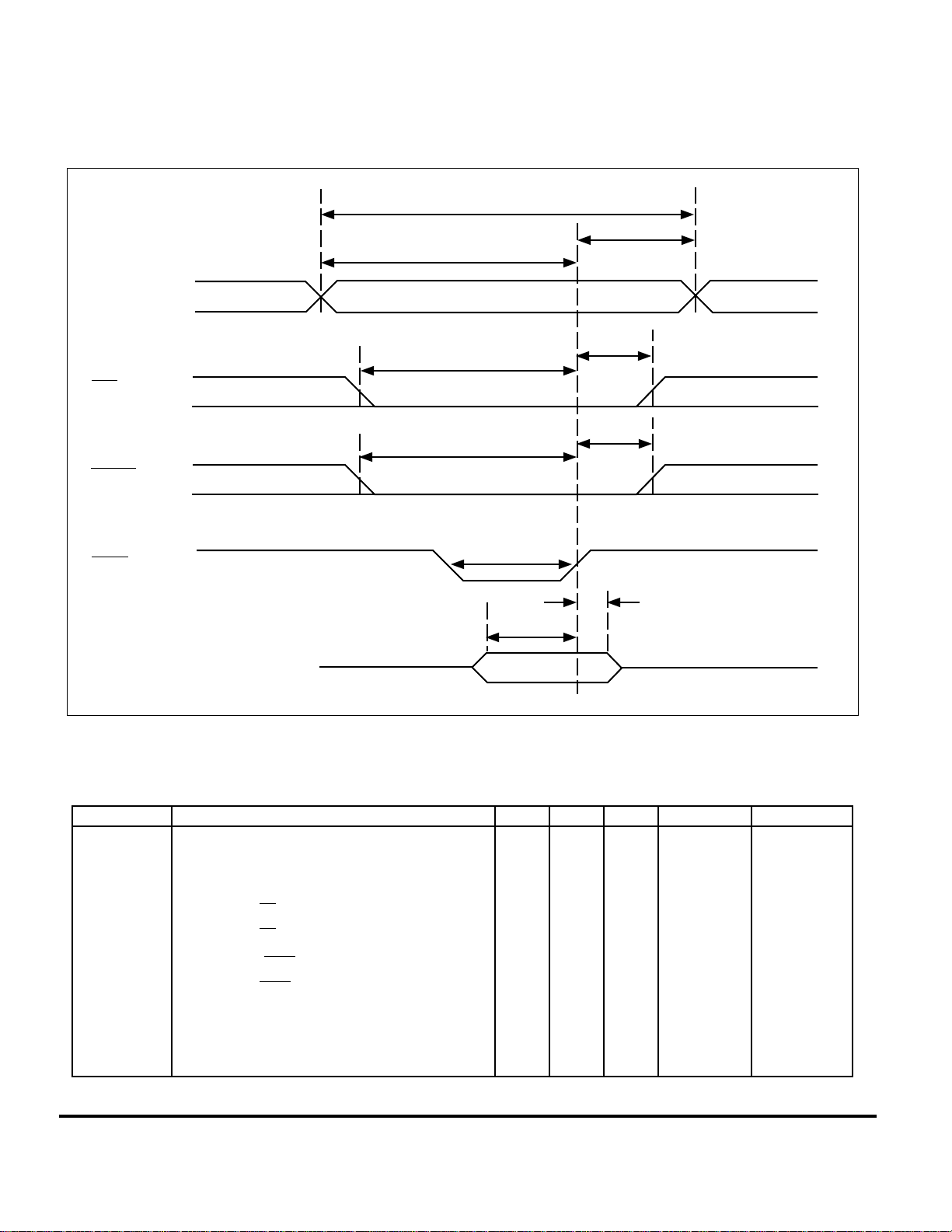

22. Downstream Output Timing (Parallel Data Output) .................................................... 38

23. De-Interleaver External SRAM Timing........................................................................ 38

24 STEL-2176 Transmitter Block Diagram........................................................................ 40

25 Bit Encoder Functional Diagram................................................................................. 42

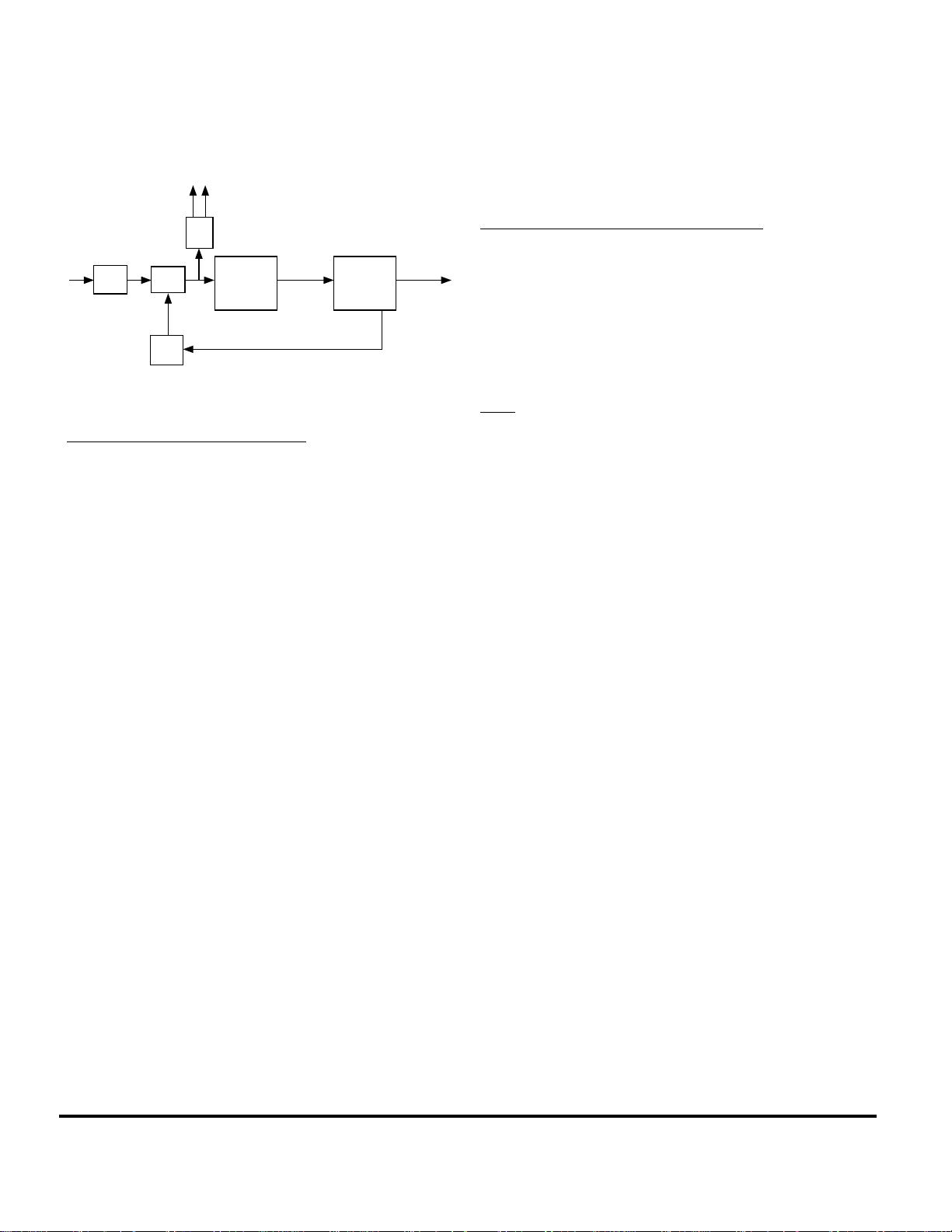

26 Scrambler Block Diagram........................................................................................... 43

27 DAVIC Scrambler...................................................................................................... 43

28 Mapping Block Functional Diagram ........................................................................... 45

29 BPSK Constellation.................................................................................................... 47

30 QPSK Constellation ................................................................................................... 47

31 Natural Mapping Constellation.................................................................................. 48

32 Gray Coded Constellation.......................................................................................... 49

33 Left Coded Constellation ........................................................................................... 49

34 DAVIC Coded Constellation ...................................................................................... 49

35 Right Coded Constellation ......................................................................................... 49

36 Nyquist FIR Filter...................................................................................................... 50

37 Interpolation Filter Block Diagram.............................................................................. 51

38. Master Clock Generation ........................................................................................... 53

User Manual iii STEL-2176

Page 8

LIST OF TABLES

TABLE PAGE

1 STEL-2176 Pin Assignments ....................................................................................... 3

2 Absolute Maximum Ratings ....................................................................................... 8

3 Recommended Operating Conditions ......................................................................... 8

4 ADC Performance Specifications ................................................................................ 9

5 DC Characteristics ..................................................................................................... 9

6 Read/Write Register Set............................................................................................. 20

7 Write Only Registers:................................................................................................. 20

8 Group 2, Sub-Group 'A' Read/Write Registers............................................................. 22

9 Sub-Group 'A' Read-Only Registers ............................................................................ 22

10 SNR to ErrPwr Conversion......................................................................................... 23

11 Group 2, Sub-Group 'B' Read/Write Registers ............................................................. 24

12 Group 2, Sub-Group 'B' Read-Only Registers............................................................... 24

13 Group 2, Sub-Group 'C' Read/Write Registers............................................................. 26

14 Group 2, Sub-Group 'C' Read-Only Registers............................................................... 26

15 Group 2, Sub-Group 'D' Read/Write Registers............................................................. 26

16 Group 2, Sub-Group 'D' Read-Only Registers .............................................................. 27

17 Group 2, Sub-Group 'E' Read/Write Registers ............................................................. 28

18 Group 2, Sub-Group 'E' Read-Only Registers............................................................... 28

19 Group 2, Sub-Group 'F' Read/Write Registers ............................................................. 29

20 Group 2, Sub-Group 'F' Read-Only Registers ............................................................... 30

21 Group 3, Sub-Group 'A' Read/Write Registers............................................................. 30

22 Group 3, Sub-Group 'B' Read-Only Registers............................................................... 31

23 Group 3, Sub-Group 'C' Read/Write Registers............................................................. 31

24 Group 3, Sub-Group 'C' Read-Only Registers............................................................... 31

25 Group 3, Sub-Group 'D' Read/Write Registers............................................................. 32

26 Group 3, Sub-Group 'D' Read-Only Registers .............................................................. 32

27 Group 3, Sub-Group 'E' Read/Write Registers ............................................................. 33

28 Group 3, Sub-Group 'E' Read-Only Registers............................................................... 33

29 Group 3, Sub-Group 'F' Read/Write Registers ............................................................. 34

30 Group 3, Sub-Group 'G' Read/Write Registers............................................................. 34

31 Group 3, Sub-Group 'G' Read-Only Registers .............................................................. 34

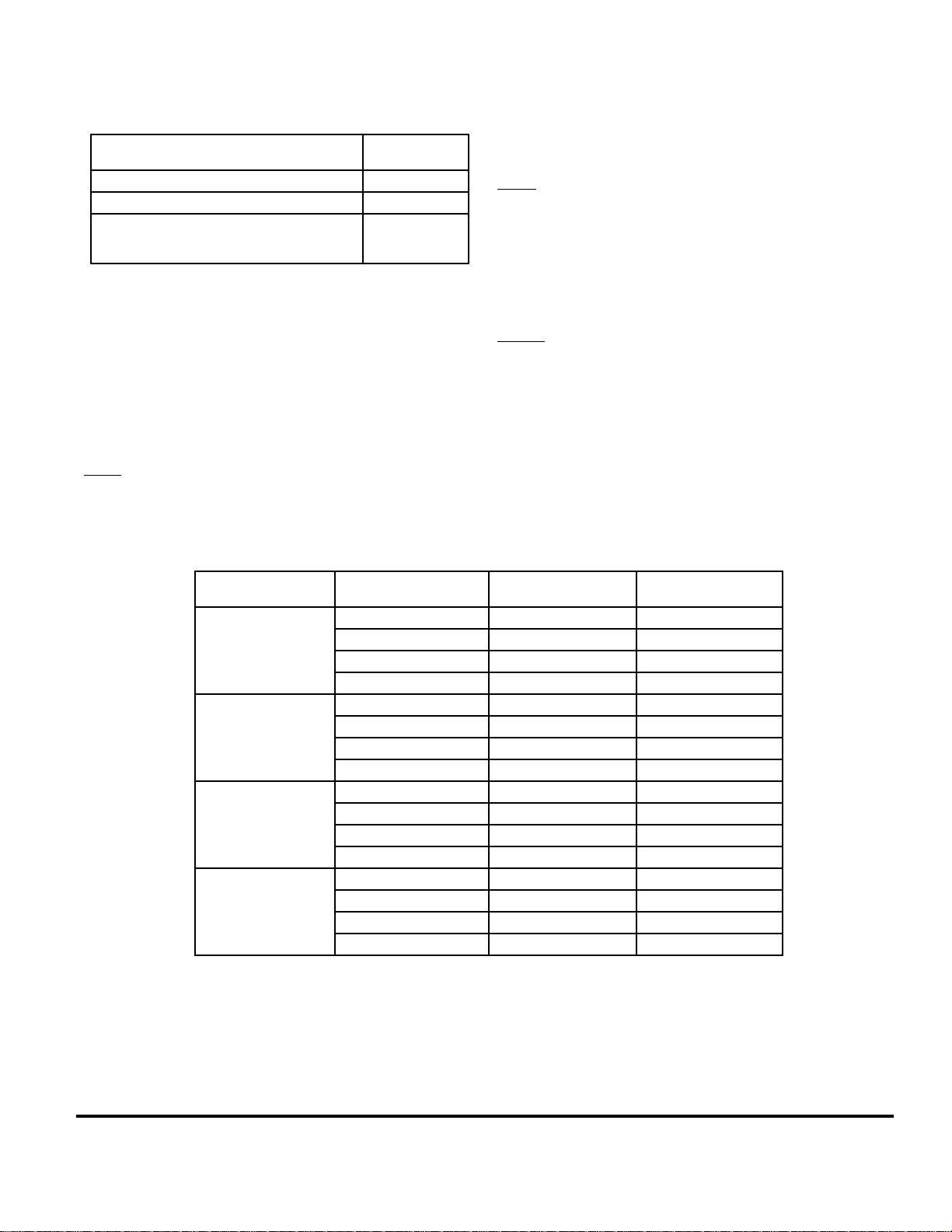

32 Transmit Features...................................................................................................... 40

33 Data Latching Options ............................................................................................... 41

34 BIT Encoding Data Path Options................................................................................. 42

35 Scrambler Parameters ................................................................................................ 43

36 Sample Scramble Register Values................................................................................ 43

37 Reed-Solomon Encoder Parameters............................................................................. 44

38 Bit Mapping Options ................................................................................................. 45

39 Differential Encoder Control....................................................................................... 46

40 QPSK Differential Encoding and Phase Shift................................................................ 46

41 Symbol Mapping Selections........................................................................................ 48

42 Symbol Mapping ....................................................................................................... 48

43 FIR Filter Configuration Options ................................................................................ 50

STEL-2176 iv User Manual

Page 9

LIST OF TABLES

TABLE PAGE

44 FIR Filter Coefficient Storage...................................................................................... 50

45 Interpolation Filter Bypass Control............................................................................. 51

46 Interpolation Filter Signal Level Control ..................................................................... 51

47 Signal Inversion Control ............................................................................................ 52

48 FCW Selection........................................................................................................... 54

49 Addresses of the STEL-2176 Register Groups .............................................................. 54

50 Transmit Block 2 Register Data Fields ......................................................................... 55

51 Clock Timing AC Characteristics................................................................................ 57

52 Pulse Width AC Characteristics.................................................................................. 58

53 Bit Clock Synchronization AC Characteristics.............................................................. 59

54 Input Data and Clock AC Characteristics .................................................................... 60

55 Write Timing AC Characteristics ................................................................................ 61

56 Read Timing AC Characteristics................................................................................. 62

57 NCO Loading AC Characteristics ............................................................................... 63

58 Digital Output Timing AC Characteristics................................................................... 64

59 TXDATAENI to TXDATAENO Timing AC Characteristics .......................................... 65

User Manual v STEL-2176

Page 10

KEY FEATURES

RECEIVER

n 10-bit A/D on chip

n 16/64/256 QAM demodulation

n Selectable ITU-T (J.83), Annex A/Annex B

forward error correction (FEC)

n MCNS, IEEE 802.14 (preliminary),

DAVIC/DVB compliant

n Parallel or serial output data with or

without gaps

n Viterbi decoder for Annex B

n Selectable Reed-Solomon decoder for

Annex A and Annex B

n Programmable De-Interleaver

n Programmable De-Randomizer

n MPEG-2 Framing

Introduction

n Programmable control registers for

maximum flexibility

n FIFO for optional removal of inter-frame

gaps

n Automatic frequency control (± 200 kHz)

n Highly integrated receiver functions

n Up to 50 MHz IF input

n Uses inexpensive Crystal in the 25 MHz

range

n Adaptive Channel Equalizer (ACE) to

compensate for channel distortion

n Selectable Nyquist filter

n Fast acquisition

TRANSMITTER

n Patented (U.S. Patent #5,412,352)

Complete BPSK/QPSK/16QAM modulator

n Complete upstream modulator

solution—serial data in, RF signal out

n Programmable over a wide range of data

rates

n Numerically Controlled Oscillator (NCO)

modulator provides fine frequency

resolution

n Carrier frequencies programmable from 5

to 65 MHz

n Uses inexpensive crystal in 25 MHz range

n Operates in continuous and burst modes

n Differential Encoder, Programmable

Scrambler, and Programmable ReedSolomon FEC Encoder

n Programmable 64-tap FIR filter for signal

shaping before modulation

n 10-bit DAC on chip

n Compatible with DAVIC, IEEE 802.14

(preliminary), Intelsat IESS-308, MCNS

Standards

n Supports low data rates for voice

applications and high data rates for

wideband applications

STEL-2176 1 User Manual

Page 11

INTRODUCTION

The STEL-2176 is a complete subscriber-side cable

modem chip that integrates both receiver and

transmitter functions. It is offered in CMOS .35 micron

geometry operating at 3.3 Volts with integrated DAC

and ADC. Its programmable register set offers a flexible

solution to meet current and evolving standards.

RECEIVER OVERVIEW

A 10-bit A/D converts the analog input signal. The

analog input signal may be up to 50ÊMHz. For MCNS

and DAVIC standards 44 MHz and 36 MHz are the two

typical IF frequencies used. For 44ÊMHz the

corresponding bandwidth is 6 MHz; for 36ÊMHz the

corresponding bandwidth is 8 MHz. Sampling of the

input may be set for 25 MHz for the 6ÊMHz bandwidth

or 29 MHz for the 8 MHz bandwidth.

The downstream receiver offers 16/64/256 QAM

demodulation for Annex A, associated with DAVIC, or

Annex B, associated with MCNS. It also offers a variety

of choices for the data and clock outputs: frames with

or without gaps and parallel or serial data.

The incoming signal is sampled. The timing recovery

circuit determines the epoch of each symbol. Automatic

frequency and gain control circuitry correct the

frequency and amplitude of the signal, and a Digital

Down Converter (DDC) brings the alias band

associated with sampling down to zero. A Nyquist filter

eliminates inter-symbol interference, and an Adaptive

Channel Equalizer (ACE) corrects for channel distortion

while fine tuning the signal. A demapper transforms

the modulated signal back into symbols and a De-

Interleaver puts the data bits back into the original

order, while Trellis and Reed-Solomon decoders handle

error correction.

For Annex A, a Reed-Solomon decoder decodes and

corrects every 204 bytes in 188 bytes. For Annex B, there

is a Viterbi decoder and a 128, 122 (code word length,

information) 7-bit Reed-Solomon decoder. A derandomizer is used to unscramble the data stream.

Format of the receiver output is MPEG-2 frames.

TRANSMITTER OVERVIEW

The transmitter is highly integrated and flexible. It

receives serial data, randomizes the data, performs

Forward Error Correction (FEC) and differential

encoding, maps the data to a constellation before

modulation, and outputs an analog RF signal.

It includes a 10-bit DAC and is capable of operating at

data rates up to 20 Mbps in QPSK mode and 40ÊMbps in

16QAM mode.

The transmitter uses a digital FIR filter to optimally

shape the spectrum of the modulating data prior to

modulation. Signal level scaling is provided after the

FIR filter to allow maximum arithmetic dynamic range.

The transmitter side offers QPSK and 16QAM

modulation with frequencies from 5 to 65 MHz. It can

operate in continuous or burst mode. And it can

operate with very short gaps between bursts less than

four symbols.

All digital interfaces support 3.3 volt and 5 volt logic.

STEL-2176 2 User Manual

Page 12

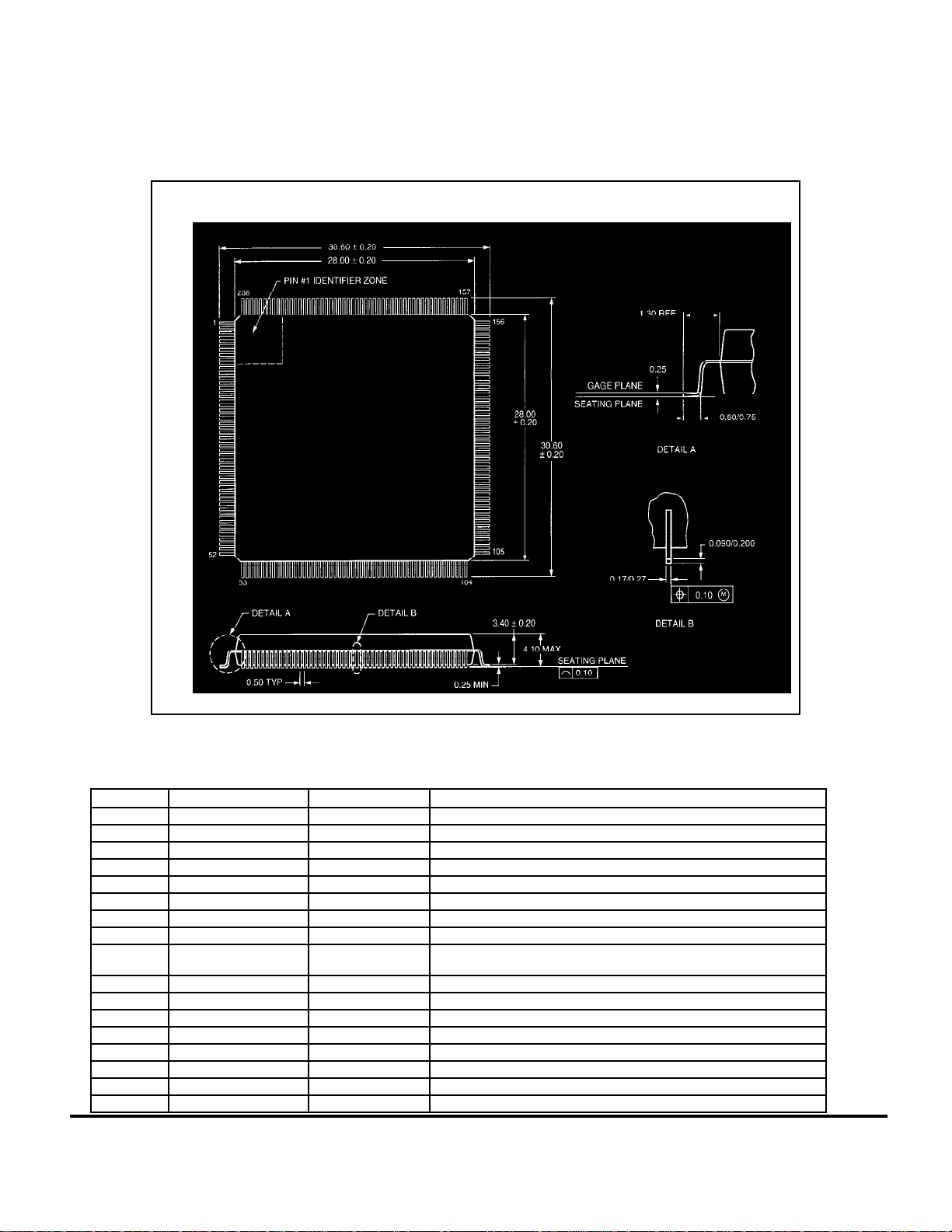

MECHANICAL SPECIFICATIONS

208-PIN SQFP PACKAGE

Dimensions are in millimeters.

Introduction

TPG 53310.c-7/29/97

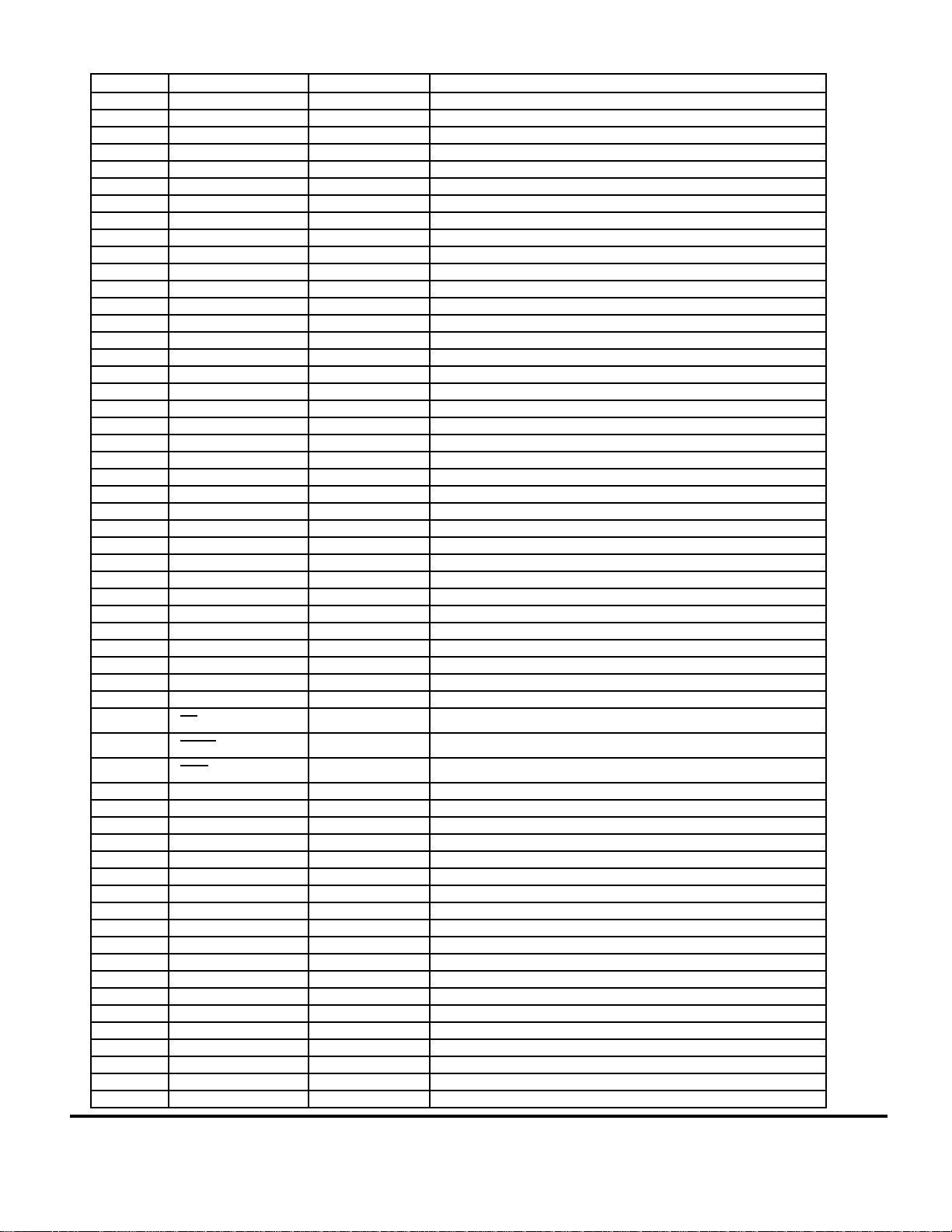

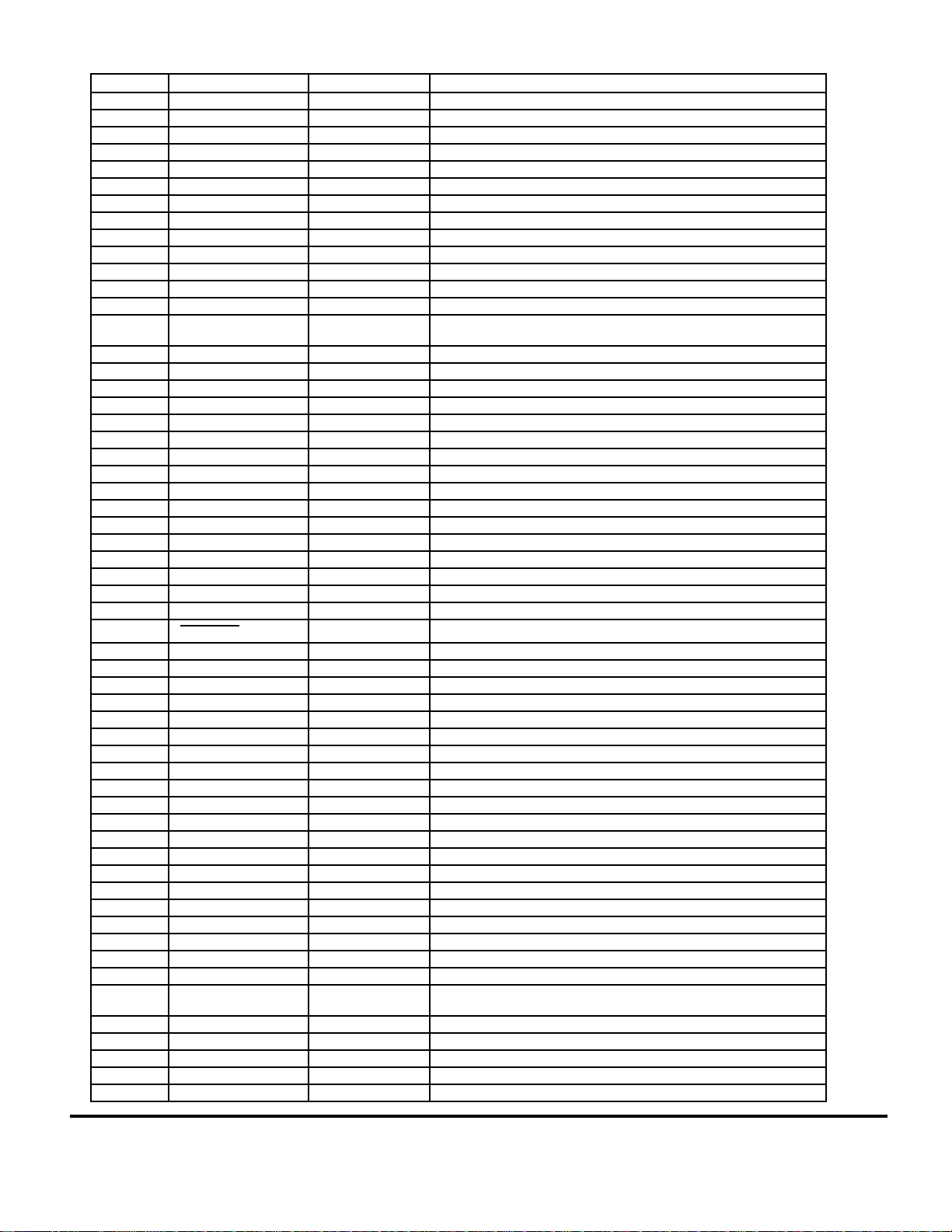

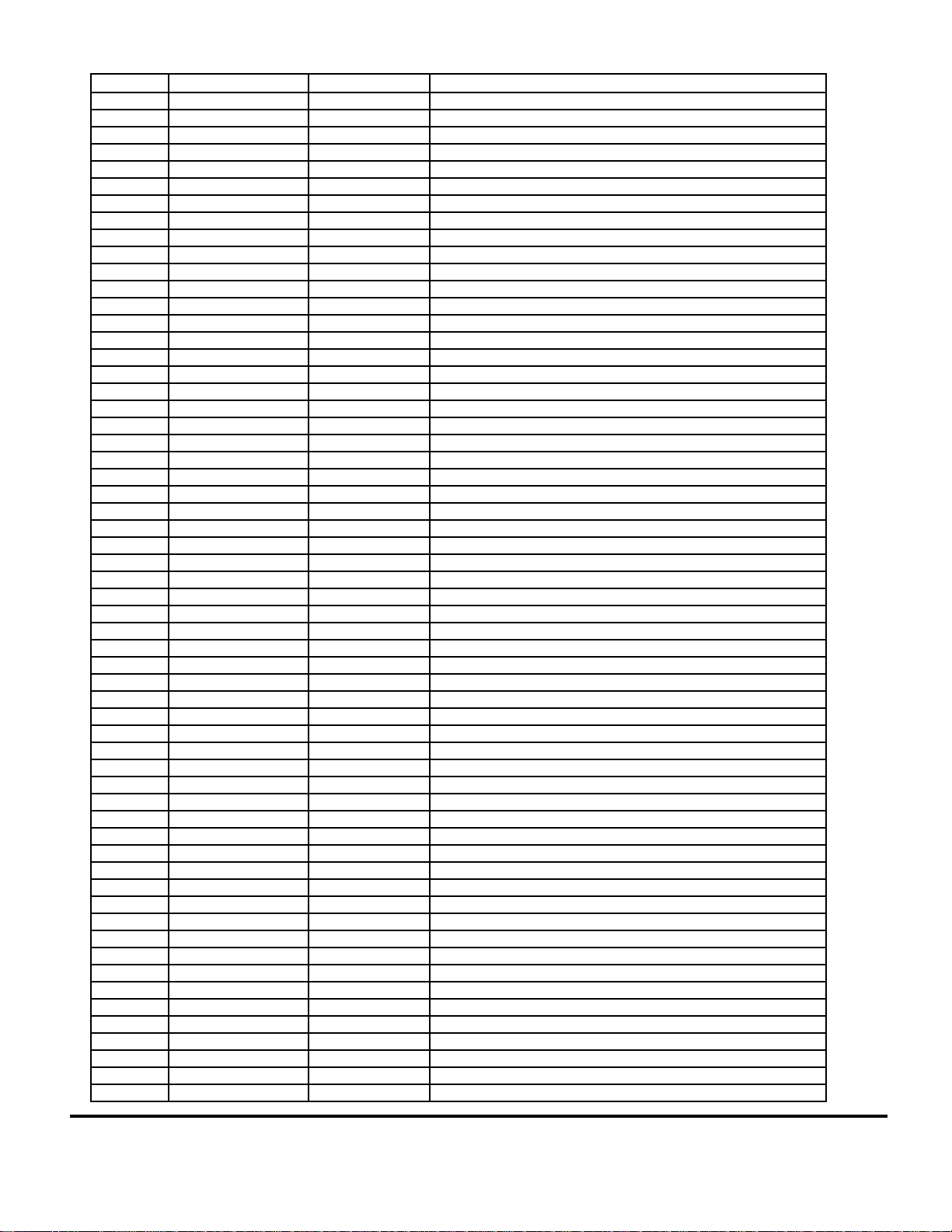

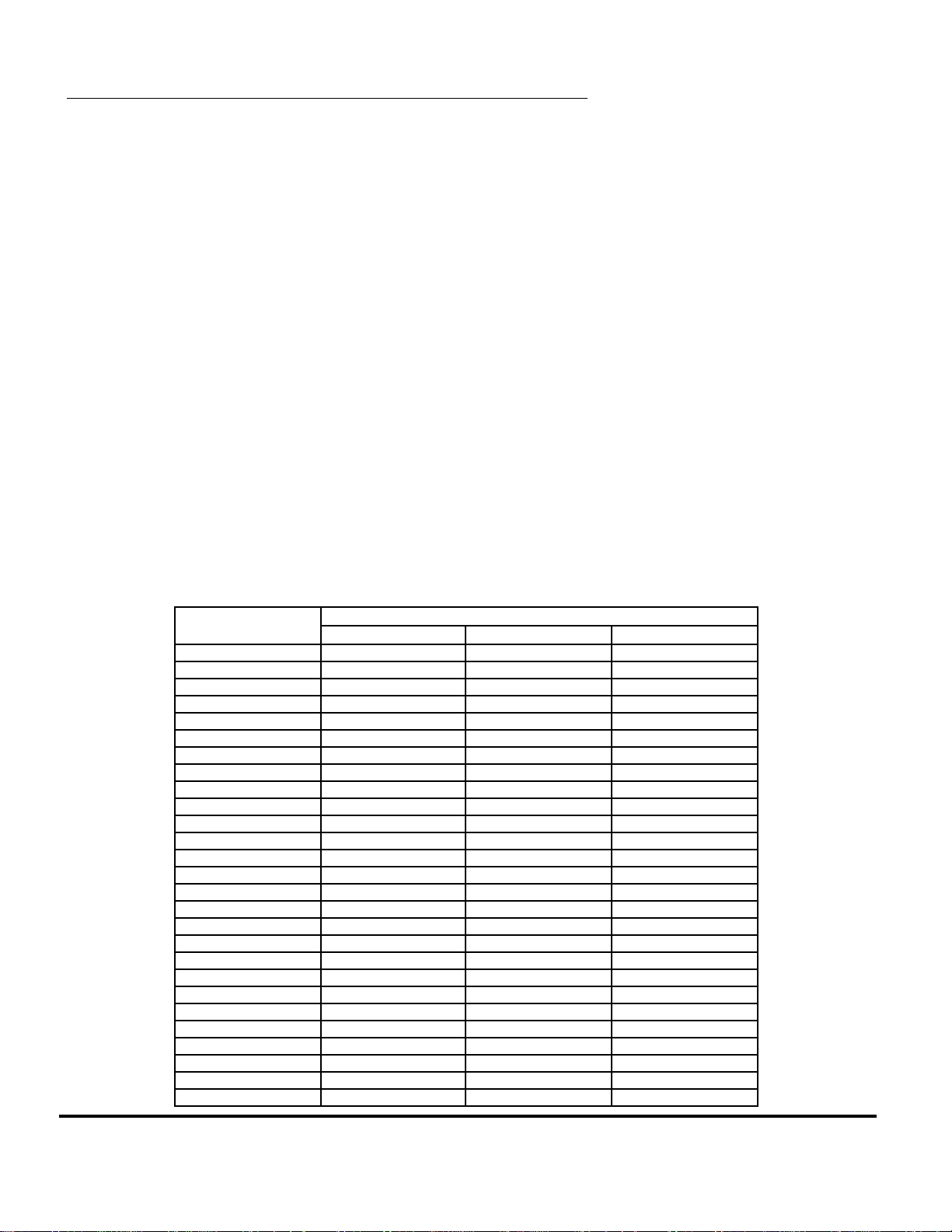

Table 1. STEL-2176 Pin Assignments

Pin No. Pin Name Pin Type Pin Description

1 VSS Ground

2 VDD Power Dedicated to crystal oscillator at pins 3 & 4

3 RXOSCIN Input Receiver oscillator input

4 RXOSCOUT Output Receiver oscillator output

5 VSS Ground Dedicated to crystal oscillator at pins 3 & 4

6 VDD Power Dedicated to digital section of receive clock multiplier

7 VDDA Power (Analog) Dedicated to analog section of receive clock multiplier

8 RXMULTEN Input Enable receive clock multiplier

9 VSSA Ground

(Analog)

10 VSS Ground Dedicated to receive clock multiplier

11 RXMULTCLK Output Receive clock multiplier output; enabled by pin 58

12 VDD Power

13 ADCDATASEL[2] Input ADC/DAC bypass mode select; 111=normal operation

14 ADCDATASEL[1] Input ADC/DAC bypass mode select; 110=bypass ADC

15 ADCDATASEL[0] Input ADC/DAC bypass mode select; 101=bypass DAC

16 VSS Ground

17 ADDATA[9] Bi-directional Bypass/test ADC/DAC

Dedicated to receive clock multiplier

User Manual 3 STEL-2176

Page 13

Introduction

Pin No. Pin Name Pin Type Pin Description

18 ADDATA[8] Bi-directional Bypass/test ADC/DAC

19 ADDATA[7] Bi-directional Bypass/test ADC/DAC

20 ADDATA[6] Bi-directional Bypass/test ADC/DAC

21 ADDATA[5] Bi-directional Bypass/test ADC/DAC

22 VDD Power

23 ADDATA[4] Bi-directional Bypass/test ADC/DAC

24 ADDATA[3] Bi-directional Bypass/test ADC/DAC

25 ADDATA[2] Bi-directional Bypass/test ADC/DAC

26 ADDATA[1] Bi-directional Bypass/test ADC/DAC

27 ADDATA[0] Bi-directional Bypass/test ADC/DAC

28 VSS Ground

29 RXAGCOUTB Output AGC output B

30 RXAGCOUTA Output AGC output A

31 VDD5 Power 3.3V or 5V for AGC pins 29 & 30

32 V3OP Input Must set high if pin 31 is 3.3V or low if pin 31 is 5V

33 VSS Ground

34 IC Internal connection - leave open

35 SO Output SPI data out

36 VDD Power

37 SI Input SPI data in

38 SCK Input SPI clock

39 VSS Ground

40 ADDR[7] Input Control/Status register parallel address bus

41 ADDR[6] Input Control/Status register parallel address bus

42 ADDR[5] Input Control/Status register parallel address bus

43 ADDR[4] Input Control/Status register parallel address bus

44 VDD Power

45 ADDR[3] Input Control/Status register parallel address bus

46 ADDR[2] Input Control/Status register parallel address bus

47 ADDR[1] Input Control/Status register parallel address bus

48 ADDR[0] Input Control/Status register parallel address bus

49 VSS Ground

50 INTSEL[1] Input Serial/parallel inter. sel.: 00=parallel, 01=SPI (serial)

51 INTSEL[0] Input Serial/parallel interface select: 10=reserved, 11=res.

52 VDD Power

53 VSS Ground

54

55

56

57 VDD Power

58 ENCLKOUT Input Enables output pins 11 & 102

59 VSS Ground

60 DATA[7] Bi-directional Control/Status register parallel data in/out

61 DATA[6] Bi-directional Control/Status register parallel data in/out

62 DATA[5] Bi-directional Control/Status register parallel data in/out

63 DATA[4] Bi-directional Control/Status register parallel data in/out

64 VDD Power

65 DATA[3] Bi-directional Control/Status register parallel data in/out

66 DATA[2] Bi-directional Control/Status register parallel data in/out

67 DATA[1] Bi-directional Control/Status register parallel data in/out

68 DATA[0] Bi-directional Control/Status register parallel data in/out

69 VSS Ground

70 RXRESCLK Output FEC test clock output (8 times RX symbol rate)

71 VDD Power

72 RXTSTDOUT[9] Output Test mux output

73 RXTSTDOUT[8] Output Test mux output

74 RXTSTDOUT[7] Output Test mux output

75 RXTSTDOUT[6] Output Test mux output

CS

WRB

DSB

Input Control/Status register chip select (active low)

Input Control/Status register read/write (low=write)

Input Control/Status register data strobe signal (active low)

STEL-2176 4 User Manual

Page 14

Pin No. Pin Name Pin Type Pin Description

76 VSS Ground

77 RXTSTDOUT[5] Output Test mux output

78 RXTSTDOUT[4] Output Test mux output

79 RXTSTDOUT[3] Output Test mux output

80 RXTSTDOUT[2] Output Test mux output

81 VDD Power

82 RXTSTDOUT[1] Output Test mux output

83 RXTSTDOUT[0] Output Test mux output

84 RXTSTCLK Output Test mux output clock

85 VSS Ground

86 VDD Power Dedicated to digital portion of DAC

87 VDDA Power (analog) Dedicated to analog portion of DAC

88 DACOUTP Analog output Output of DAC. Terminate in 37.5 ohms to ground

89 DACOUTN Analog output Comp. output of DAC. Terminate in 37.5 ohms to ground

Figure 2)

90 VSSA Power (analog) Dedicated to analog portion of DAC

91 VSS Ground Dedicated to digital portion of DAC

92 VDD Power Dedicated to crystal oscillator at pins 93 & 94

93 TXOSCIN Input TX oscillator input

94 TXOSCOUT Output TX oscillator output

95 VSS Ground Dedicated to crystal oscillator at pins 93 & 94

96 VDD Power Dedicated to digital section of transmit clock PLL

97 VDDA Power (analog) Dedicated to analog section of transmit clock PLL

98 TXPLLEN Input Enable transmit clock PLL

99 VSSA Ground (analog) Dedicated to analog section of transmit clock PLL

100 TXBYPCLK Input High speed transmit bypass clock

101 VDD Power Dedicated to digital section of transmit clock PLL

102 TXPLLCLK Output Transmit clock PLL output; enabled by pin 58

103 VSS Ground Dedicated to digital section of transmit clock PLL

104 VDD Power

105 VSS Ground

106

TXRSTB

Input Transmit reset (active low)

107 VDD Power

108 TXTSDATA Input Transmit data input

109 TXDATAENI Input Transmit data enable input

110 TXTCLK Input Transmit tclk

111 VSS Ground

112 TXFCWSEL[1] Input Transmit frequency control word (FCW) select

113 TXFCWSEL[0] Input Transmit frequency control word (FCW) select

114 VDD Power

115 TXCLKEN Input Transmit clock enable

116 TXDIFFEN Input Transmit differential encoder enable

117 TXRDSLEN Input Transmit Reed-Solomon enable

118 TXSCRMEN Input Transmit scrambler enable

119 VSS Ground

120 TXCKSUM Output Transmit Reed-Solomon check sum

121 TXACLK Output Transmit auxiliary clock output

122 TXDATAENO Output Transmit data enable output

123 VDD Power

124 TXBITCLK Output Transmit bit clock

125 TXSYMPLS Output Transmit symbol pulse output

126 TXNCOLD Input Transmit NCO load

127 VDD5 Power Input buffer bias. Set to 3.3V or 5V dep. on max. input V.

voltage.

128 RXRSTB Input Receiver reset (active low)

129 VSS Ground

130 RXPDATAOUT[7] Output Receive parallel output data

131 RXPDATAOUT[6] Output Receive parallel output data

132 RXPDATAOUT[5] Output Receive parallel output data

Introduction

(See Figure 2)

(See

User Manual 5 STEL-2176

Page 15

Introduction

Pin No. Pin Name Pin Type Pin Description

133 RXPDATAOUT[4] Output Receive parallel output data

134 VDD Power

135 RXPDATAOUT[3] Output Receive parallel output data

136 RXPDATAOUT[2] Output Receive parallel output data

137 RXPDATAOUT[1] Output Receive parallel output data

138 RXPDATAOUT[0] Output Rec. par. output data or serial data if in serial mode

139 VSS Ground

140 RXOUTCLK Output Receive output data clock

141 VDD Power

142 RXACQFLAG Output Receive demod. acquisition flag

143 RXACQFAIL Output Receive demod. acquisition failure flag

144 RXDECDFLG Output Receive FEC decodable flag

145 FRAMESYNC Output Receive output frame sync flag

146 VSS Ground

147 SRAMADDR[15] Output De-Interleaver optional external SRAM address

148 SRAMADDR[14] Output De-Interleaver optional external SRAM address

149 SRAMADDR[13] Output De-Interleaver optional external SRAM address

150 SRAMADDR[12] Output De-Interleaver optional external SRAM address

151 VDD Power

152 SRAMADDR[11] Output De-Interleaver optional external SRAM address

153 SRAMADDR[10] Output De-Interleaver optional external SRAM address

154 SRAMADDR[9] Output De-Interleaver optional external SRAM address

155 SRAMADDR[8] Output De-Interleaver optional external SRAM address

156 VSS Ground

157 VDD Power

158 VSS Ground

159 SRAMADDR[7] Output De-Interleaver optional external SRAM address

160 SRAMADDR[6] Output De-Interleaver optional external SRAM address

161 SRAMADDR[5] Output De-Interleaver optional external SRAM address

162 SRAMADDR[4] Output De-Interleaver optional external SRAM address

163 VDD Power

164 SRAMADDR[3] Output De-Interleaver optional external SRAM address

165 SRAMADDR[2] Output De-Interleaver optional external SRAM address

166 SRAMADDR[1] Output De-Interleaver optional external SRAM address

167 SRAMADDR[0] Output De-Interleaver optional external SRAM address

168 VSS Ground

169 SRAMDATA[7] Bi-Directional De-Interleaver optional external SRAM data bus

170 SRAMDATA[6] Bi-Directional De-Interleaver optional external SRAM data bus

171 SRAMDATA[5] Bi-Directional De-Interleaver optional external SRAM data bus

172 SRAMDATA[4] Bi-Directional De-Interleaver optional external SRAM data bus

173 VDD Power

174 SRAMDATA[3] Bi-Directional De-Interleaver optional external SRAM data bus

175 SRAMDATA[2] Bi-Directional De-Interleaver optional external SRAM data bus

176 SRAMDATA[1] Bi-Directional De-Interleaver optional external SRAM data bus

177 SRAMDATA[0] Bi-Directional De-Interleaver optional external SRAM data bus

178 VSS Ground

179 SRAMWEB Output De-Interleaver SRAM write enable (active low)

180 SRAMCSB Output De-Interleaver SRAM chip select (active low)

181 SRAMOEB Output De-Interleaver SRAM output enable (active low)

182 VDD Power

183 RXIENBLE Input FEC test input I clock

184 RXQENBLE Input FEC test input Q clock

185 VSS Ground

186 RXBYPCLK Bi-directional Receiver bypass clock input; output reserved

187 VDD Power

188 VSSA Ground (analog) Dedicated to analog section of ADC

189 VDDA Power (analog) Dedicated to analog section of ADC

190 VCMA Analog output From ADC

(See Figure 1)

191 VDD Power Dedicated to digital section of ADC

(See Figure 1)

(See Figure 1)

(See Figure 1)

STEL-2176 6 User Manual

Page 16

Introduction

Pin No. Pin Name Pin Type Pin Description

192 VREFN Analog output From ADC

193 VSSA Ground (analog) Dedicated to analog section of ADC

194 VSS Ground Dedicated to digital section of ADC

195 VDDA Power (analog) Dedicated to analog section of ADC

196 VDDA Power (analog) Dedicated to analog section of ADC

197 ADCINP Analog input ADC input

198 ADCINN Analog input Complementary ADC input

199 VSSA Ground (analog) Dedicated to analog section of ADC

200 VSSA Ground (analog) Dedicated to analog section of ADC

201 VDD Power Dedicated to digital section of ADC

202 VDDA Power (analog) Dedicated to analog section of ADC

203 VREFP Analog output From ADC

204 VSS Ground Dedicated to digital section of ADC

205 VCMB Analog output From ADC

206 VSSA Ground (analog) Dedicated to analog section of ADC

207 VDDA Power (analog) Dedicated to analog section of ADC

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

(See Figure 1)

208 VDD Power

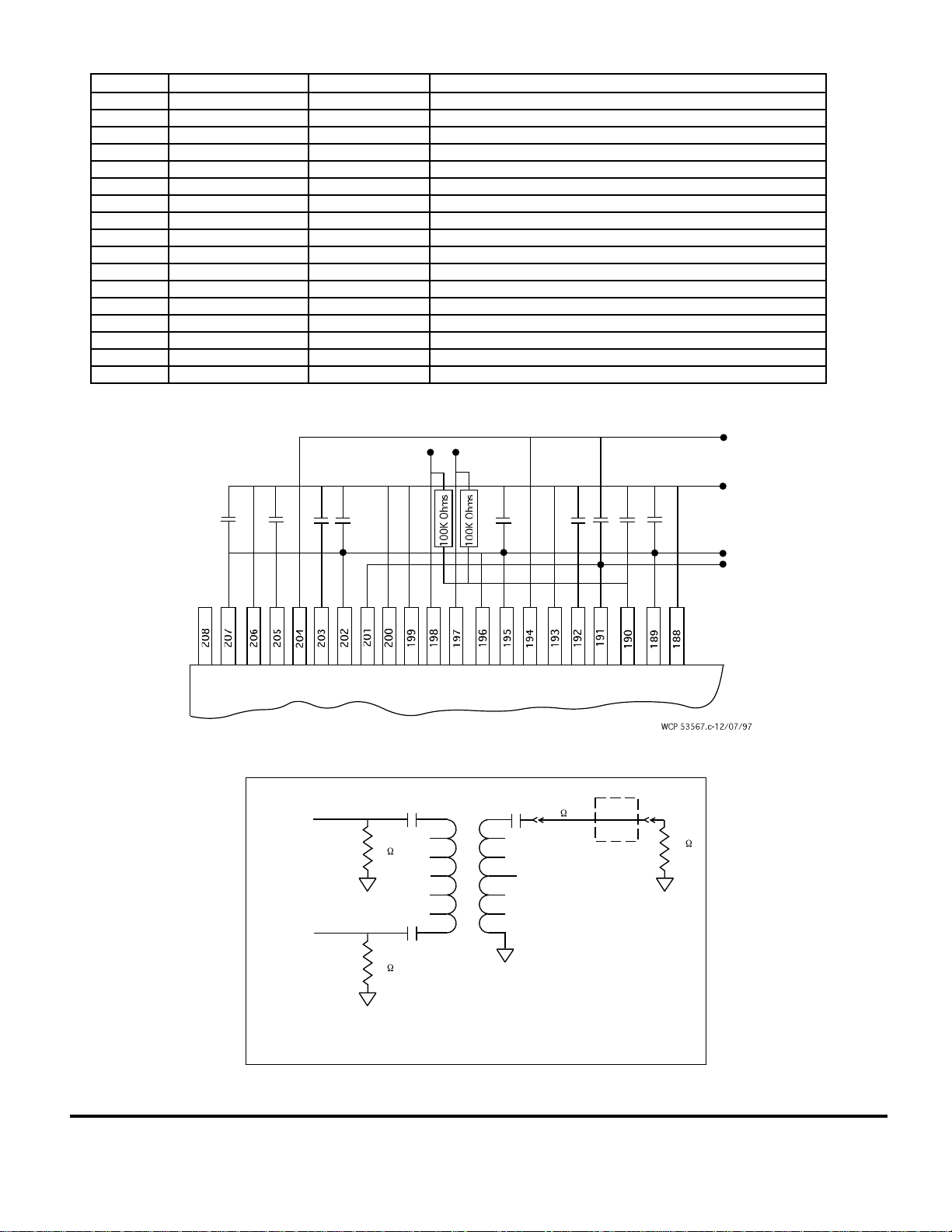

Analog In (P)Analog In (N)

0.1

µF

0.1µF0.1

µF

0.1

µF

0.1

0.1

µF

µF

0.1

µF

0.1

0.1

µF

µF

Digital GND

(VSS)

Analog GND

(VSSA)

DACOUTP

DACOUTN

STEL-2176

Figure 1. Reference A/D Wiring

T1-6TKK81

0.1 µF

50

AV

SS

0.1 µF

Mini-

50

AV

SS

Circuits

1:1

0.1 µF

50 line

X

Note 1

Digital Supply

(VDD)

50

load

Note 1: Normally some application dependent alias filtering and

amplitude control appear at this point in the circuit

WCP 53807.c-12/5/97

Figure 2. Example Output Load Schematic

User Manual 7 STEL-2176

Page 17

Introduction

ELECTRICAL SPECIFICATIONS

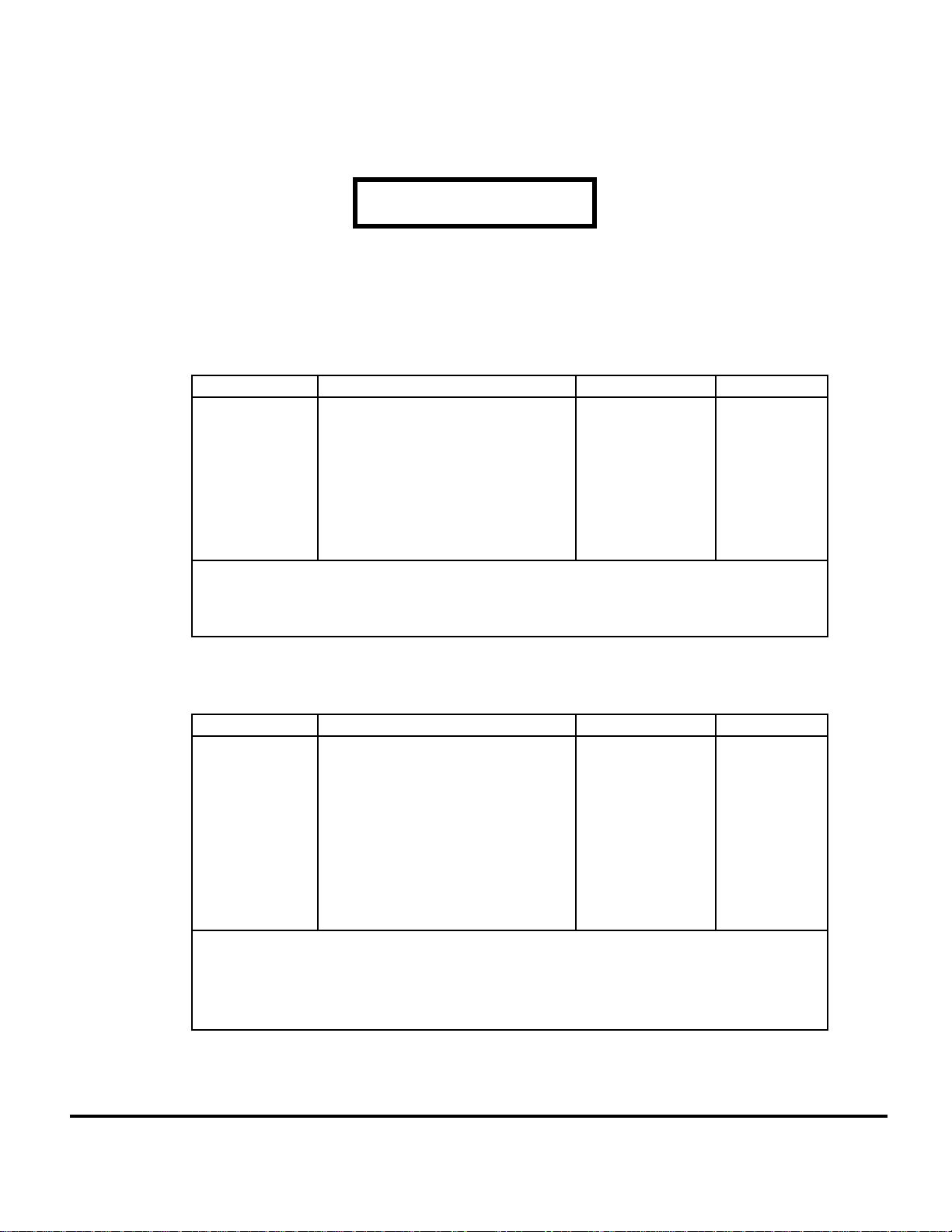

The STEL-2176 electrical characteristics are provided by Table 2 through Table 4.

WARNING

Stresses greater than those shown in Table 2 may cause permanent damage to the STEL-2176.

Exposure to these conditions for extended periods may also affect the STEL-2176 reliability.

Table 2. Absolute Maximum Ratings

Symbol Parameter Range Units

T

stg

V

DDmax

A

VDDmax

5V

AV

V

I(max)

I

i

P

Diss (max)

DDmax

SS

Storage Temperature Ð40 to +125 °C

Supply voltage on VDD Ð0.3 to +4.6 volts

Supply voltage on AVDD Ð0.3 to +4.6 volts

Supply voltage on 5VDD Ð0.3 to +7.0 volts

Analog supply return for AVDD ± 10% of VDD volts

Input voltage Ð0.3 to 5VDD+0.3 volts

DC input current ± 30 mA

Power dissipation 1500 mW

Note:

All voltages are referenced to V

5V

must be greater than or equal to VSS. This rule can be violated for a maximum of 100 msec

DD

during power up.

.

SS

Note 1

Note 2

Table 3. Recommended Operating Conditions

Symbol Parameter Range Units

AV

5V

V

DD

C

LOAD

R

LOAD

DD

DD

Supply Voltage +3.3 ± 10% Volts

Supply Voltage +5.0 ± 10% Volts

Supply Voltage +3.3 ± 10% Volts

DAC Load Capacitance

DAC Load Resistance

≤ 20

≤ 30K

pF

ohms

Recommended DAC Load 37.5 ohms

V

LOAD

T

a

DAC Output Voltage

≤ 1.25

Volts

Operating Temperature (Ambient) Ð40 to +85 °C

Note:

1. All voltages with respect to VSS and assume AV

ss

= V

ss

2. If interface logic is to be driven by VDD then connect the 5VDD pin to the VDD supply and set

pin 32 to correct value.

3. Duty Cycle Derating is required from +70° to +85° C.

Note 1

Note 2

Note 3

STEL-2176 8 User Manual

Page 18

Introduction

Table 4. ADC Performance Specifications

Parameter Min Nom Max Units

Sampling Frequency 50 MHz

Resolution 10 bits

Input Differential Signal Range -0.75 +0.75 Volts

Analog Input Bandwidth 60 MHz

Signal to Distortion Ratio 10 MHz

54 dB

signal over 25 MHz BW

Input Common Mode 1.4 1.5 1.6 Volts

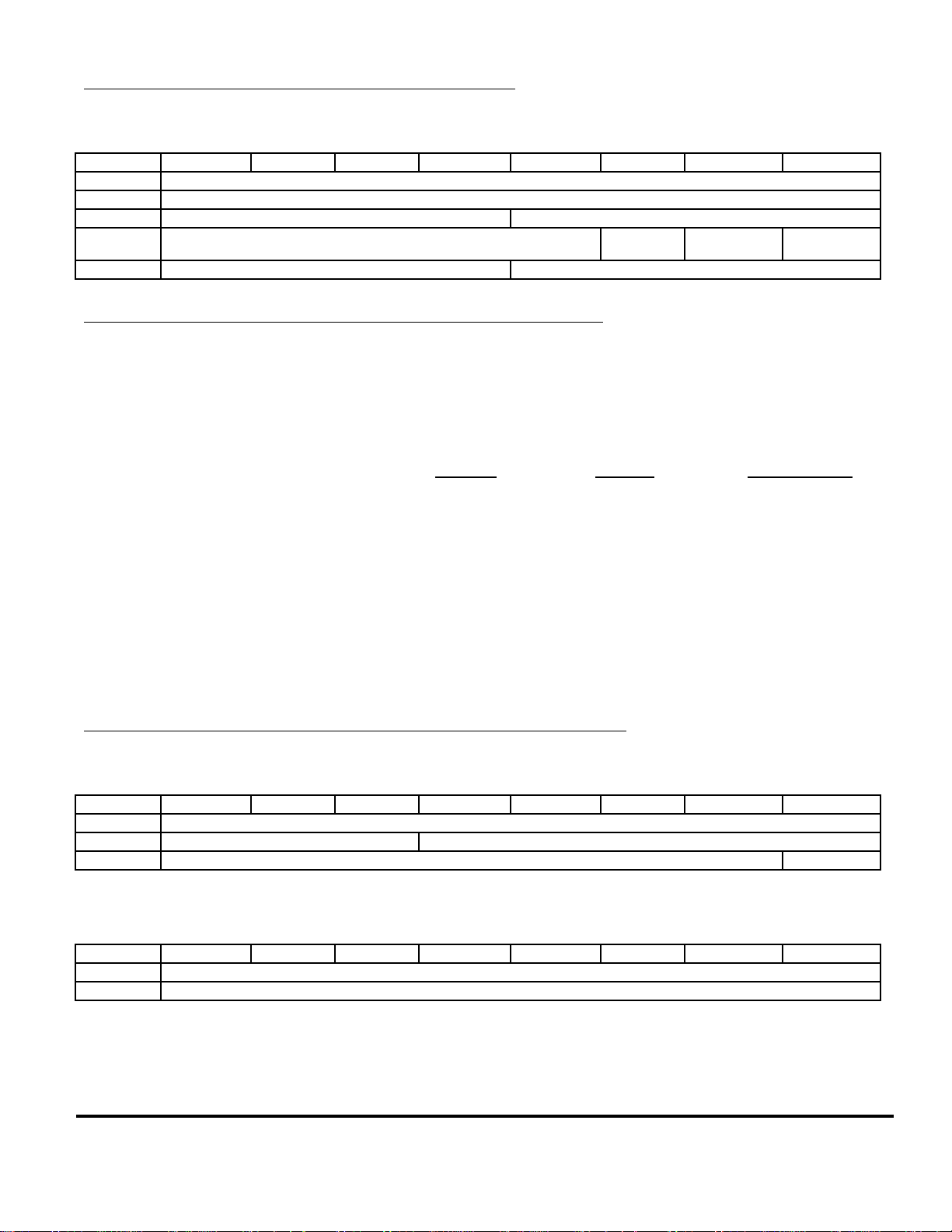

Table 5. DC Characteristics

(V

= 3.3 V ±10%, V

DD

Symbol Parameter Min. Nom. Max. Units Conditions

I

VDDQ

I

VDD

I

5V

DD

I

AV

DD

V

IH

CLK

V

IL

CLK

V

IH

V

IL

I

IH

I

IL

V

OH(min)

V

OL(max)

I

OS

C

IN

C

OUT

I

OFS

V

O

R

O

C

O

Supply Current, Quiescent 1.0 mA Static, no clock

Supply Current, Operational, V

Supply Current, Operational, 5V

Supply Current, Operational, AV

DD

DD

DD

Clock High Level Input Voltage 2.0 volts CLK, Logic '1'

Clock Low Level Input Voltage 0.8 volts CLK, Logic '0'

High Level Input Voltage 2.0 volts Other inputs, Logic '1'

Low Level Input Voltage 0.8 volts Other inputs, Logic '0'

High Level Input Current 10 µAV

Low Level Input Current Ð10 µAV

High Level Output Voltage 2.4 3.0 VDD volts IO = Ð2.0 mA

Low Level Output Voltage 0.2 0.4 volts IO = +2.0 mA

Output Short Circuit CurrentÊ 40 mA V

Input Capacitance 2 pF All inputs

Output Capacitance 4 10 pF All outputs

Output Full Scale DAC Current 16 19 22 mA Single output

DAC Compliance Voltage

(Differential)

DAC Output Resistance

1

DAC Output Capacitance 4 8 pF

= 0 V, T

SS

= -40° to 85° C)

a

1.9 mA/MHz

0.2 mA

12.0 mA

±0.96

Volts Based on 50 ohms load

N/A

= 5V

IN

IN

OUT

= V

= VDD,

DD

SS

VDDÊ=Êmax

resistance to ground.

NOTES:

1. Current source to ground output.

User Manual 9 STEL-2176

Page 19

Receiver Description

RECEIVER

OVERVIEW

The STEL-2176 is a complete subscriber-side cable

modem ASIC which integrates both the downstream

receiver and upstream transmitter functions. The

receiver includes a high performance 10-bit Analog-toDigital Converter (ADC) with a direct Intermediate

Frequency (IF) interface. The receiver also includes a

QAM demodulator and both ITU-T (J.83) Annex A and

Annex B Forward Error Correction (FEC). The

upstream transmitter includes a BPSK/QPSK/16QAM

modulator with highly flexible FEC and scrambling,

and a 10-bit low spurious digital to analog converter

(DAC) for direct synthesis of an upstream 5 to 65 MHz

signal. Both the receiver and transmitter are highly

flexible and programmable; the STEL-2176 Digital

Mod/Demod ASIC offers a solution to meet current

and evolving standards.

The input to the STEL-2176 receiver is an analog IF

signal of up to 50 MHz. Typically, the IF signal has 44

MHz center frequency with a 6 MHz bandwidth for

NTSC based systems, or a 36 MHz center frequency

with an 8 MHz bandwidth for PAL based systems. In

typical applications, the input signal is sampled by the

ADC at approximately 25 MHz for the 44 MHz IF, or at

approximately 29 MHz for the 36 MHz IF

This type of sub-sampling technique works by

intentionally undersampling the carrier frequency so

that aliased signal appears at a lower frequency. The

sampling rate is still high enough to capture all of the

modulation bandwidth without distortion. In the case

of a 44 MHz IF and a 25 MHz clock, the resulting digital

signal is centered at 6 MHz. In the case of a 36 MHz IF

and 29 MHz clock, the resulting digital signal is

centered at 7 MHz. For more information on subsampling techniques, please see Stanford Telecom

Application Note A-117.

The digital samples from the ADC are downconverted

to baseband I and Q signals in the Digital Down

Converter (DDC) block. Since the RF tuner sections of a

cable modem may have large frequency errors, an

Automatic Frequency Control (AFC) block is used in

the STEL-2176 for coarse tuning of the DDC. This

allows rapid acquisition of the input signal even with

frequency errors of ±200 kHz. Fine tuning of the DDC is

done using a carrier Phase-Lock Loop (PLL).

An Automatic Gain Control (AGC) function provides

two output signals to adjust the RF and IF analog gain

stages of circuitry external to the STEL-2176, so that the

ADC input is in the optimal range. The two outputs can

be programmed to create a sequential AGC system

which maximizes RF gain for improved receiver noise

figure. The two AGC outputs and the external gain

adjust blocks work together to maximize ADC

performance, but when large adjacent channels are

present, the power of the desired signal may change. A

second digital AGC tracks and adjusts the level of the

desired signal after the adjacent channel energy is

removed by filtering.

Following the DDC, a square root raised cosine Nyquist

filter eliminates adjacent channel signals, and performs

matched filtering to eliminate intersymbol interference.

The filter excess bandwidth or alpha is programmable

from 0.12 to 0.20. The Timing Recovery block finds the

exact location in the center of each symbol using a

special low-jitter discriminator. These values are fed to

the Adaptive Channel Equalizer.

An Adaptive Channel Equalizer (ACE) compensates for

any multipath distortion on the input signal introduced

in the channel. The equalizer uses one sample per

symbol (T spaced taps). The output of the equalizer is

baseband I and Q signals with carrier frequency and

phase errors, symbol timing errors, gain errors, and

multipath effects removed.

The Demapper takes the baseband I and Q signals

representing the QAM symbols, and translates each

symbol back into a series of binary values based on one

of the selectable constellation maps.

Following the Demapper is the Forward Error

Correction (FEC) system. This programmable system

supports both the ITU-T (J.83) Annex A (see page 14)

and Annex B (see page 16) standards. In general, both

FEC systems employ Reed Solomon Decoders, Frame

Sync circuits that determine the FEC code block

boundaries, and a De-Interleaver. Interleaving is used

in the FEC standards to improve performance when the

channel contains bursty noise. Since the transmitter

Interleaver spreads the data over a large time, when the

receiver performs the matched operation to the

Interleaver in order to bring the data back into the

correct time sequence, any burst errors appear to be

spread out in time. This helps makes these errors

STEL-2176 10 User Manual

Page 20

Receiver Description

correctable by the FEC. The STEL-2176 internal memory

can support all MCNS Interleaver configurations. For

deeper interleaving, a direct interface to external

memory is provided.

The output of the receiver is typically arranged as

MPEG-2 frames, although the MPEG-2 framing can be

Fo=44/36 MHz

BW= 6/8 MHz

A

10 bits/

Sample

4Samples/Symbol

ADC

~25 MHz

44 MHz

36 MHz

Interpolator

AFC

AGC

DDC

1st IF Output

Programmable

Nyquist

(0.12 to 0.2)

by-passed for ATM applications. The output can be 8bit parallel with a byte clock or serial with a bit clock.

The data can be output in a smooth fashion without

inter-frame gaps or with the pauses in output data

caused by the FEC system passed through to the output

(see Receiver Timing discussion).

A

Clock

Recovery

Adaptive

Channel

Equalizer

(20 taps)

De-mapper

Viterbi

Diff. Decoder

Reed-Solomon

Decoder

(204,188 and

128,122)

Micro Controller Interface

Micro Controller ( SPI, Parallel)

Figure 3. STEL-2176 Receiver Block Diagram

FUNCTIONAL BLOCKS

ADC

The ADC uses differential analog signal inputs

ADCINP and ADCINN. Differential coupling to the

ADC is important to prevent common mode noise from

the digital sections of the ASIC from coupling into the

input. The recommended input signal level is ± 0.75V.

The input is sampled by the ADC, and the samples are

converted into 10-bit digital values. The sampling rate

is typically 25 MHz for an input of 44 MHz ± 3 MHz

with a symbol rate of about 5 MHz (i.e., the MCNS

standard) or 29 MHz for an input of 36 MHz ± 4 MHz

with a symbol rate of about 7 MHz (i.e., the DAVIC and

DVB standards). The sampling rate is controlled the

choice of crystal connected between RXOSCIN and

RXOSCOUT or by the clock frequency applied to

Clock

Synthesizer

~25 MHz XO

Frame Sync

Deinterleaver

External RAM

WCP 52861.c-5/07/97

RXOSCIN. The sample rate must be slightly more than

4 samples per symbol. The sample clock generated by

the crystal/receive clock oscillator or applied to

RXOSCIN must be a low phase noise signal. For this

reason, dedicated power and ground connections for

the receive oscillator and input buffer are adjacent to

the RXOSCIN and RXOSCOUT pins.

Microcontroller Interface

The microcontroller interface provides access to the

internal programmable Universal, Downstream

(Receive), and Upstream (Transmit) registers (see page

20) via a parallel or a SPI interface. The interface used is

selected by the interface select lines (INTSEL[1-0]).

User Manual 11 STEL-2176

Page 21

Receiver Description

The parallel interface consists of an 8-bit address bus

(ADDR[7-0]), an 8-bit bi-directional data bus (DATA[70]), and the control signals chip select (CS), read/write

(WRB), and data strobe (DSB).

The SPI interface consists of a serial input (SI), serial

output (SO), and a serial clock (SCK).

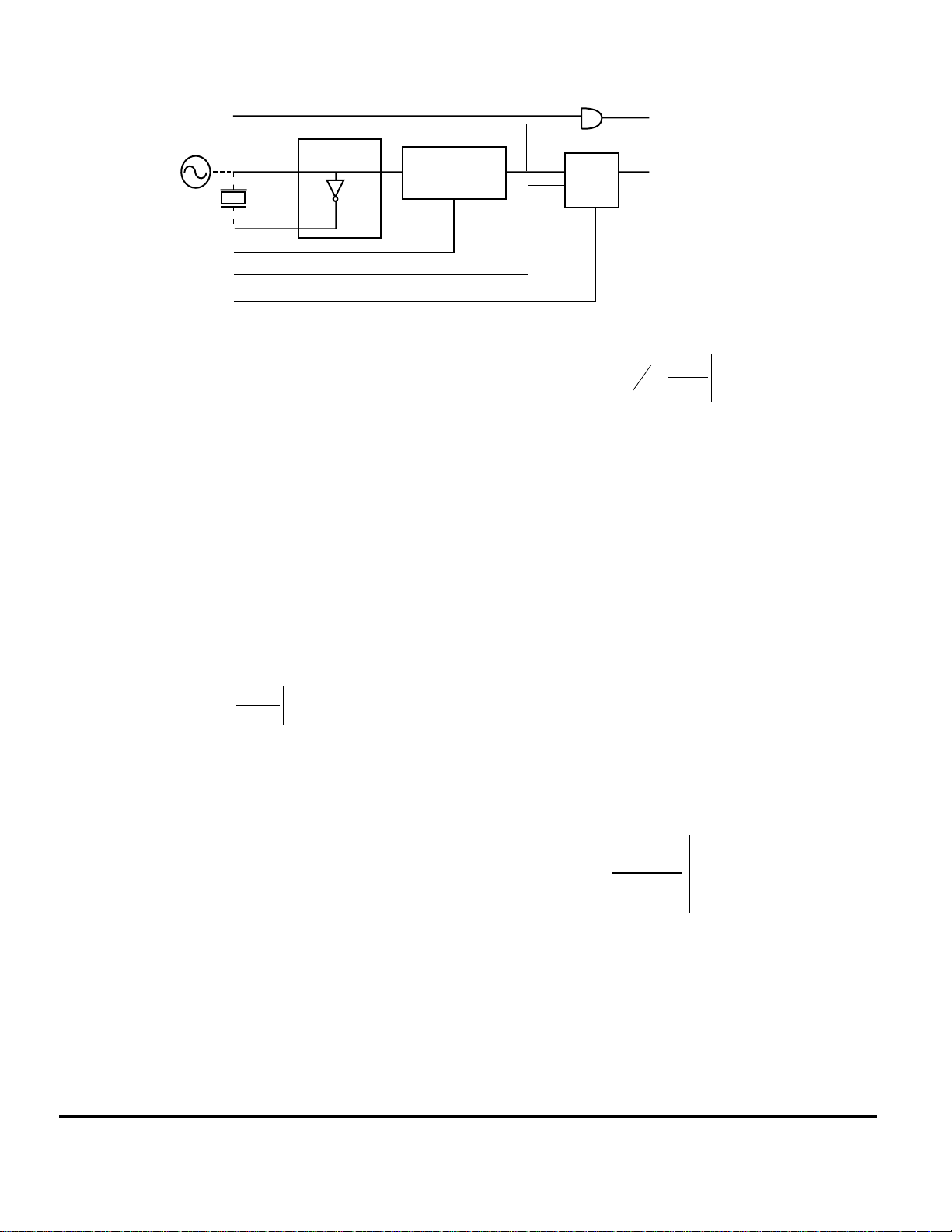

Master Receive Clock Generator

The STEL-2176 uses a master clock (MCLK) to control

the receive timing functions. MCLK can be generated in

either of three ways as shown in Figure 4.

A receive bypass clock can be applied to the

RXBYPCLK input and selected to drive CLK. The

RXMULTEN should be held high to select the

RXBYPCLK input.

An external clock can be applied to the RXOSCIN input

or a crystal can be connected across the RXOSCIN and

RXOSCOUT inputs. The oscillator circuit outputs a 2050 MHz signal to a frequency multiplier PLL, which

upconverts the signal to a 100-150 MHz clock. When the

bypass clock is not used, RXMULTEN is driven high to

select the output of the frequency multiplier to drive

the MCLK signal. The frequency multiplier output

frequency is controlled by the formula:

MCLK OscillatorOutput

=∗

N

M

where:

• The Oscillator signal (RXOSCIN and

RXOSCOUT) is four times the signal symbol rate.

• The value of M and N should be selected so

MCLK is four times the value of the Oscillator

signal.

• N is the value stored in RxFsynN (bits 6-0 of Bank

0 Register F7H), and M is the value stored in

RxFsynM (bits 6-0 of Bank 0 Register F6H).

• The recommended values for DAVIC, DVB, and

IEEE 802.14 are Oscillator Frequency = 29 MHz,

M = 2, and N = 8. The recommended values for

MCNS are Oscillator Frequency = 25 MHz, M = 2,

and N = 8.

ENCLKOUT

RXOSCIN

RXOSCOUT

RXMULTEN

RXBYPCLK

RXBYPASSFSYN

OSCILLATOR

FREQUENCY

MULTIPLIER

PLL

Figure 4. Master Receive Clock Generator

MUX

WCP 53852.c-12/7/97

RXMULTCLK

To ADC

MCLK

STEL-2176 12 User Manual

Page 22

Receiver Description

QAM Demodulator Blocks

The following diagram shows the major QAM circuit

blocks.

OutA OutB

AGC

S(t)

ADC

DDC

AFC

I,Q

Timing

Recovery

& SRRC

Filter

I,Q

(1 sample/

symbol)

Adaptive

Equalize

WCP 53702.c-10/28/97

I,Q

(to FEC)

Figure 5. QAM Demodulator Blocks

Digital Down Converter (DDC)

The digital samples from the ADC are mixed down to

baseband I and Q signals in the Digital Down

Converter (DDC) block. The input analog signal is subsampled at the rate set by the receive crystal oscillator

or a clock applied directly to the RXOSCIN input. The

resultant sub-sampled input signalÕs spectrum is

aliased to a lower frequency. In typical cases, with a 44

MHz _ 3 MHz input and a 25 MHz sample rate, the

digital signal appears to the input of the DDC as a 6

MHz _ 3 MHz signal. For a 36 MHz _ 4 MHz input and

a 29 MHz sample rate, the digital signal appears to the

input of the DDC as a 7 MHz _ 4 MHz signal. Other

input frequencies and sample rates are also possible.

The digital signal is down converted to baseband I and

Q by mixing with cos 2π fct and sin 2π f

t where fc is the

c

center frequency of the digital signal.

The Digital Down Converter contains a numerically

controlled oscillator (NCO) with cosine and sine

outputs, a pair of mixers, and an image filter. The

frequency f

is a combination of a starting value that is

c

set using DeltaTheta_in [13:0] (bits 7-2 of Bank 0

Register 10H and Bank 0 Register 11H) and any

frequency error terms computed by the Automatic

Frequency Control block. The value for DeltaTheta_in

[13:0] is given by:

DeltaTheta_in [13:0] = f

/ADC sample rate _214

c

For fc = 6 MHz and ADC sample rate = 25 MHz,

DeltaTheta_in [13:0] = 0F5C

H

For fc = 7 MHz and ADC sample rate = 29 MHz,

DeltaTheta_in [13:0] = 0F73

H

The complex NCO drives a pair of multipliers which

serve as mixers. The products of the ADC samples and

the sine and cosine outputs of the NCO produce the

desired baseband I and Q signals plus undesired higher

frequency image terms. These higher frequency terms

are removed by an image filter.

Automatic Frequency control (AFC)

The STEL-2176 can accommodate up to ±200 kHz

uncertainty in the carrier frequency. The carrier

frequency recovery is divided into two steps. The first

step is a coarse frequency estimation during initial

signal acquisition. This estimation is performed by the

AFC section. The estimated carrier frequency offset is

calculated by the AFC and fed to the DDC NCO.

AGC

The AGC takes the output from the Image Filter in the

DDC and estimates the power of the signal. The AGC

discriminator compares the estimate to one or two

different thresholds that can be set via the registers

values AGC_ThresholdA (Bank 0 Register 14

AGC_ThresholdB (Bank 0 Register 15

). Thresholds

H

) and

H

should be set to optimize ADC performance. The range

of the AGC`s power thresholds is 0 to 128 (2

8-1

). For 256-

QAM, the value ranges from about 75 to 100 (default is

96), depending on the desired A/D clipping level. The

trade off for selecting the value weighs occasional ADC

clipping with a large input versus loss of signal fidelity

with a small input. The power of the input signal

depends upon adjacent channel interference, AM hum,

burst noise, etc.

The AGC generates two 1-bit outputs OUTA and OUTB

that indicate whether that the input analog signal is too

high or too low. The OUTA and OUTB signals should

be smoothed using low pass filters. These filters can

each be a series resistor of ___ ohms and a shunt

capacitor of ___ _F. OUTA and OUTB can be set to

have a logic high voltage of either 3.3V or 5V. For 3.3V

operation, connect the power source's +3.3V output to

pins 31 and 32 and its return to VSS. For 5V operation,

connect the power source's +5V output to pin 31 and its

return to pin 32 and VSS.

The polarity of OUTA and OUTB may be controlled

with AGC_InvertOutputA (bit 0 of Bank 0 Register 12

H

and AGC_InvertOutputB (bit 1 of Bank 0 Register 12H).

For variable gain stages where a higher control voltage

at the input to the filter produces higher gain, set the

AGC_InvertOutput bit to 0. For variable gain stages

)

User Manual 13 STEL-2176

Page 23

Receiver Description

where a higher control voltage at the input to the filter

produces lower gain, set the AGC_InvertOutput bit to

1.

The two outputs can be programmed to create a

sequential AGC system which maximizes RF gain for

improved receiver noise figure. This is accomplished by

setting AGC_ThresholdA (Bank 0 Register 14H) and

AGC_ThresholdB (Bank 0 Register 15H) to slightly

different values. The threshold which is set to a lower

value will cause its associated output to command

increase gain first. This output is typically connected to

the RF variable gain stages so that the best receiver

noise figure is achieved.

Timing Recovery and Nyquist Filter

The sampled signal (> 4 times the symbol rate in I and

Q format) is fed to this block to:

¥ Eliminate inter-symbol interference (ISI) by filtering it

with a square route raised cosine filter (SRRC) of a

selectable excess bandwidth (a) for 12%<= a<=20%.

¥ Recover the exact symbol rate, within 100 ppm of the

nominal value.

The adaptive equalizer control registers are Block 1

Registers 21H to 24H.

FEC Decoder Blocks

The purpose of the FEC subsystem is to improve the bit

error rate performance of the data link. The

arrangement of the FEC blocks in the receiver is in

reverse order from the transmitter. The STEL-2176 FEC

subsystem can decode signals which are generated in

conformance with either the ITU-T (J.83) Annex A or

Annex B FEC standards.

There are two different though similar set of blocks

used for ITU-T (J.83) Annex A (Figure 6) and Annex B

(Figure 13).

The STEL-2176 supports the MPEG-2 standard.

MPEG-2 uses 188 byte packets with a sync byte and

three header bytes containing service identification,

scrambling, and control information. The 184 bytes of

data follows the sync and header bytes. Normally this

header information flows through to the receiver

output, but with ITU-T (J.83) Annex B there is an option

of bypassing the MPEG-2 outer layer of processing.

¥ Resample and transmit one composite sample (I and

Q for each symbol) to the equalizer. These samples

are taken at the epoch of each symbol.

Adaptive Channel Equalizer

The output of the Timing Recovery block is fed to the

Adaptive Equalizer at a rate of one complex

sample/symbol. The Adaptive Equalizer will:

1. Compensate for channel distortion including:

a. Multipath

b. AM hum

c. FM hum

d. Phase noise

2. Fine tune to the carrier frequency and phase offset.

3. Set the acquisition flag ÒtrueÓ, after the equalizer

successfully locks on to the signal.

4. Write to ErrPwr (Block 0 Register 44H) the estimated

output SNR.

Annex A FEC

The ITU-T (J.83) Annex A FEC subsystem consists of

the following blocks:

I,Q from

Adaptive

Equalizer

De-mapper De-Interleaver

Reed-Solomon

Decoder

De-Randomizer

Frame

Sync

To Output Clock

WCP 53703.c-10/28/97

Figure 6. ITU-T (J.83) Annex A FEC Subsystem

Demapper

This block maps the Adaptive Channel Equalizer I and

Q outputs for each symbol into 4, 6, or 8 bits for 16, 64,

or 256 QAM respectively. The mapping tables are as

follows:

STEL-2176 14 User Manual

Page 24

Receiver Description

Q

Q

110100 111100 101100 100100000100 001100 011100 010100

10

01

11

IkQk=10

0111

IkQk=10

00

00

=11 IkQk=01

I

kQk

10

10

IkQk=00

00

00

01 11

WCP 53711.c-10/29/97

Figure 7. 16 QAM Constellation

1100

1110 0110 0100 1000 1001 1101 1100

1101 1111 0111 0101 1010 1011 1111 1110

1001 1011 0011 0001 0010 0011 0111 0110

1000 1010 0010 0000 0000 0001 0101 0100

0100 0101 0001 0000 0000 0010 1010 1000

0110 0111 0011 0010 0001 0011 1011 1001

1110 1111 1011 1010 0101 0111 1111 1101

1100 1101 1001 1000 0100 0110 1110 1100

Q

I

IIIIIIIIIIIII

11

01

I

10

IkQk=00

I

I

=01IkQk=11

kQk

WCP 53712.c-10/29/97

110101 111101 101101 100101000101 001101 011101 010101

110111 111111 101111 100111000111 001111 011111 010111

110110 111110 101110 100110000110 001110 011110 010110

110010 111010 101010 100010000010 001010 011010 010010

110011 111011 101011 100011000011 001011 011011 010011

110001 111001 101001 100001000001 001001 011001 010001

rotate 90 degrees

IkQk=10

rotate 180 degrees

=11

I

kQk

rotate 270 degrees

=01

I

kQk

110000 111000 101000 100000000000 001000 011000 010000

IIIIIIIIIIIIII

I

Figure 9. 256 QAM Constellation (DAVIC)

Q

110100 110101 110001 110000100000 100001 100101 100100

110110 100111 110011 110010100010 100011 100111 100110

111110 111111 111011 111010101010 101011 100111 101110

111100 111101 111001 111000101000 101001 101101 101100

011100 011101 011001 011000001000 001001 001101 001100

011110 011111 011011 011010001010 001011 001111 001110

010110 010111 010011 010010000010 000011 000111 000110

rotate 90 degrees

IkQk=10

rotate 180 degrees

=11

I

kQk

rotate 270 degrees

=01

I

kQk

010100 010101 010001 010000000000 000001 000101 000100

IIIIIIIIIIIIII

I

IkQk=00

I

WCP 53713.c-10/29/97

IkQk=00

I

WCP 53839.c-12/5/97

Figure 8. 64 QAM Constellation

Two bits are the same for each modulation type, and

are identified as IKQK. The remaining bits are identified

as [b

q-1

. . . b

where q = 2, 4, and 6 for 16, 64 or 256

o],

QAM.

IKQK are processed by the differential decoder before

being fed to the frame sync block. The remaining bits

[b

q-1

. . . b

are fed directly to the frame sync.

o]

Differential Decoder

Two bits (IKQK) of each symbol are differentially

Figure 10. 256 QAM Constellation (DVB/IEEE 802.14)

b

= Ak = (I

q+1

bq = Bk = (Q

I

Demapper

Q

k

⊕ Q

k

⊕ I

Q

k

I

k

) ⊕ (I

k-1

) ⊕ (I

k-1

Q bits (b

Differential

Decoder

q-1

k-1

k-1

... b0)

⊕ Q

⊕ Q

Bk=b

Ak=b

) ¥ (1⊕Ik ⊕ Q

k-1

) ¥ (1⊕Ik ⊕ Q

k-1

M-tuple

q

Conversion

q+1

to

Byte

WCP 53708.c-10/28/97

Figure 11. Demapper

decoded according to the equation:

User Manual 15 STEL-2176

)

k

)

k

To Frame

Sync

Page 25

Receiver Description

Frame Sync

The frame sync receives symbols from the mapper.

Each symbol represents 4, 6 or 8 bits for 16 QAM, 64

QAM, and 256 QAM respectively. These bits are

collected into bytes. For 16 QAM, every two symbols

are converted into one byte. For 64 QAM, every 4

symbols to are converted into 3 bytes, and for 256 QAM

each symbol gives one byte..

Once bytes are formed, the frame sync block looks for a

sequence of fixed byte values separated by 203 bytes of

data.

47H (203 bytes) B8H (203 bytes) 47H (203 bytes) 47H (203

bytes) 47

47

. . .

H

H

. . .

47

. . . .

H

47

47

47

. .

. . .

H

H

H

. . .

B8

. . .

H

When the frame sync finds this pattern HIT (Block 1

Register 55H) times, the frame sync block declares

ÒacquisitionÓ and starts feeding the bytes to the DeInterleaver. The frame sync stays in the ÒacquisitionÓ

state until it misses this pattern MISS (Block 1 Register

56H) times.

De-I nterleaver

This block is a convolutional De-Interleaver, as shown:

Input

12

1

J J J J J

J

2

J J J J J

I-4

J J J J

I-3

J J J J

I-2

J J J J

I-1

J J J J

I

4 I-2 I-1

3

Output

WCP 53704.c-10/28/97

followed by 16 bytes of checksum. The code blocks are

assumed to be coded according to ITU-T (J.83) Annex A

FEC shortened R-S algorithm.

If the decoder fails to decode a code block, the decoder

sets the undecodable flag ÒtrueÓ for this block. This flag

propagates to the STEL-2176 output as RXDECDFLG.

In addition, the number of errors in each decodable

block accumulates in Error_cnt[15:0] (Block 1 Registers

72H and 73H). This register can be reset by writing a 1 to

CLR_ERR (bit 0 of Block 1 Register 74H).

De- R andomizer

The de-randomizer is exactly the same as the

randomizer described by the ITU-T (J.83) Annex A

standard.

Output Clock Block

The function of the output clock block is to evenly

distribute the output receive data of the STEL-2176 and

to eliminate gaps caused by the FEC subsystem. The

output of the Reed-Solomon decoder is 188 bytes of

data for every 204 input bytes. Therefore, there is a gap

of 16 bytes where the checksum information is

removed.

The STEL-2176 output can send the received data in

bytes on an 8-bit wide buss, or in bits on a single line as

shown in Downstream Output Timing Diagrams

(Figure 19 through Figure 21). Selecting between

ÒbytewiseÓ versus ÒbitwiseÓ can be done by setting

Serial Mode (bit 0 of Bank 1 Register 69H) to 1.

ANNEX B

The ITU-T (J.83) Annex B FEC subsystem consists of the

following blocks:

Figure 12. De-Interleaver

I and J are programmable (Block 1 Registers 47H and

I,Q from

Adaptive

Equalizer

Trellis

Coded

De-modulator

Frame

Sync

De-Randomizer

48H).

A total memory of J _ (I-1) _ I/2 is required. The STEL-

2176 has 8K internal memory. Up to 64K memory can

be added externally without any additional logic, as

shown.

De-Interleaver

Reed-Solomon

Decoder

MPEG-2

Framing

To Output Clock

WCP 53705.c-10/28/97

Figure 13. ITU-T (J.83) Annex B FEC Subsystem

Reed-Solomon Decoder

This function decodes Reed-Solomon blocks. Each code

block is 204 bytes long and contains 188 bytes of data

STEL-2176 16 User Manual

Page 26

I, Q

Demapping

C

C

C

C

C

C

C

q

q/2+1

q/2-1

2

1

q/2

0

1/2 Binary

Convolutional

Decoder

X

Differential

Y

Decoder

(4/5) punctured

Figure 14. Trellis Coded Demodulator

W

Receiver Description

Buffer

28 bits (64QAM)

Frame

Sync

38 bits (256 QAM)

Z

WCP 53706.c-10/28/97

The demapping block maps the Adaptive Channel

Equalizer I and Q outputs for each symbol into 4, 6, or 8

Q

110,111 111,011 010,111 011,011100,101 101,111 110,101 111,111

110,100 111,000 010,100 011,000 100,000101,010 110,000 111,010

100,111 101,011 000,100 001,011 000,101 001,111 010,101 011,111

100,100 101,000 000,100 001,000 000,000 001,010 010,000 011,010

010,011 011,001 000,011 001,001 000,001 001,101 100,001 101,101

010,110 011,100 000,110 001,100 000,010 001,110 100,010 101,110

110,011 111,001 100,011 101,001 010,001 011,101 110,001 111,101

bits for 16, 64, or 256 QAM respectively. The mapping

tables are as follows:

3

C5C4C

I

,

C2C1C

0

110,110 111,100 100,110 101,100 010,010 011,110 110,010 111,110

WCP 53709.c-10/29/97

Figure 15. 64 QAM Mapping

User Manual 17 STEL-2176

Page 27

Receiver Description

1110,

1111

1100,

1110

1010,

1111

1000,

1110

0110,

1111

0100,

1110

0010,

1111

0000,

1110

1110,

0001

1110,

0010

1110,

0101

1110,

0110

1110,

1001

1110,

1010

1110,

1101

1110,

1110

1111,

1101

1101,

1100

1011,

1101

1001,

1100

0111,

1101

0101,

1100

0011,

1101

0001,

1100

1101,

0001

1101,

0010

1101,

0101

1101,

0110

1101,

1001

1101,

1010

1101,

1101

1101,

1110

1110,

1011

1100,

1010

1010,

1011

1000,

1010

0110,

1011

0100,

1010

0010,

1011

0000,

1010

1010,

0001

1010,

0010

1010,

0101

1010,

0110

1010,

1001

1010,

1010

1010,

1101

1010,

1110

1111,

1001

1101,

1000

1011,

1001

1001,

1000

0111,

1001

0101,

1000

0011,

1001

0001,

1000

1001,

0001

1001,

0010

1001,

0101

1001,

0110

1001,

1001

1001,

1010

1001,

1101

1001,

1110

1110,

0111

1100,

0110

1010,

0111

1000,

0110

0110,

0111

0100,

0110

0010,

0111

0000,

0110

0110,

0001

0110,

0010

0110,

0101

0110,

0110

0110,

1001

0110,

1010

0110,

1101

0110,

1110

1111,

0101

1101,

0100

1011,

0101

1001,

0100

0111,

0101

0101,

0100

0011,

0101

0001,

0100

0101,

0001

0101,

0010

0101,

0101

0101,

0110

0101,

1001

0101,

1010

0101,

1101

0101,

1110

1110,

0011

1100,

0010

1010,

0011

1000,

0010

0110,

0011

0100,

0010

0010,

0011

0000,

0010

0010,

0001

0010,

0010

0010,

0101

0010,

0110

0010,

1001

0010,

1010

0010,

1101

0010,

1110

1111,

0001

1101,

0000

1011,

0001

1001,

0000

0111,

0001

0101,

0000

0011,

0001

0001,

0000

0001,

0001

0001,

0010

0001,

0101

0001,

0110

0001,

1001

0001,

1010

0001,

1101

0001,

1110

Q

0000,

1111

0000,

1100

0000,

1011

0000,

1000

0000,

0111

0000,

0100

0000,

0011

0000,

0000

0000,

0001

0010,

0000

0100,

0001

0110,

0000

1000,

0001

1010,

0000

1100,

0001

1110,

0000

0011,

1111

0011,

1100

0011,

1011

0011,

1000

0011,

0111

0011,

0100

0011,

0011

0011,

0000

0001,

0011

0011,

0010

0101,

0011

0111,

0010

1001,

0011

1011,

0010

1101,

0011

1111,

0010

0100,

1111

0100,

1100

0100,

1011

0100,

1000

0100,

0111

0100,

0100

0100,

0011

0100,

0000

0000,

0101

0010,

0100

0100,

0101

0110,

0100

1000,

0101

1010,

0100

1100,

0101

1110,

0100

0111,

1111

0111,

1100

0111,

1011

0111,

1000

0111,

0111

0111,

0100

0111,

0011

0111,

0000

0001,

0111

0011,

0110

0101,

0111

0111,

0110

1001,

0111

1011,

0110

1101,

0111

1111,

0110

1000,

1111

1000,

1100

1000,

1011

1000,

1000

1000,

0111

1000,

0100

1000,

0011

1000,

0000

0000,

1001

0010,

1000

0100,

1001

0110,

1000

1000,

1001

1010,

1000

1100,

1001

1110,

1000

1011,

1111

1011,

1100

1011,

1011

1011,

1000

1011,

0111

1011,

0100

1011,

0011

1011,

0000

0001,

1011

0011,

1010

0101,

1011

0111,

1010

1001,

1011

1011,

1010

1101,

1011

1111,

1010

1100,

1111

1100,

1100

1100,

1011

1100,

1000

1100,

0111

1100,

0100

1100,

0011

1100,

0000

0000,

1101

0010,

1100

0100,

1101

0110,

1100

1000,

1101

1010,

1100

1100,

1101

1110,

1100

1111,

1111

1111,

1100

1111,

1011

1111,

1000

1111,

0111

1111,

0100

1111,

0011

1111,

0000

0001,

1111

0011,

1110

0101,

1111

0111,

1110

1001,

1111

1011,

1110

1101,

1111

1111,

1110

C7C6C5C

C3C2C1C

I

4

0

Figure 16. 256 QAM Mapping

The de-mapper generates ÒqÓ bits for each symbol

where q = 6 for 64 QAM and q = 8 for 256 QAM. Two

bits (bo and b

) are processed by the binary

q/2

convolutional decoder and the differential decoder. The

remaining bits are passed directly to the output buffer.

Viterbi Decoder

The binary convolutional decoder is a 1:2 Viterbi

decoder (4/5 punctured). For every 5 consecutive input

bo or bq/2 bits, the Viterbi decoder produces only 4

output bits. With this type of punctured code there are

5 possibilities for synchronization. The synchronization

can occur automatically, or under manual control using

the programmable registers. Setting VitFeedBackEn (bit

4 of Bank 0 Register F4H) to 1 selects the automatic

mode, while setting it to 0 selects the manual mode. In

the manual mode, the decoder starts at any point in the

puncturing sequence. To skip to the next state, write 1

to VitFeedBack (bit 7 of Bank 0, Register FCH).

WCP 53710.c-10/29/97

decoder uses the following formula to produce its

output:

Wk = (X

• (X

k-1

Zk = (X

Buffer

⊕ Y

⊕ Y

k

⊕ X

k

k-1

k-1

) • (1 ⊕ X

k-1

)

) ⊕ (Yk ⊕ Y

k-1

k-1

⊕ Y

)

) ⊕ (Yk ⊕ Y

k-1

k-1

The trellis coded demodulator buffer converts groups

of 5 symbols into a bitstream (28 bits for 64 QAM, or 38

bits for 256 QAM) following Annex B convention.

Frame Sync

This block receives data from the buffer. The frame sync