Page 1

查询STEL-1109供应商

STEL-1109

Data Sheet

STEL-1109/CR

5 - 65 MHz

Burst Transmitter

R

Page 2

TABLE OF CONTENTS

TRADEMARKS................................................................................................................................................................ 4

KEY FEATURES................................................................................................................................................................ 5

INTRODUCTION............................................................................................................................................................ 6

PIN CONFIGURATION ................................................................................................................................................. 7

POWER SUPPLY PINS.................................................................................................................................................... 7

FUNCTIONAL BLOCK DIAGRAM DESCRIPTIONS............................................................................................ 8

Overview ........................................................................................................................................................................ 8

Data Path Description ................................................................................................................................................... 9

Bit Sync Block............................................................................................................................................................. 9

Bit Encoder Block....................................................................................................................................................... 10

Data Path Control (Multiplexers)........................................................................................................................ 10

Scrambler ................................................................................................................................................................ 11

Reed-Solomon Encoder......................................................................................................................................... 12

Symbol Mapper Block............................................................................................................................................... 13

Bit Mapper.............................................................................................................................................................. 13

Differential Encoder.............................................................................................................................................. 14

Symbol Mapper...................................................................................................................................................... 15

Nyquist Fir Filter ....................................................................................................................................................... 18

Interpolating Filter .................................................................................................................................................... 19

Modulator ................................................................................................................................................................... 20

10-Bit DAC.................................................................................................................................................................. 20

Control Unit Description.............................................................................................................................................. 20

Bus Interface Unit...................................................................................................................................................... 20

Clock Generator ......................................................................................................................................................... 20

NCO............................................................................................................................................................................. 21

TIMING DIAGRAMS..................................................................................................................................................... 23

Clock Timing.................................................................................................................................................................. 23

Pulse Width .................................................................................................................................................................... 23

Bit Clock Synchronization............................................................................................................................................ 24

Input Data and Clock Timing...................................................................................................................................... 25

Write Timing .................................................................................................................................................................. 26

Read Timing ................................................................................................................................................................... 27

NCO Loading (User Controlled)................................................................................................................................. 28

NCO Loading (Automatic) .......................................................................................................................................... 28

Digital Output Timing.................................................................................................................................................. 29

DATAEN to DATAENO Timing ................................................................................................................................ 30

BURST TIMING EXAMPLES........................................................................................................................................ 30

Burst Timing: Full Burst (Slave Mode, QPSK) .......................................................................................................... 31

Master Mode, BPSK Burst Timing Signal Relationships ......................................................................................... 32

Slave Mode, BPSK Burst Timing Signal Relationships............................................................................................ 32

Master Mode, QPSK Burst Timing Signal Relationships ........................................................................................ 33

Slave Mode, QPSK Burst Timing Signal Relationships ........................................................................................... 33

Master Mode, 16QAM Burst Timing Signal Relationships.................................................................................... 34

Slave Mode, 16QAM Burst Timing Signal Relationships........................................................................................ 34

ELECTRICAL SPECIFICATIONS ................................................................................................................................ 35

RECOMMENDED INTERFACE CIRCUITS.............................................................................................................. 38

Slave Mode Interface..................................................................................................................................................... 38

Master Mode Interface.................................................................................................................................................. 38

EXAMPLE OUTPUT LOAD SCHEMATIC ................................................................................................................ 39

MECHANICAL SPECIFICATIONS ............................................................................................................................. 39

STEL-1109 2 PRELIMINARY PRODUCT INFORMATION

Page 3

LIST OF ILLUSTRATIONS

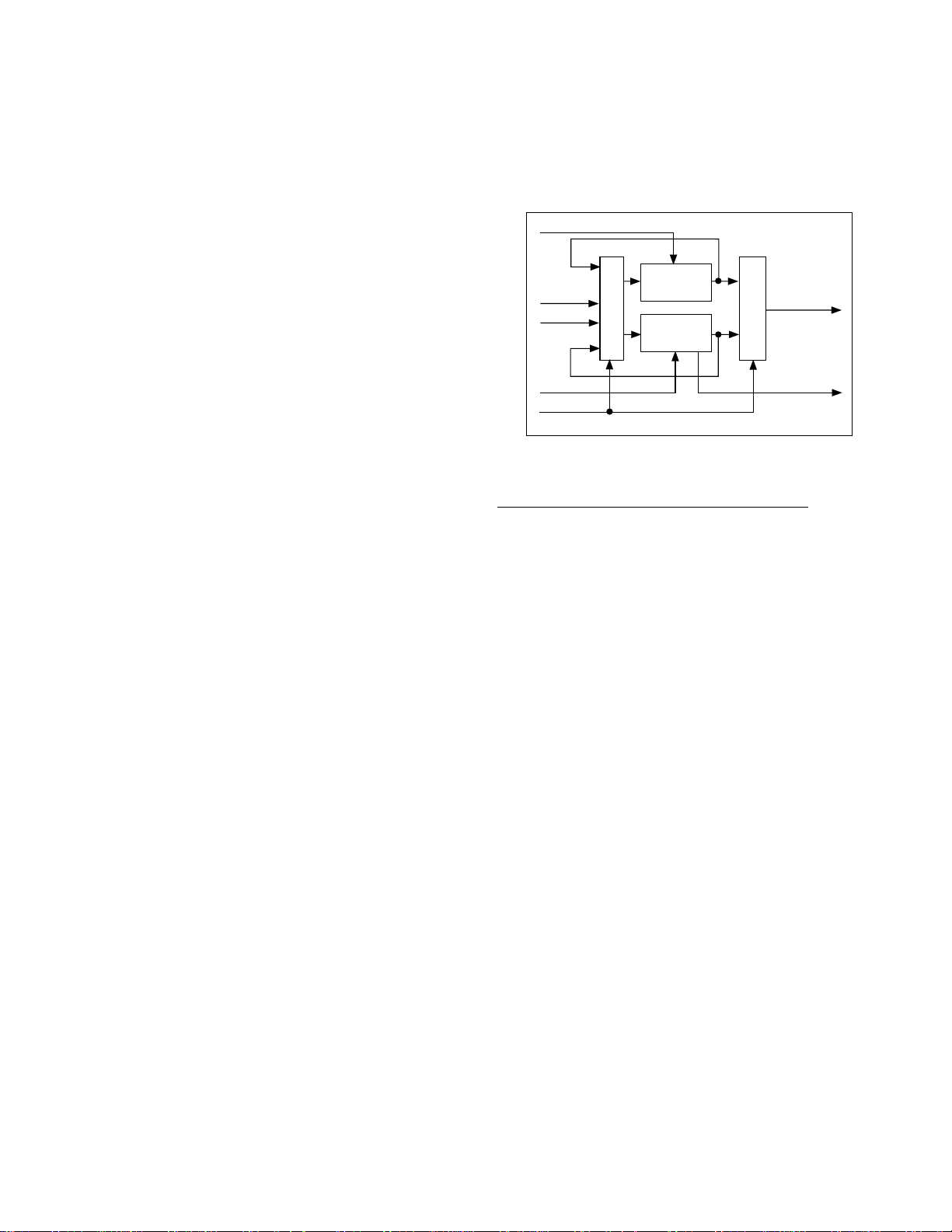

Figure 1. STEL-1109 Block Diagram.................................................................................................................... 9

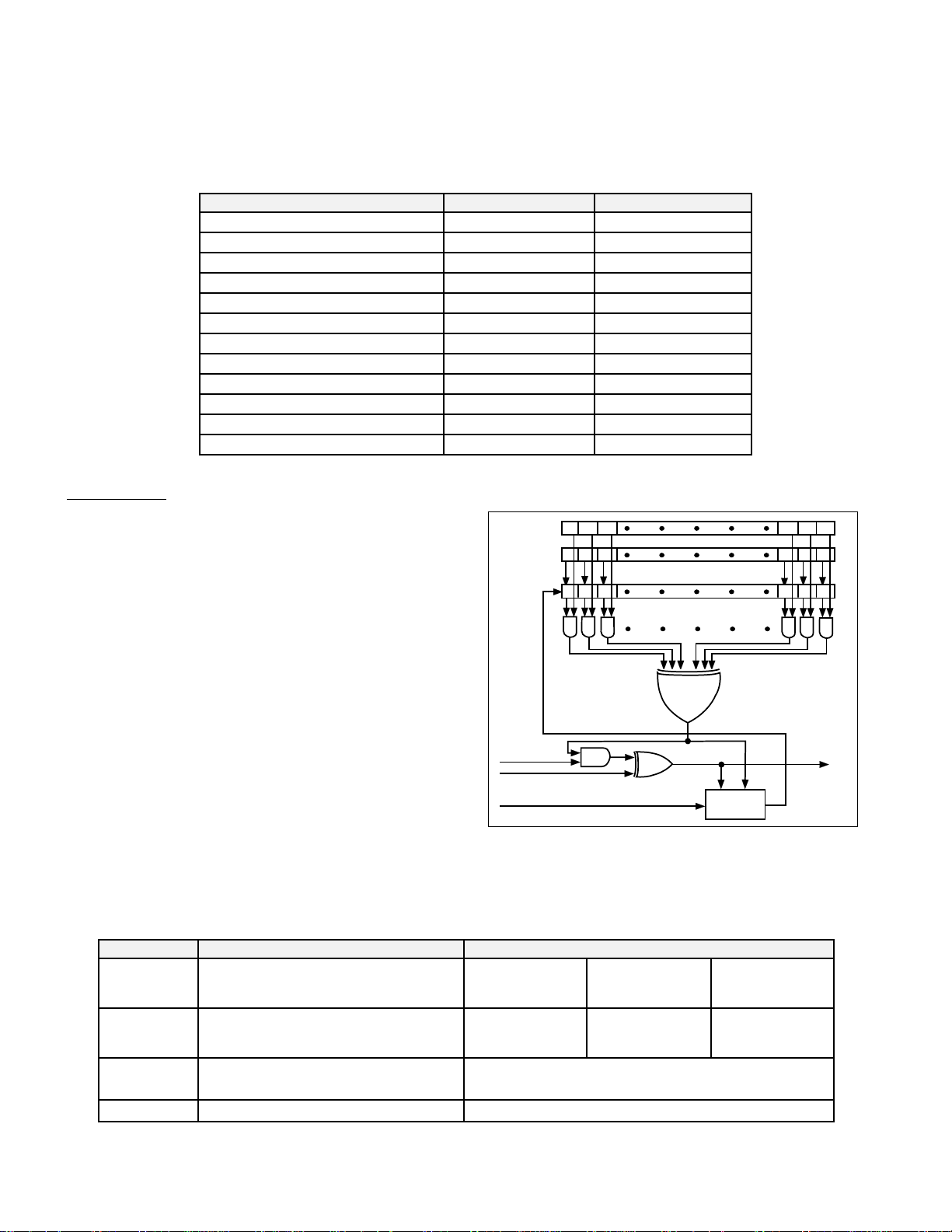

Figure 2. Bit Encoder Functional Diagram ........................................................................................................ 10

Figure 3. Scrambler Block Diagram .................................................................................................................... 11

Figure 4. DAVIC Scrambler.................................................................................................................................. 12

Figure 5. Mapping Block Functional Diagram.................................................................................................. 13

Figure 6. BPSK Constellation ............................................................................................................................... 15

Figure 7. QPSK Constellation .............................................................................................................................. 16

Figure 8. Natural Mapping Constellation.......................................................................................................... 16

Figure 9. Gray Coded Constellation ................................................................................................................... 17

Figure 10. Left Coded Constellation ..................................................................................................................... 17

Figure 11. DAVIC Coded Constellation ............................................................................................................... 18

Figure 12. Right Coded Constellation .................................................................................................................. 18

Figure 13. Nyquist FIR Filter.................................................................................................................................. 19

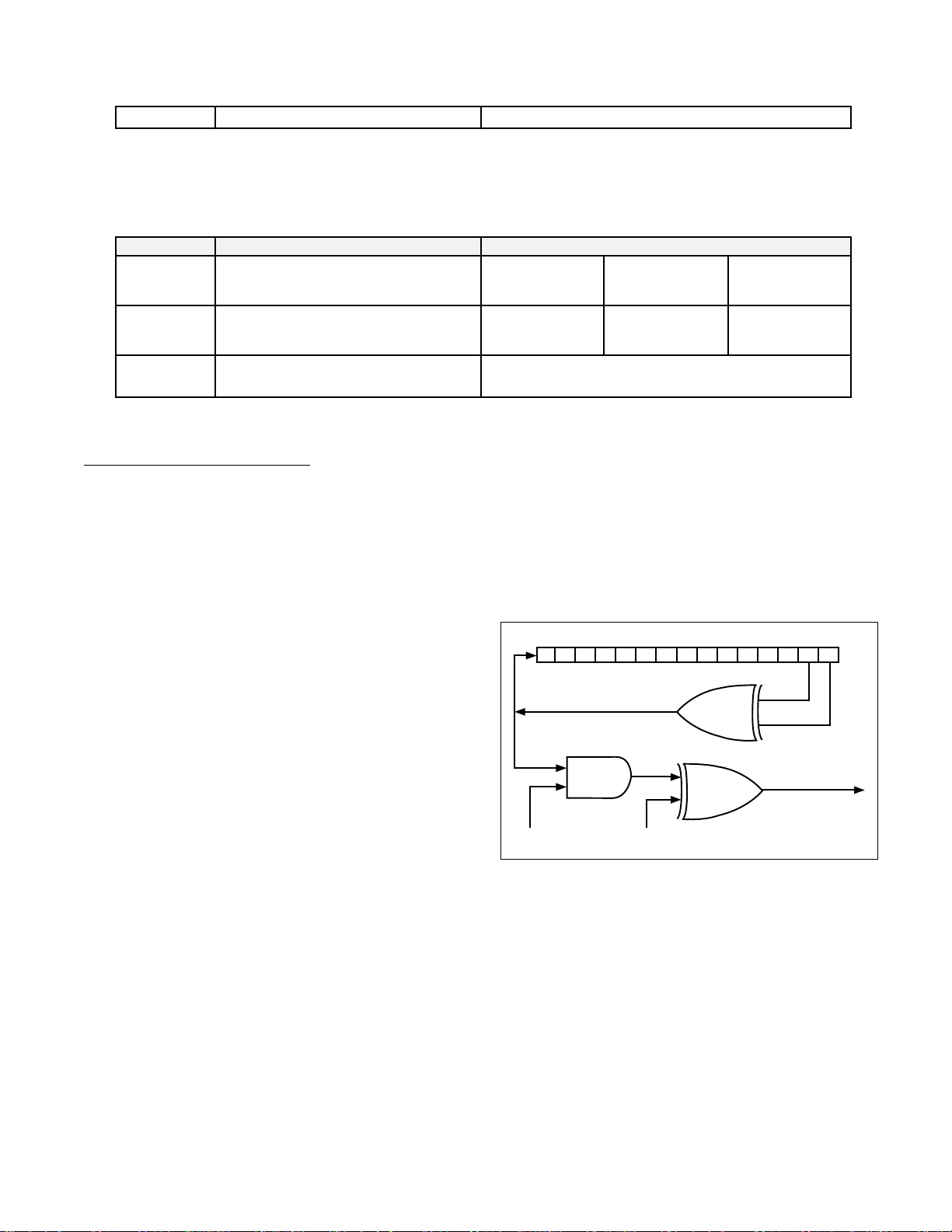

Figure 14. Interpolation Filter Block Diagram..................................................................................................... 19

Figure 15. Duty Cycle Derating Versus Temperature (@3.3v).......................................................................... 36

Figure 16. STEL-1109 Mechanical Characteristics .............................................................................................. 39

PRELIMINARY PRODUCT INFORMATION 3 STEL-1109

Page 4

LIST OF TABLES

Table 1. STEL-1109 Features .............................................................................................................................. 5

Table 2. I/O Signal Pin Assignments................................................................................................................ 7

Table 3. STEL -1109 Configuration Register Data Fields............................................................................... 8

Table 4. Data Latching Options ......................................................................................................................... 9

Table 5. Bit Encoding Data Path Options......................................................................................................... 11

Table 6. Scrambler Parameters .......................................................................................................................... 11

Table 7. Sample Scramble Register Values ...................................................................................................... 12

Table 8. Reed-Solomon Encoder Parameters................................................................................................... 13

Table 9. Bit Mapping Options............................................................................................................................ 14

Table 10. Differential Encoder Control............................................................................................................... 14

Table 11. Qpsk Differential Encoding and Phase Shift.................................................................................... 15

Table 12. Symbol Mapping Selections................................................................................................................ 16

Table 13. Symbol Mapping .................................................................................................................................. 17

Table 14. FIR Filter Configuration Options ....................................................................................................... 18

Table 15. FIR Filter Coefficient Storage.............................................................................................................. 18

Table 16. Interpolation Filter Bypass Control.................................................................................................... 19

Table 17. Interpolation Filter Signal Level Control .......................................................................................... 19

Table 18. Signal Inversion Control...................................................................................................................... 20

Table 19. FCW Selection ....................................................................................................................................... 22

Table 20. Clock Timing AC Characteristics....................................................................................................... 23

Table 21. Pulse Width AC Characteristics ......................................................................................................... 23

Table 22. Bit Clock Synchronization AC Characteristics................................................................................. 24

Table 23. Input Data and Clock AC Characteristics......................................................................................... 25

Table 24. Write Timing AC Characteristics ....................................................................................................... 26

Table 25. Read Timing AC Characteristics........................................................................................................ 27

Table 26. NCO Loading AC Characteristics...................................................................................................... 28

Table 27. Digital Output Timing AC Characteristics ....................................................................................... 29

Table 28. DATAEN to DATAENO Timing AC Characteristics...................................................................... 30

Table 29. Absolute Maximum Ratings ............................................................................................................... 35

Table 30. Recommended Operating Conditions............................................................................................... 36

Table 31. DC Characteristics................................................................................................................................ 37

TRADEMARKS

Stanford Telecom and STEL are registered trademarks of Stanford Telecommunications, Incorporated.

STEL-1109 4 PRELIMINARY PRODUCT INFORMATION

Page 5

KEY FEATURES

Complete BPSK/QPSK/16QAM modulator in

n

a CMOS ASIC

n Programmable over a wide range of data

rates

n NCO modulator provides fine frequency

resolution

n 165 MHz maximum clock rate generates a

modulated carrier at frequencies

programmable from 5 to 65 MHz

n Operates in continuous and burst modes

n Differential Encoder, Programmable

Scrambler, and Programmable

Reed-Solomon FEC Encoder

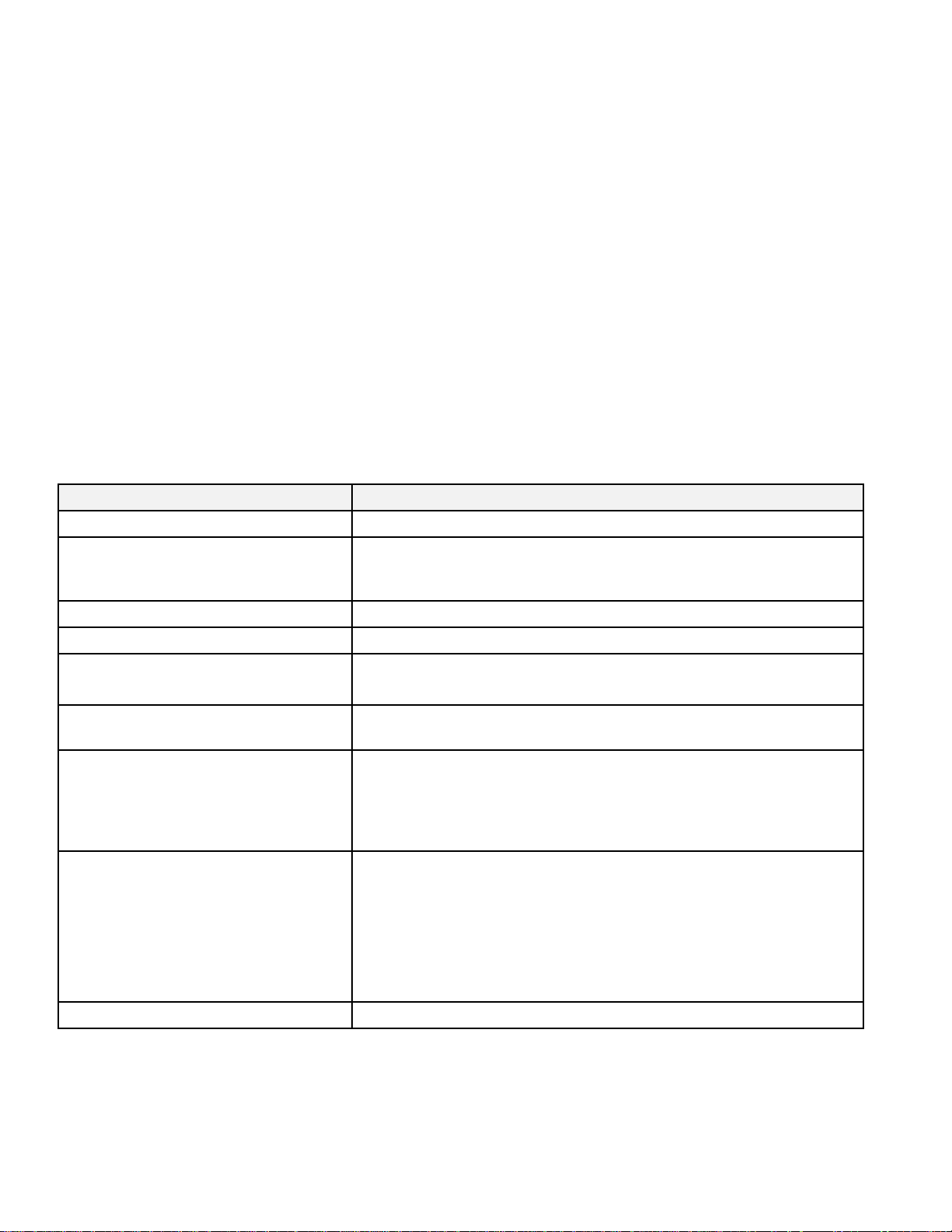

Table 1. STEL-1109 Features

Feature Characteristic

Carrier frequency: 5 to 65 MHz (maximum of approximately 40% of master clock)

Symbol rate: From Master clock divided by 16 down to Master clock divided by

16384 (in steps of 4) yielding a maximum symbol rate of 10Msps with a

160 MHz clock.

FIR filter tap coefficients: 32 programmable taps (10 bits each), symmetric response

Modulation: BPSK, QPSK, or 16QAM

16QAM constellation: Eight selectable bit-to-symbol mappings

Five selectable symbol-to-constellation mappings

I and Q modulator signs / Spectral

Inversion

Reed-Solomon encoder: Selectable on/off

Scrambler: Selectable on/off

Differential encoder: Selectable on/off

Signs of I and Q plus the mapping to Sine and Cosine carriers is

programmable.

Two selectable generator polynomials

Block length shortened any amount

Error correction capability T = 1 to 10

Self-synchronizing or frame synchronized (sidestream)

Location before or after RS Encoder

Programmable generator polynomial

Programmable length up to 224 - 1

Programmable initial seed

n Programmable 32-tap FIR Filter for signal

shaping before modulation

n 10-bit DAC implemented on chip

n Complete upstream modulator solution –

serial data in and RF signal out

n Compatible with DAVIC, IEEE 802.14

(preliminary), Intelsat IESS-308, ITU J.83

Annex A, MCNS Standards

n Supports low data rates for voice

applications and high data rates for

wideband applications

n Small Footprint, Surface Mount 80-Pin

MQFP Package

PRELIMINARY PRODUCT INFORMATION 5 STEL-1109

Page 6

INTRODUCTION

The STEL-11091 is a highly integrated, maximally

flexible, burst transmitter targeted to the cable modem

market. It receives serial data, randomizes the data,

performs FEC and differential encoding, maps the data

to a constellation before modulation, and outputs an

analog RF signal.

The STEL-1109 is the latest in a series of modulator

chips that comprise the STEL-1103 through STEL-1108

modulators. Several key components (e.g., a 10-bit

DAC, FECs, etc.) have been incorporated in the

STEL-1109 and the enhancements have resulted in

significant changes to the chipÕs electrical and software

interfaces.

The STEL-1109 is capable of operating at data rates of

up to 10 Mbps in BPSK mode, 20 Mbps in QPSK mode,

and 40 Mbps in 16QAM mode. It operates at clock

frequencies of up to 165 MHz, which allows its internal,

10-bit Digital-to-Analog Converter (DAC) to generate

RF carrier frequencies of 5 to 65 MHz.

The STEL-1109 also uses digital FIR filtering to

optimally shape the spectrum of the modulating data

prior to modulation. This optimizes the spectrum of

the modulated signal, and minimizes the analog

filtering required after the modulator. The filters are

designed to have a symmetrical (mirror image)

polynomial transfer function, thereby making the phase

response of the filter linear. This also eliminates the

inter-symbol interference that results from group delay

distortion. In this way, it is possible to change the

carrier frequency over a wide frequency range without

having to change filters, thus providing the ability to

operate a single system in many channels.

The STEL-1109 can operate with very short gaps

between transmitted bursts to increase the efficiency of

TDMA systems. The STEL-1109 (as well as the STEL1103 and STEL-1108) operates properly even when the

interburst gap is less than four (4) symbols (half the

length of the FIR filter response). In this case the

postcursor of the previous burst overlaps and is

superimposed on the precursor of the following burst.

Signal level scaling is provided after the FIR filter to

allow the STEL-1109Õs maximum arithmetic dynamic

range to be utilized. Signal levels can be changed over

a wide range depending on how the device is

programmed.

In addition, the STEL-1109 is designed to operate from

a 3.3 Vdc power supply and the chip can be interfaced

with logic that operates at 5 Vdc.

1

The STEL-1109 utilizes advanced signal processing

techniques which are covered by U.S. Patent Number

5,412,352.

STEL-1109 6 PRELIMINARY PRODUCT INFORMATION

Page 7

PIN CONFIGURATION

The STEL-1109 input and output signal pin

assignments are listed in Table 2. The location of the

pin numbers is shown by Figure 16 (page 39). The

Table 2. I/O Signal Pin Assignments

1V

DD

2 DATA

3 DATA

4 DATA

5 DATA

6V

7V

8 ADDR

9 ADDR

10 ADDR

11 V

12 ADDR

13 ADDR

14 ADDR

15 V

16 V

4

5

6

7

SS

SS

5

4

3

DD

2

1

0

SS

SS

17 TSDATA [9] (I) 37 ACLK [20] (O) 57 V

18 DATAEN [10] (I) 38 V

19 TCLK [9] (I) 39 DATAENO [20] (O) 59 V

20 FCWSEL

Notes:

1. Pin 31 is applied to input buffers only.

2. See Package Outline (Figure 16) for pin

identification.

[7] (S) 21 FCWSEL1[21] (I) 41 V

[20] (B) 22 V

[20] (B) 23 V

[20] (B) 24 V

[20] (B) 25 V

SS

SS

SS

DD

[7] (T) 42 SYMPLS [20] (O) 62 V

[7] (T) 43 V

[7] (T) 44 V

[7] (S) 45 V

[7] (S) 26 CLKEN [9,20] (I) 46 V

[7] (S) 27 V

SS

[7] (S) 47 V

[20] (I) 28 CLK [20] (I) 48 V

[20] (I) 29 RDSLEN [10] (I) 49 V

[20] (I) 30 V

[7] (S) 31 5V

DD

DD

[7] (S) 50 [7] (N.C.) 70 DIFFEN [13] (I)

[7] (I) 51 AV

[20] (I) 32 SCRMEN [10] (I) 52 OUT [20] (AO) 72

[20] (I) 33 V

[20] (I) 34 V

SS

SS

[7] (S) 53 OUTN [20] (AO) 73 DSB [20] (I)

[7] (T) 54 AV

[7] (S) 35 CKSUM [12] (O) 55 [7] (N.C.) 75 V

[7] (S) 36 V

[21] (I) 40 BITCLK [9,20] (O) 60 V

0

SS

DD

[7] (S) 56 V

[7] (S) 58 V

Legend:

(AO) Analog Output (O) Output signal

(B) Bi-directional (I/O) signal (S) Source

(I) Input signal (T) Factory Test Pin

(N.C.) Not Connected [#] Page Reference

STEL-1109 power supply pins are described in the

following paragraph.

DD

SS

SS

SS

SS

SS

SS

SS

SS

SS

SS

SS

SS

DD

SS

[7] (S) 61 V

[7] (S) 63 V

[7] (T) 64 V

[7] (T) 65 V

[7] (T) 66 V

SS

DD

DD

SS

DD

SS

[7] (T) 67 RSTB [20] (I)

[7] (T) 68 V

[7] (S) 69 V

SS

SS

[7] (S) 71 NCO LD [21] (I)

CSEL

[7] (S) 74 WR [20] (I)

DD

[7] (S) 76 DATA

[7] (T) 77 DATA

[7] (T) 78 DATA

[7] (T) 79 DATA

[7] (T) 80 V

0

1

2

3

SS

[7] (T)

[7] (S)

[7] (T)

[7] (S)

[7] (T)

[7] (S)

[7] (T)

[7] (S)

[20] (I)

[7] (S)

[20] (B)

[20] (B)

[20] (B)

[20] (B)

[7] (S)

POWER SUPPLY PINS

There are three separate power supply systems within

the STEL-1109. The primary supply for the digital logic

circuits is nominally 3.3 volts and is input on the V

pins. The digital inputs have a separate supply, 5VDD,

which can be connected to a 5 volt supply if the STEL1109 inputs are driven from 5 volt logic. If the logic

driving the STEL-1109 is run on 3.3 volts, then the 5V

PRELIMINARY PRODUCT INFORMATION 7 STEL-1109

pin should be connected to 3.3 volts. The return for

both digital supplies is VSS. The DAC has a separate

analog power supply and return, AV

DD

3.3 volt AV

input allows the user to provide a

DD

and AVSS. The

DD

separate well filtered supply for the DAC to prevent

spurs that might be created from digital noise on the

V

DD

supply system.

DD

Page 8

FUNCTIONAL BLOCK DIAGRAM DESCRIPTIONS

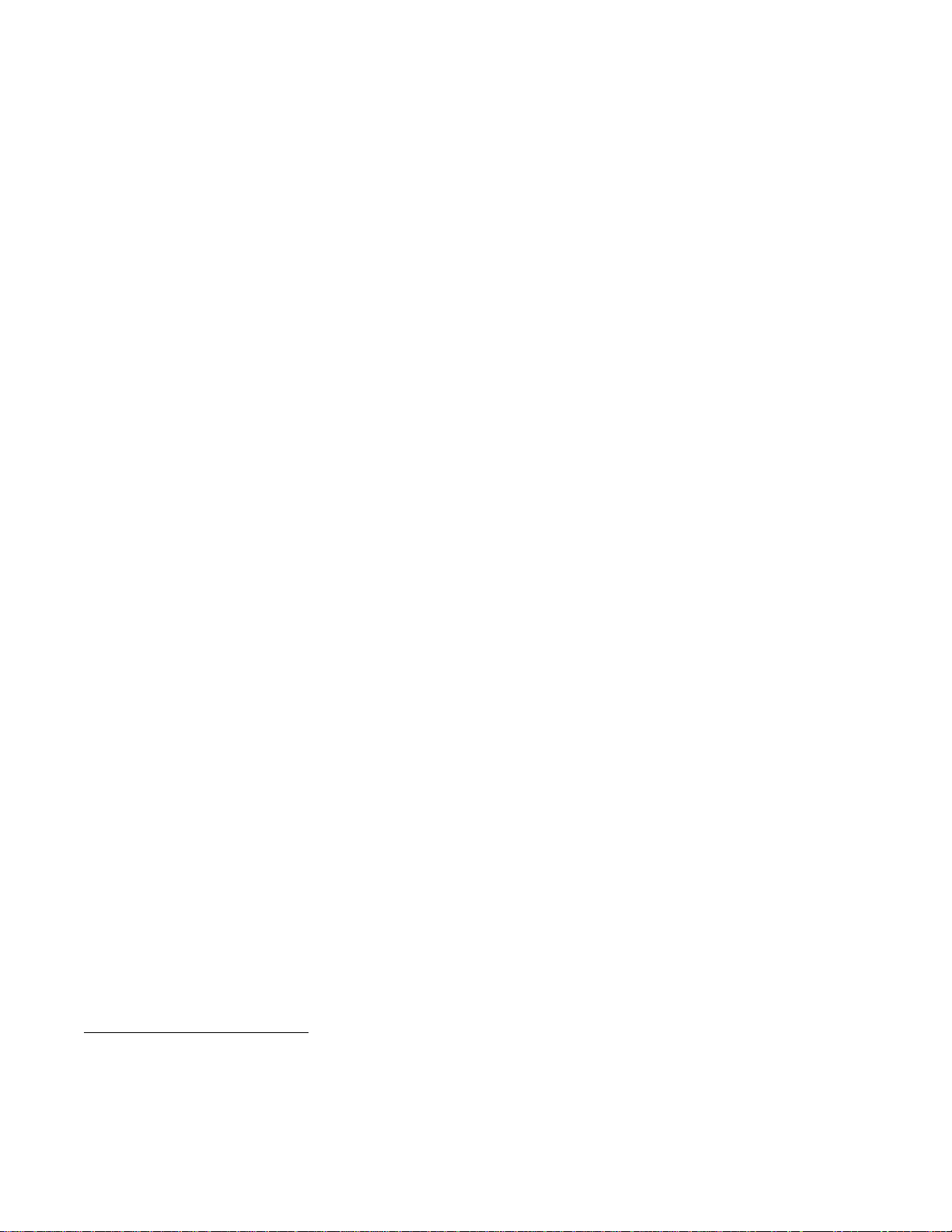

OVERVIEW

The STEL-1109 is comprised of the Data Path and

Control Unit sections shown in Figure 1. The Data Path

is comprised of a Bit Sync Block, Bit Encoder Block

(i.e.,Êthe Scrambler, Reed-Solomon Encoder, and two

Multiplexers shown in Figure 2), Symbol Mapper Block

(i.e., the Bit Mapper, Differential Encoder, and Symbol

Mapper are shown in FigureÊ5), two channels (one for I

and one for Q), a Combiner, and a 10-bit DAC. Each

channel consists of a Nyquist Filter, Interpolation Filter,

and Modulator. The Control Unit is comprised of a Bus

Interface Unit (BIU), Clock Generator, and NCO.

Table 3. STEL-1109 Configuration Register Data Fields

Address Contents

(Hex) Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

08 - 00

28 - 09

29

2A

2B

2C

2D

2E

Interpolation Filter Gain Control

Set To Zero Set To Zero

9

TCLK Sel.

FZSINB

Set To Zero Set To Zero Set To Zero

21

Symbol Mapping

LSB Sampling Rate Control (see address 39 for MSB)

Interpolation Filt. Bypass

Bit Mapping

15

13

FIR Filter Coefficients

19

Table 1 summarizes the main features of the circuits

described by the remaining paragraphs of this section.

The STEL-1109 provides 58, programmable, read/write

registers (Configuration Registers). Table 3 provides a

graphic representation of the STEL-1109Õs

Configuration Registers and their data fields. Each

register can be selected for a write or read operation

using addresses 00H through 39H.

21

NCO

18

20

20

Invert I/Q Chan.

18

19

Set To One Set To Zero

MOD

Set To One Set To Zero

CLRFIR

Auxiliary Clock Rate Divider

14

18

FIR bypass

PN Code Sel9PN On/Off

20

Set To Zero

Bit Sync Re-arm

9

9

2F

32-30

35-33

36

PPolynomial

37

38

DATAENBPB10DATAENSEL10RSENBPB10RSENSEL10SCRMENBPB10SCRMENSEL10DiffDCBPB14DiffDCSEL

39 Set To Zero Set To Zero

13

BypassB

10

S-RS

TRLSBF

Set To Zero

SCRAMBLER Init Registers

SCRAMBLER Mask Registers

10

12

Self-Sync

LDLSBF

11

12

11

11

12

T

12

K

MSB Sampling Rate Control (see address 29 for LSB)

14

20

Note: Superscripted numbers are page references where discussion on setting the particular register(s)

or bit(s) begins.

STEL-1109 8 PRELIMINARY PRODUCT INFORMATION

Page 9

DIFFEN

TCLK

TSDATA

DATAEN

RDSLEN

SCRMEN

AV

DD

5V

DD

V

DD

RST

CLKEN

CLK

NCO LD

FCWSEL

DATA

7-0

ADDR

5-0

DSB

WR

CSEL

1-0

BIT

Sync

Block

BIT

Encoder

Block

Clock

Generator

Bus

Interface

Unit

I

,

[1:0]

Q

[1:0]

4

SAMPLS

MASTER CLOCK

Symbol

Mapper

Block

Numerically

Controlled

Oscillator

I

[1:0]

2

Q

2

[1:0]

Nyquist

Filter

Nyquist

Filter

Interpolating

Filter

Interpolating

Filter

COS 2πFT

DATA PATH

Modulator

SIN 2πFT

10-Bit

DAC

OUT

OUTN

DATAENO

CKSUM

BITCLK

SYMPLS

ACLK

Figure 1. STEL-1109 Block Diagram

DATA PATH DESCRIPTION

BIT SYNC BLOCK

The Bit Sync Block has two functions, latching input

data, and synchronizing the STEL-1109 BITCLK and

symbol counters to the user data.

Latching Input Data

Latching of input data is accomplished in three ways:

• Externally supplied TSDATA is latched by the

internal BITCLK.

Table 4. Data Latching Options

Data Source Latched By Register 2C Bit 7 Register 2D Bits 1,0 Mode Name

TSDATA BITCLK 0 X,0 Master Mode

TSDATA TCLK 1 X,0 Slave Mode

PN Code 10, 3 BITCLK 0 0,1 Test Mode

PN Code 23, 18 BITCLK 0 1,1 Test Mode

CONTROL UNIT

WCP 52981.c-5/2/97

• Externally supplied TSDATA is latched by an

externally provided TCLK

• Internally generated PN code data is latched by the

internal BITCLK

See Table 4 for register settings to implement each

mode.

PRELIMINARY PRODUCT INFORMATION 9 STEL-1109

Page 10

BITCLK latches data on its falling edge. TCLK latches

data on its rising edge.

Whenever the CLKEN input is low, the BITCLK output

will stop. In order to provide customers with a

continuous clock, the STEL-1109 provides an auxiliary

clock (ACLK) output which is discussed later in the

clock generator section. The ACLK output is primarily

for use in master mode where users may need a clock to

run control circuits during the guard time between

bursts.

When using slave mode, the data that is latched by the

rising edge of TCLK is re-latched internally by the next

falling edge of BITCLK which re-synchronizes the data

to the internal master clock.

Synchronizing BITCLK / SYMPLS

The synchronization circuit aligns the STEL-1109

BITCLK and its SYMPLS counter circuits to the

beginning of the first user data symbol. The circuit has

two parts, an arming circuit and a trigger circuit. Once

armed, the first rising edge on the TCLK input will

activate (trigger) the synchronization process.

The circuit can be armed in two ways; taking CLKEN

from low to high, or toggling Configuration Register

2EH bit 0 from low to high to low again. In a normal

burst mode application, the circuit is automatically rearmed between bursts because CLKEN goes low. For

applications that will not allow CLKEN to cycle low

between bursts, some system level precautions should

be observed to maintain synchronization of user data to

the STEL-1109 BITCLK.

Once triggered, the sync circuit re-starts the BITCLK

and SYMPLS counters. The BITCLK output starts high,

and SYMPLS resets to the start of a symbol. There is a

delay equal to about three cycles of the master clock

from the rising edge of the TCLK input before this restart occurs. During this brief delay period, the BITCLK

and SYMPLS counters are still free running and may or

may not have transitions.

BIT ENCODER BLOCK

The Bit Encoder Block consists of a Scrambler, a

Reed-Solomon Encoder, and data path controls

(multiplexers), as shown in Figure 2.

SCRMEN

Input

Multiplexer

Scrambler

Reed-Solomon

Encoder

ENCODED

SERIAL DATA

Output

Multiplexer

CHKSUM

SIGNAL

WCP 52982.c-4/26/97

SERIAL

DATA

DATAEN

RDSLEN

S-RS

Figure 2. Bit Encoder Functional Diagram

Data Path Control (Multiplexers)

The STEL-1109 provides a great deal of flexibility and

control over the routing of data through or around the

encoding functions. With appropriate register

selections, data can be routed around (bypass) both

encoders, through either one and around the other,

through the scrambler then the RS Encoder, or through

the RS Encoder and then the scrambler. Control over

the bypassing can be set for software control or external

(user) input signal control. Generally, if an encoding

function will be left either on or off continuously, then

software control is appropriate. If the function must be

turned on and off dynamically (typically in order to

send the preamble Ôin the clearÕ i.e. unencoded), then

external (user) input control is required. If the ReedSolomon encoder will not be used at all, then a separate

bypass option can be activated to remove an 8 bit delay

register from the data path that is required if the

possibility of turning on the encoder exists. Each of the

external (user) input control pins (if enabled) turns on

the encoding function when high and bypasses the

function when low.

In master mode, the rising edge of TCLK normally

marks the transition of the first user data bit (which will

be latched in by the next falling edge of BITCLK). In

slave mode, the first user data bit must already be valid

at this first rising edge of TCLK.

The DATAEN input signal determines whether or not

data will advance (shift through) the encoding blocks.

The presence of a high on the DATAEN input when the

BITCLK output goes low allows the circuits to advance

data through them. The DATAEN signal is delayed

STEL-1109 10 PRELIMINARY PRODUCT INFORMATION

Page 11

internally to allow the rising edge of DATAEN to

coincide with the first rising edge of TCLK.

Table 5. BIT Encoding Data Path Options

Data Path Register 36 Bits 6,5 Register 38 Bits 7-2

Data stopped (continuously) X,X 01 XXÊXX

Data path on (continuously) X,X 11 XXÊXX

Data path enabled by pin 18 X,X X0 XXÊXX

Scrambler off (continuously) X,X XX XX 01

Scrambler on (continuously) X,X XX XX 11

Scrambler enabled by pin 32 X,X XX XX X0

RS Encode off (continuously) 1,X XX 01 XX

RS Encode on (continuously) 1,X XXÊ11 XX

RS Encode enabled by pin 29 1,X XXÊX0 XX

Scrambler then RS Encoder 1,1 XXÊXXÊXX

RS Encoder then Scrambler 1,0 XXÊXXÊXX

Bypass RS Encoder 0,X XXÊXXÊXX

Scrambler

The scrambler can be used to randomize the serial data

in order to avoid a strong spectral component that

might otherwise arise from the occurrence of repeating

patterns in the input data. The Scrambler (Figure 3)

uses a Pseudo-Random (PN) generator to generate a PN

code pattern. All 24 registers are presettable and any

combination of the registers can be connected (tapped)

to form any polynomial of up to 24 bits. The scrambler

may be either frame synchronized or self synchronized.

Table 6 shows the registers involved.

See Table 5 for a summary of register settings required

to achieve the various data path possibilities.

24-bit Mask Reg

24-bit INIT Reg

24-bit Shift Reg

123 222324

123 222324

123 222324

XOR

The value in the INIT registers is loaded into the

scrambler shift registers whenever the scrambler is

disabled. The scrambler will scramble data one bit at a

time at each falling edge of BITCLK that occurs while

both the scrambler and DATAEN are active (enabled).

SCRMEN

SERIAL INPUT

SSYNC

AND

XOR

SELF

SYNC

MUX

FRAME

SYNC

SERIAL OUTPUT

WCP 52983.c-4/26/97

Internal delays on the SCRMEN control signal input

allow for a rising edge to occur coincident with the

Figure 3. Scrambler Block Diagram

rising edge of BITCLK that precedes the latching of the

first data bit to be scrambled.

Table 6. Scrambler Parameters

Parameter Characteristic Configuration Register Setting

Generator

Polynomial

(Mask Reg)

Seed

(INIT Reg)

Scrambler

Type

p(x) = c24x24 + c23x23 + É + c1x + 1

where c

Any 24 bit binary value, s

is a binary value (0, 1)

i

24-1

Register 35

Bit 7 to Bit 0

to c

c

24

17

Register 32

Bit 7 to Bit 0

s

to s

24

17

Frame synchronized (sidestream) Register 36 Bit 4

Set to zero

Register 34

Bit 7 to Bit 0

c

to c

16

9

Register 31

Bit 7 to Bit 0

s

to s

16

9

Register 33

Bit 7 to Bit 0

c8 to c

1

Register 30

Bit 7 to Bit 0

s

to s

8

1

Scrambler Self-synchronized Register 36 Bit 4

PRELIMINARY PRODUCT INFORMATION 11 STEL-1109

Page 12

Type

The Mask, Init, and SSync fields can be programmed

for different scrambler configurations. For example, the

DAVIC Scrambler configuration shown in FigureÊ4 can

Table 7. Sample Scramble Register Values

Parameter Characteristic Configuration Register Setting

Generator

Polynomial

(Mask Reg)

Seed

(INIT Reg)

Scrambler

Type

p(x) = x15 + x14 + 1 Register 35

0000A9 Hex Register 32

Frame synchronized (sidestream) Register 36 Bit 4

Reed - Solomon Encoder

The STEL-1109 uses a standard Reed-Solomon (RS)

Encoder for error correction encoding of the serial data

stream.

When DATAEN is high and the RS Encoder is enabled,

the serial data stream both passes straight through the

RS Encoder and also into encoding circuitry. The

encoding circuitry computes a checksum that is 2T

bytes long for every k bytes of input data. After the

last bit of each block of k bytes of input data, the RS

Encoder inserts its checksum (2T bytes of data) into the

data path. There is no adverse effect to letting TCLK or

TSDATA continue to run during the checksum; the data

input will be ignored. CKSUM (pin 35) will be asserted

high to indicate that the checksum bytes are being

inserted into the data stream and will be lowered at the

end of the checksum data insertion. The width of the

CKSUM pulse is 2T bytes.

The STEL-1109 registers include two bits for

determining the bit order for data into and checksum out

of the RS Encoder circuitry. Set these to match the

Set to one

be implemented by programming the Mask, Init, and

SSync fields with the values indicated by Table 7.

Bit 7 to Bit 0

0000Ê0000

Bit 7 to Bit 0

0000Ê0000

Set to zero

Register 34

Bit 7 to Bit 0

0110Ê0000

Register 31

Bit 7 to Bit 0

0000Ê0000

Register 33

Bit 7 to Bit 0

0000Ê0000

Register 30

Bit 7 to Bit 0

1010 1001

Reed-Solomon decoding circuitry along with the other

parameters.

The error correction encoding uses GF (256) and can be

programmed for an error correction capability of 1 to

10, a block length of 3 to 255, and one of two primitive

polynomials using the data fields listed in Table 8.

100101010000000

123456789101112131415

EX-OR

Enable

AND

EX-OR

Clear Data Input

Randomized Data

WCP 52984.c-4/26/97

Figure 4. DAVIC Scrambler

STEL-1109 12 PRELIMINARY PRODUCT INFORMATION

Page 13

Table 8. Reed-Solomon Encoder Parameters

Field Name Configuration Register Description

PP 36H (bit 7) 1-bit field for selecting Primitive Polynomial:

8

0 ⇒ p(x) = x

1 ⇒ p(x) = x

T36

K37

(bits 3-0) 4-bit field for setting Error Correction Capability. Programmable over the range

H

(bits 7-0) 8-bit field for setting User Data Packet Length (K) in bytes.

H

of 1 to 10.

Programmable over the range of 1 to (255 - 2T). [ Net block length, N = K + 2T ]

LDLSBF 39H (bit 4) Determines whether the first bit of the serial input is to be the MSB (bit 4 = 0) or

LSB (bit 4 = 1) of the byte applied to the RS Encoder.

TRLSBF 39H (bit 5) Determines whether the MSB (bit 5 = 0) or LSB (bit 5 = 1) of the RS Encoder

checksum byte is to be the first bit of the serial output data.

Notes:

1. GF (256).

2. Code generator polynomial 1 is used when PP=0:

3. Code generator polynomial 2 is used when PP=1.

+ x4 + x3 + x2 + 1

8

+ x7 + x2 + x + 1

T

+

119 2

Gx x

() ( )=−

Gx x

() ( )=−

∏

i

=

120

T

−

21

∏

i

=

0

i

α

i

α

α

α 02

=

= 02H

H

SYMBOL MAPPER BLOCK

The Symbol Mapper Block (Figure 5) maps the serial

data bits output by the Bit Encoder Block to symbols,

differentially encodes the symbols, and (in 16QAM)

maps the symbols to one of five constellations. The

Symbol Mapper Block functions are modulation

dependent. The modulation mode also defines the

number of bits per symbol. The Symbol Mapper Block

outputs 2 bits for each symbol to each of the two

Nyquist (FIR) Filters.

ENCODED

SERIAL DATA

1

DIFFEN

1

Bit

Mapper

I

[1:0]

Q

[1:0]

4

**

**

Differential

Encoder

I

Q

[1:0]

[1:0]

*

*

I

[1:0]

2

Symbol

Mapper

4

Q

[1:0]

2

WCP 52985.c-4/26/97

Figure 5. Mapping Block Functional Diagram

Bit Mapper

The Bit Mapper receives serial data and maps the serial

data bits to output symbol bits (I

There are four output bits per symbol even in BPSK and

QPSK modes. In BPSK, all bits are set equal to each

other. In QPSK, each input symbol bit drives a pair of

output bits. The four symbol bits are routed to the

Differential Encoder in parallel.

For BPSK modulation, each bit (symbol = b0) of the

input serial data stream is mapped directly to I

**

I

, and Q

0

**

(i.e., I

0

**

**

= I

= Q

1

0

mapping has no affect on the respective value of the

symbolÕs four bits, as shown in Table 9.

For QPSK modulation, each pair of bits (a dibit) forms a

symbol (b0 b1). The QPSK dibit is mapped so that

*Ê

**

I

=ÊI

and Q

1

0

1

** =

**,

Q

as shown in Table 9.

0

For 16QAM, every four bits (a nibble) forms a symbol

(b0b1b2b3). The 16QAM nibble is mapped to I

**

and Q

, as shown in Table 9.

0

1

**

= Q

**

**

, I

1

0

**

, Q

, and Q

0

1

**

= b0). Thus, bit

1

**

0

**

**

, Q

1

1

**

**

, Q

**

, I

1

0

).

,

,

PRELIMINARY PRODUCT INFORMATION 13 STEL-1109

Page 14

Table 9. Bit Mapping Options

Bit-To-Symbol Mapping Bit Mapping Mod Mode

Mode

BPSK I

QPSK I

QPSK Q

16QAM I

16QAM Q

16QAM I

16QAM Q

16QAM I

16QAM Q

16QAM I

16QAM Q

b

0

**

**

**

Q

1

1

**

**

I

1

0

**

Q

1

**

1

**

1

**

0

**

0

**

1

**

1

**

0

**

0

**

I

Q

0

0

**

0

b

1

N/A N/A N/A XXX 1X

**

**

Q

Q

1

0

**

**

I

I

1

0

**

I

0

**

Q

0

**

I

1

**

Q

1

**

Q

1

**

I

1

**

Q

0

**

I

0

N/A N/A XX0 00

N/A N/A XX1 00

**

Q

1

**

I

1

**

Q

0

**

I

0

**

I

0

**

Q

0

**

I

1

**

Q

1

Note: b0 is the first serial data bit to arrive at the Bit Mapper

Differential Encoder

**

The Differential Encoder encodes the bits (i.e., I

**

Q

1

, and Q

**

) of each symbol received from the Bit

0

Mapper to determine the output bit values (i.e., I

*

I

, and Q

0

*

), which are routed to the Symbol Mapper.

0

The differential encoder can be either enabled or

bypassed under the control of either a register bit or a

user supplied control signal (DIFFEN pin 70). The

selection between user input pin control or register

control is made in another register bit, as shown in

Table 10.

Table 10. Differential Encoder Control

Register 38

Level/Value

Bits 1,0

Encoding off (continuously) 0,1

Encoding on (continuously) 1,1

Encoding enabled by pin 70

X,0

high - enable the Differential Encoder

low - disable the Differential Encoder

For any modulation mode, if differential encoding is

disabled then:

*

*

*

I

Q

I

1

1

0

Q

0*Ê=ÊI1

**

**

**

I

0

**

Q

Q

1

0

**

, I

1

0

*

, Q

1

1

b

2

,

If differential encoding is enabled, then the results are

b

3

**

Q

0

**

I

0

**

Q

1

**

I

1

**

Q

0

**

I

0

**

Q

1

**

I

1

bits 6-4

000 01

001 01

010 01

011 01

100 01

101 01

110 01

111 01

Register 2D

Register 2C bits

3,2

described below for each modulation type.

*

,

BPSK

In BPSK mode, the next output bit is found by XORing

the input bit with the current output bit. The result is a

180 degree phase change if the output is high and

0Êdegrees if the output is low.

QPSK

In QPSK mode, the next output dibit is found by

XORing the input dibit with the current output dibit.

Table 11 shows the results of the differential encoding

performed for QPSK modulation and the resulting

phase shift. In the table, I = I1 = I0 and Q = Q1= Q0.

16QAM

In 16QAM mode, the differential encoding algorithm is

the same as in QPSK. Only the two MSBÕs, I

are encoded. The output bits I

the inputs bits I

**

and Q

0

**

0

*

and Q

0

*

are set equal to

0

.

and Q

1**

**

1

STEL-1109 14 PRELIMINARY PRODUCT INFORMATION

Page 15

Table 11. QPSK Differential Encoding and Phase Shift

Current Input

(IQ)

00 00 00 0

01 00 01 -90 (CW)

10 00 10 90 (CCW)

11 00 11 180

Current Output

(IQ)

01 01 -90 (CW)

10 10 90 (CCW)

11 11 180

01 11 180

10 00 0

11 10 90 (CCW)

01 00 0

10 11 180

11 01 90 (CCW)

01 10 90 (CCW)

10 01 -90 (CW)

11 00 0

Symbol Mapper

*

*

The Symbol Mapper receives I

1

, Q

symbol. Based on the signal modulation and the

symbol mapping selection, the Symbol Mapper block

maps the symbol to a constellation data point

(I1,Q1,I0,Q0). The Symbol Mapping field (bits 7-5 of

Configuration Register 2EH) will map the four input bits

to a new value, as indicated in Table 12.

For BPSK and QPSK, the settings of the symbol to

constellation mapping bits is ignored. The

constellations for BPSK (Figure 6) and QPSK (Figure 7)

are shown below. I1Q1 values are indicated by large,

bold font (00 and 11) and I

values by the smaller

0Q0

font (00 and 11).

*

, I

, Q

1

of each

0

0*

Next Output

(IQ)

Phase Shift

(degrees)

Q

3

1

-3 -1 1 3

-1

00

11

11

I

-3

00

WCP 52999.c-10/29/97

Figure 6. BPSK Constellation

PRELIMINARY PRODUCT INFORMATION 15 STEL-1109

Page 16

Q

Q

01 11

3

1101

1

-3 -1 1 3

I

-1

00 10

00

-3

Figure 7. QPSK Constellation

16QAM

For 16QAM modulation, the Symbol Mapper maps

each input symbol to one of the 16QAM constellations.

The specific constellation is programmed by the Symbol

Mapping field (bits 7-5 of Configuration Register 2EH)

to select the type of symbol mapping. If the MSB of the

Symbol Mapping field is set to 0, the mapping will be

bypassed and I1Q1I0Q0 = I

constellation (Figure 8) is the natural constellation for

the STEL-1109.

*

*

*

Q

I

1

Q

1

0

10

WCP 52986.c-10/29/97

*

. The resulting

0

10

10

11

-3 -1 1 3

10

11

11

00

01

00

01

10

00

1

11

10

01

11 01

WCP 52987.c-10/29/97

Figure 8. Natural Mapping Constellation

Table 12. Symbol Mapping Selections

Mapping

Selection

Natural 0XX

Gray 100

DAVIC 101

Left 110

Right 111

Register 2E

Bits 7-5

00

01

I

00

If the MSB of the Symbol Mapping field is set to 1, bits

6-5 can select any of four possible types of symbol

mapping (Gray, DAVIC, Left, or Right), as indicated by

Table 12.

Table 13 summarizes the symbol mapping and the

resulting constellations are shown in Figure 8 and

Figure 9. In these figures, I1Q1 are indicated by large,

bold font (00, 01, 10, and 11) and I

0Q0

by the

smaller font (00, 01, 10, and 11).

STEL-1109 16 PRELIMINARY PRODUCT INFORMATION

Page 17

Table 13. Symbol Mapping

Input Code

Natural

Mapping

(Bypass)

*

*

*

I

Q

1

*

I

Q

1

0

0

0000 0011 0011 0011 0011 0000

0001 0010 0001 0010 0001 0001

0010 0001 0010 0001 0010 0010

0011 0000 0000 0000 0000 0011

0100 0110 0110 0101 1010 0100

0101 0111 0111 0111 1011 0101

0110 0100 0100 0100 1000 0110

0111 0101 0101 0110 1001 0111

1000 1001 1001 1010 0101 1000

1001 1000 1000 1000 0100 1001

1010 1011 1011 1011 0111 1010

1011 1010 1010 1001 0110 1011

1100 1100 1100 1100 1100 1100

1101 1101 1110 1101 1110 1101

1110 1110 1101 1110 1101 1110

1111 1111 1111 1111 1111 1111

Gray DAVIC Left Right

*

*

*

I

Q

1

*

I

Q

1

0

0

*

*

*

I

Q

1

*

I

Q

1

0

0

*

*

*

I

Q

1

*

I

Q

1

0

0

I

*

*

*

Q

1

*

I

Q

1

0

0

Output

Code

I

Q

1

1

I0 Q

0

Q

11

01

01

-3 -1 1 3

0010

1

0010

00

11

Figure 9. Gray Coded Constellation

01

1101

11

1000

1000

10

1101

WCP 52988.c-10/29/97

Q

11

10

-3 -1 1 3

I

11

11

10

0001

0010

01

1101

00

1

1000

I

0100

01

1110

WCP 52989.c-4/26/97

Figure 10. Left Coded Constellation

PRELIMINARY PRODUCT INFORMATION 17 STEL-1109

Page 18

Q

11

01

10

-3 -1 1 3

0010

0001

1

00

NYQUIST FIR FILTER

The finite impulse response (FIR) filters are used to

shape each transmitted symbol pulse by filtering the

1110

pulse to minimize the sidelobes of its spectrum. The

Symbol Mapper Block outputs the I1I0 data to a pair of

I-channel FIR filters and the Q1Q0 data to a pair of

Q-channel FIR filters. Figure 13 shows the filter block

diagram for a channel pair (I or Q). The FIR filter can

0100

I

be bypassed altogether or, in BPSK or QPSK modes,

individual channels can be turned on and off which

changes the effective filter gain. Table 14 shows the

1000

various FIR configuration options.

10

WCP 52990.c-4/26/97

11

11

10

Figure 11. DAVIC Coded Constellation

Q

11

01

-3 -1 1 3

11

11

01

0010

0001

10

00

1

10

WCP 52991.c-4/26/97

Figure 12. Right Coded Constellation

Table 14. FIR Filter Configuration Options

Mode Gain

1101

No FIR Filter N/A XXXX 1

16QAM Unity 1010 0

BPSK/QPSK Unity 0000 0

BPSK/QPSK x2 1111 0

BPSK/QPSK x3 1010 0

Register 2E

Bits 4-1

Register 2C

Bit 1

Each of the 32-tap, linear phase, FIR filters use

16Êten-bit, coefficients, which are completely pro-

1110

grammable for any symmetrical (mirror image) polynomial. The FIR filter coefficients are stored in

addresses 09H - 28H, using two addresses for each 10-bit

coefficient as shown in Table. The coefficients are stored

as TwoÕs Complement numbers in the range -512 to

0100

I

1000

+511 (200H to 1FFH). The filter is always constrained to

have symmetrical coefficients, resulting in a linear

phase response. This allows each coefficient to be

stored once for two taps, as shown in Table 15.

Table 15. FIR Filter Coefficient Storage

MSB

(Bits 9-8)

0A

1101

Note: For MSB storage, only bits 1-0 are used.

H

0C

H

0E

H

10

H

ÉÉ É

ÉÉ É

22

H

24

H

26

H

28

H

LSB

(Bits 7-0) Filter Taps

09

0B

0D

0F

21

23

25

27

H

H

H

H

H

H

H

H

Taps 0 and 31

Taps 1 and 30

Taps 2 and 29

Taps 3 and 28

Taps 12 and 19

Taps 13 and 18

Taps 14 and 17

Taps 15 and 16

STEL-1109 18 PRELIMINARY PRODUCT INFORMATION

Page 19

I

1/Q1

COEFFICIENT

I

0/Q0

FIR

FIR

momentary ÒhitsÓ of broad band spectral noise, then

X2

1

M

U

X

0

1

M

U

X

0

L

O

OUT

G

I

C

the digital gain is too high. The interpolation filter gain

is the first place to adjust gain because it does not

directly affect the shape of the signal spectrum and it

has a very wide adjustment range. Overall, gain can

affected in the FIR filter function, the interpolation gain

function, and by the number of interpolation stages

(and therefore accumulators) used.

CLRFIR

BYPASS

2

WCP-52992.c-4/26/97

Figure 13. Nyquist FIR Filter

INTERPOLATING FILTER

The Interpolating Filter, shown in Figure 14, is a

configurable, three-stage, interpolating filter. The filter

increases the STEL-1109Õs sampling rate (to permit the

wide range of RF carrier frequencies possible) by

interpolating between the FIR filter steps at the master

clock frequency. This smoothes the digital

representation of the signal which removes spurious

signals from the spectrum.

Data Enable

16

2

3-Stage

Differentiator

4

16

G

a

i

n

3-Stage

Integrator

1132

WCP 52993.c-5/2/97

Bypass

Sample

Clock

Gain Control

Master Clock

Figure 14. Interpolation Filter Block Diagram

The interpolation filter contains accumulators. As the

interpolation ratio grows larger, the number of

accumulations per period of time increases. If the

interpolation ratio becomes too large, the accumulator

will overflow which will destroy the output spectral

characteristics. To compensate for this, the

interpolation filter has a gain function. This gain is

normally set empirically. If the output spectrum is

broad band noise or if it appears correct but has regular

Normally, three interpolation stages are used, but there

is a bypass option for use when the interpolation is very

high. It should be used only as a last resort after all

other gain reduction options have been exercised

because of the severe impact to spurious performance.

The register bits that affect the interpolation filter

functions are shown inTable 16 and Table 17.

Table 16. Interpolation Filter Bypass Control

Number of

Interpolation Stages

Selected

3 0Ê0

2 0Ê1

2 1Ê0

1 1Ê1

Interpolation Filter Bypass

Register 2B Bits 5,4

Table 17. Interpolation Filter Signal Level Control

Gain Factor

(Relative)

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

2

10

2

11

2

12

2

13

2

14

2

15

2

Filter Gain Control

Register 2A Bits 7-4

0

H

1

H

2

H

3

H

4

H

5

H

6

H

7

H

8

H

9

H

A

H

B

H

C

H

D

H

E

H

F

H

PRELIMINARY PRODUCT INFORMATION 19 STEL-1109

Page 20

MODULATOR

The interpolated I and Q data signals are input from the

Interpolation Filter, fed into two complex modulators,

and multiplied by the sine and cosine carriers which are

generated by the NCO. The I channel signal is

multiplied by the cosine output from the NCO and the

Q channel signal is multiplied by the sine output. The

resulting modulated sine and cosine carriers are

applied to an adder and either added or subtracted

together according to the register settings shown in

Table 18. This provides control over the characteristics

of the resulting RF signal by allowing either or both of

the two products to be inverted prior to the addition.

Data Enable Output. The DATAENO output pin is a

modified replica of the DATAEN input. DATAENO is

asserted as a high 2 symbols after DATAEN goes high

and it is asserted as a low 13 symbols after DATAEN

goes low. In this way, a high on the DATAENO line

indicates the active period of the DAC during

transmission of the data burst. However, if the guard

time between the current and next data burst is less

than 13 symbols, then the DATAENO line will be held

high through the next burst.

Table 18. Signal Inversion Control

Output of Adder Block

Sum = I

Sum = ÐI

Sum = I

Sum = ÐI

.

cos(ωt) + Q

.

cos(ωt) + Q

.

cos(ωt) Ð Q

.

cos(ωt) Ð Q

.

sin(ωt)

.

sin(ωt)

.

sin(ωt)

.

sin(ωt)

Invert I/Q Channel

Register 2B Bits 1,0

0Ê0

0Ê1

1Ê0

1Ê1

10-BIT DAC

The 10-bit Digital-to-Analog Converter (DAC) receives

the modulated digital data and the Master clock. The

DAC samples the digital data at the rate of the Master

clock and outputs a direct analog RF signal at a

frequency of 5 to 65 MHz. The DAC outputs, OUT and

OUTN, are complementary current sources designed to

drive double terminated 50Ω or 75Ω (25Ω or 37.5Ω

total) load to ground. The nature of digitally sampled

signals creates an image spur at a frequency equal to

the Master Clock minus the output RF frequency. This

image spur should be filtered by a user supplied low

pass filter. For best overall spurious performance, the

gain of the STEL-1109 should be the highest possible

(before digital overflow occurs - see Interpolation Filter

discussion).

CONTROL UNIT DESCRIPTION

BUS INTERFACE UNIT

The Bus Interface Unit (BIU) contains the Configuration

Registers (58 programmable 8-bit registers). The Reset

( RST ) input signal is the master reset for the

STEL-1109. Asserting a low on RST will reset the

contents of all Configuration Registers to 00H (as well as

clearing the data path registers). Asserting a high on

RST enables normal operation. After power is applied

and prior to configuring the STEL-1109, a low should

be asserted on RST . Since RST is asynchronous, the

CLKEN input should be held low whenever RST is

low.

The parallel address bus (ADDR

one of the 58 Configuration Registers by placing its

address on the ADDR

(DATA

) is an 8-bit, bi-directional data bus for writing

7-0

bus lines. The data bus

5-0

data into or reading data from the selected

Configuration Register.

The access operation is performed using the control

signals DSB , CSEL , and WR . The Chip Select

( CSEL ) input signal is used to enable or disable access

operations to the STEL-1109. When a high is asserted

on CSEL , all access operations are disabled and a low

is asserted to enable the access operations. The

CSEL input only affects Configuration Register access

and has no effect on the data path.

The Data Strobe ( DSB ) input signal is used to write the

data that is on the data bus (DATA

Configuration Register selected by ADDR

Write/Read ( WR ) input signal is used to control the

direction of the Configuration Register access

operation. When WR is high, the data in the selected

Configuration Register is output onto the DATA

When WR is low, the rising edge of DSB is used to

latch the data on the DATA

Configuration Register. (Refer to the Write and Read

Timing diagrams in the Timing Diagrams section.)

Some of the Configuration Register data fields are used

for factory test and must be set to specific values for

normal operation. These values are noted in Table 3.

CLOCK GENERATOR

The timing of the STEL-1109 is controlled by the Clock

Generator, which uses an external master clock (CLK)

and programmable dividers to generate all of the

internal and output clocks. There are primarily two

) is used to select

5-0

) into the

7-0

5-0

7-0

bus into the selected

7-0

. The

bus.

STEL-1109 20 PRELIMINARY PRODUCT INFORMATION

Page 21

clock systems, the auxiliary clock and the data path

timing signals (bit, symbol, and sampling rate signals).

The auxiliary clock (ACLK) output is primarily for use

in master mode where users may need a clock to run

control circuits during the guard time between bursts

(when CLKEN is low and BITCLK has stopped). The

output clock rate is set by the frequency (f

CLK

) of the

external master clock and the value (N) of the Auxiliary

Clock Rate Control field (bits 3-0 of Configuration

Register 2AH). The clock rate is set to:

f

ACLK =

CLK

N+1

2 N 15

≤≤

If N is set to 1 or 0, the ACLK output will remain set

high, thereby disabling this function. If the ACLK

signal is not required, it is recommended that it be set

in this mode to conserve power consumption. The

ACLK output is a pulse that will be high for 2 cycles of

CLK and low for (N-1) CLK cycles. Unlike other

functions, the ACLK output is not affected by CLKEN.

The data path timing is based on the ratio of the master

clock frequency to the symbol data rate. The ratio must

be a value of four times an integer number (N+1). The

value of N must be in the range of 3 to 4095. This value

is represented by a 12 bit binary number that is

programmed by LSB and MSB Sampling Rate Control

fields [Configuration Register 29H (LSB) and bits 3-0 of

Configuration Register 39H (MSB)], which sets the

SYMPLS frequency [based on the frequency (f

CLK

) of

the external master clock] to:

f

CLK

1

∗

4

N1

+

3 N 4095

≤≤

Symbol Rate =

The symbol pulse (SYMPLS) signal output is intended

to allow the user to verify synchronization of the

external serial data (TSDATA) with the STEL-1109

symbol timing. SYMPLS is normally low and pulses

high for a period of one CLK cycle at the point where

the last bit of the current symbol is internally latched by

the falling edge of the internal BIT Clock (BITCLK)

signal. (Refer to the Timing Diagrams section.)

The internal BITCLK period is a function of the MOD

field (bits 3-2 of Configuration Register 2CH), which

determines the signal modulation. BITCLK has a 50%

duty cycle for BPSK and QPSK modes. It also has a

50% duty cycle in 16QAM mode when N+1 is even. If

N+1 is odd, then BITCLK will be high for (N÷2)+1

clocks and then low for N÷2 clocks. (Refer to the Bit

Clock Synchronization Timing diagram in the Timing

Diagrams section.)

The BITCLK frequency is determined by :

BITCLK =

CLK

(N+1) K

K = 1 for 16QAM,

2 for QPSK,

∗

4 for BPSK

3 N 4095

≤≤

NCO

A 24-bit, Numerically Controlled Oscillator (NCO) is

used to synthesize a digital carrier for output to the

Modulator. The NCO gives a frequency resolution of

about 6 Hz at a clock frequency of 100 MHz. The NCO

also uses 12-bit sine and cosine lookup tables (LUTs) to

synthesize a carrier with very high spectral purity, typically better than -75 dBc at the digital outputs.

The STEL-1109 provides register space for three

different carrier frequencies. The carrier frequency that

will drive the modulator is selected by the FCWSEL

1-0

control pin input signals. A high on the NCO LD input

pin causes the registers selected by FCWSEL to drive

the NCO at the frequency determined by the register

value.

The NCOÕs frequency is programmable using the NCO

field (Configuration Registers 08H -00H). The nine 8-bit

registers at addresses 00H through 08H are used to store

the three 24-bit frequency control words FCW ÔAÕ, FCW

ÔBÕ and FCW ÔCÕ as shown in Table 19.

The output carrier frequency of the NCO (f

.

f FCW

CLK

24

2

where, f

f =

CARR

is the frequency of the CLK input signal.

CLK

CARR

) will be:

The FZSINB field (bit 7 Configuration Register 2DH)

controls the sine component output of the NCO. This

can be used in BPSK to rotate the constellation 45

degrees (to Ôon axisÕ modulation). For normal

operation, it should be set to one.

PRELIMINARY PRODUCT INFORMATION 21 STEL-1109

Page 22

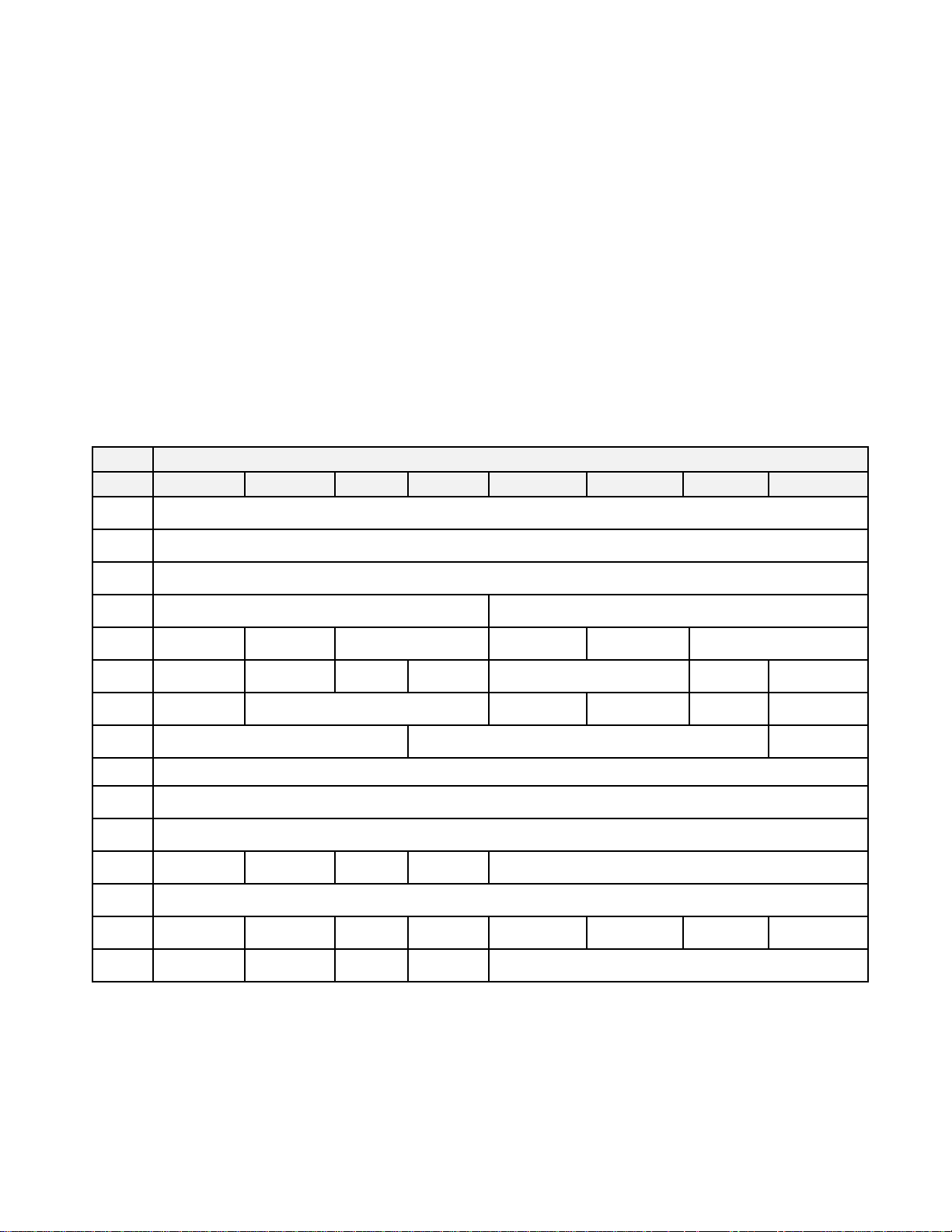

Table 19. FCW Selection

FCW Value Bits

FCWSEL

00 FCW A Register 02H Bits 7 - 0 Register 01H Bits 7 - 0 Register 00H Bits 7 - 0

01 FCW B Register 05H Bits 7 - 0 Register 04H Bits 7 - 0 Register 03H Bits 7 - 0

10 FCW C Register 08H Bits 7 - 0 Register 07H Bits 7 - 0 Register 06H Bits 7 - 0

11 Zero Frequency

FCW Selected 23 - 16 15 - 8 7 - 0

1-0

STEL-1109 22 PRELIMINARY PRODUCT INFORMATION

Page 23

TIMING DIAGRAMS

CLOCK TIMING

CLK

PIN 28

t

CLK

Symbol Parameter Min. Nom. Max. Units Conditions

t

CLK

t

CLKH

t

CLKL

t

R

t

F

PULSE WIDTH

t

CLKH

t

r

t

f

t

CLKL

WCP 52787.c-3/26/97

Table 20. Clock Timing AC Characteristics

(V

= 3.3 V ±10%, V

DD

Clock Frequency (

1

)

t

CLK

Clock Period 6 nsec

Clock High Period 2.5 nsec

Clock Low Period 2.5 nsec

Clock Rising Time 0.5 nsec

Clock Falling Time 0.5 nsec

CLKEN

PIN 26

= 0 V, T

SS

t

CEL

= Ð40° to 85° C)

a

165 MHz

t

RSTL

RSTB

PIN 67

NCO LD

PIN 71

t

NLDH

WCP 52930.c-4/26/97

Table 21. Pulse Width AC Characteristics

(V

= 3.3 V ±10%, V

DD

= 0 V, T

SS

= Ð40° to 85° C)

a

Symbol Parameter Min. Nom. Max. Units Conditions

t

CEL

t

RSTL

t

NLDH

Clock Enable (CLKEN) Low 4 nsec

Reset (RSTB) Low 5 nsec

NCO Load (NCO LD) High 1 CLK cycles

PRELIMINARY PRODUCT INFORMATION 23 STEL-1109

Page 24

BIT CLOCK SYNCHRONIZATION

CLK

PIN 28

CLKEN

PIN 26

t

CESU

TCLK

PIN 19

t

CO

t

CO

BITCLK

PIN 40

Note 1: BITCLK will be forced high on the second rising edge of CLK following the rising edge of TCLK.

Note 2: The period of time that BITCLK is high is measured in cycles of CLK (e.g. (N + 1) in QPSK). "N" is a 12 bit

binary number formed by taking bits 3-0 of Configuration Register 39 H as the MSB's and taking bits 7-0 of

Configuration Register 29H as the LSB's. The BITCLK low period is the same except for 16QAM when "N"

is even in which case the low period is (N/2) yielding the correct BITCLK period but not a perfect

squarewave.

2 (N +1) BPSK

(N +1) QPSK

N +1

16QAM

2

n = Odd

N +2

16QAM

2

n = Even

See Note 2 See Note 1

WCP 52786.c-5/2/97

Table 22. Bit Clock Synchronization AC Characteristics

(V

= 3.3 V ±10%, V

DD

Symbol Parameter Min. Nom. Max. Units Conditions

t

t

CO

CESU

Clock to BITCLK, SYMPLS, DATAENO, or

AUXCLK edge

Clock Enable (CLKEN to TCLK Setup) 3 nsec

= 0 V, T

SS

= Ð40° to 85° C)

a

2 nsec

STEL-1109 24 PRELIMINARY PRODUCT INFORMATION

Page 25

INPUT DATA AND CLOCK TIMING

MASTER MODESLAVE MODE

DON'T CARE

t

CLK

tSU tHD

NOTE 1

WCP 52935.c -5/2/97

TCLK

BITCLK DON'T CARE

TSDATA

NOTE 2

tSU

tHD

NOTE 1

TCLK

BITCLK

TSDATA

NOTE 3

Note 1: Mode is determined by setting of BIT 7 in Configuration Register 2CH. Bit 7 high is slave mode; Bit 7

low is master mode.

Note 2: In slave mode, even though BITCLK is shown as ÒDon't CareÓ, it should be noted that internally the

STELÊ1109 will relatch the data on the next falling edge of BITCLK. Thus, avoid changing the control

signal inputs (DATAEN, DIFFEN, RDSLEN, SCRMEN) at the falling edges of BITCLK.

Note 3: In the STEL-1109, data is latched on the rising edge of the CLK that follows the falling edge of BITCLK.

Thus, the data validity window is one CLK period (t

) delayed. CLK not shown.

CLK

Table 23. Input Data and Clock AC Characteristics

(V

= 3.3 V ±10%, V

DD

Symbol Parameter Min. Nom. Max. Units Conditions

t

CLK

t

SU

t

HD

Clock Period 6 nsec

TSDATA to Clock Setup 2 nsec

TSDATA to Clock Hold 2 nsec

= 0 V, T

SS

= Ð40° to 85° C)

a

PRELIMINARY PRODUCT INFORMATION 25 STEL-1109

Page 26

WRITE TIMING

Address

ADDR

CSEL

Pin 72

WR

Pin 74

DSB

Pin 73

Data

DATA

[5-0]

[7-0]

t

WASU

t

t

CSSU

WRSU

t

AVA

t

DSBL

t

t

DH

DSU

t

WAHD

t

CSHD

t

WRHD

WCP 52717.c-5/2/97

Table 24. Write Timing AC Characteristics

(V

= 3.3 V ±10%, V

DD

Symbol Parameter Min. Nom. Max. Units Conditions

t

WASU

t

WAHD

t

AVA

t

CSSU

t

CSHD

t

WRSU

t

WRHD

t

DSBL

t

DH

t

DSU

Write Address Setup 10 nsec

Write Address Hold 6 nsec

Address Valid Period

Chip Select CSEL Setup

Chip Select (

CSEL

) Hold

Write Setup ( WR) 5 nsec

Write Hold ( WR) 3 nsec

Data Strobe Pulse Width 10 nsec

Data Hold Time 1 nsec

Data Setup Time 3 nsec

= 0 V, T

SS

= Ð40° to 85° C)

a

20 nsec

5 nsec

3 nsec

STEL-1109 26 PRELIMINARY PRODUCT INFORMATION

Page 27

READ TIMING

Address

CS

WR

Data

t

ADV

t

DVCSL

t

AVA

t

ADIV

Table 25. Read Timing AC Characteristics

t

DICSH

WCP 52928.c-5/2/97

(V

= 3.3 V ±10%, V

DD

Symbol Parameter Min. Nom. Max. Units Conditions

t

AVA

t

ADV

t

ADIV

t

DVCSL

t

DICSH

Address Valid Period 20 nsec

Address to Data Valid Delay 9 nsec

Address to Data Invalid Delay 6 nsec

Data Valid After Chip Select Low 2 nsec

Data Invalid After Chip Select High 1 nsec

= 0 V, T

SS

= Ð40° to 85° C)

a

PRELIMINARY PRODUCT INFORMATION 27 STEL-1109

Page 28

NCO LOADING (USER CONTROLLED)

OUTPUT

t

FCWSU

FCWSEL

DON'T CARE

1-0

NCO_LD

NOTE 1

NCO LOADING (AUTOMATIC)

OUTPUT

FCWSEL

DATAENO

1-0

DON'T CARE

ZERO

t

FCWHD

VALID DON'T CARE

t

LDPIPE

SELECTED FREQUENCY ZERO

t

DENHV

VALID DON'T CARE

OLD FREQ.

t

DENLZ

NEW FREQ.

WCP 52909.c-5/2/97

t

DOFCWV

t

DOFCWI

WCP 52909.c-5/2/97

NOTE 1: The first rising edge of CLK after NCO LD goes high initiates the load process.

Table 26. NCO Loading AC Characteristics

(V

= 3.3 V ±10%, V

DD

Symbol Parameter Min. Nom. Max. Units Conditions

t

LDPIPE

NCO-LD to Change in Output Frequency Pipeline

Delay

t

FCWSU

t

FCWHD

t

DENLZ

t

DENHV

t

DOFCWV

t

DOFCWI

FCWSEL

FCWSEL

to NCO-LD Setup 3 CLK cycles

1-0

to NCO-LD Hold 10 CLK cycles

1-0

DATAENO Low to Zero Frequency Out Delay 23 CLK cycles

DATAENO High to Valid Frequency Out Delay 23 CLK cycles

DATAENO to FCWSEL

DATAENO to FCWSEL

Valid 3 CLK cycles

1-0

Invalid 10 CLK cycles

1-0

= 0 V, T

SS

= Ð40° to 85° C)

a

23 CLK cycles

STEL-1109 28 PRELIMINARY PRODUCT INFORMATION

Page 29

DIGITAL OUTPUT TIMING

CLK

t

CO

t

AUXCLK

Note 1

CO

t

ACKH

BITCLK

SYMPLS

DATAENO

t

ACKL

t

CO

t

SPH

t

CO

t

DENOD

t

CO

WCP 52908.c-5/2/97

NOTE 1: AUXCLK shown for "n" equal to 2: where n is the 4-bit binary value in Configuration

Register 2AH, BITSÊ3-0.

Table 27. Digital Output Timing AC Characteristics

(V

= 3.3 V ±10%, V

DD

Symbol Parameter Min. Nom. Max. Units Conditions

t

CO

t

ACKH

t

ACKL

t

SPH

t

DENOD

Notes:

1. ÒnÓ is the 4 bit binary value in Configuration Register 2A

Clock to BITCLK, SYMPLS, DATAENO,

or AUXCLK edge

Auxiliary Clock (ACLK) High 2 CLK cycles

Auxiliary Clock (ACLK) Low

Symbol Pulse (SYMPLS) High 1 CLK cycles

BITCLK Low to DATAENO edge 1 CLK cycles

= 0 V, T

SS

H ,

bits 3-0.

= Ð40° to 85° C)

a

2 nsec

(n-1) CLK cycles Note 1

PRELIMINARY PRODUCT INFORMATION 29 STEL-1109

Page 30

DATAEN TO DATAENO TIMING

t

DENSP

DATAEN

t

DIHDO

t

t

SPDEN

DATAENO

t

DENSP

SYMPLS