Page 1

Intel® Server Board

SE7505VB2

Technical Product Specification

Intel part number C32194-002

Enterprise Platforms and Services Marketing

Revision 1.2

April 2004

Page 2

Revision History Intel® Server Board SE7505VB2

Revision History

Date Revision Number Modifications

January 2003 1.0 Initial Release

Added memory cooling duct information, added section on BIOS event

March 2003 1.1

April 2004 1.2 New graphics for Mechanical Changes.

log, incorporated Technology Leadership terminology, and corrected

miscellaneous minor technical details.

Revision 1.2

ii

Intel part number C32194-002

Page 3

Intel® Server Board SE7505VB2 Disclaimers

Disclaimers

Information in this document is provided in connection with Intel® products. No license, express

or implied, by estoppel or otherwise, to any intellectual property rights is granted by this

document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel

assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property

right. Intel products are not intended for use in medical, life saving, or life sustaining

applications. Intel may make changes to specifications and product descriptions at any time,

without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked

"reserved" or "undefined." Intel reserves these for future definition and shall have no

responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SE7505VB2 server system may contain design defects or errors known as errata that may

cause the product to deviate from published specifications. Current characterized errata are

available on request.

Intel and Xeon are trademarks or registered trademarks of Intel Corporation.

*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2003.

Revision 1.2

Intel part number C32194-002

iii

Page 4

Table of Contents Intel® Server Board SE7505VB2

Table of Contents

1. Introduction ........................................................................................................................13

2. SE7505VB2 Server Board Overview ................................................................................. 14

2.1 Intel® Server Board SE7505VB2 Feature Set................................................................ 14

3. Functional Architecture ..................................................................................................... 16

3.1 Processor and Memory Subsystem............................................................................... 16

3.1.1 Processor Support ...................................................................................................16

3.1.2 Memory Subsystem .................................................................................................17

3.2 The Intel® E7505 Chipset............................................................................................... 21

3.2.1 MCH Memory Architecture Overview....................................................................... 22

3.2.2 Memory Controller Hub (MCH) ................................................................................ 23

3.2.3 P64H2 ...................................................................................................................... 24

3.2.4 ICH4 ......................................................................................................................... 24

3.3 Super I/O .......................................................................................................................28

3.3.1 GPIOs ......................................................................................................................29

3.3.2 Serial Ports............................................................................................................... 29

3.3.3 BIOS Flash............................................................................................................... 30

4. Clock Generation and Distribution ................................................................................... 31

5. PCI I/O Subsystem .............................................................................................................33

5.1 PCI Subsystem ..............................................................................................................33

5.1.1 P32-A: 32-bit/33-MHz PCI Subsystem..................................................................... 33

5.1.2 P64-B and P64-C: 64-bit/100- or 66-MHz PCI Subsystem ...................................... 34

5.2 Serial ATA Controller .....................................................................................................35

5.3 Video Controller ............................................................................................................. 36

5.3.1 Video Modes ............................................................................................................ 37

5.3.2 Video Memory Interface ........................................................................................... 37

5.3.3 Host Bus Interface.................................................................................................... 38

5.4 Network Interface Controller (NIC) ................................................................................ 39

5.4.1 NIC Connector and Status LEDs .............................................................................39

5.5 Interrupt Routing ............................................................................................................ 40

5.5.1 Legacy Interrupt Routing.......................................................................................... 40

5.5.2 APIC Interrupt Routing ............................................................................................. 40

5.5.3 Serialized IRQ Support ............................................................................................41

Revision 1.2

iv

Intel part number C32194-002

Page 5

Intel® Server Board SE7505VB2 Table of Contents

5.5.4 IRQ Scan for PCIIRQ ...............................................................................................41

5.6 PCI Error Handling......................................................................................................... 41

6. Hardware Monitoring ......................................................................................................... 45

6.1 Monitored Components .................................................................................................45

6.2 Fan Speed Control......................................................................................................... 46

6.3 Chassis Intrusion ........................................................................................................... 46

7. SE7505VB2 ACPI Implementation .................................................................................... 48

7.1 ACPI ..............................................................................................................................48

7.1.1 Front Panel Switches ............................................................................................... 48

7.1.2 Wake up Sources (ACPI and Legacy) .....................................................................49

8. SE7505VB2 Connectors..................................................................................................... 50

8.1 Main Power Connector .................................................................................................. 50

8.2 Memory Module Connector ........................................................................................... 51

8.3 Processor Socket........................................................................................................... 52

8.4 I2C Header ..................................................................................................................... 55

8.5 PCI Slot Connector ........................................................................................................55

8.6 AGP 3.0 Pro50 Connector .............................................................................................58

8.7 Front Panel Connector................................................................................................... 59

8.8 VGA Connector.............................................................................................................. 59

8.9 NIC Connector ...............................................................................................................60

8.10 IDE Connector ............................................................................................................ 60

8.11 SATA Connector......................................................................................................... 61

8.12 USB Connector........................................................................................................... 62

8.13 Floppy Connector ....................................................................................................... 63

8.14 Serial Port Connector ................................................................................................. 63

8.15 Keyboard and Mouse Connector................................................................................ 64

8.16 Miscellaneous Headers .............................................................................................. 64

8.16.1 Fan Header ............................................................................................................64

8.16.2 Intrusion Cable Connector...................................................................................... 65

9. Configuration Jumpers...................................................................................................... 66

9.1 System Recovery and Update Jumpers ........................................................................66

10. BIOS..................................................................................................................................... 67

10.1 Using the BIOS Setup Utility....................................................................................... 67

10.1.1 If You Cannot Access Setup ..................................................................................67

10.1.2 Starting Setup......................................................................................................... 67

Revision 1.2

Intel part number C32194-002

v

Page 6

Table of Contents Intel® Server Board SE7505VB2

10.1.3 Setup Menus .......................................................................................................... 67

10.1.4 Menu Selection Bar ................................................................................................69

10.1.5 Main Menu.............................................................................................................. 70

10.1.6 Advanced Menu ..................................................................................................... 72

10.1.7 Security Menu ........................................................................................................ 83

10.1.8 Power Menu ........................................................................................................... 84

10.1.9 Boot Menu ..............................................................................................................85

10.1.10 System Menu......................................................................................................... 86

10.1.11 Exit Menu............................................................................................................... 87

10.2 Upgrading the BIOS ...................................................................................................88

10.2.1 Preparing for the Upgrade...................................................................................... 88

10.2.2 Upgrading the BIOS ............................................................................................... 89

10.2.3 Crisis Recovery Diskette ........................................................................................ 90

10.3 Error Handling and Reporting.....................................................................................93

10.3.1 POST Error Beep Codes........................................................................................ 93

10.3.2 BIOS Event Log...................................................................................................... 93

11. Absolute Maximum Ratings .............................................................................................. 94

12. Power Information.............................................................................................................. 95

12.1 SE7505VB2 Server Board Power Budget .................................................................. 95

12.2 Power Supply Specifications ...................................................................................... 96

12.2.1 Power Timing ......................................................................................................... 96

12.2.2 Voltage Recovery Timing Specifications ................................................................ 99

13. Product Regulatory Compliance..................................................................................... 100

13.1.1 Product Safety Compliance.................................................................................. 100

13.1.2 Product EMC Compliance .................................................................................... 100

13.1.3 Mandatory / Standard: Certifications; Registration; Declarations......................... 100

13.1.4 Other Product Mandatory Regulations to Consider due to new Emerging

International Requirements ................................................................................................ 101

13.1.5 Important Product Regulation Requirements .......................................................101

13.1.6 Product Regulatory Compliance Markings ........................................................... 101

13.2 Electromagnetic Compatibility Notices ..................................................................... 102

13.2.1 Europe (CE Declaration of Conformity)................................................................ 102

13.2.2 Australian Communications Authority (ACA) (C-Tick Declaration of Conformity)102

13.2.3 Ministry of Economic Development (New Zealand) Declaration of Conformity .... 102

13.2.4 BSMI (Taiwan)...................................................................................................... 102

Revision 1.2

vi

Intel part number C32194-002

Page 7

Intel® Server Board SE7505VB2 Table of Contents

13.3 Replacing the Back up Battery ................................................................................. 102

14. Mechanical Specifications............................................................................................... 104

Glossary................................................................................................................................... 106

Reference Documents ............................................................................................................108

Index................................................................................................. Error! Bookmark not defined.

Revision 1.2

Intel part number C32194-002

vii

Page 8

List of Figures Intel® Server Board SE7505VB2

List of Figures

Figure 1. The Board Block Diagram............................................................................................ 15

Figure 2. Memory Sub-system Block Diagram............................................................................ 18

Figure 3. Memory Bank Label Definition..................................................................................... 20

Figure 4. SE7505VB2 Clock Distribution Diagram...................................................................... 32

Figure 5. Video Controller PCI Bus Interface.............................................................................. 38

Figure 6. Interrupt Routing Diagram (ICH4 Internal)................................................................... 42

Figure 7. Interrupt Routing Diagram ...........................................................................................43

Figure 8. The Board PCI Interrupt Mapping Diagram ................................................................. 44

Figure 9. Hardware Monitoring ...................................................................................................47

Figure 10. System Recovery and Update Jumpers (J4J1) ......................................................... 66

Figure 11. BIOS Recovery Jumper ............................................................................................. 92

Figure 12. Output Voltage Timing ............................................................................................... 97

Figure 13. Turn on / off Timing.................................................................................................... 98

Figure 14. Intel Server Board SE7505VB2 Mechanical Drawing.............................................. 104

Figure 15. Board Photograph (Reference Only) ....................................................................... 105

Revision 1.2

viii

Intel part number C32194-002

Page 9

Intel® Server Board SE7505VB2 List of Tables

List of Tables

Table 1. Processor Support Matrix .............................................................................................16

Table 2. Memory Bank Labels .................................................................................................... 20

Table 3. I2C Addresses for Memory Module SMB ......................................................................21

Table 4. Supported DDRs...........................................................................................................23

Table 5. ICH4 GPIO Usage Table ..............................................................................................26

Table 6. Super I/O GPIO Usage Table ....................................................................................... 29

Table 7. PCI Bus Segment Characteristics................................................................................. 33

Table 8. P32-A Configuration IDs ............................................................................................... 33

Table 9. P32-A Arbitration Connections...................................................................................... 34

Table 10. P64-B Configuration IDs ............................................................................................. 34

Table 11. P64-C Configuration IDs .............................................................................................34

Table 12. P64-B Arbitration Connections.................................................................................... 35

Table 13. P64-C Arbitration Connections ...................................................................................35

Table 14. sATA RAID Level ........................................................................................................36

Table 15. Video Modes ............................................................................................................... 37

Table 16. PCI Interrupt Routing/Sharing..................................................................................... 40

Table 17. Interrupt Definitions.....................................................................................................41

Table 18. Monitored Components............................................................................................... 45

Table 19. Supported Wake Events ............................................................................................. 49

Table 20. Power Connector Pin-out (J9B1) ................................................................................ 50

Table 21. Auxiliary Signal Connector (J7K1) .............................................................................. 50

Table 22. Auxiliary CPU Power Connector Pin-out (J9K1) ......................................................... 50

Table 23. DIMM Connectors (J9H1, J9J1, J9H2, J9J2).............................................................. 51

Table 24. Socket 604 Processor Socket Pin-out (U8C1, U5C1)................................................. 52

Table 25. SCSI HDD Header Pin-out (J3K2, J4K1).................................................................... 55

Table 26. P32-A 5V 32-bit/33-MHz PCI Slot Pin-out (J4B1, J3B1)............................................. 55

Table 27. P64-B 3.3V 64-bit/100-MHz PCI-X Slot Pin-out (J2B1, J2B2) .................................... 56

Table 28. P64-C 3.3V 64-bit/66-MHz PCI Slot Pin-out (J1B1).................................................... 57

Table 29. AGP 3.0 Pro Connector Pin-out (J4C1) ......................................................................58

Table 30. Front Panel 34-Pin Header Pin-out (J1J1).................................................................. 59

Table 31. VGA Connector Pin-out (J7A1)................................................................................... 59

Table 32. NIC1 (10/100) Connector Pin-out (J5A1).................................................................... 60

Revision 1.2

Intel part number C32194-002

ix

Page 10

List of Tables Intel® Server Board SE7505VB2

Table 33. NIC2 (Gbit 10/100/1000) Connector Pin-out (J6A1) ................................................... 60

Table 34. ATA 40-pin Connector Pin-out (J3K2, J4K1) .............................................................. 60

Table 35. SATA Connector Pin-out (J1H1)................................................................................. 61

Table 36. SATA Connector Pin-out (J1H2)................................................................................. 61

Table 37. USB Connectors Pin-out (J9A2) ................................................................................. 62

Table 38. Optional USB Connection Header Pin-out (J5K1) ...................................................... 62

Table 39. Legacy 34-pin Floppy Connector Pin-out (J3K1) ........................................................63

Table 40. External DB9 Serial A Port Pin-out (J8A1).................................................................. 63

Table 41. 9-pin Header Serial B Port Pin-out (J1J2)................................................................... 64

Table 42. Keyboard and Mouse PS/2 Connectors Pin-out (J9A1).............................................. 64

Table 43. Three-pin Fan Headers Pin-out (J8A3, J7B1, J5K2, J5K3, J8A2, J5A2).................... 64

Table 44. Intrusion Cable Connector Pin-Out ............................................................................. 65

Table 45. System Recovery and Update Jumper Options.......................................................... 66

Table 46. Keyboard Commands ................................................................................................. 68

Table 47. On-Screen Options .....................................................................................................69

Table 48. Menu Selection Bar..................................................................................................... 69

Table 49. Main Menu .................................................................................................................. 70

Table 50. Primary/Secondary, Master/Slave Submenu .............................................................. 71

Table 51. Advanced Menu .......................................................................................................... 72

Table 52. I/O Device Configuration Submenu ............................................................................74

Table 53. On Board Device Submenu ........................................................................................ 76

Table 54. PCI Configuration Submenu ....................................................................................... 77

Table 55. Onboard Serial ATA Submenu ...................................................................................78

Table 56. Onboard NICs Submenu............................................................................................. 78

Table 57. Option ROM Scan Submenu ...................................................................................... 78

Table 58. Server Menu Submenu ...............................................................................................79

Table 59. Console Redirection Submenu ................................................................................... 80

Table 60. Event Logging Submenu............................................................................................. 81

Table 61. Hardware Monitor Submenu .......................................................................................82

Table 62. Security Menu ............................................................................................................. 83

Table 63. Power Menu................................................................................................................84

Table 64. Boot Menu................................................................................................................... 85

Table 65. System Menu ..............................................................................................................86

Table 66. Exit Menu .................................................................................................................... 87

Table 67. POST Error Beep Codes ............................................................................................93

Revision 1.2

x

Intel part number C32194-002

Page 11

Intel® Server Board SE7505VB2 List of Tables

Table 68. BIOS Event Log Error Messages................................................................................ 93

Table 69. Absolute Maximum Ratings ........................................................................................ 94

Table 70. The Board Power Budget............................................................................................ 95

Table 71. The Board Power Supply Voltage Specification .........................................................96

Table 72. Voltage Timing Parameters ........................................................................................97

Table 73. Turn On / Off Timing ................................................................................................... 98

Table 74. Transient Load Requirements..................................................................................... 99

Revision 1.2

Intel part number C32194-002

xi

Page 12

List of Tables Intel® Server Board SE7505VB2

<This page intentionally left blank>

Revision 1.2

xii

Intel part number C32194-002

Page 13

Intel® Server Board SE7505VB2 Introduction

1. Introduction

The Intel® Server Board SE7505VB2 Technical Product Specification (TPS) provides technical

details for the server board’s functional architecture and feature set. It also provides a high-level

detail of some of the board’s functional sub-systems.

This document is intended to be the technical reference for this board. Updates to this

document will be made via the Specification Update published monthly from the date of product

launch. Please refer to the Intel Server Board SE7505VB2 support website for any updates to

this document: http://support.intel.com/support/motherboards/server/se7505vb2

.

Revision 1.2

Intel part number C32194-002

13

Page 14

SE7505VB2 Server Board Overview Intel® Server Board SE7505VB2

2. SE7505VB2 Server Board Overview

The Intel® Server Board SE7505VB2 is a monolithic printed circuit board with features that were

designed to support the general purpose, pedestal server market and meet the needs of a high

end workstation system as well. The architecture is based around the Intel

is capable of supporting one or two Intel

®

Xeon™ processors with 512KB L2 cache and up to

8GB of memory.

2.1 Intel® Server Board SE7505VB2 Feature Set

The Intel Server Board SE7505VB2 supports the following feature set:

Processor/FSB support

- Dual Intel Xeon processors with 512KB L2 cache using the 604-pin FCPGA

processor package

- 533 MHz FSB or 400 MHz FSB support

- 4.2 GB/sec Bus Bandwidth

- One version 9.1 compliant VRD to supply CPU core voltage

Intel E7505 chipset components

- MCH memory controller

- P64H2 64-bit I/O Hub

- ICH4 I/O controller

- FWH Firmware Hub

Glue4-PAL

Support for up to four DDR266 compliant ECC DDR DIMMs providing up to 8 GB of

memory

Three separate and independent PCI buses:

- Segment A: Two PCI 32-bit/33-MHz, 5 V connectors supporting full length PCI add-in

cards and three embedded devices:

• 2D/3D graphics controller: ATI Rage XL video controller with 8 MB of SDRAM

• One Intel 10/100 82550PM Fast Ethernet Controller

• Dual port Serial ATA controller: Silicon Image 3112A

- Segment B: Two PCI-X 64-bit/100-MHz, 3.3 V slots supporting full length PCI / PCI-X

add-in cards

- Segment C: One PCI 64-bit/66-MHz, 3.3 V slot supporting full length PCI add-in

cards and one embedded component:

• Intel 82540EM 10/100/1000 gigabit Ethernet controller

LPC (Low Pin Count) bus segment with two embedded devices:

- Super I/O (sIO) controller chip, Winbond* 83627HF, providing all PC-compatible I/O

(floppy, serial, keyboard, mouse, parallel) and integrated hardware monitoring

- Flash ROM device for system BIOS: Intel 8 megabit N82802AC Flash ROM

®

E7505 chipset and

Revision 1.2

14

Intel part number C32194-002

Page 15

Intel® Server Board SE7505VB2 SE7505VB2 Server Board Overview

Graphic AGP 3.0 Pro50 watt support

- Support 2X, 4X and 8X AGP protocol

- AGP Pro50 supported by additional power pins in 4X and 8X mode

- Support 1.5V signal levels only

- Maximum of 2.03 GB/sec Bus Bandwidth

Three external Universal Serial Bus (USB) ports with an additional internal header

providing one optional USB ports for front panel support.

Two IDE connectors, supporting up to four ATA-100 compatible devices

Support for up to four system fans and two processor fans

SSI-compliant connectors for SSI interface support: front panel and power connectors.

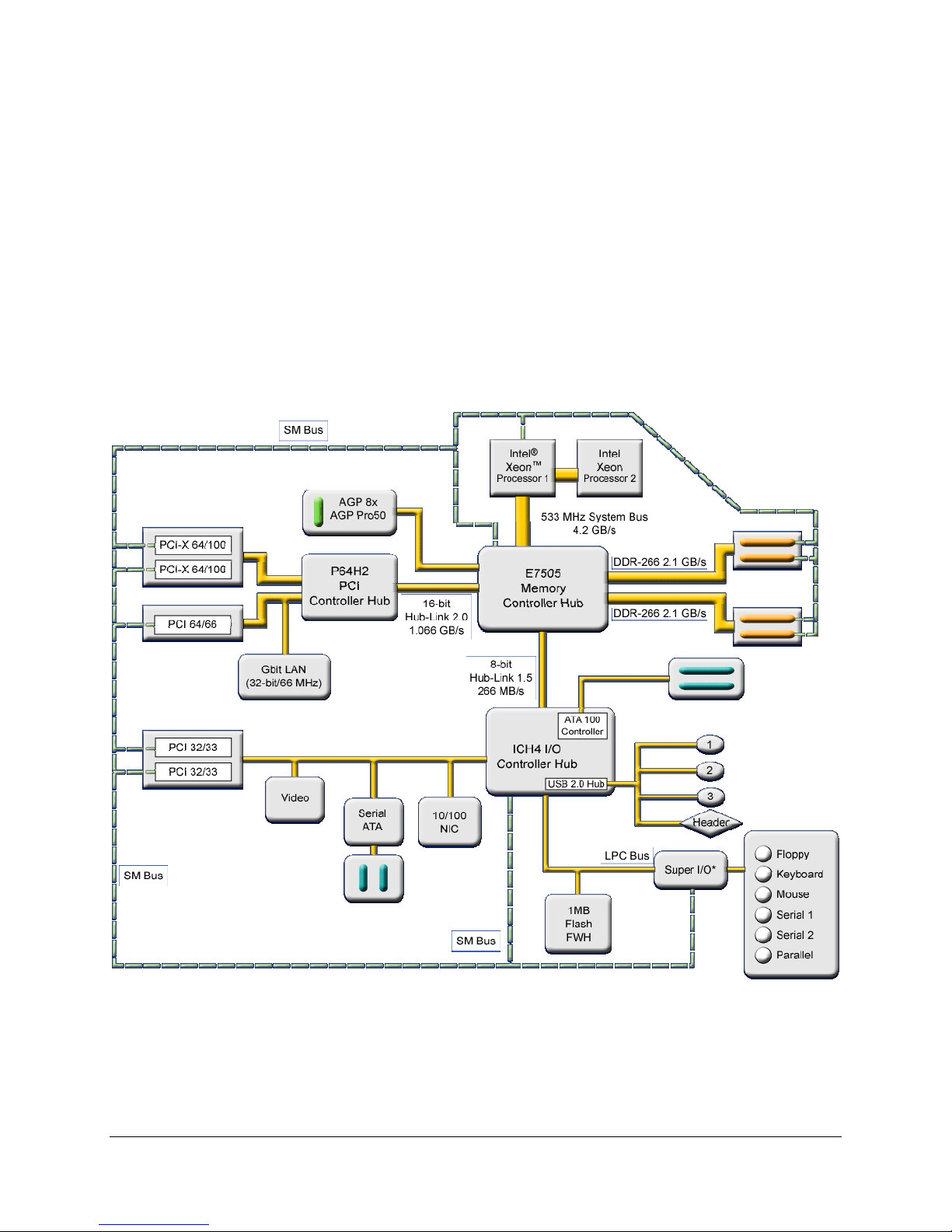

The following figure below shows the functional blocks of the server board and the plug-in

modules that it supports.

Revision 1.2

Intel part number C32194-002

Figure 1. The Board Block Diagram

15

Page 16

Functional Architecture Intel® Server Board SE7505VB2

3. Functional Architecture

This chapter provides a high-level description of the functionality distributed between the

architectural blocks of the Intel

®

Server Board SE7505VB2.

3.1 Processor and Memory Subsystem

The Intel® chipset E7505 provides a 36-bit address, 64-bit data processor host bus interface,

operating at 533 MHz in the AGTL+ signaling environment. The MCH component of the chipset

provides an integrated memory controller, an 8-bit hub interface, and one 16-bit hub interfaces.

The hub interface provides the interface to two 64-bit/100-MHz PCI-X buses and one 64-bit/66MHz PCI bus via the P64H2, and the interface to two 32-bit/33-MHz PCI buses via the ICH4.

The board directly supports up to 8 GB of ECC memory, using four DDR266 compliant ECC

DIMMs. The ECC implementation in the MCH can detect and correct single-bit errors (SBE),

detect multiple-bit errors (MBE), and supports Intel

SDDC) feature with x4 DIMMs.

3.1.1 Processor Support

The Intel Server Board SE7505VB2 supports one or two processors in the 604-pin FCPGA

package. When two processors are installed, all processors must be of identical revision, core

voltage, and bus/core speed. When only one processor is installed, it should be in the socket

labeled CPU1 and the other socket must be empty. The support circuitry on the server board

consists of the following:

®

x4 Single Data Device Correction (Intel x4

Dual 604-pin processor sockets supporting 533MHz FSB Intel Xeon processors.

Processor host bus AGTL+ support circuitry.

Table 1. Processor Support Matrix

Processor Family Package Type Frequency Cache Size Front Side Bus Speed

Intel Xeon FCPGA 3.06GHz 512KB 533

Intel Xeon FCPGA 2.8 GHz 512KB 400 / 533

Intel Xeon FCPGA 2.67 GHz 512KB 400 / 533

Intel Xeon mPGA / FCPGA 2.4 GHz 512KB 400 / 533

Intel Xeon mPGA / FCPGA 2.2 GHz 512KB 400 / 533

Intel Xeon mPGA / FCPGA 2.0GHz 512KB 400 / 533

Intel Xeon mPGA / FCPGA 1.8GHz 512KB 400

Notes:

Processors must be populated in sequential order. Processor socket 1 must be

populated before processor socket 2.

The board is designed to provide up to 65A of current per processor. Processors with

higher current requirements are not supported.

No terminator is required in the second processor socket when using a uni-processor

configuration.

Revision 1.2

16

Intel part number C32194-002

Page 17

Intel® Server Board SE7505VB2 Functional Architecture

In addition to the circuitry described above, the processor subsystem contains the following:

Reset configuration logic

Processor module presence detection logic

Server management registers and sensors

3.1.1.1 Processor VRD

The Intel Server Board SE7505VB2 has a single VRD (Voltage Regulator Down) to support two

processors. It is compliant with the VRM 9.1 specification and provides a maximum of

130 AMPs, which is capable of supporting the requirements for two Intel

®

Xeon™ processors.

The board hardware and PMC (Power Management Controller) must read the processor VID

(voltage identification) bits for each processor before turning on the VRD. If the VIDs of the two

processors are not identical, then the PMC will not turn on the VRD.

3.1.1.2 Reset Configuration Logic

The BIOS determines the processor stepping, cache size, etc through the CPUID instruction.

The requirements are as follows:

All processors in the system must operate at the same frequency, have the same cache

sizes, and same VID. No mixing of product families is supported.

Processors run at a fixed speed and cannot be programmed to operate at a lower or

higher speed.

The processor information is read at every system power-on.

Note: The processor speed is the processor power on reset default value. No manual processor

speed setting options exist either in the form of a BIOS setup option or jumpers.

3.1.1.3 Processor Module Presence Detection

Logic is provided on the baseboard to detect the presence and identity of installed processors.

The PMC checks the logic and will not turn on the system DC power unless the VIDs of both the

processors match in a DP configuration.

3.1.1.4 Interrupts and APIC

Interrupt generation and notification to the processors is done by the APICs in the ICH4 and the

P64H2 using messages on the front side bus.

3.1.2 Memory Subsystem

The baseboard supports up to four DIMM slots for a maximum memory capacity of 8 GB. The

DIMM organization is x72, which includes eight ECC check bits. The memory interface runs at

266MT/s. The memory controller supports memory scrubbing, single-bit error correction and

multiple-bit error detection and Intel x4 SDDC support with x4 DIMMs. Memory can be

implemented with either single sided (one row) or double-sided (two row) DIMMs.

Revision 1.2

Intel part number C32194-002

17

Page 18

Functional Architecture Intel® Server Board SE7505VB2

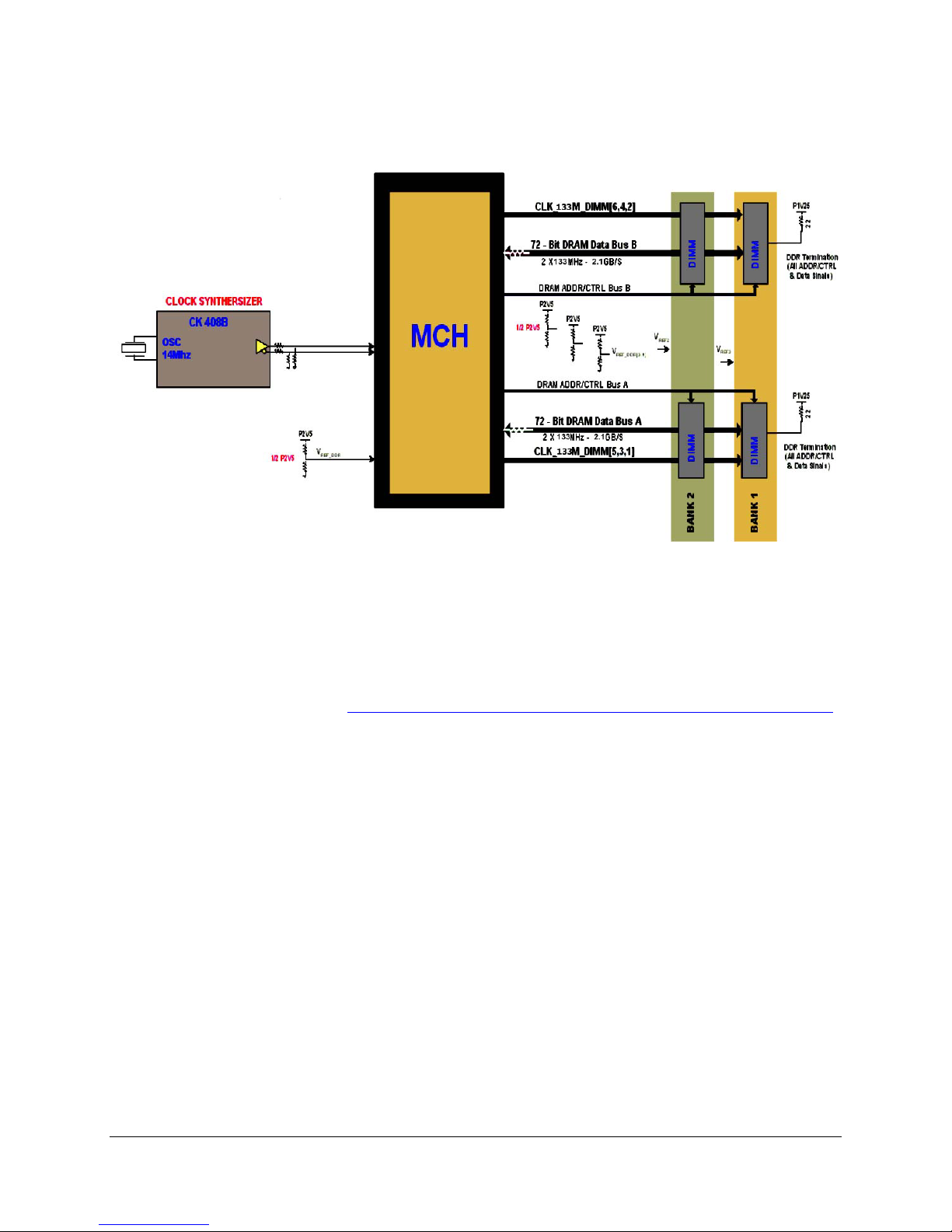

The figure below provides a block diagram of the memory sub-system implemented on the

board.

Figure 2. Memory Sub-system Block Diagram

3.1.2.1 Memory DIMM Support

The board supports DDR266-compliant ECC DIMMS operating at 266MT/s. Only DIMMs tested

and qualified by Intel or a designated memory test vendor are supported on this board. A list of

qualified DIMMs is available at http://support.intel.com/support/motherboards/server/se7505vb2

Note that all DIMMs are supported by design, but only fully qualified DIMMs will be supported on

the board.

The minimum supported DIMM size is 128 MB. Therefore, the minimum main memory

configuration is 1 x 128 MB or 128 MB. The largest size DIMM supported is a 2 GB registered

DDR266 ECC DIMM based on 512 megabit technology. Therefore the maximum main memory

configuration is 4 x 2 GB or 8 GB.

Only registered DDR266 compliant, ECC, DDR memory DIMMs will be supported

ECC single-bit errors (SBE) will be corrected and multiple-bit error (MBE) will be

detected.

Intel server board also supports Intel x4 SDDC with x4 DIMMs.

The maximum memory capacity is 8 GB

The minimum memory capacity is 128 MB

.

Revision 1.2

18

Intel part number C32194-002

Page 19

Intel® Server Board SE7505VB2 Functional Architecture

3.1.2.2 Memory Configuration

The memory interface between the MCH and the DIMMs is 144-bits wide (72-bits for each

bank).

There are two banks of DIMMs, labeled 1 and 2. Bank 1 contains DIMM socket locations 1A and

1B. Bank 2 contains 2A and 2B. The sockets associated with each bank are located next to

each other and the DIMM socket identifiers are marked on the baseboard silkscreen, near the

DIMM socket.

For designs that require a lower price point, a single 128 MB DIMM can be populated in the

DIMM1A socket. When a single DIMM is installed, interleaving and Intel x4 SDDC are not

available. Bank 2 will only operate with two DIMMs installed.

The baseboard’s signal integrity and cooling are optimized when memory banks are populated

in order. Before populating either DIMM socket in bank 2, both DIMMs in bank 1 must be

populated. No empty DIMM sockets are allowed between populated DIMMs.

DIMM and memory configurations must adhere to the following:

DDR266 ECC, registered, DDR DIMM modules

DIMM organization: x72 ECC

Pin count: 184

DIMM capacity: 128 MB, 256 MB, 512 MB, 1 GB, 2GB DIMMs

Serial PD: JEDEC Rev 2.0

Voltage options: 3.3 V (VDD/VDDQ)

Interface: SSTL2

3.1.2.3 Memory Cooling

The SE7505VB2 server board supports DDR memory in a variety of sizes and densities (see

Table 4). Due to the specific orientation of the memory on the SE7505VB2 server board,

certain memory densities and configurations are more difficult to cool in chassis that provide

traditional front to back airflow such as the Intel SC5200 and SC5250-E server chassis. To

ensure the memory used with this board has sufficient thermal margin to operate within

specifications, Intel has designed a memory cooling duct specifically for the SE7505VB2 server

board. Intel’s testing has shown only 2GB and stacked 1GB (low profile) DIMMs are thermally

at risk. If your specific design uses either of these size memory parts, contact Intel Customer

Support and request the SE7505VB2 server board memory cooling duct, part number C28482-

001.

Revision 1.2

Intel part number C32194-002

19

Page 20

Functional Architecture Intel® Server Board SE7505VB2

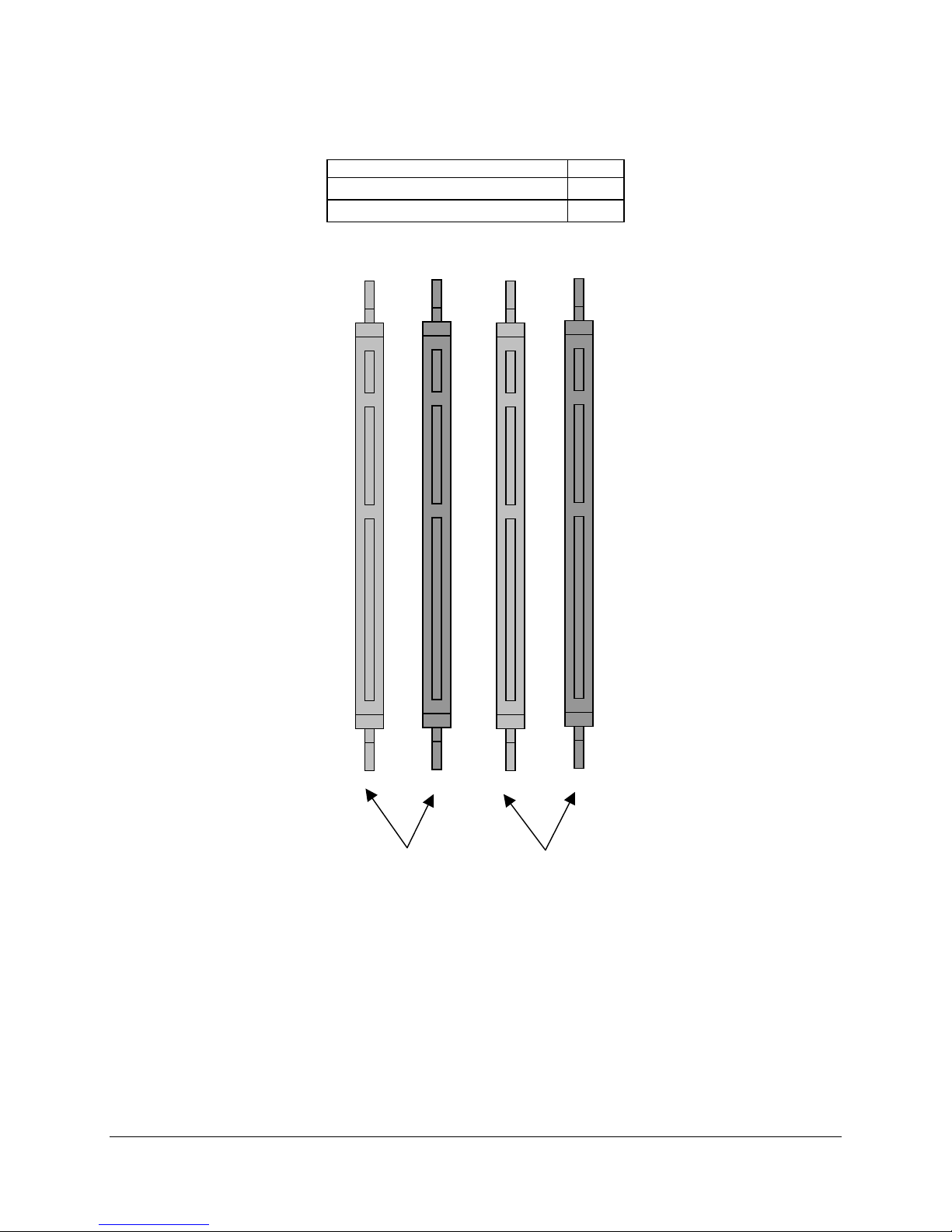

Table 2. Memory Bank Labels

Memory DIMM Bank

J9H1 (DIMM 1A), J9H2 (DIMM 1B) 1

J9J1 (DIMM 2A), J9J2 (DIMM 2B) 2

J9H1 J9H2 J9J1 J9J2

Revision 1.2

20

1A 2A1B 2B

Bank 2

Figure 3. Memory Bank Label Definition

Intel part number C32194-002

Page 21

Intel® Server Board SE7505VB2 Functional Architecture

2

3.1.2.4 I

2

The I

C bus is used by the system BIOS to retrieve DIMM information needed to program the

C Bus

MCH memory registers, which are required to boot the system.

The following table provides the I

Table 3. I2C Addresses for Memory Module SMB

2

C addresses for each DIMM slot.

Device Address

DIMM 1A 0xA0

DIMM 1B 0xA2

DIMM 2A 0xA4

DIMM 2B 0xA6

3.1.2.5 DRAM ECC

The ECC used for DRAM provides Intel x4 SDDC technology for x4 SDRAMs. DRAMs that are

x8 use the same algorithm but will not have Intel x4 SDDC technology, since at most only four

bits can be corrected with this ECC.

The method provides more ECC bits so each ECC word can correct more than a single-bit

failure. This is possible because different mathematical algorithms provide multiple-bit

correction with the right number of data bits and ECC bits. For example, a 144-bit ECC word

that consists of 128 data bits and 16 ECC bits can be used to correct up to 4 bit errors within

certain bit fields of data. These four bits must be adjacent, not random. Even though the ratio of

the ECC bits to data bits is the same as the previous example (16/128 vs. 8/64), the longer ECC

word allows for a correction and detection algorithm that is more efficient.

3.2 The Intel® E7505 Chipset

The Intel Server Board SE7505VB2 is designed around the Intel E7505 chipset. The chipset

provides an integrated I/O bridge and memory controller, and a flexible I/O subsystem core (PCI

/ PCI-X) . This is targeted for multiprocessor systems and standard high-volume servers. The

chipset consists of three components:

MCH: Memory Control Hub. The MCH accepts access requests from the host

(processor) bus and directs those accesses to memory or to one of the PCI buses. The

MCH monitors the host bus, examining addresses for each request. Accesses may be

directed to a memory request queue for subsequent forwarding to the memory

subsystem, or to an outbound request queue for subsequent forwarding to one of the

PCI buses. The MCH also accepts inbound requests from the P64H2 and the ICH4. The

MCH is responsible for generating the appropriate controls to control data transfer to and

from memory.

P64H2: PCI-X 64bit Hub 2.0 I/O Bridge. The P64H2 provides the interface for two PCI-

X buses capable of 133MHz operation. The P64H2 is both master and target on both

buses.

Revision 1.2

Intel part number C32194-002

21

Page 22

Functional Architecture Intel® Server Board SE7505VB2

ICH4: I/O Controller Hub 4. The ICH4 controller has several components. It provides

the interface for a 32-bit/33-MHz PCI bus. The ICH4 can be both a master and a target

on that PCI bus. The ICH4 also includes a USB 2.0 controller and an IDE controller. The

ICH4 is also responsible for much of the power management functions, with ACPI

control registers built in. The ICH4 also provides a number of GPIO pins and has the

LPC bus to support low speed legacy I/O.

The MCH, P64H2, and ICH4 chips provide the pathway between processor and I/O systems.

The MCH is responsible for accepting access requests from the host (processor) bus, and

directing all I/O accesses to one of the PCI buses or legacy I/O locations. If the cycle is directed

to one of the 64-bit PCI segments, the MCH communicates with the P64H2 through a private

interface called the HI (Hub Interface). If the cycle is directed to the ICH4, the cycle is output

on the MCH’s 8-bit HI 1.5 bus. The P64H2 translates the HI 2.0 bus operation to a 64-bit PCI

signaling environment operating between 133 MHz and 33 MHz.

The HI 2.0 bus is 16 bits wide and operates at 66 MHz with 512MT/s, providing over 1 GB per

second of bandwidth.

All I/O for the board, including PCI and PC-compatible I/O, is directed through the MCH and

then through either the P64H2 or the ICH4 provided PCI buses.

The ICH4 provides one 32-bit/33-MHz PCI bus hereafter called P32-A.

The P64H2 provides one 64-bit/100-MHz PCI-X bus, hereafter called P64-B, and one

64bit/66MHz PCI bus, hereafter called P64-C.

This independent bus structure allows all three PCI buses to operate independently and

concurrently providing additional bandwidth to the system.

3.2.1 MCH Memory Architecture Overview

The MCH supports a 144-bit wide memory sub-system that can support a maximum of 8 GB of

DDR266 memory using 2 GB DIMMs. This configuration needs external registers for buffering

the memory address and control signals. The four chip selects are registered inside the MCH

and need no external registers for chip selects.

The memory interface runs at 266MT/s. The memory interface supports a 72-bit or 144-bit wide

memory array. It uses fifteen address lines (BA [1:0] and MA [12:0]) and supports 64 Mb,

128 Mb, 256 Mb, 512 Mb DRAM densities. The DDR DIMM interface supports memory

scrubbing, single-bit error correction, and multiple bit error detection and Intel x4 SDDC with x4

DIMMs.

Revision 1.2

22

Intel part number C32194-002

Page 23

Intel® Server Board SE7505VB2 Functional Architecture

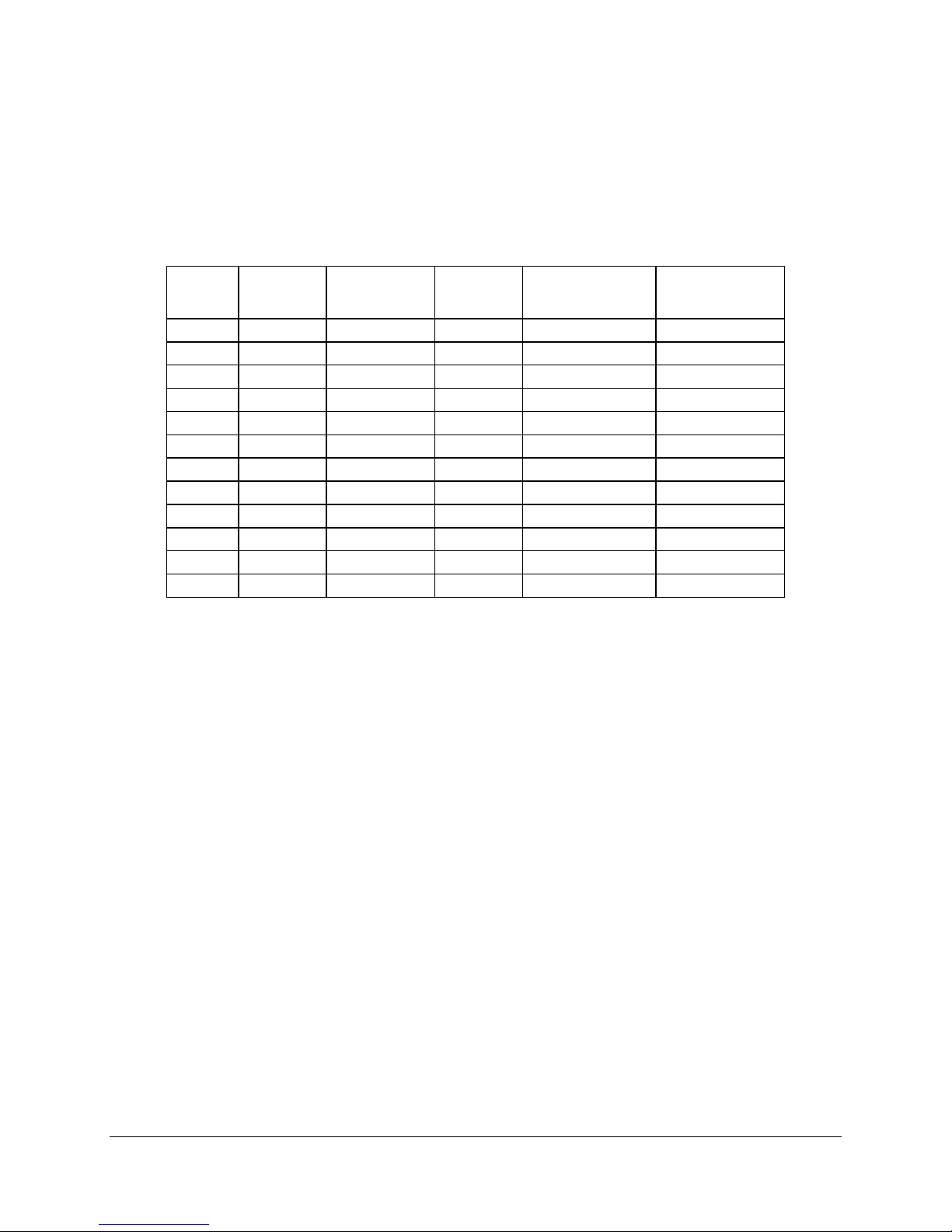

3.2.1.1 DDR Configurations

The DDR interface supports up to 8 GB of main memory and supports single- and doubledensity DIMMs. The DDR can be any industry-standard DDR. The following table shows the

DDR DIMM technology supported.

Table 4. Supported DDRs

DIMM

Capacity

128MB 16M x 72 128Mbit 16M x 8 9/1/4 12/2/10

256MB 32M x 72 64Mbit 16M x 4 36/2/4 12/2/10

256MB 32M x 72 128Mbit 32M x 4 18/1/4 12/2/11

256MB 32M x 72 128Mbit 16M x 8 18/2/4 12/2/10

256MB 32M x 72 256Mbit 32M x 8 9/1/4 13/2/10

512MB 64M x 72 256Mbit 64M x 4 18/1/4 13/2/11

512MB 64M x 72 256Mbit 32M x 8 18/2/4 13/2/10

512MB 64M x 72 512Mbit 64M x 8 9/1/4 13/2/11

1GB 128M x 72 256Mbit 64M x 4 36/2/4 13/2/11

1GB 128M x 72 512Mbit 64M x 8 18/2/4 13/2/11

1GB 128M x 72 512Mbit 128M x 4 18/1/4 13/2/12

2GB 256M x 72 512Mbit 128M x 4 36/2/4 13/2/12

DIMM

Organization

SDRAM Density

SDRAM

Organization

# SDRAM Devices /

Rows / Banks

# Address Bits

Rows / Banks /

Column

3.2.2 Memory Controller Hub (MCH)

The MCH is a 1005-ball FC-BGA device and uses the proven components of previous

generations like the Intel Xeon processor bus interface unit, the hub interface unit, and the DDR

memory interface unit. In addition, the MCH incorporates a hub interface (HI) . The HI interface

allows the MCH to directly interface with the P64H2. The MCH also increases the main memory

interface bandwidth and maximum memory configuration with a 144-bit wide memory interface.

The MCH integrates the following main functions:

An integrated high performance main memory subsystem.

An HI 2.0 bus which provides an interface to the P64H2

An HI 1.5 bus which provides an interface to the ICH4

AGP pro slot: Video controller with 3D/2D graphics accelerator

Other features provided by the MCH include the following:

Full support of ECC on the processor bus

Full support of Intel x4 SDDC on the memory interface with x4 DIMMs

Twelve deep in-order queue, two deep defer queue

Full support of registered DDR266 ECC DIMMs.

Support for 2 GB DDR memory modules

Memory scrubbing

Revision 1.2

Intel part number C32194-002

23

Page 24

Functional Architecture Intel® Server Board SE7505VB2

3.2.2.1 AGP 8X Bus

The AGP 8X bus features include the following:

Single AGP device

AGP interface asynchronously coupled to core

AGP 3.0 specification compliant

AGP 8X / 4X / 2X at 1.5V

0.8V and 1.5V AGP electrical. No 3.3V support

Isochronous support for AGP 8X, non-snooped

32 deep AGP request queue

32-bit upstream address support for inbound AGP and PCI cycles

32-bit downstream address support for outbound PCI and fast write cycles

3.2.3 P64H2

The P64H2 is a 567-ball FC-BGA device that provides an integrated I/O bridge for a highperformance data flow path between the HI 2.0 bus and the 64-bit I/O subsystem. This

subsystem supports peer 64-bit PCI-X segments. Because it has two PCI interfaces, the P64H2

can provide large and efficient I/O configurations. The P64H2 functions as the bridge between

the HI 2.0 interface and the two 64-bit PCI-X I/O segments. The HI interface can support 1GB/s

of data bandwidth.

3.2.3.1 PCI Bus P64-B I/O Subsystem

P64-B supports two 184-pin, 3.3-volt keyed, 64-bit PCI expansion slot connectors running at

100MHz. Both of the slots support 184-pin, 3.3V keyed, 64-bit PCI-X expansion cards. Both

slots support full-length PCI-X or PCI add-in cards.

The BIOS is responsible for setting the bus speed of P64-B. The bus speed runs at the speed of

the slowest card installed.

3.2.3.2 PCI Bus P64-C I/O Subsystem

P64-C supports the following embedded devices and connectors:

One 184-pin, 3.3-volt keyed, 64-bit PCI expansion slot connector running at 66MHz. This

slot is capable of supporting a full-length add-in PCI card

One integrated Intel

®

82540EM fast Ethernet gigabit (10/100/1000) controller

The BIOS is responsible for setting the bus speed of P64-C. The bus speed runs at the speed

of the slowest card installed.

3.2.4 ICH4

The ICH4 is a multi-function device, housed in a 421-pin BGA device, providing a HI 1.5 to PCI

bridge, a PCI IDE interface, a PCI USB controller, and a power management controller. Each

function within the ICH4 has its own set of configuration registers. Once configured, each

appears to the system as a distinct hardware controller sharing the same PCI bus interface.

Revision 1.2

24

Intel part number C32194-002

Page 25

Intel® Server Board SE7505VB2 Functional Architecture

The primary role of the ICH4 is to provide the gateway to all PC-compatible I/O devices and

features. The board uses the following the ICH4 features:

PCI bus interface

LPC bus interface

IDE interface, with Ultra DMA 100 capability

Universal Serial Bus (USB) 2.0 interface

PC-compatible timer/counter and DMA controllers

APIC and 8259 interrupt controller

Power management

System RTC

General purpose I/O (GPIO)

The following are the descriptions of how each supported feature is used on the board .

3.2.4.1 PCI Bus P32-A I/O Subsystem

The ICH4 provides a legacy 32-bit PCI subsystem and acts as the central resource on this PCI

interface. P32-A supports the following embedded devices and connectors:

An ATI Rage XL video controller with 3D/2D graphics accelerator

Silicon Image 3112A dual channel SATA controller

One Intel

Two expansion slots capable of supporting full length PCI add-in cards operating at 33 MHz

®

82550PM network controller

3.2.4.2 PCI Bus Master IDE Interface

The ICH4 acts as a PCI-based Ultra DMA 100 IDE controller that supports programmed I/O

transfers and bus master IDE transfers. The ICH4 supports two IDE channels, supporting two

drives each (drives 0 and 1). The baseboard provides two 40-pin (2x20) IDE connectors to

access the IDE functionality.

The IDE interface supports Ultra DMA 100 Synchronous DMA Mode transfers on each 40-pin

connector.

3.2.4.3 USB Interface

The ICH4 contains three USB 2.0 controllers and four USB hubs. The USB controller moves

data between main memory and up to six USB connectors. All ports function identically and with

the same bandwidth. The SE7505VB2 server board implements four ports on the board.

The baseboard provides three external USB ports on the back of the server board. The triplestack USB connector is located within the standard ATX I/O panel area next to the keyboard

and mouse housing. The USB specification defines the external connectors.

The fourth USB port is optional and can be accessed by cabling from an internal 9-pin

connector located on the baseboard to an external USB port located either in front or the rear of

a given chassis.

Revision 1.2

Intel part number C32194-002

25

Page 26

Functional Architecture Intel® Server Board SE7505VB2

3.2.4.4 Compatibility Interrupt Control

The ICH4 provides the functionality of two 82C59 PIC devices for ISA-compatible interrupt

handling.

3.2.4.5 APIC

The ICH4 integrates an I/O APIC capability with 24 interrupts.

3.2.4.6 General Purpose Input and Output Pins

The ICH4 provides a number of general purpose input and output pins. Many of these pins have

alternate functions, and thus all are not available. The following table lists the GPI and GPO

pins used on the board and gives a brief description of their function.

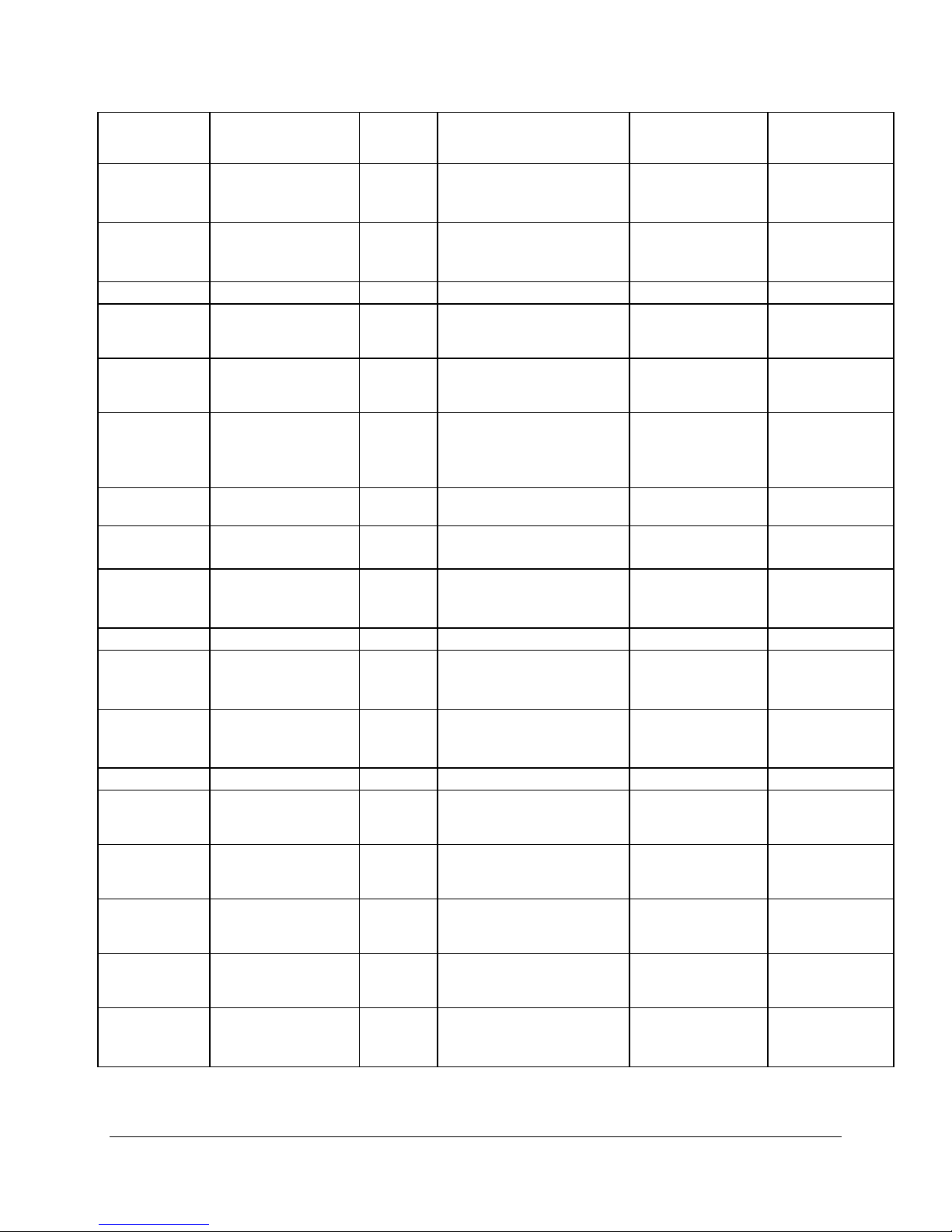

Table 5. ICH4 GPIO Usage Table

Pin Name

(Powe Well)

GPI0 / REQA#

(Core)

GPI1 / REQB#

(Core)

GPI2 / PIRQE#

(Core)

GPI3 / PIRQF#

(Core)

GPI4 / PIRQG#

(Core)

GPI5 / PIRQH#

(Core)

GPI6

(Core)

GPI7

(Core)

GPI8

(Resume)

GPI9 ~ GPI10 N/A

GPI11

(Resume)

Used As GPI /

GPO /

Function

BUS P1 Parity

DETECT

(P1_PERR#)

BUS P2/ICH4 Parity

DETECT

(P2_PERR#)

PIRQ_E GPIO:R00h[2]=0 (PIRQ_E)

PIRQ_F GPIO:R00h[3]=0 (PIRQ_F)

PIRQ_G GPIO:R00h[4]=0 (PIRQ_G)

PIRQ_H GPIO:R00h[5]=0 (PIRQ_H)

IDE ATA66/100

Detect (IDES_DET)

IDE ATA66/100

Detect (IDEP_DET)

CPU_HOT# GPI (GPIO:R04h[8] always = 1)

NC GPI GPIO:R00h[11]=1 (GPIO)

GPI GPIO:R00h[0]=1 (GPIO)

GPI GPIO:R00h[1]=1 (GPIO)

GPI (GPIO:R04h[6] always = 1)

GPI (GPIO:R04h[7] always = 1)

Function Select Data. Pin Description

PM:R2Eh[0] 1: Normal

(GPIO:R04h[0] always = 1)

GPIO:R2Ch[0]=1 (Active

Low)

PM:R2Eh[1] 1: Normal

(GPIO:R04h[1] always = 1)

GPIO:R2Ch[1]=1 (Active

Low)

PM:R2Eh[6] 1: ATA33

GPIO:R2Ch[6]=0 (Active

High)

PM:R2Eh[7] 1: ATA33

GPIO:R2Ch[7]=0 (Active

High)

PM:R2Eh[8] 1: Normal

GPIO:R2Ch[8]=1 (Active

Low)

PM:R2Eh[11]

(GPIO:R04h[11] always = 1)

GPIO:R2Ch[11]=0 (Active

High)

0: SMI or SCI or

Wakeup event

0: SMI or SCI or

Wakeup Event

0: ATA66/100

0: ATA66/100

0: SMI or SCI or

Wakeup Event

Revision 1.2

26

Intel part number C32194-002

Page 27

Intel® Server Board SE7505VB2 Functional Architecture

Pin Name

(Powe Well)

GPI12

(Resume)

GPI13

(Resume)

GPI14 ~ GPI15 N/A

GPO16 /

GNTA#

(Core)

GPO17 /

GNTB#

(Core)

GPO18:19

(Core)

GPO20:23

(Core)

GPIO24

(Resume)

GPIO25

(Resume)

GPIO26 N/A

GPIO27

(Resume)

GPIO28

(Resume)

GPIO29:31 N/A

GPIO32 /

USBLED_A#

(Core)

GPIO33 /

USBLED_B#

(Core)

GPIO34 /

USBLED_C#

(Core)

GPIO35 /

USBLED_D#

(Core)

GPIO36 /

USBLED_E#

(Core)

Used As GPI /

GPO /

Function

Overtemperature

shutdown for CPU 1

& 2

GPI (GPIO:R04h[13] always = 1)

N/C GPO GPIO:R00h[16]=1 (GPIO)

N/C GPO GPIO:R00h[17]=1 (GPIO)

N/C GPO GPIO:R18h[18:19] for

N/C GPO (GPIO:R04h[18:23] always =

N/C GPO GPIO:R04h[24] = 0 GPIO:R0Ch[24] TTL Driver Output

CPU1 SKTOCC# GPI GPIO:R04h[25] = 1

NC GPI GPIO:R04h[27] = 1

NC GPI GPIO:R04h[28] = 1

NC GPI GPIO:R30h[0]=1

CPU2_SKTOCC# GPI GPIO:R30h[1]=1

CPU1_604# GPI GPIO:R30h[2]=1

CPU2_604# GPI GPIO:R30h[3]=1

NC GPO GPIO:R30h[4]=1

GPI (GPIO:R04h[12] always = 1)

Function Select Data. Pin Description

PM:R2Eh[12]

GPIO:R2Ch[12]=0 (Active

High)

PM:R2Eh[13] NC

GPIO:R2Ch[13]=1 (Active

Low)

GPIO:R0Ch[16] TTL Driver Output

(GPIO:R04h[16] always = 0)

GPIO:R0Ch[17] TTL Driver Output

(GPIO:R04h[16] always = 0)

GPIO:R0Ch[18:19] TTL Driver Output

Blinking

(GPIO:R04h[18:19] always =

0)

GPIO:R0Ch[18:23] TTL Driver Output

0)

GPIO:R0Ch[25]

GPIO:R0Ch[25]=0(Active

Low)

GPIO:R0Ch[27]

GPIO:R0Ch[27]=0 (Active

Low)

GPIO:R0Ch[28]

GPIO:R0Ch[28]=0 (Active

Low)

GPIO:R38h[0] 0: present

GPIO:R34h[0]=1

GPIO:R38h[1] 0: present

GPIO:R34h[1]=1

GPIO:R38h[2] 0: CPU1 w/604

GPIO:R34h[2]=1

GPIO:R38h[3] 0: CPU2 w/604

GPIO:R34h[3]=1

GPIO:R38h[4] 0:Disabled

GPIO:R34h[4]=0

1: non-present

1: non-present

1: CPU1 w/603

1: CPU2 w/603

1:Enable

Revision 1.2

Intel part number C32194-002

27

Page 28

Functional Architecture Intel® Server Board SE7505VB2

Pin Name

(Powe Well)

GPIO37 /

USBLED_F#

(Core)

GPIO38 /

USBLED_G#

(Core)

GPIO39 /

USBLED_H#

GPIO40 /

USBLED_I#

GPIO41 /

USBLEDJ

GPIO42 /

USBLED_K#

(Core)

GPIO43 /

USBLED_L#

(Core)

Used As GPI /

GPO /

Function

NC GPO GPIO:R30h[5]=1

RASERR# GPI GPIO:R30h[6]=1

PWR_Alert# GPI GPIO:R30h[7]=1b

AGP_PRST#2 (bit2) GPI GPIO:R30h[8]=1b

AGP_PRST#1 (bit1) GPI GPIO:R30h[9]=1b

DIS_NIC1 GPO GPIO:R30h[10]=1b

NC GPO GPIO:R30h[11]=1b

Function Select Data. Pin Description

GPIO:R38h[5] 0:Disabled

GPIO:R34h[5]=0

GPIO:R38h[5] 0: Disabled

GPIO:R34h[6]=1

GPIO:R38h[7]

GPIO:R34h[7]=1b

GPIO:R38h[8]

GPIO:R34h[8]=1b

GPIO:R38h[9]

GPIO:R34h[9]=1b

GPIO:R38h[10] 0: Disabled

GPIO:R34h[10]=0b

GPIO:R38h[11]

GPIO:R34h[11]=0b

1:Enable

1: Enabled

1: Enabled

3.2.4.7 Power Management

One of the embedded functions of the ICH4 is a power management controller. This is used to

implement ACPI-compliant power management features. The baseboard does support sleep

states S0, S1, S4, and S5.

3.3 Super I/O

The Winbond 83627HF sIO device contains all of the necessary circuitry to control two serial

ports, one parallel port, floppy disk, PS/2-compatible keyboard and mouse and hardware

monitor controller. The baseboard implements the following features:

GPIOs

Two serial ports

Floppy

Keyboard and mouse

Local hardware monitoring

Wake up control

Revision 1.2

28

Intel part number C32194-002

Page 29

Intel® Server Board SE7505VB2 Functional Architecture

3.3.1 GPIOs

The sIO provides a number of general-purpose input/output pins that the baseboard utilizes.

The following table identifies the pin and the signal name used in the schematic:

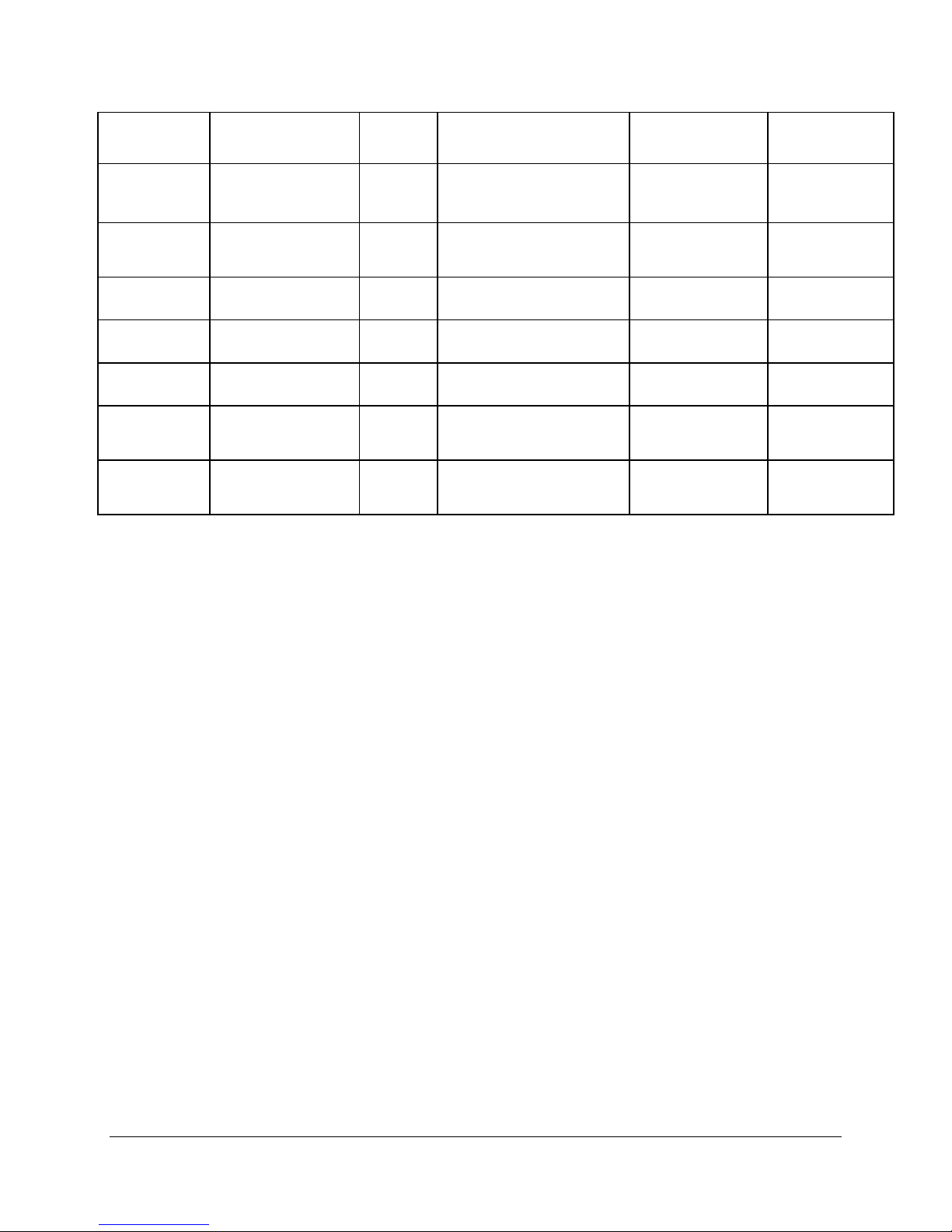

Table 6. Super I/O GPIO Usage Table

Pin

Name

Pin No.

GPIO12

(Pin 126)

GPIO13

(Pin 125)

GPIO15

(Pin 123)

GPIO17

(Pin 121)

GPIO20

(Pin 119)

GPIO25

(Pin 88)

GPIO26

(Pin 87)

GPIO35

(Pin 64)

GPI/GPO

Used as

CLRPAS# GPI

FanSlct1# GPO

FanSlct2# GPO

MAG_jmpr GPI

RECRYMD# GPI

Flash_EN# GPO

Btn_dsabl# GPO

Blink_LED SUSLED

/

Function

Function Select Data Description

CR2A<7>=1 & CR2A<4>=1 & LD7

[F0h]<2>=1

CR2A<7>=1 & CR2A<3>=1 & LD7

[F0h]<3>=0

CR2A<7>=1 & LD7 [F0h]<7>=1 LD7[F1h]<7>

CR2A<0>=1 & LD8[F0h]<0>=1 LD8[F1h]<0>

CR2B<3>=1 & LD8[F0h]<5>=0 LD8[F1h]<5>

CR2B<2>=1 & LD8[F0h]<6>=0 LD8[F1h]<6>

CR29h<7>=0

LD7[F1h]<2>

LD7[F1h]<3>

0: Clear Password

1: Normal

0: Factory mode

1: normal

0: Recovery mode

1:Normal

0: Flash ROM

Write En

1: normal

0: Power button

Disabled

1: normal

3.3.2 Serial Ports

The board provides two serial ports, an external serial port, and an internal serial header. The

following sections provide details on the use of the serial ports.

3.3.2.1 Serial A

Serial A is a standard DB9 interface located at the rear I/O panel of the server board, to the left

of the video connector below the parallel port connector. Serial A is designated by as “Serial A”

on the silkscreen. The reference designator is J8A1.

3.3.2.2 Serial B

Serial B is an optional port, accessed through a 9-pin internal header (J1J2). A standard DH-10

to DB9 cable can be used to direct serial B to an external connector on any given chassis. The

serial B interface follows the standard RS232 pinout. The baseboard has a “Serial B” silkscreen

label next to the connector and is located below the floppy connector.

Revision 1.2

Intel part number C32194-002

29

Page 30

Functional Architecture Intel® Server Board SE7505VB2

3.3.2.3 Floppy Disk Controller

The floppy disk controller (FDC) in the sIO is functionally compatible with floppy disk controllers

in the DP8473 and N844077. All FDC functions are integrated into the sIO including analog data

separator and 16-byte FIFO. The baseboard provides a standard 34-pin interface for the floppy

disk controller.

3.3.2.4 Keyboard and Mouse

Two external PS/2 ports, located on the back of the baseboard, are provided to access the

keyboard or mouse functions. The two ports are interchangeable and will automatically detect

and configure a keyboard or mouse plugged into either port.

3.3.2.5 Wake-up Control

The sIO contains functionality that allows various events to control the power-on and power-off

the system.

3.3.3 BIOS Flash

The board incorporates an Intel® N82802AC (FWH8) flash memory component. The N82802AC

is a high-performance 8-megabit memory component that provides 1024K x 8 of BIOS and nonvolatile storage space. The flash device is connected through the LPC Bus from the ICH4 from

the sIO.

Revision 1.2

30

Intel part number C32194-002

Page 31

Intel® Server Board SE7505VB2 Clock Generation and Distribution

4. Clock Generation and Distribution

All buses on the Intel Server Board SE7505VB2 operate using synchronous clocks. Clock

synthesizer/driver circuitry on the baseboard generates clock frequencies and voltage levels as

required, including the following:

100 MHz at 3.3 V logic levels. For Processor 0, Processor 1, Debug Port and MCH.

66 MHz at 3.3 V logic levels: For MCH, ICH4, AGP, and P64H2

48 MHz at 3.3V logic levels: For ICH4

33 MHz at 3.3V logic levels: For ICH4, PCI Connector, sIO and FWH

14.318 MHz at 2.5 V logic levels: For ICH4 and sIO

The following figure illustrates clock generation and distribution on the board.

Revision 1.2

Intel part number C32194-002

31

Page 32

Clock Generation and Distribution Intel® Server Board SE7505VB2

Figure 4. SE7505VB2 Clock Distribution Diagram

Revision 1.2

32

Intel part number C32194-002

Page 33

Intel® Server Board SE7505VB2 PCI I/O Subsystem

5. PCI I/O Subsystem

5.1 PCI Subsystem

The primary I/O bus for the server board SE7505VB2 is PCI, with three independent PCI bus

segments. The PCI buses comply with the PCI Local Bus Specification, Rev 2.3. The P32-A bus

segment is directed through the ICH4 while the two 64-bit segments, P64-B and P64-C, are

directed through the P64H2 I/O Bridge. The table below lists the characteristics of the three PCI

bus segments.

Table 7. PCI Bus Segment Characteristics

PCI Bus Segment Voltage Width Speed Type PCI I/O Card Slots

P32-A 5 V 32-bits 33 MHz PCI Two slots, support full-length cards

P64-B 3.3 V 64-bits 100 MHz PCI-X Two slots, support full-length cards

P64-C 3.3 V 64-bits 66 MHz PCI One slot, supports full-length cards

5.1.1 P32-A: 32-bit/33-MHz PCI Subsystem

All 32-bit/33-MHz PCI I/O for the board is directed through the ICH4. The 32-bit/33-MHz PCI

segment created by the ICH4 is known as the P32-A segment. The P32-A segment supports

the following embedded devices and connectors:

Serial ATA controller: Silicon Image* 3112A.

One 10/100 Network Interface Controller: Intel 82550PM Fast Ethernet Controller.

2D/3D Graphics Accelerator: ATI Rage XL Video Controller

The Serial ATA controller and the NIC will each be allocated a GPIO to disable the device. The

video controller will be disabled when an off-board video device is detected in either the AGP or

PCI bus segments

5.1.1.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD[31:16],

which acts as a chip select on the PCI bus segment in configuration cycles. This determines a

unique PCI device ID value for use in configuration cycles. The following table shows the bit to

which each IDSEL signal is attached for P32-A devices and the corresponding device

description.

Table 8. P32-A Configuration IDs

IDSEL Value Device

16 PCI 33MHz Slot 1

17 PCI 33MHz Slot 2

18 ATI Rage XL Video Controller

19

20 SATA controller Silicon Image 3112A

Intel 82550PM Fast Ethernet Controller (NIC1)

Revision 1.2

Intel part number C32194-002

33

Page 34

PCI I/O Subsystem Intel® Server Board SE7505VB2

5.1.1.2 P32-A Arbitration

P32-A supports six PCI devices: the ICH4 and five PCI bus masters (one NIC, one sATA RAID

controller, two PCI slots and one ATI Rage XL video controller). All PCI masters must arbitrate

for PCI access, using resources supplied by the ICH4. The host bridge PCI interface (ICH4)

arbitration lines REQx* and GNTx* are a special case in that they are internal to the host bridge.

The following table defines the arbitration connections.

Table 9. P32-A Arbitration Connections

Baseboard Signals Device

P32_REQ0*/P32_GNT0* PCI 33MHz Slot 1

P32_REQ1*/P32_GNT1* PCI 33MHz Slot 2

P32_REQ2*/P32_GNT2* ATI Rage XL video controller

P32_REQ3*/P32_GNT3* Intel 82550PM Fast Ethernet Controller (NIC1)

P32_REQ4*/P32_GNT4* Silicon Image Serial ATA Controller

5.1.2 P64-B and P64-C: 64-bit/100- or 66-MHz PCI Subsystem

Two peer 64-bit bus segments are directed through the P64H2 I/O Bridge. The first PCI

segment, P64-B, provides two 3.3V 64-bit PCI-X slots capable of 100 MHz operation and

support full-length PCI cards.

The second PCI segment, P64-C, provides a single 3.3V 64-bit PCI slot operating at 66 MHz.

This segment supports full-length PCI cards. P64-C also has an embedded Intel 82540EM fast

Ethernet gigabit controller.

5.1.2.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD[31:16],

which acts as a chip select on the PCI bus segment in configuration cycles. This determines a

unique PCI device ID value for use in configuration cycles. The following table shows the bit to

which each IDSEL signal is attached for P64-B devices and corresponding device description.

Table 10. P64-B Configuration IDs

IDSEL Value Device

17 PCI-X 100MHz Slot 4

18 PCI-X 100MHz Slot 3

Table 11. P64-C Configuration IDs

IDSEL Value Device

17 PCI 66MHz Slot 5

18

Intel 82540EM Fast Ethernet Controller (NIC2)

Revision 1.2

34

Intel part number C32194-002

Page 35

Intel® Server Board SE7505VB2 PCI I/O Subsystem

5.1.2.2 P64-B Arbitration

P64-B supports three PCI masters: two PCI-X slots and the P64H2. All PCI masters must

arbitrate for PCI access using resources supplied by the P64H2. The host bridge PCI interface

(P64H2) arbitration lines REQx* and GNTx* are a special case in that they are internal to the

host bridge. The following table defines the arbitration connections.

Table 12. P64-B Arbitration Connections

Baseboard Signals Device

P64_P_REQ0*/P64_P_GNT0* PCI-X 100MHz Slot 4

P64_P_REQ1*/P64_P_GNT1* PCI-X 100MHz Slot 3

5.1.2.3 P64-C Arbitration

P64-C supports three PCI masters: one PCI slot, Intel 82540EM controller and the P64H2. All

PCI masters must arbitrate for PCI access, using resources supplied by the P64H2. The host

bridge PCI interface (P64H2) arbitration lines REQx* and GNTx* are a special case in that they

are internal to the host bridge. The following table defines the arbitration connections.

Table 13. P64-C Arbitration Connections

Baseboard Signals Device

P64_S_REQ0*/P64_S_GNT0* PCI 66MHz Slot 5

P64_S_REQ1*/P64_S_GNT1* Intel 82540EM Fast Ethenet Controller (NIC 2)

5.2 Serial ATA Controller

The board provides an embedded dual port Serial ATA controller through the use of the Silicon

Image* 3112A ASIC. The Silicon Image 3112A provides a single 32-bit / 33-MHz PCI bus

master interface as a multifunction device, packaged in a 128-pin PQFP. It supports two modes:

base mode and RAID mode.

The Silicon Image 3112A controller supports the following features:

Automatically selects highest available transfer speed for all devices

Supports:

- UDMA up to 150MB/second

- All UDMA and PIO modes

- Up to two SATA devices

- ACPI and ATA/ATAPI6

RAID 0 and 1

On-line mirror rebuilding

RAID set accommodates multiple size HDDs

HDDs function normally when not in RAID sets

Adjustable stripe size for RAID 0

1

1

RAID functionality available under most operating systems. Check the SE7505VB2 support website at

http://support.intel.com/support/motherboards/server/se7505vb2

Revision 1.2

Intel part number C32194-002

for details.

35

Page 36

PCI I/O Subsystem Intel® Server Board SE7505VB2

The baseboard ships with the Silicon Image controller set to Base ATA mode. To switch the

controller to RAID mode, a utility needs to be downloaded from the SE7505VB2 support website

or run from the resource CD. This utility switches the controller from one mode to the other.

Appropriate drivers need to be loaded, depending on the mode the controller is set to.

This method was chosen over a BIOS F2 setup switch to allow the controller settings to be

maintained in the event of a Clear CMOS operation. If the RAID drivers were loaded and a

Clear CMOS operation was executed, but the device was not reset to RAID mode, the operating

system would not load. Refer to the SE7505VB2 support website for details on which operating

systems support RAID mode.

Note: The onboard NICs need to be enabled for the ATA mode/RAID mode utility to properly

program the device. The utility toggles the Sub-System ID (SSID) in the NIC EEPROM between

two different values. The BIOS will load the appropriate Silicon Image Option ROM based on

the SSID that is set in the NIC EEPROM. The NICs need to be enabled for the BIOS to know

which SSID is set and subsequently which option ROM to load.

When in RAID mode, the Silicon Image controller can support the following RAID levels:

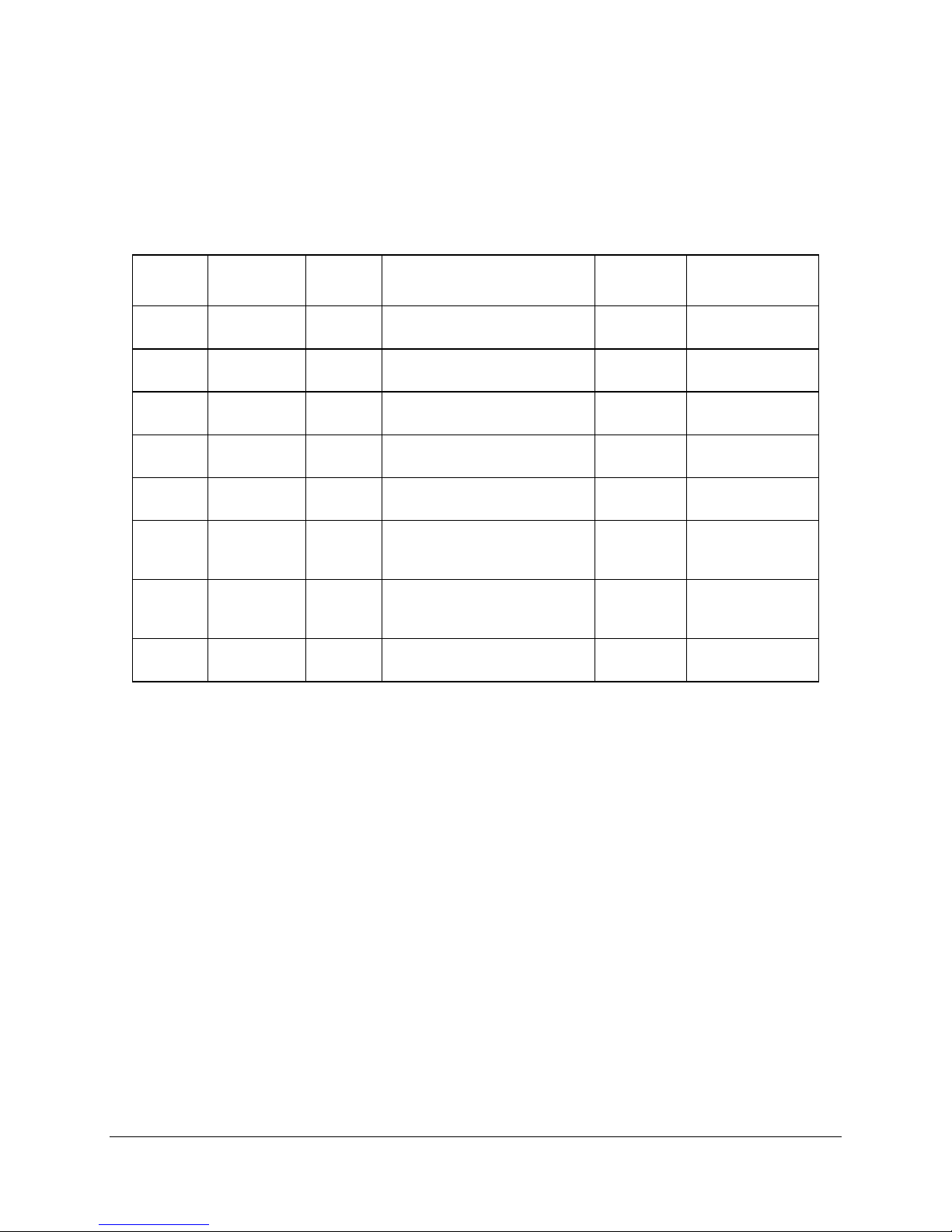

Table 14. sATA RAID Level

RAID Level Performance Capacity # of

Drives

RAID 0 (Striping) Highest Number of drives multiplied

by the smallest drive size

RAID 1

(Mirroring)

Normal 50% min 2

2

RAID 0 configurations are primarily used for high performance applications, as it doubles the

sustained transfer rate of its drives. RAID 1 configurations are primarily used for data protection.

RAID 1 creates an identical backup of the primary drive to a secondary drive. Whenever a disk

write is performed, the controller sends data simultaneously to a second drive located on a

different data channel.

5.3 Video Controller

The baseboard provides an ATI Rage XL PCI graphics accelerator, along with 8 MB of video

SDRAM and support circuitry for an embedded SVGA video subsystem. The ATI Rage XL chip

contains a SVGA video controller, clock generator, 2D and 3D engine, and RAMDAC in a 272pin PBGA. One 2Mx32 SDRAM chip provides 8 MB of video memory.

The SVGA subsystem supports a variety of modes, up to 1600 x 1200 resolution in 8/16/24/32

bpp modes under 2D, and up to 1024 x 768 resolution in 8/16/24/32 bpp modes under 3D. It

supports both CRT and LCD monitors with up to 100 Hz vertical refresh rate.

The baseboard provides a standard 15-pin VGA connector at the rear of the system, in the

standard ATX I/O opening area. The video controller disabled by default in BIOS Setup when an

off-board video adapter is detected in either the AGP or PCI slots. Optionally, the video

controller can be set to support dual monitor mode when an off-board AGP adapter is detected.

The onboard controller would act as the primary video controller and the AGP adapter becomes

the secondary adapter under an operating system that supports this functionality.

Revision 1.2

36

Intel part number C32194-002

Page 37

Intel® Server Board SE7505VB2 PCI I/O Subsystem

5.3.1 Video Modes

The ATI Rage XL chip supports all standard IBM VGA modes. The following table shows the

2D/3D modes supported for both CRT and LCD. The table specifies the minimum memory

requirement for various display resolution, refresh rates and color depths.

Table 15. Video Modes

SE7505VB2 2D Video Mode Support 2D Mode Refresh Rate (Hz)

8 bpp 16 bpp 24 bpp 32 bpp

640x480 60, 72, 75, 90, 100 Supported Supported Supported Supported

800x600 60, 70, 75, 90, 100 Supported Supported Supported Supported

1024x768 60, 72, 75, 90, 100 Supported Supported Supported Supported

1280x1024 43, 60 Supported Supported Supported Supported

1280x1024 70, 72 Supported – Supported Supported

1600x1200 60, 66 Supported Supported Supported Supported

1600x1200 76, 85 Supported Supported Supported –

3D Mode Refresh Rate (Hz) SE7505VB2 3D Video Mode Support with Z Buffer Enabled

640x480 60,72,75,90,100 Supported Supported Supported Supported

800x600 60,70,75,90,100 Supported Supported Supported Supported

1024x768 60,72,75,90,100 Supported Supported Supported Supported

1280x1024 43,60,70,72 Supported Supported – –

1600x1200 60,66,76,85 Supported – – –

3D Mode Refresh Rate (Hz) SE7505VB2 3D Video Mode Support with Z Buffer Disabled

640x480 60,72,75,90,100 Supported Supported Supported Supported

800x600 60,70,75,90,100 Supported Supported Supported Supported

1024x768 60,72,75,90,100 Supported Supported Supported Supported

1280x1024 43,60,70,72 Supported Supported Supported –

1600x1200 60,66,76,85 Supported Supported – –

5.3.2 Video Memory Interface

The memory controller subsystem of the ATI Rage XL arbitrates requests from direct memory

interface, the VGA graphics controller, the drawing coprocessor, the display controller, the video

scalar, and hardware cursor. Requests are serviced in a way that ensures display integrity and

maximum CPU/coprocessor drawing performance.

The board supports an 8 MB (512Kx32bitx4 Banks) SDRAM device for video memory.

Revision 1.2

Intel part number C32194-002

37

Page 38

PCI I/O Subsystem Intel® Server Board SE7505VB2

K

A

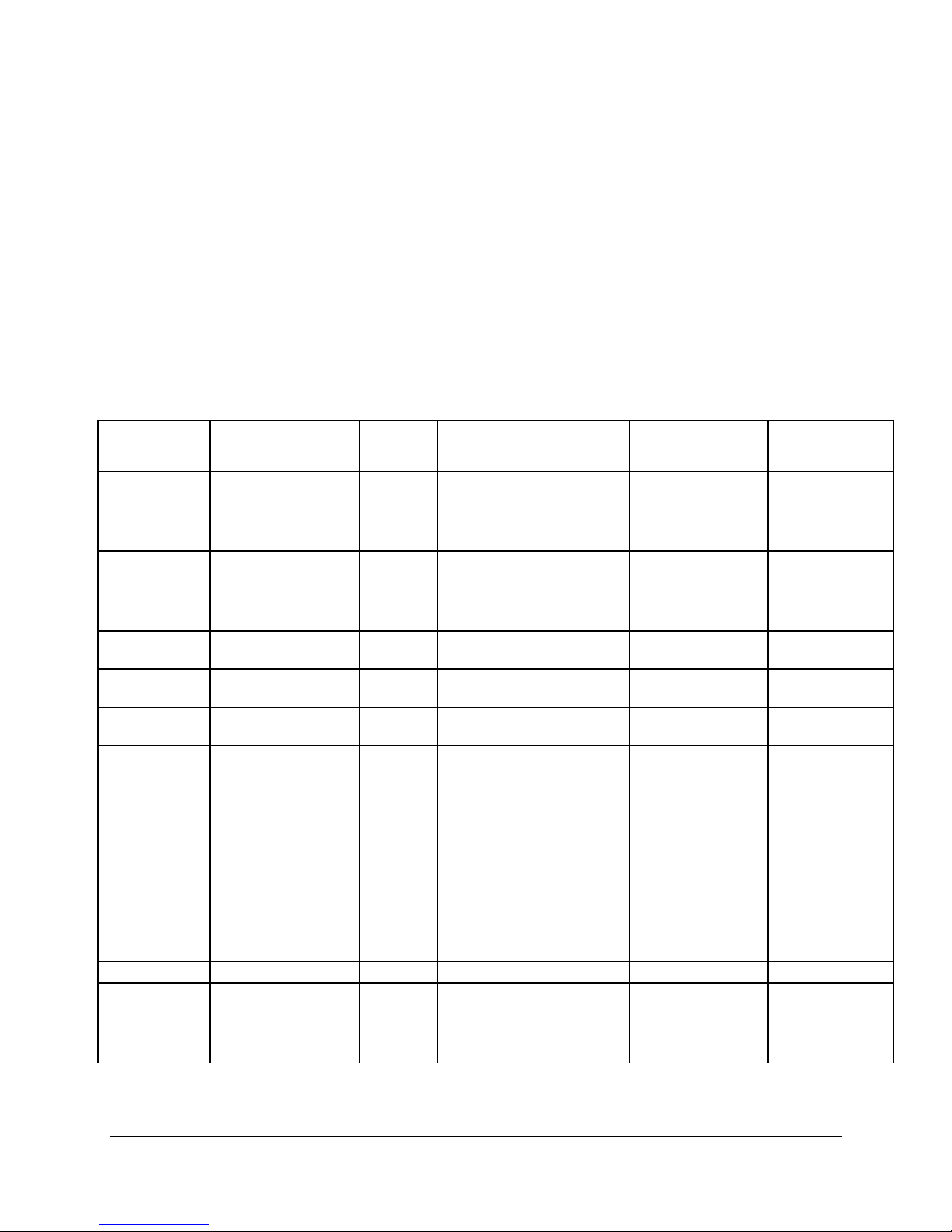

5.3.3 Host Bus Interface

The ATI Rage XL supports a PCI 33 MHz bus. The following diagram shows the signals for the

PCI interface:

PCICL

D[31..0] AD[31..0]