Page 1

iSBC®

546/547/548

HIGH

TERMINAL CONTROLLERS

HARDWARE

Order Number: 122704-001

PERFORMANCE

REFERENCE

MANUAL

I

Intel Corporation,

Copyright

1986,

3065

Intel

Corporation,

Bowers

Avenue,

All

Santa

Rights

Clara,

Reserved

California

95051

r

Page 2

Additional copies

Literature Department

Intel Corporation

3065 Bowers Avenue

Santa Clara,

The

int(lrmation

of

this manual

CA

95051

in

this document

or

other Intclliterature may be obtained from:

is

subject to change without notice.

Intel Corporation makes no warranty

implied warranties

sibility for any

of

merchantability and

errors

that may appear

to keep current the information contained

Intel Corporation assumes no responsibility for the usc

of

any kind with regard to this material. including, but not limited to, the

fitne~s

in

for a particular purpose. Intel Corporation assumes no

this document. Intel Corporation makes no commitment to update nor

in

this dDcument.

of

any circuitry other than circuitry embodied

product. No other circuit patent licenses arc implied.

Intel software

or

disclosure

No part

consent

products arc copyrighted by and shall remain the property

is

subject to restrictions stated

of

this document may be copied

of

Intel Corporation.

in

Inters

or

reproduced

Intel Corporation makes no warranty for the usc

which may appear

in

this document nor docs

it

software license.

in

any form

of

its products and assumes no responsibility for any

make a commitment to update the information contained herein.

of

Intel Corporation. Use, duplication

or

as defined

or

by any means without

in

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your

The

local sales office to ohtain the latest specifications bef()re placing your order.

following are trademarks

of

Intel Corporation and its affiliates and may be used only

products:

Above iLBX

BITBLJS

COMMputer

CREDIT

Data Pipeline lnsite

GENIUS

-'

i

ICICE

ICE

rCEL

iCS

iDBP

iDIS

im

iMDDX

iMMX

Intel

inte

intclBOS

lntelcvision

intc1igcnt

intcligent Programming

lntcllec

Intcllink

iOSP

l

Identifier

iPDS

iPSC

iRMX

iSBC

iSBX

iSDM

iSXM

Library Manager

MCS

Megachassis

MICROMAINFRAME

MLJLTIBUS

MULTICHANNEL

MULTIMODULE

respon~

in

an Intel

ASPR

7~104.9(a)(9).

prior

to

identify Intel

ONCE

OpenNET

Plug~A~Bubblc

PROMPT

Promware

QucX

QUEST

Ripplcmodc

RMX/SO

RUPI

Seamless

SLD

UPI

VLSiCEL

written

errors

MDS is an ordering code only and is not used as a product name or trademark.

of

trademark

*MULTlBlJS

Copyright

11

Mohawk Data Sciences Corporation.

is

a patented Intel bus.

1985, Intel Corporation, All

Righb

Reserved

MDS"

is

a regi,tered

Page 3

REV.

REVISION

HISTORY

DATE

-001

Original Issue.

2/86

iii/tv

Page 4

Page 5

PREFACE

This

Eight

Printer

functionally

(10"

is

printer

General

1.

of

install

4

all

schematic

For

the

In

material

see

manual

Channel

x

a

four

Chapter

the

as

well

boards

reference

boards.

addition

page

Controller.

12")

interface.

information

boards.

the

o

provides

Terminal

identical,

board

channel

2

provides

board.

as

in

is

shown

diagrams

purposes

Appendix

to

(

all

ii

for

Intel

information

The iSBC 548

with

board

about

Chapter

Programming

Appendix

in

see

B

this

are

manual

available

address).

MULTIBUS

about

Controllers

but

the

backpanel

with

a

block

3

Chapter

Chapter

Appendix A provides

covers

a

all

three

diagrams

provides

A

and

the

you

from

Handbook,

and

and

iSBC 547

iSBC 547

connectors

clock

information

B.

5.

6.

will

calendar

boards

the

information

Connector

If

you

board

need

the

Intel

Order

the

iSBC

the

iSBC

boards

is

a

larger

on-board.

and a centronix

is

provided

and

functional

is

provided

pin-out

need

firmware.

the

to

jumper

following

Literature

Number 210883

54B

and

546

Terminal

are

form

The iSBC 546

descriptions

required

information

refer

information

iSBC 547

and

factor

in

Chapter

to

in

Chapter

to

the

for

reference

Department,

for

Microsystem

o

Serial

o

Order

Components

Communications

Number

230834.

Handbook,

Controller

v

Order

Technical

Number 230843

Manual,

Page 6

Page 7

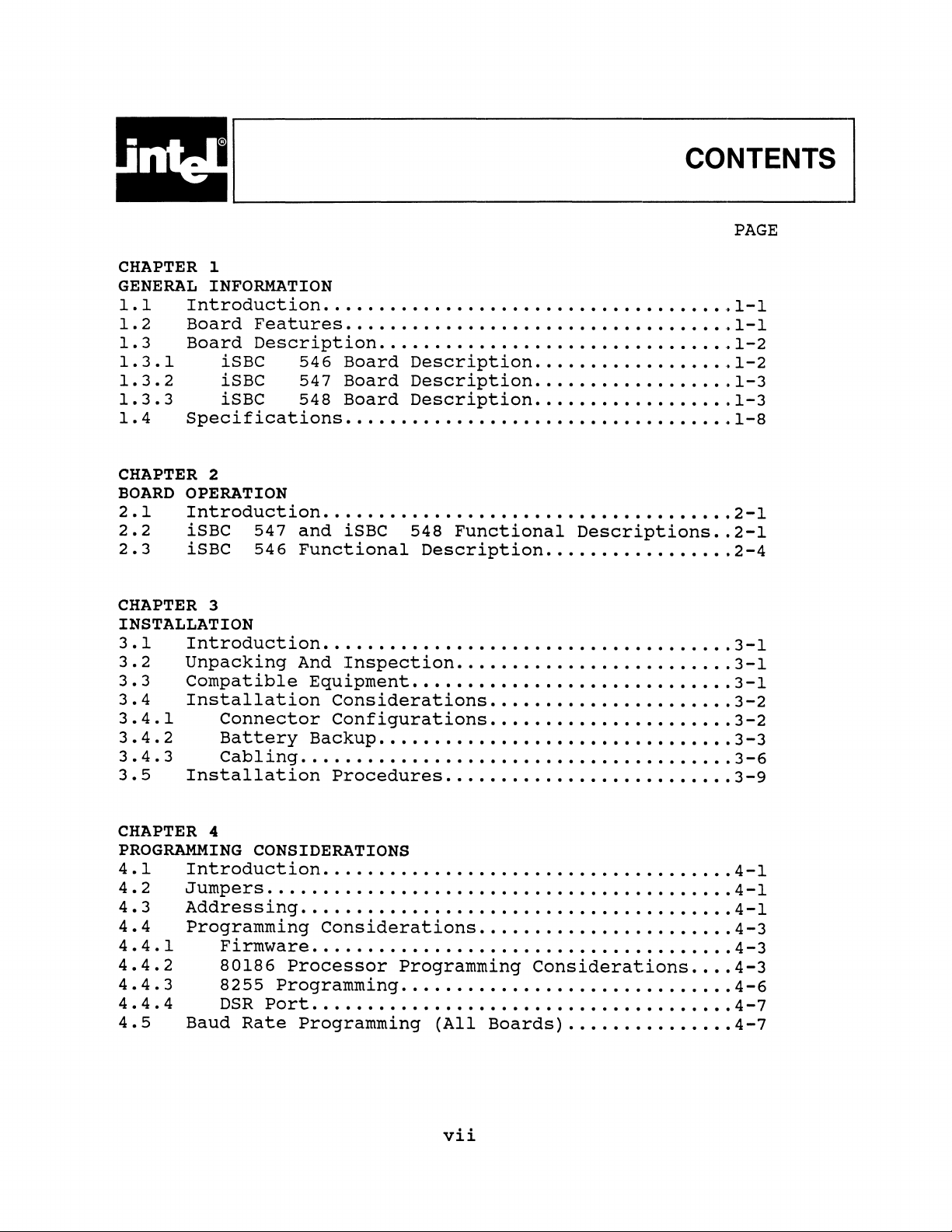

CHAPTER 1

GENERAL

1.

1

1.2

1.3

1.3.1

1.3.2

1.3.3

1.4

CHAPTER 2

BOARD

2 • 1

2.2

2.3

CHAPTER 3

INSTALLATION

3 • 1

3.2

3.3

3.4

3.4.1

3.4.2

3.4.3

3.5

INFORMATION

Introduction

Board

Board

iSBC

iSBC 547

iSBC 548

Specifications

OPERATION

Introduction

iSBC

iSBC

Introduction

Unpacking

Compatible

Installation

Connector

Battery

Cabling

Installation

....................................

Features

Description

546

...................................

................................

Board

Board

Board

...................................

....................................

547

and

iSBC 548

546

Functional

.....................................

And

Inspection

Equipment

Considerations

Configurations

Backup

.......................................

................................

Procedures

Description

Description

Description

..................

..................

..................

Functional

Description

.................

.........................

.......•.....................

......................

......................

..........................

Descriptions

CONTENTS ]

PAGE

"

1-1

l-l

1-2

1-2

1-3

1-3

1-8

"

2-1

..

2-l

2-4

3-1

3-l

3-l

3-2

3-2

3-3

3-6

3-9

CHAPTER 4

PROGRAMMING

4.1

4 • 2

4.3

4.4

4.4.1

4.4.2

4.4.3

4.4.4

4.5

Introduction

Jumpers

Addressing

Programming

Firmware

80186

8255

DSR

Baud

CONSIDERATIONS

.....................................

..........................................

.......................................

Considerations

......................................

Processor

Programming

Port

Rate

......................................

Programming

Programming

..............................

(All

.......................

Considerations

Boards)

vii

...............

....

4-1

4-1

4-1

4-3

4-3

4-3

4-6

4-7

4-7

Page 8

CONTENTS

CHAPTER 5

INTERFACING

5.1

5.2

5.3

5.4

CHAPTER 6

SERVICE ASSISTANCE INFORMATION

6

-1

6-2

6-3

APPENDIX A

JUMPER INFORMATION

A.1

A.2

A.3

A.4

Introduction

MULTI

serial

Printer

Introduction

Service

Service

Introduction

Flag

MULTIBUS

Memory

INFORMATION

....

BUS

Information

Interfaces

InterfaCE~

......................................

and

Repair

Diagrams

......................................

Byte

Address

Interrupt

Mapping

to

•••••••••••••••••••••••••••••••

...........................

................................

(iSBC

Assistance

..................................

Jumpers

Jumpers

Jumpers

...........................

(continued)

546

Only)

...............

....................

........................

.....................

PAGE

•

5-1

5-1

5-6

5-11

6-1

6-1

6-3

A-1

A-4

A-5

A-5

APPENDIX B

FIRMWARE

B.1

B.2

B.2.1

B.2.2

B.3

B.3.1

B.3 . 1.

Introduction

Firmware

Firmware

Recommendations

Functional

structures

1

B.3.1.2

B.3.1.3

B . 3 . 1 . 4

B.3.1.5

B.3.1.6

B.3.2

Inter-Processor

B.3.2.l

B.3.2.1.1

B.3.2.1.2

B.3.2.1.3

B.2.2.1.4

B.3.2.1.5

B.3.2.1.6

B.3.2.1.7

B.3.2.1.8

......................................

Overvie'iliT

Operation

................................

............................

For

Architecture

of

Test

EnginE~ering

static

Dynamic

Queue.

Receive

Transmit

Dual

Structures

Structures

. . . . " . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Buffers

Buffers

Ported

............................

...........................

Messages

Host

CPU

to

Controller

Initialize

Enable

Disable. ~ ........................

Conf

igurE~

Transmit

Abort

Suspend

Resume

...............................

..

~I

••••••••••••••••••••••

......................

Buffer

Transmit

...........................

Transmit

Transmit

High

Performance

..........................

RAM

.................

Boot

Area

.................

..........................

.........................

......................

Messages

..........................

...............

................

..........

............

"

•••••••••

'

........

"

.........

"

.........

"

.........

B-1

B-1

B-4

B-5

B-6

B-6

B-7

B-8

B-10

B-1

B-11

B-11

B-11

B-ll

B-12

B-13

.

B-14

B-15

B-20

B-2

B-23

B-24

0

2

viii

Page 9

TABLEfJ

(continued)

3-2

5-1

5-2

5-3

5-4

5-5

5-6

5-7

5-8

A-l

A-2

A-3

A-4

B-1

B-2

1-1

1-2

1-3

1-4

2-1

2-2

3-1

3-2

3-3

3-4

4-1

6-1

6-2

6-3

6-4

A-l

A-2

A-3

B-1

B-2

B-3

B-4

B-5

B-6

Pin

to

Pin

MULTI

MULTI

BUS

BUS

Connector

Serial

Connectors

Board

Serial

Connectors

Board

Serial

Connectors

Board

Printer

Connector

Jumper

Jumper

Flag

Memory

iSBC

Combinations

Combinations

Byte

Map

546/547/548

Confidence

iSBC

Block

iSBC

iSBC

iSBC

iSBC

iSBC

iSBC

iSBC

iSBC

iSBC

iSBC

546,

Diagram

548

547

548

547

546

546

547

548

548

546/547/548

Territorial

iSBC

iSBC

iSBC

iSBC

iSBC

iSBC

548

547

546

546

547

548

Layout

Test

Engineering

static

Dynamic

Layout

Initialize

Wiring

Connector

Connector

P2

Pin

Interface

J5

Signal

Address

jumpers

Test

iSBC

High

High

High

and

Functional

Board

Board

Board

RS232

Service

Schematic

Schematic

Schematic

Board

Board

Board

of

Shared

Structure

Structure

of

Queue

Message

List

•.....•.......•..•.•...•....

Pl

Pl

Assignments

Pin

Assignments,

Pin

A!;signments,

Pin

Assignments,

Connec:::tor

Desc:::riptions

iSBC

iSBC

options

and

Addresses

Firmware

Result

547

Codes

FIGUlRES

and

Performance

Performance

Performance

iSBC

548

BLock

Connector

Connector

Connector

Cable

Construction

Boards

Telephone

Diagram

Diagram

Diagram

Jumper

Jumper

Jumper

(Dual

Boot

Area

Area

Layout

Layout

Area

.............................

Format

Pin

Assignments

Signal

Descriptions

......................

J5

Pin

..................

546

Boards

547/548

And

Boards

Jumpers

..................

Features

..•..........•........

iSBC

548

Terminal

Terminal

Terminal

Functional

Diagram

Locations

Locations

Locations

Memory

Map

Numbers

......................

......................

......................

Location

Location

Location

Port)

..................

..................

..................

Memory

Layout

................

.....................

.........................

........................

......•....

.......

iSBC

iSBC

iSBC

546

547

548

......

......

......

Assignments

.....••.......

..........

.............

...............

Boards

........

Controller

Controller

Controller

Block

Diagram.2-2

...............

.............

..............

..............

...............

..............

............

..............

....

...

...

...

3-7

5-l

5-3

5-5

5-6

5-7

5-9

5-ll

5-12

A-l

A-3

A-4

A-6

B-2

B-59

1-5

1-6

1-6

1-7

2-6

3-4

3-5

3-6

3-8

4-2

6-2

6-4

6-l5

6-27

A-7

A-8

A-9

B-6

B-7

B-9

B-10

B-10

B-12

x

Page 10

FIGURES

(continued)

PAGE

B-7

B-8

B-9

B-10

B-11

B-12

B-13

B-14

B-15

B-16

B-17

B-18

B-19

B-20

B-21

B-22

B-23

B-24

B-25

B-26

B-27

B-28

B-29

B-30

B-31

B-32

B-33

B-34

B-35

B-36

B-37

B-38

B-39

Enable

Disable

Message

Message

Configure

Transmit

Abort

Suspend

Resume

Assert

Set

CTS

Clear

Set

DSR

Clear

Set

RI

Clear

Clear

Set

Break

Clear

Download

Execute

Clear

Transmit

Input

Download

Carrier

Carrier

Buffer

Transmit

Transmit

Transmit

DTR

and

CTS

Report

DSR

Report

RI

Report

DTR

Break

Message

Command

Receive

Complete

Available

Complete

Detect

Loss

Initialization

Autobaud

Special

DSR

Detected

DSR

Lost

RI

Detected

RI

Lost

EPROM

Complete

Character

Message

Message

Checksum

F0rIl1at

Format

Message

Message

Message

Message

Message

CD

GatE~s

and

CD

Message

Report

Message

Message

Message

Message

Message

Message

Buffer

message

Message

Message

Responses

Message

Message

Format

.... " ..............................

...................

..................

Pormat

Format

Message

Format

Message

Gates

Message

Format

Message

Format

Format

Format

Format

Format

Command

Message

'Message

Format

Format

Message

Received

Format

Format

Format

...........................

................

Format

..........

...........

Format

Format

.........

..........

•..............

Format

.....

Format

...........

Format

•........

............

Format

..........

................

................

.......................

.................

Format

...................

Message

Format

Format

Format

.................

...................

.................

....................

.....••.•.............

Message

Format

Message

Format

.................

Format

......................

..........................

.......................

"

........

"

........

"

........

"

........

"

........

"

........

"

........

"

........

"

........

... " ........

"

........

"

........

'

.........

'

.........

,

.........

'

.........

'

.........

Format

......

..........

........

B-13

B-14

B-15

B-21

B-22

B-23

B-24

B-25

B-2 6

B-27

B-28

B-29

B-3 0

B-31

B-32

B-3 3

B-34

B-3 7

B-38

B-40

B-41

B-43

B-44

B-45

B-46

B-47

B-48

B-49

B-50

B-51

B-52

B-53

B-60

xi

Page 11

Page 12

CHAPTER

1

1.1

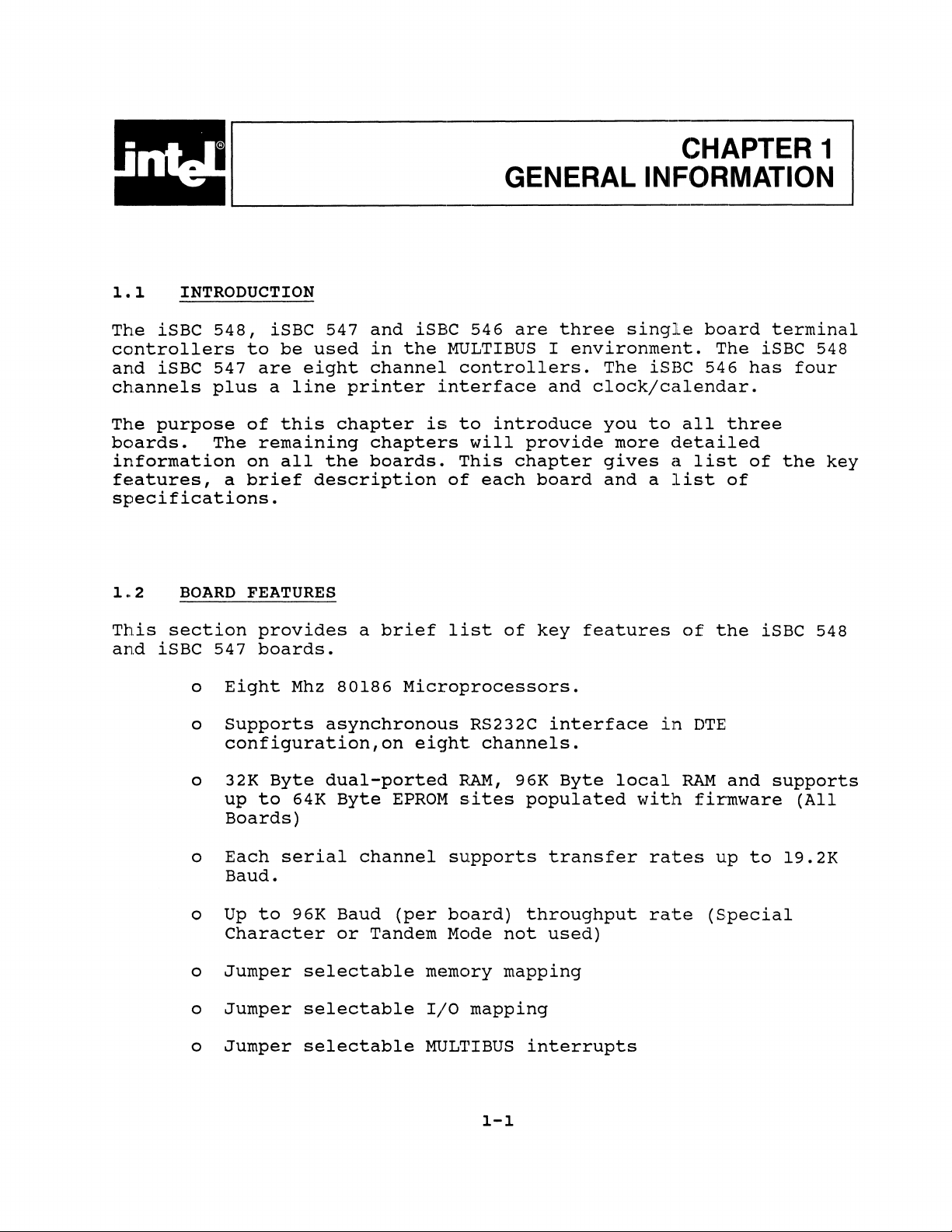

The iSBC

INTRODUCTION

548,

controllers

and

iSBC 547

channels

The

purpose

boards.

plus

The

information

features,

a

specifications.

1.2

This

and

BOARD

section

iSBC 547

iSBC 547

to

be

used

are

eight

a

line

of

this

remaining

on

all

the

brief

FEATURES

description

provides

boards.

and

in

channel

printer

chapter

chapters

boards.

a

brief

GENERAL

iSBC 546

the

MULTIBUS I environment.

controllers.

i.nterface

is

to

This

of

list

are

introduce

will

chapter

each

of

three

and

provide

board

key

features

clock/ca.lendar.

INFORMATION

single

The iSBC 546

you

to

more

gives

and a list

board

The iSBC 548

all

three

detailed

a.

list

of

of

the

terminal

has

four

of

the

iSBC 548

key

o

Eight

o

Supports

Mhz

configuration,on

o 32K

up

Byte

to

64K

Boards)

o

Each

serial

Baud.

Up

to

0

96K

Character

Jumper

0

0

Jumper

0

Jumper

80186

asynchronous

dual-ported

Byte

EPROM

channel

Baud

or

Tandem

selectable

selectable

selectable

Microprocessors.

RS232C

eight

channels.

B~,

sites

96K

populated

supports

(per

board)

Mode

memory

I/O

MUL'l'IBUS

mapping

throughput

not

mapping

interrupts

1-1

interface

Byte

local

transfer

used)

in

with

rates

rate

DTE

RAM

and

:i:irmware

up

to

(Special

supports

(All

19.2K

Page 13

The

iSBC

follows:

o

546

o

o

o

The

iSBC

on-board

board

Four

Line

channels

printer

Clock

547

backpanel

differs

calendar

GENERAL

is

a

10"x

connectors.

from

of

RS232C

interface

with

:rNl~ORMATION

12"

the

instead

battery

form

iSBC

factor

548

of

back-up

and

eight

board

iSBC

channels

with

548

boards

as

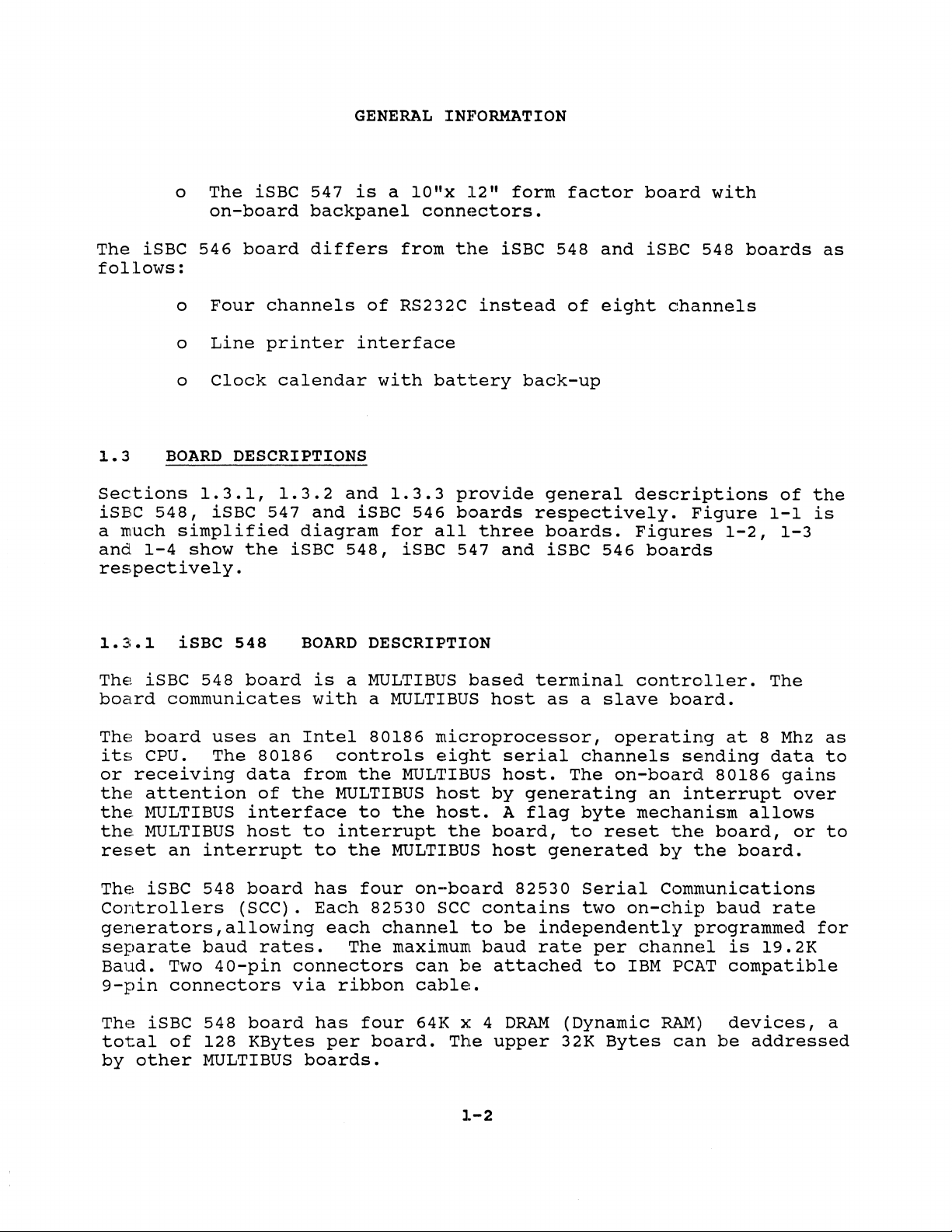

1.3

BOARD

sections

iSBC

a

and

548,

much

1-4

simplified

show

respectively.

1.3.1

ThE:

boa.rd

The

its

or

the

the

the

reset

The:

iSBC

iSBC

communicates

board

cpu.

receiving

attention

MULTIBUS

MULTIBUS

an

iSBC

Controllers

generators,

separate

Baud.

9-pin

Two

connectors

DESCRIPTIONS

1.3.1,

iSBC

the

1.3.2

547

iSBC

548

548

board

uses

The

an

80186

data

of

the

interface

host

interrupt

548

board

(SCC).

allowing

baud

rates.

40-pin

and

and

iSBC

diagram

548,

BOARD

is

with

Intel

DESCRIPTION

a MULTIBUS

a MULTIBUS

80186

controls

from

the

MULTI

to

to

interrupt

to

the

has

four

Each

82530

each

The

connectors

via

ribbon

1.3.3

for

iSBC

546

all

provide

boards

three

547

based

host

microprocessor,

eight

MUL'TIBUS

BUS

host

the

host.

MULTIBUS

the

by

board,

host

on-·board

SCC

contains

channE~l

maximum

can

to

baud

be

attached

cable.

general

respectively.

boards.

and

iSBC

terminal

as

serial

host.

The

generating

A

flag

generated

82530

be

independently

rate

546

a

slave

operating

channels

on-board

byte

to

reset

Serial

two

per

to

descriptions

Figure

Figures

boards

con1:roller.

boa.rd.

sending

80186

an

interrupt

mechanism

thE!

board,

by

the

Communications

on-chip

baud

programmed

channel

IBM

PCAT

of

1-1

1-2,

1-3

The

at

8 Mhz

data

gains

over

allows

or

board.

rate

is

19.2K

compatible

the

is

as

to

to

for

ThE!

total

by

iSBC

of

other

548

board

128

KBytes

MULTIBUS

has

per

boards.

four

board.

64K x 4

The

J.-2

DRAM

upper

(Dynamic

32K

Bytes

RAM)

can

devices,

be

addressed

a

Page 14

The

board

populated

also

with

includes

firmware

GENERAL

two

28-pin

EPROMs.

INFORMATION

sockets.

These

sockets

are

1.3.2

The iSBC 547

system

iSBC

320.

547

board

The

board.

The

board

its

CPU.

or

receiving

t~e

attention

the

MULTIBUS

the

MULTIBUS

reset

The

eight

9-pin

the

IBM

The iSBC 547

Controllers

uses

The 80186

data

of

interface

host

an

interrupt

serial

connectors.

PCAT

connections.

board

(SCC).

an

generators,allowing

separate

baud

rates.

Baud.

The iSBC 547

total

by

of

other

board

128

KBytes

MULTIBUS

BOARD

is

a

board

communicates

Intel

controls

from

the

MULTI

to

interrupt

to

the

interfaces

The

9-pin

has

Each

each

The maximum

has

per

boards.

DESCRIP'l~ION

terminal

controller

with

80186

microprocessor,

eight

the

MULTIBUS

BUS

to

the

MULTIBUS

host

host.

on

the

the

by

board,

host

iSBC 547

connections

four

on-~)oard

82530

sec

channel

contains

to

baud

four

64K

board.

x 4

~~he

upper

a

MULTIBUS

serial

host.

channels

The

generating

A

flag

byte

to

generated

are

82530

Serial

two

be

independently

rate

DRAM

(Dynamic

32K

expansion

host

operating

on-board

an

mechanism

reset

the

by

board

fully

are

compatible

communications

on-chip

per

channel

RAM)

Bytes

can

to

the

as

a

at

8

sending

data

80186

interrupt

allows

board,

the

board.

through

baud

rate

programmed

is

19.2K

devices,

be

addressed

Intel

slave

Mhz

gains

over

or

eight

with

for

as

to

to

a

The

board

populated

1.3.3

also

with

iSBC

The iSBC 546

board

communicates

includes

firmware

546

board

BOARD

is

a

with

two

28-pin

EPROMs.

DESCRIPTION

terminal

a

MULTIBUS

and

1-3

sockets.

line

host

as

These

printer

a

slave

sockets

controller.

board.

are

The

Page 15

The

board

its

cpu. The 80186

or

receiving

uses

interface.

host

host.

the

MULTI

by

generating

A

flag

board,

BUS

host

data

The

byte

to

reset

generated

an

Intel

controls

from

on-board

an

mechanism

the

GENERAL

80186

the

MULTIBUS

80186

interrupt

allows

board,

by

the

INFORMATION

microprocessor,

four

ga.ins

over

or

serial

host,

the

the

to

channels,

and a line

attention

the

MULTI

MULTIBUS

reset

l:Jioard.

operating

BUS

an

interrupt

sending

of

interface

host

at

printer

t.he

MULTIBUS

to

interrupt

to

8

Mhz

data

to

the

as

to

the

The

9-pin

the

The

four

serial

connectors.

IBM

PCAT

line

printer

connections.

interface.

The iSBC 546

Controllers

board

(SCC).

generators,allowing

separate

baud

rates.

Baud.

The iSBC 546

total

by

The

of

other

board

populated

A

clock/calendar

board

128

KBytes

MULTIBUS

also

with

non-rechargeable

for

six

months

interfaces

The

interface

has

Each

each

has

per

boards.

includes

firmware

circuit,

battery

with

all

on

the

9-pin

two

connections

is

compatible

on-board

82530 sec

channel

The maximum

four

64K

board.

two

28-pin

The

EPROMs.

unique

which

other

keeps

power

iSBC 546

82530

contains

to

be

baud

x 4

DRAM

upper

sockets.

to

the

the

off.

are

with

Serial

board

fully

two

are

the

Communications

on-chip

independently

rate

per

channel

(Dynamic

32K

Bytes

These

iSBC

546,

clock/calendar

through

compatible

IBM

line

baud

programmed

is

RAJ~)

can

devices,

be

sockets

is

backed

operating

four

with

printer

rate

for

19.2K

a

addressed

are

up

by

a

1-4

Page 16

INTERFACE

CHLS 7 AND

(iSBC'

,------

INTERFACE

CHlS

(iSBe'

548

548

RS232

ONLY)

RS232

5 AND 6

ONLY)

5471

5471

GENERAL

8

---

-

INFORMATION

REFRESH

LOGIC

(ALL

BOARDS)

5

MULTIBUS'

3

r

'"

RAM

(ALL

BOARDS)

REFRESH

CONTROL

SIGNALS

I RAM CONTROL

SIGNALS

RAM

CONTROL

(ALL

BOARDS)

PAINTER

INTERFACE

(iSBe

ONLY)

Figure

546

1-1.

I

I

L

CLOCK!

CALENDAR

INTERFACE

(iSBC'

546

ONLY)

iSBC

Block

__

546,

Diagram

iSBC

MICROPROCESSOR

_

(ALL

547

80186

(ALL

ROM

and

BOARDS)

BOARDS)

iSBC

548

2335

Boards,

1-5

Page 17

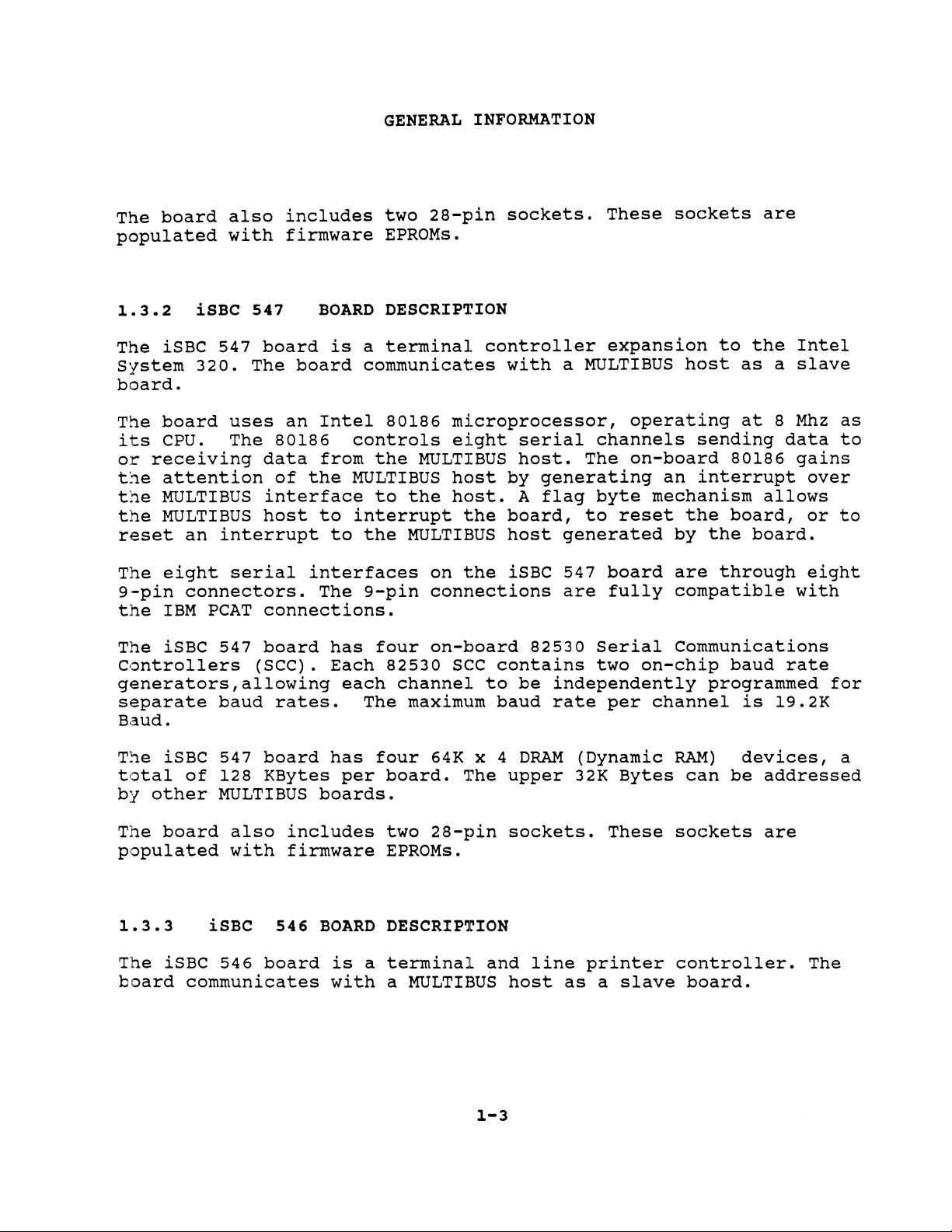

GENERAL

INFORMATION

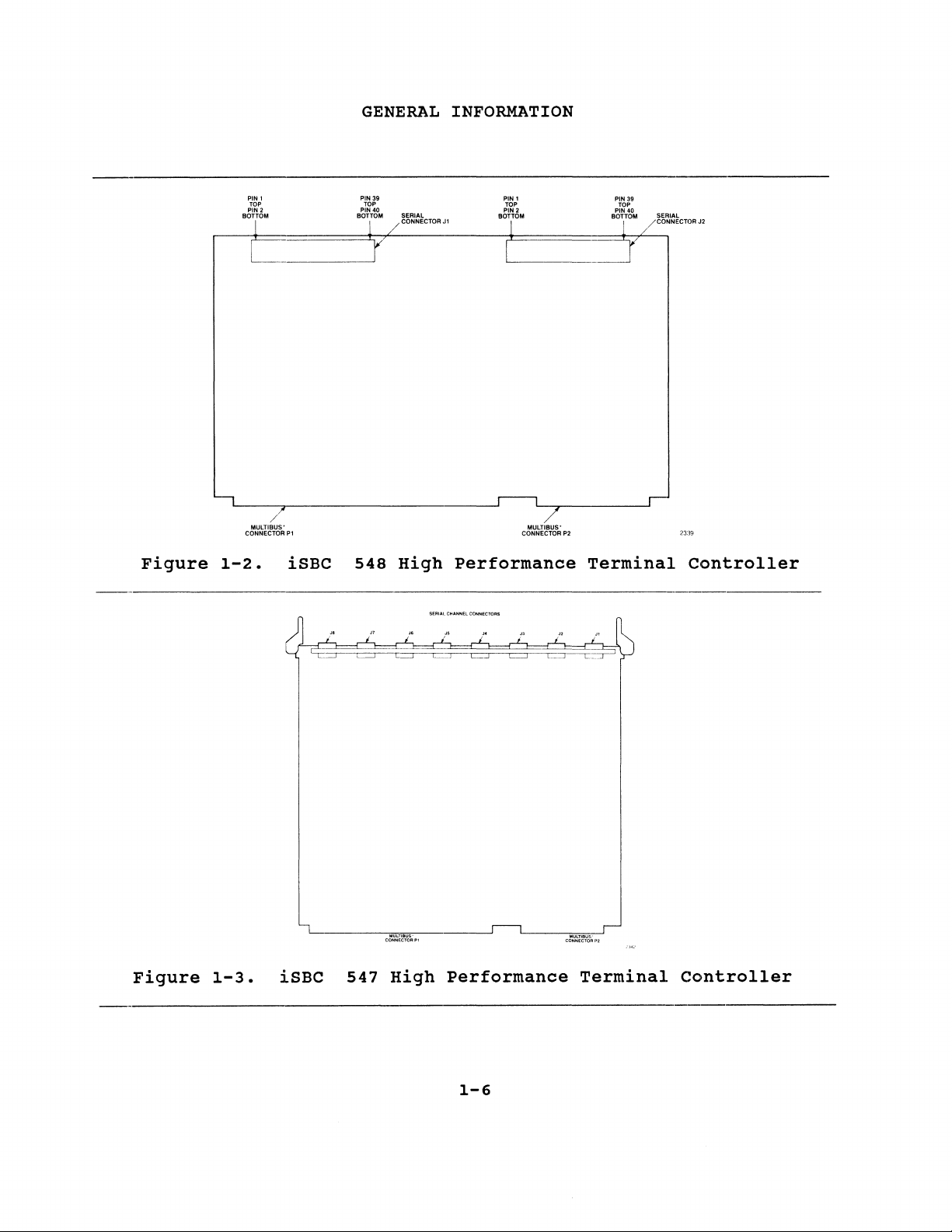

Figure

PIN 1

TOP

PIN2

BOTTOM

CONNECTOR

1-2.

MULTIBUS'

P1

iSBC

PIN 39

TOP

PIN 40

BOTTOM

548

SERIAL

CONNECTOR

High

PIN 1

TOP

PIN2

J1

BOTTOM

MULTIBUS'

CONNECTOR

Performance

P2

Terminal

PIN 39

TOP

PIN

BOTTOM

40

SERIAL

CONNECTOR

J2

Controller

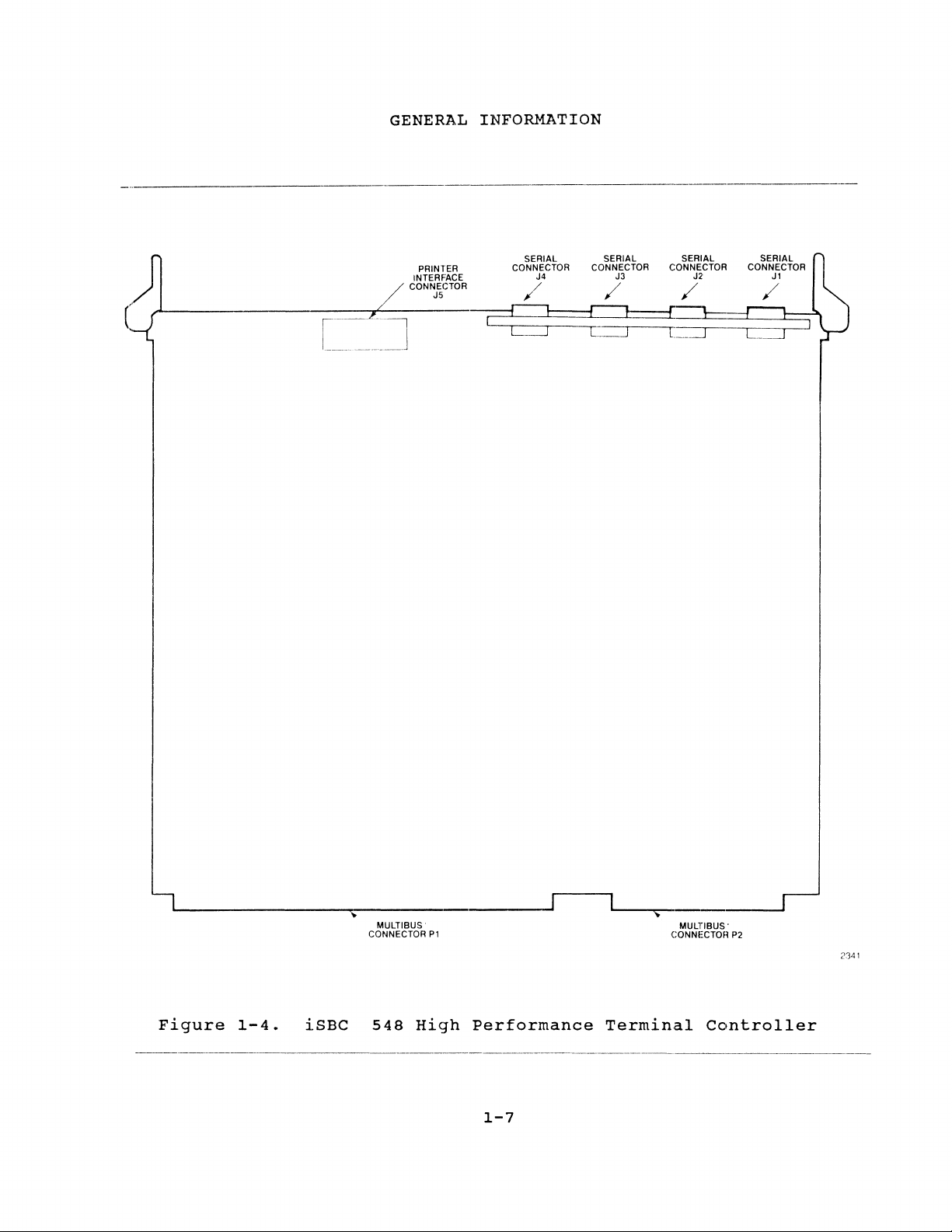

Figure

1-3.

iSBC

547

High

Performance

1-6

Terminal

Controller

Page 18

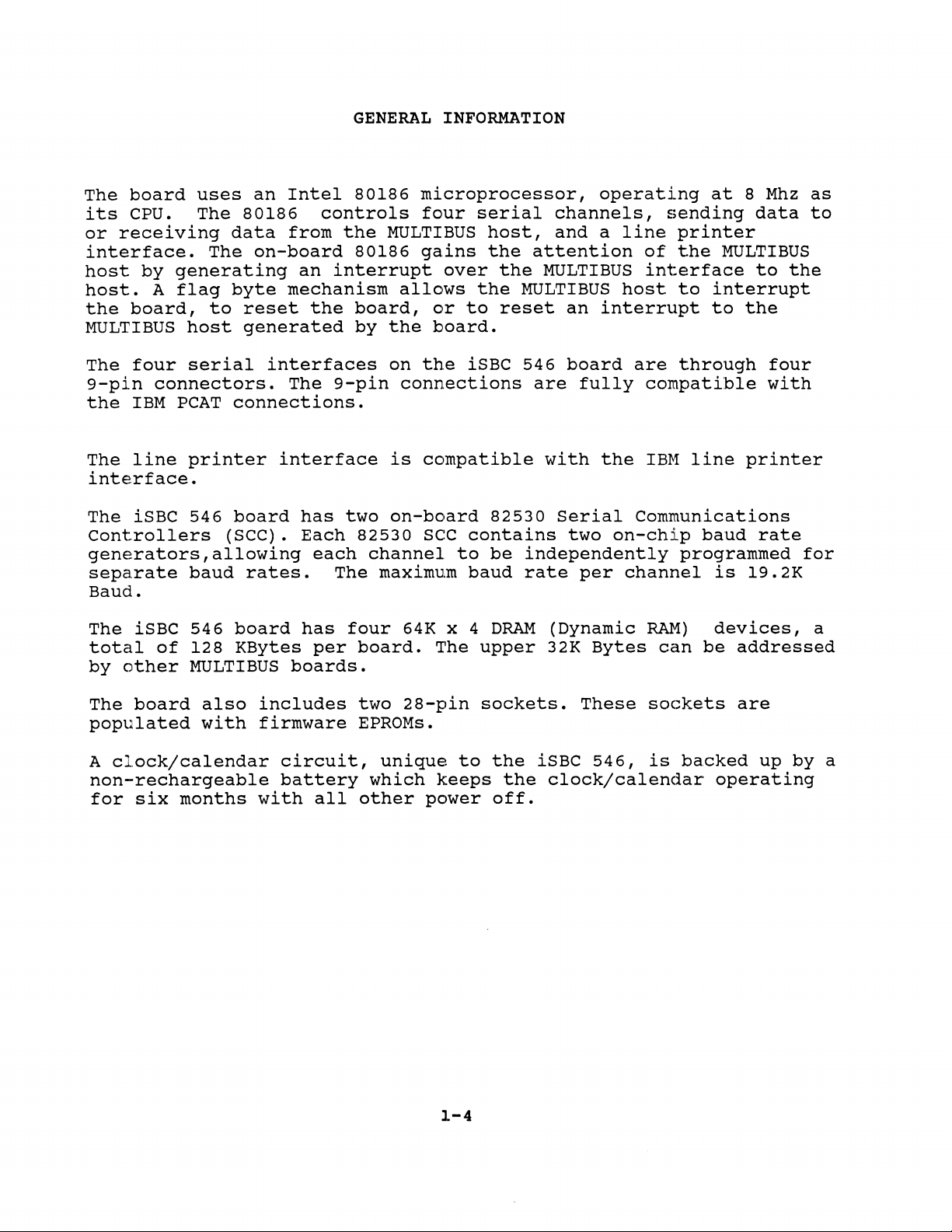

GENERAL

INFORMATION

PRINTER

INTERFACE

CONNECTOR

J5

SERIAL

CONNECTOR

J4

/

SERIAL

CONNECTOR

J3

/

SERIAL

CONNECTOR

J2

/

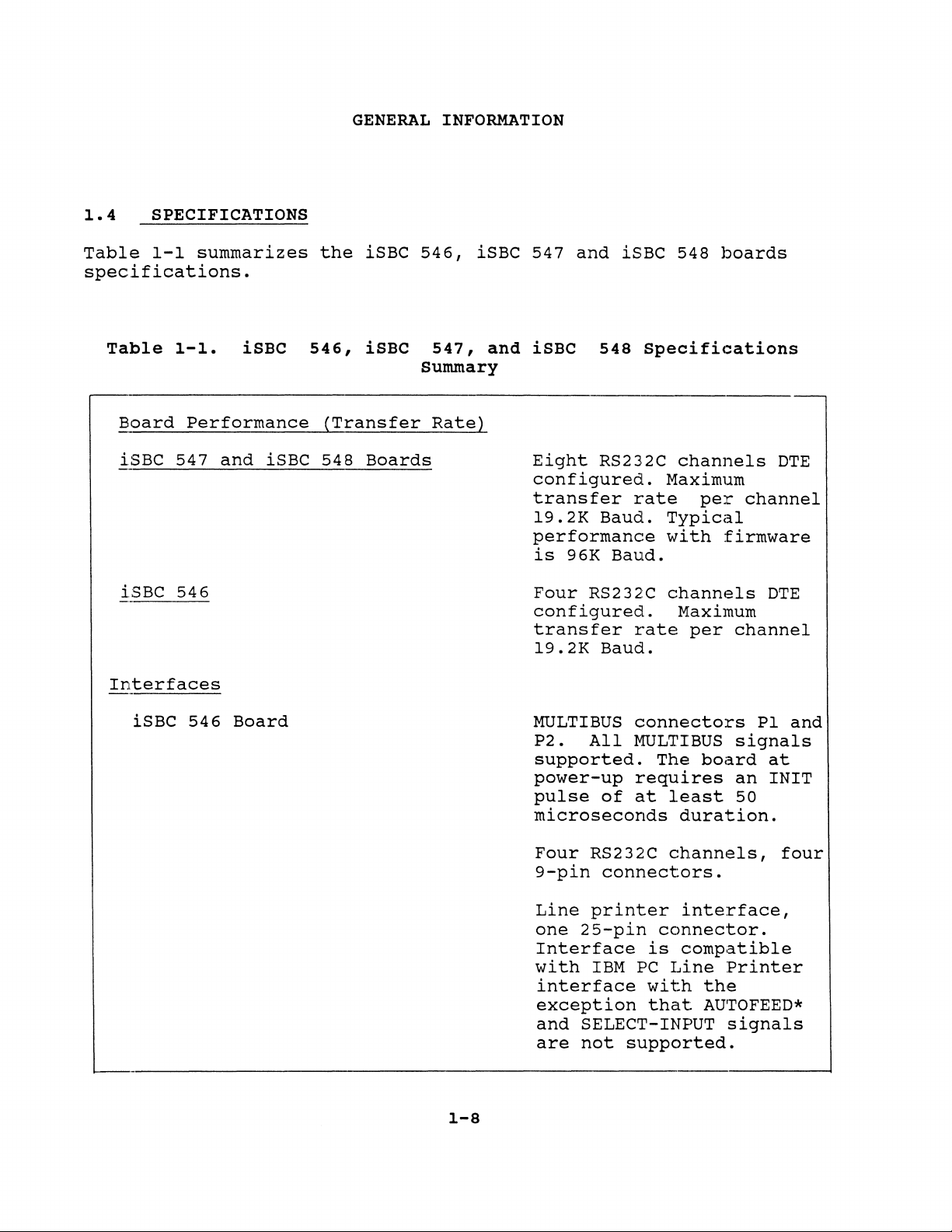

Figure

1-4.

iSBC

MULTI BUS .

CONNECTOR

548

High

P1

Performance

1-7

GONNECTOR P2

Terminal

MULTIBUS'

2341

Controller

Page 19

GENERAL

INFORMATION

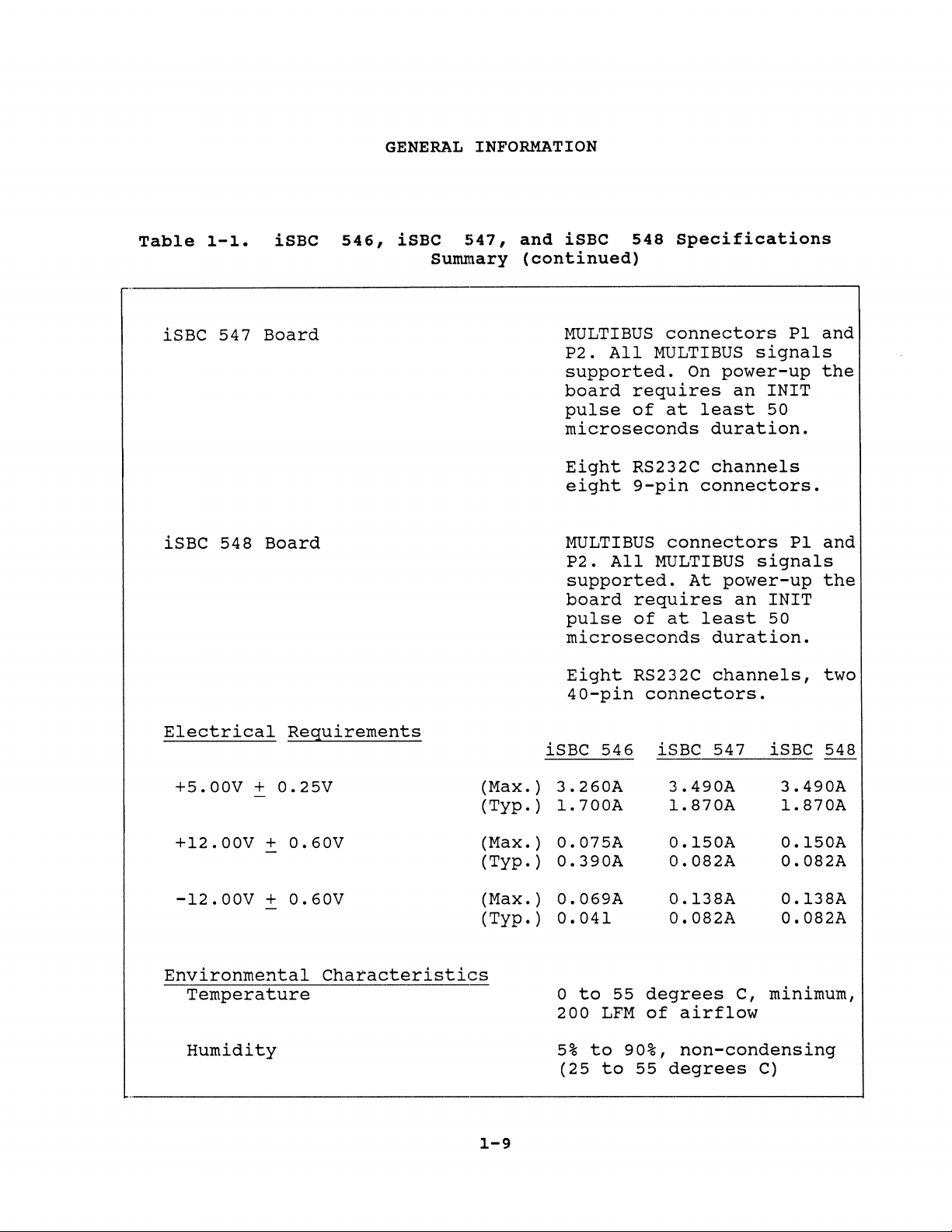

1.4

Table

SPECIFICATIONS

1-1

specifications.

Table

Board

iSBC

iSBC

1-1.

Performance

547

546

summarizes

iSBC

and

iSBC

the

546,

(Transfer

548

iSBC

iSBC

Boards

546,

summary

547,

iSBC

and

Rate)

547

and

iSBC

iSBC

Eight

548

RS232C

configured.

transfer

19.2K

Baud.

performance

is

96K

Baud.

Four

RS232C

configured.

transfer

19.2K

Baud.

548

boards

Specifications

channels

Maximum

rate

per

Typical

with

:firmware

channels

Maximum

rate

per

channel

DTE

channel

DTE

Interfaces

iSBC

546

Board

1-8

MULTI

P2.

BUS

All

connectors

MUL'I'IBUS

supported.

power-up

pulse

of

requires

at

microseconds

Four

9-pin

Line

one

RS232C

connectors.

printer

25-pin

Interface

with

IBM

interface

exception

and

SELECT-INPUT

are

not

supported.

The

least

duration.

channels,

interface,

connector.

is

compatible

PC

Line

with

that.

PI

signals

board

an

at

INIT

50

four

Printer

the

AU'rOFEED*

signals

and

Page 20

GENERAL

INFORMATION

Table

iSBC 547

iSBC 548

1-1.

iSBC

Board

Board

546,

iSBC

Sumlllary

S47,

and

iSBC

(continued)

MULTI

P2.

supported.

board

pulse

microseconds

Eight

eight

MULTI

P2.

supported.

board

pulse

microseconds

Eight

40-pin

548

BUS

connectors

All

MULTIBUS

requires

of

at

RS232C

9-pin

BUS

connectors

All

MULTIBUS

requires

of

RS232C

connectors.

specifications

signals

On

power-up

an

least

duration.

channels

connectors.

signals

At

power-up

an

at

least

duration.

channels,

PI

INIT

50

Pl

INIT

50

and

the

and

the

two

Electrical

Requirements

+5.00V + 0.25V

+l2.00V

-12.00V

+

0.60V

+

0.60V

Environmental

Temperature

Humidity

Characteristics

(Max. )

(Typ.

(Max. )

(Typ.

(Max. )

(Typ.

1-9

iSBC 546 iSBC 547 iSBC 548

3.260A

1.

)

0.075A

)

0.390A

0.069A

)

0.041

o

200

5%

(25

700A

to

55

LFM

to

to

degrees

of

90%,

55

3.490A

1.

870A

0.l50A

0.082A

0.l38A

0.082A

3.490A

1.

0.150A

0.082A

0.138A

0.082A

C, minimum,

airflow

non-condensing

degrees

C)

870A

Page 21

GENERAL

INFORMATION

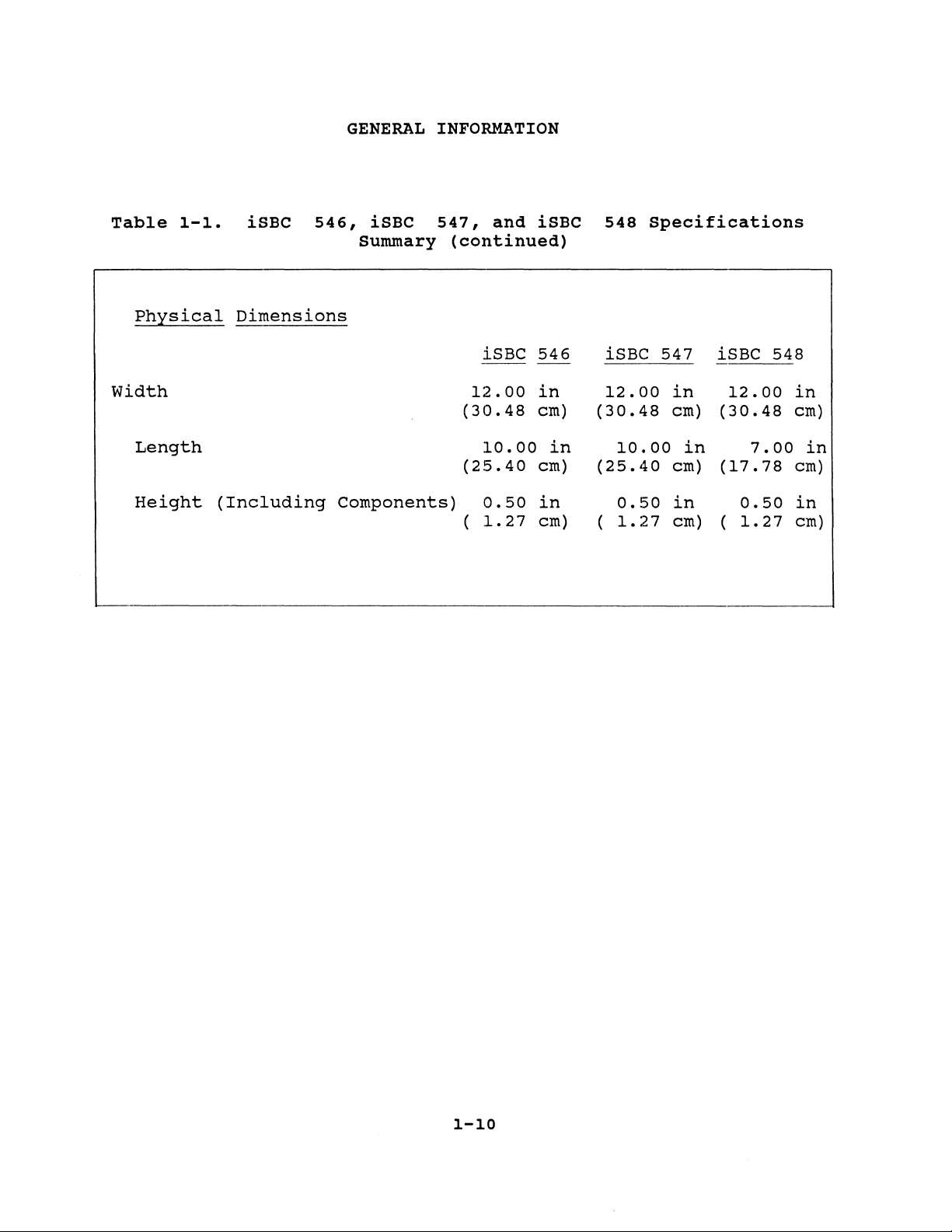

Table

Physical

width

Length

Height

1-1.

(Including

iSBC

546,

Dimensions

iSBC

Summary

Components)

547,

and

(continued)

iSBC

1:2.00

(30.48

10.00

(25.40

0.50

(

1.

27

iSBC

546

in

cm)

in

cm)

in

cm)

548

iSBC

12.00

(30.48

10,,00

(25.40

0.50

(

1.

27

specifications

547

in

cm)

in

cm)

in

cm)

iSBC

12.00

(30.48

7.00

(17.78

0.50

(

1.

548

27

in

cm)

in

cm)

in

cm)

1-10

Page 22

CHAPTER 2

2.1

This

boards,

and

will

INTRODUCTION

chapter

the

iSBC 548

be

described

separately.

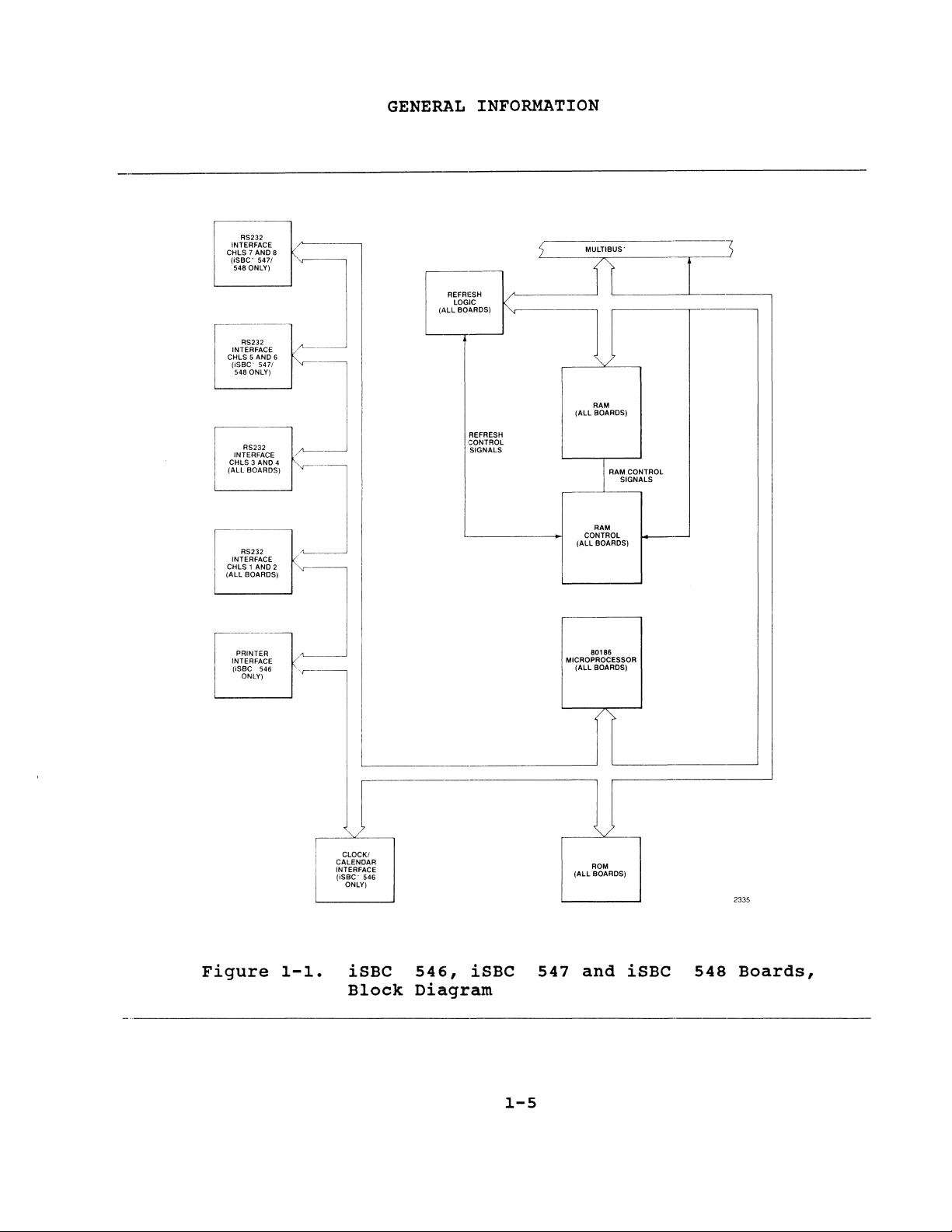

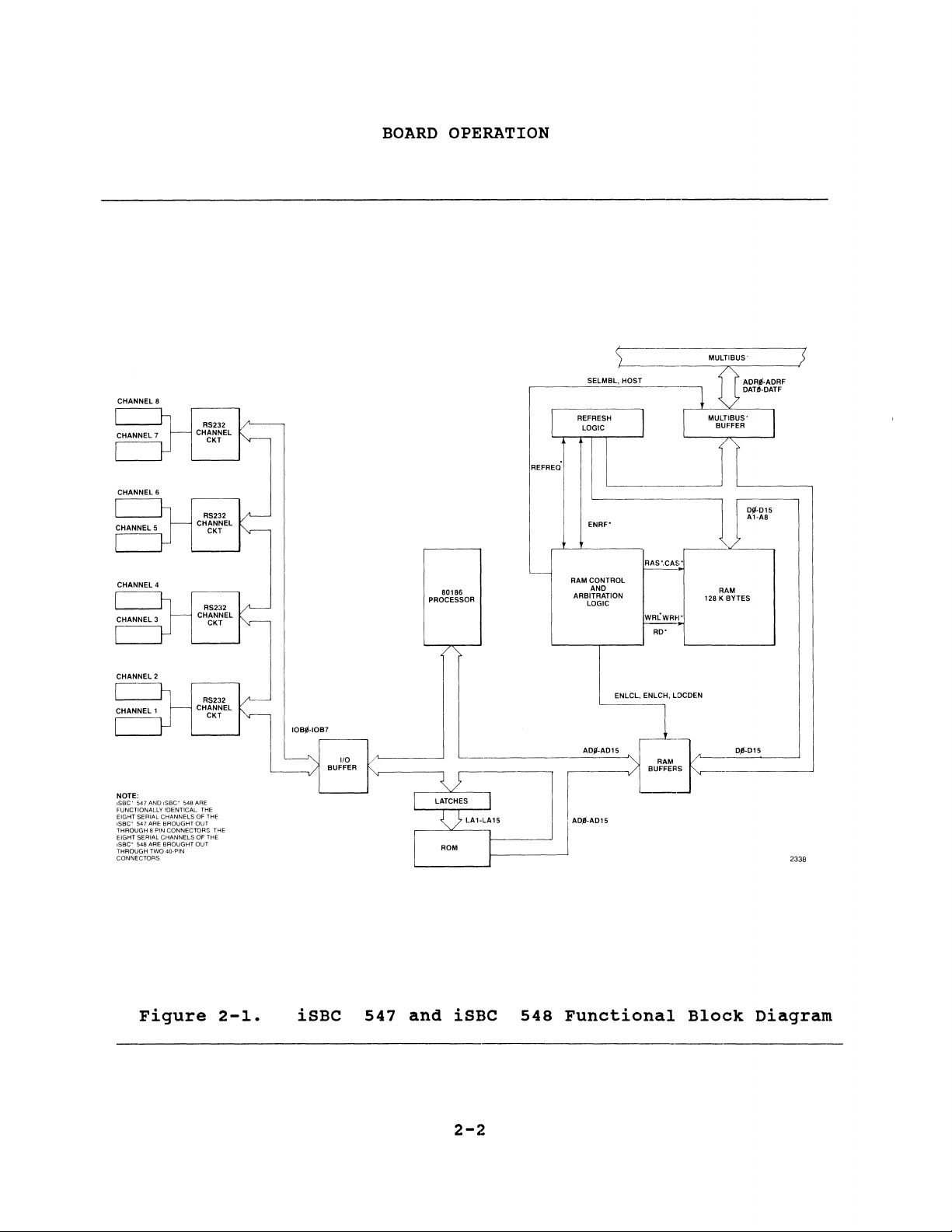

2.2

Figure

boards.

iSBC

2-1

The

dimensions

connectors

connectors

The

iSBC 547

interface,

~ruLTIBUS

is

describes

iSBC

boards

547

is

a

boards

and

in

(eight

for

the

and

both

through

546,

are

jointly.

AND

iSBC

block

are

the

9-pin

iSBC

iSBC 548

are

slave

edge

the

operation

the

iSBC

functionally

The iSBC

548

diagram

functionally

type

and

connectors

548).

boards

boards

connectors

of

547,

and

identical

546

FUNCTIONAL

for

the

iSBC 547

identical

number

of

for

can

not

only.

PI

BOARD

the

three

the

iSBC

and

board

DESCRIPTIONS

serial

the

address

The

and

will

and

and

iSBC 547

interface

P2.

OPERATION

controller

548.

interface

the

The

their

be

considered

iSBC 548

differ

and

MULTIBUS

to

iSBC 547

operation

only

two

40-pin

the

in

30th

as

bit

without

'rhe

sending

data,

from

(shared

HULTIBUS

enabled.

for

HULTIBUS

The

B,

boards

their

internal

the

80186

data

through

the

dual

data

structure

section

main

on

MULTIBUS

host

The

from

host.

B.3.1

communication

(dynamic

structures

use

an

Intel

processors.

architecture.

need

the

of

a

iSBC

,through

them,

to

is

port

memory)

informs

80186

the

of

table

then

MULTIBUS

the

of

this

in

area),

80186

The

separate

547/548

them,

the

by

use

the

polls

in

on-bc)ard

microprocessor,

80186

The

80186

bus

controls

from

MUL'l~IBUS

of

a 32K

the

those

host,

communication

manual.

the

on-board

a

status

2-1

has

provides

controller

eight

the

MULTIBUS

host.

Byte

on-board

80186

channels

or

the

table

The

main

RAM

queue

operating

a

16

bit

data

all

device.

serial

host

Data

transfer

communication

dual-port

which

serial

continuously,

need

are:

to

is

described

blocks

a command

supply

in

(static

bus

bus

controls

channels

or

receiving

to

table

RAM.

channels

data

in

the

queue

structures

at

8

Mhz

and

16

and

The

are

looking

to

the

Appendix

Page 23

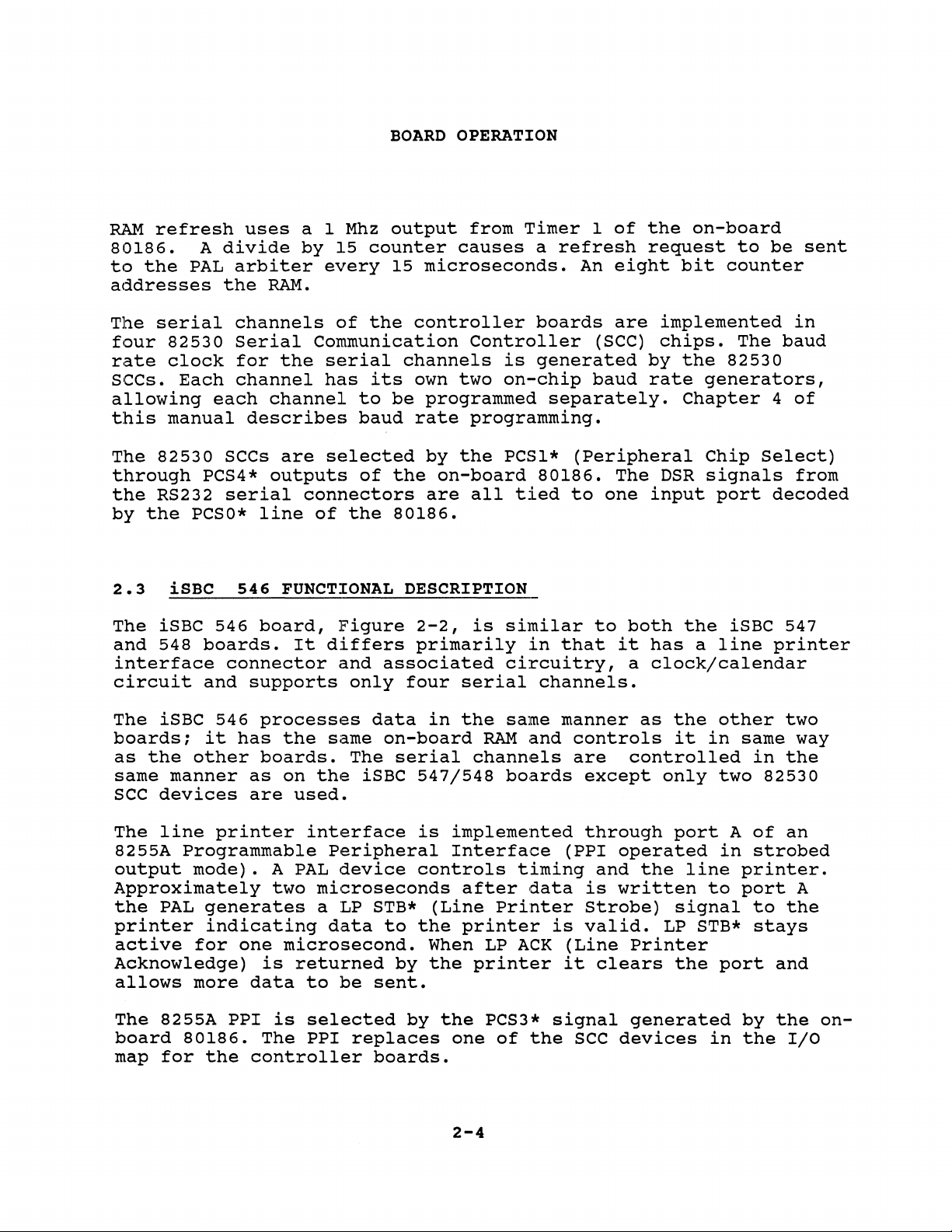

CHANNEL

CHANNEL 4

BOARD

8

OPERATION

80186

PROCESSOR

,-------------

REFREQ

,-~~----

C

SELMBL,

REFRESH

LOGIC

______

HOST

M_V_L,T,',B_V_S_' ____

·:-----1

,---'"'----,

RAS',eM,'

RAM

CONTROL

AND

ARBITRATION

LOGIC

----

WRLWRH'

---

AD'

128 K

AAM

BYTES

o~-o15

A1·A8

----<J

CHANNEL

2

CHANNEL

RS23~1

CKT

NOTE:

ISBC'

547 AND

ISBC"

FUNCTIONALLY IDENTICAL

EIGHT SERIAL CHANNELS OF THF

Isac"

THROUGH 8 PIN CONNECTORS THE

EIGHT SERIAL CHANNELS OF THE

ISSC' 548 ARE BROUGHT OUT

THROUGH TWO 40·PIN

CONNECTORS

548 ARE

BROUGHT

THE

our

547

ARE-

Figure

2-1.

IOB~·IOB7

I/O

BUFFER

iSBC

547

ENLCL, ENLCH, LDCOEN

~-~-l

-

,.---------"'-=~·I

L-----,JJ

and

iSBC

548

'~=-l-""

[I"'"''

I

Functicmal

F~==-d

-='

.

Block

Diagram

j

2338

2-2

Page 24

BOARD

OPERATION

a~ea),

rE:!cei

board

board

queue

the

Table

T::1e

a

ve

80186

80186

by

host.

A-2.

flag

transmission

buffers.

generating

The

byte

controller

t::le

MULTIBUS

interrupt,

eige

The

a::idress

tile

through

Ea.ch

triggered

flag

byte

(see

MULTIBUS

PCS5*

of

the

populated

firmware.

dl:~tail.

Although

boards

with

o:E

250

the

can

zero

ns

different

The

to

the

gains

interrupt

mechanism

board,

host

sent

by

input

is

mapped

Appendix

host

(asterisk

controller

by

two

Appendix

controller

support

wait

or

size

states.

less.

EPROMs

area

MULTIBUS

command

the

attention

an

interrupt

to

reset

generated

the

MULTIBUS

to

A ,

is

done

boards

Intel

B

2764

of

27128

The

No

jumper

are

(transmit

host

queUE!

line

is

allows

the

by

the

interrupt

to

I/O

Table

by

writing

indicates

include

EPROMs

this

manual

boards

and

27256

optional

changes

used.

gains

by a flag

of

the

over

jumper

the

MULTIBUS

board,

the

board.

host

space

A-2

of

signal

which

describes

are

supplied

EPROMs

EPROMs

buffers),

the

byte

MULTIBUS

the

MULTIBUS

selectable

or

to

The

to

the

line

at

a

jumper

of

this

data

to

is

two

28-pin

contain

as

must

need

be

and a set

attention

interrupt.

host

interface

as

host

reset

to

an

flag

controller

the

on-board

selectable

manual).

an

I/O

active

low).

sockets

the

the

firmware

with

well.

2764

The

have

made when

of

of

the

The

to

the

shown

in

interrupt

interrupt

byte

board

80186.

Interrupting

port

addressed

which

controller

in

EPROMs

EPROM

access

the

on-

on-

status

to

the

to

is

are

the

runs

times

an

Each

of

RAM

b::>ard

at

are

of

128K

can

processor.

several

jumper

manual).

'Il:1e

RAM

device.

arbitrate

80186

H

..

hl1

is

the

on-board

even

when

the

boards

Bytes

be

addressed

different

selectable

The

is

controlled

The

PAL

between

and

enables

selected

the

of

on-board

The

RAM

operates

generates

by

80186.

memory

has

by

dual-port

starting

the

the

the

The

is

four

64K x 4

RAM.

other

(see

Table

with

with

a

PAL

all

MULTIBUS

address

LCS

(Lowler

memory

locked.

DRAMs

~rhe

upper

MULTI

HAM

BUS

can

addresses.

A-3

in

:z:ero

wait

(Programmable

signals

host,

the

lbuffers

Chip

arbiter

2-3

(Dynamic

32K

boards

be

seen

The

Appendix

states.

needed

refresh

as

required.

Select)

allows

Bytes

as

well

from

starting

A

Array

to

control

logic

signal

refresh

RAMs), a

of

the

on-board

as

the

the

MULTIBUS

addresses

of

this

Logic)

the

and

The

on-board

generated

of

the

total

on-

RAM,

the

by

RAM

Page 25

RAM

refresh

80186.

to

the

addresses

The

serial

flour

rate

secs.

82530

clock

Each

allowing

this

manual

A

PAL

each

uses

divide

arbiter

the

RAM.

channels

Serial

for

the

channel

channel

describes

BOARD

a 1

Mhz

output

by

15

counter

every

of

15

the

controller

Communication

serial

has

its

to

be

baud

channels

own

rate

OPERATION

from

causes

Timer 1 of

a

microseconds.

boards

Controller

is

generated

two

on-chip

programmed

programming.

refresh

An

eight

are

(SCC)

baud

separately.

the

on-board

request

bit

to

counter

implemented

chips.

by

the

rate

The

82530

generators,

Chapter

be

baud

4

sent

in

of

The

82530

through

the

RS232

by

the

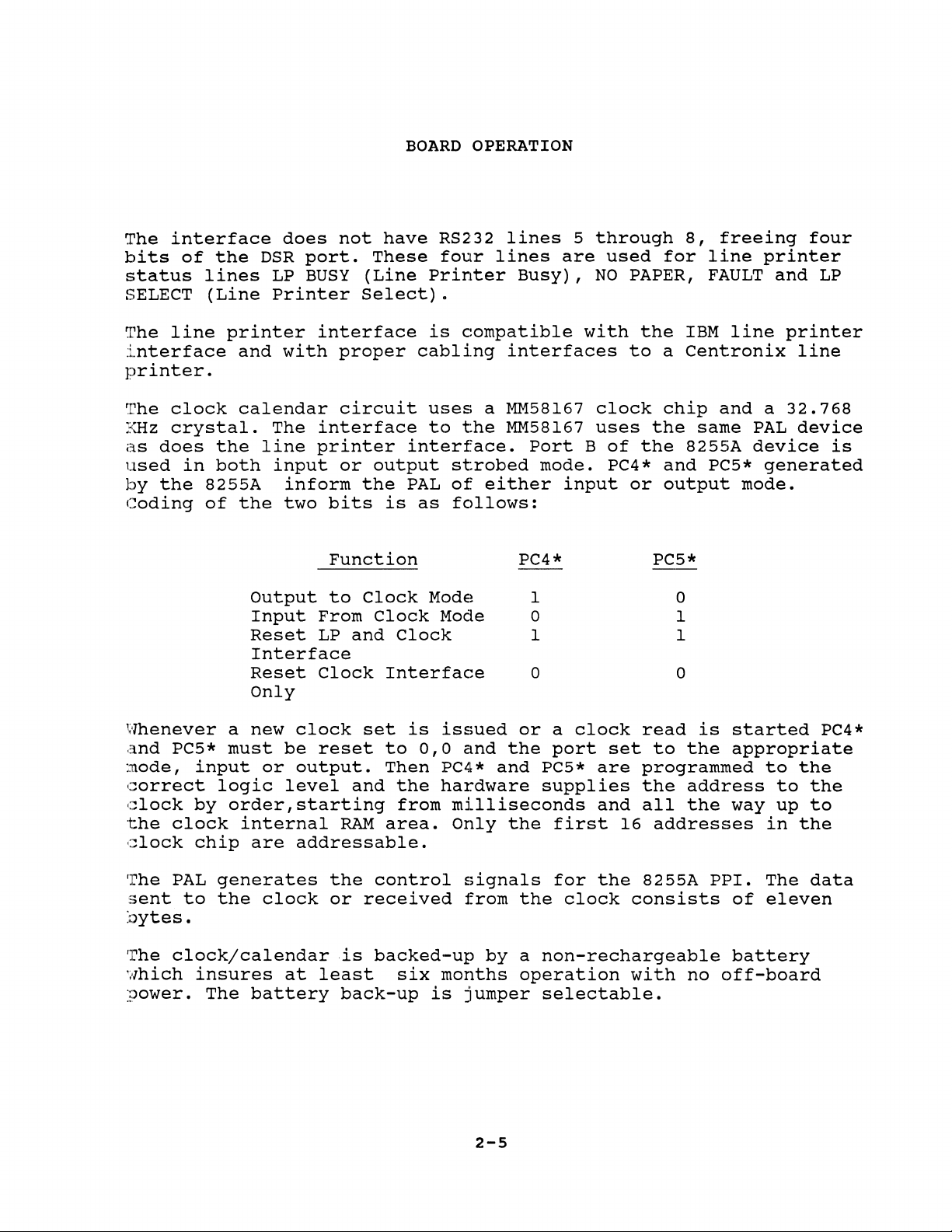

2.3

The

and

iSBC

iSBC 546

548

interface

circuit

The

iSBC

boards;

as

the

same

SCC

The

manner

devices

line

8255A

output

SCCs

PCS4*

serial

PCSo*

boards.

connector

and

546

it

other

printer

Programmable

mode).

Approximately

the

PAL

generates

printer

active

indicating

for

Acknowledge)

allows

more

are

selected

outputs

of

connectors

line

546

board,

of

the

FUNCTIONAL DESCRIPTION

Figure

It

differs

and

supports

processes

has

the

boards.

as

on

are

used.

same

the

only

data

The

iSBC

interface

by

the

are

80186.

2-2,

primarily

associated

four

in

on-board

serial

547/548

is

Peripheral

A

PAL

two

one

microsecond.

is

returned

data

to

device

microseconds

a

LP

data

be

STB*

to

by

sent.

controls

the

When

the

the

PCSl*

on-board

all

tied

is

similar

circuitry,

serial

the

same

RAM

channels

boards

implemented

Interfa,ce

timing

after

(Line

Printer

printer

LP

ACK

printer

(Peripheral

80186.

to

in

that

channels.

manner

and

controls

are

except

through

(PPI

data

is

Strobe)

is

valid.

(Line

it

The

one

to

both

it

a

as

controlled

operated

and

the

written

Printer

clears

DSR

input

the

has

Chip

signals

a

Select)

port

iSBC 547

line

clock/calendar

the

other

it

in

same way

in

only

LP

two

port

line

to

signal

STB*

the

port

A

of

in

strobed

printer.

port

to

stays

82530

from

decoded

printer

two

the

an

A

the

and

The

board

map

8255A

80186.

for

the

PPI

is

The

controller

selected

PPI

replaces

by

boards.

the

one

2-4

PCS3*

of

signal

the

SCC

generated

devices

in

by

the

the

I/O

on-

Page 26

The

interface

bits

of

status

SELECT

The

line

interface

printer.

rrhe

clock

KHz

crystal.

as

does

used

by

in

the

Coding

the

lines

(Line

printer

and

calendar

the

both

8255A

of

the

does

DSR

LP

Printer

with

The

line

input

inform

two

not

port.

BUSY

Select).

interface

proper

circuit

interface

printer

or

the

bits

have

These

(Line

output

is

BOARD

OPERATION

RS2:32

four

Printer

is

compatible

cabling

uses

to

the

interface.

strobed

PAL

of

as

follows:

lines

lines

Busy),

interfaces

a

MM58167

MM58167

Port

mode. PC4*

either

5

through

are

NO

with

clock

uses

B

input

used

PAPER,

to

of

or

for

the

a

chip

the

the

and

output

8,

freeing

line

printer

FAULT

IBM

line

Centronix

and

a

same

8255A

PC5*

PAL

device

generated

mode.

four

and

printer

line

32.768

device

LP

is

Output

Input

Reset

Interface

Reset

Only

1;'1henever a new

,.3.nd

PC5*

::node,

correct

clock

'the

clock

clock

'rhe

PAL

sent

must

input

logic

by

chip

generates

to

the

or

order,

internal

are

clock

::.')ytes.

'rhe

clock/calendar

'ilhich

power.

insures

The

battery

Function

to

Clock

From

LP

and

Clock

clock

be

set

reset

output.

level

and

starting

RAM

addressable.

the

or

received

is

at

least

back-up

Mode

Clock

Mode

Clock

Interface

is

issued

to

0,0

Then

area.

the

from

PC~~*

hardware

milliseconds

Only

control

backed-up

six

months

is

PC4* PC5*

1

0 1

1 1

0 0

or a clock

and

the

port

and

PC5*

supplies

the

first

~;ignals

from

the

for

clock

read

set

are

programmed

the

and

all

16

the

8255A

consists

by a non-rechargeable

operation

~iumper

selectable.

with

0

is

to

the

address

the

addresses

PPI.

no

off-board

started

PC4

appropriate

to

the

to

the

way

up

to

in

the

The

data

of

eleven

battery

*

2-5

Page 27

BOARD

OPERATION

PRINTER

CONNECTOR

CHANNEL 4

LOAlO·

LDAT7,

OSR5·0SRs

TRANSCEIVER

IOBP-9

PROGRAMMABLE

PERIPHERAL

INTERFACE

ClKBUSO-

CLKBUS7

CLOCK

AND

CALENDER

CKT

110

BUFFER

10BO-

IOB7

'r----------

ADO-AD?

80186

PROCESSOR

ADO-.I\.015

'------

MUlTiBUS"

t)

~

MULTIBUS"

BUFFER

AORO-.IORF

DATO-CIATF

]

SELMBL,

REFRESH

LOGIC

(~

HOS

T

~

Ii

U

00-015

Al-AB

LOC

DEW

:::)

RAS·. CAS'

r--------

WRl',

WRH'

~

1

RAM

BUFFERS

128K

RAM

BYTES

00-015

i

~

~

AAMCONTROL

AND

ARBITRATION

LOGIC

ADO-AD15

Figure

2-2.

iSBC

546

Board

2-6

Functional

Block

2336

Diagram

Page 28

CHAPTER 3

INSTALLATION

3.1

This

iSBC

INTRODUCTION

chapter

548,

installation

and

Appendix

according

procedures

3.2

Inspect

of

water

carton

carton

packing

United

UNPACKING

the

mishandling

stained,

is

is

material

states

contacting

(see

states

Chapter

should

authorized

assistance.

explains

iSBC 547

to

you

A

your

in

should

Jumper

this

AND

shipping

during

request

opened.

opened

and

for

customers

the

Intel

6

for

contact

distributor)

how

and

iSBC 546

read

Information.

system

requirements

chapter.

INSPECTION

carton

transit.

the

If

the

carrier's

the

contents

the

agents

can

product

more

information).

their

for

to

receive,

boards.

Chapter

immediately

If

carrier's

inspection.

obtain

service

sales

service

inspect

However,

4

Programming

Once

you

proceed

upon

the

shipping

agent

agent

are

damaged,

service

hotline

customers

source

information

have

be

is

not

and

(Intel

and

before

set

with

receipt

carton

present

present

keep

repair

in

Phoenix,

outside

sales

and

then

install

Considerations

up

the

jumpers

the

installation

for

evidence

is

damaged

when

the

when

the

carton

assistance

Arizona

the

United

office

repair

the.

or

the

and

by

or

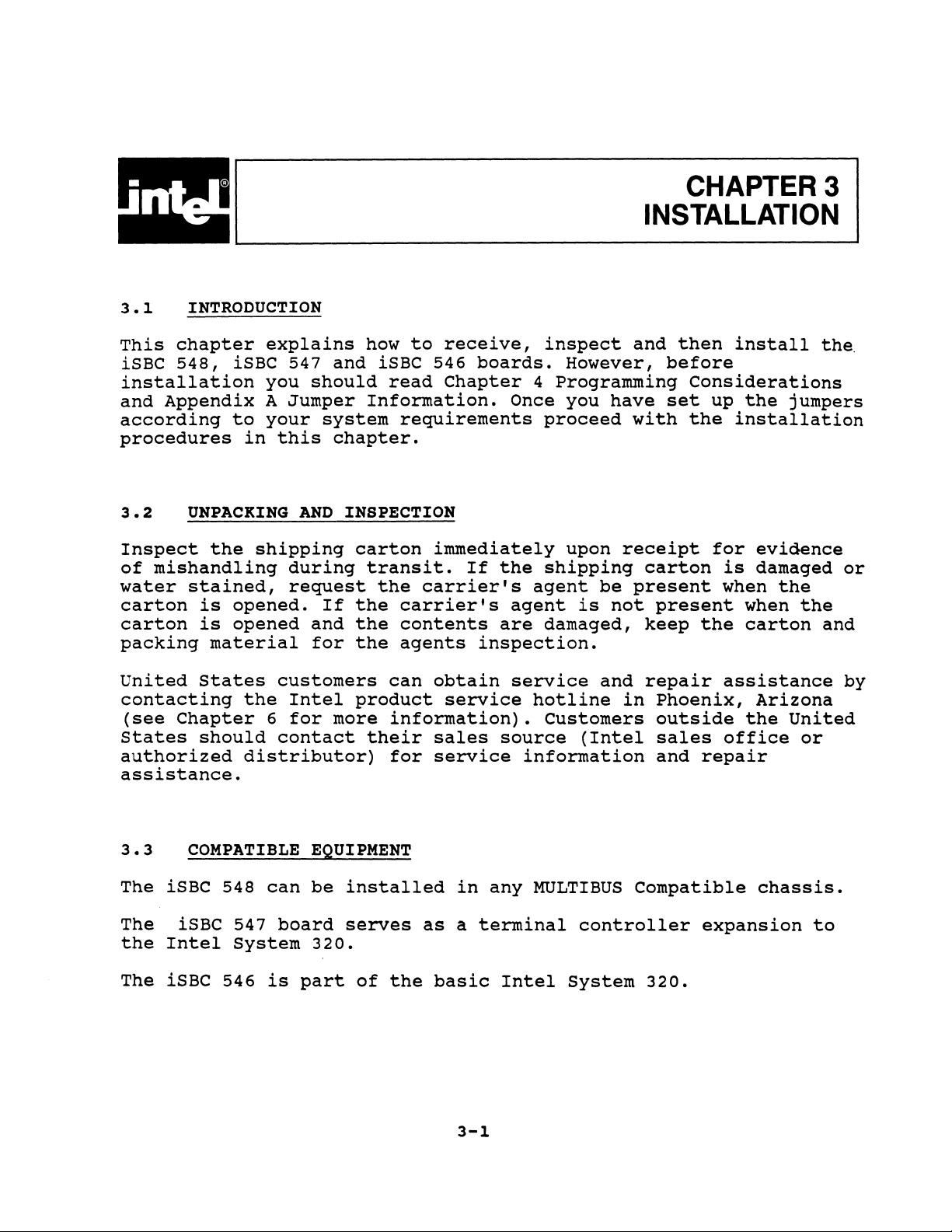

3.3

COMPATIBLE

The iSBC 548

The iSBC 547

the

Intel

System

The iSBC 546

EQUIPMENT

can

be

board

320.

is

part

installed

serves

of

the

in

any

MULTIBUS

as a terminal

basic

Intel

3-1

Compatible

controller

System

320.

chassis.

expansion

to

Page 29

INSTALLATION

3.4

The

INSTALLATION CONSIDERATIONS

following

consideration

THe

different

iSBC

space.

548,

address

The

selectable

MULTIBUS

each

I/O

mapping,

lines.

used

In

a

required

same

cannot

As

an

unused

unused

address

controller

Under

in

a

system

the

I/O

address

share

example,

I/O

address

configured

can

be

installed

interrupt

sections

for

547,

board's

(see

Table

board

different

these

system.

application

boards

the

if

address

locations

to

(see

line

and

the

three

and

locations

flag

A-3)

space.

(iSBC

conditions

are

and

the

same

a

system

address

lines,

Table

in

the

use

describe

some

boards.

546

boards

(see

byte

with

Table

address

eight

The iSBC 548

548,

memory

where

grouped

same

mapping

up

to

more

so

interrupt

space.

has

one

in

the

in

the

range

A-4),

system.

either

than

The

one

can

547

eight

than

that

unused

8AO

20

boards

or

of

the

be

configured

A-4)

(wake-up

options

and

iS4H

or

546)

and

different

controller

eight

several

line.

interrupt

through

the

controller

different

will

two

I/O

installation

to

in

the

MULTIBUS

address)

available

In

the

would

have

.interrupt

controller

boards

The

boards

line,

8A7

range,

controller

share

addresses.

reside

is

in

most

different

boards

boards

share

however

and

boards

the

in

address

jumper

the

ideal

can

the

two

20

can

boards

same

32

mult

be

are

be

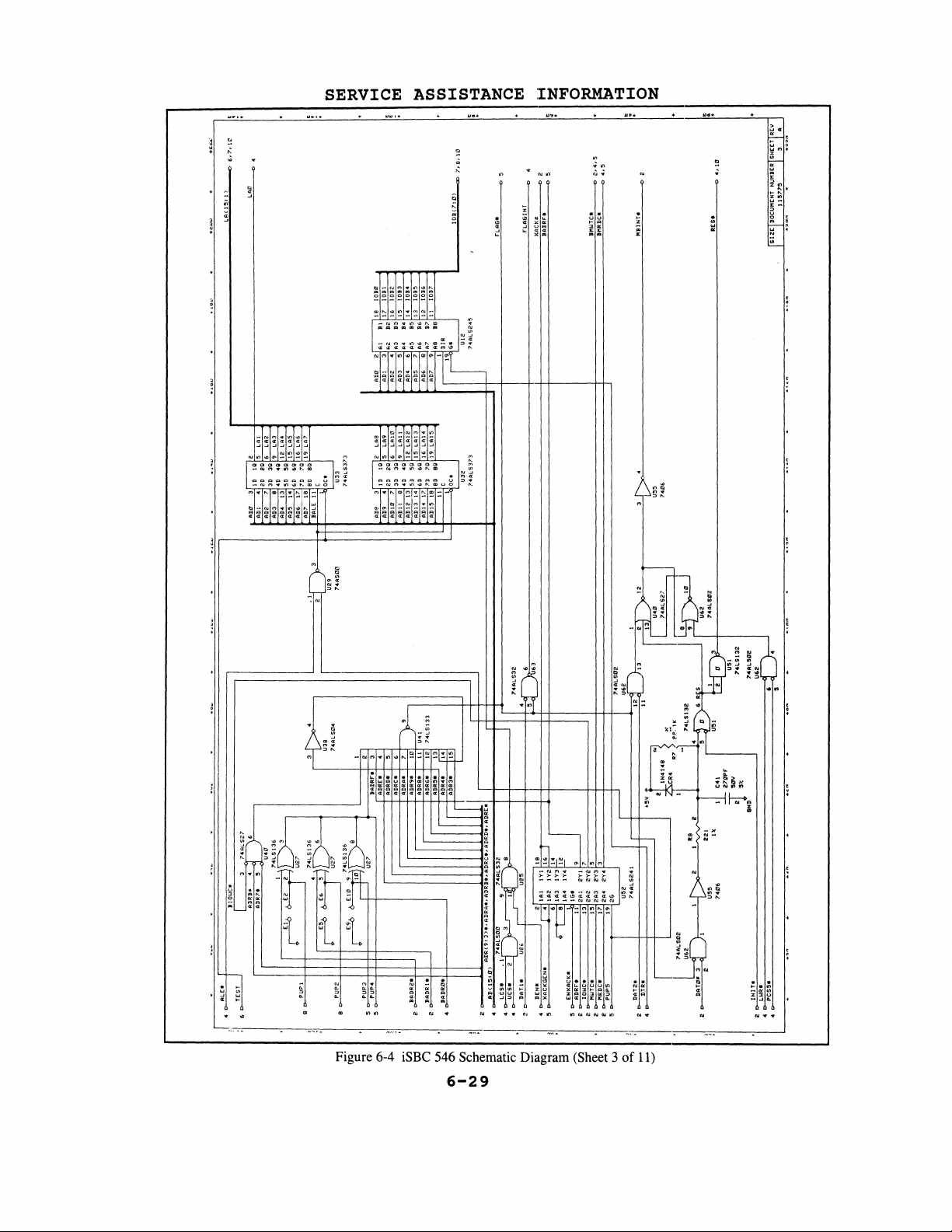

3.4.1

On

all

CONNECTOR

three

connectors.

Table

5-1

connector

Table

On

5-1

the

iSBC 548

connectors

Pin

and

on

and

(see

CONFIGURATIONS

boards

assignments

Table

each

board

Table

board

Table

connectors

5-3

respectively.

is

shown

5-3

respectively.

connectors

5-6

for

for

PI

and

each

in

Figures

Jl

and

pin

assignments).

3-2

P2

are

connector

The

location

3-1,

J2

are

the

MULTIBUS

are

the

provided

of

3-2,

serial

each

and

in

3-3.

I/O

Page 30

On

the

iSBC 547

connectors

On

the

iSBC 546

connectors

the

printer

and

Table

(see

(see

interface

5-8

for

board

Table

board

Table

signal

INSTALLATION

connectors

5-5

for

connectors

5-4

for

connector

descriptions).

Jl

through

pin

assignments)

Jl

through

pin

assignments).

(see

Table

J8

J4

5-7

are

the

.

are

the

connector

for

pin

serial

serial

J5

I/O

I/O

is

assignments

3.4.2

In

order

iSBC 546

the

user.

the

backup

BATTERY

to

use

board

In

the

battery

BACKUP

the

the

jumper

default

is

battery

installed

backup

between

condition

E30

but

for

(as

the

the

clock/calendar

and

E3l

delivered

jumper

must

from

is

be

not.

on

installed

the

factory)

the

by

3-3

Page 31

PIN 1

TOP

PIN2

BOTTOM

PIN

39

TOP

PIN 40

BOTTOM

INSTALLATION

SERIAL

CONNECTOR

J1

PIN 1

TOP

PIN2

BOTTOM

PIN 39

TOP

PIN 40

BOTTOM

SERIAL

CONNECTOR

J2

MULTIBUS®

CONNECTOR

Figure

P1

3-1.

iSBC

548

Board

3-4

MULTIBUS@

CONNECTOR P2

Connector

2339

Locations

Page 32

INSTALLATION

SERIAL

CIHANNEL

CONNECTORS

Figure

3-2.

MULTIBUS®

CONNECTOR

iSBC

Pl

547

Board

:3-5

Connector

Locations

MULTIBUS~

CONNECTOR

P2

2342

Page 33

INSTALLATION

PRINTER

INTERFACE

CONNECTOR

J5

SERIAL

CONNECTOR

J4

/

SERIAL

CONNECTOR

J3

/

SERIAL

CONNECTOR

J2

/

3.4.3

The

to

the

of

the

3-1

for

Table

3-4.

Figure

CABLING

iSBC 548

back

Intel

summarizes

the

iSBC 548

3-2

lists

3-3.

board

panel.

310

the

the

MULTIBUS®

CONNECTOR

iSBC

requires

These

Cable

Kit

recommended

board.

pin

Figure

to

Pl

546

Board

two

cables

or

pin

flat

can

can

cable

3-4

wiring

3-6

Connector

40

conductor

be

acquired

be

fabricated

and

shows

for

MULTIBUS®

CONNECTOR

Locations

connector

the

cable

the

cable

P2

cables

from

by

Intel

the

part

construction.

shown

2341

to

as

user.

numbers

in

connect

part

Table

Figure

Page 34

INSTALLATION

The

iSBC

is

made

Connector

40

40

40

40

Pin

Pin

Pin

9

Pin

Pin

546

directly

Table

or

or

or

and

iSBC

on

3-1.

Manufacturer

3M

3M

T&B

T&B

T&B

Table

40

Connector Connector

10

11

12

13

14

15

16

17

18

547

boards

the

card

Recommended

Ansley

Ansley

Ansley

3-2.

Pin

1

2 9

3 4

4 8

5 3

6 7

7 2

8 6

9 1

P4

5

-

-

-

-

-

-

-

-

-

do

edge.

Part

3417··6000

3417-6040

609-4000M

609-400lM

609-9P-ML

Pin

to

P3

Number

Pin

-

-

-

-

-

-

-

-

-

5

9

4

8

3

7

2

6

1

not

Cables

(without

(with

(without

(with

(metal

wiring

40

19

20

21

22

23 3

24

25

26

27

28

29

30

31

32

33

34

35

36

require

and

Pin

Connectors

strain

strain

strain

strain

shroud,

List

P2

5

9

4

8

7

2

6

1

-

-

-

-

-

-

-

-

-

cables.

relief)

relief

male)

P1

-

-

-

-

-

-

-

-

-

5

9

4

8

3

7

2

6

1

Connection

relief)

relief)

P1ns

used.

37

P1

through

through

40

P4

of

3-7

are

40

p1n

9-pin

connector

connectors.

not

Page 35

EACH 9

CONDUCTOR

IS 5 INCHES

LENGTH

INSTALLATION

r---~-5

BOTTOM

iSBC® 548

COMPONENT SIDE

Figure

3-4.

LAST

PINS OPEN

MALE

40 PIN

CONNECTOR

iSBC

FOUR

548

RS232C

3-8

Cable

2334

Construction

Page 36

INSTALLATION

3.5

The

INSTALLATION

following

controller

is

boards.

1.

2.

3.

4.

PROCEDURE

a

general

Check

Ensure

For

40

Install

Appendix A for

that

the

iSBC 548

pin

connectors.

the

appropriate

connectors

cardcage.

procedure

power

board

terminal

slot

Pl

in

and

for

the

to

your

controller

your

P2

are

installing

jumper

system

install

cardcage.

fully

the

configuration.

is

turned

the

I/O

cables

board

into

Ensure

seated

in

terminal

off.

to

the

that

the

the

3-9

Page 37

Page 38

CHAPTER 4

PROGRAMMING CONSIDERATIONS

4.1

This

the

INTRODUCTION

chapter

users

information

on

the

boards,

4.2

JUMPERS

Appendix

three

should

have

install

4.3

Figure

controller

reference

been

his

ADDRESSING

4-1

describes

of

the

can

A

of

installed

own

is

the

iSBC

be

using

this

boards)

this

546,

used

by a user

the

manual

appendix

by

the

download

and

configuration.

a memory map

programming

iSBC 547

wishing

feature.

locates

the

describes

to

verify

factory

for

the

(the

iSBC

considerations

and

iSBC 548

to

various

their

that

default

546/547/548

boards.

run

his

jumpers

functions.

the

required

condition)

controllers.

applicable

This

own

software

(for

all

The

jumpers

or

to

user

to

The

controller

either

is

done

Because

for

this

EPROM

2764

27128

27256

There

128K

Bytes.

2764,

by

of

are

27128

the

the

memory

four

The

boards

or

80185

different

portion

64K

x 4

upper

include

27256

EPROMs.

processors

EPROMs

will

Memory

16K

32K

64K

DRAMS

32K

Bytes

two

UCS

vary

Size

on

each

can

4-1

28

pin

Decoding

(Upper

capacities

as

follows:

controller

be

addressed

sockets

of

Chip

the

that

this

memory

Select)

starting

Starting

FCOOO(H)

F8000(H)

FOOOO(H)

board,

by

other

can

signal.

addresses

Address

a

total

MULTIBUS

support

portion

of

Page 39

PROGRAMMING

INFORMATION

OFFFFF(H)

FCOOO(H),

2764

EPROM/

FBOOO(H),

2712B

FOOOO

27256

EPROM/

(H),

EPROM

BOIB6

Microprocessor

~-===

__

~

UCS

64K

Bytes

/

On-Board

Memory

16/32~64

K

Bytes

EPROM

MULTI

BUS

FFBOOO(H)

-:..-

- - - -

32K

Bytes

'------

FSOOOO(H)

OFFFFF

(H)

I

Figure

LCS

12BK

4-1.

Bytes

iSBC

64K

Dual

Dual-ported

MULTIBUS

or

FBOOOO(H)

boundary.

546/547/548

4-2

Bytes

Port

RAM

RAM

RAM

between

and

Boards

r:,.-

- - - -

32K

Bytes

--

- - - -

OSOOOO(H) ~ ______

NOTE

can

be

accessed

SOOOO(H)

FFBOOO(H)

Memory

and

on

Map

FSOOO(H)

any

on

~

the

32K

Page 40

PROGRAMMING

CONSIDERATIONS

master

boards.

MULTIBUS

and

F8000(H)

jumper

determined

default

boards

4.4

the

PROGRAMMING

sections

for

the

4.4.1

The

FIRMWARE

firmware

Appendix

description

The

80186

control

controls

channel

transmitted

MULTIBUS

enable

and

channels

The

interface

or

between

see

starting

address

default

CONSIDERATIONS

4.4.1

three

B

through

controller

for

of

this

of

firmware

the

microprocessors

eight

four

is

host

looking

serial

serial

communicated

to

the

informs

which

not.

for

dual-ported

at

any

32K

F80000

Appendix

is

starting

4.4.3

boards

controller

manual.

The

operation.

on

data

data

channel

data

to

the

The

channels.

channels.

the

is

controller's

80186

or

RAM

can

boundary

and

FF8000.

A).

For

OFAOOOO(H).

address

discuss

is

the

boards

following

the

iSBC 547

The

The

MULTI

BUS

received

continuously

the

request

be

addressed

starting

The

the

iSBC 546

For

the

between

starting

iSBC 547

OF90000(H).

programming

is

described

paragraphs

and

iSBC 548

80186

data

host

from

80186

on

received

and

the

MULTIBUS

which

polls

for

data.

from

board

considerations

in

detail

provide

boards

the

iSBC 546

from

the

data

channels

the

enabled

the

80000(H)

address

the

and

548

in

a

brief

the

host.

to