Page 1

inter

iSBC

432/100™

Processor

Board

Hardware

Reference

Manual

PN

171820-001

Page 2

I I

11

11

I

iSBC

PROCESSOR

432/100™

BOARD

HARDWARE REFERENCE MANUAL

Manual Order Number:

171820-001

11

I

Intel Corporation,

Copyright©

3065

1981

Bowers Avenue, Santa Clara, California

Intel Corporation

95051

Page 3

Additional copies

Literature Department

Intel Corporation

3065

Bowers Avenue

Santa

Clara, CA

of

this manual or other Intel literature may

95051

be

obtained from:

The information

Intel Corporation makes no warranty

to, the implied warranties

assume<,

-:ommitment to update nor to keep current the information contained

Intel Corporation assumes no responsibility for the use

in

this document

is

subject to change without notice.

of

of

merchantability and fitness for a particular purpose. lniel Corporation

any kind with regard to this material. including, but not limited

no responsibility for any errors that may appear

in

this document. Intel Corporation

in

this document.

of

any circuicry other than circuitry embodied

make~

no

in

an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted

duplication or disclosure

is

subject to restrictions stated

by

and shall remain the property

in

Intel's software license, or as defined

of

Intel Corporation. Lse,

in

ASPR

7-104.9(a)(9).

No

part of this document may

written consent of

Intel Corporation.

The follo,,ing are trademarks of Intel Corporation and its affiliate' and may

be

copied or reproduced

in

any form or

by

any means without the prior

be

used only to identify Intel

products:

BXP

CRI

IC!:-

iCS

lrPt'i

inr

and the combination

DIT

el

of

ICE. iCS. iR\1X. iSBC. iSBX, l\1CS. or R\1X and a numerical suffix.

lntde1i,ion

Intel

le.:

iR~I\

iSHC

iSHX

I

ihrrir'.··

\h1naL~er

\1CS

\1egd~·ha\.."1i\

\licrnnwr

\luliihu'

\lultimoduk

Plu~-A.-Buhhlf

PRO\IPT

Prol1l\\arc

R\1\

~o

~htcn,

~non

LJl'I

~score

ii

Page 4

This

manual

and principles

hardware/

available in the following documents:

•

iAPX

171860-001.

• Intel

Appiication

contains general information, installation, programming information,

of

operation

architectural information pertaining to the iSBC

for the Intel iSBC

432/

100 Processor Board. Additional

432 General Data Processor Architecture Reference Manual, Order No.

8251

Universal Synchronous/ Asynchronous Receiver/Transmitter,

Note

AP-i6.

• Intel Multibus Specification, Order No 9800683.

• Intel Multibus Interfacing, Application Note AP-28.

432/

PREFACE

100

board

is

Introductory

documents:

• The

• Introduction to the

• GettingStartedontheintellec432/JOO,

• Object Builder User's Guide,

iAPX

432 information, if required,

iAP

X 432 Object Primer, Order No. 171858-001.

iAPX

432 Architecture, Order No. 171821-001.

OrderNo.171819-001.

Order

No. 171859-001.

is

contained

in

the following

• Object Programming Language User's Manual, Order No. 171823-001.

iii

Page 5

Page 6

.

~

n

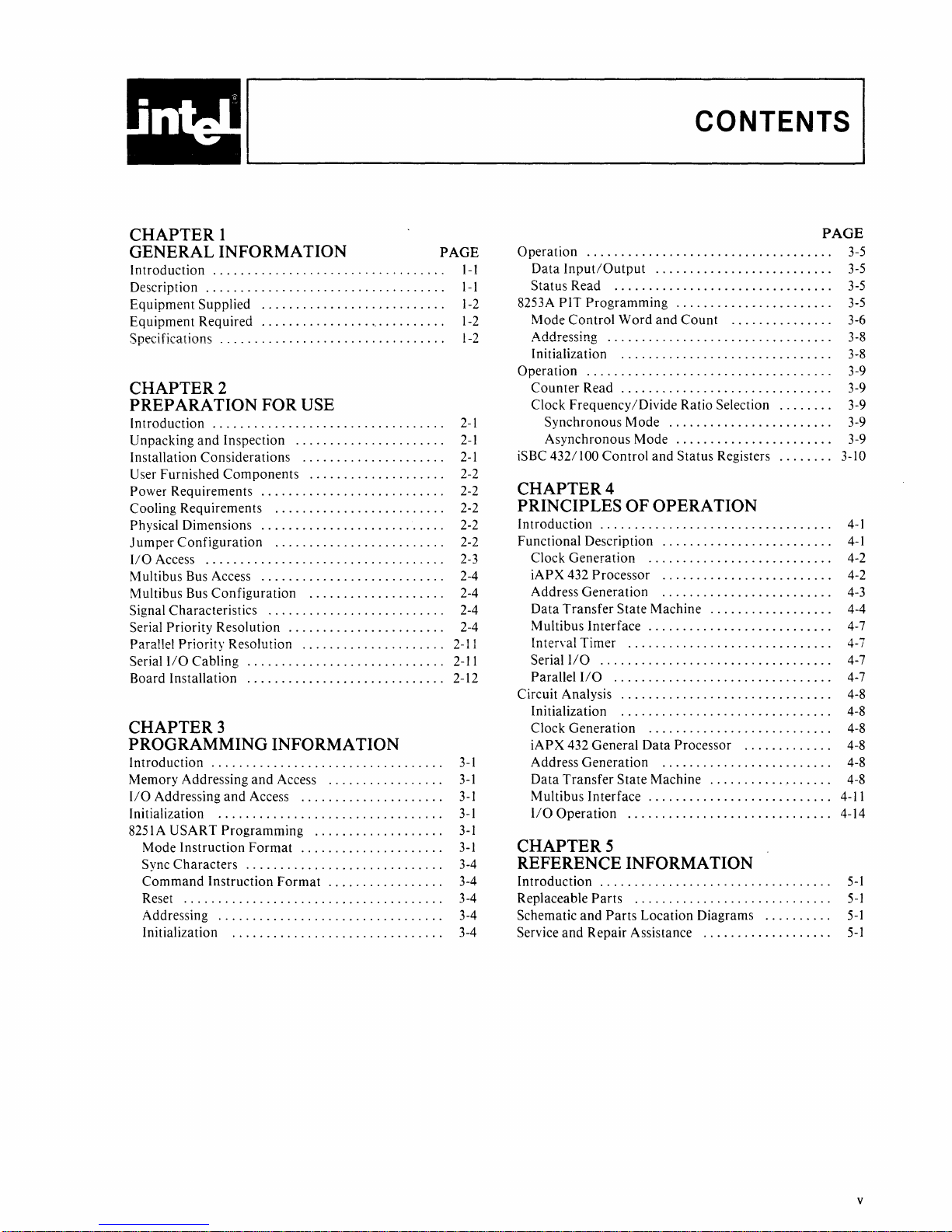

CHAPTER 1

GENERAL

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Equipment Supplied . . . . . . . . . . . . . . . . . . . . . . . . . . . l-2

Equipment Required . . . . . . . . . . . . . . . .

Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . !-2

CHAPTER2

PREPARATION

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-l

Unpacking and Inspection . . . . . . . . . . . . . . . . . . . . . .

Installation Considerations . . . . . . . . . . . . . . . . . . . . . 2-l

User Furnished Components . . . . . . . . . . . . . . . . . . . .

Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . .

Cooling Requirements . . . . . . . . . . . . . . . . . . . . . . . . .

Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . .

Jumper Configuration . . . . . . . . . . . . . . . . . . . . . . . . .

1/0

Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Multibus

Multibus

Signal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Priority Resolution . . . . . . . . . . . . . . . . . . . . . . .

Parallel Priority Resolution

Serial

1/0

Board Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CHAPTER3

PROGRAMMING

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-l

Memory Addressing and Access . . . . . . . . . . . . . . . . .

1/0

Addressing and Access . . . . . . . . . . . . . . . . . . . . .

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-l

USART Programming . . . . . . . . . . . . . . . . . . .

8251A

Mode Instruction Format . . . . . . . . . . . . . . . . . . . . .

Sync Characters . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Command Instruction Format . . . . . . . . . . . . . . . . .

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

INFORMATION

..

. . . . . . . . . . l-2

FOR

USE

Bus

Access . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bus

Configuration . . . . . . . . . . . . . . . . . . . .

.....................

Cabling . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

INFORMATION

PAGE

l-1

l-l

2-1

2-2

2-2

2-2

2-2

2-2

2-3

2-4

2-4

2-4

2-4

2-l l

2-11

2-12

3-1

3-1

3-1

3-1

3-4

3-4

3-4

3-4

3-4

CONTENTS

PAGE

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8253A PIT Programming . . . . . . . . . . . . . . . . . . . . . . .

Mode Control Word and Count . . . . . . . . . . . . . . .

Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Counter Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clock Frequency/Divide Ratio Selection . . . . . . . .

Synchronous Mode

Asynchronous Mode

iSBC

432/

100

Control and Status Registers . . . . . . . .

........................

.......................

CHAPTER4

PRINCIPLES

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . 4-l

Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . .

iAPX

432

Address Generation . . . . . . . . . . . . . . . . . . . . . . . . .

Data Transfer State Machine . . . . . . . . . . . . . . . . . .

Multibus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interval Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial

1/0

Parallel

Circuit Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . .

iAPX

432

Address Generation . . . . . . . . . . . . . . . . . . . . . . . . .

Data Transfer State Machine . . . . . . . . . . . . . . . . . .

Multibus Interface

1/0

Operation

OF

OPERATION

Processor . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1/0

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

General Data Processor . . . . . . . . . . . . .

...........................

..............................

CHAPTERS

REFERENCE

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Replaceable Parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Schematic and Parts Location Diagrams . . . . . . . . . .

Service and Repair Assistance . . . . . . . . . . . . . . . . . . .

INFORMATION

3-5

3-5

3-5

3-5

3-6

3-8

3-8

3-9

3-9

3-9

3-9

3-9

3-10

4-1

4-2

4-2

4-3

4-4

4-7

4-7

4-7

4-7

4-8

4-8

4-8

4-8

4-8

4-8

4-11

4-14

5-1

5-1

5-1

5-1

v

Page 7

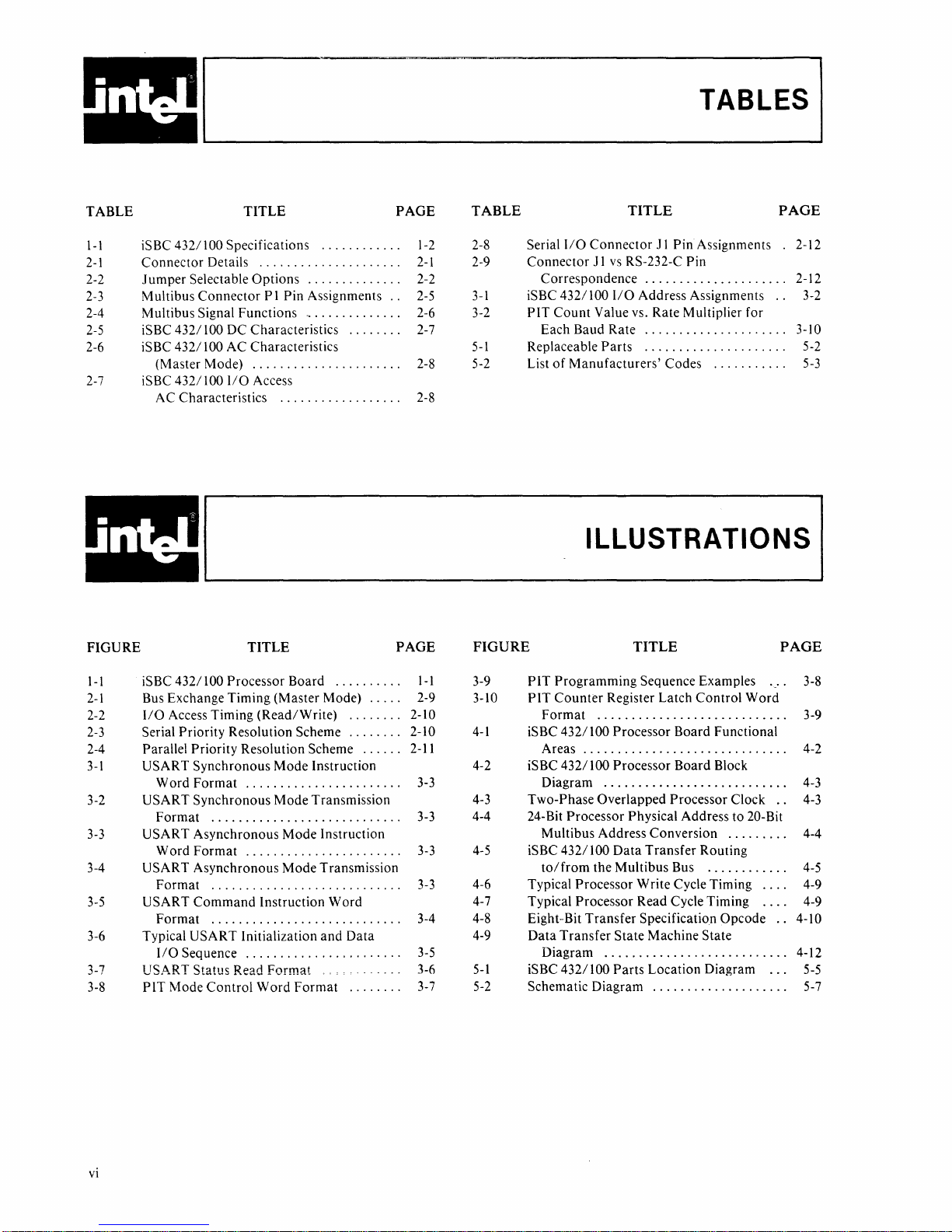

TABLES

TABLE

1-1

2-1

2-2

2-3

2-4

2-5

2-6

2-7

FIGURE

TITLE PAGE

iSBC

432/

100

Specifications . . . . . . . . . . . .

Connector Details . . . . . . . . . . . . . . . . . . . . .

Jumper Selectable Options . . . . . . . . . . . . . .

Multibus Connector P 1 Pin Assignments . .

Multibus Signal Functions

iSBC

432/

100

DC

Characteristics . . . . . . . .

iSBC

432/

100

AC

Characteristics

(Master Mode) . . . . . . . . . . . . . . . . . . . . . .

iSBC

432/

100

l/O

Access

AC

Characteristics . . . . . . . . . . . . . . . . . .

TITLE

-.

. . . . . . . . . . . . .

1-2

2-1

2-2

2-5

2-6

2-7

2-8

2-8

PAGE

TABLE

2-8

2-9

3-1

3-2

5-1

5-2

FIGURE

TITLE

Serial

l/O

Connector J 1 Pin Assignments

Connector J 1

Correspondence . . . . . . . . . . . . . . . . . . . . . 2-12

iSBC

432/

PIT Count Value vs. Rate Multiplier for

Each Baud Rate . . . . . . . . . . . . . . . . . . . . . 3-10

Replaceable

List of Manufacturers' Codes . . . . . . . . . . .

vs

RS-232-C Pin

100

l/O

Address Assignments . .

Parts . . . . . . . . . . . . . . . . . . . . .

PAGE

ILLUSTRATIONS

TITLE

PAGE

2-12

3-2

5-2

5-3

1-1

2-1

2-2

2-3

2-4

3-1

3-2

3-3

3-4

3-5

3-6

3-7

3-8

iSBC

432/

100

Processor Board

Bus

Exchange Timing (Master Mode)

I/O

Access Timing (Read/Write)

Priority Resolution Scheme

Serial

Parallel Priority Resolution Scheme

USART Synchronous Mode Instruction

Word Format

USART Synchronous Mode Transmission

Format

USART Asynchronous Mode Instruction

Word Format

USART Asynchronous Mode Transmission

Format

USART Command Instruction Word

Format

Typical

USART Status Read Format

PIT Mode Control Word Format

USART Initialization and Data

I/O

Sequence

......................

...........................

......................

...........................

...........................

......................

....

.......

.......

.....

.......

.

.

.

.

.

.

.

.

.

.

.

1-1

2-9

2-10

2-10

2-11

3-3

3-3

3-3

3-3

3-4

3-5

3-6

3-7

3-9

3-10

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

5-1

5-2

PIT Programming Sequence Examples

PIT Counter Register Latch Control Word

Format . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iSBC

432/

100

Processor Board Functional

Areas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iSBC 4321100 Processor Board Block

Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . .

Two-Phase Overlapped Processor Clock . .

24-Bit Processor Physical Address to 20-Bit

Multibus Address Conversion . . . . . . . . .

iSBC

432/

100

Data Transfer Routing

to/from

Typical Processor Write Cycle Timing . . . .

Typical Processor Read Cycle Timing . . . .

Eight--Bit Transfer Specification Opcode

Data Tran sf er State Machine State

Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . .

iSBC

Schematic Diagram . . . . . . . . . . . . . . . . . . . . 5-7

the Multibus Bus . . . . . . . . . . . .

432/100 Parts Location Diagram . . .

..

3-8

3-9

4-2

4-3

4-3

4-4

4-5

4-9

4-9

4-10

4-12

5-5

vi

Page 8

CHAPTER 1

1.1

INTRODUCTION

The

iSBC

432/100

compatible

mainframe,

board

Intellec

board

communications

Multibus

interfacing with

implementation

is

designed

microcomputer

contains

control

Processor

a 32-bit VLSI microprocessor. This

to

operate

systems.

an

iAPX

432 microprocessor, a serial

interface,

logic,

and

other

Multibus-compatible

1.2 DESCRIPTION

The iSBC

controlled by

(GDP).

43201

the

Instruction Execution Unit.

set supports a wide range

and

efficient

iSBC 432/100

bus for all

The

data

manipulation

and

memory

432/

100 Processor Board (figure 1-1)

an

iAPX

432 General

GDP

consists

Instruction

secure protection mechanisms.

board

and

of

Decode Unit

of

operations, as well as highly

accesses the Multibus system

1/0

Board

of

as a Multibus master in

programmable

bus expansion drivers for

two VLSI components:

The

data

operations.

is

a Multibus-

the

iAPX

432 Micro-

The

iSBC 432/100

boards.

Data

Processor

and

the 43202

GDP's

addressing modes

instruction

timers,

is

The

GENERAL

An

RS-232-C

by an Intel 8251A

Asynchronous Receiver

standard

19.2K

grammable for

asynchronous serial

(including IBM Bi-sync). In operation, most

transmission characteristics (e.g., character length,

parity,

In

the serial 110

double

addition,

for parity,

transmit

programmable

control lines, serial

are

upper right

or

connector).

CRT

bits/second.

and

both

the

buffered

USART

and

brought

round

baud

synchronous

overrun,

out

corner

cable

INFORMATION

compatible

USART

terminals

operation

rate) are

port

transmit

error

receive clocks are supplied by a

baud

to a 26-pin edge connector (in the

of

(through a standard

serial 110

(Universal

/Transmitter),

at

baud

The

USART

in many synchronous

data

programmable.

and

features half-

and

detection circuits can check

and

framing errors.

rate

generator.

data

lines,

the

board)

port,

Synchronous/

operates with

rates from 110 to

is

individually pro-

transmission

asynchronous

or

receive capability. In

The

The

and

signal

ground

that

mates with flat

controlled

formats

full-duplex,

USART

RS-232-C

board

and

modes,

lines

edge

Figure 1-1. iSBC

432/

1

OO'M

Processor Board

171820-1

1-1

Page 9

General Information

Three

programmable

16-bit interval timers are pro-

vided by

an

Intel 8253

Programmable

Interval Timer

(PIT). All three timers are reserved for processor

time base generation

and

serial

I/O

baud

rate genera-

tion. Additional

on-board

l/O

registers, containing

processor control

and

status information, may be

accessed from the Multibus bus.

The

iSBC 432/100

board

provides full Multibus arbi-

tration

control

logic. This control logic allows up to

three bus masters to share the Multibus bus in serial

(daisy-chain) fashion

or

up

to

16

bus masters

to

share

the Multibus bus using

an

external parallel priority

resolution network.

The

Multibus

aribtration

logic

operates synchronously with the bus clock, which

is

derived from

another

Multibus master

or

generated

by customer supplied logic. (The

iSBC 432/100

board

does

not

generate the bus clock signal.)

Data

is

transferred by means

of

a handshake between the

controlling master

and

the addressed bus module.

This arrangement allows different speed controllers

to share resources

on

the same bus,

and

transfers via

the bus proceed asynchronously. The transfer speed

is

dependent

on

the transmitting

and

receiving

devices only. This design prevents slower master

modules from being handicapped in their attempts to

iSBC 432/100

gain control

of

the bus,

but

does not restrict the

speed

at

which faster modules can transfer

data

over

the same bus.

1.3 EQUIPMENT SUPPLIED

The following items are supplied with the iSBC

432/

100

Processor Board:

a.

Schematic diagram, drawing no. 171773

b. Assembly drawing, drawing no. 171826

1.4 EQUIPMENT REQUIRED

The iSBC

432/

100 Processor Board

is

designed to

operate in

an

Intellec 800, Intellec Series II, or

Intellec

Series III Microcomputer Development

System.

1.5

SPECIFICATIONS

Specifications

of

the iSBC

432/

100

Processor Board

are listed in table 1-1.

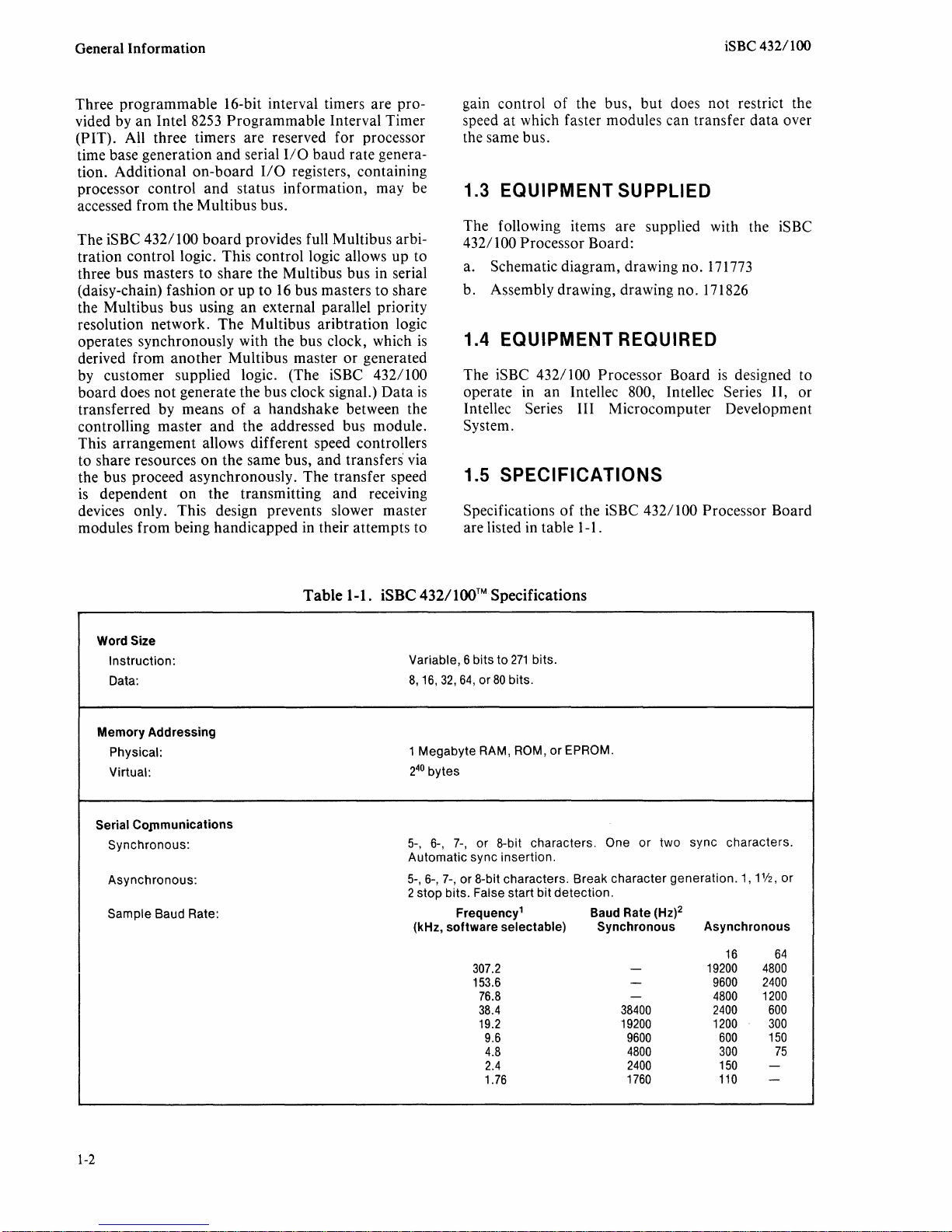

Table 1-1. iSBC 432/100™ Specifications

Word Size

Instruction:

Variable, 6 bits

to

271

bits.

Data:

8,

16,

32,

64,

or

80

bits.

Memory

Addressing

Physical:

1

Megabyte

RAM, ROM,

or

EPROM.

Virtual:

2

40

bytes

Serial

Cojllmunications

Synchronous:

5-,

6-,

7-,

or

8-bit characters. One

or

two

sync

characters.

Automatic sync

insertion.

Asynchronous:

5-,

6-,

7-,

or

8-bit characters. Break

character

generation.

1,

11/2,

or

2

stop

bits. False start bit

detection.

Sample Baud Rate:

Frequency

1

Baud Rate (Hz)

2

(kHz,

software

selectable)

Synchronous

Asynchronous

16

64

307.2

-

19200

4800

153.6

-

9600

2400

76.8

-

4800

1200

38.4

38400

2400

600

19.2

19200

1200

300

9.6

9600

600

150

4.8

4800

300

75

2.4

2400

150

-

1.76

1760

110

-

1-2

Page 10

iSBC 432/100

General Information

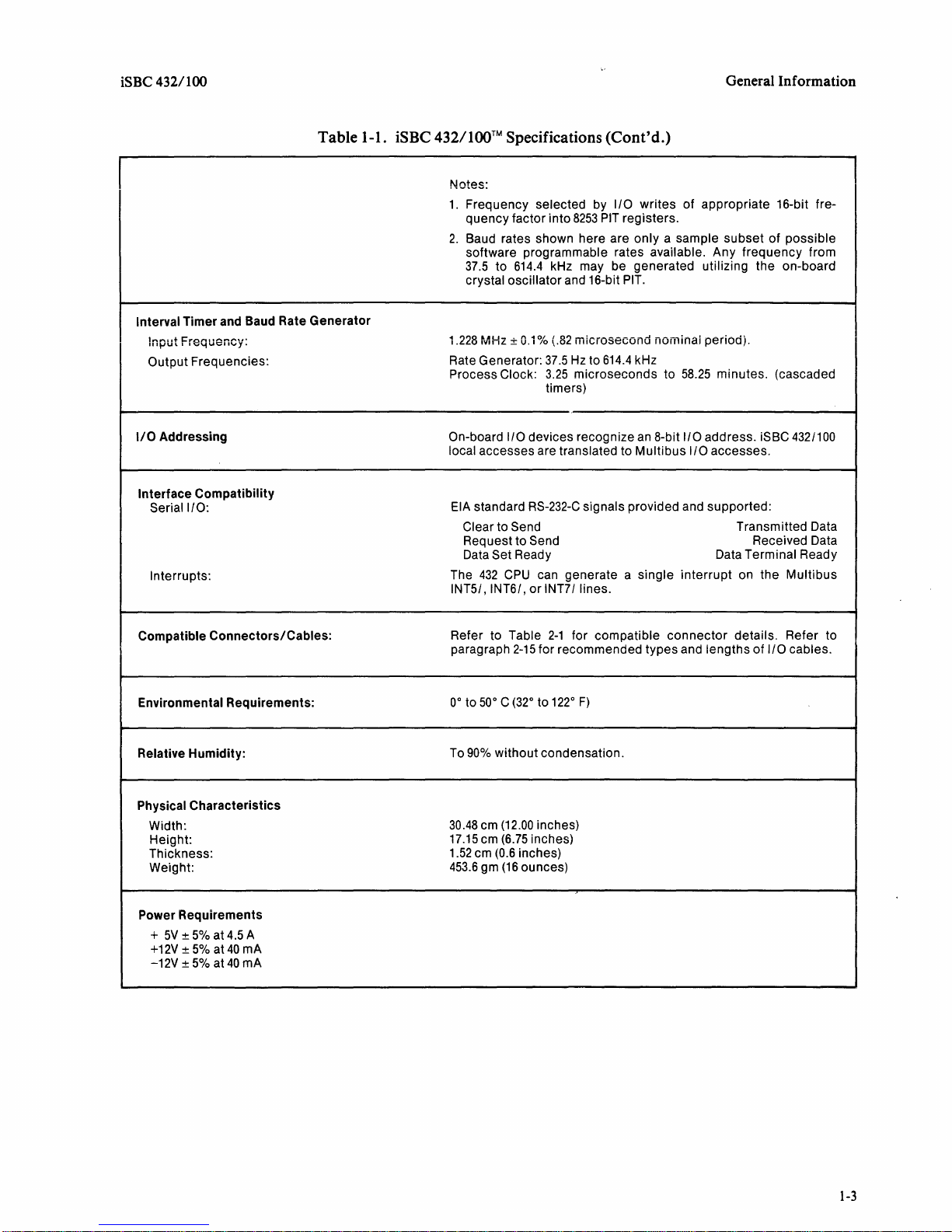

Table 1-1. iSBC 432/100™ Specifications

Interval Timer and Baud Rate Generator

Output Frequencies:

1/0

Addressing

Interface Compatibility

Serial 1/0:

Interrupts:

(Cont'd.)

Notes.

1.

Frequency selected by 1/0 writes of appropriate 16-bit frequency factor into

2.

Baud rates shown here are only a sample subset

software programmable rates available. Any frequency from

37.5

to

crystal oscillator and 16-bit

1.228

Rate Generator:

Process

On-board

local accesses are translated to Multibus 1/0 accesses.

EIA

Clear to Send

Request to Send

Data Set Ready

The

INT5/, INT6/,

614.4

MHz±

0.1%

Clock:

1/0 devices recognize

standard

432

CPU

8253

PIT

registers.

of

possible

kHz may be generated utilizing the on-board

(.82

micmsecond nominai period).

37.5

Hz

3.25

microseconds to

timers)

RS-232-C

can generate a single interrupt on the Multibus

or INT7/ lines.

PIT.

to

614.4

kHz

58.25

minutes. (cascaded

an

8-bit 1/0 address. iSBC

signals provided and supported:

Transmitted Data

Received Data

Data Terminal Ready

432/100

Compatible

Environmental Requirements:

Relative Humidity:

Physical Characteristics

Width:

Height:

Thickness:

Weight:

Power Requirements

+

+12V

-12V

Connectors/Cables:

5V

5%

at

4.5

5%

at

40

5%

at

40

A

mA

mA

Refer to Table

paragraph

0°

to

To

90%

30.48

17.15

1.52

453.6

2-15

50° C (32°

without condensation.

cm

(12.00

cm

(6.75

cm

(0.6

inches)

gm

(16

ounces)

2-1

for compatible connector details. Refer to

for recommended types and lengths of 1/0 cables.

to

122°

F)

inches)

inches)

1-3

Page 11

Page 12

2.1

INTRODUCTION

This

chapter

provides instructions

for

configuring

the

iSBC

432/

100

Processor

Board

for

operation

in a

user-defined

environment.

It

is

advisable

that

the

contents

of

Chapters 1 and

3 be fully

understood

before

beginning the

configuration

and

installation

procedures described in this

chapter.

2.2

UNPACKING

AND

INSPECTION

Inspect the shipping

carton

immediately

upon

receipt

for evidence

of

mishandling

during

transit.

If

the

shipping

carton

is

severely

damaged

or

waterstained,

request

that

the

carrier's

agent

be present when the

carton

is

opened.

If

the

carrier's

agent

is

not

present

when the

carton

is

opened

and

the contents

of

the

carton

are

damaged,

keep the

carton

and

packing

material

for

the

agent's

inspection.

CHAPTER 2

PREPARATION

FOR

USE

For

repairs

to a product

damaged

in shipment, refer

to the

customer

letter

contained

in

the

shipping car-

ton.

It

is

suggested

that

salvageable shipping

cartons

and

packing

material

be

saved

for

future use in the

event the

product

must

be

reshipped.

2.3 INSTALLATION

CONSIDERATIONS

The

iSBC

432/

100

board

is

designed for use as a bus

master in

an

lntellec 800, Intellec Series II,

or

Intellec

Series III

Microcomputer

Development System.

Important

criteria

for

installing

and

interfacing the

iSBC

432/

100

board

in

this

configuration

are

presented in the following

paragraphs.

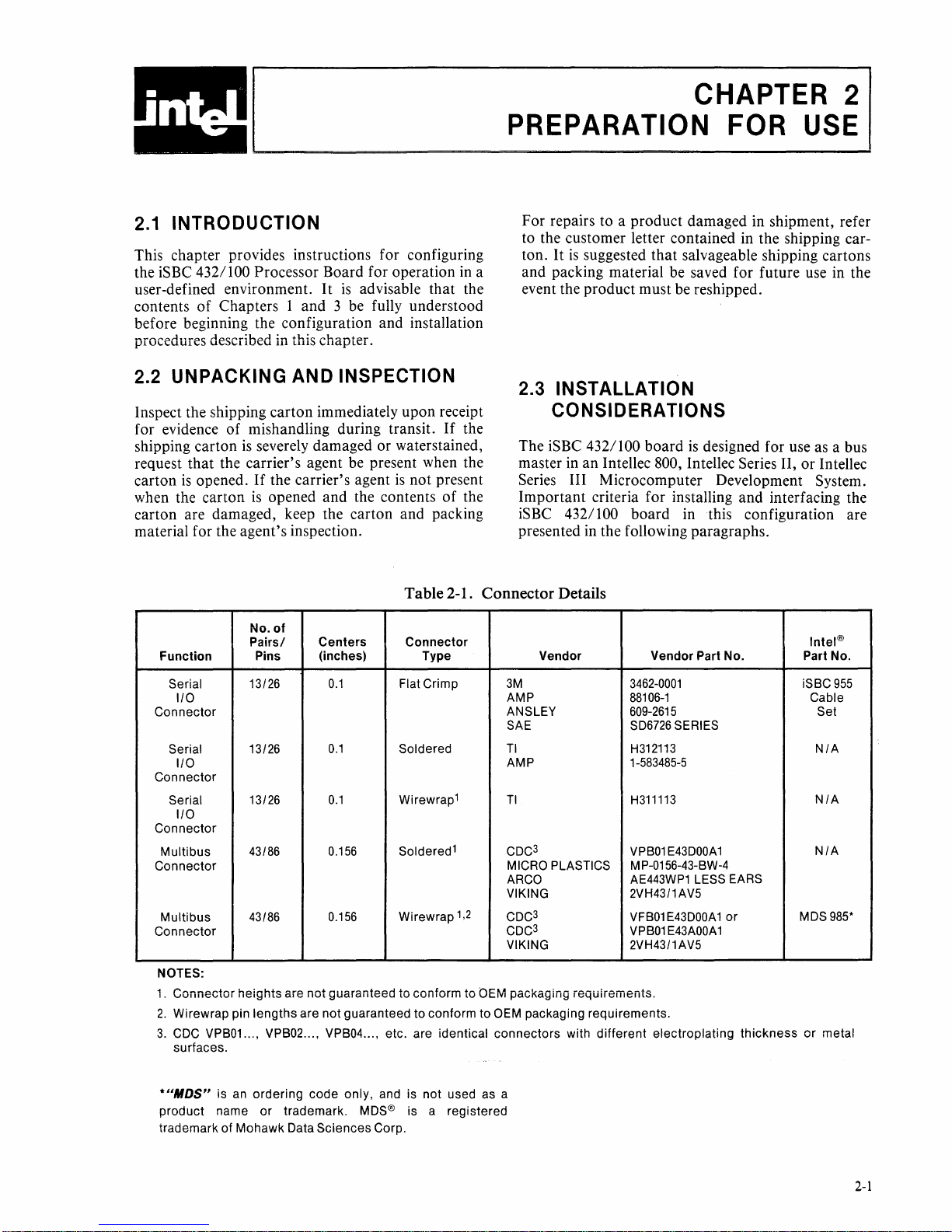

Table 2-1. Connector Details

No.

of

Pairs/

Centers

Connector

Intel®

Function

Pins

(inches)

Type

Vendor

Vendor

Part

No.

Part

No.

Serial 13/26

0.1

Flat

Crimp

3M

3462-0001

iSBC

955

1/0

AMP

88106-1

Cable

Connector

ANSLEY

609-2615

Set

SAE

SD6726 SERIES

Serial

13/26

0.1

Soldered

Tl

H312113

N/A

1/0

AMP 1-583485-5

Connector

Serial

13/26

0.1

Wirewrap1

Tl

H311113

N/A

1/0

Connector

Multibus

43/86

0.156

Soldered1

CDC3

VPB01E43DOOA1

N/A

Connector

MICRO PLASTICS

M P-0156-43-BW-4

ARCO

AE443WP1 LESS EARS

VIKING

2VH43/1AV5

Multibus

43/86

0.156

Wirewrap

1,2

CDC3

VFB01E43DOOA1

or

MDS 985*

Connector

CDC3

VP

801E43AOOA1

VIKING 2VH43/1AV5

NOTES:

1.

Connector heights are not guaranteed to conform to

OEM

packaging requirements.

2.

Wirewrap

pin

lengths

are

not

guaranteed

to

conform

to

OEM

packaging

requirements.

3.

CDC

VPB01

... , VPB02 ... , VP804 ... , etc. are

identical

connectors

with

different

electroplating

thickness

or

metal

surfaces.

*"MOS"

is an

ordering

code

only,

and is

not

used

as a

product

name

or

trademark.

MDS® is a

registered

trademark

of

Mohawk

Data

Sciences

Corp.

2-1

Page 13

:Preparation for Use

2.4

USER

FURNISHED

COMPONENTS

2.7

PHYSICAL

iSBC 432/100

DIMENSIONS

A serial

cable

board

2.5

The

- l

1-1.

2.6

The iSBC 432/100

calories/minute

1/0

must

be installed to interface the processor

to a

CRT

.POWER

iSBC

432/

2V

power supplies

COOLING

connector (see ·table 2-1)

terminal.

REQUIREMENTS

100

board

requires +5V, + l 2V, and

at

the currents listed

REQUIREMENTS

board

(1.33

dissipates 336.5 gram-

BTU/minute),

and

and

RS-232-C

in

table

adequate

circulation must be provided to prevent a

temperature rise above

50° C (122° F). Intellec

systems include fans to provide adequate intake and

exhaust

of

ventilating air.

Table 2-2. Jumper Selectable Options

Fig.

Function

1/0

Base Address

5-1

Grid Ref. Grid Ref.

1B6

Fig.

2C5

5-2

Physical dimensions

of

the iSBC

432/

as follows:

a. Width:

b. Height:

c. Thickness: 1.52 cm

2.8

The iSBC

jumper-selectable options

configure the

30.48 cm (12.00 inches)

17

.15 cm (6.

JUMPER

CONFIGURATION

432/

100 design includes a variety

board

75

inches)

(0.6 inch)

for

his/her

that

allow the user to

particular applica-

tion. Table 2-2 summarizes these options

of

the

grid reference locations

figure

5-1

(parts location diagram)

jumpers

(schematic diagram).

Description

Selects the Multibus base address for on-board

default jumper

value of X is

to table

(79-80*)

determined

3-1

).

Other base addresses are selected as follows:

configures the

by the

address

110

1/0

addresses to

port to be addressed (refer

jumper

100

and

as shown

and

1/0

ports. The

board

are

of

lists the

in

figure 5-2

1X.

The

XACK/Timing

8/16-bit bus access

Bus Lock

I

Processor

Interrupt Signals

•Default jumper configured at the factory

ID

1B8

1B4

187

1C8

1

B7

J

3A6

7C2

2A6

2C4

4D1

7X

6X

5X

4X

3X

2X

1X

The factory default

delay to read and write on-board

not be modified.

Selects 8-or 16-bit Multibus transfer mode. The default

configuration

mode, all Multibus accesses are single-byte accesses. By

jumpering

Default jumper

data transfer. A

many as ten Multibus transfers in

other masters

this jumper and connect

Default jumpr

from

should not be removed.

A board generated interrupt may be routed to one of the

Multibus interrupt lines

86-87*

line is desired. remove this jumper and connect

90-91

45-46,

an

on-board register at

routes the interrupt signal to INT6/. If another

(INT51).

jumper

54-55*

(46-47*)

to

33-34*

selects the ·a-bit transfer mode.

the 16-bit Multibus mode is selected.

65-66*

locks the Multibus bus during each

GDP

initiated data transfer may require as

acquire the bus during GDP transfers, remove

64-65.

permits the

(INT5/, INT6/,

-~

67-68

69-70

71-72

73-74

75-76

77-78

79-80*

provides the

1/0

ports. This

the

GOP

to

1/0

address

or

correct

jumper

8-bit mode. To allow

read its

OOH.

INT?/). Default

88-89

XACK

should

jumper

In

GDP

processor

This

jumper

jumper

interrupt

(INT?/)

this

ID

or

2-2

Page 14

iSBC 432/100

Preparation for

Use

Table 2-2.

Jumper

Selectable Options

(Cont'd.)

Function

Fig.

5-1

I Fig.

5-2

I

Grid Ref. Grid Ref.

Bus Arbitration

1B7

2A4

User Selectable Inputs

1B6

4C5

GDP

Initialization

1C5

4D6

Serial

1/0

Port

1C4

3C2

*Default

jumper

configured at the factory.

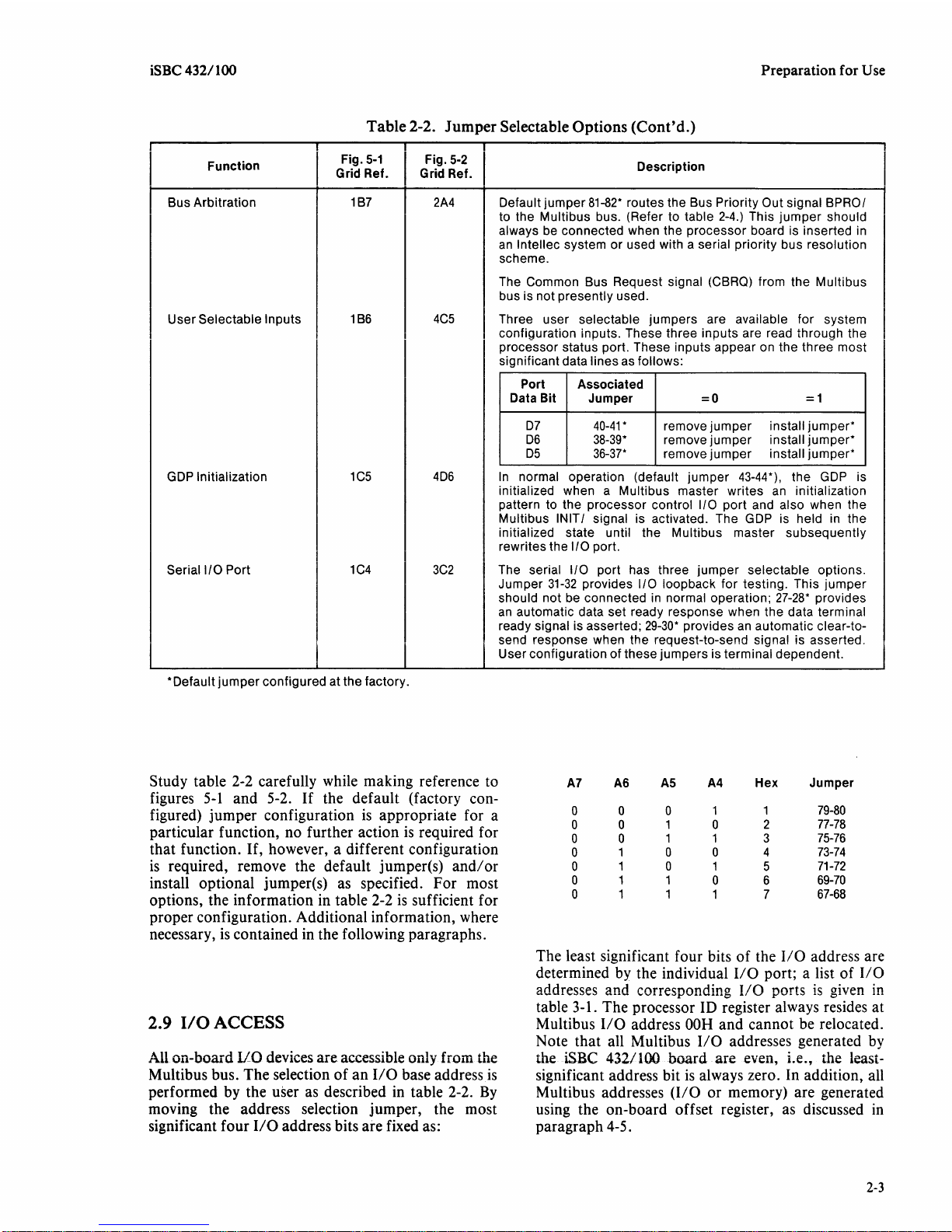

Study table 2-2 carefully while making reference to

figures

5-1

and

5-2.

If

the

default

(factory con-

figured)

jumper

configuration

is

appropriate

for a

particular function, no further action

is

required for

that

function.

If,

however, a different configuration

is

required, remove the default jumper(s)

and/

or

install optional jumper(s) as specified.

For

most

options, the

information

in table 2-2

is

sufficient for

proper

configuration. Additional information, where

necessary,

is

contained in the following paragraphs.

2.9

1/0

ACCESS

All

on-board

1/0

devices

are

accessible only from the

Multibus bus.

The

selection

of

an

1/0

base address

is

performed by the user as described in table 2-2.

By

moving the address selection

jumper,

the most

significant

four

1/0

address bits are fixed as:

Description

Default

jumper

81-82*

routes the Bus Priority Out signal BPRO/

to the Multibus bus. (Refer to table

2-4.)

This

jumper

should

always

be connected when the processor board is inserted in

an

lntellec system

or

used with a serial priority bus resolution

scheme.

The Common Bus Request

signal (CBRQ) from the Multibus

bus is not presently used.

Three user

selectable jumpers are available for system

confiQuration inputs. These three inputs are read throuqh the

processor status port. These inputs

·appear on the

three

most

significant data lines as follows:

Port Associated

Data Bit

Jumper

=0

=1

07

40-41

*

remove

jumper

install jumper*

06

38-39*

remove

jumper

install jumper*

05

36-37*

remove

jumper

install jumper*

In

normal operation (default

jumper

43-44*), the GDP is

initialized when a Multibus master writes

an

initialization

pattern to the processor control 1/0 port and also when the

Multibus INIT I signal is activated. The GDP is held in the

initialized state until the Multibus master subsequently

rewrites the

110

port.

The

serial 1/0 port has three

jumper

selectable options.

Jumper

31-32

provides 1/0 loopback for testing. This

jumper

should not be connected

in

normal operation;

27-28*

provides

an

automatic data set ready response when the data terminal

ready signal is asserted;

29-30*

provides an automatic clear-tosend response when the request-to-send signal is asserted.

User configuration

of

these jumpers is terminal dependent.

A7 A6

AS

A4

Hex

Jumper

0 0 0

1

1

79-80

0 0

1

0

2

77-78

0 0

1 1 3

75-76

0

1 0 0

4

73-74

0

1 0 1

5

71-72

0 1

1

0 6

69-70

0

1 1

1 7

67-68

The least significant four bits

of

the

1/0

address are

determined by the individual

1/0

port; a list

of

1/0

addresses

and

corresponding

I/O

ports

is

given

in

table 3-1.

The

processor ID register always resides

at

Multibus

1/0

address

OOH

and

cannot

be relocated.

Note

that

all Multibus

1/0

addresses generated by

the iSBC 432/

100

board

are even, i.e., the least-

significant address bit

is

always zero. In addition, all

Multibus addresses

(110

or

memory) are generated

using the

on-board

off

set register, as discussed

in

paragraph

4-5.

2-3

Page 15

Preparation for Use

2.10 MULTIBUS BUS ACCESS

The iSBC

432/

100

board

contains no local memory.

All system memory resides

on

separate Multibus

modules. Both system

memory

and

all

1/0

ports

(including

1/0

ports contained

on

the processor

board) must be accessed via the Multibus bus. Each

GDP

access specifies either a local address

or

a

physical address (refer

to

the discussion in

Chapter

3). Local address requests are translated into

Multibus

1/0

commands; physical address requests

are translated into Multibus memory commands.

The

iSBC

432/

100

board

is

designed to operate with

either 8-bit

or

16-bit memory modules. A user-

selectable

jumper

(table 2-2)

is

provided to select the

8-bit

or

16-bit Multibus transfer mode. (The

board

is

factory-configured to operate in the 8-bit mode.)

GDP

memory accesses may require the transfer

of

one to ten

data

bytes over the Multibus bus. In the

8-

bit mode, all

GDP

memory requests initiate a series

of

single-byte read

or

write accesses. In the 16-bit

mode, all

GDP

multibyte memory requests that

originate

on

even byte boundaries are satisfied by a

series

of

double-byte (16-bit) read

or

write accesses.

All

other

accesses are

performed

in the same manner

as are accesses in the 8-bit mode.

When operating with

iSBC/MDS* 016

16K

RAM memory modules, the 8-bit mode must

be used. The 16-bit

mode

may be used with

iSBC/MDS

032/048/064

RAM memory

modules.

As mentioned earlier, a single

GDP

memory request

may require the transfer

of

ten

data

bytes over the

Multibus bus. In

order

to shorten the overall time

required for these

data

transfers, the bus may be

locked from the beginning

of

the first transfer until

the

GDP

memory transfer has been completed.

Locking the bus eliminates the time required

to·

acquire

and

release the bus for each byte

data

transfer. This

"bus

lock"

feature, which results in

higher processor

throughput,

is

user selectable as

described in table 2-2. The processor

board

is

shipped

with the

"bus

lock"

feature enabled.

The bus lock provision

cannot

be enabled in

systems

with

double-density

diskette

controllers and 8-bit memory if the diskette

controller will operate simultaneously with

· the iSBC 432/100

board.

*"lllDS" is

an

ordering code only, and is not used

as

a

product name or trademark.

MOS®

is

a registered

trademark of Mohawk Data Sciences Corp.

2-4

iSBC 432/100

2.11 MULTIBUS BUS CONFIGURATION

For

system applications, the iSBC

432/

100

board

is

designed for installation in a

standard

Multibus

backplane (e.g.,

an

Intellec Microcomputer Develop-

ment

System). Multibus signal characteristics and

methods

of

implementing a serial

or

parallel priority

resolution scheme for resolving bus contention in a

multiple bus master system are described in the

following paragraphs.

Always

turn

off

the system power supply

before installing

or

removing any

board

from the backplane. Failure to observe this

precaution can cause damage to the

board.

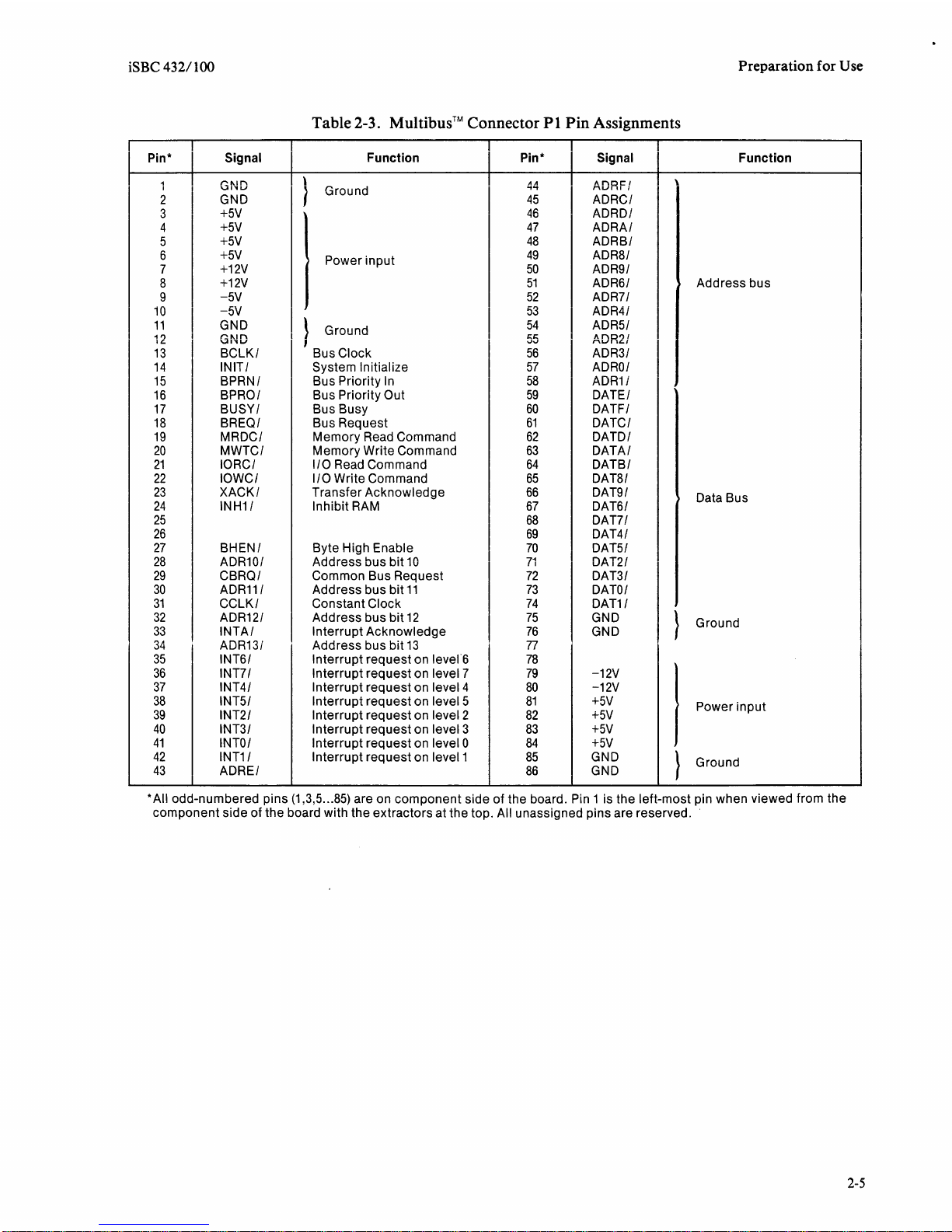

2.12 SIGNAL CHARACTERISTICS

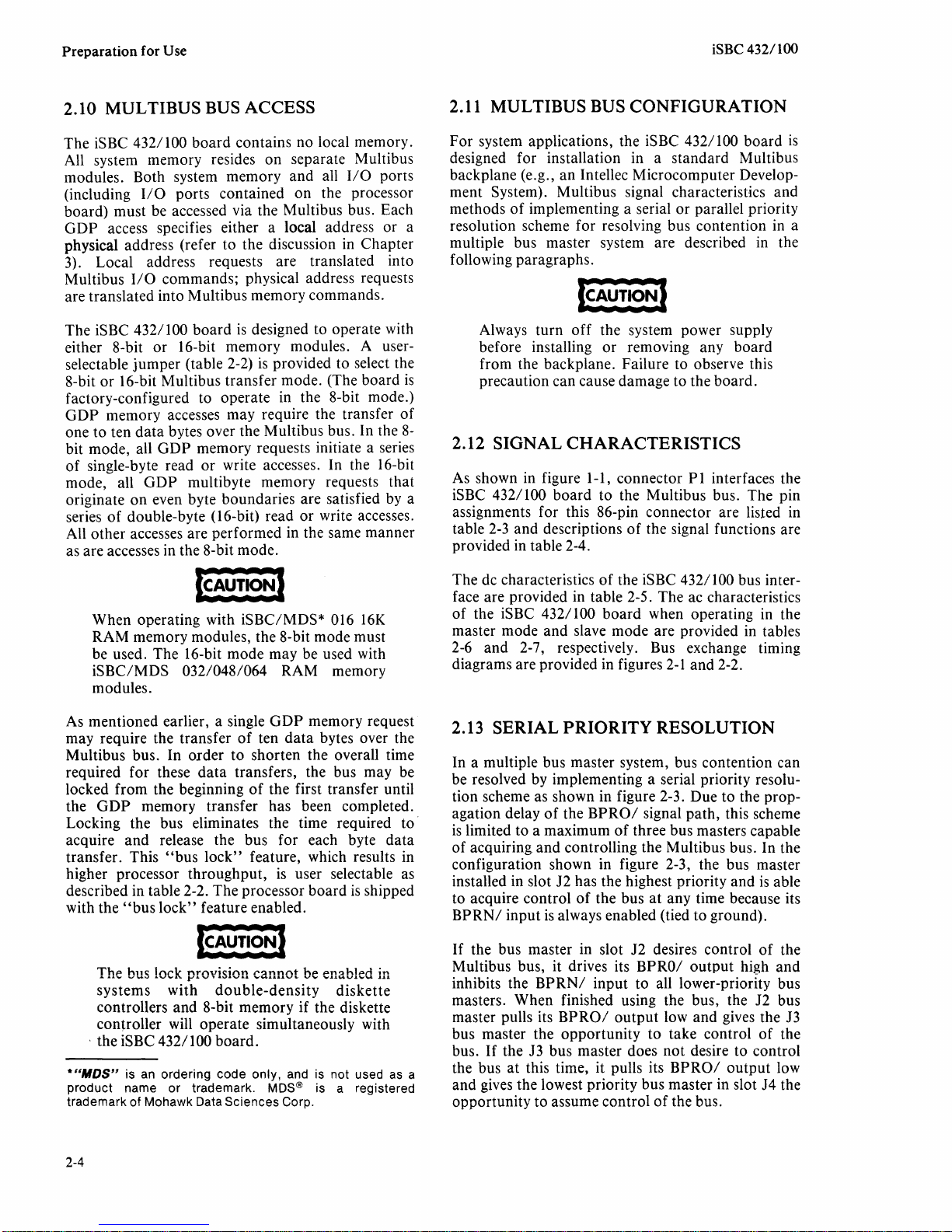

As shown in figure 1-1, connector P 1 interfaces the

iSBC 432/100

board

to the Multibus bus. The pin

assignments for this 86-pin connector are listed in

table

2-3

and

descriptions

of

the signal functions are

provided in table 2-4.

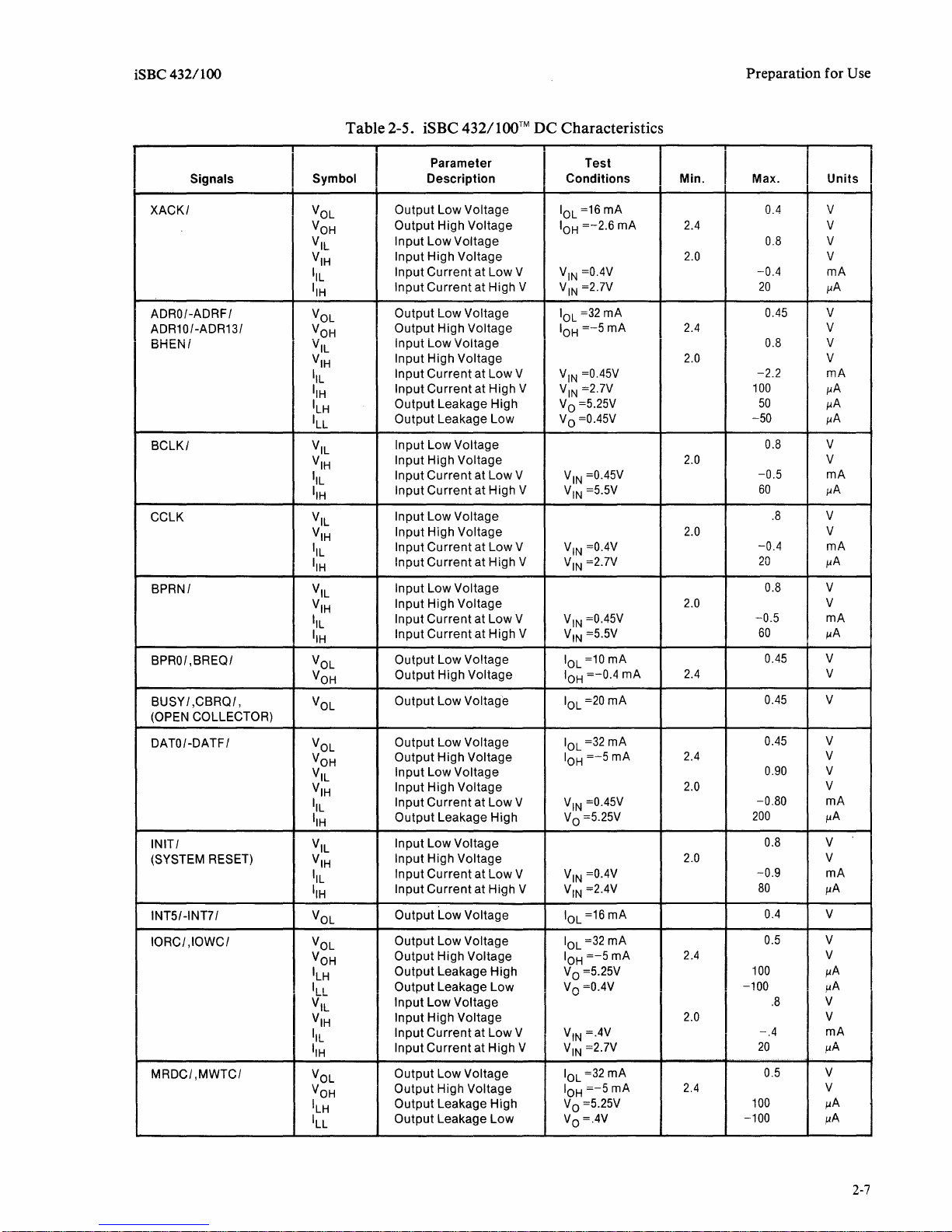

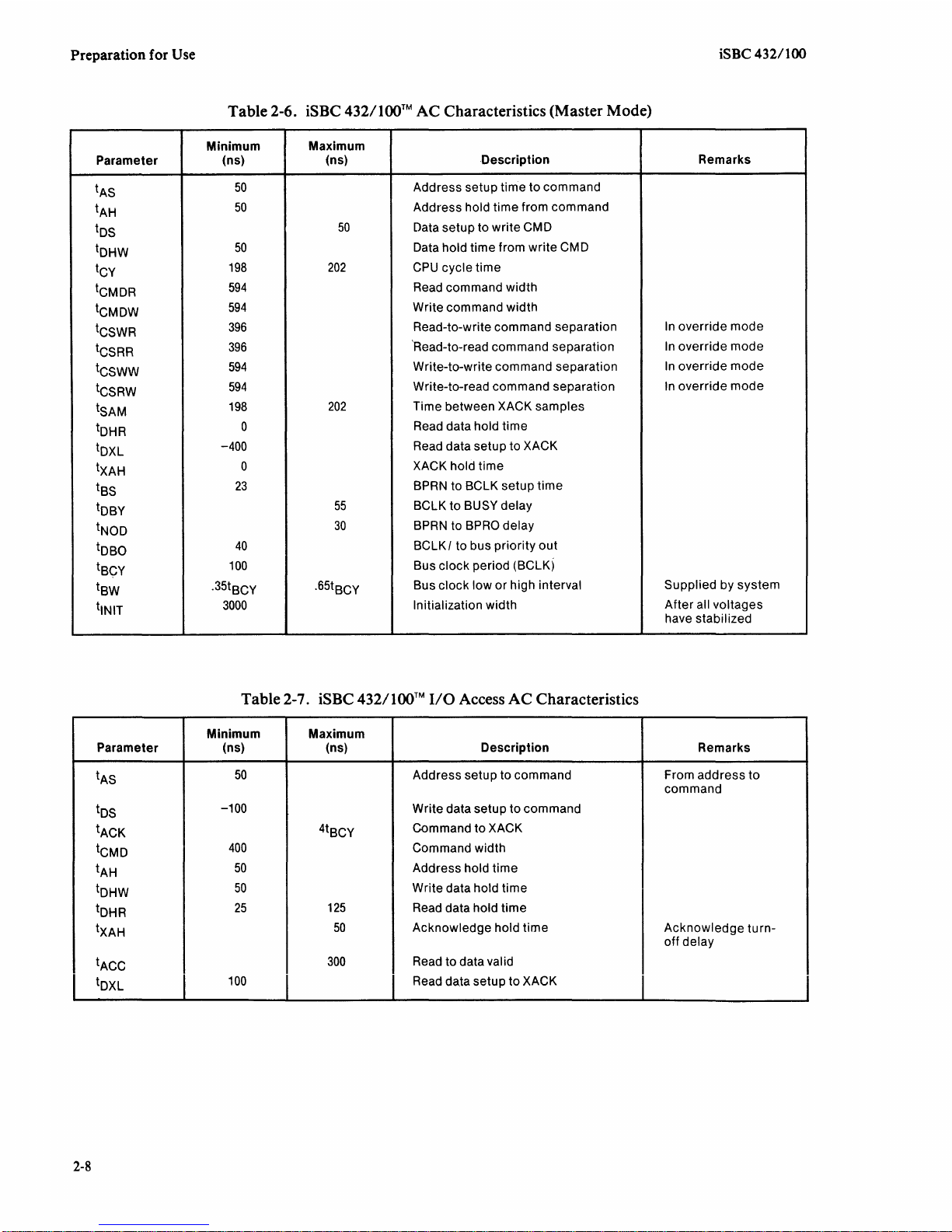

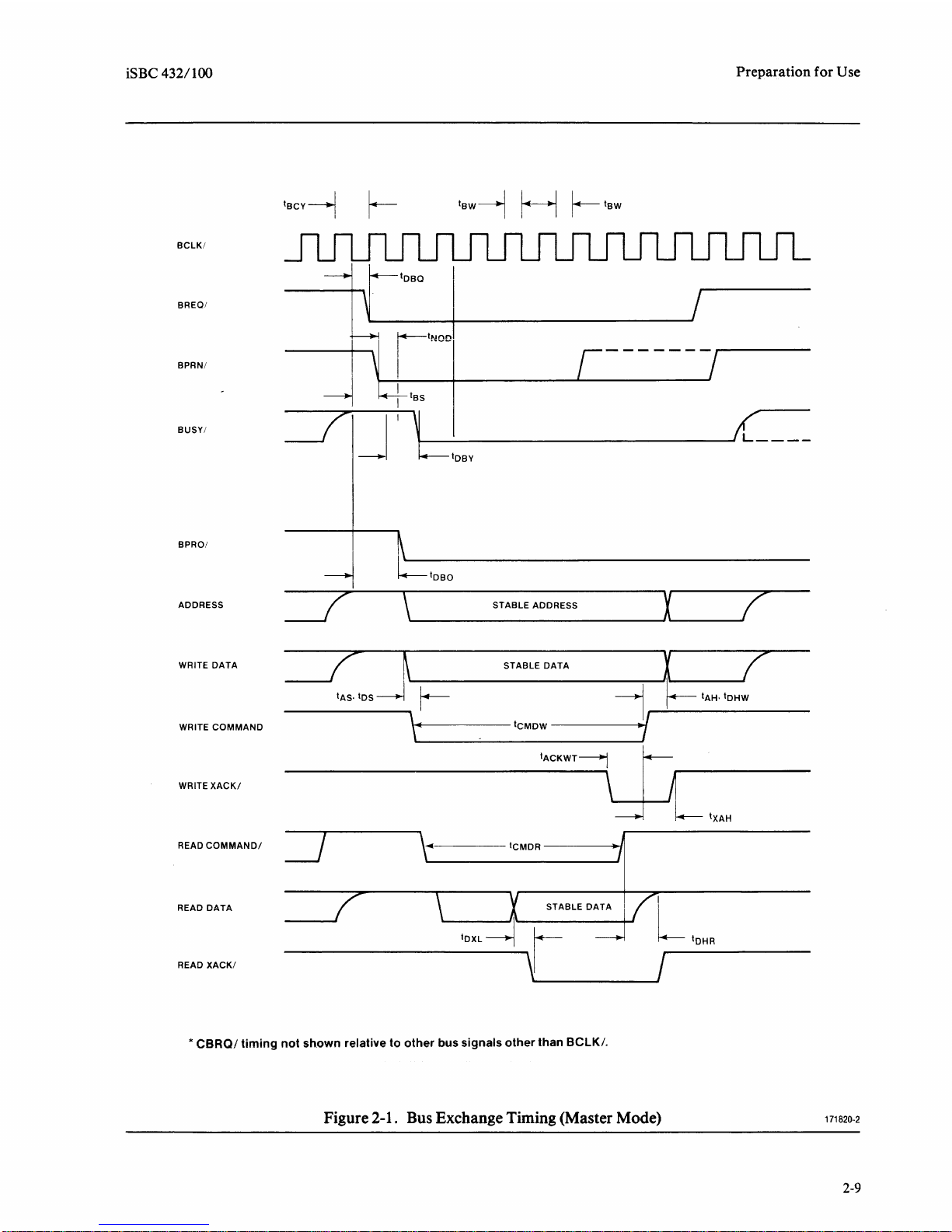

The de characteristics

of

the iSBC

432/

100 bus inter-

face are provided in table 2-5. The ac characteristics

of

the iSBC

432/

100

board

when operating in the

master mode

and

slave mode are provided in tables

2-6

and 2-7, respectively. Bus exchange timing

diagrams are provided in figures

2-1

and 2-2.

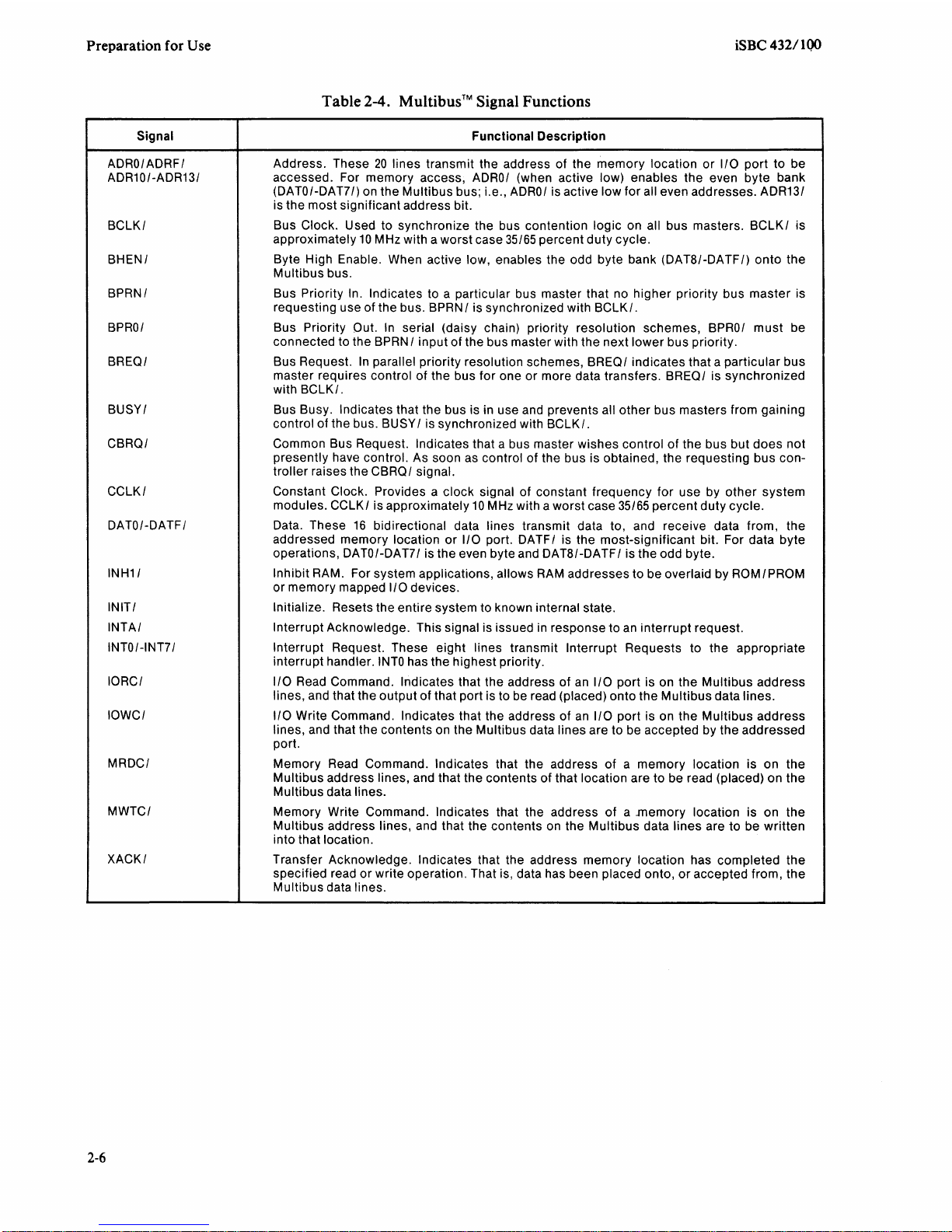

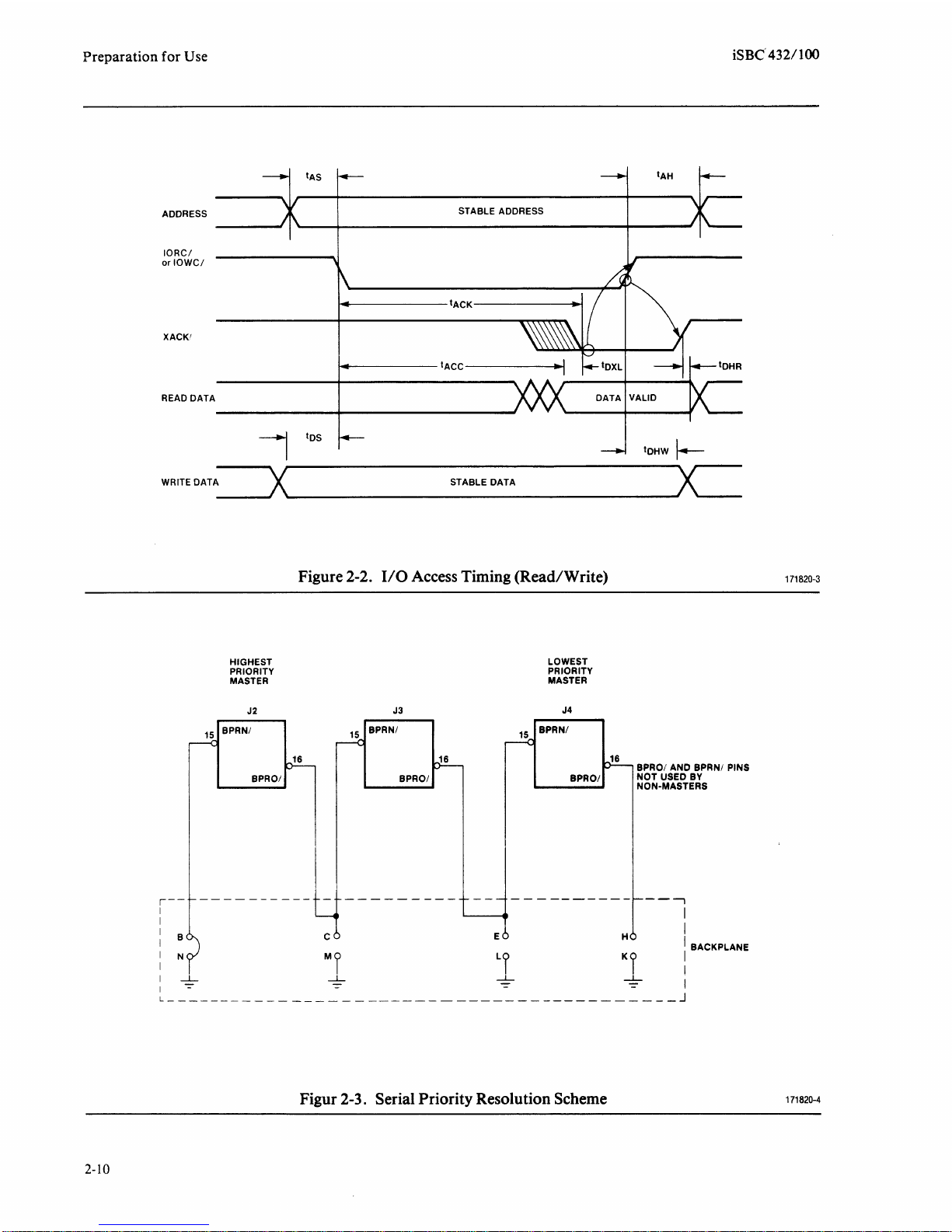

2.13 SERIAL PRIORITY RESOLUTION

In a multiple bus master system, bus contention can

be resolved by implementing a serial priority resolution scheme as shown in figure 2-3. Due to the propagation delay

of

the

BPRO/

signal path, this scheme

is

limited to a maximum

of

three bus masters capable

of

acquiring

and

controlling the Multibus bus. In the

configuration shown in figure 2-3, the bus master

installed in slot J2 has the highest priority

and

is

able

to acquire control

of

the bus

at

any time because its

BPRN/

input

is

always enabled (tied to ground).

If

the bus master in slot J2 desires control

of

the

Multibus bus, it drives its

BPRO/

output

high

and

inhibits the

BPRN/

input

to all lower-priority bus

masters. When finished using the bus, the J2 bus

master pulls its

BPRO/

output

low

and

gives the

J3

bus master the

opportunity

to

take control

of

the

bus.

If

the J3 bus master does

not

desire to control

the bus

at

this time, it pulls its

BPRO/

output

low

and gives the lowest priority bus master in slot J4 the

opportunity to assume control

of

the bus.

Page 16

iSBC 4321100

Preparation for Use

Table 2-3. Multibus™ Connector

Pl

Pin

Assignments

Pin*

Signal Function Pin* Signal

Function

1

I

GND

\

AA

ADRF/

\

I

1

Ground

....

2

GND

45

ADRC/

3

+5V

46

ADRD/

4 +5V

47

ADRA/

5

+5V

48

ADRB/

6

+5V

Power

input

49

ADR8/

7 +12V

50

ADR9/

8

+12V

51

ADR6/

Address

bus

9

-5V

52

ADR7/

10

-5V

53

ADR4/

11

GND

l

Ground

54

ADR5/

1"1

I

GND

I

r::r::

ADR2/

1£.

,

.J.J

13

BCLK/

Bus

Clock

56

ADR3/

14

INIT/

System

Initialize

57

AORO/

15

BPRN/

Bus

Priority

In

58

ADR1i

16

BPRO/

Bus

Priority

Out

59

DATE/

17

BUSY/

Bus

Busy

60

DATF/

18

BREQ/

Bus

Request

61

DATC/

19

MRDC/

Memory

Read

Command

62

DATO/

20

MWTC/

Memory

Write

Command

63

DATA/

21

IORC/

1/0 Read

Command

64

DATB/

22

IOWC/

1/0

Write

Command

65

OATS/

23

XACK/

Transfer

Acknowledge

66

DAT9/

Data

Bus

24

INH1/

Inhibit

RAM

67

DAT6/

25

68

DAT?/

26

69

DAT4/

27

BHEN/

Byte

High

Enable

70

DAT5/

28

ADR10/

Address

bus

bit

10

71

DAT2/

29

CBRQ/

Common

Bus

Request

72

DAT3/

30

AOR11

/

Address

bus

bit

11

73

DATO/

31

CCLK/

Constant

Clock

74

DAT1/

32

ADR12/

Address

bus

bit

12

75

GND

}

Ground

33

INTA/

Interrupt

Acknowledge

76

GND

34

ADR13/

Address

bus

bit

13

77

35

INT6/

Interrupt

request

on

levern

78

36

INT?/

Interrupt

request

on

level 7

79

-12V

37

INT4/

Interrupt

request

on

level 4

80

-12V

38

INT5/

Interrupt

request

on

level 5

81

+5V

Power

input

39

INT2/

Interrupt

request

on

level 2

82

+5V

40

INT3/

Interrupt

request

on

level 3

83

+5V

41

INTO/

Interrupt

request

on level 0

84

+5V

42

INT1 I

Interrupt

request

on level 1

85

GND

}

Ground

43

ADRE/

86

GND

*All

odd-numbered

pins

(1,3,5 ...

85)

are

on

component

side

of

the

board. Pin 1 is

the

left-most

pin

when

viewed

from

the

component

side

of

the

board

with

the

extractors

at

the

top. All

unassigned

pins

are

reserved.

2-5

Page 17

Preparation for Use

iSBC

432/lQO

Table 2-4. Multibus™ Signal Functions

Signal Functional Description

ADRO/ADRF/ Address. These

20

lines transmit the address of the memory location

or

1/0 port to be

AOR10/-ADR13/ accessed. For memory access,

ADRO/

(when active low) enables the even byte bank

(DATO/-DAT71) on the Multibus bus; i.e.,

ADRO/

is active low for all even addresses. ADR13/

is the most significant address bit.

BCLK/ Bus Clock. Used to synchronize the bus contention logic on all bus masters. BCLK/ is

approximately

10

MHz with a worst case 35/65 percent duty cycle.

BHENI

Byte High Enable. When active low, enables the odd byte bank (DAT8/-DATFI) onto the

Multibus bus.

BPRN/

Bus Priority In. Indicates to a particular bus master that no higher priority bus master is

requesting use of the bus. BPRN I is synchronized with BCLK/.

BPRO/

Bus Priority Out.

In

serial (daisy chain) priority resolution schemes,

BPRO/

must be

connected to the

BPRN

I input of the bus master with the next lower bus priority.

BREQ/

Bus Request.

In

parallel priority resolution schemes, BREQ/ indicates that a particular bus

master requires

control of the bus for one or more data transfers. BREQ/ is synchronized

with BCLK/.

BUSY/

Bus Busy. Indicates that the bus is in use and prevents all

other

bus masters from gaining

control of the bus. BUSY I is synchronized with BCLK/.

CBRQ/

Common Bus Request. Indicates that a bus master wishes control of the bus but does not

presently have

control. As soon

as

control of the bus is obtained, the requesting bus con-

troller raises the CBRQ/ signal.

CCLK/

Constant Clock. Provides a clock signal of constant frequency for use by other system

modules. CCLK/ is approximately

10

MHz with a worst case 35/65 percent duty cycle.

DATO/-DATF/

Data. These

16

bidirectional data lines transmit data to, and receive data from, the

addressed memory location

or

1/0 port. DATF/ is the most-significant bit. For data byte

operations, DATO/-DAT7/ is the even byte and DAT8/-DATF

I is the odd byte.

INH1/

Inhibit RAM. For system applications, allows

RAM

addresses to be overlaid by

ROM

I PROM

or memory mapped 1/0 devices.

INIT/

Initialize. Resets the entire system to known internal state.

INTA/

Interrupt Acknowledge. This signal is issued in response to

an

interrupt request.

INTO/-INT7 /

Interrupt Request. These eight lines transmit Interrupt Requests to the appropriate

interrupt handler.

INTO

has the highest priority.

IORC/

1/0 Read Command. Indicates that the address of

an

1/0 port is on the Multibus address

lines, and that the output of that port is to

be

read (placed) onto the Multibus data lines.

IOWC/

1/0 Write Command. Indicates that the address of

an

1/0 port is on the Multibus address

lines, and that the contents on the Multibus data lines are to be accepted by the addressed

port.

MRDC/

Memory Read Command. Indicates that the address of a memory location is on the

Multibus address

lines, and that the contents of that location are to be read (placed) on the

Multibus data

lines.

MWTC/

Memory Write Command. Indicates that the address of a

memory

location is on the

Multibus address

lines, and that the contents on the Multibus data lines are to be written

into that location.

XACK/

Transfer Acknowledge. Indicates that the address memory location has completed the

specified read

or

write operation. That is, data has been placed onto,

or

accepted from, the

Multibus data lines.

2-6

Page 18

iSBC 432/100

Table 2-5. iSBC 432/100™ DC Characteristics

Preparation for

Use

r

Signals

XACK/

ADRO/-ADRF/

ADR10/-ADR13/

BHENi

BCLK/

CCLK

BPRN/

BPRO/ ,BREQ/

BUSY/

,CBRQ/,

(OPEN COLLECTOR)

DATO/-DATF/

INIT/

(SYSTEM RESET)

INT5/-INT7/

IORC/ ,IOWC/

MRDC/ ,MWTC/

l

I

Symbol

Vol

VoH

VIL

VIH

Ill

llH

Vol

VoH

VIL

VIH

Ill

llH

ILH

1

LL

VIL

VIH

1

1L

llH

VIL

VIH

1

1L

llH

VIL

VIH

Ill

llH

Vol

VoH

Vol

Vol

VoH

VIL

VIH

Ill

llH

VIL

VIH

Ill

llH

Vol

Vol

VoH

ILH

ILL

VIL

VIH

Ill

llH

Vol

VoH

ILH

ILL

Parameter

Description

Output

Low Voltage

Output

High Voltage t0H

Input

Low

Input High Voltage

Input

Input

Output

Output

input

Input High Voltage

Input

Input

Output

Output

Input

Input High Voltage

Input

Input

Input

Input High Voltage

Input

Input

Input Low Voltage

Input High Voltage

Input

Input

Output

Output

Output

Output

Output

Input

Input High Voltage

Input

Output

Input

Input High Voltage

Input

Input

Output

Output

Output

Output

Output

Input

Input

Input

Input

Output

Output

Output

Output

Voltage

Current

Current

Low Voltage

Current

Current

Low Voltage

Current

Current

Low Voltage

Current

Current

Current

Current

Low Voltage

Current

Low Voltage

Current

Current

Low Voltage

High Voltage

Current

Current

at Low V

at High V

Low

Voltage

High Voltage

at Low V

at High V

Leakage High

Leakage Low

at

Low

at High V

at Low V

at High V

at Low V

at High V

Low

Voltage

High Voltage

Low Voltage

Low Voltage

High Voltage

at Low V

Leakage High

at Low V

at High V

Low

Voltage

Low Voltage

High Voltage t0H

Leakage High

Leakage Low

at

Low

at High V

Low Voltage t0L

High Voltage

Leakage High

Leakage

Low

V

V

Conditions

l

t

0

VIN

VIN

t

0

loH

VIN

VIN

v

v 0 =0.45V

VIN

VIN

VIN

VIN

VIN

VIN

loL

loH

loL

loL

loH

VIN

v

VIN

VIN

loL

loL

V0=5.25V

Vo

VIN

VIN

loH

v

v

Test

L

=16

=-2.6

=0.4V

=2.7V

L

=32

=-5

=0.45V

=2.7V

=5.25V

0

=0.45V

=10

=20

=32

=5.25V

0

=16

=32

=0.4V

=.4V

=2.7V

=32

=5.25V

0

=.4V

0

mA

mA

mA

=0.45V

=5.5V

=0.4V

=2.7V

=5.5V

mA

=-0.4

mA

mA

=-5

mA

=0.45V

=0.4V

=2.4V

mA

mA

=-5

mA

mA

=-5

mA

mA

mA

Min. Max.

I

0.4

2.4

2.0

2.4

2.0

2.0

2.0

2.0

2.4

2.4

2.0

2.0

2.4

2.0

2.4

0.8

-0.4

20

0.45

0.8

-2.2

100

50

-50

0.8

-0.5

60

-0.4

20

0.8

-0.5

60

0.45

0.45

0.45

0.90

-0.80

200

0.8

-0.9

80

0.4

0.5

100

-100

-.4

20

0.5

100

-100

Units

l

v

v

v

v

mA

µA

v

v

v

v

mA

µA

µA

µA

v

v

mA

µA

.8

v

v

mA

µA

v

v

mA

µA

v

v

v

v

v

v

v

mA

µA

v

v

mA

µA

v

v

v

µA

µA

.8

v

v

mA

µA

I

v

v

µA

µA

2-7

Page 19

Preparation for Use

iSBC 432/100

Table 2-6. iSBC 432/100™ AC Characteristics (Master Mode)

Minimum

Maximum

Parameter

(ns)

(ns) Description

Remarks

tAS

50

Address setup time to command

tAH

50

Address hold time from command

tos

50

Data setup to write

GMO

toHW

50

Data hold time from write CMD

tcv

198

202

CPU

cycle time

tcMDR

594

Read command width

tcMDW

594

Write command width

tcswR

396

Read-to-write command separation

In

override mode

tcsRR

396

'Read-to-read command separation

In

override mode

tcsww

594

Write-to-write command separation

In

override mode

tcsRw

594

Write-to-read command separation

In

override mode

tsAM

198

202

Time between XACK samples

to

HR

0

Read data hold time

toxL

-400

Read data setup to XACK

txAH

0

XACK hold time

tBs

23

BPRN

to BCLK setup time

to

BY

55

BCLK to BUSY delay

tNOD

30

BPRN

to

BPRO

delay

to

Bo

40

BCLK I to bus priority out

tBcv

100

Bus clock period (BCLK)

tBw

.35tBcv

.65tBcv

Bus clock low

or

high interval

Supplied by system

ti NIT

3000

Initialization width

After all voltages

have stabilized

Table 2-7. iSBC

432/

100™

1/0

Access

AC

Characteristics

Minimum Maximum

Parameter

(ns) (ns)

Description Remarks

tAs

50

Address setup to command From address to

command

tos

-100

Write data setup to command

tACK

4

tBcv

Command to XACK

tcMO

400

Command width

tAH

50

Address hold time

toHW

50

Write data hold time

toHR

25

125

Read data hold time

txAH

50

Acknowledge hold time

Acknowledge turnoff

delay

tACC

300

Read to data valid

toxL

100

Read data setup to XACK

2-8

Page 20

iSBC 432/100

BCLK/

BREQ/

BPRN/

BUSY/

BPRO/

ADDRESS

WRITE

DATA

WRITE

COMMAND

WRITEXACK/

READ

COMMAND/

READ

DATA

READ

XACK/

1

acv---..j

I

'aw---1

H

r-

taw

Preparation for Use

I

tt~.J

--------------

~

tas

=7

_J

~1---------____,r(

___

_

l.--1DBY

~

l.:==1Dao

=7

\

STABLE

ADDRESS

~

(

=7

J

~TABLE

DATA

x T

IAS·

IDS

.____r-

____

--1____,i:==

'AH·

'DHW

\w

•

......_~~~~~tcMDw~~~~~-----4https://manualmachine.com/r-----------

\'--__

__;.

____________

--'7

IACKWT\

u

__J

k-

txAH

STABLE

DATA

IDXL~

r-

---1

I

L.DHR

*

CBRQ/

timing

not

shown

relative

to

other

bus signals

other

than

BCLK/.

Figure 2-1. Bus Exchange Timing (Master Mode)

171820-2

2-9

Page 21

Preparation

for Use

ADDRESS

IORC/

or

IOWC/

XACK

1

READ DATA

WRITE DATA

I

x

HIGHEST

PRIORITY

MASTER

J2

15

BPRN/

r--

1

I

I B

I

I N

I

I

BPRO/

IAS

STABLE ADDRESS

IACK

IACC

tDs

STABLE DATA

Figure 2-2.

1/0

Access Timing (Read/Write)

J3

15

BPRN/

16 16

BPRO/

c

E

LOWEST

PRIORITY

MASTER

J4

15

BPRN/

BPRO/

16

H

iSBC432/100

IAH

IOHW

~

x=

BPRO/ AND BPRN/ PINS

NOT USED BY

NON-MASTERS

---,

I

I

: BACKPLANE

I

I

171820-3

L_

-------

- - -

---

- - -

------

-

-----

--

------

- - - -

_j

Figur 2-3. Serial Priority Resolution Scheme

171820-4

2-10

Page 22

iSBC 432/100

NO.

2

PRIORITY

J2

(NOTE

1)

15

BPRN/

18

BREQ/

N0.1

PRIORITY

(HIGHEST)

J3

(NOTE

1)

15

BPRN/

BREQ/

15

18

BUS

PRIORITY

RESOLVER

(NOTE

2)

7 p

R

'-----------<116

I

p 0

R

I 1

0

BREO/INPUTS

FROM MASTERS

IN BACKPLANE

0

5 R

I

4 T

y

E

2 N

c

1 0

D

0 E

R 2

I

T 3

y

NOTE: REFER TO TEXT REGARDING THE

DISABLING OF

BPRO/

OUTPUT.

Preparation

for Use

NO.

8

NO.

7

PRIORITY

PRIORITY

(LOWEST)

J4

JS

(NOTE

1)

15

(NOTE

1)

BPRN/

BPRN/

BREQ/

Figure 2-4. Parallel

Priority

Resolution Scheme

171820-5

2.14 PARALLEL PRIORITY

RESOLUTION

A parallel priority resolution scheme allows up to

16

bus masters

to

acquire

and

control the Multibus bus.

Figure 2-4 illustrates one

method

of

implementing

such a scheme for resolving bus contention in a

system containing eight bus masters. Notice

that

the

two highest

and

two lowest priority bus masters are

shown installed in the system backplane.

In the scheme shown in figure 2-4, the priority

encoder is a 7 4148

and

the priority decoder

is

an· Intel

8205.

Input

connections

to

the priority encoder deter-

mine the bus priority, with

input

7 having the highest

priority

and

input

0 having the lowest priority (the

15

bus master has the lowest priority).

IMPORTANT:

In a parallel priority resolution

scheme, the

BPRO/

output

must be disabled

on

all

bus masters.

On

the iSBC

432/

100

board,

the

BPRO/

output

signal may be disabled by removing

jumper

40-41.

2.15 SERIAL

I/O

CABLING

Pin assignments

and

signal definitions for the

RS-232-C serial

1/0

interface are listed in table 2-8.

An Intel iSBC

955

cable set may

be

used for inter-

facing. The serial cable assembly consists

of

a

25-conductor flat cable with a 26-pin printed circuit

board

edge connector

at

one end and a 25-pin

RS-232-C interface connector

at

the other end.

2-11

Page 23

Preparation

for Use

iSBC 432/100

Pin

10

12

13

14

2

4

6

8

Table 2-8. Serial

1

NOTES:

1.

All odd-numbered pins

right-most pin when viewed from the component side of the board with the extractors at the

top.

2.

For applications without

8251A

CTS

input.

3.

For applications without

8251

A

DSR

input.

Signal

PROTECTIVE

RXD

TXD

2

cTs

2

RTs

3

DTR

3

DSR

SIGGND

(1,

CTS

DSR

1/0

Connector

GND

3,

5,

... ,

25)

are

capability, connect jumper

capability, connect jumper

For applications where ,cables may be made by the

user for the iSBC

note

that

the mating connector for J 1 has

whereas the RS-232-C connector has

432/

100

board,

it

is

important to

25

pins. Conse-

26

pins

quently, when connecting the 26-pin mating connector to 25-conductor flat cable, be sure

makes contact with pins 1 and 2

nector

correspondence between the

(JI)

cable to

and

and

not

with pin 26. Table 2-9 provides pin

board

an

RS-232-C connector. When attaching the

JI,

be sure

that

the

PC

connector

that

the cable

of

the mating con-

edge connector

is

oriented

properly with respect to pin 1 on the edge connector.

(Refer to the footnote in table 2-8.)

2.16 BOARD INSTALLATION

Always

supply before installing

iSBC

removing device interface cables. Failure to

take these precautions can result in damage

to the

turn

432/

100

board.

off

the computer system power

or

removing the

board

and before installing

or

JI

Pin

Assignments

Description

Protective Chassis Ground

8251A

receiver data input

8251A

transmitter data output

8251

A Clear-to-send input

8251A

Request-to-send output

8251

A Data Terminal Ready output

8251A

Data Set Ready input

Signal Ground

on

the component side of the board. Pin 1 is the

5-6.

This routes

3-4.

This routes

In

an

Intellec system, install the iSBC 432/100

8251A

8251A

RTS

DTR

(RXD)

(CTS)

(DSR)

output to

output to

in any odd-numbered slot except slot I

appropfiate serial

connector

JI

Table 2-9. Connector J 1

PC

Conn.

J1

1

2

3

4

5

6

7

8

9

10

11

12

13

1/0

.

Pin

Correspondence

RS232C

Conn.

14 14

1

15 16

2

16

3

17

4

18

5

19

6

20

cable assembly to the edge

Vs

PC

(TXD)

(RTS)

(DTR)

and

RS-232-C

Conn.

J1

15

17

18

19

20

21

22

23

24

25

26

board

attach the

RS232C

Conn.

7

21

8

22

9

23

10

24

11

25

12

N/C

13

2-12

Page 24

3.1

INTRODUCTION

This chapter lists

the effects

programming information for the Intel

USART (Universal

Receiver/Transmitter), the Intel 8253

mabie intervai Timer),

status registers.

A complete description

General

programming,

found in the

Data

Architecture Reference Manual,

171860-00

I.

1/0

address assignments, describes

of

hardware initialization, and provides

Processor

and

protection

iAPX

432 General Data Processor

Synchronous/

and

the on-board controi and

of

the Intel iAPX 432

(GDP)-its

Asynchronous

PIT

(Program-

instruction set,

mechanisms-may

Order

CHAPTER 3

PROGRAMMING INFORMATION

3.3

1/0

ADDRESSING AND ACCESS

GDP

local address references are translated into

8251

No.

A

be

Multibus

accesses (including accesses to on-board devices)

occur via

located

logically situated

access the

address generation

as memory address generation (described in

paragraph 4-5).

3.4 INITIALIZATION

1/0

read/write

the Multibus bus.

on

the iSBC

board's

432/

on

the bus.

1/0

is

performed in the same manner

commands. All

1/0

ports physically

100 Processor Board are

Any

bus master may

ports (listed in table 3-1).

1/0

port

1/0

3.2

MEMORY

ADDRESSING

AND ACCESS

The iSBC

memory; all

over the Multibus architecture.

address references are translated into Multibus

memory

generated by the

off

set register

processor to share Multibus memory with the

432/

When the

bus) each

or

access mechanisms are described in detail beginning

in paragraph 4-4. Briefly, to perform Multibus

transfers, the iSBC

control

memory location

Memory Write

until a Transfer Acknowledge

from the addressed memory module. When the

transfer

releases the bus to permit

When a

data

one Multibus transfer, a

the processor

the complete sequence

feature eliminates the time required to release

regain bus control between

increasing

width requirements.

432/

100 Processor Board contains no local

GDP

memory accesses are processed

read/write

100

processor.

GDP

GDP

more 8/16-bit Multihus

of

the bus.

is

completed, the iSBC 432/100

GDP

transfer

that

throughput

commands. Physical addresses

GDP

are modified by an on-board

to

permit an Intellec

addresses memory (via the Multibus

access request

432/

100

After

and

issuing a Memory Read

command,

access request specifies a multibyte

must be translated into more

"bus

board

to

retain Multibus control for

of

and

GDP

or

is

implemented as one

data

transfers. Memory

board

must first gain

addressing the correct

the processor board waits

(XACK/)

other

masters

lock"

Multibus transfers. This

data

transfers, thereby

lowering Multibus band-

physical

iSBC system

iSBC

data

or

is

received

data

board

to

use it.

than

feature permits

and

The Multibus initialization signal line (INIT

activated, resets the

USART

Command

The

In addition to the

Multibus master may reset the

processor reset flag (contained within the processor

control

to

enter

Words to program the desired function.

8253

PIT

register-refer

is

3.5 8251A USART

The USART converts parallel

serial

output

half-

or

verts serial input

Prior

to the start

tion, the

words. These control words, which define the com-

plete functional operation

immediately follow a reset (internal

control words are either Mode instructions

Command

data

full-duplex operation. The USART also con-

USART

instructions.

GDP

and

causes the 8251A

an

"idle"

not

affected by the INIT I signal.

INIT

state waiting for a set

I reset sequence, another

GDP

to

table 3-1).

PROGRAMMING

output

format

data

of

data

must be loaded with a set

(e.g., IBM Bi-Sync) for

into parallel

transmission

data

of

the USART, must

or

/),

when

of

by writing the

data

into a

format.

or

data

recep-

of

control

external).

The

or

3.6 MODE INSTRUCTION FORMAT

The Mode instruction word defines the general

characteristics

operation.

of

the

Once the

USART

Mode

and

must follow a reset

instruction word has been

3-1

Page 25

Programming

Information

iSBC 432/100

Table 3-1. iSBC

1/0

Address

00

XO

X2

X4

X6

X8

XA

xc

XE

XE

R/W

R

R/W

R/W

R/W

R/W

R/W

R/W

w

R

w

432/

100™

1/0

Address Assignments

Description

ID

Processor

8253

PIT

Process Clock Timer

Read:

Write:

Process

'Read: Counter 1

Write: Counter 1

Baud Rate Generator

Read: Counter 2

Write: Counter 2

Read:

Write:

8251A

Read: Data (J1)

Write: Data (J1)

Read:

Write: Mode

Memory Address Offset Register (contains

8-bit memory

operations)

Processor

bit#

0

1

2

3 stop command active

4

5-7

Processor Control

bit#

0 release

1 issue

2 issue

3 stop

4 issue

Register

Counter

Counter

Clock Timer

None

Control

USART

Status

offset

Status Register

description

processor

interrupt pending

GDP

accesses stopped

fatal error

user selectable

description

initialized state

Multibus

interprocessor

munication request

GDP

alarm signal

0

O (load count)

(load count)

(load count)

or

Command

for all memory addressing

initialization hold

jumpers

processor

accesses

from

interrupt

com-

an

Note:

Xis

jumper

written into the

mand

instructions

instruction

a.

For

Synchronous Mode:

(

1)

Character

(2)

Parity

(3)

Even/

(4) External sync detect

iSBC

(5) Single-

USART,

may

word

defines the following:

length

enable

odd

parity generation

432/100

board)

or

double-character sync

sync characters

be inserted.

(not

3-2

selectable

The

and

check

supported

or

Mode

by the

(1-7)

as described in table

com-

b.

Instruction

synchronous

figures

2-2.

For

Asynchronous

Baud

(1)

(2)

Character

(3)

Parity

Even/odd

(4)

Number

(5)

word

3-1

through

Mode:

rate factor

(Xl,

X16,

or

X64)

length

enable

parity generation

of

stop

bits

and

data

transmission formats for

and

asynchronous modes are shown in

and

check

3-4.

Page 26

iSBC 432/100

CHARACTER

Lti'llGTH

0

1

0

1

0 0

1 1

5

6

7

a.

BITS

BITS

BITS

BITS

'----------

PARITY

ENABLE

11=ENABLEI

IO=DISABLEI

'------------

EVEN

PARITY

GENERATION/CHECK

1

=EVEN

0

=OOD

EXTERNAL

SYNC

DETECT

1 =

SYNDET

IS

AN

INPUT

O=SYNDET

IS AN

OUTPUT

SINGLE

CHARACTER

SYNC

l=SINGLE

SYNC

CHARACTER

O=

DOUBLE

SYNC

CHARACTER

NOTE IN

EXTERNAL

SYNC MODE.

PROGRAMMING

DOUBLE

CHARACTER

SYNC

WILL

AFFECT

ONLY

THE

Tx

Figure 3-1.

USART

Synchronous Mode

Instruction Word Format

111820-s

SYNC

CHAR

1

RECEIVE

FORMAT

SYNC

CHAR