Page 1

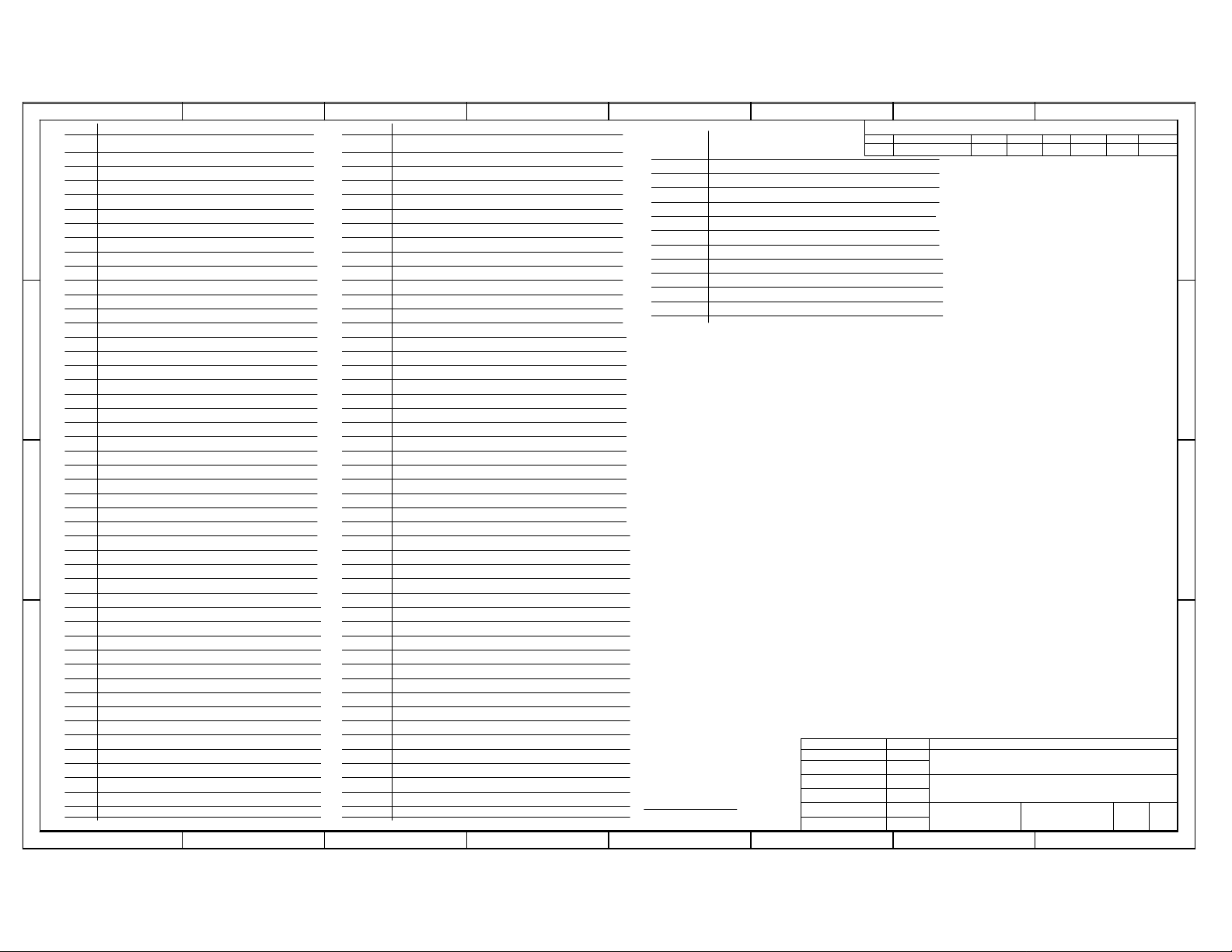

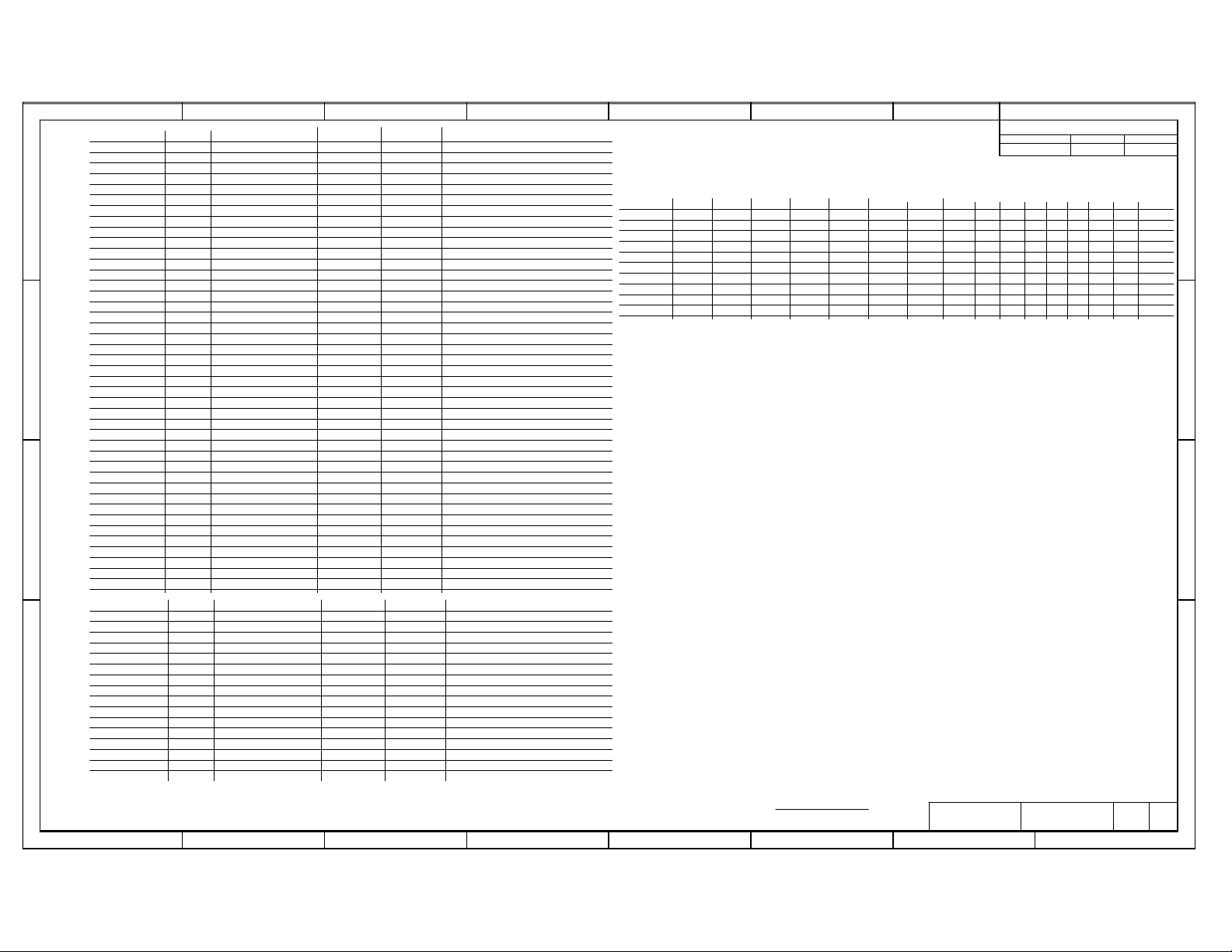

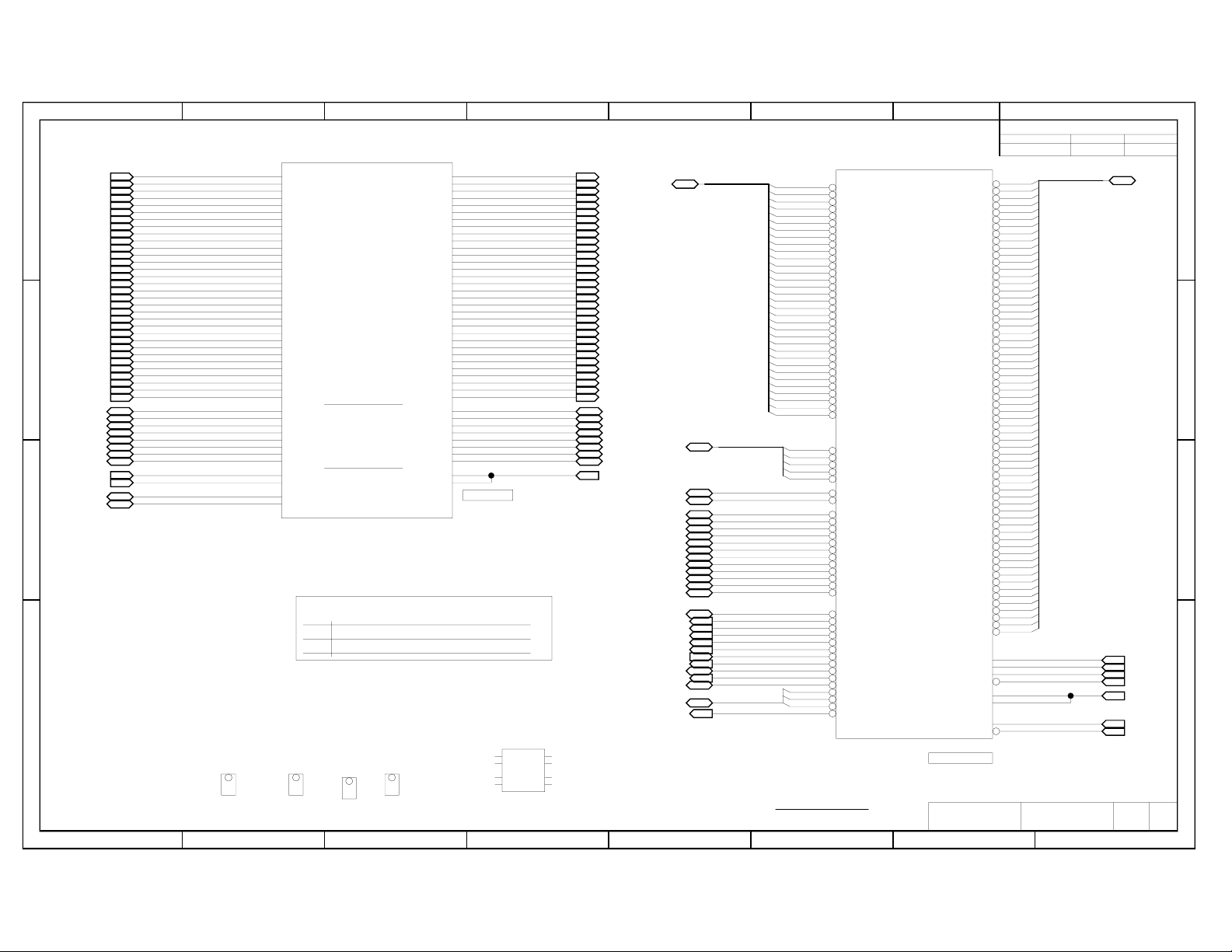

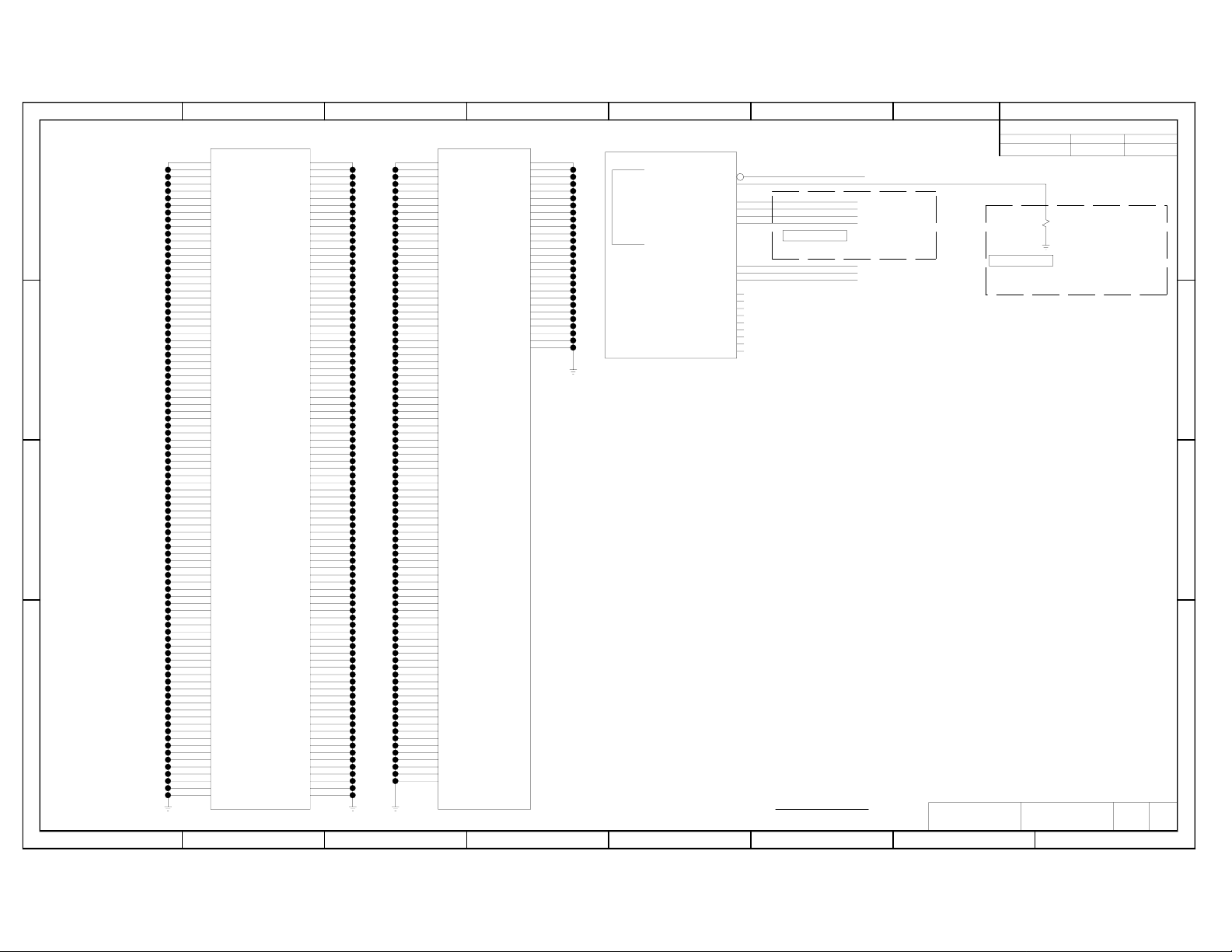

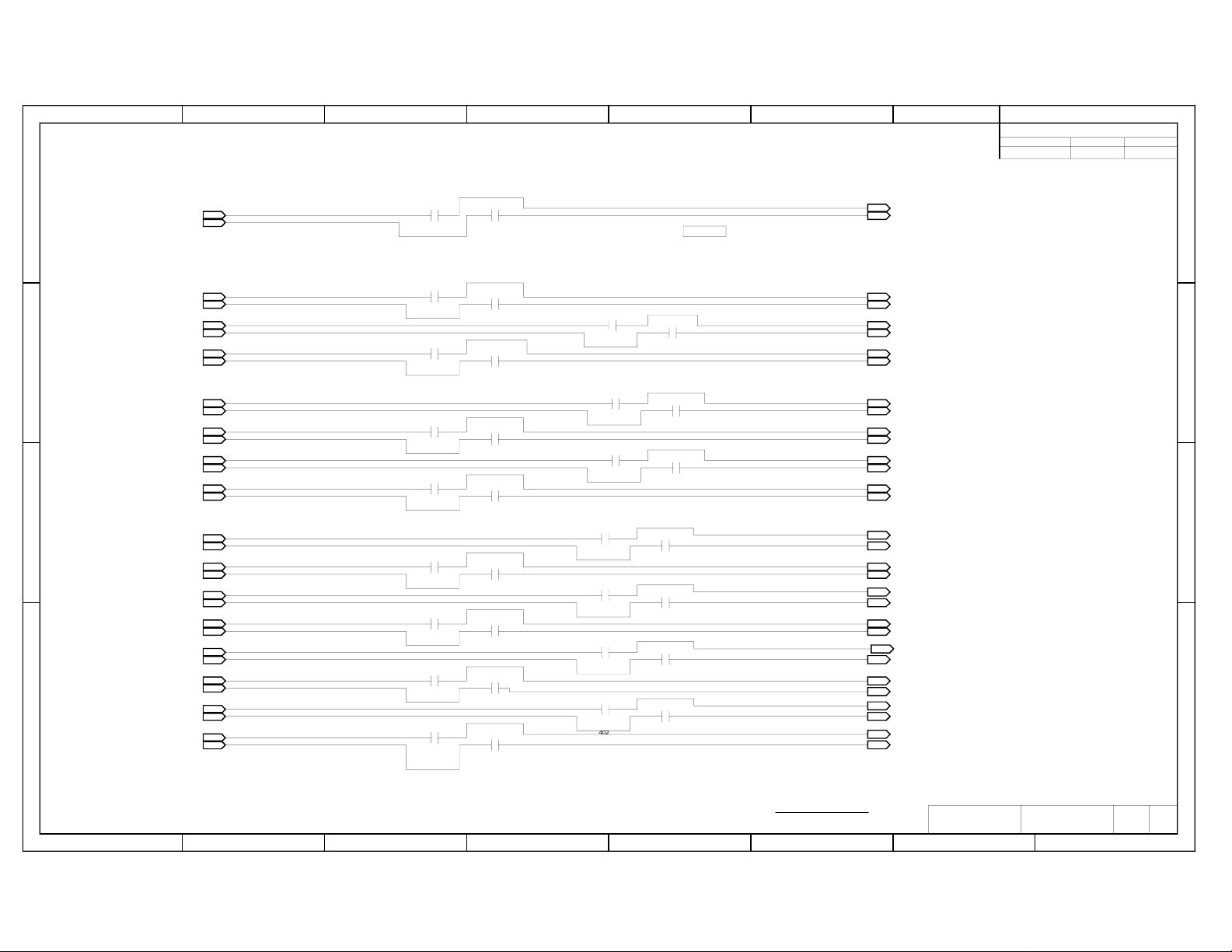

CR-1 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE1

8 2

PAGE #

COMPONENT/FUNCTION

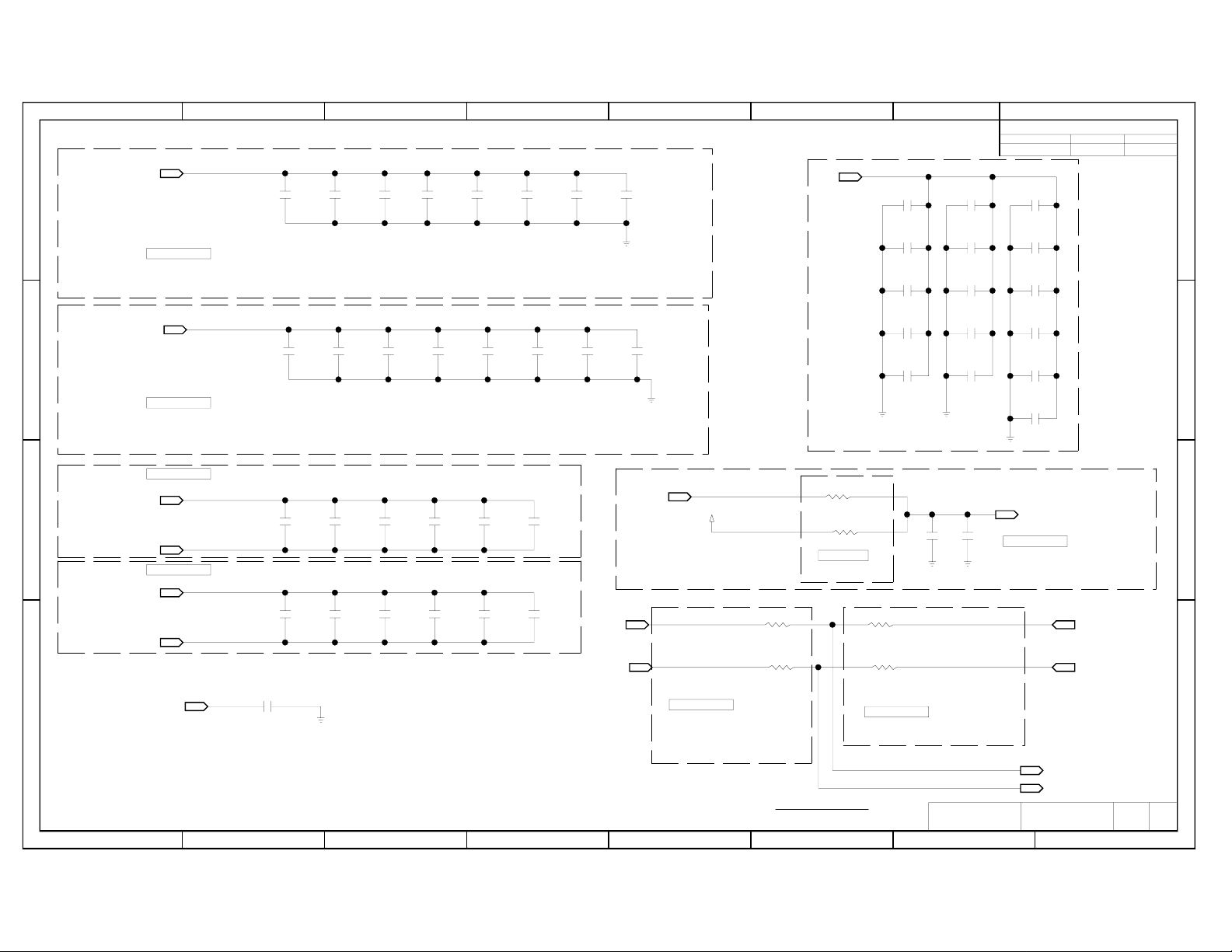

[1. INDEX]

[2. BLOCK DIAGRAM]

[3. RESET MAP]

[4. CLOCK DISTRIBUTION]

D

[5. GPIO, IRQ, IDSEL MAP]

[6. CPU-SOCKET 1 OF 2]

[7. CPU SOCKET 2 OF 2]

[8. CPU TERMINATION & MISC P/U P/D]

[9. CPU PLL FILTERED SUPPLY]

[10. MCH SECTIONS PAGE 1 OF 6]

[11. MCH SECTIONS PAGE 2 OF 6]

[12. MCH SECTIONS PAGE 3 OF 6]

[13. MCH SECTIONS PAGE 4 OF 6]

[14. MCH SECTIONS PAGE 5 OF 6]

[15. MCH SECTIONS PAGE 6 OF 6]

C

[16. PLL & CRT FILTERS]

[17. MCH DECOUPLING AND COMP]

[18. MCH DCPL & VGA TERMINATION]

[19. MCH VREFS & TERMINATION]

[20. VGA CONNECTOR]

[21. PCI EXPRESS X16]

[22. PCI EXPRESS X16]

[23. PCI EXPRESS X16 COUPLING]

[24. 240P CONN DDR2, CH A]

[25. 240P CONN DDR2, CH B]

[26. DDR VTT TERMINATION]

[27. DDR VTT DECOUPLING]

B

[28. CK505 PAGE 1 OF 2]

[29. CK505 PAGE 2 OF 2]

[30. ICH9 1 0F 6 CONTROL]

[31. ICH9 2 OF 6 CONTROL]

[32. ICH9 3 OF 6 CONTROL]

[33. ICH9 4 OF 6 - CONTROL]

[34. ICH 5 OF 6 - CONTROL]

[35. ICH 6 OF 6 - GROUND BODY]

[36. GPIO TERMINATION & RST STRAPS]

[37. ICH PIN STRAPS]

[38. ICH DECOUPLING]

[39. ME & CONTROL BUFFERS/ICH CIRCUITS]

[40. SERIAL FLASH PRIMARY]

[41. SATA CONNECTORS]

[42. USB FP HDR 1]

[43. USB FP HDR 2]

[44. USB FP HDR 2]

[45. BACK PANEL USB]

[46. BACK PANEL USB WITH ESATA]

[47. PCI EXPRESS X1 #1]

[48. PCI CONN 1]

[49. PCI CONN 2]

8

7

PAGE #

6

COMPONENT/FUNCTION

[50. PCI TERMINATION]

[51. STD FRONT PANEL HDR]

[52. USB_FP_HEADER_POWER]

[53. 1394 CONTROLLER]

[54. 1394 BP REV1]

[55. 1394 PWR/DCPL]

[56. LAN NINEVEH]

[57. LAN NINEVEH]

[58. LAN NINEVEH]

[59. AUDIO CODEC]

[60. AUDIO DECOUPLING & JACK SENSE]

[61. AUDIO SPDIF]

[62. AUDIO JACK (BLUE GREEEN PINK]

45

PAGE #

COMPONENT/FUNCTION

[97. PRIMARY XDP-LITE]

[98. PATA]

[99. PATA]

[100. TEST SITE CAPS]

[101. PCI EXPRESS X1 #2]

[102. PCI EXPRESS X1 #3]

[103. PCI CONN 3]

[104. AUX FAN CONFIGURATION]

[105. HARDWARE MANAGEMENT: HECETA]

[106. ITE IT8211F 1 OF 2]

[107. PATA 2ND CONNECTOR]

3

REVISIONS

REV

REV

2.02

DESCRIPTION

DESCRIPTION

DESIGN

REVISIONS

DFT

DATE

DFT

DATE

2006

CHK APVD

CHK

1

DATE DATE

DATE

APVD

DATE

D

[63. AUDIO JACK (BLACK ORANGE]

[64. AUDIO FP HEADERS & HDA HEADER]

[65. AUDIO MIC BIAS]

[66. AUDIO VREG]

[67. SPDIF HEADER]

[68. TPM 1.2]

[69. PORT ANGELES 1 OF 2]

[70. PORT ANGELES 2 OF 2]

[71. FDD CONN]

BEARLAKE-B ATX

CLASSIC SKU

FROSTBURG

DRAGONTAIL PEAK

FAB C

C

[72. PS/2 CONNECTOR]

[72. LPT SIGNALS]

[73. LPT SIGNALS]

[74. SERIAL PORT A]

[75. STUDIES PURPOSE]

[76. SST SENSOR]

[77. FAN CONFIGURATION]

[78. MTG HOLES/LABELS]

[79. CORE VREG]

[80. CORE VREG]

TAPE-OUT: WWXX-2006

FAB A

REV

CONROE, BEARLAKE, DDR?, ICH9,

2-CHANNEL DDR2, PCIEXPRESS GFX, ATX

CUSTOMER REFERENCE BOARD

POWER SYMBOLS USED:

VCC3

VCC

+12V

-12V

3.03

B

[81. VREG_SM_VTT]

[82. VREG_1P25_CORE MCH]

[83. MCH DCPL]

[84. CORE VREG]

[85. VREG_FSB VTT & SFR]

[86. VREG 1.25 MCH CL]

[87. CORE VREG]

[88. CORE VREG]

[89. CORE VREG]

[90. NO PAGE TITLE FOUND!!!]

[91. WAKE CONTROL SWITCH PS2/USB (BP RIGHT)]

[92. VREG: DECOUPLING AND STITCHING]

[93. VCCP VREG]

[94. VCCP VREG]

[95. VCCP VREG]

[96. VREG: VCCP DECOUPLING / 2X2 CONN]

7

65

[PAGE_TITLE=INDEX]

BPAGE DRAWING

frostburg_fabc.sch_1.1

Sun Mar 18 18:42:55 2007

4 2

NOTES:

1. THIS SCHEMATIC DOCUMENTS THE GENERIC PRODUCT WITH

ALL POSSIBLE CONFIGURATIONS.

PLEASE REFER TO SPECIFIC PRODUCT PBA EPL FOR

ITEMS SHOWN AS OPTIONAL IN THE SCHEMATIC.

2. RESISTORS ARE IN OHMS UNLESS OTHERWISE SPECIFIED.

3. VCC = +5V UNLESS OTHERWISE SPECIFIED.

4. * SUFFIX INDICATES ACTIVE LOW SIGNAL.

5. \I SUFFIX INDICATES SIGNAL EXITS HIERARCHICAL BLOCK.

6. THIS DOCUMENT ALSO EXISTS ON ELECTRONIC MEDIA.

BOM_RELEASE_DATE

SIGNATURE

?

DRN_BY

?

CHK_BY

ENGR_APVD

CUSTOM TEXT B-PAGE

3

?

?

PB_NUMBER

?

inte

TITLE

?

?

?

CONFIDENTIAL

INTEL

?

DOCUMENT_NUMBER

xxxxxx

S

3065 BOWERS AVEDATE

SANTA CLARA, CA

PAGE REV

1/107

1

95051

3.01

AA

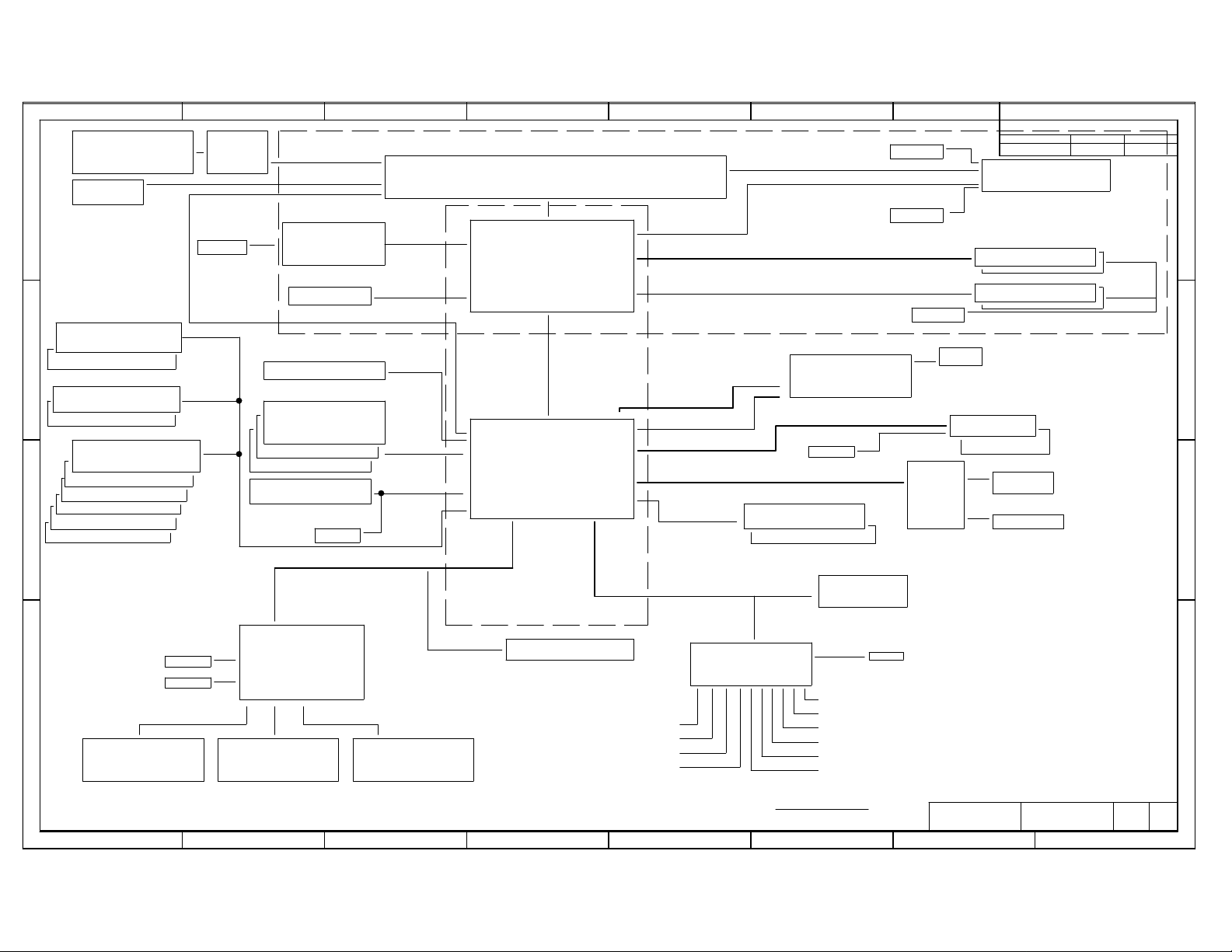

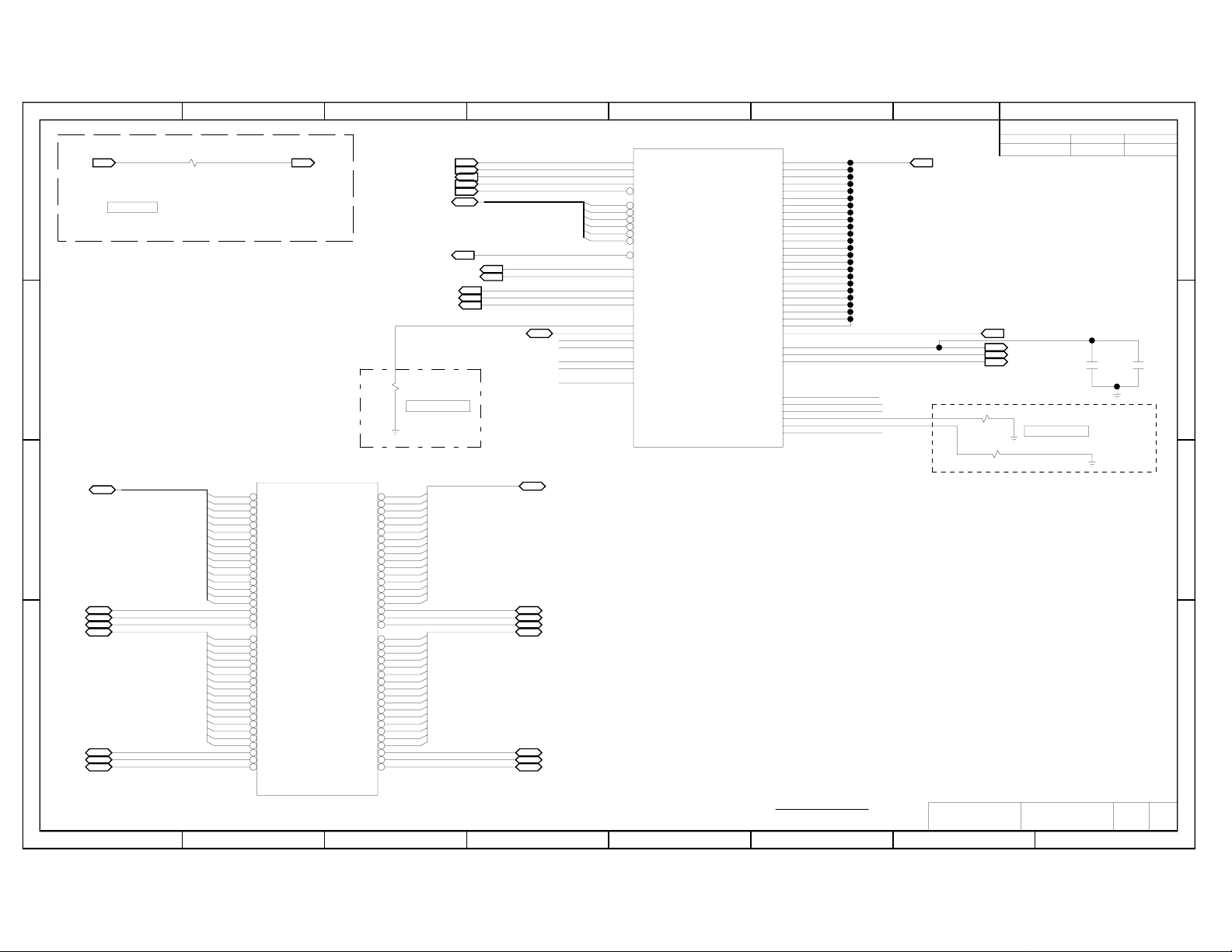

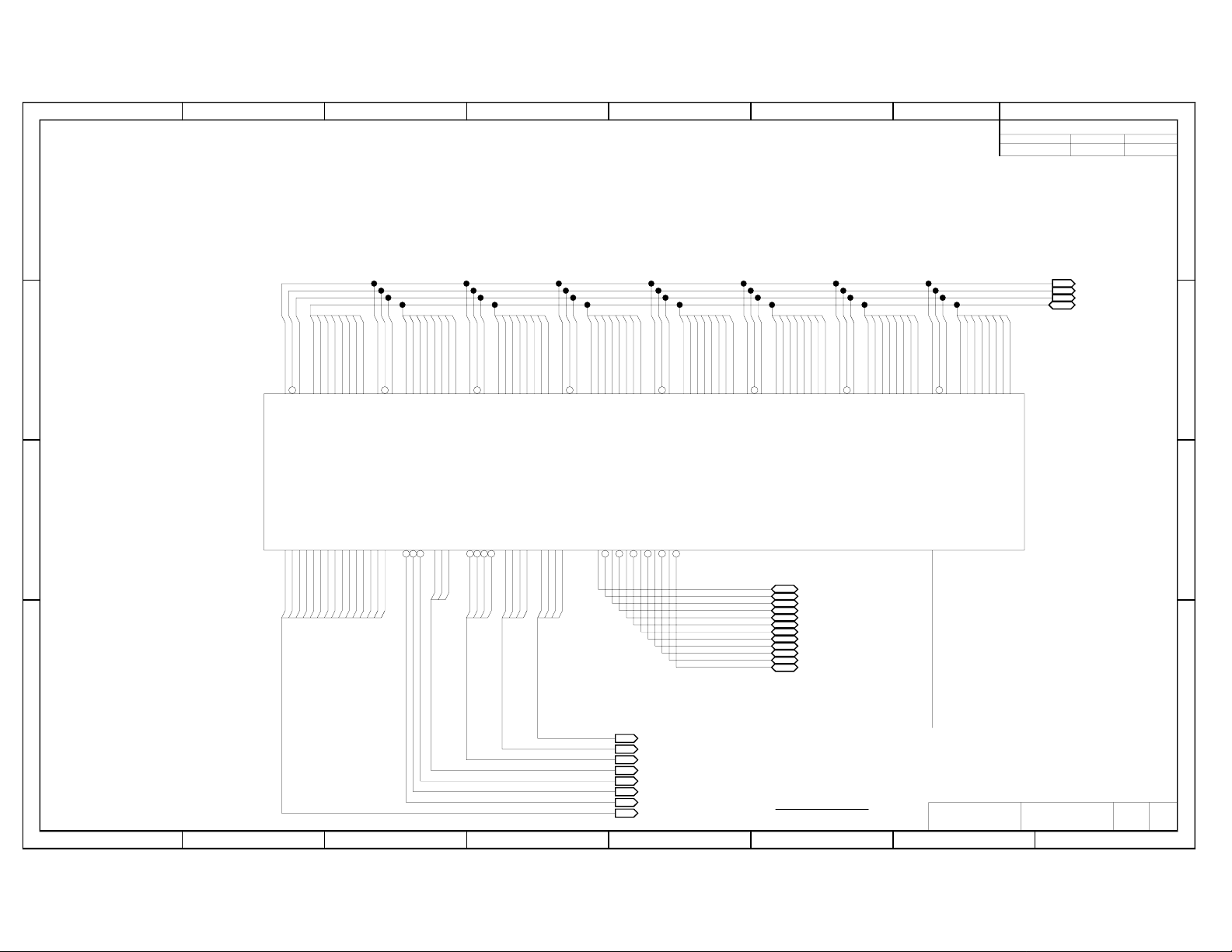

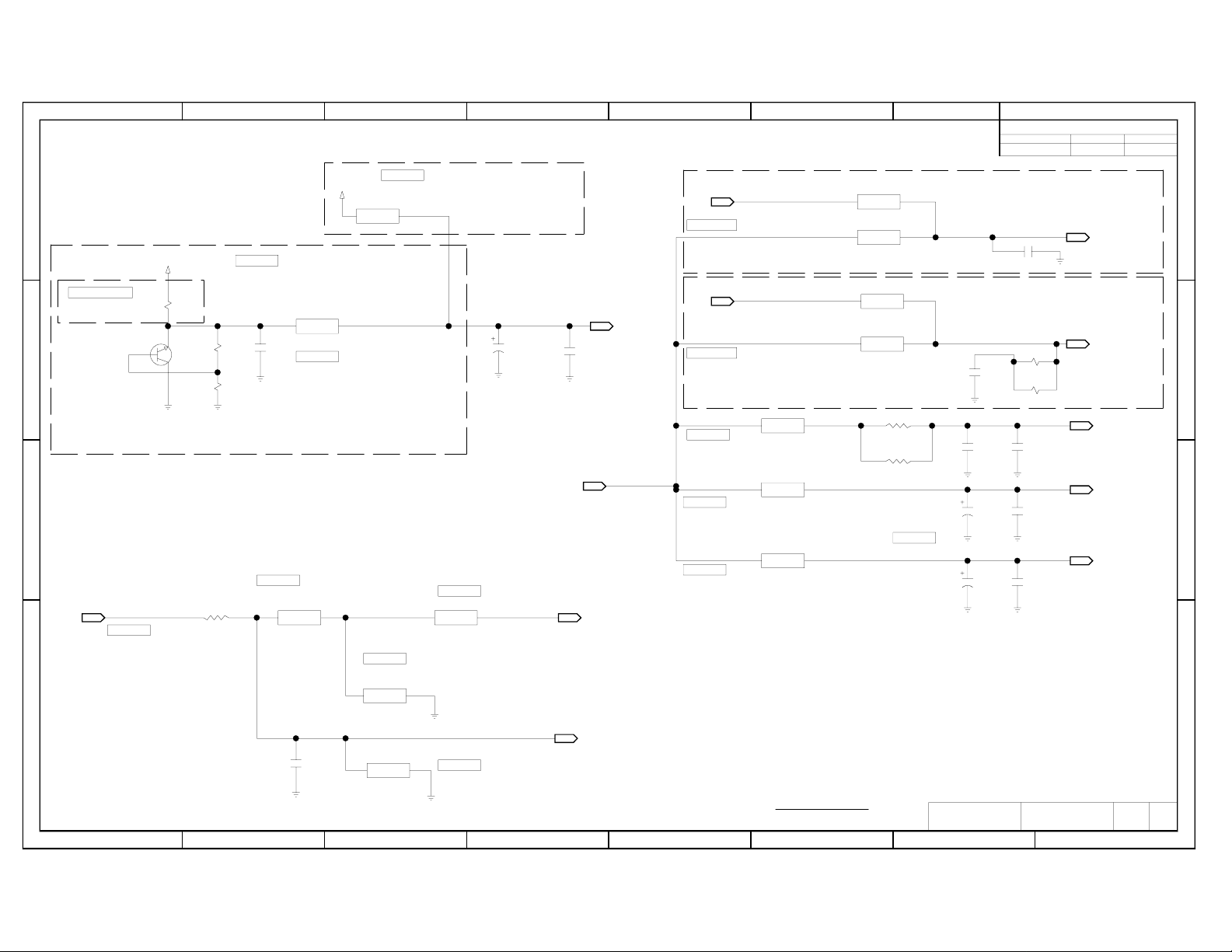

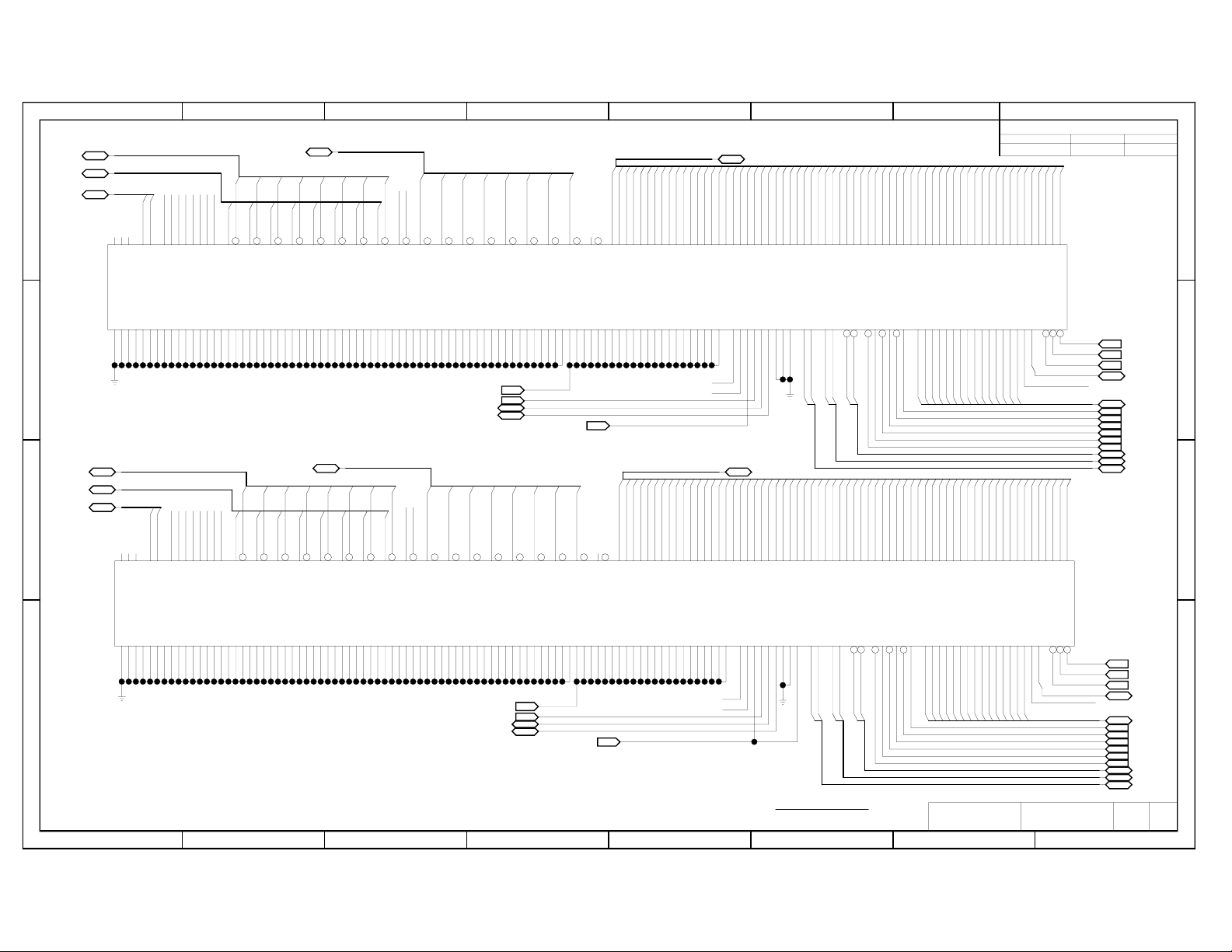

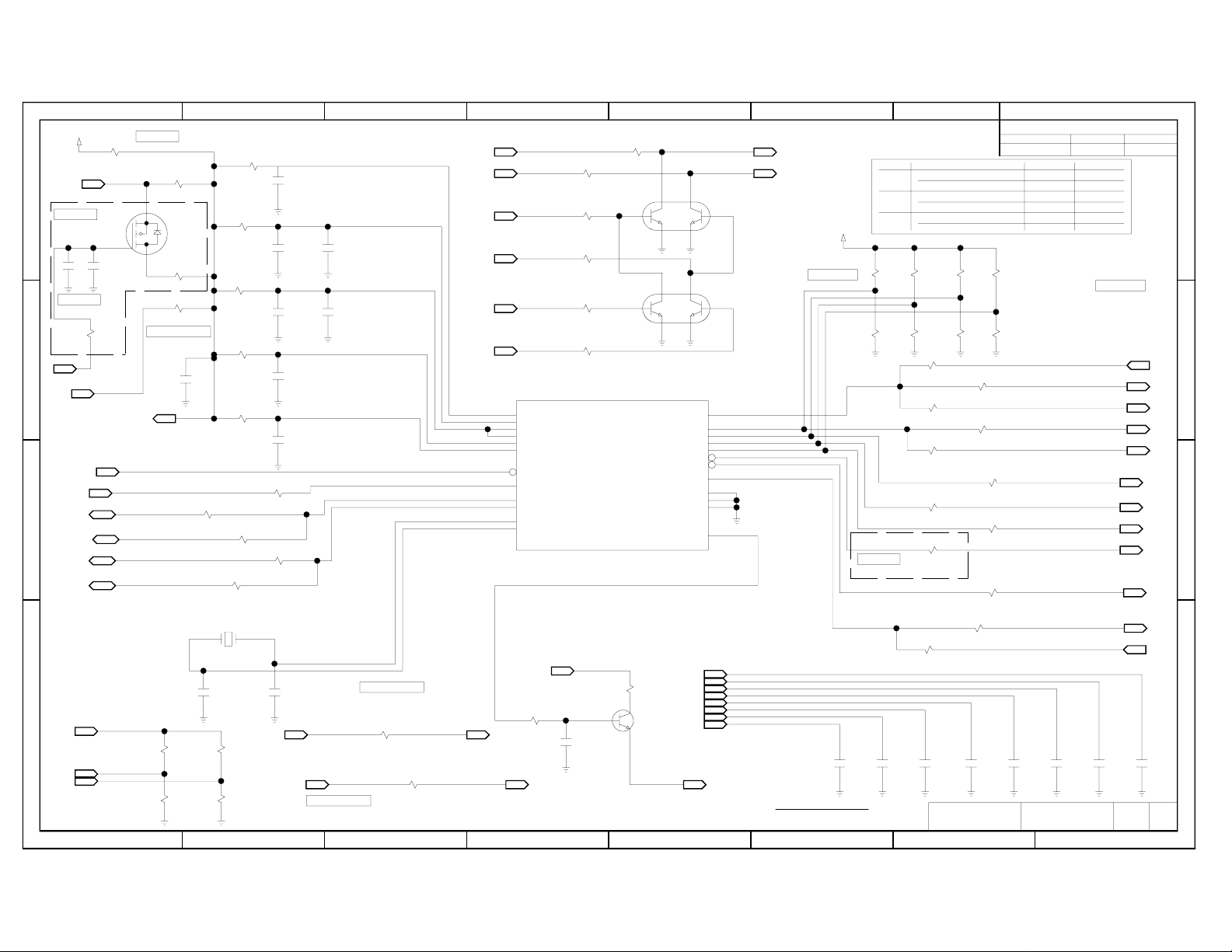

Page 2

POWER

SUPPLY CONN

XDP SSA

D

FRONT PANEL

USB PORT 1

C

USB PORT 2

FRONT PANEL

USB PORT 3

USB PORT 4

BACK PANEL

USB PORT 1

USB PORT 2

USB PORT 3

USB PORT 4

B

USB PORT 5

USB PORT 6

CR-2 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE2

8

7

VREG

(BACKSIDE)

PECI

SM BUS S3

SATA CONN

PCIE SLOT 1

E

PCI 1X16

GRFX CONN

VGA CONN

SPI FLASH

1&2

3&4

5&6

SM BUS S3

LPC BUS

6

SPI

PCIE X1

LAND GRID ARRAY (LGA) CONNECTOR

LGA775

PROCESSOR SOCKET

FSB

GMCH:

GRAPHICS MEMORY

CONTROLLER HUB

DMI

ICH9: I/O

CONTROLLER HUB

45

CHANNEL A DDR2 667/800

CHANNEL B DDR2 667/800

GLCI

LCI

(LAN CONNECT INTERFACE)

PCI (33MHZ)

PCI (33MHZ)

SST_CTL

3

CORE

DUAL DATA RATE SDRAM

(2-DDR SDRAM DIMMS)

DUAL DATA RATE SDRAM

(2-DDR SDRAM DIMMS)

NINEVEH

OR EKRON

SM BUS S3

THERMAL SENSOR

THERMAL SENSOR

LAN

SM BUS S0

SM BUS S3

SM BUS S0

1394

2

CK_505 CLOCK

DIMM 0:1

DIMM 0:1

RJ45

PCI SLOT 1

PCI SLOT 2

1

MODULE REV DETAILS

MODULE NAME

FP HDR

2 PER

BACK PANEL

REV

DATE

D

C

B

BROADWATER

HIGH DEF AUDIO LINK

HD AUDIO

2X8 HDR

CHIPSET

SM BUS S3

A

SM BUS S0

PS2 MOUSE &

KEYBOARD

BLOCK DIAGRM UPDATED: 09/06/2005

8

PORT

ANGELES

SIO

PARALLEL (1)

SERIAL HEADER (2)

7

FLOPPY DISK

DRIVE CONN

SM BUS S3 = RESUME WELL

SM BUS S0 = MAIN POWER WELL

6

TPM: SECURITY

MIC IN

LINE IN

CD IN (ATAPI, BLACK)

SP/DIF IN

5

HD 10 CH

AUDIO CODEC

FRONT PANEL

LINE OUT

SP/DIF OUT

LINE OUT (SURR)

LINE OUT (SURR)

LINE OUT (LFE/CENTER)

BPAGE DRAWING

frostburg_fabc.sch_1.2

Sun Mar 18 18:42:55 2007

4 2

3

PC_SPKR

[PAGE_TITLE=BLOCK DIAGRAM]

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

xxxxxx

PAGE REV

2

1

A

3.01

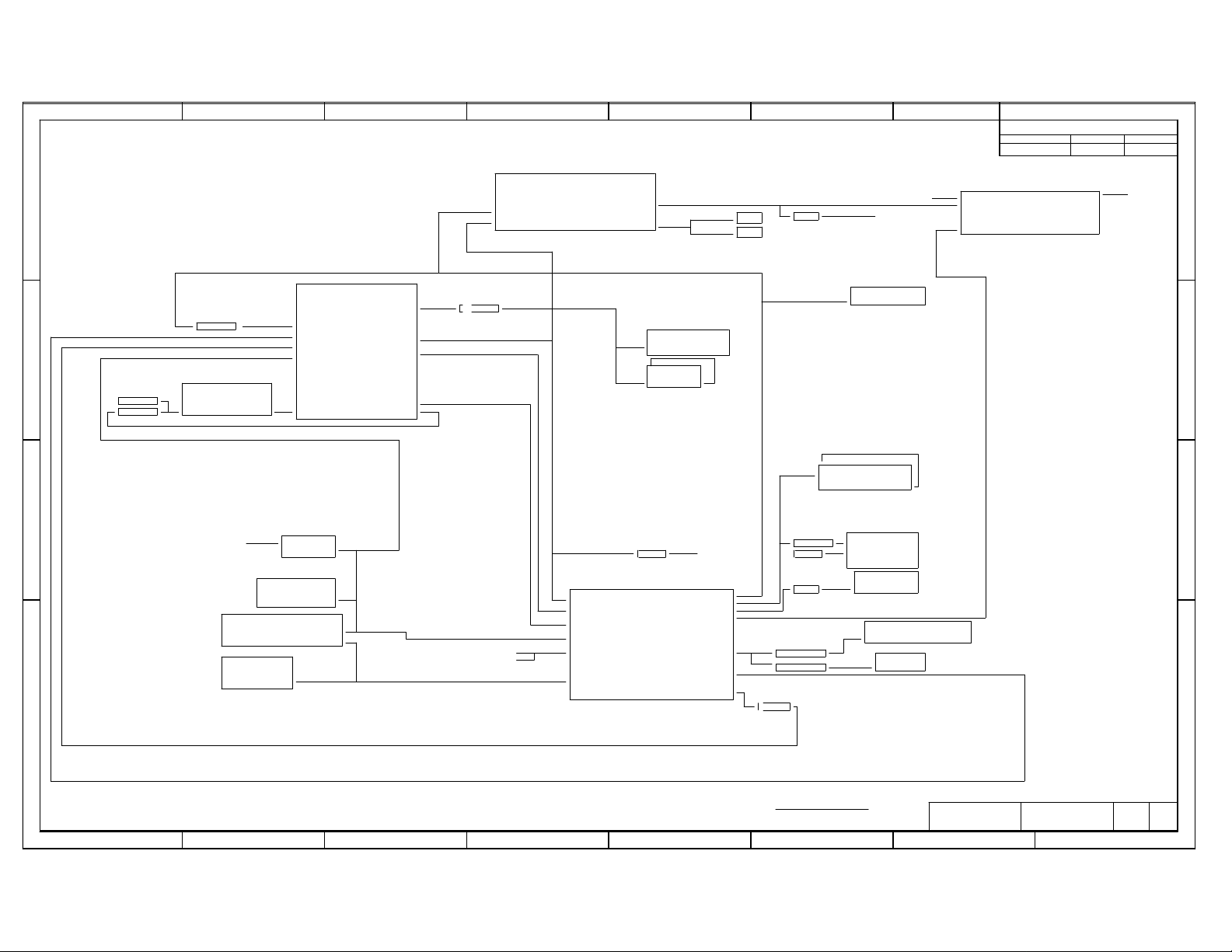

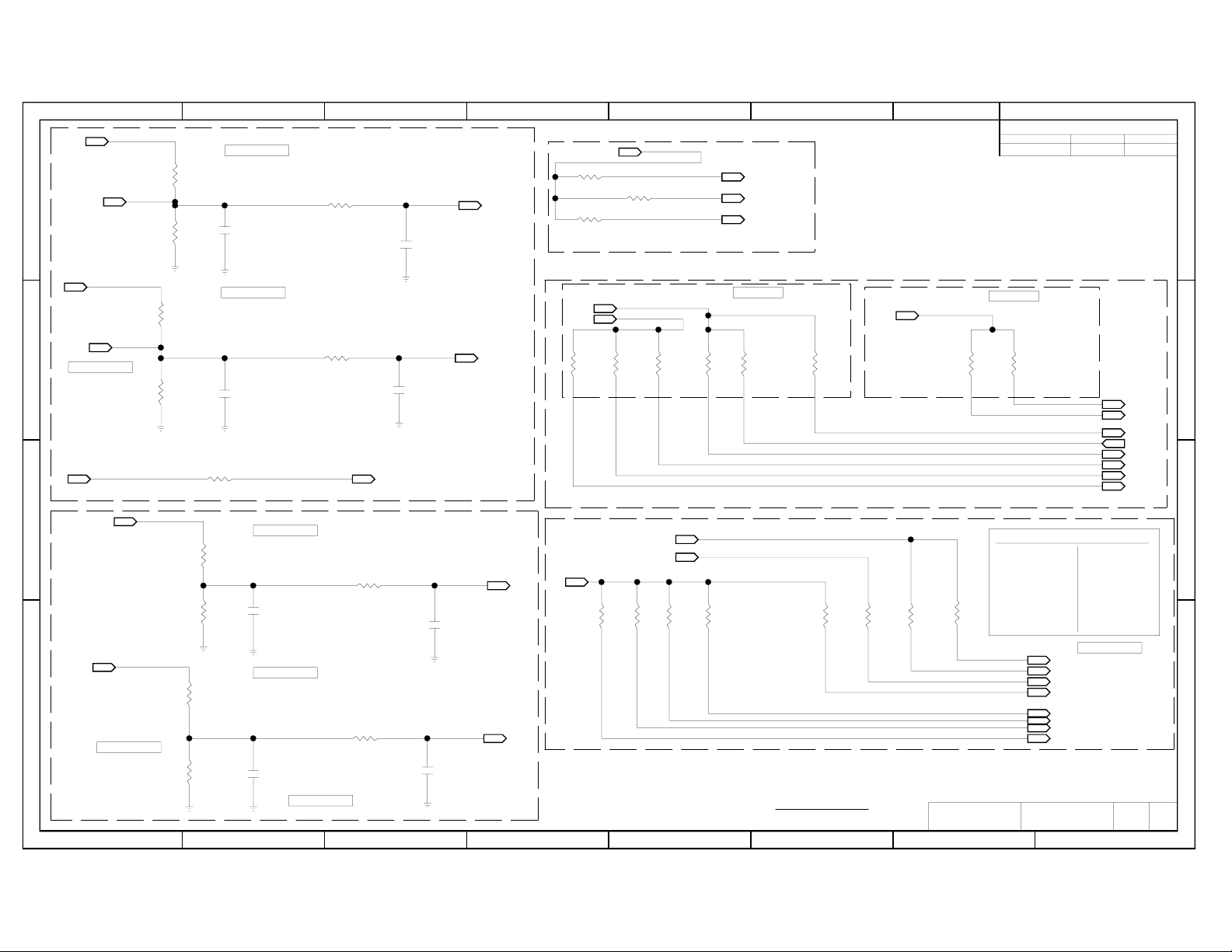

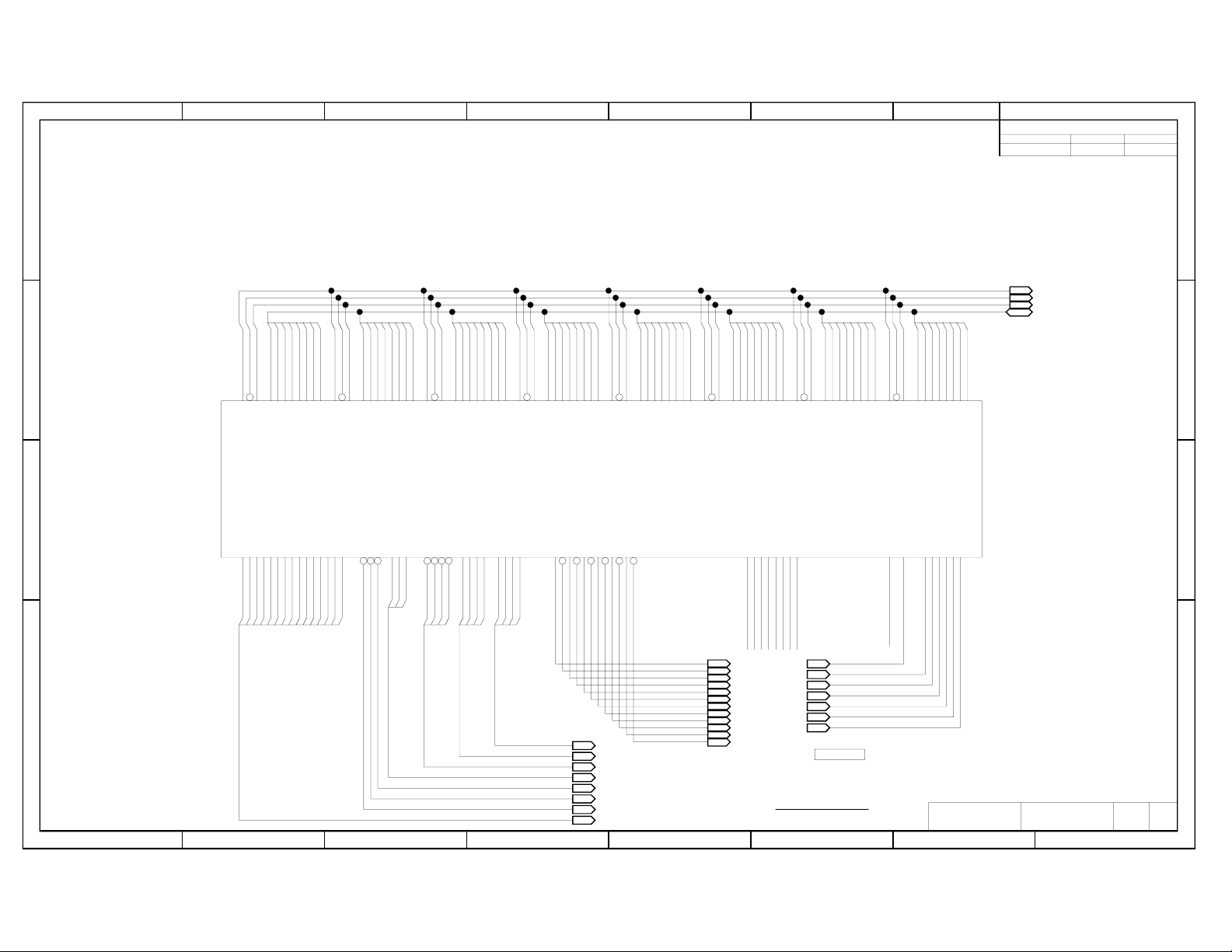

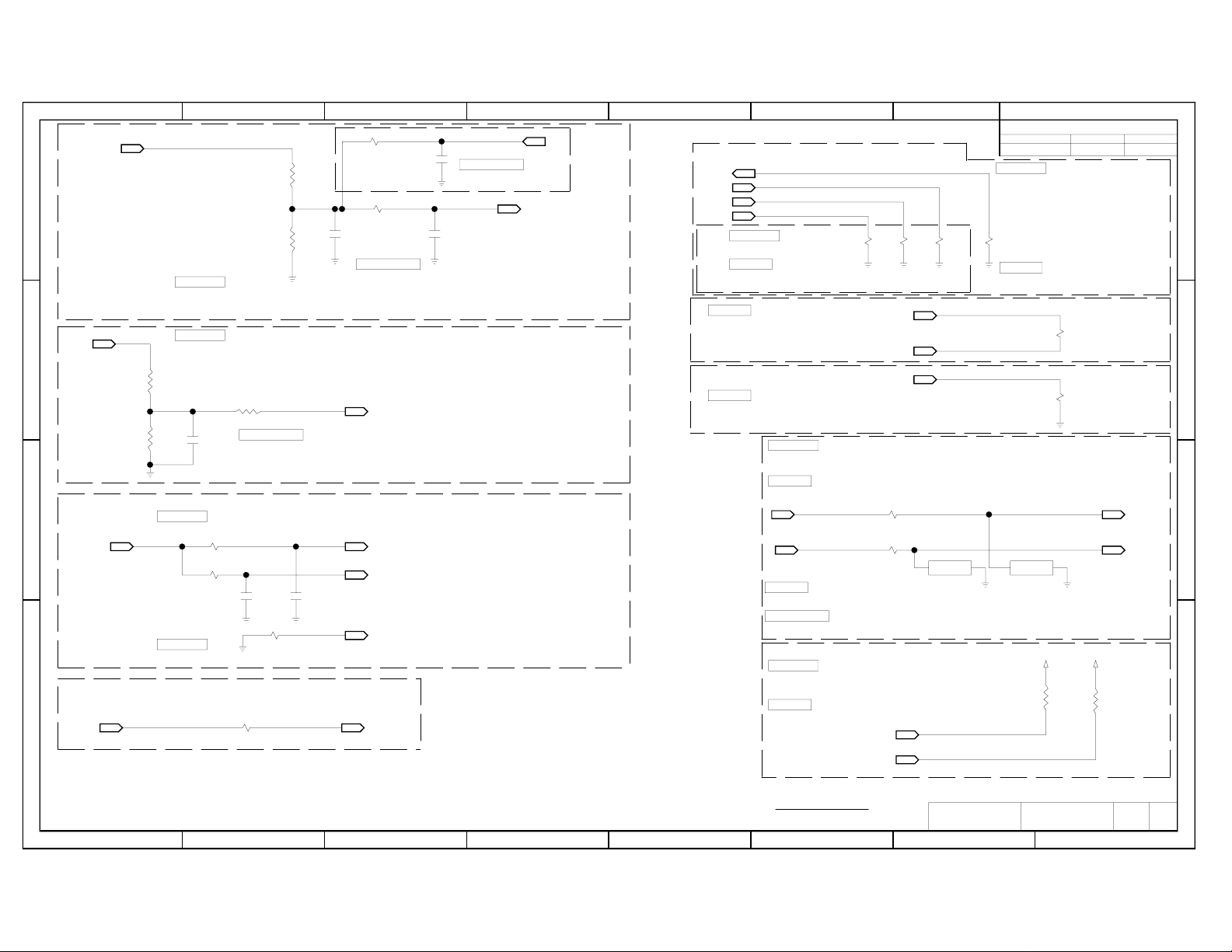

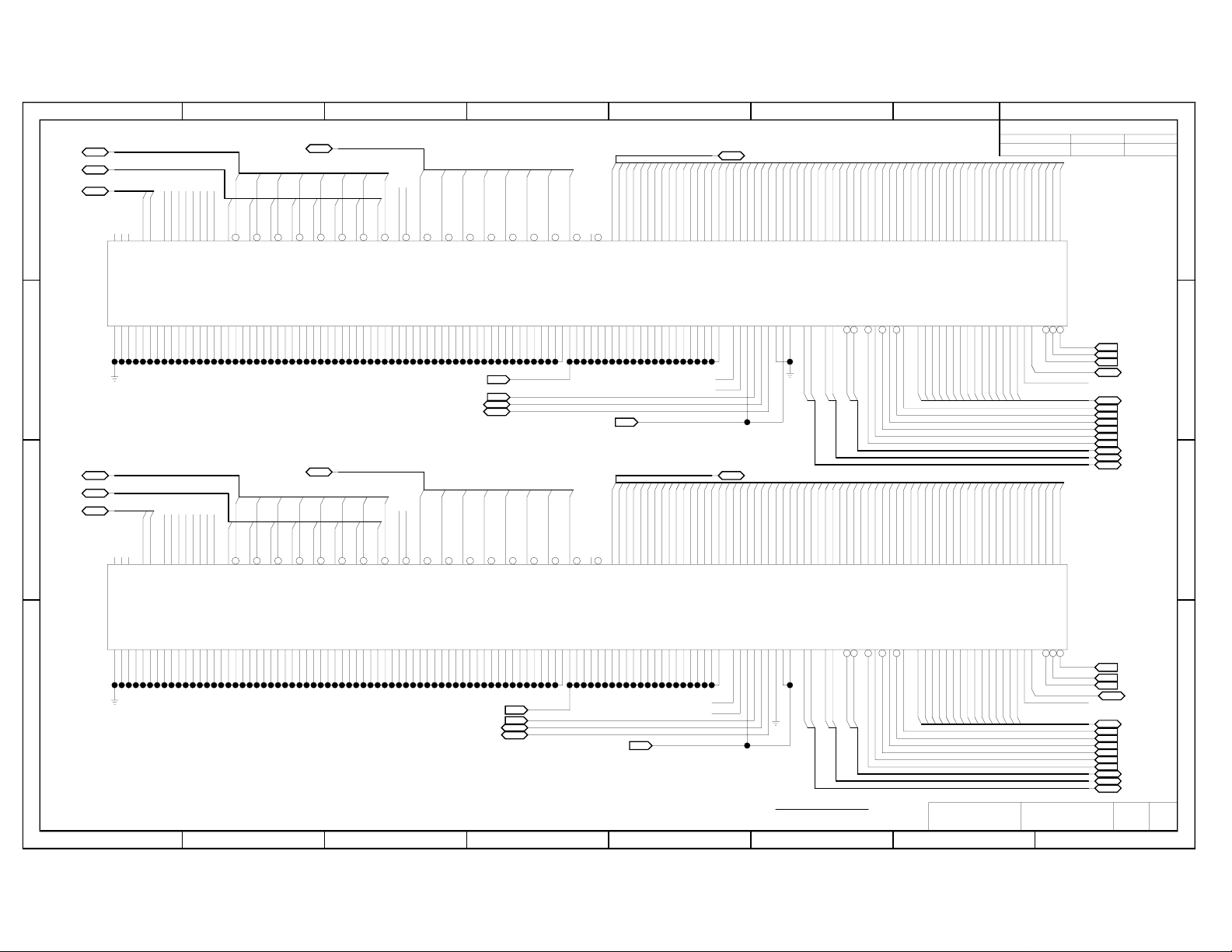

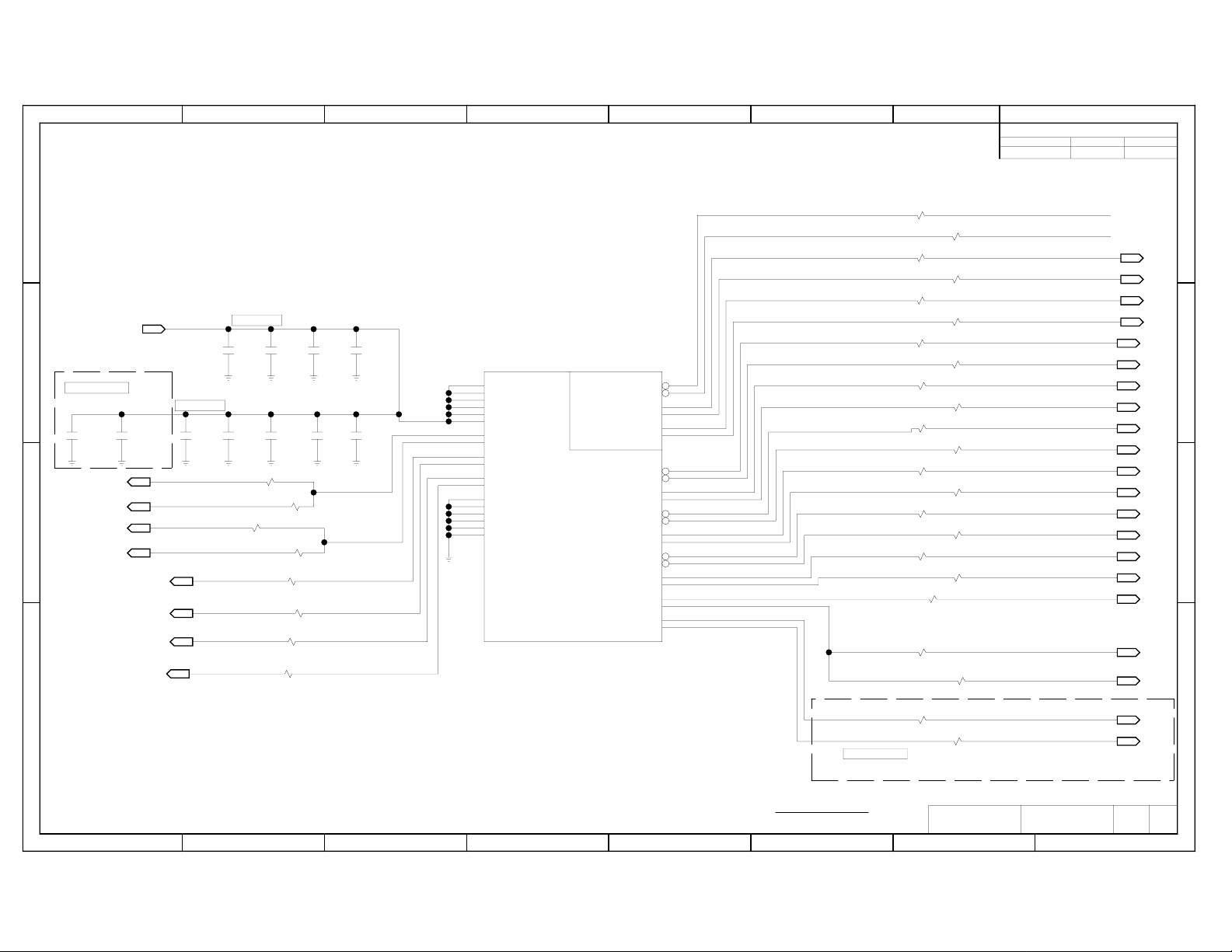

Page 3

CR-3 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE3

8

D

7

6

AFTER P_PCIRST*, HANDSHAKE (ON HL BUS) BETWEEN ICH/MCH MUST

HAPPEN BEFORE H_CPURST* WILL BE ASSERTED/DE-ASSERTED

MCH: MEMORY

CONTROLLER HUB

P_PCIRST*

PWRGD_3V

H_CPURST*

DB_RESET*

45

ICH

FP_RST*

SIO

RES:H_CPURST

3

XDP T_RST

XDP-SSA 30-PIN

2

MODULE REV DETAILS

MODULE NAME

TRST*

H_CPURST*

LGA775 SOCKET

H_PWRGD

CPU\DBR*

1

REV

DATE

FP_RST*

D

PORT ANGELES

PCIRST_OUT*

RES: PA_PLTRST*

C

RES:5V_STBY - PS ON

RES: PS_ON_ HEADER*

POWER (2X12)

SUPPLY CONN

PS_ON*

PWRGD_PS

PCI_RST*

SLP_S4/S5*

SLP_S3*

FP_RST*

PWRGD_PS

PWRGD_3V

RSMRST*

KBRST*

PS_ON*

RES:PLTRST - PCIE

E

PCI GRAPHICS

PWRGD

1X16 CONN

X1-PORT (2)

E

PCI CONN

X1-PORT (1)

PWRGD

TPM (SECURITY)

LRESET*

PCI SLOT 2

PCI SLOT 1

C

P_PCIRST*

B

RESET*

FRONT PANEL CONN

2X8 HEADER

PWR ON SWITCH

A

H_CPURST*

XDP-SSA 31-PIN

DBR*

RESET SWITCH

FP_RST*

FP_RST*

SW_ON*

SW_ON*

JUMPER-STRAP-GND

PULL-UP TERMINATION

PWRGD_3V

RSMRST*

RCIN*

SYS_RESET*

RTC_RST*

SW_ON*

CKT: G_RST*

P_PCIRST*

JRSTSYNC

ICH9: I/O

CONTROLLER HUB

H_PWRGD

ACZ_RST*

S4_STATE

SLP_S4*

SLP_S3*

1394

PLTRST*

RES: SLP_S3*

RES: 1394_PCI_RST*

CKT: G_RST*

RES:JRSTSYNC

RES: CDC_DOWN_RST*

RES: AUD_LINK_RST_HDR*

P_PCIRST*

G_RST*

1394

LAN

JRSTSYNC

AC04 AUDIO CODEC

RESET*

2X8 HDR

AUD_LINK_RST_HDR*

B

A

RESET MAP UPDATED: 09/06/2005

8

7

BPAGE DRAWING

frostburg_fabc.sch_1.3

Sun Mar 18 18:42:56 2007

6

5

4 2

3

[PAGE_TITLE=RESET MAP]

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

xxxxxx

PAGE REV

3

1

3.01

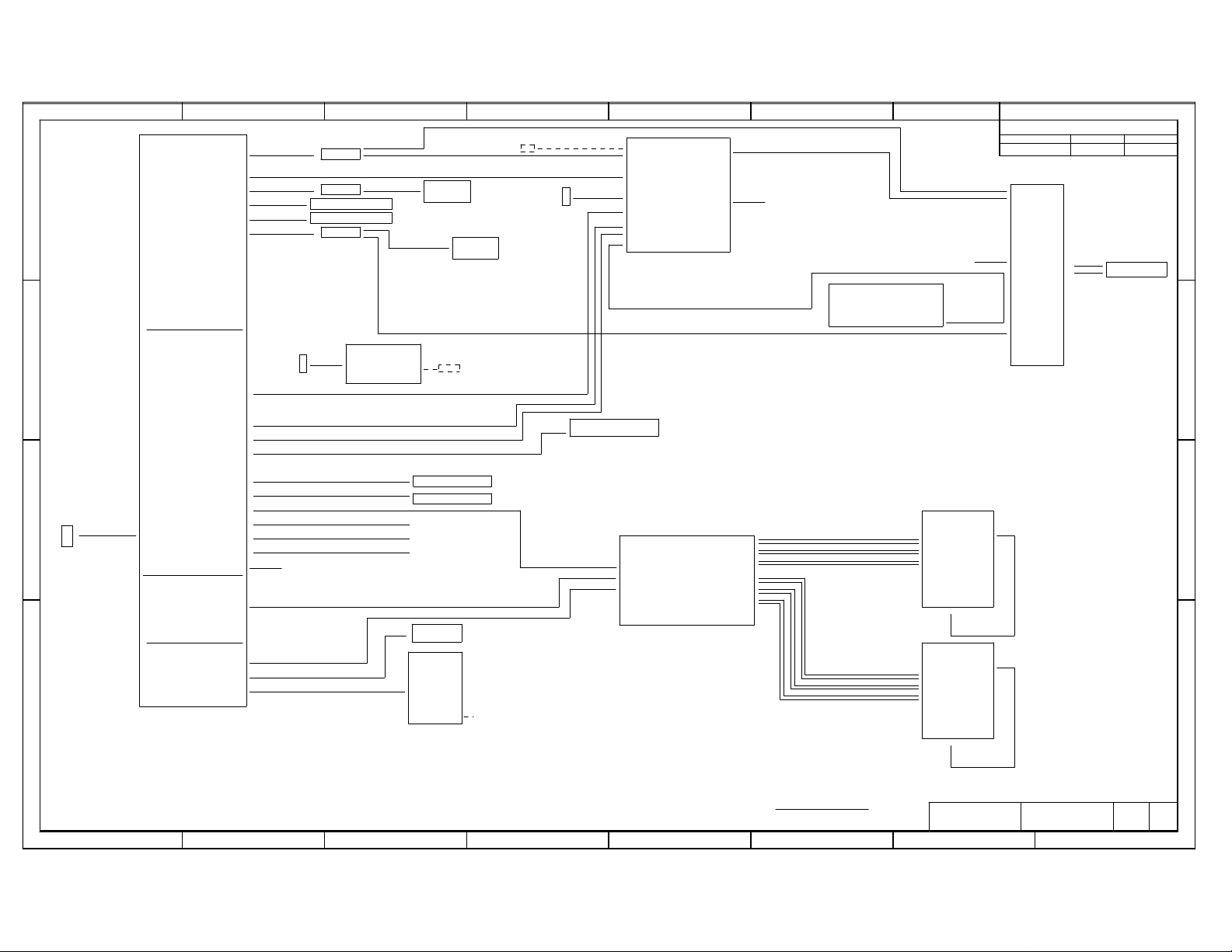

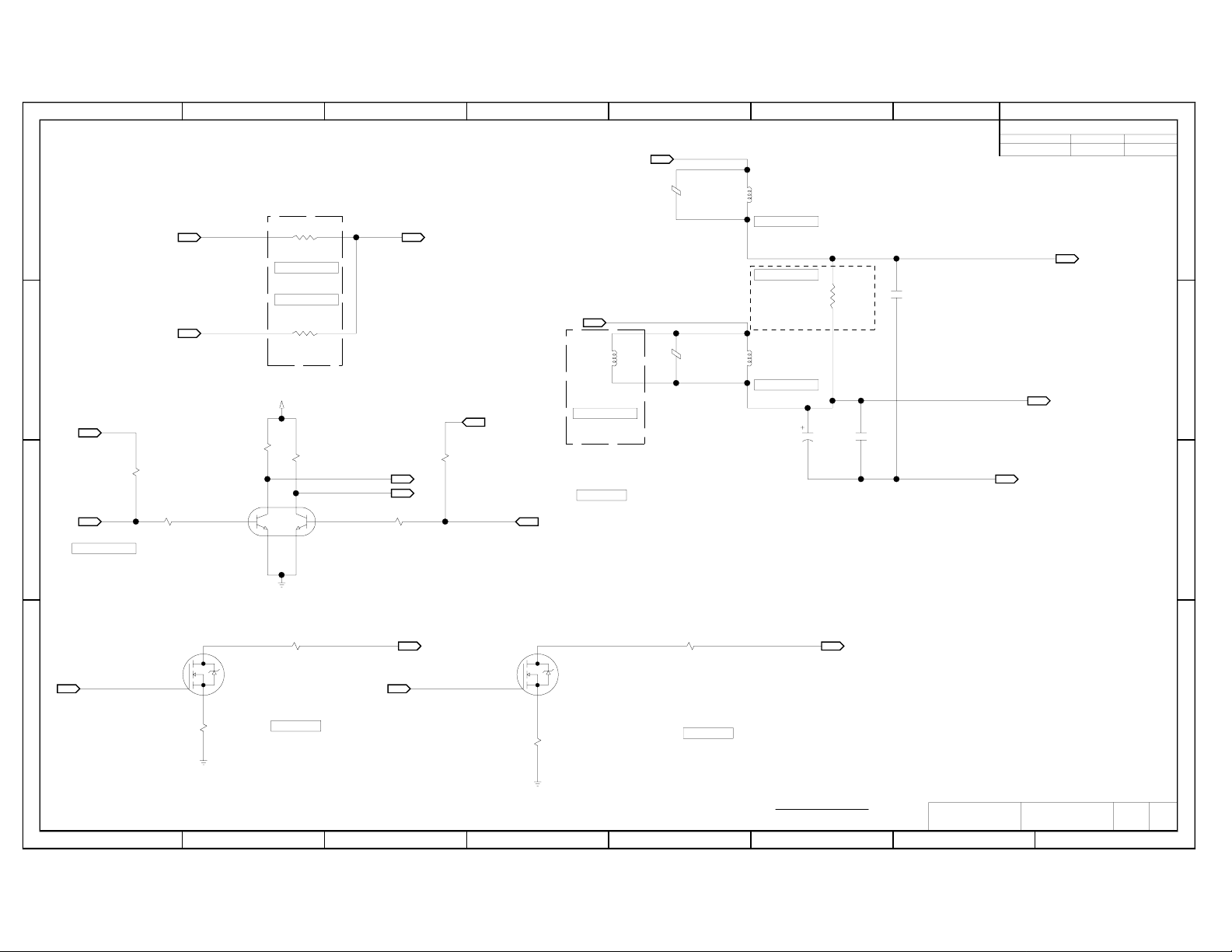

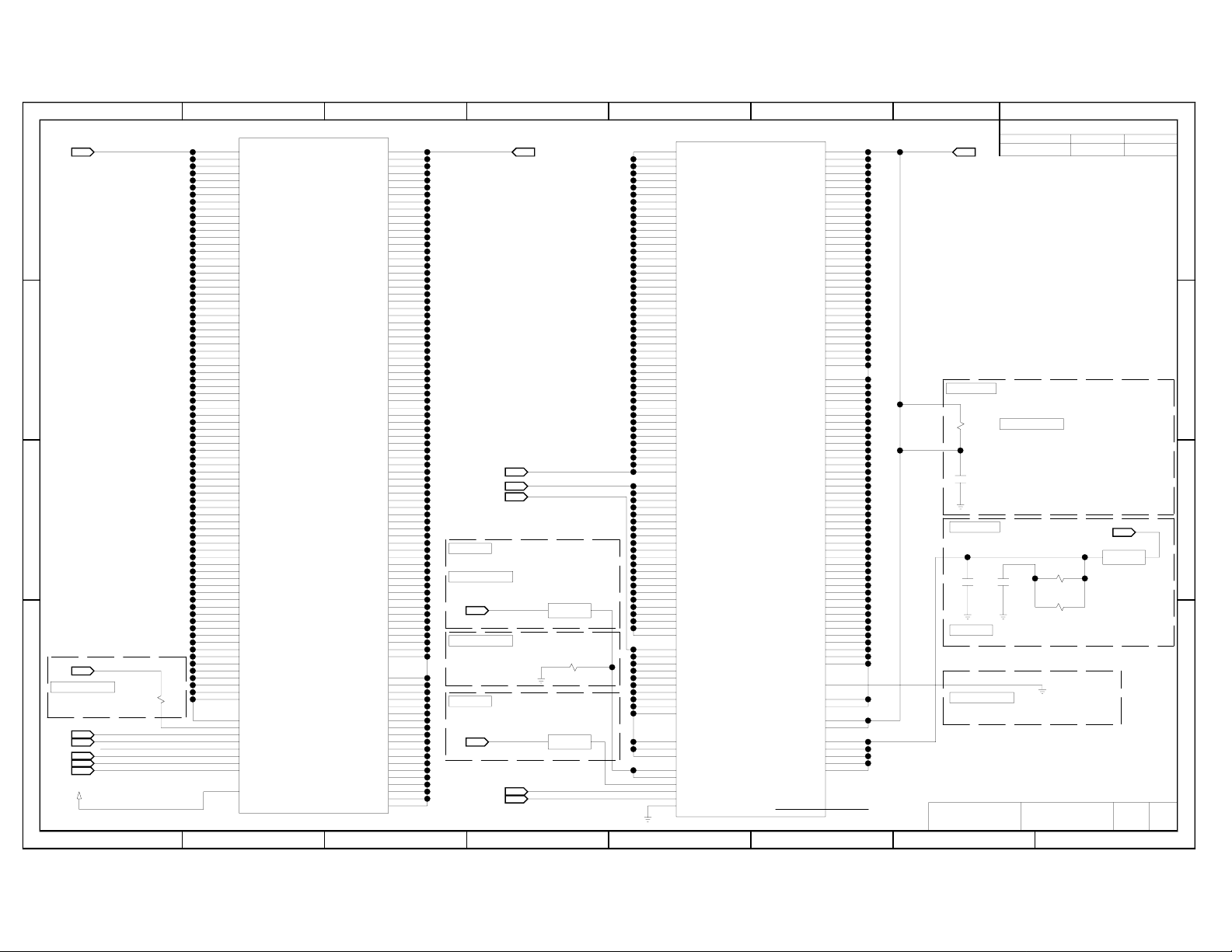

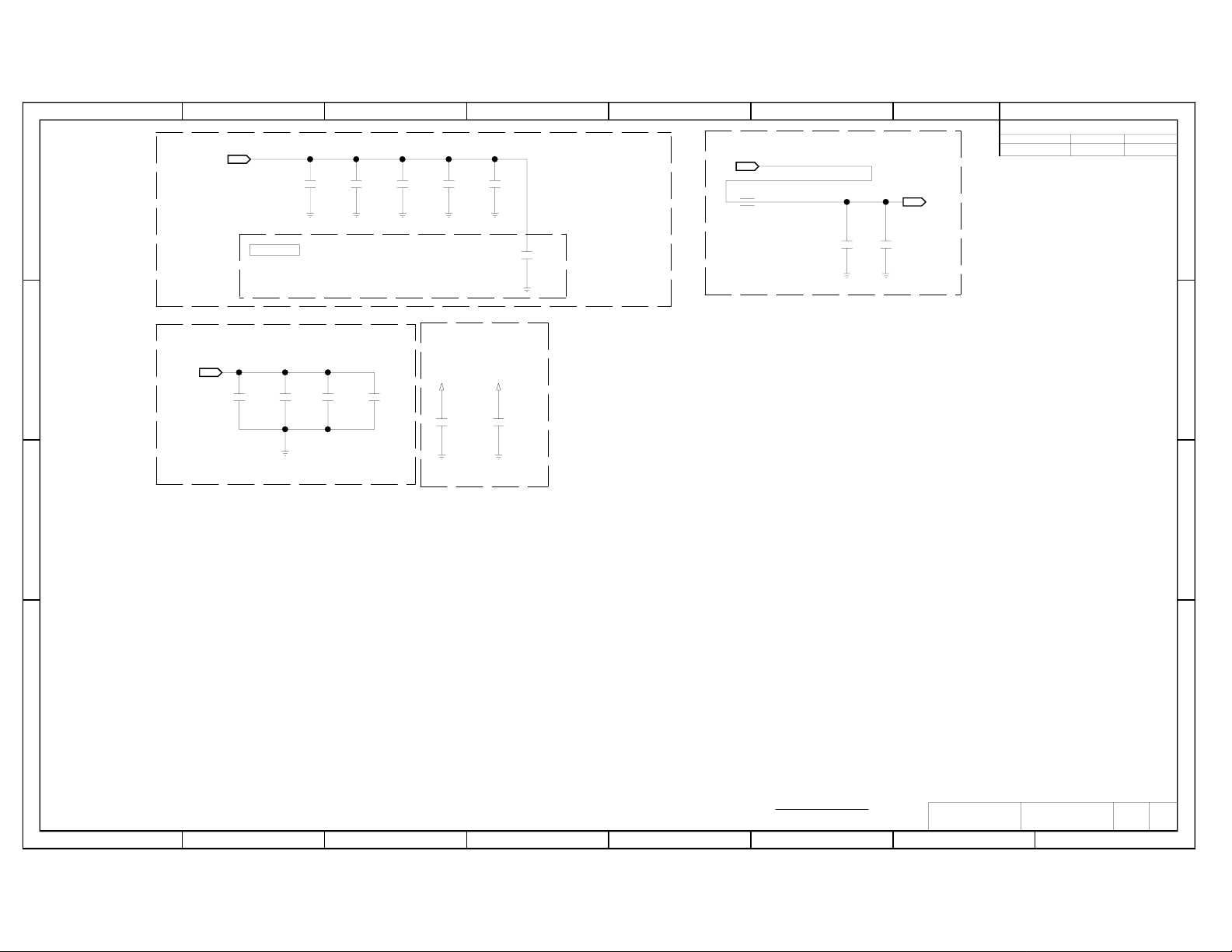

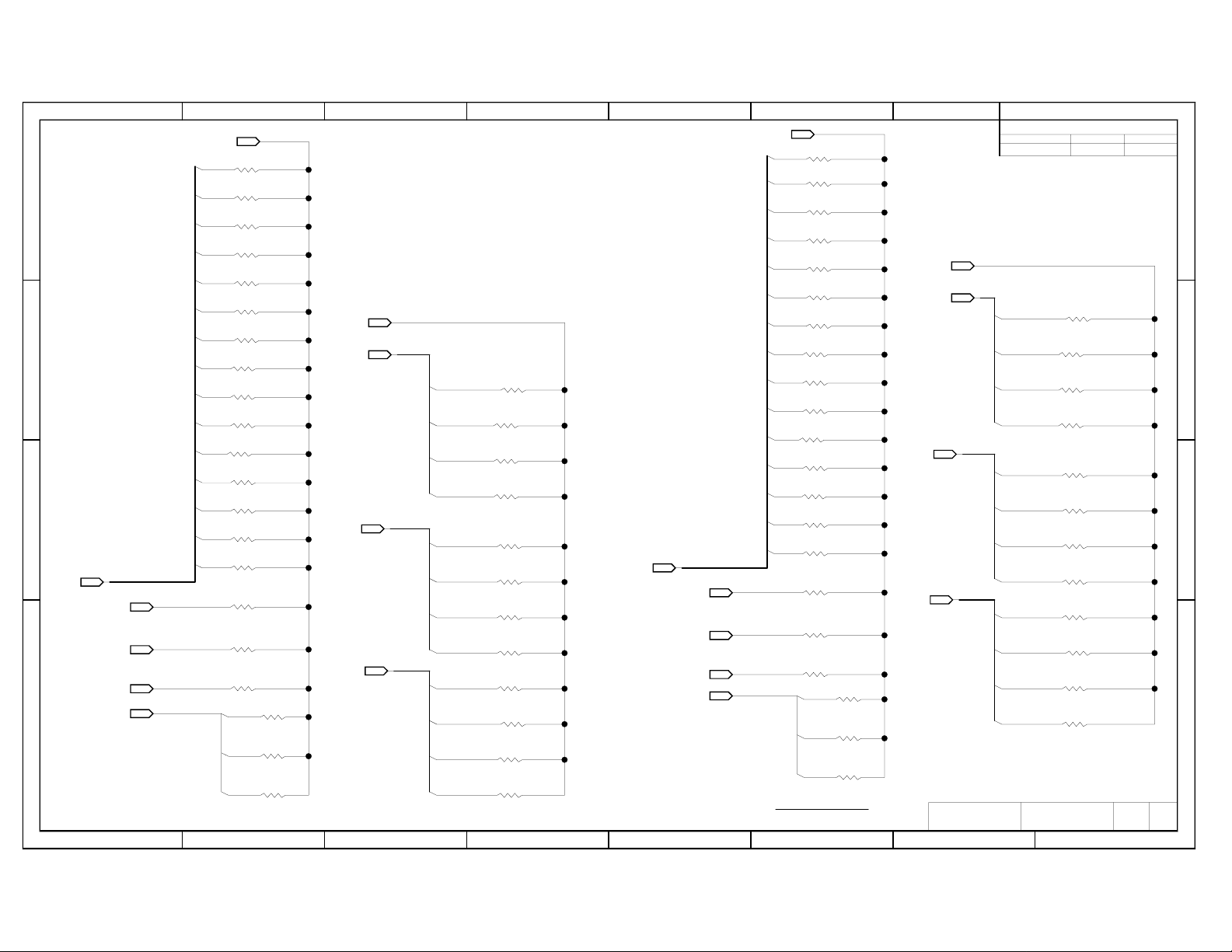

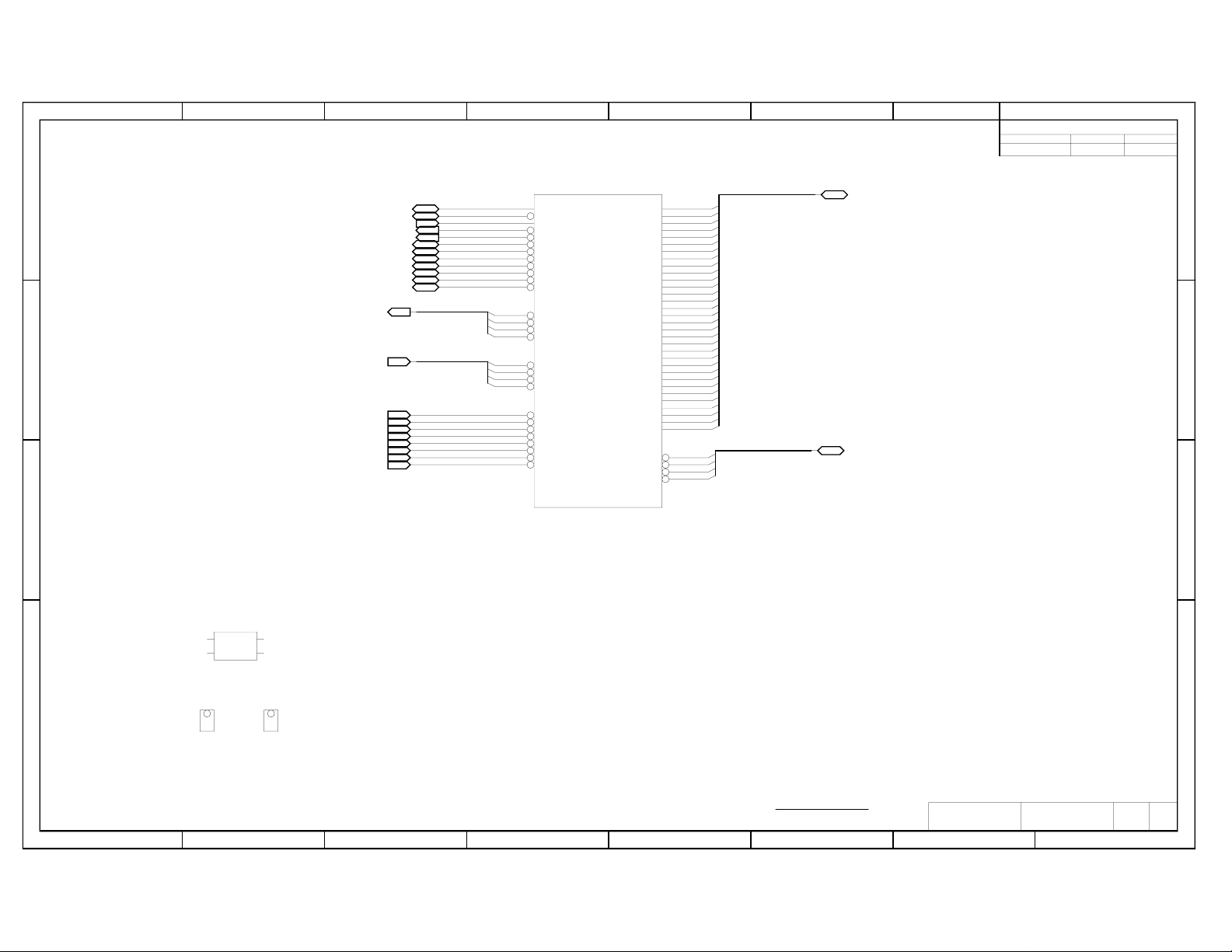

Page 4

CR-4 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE4

8

7

14.318MHZ

RES: 14MHZ

6

JORDAN

LAN

33MHZ

D

3.3 VOLT

33MHZ

33MHZ

33MHZ

33MHZ

RES: 33MHZ

LPC BUS 2X10 (TPM)

PCI SLOT 1

RES: 33MHZ

1394

32.7KHZ

TPM

CLK14

PCICLK

RTCCLK

USBCLK

DMICLK

SATACLK

AUD_BCLK

45

ICH

SUSCLK

SMBUS CLK

32.7KHZLANCLK

SCLK

3

SCLK

2

MODULE REV DETAILS

MODULE NAME

CLK14

SUSCLK

PORT

ANGELES

KBCLK

MCLK

REV

1

DATE

D

MS/KB

AUDIO

CODEC

AUD_BCLK

3.3 VOLT

C

CK505

48MHZ

25MHZ

CRYSTAL

LAN

JORDAN

ICH

12.288 MHZ

33M

C

SRC CLOCK PAIRS

B

A

14.318MHZ

SRC CLOCK PAIR

HOST CLOCK PAIRS

CLOCK DISTRIBUTION UPDATED: 09/07/2005

8

100MHZ

100MHZ

100MHZ

100MHZ

100MHZ

100MHZ

100MHZ

100MHZ

100MHZ

SCLK

96MHZ

100/133/167/200 MHZ CPU_CK

100/133/167/200 MHZ CPU_CK

100/133/167/200 MHZ CPU_CK

7

X1 PCI-EXPRESS #1

X1 PCI-EXPRESS #2

SPARE

SPARE

SPARE

XDP PORT

CPU

CORE

6

XDP

CLK-OUT

XDP CLK-OUT OPTION

5

X16 PCI-EXPRESS

GCLKIN

REFCLKIN

HOST

PCI - GRAPHICS

MCH

DUAL CHANNEL

DDR

2X200/266/333 MHZ

E

BPAGE DRAWING

frostburg_fabc.sch_1.4

Sun Mar 18 18:42:56 2007

4 2

3

CHAN A

DIMM0

DIMM1

CHAN B

DIMM0

DIMM1

[PAGE_TITLE=CLOCK DISTRIBU T I ON]

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

xxxxxx

PAGE REV

1

B

A

4

3.01

Page 5

CR-5 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE5

ICH

D

C

B

PORT ANGELES

GPXX

GPXX

GPXX

GPXX

GPXX

GPXX

GPXX

GPXX

A

GPXX

GPXX

GPXX

GPXX

GPXX

GPXX

GPXX

8

PIN NAME

GP[0]

GP[1]

GP[2]

GP[3]

GP[4]

GP[5]

GP[6]

GP[7]

GP[8]

GP[9]

GP[10]

GP[11]

GP[12]

GP[13]

GP[14]

GP[15]

GP[16]

GP[17]

GP[18]

GP[19]

GP[20]

GP[21]

GP[22]

GP[23]

GP[24]

GP[25]

GP[26]

GP[27]

GP[28]

GP[29]

GP[30]

GP[31]

GP[32]

GP[33]

GP[34]

GP[35]

GP[36]

GP[37]

GP[38]

GP[39]

GP[48]

GP[49]

(PIN 103/118)

(PIN 104/119)

(PIN 105/120)

(PIN 106/121)

(PIN 108/124)

(PIN 109/126)

(PIN 111/127)

(PIN 112/128)

(PIN 116)

(PIN 114)

(PIN 74/115/122)

(PIN 75/113/125)

(PIN 101)

(PIN 100)

(PIN 102)

7

POWER

WELL

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

RESUME (STBY)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

MAIN (CORE)

CPU

(BASED ON NATIONAL PA3.0, MAY 2004, REV 1.1; MULTI-PLEXED/PROGRAMMABLE GPIO PINS)

STBY/VCC3

STBY/VCC3

STBY/VCC3

STBY/VCC3

STBY/VCC3

STBY/VCC3

STBY/VCC3

STBY/VCC3

STBY

STBY

STBY/STBY/VCC3

STBY/STBY/VCC3

STBY

STBY

N/C (P A30)

USAGE

FP AUD DETECT

FRONT FAN TACH

P_INTE

P_INTF

P_INTG

P_INTH

REAR FAN TACH

EV FAN TACH

SATA/HOT-SWAP

WOL

NOT USED (RVP)

PORT 80 LED

BOARD ID 3

LPC_SIO_PME

NOT USED (RVP)

LAN DISABLE

BOARD ID 1

CPU FAN TACH

BOARD ID 2

SATA1GP

NOT USED (TP): SATA HOTSWAP CTL

SATA0GP

NOT USED

LDRQ1

V_SM LED CONTROL

BOARD ID 4

S4_STATE

NOT USED (TP)

NOT USED (TP)

OC5

OC6

OC7

BOARD ID 0

MFG_MODE (RVP)

ICH CFG JUMPER

NOT USED (TP)

SATA2GP

SATA3GP

NOT USED

NOT USED

NOT USED

CPUPWRGD

NOT USED (TP)

1394 ENABLE

NOT USED (TP)

1 WATT VREG CONTROL

1 WATT VREG CONTROL+

MEM. OVERVOLTAGECONTROL1

MEM. OVERVOLTAGE CONTROL2 (TP)

BOARD ID 5

5V_DDCSDA 2.2K P/U TO VCC

5V_DDCSCL

3V_DDCSDA

3V_DDCSCL

2X12 HDR DETECT

NOT USED (TP)

NOT USED (PA30)

AFTER

PLTRST

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT(ALERT)

IN

IN

IN

OUT

IN

IN

IN

IN

OUT

IN

IN

OUT

OUT

IN

OUT

LOW

LOW

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

N/C (PA30)

6

GPIO SIGNALS NOT USED: GP40-47

S3/S5

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

NOTES

10K P/U TO VCC3

3.3K P/U TO +12V (THRU 15K)

8.2K P/U TO VCC

8.2K P/U TO VCC

8.2K P/U TO VCC

8.2K P/U TO VCC

3.3K P/U TO +12V (THRU 15K)

3.3K P/U TO +12V (THRU 15K),10K VCC3

10K P/U TO V_3P3_STBY

100K P/D TO GND

10K P/U TO V_3P3_STBY

10K P/U TO V_3P3_STBY

10K P/U TO V_3P3_STBY, 10K P/D

10K P/U TO V_3P3_STBY

10K P/U TO VCC3, 10K P/D

3.3K P/U TO +12V (THRU 15K)

10K P/U TO VCC3, 10K P/D

10K P/U TO VCC3

10K P/U TO VCC3

10K P/U TO VCC3

10K P/U TO VCC3

1K P/U TO V_SM (THRU EMPTY 0 OHM RES)

10K P/U TO V_3P3_STBY, 10K P/D

10K P/U TO V_3P3_STBY (EV DESIGN ONLY)

ENERGY LAKE STATUS LED: GREEN

ENERGY LAKE STATUS LED: YELLOW

NOA SHARED WITH OVER-CURRENT

NOA SHARED WITH OVER-CURRENT

NOA SHARED WITH OVER-CURRENT

10K P/U TO VCC3, 10K P/D

4.7K P/U TO VCC3

1K P/U TO VCC3 (SUITCASE JMPR); 4.7K P/D TO GND: BIOS NORMAL, RECOVER, CONFIGURE

10K P/U TO VCC3

10K P/U TO VCC3

10K P/U TO VCC3

10K P/D TO GND

10K P/U TO VCC3

EMPTY 100 OHM P/U (VTT)

1K P/D TO GND

10K EMPTY P/U TO V_3P3_STBY (1.8/1.9 VREG CTL)

2.2K P/U TO VCC

2.2K P/U TO VCC3

2.2K P/U TO VCC3

AUDIO

A

LAN

2

MODULE REV DETAILS

MODULE NAME

PCI X1

USB2

USB1

2.0

2.0

#2

#1

B

A

C

A

A

2420

45

3

IRQ ROUTING TABLE (EXCERPT FROM ICH BIOS BKM REV 0.72)

SLOT2

P_INTA*

P_INTB*

P_INTC*

P_INTD*

P_INTE*

P_INTF*

P_INTG*

P_INTH*

REQ/GNT

IDSEL

SLOT1

IRQD

IRQA

IRQB

IRQC

16

SLOT4

SLOT3

IRQD

IRQC

IRQA

IRQB IRQA

IRQB

IRQC

IRQB

IRQA

IRQD

1

0

IRQA

IRQC

IRQD

3

2

19

1817

SLOT5

IRQC

IRQD

IRQB

SLOT6

IRQA

IRQB

IRQD

IRQC

21

SMBUS ADDRESS LINES SA [2-0] SMBUS ADDRESS

MEMORYSLOT-0 (CHANNEL-A: SLOT-0) 0000A1H0A0H

MEMORYSLOT-1 (CHANNEL-A: SLOT-1) 0010A3H0A2H

MEMORYSLOT-2 (CHANNEL-B: SLOT-0) 0100A5H0A4H

MEMORYSLOT-3 (CHANNEL-B: SLOT-1) 0110A7H0 A6H

CK410 - - - 0D3H 0D2H

DB800/DB400 - - - 0DDH 0DCH

SMBUS DATA (EXCERPT FROM ICH BIOS BKM REV 0.72)

#3

C

1

REV

PCI X16

#1

A

DATE

D

SMBUS

#2

C

C

B

A

MULTI-PLEXED GPIO PINS ON PORT ANGELES WHICH ARE USED FOR SPECIFIC FUNCTIONS (NOT AS GPIO) ARE NOT IDENTIFIED HERE

UN-USED GPIO PINS ON PORT ANGELES ARE NOT IDENTIFIED HERE

TOTAL OF (33) POSSIBLE GPIO PINS ON PORT ANGELES (POWER WELL: STBY OR V_3P3_STBY = RESUME, VCC3 = MAIN).

NOTE: (0-4) GP'S FROM THE FWH WERE NOT USED (POWER WELL = CORE, INPUT ONLY)

8

7

6

5

4 2

BPAGE DRAWING

frostburg_fabc.sch_1.5

Sun Mar 18 18:42:57 2007

3

[PAGE_TITLE=GPIO, IRQ, IDSEL MAP]

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

xxxxxx

PAGE REV

5

1

3.01

Page 6

CR-6 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE6

8

BI

BI

BI

BI

BI

H_ADSTB1_N

H_A_N<16..3>

H_REQ_N<4..0>

H_ADSTB0_N

H_A_N<35..17>

TP_CPU_AC4

TP_CPU_AE4

3

4

5

6

7

8

9

10

11

12

13

14

15

16

TP_RSVD_N4

TP_RSVD_P5

0

1

2

3

4

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

10

D

10

10

10

C

10

B

105

1

VTT_OUT_RIGHT

6

7

IN

89397

2

R128PR

51

5%

CH

402

VTT_OUT_RIGHT

7893

97

105

A

6

IN

1

C1PR

.1UF

20%

25V

2

EMPTY

603

DESIGN NOTE:

INTERNAL PU AVAILABLE

R1BU

ATX DESIGN ONLY

1K

5%

EMPTY

402

CPU_BOOT

1

DESIGN NOTE:

STUFF R128PR TO PREVENT

2

PSC,SMF,CDM & PSL CPU

FROM BOOTING

R7PR

1

49.9

1%

2

CH

402

8

1

2

AB6

AA4

AD6

AA5

AB5

AC5

AB4

AF5

AF4

AG6

AG4

AG5

AH4

AH5

AJ5

AJ6

AC4

AE4

AD5

L5

P6

M5

L4

M4

R4

T5

U6

T4

U5

U4

V5

V4

W5

N4

P5

K4

J5

M6

K6

J6

R6

W6

Y6

Y4

R16PR

49.9

1%

CH

402

A<3>*

A<4>*

A<5>*

A<6>*

A<7>*

A<8>*

A<9>*

A<10>*

A<11>*

A<12>*

A<13>*

A<14>*

A<15>*

RSVD

RSVD

REQ<0>*

REQ<1>*

REQ<2>*

REQ<3>*

REQ<4>*

ADSTB<0>*

A<17>*

A<18>*

A<19>*

A<20>*

A<21>*

A<22>*

A<23>*

A<24>*

A<25>*

A<26>*

A<27>*

A<28>*

A<29>*

A<30>*

A<31>*

A<32>*

A<33>*

A<34>*

A<35>*

RSVD

RSVD

ADSTB<1>*

OUT

7

6

1

R8PR

130

1%

EMPTY

402

2

H_COMP6

H_COMP7

7

J1PR

LGA775_C

REV=1.8

H_FORCEPH_N

ADS*

BNR*

HIT*

RSP*

BPRI*

DBSY*

DRDY*

HITM*

IERR*

INIT*

LOCK*

TRDY*

BINIT*

DEFER*A<16>*

MCERR*

AP<0>*

AP<1>*

BR<0>*

TESTHI_8

TESTHI_9

TESTHI_10

DP<0>*

DP<1>*

DP<2>*

DP<3>*

GTLREF0

GTLREF1

GTLREF2

GTLREF_SEL

RESET*

RS<0>*

RS<1>*

RS<2>*

1of 4

IC

OUT

OUT

OUT

6

H_ADS_N

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

G7

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H1

H2

E24

H29

G23

B3

F5

A3

TP_RSP_N

TP_BINIT_N

TP_MCERR_N

TP_AP<0>

TP_AP<1>

TP_CPU_J16

TP_CPU_H15

TP_CPU_H16

TP_CPU_J17

0

1

2

H_BNR_N

H_HIT_N

H_BPRI_N

H_DBSY_N

H_DRDY_N

H_HITM_N

H_IERR_N

H_INIT_N

H_LOCK_N

H_TRDY_N

H_DEFER_N

H_BR_N<0>

H_BPM3_2

H_BPM2_2

H_TESTHI_10

CPU_GTLREF0

CPU_GTLREF1

CPU_MCH_GTLREF

TP_GTL_DET

H_CPURST_N

H_RS_N<2..0>

OUT

BI

BI

BI

IN

BI

BI

BI

IN

BI

IN

IN

BI

BI

BI

BI

IN

IN

OUT

IN

IN

10

10

10

10

10

10

10

8

32

10

10

10

8

10

97

97

8

8

8

17

8

10 97

10

R19PR

PRECISION FSB COMPENSATION RESISTORS

69

16

6

95

6

6

6

7897

IN

IN

VTT_OUT_LEFT

1

C2PR

.1UF

20%

25V

2

EMPTY

603

H_VCCPLL

1

2

C18PR

10UF

20%

6.3V

EMPTY

805

1

2

5

C3PR

.01UF

20%

50V

X7R

603

32

16

93

70

949596105

H_CPU_PD_F6

1

51

5%

2

CH

402

1

R14PR

49.9

1%

CH

402

2

32

32

8

32

32

32

33

9

9

9

69

93

8

29

29

33

76

76

93

93

93

93

76

DESIGN NOTE:

50OHM ON 1080

TP ON 2116

45

ICH_H_SMI_N H_TESTHI_0

IN

H_A20M_N

IN

H_FERR_N

OUT

H_INTR

IN

H_NMI

IN

H_IGNNE_N

IN

H_STPCLK_N

IN

H_VCCA

IN

H_VSSA

IN

H_VCCIOPLL

IN

H_VCCPLL

IN

H_VID<7..0>

2

1

OUT

OUT

IN

IN

OUT

IN

OUT

OUT

OUT

OUT

OUT

IN

105

R18PR

49.9

1%

CH

402

VRD_VIDSEL

CK_H_CPU_DP

CK_H_CPU_DN

H_SKTOCC_N

H_TEMP_SRC_DP

H_TEMP_RET_DN

VCC_SENSE

VSS_SENSE

VCC_PKGSENSE

VSS_PKGSENSE

TP_VTT_PKGSENSE

TP_SLEW_CTRL

H_PECI

BI

TP_MPG_NOBOOT

1

R17PR

49.9

1%

CH

402

2

2

1

VCCP

R20PR

49.9

1%

CH

402

0

1

2

3

4

5

6

7

6

IN

6

IN

1

1

R12PR

49.9

1%

CH

402

2

2

Sun Mar 18 18:42:58 2007

4 2

3

J1PR

LGA775_C

P2

K3

R3

K1

L1

N2

M3

A23

B23

C23

D23

AM2

AL5

AM3

AL6

AK4

AL4

AM5

AM7

AN7

F28

G28

AE8

AL1

AK1

AJ7

AH7

AN3

AN4

AN5

AN6

AL8

AL7

F29

F6

G6

G5

AL3

DESIGN NOTE:

STUFF R15PR FOR 95W YORKFIELD

DESIGN NOTE:

STUFF R13PR FOR 65W CPU:CNR/WOLFDALE

1

R22PR

49.9

1%

2

CH

402

BPAGE DRAWING

frostburg_fabc.sch_1.6

REV=1.8

SMI*

A20M*

FERR*/PBE*

LINT0

LINT1

IGNNE*

STPCLK*

VCCA

VSSA

VCCIOPLL

VCC_PLL

VID<0>

VID<1>

VID<2>

VID<3>

VID<4>

VID<5>

VID<6>

VID<7>

VID_SELECT

BCLK<0>

BCLK<1>

SKTOCC*

THERMDA

THERMDC

RSVD

RSVD

VCC_SENSE

VSS_SENSE

VCC_MB_REGULATION

VSS_MB_REGULATION

VCC

VSS

RSVD

IMPSEL

RSVD

PECI

NC

105

H_MSID0

H_MSID1

R21PR

24.9

1%

CH

402

H_COMP8

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_COMP4

H_COMP5

0

402

R13PR

1

EMPTY

3of 4

6789397

5%

3

TESTHI_0

TESTHI_1

TESTHI_2

TESTHI_3

TESTHI_4

TESTHI_5

TESTHI_6

TESTHI_7

TESTHI_11

TESTHI_12

TESTHI_13

FORCEPR*

PWRGOOD

PROCHOT*

THERMTRIP*

COMP<0>

COMP<1>

COMP<2>

COMP<3>

COMP<4>

COMP<5>

COMP<6>

COMP<7>

COMP<8>

MSID<1>

MSID<0>

BOOTSELECT

LL_ID<0>

LL_ID<1>

IN

R15PR

0

2

402

OUT

OUT

OUT

OUT

OUT

OUT

OUT

2

MODULE REV DETAILS

MODULE NAME

F26

H_TESTHI_1

W3

H_TESTHI_2_7

F25

G25

G27

G26

G24

F24

H_TESTHI_11

P1

H_TESTHI_M

W2

H_TESTHI_13

L2

H_FORCEPH_N

AK6

H_PWRGD

N1

H_PROCHOT_N

AL2

H_THERMTRIP_N

RSVD

RSVD

RSVD

RSVD

FC5

RSVD

RSVD

M2

A13

T1

G2

R1

J2

T2

Y3

AE3

B13

G1

U1

A24

E29

F2

G10

AH2

V1

W1

Y1

V2

AA2

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_COMP4

H_COMP5

H_COMP6

H_COMP7

H_COMP8

H_BPM0_2

H_TESTHI_M

H_DCKLPH2

TP_SFRANAD2

CPU_GTLREF2

CPU_GTLREF3

TP_CPU_AH2

H_MSID1

H_MSID0

CPU_BOOT

TP_V2

TP_LL_ID1

BI

OUT

OUT

97

6

8

8

IN

8

IN

OUT

OUT

IC

VTT_OUT_RIGHT

R131PR

1

R130PR

1

1K

5%

2

EMPTY

1

2

5%

EMPTY

DESIGN NOTE:

EMPTY Q1PR FOR VTT TOOL TEST

6

6

6

6

6

6

6

[PAGE_TITLE=CPU-SOCKET 1 OF 2]

CONFIDENTIAL

CUSTOM TEXT BPAGE

402

H_MSID_XSTR_BASE_1

INTEL

680

5%

CH

2

VRD_ENABLE

402

3

Q1PR

1

MMBT3904

EMPTY

2

DOCUMENT_NUMBER

xxxxxx

REV

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

402

1

R112PR

1

1K

8

8

8

8

68

8

6

8

837

8

6

6

6

6

6

6

6

6

6

6

6

6

1

DATE

95

33

95

32

2

5%

EMPTY

OUT

PAGE REV

6

D

C

B

93

A

3.01

Page 7

CR-7 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE7

8

R124PR

2

VR_READY

8

39

IN

93

0CH5%

402

1

D

CAD NOTE:

H_VR_READY

7

7

OUT

6

97

97

97

97

97

97

PLACE CLOSE TO VR CONTROLLER

333651

7097

C

R33PR

1

1K

5%

2

EMPTY

402

DESIGN NOTE:

FOR DEBUG ONLY

J1PR

H_D_N<15..0>

10

BI

B

H_DBI_N<0>

10

BI

H_STBN_N<0>

10

BI

H_STBP_N<0>

10

BI

H_D_N<31..16> H_D_N<63..48>

10 10

BI

A

H_DBI_N<1>

10

BI

H_STBN_N<1> H_STBN_N<3>

10 10

BI

H_STBP_N<1> H_STBP_N<3>

10 10

BI

B4

0

C5

1

A4

2

C6

3

A5

4

B6

5

6

B7

A7

7

A10

8

A11

9

B10

10

C11

11

D8

12

13

B12

14

C12

D11

15

A8

C8

B9

G9

16

F8

17

18

F9

19

E9

20

D7

E10

21

D10

22

F11

23

F12

24

D13

25

E13

26

G13

27

F14

28

G14

29

F15

30

G15

31

G11

G12

E12

D<0>*

D<1>*

D<2>*

D<3>*

D<4>*

D<5>*

D<6>*

D<7>*

D<8>*

D<9>*

D<10>*

D<11>*

D<12>*

D<13>*

D<14>*

D<15>*

DBI<0>*

DSTBN<0>*

DSTBP<0>*

D<16>*

D<17>*

D<18>*

D<19>*

D<20>*

D<21>*

D<22>*

D<23>*

D<24>*

D<25>*

D<26>*

D<27>*

D<28>*

D<29>*

D<30>*

D<31>*

DBI<1>*

DSTBN<1>*

DSTBP<1>*

LGA775_C

REV=1.8

D<32>*

D<33>*

D<34>*

D<35>*

D<36>*

D<37>*

D<38>*

D<39>*

D<40>*

D<41>*

D<42>*

D<43>*

D<44>*

D<45>*

D<46>*

D<47>*

DBI<2>*

DSTBN<2>*

DSTBP<2>*

D<48>*

D<49>*

D<50>*

D<51>*

D<52>*

D<53>*

D<54>*

D<55>*

D<56>*

D<57>*

D<58>*

D<59>*

D<60>*

D<61>*

D<62>*

D<63>*

DBI<3>*

DSTBN<3>*

DSTBP<3>*

G16

E15

E16

G18

G17

F17

F18

E18

E19

F20

E21

F21

G21

E22

D22

G22

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

H_D_N<47..32>

H_DBI_N<2>

H_STBN_N<2>

H_STBP_N<2>

H_DBI_N<3>

2of 4

IC

8

7

6

OUT

81328

81328

81328

IN

IN

OUT

IN

IN

BI

OUT

OUT

OUT

97

97

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST_N

H_BPM_N<5..0>

FP_RST_N

XDP_CLKOUT_DP

OUT

XDP_CLKOUT_DN

OUT

H_FSBSEL0

H_FSBSEL1

H_FSBSEL2

97

891417 34 38

IN

2

MODULE REV DETAILS

MODULE NAME

85

7

IN

689397

105

68

97

85

DESIGN NOTE:

ENG FEATURE: 1K RES (EMPTY)

R32PR

2

5%

EMPTY

R31PR

2

5%

EMPTY

OUT

OUT

OUT

1

1K

402

1

1K

402

45

J1PR

LGA775_C

TCK

TDI

TDO

TMS

TRST*

BPM<0>*

BPM<1>*

BPM<2>*

BPM<3>*

BPM<4>*

BPM<5>*

DBR*

ITPCLK<0>

ITPCLK<1>

BSEL<0>

BSEL<1>

BSEL<2>

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

REV=1.8

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT_PWRGD

VTT_SEL

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

4of 4

AE1

AD1

AF1

AC1

AG1

AJ2

0

AJ1

1

AD2

2

AG2

3

AF2

4

AG3

5

AC2

AK3

AJ3

G29

H30

G30

N5

CPU_N5

H_BPM1_2

BI

TP_CPU_E7

TP_CPU_AE6

TP_CPU_D16

TP_ACLKPH2

TP_SFRANAC2

10

BI

10

BI

10

BI

10

BI

BI

C9

E7

AE6

D16

A20

E23

VCCP=AG22,K29,AM26,AE12,AE11

VCCP=W23,W24,W25,T25,Y28,AL18,AC25,W30,Y30,AN14,AD28,Y26,AC29,M29,U24,J23,AC27,AM18,AM19,AB8

VCCP=AC26,J8,J28,T30,AM9,AF15,AC8,AE14,N23,W29,U29,AC24,AC23,Y23,AN26,AN25,AN11,AN18,Y27,Y25

VCCP=U27,AD24,AE23,AE22,AN19,V8,K8,AE21,AM30,AE19,AC30,AE15,M30,K27,M24,AN21,T8,AC28,N25,AE18,W26

VCCP=AD25,M8,N30,AD26,AJ26,AM29,M25,M26,L8,U25,Y8,AJ12,AD27,U23,M23,AG29,N27,AM22,U28,K28

VCCP=U8,AK18,AD8,K24,AH28,AH21,AK12,AH22,T29,AM14,AM25,AE9,Y29,AK25,AK19,AG15,J22,T24,AG21,AM21

VCCP=J25,U30,AL21,AG25,AJ18,J19,AH30,J15,AG12,AJ22,J20,AH18,AH26,W27,AL25,AN8,AH14,T23,R8

VCCP=AK22,AN29,AG11,AK26,J10,AJ15,AG26,AN9,AH15,AF18,AL15,J26,J18,J21,AG27,AK15,AF11,AD23,AM15,AF8

VCCP=AK21,AG30,AJ21,AM11,AL11,AJ11,K30,AL14,AN30,AH25,AL12,AJ9,AK11,AG14,N29,AL30,AJ25,AH9,J29,J11

VCCP=K25,P8,K23,AL19,AM8,T26,N28,AH12,AL22,AN15,AJ8,U26,AJ19,T27,AK8,AN12,AG9,N26,AF9,AF22

VCCP=AH11,AJ14,AH19,AH29,AH27,AG28,AL26,AM12,J24,J13,T28,W28,J12,J27,AG19,AL9,AD30,AF21,Y24,AK14

VCCP=J9,M27,AF14,J30,AG18,AA8,AG8,AL29,AD29,W8,AH8,N24,AN22,J14,K26,AF19,N8,AF12,M28,AK9

GND=C10,D12,C24,K2,C22,AN1,B14,K7,AE16,B11,AL10,AK23,H12,AF7,AK7

GND=H7,E14,L28,Y5,E11,AL16,AL24,AK13,D21,AL20,D18,AN2,AK16,AK20,AM27,AM1,AL13,AL17,C19

GND=E28,AK30,D24,AL23,A12,L25,J7,AE28,AE29,K5,J4,AE30,AN20,AF10,AE24,AM24,AN23,H9,H8

GND=H13,AC6,AC7,AH6,C16,AM16,AE25,AE27,AJ28,F19,AH13,AD7,AH16,AK17,E17,AH17,AH20,AE5,AH23

GND=AE7,AM13,AH24,AJ30,AJ10,AF3,AK5,AJ16,AF6,AK29,AJ17,F22,AH3,AK10,AM10,F16,AJ23,F13,AG7,F10

GND=L26,AD4,H11,L24,L23,AM23,A15,AH10,B24,L3,H27,A21,AE2,AJ29,AK27,AK28,B20,AM20

GND=H26,B17,H25,H24,AA3,AA7,H23,AA6,H10,H22,H21,H20,H19,H18,AB7,H17,AJ24,AM17,AC3,H14

GND=P28,V6,AK2,P27,P26,AM28,AJ13,W4,P25,AJ20,W7,P23,C7,L30,L29,D15,AL27,Y7,L27

GND=AA29,N6,N7,AA28,AN13,AA27,AA26,P4,AA25,AA24,P7,E26,V30,R2,V29,V28,R5,V27,R7,E20

GND=AN10,V25,T3,V24,V23,T6,E25,R29,R28,R27,R26,R25,U7,R24,R23,P30,V3,P29

GND=AF16,AE10,AF13,H6,A18,A2,E2,D9,C4,A6,D6,D5,A9,D3,B1,B5,B8,AJ4,AE26,AH1

GND=V7,C13,AK24,AB30,L6,L7,AB29,M1,AB28,AN17,AB27,AB26,AN16,M7,AB25,AB24,AB23,N3,AA30

GND=F4,AG10,AE13,AF30,H28,F7,AF29,AF28,AF27,AF26,AF25,AN28,AN27,AF24,AF23,AG24,AF17,AN24,H3

GND=Y2,P24,AE20,AE17,E27,T7,R30,AJ27,AB1,AM4,V26,AA23,AL28,AF20,AG23,AG20,E8,AG17,AG16,AG13

3

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL

F27

TP_EXTBGREF

F23

D14

TP_SFRANAD

TP_SFRANAC

E6

H_DCLKPH

E5

H_ACLKPH

J3

TP_HFPLL

D1

CAD NOTE:

PLACE A GND VIA

IC

NEAR TP ON

PIN D1

V_FSB_VTT

H_VR_READY

1

REV

DATE

D

1

1

C4PR

2

X7R

603

.1UF

10%

16V

C5PR

C

.1UF

10%

16V

2

X7R

603

B

A

10

BI

BI

BI

BPAGE DRAWING

frostburg_fabc.sch_1.7

Sun Mar 18 18:42:59 2007

5

4 2

3

[PAGE_TITLE=CPU SOCKET 2 OF 2]

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

xxxxxx

PAGE REV

7

1

3.01

Page 8

D

C

B

A

CR-8 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE8

8

105

VTT_OUT_RIGHT

678

IN

93

97

97

8

6

IN

7

93

105

9

DESIGN NOTE:

PRODUCT MAY

TIE GTLREFS

TOGETHER

6

IN

8

97

678

97

9

IN

VTT_OUT_RIGHT

IN

CPU_GTLREF1

678

IN

IN

DESIGN NOTE:

PRODUCT MAY

TIE GTLREFS

TOGETHER

1

2

1

2

VTT_OUT_LEFT

VTT_OUT_LEFT

1

R59PR

115

1%

CH

402

2

CPU_GTLREF0_DIVIDER

1

R65PR

200

1%

CH

402

2

R60PR

115

1%

CH

402

CPU_GTLREF1_DIVIDER

R56PR

200

1%

CH

402

1

0

402

1

2

1

2

1

R117PR

115

1%

CH

402

2

CPU_GTLREF3_DIVIDER

1

R118PR

200

1%

CH

402

2

R62PR

R114PR

115

1%

CH

402

CPU_GTLREF2_DIVIDER

R115PR

200

1%

CH

402

8

7

DESIGN NOTE:

GTLREF VOLTAGE SHOULD BE 0.67*VTT

(67% OF 1.2V) = 0.80V

<FOR THIS DESIGN>

100OHM OVER 200 OHM RESISTORS

R63PR

1

5%

10

CH

1

C9PR

1.0UF

20%

10V

2

Y5V

603

DESIGN NOTE:

GTLREF VOLTAGE SHOULD BE 0.67*VTT

(67% OF 1.2V) = 0.80V

<FOR THIS DESIGN>

100OHM OVER 200

1

C10PR

1.0UF

20%

10V

2

Y5V

603

2

CPU_GTLREF0

5%

EMPTY

DESIGN NOTE:

GTLREF VOLTAGE SHOULD BE 0.67*VTT

(67% OF 1.2V) = 0.80V

<FOR THIS DESIGN>

100OHM OVER 200 OHM RESISTORS

1

C14PR

1.0UF

20%

10V

2

Y5V

603

DESIGN NOTE:

GTLREF VOLTAGE SHOULD BE 0.67*VTT

(67% OF 1.2V) = 0.80V

<FOR THIS DESIGN>

100OHM OVER 200

402

OHM RESISTORS

R57PR

2

1

5%

10

CH

402

OUT

R116PR

1

10

402

OHM RESISTORS

R119PR

1

402

1

C16PR

1.0UF

20%

10V

2

Y5V

603

DESIGN NOTE:

KF CPU GTLREF: DEFAULT EMPTY

7

6

CPU GTLREF

CPU_GTLREF0

2

1

C8PR

220PF

50V

2

EMPTY

402

CPU_GTLREF1

1

C7PR

220PF

10%

50V

2

EMPTY

402

68

2

5%

CH

2

CPU_GTLREF3

5%10

CH

6

10%

CPU_GTLREF2

1

2

1

2

C15PR

220PF

10%

50V

EMPTY

402

C17PR

220PF

10%

50V

EMPTY

402

OUT

OUT

68

68

OUT

OUT

45

V_FSB_VTT

7

89141734

IN

38

85

R67PR

2

470

4025%CH

R69PR

2

470

402

105

7

8

6

93

97

678

97

1

R55PR

62

5%

CH

402

2

1

1

5%

CH

IN

IN

R68PR

2

470

4025%CH

VTT_OUT_RIGHT

VTT_OUT_LEFT

1

R52PR

100

5%

EMPTY

402

2

H_FSBSEL0

1

H_FSBSEL1

H_FSBSEL2

FSB SELECTS

R51PR

62

5%

CH

402

1

2

1

2

OUT

OUT

OUT

R75PR

680

5%

CH

402

CPU SIGNAL TERMINATION

3

71328

71328

71328

CAD NOTE:

PLACE AT CPU END OF

1

R76PR

330

5%

CH

402

2

ROUTE

1

2

R66PR

130

1%

EMPTY

402

2

MODULE REV DETAILS

MODULE NAME

CAD NOTE:

3438

85

17

V_FSB_VTT

7

89

IN

14

PLACE AT ICH END OF

ROUTE

1

1

R71PR

R72PR

62

62

5%

5%

CH

CH

402

2

402

2

H_THERMTRIP_N

H_FERR_N

H_PROCHOT_N

VR_READY

VRD_VIDSEL

H_CPURST_N

H_PWRGD

H_BR_N<0>

1

REV

DATE

D

C

32

6

OUT

32

6

OUT

6

37

IN

OUT

OUT

73993

6

93

6

10 97

6

33

6

10

95

OUT

OUT

OUT

B

V_FSB_VTT

7

89

1

2

105

R54PR

51

5%

CH

402

14173438

9397

VTT_OUT_LEFT

1

R49PR

51

5%

CH

402

2

1

2

IN

678

IN

R53PR

51

5%

CH

402

VTT_OUT_RIGHT

1

R64PR

51

5%

CH

402

2

1

2

R50PR

51

5%

CH

402

1

2

R48PR

62

5%

CH

402

1

2

R70PR

51

5%

CH

402

85

6

7

6

IN

8

97

TESTHI PULLUPS

[PAGE_TITLE=CPU TERMINATION & MISC P/U P/D]

BPAGE DRAWING

frostburg_fabc.sch_1.8

Sun Mar 18 18:43:01 2007

5

4 2

3

CONFIDENTIAL

CUSTOM TEXT BPAGE

TESTHI PIN NAME MAPPING

TESTHI[0]

TESTHI[1]

TESTHI[5:2]

TESTHI[7:6]

1

TESTHI[10:8]

R35PR

TESTHI[11]

51

5%

TESTHI[12]

CH

TESTHI[13]

402

2

H_TESTHI_0

H_TESTHI_2_7

H_IERR_N

H_TESTHI_1

H_TESTHI_10

H_TESTHI_11

H_TESTHI_M

H_TESTHI_13

INTEL

BYPASSEN

ODT

MCLK[3:0]

MCLKIO[1:0]

BR#[3:1]

DPSLP#

DT_SVR#

SLP#

DESIGN NOTE:

CHANGE TO H_TESTHI_2-7

6

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

FOR CRB

6

6

6

6

6

6

66

DOCUMENT_NUMBER

xxxxxx

PAGE REV

8

1

A

3.01

Page 9

CR-9 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE9

8

D

C

105

9092

101

848586

596469

39

47

48

333436

V_3P3_STBY\G

92122

IN

28

32

3738

4953

70

82

87

88

102103

B

SIO_PIN_108

69

IN

DESIGN NOTE:

PULL UP FOR PIN 106 IS AVAILABLE ON SIO PAGE

1

2

7

VCCPLL SUPPLY

V_SFR_OUT

87

IN

V_1P5_ICH

3438

829298

IN

R146PR

10K

5%

EMPTY

402

R137PR

SIO_PIN_108_R SIO_PIN_106_R

1

2

5%

1K

EMPTY

402

MBT3904DUAL

Q4PR

5

R90PR

1

0

603

DESIGN NOTE:

DO NOT STUFF

BOTH R90PR, R87PR

DESIGN NOTE:

COST REDUCTION EXP

R87PR

1

0

603

VCC3

R139PR

1

1K

1

5%

EMPTY

2

402

2

3

4

1A

CH

1A

EMPTY

R140PR

1K

5%

EMPTY

402

6

EMPTY

1

2

H_VCCPLL

2

GTLREF_FET0

GTLREF_FET1

2

R138PR

1

1K

402

6

OUT

OUT

EMPTY

OUT

5%

45

3

PLL SUPPLY FILTER

V_FSB_VTT

7

85

6

16

7

IN

8914173438

IN

DESIGN NOTE:

L3PR: DUAL CORE SUPPORT

47

CAD NOTE:

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

69

TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12 MIL

85

105

921222832 33

IN

34 36 37 38 39

64 697082 84 85

92

SIO_PIN_106

868788 90

484953 59

101

102 103

V_3P3_STBY\G

R145PR

1

10K

5%

EMPTY

2

402

9

9

2

8914173438

V_FSB_VTT

10UH

1

L3PR

EMPTY

721891-026

2

IN

1

2

1

2

693286-014

FB1PR

EMPTY

693286-014

FB2PR

EMPTY

10UH

1

L1PR

EMPTY

721891-026

2

DESIGN NOTE:

INDUCTOR: 125 MA

0805 PACKAGE

DESIGN NOTE:

COST REDUX EXPERIMENT

EMPTY ONE INDUCTOR

TO EVALUATE

10UH

1

L2PR

EMPTY

721891-026

2

DESIGN NOTE:

INDUCTOR: 125 MA

0805 PACKAGE

1

C13PR

2

1

2

33UF

20%

25V

EMPTY

RDL

R86PR

0

5%

EMPTY

402

1

C11PR

1.0UF

20%

10V

2

EMPTY

603

1

C12PR

1.0UF

20%

10V

2

EMPTY

603

2

H_VSSA

MODULE REV DETAILS

MODULE NAME

H_VCCIOPLL

H_VCCA

OUT

OUT

6

OUT

6

1

REV

DATE

D

6

C

B

3

CPU_GTLREF0_DIVIDER_R CPU_GTLREF1_DIVIDER_R

Q3PR

D

BSS138N

GTLREF_FET0

9

A

1

EMPTY

S

G

2

GTLREF_FET0_Q

R143PR

1

1.3K

1%

2

EMPTY

402

8

R142PR

2

1

CPU_GTLREF0_DIVIDER

0

5%

EMPTY

402

CAD NOTE:

PLACE CLOSE TO THE GTLREF DIVIDER

7

8 8

GTLREF_FET1

9

ININ

6

3

Q2PR

D

BSS138N

1

EMPTY

S

G

2

GTLREF_FET1_Q

R144PR

1

576

1%

EMPTY

2

402

5

R141PR

1

2

CPU_GTLREF1_DIVIDER

5%

0

EMPTY

402

CAD NOTE:

PLACE CLOSE TO THE GTLREF DIVIDER

BPAGE DRAWING

frostburg_fabc.sch_1.9

Sun Mar 18 18:43:02 2007

4 2

OUTOUT

[PAGE_TITLE=CPU PLL FILTERED SUPPLY]

CONFIDENTIAL

3

CUSTOM TEXT BPAGE

INTEL

DOCUMENT_NUMBER

xxxxxx

PAGE REV

9

1

A

3.01

Page 10

CR-10 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE10

8

EXP_A_RX_0_DP EXP_A_TX_0_DP

21

22 23

IN

EXP_A_RX_0_DN

21

22

IN

EXP_A_RX_1_DP

21

22

D

C

IN

EXP_A_RX_1_DN

21

22

IN

EXP_A_RX_2_DP

21

22

IN

EXP_A_RX_2_DN

21

22

IN

EXP_A_RX_3_DP

21

22

IN

EXP_A_RX_3_DN

21

22

IN

EXP_A_RX_4_DP

21

22

IN

EXP_A_RX_4_DN

21

22

IN

EXP_A_RX_5_DP

21

22

IN

EXP_A_RX_5_DN

21

22

IN

EXP_A_RX_6_DP

21

22

IN

EXP_A_RX_6_DN

21

22

IN

EXP_A_RX_7_DP

21

22

IN

EXP_A_RX_7_DN

21

22

IN

EXP_A_RX_8_DP

21

22

IN

EXP_A_RX_8_DN

21

22

IN

EXP_A_RX_9_DP

21

22

IN

EXP_A_RX_9_DN

21

22

IN

EXP_A_RX_10_DP

21

22

IN

EXP_A_RX_10_DN

21

22

IN

EXP_A_RX_11_DP

21

22

IN

EXP_A_RX_11_DN

21

22

IN

EXP_A_RX_12_DP

21

22

IN

EXP_A_RX_12_DN

21

22

IN

EXP_A_RX_13_DP

21

22

IN

EXP_A_RX_13_DN

21

22

IN

EXP_A_RX_14_DP

21

22

IN

EXP_A_RX_14_DN

21

22

IN

EXP_A_RX_15_DP

21

22

IN

EXP_A_RX_15_DN

21

22

IN

29

29

DMI_IT_MR_0_DP

BI

DMI_IT_MR_0_DN

BI

DMI_IT_MR_1_DP

BI

DMI_IT_MR_1_DN

BI

DMI_IT_MR_2_DP

BI

DMI_IT_MR_2_DN

BI

DMI_IT_MR_3_DP

BI

DMI_IT_MR_3_DN

BI

CK_PE_100M_MCH_DP

IN

CK_PE_100M_MCH_DN

IN

SDVO_CTRL_DATA

BI

SDVO_CTRL_CLK

BI

31

31

31

31

31

31

31

31

21

22

21

22

B

SIGNAL NAMING CONVENTION

EXP: PCI EXPRESS

DMI: DIRECT MEDIA INTERFACE

ITP: ICH TRANSMIT POSITIVE

ITN: ICH TRANSMIT NEGATIVE

IRP: ICH RECEIVE POSITIVE

IRN: ICH RECEIVE NEGATIVE

MTP: MCH TRANSMIT POSITIVE

MTN: MCH TRANSMIT NEGATIVE

MRP: MCH RECEIVE POSITIVE

A

MRN: MCH RECEIVE NEGATIVE

8

7

F13

E13

K15

J15

F12

E12

J12

H12

J11

H11

F7

E7

E5

F6

C2

D2

G6

G5

L9

L8

M8

M9

M4

L4

M5

M6

R9

R10

T4

R4

R6

R7

W2

V1

Y8

Y9

AA7

AA6

AB3

AA4

B12

B13

G17

E17

J3UB

1

NC NC

HDR

C85376-001

7

6

U1UB

BRLK_B

REV=1

PEG_RXP_0

PEG_RXN_0

PEG_RXP_1

PEG_RXN_1

PEG_RXP_2

PEG_RXN_2

PEG_RXP_3

PEG_RXN_3

PEG_RXP_4

PEG_RXN_4

PEG_RXP_5

PEG_RXN_5

PEG_RXP_6

PEG_RXN_6

PEG_RXP_7

PEG_RXN_7

PEG_RXP_8

PEG_RXN_8

PEG_RXP_9

PEG_RXN_9

PEG_RXP_10

PEG_RXN_10

PEG_RXP_11

PEG_RXN_11

PEG_RXP_12

PEG_RXN_12

PEG_RXP_13

PEG_RXN_13

PEG_RXP_14

PEG_RXN_14

PEG_RXP_15

PEG_RXN_15

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

DMI_RXN_3

EXP_CLKINP

EXP_CLKINN

SDVO_CTRLDATA

SDVO_CTRLCLK

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PCIE

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI

DMI_TXP_3

DMI_TXN_3

EXP_COMPO

EXP_COMPI

2OF8

SDVO CTRL DATA

1 SDVO CARD PRESENT, PEG DISABLED

0 SDVO DISABLED (DEFAULT)

1

J2UB

1

HDR

J9UB

NC

1

HDR

J7UB

NC

HDR

6

D11

D12

EXP_A_TX_0_DN

B11

EXP_A_TX_1_DP

A10

EXP_A_TX_1_DN

C10

EXP_A_TX_2_DP

D9

EXP_A_TX_2_DN

B9

EXP_A_TX_3_DP

B7

EXP_A_TX_3_DN

EXP_A_TX_4_DP

D7

D6

EXP_A_TX_4_DN

EXP_A_TX_5_DP

B5

B6

EXP_A_TX_5_DN

EXP_A_TX_6_DP

B3

B4

EXP_A_TX_6_DN

F2

EXP_A_TX_7_DP

E2

EXP_A_TX_7_DN

EXP_A_TX_8_DP

F4

G4

EXP_A_TX_8_DN

EXP_A_TX_9_DP

J4

K3

EXP_A_TX_9_DN

L2

EXP_A_TX_10_DP

EXP_A_TX_10_DN

K1

N2

EXP_A_TX_11_DP

EXP_A_TX_11_DN

M2

EXP_A_TX_12_DP

P3

EXP_A_TX_12_DN

N4

EXP_A_TX_13_DP

R2

EXP_A_TX_13_DN

P1

EXP_A_TX_14_DP

U2

T2

EXP_A_TX_14_DN

EXP_A_TX_15_DP

V3

EXP_A_TX_15_DN

U4

V7

DMI_MT_IR_0_DP

V6

DMI_MT_IR_0_DN

W4

DMI_MT_IR_1_DP

Y4

DMI_MT_IR_1_DN

AC8

DMI_MT_IR_2_DP

AC9

DMI_MT_IR_2_DN

Y2

DMI_MT_IR_3_DP

AA2

DMI_MT_IR_3_DN

AC11

GRCOMP

AC12

CAD NOTE:

MCH COMP0/1 SIGNALS:

TIE TOGETHER AT PINS.

IC

HS1UB

BRDWTR_ATX_HS

1

NC_3

NC_1

2

NC_4

NC_2

8

NC_8

NC_5

7

NC_7

NC_6

5

3

4

5

6

HEATSINK

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

45

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

31

BI

31

BI

31

BI

31

BI

31

BI

31

BI

31

BI

31

BI

17

IN

H_A_N<35..3>

6

BI

H_REQ_N<4..0>

6

BI

H_ADSTB0_N

6

BI

H_ADSTB1_N

6

BI

H_STBP_N<0>

7

BI

H_STBN_N<0>

7

BI

H_DBI_N<0>

7

BI

H_STBP_N<1>

7

BI

H_STBN_N<1>

7

BI

H_DBI_N<1>

7

BI

H_STBP_N<2>

7

BI

H_STBN_N<2>

7

BI

H_DBI_N<2>

7

BI

H_STBP_N<3>

7

BI

H_STBN_N<3>

7

BI

H_DBI_N<3>

7

BI

H_ADS_N

6

BI

H_TRDY_N

6

OUT

H_DRDY_N

6

OUT

H_DEFER_N

6

OUT

H_HITM_N

6

OUT

H_HIT_N

6

OUT

H_LOCK_N

6

IN

H_BR_N<0>

68

OUT

H_BNR_N

6

BI

H_BPRI_N

6

OUT

H_DBSY_N

6

BI

H_RS_N<2..0>

6

BI

H_CPURST_N

68

97

OUT

3

U1UB

BRLK_B

3

J42

FSB_AB_3

L39

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

0

1

2

3

4

0

1

2

AA37

AA42

AA41

J40

L37

L36

K42

N32

N34

M38

N37

M36

R34

N35

N38

U37

N39

R37

P42

R39

V36

R38

U36

U33

R35

V33

V35

Y34

V42

V38

Y36

Y38

Y39

F40

L35

L38

G43

J37

M34

U34

M42

M43

M40

G35

H33

J33

G27

H27

G29

B38

C38

E33

W40

Y40

W41

T43

Y43

U42

V41

W42

G39

U40

U41

U39

C31

FSB_AB_4

FSB_AB_5

FSB_AB_6

FSB_AB_7

FSB_AB_8

FSB_AB_9

FSB_AB_10

FSB_AB_11

FSB_AB_12

FSB_AB_13

FSB_AB_14

FSB_AB_15

FSB_AB_16

FSB_AB_17

FSB_AB_18

FSB_AB_19

FSB_AB_20

FSB_AB_21

FSB_AB_22

FSB_AB_23

FSB_AB_24

FSB_AB_25

FSB_AB_26

FSB_AB_27

FSB_AB_28

FSB_AB_29

FSB_AB_30

FSB_AB_31

FSB_AB_32

FSB_AB_33

FSB_AB_34

FSB_AB_35

FSB_REQB_0

FSB_REQB_1

FSB_REQB_2

FSB_REQB_3

FSB_REQB_4

FSB_ADSTBB_0

FSB_ADSTBB_1

FSB_DSTBPB_0

FSB_DSTBNB_0

FSB_DINVB_0

FSB_DSTBPB_1

FSB_DSTBNB_1

FSB_DINVB_1

FSB_DSTBPB_2

FSB_DSTBNB_2

FSB_DINVB_2

FSB_DSTBPB_3

FSB_DSTBNB_3

FSB_DINVB_3

FSB_ADSB

FSB_TRDYB

FSB_DRDYB

FSB_DEFERB

FSB_HITMB

FSB_HITB

FSB_LOCKB

FSB_BREQ0B

FSB_BNRB

FSB_BPRIB

FSB_DBSYB

FSB_RSB_0

FSB_RSB_1

FSB_RSB_2

FSB_CPURSTB

REV=1

1OF8

BPAGE DRAWING

frostburg_fabc.sch_1.10

Sun Mar 18 18:43:03 2007

4 2

3

[PAGE_TITLE=MCH SECTIONS PAGE 1 OF 6]

2

MODULE REV DETAILS

MODULE NAME

H_D_N<63..0>

0

INTEL

R40

P41

R41

N40

R42

M39

N41

N42

L41

J39

L42

J41

K41

G40

F41

F42

C42

D41

F38

G37

E42

E39

E37

C39

B39

G33

A37

F33

E35

K32

H32

B34

J31

F32

M31

E31

K31

G31

K29

F31

J29

F29

L27

K27

H26

L26

J26

M26

C33

D35

E41

B41

D42

C40

C35

B40

D38

D37

B33

D33

C34

B35

A32

D32

B25

D23

C25

D25

D24

B24

R32

U32

IC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

HXSWING

HXRCOMP

HXSCOMP

HXSCOMPB

MCH_GTLREF

CK_H_MCH_DP

CK_H_MCH_DN

DOCUMENT_NUMBER

xxxxxx

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_SCOMP

FSB_SCOMPB

FSB_DVREF

FSB_ACCVREF

HPL_CLKINP

HPL_CLKINN

DESIGN NOTE:

MCH GTLREF0/1: SEPARATE SIGNALS ON EV ONLY;

TIE TOGETHER AT PINS ON CRB.

CONFIDENTIAL

CUSTOM TEXT BPAGE

REV

1

BI

17

IN

17

IN

17

IN

17

IN

17

IN

29

IN

29

IN

PAGE REV

10

1

DATE

7

D

C

B

A

3.01

Page 11

CR-11 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE11

8

7

6

45

3

2

MODULE REV DETAILS

MODULE NAME

1

REV

DATE

D

M_DQS_A_DP<7..0>

M_DQS_A_DN<7..0>

M_DQM_A<7..0>

M_DATA_A<63..0>

111

101112

13

8

AV4

DDR_A_DQ_8

DDR_A_WEB

BA33

9

AV3

DDR_A_DQ_9

DDR_A_CASB

AW35

BA4

DDR_A_DQ_10

DDR_A_RASB

AY33

BB3

DDR_A_DQ_11

AU1

AU2

DDR_A_DQ_12

DDR_A_BS_0

BA31

AY31

1

0

DDR_A_DQ_13

DDR_A_BS_1

14

AY2

DDR_A_DQ_14

DDR_A_BS_2

AY20

2

AN3

DDR_A_DQ_1

DDR_A_MA_5

BB22

AR2

DDR_A_DQ_2

DDR_A_MA_6

BA22

AR3

AL3

DDR_A_DQ_3

DDR_A_MA_7

BB21

AW21

7

8

DDR_A_DQ_4

DDR_A_MA_8

AM2

AR5

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_MA_10

DDR_A_MA_9

BA21

BB31

101113

9

7

AR4

DDR_A_DQ_7

DDR_A_MA_11

BC20

AY21

DDR_A_MA_12

12

AW2

AY38

DDR_A_DQS_1

DDR_A_MA_13

AW1

DDR_A_DQSB_1

DDR_A_MA_14

BA19

14

AW3

DDR_A_DM_1

000

0123456

C

AM1

AP2

AP3

AN2

DDR_A_DQ_0

DDR_A_DM_0

DDR_A_DQS_0

DDR_A_DQSB_0

BRLK_B

U1UB

REV=1

B

DDR_A_MA_4

DDR_A_MA_3

DDR_A_MA_2

DDR_A_MA_1

DDR_A_MA_0

BA23

BB23

AY23

AY25

BB30

1

05923456

A

15

2

AY3

AY7

DDR_A_DQ_15

BA34

01230

161718

2

2

BA6

BB6

BB5

AY6

BA9

DDR_A_DM_2

DDR_A_DQ_18

DDR_A_DQ_17

DDR_A_DQ_16

DDR_A_DQS_2

DDR_A_DQSB_2

DDR_A_CKE_1

DDR_A_CKE_0

DDR_A_CSB_3

DDR_A_CSB_2

DDR_A_CSB_1

DDR_A_CSB_0

AY35

BB33

BB38

AY19

AW18

1

19

BB9

DDR_A_DQ_19

DDR_A_CKE_2

BB19

2

202122

BA5

BB4

DDR_A_DQ_21

DDR_A_DQ_20

DDR_A_CKE_3

BA18

3

BC7

DDR_A_DQ_22

DDR_A_ODT_0

BB35

0

23

AY9

DDR_A_DQ_23

DDR_A_ODT_1

BA38

1

333

2425262728

AT20

AU18

AN18

AT18

DDR_A_DM_3

DDR_A_DQ_24

DDR_A_DQS_3

DDR_A_DQSB_3

DDR_A_ODT_3

DDR_A_ODT_2

BA35

BA39

3

2

AR18

AU21

DDR_A_DQ_26

DDR_A_DQ_25

DDR_A_CKB_0

DDR_A_CK_0

AU31

AR31

AP17

AT21

DDR_A_DQ_27

DDR_A_CK_1

AP27

AN27

DDR_A_DQ_28

DDR_A_CKB_1

29

AN17

DDR_A_DQ_29

DDR_A_CK_2

AV33

30

AP20

DDR_A_DQ_30

DDR_A_CKB_2

AW33

31

AV20

AP29

DDR_A_DQ_31

DDR_A_CK_3

444

AR41

DDR_A_DQS_4

DDR_A_CKB_3

DDR_A_CK_4

AM26

AP31

32333435363738

AR40

AU43

AV42

DDR_A_DM_4

DDR_A_DQSB_4

DDR_A_CK_5

DDR_A_CKB_5

DDR_A_CKB_4

AM27

AU33

AT33

AU40

AP42

AN39

AV40

AV41

DDR_A_DQ_37

DDR_A_DQ_36

DDR_A_DQ_35

DDR_A_DQ_34

DDR_A_DQ_33

DDR_A_DQ_32

CK_M_DDR0_A_DP

CK_M_DDR0_A_DN

CK_M_DDR1_A_DP

CK_M_DDR1_A_DN

CK_M_DDR2_A_DP

CK_M_DDR2_A_DN

CK_M_DDR3_A_DP

CK_M_DDR3_A_DN

CK_M_DDR4_A_DP

CK_M_DDR4_A_DN

CK_M_DDR5_A_DP

CK_M_DDR5_A_DN

AR42

DDR_A_DQ_38

39

AP41

DDR_A_DQ_39

555

AL40

AL41

DDR_A_DQS_5

DDR_A_DQSB_5

40414243444546

AM43

AM39

AN41

DDR_A_DM_5

DDR_A_DQ_41

DDR_A_DQ_40

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

AK42

DDR_A_DQ_42

AN40

AK41

DDR_A_DQ_44

DDR_A_DQ_43

24

24

24

24

24

24

24

24

24

24

24

24

AN42

DDR_A_DQ_45

AL42

DDR_A_DQ_46

47

AL39

DDR_A_DQ_47

666

AG42

AG41

DDR_A_DQS_6

DDR_A_DQSB_6

AG40

DDR_A_DM_6

48495051525354755

AJ40

AH43

AF39

AE40

AJ42

AJ41

AF41

DDR_A_DQ_54

DDR_A_DQ_53

DDR_A_DQ_52

DDR_A_DQ_51

DDR_A_DQ_50

DDR_A_DQ_49

DDR_A_DQ_48

DDR_A

AF42

DDR_A_DQ_55

7

AC42

AC41

DDR_A_DQS_7

DDR_A_DQSB_7

RSVD

AN21

7

AC40

DDR_A_DM_7

565758

AD40

AD43

DDR_A_DQ_57

DDR_A_DQ_56

AB41

DDR_A_DQ_58

AA40

DDR_A_DQ_59

60

AE42

DDR_A_DQ_60

61

AC39

AE41

DDR_A_DQ_61

62

DDR_A_DQ_62

63

AB42

DDR_A_DQ_63

3OF8

IC

OUT

OUT

OUT

BI

24

24

24

24

D

C

B

A

M_ODT_A<3..0>

M_SCKE_A<3..0>

M_SCS_A_N<3..0>

M_SBS_A<2..0>

M_RAS_A_N

M_CAS_A_N

M_WE_A_N

M_MAA_A<14..0>

8

7

6

5

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

24 26

24 26

24 26

24 26

24 26

24 26

24 26

4 2

BPAGE DRAWING

frostburg_fabc.sch_1.11

Sun Mar 18 18:43:04 2007

3

[PAGE_TITLE=MCH SECTIONS PAGE 2 OF 6]

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

xxxxxx

PAGE REV

11

1

3.01

TP_A_RCVEN_N

Page 12

CR-12 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE12

8

7

6

45

3

2

MODULE REV DETAILS

MODULE NAME

1

REV

DATE

D

M_DQS_B_DP<7..0>

M_DQS_B_DN<7..0>

M_DQM_B<7..0>

M_DATA_B<63..0>

31

2524262728

AV24

AT23

30

29

AT26

AP26

AU23

AW23

AR24

AN26

10111213146115

111

AN8

7

AW7

AU7

AW5

AN5

AN6

AN9

9

8

AT11

AU11

AR12

AP12

AR11

AW9

AP13

AR13

AU9

AV12

AU12

059000123456

C

AR7

AN7

AV6

AU5

18

17

16

222

AP15

AR15

AW13

AU15

AV13

AU17

333

19

20

222123

AT17

AU13

AM13

AV15

AW17

AT24

AU26

AP23

444

AW39

AU39

AU37

AW37

33323435363738539

AV38

AN36

AN37

AU35

AR35

AN35

7

7

41

5

5

4042434446

AR37

AL35

AL34

AM37

AM35

AM38

AJ34

AL38

AR39

45647

AM34

AL37

AL32

6

AG35

AG36

6

48495051525354

AG39

AG38

AJ38

AF35

AF33

AJ37

7

55

56

58

60

62

63

AJ35

AG33

AF34

AC36

AC37

AD38

AD36

AC33

AA34

AA36

AD34

AF38

AC34

AA33

OUT

OUT

OUT

BI

25

25

25

25

D

C

IC

DDR_B_DQ_0

DDR_B_DM_0

DDR_B_DQ_1

DDR_B_DQ_4

DDR_B_DQ_3

DDR_B_DQ_2

DDR_B_DQS_0

U1UB

B

DDR_B_DQSB_0

BRLK_B

REV=1

DDR_B_MA_8

DDR_B_MA_7

DDR_B_MA_6

DDR_B_MA_5

DDR_B_MA_4

DDR_B_MA_3

DDR_B_MA_2

DDR_B_MA_1

DDR_B_MA_0

AW15

BB15

BA15

AY15

BA14

BB14

AW12

BA13

BB13

01234575

679

8

DDR_B_DM_1

DDR_B_DQ_7

DDR_B_DQ_6

DDR_B_DQ_5

DDR_B_DQ_9

DDR_B_DQ_8

DDR_B_DQS_1

DDR_B_DQSB_1

DDR_B_DQ_10

DDR_B_DQ_11

DDR_B_DQ_12

DDR_B_DQ_13

DDR_B_DQ_14

DDR_B_DQ_15

DDR_B_DM_2

DDR_B_DQ_20

DDR_B_DQ_19

DDR_B_DQ_18

DDR_B_DQ_17

DDR_B_DQ_16

DDR_B_DQS_2

DDR_B_DQSB_2

DDR_B_DQ_21

DDR_B_DQ_22

DDR_B_DQ_23

DDR_B_DM_3

DDR_B_DQ_28

DDR_B_DQ_27

DDR_B_DQ_26

DDR_B_DQ_25

DDR_B_DQ_24

DDR_B_DQS_3

DDR_B_DQSB_3

DDR_B_DQ_29

DDR_B_DQ_30

DDR_B_DQ_31

DDR_B_DM_4

DDR_B_DQ_36

DDR_B_DQ_35

DDR_B_DQ_34

DDR_B_DQ_33

DDR_B_DQ_32

DDR_B_DQS_4

DDR_B_DQSB_4

DDR_B_DQ_37

DDR_B_DQ_38

DDR_B_DQ_39

DDR_B_DM_5

DDR_B_DQ_44

DDR_B_DQ_43

DDR_B_DQ_42

DDR_B_DQ_41

DDR_B_DQ_40

DDR_B_DQS_5

DDR_B_DQSB_5

DDR_B_DQ_45

DDR_B_DQ_46

DDR_B_DQ_47

DDR_B_DM_6

DDR_B_DQ_52

DDR_B_DQ_51

DDR_B_DQ_50

DDR_B_DQ_49

DDR_B_DQ_48

DDR_B_DQS_6

DDR_B_DQSB_6

DDR_B_DQ_53

DDR_B_DQ_54

DDR_B_DQ_55

DDR_B_DM_7

DDR_B_DQ_56

DDR_B_DQS_7

DDR_B_DQSB_7

DDR_B_DQ_57

DDR_B_DQ_58

DDR_B_DQ_59

DDR_B_DQ_60

DDR_B_DQ_61

DDR_B_DQ_62

DDR_B_DQ_63

4OF8

B

RSVD

RSVD

AA39

AP21

DDR_B

RSVD

AM21

DDR_RCOMPVOH

DDR_RCOMPVOL

DDR_RCOMPYPU

DDR_RCOMPYPD

DDR_RCOMPXPU

DDR_RCOMPXPD

DDR_VREF

AM6

AM8

AL4

AL2

BB40

BA40

AM10

RSVD

RSVD

RSVD

RSVD

RSVD

DDR_B_MA_9

AY13

BA17

AY12

AY27

BB25

AW26

AY24

BB17

BA11

BB11

14

10

13

12

11

AY17

012

AY11

DDR_B_CSB_1

DDR_B_CSB_0

BA25

BA29

1

0

DDR_B_CSB_3

BA26

BA30

AW11

23012

BC12

DDR_B_ODT_3

DDR_B_CKE_2

BA10

BB10

BB27

AW29

BA27

AY29

3

1

032

AW31

AV31

AT27

AV32

AU27

DDR_B_CKB_5

AT32

AR29

AU29

AV29

AP32

AN33

AW27

DDR_B_CK_5

DDR_B_CKB_4

DDR_B_CK_4

DDR_B_CKB_3

DDR_B_CK_3

DDR_B_CKB_2

DDR_B_CK_2

DDR_B_CKB_1

DDR_B_CK_1

DDR_B_CKB_0

DDR_B_CK_0

DDR_B_ODT_2

DDR_B_ODT_1

DDR_B_ODT_0

DDR_B_CKE_3

DDR_B_CKE_1

DDR_B_CKE_0

DDR_B_CSB_2

DDR_B_BS_2

DDR_B_BS_1

DDR_B_BS_0

DDR_B_RASB

DDR_B_CASB

DDR_B_WEB

DDR_B_MA_14

DDR_B_MA_13

DDR_B_MA_12

DDR_B_MA_11

DDR_B_MA_10

RSVD

BA2

AW42

AN32

AG32

AM31

AF32

TP_DDR_OBSERV_1

TP_DDR_OBSERV_0

TP_DDR_ANALOG_1

TP_DDR_ANALOG_0

TP_DDR_RCOMPYPAD

CK_M_DDR0_B_DP

CK_M_DDR0_B_DN

CK_M_DDR1_B_DP

CK_M_DDR1_B_DN

A

M_ODT_B<3..0>

M_SCKE_B<3..0>

M_SCS_B_N<3..0>

M_SBS_B<2..0>

M_RAS_B_N

M_CAS_B_N

M_WE_B_N

M_MAA_B<14..0>

8

7

6

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

5

CK_M_DDR2_B_DP

CK_M_DDR2_B_DN

CK_M_DDR3_B_DP

CK_M_DDR3_B_DN

CK_M_DDR4_B_DP

CK_M_DDR4_B_DN

CK_M_DDR5_B_DP

CK_M_DDR5_B_DN

26

25

25

26

25

26

25

26

25

26

25

26

25

26

4 2

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

TP_DDR_RCOMPXPAD

25

25

25

25

25

25

25

25

25

25

25

25

TP_DDR_SLEWYDB

TP_DDR_SLEWXDB

MCH_VREF

19

IN

MCH_DDR_RCOMPXPD

19

IN

MCH_DDR_RCOMPXPU

19

IN

MCH_DDR_RCOMPYPD

19

IN

MCH_DDR_RCOMPYPU

19

IN

MCH_DDR_RCOMPVOL

19

IN

MCH_DDR_RCOMPVOH

19

IN

CAD NOTE:

BTX SPECIFIC: TESTPOINT ON DDR_RCOMPY_PAD (U1UB)

ATX SPECIFIC: DO NOT TESTPOINT (U1UB_PIN AW42)

BPAGE DRAWING

frostburg_fabc.sch_1.12

Sun Mar 18 18:43:05 2007

3

TP_B_RCVEN_N

[PAGE_TITLE=MCH SECTIONS PAGE 3 OF 6]

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

xxxxxx

PAGE REV

12

1

A

3.01

Page 13

CR-13 : @FROSTBURG_FABC_LIB.FROSTBURG_FABC(SCH_1):PAGE13

8

13

33

53

70

IN

PWRGD_3V

7

R10UB

1

2

5%

0

CH

402

D

DESIGN NOTE:

0 OHM ISOLATION RESISTOR (R10UB) ON PWRGD_3V TO PWRGD_3V_R

DESIGN NOTE: