5

4

3

2

1

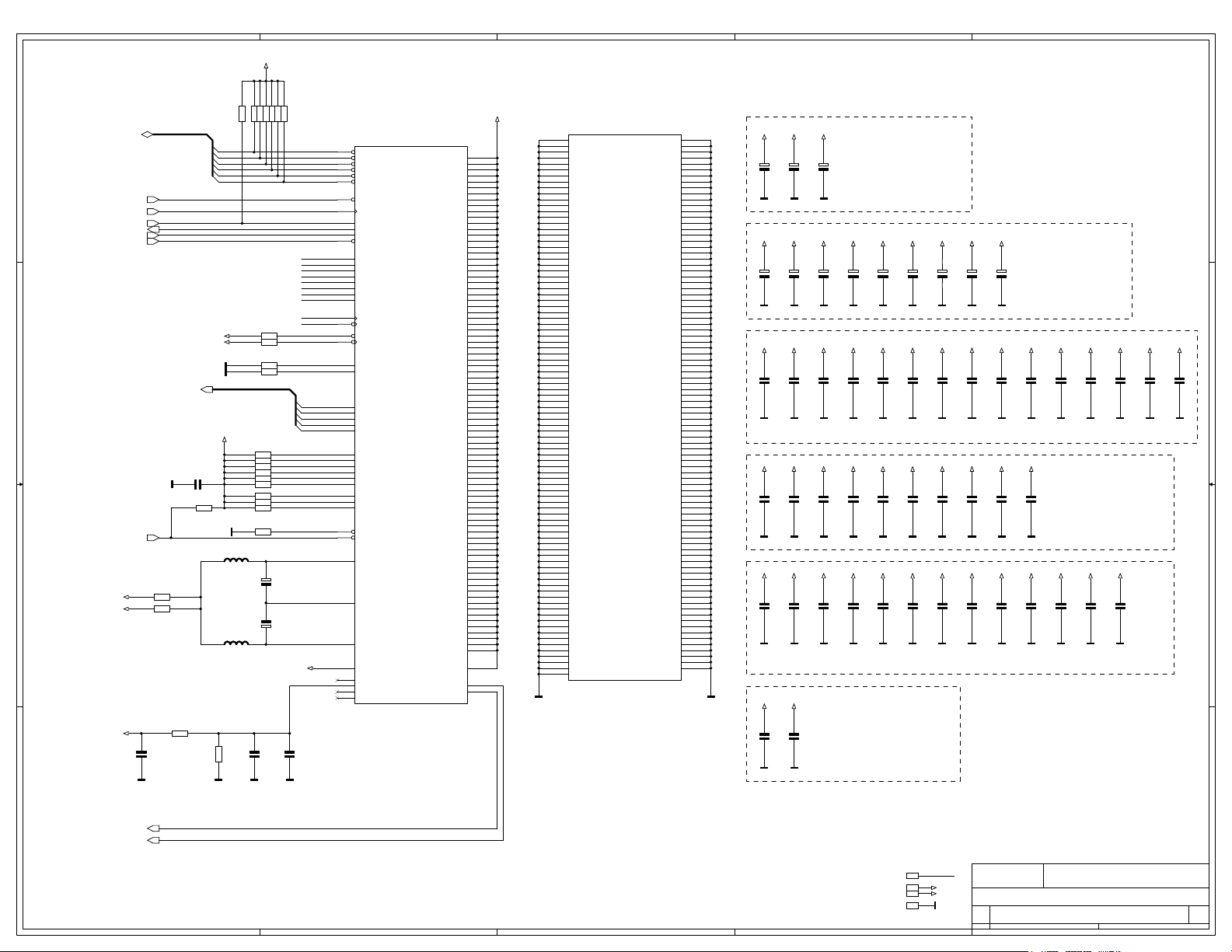

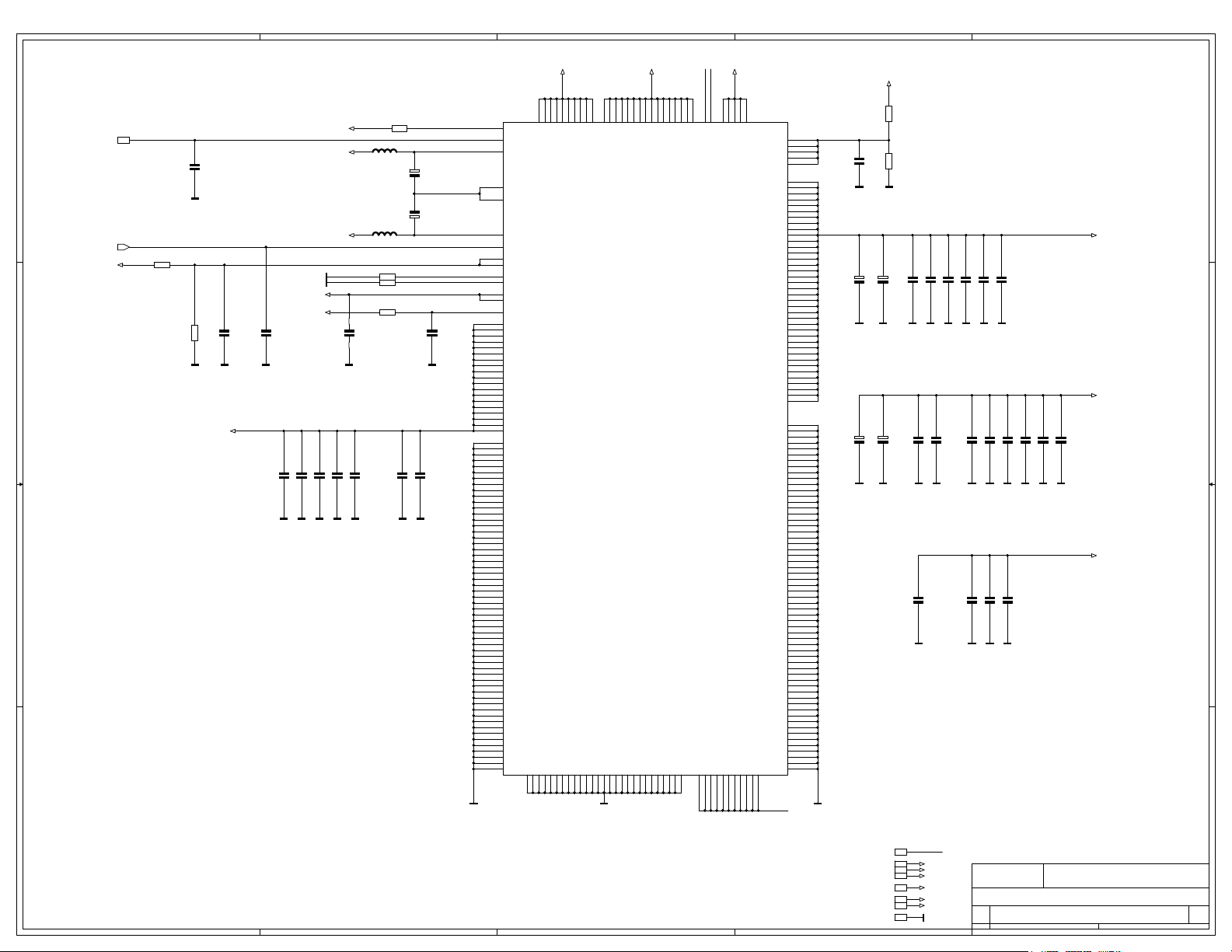

Intel (R) 845E Interactive

Client Reference Design

D D

Revision X2

Last Change : 2002-09-26

Schematic Page#

COVER SHEET1

2

BLOCK DIAGRAM

3

BLOCK-POWER

4

MECH-ROUTE

5

NOTES

6

CPU-P4 BUS

7

CPU-P4 POWER

8

CPU-ITP

910MCH-SYSBUS & CLOCK

MCH-AGP & DDR

C C

B B

MCH-POWER11

12

CLK-ICS950201

1314DDR-DIMM 0

DDR-DIMM 1

ICH4-SYSBUS & PCI

15

16

ICH4-LPC & IDE & USB

17

ICH4-POWER

18

GLUE LOGIC

SIO0-LPC47M107

19

20

SIO1-LPC47N227

21

CONN-COM1/COM2/LPT

22

CONN-COM3/COM4/KBC

23

AC97-AD1885

LAN-10/100/1000 BUS

24

25

LAN-10/100/1000 CONN

26

VGA-COUGAR-01

27

VGA-COUGAR-02

28

VGA-COUGAR-03

CONN-PCI

29

CONN-01 IDE-FLOPPY

30

USB0-USB1-LAN0

31

32 USB2-USB5

SYSTEM CONTROL

33

DDR-POWER

34

POWER

35

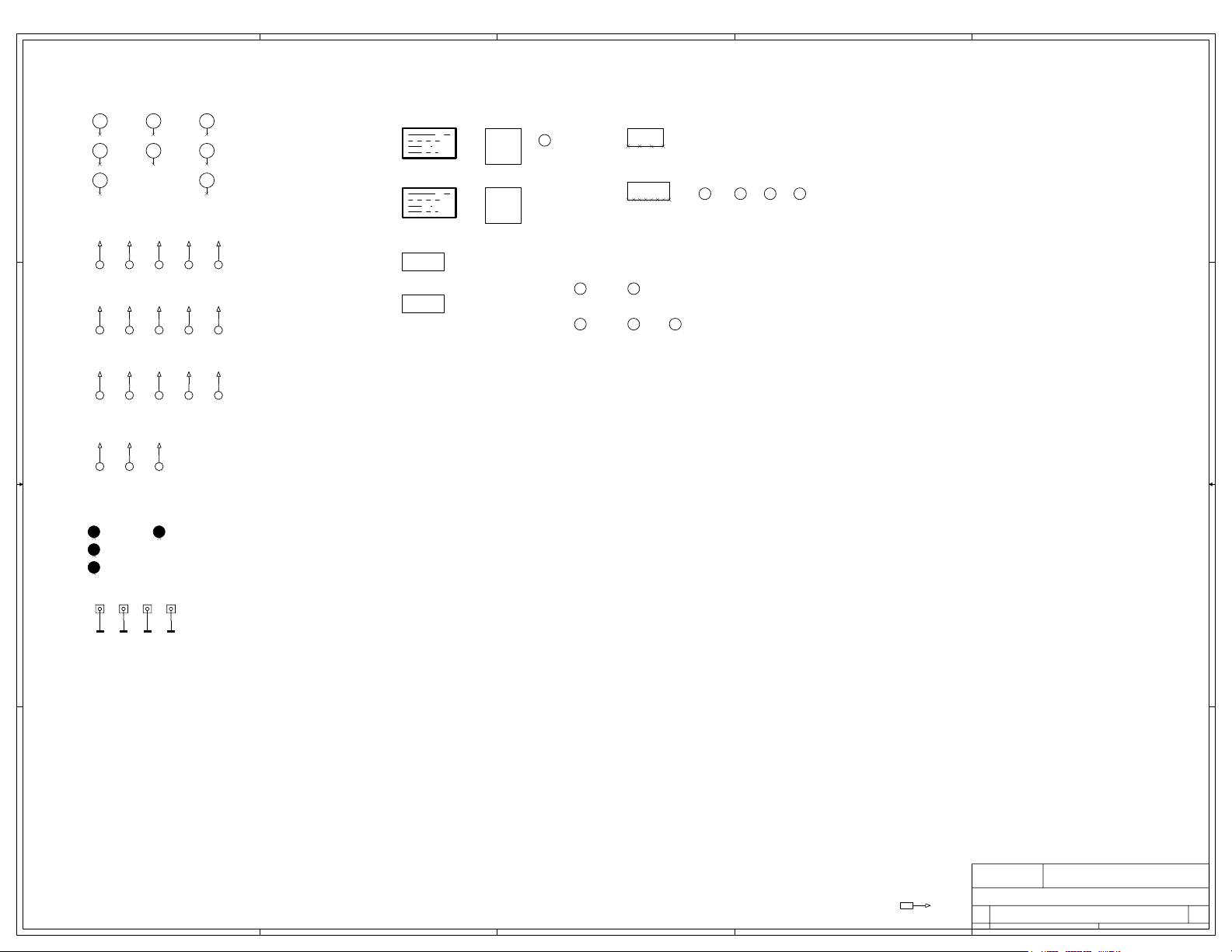

Prefix Netobject

A_ CRITICAL ANALOG TRACES

AC_ AC97 SIGNAL

APIC_ APIC SIGNAL

AUD_ ANALOG AUDIO SIGNAL

CLOCK SIGNALCK_

EEn_ SERIAL EEPROM LANn

EN_ ENABLE FOR POWER SOURCES

F_ FLOPPY DISK SIGNAL

FWH_ FIRMWARE HUB SIGNAL

G_ AGP BUS SIGNAL

GND_ GND SIGNAL DERIVED

GND GND POWER

H_ P4 HOSTBUS SIGNAL

I2C_ I2C BUS SIGNAL

IDE_ IDE SIGNAL

INT_ INTERRUPT SIGNAL

KB_ KEYBOARD SIGNAL

L_ LPC BUS SIGNAL

LANn_ LAN CONTROLLER n SIGNAL

LP_ LPT1284 SIGNAL

M_ MEMORY BUS SIGNAL

MIDI_ MIDI SIGNAL

MS_ MOUSE SIGNAL

P_ PCI BUS SIGNAL

SPn_ SERIAL PORT n SIGNAL

USB_ USB PORT SIGNAL

V_ POWER

ZV_ ZV VIDEO PORT SIGNAL

Changes from X1 to X2

12All BAT54A (0-0031-1261) changed to BAT54 (0-0031-1104) due to wrong polarity

R712 changed from 10k to 15k to adjust voltage

3 PU R756 and R757 added @ U38.15 (PG_VDDR) and U38.16 (PG_V1V5)

4 Net on pins U3.54 and U3.55 separated (BSEL[0..1]) due to naming error

PU R758 added at CN34.7 (SYS_RESET#)5

6

PU R759 added at U39.4 (VIDPWRGD)

7

C717 changed from 4u7 to 1u

8

R607 not populated

9

R571 and R572 not populated (FWH Test Pins)

10

R585 and R586 not populated (for LVDS 18 Bit)

11

R760 and C741 added to U7.50 to generate a V_3V3SB input delay for resume reset

12

R501 and R494 not populated due to PCI config of LAN 82540

13

U36 FWH symbol changed due to wrong pinout (Pin 23, 24 and 25)

14

R496 changed to 4k7 and set to GND (PD M66EN)

15

R525 and R499 is now populated

16

R530 not populated due to wrong V_2V5LAN voltage

17

U20.G4 is now 51R Pulldown to GND

18

U20.H4 is now 33R Pullup to V_3V3LAN

19

AC97 Fixup (AC_SDIN0 -> Changed to AC_SDIN2 on ICH4)

20

Swap ICH4 Pin N20 and P21 (H_HISTB+ / H_HISTB-) due to wrong info in yellow cover

21

LAN 82540 Fixup (R519 populated with 0R, R517 changed to 2K49 and R513 changed to 330R)

22

R615 changed to 4K32 due to Cougar Bug

23

HW Rev changed to 2 at Glue Logic

24

R373 is now populated with 10M

25

CN12.4 must be isolated cause of shortcut of AUD_MIC_BIAS to GND

26

PU R761-R765 added to VID[0:4]

27

PU R766 added to U23.15, PD R767 added to U23.14 (Panellink strapping options)

28

HD-LED-power connected to V_5V0 instead of V_5V0SB

29

PD R768 added to PS_ON

30

PU R769 added to U3.28 (PGOOD408#)

31

PD R770, R771, R772 added to power enables (default off, if CPLD not configured)

32

PD R773-R776 added to serial port shut down pins

33

Splitted SMI# and PME# signals of SIO0 and SIO1 on ICH4-GPIOs

34 Removed R383, R384, R385

35 Added D25 to avoid crossvoltages from VGA Monitor

36 Added D26 to avoid crossvoltages LPT Port

37 Alternative population of L7 to L12 with resistors (0R)

PME# Signal of Cougar (PinB7) is set to V_3V3 via 0R38

39 U29 (LP3965EMP) can be replaced by an 0R_1206 to power 3V3 on Cougar

40 Possibility to PullDown Pin D8(MD24) on Cougar to enable SDRAM

41 CN41 (JUMPER 3x1) added to connect to MPCI Pins (TIP and RING)

42 V_5V0 input at V_DDR supply is now controlled by XILINX CPLD (Pin 25)

43 Delay of PWRGOOD# (LAN 82540EM Pin A9) to enable correct EEPROM detection

THIS SCHEMATIC IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER,

INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR

PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF PROPOSAL, SPECIFICATION

OR SAMPLE.

A A

General Note:

All Parts marked 'XXX1' will not be assembled in V1.

All Parts marked 'XXX2' will not be assembled in V2.

5

4

No license, express or implied, by estoppel or otherwise, to any

intellectual property rights is granted herein. Intel disclaims all

liability, including liability for infringement of any proprietary rights,

relating to use of information in this specification. Intel does not

warrant or represent that such use will not infringe such rights.

THIS DRAWING CONTAINS INFORMATION WHICH HAS NOT BEEN VERIFIED FOR

MANUFACTURING AS AN END USER PRODUCT. INTEL IS NOT RESPONSIBLE OR THE

MISUSE OF THIS INFORMATION.

* Other names and brands may be claimed as the property of others.

3

2

Intel (R) 845E Interactive Client Reference Design

Title

COVER SHEET

Size Document Number Rev

C

Date Sheet of

B444B-W

135Friday, September 26, 2003

1

2.00

5

4

3

2

1

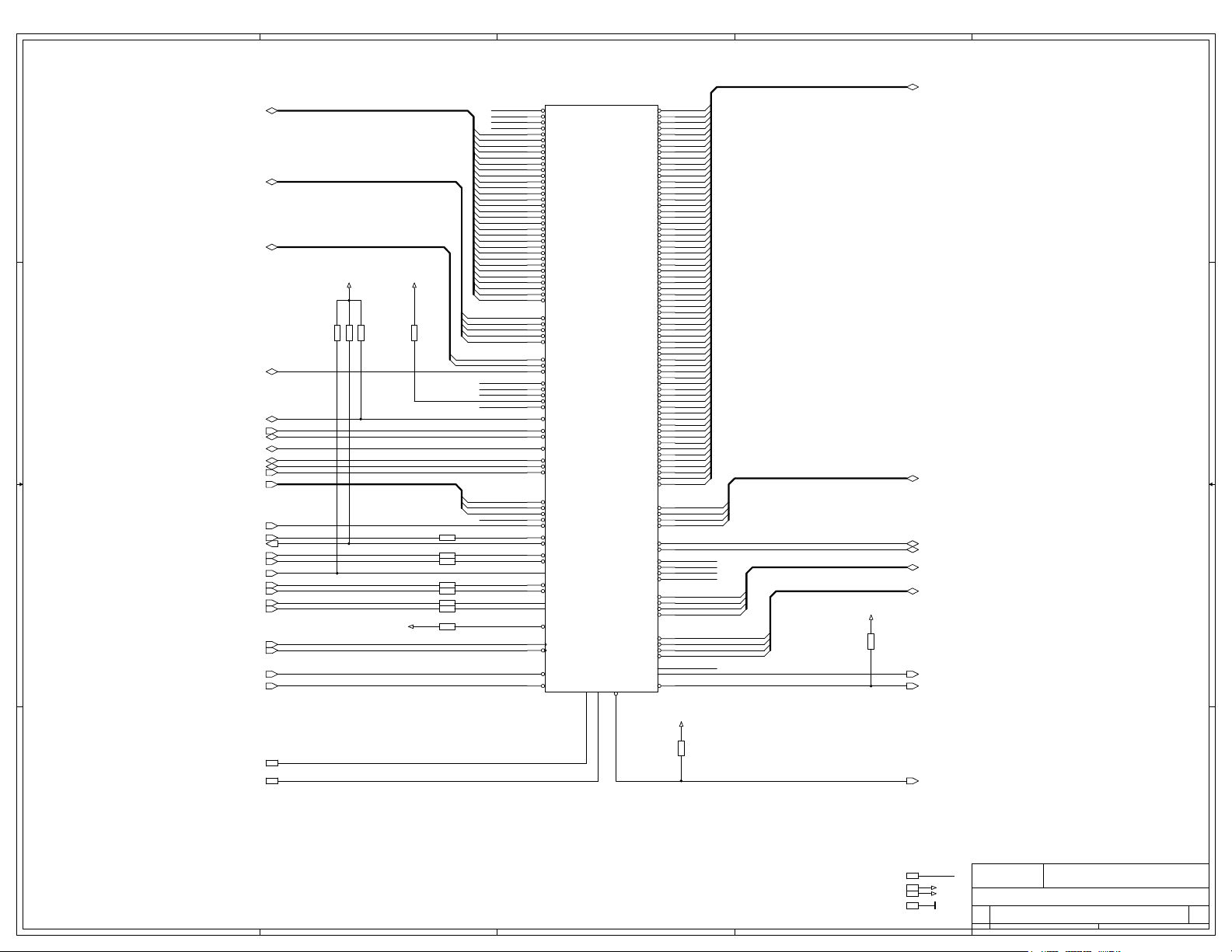

Block Diagram

D D

CPU VRM

Pg. 35

ITP

Pg. 8

CPU

Pentium(R) 4 Processor

FCPGA478

Pg. 6, 7

Clocking

ICS950201

CK 408

Pg. 12

Glue Logic

Xilinx *

Coolrunner

Pg. 18

- Postcode decoding

- Speedstep logic

- Powerup sequencing

1280x1024 @ 18Bit

LVDS

Pg. 27

DVI-I

Pg. 27

I/O panel

planar

DVI/VGA

Cougar 3DR *

BGA385

16 MB int. mem.

Pg. 26, 27, 28

AGP 1.5V, 66MHz x4, 32b (1.1 GB/s)

C C

TV-OUT

Pg. 27

I/O panel

PHY

i82562

845E MCH

i82845-E

BGA593

Pg. 9, 10, 11

RJ45

Pg. 31

I/O panel

PCI, 33MHz, 32b (132 MB/s)

B B

5V PCI-Slot

Pg. 29

miniPCI-Slot

Pg. 29

RJ45

Pg. 25

I/O panel

Pg. 31

LAN

i82540

(optional

i82551/i82559)

Pg. 24, 25

ATA66/100

ICH4

i82801

BGA421

Pg. 15, 16, 17

USB2.0

IDE0

Pg. 30

planar

IDE1

Pg. 30

A A

planar

USB

Pg. 31, 32

2 * I/O panel

2 * I/O panel, powered

2 * planar

FSB 133MHz x4, 64b (4.3 GB/s)

DDR SDRAM 2.5V, 266MHz, 64b (2.1 GB/s)

Hub Interface 66MHz x4, 8b (266 MB/s)

SMB

SYSMON

LM87

Pg. 33

FAN

PHOTO DIODE

AC'97

AC97

AD1885

Pg. 23

LINE-IN

LINE-OUT

HEADPHONE

MICRO

CD-ROM

LPC 3.3V, 33MHz

FWH

8 Mbit

i82802AC

PLCC32

Pg. 33

I/O panel

planar

I/O panel

I/O panel

planar

max. 2 GB

DDR-DIMM

Pg. 13

Pg. 14

Pg. 20

Pg. 22

SERIAL2

Pg. 22

SERIAL3

Pg. 20

FIR

SIO

LPC47N227

3 * planar

DDR VR

Pg. 34

Pg. 19

SERIAL0

SERIAL1

FDD

PARALLEL

K/B

MOUSE

SIO

LPC47M107

I/O panel

I/O panel

planar

I/O panel

planar

planar

Pg. 21

Pg. 21

Pg. 30

Pg. 21

Pg. 22

Pg. 22

Intel (R) 845E Interactive Client Reference Design

Title

BLOCK-DIAGRAM

Size Document Number Rev

C

5

4

3

2

Date Sheet of

B444B-W

235Friday, September 26, 2003

1

2.00

5

4

3

2

1

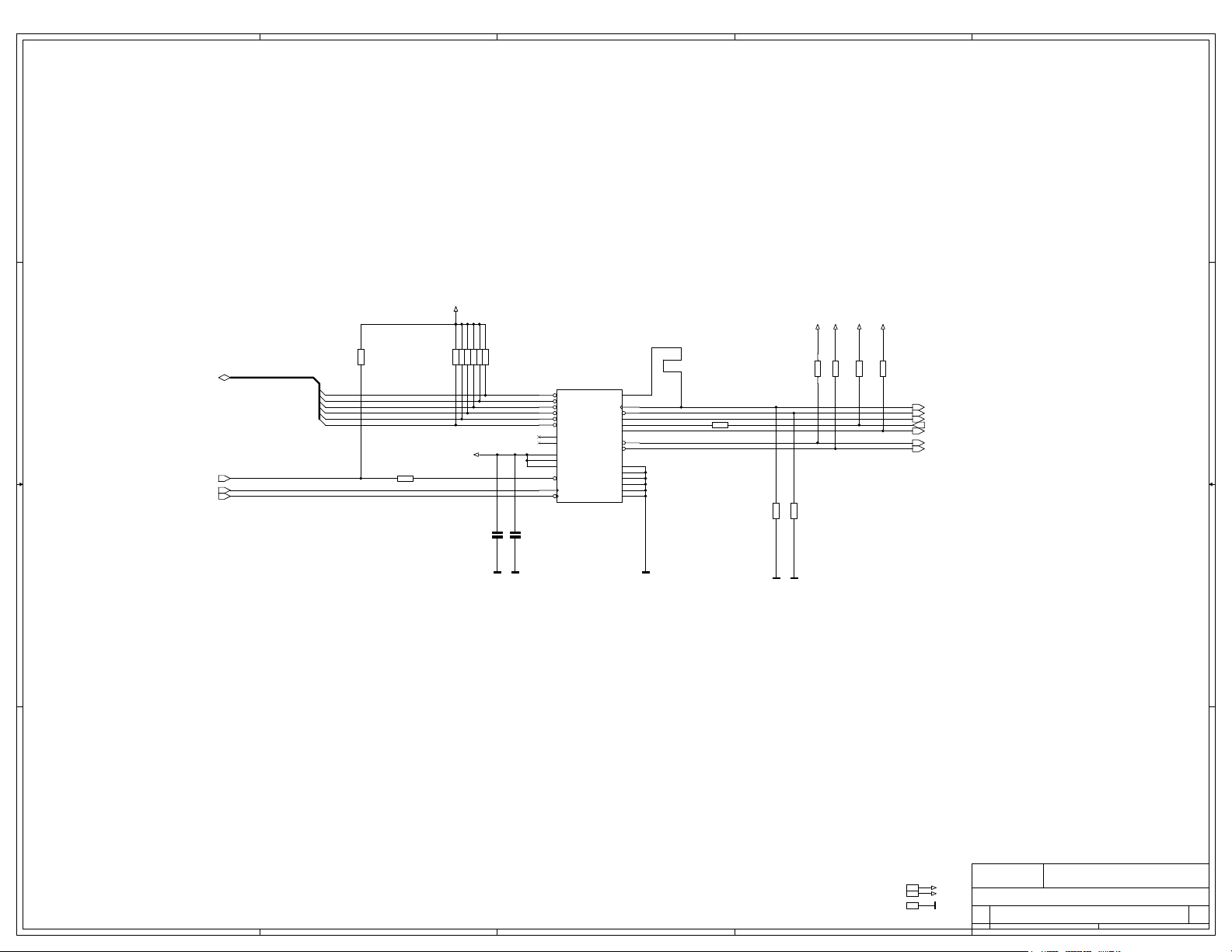

SLP_S3#

ATX POWER

D D

12V

5V

5VSB

3V3

ATX 12V

12V

CPU

VRM MODULE

MIC5284

VCCP

VCC_1V2VID

CLK

VCC_CLK

MCH

VTT

C C

ISL6225

A

LTC1117

VCC_1V5

VCC_1V8

VCC_DDR

DIMM

VCC_DDR

VCC_REF

VCC_TERM

SLP_S4#

SLP_S3#

ISL6225

A

B

B B

ICH4

VCC_5V0SUS

LTC1117

LTC1117

VCC_3V3SUS

VCC_1V5SUS

VCC_1V8S

VCC_1V5S

VCC_3V3S

VCC_5V0S

A A

COUGAR *

ISL6225

5

4

B

3

V_3V3AGP

Intel (R) 845E Interactive Client Reference Design

Title

BLOCK-POWER

Size Document Number Rev

C

2

Date Sheet of

B444B-W

335Friday, September 26, 2003

1

2.00

5

4

3

2

1

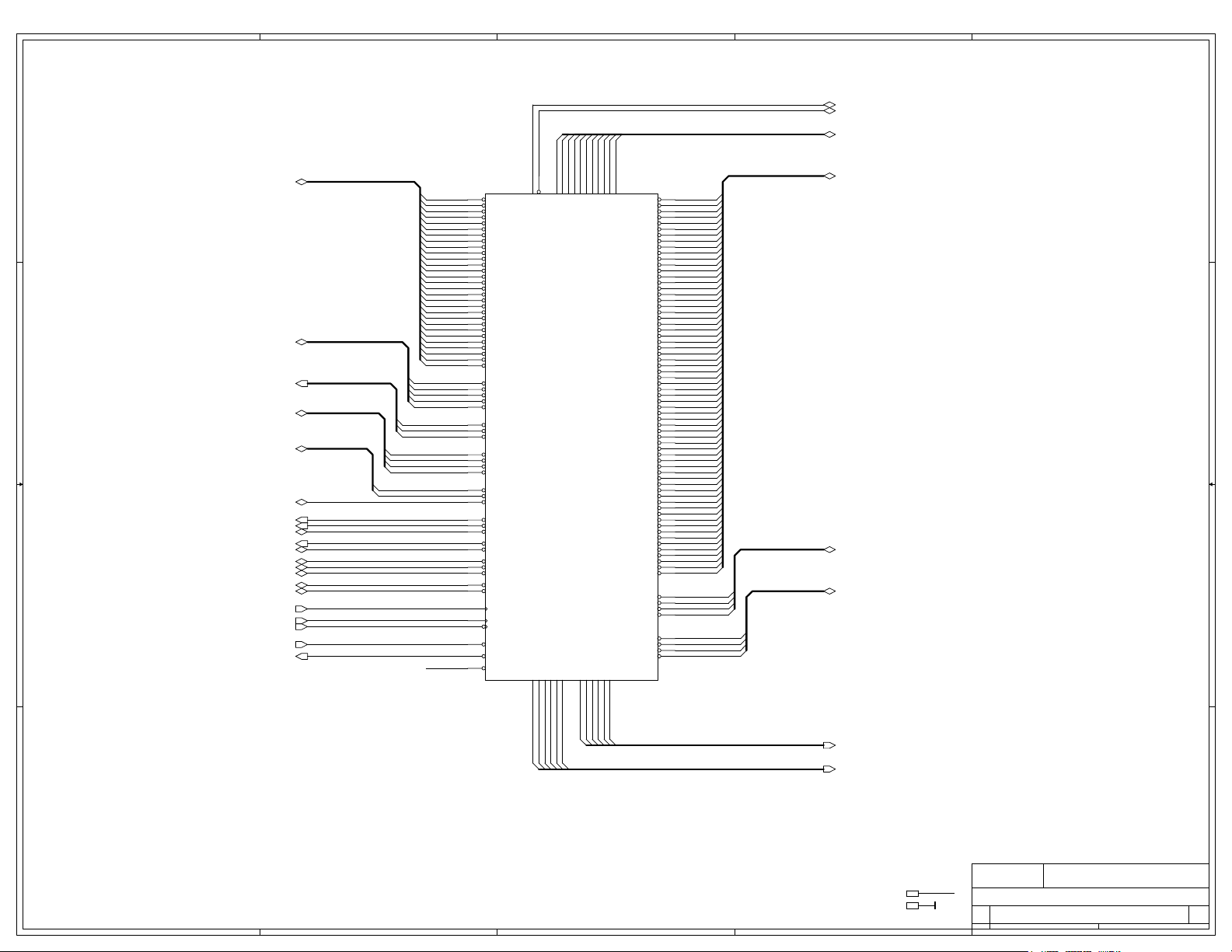

DK4

DK204060

DK9

DK204060

DK14

DK204060

B7

BOHR4.0

Mx

B8

BOHR4.0

Mx

B9

BOHR4.0

Mx

DK5

DK204060

DK10

DK204060

V_COREV_COREV_CORE V_COREV_CORE

DK15

DK204060

M29

MACADRESS

M30

MACADRESS

XXX1

XXX2

M31

M E C H

BAT_CR2032

M32

M E C H

JMP_2mm54

M10

FWH

82802AC

BRD1

PCB

B444B

M7

B4441000.01

BIOS IN

Firmware-Hub

M11

HS_MCH_PIN_FIN

XXX1

XXX2

M15

HS_MCH_LEVER

XXX1

XXX2

M1

123

P4_RETENT

M2

1234567

BGA593A/COOL

M12

HS_MCH_INTERFACE

XXX1

XXX2

M16

HS_MCH_PORON

HS_MCH_CLIP

XXX1

XXX1

XXX2

XXX2

4

M24

M25

SM02/RD

M26

SM02/RD

M23

SM02/RD

SM02/RD

8

M17

B1

BOHR4.0

Mx

B2

D D

C C

BOHR4.0

Mx

B3

BOHR4.0

Mx

V_CORE V_CORE V_CORE V_CORE V_CORE

DK1

DK204060

DK204060

DK6

DK204060

DK204060

DK11

DK204060

DK204060

DK16

DK204060

DK204060

MARKE1

MARKETOP

MARKE2

MARKETOP

MARKE3

MARKETOP

B4

BOHR4.0

Mx

B5

BOHR4.0

Mx

DK2

DK3

DK204060

V_CORE V_CORE V_CORE V_COREV_CORE

DK7

DK8

DK204060

DK12

DK13

DK204060

V_CORE V_COREV_CORE

DK17

DK18

DK204060

MRKF1

MARKFPIT

B B

A A

TP2

TP1

GND GND GND GND

TP3

5

TP4

Intel (R) 845E Interactive Client Reference Design

Title

V_CORE6..8,11,17,33,35

4

3

2

V_CORE

MECH-ROUTE

Size Document Number Rev

C

Date Sheet of

B444B-W

435Friday, September 26, 2003

1

2.00

5

4

3

2

1

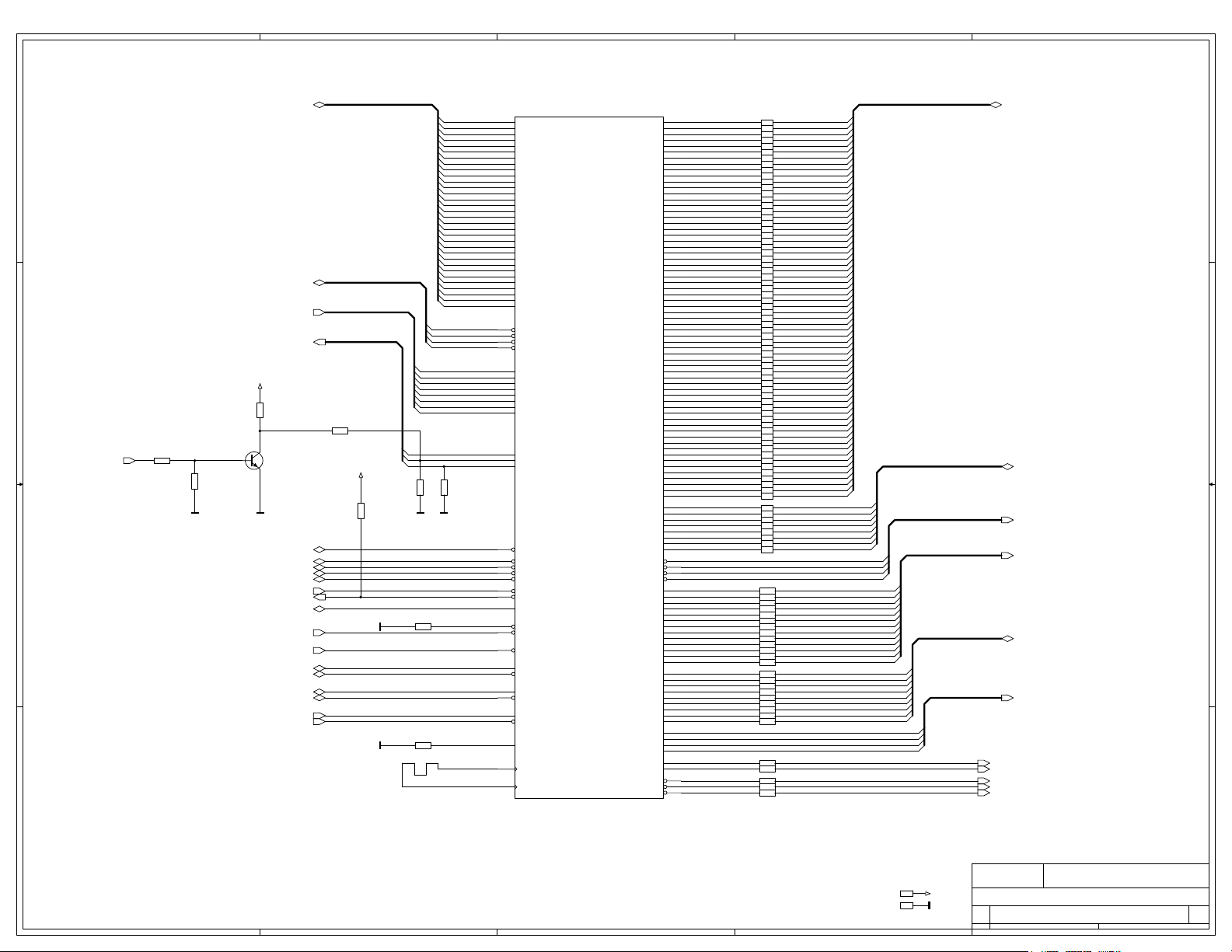

INPUT

VOLTAGES

V_12V0VRM V_12V0VRMF

V_12V0

D D

V_5V0SB

V_5V0

C C

DERIVED VOLTAGES -->

V_FAN1

V_FAN1S

V_FAN1SF

V_FAN2

V_FAN2S

V_FAN2SF

V_12USB2

V_12USB2F

V_12USB2S

V_12USB3

V_12USB3F

V_12USB3S

V_3V3SB

V_1V5SB

V_KB

V_KBF

V_DDR

V_USB0

V_USB1

V_USB2

V_USB3

V_USB4

V_USB5

V_USB0X

V_USB1X

V_USB2X

V_USB3X

V_USB4X

V_USB5X

V_1V5

V_3V3AGP

V_12VAUD

V_AUDOUT

V_5VAUD

V_BLI

V_DDRVTT

V_CORE

V_3V3LAN

V_3V3LAN0

V_VCCA

V_VCCIOPLL

V_1V5LAN

V_2V5LAN

V_DDRREF

V_1V5A1

V_1V5A2

V_2V5_LVD V_2V5_LVD1

V_HVDD

V_ICHPLL

V_LVDD1

V_LVDD2

V_PLLVDD

V_2V5_LVD2

V_CVDD

V_2V0_2V5 V_VDD1

V_2V5_VDD V_VDD2

V_VCC1

V_AVCC1

V_PVCC1

V_VREF_SII

V_DBL

V_5DVI

V_PIDE

B B

V_3V3

V_SIDE

V_FIR

V_IR

V_1V2VID

V_1V8

V_CLK

V_5V0CF

V_5DVIF

V_IOLAN

V_GAME

V_GAMEF

V_AMP

V_AMPIN

V_AMPINX

V_AMPOUT

V_5V0REF

V_DL_CL

V_DL_CLF

V_AVDD

V_FPVDD

V_TVDD

V_VPVDD

V_VDD3

V_3V3SB

V_BAT

V_RTC

V_RTCBIAS

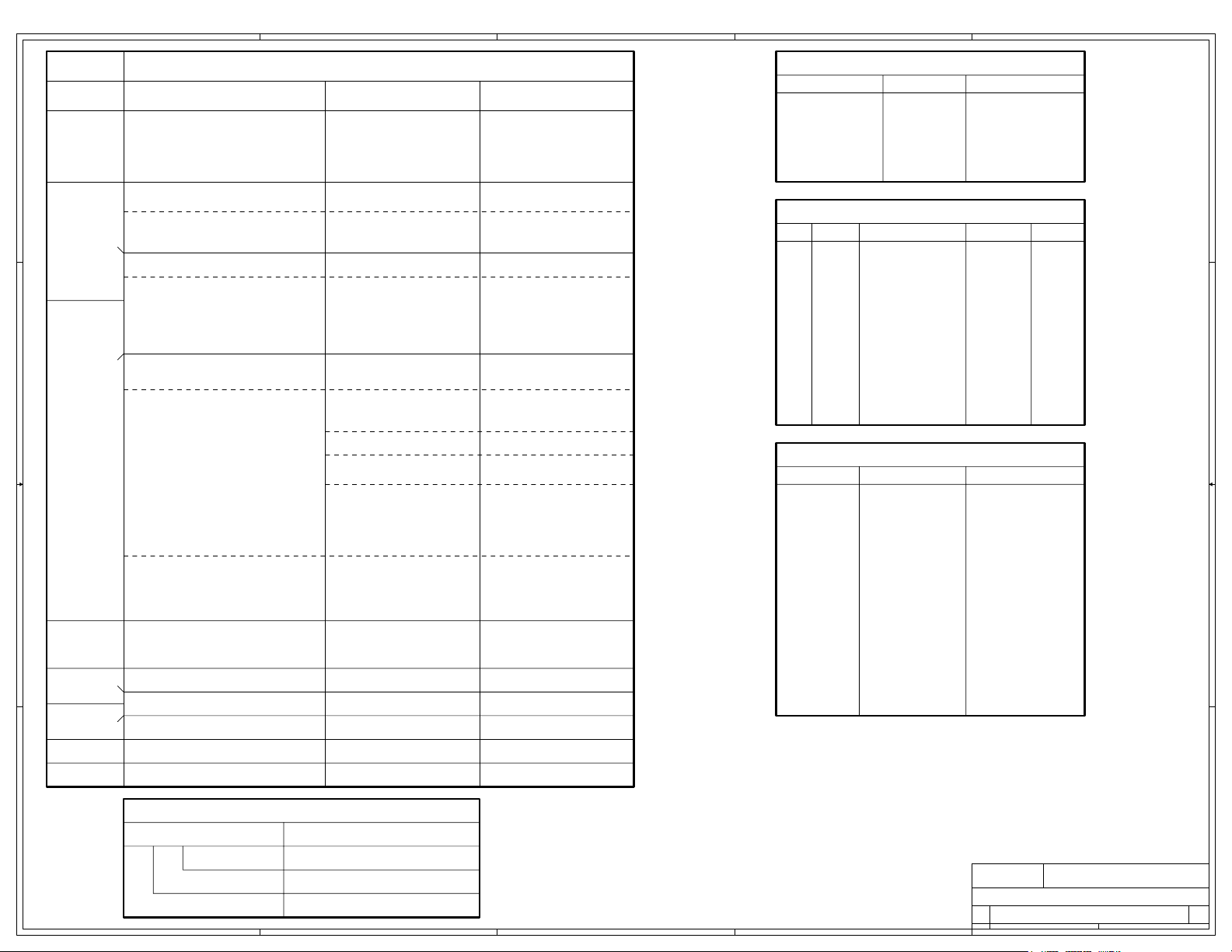

I2C DEVICES

DEVICE ADDRESS

CLOCK GENERATOR

SO-DIMM0

SO-DIMM1

ICH4 SLAVE

LAN CONTROLLER

LM87 HW MONITOR

1101001x

1010000x

1010001x

1000100x

N/A

0101110x

BUS

SM BUS

SM BUS

SM BUS

SM LINK

SM LINK

SM BUS

PCI/AGP DEVICES

DEV IDSEL DEVICE IRQ REQ/GNT

AD16

00

AD17

01

AD18

02

AD19

03

AD20

04

AD21

05

AD22

06

AD23

07

AD24

08

AD25

09

AD26

10

AD27

11

AD28

12

AD29

13

AD30

14

AD31

15

COUGAR AGP

LAN10/100/1000T

INTERNAL LAN

MINI PCI SLOT

STD PCI SLOT

RISER SLOT1

RISER SLOT2

RISER SLOT3

A

G

N/A

E-F

A-B-C-D

B-C-D-A

C-D-A-B

D-A-B-C

AGP

4

N/A

3

0

0

1

2

ICH4 GPIOs

GPIO DEVICE

GPI6

GPI7

GPI8

GPI12

GPI13

GPIO25

GPIO27

GPIO28

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

GPIO38

GPIO39

GPIO40

GPIO41

GPIO42

GPIO43

SUPER I/O 0

SUPER I/O 1

SUPER I/O 0

SUPER I/O 1

CPLD

LAN0 KINNERETH

MINI PCI

CPLD

PRIMARY IDE

SECONDARY IDE

POWERED USB

POWERED USB

FIRMWARE HUB

FIRMWARE HUB

PCI RISER

PCI RISER

AUDIO AMPLIFIER

PCI RISER

PCI SLOT

PCI SLOT

SIGNAL NAME

SIO0_SMI#

SIO1_SMI#

SIO0_PME#

SIO1_PME#

XC_GPIO2

LAN0_ENA

MPCI_ACT#

XC_GPIO1

IDE_PPDIAG#

IDE_SPDIAG#

USB_PWR2ENA#

USB_PWR3ENA#

FWH_WP#

FWH_TBL#

RISER_ID1

RISER_ID2

AMP_SHDN

NOGO

P_PRSNT1#

P_PRSNT2#

V_-12V0

V_-5V0

A A

POWER STATES

ON IN STATE

S5 (SOFT OFF)

S0 (FULL ON)

5

POWER PLANE

V_*SB, V_KB, V_*LAN, V_USB*

V_DDR, V_DDRREFS3 (SUS. TO RAM)

OTHERS

4

Intel (R) 845E Interactive Client Reference Design

Title

NOTES

Size Document Number Rev

C

3

2

Date Sheet of

B444B-W

535Friday, September 26, 2003

1

2.00

5

4

3

2

1

H_A#[3..31]9

D D

H_REQ#[0..4]9

H_ADSTB#[0..1]9

C C

H_DEFER#9

H_RS#[0..2]9

H_IGNNE#15

PWRGOOD15

B B

H_CPURST#8,9

H_A#[3..31]

H_REQ#[0..4]

H_ADSTB#[0..1]

V_CORE V_CORE

R362RA

R2301RA

R451RA

R562RA

H_ADS#9

H_BR0#9

H_BPRI#9

H_BNR#9

H_LOCK#9

H_HIT#9

H_HITM#9

H_RS#[0..2]

H_TRDY#9

H_A20M#15

H_FERR#15

H_SMI#15

STPCLK#15

CPUSLP#15,18

H_INTR15

H_NMI15

V_CORE

CK_CPU+12

CK_CPU-12

H_INIT#15

SPAREPIN

SPAREPIN

SPAREPIN

SPAREPIN

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

H_A#16

H_A#15

H_A#14

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

H_A#6

H_A#5

H_A#4

H_A#3

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_ADSTB#1

H_ADSTB#0

H_ADS#

SPAREPIN

SPAREPIN

SPAREPIN

IERR#

SPAREPIN

H_BR0#

H_BPRI#

H_BNR#

H_LOCK#

H_HIT#

H_HITM#

H_DEFER#

H_RS#2

H_RS#1

H_RS#0

SPAREPIN

H_TRDY#

H_A20MX#

R662RA

H_FERR#

H_IGNNEX#

R762RA

H_SMIX#

R862RA

PWRGOOD

STPCLKY#

R962RA

CPUSLPY#

R1062RA

H_INTRX

R1162RA

H_NMIX

R1262RA

PROCHOT#

R1362RA

CK_CPU+

CK_CPU-

H_INIT#

H_CPURST#

U1A SW478/S1

AB1

A35#

Y1

A34#

W2

A33#

V3

A32#

U4

A31#

T5

A30#

W1

A29#

R6

A28#

V2

A27#

T4

A26#

U3

A25#

P6

A24#

U1

A23#

T2

A22#

R3

A21#

P4

A20#

P3

A19#

R2

A18#

T1

A17#

N5

A16#

N4

A15#

N2

A14#

M1

A13#

N1

A12#

M4

A11#

M3

A10#

L2

A9#

M6

A8#

L3

A7#

K1

A6#

L6

A5#

K4

A4#

K2

A3#

H3

REQ4#

J3

REQ3#

J4

REQ2#

K5

REQ1#

J1

REQ0#

R5

ADSTB1#

L5

ADSTB0#

G1

ADS#

V5

AP1#

AC1

AP0#

AA3

BINIT#

AC3

IERR#

V6

MCERR#

H6

BR0#

D2

BPRI#

G2

BNR#

G4

LOCK#

F3

HIT#

E3

HITM#

E2

DEFER#

F4

RS2#

G5

RS1#

F1

RS0#

AB2

RSP#

J6

TRDY#

C6

A20M#

B6

FERR#

B2

IGNNE#

B5

SMI#

AB23

PWRGOOD

Y4

STPCLK#

AB26

CPUSLP#

D1

LINT0

E5

LINT1

C3

PROCHOT#

AF22

BCLK0

AF23

BCLK1

W5

INIT#

AB25

RESET#

THERMDA

THERMDC

THERMTRIP#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

SKTOCC#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

D23#

D22#

D21#

D20#

D19#

D18#

D17#

D16#

D15#

D14#

D13#

D12#

D11#

D10#

DBI3#

DBI2#

DBI1#

DBI0#

DBSY#

DRDY#

DP3#

DP2#

DP1#

DP0#

BSEL1

BSEL0

H_D63

AA24

H_D62

AA22

H_D61

AA25

H_D60

Y21

H_D59

Y24

H_D58

Y23

H_D57

W25

H_D56

Y26

H_D55

W26

H_D54

V24

H_D53

V22

H_D52

U21

H_D51

V25

H_D50

U23

H_D49

U24

H_D48

U26

H_D47

T23

H_D46

T22

H_D45

T25

H_D44

T26

H_D43

R24

H_D42

R25

H_D41

P24

H_D40

R21

H_D39

N25

H_D38

N26

H_D37

M26

H_D36

N23

H_D35

M24

H_D34

P21

H_D33

N22

H_D32

M23

H_D31

H25

H_D30

K23

H_D29

J24

H_D28

L22

H_D27

M21

H_D26

H24

H_D25

G26

H_D24

L21

H_D23

D26

H_D22

F26

H_D21

E25

H_D20

F24

H_D19

F23

H_D18

G23

H_D17

E24

H_D16

H22

H_D15

D25

H_D14

J21

H_D13

D23

H_D12

C26

H_D11

H21

H_D10

G22

H_D9

B25

D9#

H_D8

C24

D8#

H_D7

C23

D7#

H_D6

B24

D6#

H_D5

D22

D5#

H_D4

C21

D4#

H_D3

A25

D3#

H_D2

A23

D2#

H_D1

B22

D1#

H_D0

B21

D0#

H_DBI#3

V21

H_DBI#2

P26

H_DBI#1

G25

H_DBI#0

E21

H_DBSY#

H5

H_DRDY#

H2

SPAREPIN

L25

SPAREPIN

K26

SPAREPIN

K25

SPAREPIN

J26

H_DSTBN#3

W22

H_DSTBN#2

R22

H_DSTBN#1

K22

H_DSTBN#0

E22

H_DSTBP#3

W23

H_DSTBP#2

P23

H_DSTBP#1

J23

H_DSTBP#0

F21

SPAREPIN

AD5

AD6

SKTOCC#

AF26

H_DBI#[0..3]

H_DSTBN#[0..3]

H_DSTBP#[0..3]

V_3V3

H_D[0..63]

H_D[0..63] 9

H_DBI#[0..3] 9

H_DBSY# 9

H_DRDY# 9

H_DSTBN#[0..3] 9

H_DSTBP#[0..3] 9

R14

4k7A

BSEL0 10,12

SKTOCC# 18

B3C4A2

V_CORE

R17

THERMDC

THERMDA

62RA

THERMDA33

THERMDC33

THERMTRIP# 16

A A

SPAREPIN7,9,11,15,16,24..27

5

4

3

2

SPAREPIN

V_3V38,12,15..17,19,20,23,26..29,33,35

V_CORE4,7,8,11,17,33,35

GND4,7,8,10..35

V_3V3

Title

V_CORE

GND

CPU BUS

Size Document Number Rev

C

Date Sheet of

Intel (R) 845E Interactive Client Reference Design

B444B-W

635Friday, September 26, 2003

1

2.00

5

V_CORE

R2251RA

R1851RA

R2351RA

R2051RA

R47150RA

R2151RA

R1951RA

BPM#[0..5]

BPM#[0..5]8

D D

ITP_DBR#8,18

H_TCK8

H_TDI8

H_TDO8

H_TMS8

H_TRST#8

V_CORE

V_CORE

GND

C C

GND

DPSLP#18

VID[0..4]18,33

R36

270RA

GND

VID[0..4]

V_CORE

C27

100nA

GND

L1

4uH7/SB

V_VCCAX

B B

V_CORE

V_1V2VID

R390RA

R400RA

XXX1

XXX2

+

+

L2

C39

33u/TA

C56

33u/TA

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

SPAREPIN

SPAREPIN

SPAREPIN

SPAREPIN

SPAREPIN

SPAREPIN

SPAREPIN

SPAREPIN

SPAREPIN

SPAREPIN

ITP_CKO0

R241KA

ITP_CKO1

R251KA

COMP0

R2651RA

COMP1

R2751RA

VID4

VID3

VID2

VID1

VID0

TSTHI0

R2851RA

TSTHI1

R2951RA

TSTHI2

R3051RA

TSTHI3

R3151RA

TSTHI4

R3251RA

TSTHI5

R3351RA

TSTHI8

R3451RA

TSTHI9

R3551RA

TSTHI10

R3751RA

GHI#

R380RA

V_VCCA

GND_ACPU

V_VCCIOPLL

4uH7/SB

V_1V2VID

R4149R9A

V_CORE

C65

10nA

GTLREF

R42

100RA

C67

C66

220pA

1u/CA

GND GNDGND GND

4

U1B SW478/S1

AB4

BPM5#

AA5

BPM4#

Y6

BPM3#

AC4

BPM2#

AB5

BPM1#

AC6

BPM0#

AE25

DBR#

D4

TCK

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

A22

RESEVED_0

A7

RESEVED_1

AD2

RESEVED_2

AD3

RESEVED_3

AE21

RESEVED_4

AF3

RESEVED_5

AF24

RESEVED_6

AF25

RESEVED_7

AC26

ITP_CLK0

AD26

ITP_CLK1

AA20

ITPCLKOUT0

AB22

ITPCLKOUT1

L24

COMP0

P1

COMP1

AE1

VID4

AE2

VID3

AE3

VID2

AE4

VID1

AE5

VID0

AD24

TESTHI0

AA2

TESTHI1

AC21

TESTHI2

AC20

TESTHI3

AC24

TESTHI4

AC23

TESTHI5

U6

TESTHI8

W4

TESTHI9

Y3

TESTHI10

A6

GHI#/TESTHI11

AD25

DPSLP#/TESTHI12

AD20

VCCA

AD22

VSSA

AE23

VCCIOPLL

AF4

VCCVID

F6

GTLREF_3

F20

GTLREF_2

AA6

GTLREF_1

AA21

GTLREF_0

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_59

VCC_57

VCC_58

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_75

VCCSENSE

VSSSENSE

A8

A10

A12

A14

A16

A18

A20

B7

B9

B11

B13

B15

B17

B19

C8

C10

C12

C14

C16

C18

C20

D7

D9

D11

D13

D15

D17

D19

E8

E10

E12

E14

E16

E18

E20

F9

F11

F13

F15

F17

F19

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AC8

AC10

AC12

AC14

AC16

AC18

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF2

A5

A4

V_CORE

3

U1C SW478/S1

A3

VSS_0

A9

VSS_1

A11

VSS_2

A13

VSS_3

A15

VSS_4

A17

VSS_5

A19

VSS_6

A21

VSS_7

A24

VSS_8

A26

VSS_9

B4

VSS_10

B8

VSS_11

B10

VSS_12

B12

VSS_13

B14

VSS_14

B16

VSS_15

B18

VSS_16

B20

VSS_17

B23

VSS_18

B26

VSS_19

C2

VSS_20

C5

VSS_21

C7

VSS_22

C9

VSS_23

C11

VSS_24

C13

VSS_25

C15

VSS_26

C17

VSS_27

C19

VSS_28

C22

VSS_29

C25

VSS_30

D3

VSS_31

D6

VSS_32

D8

VSS_33

D10

VSS_34

D12

VSS_35

D14

VSS_36

D16

VSS_37

D18

VSS_38

D20

VSS_39

D21

VSS_40

D24

VSS_41

E1

VSS_42

E4

VSS_43

E7

VSS_44

E9

VSS_45

E11

VSS_46

E13

VSS_47

E15

VSS_48

E17

VSS_49

E19

VSS_50

E23

VSS_51

E26

VSS_52

F2

VSS_53

F5

VSS_54

F8

VSS_55

F10

VSS_56

F12

VSS_57

F14

VSS_58

F16

VSS_59

F18

VSS_60

F22

VSS_61

F25

VSS_62

G3

VSS_63

G6

VSS_64

G21

VSS_65

G24

VSS_66

H1

VSS_67

H4

VSS_68

H23

VSS_69

H26

VSS_70

J2

VSS_71

J5

VSS_72

J22

VSS_73

J25

VSS_74

K3

VSS_75

K6

VSS_76

K21

VSS_77

K24

VSS_78

L1

VSS_79

L4

VSS_80

L23

VSS_81

L26

VSS_82

M2

VSS_83

M5

VSS_84

M22

VSS_85

M25

VSS_86

N3

VSS_87

N6

VSS_88

N21

VSS_89

N24

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

P2

P5

P22

P25

R1

R4

R23

R26

T3

T6

T21

T24

U2

U5

U22

U25

V1

V4

V23

V26

W3

W6

W21

W24

Y2

Y5

Y22

Y25

AA1

AA4

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AB3

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC2

AC5

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC22

AC25

AD1

AD4

AD8

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AE7

AE9

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AF1

AF6

AF8

AF10

AF12

AF14

AF16

AF18

AF20

2

V_CORE

V_CORE V_CORE

C2

C1

+

+

3300u/EA

3300u/EA

GND

GND GND

V_CORE V_CORE V_COREV_CORE V_COREV_COREV_CORE V_CORE V_CORE

C4

C5

+

+

680u/PA

680u/PA

GND GND GND GND GND GND GNDGND GND

V_CORE

V_CORE V_CORE V_CORE V_COREV_CORE V_COREV_CORE V_CORE V_CORE V_COREV_CORE

C1410u/CA

C1310u/CA

GND

GND GNDGND GNDGND GNDGND GND GND GND GND

3x Al Electrolytic 3300uF

Place : Northside of P4

C3

+

3300u/EA

C7

C6

+

+

680u/PA

680u/PA

C1510u/CA

C1610u/CA

ESR max = 12mR each

ESL max = 5nH each

C9

C8

+

+

680u/PA

C1710u/CA

+

680u/PA

C10

680u/PA

C1910u/CA

+

C11

680u/PA

C2010u/CA

+

C12

680u/PA

C2110u/CA

14x 1206 ker Place : Northside of P4

C2810u/CA

C3010u/CA

C2910u/CA

C3210u/CA

C3110u/CA

C3410u/CA

C3310u/CA

C3610u/CA

C3510u/CA

Place : Northside of P4

ESR max = 9.28mR each

ESL max = 6.4nH each

Iripple = 4.080 each

C2210u/CA

ESL typ = 1.15nH eachESR max = 3.5mR each

V_COREV_COREV_CORE V_COREV_CORE V_COREV_CORE V_COREV_CORE V_CORE

C3710u/CA

1

9x Oscon 560uF

C2310u/CA

C2410u/CA

GND GND

10x 1206 ker

Place : Inside P4 Socket

V_CORE

V_COREV_CORE

C4110u/CA

C2610u/CA

C2510u/CA

GND

ESR max = 9.28mR each

C5210u/CA

C5110u/CA

ESL max = 6.4nH each

V_CORE V_CORE

C5310u/CA

C5410u/CA

GNDGND

GNDGND GND GND GNDGND GND GNDGNDGND

V_COREV_COREV_CORE V_COREV_CORE V_COREV_CORE

V_COREV_COREV_CORE V_CORE

C4410u/CA

C4310u/CA

C4210u/CA

C4510u/CA

C4610u/CA

GND GND GNDGNDGND

GNDGND GND GND GNDGND

C4810u/CA

C4710u/CA C1810u/CA

C5010u/CA

C4910u/CA

ESR max = 3.5mR each ESL typ = 1.15nH eachPlace : Southside of P414x 1206 ker

GNDGND

V_CORE V_CORE

C59

47pA

6x 0603 ker

to eliminate

133MHz x N

C60

Freqs

47pA

Place : Between 1206 ker

GND GND

A A

VSSSENSE35

VCCSENSE35

SPAREPIN6,9,11,15,16,24..27

5

4

3

2

SPAREPIN

V_CORE4,6,8,11,17,33,35

V_1V2VID35

V_CORE

Title

V_1V2VID

GND4,8,10..35

GND

CPU POWER

Size Document Number Rev

C

Date Sheet of

Intel (R) 845E Interactive Client Reference Design

B444B-W

735Friday, September 26, 2003

1

2.00

5

D D

C C

H_CPURST#6,9

BPM#[0..5]

BPM#[0..5]7

CK_ITP+12

CK_ITP-12

4

V_CORE

R154R9A

R75522R6A

R73351RA

R73451RA

R73251RA

R73151RA

V_CORE

H_CPURSTX#

R73551RA

R73651RA

C739100nA

13

15

17

19

21

23

26

28

27

12

6

4

9

8

CN1

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

NC2

NC1

VTAP

VTT

VTT

RESET#

BCLK+

BCLK-

SW28/FD

XXX1

XXX2

C738100nA

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

TRST#

DBA#

DBR#

3

11

FBO

5

TCK

3

1

TDI

H_TDOITP

7

TDO

2

TMS

24

25

22

GND

20

GND

18

GND

16

GND

14

GND

10

GND

R75422R6A

R5227RA

R53680RA

V_3V3

2

V_CORE

V_COREV_3V3

R4939RA

R4854R9A

R46220RA

R45220RA

H_TCK 7

H_TRST# 7

H_TDI 7

H_TDO 7

H_TMS 7

ITP_DBA#

ITP_DBR# 7,18

1

GND GND

B B

A A

5

4

GND

3

GND

GND

Intel (R) 845E Interactive Client Reference Design

V_3V36,12,15..17,19,20,23,26..29,33,35

V_CORE4,6,7,11,17,33,35

GND4,7,10..35

2

V_3V3

Title

V_CORE

GND

CPU-ITP

Size Document Number Rev

C

Date Sheet of

B444B-W

835Friday, September 26, 2003

1

2.00

5

D D

H_A#[3..31]6

H_REQ#[0..4]6

C C

B B

H_RS#[0..2]6

H_DBI#[0..3]6

H_ADSTB#[0..1]6

H_DEFER#6

CK_MCH6612

H_CPURST#6,8

H_A#[3..31]

H_REQ#[0..4]

H_RS#[0..2]

H_DBI#[0..3]

H_ADSTB#[0..1]

H_ADS#6

H_TRDY#6

H_LOCK#6

H_BPRI#6

H_BR0#6

H_BNR#6

H_DBSY#6

H_DRDY#6

H_HIT#6

H_HITM#6

CK_MCH+12

CK_MCH-12

P_RST0#15,18,33

4

H_HISTB-

H_HISTB+

H_HI10

H_HI8

H_HI9

M27

N28

M24

N25

HI_STB+

SCK5+

H5

N24

E24

HI_STB-

SCK3+

SCK4+

HI_10

U2A

82845E

SCK1+

SCK2+

E14

J24G6G15

HI_9

SCK0+

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

H_A#16

H_A#15

H_A#14

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

H_A#6

H_A#5

H_A#4

H_A#3

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_RS#2

H_RS#1

H_RS#0

H_DBI#3

H_DBI#2

H_DBI#1

H_DBI#0

H_ADSTB#1

H_ADSTB#0

H_ADS#

H_TRDY#

H_DEFER#

H_LOCK#

H_BPRI#

H_BR0#

H_BNR#

H_DBSY#

H_DRDY#

H_HIT#

H_HITM#

CK_MCH66

CK_MCH+

CK_MCH-

P_RST0#

H_CPURST#

SPAREPIN

AD15

AE17

L7

HA#31

M6

HA#30

G2

HA#29

N5

HA#28

H4

HA#27

L2

HA#26

J3

HA#25

M5

HA#24

J2

HA#23

K3

HA#22

L5

HA#21

L3

HA#20

M3

HA#19

M4

HA#18

K4

HA#17

N3

HA#16

N7

HA#15

N2

HA#14

P3

HA#13

P5

HA#12

R6

HA#11

P4

HA#10

R2

HA#9

P7

HA#8

R3

HA#7

U3

HA#6

T3

HA#5

T5

HA#4

T4

HA#3

U2

HREQ#4

U5

HREQ#3

R7

HREQ#2

T7

HREQ#1

U6

HREQ#0

W6

RS#2

W7

RS#1

W2

RS#0

DBI#3

AH9

DBI#2

AG4

DBI#1

AD5

DBI#0

N6

HADSTB1#

R5

HADSTB0#

V3

ADS#

U7

HTRDY#

Y4

DEFER#

W5

HLOCK#

Y7

BPRI#

V7

BR0#

W3

BNR#

V5

DBSY#

V4

DRDY#

Y5

HIT#

Y3

HITM#

P22

66IN

J8

BCLK+

K8

BCLK-

J27

RSTIN#

CPURST#

H26

TESTIN#

3

H_HI[0..10]

H_HI0

H_HI1

H_HI2

H_HI3

H_HI4

H_HI5

H_HI6

H_HI7

P25

P24

N27

P23

M26

M25

L28

L27

HI_5

HI_6

HI_7

HI_8

SCK4-

SCK5-

G24

F5

HI_4

SCK3-

HI_3

SCK2-

G25G7G14

HI_2

SCK1-

F15

HI_1

SCK0-

HI_0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HD#53

HD#52

HD#51

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

HD#24

HD#23

HD#22

HD#21

HD#20

HD#19

HD#18

HD#17

HD#16

HD#15

HD#14

HD#13

HD#12

HD#11

HD#10

HD#9

HD#8

HD#7

HD#6

HD#5

HD#4

HD#3

HD#2

HD#1

HD#0

AE16

AD17

AH17

AE15

AF16

AC17

AH15

AG17

AG16

AG15

AE14

AG14

AF14

AC14

AH13

AG13

AF12

AE13

AG12

AH11

AG10

AG11

AF10

AE12

AC10

AG9

AD9

AE10

AC9

AE9

AC12

AC11

AH5

AF8

AG6

AG7

AG8

AF4

AH3

AH7

AE5

AG3

AF3

AH2

AF6

AE8

AG2

AG5

AE2

AC8

AC3

AC6

AC7

AD7

AB7

AE3

AA6

AA3

AC5

AB4

AB3

AA5

AB5

AA2

AC16

AD11

AE7

AD3

AC15

AE11

AE6

AD4

H_D63

H_D62

H_D61

H_D60

H_D59

H_D58

H_D57

H_D56

H_D55

H_D54

H_D53

H_D52

H_D51

H_D50

H_D49

H_D48

H_D47

H_D46

H_D45

H_D44

H_D43

H_D42

H_D41

H_D40

H_D39

H_D38

H_D37

H_D36

H_D35

H_D34

H_D33

H_D32

H_D31

H_D30

H_D29

H_D28

H_D27

H_D26

H_D25

H_D24

H_D23

H_D22

H_D21

H_D20

H_D19

H_D18

H_D17

H_D16

H_D15

H_D14

H_D13

H_D12

H_D11

H_D10

H_D9

H_D8

H_D7

H_D6

H_D5

H_D4

H_D3

H_D2

H_D1

H_D0

H_DSTBP#3

H_DSTBP#2

H_DSTBP#1

H_DSTBP#0

H_DSTBN#3

H_DSTBN#2

H_DSTBN#1

H_DSTBN#0

H_D[0..63]

H_DSTBP#[0..3]

H_DSTBN#[0..3]

2

H_HISTB+ 15

H_HISTB- 15

H_HI[0..10] 15

H_D[0..63] 6

H_DSTBP#[0..3] 6

H_DSTBN#[0..3] 6

1

CK_SCK+2

A A

5

4

3

CK_SCK-[0..5]

CK_SCK+[0..5]

CK_SCK-[0..5] 13,14

CK_SCK+[0..5] 13,14

SPAREPIN6,7,11,15,16,24..27

2

Intel (R) 845E Interactive Client Reference Design

SPAREPIN

GND4,7,8,10..35

Title

GND

MCH-SYSBUS & CLOCK

Size Document Number Rev

C

Date Sheet of

B444B-W

935Friday, September 26, 2003

1

2.00

CK_SCK-1

CK_SCK-5

CK_SCK-4

CK_SCK-3

CK_SCK-2

CK_SCK-0

CK_SCK+1

CK_SCK+0

CK_SCK+5

CK_SCK+3

CK_SCK+4

5

4

3

2

1

G_AD[0..31]26

D D

G_C/BE#[0..3]26

G_SBA[0..7]26

C C

V_1V5

R106

1KA

G_ST1X

3

R117

BSEL06,12

B B

1K5A

R121

1K5A

Q1

1

BC847/B

2

GNDGND GND

G_DEVSEL#26

G_FRAME#26

G_ADSTB1+26

G_ADSTB1-26

G_ADSTB0+26

G_ADSTB0-26

G_AD[0..31]

G_AD31

G_AD30

G_AD29

G_AD28

G_AD27

G_AD26

G_AD25

G_AD24

G_AD23

G_AD22

G_AD21

G_AD20

G_AD19

G_AD18

G_AD17

G_AD16

G_AD15

G_AD14

G_AD13

G_AD12

G_AD11

G_AD10

G_AD9

G_AD8

G_AD7

G_AD6

R123

2KA

XXX1

XXX2

GND

G_AD5

G_AD4

G_AD3

G_AD2

G_AD1

G_AD0

G_C/BE#3

G_C/BE#2

G_C/BE#1

G_C/BE#0

G_SBA7

G_SBA6

G_SBA5

G_SBA4

G_SBA3

G_SBA2

G_SBA1

G_SBA0

G_ST2

G_ST1BSELX0

G_ST0

R124

2KA

SET=ENABLE

DDR MODE

G_WBF#

R1430RA

G_C/BE#[0..3]

G_SBA[0..7]

G_ST[0..2]

G_ST[0..2]26

R111

1KA

V_1V5

R1286K8A

G_IRDY#26

G_TRDY#26

G_STOP#26

G_REQ#26

G_GNT#26

G_PAR26

G_RBF#26

GND

G_PIPE#26

G_SBSTB+26

G_SBSTB-26

GRCOMP

GND

R16040R2A

RCVEN#

U2B 82845E

AD24

G_AD31

AC22

G_AD30

AC24

G_AD29

AC25

G_AD28

AB24

G_AD27

AA25

G_AD26

AA24

G_AD25

AB23

G_AD24

Y23

G_AD23

AB26

G_AD22

AA27

G_AD21

AB27

G_AD20

AB25

G_AD19

AA28

G_AD18

Y26

G_AD17

Y27

G_AD16

V24

G_AD15

U25

G_AD14

U24

G_AD13

T24

G_AD12

U23

G_AD11

T23

G_AD10

V27

G_AD9

V26

G_AD8

U28

G_AD7

U27

G_AD6

T27

G_AD5

T26

G_AD4

R25

G_AD3

T25

G_AD2

R28

G_AD1

R27

G_AD0

AA23

G_C/BE3#

Y25

G_C/BE2#

V23

G_C/BE1#

V25

G_C/BE0#

AE25

SBA7

AE24

SBA6

AE27

SBA5

AE28

SBA4

AG27

SBA3

AG28

SBA2

AH27

SBA1

AH28

SBA0

AG26

ST2

AF24

ST1

AG25

ST0

W28

GDEVSEL#

Y24

GFRAME#

W27

GIRDY#

W24

GTRDY#

W23

GSTOP#

AG24

GREQ#

AH25

GGNT#

W25

GPAR

AE23

WBF#

AE22

RBF#

AF22

PIPE#

AC27

AD_STB1+

AC28

AD_STB1-

R24

AD_STB0+

R23

AD_STB0-

AF27

SB_STB+

AF26

SB_STB-

AD25

GRCOMP

G3

RCVENIN#

H3

RCVENOUT#

SDQ63

SDQ62

SDQ61

SDQ60

SDQ59

SDQ58

SDQ57

SDQ56

SDQ55

SDQ54

SDQ53

SDQ52

SDQ51

SDQ50

SDQ49

SDQ48

SDQ47

SDQ46

SDQ45

SDQ44

SDQ43

SDQ42

SDQ41

SDQ40

SDQ39

SDQ38

SDQ37

SDQ36

SDQ35

SDQ34

SDQ33

SDQ32

SDQ31

SDQ30

SDQ29

SDQ28

SDQ27

SDQ26

SDQ25

SDQ24

SDQ23

SDQ22

SDQ21

SDQ20

SDQ19

SDQ18

SDQ17

SDQ16

SDQ15

SDQ14

SDQ13

SDQ12

SDQ11

SDQ10

SDQ9

SDQ8

SDQ7

SDQ6

SDQ5

SDQ4

SDQ3

SDQ2

SDQ1

SDQ0

SCB7

SCB6

SCB5

SCB4

SCB3

SCB2

SCB1

SCB0

SCS#3

SCS#2

SCS#1

SCS#0

SMA12

SMA11

SMA10

SMA9

SMA8

SMA7

SMA6

SMA5

SMA4

SMA3

SMA2

SMA1

SMA0

SDQS8

SDQS7

SDQS6

SDQS5

SDQS4

SDQS3

SDQS2

SDQS1

SDQS0

SCKE3

SCKE2

SCKE1

SCKE0

SBS1

SBS0

SRAS#

SCAS#

SWE#

M_DX63

G5

M_DX62

E2

M_DX61

C2

M_DX60

B2

M_DX59

F3

M_DX58

F4

M_DX57

D3

M_DX56

C3

M_DX55

E5

M_DX54

C4

M_DX53

B5

M_DX52

E6

M_DX51

B3

M_DX50

D4

M_DX49

D6

M_DX48

C6

M_DX47

C7

M_DX46

B7

M_DX45

B9

M_DX44

E11

M_DX43

E8

M_DX42

D8

M_DX41

C9

M_DX40

E10

M_DX39

D10

M_DX38

C11

M_DX37

C13

M_DX36

B13

M_DX35

C10

M_DX34

B11

M_DX33

C12

M_DX32

E13

M_DX31

E17

M_DX30

C18

M_DX29

E19

M_DX28

C20

M_DX27

D18

M_DX26

C19

M_DX25

D20

M_DX24

C21

M_DX23

B21

M_DX22

D22

M_DX21

B23

M_DX20

C24

M_DX19

E21

M_DX18

C22

M_DX17

E23

M_DX16

D24

M_DX15

E25

M_DX14

D26

M_DX13

D27

M_DX12

B27

M_DX11

C25

M_DX10

B25

M_DX9

C27

M_DX8

E27

M_DX7

B28

M_DX6

F25

M_DX5

G27

M_DX4

H25

M_DX3

E28

M_DX2

C28

M_DX1

F27

M_DX0

G28

M_SCBX7

D14

M_SCBX6

C15

M_SCBX5

C17

M_SCBX4

B17

M_SCBX3

C14

M_SCBX2

B15

M_SCBX1

D16

M_SCBX0

C16

M_SCS#1

E7

M_SCS#0

F9

M_SCS#3

F7

M_SCS#2

E9

M_SMAX12

G22

M_SMAX11

E20

M_SMAX10

F13

M_SMAX9

F21

M_SMAX8

G20

M_SMAX7

G21

M_SMAX6

F19

M_SMAX5

E18

M_SMAX4

G19

M_SMAX3

G18

M_SMAX2

E16

M_SMAX1

F17

M_SMAX0

E12

M_SDQSX8

E15

M_SDQSX7

E3

M_SDQSX6

C5

M_SDQSX5

C8

M_SDQSX4

D12

M_SDQSX3

B19

M_SDQSX2

C23

M_SDQSX1

C26

M_SDQSX0

F26

M_SCKE1

F23

M_SCKE0

H23

M_SCKE3

E22

M_SCKE2

G23

M_SBSX1

G13

M_SBSX0

G12

M_SRASX#

F11

M_SCASX#

G8

M_SWEX#

G11

M_D63

RN1B33RX4

34

M_D62

RN1A33RX4

12

M_D61

RN2B33RX4

34

M_D60

RN2A33RX4

12

M_D59

RN1D33RX4

78

M_D58

RN1C33RX4

56

M_D57

RN2D33RX4

78

M_D56

RN2C33RX4

56

M_D55

RN3B33RX4

34

M_D54

RN3A33RX4

12

M_D53

RN4D33RX4

78

M_D52

RN4C33RX4

56

M_D51

RN3D33RX4

78

M_D50

RN3C33RX4

56

M_D49

RN4B33RX4

34

M_D48

RN4A33RX4

12

M_D47

RN5D33RX4

78

M_D46

RN5C33RX4

56

M_D45

RN7C33RX4

56

M_D44

RN7A33RX4

12

M_D43

RN5B33RX4

34

M_D42

RN5A33RX4

12

M_D41

RN7D33RX4

78

M_D40

RN7B33RX4

34

M_D39

RN8C33RX4

56

M_D38

RN8B33RX4

34

M_D37

RN9D33RX4

78

M_D36

RN9B33RX4

34

M_D35

RN8D33RX4

78

M_D34

RN8A33RX4

12

M_D33

RN9C33RX4

56

M_D32

RN9A33RX4

12

M_D31

RN13D33RX4

78

M_D30

RN13B33RX4

34

M_D29

RN14D33RX4

78

M_D28

RN14B33RX4

34

M_D27

RN13C33RX4

56

M_D26

RN13A33RX4

12

M_D25

RN14C33RX4

56

M_D24

RN14A33RX4

12

M_D23

RN15D33RX4

78

M_D22

RN15B33RX4

34

M_D21

RN16D33RX4

78

M_D20

RN16A33RX4

12

M_D19

RN15C33RX4

56

M_D18

RN15A33RX4

12

M_D17

RN16C33RX4

56

M_D16

RN16B33RX4

34

M_D15

RN17B33RX4

34

M_D14

RN17A33RX4

12

M_D13

RN18D33RX4

78

M_D12

RN18B33RX4

34

M_D11

RN17D33RX4

78

M_D10

RN17C33RX4

56

M_D9

RN18C33RX4

56

M_D8

RN18A33RX4

12

M_D7

RN19C33RX4

56

M_D6

RN19A33RX4

12

M_D5

RN20C33RX4

56

M_D4

RN20B33RX4

34

M_D3

RN19D33RX4

78

M_D2

RN19B33RX4

34

M_D1

RN20D33RX4

78

M_D0

RN20A33RX4

12

M_SCB7

RN10D33RX4

78

M_SCB6

RN10B33RX4

34

M_SCB5

RN12B33RX4

34

M_SCB4

RN12A33RX4

12

M_SCB3

RN10C33RX4

56

M_SCB2

RN10A33RX4

12

M_SCB1

RN12D33RX4

78

M_SCB0

RN12C33RX4

56

M_SMA12

R1380RA

M_SMA11

R1410RA

M_SMA10

R1390RA

M_SMA9

R1420RA

M_SMA8

R1440RA

M_SMA7

R1450RA

M_SMA6

R1480RA

M_SMA5

R1460RA

M_SMA4

R1490RA

M_SMA3

R1500RA

M_SMA2

R7370RA

M_SMA1

R7380RA

M_SMA0

R7390RA

M_SDQS8

R74033RA

M_SDQS7

R74133RA

M_SDQS6

R74233RA

M_SDQS5

R74333RA

M_SDQS4

R74433RA

M_SDQS3

R14733RA

M_SDQS2

R14033RA

M_SDQS1

R13733RA

M_SDQS0

R12733RA

R7450RA

R7460RA

R7470RA

R7480RA

R7490RA

M_D[0..63]

M_SCB[0..7]

M_SCS#[0..3]

M_SMA[0..12]

M_SDQS[0..8]

M_SCKE[0..3]

M_D[0..63] 13,14

M_SCB[0..7] 13,14

M_SCS#[0..3] 13,14

M_SMA[0..12] 13,14

M_SDQS[0..8] 13,14

M_SCKE[0..3] 13,14

M_SBS1 13,14

M_SBS0 13,14

M_SRAS# 13,14

M_SCAS# 13,14

M_SWE# 13,14

A A

Intel (R) 845E Interactive Client Reference Design

Title

V_1V511,17,28,33,34

5

4

3

2

V_1V5

GND4,7,8,11..35

GND

MCH-AGP & DDR

Size Document Number Rev

C

Date Sheet of

B444B-W

10 35Friday, September 26, 2003

1

2.00

5

4

3

2

1

V_1V5 V_1V5

AC29

W29

HLRCOMP

L3

4uH7/SB

L4

4uH7/SB

R16240R2A

+

C72

33u/TA

C75

+

33u/TA

R16524R9A

R16624R9A

R16730R1A

C90

100nA

GNDGNDGND GND

C10910u/CA

C11010u/CA

GNDGNDGND GNDGNDGND GND

V_DDRREF

V_DDRVTT

C103100n

V_1V8

V_1V5

V_1V5

GND

GND

C91

100nA

GND

C104100n

C105100n

C106100n

D D

AGP_REF28

C70

100nA

GND

HI_REF15

V_CORE

C C

R164301RA

C88

R168

150RA

V_CORE

C89

10nA

10nA

C102100n

1206 / X5R1206 / X7R

B B

A A

V_1V5A1

GND_AMCH

V_1V5A2

HSWNG

HRCOMP1

HRCOMP0

SMRCOMP

P27

AA21

T17

U17

U13

T13

P26

AD13

AA7

AC13

AC2

J21

J9

J28

AJ23

AG23

AJ21

AG21

AF20

AE21

AD20

AB20

AJ19

AG19

AE19

AC19

AF18

AD18

AB18

AA9

AB8

U8

M8

A3

A7

A11

A15

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J26

J29

K5

K7

K27

L1

L4

L6

L8

L22

L24

L26

M23

N1

N4

N8

N13

N15

N17

N22

N29

P6

P8

GND

HLRCOMP

AGPREF

VCC1_5

VSS

VSS

VCC1_5

HI_REF

HSWNG1

HSWNG0

HRCOMP1

HRCOMP0

SDREF2

SDREF1

SMRCOMP

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

P14

GND

P16R1R4

P13

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

U2C

82845E

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

R13

R15

R17

R26T6T8

GND

T14

T16

T22U1U4

U15

U29V6V8

GND GND

R29

U26

W22

U22

R22

P17

U16

R16

N16

T15

P15

U14

R14

N14

AA26

AA22

AB21

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

GND

GND

GND

GND

GND

V22W1W4W8W26Y6Y22

AJ3

AE26

AF23

AD23

AD21

VCC1_5

VCC1_5

VCC1_5

VCC1_5

GND

GND

GND

GND

V_1V8

SPAREPIN

SPAREPIN

AG29

AJ25

L25

L29

N26

N23

M22

AD26

AD27

NC1

NC2

VCC1_5

VCC1_5

VCC1_5

RSVD3

RSVD2

RSVD1

GND

K23

K25

H27

RSVD4

J23

VCC1_8

RSVD5

VCC1_8

RSVD6

G10G9J25

VCC1_8

RSVD7

G16

VCC1_8

RSVD8

VCC1_8

RSVD9

HVREF1

HVREF2

HVREF3

HVREF4

HVREF5

RSVD11

RSVD10

H7H6G17

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AB11

AB17

M7

R8

Y8

A5

A9

A13

A17

A21

A25

C1

C29

D7

D11

D15

D19

D23

D25

F6

F10

F14

F18

F22

G1

G4

G29

H8

H10

H12

H14

H16

H18

H20

H22

H24

J5

J7

K6

K22

K24

K26

L23

AA1

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ5

AJ7

AJ9

AJ15

AJ13

AJ11

AJ17

AJ27

HVREF_MCH

V_CORE

R161

49R9A

R163

C69

100RA

100nA

GND GND

WIRED

C80100nA

C77100u/BP

+

GND GND

Between

MCH and

DIMM

C92100u/TA

+

C79100nA

C78100u/BP

+

C93100u/TA

+

GNDGND GND GND GND GND GNDGND GND GND

C83100nA

All VCCSM Balls of MCH

0603 / X7R

C9410u/CA

C9510u/CA

C86100nA

C84100nA

C85100nA

GNDGNDGND GND GNDGND

C97100nA

C96100nA

1206 / X7R 0603 / X7R

C114100nA

C11210u/CA

GND GND GNDGND

1206 / X7R

C113100nA

0603 / X7R

C98100nA

C115100nA

C99100nA

C100100nA

V_DDR

V_1V5

C101100nA

V_1V8

SPAREPIN

SPAREPIN6,7,9,15,16,24..27

V_DDRREF13,14,34

V_DDRVTT14,34

5

4

3

2

SPAREPIN

V_DDR13,14,33,34

V_CORE4,6..8,17,33,35

V_1V815,17,33,35

V_1V510,17,28,33,34

V_DDR

V_DDRREF

V_DDRVTT

V_CORE

V_1V8

V_1V5

GND4,7,8,10,12..35

GND

Title

MCH-POWER

Size Document Number Rev

C

Date Sheet of

Intel (R) 845E Interactive Client Reference Design

B444B-W

11 35Friday, September 26, 2003

1

2.00

5

D D

4

3

2

1

V_3V3

FB1

BLM21B601S

C118

V_CLK

1KA

R181

C117

100nA

GND GND GND GND GND GNDGND

V_3V3 V_3V3 V_3V3

1KA

1KA

R183

R182

100nA

V_3V3

1KA

R769

R184

C126

10u/CA

V_3V3

FB2

BLM21B601S

C116

C C

10u/CA

GND

BSEL06,10

CPU_STOP#18

PCI_STOP#18

PWRDWN#18

SMBISOD13..15

SMBISOC13..15

PGOOD408#18

B B

C119

100nA

GND GND GND

1KA

V_3V3

C120

100nA

C124

10nA

V_CLK

V_CLK

V_CLKA

GND

C121

100nA

C125

10nA

C122

100nA

C123

10nA

GND

BSEL2

R1881KA

FS0

R1901KA

R200

1KA

R201

475RA

MULTISEL

IREF_CK

R19810KA

U3 ICS950201GT

50

VDDCPU

46

VDDCPU

32

VDD3V66

19

VDD3V66

14

VDDPCI2

8

VDDPCI1

37

VDDA48

26

VDDA

1

VDDAREF

4

9

15

20

31

36

41

47

27

40

55

54

53

34

25

29

30

43

42

28

2 3

A_CLKX1

3V66_1/VCH_CLK

GND

66M_OUT0/3V66_2

GND

66M_OUT1/3V66_3

GND

66M_OUT2/3V66_3

GND

GND

GND

GND

GND

GNDA

FS2

FS1

FS0

CPU_STOP#

PCI_STOP#

PWRDN#

SDATA

SDCLOCK

MULTESEL0

IREF

VTT_PWRGD#

66M_IN/3V66_5

XTAL_IN XTAL_OUT

XT1

14MHZ3181/QA

C144

10pA

CPUCLK0+

CPUCLK0-

CPUCLK1+

CPUCLK1-

CPUCLK2+

CPUCLK2-

3V66_0

48M_DOT

48M_USB

PCICLK_F0

PCICLK_F1

PCICLK_F2

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

14MREF

52

51

49

48

45

44

33

35

21

22

23

24

38

39

5

6

7

10

11

12

13

16

17

18

56

C145

10pA

CK_CPUX+

CK_CPUX-

CK_ITPX+

CK_ITPX-

CK_MCHX+

CK_MCHX-

CK_MCH66X

CK_ICH66X

CK_AGP66X

CK_RESX0

CK_RESX1

CK_RESX2

CK_ICH48X

CK_ICH33X

CK_CPLDX

CK_FWHX

CK_LPC0X

CK_LPC1X

CK_LANX

CK_MPCIX

CK_SLOT1X

CK_SLOT2X

CK_SLOT3X

CK_14MX

A_CLKX2

R169 27RA

R170 27RA

R171 27RA

R172 27RA

R173 27RA

R174 27RA

R175 33RA

R176 33RA

R177 33RA

R178 33RA

R179 33RA

R180 33RA

R185 33RA

R186 33RA

R187 33RA

R189 33RA

R191 33RA

R192 33RA

R193 33RA

R194 33RA

R195 33RA

R196 33RA

R197 33RA

R199 33RA

CK_RES0

CK_RES1

CK_RES2

C12710pA

CK_CPU+ 6

CK_CPU- 6

CK_ITP+ 8

CK_ITP- 8

CK_MCH+ 9

CK_MCH- 9

CK_MCH66 9

CK_ICH66 16

CK_AGP66 26

CK_ICH48 16

CK_ICH33 15

CK_CPLD 18

CK_FWH 33

CK_LPC0 19

CK_LPC1 20

CK_LAN 24

CK_MPCI 29

CK_SLOT1 29

CK_SLOT2 29

CK_SLOT3 29

CK_14M 16,19,20,27

R5649R9A

R5449R9A

R1649R9A

C12910pA

C12810pA

GND GND GND GND GND GNDGNDGNDGNDGND

C13210pA

C13410pA

C13510pA

C13610pA

C13310pA

C13110pA

C13010pA

C13710pA

C13810pA

C13910pA

C14010pA

C14110pA

C14210pA

C14310pA

R1549R9A

GND GND GND GNDGNDGND

R5749R9A

R5549R9A

A A

Intel (R) 845E Interactive Client Reference Design

V_CLK

V_3V36,8,15..17,19,20,23,26..29,33,35

5

4

3

2

V_CLK

Title

V_3V3

GND4,7,8,10,11,13..35

GND

CLK ICS950201

Size Document Number Rev

C

Date Sheet of

B444B-W

12 35Friday, September 26, 2003

1

2.00

5

4

3

2

1

DIMM 0

D D

M_SMA[0..12]10,14 M_D[0..63] 10,14

M_SCS#[0..3]10,14

C C

M_SCKE[0..3]10,14

CK_SCK+[0..5]9,14

CK_SCK-[0..5]9,14

M_SDQS[0..8]10,14

B B

M_SMA[0..12]

M_SMA0

M_SMA1

M_SMA2

M_SMA3

M_SMA4

M_SMA5

M_SMA6

M_SMA7

M_SMA8

M_SMA9

M_SMA10

M_SMA11

M_SMA12

V_DDR

V_DDRREF

M_SBS0

M_SBS1

M_SCS#1

M_SCS#0

GND

M_SWE#

M_SCAS#

M_SRAS#

M_SCKE0

M_SCKE1

CK_SCK+0

CK_SCK+1

CK_SCK+2

CK_SCK-0

CK_SCK-1

CK_SCK-2

M_SDQS0

M_SDQS1

M_SDQS2

M_SDQS3

M_SDQS4

M_SDQS5

M_SDQS6

M_SDQS7

M_SDQS8

GND

GND

M_SBS010,14

M_SBS110,14

M_SCS#[0..3]

M_SWE#10,14

M_SCAS#10,14

M_SRAS#10,14

M_SCKE[0..3]

CK_SCK+[0..5]

CK_SCK-[0..5]

M_SDQS[0..8]

SMBISOD12,14,15

SMBISOC12,14,15

C146

100nA

130

125

122

141

118

115

103

113

163

158

157

107

119

129

149

159

169

177

140

154

111

137

138

101

102

173

167

181

182

183

184

48

43

41

37

32

29

27

59

52

71

97

63

65

21

16

76

17

75

5

14

25

36

56

67

78

86

47

9

10

91

92

82

1

15223054627796

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

CS3#/NC

CS2#/NC

CS1#

CS0#

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE#

CAS#

RAS#

CKE0

CKE1

CK0/DNU

CK1

CK2/DNU

CK0#/DNU

CK1#

CK2#/DNU

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

NC1

NC/RESET#

NC2

NC3

NC4

NC/FETEN

SDA

SCL

SA0

SA1

SA2

VDDID

VDDSPD

VREF

VDDQ

VDDQ

VDDQ

V_DDR

104

112

128

136

143

156

164

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

CN2

SW184/D1

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

3111826344250586674818993

GND

GND

172

180738467085108

VDD

VDD

VDD

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

100

116

124

132

120

148

168

VDD

VDD

VDD

VDD

VDD

VDD

M_D0

2

D0

M_D1

4

D1

M_D2

6

D2

M_D3

8

D3

M_D4

94

D4

M_D5

95

D5

M_D6

98

D6

M_D7

99

D7

M_D8

12

D8

M_D9

13

D9

M_D10

19

D10

M_D11

20

D11

M_D12

105

D12

M_D13

106

D13

M_D14

109

D14

M_D15

110

D15

M_D16

23

D16

M_D17

24

D17

M_D18

28

D18

M_D19

31

D19

M_D20

114

D20

M_D21

117

D21

M_D22

121

D22

M_D23

123

D23

M_D24

33

D24

M_D25

35

D25

M_D26

39

D26

M_D27

40

D27

M_D28

126

D28

M_D29

127

D29

M_D30

131

D30

M_D31

133

D31

M_D32

53

D32

M_D33

55

D33

M_D34

57

D34

M_D35

60

D35

M_D36

146

D36

M_D37

147

D37

M_D38

150

D38

M_D39

151

D39

M_D40

61

D40

M_D41

64

D41

M_D42

68

D42

M_D43

69

D43

M_D44

153

D44

M_D45

155

D45

M_D46

161

D46

M_D47

162

D47

M_D48

72

D48

M_D49

73

D49

M_D50

79

D50

M_D51

80

D51

M_D52

165

D52

M_D53

166

D53

M_D54

170

D54

M_D55

171

D55

M_D56

83

D56

M_D57

84

D57

M_D58

87

D58

M_D59

88

D59

M_D60

174

D60

M_D61

175

D61

M_D62

178

D62

M_D63

179

D63

M_SCB0

44

CB0

M_SCB1

45

CB1

M_SCB2

49

CB2

M_SCB3

51

CB3

M_SCB4

134

CB4

M_SCB5

135

CB5

M_SCB6

142

CB6

M_SCB7

144

CB7

90

WP

GND

GND

GND

GND

GND

139

145

152

160

176

M_D[0..63]

M_SCB[0..7]

M_SCB[0..7] 10,14

A A

Intel (R) 845E Interactive Client Reference Design

V_DDRREF11,14,34

V_DDR11,14,33,34

5

4

3

2

V_DDRREF

Title

V_DDR

GND4,7,8,10..12,14..35

GND

DDR DIMM 0

Size Document Number Rev

C

Date Sheet of

B444B-W

13 35Friday, September 26, 2003

1

2.00

5

4

3

2

1

DIMM 1

V_DDR

D D

M_SMA[0..12]10,13

M_SCS#[0..3]10,13

C C

M_SCKE[0..3]10,13

CK_SCK+[0..5]9,13

CK_SCK-[0..5]9,13

M_SDQS[0..8]10,13

B B

M_SMA[0..12]

M_SMA0

M_SMA1

M_SMA2

M_SMA3

M_SMA4

M_SMA5

M_SMA6

M_SMA7

M_SMA8

M_SMA9

M_SMA10

M_SMA11

M_SMA12

V_DDRREF

V_DDR

M_SBS0

M_SBS1

M_SCS#3

M_SCS#2

GND

M_SWE#

M_SCAS#

M_SRAS#

M_SCKE2

M_SCKE3

CK_SCK+3

CK_SCK+4

CK_SCK+5

CK_SCK-3

CK_SCK-4

CK_SCK-5

M_SDQS0

M_SDQS1

M_SDQS2

M_SDQS3

M_SDQS4

M_SDQS5

M_SDQS6

M_SDQS7

M_SDQS8

V_DDR

GND

GND

M_SBS010,13

M_SBS110,13

M_SCS#[0..3]

M_SWE#10,13

M_SCAS#10,13

M_SRAS#10,13

M_SCKE[0..3]

CK_SCK+[0..5]

CK_SCK-[0..5]

M_SDQS[0..8]

SMBISOD12,13,15

SMBISOC12,13,15

C212

100nA

130

125

122

141

118

115

103

113

163

158

157

107

119

129

149

159

169

177

140

154

111

137

138

101

102

173

167

181

182

183

184

48

43

41

37

32

29

27

59

52

71

97

63

65

21

16

76

17

75

5

14

25

36

56

67

78

86

47

9

10

91

92

82

1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

CS3#/NC

CS2#/NC

CS1#

CS0#

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE#

CAS#

RAS#

CKE0

CKE1

CK0/DNU

CK1

CK2/DNU

CK0#/DNU

CK1#

CK2#/DNU

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

NC1

NC/RESET#

NC2

NC3

NC4

NC/FETEN

SDA

SCL

SA0

SA1

SA2

VDDID

VDDSPD

VREF

15223054627796

104

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

3111826344250586674818993

112

128

136

143

VDDQ

VDDQ

VDDQ

CN3

SW184/D1

GND

GND

GND

VDDQ

GND

156

164

172

VDDQ

VDDQ

GND

GND

GND

180738467085108

VDD

VDD

VDD

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

100

116

124

132

139

120

148

168

VDD

VDD

VDD

VDD

VDD

VDD

M_D0

2

D0

M_D1

4

D1

M_D2

6

D2

M_D3

8

D3

M_D4

94

D4

M_D5

95

D5

M_D6

98

D6

M_D7

99

D7

M_D8

12

D8

M_D9

13

D9

M_D10

19

D10

M_D11

20

D11

M_D12

105

D12

M_D13

106

D13

M_D14

109

D14

M_D15

110

D15

M_D16

23

D16

M_D17

24

D17

M_D18

28

D18

M_D19

31

D19

M_D20

114

D20

M_D21

117

D21

M_D22

121

D22

M_D23

123

D23

M_D24

33

D24

M_D25

35

D25

M_D26

39

D26

M_D27

40

D27