Page 1

82551ER Fast Ethernet PCI Controller

Networking Silicon - 82551ER

Datasheet

Product Features

■

Enhanced IP Protocol Support

—TCP, UDP, IPv4 checksum offload

—Received checksum verification

■ Quality of Service (QoS)

—Multiple priority transmit queues

■ Optimum Integration for Lowest Cost

Solution

—Integrated IEEE 802.3 10BASE-T and

100BASE-TX compatible PHY

—32-bit PCI master interface

—Thin BGA 15mm

■ Integrated power management function s

2

package

—ACPI and PCI power management

standards compliance

—Wake on “interesting” packets and link

status change support

■ PHY detects polarity, MDI-X, and cable

lengths. Auto MDI, MDI-X crossover at all

speeds

■ XOR tree mode support

■ High Perfor mance Networking Function s

—Early release

—8255x controller family chained

memory structure

—Improved dynamic transmit chaining

with multiple priorities transmit queues

—Full pin compatibility with the 82559

and 82559ER controllers

—Backward compatible software to

82559ER controllers

—Full duplex support at 10 and 100 Mbps

—IEEE 802.3u auto-negotiation support

—3 KB transmit and receive FIFOs

—Fast back-to-back transmission support

with minimum interframe spacing

—IEEE 802.3x 100BASE-TX flow control

support

—Adaptive Technology

■ Low Power Features

—Adv anced Power Mana gement (APM)

capabilities

—Low power 3.3 V device

—Efficient dynamic standby mode

—Deep power-down support

—Clockrun protocol support

■ 82551ER Enhancements

—Improved bit error rate performance

—HWI support

—Deep power-down state power reduction

■ Lead-free

1

196-pin Ball Grid Array (BGA).

Devices that are lead-free are marked with

a circled “e1” and have the product code:

LUxxxxxx.

1

This device is lead-free. That is, lead has not been intentionally added, but lead may still exist as an

impurity at <1000 ppm. The Material Declaration Data Sheet, which includes lead impurity levels and the

concentration of other Restriction on Hazardous Substances (RoHS)-banned materials, is available at:

ftp://download.intel.com/design/packtech/material_content_IC_Package.pdf#pagemode=bookmarks

In addition, this device has been tested and conforms to the same parametric specifications as previous

versions of the device.

For more information regarding lead-free products from Intel Corporation, contact your Intel Field Sales

representative.

Revision 2.6

October 2006

Page 2

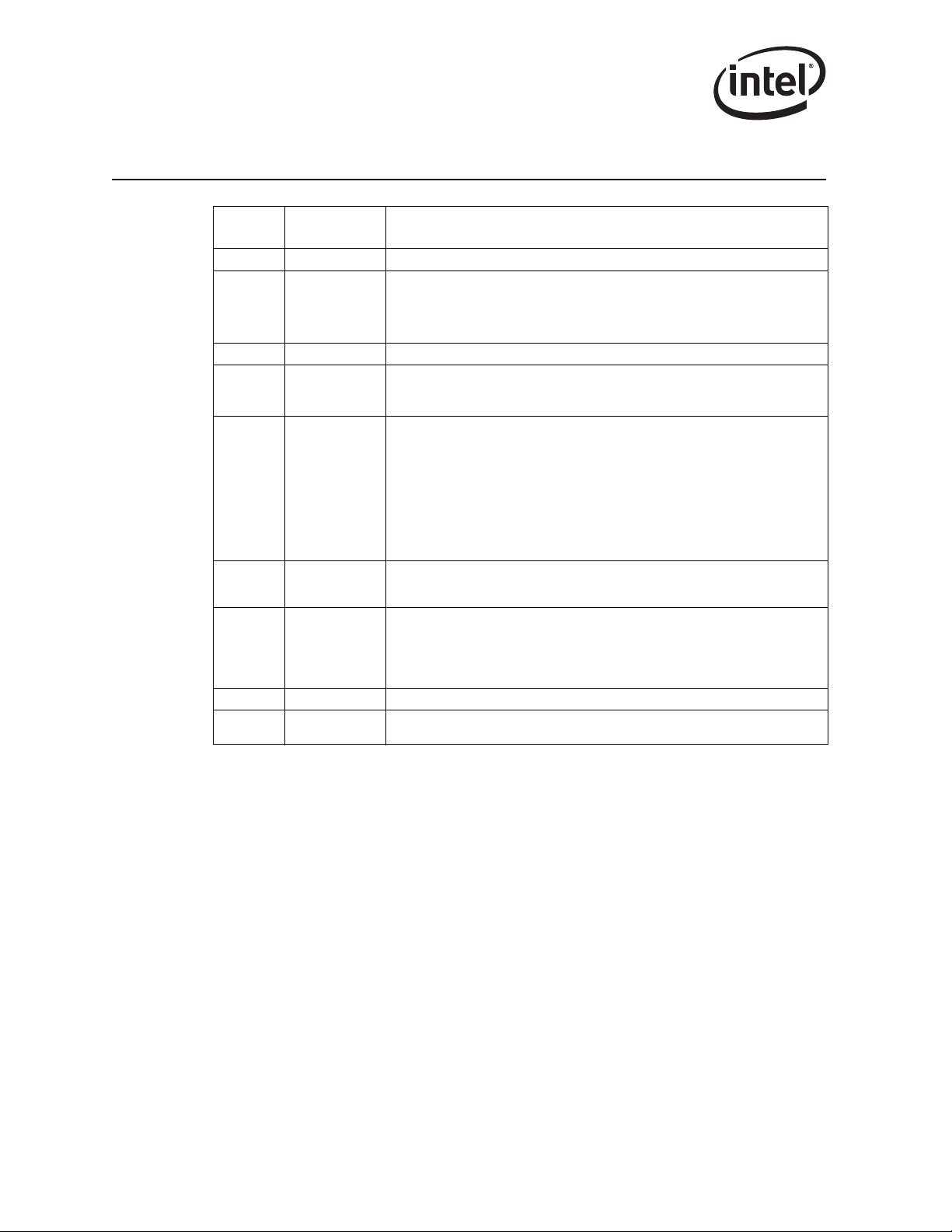

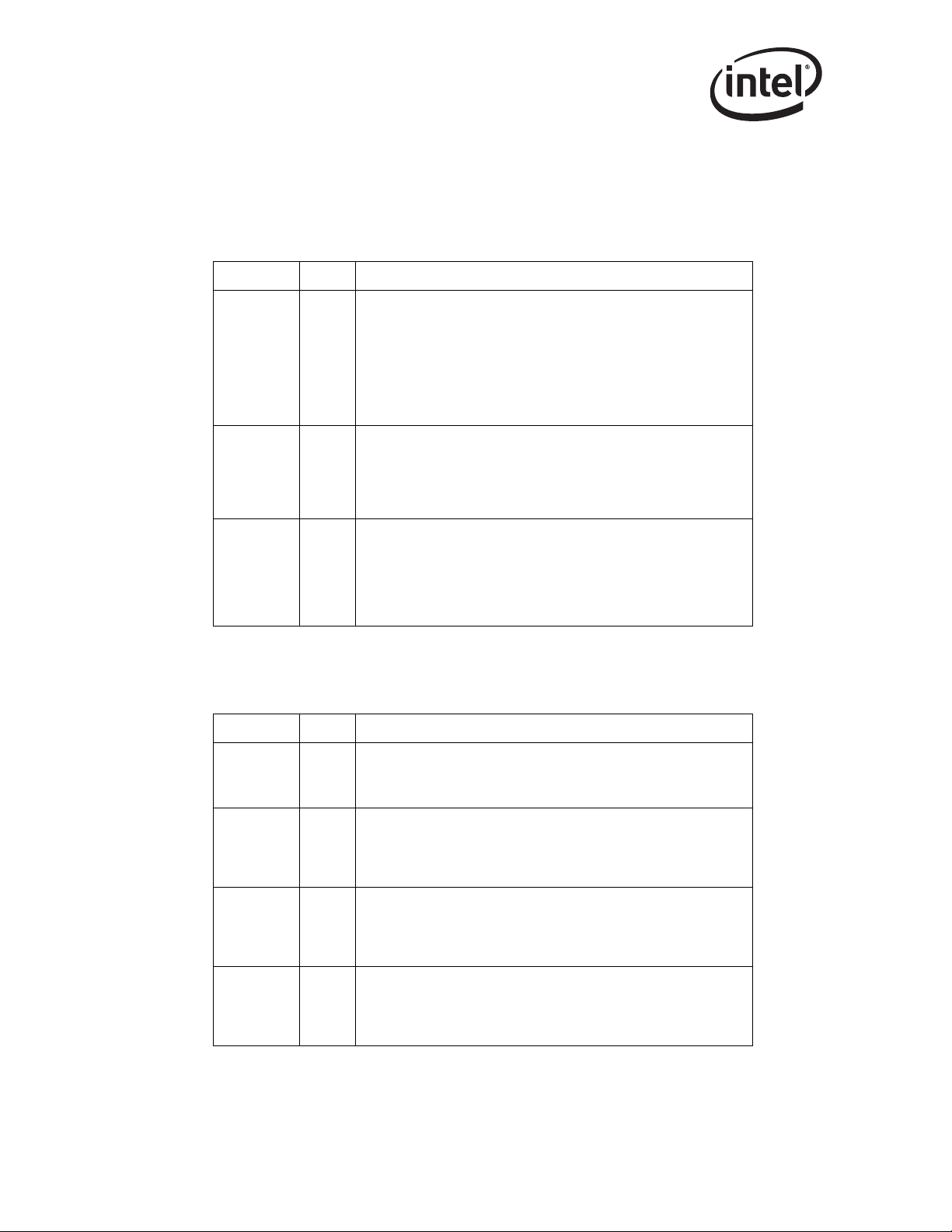

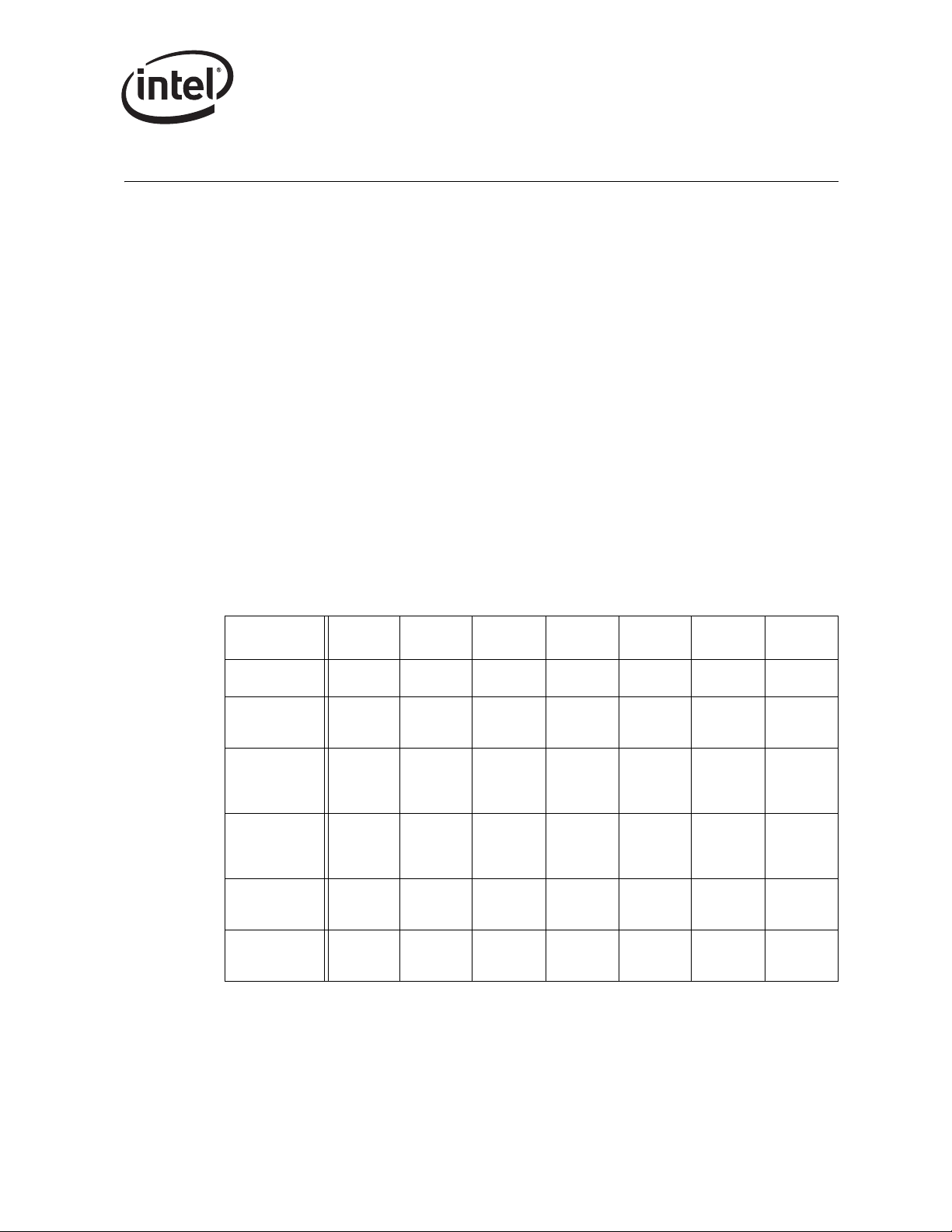

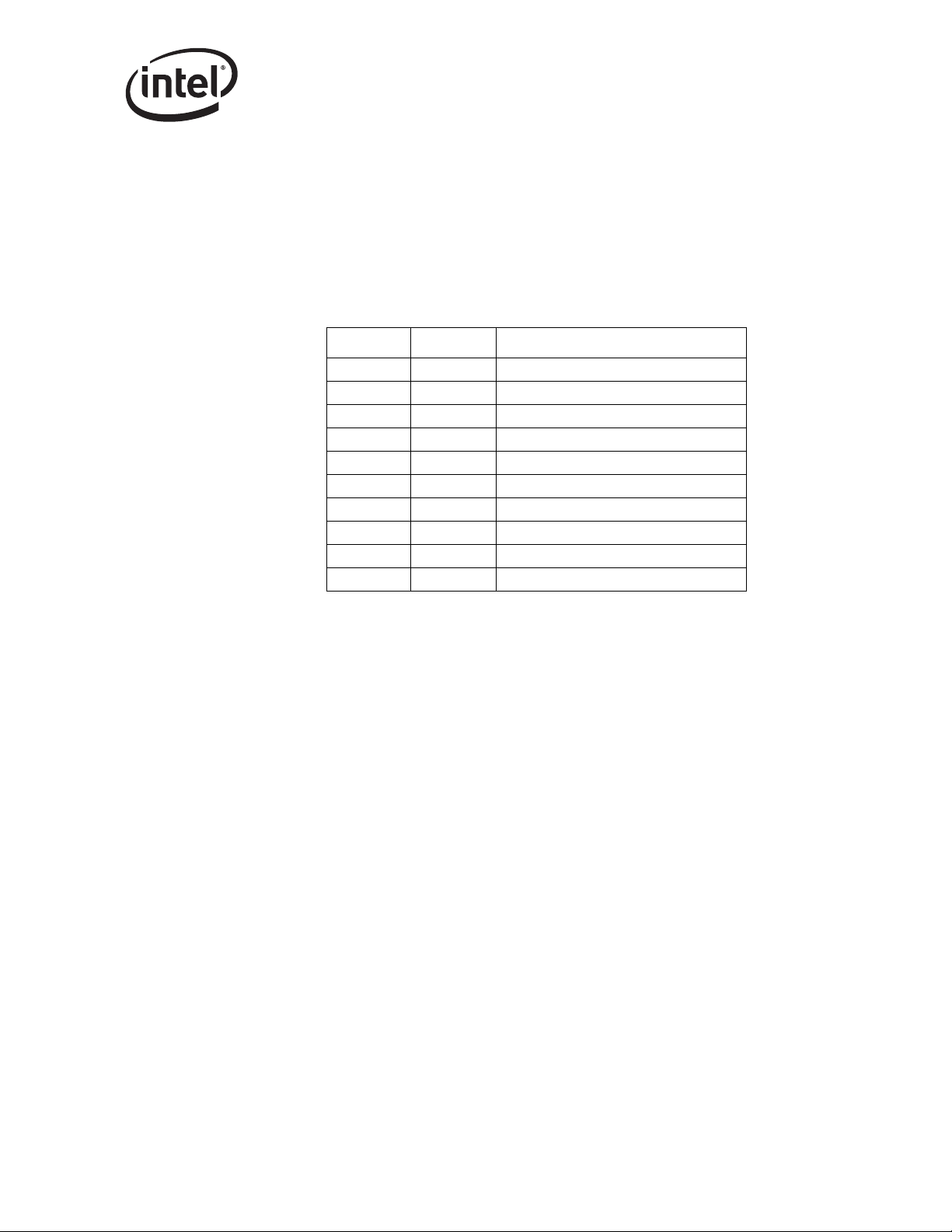

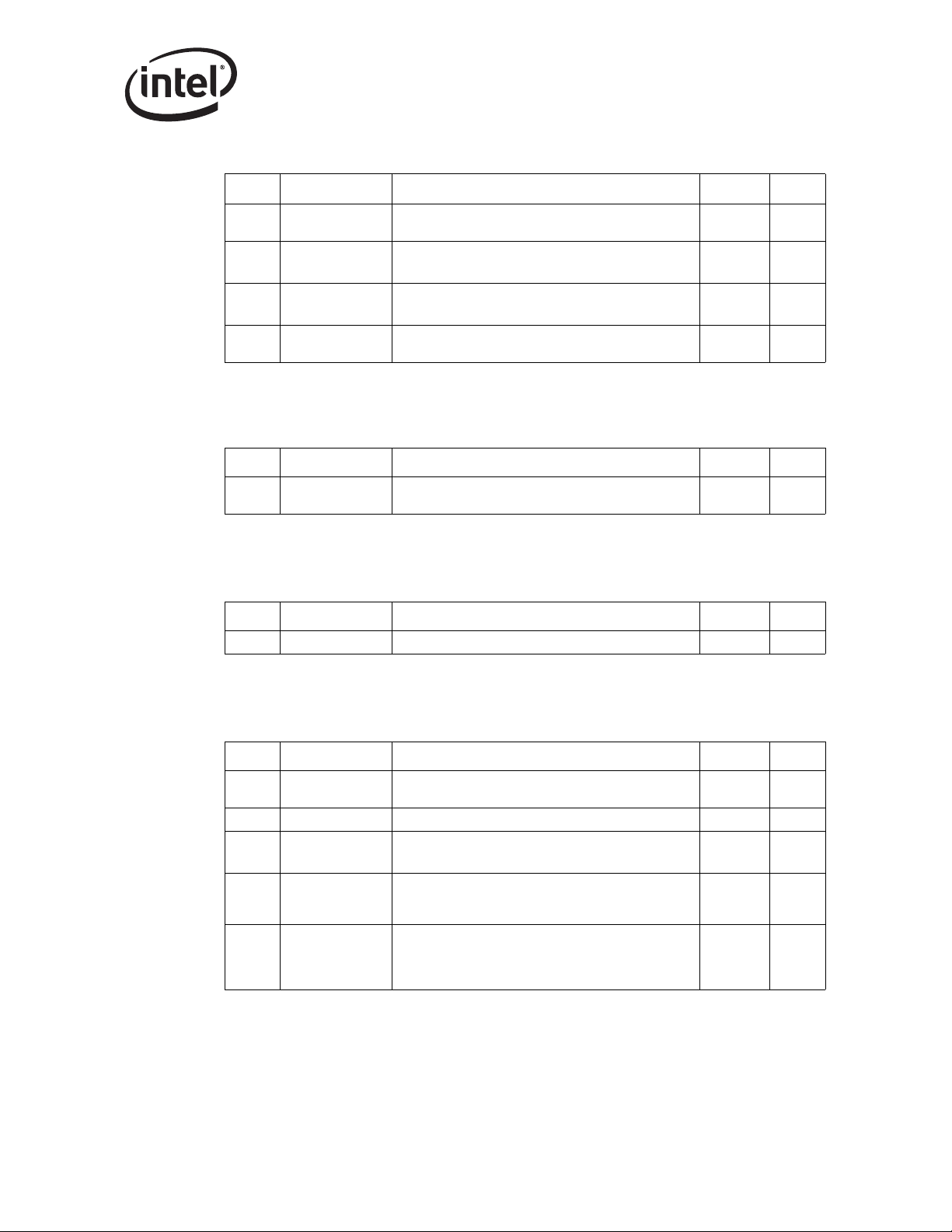

Revision History

Revision

Date

Revision Description

Nov 2001 0.7 Initial draft for release (Intel Secret).

Jan 2002 1.0 • Added description for No Connect pins.

• Clarified EEPROM address map and word definitions for the 82551ER.

• Added more detailed information for I

in the DC specifications table.

CC

• Corrected typographical errors.

Apr 2002 2.0 Changed document status to Intel Confidential.

Mar 2003 2.1 • Removed document status.

• Removed references to MDI/MDI-X feature, which is not supported by the

82551ER.

Sep 2004 2.2 • Added references to the MDI/MDI-X feature.

• Added lead-free information.

• Removed EEPROM Map bit descriptions. These descriptions can now be

found in the 82551QM/ER/IT EEPROM Map and Programming Information.

• Added 82551ER Test Port Functionality (Chapter 10).

• Added new values for RBIAS100 and RBIAS10. RBIAS100 = 649 Ω and

RBIAS10 = 619 Ω.

• Removed all references to the 82551IT and 82551QM controllers. 82551IT

and 82551QM information can now be found in their respective datasheets.

Nov 2004 2.3 • Added information about migrating from a 2-layer 0.36 mm wide-trace sub-

strate to a 2-layer 0.32 mm wide-trace substrate. Refer to the section on

Package and Pinout Information.

Nov 2004 2.4 • Updated the section describing “Multiple Priority Transmit Queues”.

• Updated the section describing “VLAN Support”.

• Added statement that no changes to existing soldering processes are

needed for the 2-layer 0.32 mm wide-trace substrate change in the section

describing “Package Information”.

Jan 2005 2.5 • Added a note for PHY signals RBIAS100 and RBIAS10 to Table 8.

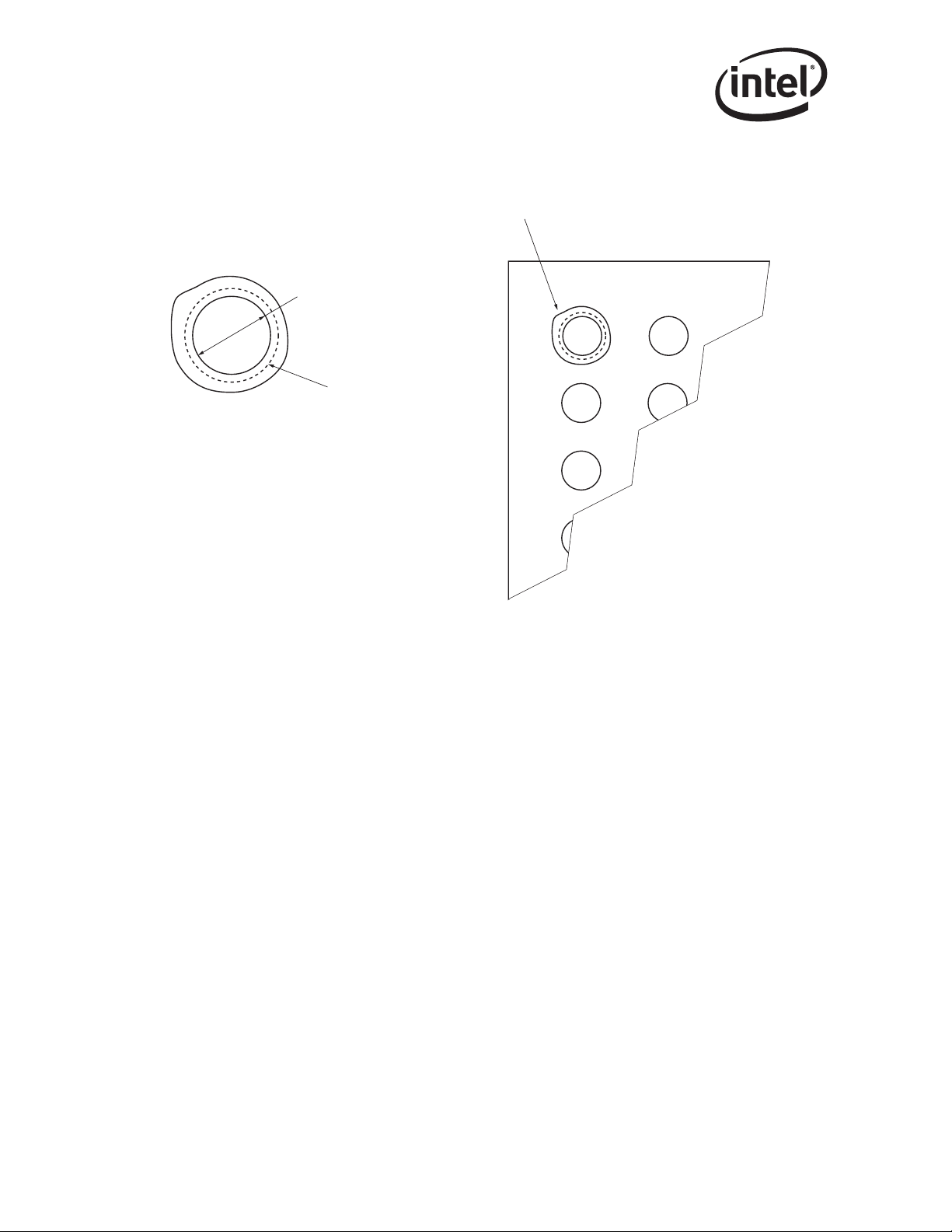

Oct 2006 2.6 • Added Figure 28 “196 PBGA Package Pad Detail”. The figure shows solder

resist opening and metal diameter dimensions.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to the m.

The 82551ER may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current

characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled

platforms may require licenses from various entities, including Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's Web site at http://www.intel.com.

®

Intel

is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2006, Intel Corporation.

* Other product and corporate names may be trademarks of other companies and are used only for explanation and to the owners’ benefit, without

intent to infringe.

ii Datasheet

Page 3

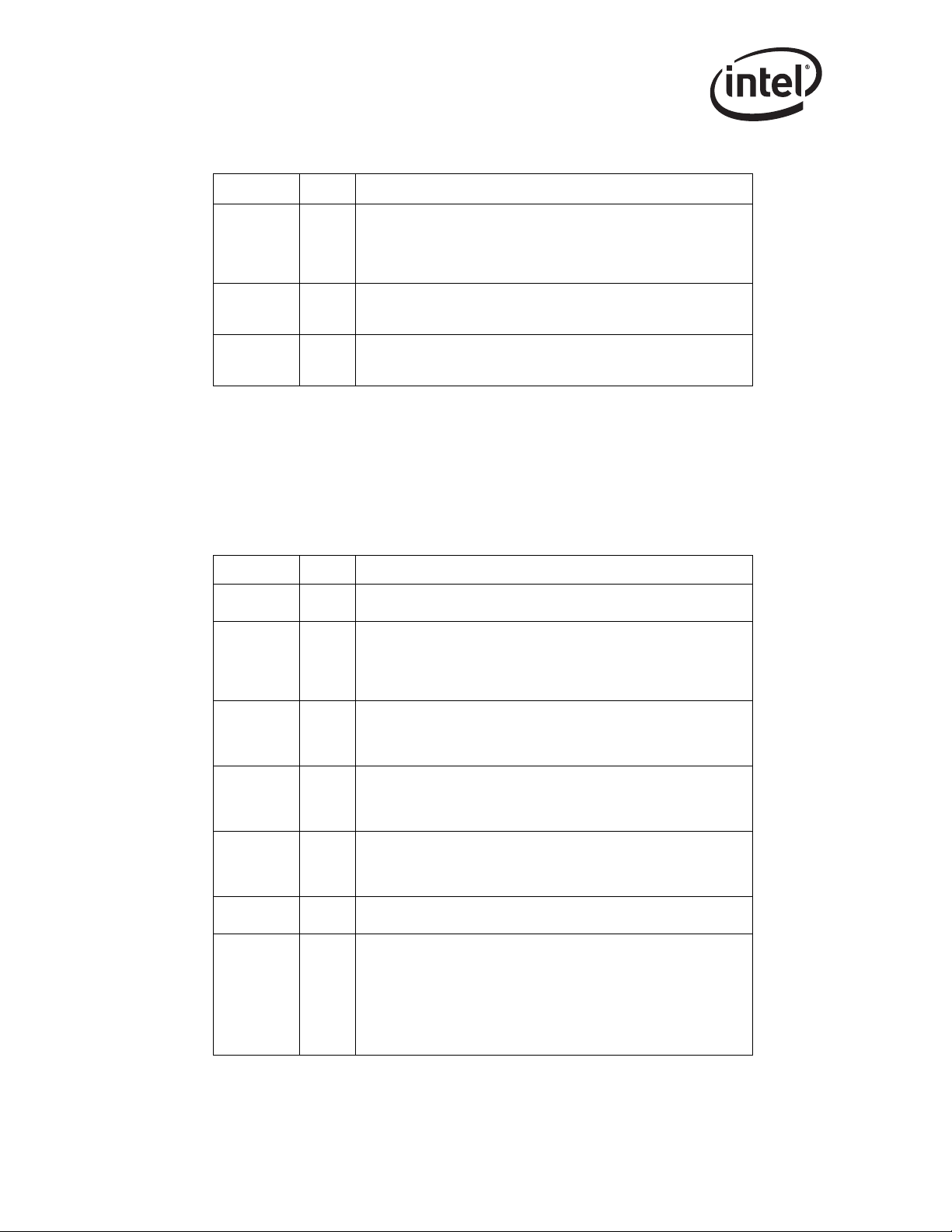

Networking Silicon — 82551ER

Contents

1.0 Introduction.........................................................................................................................1

1.1 Overview ...............................................................................................................1

1.2 Byte Ordering ........................................................................................................1

1.3 References............................................................................................................1

1.4 Product Codes.......................................................................................................2

2.0 Architectural Overview .......................................................................................................3

2.1 Parallel Subsystem Overview................................................................................3

2.2 FIFO Subsystem Overview ...................................................................................3

2.3 10/100 Mbps Serial CSMA/CD Unit Overview ......................................................4

2.4 10/100 Mbps Physical Layer Unit..........................................................................4

3.0 Performance Enhancements..............................................................................................5

3.1 Multiple Priority Transmit Queue s ......................................... ....... ...... ...................5

3.2 Early Release........................................................................................................5

3.3 Hardware Integrity Support ...................................................................................6

3.4 Management Data Interface MDI/MDI-X Feature..................................................6

4.0 Signal Descriptions.............................................................................................................7

4.1 Signal Type Definitions .........................................................................................7

4.2 PCI Bus Interface Signals .....................................................................................8

4.2.1 Address and Data Signals .......................................................................8

4.2.2 Interface Control Signals .........................................................................8

4.2.3 System and Power Management Signals ...............................................9

4.3 Local Memory Interface Signals..........................................................................10

4.4 Test Port Signals ................................................................................................11

4.5 PHY Signals .. ....... ...... ....... ...... ....... ...... ...... ....................................... ....... ...... ....12

4.6 Power and Ground Signals .................................................................................13

5.0 Media Access Control Functional Description..................................................................15

5.1 Device Initialization..............................................................................................15

5.1.1 Initialization Effects.................................................................................15

5.2 PCI Interface .......................................................................................................16

5.2.1 Bus Operations.......................................................................................16

5.2.2 Clock Run Signal................ ...... ...... ....... ...... ....... ...... ....... .......................24

5.2.3 Power Management Event.....................................................................25

5.3 PCI Power Management .....................................................................................25

5.3.1 Power States..........................................................................................25

5.3.2 Wake-up Events................. ...... ...... ....... ...... ....... ...... ....... .......................29

5.4 Parallel Flash.......................................................................................................30

5.5 Serial EEPROM Interface....................................................................................30

5.5.1 EEPROM Address Map..........................................................................32

5.6 10/100 Mbps CSMA/CD Unit...............................................................................32

5.6.1 Full Duplex .............................................................................................33

5.6.2 Flow Control ...........................................................................................33

5.6.3 Address Filtering Modifications ..............................................................33

5.6.4 VLAN Support ........................................................................................33

Datasheet iii

Page 4

82551ER — Networking Silicon

5.7 Media Independent Interface (MII) Management Interface.................................34

6.0 Physical Layer Functional Description .............................................................................35

6.1 100BASE-TX PHY Unit.......................................................................................35

6.1.1 100BASE-TX Transmit Clock Generation..............................................35

6.1.2 100BASE-TX Transmit Blocks...............................................................35

6.1.3 100BASE-TX Receive Blocks................................................................35

6.1.4 100BASE-TX Link Integrity Auto-Negotiation.........................................36

6.2 10BASE-T PHY Functions..................................................................................36

6.2.1 10BASE-T Transmit Clock Generation...................................................36

6.2.2 10BASE-T Transmit Blocks....................................................................36

6.2.3 10BASE-T Receive Blocks.....................................................................36

6.2.4 10BASE-T Link Integrity and Full Duplex...............................................37

6.3 Auto-Negotiation .................................................................................................37

6.3.1 Description .............................................................................................37

6.3.2 Parallel Detect and Auto-Negotiation.....................................................37

6.4 LED Description .................................................... ...... ....... ...... ....... ...... ....... ...... .38

7.0 Configuration Registers....................................................................................................41

7.1 Function 0: LAN (Ethernet) PCI Configuration Space.........................................41

7.1.1 PCI Vendor ID and Device ID Registers ................................................41

7.1.2 PCI Command Register .........................................................................42

7.1.3 PCI Status Register................................................................................43

7.1.4 PCI Revision ID Register........................................................................45

7.1.5 PCI Class Code Register .......................................................................45

7.1.6 PCI Cache Line Size Register................................................................45

7.1.7 PCI Latency Timer .................................................................................45

7.1.8 PCI Header Type ...................................................................................45

7.1.9 PCI Base Address Registers..................................................................46

7.1.10 Base Address Registry Summary ..........................................................47

7.1.11 PCI Subsystem Vendor ID and Subsystem ID Registers.......................47

7.1.12 Capability Pointer ...................................................................................48

7.1.13 Interrupt Line Register............................................................................48

7.1.14 Interrupt Pin Register .............................................................................48

7.1.15 Minimum Grant Register ........................................................................49

7.1.16 Maximum Latency Register...................... ...... ....... ...... ....... ...... ....... ...... .49

7.1.17 Capability ID Register ............................................................................49

7.1.18 Next Item Pointer ...................................................................................49

7.1.19 Power Management Capabilities Register .............................................49

7.1.20 Power Management Control/Status Register (PMCSR).........................50

7.1.21 Data Register ................................................. ....... ...... ....... ...... ....... ...... .51

8.0 Control/Status Registers..................................................................................................53

8.1 LAN (Ethernet) Control/Status Registers ............................................................53

8.1.1 System Control Block Status Word........................................................54

8.1.2 System Control Block Command Word..................................................55

8.1.3 System Control Block General Pointer...................................................55

8.1.4 PORT .....................................................................................................55

8.1.5 Flash Control Register ...........................................................................55

8.1.6 EEPROM Control Register....................... ...... ....... ...... ....... ...... ....... .......56

8.1.7 Management Data Interface Control Register........................................56

iv Datasheet

Page 5

Networking Silicon — 82551ER

8.1.8 Receive Direct Memory Access Byte Count...........................................56

8.1.9 Flow Control Register.............................................................................56

8.2 Statistical Counters .............................................................................................57

9.0 PHY Unit Registers ...................................... ...... ...... ....................................... ....... ...... ....61

9.1 MDI Registers 0 - 7 .............................................................................................61

9.1.1 Register 0: Control Register ..................................................................61

9.1.2 Register 1: Status Register ...................................................................62

9.1.3 Register 2: PHY Identifier Register .......................................................63

9.1.4 Register 3: PHY Identifier Register .......................................................63

9.1.5 Register 4: Auto-Negotiation Advertisement Register ...........................63

9.1.6 Register 5: Auto-Negotiation Link Partner Ability Register ....................64

9.1.7 Register 6: Auto-Negotiation Expansion Register .................................64

9.2 MDI Registers 8:15..............................................................................................64

9.3 MDI Register 16:31 .............................................................................................65

9.3.1 Register 16: PHY Unit Status and Control Register ..............................65

9.3.2 Register 17: PHY Unit Special Control Register ...................................65

9.3.3 Register 18: PHY Address Register.......................................................66

9.3.4 Register 19: 100BASE-TX Receive False Carrier Counter ...................66

9.3.5 Register 20: 100BASE-TX Receive Disconnect Counter ......................67

9.3.6 Register 21: 100BASE-TX Receive Error Frame Counter ....................67

9.3.7 Register 22: Receive Symbol Error Counter .........................................67

9.3.8 Register 23: 100BASE-TX Receive Premature End of Frame Error

Counter 67

9.3.9 Register 24: 10BASE-T Receive End of Frame Error Counter .............67

9.3.10 Register 25: 10BASE-T Transmit Jabber Detect Counter .....................68

9.3.11 Register 26: Equalizer Control and Status Register ..............................68

9.3.12 Register 27: PHY Unit Special Control Register ...................................68

9.3.13 Register 28: MDI/MDI-X Control Register ..............................................69

9.3.14 Register 29: Hardware Integrity Control Register ..................................69

10.0 82551ER Test Port Functionality ..... ...................................... ....... ...... ....... ...... ....... ...... ....71

10.1 Introduction..........................................................................................................71

10.2 Test Function Description....................................................................................71

10.2.1 Tristate ...................................................................................................71

10.2.2 XOR Tree ...............................................................................................72

11.0 Electrical and Timing Specifications.................................................................................75

11.1 Absolute Maximum Ratings.................................................................................75

11.2 DC Specifications .................... ....... ...... ...... ....... ...... ....... ...... ..............................76

11.3 AC Specifications ................................................................................................80

11.4 Timing Specifications ..........................................................................................81

11.4.1 Clocks Specifications .............................................................................81

11.4.2 Timing Parameters.................................................................................82

12.0 Package and Pinout Information......................................................................................89

12.1 Package Information ...........................................................................................89

12.2 Pinout Information ...............................................................................................91

12.2.1 Pin Assignments ....................................................................................91

12.2.2 Ball Grid Array Diagram .........................................................................93

Datasheet v

Page 6

82551ER — Networking Silicon

Figures

1 CSR I/O Read Cycle ...........................................................................................17

2 CSR I/O Write Cycle ...........................................................................................18

3 Flash Buffer Read Cycle.....................................................................................19

4 Flash Buffer Write Cycle .....................................................................................20

5 PCI Retry Cycle...................................................................................................21

6 Memory Read Burst Cycle ..................................................................................22

7 Memory Write Burst Cycle ..................................................................................22

8 Initialization upon RST# and ISOLATE#.............................................................28

9 64-Word EEPROM Read Instruction Waveform .................................................31

10 Auto-Negotiation and Parallel Detect..................................................................38

11 Two and Three LED Schematic Diagram............................................................39

12 PCI Configuration Registers................................................................................41

13 PCI Command Register ......................................................................................42

14 PCI Status Register.............................................................................................43

15 Cache Line Size Register....................................................................................45

16 Base Address Register for Memory Mapping .....................................................46

17 Base Address Register for I/O Mapping..............................................................46

18 Control/Status Register.......................................................................................53

19 PCI Clock Waveform...........................................................................................81

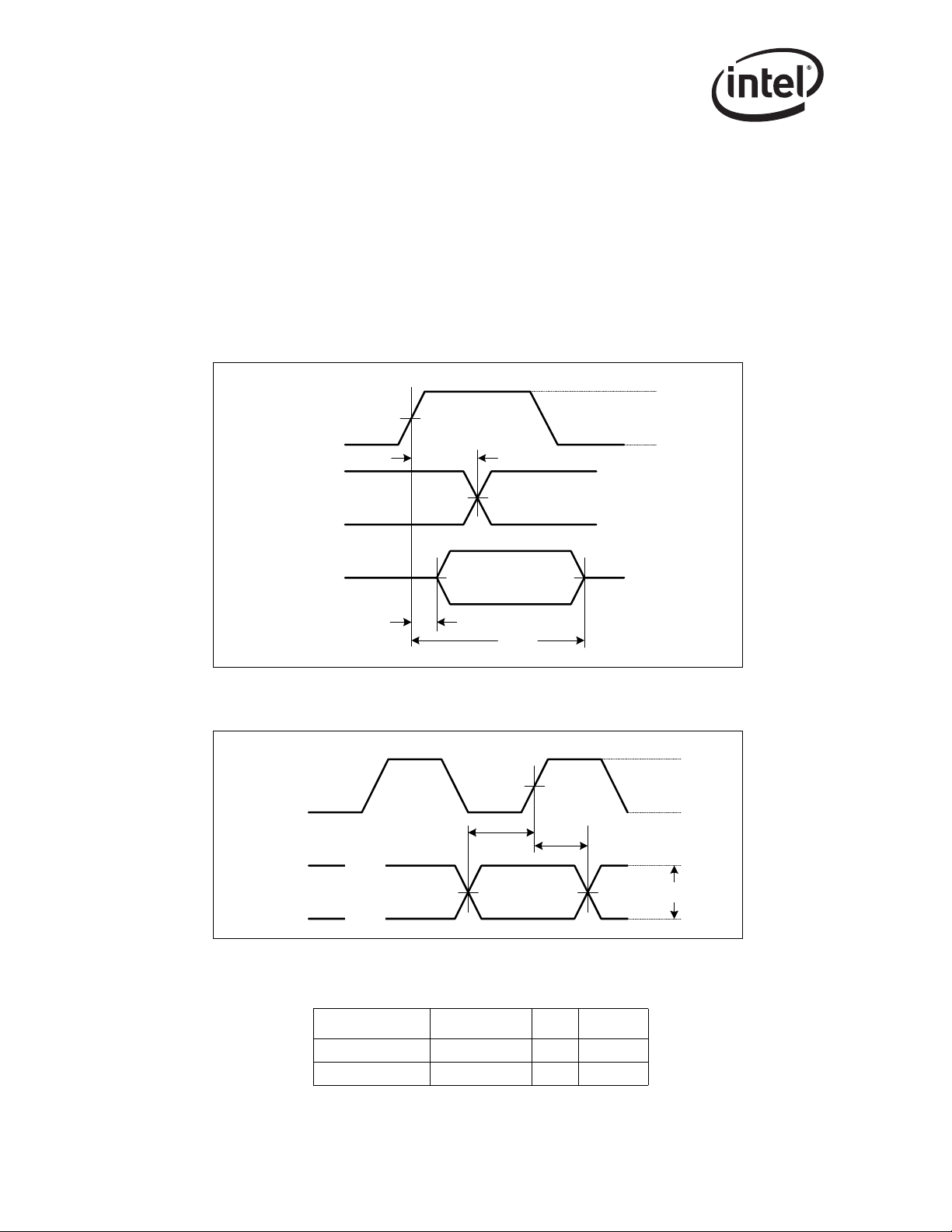

20 Output Timing Measurement Conditions.............................................................82

21 Input Timing Measurement Conditions ...............................................................82

22 Flash Timings for a Read Cycle..........................................................................85

23 Flash Timings for a Write Cycle..........................................................................85

24 EEPROM Timings................. ...... ....... ...... ...... ....... ...... ....... ...... ....... ...... ....... .......86

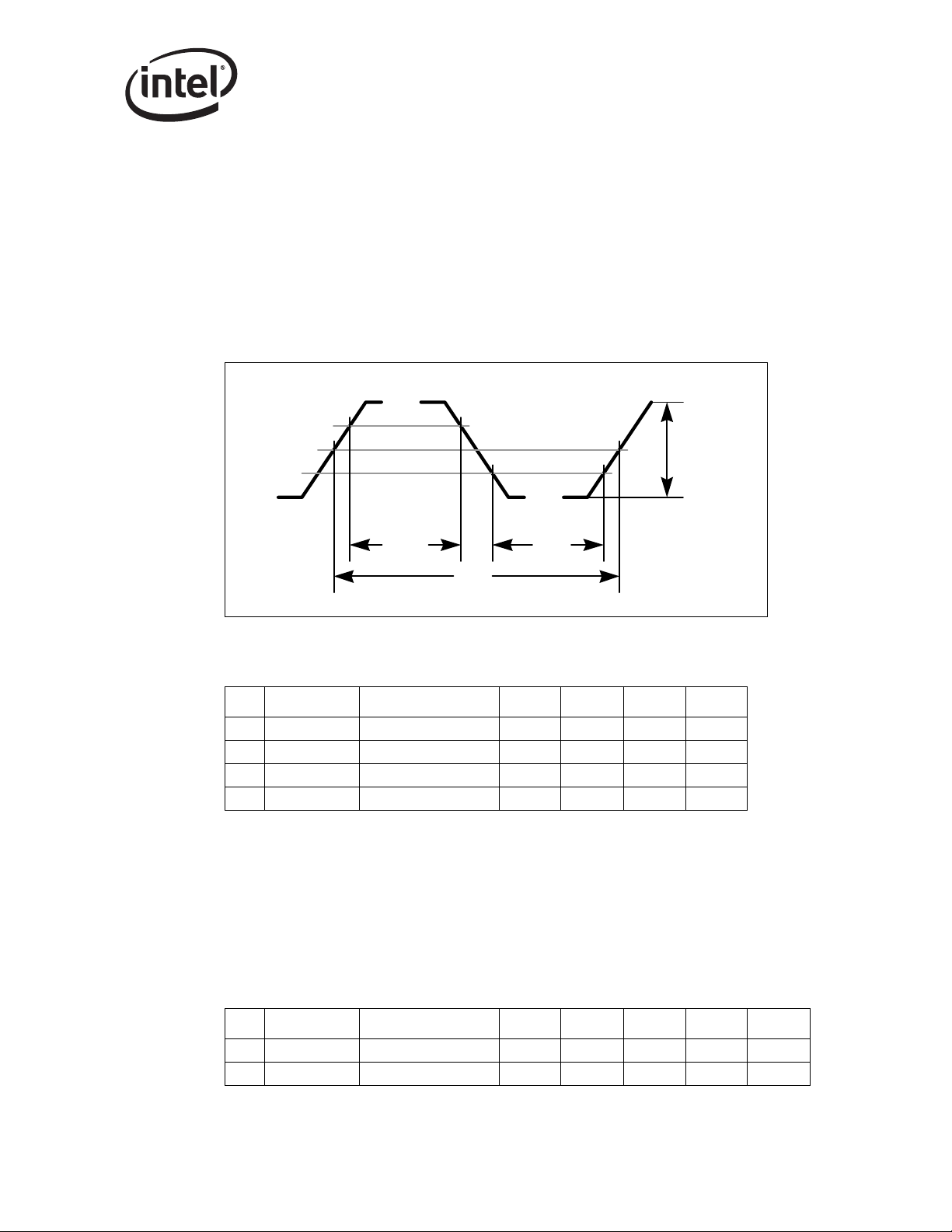

25 10BASE-T Normal Link Pulse (NLP) Timings .....................................................87

26 Auto-Negotiation Fast Link Pulse (FLP) Timings................................................87

27 Dimension Diagram for the 196-pin BGA............................................................89

28 196 PBGA Package Pad Detail...........................................................................90

29 Ball Grid Array Diagram ......................................................................................93

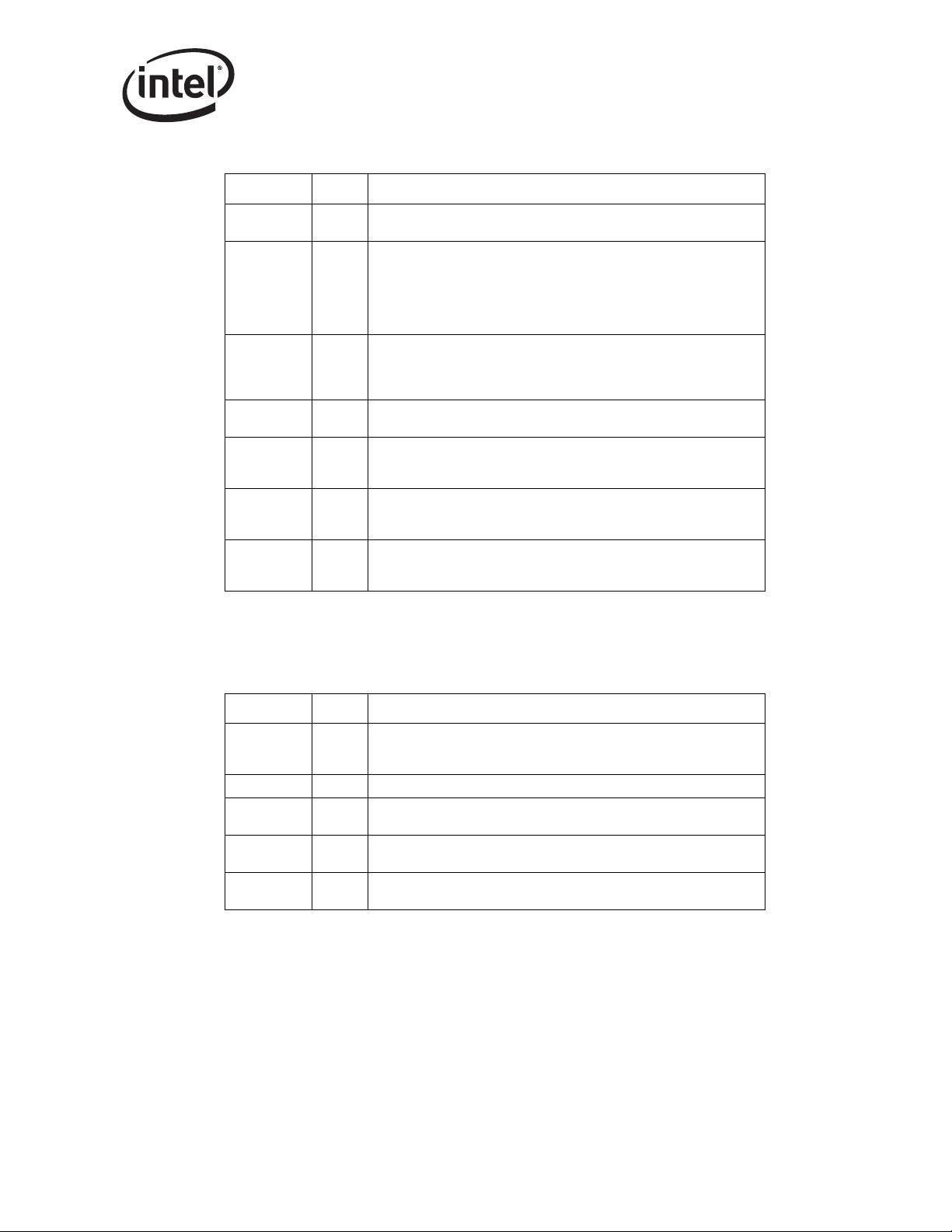

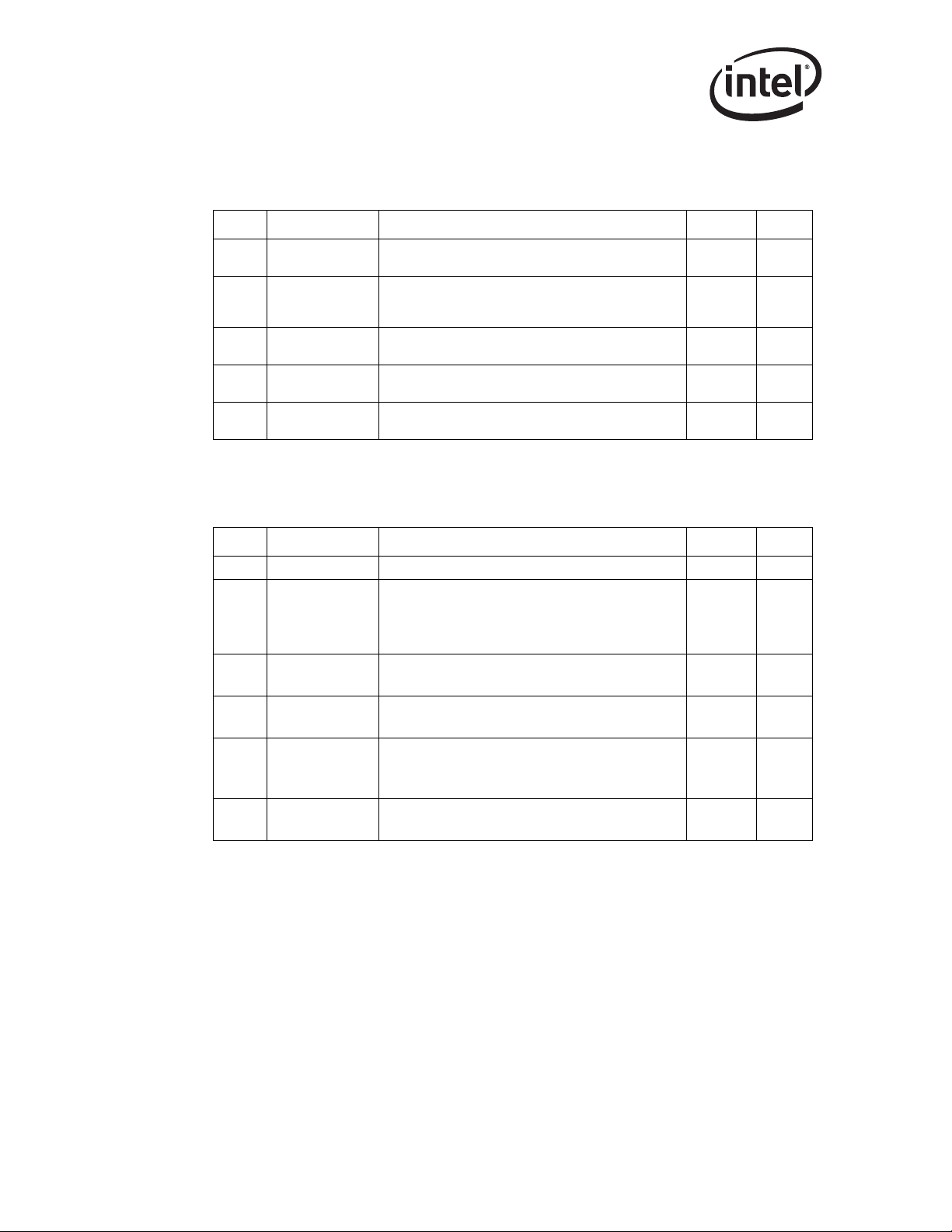

Tables

1 RJ-45 Connections................................................................................................6

2 Signal Type Descriptions ......................................................................................7

3 Address and Data Signals.....................................................................................8

4 Interface Control Signals.......................................................................................8

5 System and Power Management Signals .............................................................9

6 Local Memory Interface Signals..........................................................................10

7 Test Port Signals...... ...... ....... ...... ....... ...... ....................................... ...... ....... ...... .11

8 PHY Signals........................................................................................................12

9 Power and Ground Signals.................................................................................13

10 Initialization Effects .............................................................................................15

11 Functionality at the Different Power States.........................................................29

12 82551ER EEPROM Address Map ......................................................................32

13 PCI Command Register Bits...............................................................................43

14 PCI Status Register Bits......................................................................................44

15 Base Address Register Functions.......................................................................47

vi Datasheet

Page 7

Networking Silicon — 82551ER

16 ID Fields Programming ....... ...... ....... ...... ...... ....................................... ....... ...... ....48

17 Power Management Capability Register.............................................................49

18 Power Management Control and Status Register...............................................50

19 Ethernet Data Register........................................................................................51

20 System Control Block Status Word .....................................................................54

21 System Control Block Command Word...............................................................55

22 MDI Control Register...........................................................................................56

23 Statistical Counters .............................................................................................57

24 Register 0: Control ..............................................................................................61

25 Register 1: Status................................................................................................62

26 Register 2: PHY Identifier....................................................................................63

27 Register 3 PHY Identifier.....................................................................................63

28 Register 4: Auto-Negotiation Advertisement .......................................................63

29 Auto-Negotiation Link Partn er Abil ity........................ ....... ...... ....... ...... ....... ...... ....64

30 Register 6: Auto-Negotiation Expansion .............................................................64

31 PHY Unit Status and Control...............................................................................65

32 Register 17: PHY Unit Special Control................................................................65

33 Register 18: PHY Address ..................................................................................66

34 Register 19: 100BASE-TX Receive False Carrier Counter.................................66

35 Register 20: 100BASE-TX Receive Disconnect Counter....................................67

36 Register 21: 100BASE-TX Receive Error Frame Counter ..................................67

37 Register 22: Receive Symbol Error Counter .......................................................67

38 Register 23: 100BASE-TX Receive Premature End of Frame Error Counter .....67

39 Register 24: 10BASE-T Receive End of Frame Error Counter ...........................67

40 Register 25: 10BASE-T Transmit Jabber Detect Counter...................................68

41 Register 26: Equalizer Control and Status ..........................................................68

42 Register 27: PHY Unit Special Control................................................................68

43 Register 28: MDI/MDI-X Control..........................................................................69

44 Register 29: Hardware Integrity Control..............................................................69

45 XOR Tree Chains................................................................................................72

46 General DC Specifications ....................................... ....... ...... ....... ...... ....... ..........76

47 PCI Interface DC Specifications..........................................................................77

48 Flash/EEPROM Interface DC Specifications.......................................................77

49 LED Voltage/Current Characteristics ..................................................................78

50 100BASE-TX Voltage/Curren t Char ac teristi cs......... ....... ...... ..............................78

51 10BASE-T Voltage/Current Characteristics ........................................................79

52 AC Specifications for PCI Signaling ....................................................................80

53 PCI Clock Specifications.....................................................................................81

54 X1 Clock Specifications.......................................................................................81

55 Measure and Test Condition Parameters............................................................82

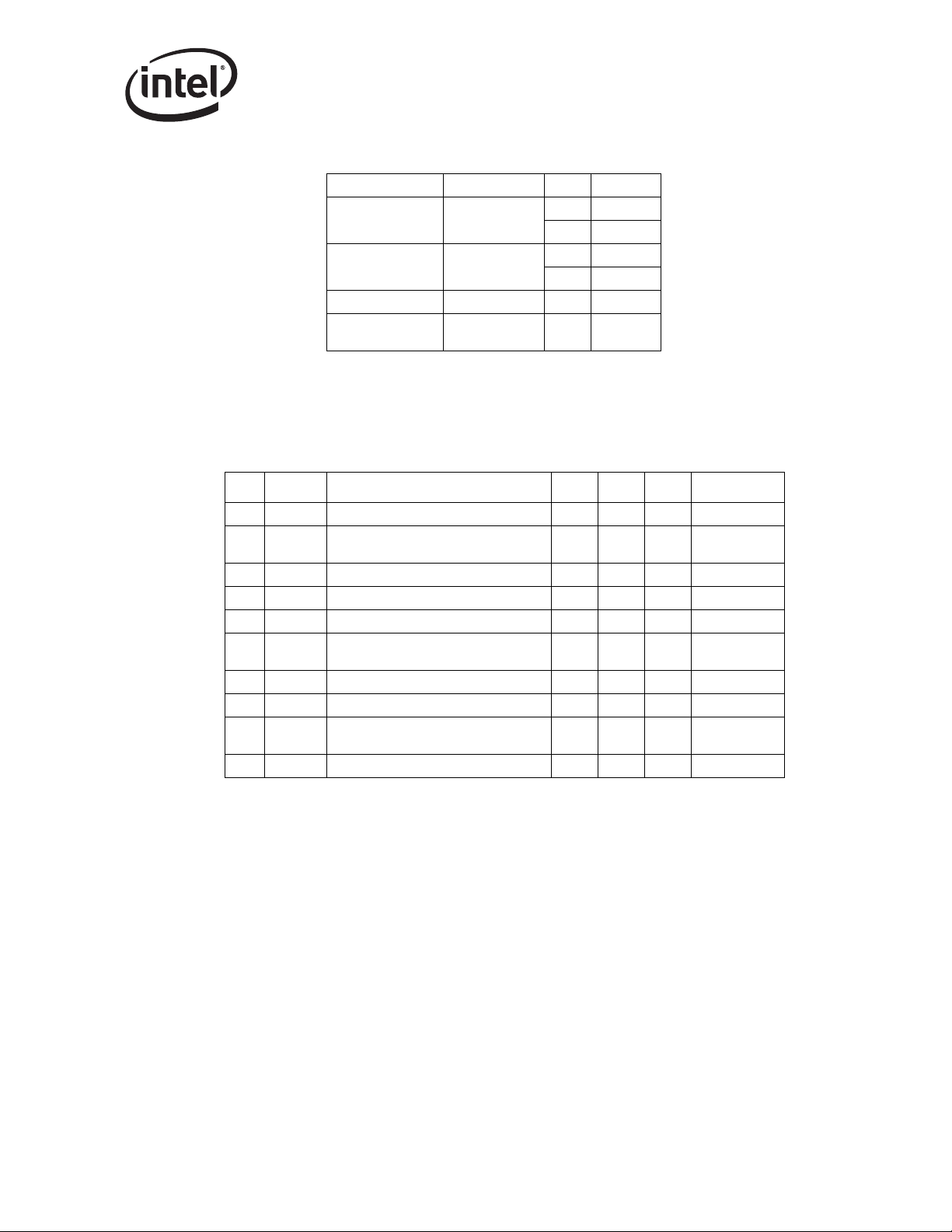

56 PCI Timing Parameters.......................................................................................83

57 Flash Timing Parameters ....................................................................................84

58 EEPROM Timing Parameters .............................................................................86

59 10BASE-T Normal Link Pulse (NLP) Timing Parameters ...................................87

60 Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters...............................87

61 100Base-TX Transmitter AC Specification..........................................................88

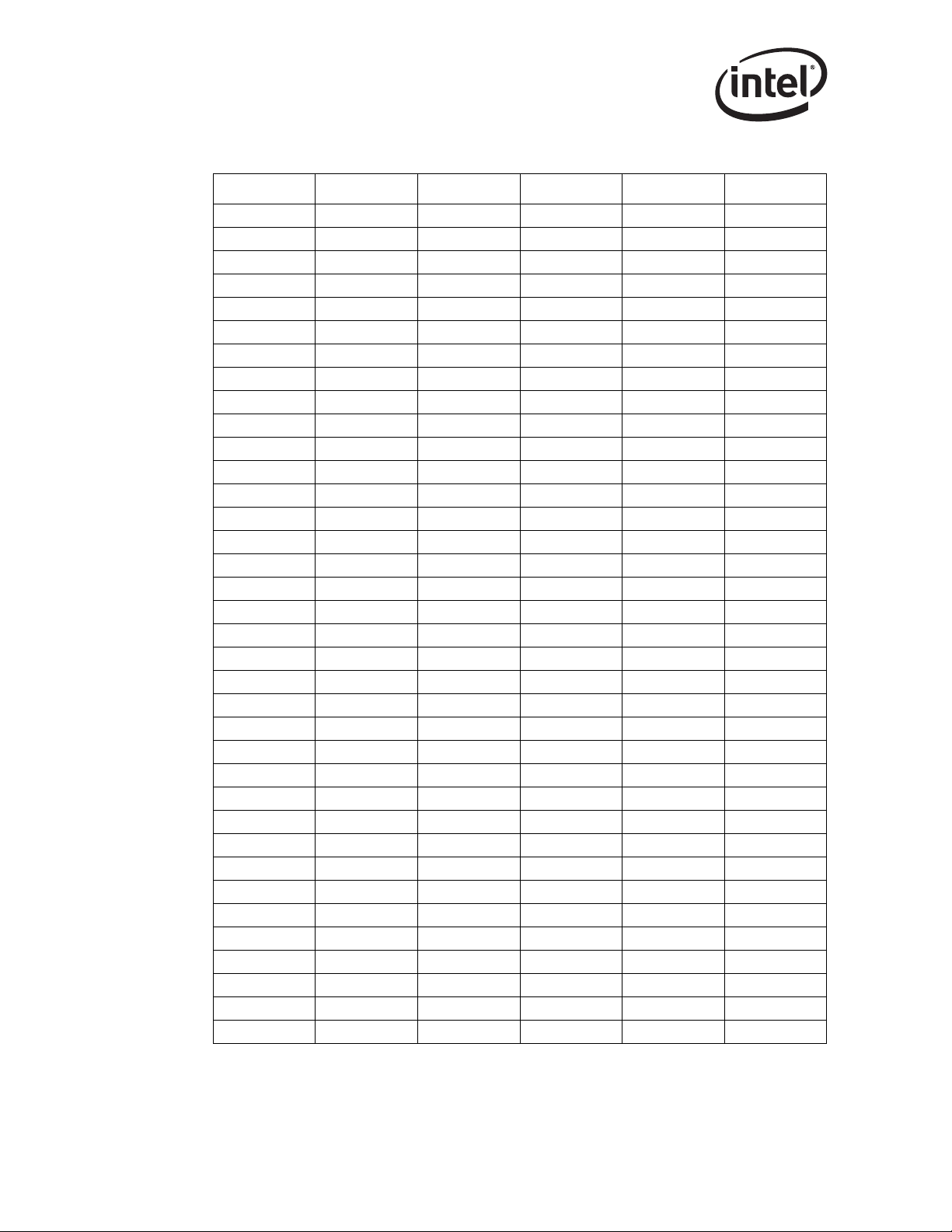

62 Pin Assignments..................................................................................................91

Datasheet vii

Page 8

82551ER — Networking Silicon

Note: This page intentionally left blank.

viii Datasheet

Page 9

1.0 Introduction

This datasheet is applicable to the Intel® 82551ER Fast Ethernet PCI Controller, a member of the

8255x Fast Ethernet Controller family.

1.1 Overview

The 82551ER is an evolutionary addition to Intel’s family of 8255x controllers. It provides

excellent performance by of floa ding TCP, UDP and IP checksums and sup ports TCP segmenta tion

off-load for operations such as Large Send.

Its optimized 32-bit interface and efficient scatter-gather bus mastering capabilities enable the

82551ER to perform high speed data transfers over the PCI bus. This capab ility accelerates the

processing of high level commands and operations, which lowers CPU utilization. Its architecture

enables data to flow efficiently from the bus interface unit to the 3 KB Transmit and Receive

FIFOs, providing the perfect balance between the wire and system bus. In addition, multiple

priority queues are provided to prevent data underruns and overruns.

The 82551ER includes both a MAC and PHY. In also has a simple interf ace to the analog front end,

which allows cost effective designs requiring minimal board real estate. The 82551ER is pin

compatible with the 82559 family of controllers and is offered with software that provides

backwards compatibility with previous 82559ER controllers.

Networking Silicon — 82551ER

1.2 Byte Ordering

TCP and IP Internet Engineering Task Force (IETF) Request for Comments (RFCs) and literature

use big endian (BE) byte ordering. This document uses big endian ordering for all IP and TCP

frame formats. However, little endian byte ordering is used for referencing 82551ER memory

resident structures and internal structures.

1.3 References

The following documents may provide further information on topics discussed in this document.

• 10/100 Mbit Ethernet Controller Family Software Deve loper’s Manual. Intel Corporation.

• Advanced Configuration and Power Interface Specification, Revision 1.0. Intel Corporation,

Microsoft Corporation, and Toshiba.

• IEEE 802.3x and 802.1y Standards.

• Network Device Class Power Management Reference Specification, Revision 1.0a. AMD, Inc.

and Microsoft Corporation.

Datasheet 1

Page 10

82551ER — Networking Silicon

1.4 Product Codes

Product ordering codes for the 82551ER Fast Ethernet PCI controller:

• GD82551ER

• LU82551ER

2 Datasheet

Page 11

2.0 Architectural Overview

The Intel® 82551ER is di vided int o four m ain subs ystems : a parall el subs ystem, a FIFO subsystem ,

a 10/100 Mbps Carrier Sense Multiple Access with Collision Detect (CSMA/CD) unit, and a 10/

100 Mbps physical layer (PHY) unit.

2.1 Parallel Subsystem Ove rview

The parallel subsystem is comprised of several functional blocks: a PCI bus master interface, a

micromachine processing unit and its corresponding microcode ROM, and a PCI Target Control/

Flash/EEPROM interface. The parallel subsystem also interfaces to the FIFO subsystem, passing

data (such as transmit, receive, and configuration data) and command and status parameters

between these two blocks.

The PCI bus master interface provides a complete glueless interface to a PCI bus and is compliant

with the PCI Bus Specification, Revision 2.2. The 82551ER provides 32 bits of addressing and

data, as well as the PCI control interface. As a PCI target, it conforms to the PCI configuration

scheme, which allows all accesses to the 82551ER to be automatically mapped into free memory

and I/O space upon initialization of a PCI system. When transmit and receive data is pr ocessed, the

82551ER operates as a master on the PCI bus, initiating zero wait state transfers.

Networking Silicon — 82551ER

The 82551ER Control/Status Register Block is part of the PCI target element. The Control/Status

Register block consists of the following 82551ER internal control registers: System Control Block

(SCB), PORT, Flash Control, EEPROM Control, and Management Data Interface (MDI) Control.

An embedded micromachine consisting of independent transmit and receive processing units allow

the 82551ER to execute commands and receive incoming frames with no real time CPU

intervention.

The 82551ER contains a multiplexed interface to connect an external serial EEPROM and Flash

memory. The Flash interface, which can also be used to connect to any standard 8-bit device,

provides up to 128 KB of addressing to the Flash. Both read and write accesse s are supported. The

Flash can be used for remote boot functions, network statistical and diagnostics functions, and

management functions. The Flash is mapped into host system memory (anywhere within the 32-bit

memory address space) for software accesses. It is also mapped into an available boot expansion

ROM location during boot time of the system. More information on the Flash interface is detailed

in Section 5.4, “Parallel Flash”. The serial EEPROM is used to store relevant information for a

LAN connection such as node address, as well as board manufacturing and configuration

information. Both read and write accesses to the EEPROM are supported by the 82551ER.

Information on the EEPROM interface is detailed in Section 5.5, “Serial EEPROM Interface”.

2.2 FIFO Subsystem Overview

The 82551ER FIFO subsystem consists of independent 3 KB transmit and receive FIFOs. Each

FIFO provides a temporary buffer for frames as they are transmitted or received. Transmit frames

queued within the transmit FIFO allow back-to-back transmissio n within the minimum Interframe

Spacing (IFS). The FIFOs allow the 82551ER to withstand long PCI bus latencies without losing

incoming data. Additional attributes of the FIFOs that enhance performance and functionality are:

Datasheet 3

Page 12

82551ER — Networking Silicon

• Tunable transmit FIFO threshold allows elimination of underruns while concurrent transmits

are being performed.

• Extended PCI zero wait state burst accesses to and from the 82551ER for both transmit and

receive FIFOs

• Efficient re-transmission of da ta directly from the transmit FIFO when physical or data link

errors (collision detection or data underrun) are encountered, increasing performance by

eliminating the need to re-access the data from host memory

• Automatic discard of incoming runt receive frames

2.3 10/100 Mbps Seri al CSMA/CD Unit Over view

The 82551ER’s CSMA/CD unit allows it to be connected to a 10 or 1 00 Mb ps Et hern et net work at

half or full duplex. The CSMA/CD unit performs all of the functions of the 802.3 protocol such as

frame formatting, frame stripping, collision handling, deferral to link traffic, etc.

2.4 10/100 Mbps Physical Layer Unit

The integrated Physical Layer (PHY) unit of the 82551ER allows connection to either a 10 or 100

Mbps Ethernet network. The PHY supports Auto-Negotiation for 100BASE-TX Full Duplex,

100BASE-TX Half Duplex, 10BASE-T Full Duplex, and 10BASE-T Half Duplex. Three LED

pins indicate link status, network activity, and speed.

4 Datasheet

Page 13

3.0 Performance Enhancements

All of Intel’s Fast Ethernet controllers have the ability to support full wire speeds. The 82551ER

has been designed to provide improved networking throughput. Performance is limited to the

system’s ability to feed data to the network controller.

As networks grow, the task of servicing the network becomes a large burden on the platform.

System bottlenecks prevent optimal performance in typical operating conditions. Thus, to help

alleviate these issues, Network Operating System (NOS) vendors ar e establishing normali zed offload specifications. These specifications define the types of off-load support required by the OS

and interface between the network drivers. The 825 51ER pr ovides support for these initiatives and

enables an improvement in platform network efficiency. With the pervasiveness of Internet

Protocols, the off-load capabilities have focused on improving IP efficiency. As part of this effort,

the 82551ER includes support for Multiple Priority Transmit Queues.

3.1 Multiple Priority Transmit Queues

The 82551ER supports two queues: High Priority Queue (HPQ) and Low Priority Queue (LPQ).

The 82551ER provides a method for the driver to modify the HPQ while processing data. A new

read only register is defined in the Control/Status Register (CSR) that enables the driver to change

the transmit priority of elements within the HPQ. When software reads this register, the address of

the next Command Block to be processed by the 82551ER on the HPQ is returned. After reading

this register, software can freely modify the next Command Block (for example, ov erwrite it with a

different Command Block) and any subsequent Command Block, without any conflict with the

82551ER.

Networking Silicon — 82551ER

Note: The 82551ER Windows* driver supports the Command Block Pointer register (in the CSR).

3.2 Early Release

Like the 82558, 82559 and 82550, the 82551ER supports a 3 KB transmit FIFO. The 82551ER

provides a transmit FIFO enhancement called “early release” that effectively increases the amount

of free capacity in the transmit FIFO. The enabling of early release is controlled through

configuration space and occurs when the following conditions are met:

1. The transmitted frame is the oldest one in the queue (in other words, it is located at the head of

the queue).

2. The transmitted frame has been completely transferred to the XMT-SRAM and processed (for

example, XSUM). Large frames (greater than 3 KB) are never candidates for an early release.

3. When the preemptive queue mechanism is on, a frame which satisfies condition 2 may not

satisfy condition 1 and therefore will not benefit from an early release.

4. More than 128 bytes have already been transferred to the XMT- SYNC-FIFO. This condition

guarantees that at least one slot time elapsed (collision window).

Datasheet 5

Page 14

82551ER — Networking Silicon

3.3 Hardware Integrity Support

Cabling problems are a common cause for network dow ntime situations. Hardware Integrity

(HWI) can help reduce this by locating cabling problems. It uses transmission line theory to

measure the arrival time and electrical characteristics of the wave reflected from an incident test

wave launched on the media. With these measurements, opens, shorts, and degraded cable quality

can be located along the wire.

HWI is controlled and activated by software. The Hardware Integrity Control, register 29 of the

MDI Registers, is used for activating HWI (Section 9.3.14, “Register 29: Hardware Integrity

Control Register”).

3.4 Management Data Interface MDI/MDI-X Feature

The 82551ER controller MDI/MDI-X feature provides the ability to automatically detect the

required cable connection type and configure the controller-side MAU to the cable type. This

feature effectively allows all properly wired Ethernet cables usable with any Ethernet device to be

connected to the 82551ER without any additional external logic.

This advanced feature enables auto-correction of incorrect cabling with respect to cross-over

versus straight-through cables. The 82551ER can identify the cable connection type and adjust its

MDI port to the cable by switching between the TD and RD pairs. The auto-switching is done prior

to the start of the hardware auto negotiation algorithm.

In a standard straight -through RJ -45 port co nfigurati on, the tran smit pai r is on contact s 1 and 2, and

the receive pair on contacts 3 and 6. These are defined by Clause 23.7.1 of the IEEE 802.3u

standard.

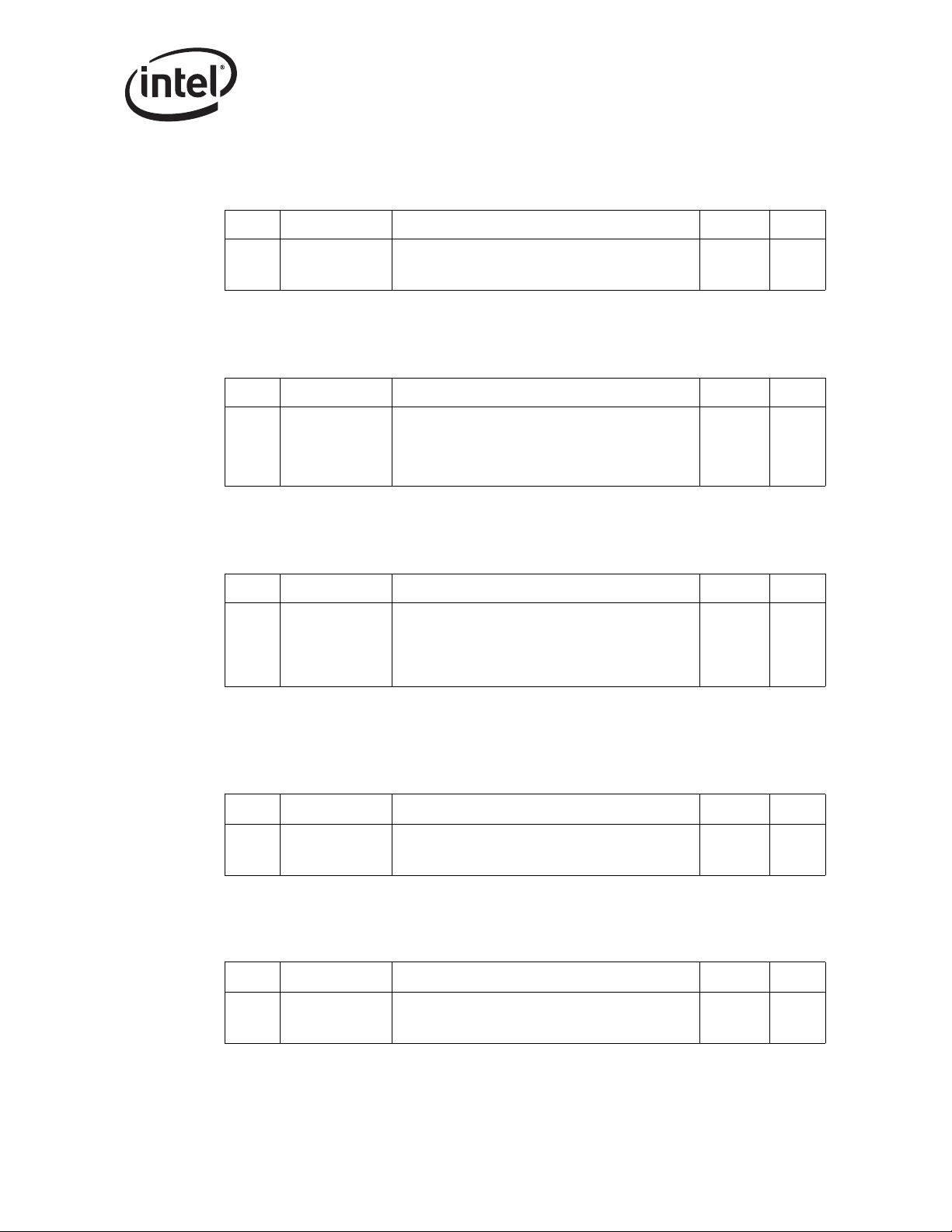

Table 1 lists the connections for both straight-through and cross-over RJ-45 ports for comparison.

Table 1. RJ-45 Connections

RJ-45

Contact

1 TD+ RD+

2 TD- RD3RD+ TD+

4 Not Used Not Used

5 Not Used Not Used

6RD- TD7 Not Used Not Used

8 Not Used Not Used

a. Straight-through connections us ed on DTE applications.

b. Cross-over connections used on Hub and Switch applications.

Straight-Through

MDI Signal

a

Cross-Over MDIX

Signal

b

6 Datasheet

Page 15

4.0 Signal Descriptions

4.1 Signal Type Definitions

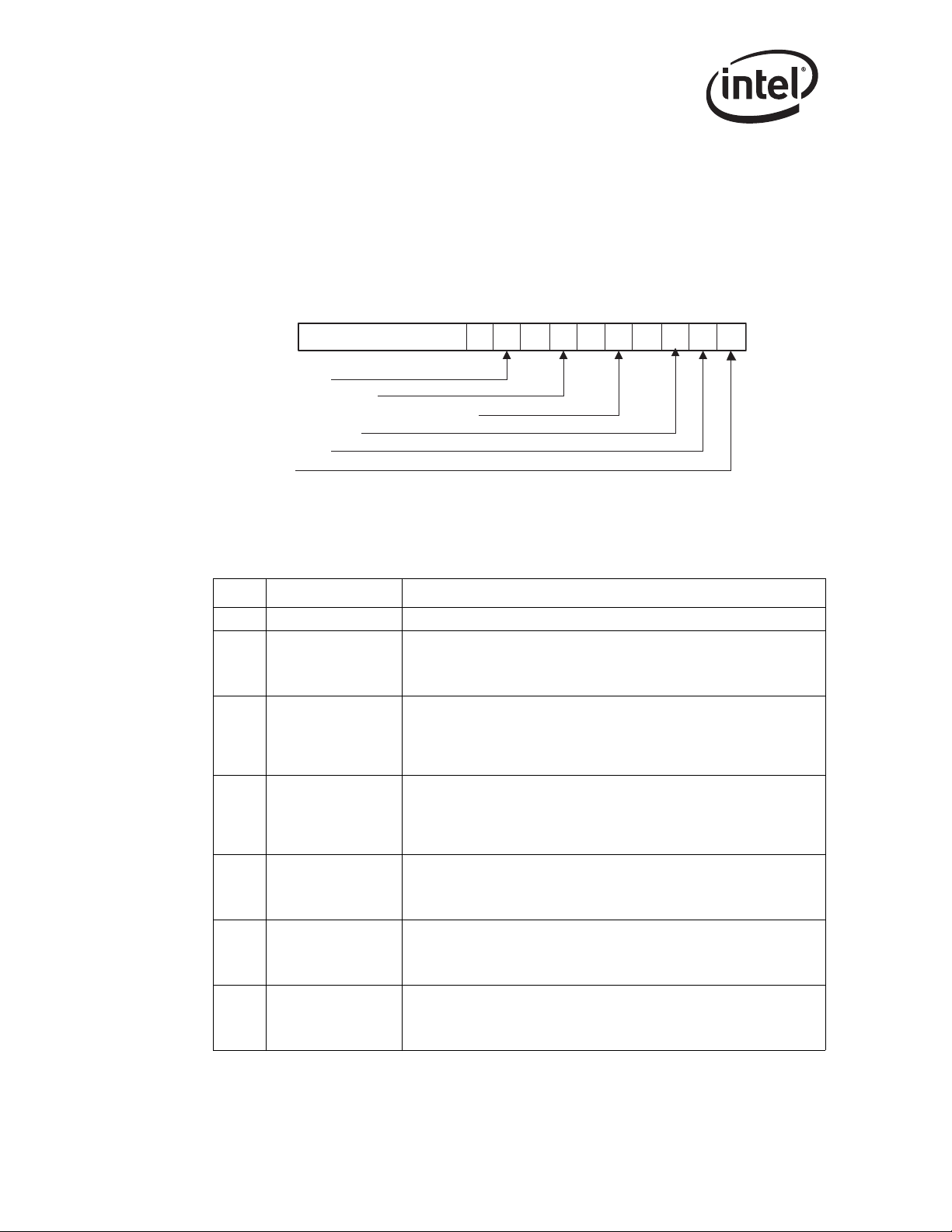

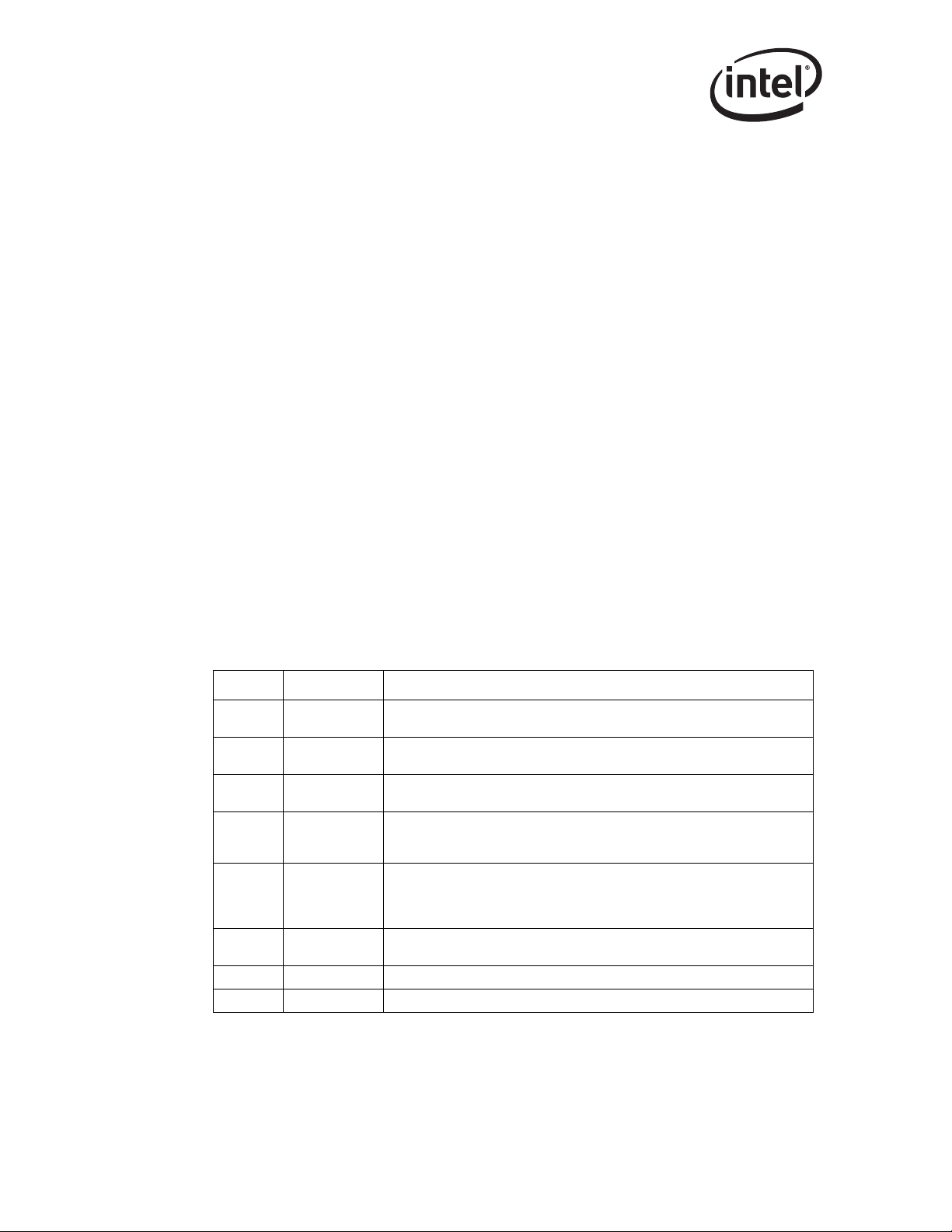

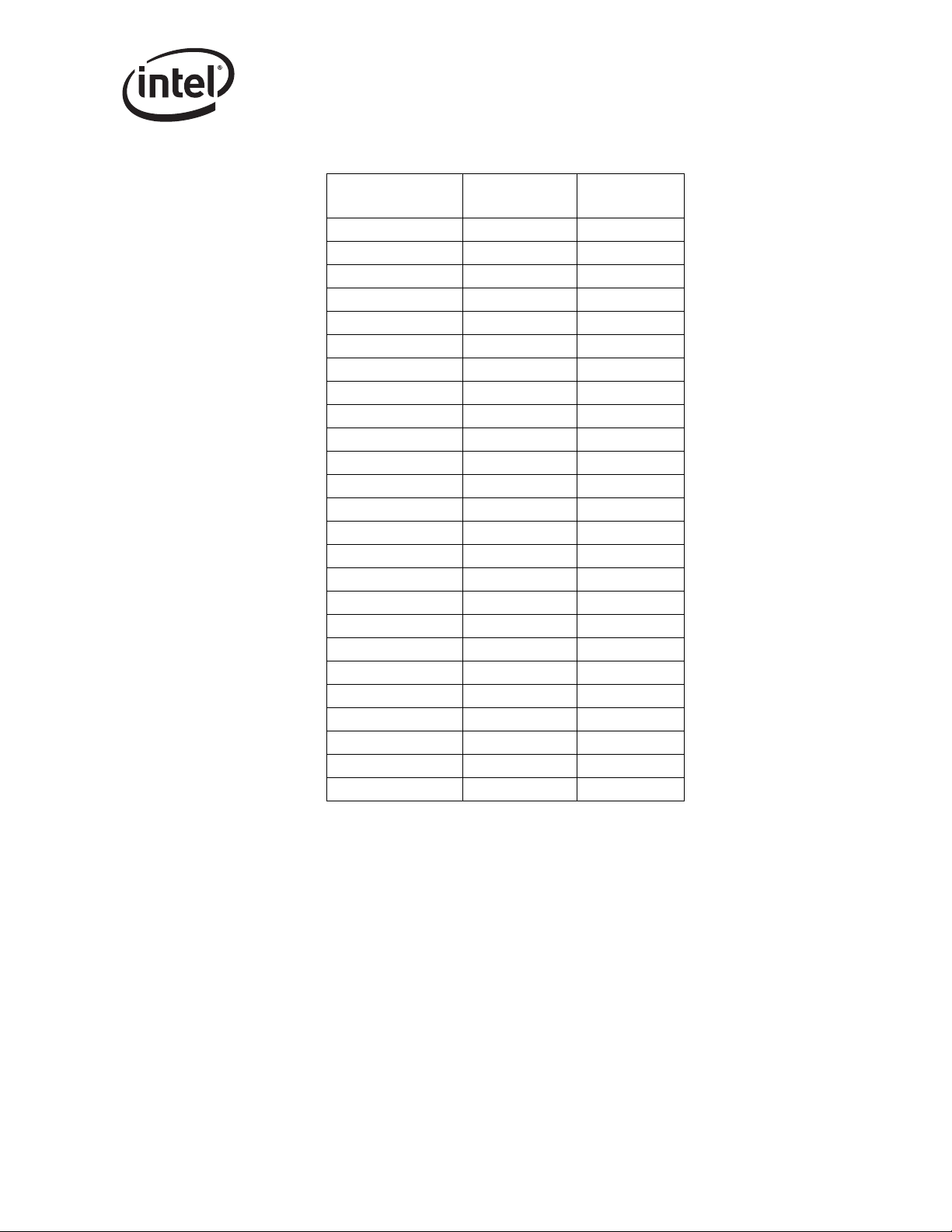

Table 2. Signal Type Descriptions

Type Name Description

IN Input The input pin is a standard input only signal.

OUT Output

TS Tri-State The tri-state pin is a bidirectional, input/output pin.

STS Sustained Tri-State

OD Open Drain

AI Analog Input The analog input pin is used for analog input signals.

AO Analog Output The analog output pin is used for analog output signals.

B Bias The bias pin is an input bias.

DPS

APS

Digital Power

Supply

Analog Power

Supply

The output pin is a Totem Pole Output pin and is a standard

active driver.

The sustained tri-state pin is an active low tri-state signal owned

and driven by one agent at a time. The agent asserting the STS

pin low must drive it high at least one clock cycle before floating

the pin. A new agent can only assert an STS signal low one

clock cycle after it has been tri-stated by the previous owner.

The open drain pin allows multiple devices to share this signal

as a wired-OR.

Digital power or ground for the device.

Analog power or ground for the device.

Networking Silicon — 82551ER

Datasheet 7

Page 16

82551ER — Networking Silicon

4.2 PCI Bus Interface Signals

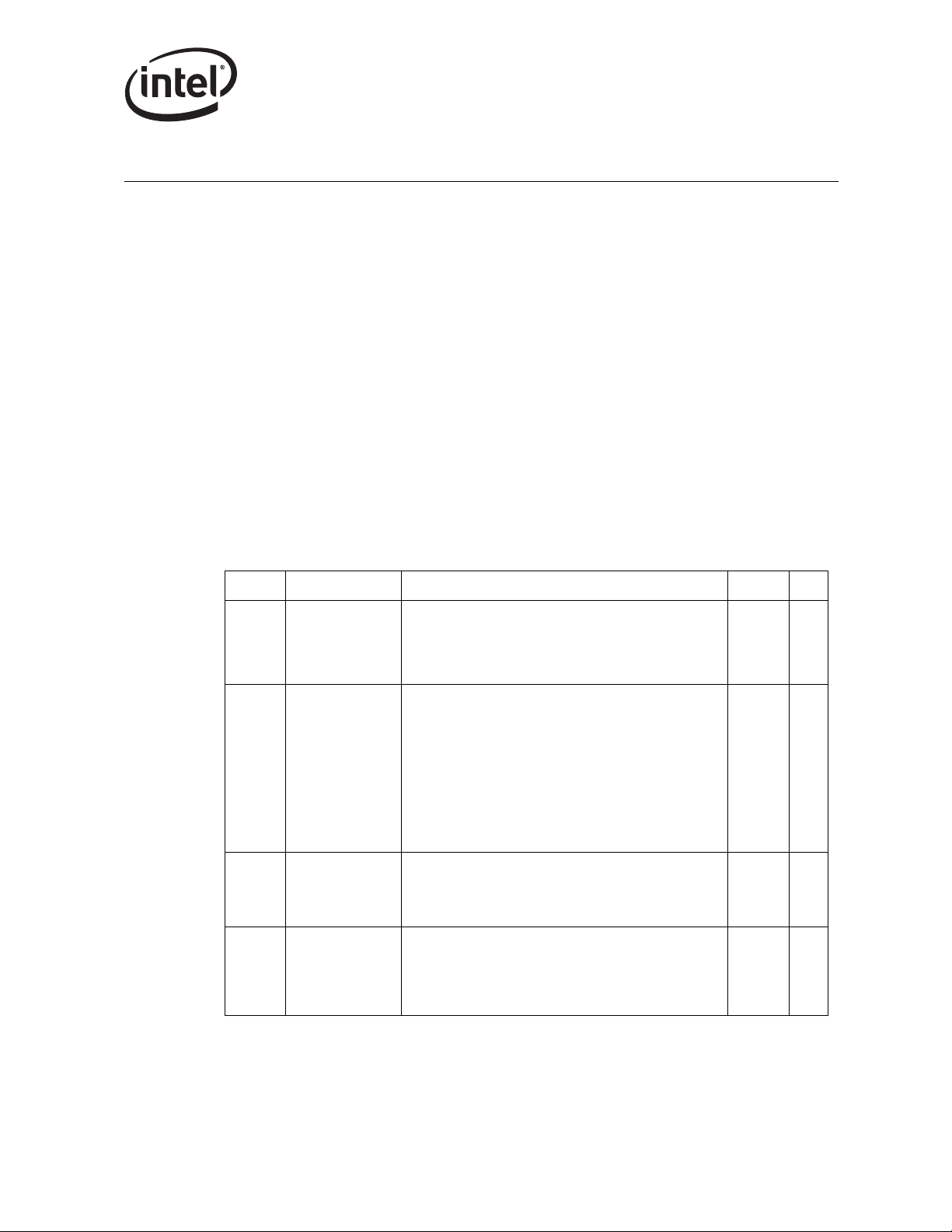

4.2.1 Address and Data Signals

Table 3. Address and Data Signals

Symbol Type Name and Function

Address and Data. The address and data lines are multiplexed on

the same PCI pins. A bus transaction consists of an address phase

followed by one or more data phases. During the address phase, the

AD[31:0] TS

C/BE#[3:0] TS

PAR TS

address and data lines contain the 32-bit physical address. For I/O,

this is a byte address; for configuration and memory, it is a Dword

address. The 82551ER uses little-endian byte ordering (in other

words, AD[31:24] contain the most significant byte and AD[7:0]

contain the least significant byte). During the data phases, the address

and data lines contain data.

Command and Byte Enable. The bus command and byte enable

signals are multiplexed on the same PCI pins. During the address

phase, the C/BE# lines define the bus command. During the data

phase, the C/BE# lines are used as Byte Enables. The Byte Enables

are valid for the entire data phase and determine which byte lanes

carry meaningful data.

Parity. Parity is even across AD[31:0] and C/BE#[3:0] lines. It is stable

and valid one clock after the address phase. For data phases, PAR is

stable and valid one clock after either IRDY# is asserted on a write

transaction or TRDY# is asserted on a read transaction.Once PAR is

valid, it remains valid until one clock after the completion of the current

data phase. The master drives PAR for address and write data

phases; and the target, for read data phases.

4.2.2 Interface Control Signals

Table 4. Interface Control Signals

Symbol Type Name and Function

Cycle Frame. The cycle frame signal is driven by the current master

FRAME# STS

IRDY# STS

TRDY# STS

STOP# STS

to indicate the beginning and duration of a transaction. FRAME# is

asserted to indicate the start of a transaction and de-asserted during

the final data phase.

Initiator Ready. The initiator ready signal indicates the bus master’s

ability to complete the current data phase and is used in conjunction

with the target ready (TRDY#) signal. A data phase is completed on

any clock cycle where both IRDY# and TRDY# are sampled asserted

(low) simultaneously.

Target Ready. The target ready signal indicates the selected device’s

ability to complete the current data phase and is used in conjunction

with the initiator ready (IRDY#) signal. A data phase is completed on

any clock cycle where both IRDY# and TRDY# are sampled asserted

(low) simultaneously.

Stop. The stop signal is driven by the target to indicate to the initiator

that it wishes to stop the current transaction. As a bus slave, STOP# is

driven by the 82551ER to inform the bus master to stop the current

transaction. As a bus master, STOP# is received by the 82551ER to

stop the current transaction.

8 Datasheet

Page 17

Table 4. Interface Control Signals

Symbol Type Name and Function

Initialization Device Select. The initialization device select signal is

IDSEL IN

DEVSEL# STS

REQ# TS

GNT# IN

INTA# OD

SERR# OD

PERR# STS

used by the 82551ER as a chip select during PCI configuration read

and write transactions. This signal is provided by the host in PCI

systems.

Device Select. The device select signal is asserted by the target once

it has detected its address. As a bus master, the DEVSEL# is an input

signal to the 82551ER indicating whether any device on the bus has

been selected. As a bus slave, the 82551ER asserts DEVSEL# to

indicate that it has decoded its address as the target of the current

transaction.

Request. The request signal indicates to the bus arbiter that the

82551ER desires use of the bus. This is a point-to-point signal and

every bus master has its own REQ#.

Grant. The grant signal is asserted by the bus arbiter and indicates to

the 82551ER that access to the bus has been granted. This is a pointto-point signal and every master has its own GNT#.

Interrupt A. The interrupt A signal is used to request an interrupt by

the 82551ER. This is an active low, level-triggered interrupt signal.

System Error. The system error signal is used to report address

parity errors. When an error is detected, SERR# is driven low for a

single PCI clock.

Parity Error. The parity error signal is used to report data parity errors

during all PCI transactions except a Special Cycle. The parity error pin

is asserted two clock cycles after the error was detected by the device

receiving data. The minimum duration of PERR# is one clock for each

data phase where an error is detected. A device cannot report a parity

error until it has claimed the access by asserting DEVSEL# and

completed a data phase.

Networking Silicon — 82551ER

4.2.3 System and Power Management Signals

Table 5. System and Power Management Signals

Symbol Type Name and Function

Clock. The Clock signal provides the timing for all PCI transactions

CLK IN

CLK_RUN#

RST# IN

PME# OD

IN/OUT

OD

Datasheet 9

and is an input signal to every PCI device. The 82551ER requires a

PCI Clock signal (frequency greater than or equal to 16 MHz) for

nominal operation. The 82551ER supports Clock signal suspension

using the Clockrun protocol.

Clock Run. The Clock Run signal is used by the system to pause or

slow down the PCI Clock signal. It is used by the 82551ER to enable

or disable suspension of the PCI Clock signal or restart of the PCI

clock. When the Clock Run signal is not used, this pin should be

connected to an external pull-down resistor.

Reset. The PCI Reset pin is used to place PCI registers, sequencers,

and signals into a consistent state. When RST# is asserted, the

82551ER ignores other PCI signals and all PCI output signals will be

tristated. The PCI Reset pin should be pulled high to the main digital

power supply.

Power Management Event. The Power Management Event signal

indicates that a power management event has occurred in a PCI bus

system.

Page 18

82551ER — Networking Silicon

Table 5. System and Power Management Signals

Symbol Type Name and Function

Isolate. The Isolate pin is used to isolate the 82551ER from the PCI

ISOLATE# IN

ALTRST# IN

VIO

B

IN

bus. It also provides PCI Reset pin functionality. When Isolate is active

(low), the 82551ER does not drive its PCI outputs (except PME#) or

sample its PCI inputs (including CLK and RST#). The ISOLATE# pin

should be driven by the PCI Reset signal.

Alternate Reset. The Alternate Reset pin is used to reset the

82551ER on power-up. The Alternate Reset signal should be pulled

high to the main digital power supply.

Voltage Input/Output . The VIO pin is the voltage bias pin and should

be connected to a 5 V supply in a 5 V PCI signaling environment and a

3.3 V supply in 3.3 V signaling environment.

4.3 Local Memory Interface Signals

Note: All unused Flash Address and Data pins MUST be lef t flo ating. Some of these pins have

undocumented test functionality and can cause unpredictable behavio r if they are

unnecessarily connected to a pull-up or pull-down resistor.

T able 6. Local Memory Interface Signals

Symbol Type Name and Function

FLD7:0 IN/OUT

FLA16/

CLK25

FLA15/EESK OUT

FLA14/

EEDO

FLA[13]/

EEDI

FLA 12:8 IN/OUT

FLA7/

CLKEN

IN/OUT

IN/OUT

OUT

IN/OUT

Flash Data Input/Output. These pins are used for the Flash data

interface. These pins should be left floating if the Flash is not used.

Flash Address 16/25 MHz Clock. This multiplexed pin is controlled

by the status of the Flash Address 7 (FLA7) pin. If FLA7 is left floating,

this pin is used as FLA16; otherwise, if FLA7 is connected to a pull-up

resistor, this pin is used as a 25 MHz clock output. This pin should be

left floating if the Flash and the CLK25 functionality are not used.

Flash Address 15/EEPROM Data Output. During Flash accesses,

this multiplexed pin acts as the Flash Address 15 output signal. During

EEPROM accesses, it acts as the serial shift clock output to the

EEPROM.

Flash Address 14/EEPROM Data Output. During Flash accesses,

this multiplexed pin acts as the Flash Address 14 output signal. During

EEPROM accesses, this pin accepts serial input data from the

EEPROM Data Output pin.

Flash Address[13]/EEPROM Data Input. During Flash accesses,

this multiplexed pin acts as the Flash Address [13] output signal.

During EEPROM accesses, this pin provides serial output data to the

EEPROM Data Input pin.

Flash Address 12:8. These pins act as Flash address outputs. They

should be left floating if Flash is not used.

Flash Address 7/Clock Enable. This multiplexed pin acts as the

Flash Address 7 output signal during nominal operation. When the

power-on reset of the 82551ER is active, this pin acts as input control

over the FLA16/CLK25 output signal. If the FLA7/CLKEN pin is

connected to a pull-up resistor (3.3 KΩ) , a 25 MHz clock signal is

provided on the FLA16/CLK25 output; otherwise, it is used as FLA16

output. For systems that do not use the 25 MHz clock output or Flash,

this pin should be left floating.

10 Datasheet

Page 19

T a ble 6. Local Memory Interface Signals

Symbol Type Name and Function

FLA6:2 OUT

FLA1/

AUXPWR

FLA0/

PCIMODE#

EECS OUT

FLCS# OUT

FLOE# OUT

FLWE# OUT

TS

TS

Flash Address[6:2]. These pins are used as Flash address outputs.

These pins should be left floating if the Flash is not used.

Flash Address1/Auxiliary Power. This multiplexed pin acts as the

Flash Address 1 output signal during nominal operation. When the

power-on reset of the 82551ER is active (low), it acts as the power

supply indicator. If the 82551ER is fed by auxiliary power, it should be

connected to VCC through a pull-up resistor (3.3 KΩ). Otherwise, this

pin should be left floating.

Flash Address 0/PCI Mode. This multiplexed pin acts as the Flash

Address 0 output signal during nominal operation. When power-on

reset of the 82551ER is active (low), it acts as the input system type.

For PCI systems that do not use Flash, this pin should be left floating.

EEPROM Chip Select. The EEPROM Chip Select signal is used to

assert chip select to the serial EEPROM.

Flash Chip Select. The Flash Chip Select pin provides an active low

Flash chip select signal. This pin should be left floating if Flash is not

used.

Flash Output Enable. This pin provides an active low output enable

control (read) to the Flash memory. This pin should be left floating if

Flash is not used.

Flash Write Enable. This pin provides an active low write enable

control to the Flash memory. This pin should be left floating if Flash is

not used.

Networking Silicon — 82551ER

4.4 Test Port Signals

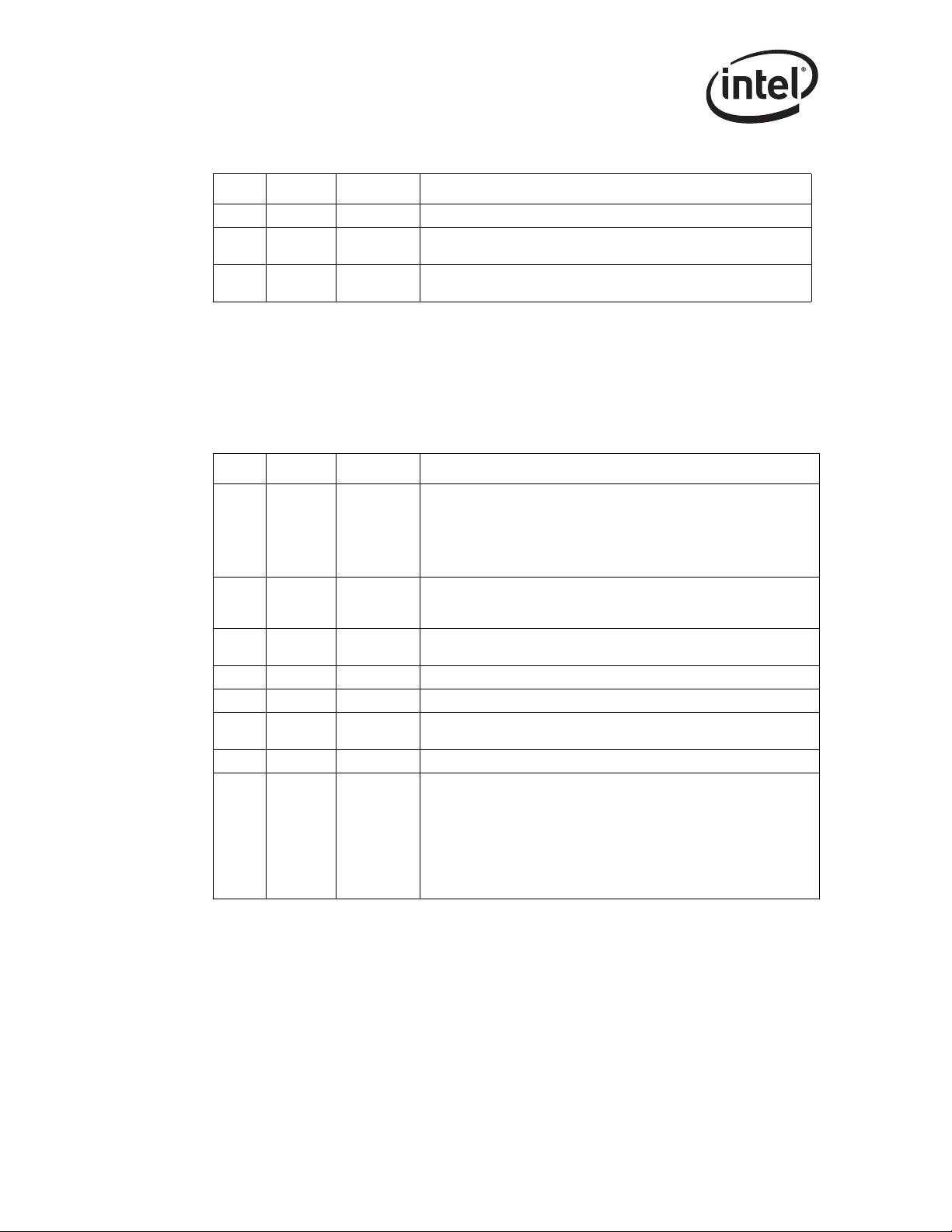

T able 7. Test Port Signals

Symbol Type Name and Function

TEST IN

TCK IN Test Port Clock. This pin is used for the Test Port Clock signal.

TI IN

TEXEC IN

TO OUT

Note: These test port signals are not JTAG compatible. As a result, a BSDL file is not required.

Test Port. If this input pin is high, the 82551ER will enable the test

port. During nominal operation this pin should be connected to a 1K Ω

pull-down resistor.

Test Port Data Input. This pin is used for the Test Port Data Input

signal.

Test Port Execute Enable. This pin is used for the Test Port Execute

Enable signal.

Test Port Data Output. This pin is used for the Test Port Data Output

signal.

Datasheet 11

Page 20

82551ER — Networking Silicon

4.5 PHY Signals

Table 8. PHY Signals

Symbol Type Name and Function

X1 AI

X2 AO

TDP

TDN

RDP

RDN

ACTLED# OUT

LILED# OUT

SPEEDLED# OUT

RBIAS100 B

RBIAS10 B

VREF B

a. Based on some board designs, RBIAS100 and RBIAS10 values may need to be increased/decreased to com-

pensate fo r high /lo w MDI t ransmi t am plitu de. S ee th e 82562EZ(EX)/82551ER(IT) & 82541ER Combined Foot-

print LOM Design Guide for more inform ation.

AO

AI

Crystal Input One. X1 and X2 can be driven by an external 3.3 V 25

MHz crystal. Otherwise, X1 may be driven by an external metal-oxide

semiconductor (MOS) level 25 MHz oscillator when X2 is left floating.

Crystal Input Two. X1 and X2 can be driven by an external 3.3 V 25

MHz crystal. Otherwise, X1 may be driven by an external MOS level

25 MHz oscillator when X2 is left floating.

Analog Twisted Pair Ethernet Transmit Di ff e re ntial Pair. These

pins transmit the serial bit stream for transmission on the Unshielded

Twisted Pair (UTP) cable. The current-driven differential driver can be

two-level (10BASE-T) or three-level (100BASE-TX) signals depending

on the mode of operation. These signals interface directly with an

isolation transformer.

Analog Twisted Pair Ethernet Receive Differential Pair. These pins

receive the serial bit stream from the isolation transformer. The bit

stream can be two-level (10BASE-T) or three-level (100BASE-TX)

signals depending on the mode of operation.

Activity LED. The Activity LED pin indicates either transmit or receive

activity. When activity is present, the activity LED is on (ACTLED#

active low); when no activity is present, the activity LED is off.

Link Integrity LED. The Link Integrity LED pin indicates link integrity.

If the link is valid in either 10 or 100 Mbps, the LED is on (LILED#

active low); if link is invalid, the LED is off.

Speed LED. The Speed LED pin indicates the speed. The speed LED

will be on at 100 Mbps (SPEEDLED# active low) and off at 10 Mbps.

Reference Bias Resistor (100 Mbps). This pin should be connected

to a pull-down resistor.

Reference Bias Resistor (10 Mbps). This pin should be connected

to a pull-down resistor.

Voltage Referen ce. This pin is connected to a 1.25 V ± 1% external

voltage reference generator. To use the internal voltage reference

source, this pin should be left floating. Under normal circumstances,

the internal voltage reference should be used and this pin would be left

open.

a

a

12 Datasheet

Page 21

4.6 Power and Ground Signals

Table 9. Power and Ground Signals

Symbol Type Name and Function

Networking Silicon — 82551ER

Digital 3.3 V Power. The VCC pins should be connected to the main

VCC DPS

VCCR APS Analog Power. These pins should be connected directly to VCC.

VSSPL,

VSSPP,

VSSPT, VSS

NC DPS

DPS

digital power supply. This is 3.3 V

power supply and PCI power in systems without an auxiliary power

supply. The power source is configured through the FLA[1]/AUXPWR

pin.

Digital Ground. These pins should be connected to the main digital

ground plane.

No Connect. These pins should not be connected to any circuit. Pullup or pull-down resistors should not be used.

in systems with an auxiliary

AUX

Datasheet 13

Page 22

82551ER — Networking Silicon

Note: This page is intentionally left blank.

14 Datasheet

Page 23

Networking Silicon — 82551ER

5.0 Media Access Control Functional Description

5.1 Device Initiali zation

The 82551ER has six sources for initialization. They are listed according to their precedence:

1. Internal Power-on Reset (POR)

2. ALTRST# pin

3. RST# pin

4. ISOLATE# pin

5. Software Reset (Software Command)

6. Selective Reset (Software Command)

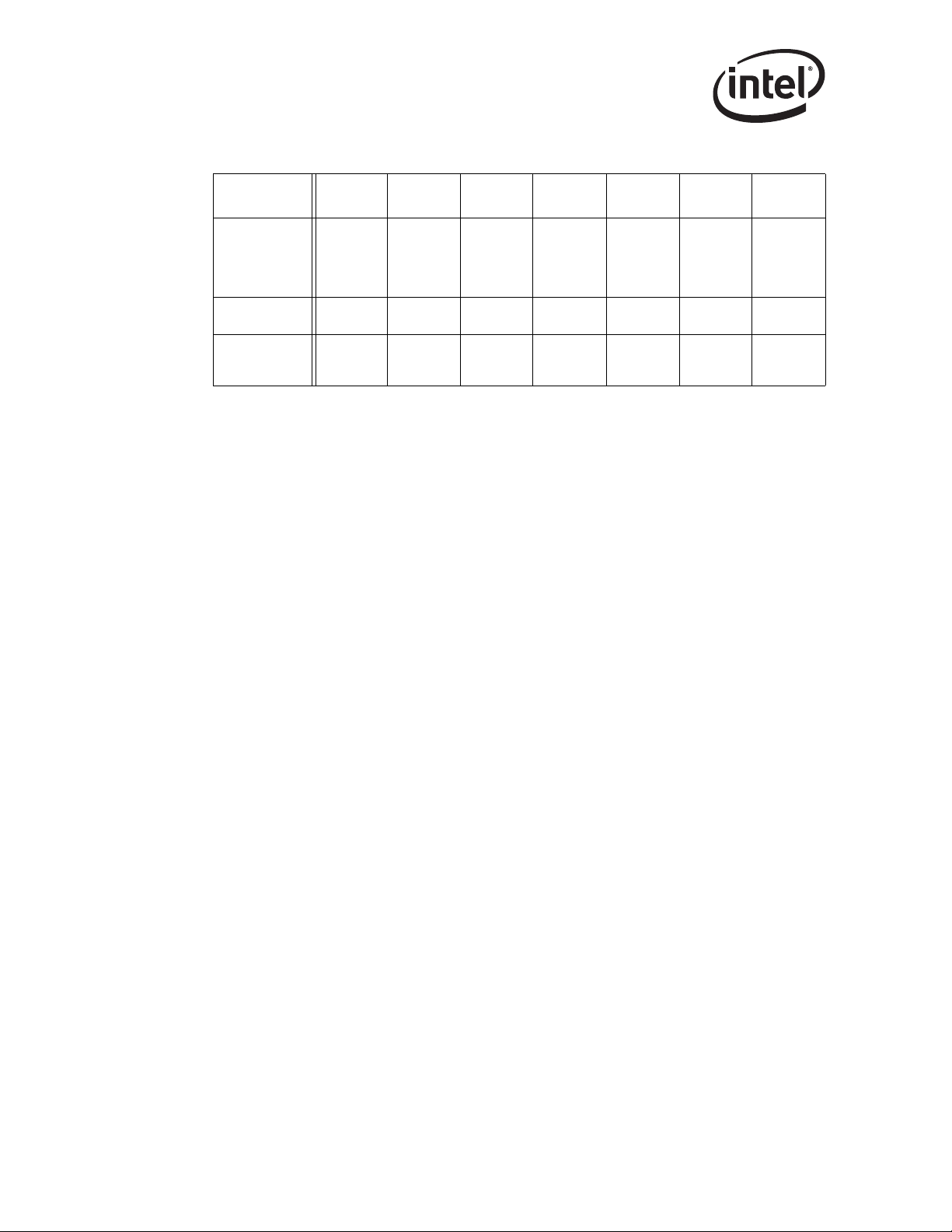

5.1.1 Initialization Effects

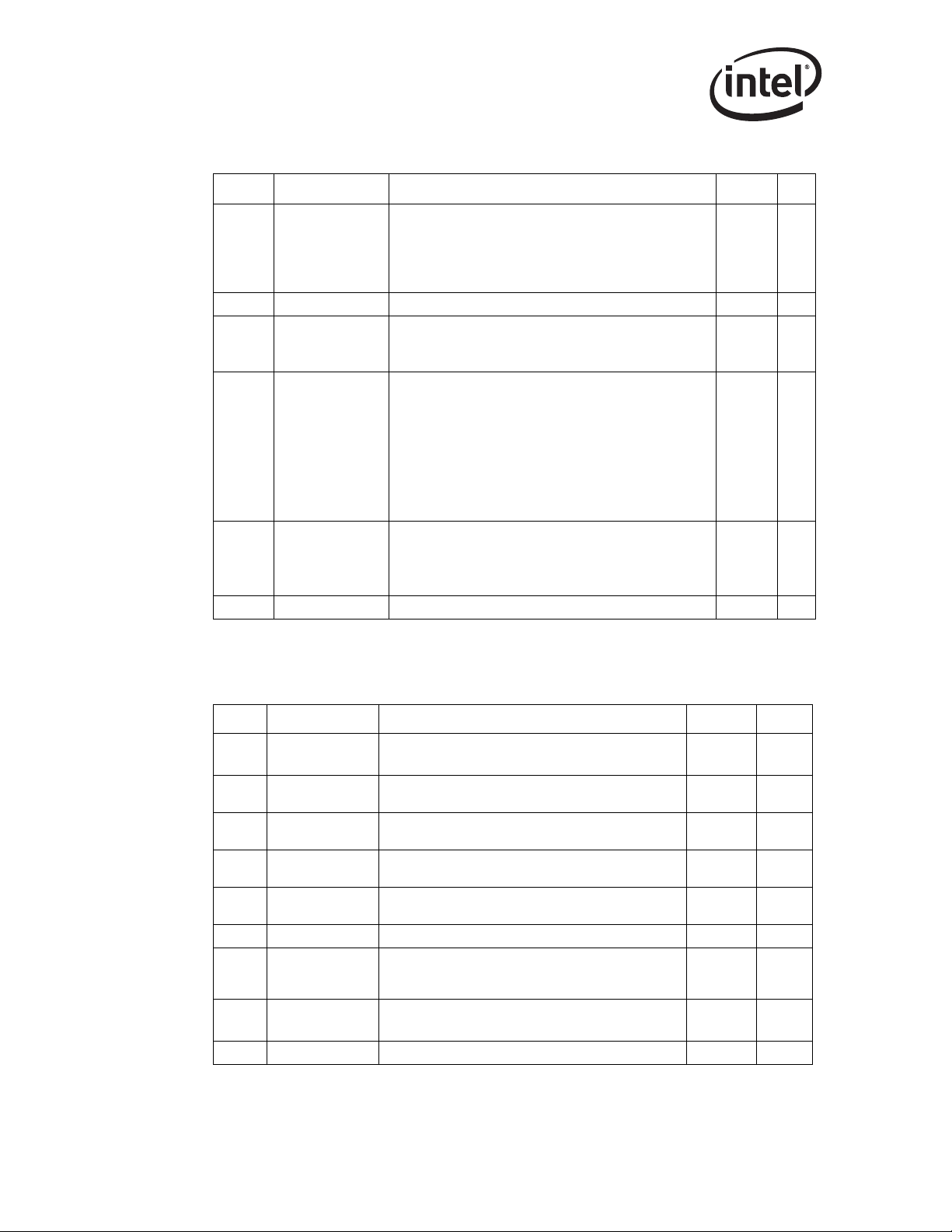

The following table lists the effect of each of the different initialization sources on major portions

of the 82551ER. The initialization sources are listed in order of precedence. For example, any

resource that is initialized by the software reset is also initialized by the D3 to D0 transition and

ALTRST# and PC I RST# but not necessarily by th e selectiv e reset.

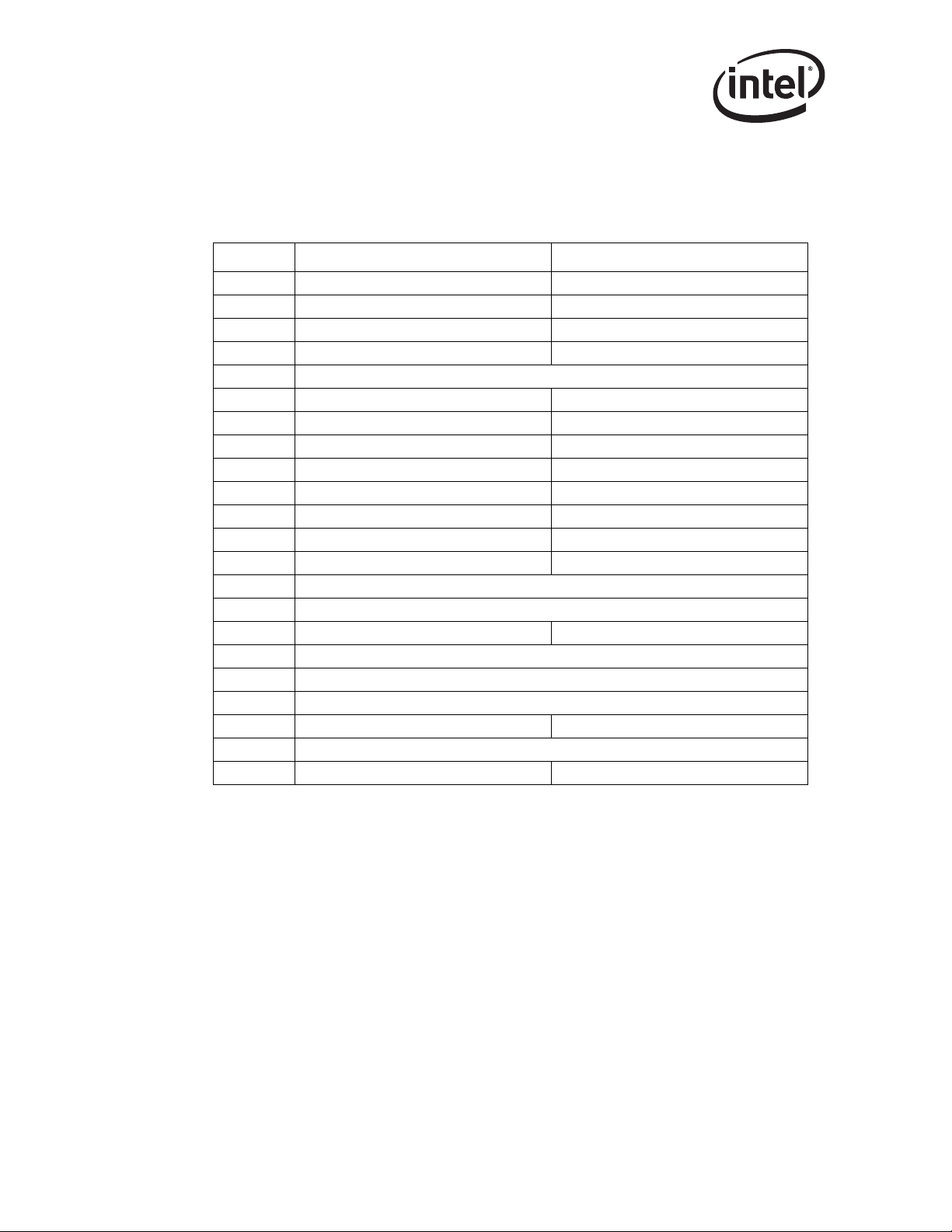

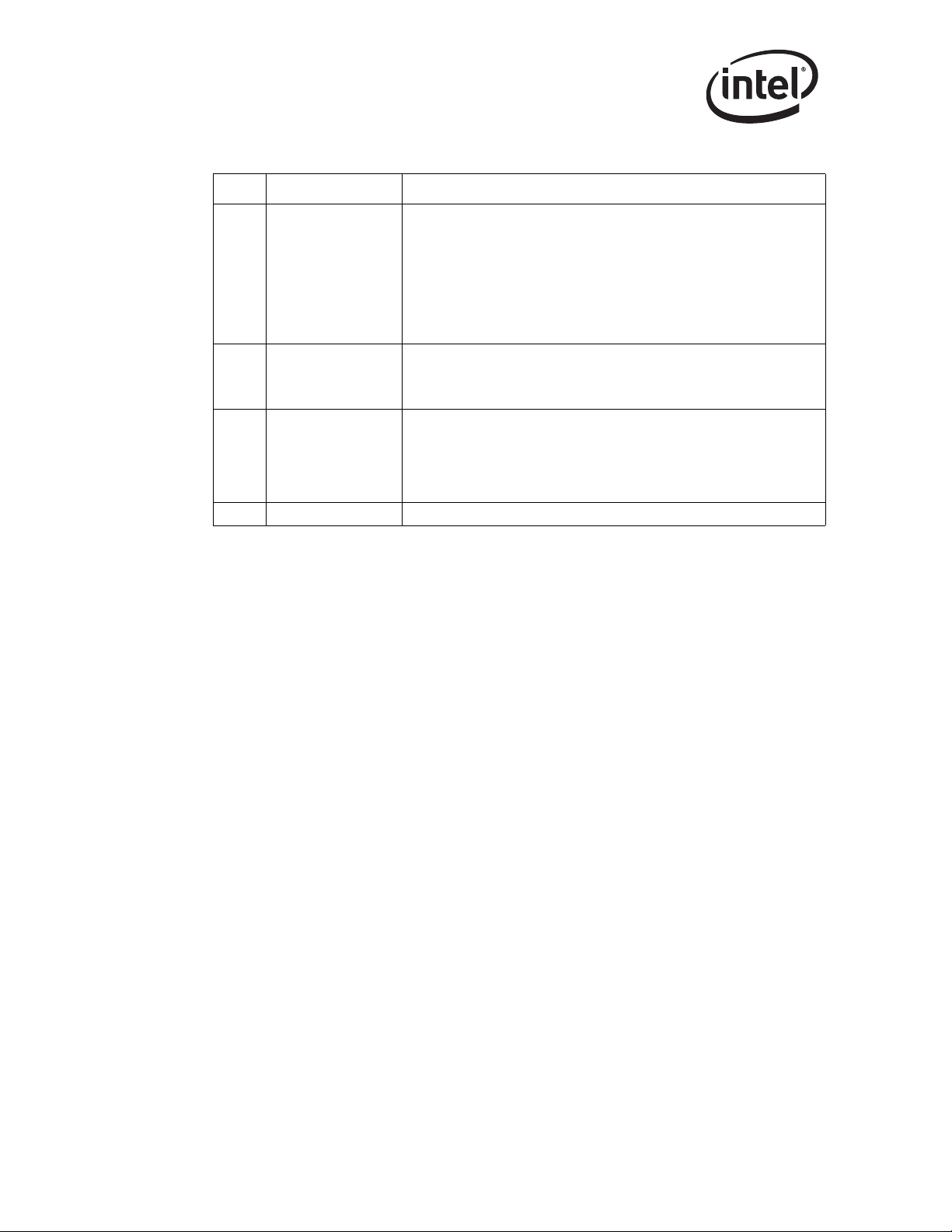

Table 10. Initialization Effects

Internal

POR

EEPROM read

and initialization

Loadable

microcode

decoded/reset

MAC

configuration

reset and

multicast hash

Memory

pointers and

mircomachine

state reset

PCI

Configuration

register reset

PHY

configuration

reset

✓✓✓✓-- -- --

✓✓✓✓✓✓--

✓✓✓✓✓✓--

✓✓✓✓✓✓✓

✓✓✓✓✓-- --

✓✓✓-- -- -- --

ALTRST# RST# ISOLATE#

D3 to D0

Transition

Software

Reset

Selective

Reset

Datasheet 15

Page 24

82551ER — Networking Silicon

Table 10. Initialization Effects

Internal

POR

Power

management

event reset

Statistic

counters reset

Sampling of

configuration

input pins

5.2 PCI Interface

5.2.1 Bus Operations

After configuration, the 82551ER is ready for its normal operation. As a Fast Ethernet Controller,

the role of the 82551ER is to access transmitted data or deposit received data. In both cases the

82551ER, as a bus master device, will initiate memory cycles by way of the PCI bus.

To perform these actions, the 82551ER is controlled and examined by the CPU through its control

and status structures and registers. Some of these structures reside in the 82551 ER and some reside

in system memory . For access to th e 82551ER ’s Control/Status Registers (CSR), the 82551ER acts

as a slave device. The 82551ER serves as a slave also while the CPU accesses its 128 KB Flash

buffer or its EEPROM.

ALTRST# RST# ISOLATE#

Clear only

✓✓

✓✓✓✓✓✓--

✓✓✓-- -- -- --

if no

auxiliary

power

present

Clear only

if no

auxiliary

power

present

D3 to D0

Transition

-- -- --

Software

Reset

Selective

Reset

Section 5.2.1.1 describes the 82551ER slave operation. It is followed by a description of the

82551ER operation as a bus master (initiator) in Section 5.2.1.2.

5.2.1.1 Bus Slave Operation

The 82551ER serves as a target device in the following cases:

• CPU accesses to the 82551ER System Control Block (SCB) Control/Status Registers (CSR)

• CPU accesses to the EEPROM through its CSR

• CPU accesses to the 82551ER PORT address through the CSR

• CPU accesses to the MDI control register in the CSR

• CPU accesses to the Flash control register in the CSR

• CPU accesses to the 128 KB Flash

The CSR and the 1 MB Flash buffer are considered by the 82551ER as totally separated memory

spaces. The 82551ER provides separate Ba se Address Regis ters (BARs) in the configu ration space

to distinguish between them. The size of the CSR memory space is 4 KB in the memory space and

64 bytes in the I/O space. The 82551ER treats accesses to these memory spaces differently.

16 Datasheet

Page 25

5.2.1.1.1 Control/St atus Register (CSR) Accesses

The 82551ER supports zero wait state single cycle memory or I/O mapped accesses to its CSR

space. Separate BARs request 4 KB of memory space and 64 bytes of I/O space to accomplish

these accesses. The 82551ER provides 4 valid KB of CSR space, which include the following

elements:

• System Control Block (SCB) registers

• PORT register

• Flash control register

• EEPROM control register

• MDI control register

• Flow control register s

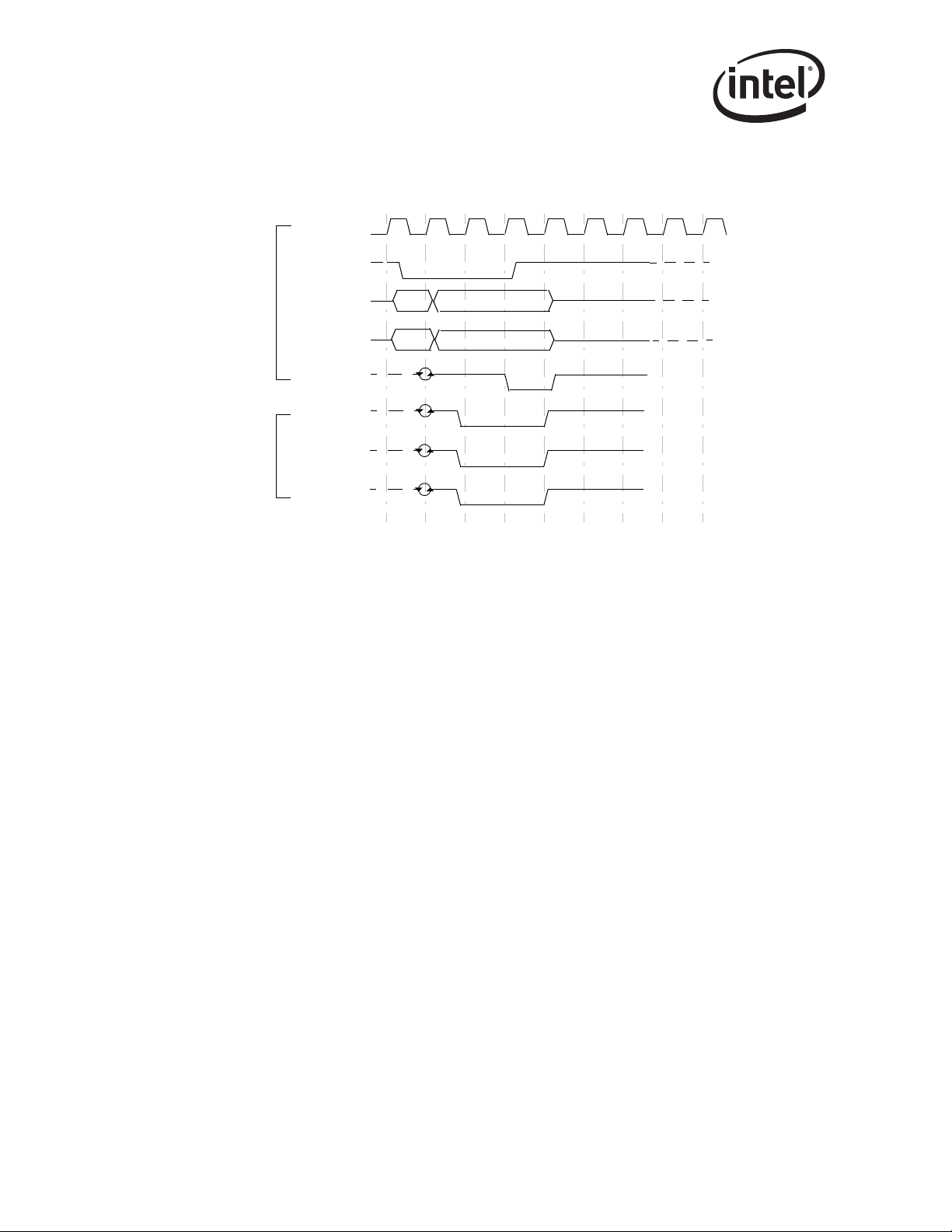

The following figures show CSR zero wait state I/ O read and write cycles. In the cas e o f accessin g

the Control/Status Registers, the CPU is the initiator and the 82551ER is the target of the

transaction.

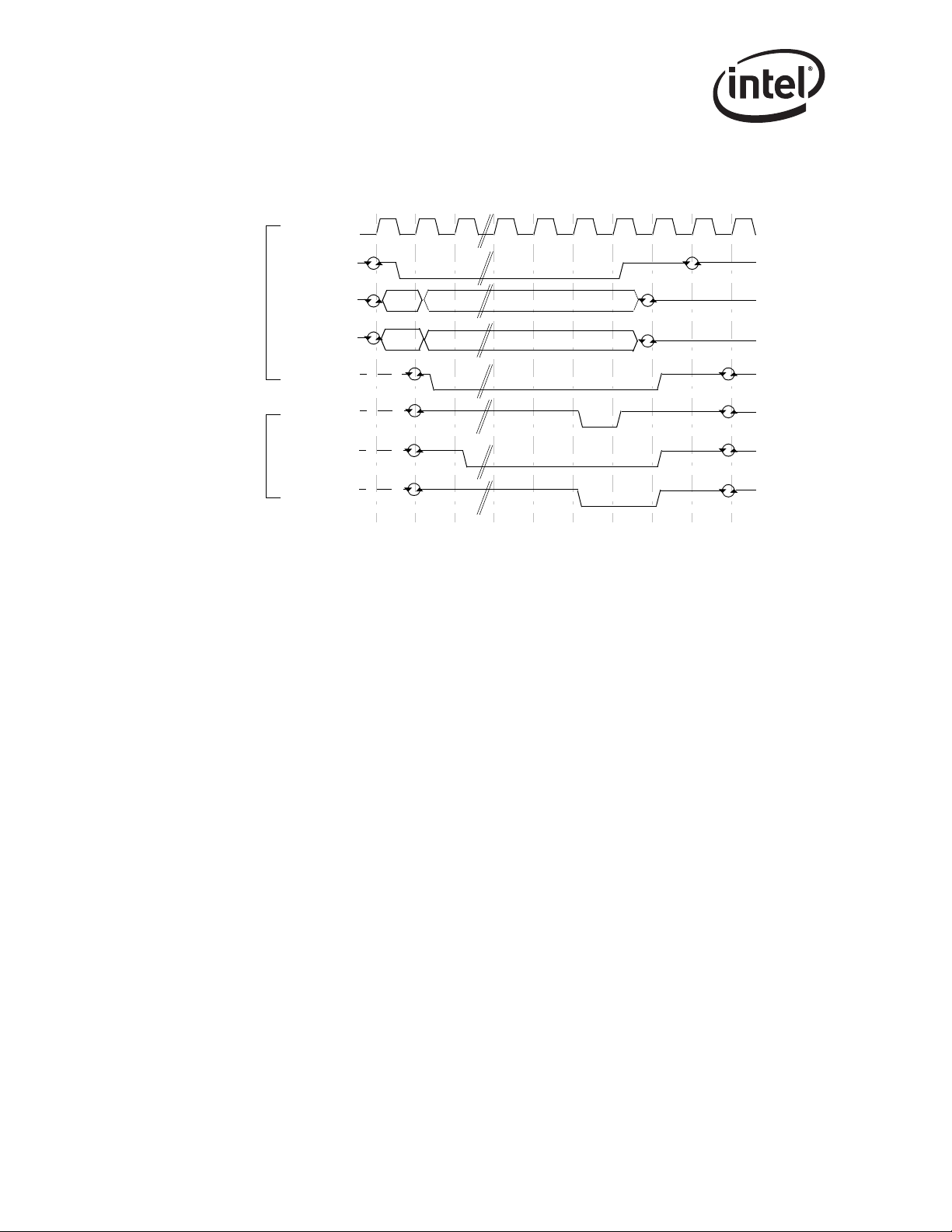

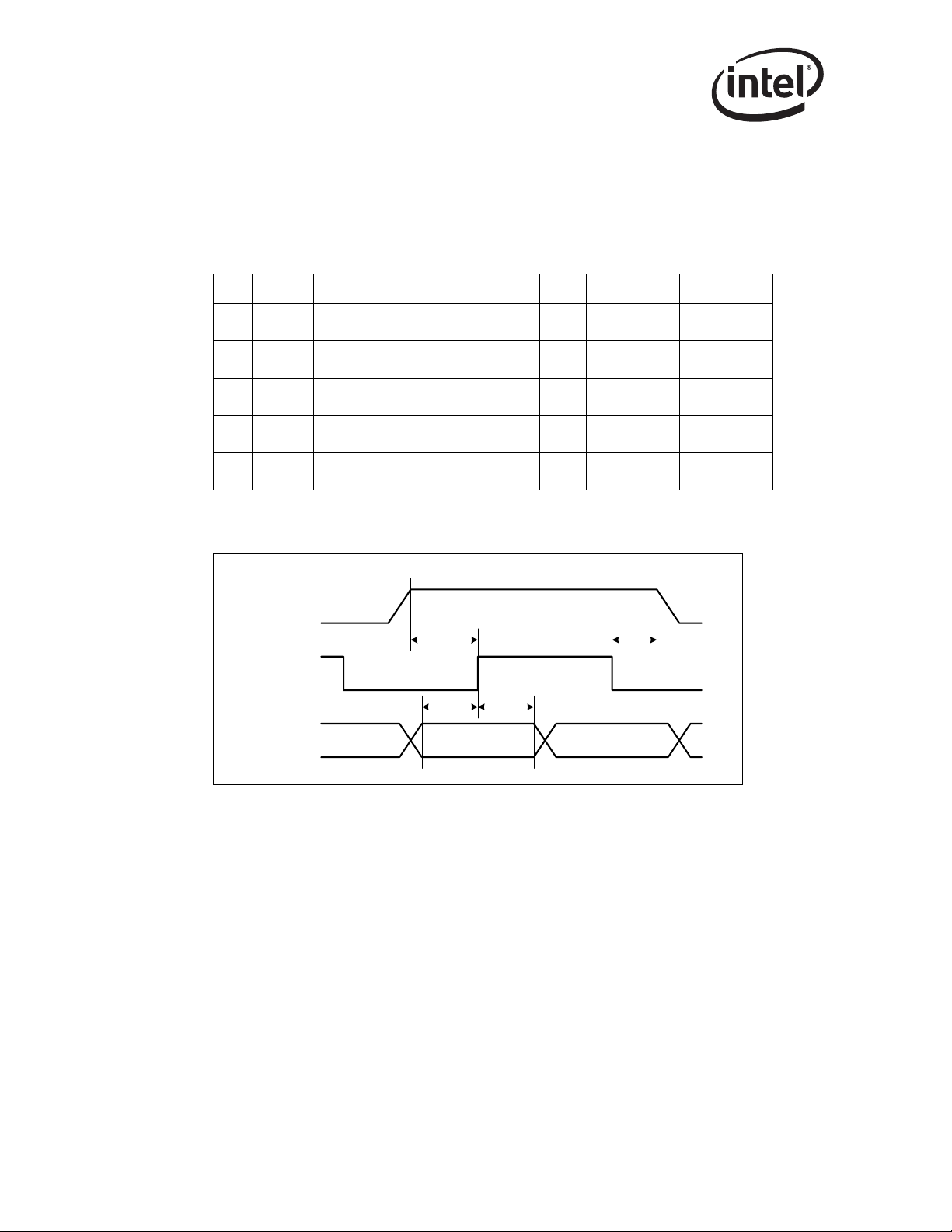

Figure 1. CSR I/O Read Cycle

Networking Silicon — 82551ER

CLK

FRAME#

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

ADDR

I/O RD BE#

3421 56789

DATA

82551ER SYSTEM

STOP#

Read Accesses: The CPU, as the initiator, drives address lines AD[31:0], the command and byte

enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. As a slave, the 82551ER

controls the TRDY# signal and provides valid data on each data access. The 82551ER allows the

CPU to issue only one read cycle when it accesses the Control/Status Registers, generating a

disconnect by asserting the STOP# signal. The CPU can ins er t wait states by de-asserting IRDY#

when it is not ready.

Datasheet 17

Page 26

82551ER — Networking Silicon

Figure 2. CSR I/O Write Cycle

CLK

FRAME#

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

ADDR DATA

I/O WR BE#

3421 56789

82551ER SYSTEM

STOP#

Write Accesses: The CPU, as the initiator, drives the address lines AD[31:0], the command and

byte enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. It also provides the

82551ER with valid data on each data access immediately after asserting IRDY#. The 82551ER

controls the TRDY# signal and asserts it from the data access. The 82551ER allows the CPU to

issue only one I/O write cycle to the Control/Status Registers, generating a disconnect by asserting

the STOP# signal. This is true for both memory mapped and I/O mapped accesses.

18 Datasheet

Page 27

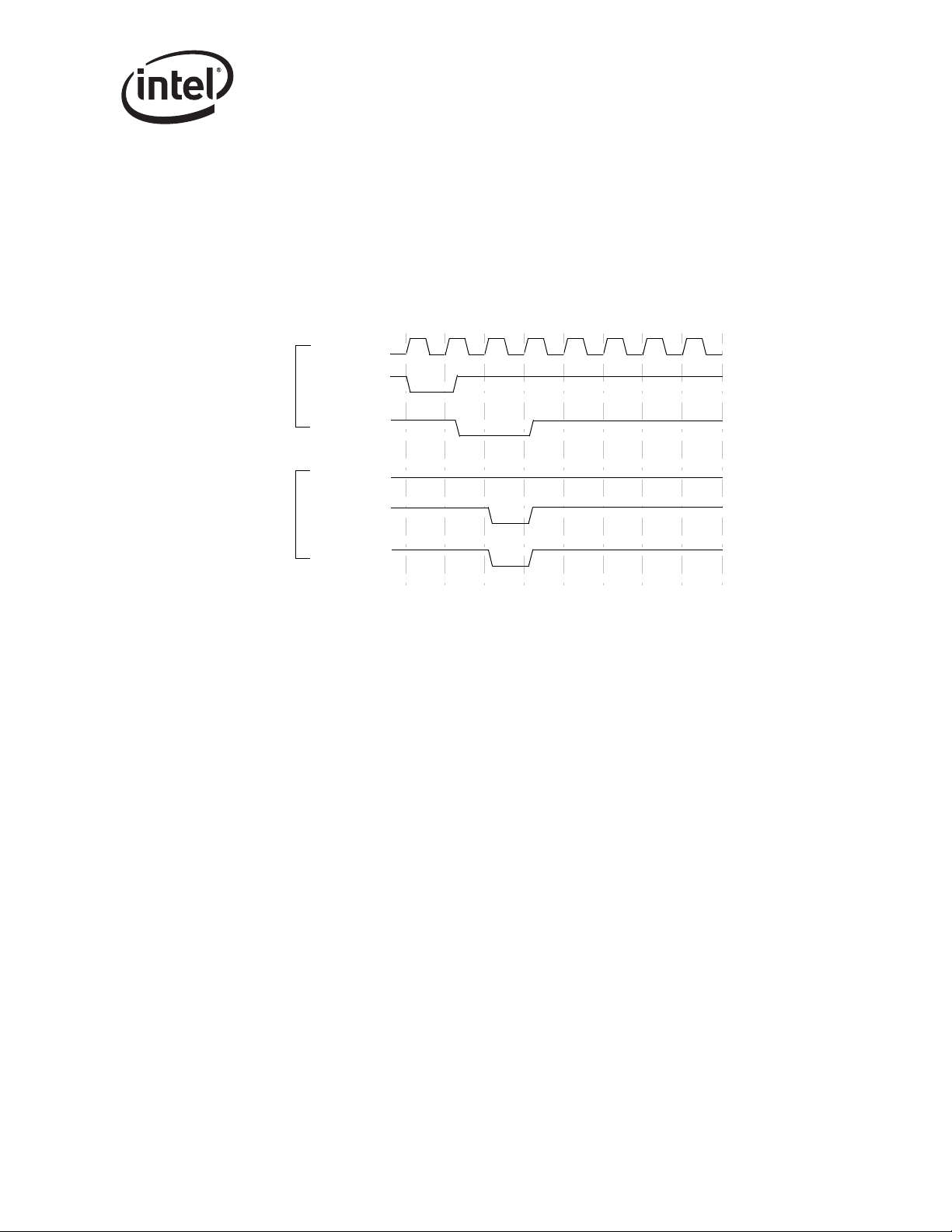

5.2.1.1.2 Flash Buffer Accesses

The CPU accesses to the Flash buffer are very slow and the 82551ER issues a target-disconnect at

the first data access. The 82551ER asserts the STOP# signal to indicate a target-disconnect. The

figures below illustrate memory CPU read and write accesses to the 128 KB Flash buffer. The

longest burst cycle to the Flash buffer contains one data access only.

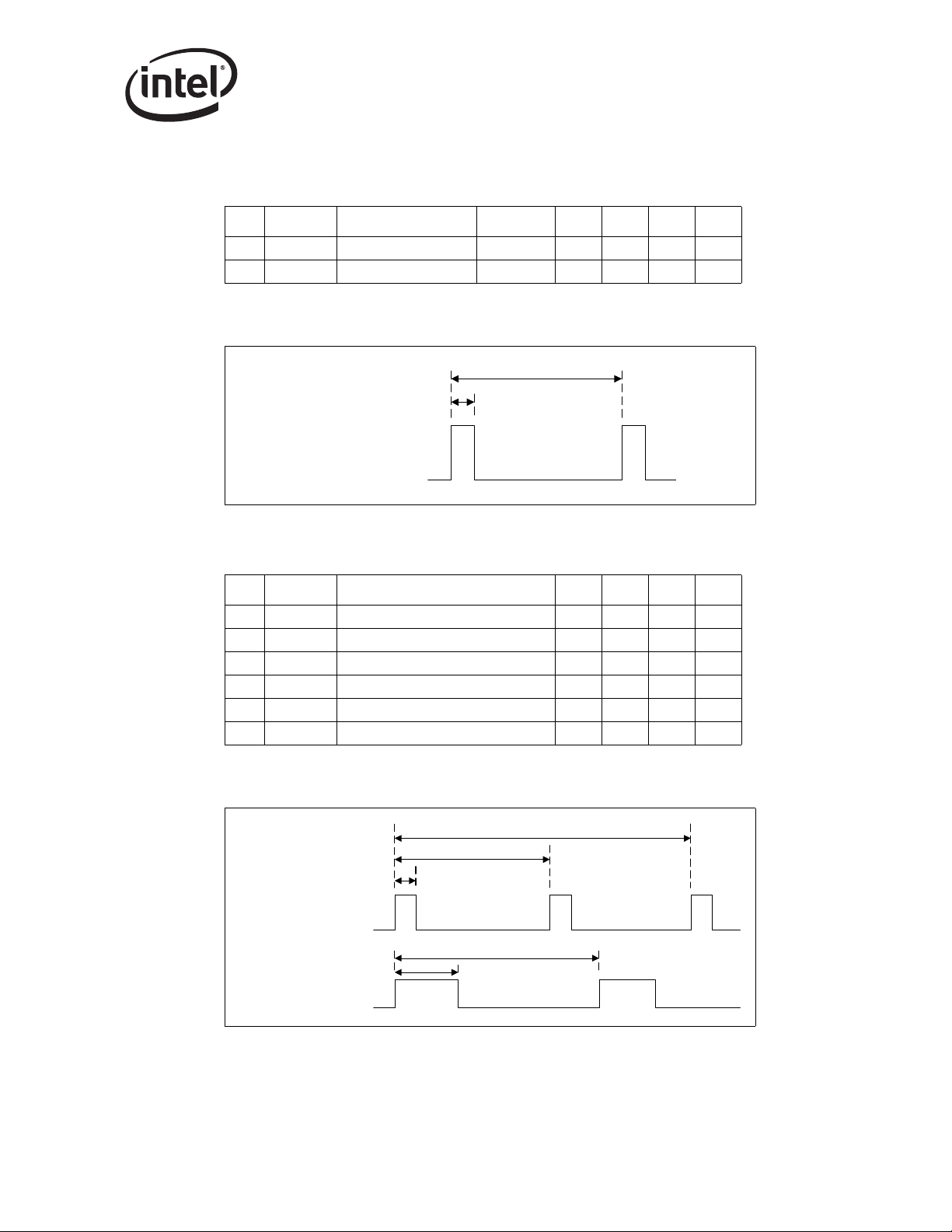

Figure 3. Flash Buffer Read Cycle

CLK

FRAME#

Networking Silicon — 82551ER

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

ADDR DATA

MEM RD BE#

82551ER SYSTEM

STOP#

Read Accesses: The CPU, as the initiator, drives the address lines AD[31:0], the command and

byte enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. The 82551ER controls

the TRDY# signal and de-asserts it for a certain n umb er o f clocks un til valid d ata can be read from

the Flash buffer. When TRDY# is asserted, the 82551ER drives valid data on the AD[31:0] lines.

The CPU can also insert wait states by de-asserting IRDY# until it is ready. Flash buffer read

accesses can be byte or word length.

Datasheet 19

Page 28

82551ER — Networking Silicon

Figure 4. Flash Buffer Write Cycle

CLK

FRAME#

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

ADDR

MEM WR BE#

DATA

82551ER SYSTEM

STOP#

Write Accesses: The CPU, as the initiator, drives the address lines AD[31:0], the command and

byte enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. It also provides the

82551ER with valid data immediately after asserting IRDY#. The 82551ER controls the TRDY#

signal and de-asserts it for a certain number of clocks until valid data is written to the Flash buffer.

By asserting TRDY#, the 82551ER signals the CPU that the current data access has completed.

Flash buffer write accesses can be byte length only.

20 Datasheet

Page 29

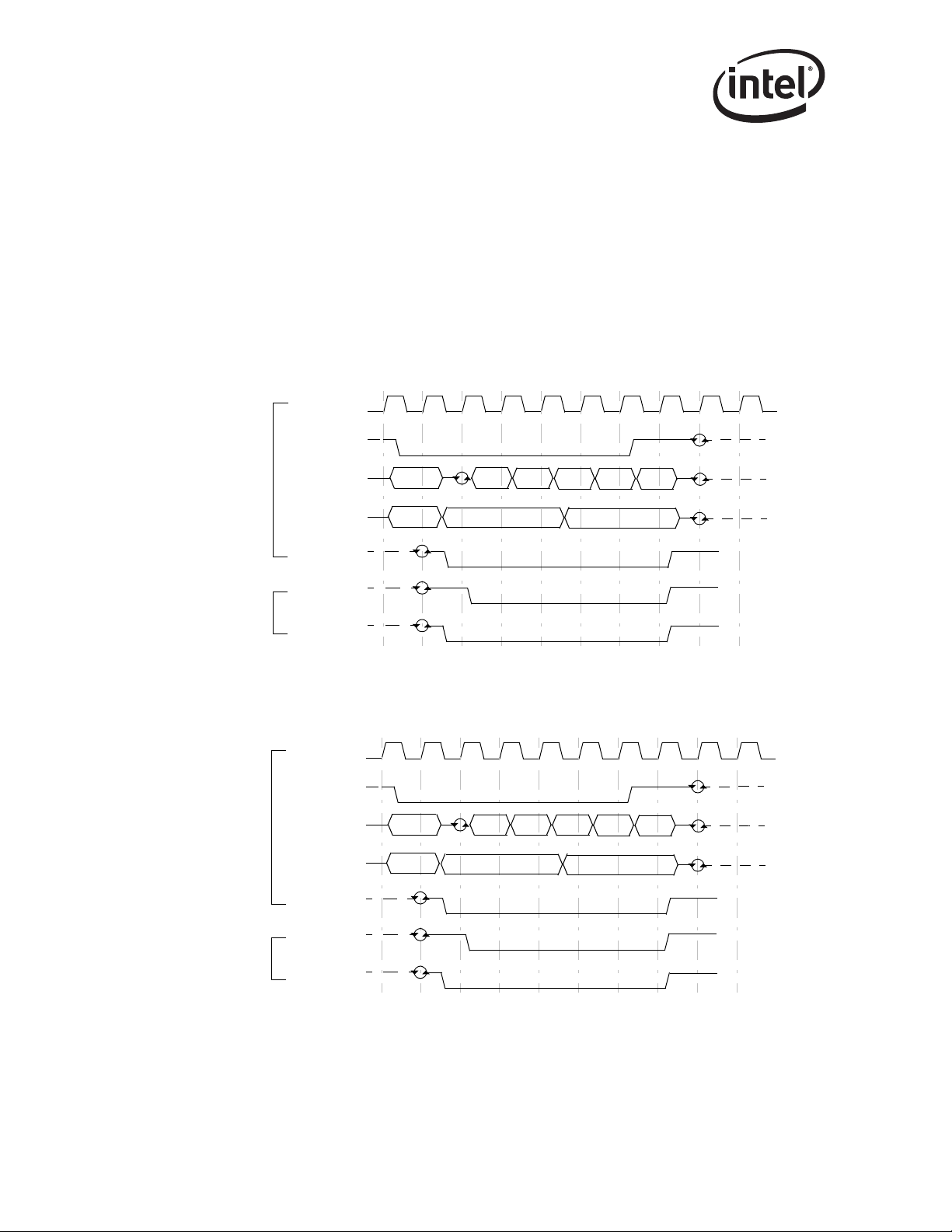

5.2.1.1.3 Retry Premature Accesses

The 82551ER responds with a Retry to any configuration cycle accessing the 82551ER before the

completion of the automatic read of the EEPROM. The 82551ER may continue to Retry any

configuration accesses until the EEPROM read is complete. The 82551ER does not enforce the

rule that the retry master must attempt to access the same address again to complete any delayed

transaction. Any master access to the 82551ER after the completion of the EEPROM read will be

honored. Figure 5 below shows how a Retry looks when it occurs.

Figure 5. PCI Retry Cycle

CLK

FRAME#

IRDY#

TRDY#

DEVSEL#

Networking Silicon — 82551ER

82551ER SYSTEM

STOP#

Note: The 82551ER is considered the target in the above diagram; thus, TRDY# is not asserted.

5.2.1.1.4 Error Handling

Data Parity Errors: The 82551ER checks for data parity errors while it is the target of the

transaction. If an error was detected, the 82551ER always sets the Detected Parity Error bit in the

PCI Configuration Status register, bit 15. Th e 82551ER also asserts PERR#, if the Parity Error

Response bit is set (PCI Configuration Command register, bit 6). The 82551ER does not attempt to

terminate a cycle in which a parity error was detected. This gives the initiator the option of

recovery.

Target-Disconnect: The 82551ER prematurely terminates a cycle in the following cases:

• After accesses to the Flash buffer

• After accesses to its CSR

• After accesses to the configuration space

System Error: The 82551ER repor ts pari ty error d uring the addr ess phas e using the SERR# pi n. If

the SERR# Enable bit in the PCI Configuration Command register or the Parity Error Response bit

is not set, the 82551ER only sets the Detected Parity Error bit (PCI Configuration Status register,

bit 15). If SERR# Enable and Parity Error Response bits are both set, the 82551ER sets the

Signaled System Error bit (P CI C onf i guration Status register, bit 14) as well as the Detected Parity

Error bit and asserts SERR# for one clock.

Datasheet 21

Page 30

82551ER — Networking Silicon

Note: The 82551ER detects a system err or fo r any parity error during an address phase, whether or no t it

is involved in the current transaction.

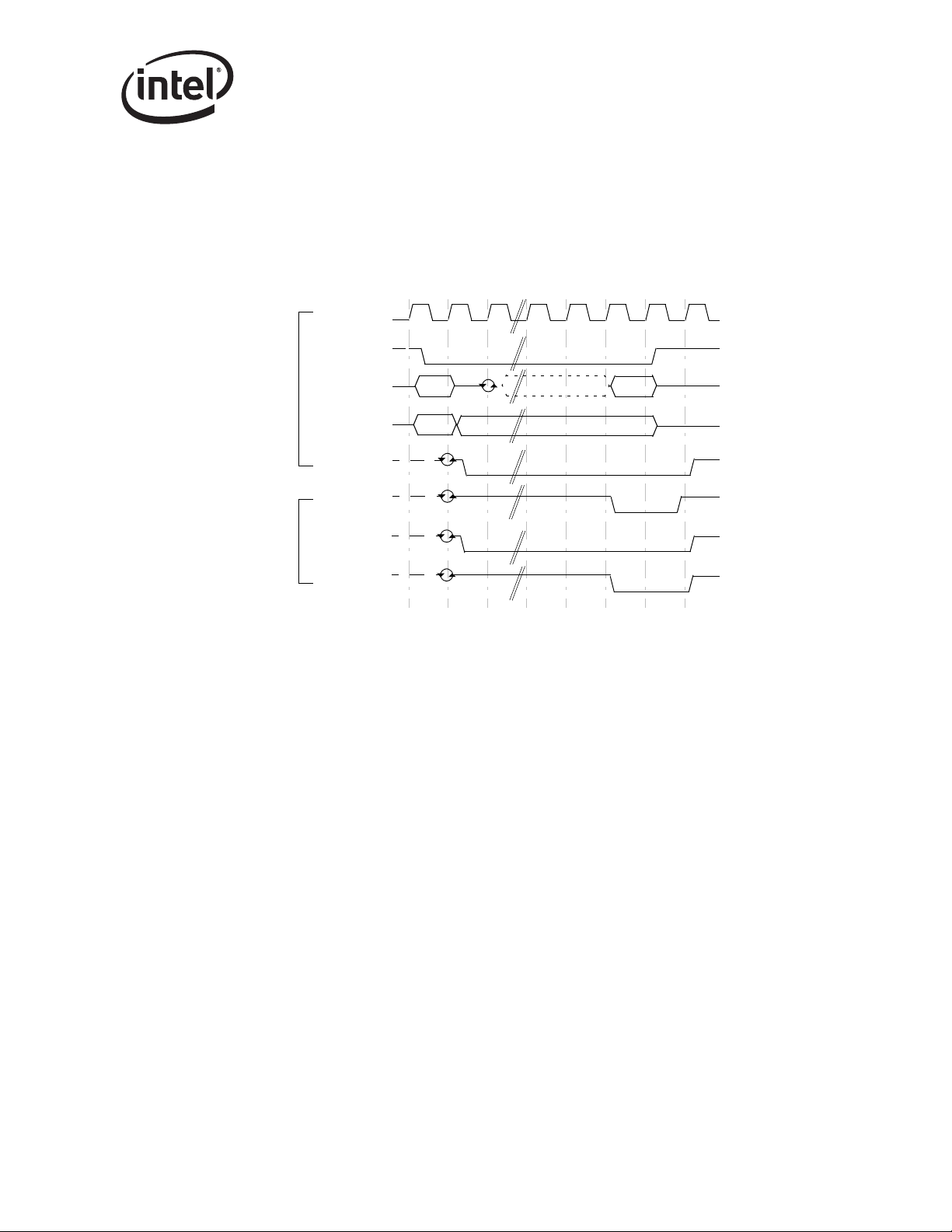

5.2.1.2 Bus Master Operation

As a PCI Bus Master, the 82551ER initiates memory cycles to fetch data for transmission or

deposit received data and to access the memory resi dent contro l structures. Th e 82 551ER p erforms

zero wait state burst read and write cycles to the host main memory. Figure 6 and Figure 7 show

memory read and write burst cycles. For bus master cycles, the 82551ER is the initiator and the

host main memory (or the PCI host bridge, depending on the configur atio n of the system) is the

target.

Figure 6. Memory Read Burst Cycle

CLK

FRAME#

AD

C/BE#

IRDY#

TRDY#

SYSTEM 82551ER

DEVSEL#

Figure 7. Memory Write Burst Cycle

CLK

FRAME#

AD

82551ERSYSTEM

C/BE#

3421 5678910

ADDR

MR BE# BE#

ADDR

MW BE#

DATA

DATA

DATA

DATA

3421 5678910

DATA

DATA

DATA

DATA

BE#

DATA

DATA

IRDY#

TRDY#

DEVSEL#

The CPU provides the 82551ER with action commands and pointers to the data buffers that reside

in host main memory. The 82551ER independently manages these structures and initiates burst

memory cycles to transfer data to and from them. The 82551ER uses the Memory Read Multiple

(MR Multiple) command for burst accesses to data buffers and the Memory Read Line (MR Line)

22 Datasheet

Page 31

Networking Silicon — 82551ER

command for burst accesses to control structur es. For all write accesses to the control s tructure, the

82551ER uses the Memory Write (MW) command. For write accesses to data structure, the

82551ER may use either the Memory Write or Memory Write and Invalidate (MWI) commands.

Read Accesses: The 82551ER performs block transfers from host system memory to perform

frame transmission on the serial link. In this case, the 82551ER initiates zero wait state memory

read burst cycles for these accesses. The length of a burst is bounded by the system and the

82551ER’s internal FIFO. The length of a read burst may also be bounded by the value of the

Transmit DMA Maximum Byte Count in the Configure command. The Transmit DMA Maximum

Byte Count value indicates the maximum number of transmit DMA PCI cycles that will be

completed after an 82551ER internal arbitration.

The 82551ER, as the initiator, drives the address lines AD[31:0], the command and byte enable

lines C/BE#[3:0] and the control lines IRDY# and FRAME#. The 82551ER asserts IRDY# to

support zero wait state burst cycles. The target signals the 82551ER that valid data is ready to be

read by asserting the TRDY# signal.

Write Accesses: The 82551ER performs block transfers to host system memory during frame

reception. In this case, the 82551ER initiates memory write burst cycles to deposit the data, usually

without wait states. The length of a burst is bounded by the system and the 82551ER’s internal

FIFO threshold. The length of a write burst may also be bounded by the value of the Receive DMA

Maximum Byte Count in the Configure comman d. The Receive DMA Maximum Byte Count v alue

indicates the maximum number of receive DMA PCI transfers that will be completed before the

82551ER internal arbitration.

The 82551ER, as the initiator, drives the address lines AD[31:0], the command and byte enable

lines C/BE#[3:0] and the control lines IRDY# and FRAME#. The 82551ER asserts IRDY# to

support zero wait state burst cycles. The 82551ER also drives valid data on AD[31:0] lines during

each data phase (from the first clock and on). The target controls the len gth and si gnals co mpletion

of a data phase by de-assertion and assertion of TRDY#.

5.2.1.2.1 Memory Write and Invalidate

The 82551ER has four Direct Memory Access (DMA) channels. Of these four channels, the

Receive DMA is used to deposit the large number of data bytes received from the link into system

memory. The Receive DMA uses both the Memory Write (MW) and the Memory Write and

Invalidate (MWI) commands. To use MWI, the 82551ER must guarantee the following:

1. Minimum transfer of one cache line

2. Active byte enable bits (or BE[3:0]# are all low) during MWI access

3. The 82551ER may cross the cache line boundary only if it intends to transfer the next cache

line too.

To ensure the above conditions, the 82551ER may use the MWI command only if the following

conditions are true:

1. The Cache Line Size (CLS) written in the CLS register during PCI configuration is 8 or 16

Dwords.

2. The accessed address is cache line aligned.