ICST AV9250F-25-T, ICS9250F-25-T Datasheet

Integrated

Circuit

Systems, Inc.

ICS9250-25

Third party brands and names are the property of their respective owners.

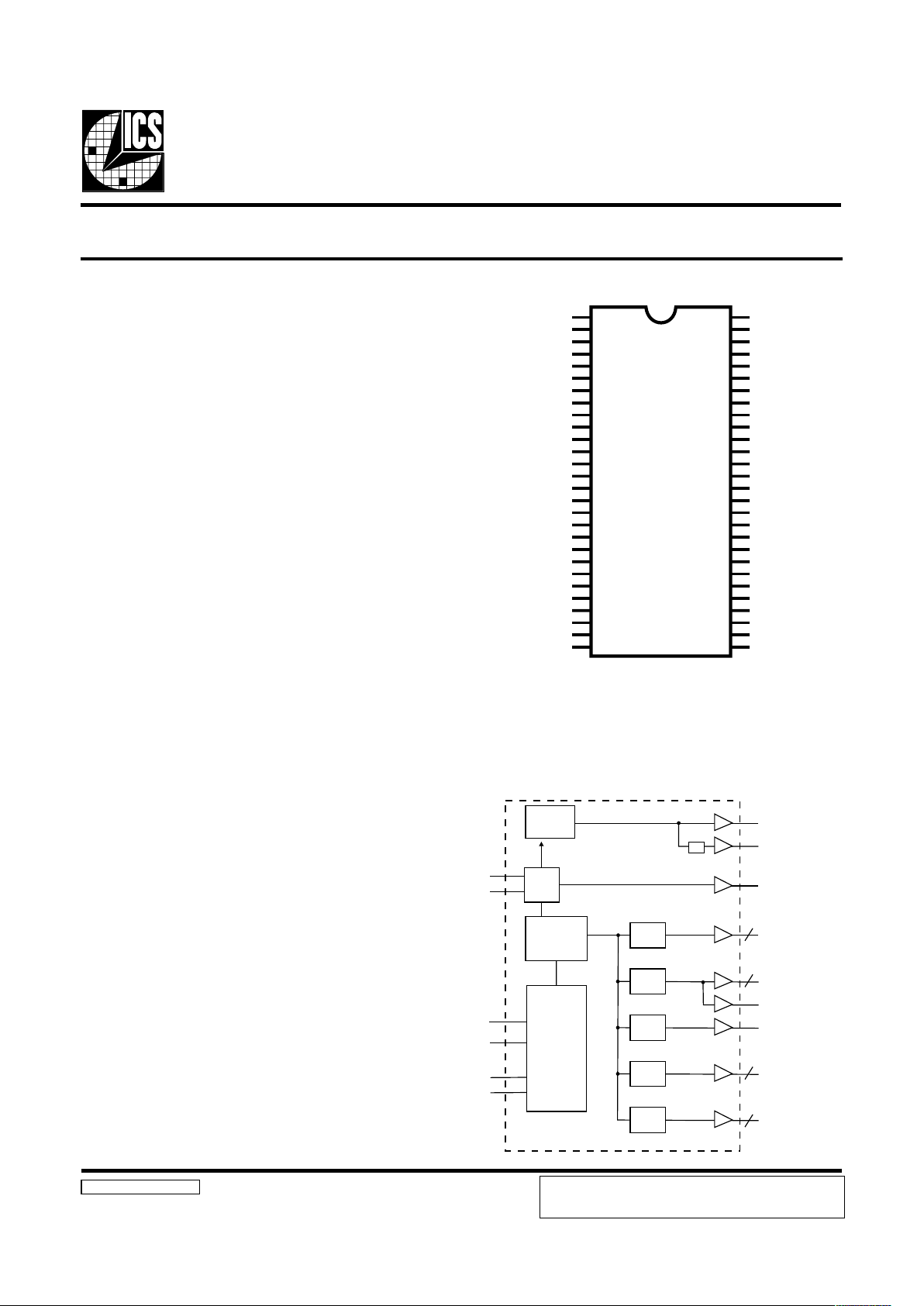

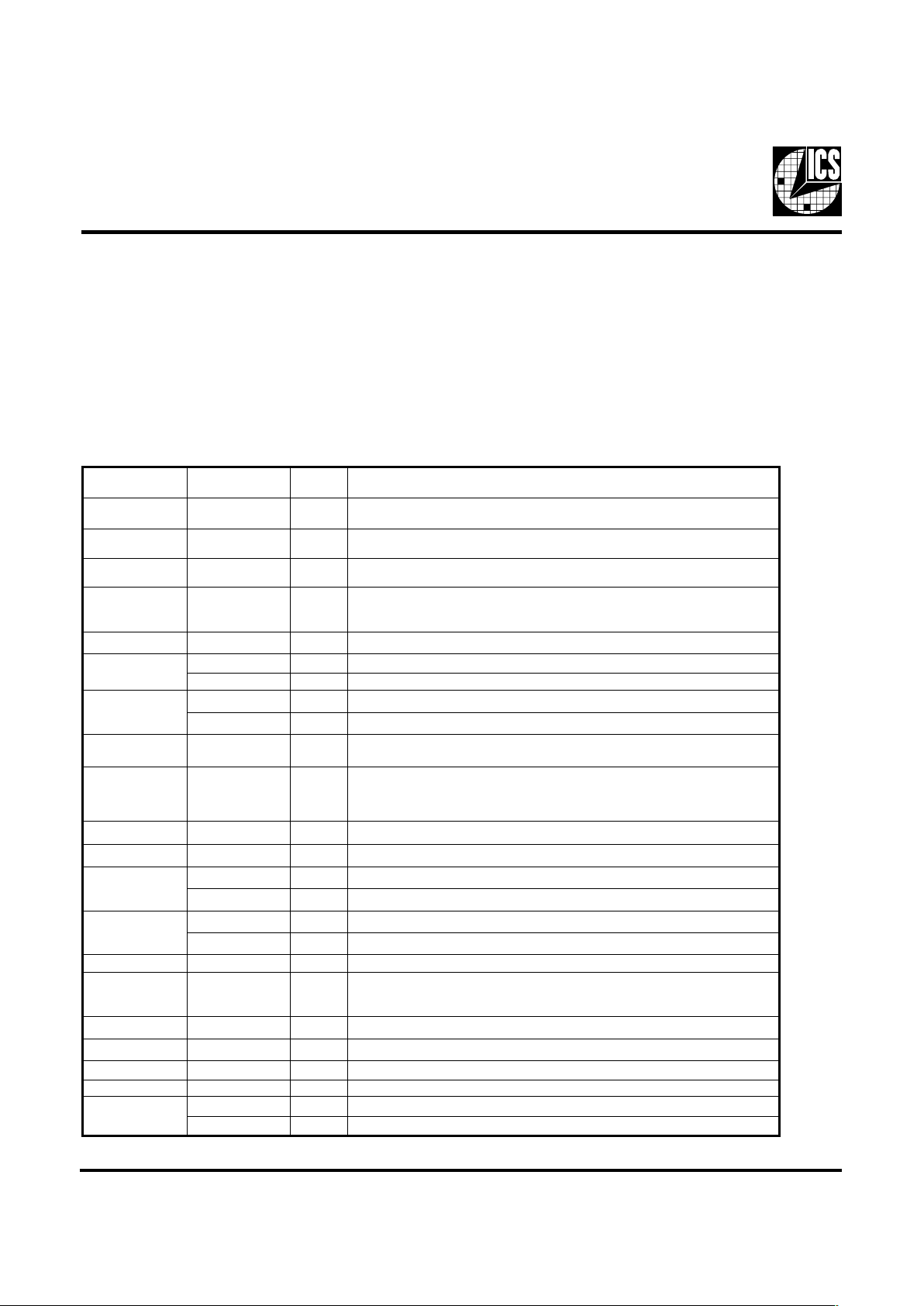

Block Diagram

9250-25 Rev A 10/03/00

Pin Configuration

Recommended Application:

810/810E and Solano type chipset

Output Features:

• 2 - CPUs @ 2.5V, up to 153.33MHz.

• 13 - SDRAM @ 3.3V, up to 153.33MHz.

• 3 - 3V66 @ 3.3V, 2x PCI MHz.

• 8 - PCI @3.3V.

• 1 - 48MHz, @3.3V fixed.

• 1 - 24MHz @ 3.3V

• 1 - REF @3.3V, 14.318MHz.

Features:

• Up to 153.33MHz frequency support

• Support power management through PD#.

• Spread spectrum for EMI control (± 0.25%)

center spread.

• Uses external 14.318MHz crystal

• FS pins for frequency select

Key Specifications:

• CPU Output Jitter: <250ps

• IOAPIC Output Jitter: <500ps

• 48MHz, 3V66, PCI Output Jitter: <500ps

• Ref Output Jitter. <1000ps

• CPU Output Skew: <175ps

• PCI Output Skew: <500ps

• 3V66 Output Skew <175ps

• For group skew timing, please refer to the

Group Timing Relationship Table.

Frequency Generator & Integrated Buffers for Celeron & PII/III™

56-Pin 300 mil SSOP

1. These pins will have 1.5 to 2X drive strength.

* 120K ohm pull-up to VDD on indicated inputs.

SDATA

SCLK

PLL2

PLL1

Spread

Spectrum

48MHz

24MHz

CPUCLK [1:0]

2

12

8

3

SDRAM [11:0]

IOAPIC

PCICLK [7:0]

SDRAM_F

3V66 [2:0]

X1

X2

XTAL

OSC

CPU

DIVDER

SDRAM

DIVDER

IOAPIC

DIVDER

PCI

DIVDER

3V66

DIVDER

FS[4:0]

PD#

Control

Logic

Config.

Reg.

/ 2

REF0

VDDREF

X1

X2

GNDREF

GND3V66

3V66-1

3V66-2

VDD3V66

VDDPCI

*FS0/PCICLK0

*FS1/PCICLK1

PCICLK2

GNDPCI

PCICLK3

PCICLK4

PCICLK5

VDDPCI

PCICLK6

PCICLK7

GNDPCI

PD#

SCLK

SDATA

VDDSDR

SDRAM11

SDRAM10

GNDSDR

3V66-0

1

1

REF0/FS4*

VDDLAPIC

IOAPIC

VDDLCPU

CPUCLK0

CPUCLK1

GNDLCPU

GNDSDR

SDRAM0

SDRAM1

SDRAM2

VDDSDR

SDRAM3

SDRAM4

SDRAM5

GNDSDR

SDRAM6

SDRAM7

SDRAM_F

VDDSDR

GND48

24MHz/FS2*

48MHz/FS3*

VDD48

VDDSDR

SDRAM8

SDRAM9

GNDSDR

1

1

ICS9250-25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

Preliminary Product Preview

PRODUCT PREVIEW documents contain information on new products

in the sampling or preproduction phase of development. Characteristic

data and other specifications are subject to change without notice.

2

ICS9250-25

Preliminary Product Preview

Third party brands and names are the property of their respective owners.

General Description

Pin Configuration

NIP

REBMUN

EMANNIPEPYTNOITPIRCSED

,52,81,01,9,1

54,73,33,23

DDVRWPylppusrewopV3.3

21XNI

kcabdeefdna)Fp33(pacdaollanretnisah,tupnilatsyrC

2Xmorfrotsiser

32XTUO

daollanretnisaH.zHM813.41yllanimon,tuptuolatsyrC

)Fp33(pac

,12,41,5,4

,63,92,82

94,14

DNGRWPylppusV3.3rofsnipdnuorG

6,7,8]0:2[66V3TUOBUHrofstuptuokcolczHM66dexiFV3.3

11

0KLCICP

1

TUOSKLCUPCsuonorhcnyShtiw,stuptuokcolcICPV3.3

0SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

21

1KLCICP

1

NISKLCUPCsuonorhcnyShtiw,stuptuokcolcICPV3.3

1SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

,61,71,91,02

31,51

]2:7[KLCICPTUOSKLCUPCsuonorhcnyShtiw,stuptuokcolcICPV3.3

22#DPNI

otniecivedehtnwodrewopotdesuniptupniwolevitcasuonorhcnysA

dnaOCVehtdnadelbasideraskcolclanretniehT.etatsrewopwola

ebtonlliwnwodrewopehtfoycnetalehT.deppotseralatsyrceht

.sm3nahtretaerg

32KLCSNIIfotupnikcolC

2

tupniC

42ATADSNIIroftupniataD

2

.tupnilairesC

43

zHM84TUOBSUroftuptuokcolczHM84dexiFV3.3

3SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

53

2SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

zHM42TUOtuptuozHM42dexifV3.3

83F_MARDSTUOIybdetceffatonMARDSzHM001gninnureerfV3.3

2

C

,34,44,74,84

,13,93,04,24

62,72,03,03

]0:11[MARDSTUO

ffodenrutebnacstuptuoMARDSllA.zHM001gninnurtuptuoV3.3

Ihguorht

2

C

05LDNGRWPCIPA&UPCrofylppusrewopV5.2rofdnuorG

25,15]0:1[KLCUPCTUO.snipSFmorfdeviredycneuqerftuptuO.tuptuokcolcsubtsoHV5.2

55,35LDDVRWPCIPAOI,UPCrofylppyusrewopV5.2

45CIPAOITUO.zHM76.61tagninnurstuptuokcolcV5.2

65

4SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

0FER

1

TUO.tuptuokcolcecnereferzHM813.41,V3.3

The ICS9250-25 is a single chip clock solution for desktop designs using the 810/810E and Solano style chipset. It provides all

necessary clock signals for such a system.

Spread spectrum may be enabled through I

2

C programming. Spread spectrum typically reduces system EMI by 8dB to 10dB. This

simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS9250-25 employs a proprietary

closed loop design, which tightly controls the percentage of spreading over process and temperature variations.

Serial programming I

2

C interface allows changing functions, stop clock programming and frequency selection.

3

ICS9250-25

Preliminary Product Preview

Third party brands and names are the property of their respective owners.

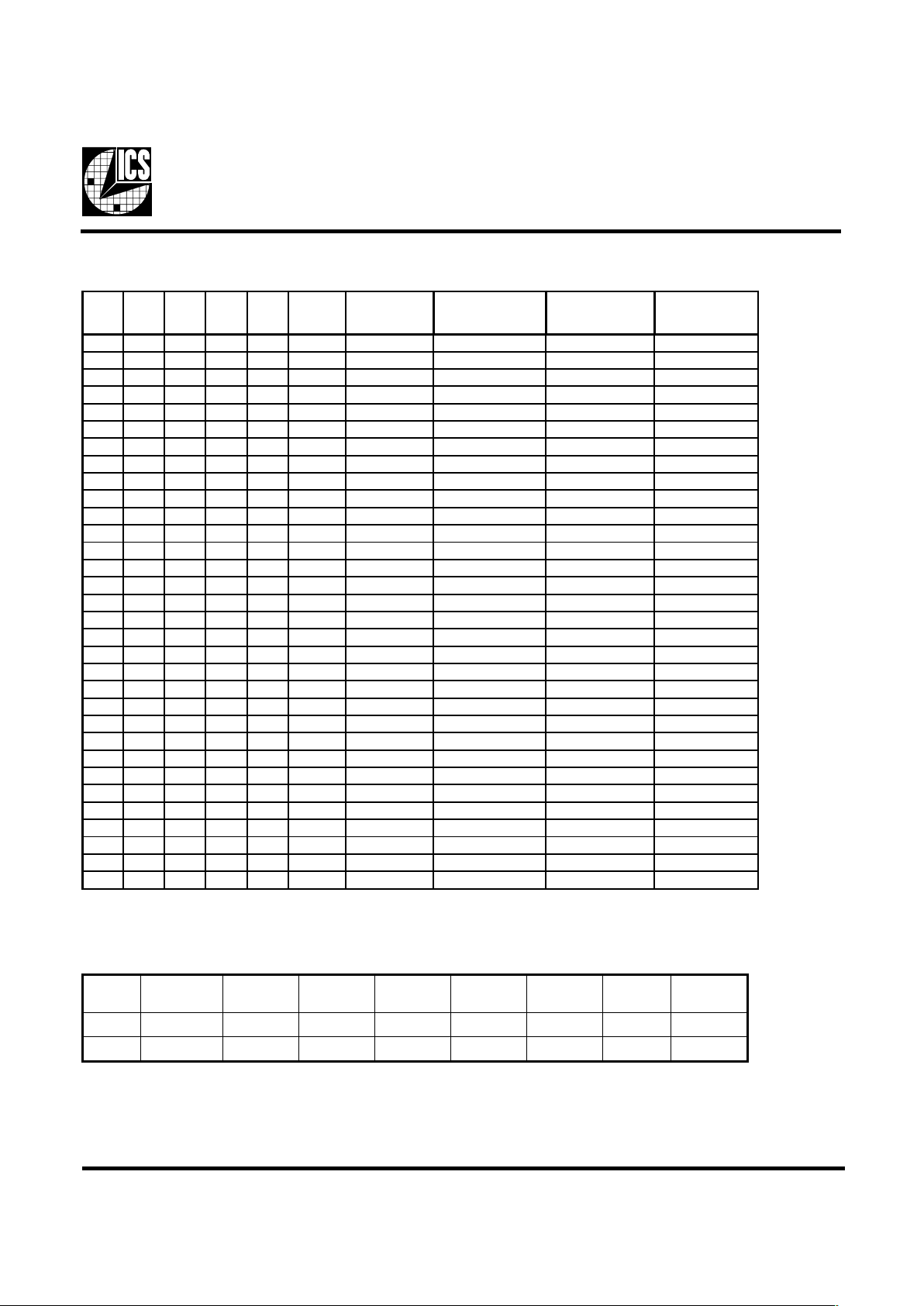

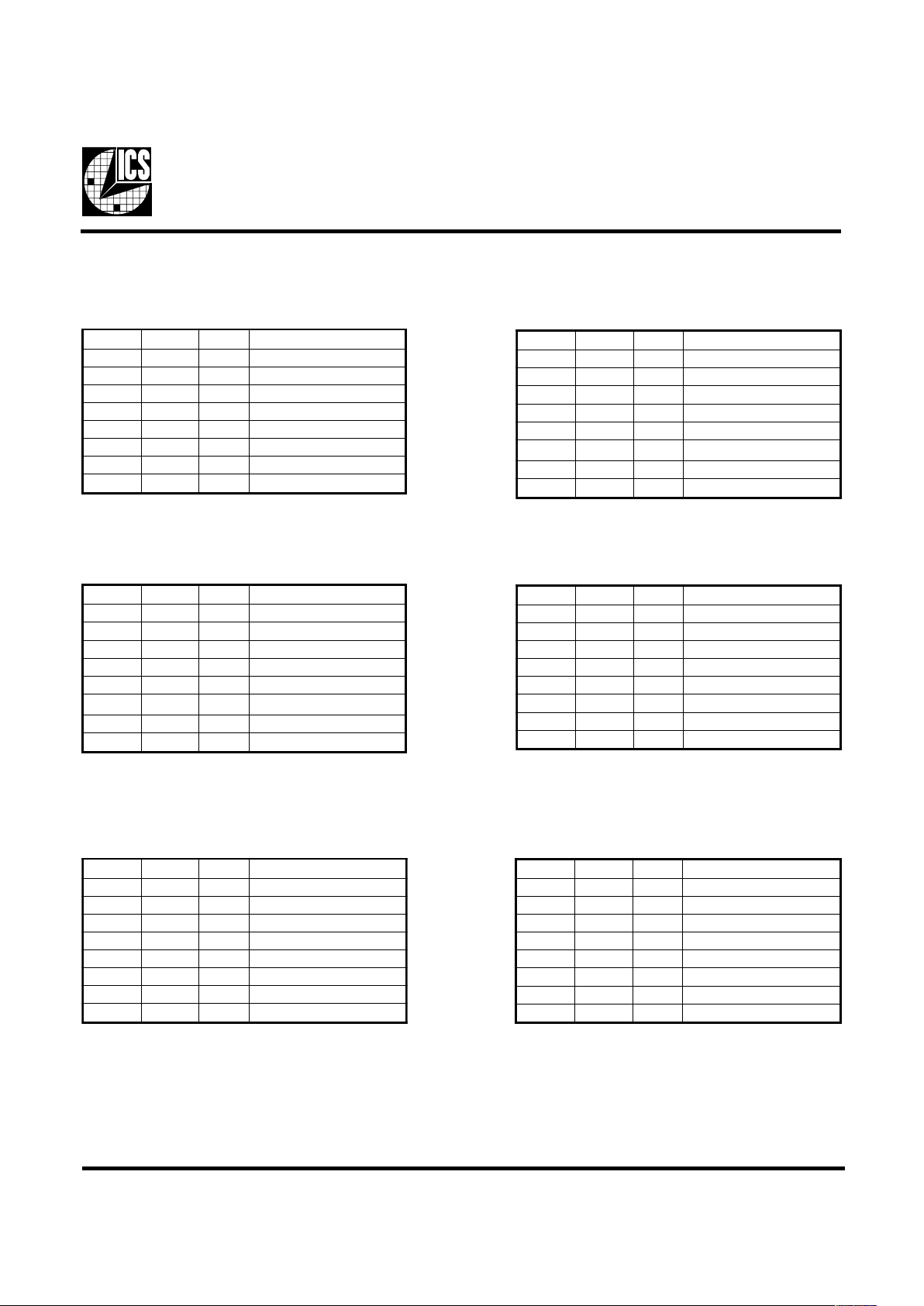

Frequency Selection

Clock Enable Configuration

4SF3SF2SF1SF0SF

UPC

zHM

MARDS

zHM

zHM66V3

ICP

zHM

zHMCIPAOI

00000 00.5505.2800.555.7257.31

00001 00.0600.0900.060351

00010 08.6602.00108.664.337.61

00011 33.8605.20133.86561.435280.71

00100 00.0700.50100.07535.71

00101 00.2700.80100.276381

00110 00.5705.21100.575.7357.81

00111 00.7705.51100.775.8352.91

01000 03.3803.3835.558.729.31

01001 00.0900.0900.060.030.51

01010 03.00103.00178.664.337.61

01011 00.30100.30176.863.432.71

01100 05.21105.21100.575.738.81

01101 00.51100.51176.673.832.91

01110 00.02100.02100.080.040.02

01111 00.52100.52133.387.148.02

10000 00.82100.82100.460.230.61

1000 1 00.03100.03100.565.233.61

100 10 07.33107.33158.664.337.61

100 11 00.73100.73105.863.431.71

10 100 00.04100.04100.070.535.71

10 10 1 00.54100.54105.273.631.81

10 110 00.05100.05100.575.738.81

10111 33.35133.35176.673.832.91

11000 00.52157.3905.263.136.51

11001 00.03105.7900.565.233.61

11010 07.33182.00158.664.337.61

11011 00.73157.20105.863.431.71

11100 00.04100.50100.070.535.71

11101 00.54157.80105.273.631.81

11110 00.05105.21100.575.738.81

11111 33.35100.51176.673.832.91

#DPKLCUPCMARDSCIPAOIzHM66KLCICP

,FER

zHM84

csOsOCV

0WOLWOLWOLWOLWOLWOLFFOFFO

1NONONONONONONONO

4

ICS9250-25

Preliminary Product Preview

Third party brands and names are the property of their respective owners.

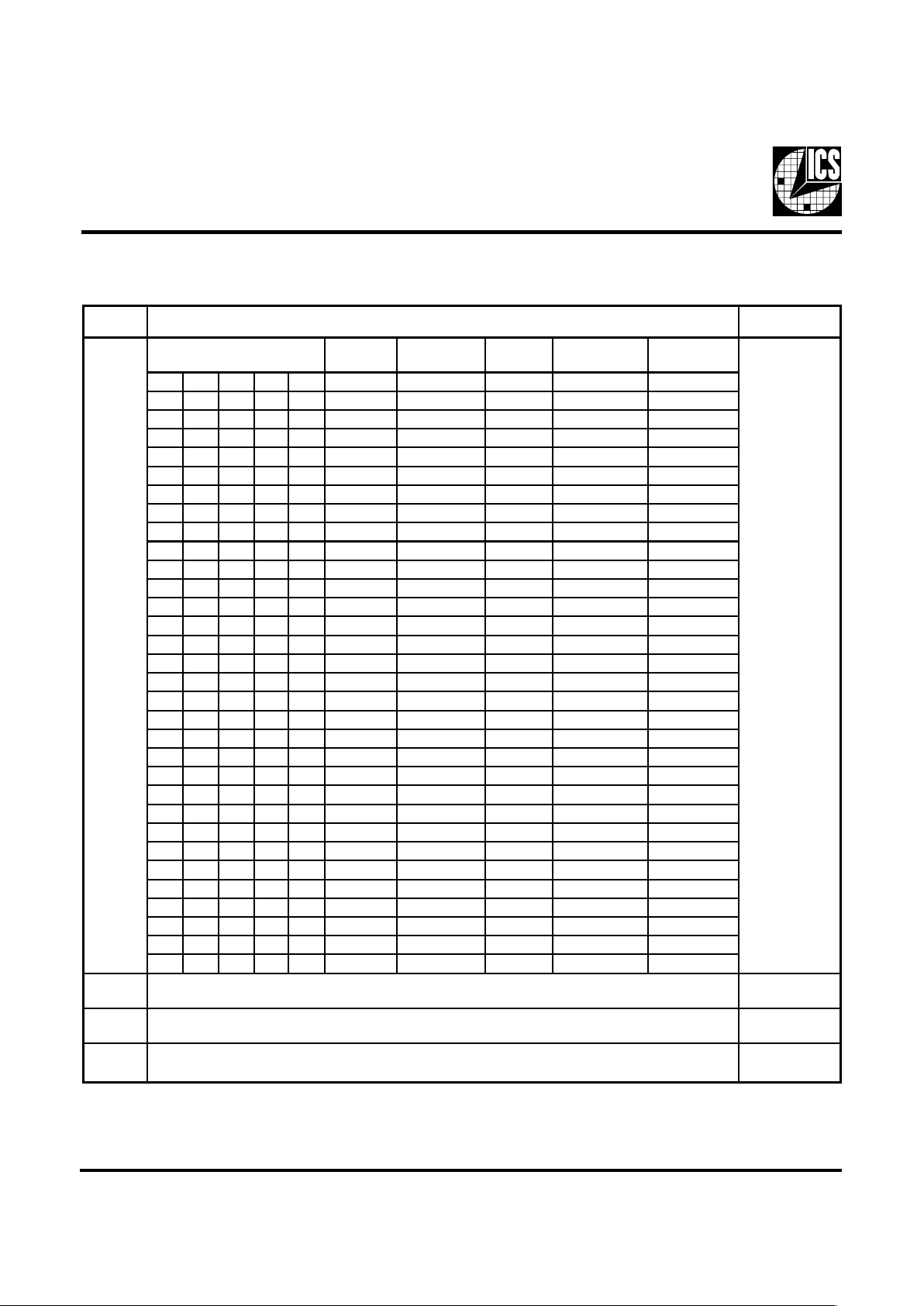

Byte 0: Functionality and frequency select register (Default=0)

(1 = enable, 0 = disable)

Notes:

1.

Default at power-up will be for latched logic inputs to define frequency, as displayed by Bit 3.

2. The I

2

C readback for Bit 2, 7:4 indicate the revision code.

tiB

noitpircseD

DWP

tiB

)4:7,2(

)4:7,2(tiB

KLCUPC

zHM

MARDS

zHM

66V3

zHM

KLCICP

CIPAOI

zHM

10000

1etoN

00000 00.5505.2800.555.7257.31

00001 00.0600.0900.060351

00010 08.6602.00108.664.337.61

00011 33.8605.20133.86561.435280.71

00100 00.0700.50100.07535.71

00101 00.2700.80100.276381

00110 00.5705.21100.575.7357.81

00111 00.7705.51100.775.8352.91

01000 03.3803.3835.558.729.31

01001 00.0900.0900.060.030.51

01010 03.00103.00178.664.337.61

01011 00.30100.30176.863.432.71

01100 05.21105.21100.575.738.81

01101 00.51100.51176.673.832.91

01110 00.02100.02100.080.040.02

01111 00.52100.52133.387.148.02

10000 00.82100.82100.460.230.61

1000 1 00.03100.03100.565.233.61

10010 07.33107.33158.664.337.61

10011 00.73100.73105.863.431.71

10100 00.04100.04100.070.535.71

1010 1 00.54100.54105.273.631.81

10110 00.05100.05100.575.738.81

10111 33.35133.35176.673.832.91

11000 00.52157.3905.263.136.51

11001 00.03105.7900.565.233.61

11010 07.33182.00158.664.337.61

11011 00.73157.20105.863.431.71

11100 00.04100.50100.070.535.71

11101 00.54157.80105.273.631.81

11110 00.05105.21100.575.738.81

11111 33.35100.51176.673.832.91

3tiB

stupnidehctal,tceleserawdrahybdetcelessiycneuqerF-0

4:6,2tiBybdetcelessiycneuqerF-1

0

1tiB

lamroN-0

daerpSretneC%52.0±elbanemurtcepsdaerpS-1

1

0tiB

gninnuR-0

stuptuollaetatsirT-1

0

5

ICS9250-25

Preliminary Product Preview

Third party brands and names are the property of their respective owners.

Byte 1: Control Register

(1 = enable, 0 = disable)

Notes:

1. Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be configured at

power-on and are not expected to be configured during the normal modes of operation.

2. PWD = Power on Default

tiB#niPDWPnoitpircseD

7tiB-X #3SF

6tiB-X #0SF

5tiB-X #2SF

4tiB531 zHM42

3tiB-1 )devreseR(

2tiB431 zHM84

1tiB-1 )devreseR(

0tiB831 F_MARDS

tiB#niPDWPnoitpircseD

7tiB021 7KLCICP

6tiB911 6KLCICP

5tiB711 5KLCICP

4tiB611 4KLCICP

3tiB511 3KLCICP

2tiB31

1

2KLCICP

1tiB211 1KLCICP

0tiB111 0KLCICP

Byte 3: Control Register

(1 = enable, 0 = disable)

Byte 2: Control Register

(1 = enable, 0 = disable)

tiB#niPDWPnoitpircseD

7tiB931 7MARDS

6tiB041 6MARDS

5tiB241 5MARDS

4tiB341 4MARDS

3tiB441 3MARDS

2tiB64

1

2MARDS

1tiB741 1MARDS

0tiB841 0MARDS

tiB#niPDWPnoitpircseD

7tiB81 2_66V3

6tiB61 0_66V3

5tiB71 1_66V3

4tiB-X #4SF

3tiB451 CIPAOI

2tiB-X #1SF

1tiB151 1KLCUPC

0tiB251 0KLCUPC

Byte 4: Control Register

(1 = enable, 0 = disable)

tiB#niPDWPnoitpircseD

7tiB-1 )devreseR(

6tiB-1 )devreseR(

5tiB-1 )devreseR(

4tiB-1 )devreseR(

3tiB621 11MARDS

2tiB721 01MARDS

1tiB031 9MARDS

0tiB131 8MARDS

Byte 5: Control Register

(1 = enable, 0 = disable)

Byte 6: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

Note: Dont write into this register, writing into this register

can cause malfunction

tiB#niPDWPnoitpircseD

7tiB-0 )etoN(devreseR

6tiB-0 )etoN(devreseR

5tiB-0 )etoN(devreseR

4tiB-0 )etoN(devreseR

3tiB-0 )etoN(devreseR

2tiB-1 )etoN(devreseR

1tiB-1 )etoN(devreseR

0tiB-0 )etoN(devreseR

Loading...

Loading...