Integrated

Circuit

Systems, Inc.

ICS9250-22

Third party brands and names are the property of their respective owners.

9250-22 Rev B 12/08/00

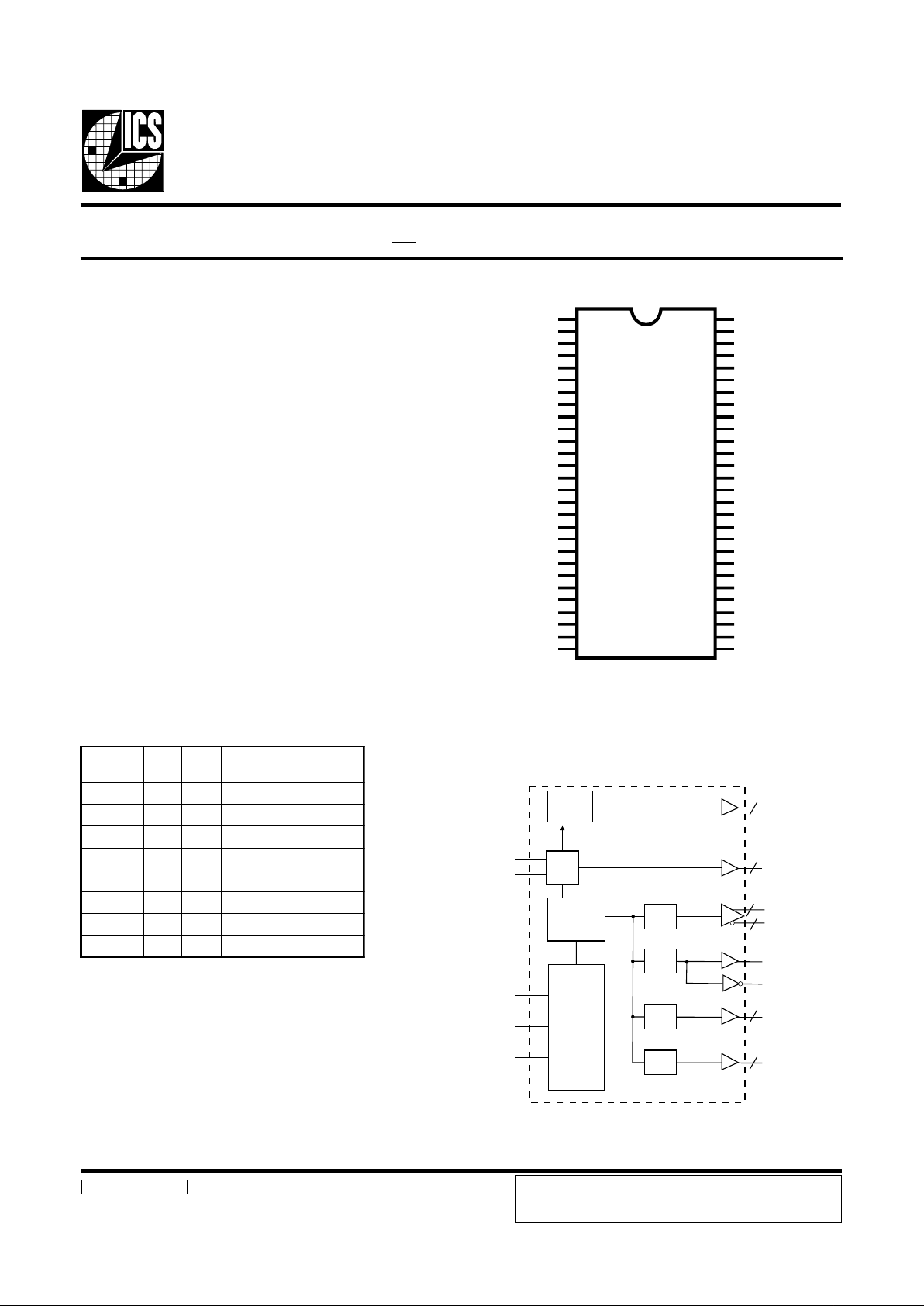

Pin Configuration

56-Pin 300mil SSOP & TSSOP

Recommended Application:

P IV Chipset Support

Output Features:

• 4 Differential CPU Clock Pairs @ 3.3V

• 2 - 3V MREF clocks for memory reference seeds,

(separate single ended but 180 degrees out of phase)

• 4 - 66MHz reference output

• 10 - 3V 33MHz PCI clocks

• 2 - 48MHz clocks

• 2 - 14.318 reference output

Features:

• Support power management: Power Down Mode

• Supports Spread Spectrum modulation: 0 to -0.5% down

spread.

• Uses external 14.318MHz crystal

• Select logic for Differential Swing Control, Test mode,

Tristate, Power down, Spread Spectrum, limited

frequency select, selective clock enable.

• External resistor for current reference

• FS pins for frequency select

Key Specifications:

• 3V66 Output jitter <300ps

• CPU Output Jitter <200ps

• MREF Output jitter <250ps

Frequency Generator for P IV™

GND

REF

VDDREF

X1

X2

GNDREF

PCICLK0

PCICLK1

VDDPCI

PCICLK2

PCICLK3

GNDPCI

PCICLK4

PCICLK5

VDDPCI

PCICLK6

PCICLK7

GNDPCI

PCICLK8

PCICLK9

VDDPCI

SEL100/133

GND48

48MHz

48MHz

VDD48

PD#

MULTSEL0/

MULTSEL1/REF

FS0/

FS1/

VDDMREF

3VMREF

3VMREF_B

GNDMREF

SPREAD#

CPUCLKST3

CPUCLKSC3

VDDCPU

CPUCLKST2

CPUCLKSC2

GNDCPU

CPUCLKST1

CPUCLKSC1

VDDCPU

CPUCLKST0

CPUCLKSC0

GNDCPU

I REF

VDDA

GNDA

VDD3V66

3V66-3

3V66-2

GND3V66

GND3V66

3V66-1

3V66-0

VDD3V66

ICS9250-22

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

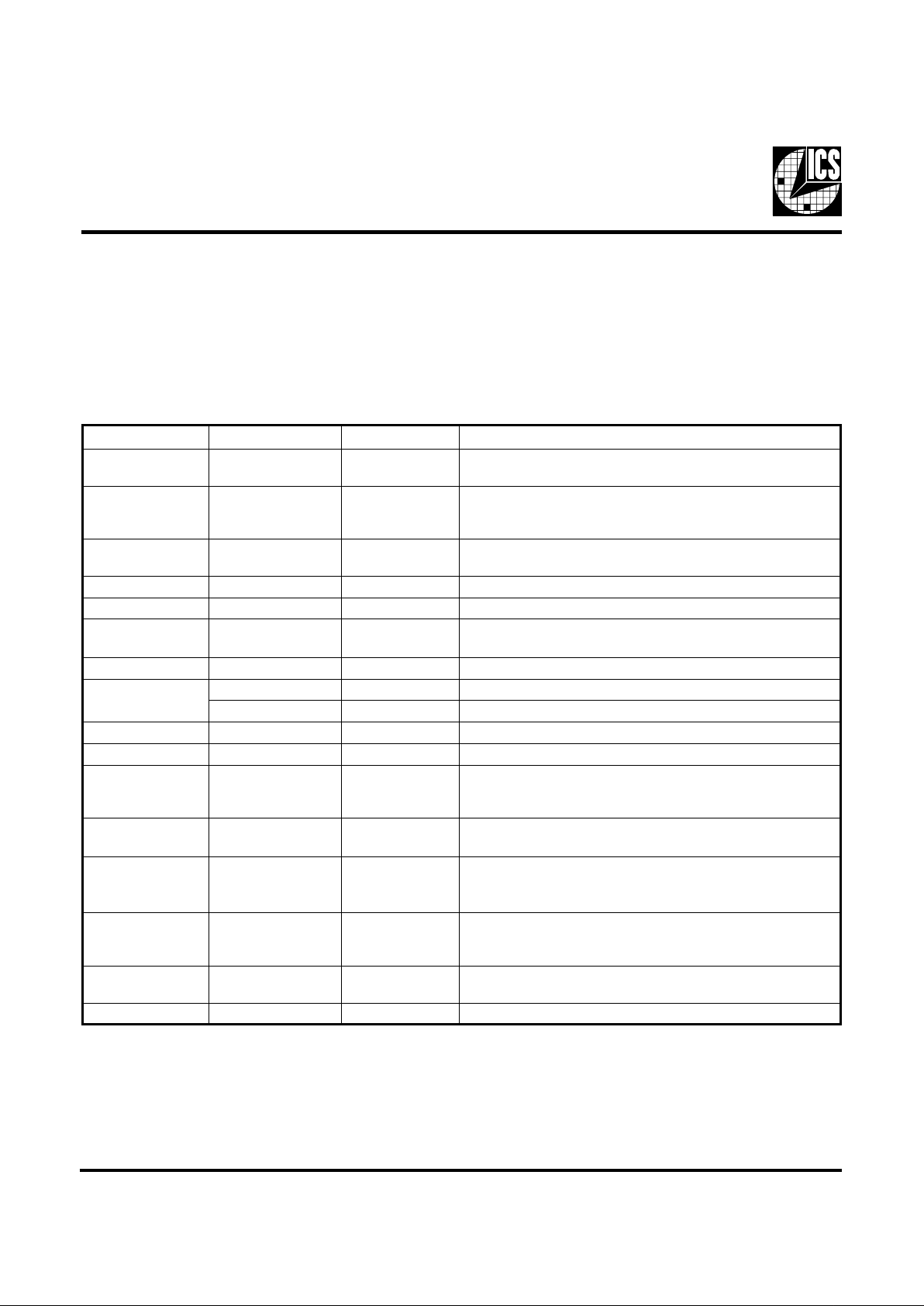

Functionality

PLL2

PLL1

Spread

Spectrum

48MHz

3VMREF

PCICLK (9:0)

3VMREF_B

3V66 (3:0)

4

10

2

2

X1

X2

XTAL

OSC

CPU

DIVDER

3VMREF

DIVDER

PCI

DIVDER

3V66

DIVDER

PD#

SPREAD#

MULTSEL (1:0)

SEL100/133

FS(1:0)

Control

Logic

Config.

Reg.

REF

4

4

CPUCLKST (3:0)

CPUCLKSC (3:0)

/331LES

001

0SF1SFnoitcnuF

000 zHM001evitcA

001 )devreseR(

010 )devreseR(

011 stuptuollaetatsirT

100 zHM331evitcA

101 )devreseR(

110 )devreseR(

111 edoMtseT

Block Diagram

Po wer Groups

VDDREF , GNDREF= REF, X1, X2

VDDPCI, GNDPCI = PCICLK

VDD48, GND48 = 48MHz, PLL2

VDD3V66, GND3V66=3V66

VDDCPU, GNDCPU = CPUCLK

VDDMREF , GNDMREF=3VMREF, 3VMREF_B

VDDA=VDD (core supply voltage 3.3V)

GNDA=Ground for core supply

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9250-22

Third party brands and names are the property of their respective owners.

General Description

Pin Configuration

The ICS9250-22 is a single chip clock solution.

Spread spectrum typically reduces system EMI by 8dB to 10dB. This simplifies EMI qualification without resorting to

board design iterations or costly shielding. The ICS9250-22 employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and temperature variations.

REBMUNNIPEMANNIPEPYTNOITPIRCSED

,23,42,91,31,7,1

35,64,04,73,33

DNGRWPylppusV3.3rofsnipdnuorG

2,3)0:1(LESTLUM/FERNI

dnapu-rewopnodesneserastupni1LESTLUMdna0LESTLUM

V3notuptuorofdesugniebnipehtotroirpdehctalyllanretnineht

.skcolczHM813.41

,92,72,22,61,01,4

65,94,34,83,63

DDVRWPylppusrewopV3.3

51XtupnIlatsyrC2XtupnilatsyrCzHM813.41

62XtuptuOlatsyrC1XtuptuolatsyrCzHM813.41

,51,71,81,02,12

8,9,11,21,41

)0:9(KLCICPTUOstuptuokcolcICP

32331/001LESNIzHM331=hgiH,zHM001=woL.tceleSycneuqerFUPC

52,62

)0:1(SFNIsniptcelesycneuqerF

zHM84TUOtuptuokcolczHM84

82#DPNI.woLevitcA.edomnwod-rewopsekovnI

03,13,43,53)0:3(66V3TUOskcolcecnereferzHM66

93FERITUO

.sriapKLCUPCehtroftnerrucecnereferehtsehsilbatsenipsihT

otredronidnuorgotdeitrotsisernoisicerpdexifasekatnipsihT

.tnerrucetairporppaehthsilbatse

24,54,84,15)0:3(TSKLCUPCTUO

dehctiwseraesehT.stuptuoUPCriaplaitnereffidfoskcolc"eurT"

.saibegatlovrofderiuqererasrotsiserlanretxednastuptuotnerruc

14,44,74,05)0:3(CSKLCUPCTUO

esehT.stuptuoUPCriaplaitnereffidfoskcolc"yrotnemelpmoC"

rofderiuqererasrotsiserlanretxednastuptuotnerrucdehctiwsera

.saibegatlov

25#DAERPSNI

tsohlaitnereffiDehtnoytilanoitcnufmurtcepSdaerpSsekovnI

ICPzHM33dna,skcolczHM66,skcolcb_feRM/feRM,skcolc

woLevitcA.skcolc

45B_FERMV3TUO

revirdkcolcyromemotecnereferV3

)fermV3htiwesahpfotuo(

55FERMV3TUOrevirdkcolcyromemotecnereferV3

3

ICS92 50-22

Third party brands and names are the property of their respective owners.

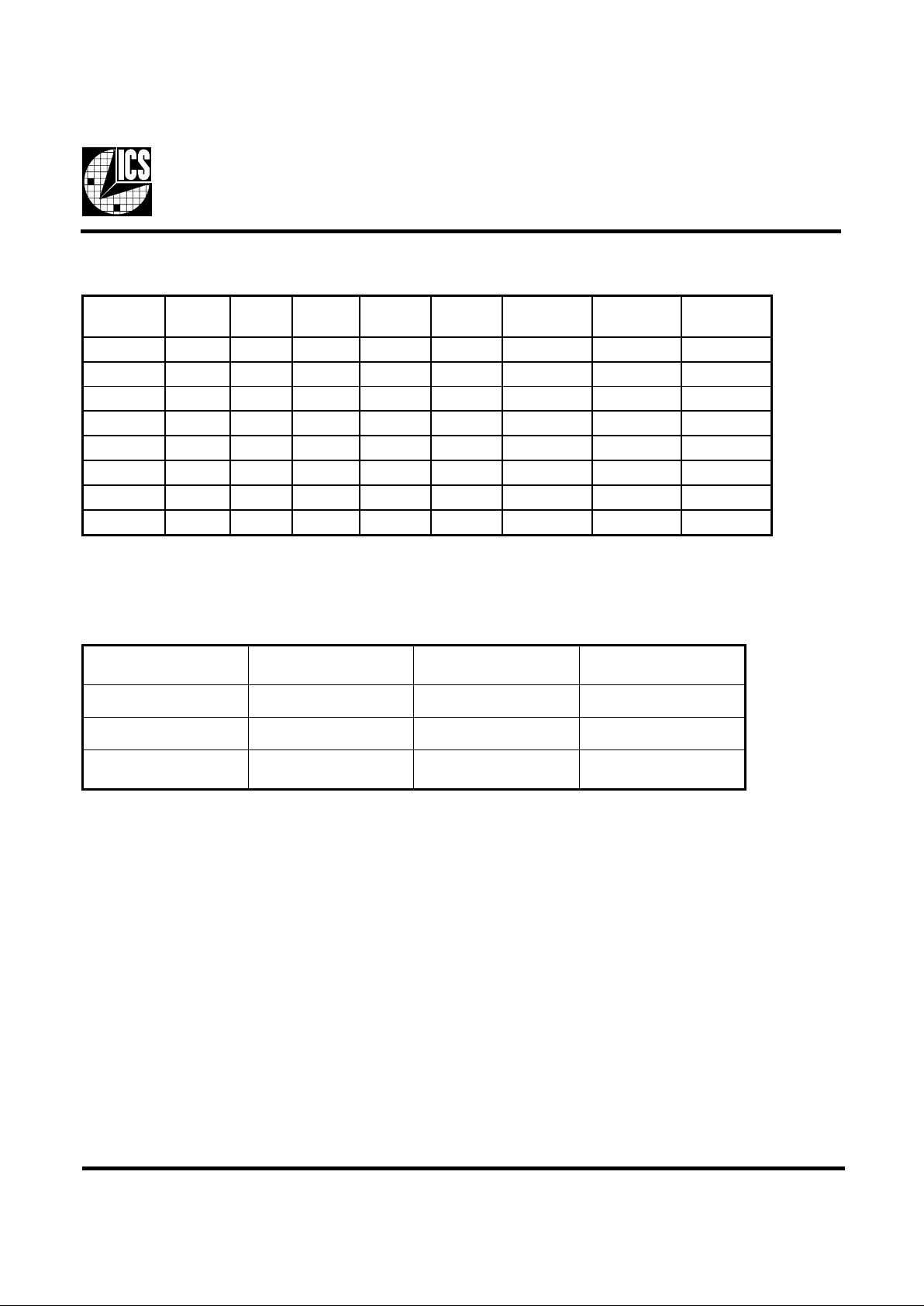

Truth Table

Group Offset Limits

puorGtesffO

sdaoLtnemerusaeM

)depmul(

stnioPerusaeM

66V3otUPCtnemeriuqeRoN

ICPotUPC

ICPot66V3

sn5.3-5.1

sdael66V3

Fp03V5.1

LES

001/331

0SF1SFUPCfeRM66V3ICPzHM84FER

000 zHM001zHM05zHM66zHM33zHM84zHM813.41

001A/NA/NA/NA/NA/NA/N

010A/NA/NA/NA/NA/NA/N

011 etatsirTetatsirTetatsirTetatsirTetatsirTetatsirT

100 zHM331zHM66zHM66zHM33zHM84zHM813.41

101A/NA/NA/NA/NA/NA/N

110A/NA/NA/NA/NA/NA/N

111 2/KLCT4/KLCTKLCT6/KLCTKLCT

4

ICS9250-22

Third party brands and names are the property of their respective owners.

CPUCLK Buffer Configuration

snoitidnoCnoitarugifnoCdaoLniMxaM

tuoI

)V03.3(lanimon=ddV

,0MfosnoitanibmocllA

ninwohsrRdna1M

wolebelbat

rofdaoltsetlanimoN

noitarugifnocnevig

%7- I lanimon%7+ I lanimon

tuoI

%5±03.3=ddV

,0MfosnoitanibmocllA

ninwohsrRdna1M

wolebelbat

rofdaoltsetlanimoN

noitarugifnocnevig

%21- I lanimon%21+ I lanimon

0LESTLUM1LESTLUM

tegraTdraoB

ZmreT/ecarT

,RecnerefeR

=ferI

)rR*3(/ddV

tuptuO

tnerruC

,Z@hoV

Am23.2=ferI

00 smho06

%1574=rR

Am23.2=ferI

ferI*5=hoI06@V17.0

00 smho05

%1574=rR

Am23.2=ferI

ferI*5=hoI05@V95.0

01 smho06

%1574=rR

Am23.2=ferI

ferI*6=hoI062/V58.0

01 smho05

%1574=rR

Am23.2=ferI

ferI*6=hoI05@V17.0

10 smho06

%1574=rR

Am23.2=ferI

ferI*4=hoI06@V65.0

10 smho05

%1574=rR

Am23.2=ferI

ferI*4=hoI05@V74.0

11 smho06

%1574=rR

Am23.2=ferI

ferI*7=hoI06@V99.0

11 smho05

%1574=rR

Am23.2=ferI

ferI*7=hoI05@V28.0

00 )viuqeCD(03

%1122=rR

Am5=ferI

ferI*5=hoI03@V57.0

00 )viuqeCD(52

%1122=rR

Am5=ferI

ferI*5=hoI02@V26.0

01 )viuqeCD(03

%1122=rR

Am5=ferI

ferI*6=hoI03@V09.0

01 )viuqeCD(52

%1122=rR

Am5=ferI

ferI*6=hoI02@V57.0

10 )viuqeCD(03

%1122=rR

Am5=ferI

ferI*4=hoI02@06.0

10 )viuqeCD(52

%1122=rR

Am5=ferI

ferI*4=hoI02@V5.0

11 )viuqeCD(03

%1122=rR

Am5=ferI

ferI*7=hoI03@V50.1

11 )viuqeCD(52

%1122=rR

Am5=ferI

ferI*7=hoI02@V48.0

CPUCLK Swing Select Functions

Loading...

Loading...