Page 1

S-14425XZ-C1

Jun. 2008

VHF FM REPEATER

Page 2

This service manual describes the latest service information

for the IC-FR5000 IC-FR5100 VHF FM REPEATER at the

time of publication.

NEVER connect the repeater to an AC outlet or to a DC

power supply that uses more than specifed. This will ruin

the repeater.

DO NOT expose the repeater to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when

connecting the repeater.

DO NOT apply an RF signal of more than 20 dBm (100 mW)

to the antenna connector. This could damage the repeater’s

front-end.

To upgrade quality, any electrical or mechanical parts and

internal circuits are subject to change without notice or

obligation.

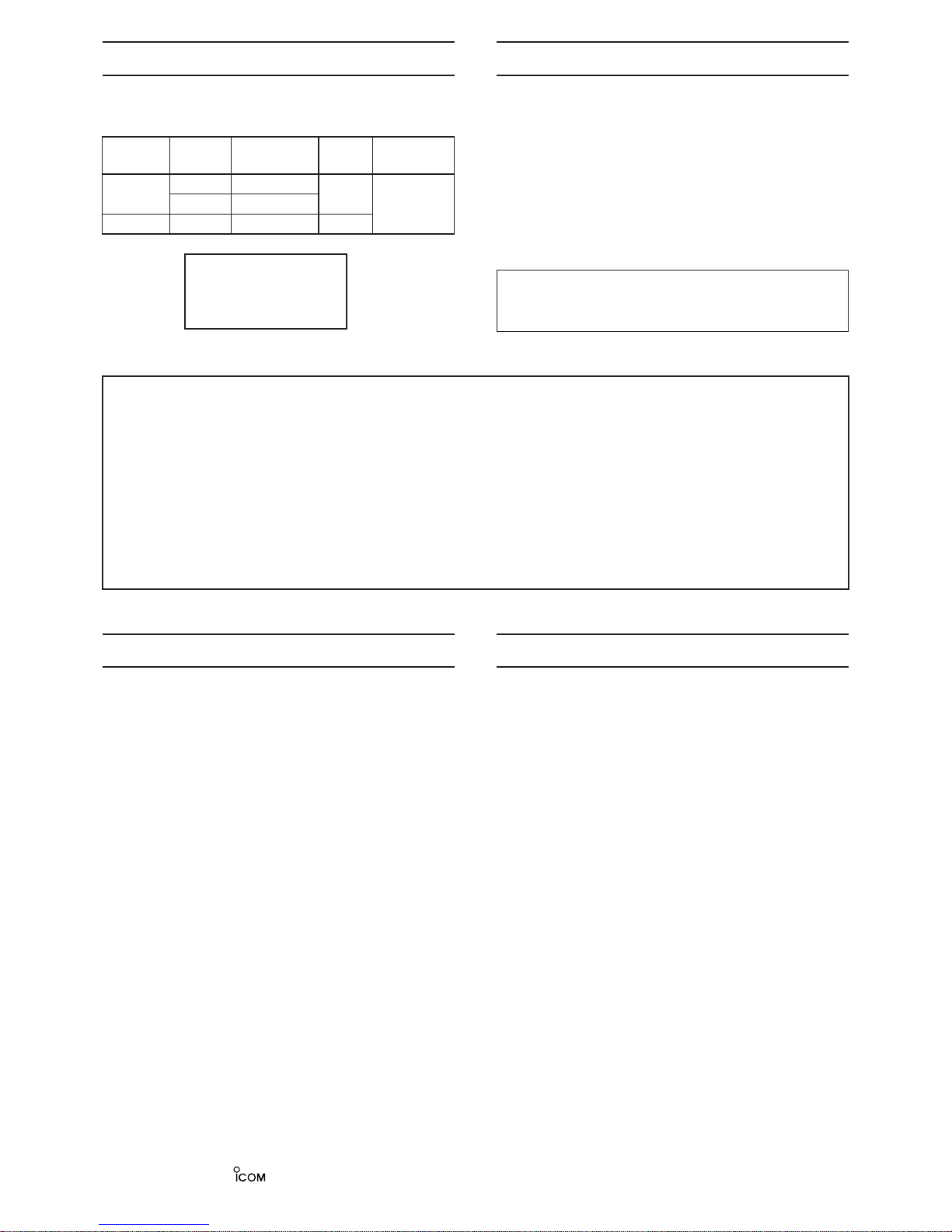

MODEL VERSION

CH. SPACING

(kHz)

TX

POWER

FREQUENCY

RANGE

IC-FR5000

USA-01 7.5/15/30

50 W

136–174 MHzEXP-01 12.5/25.0

IC-FR5100 EUR-01 12.5/20.0/25.0 25 W

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit Icom parts numbers

2. Component name

3. Equipment model name and unit name

4. Quantity required

<ORDER EXAMPLE>

1110003491 S.IC TA31136FNG IC-FR5000 MAIN UNIT 5 pieces

8820001210 Screw 2438 screw IC-FR5000 Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

Icom, Icom Inc. and

logo are registered trademarks of Icom Incorporated (Japan) in the United States, the United

Kingdom, Germany, France, Spain, Russia and/or other countries.

ORDERING PARTS

1. Make sure the problem is internal before disassembling

the repeater.

2. DO NOT open the repeater until the repeater is

disconnected from its power source.

3. DO NOT force any of the variable components. Turn

them slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An

insulated tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the

repeater is defective.

6. DO NOT transmit power into a Standard Signal

Generator or a Sweep Generator.

7. ALWAYS connect a 50 dB to 60 dB attenuator between

the repeater and a Deviation Meter or Spectrum

Analyzer when using such test equipment.

8. READ the instructions of test equipment throughly

before connecting a test equipment to the repeater.

REPAIR NOTES

INTRODUCTION CAUTION

UNIT ABBREVIATIONS:

F=FRONT UNIT

M=MAIN UNIT

CN=CONNECT UNIT

Page 3

CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 DISASSEMBLY INSTRUCTION

SECTION 4 OPTIONAL UNIT INSTALLATION

SECTION 5 CIRCUIT DESCRIPITON

5-1 RECEIVER CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5-2 TRANSMITTER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5-3 OTHER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5-4 CPU (M: IC20) PORT ALLOCATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

SECTION 6 ADJUSTMENT PROCEDURES

6-1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6-2 FREQUENCY ADJUSTMENT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6-3 TRANSMIT ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6-4 RECEIVE ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

SECTION 7 PARTS LIST

SECTION 8 MECHANICAL PARTS

SECTION 9 BOARD LAYOUTS

SECTION 10 BLOCK DIAGRAM

SECTION 11 VOLTAGE DIAGRAM

FRONT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

MAIN UNIT (1/3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

MAIN UNIT (2/3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

MAIN UNIT (3/3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4

CONNECT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

Page 4

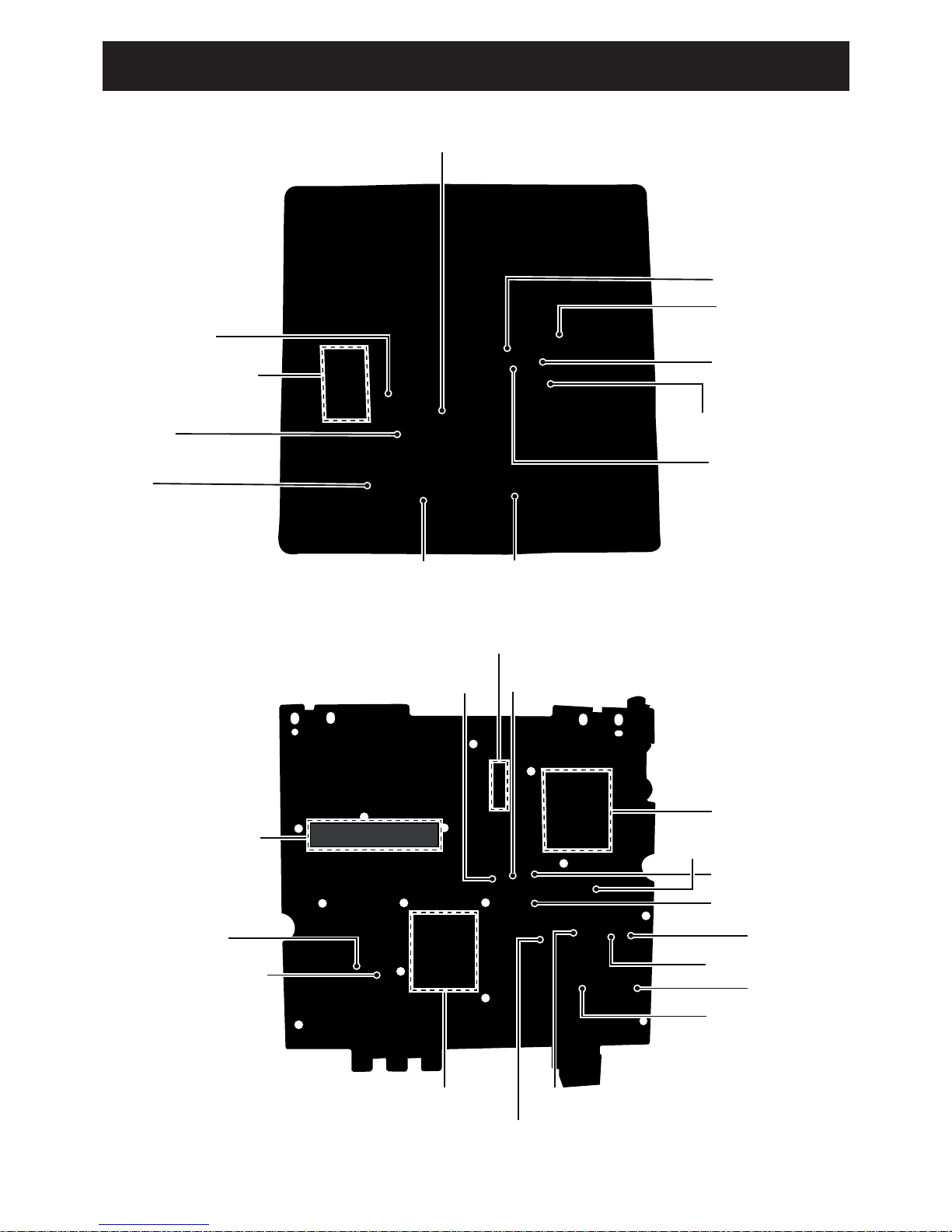

1 - 1

SECTION 1 SPECIFICATIONS

M GENERAL

[FR5000] [FR5100]

• Frequency coverage 136–174 MHz

• Conventional channels max. 32 ch

• Type of emission Wide

16K0F3E

Middle – 14K0F3E

Narrow

11K0F3E/11K0F7E/11K0F7D/11K0F7W

/

8K50F3E ([EXP-01] only)

8K50F3E

Digital 4K00F1E/4K00F1D/4K00F3E

• Antenna impedance 50 Ω (Nominal)

• Operating temperature range –22˚F to +140˚F (–30˚C to +60˚C) –25˚C to +55˚C

• Power supply requirement

(nominal)

13.6 V DC (Negative ground) 13.2 V DC (Negative ground)

• Current drain (Approx.) Receiving 500 mA (stand-by), 1900 mA (max. audio)

Transmitting 15 A (at 50 W) 8.0 A (at 25 W)

• Dimensions

(Projections not included)

19 (W)×3

15

⁄32 (H)×10 1⁄4 (D) in. 483 (W)×88 (H)×260 (D) mm

• Weight (Approx.) 12 Ib 5

17

/32 oz. 5.6 kg

M TRANSMITTER

[FR5000] [FR5100]

• Output power 50 W 25 W

• Modulation Variable reactance frequency modulation

• Max. frequency deviation Wide ±5.0 kHz

Middle – ±4.0 kHz

Narrow ±2.5 kHz

• Frequency stability ±0.5 ppm ±0.2 kHz

• Spurious emissions 80 dB typ. 0.25 μW (≤1 GHz), 1.00 μW (>1 GHz)

• Adjacent channel power Wide 76 dB typ. 76 dB typ.

Middle – 76 dB typ.

Narrow 69 dB typ. 70 dB typ.

Digital 65 dB typ. 66 dB typ.

• Audio harmonic distortion 1% typ. (at AF 1 kHz 40% deviation)

• Intermodulation attenuation – 40 dB min.

• Audio frequency response +2 dB to –8 dB of 6 dB/oct. Wide/Middle from 300 Hz to 3000 Hz

Narrow from 300 Hz to 2550 Hz

• FM Hum and noise

(300 Hz–3000 Hz, 750 µs)

Wide 52 dB typ.

–

Narrow 49 dB typ.

• Audio input impedance (Microphone) 600

Ω

Page 5

1 - 2

M RECEIVER

[FR5000] [FR5100]

• Receive system Double-conversion superheterodyne system

• Intermediate frequencies 1st IF: 46.35 MHz, 2nd IF: 450 kHz

• Sensitivity Wide/Narrow 0.3 μV typ. at 12 dB SINAD –10 dBμV max. at 12 dB SINAD

Wide/Middle/Narrow – –10 dBμV max. at 12 dB SINAD

Digital 0.25 μV typ. at 5% BER 0 dBμV emf max. at 1% BER (PN9)

• Squelch sensitivity (at threshold) 0.25 μV typ.

• Adjacent channel selectivity Wide 80 dB typ. (TIA-603-B)

85 dB typ. (TIA-603)

86 dB typ.

Middle – 83 dB typ.

Narrow 56 dB typ. (TIA-603-B)

77 dB typ. (TIA-603)

77 dB typ.

Digital 66 dB typ. (EN 301 166, 400 Hz @1%)

63 dB typ. (EN 301 166, PN15 @5%)

67 dB typ.

• Spurious response Analog 90 dB 80 dB typ.

Digital 90 dBµV emf 90 dBµ Vemf typ.

• Intermodulation Wide 78 dB typ. 72 dB typ.

Middle – 72 dB typ.

Narrow 78 dB typ. 71 dB typ.

Digital 75 dBµV emf typ. 76 dBµV emf typ.

• Hum and noise Wide 52 dB typ. –

Middle – –

Narrow 50 dB typ. –

Digital 66 dB typ. –

• Audio output power

(at 5% distortion with a 4 Ω load)

4.0 W typ. 3.5 W min.

• Audio output impedance 4

Ω

Specifications are measured in accordance with TIA–603–B (for Wide and Narrow) or EN 300 166 (Digital) for FR5000.

Specifications are measured in accordance with EN 300 086 (for Wide, Middle and Narrow) or EN 301 166 (Digital) for FR5100.

All stated specifications are subject to change without notice or obligation.

Page 6

2 - 1

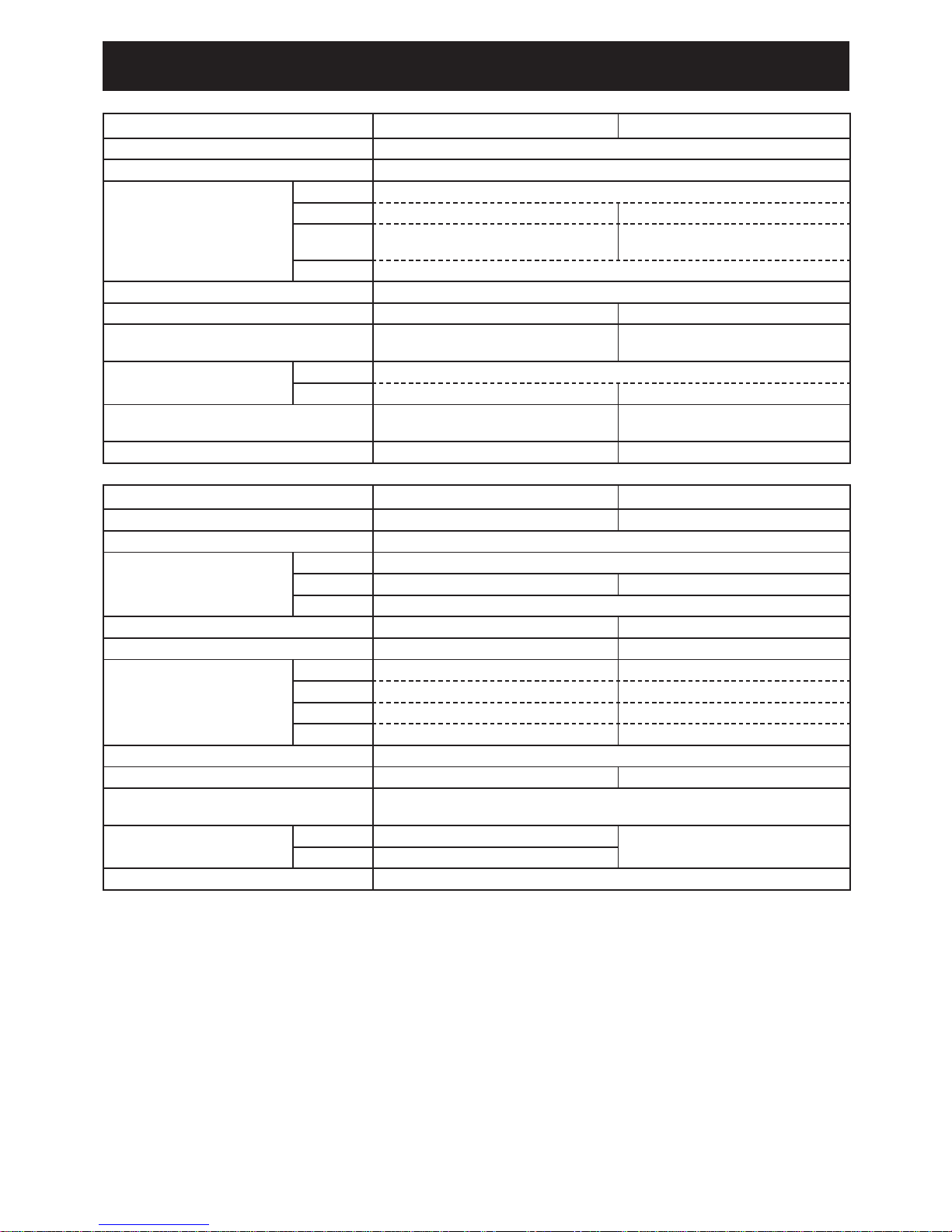

SECTION 2 INSIDE VIEWS

RX VCOs

• MAIN UNIT

(TOP VIEW)

• MAIN UNIT

(BOTTOM VIEW)

Power SW (VCC line)

(Q57)

8V regulator (8V line)

(IC27)

AF AMP

(IC34)

FUNCTION

(Ref.No.)

2nd IF filter (Wide)

(FI1)

2nd IF filter (Narrow)

(FI2)

CPU

(IC20)

5V regulator (DSP5V line)

(IC39)

CPU clock

(X5)

PLL IC (TX lopp)

(IC3)

TX VCOs

Optional digital unit slot

TX power AMP

(IC22)

1st mixer (DBM)

(D62, L27, 32)

5V regulator (CPU5V)

(IC30)

5V regulator (+5V line)

(Q41)

EEPROM

(IC21)

DSP

(IC12)

AF SW

(IC35)

PLL IC (RX loop)

(IC4)

Ref. OSC

(X1)

Level converter

(IC26)

8V regulator (T8V line)

(Q45)

D/A converter

(IC20)

Discriminator

(X3)

IF IC

(IC5)

FUNCTION

(IC40)

Liner codec

(IC8)

Page 7

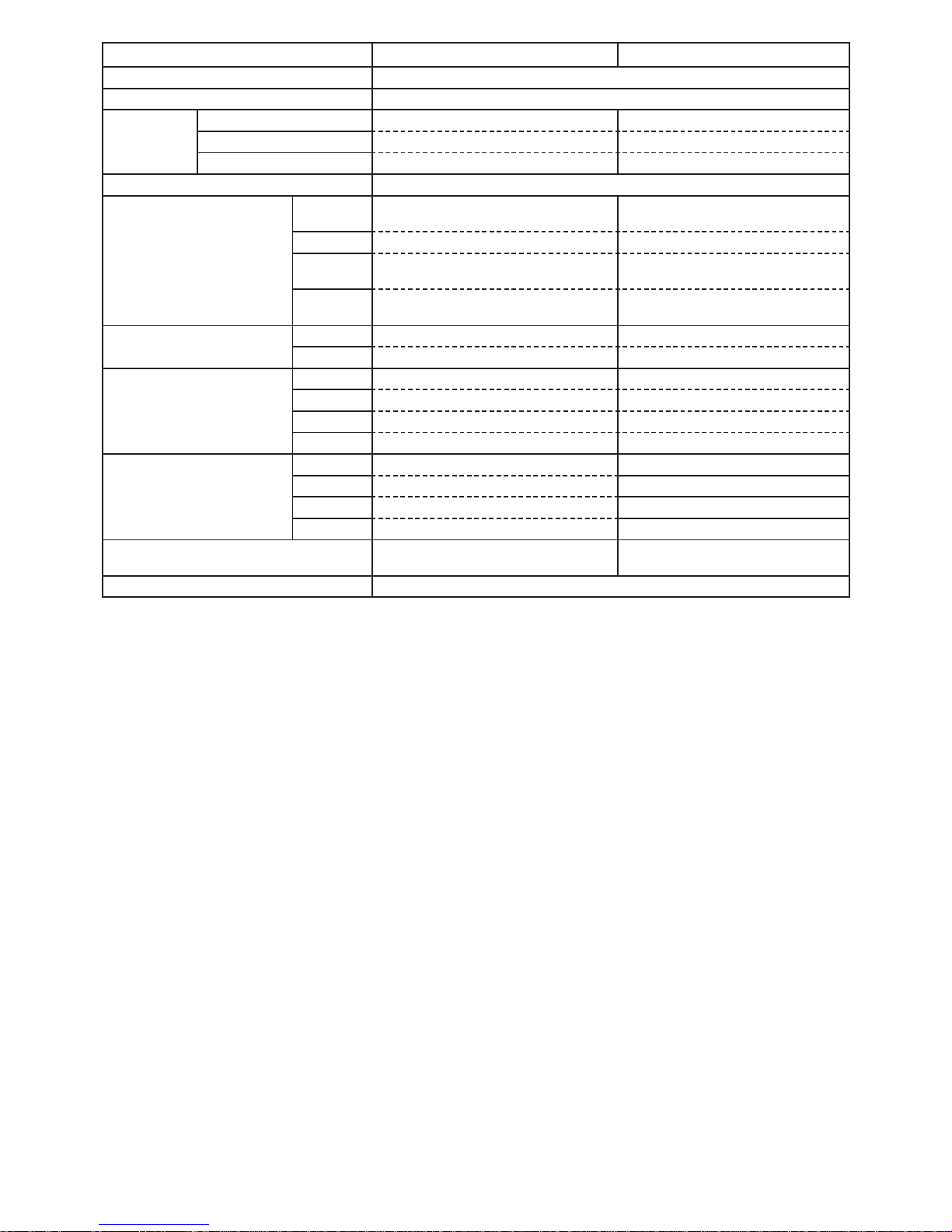

2 - 2

• FRONT UNIT

FRONT CPU

(IC503)

CLOCK OSC

(X501)

LCD DRIVER

(IC500)

ANALOG SW

(IC506)

AF POWER AMP.

(IC509)

SPEAKER SW

(Q508)

Page 8

3 - 1

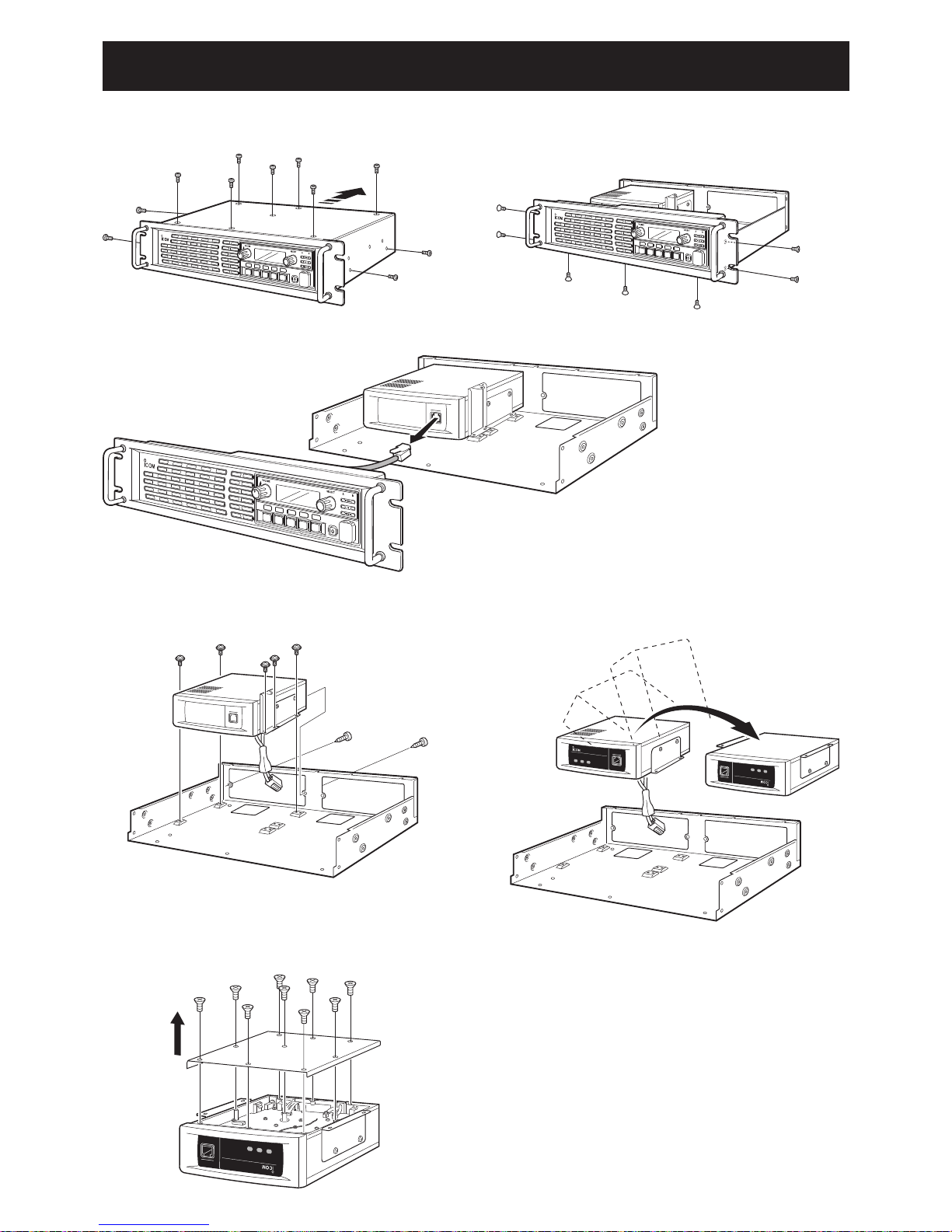

SECTION 3 DISASSEMBLY INSTRUCTION

1. Removing the front panel

q Unscrew 11 screws from the top cover.

3. Removing the MAIN UNIT

q Unscrew 9 screws, and remove the cover.

(If you are going to install an optional unit, see page 4-1 for the installation.)

2. Removing the MAIN UNIT assembly

q Uscrew 5 screws which settles the MAIN UNIT assembly.

P

0

P

1

P

2

P

3

P

4

P

0

P

1

P

2

P

3

P

4

P

0

P

1

P

2

P

3

P

4

PWR TX RX

PWR

TX RX

PWR TX RX

w Unscrew 7 screws from the front panel.

e Disconnect the cable from the MAIN UNIT assembly, and remove the front panel.

w Turn the MAIN UNIT assembly upside down.

(To be continued to next page)

Page 9

3 - 2

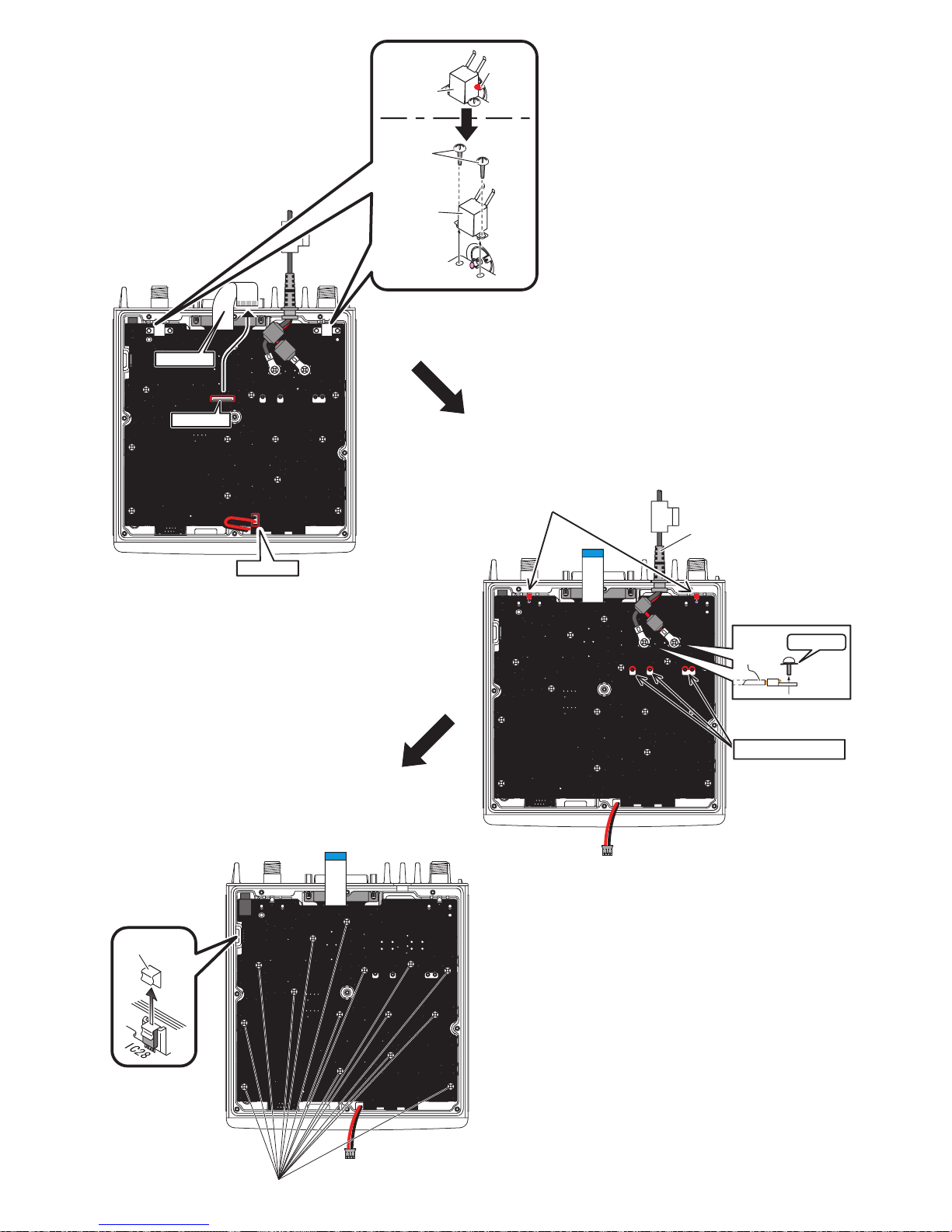

MAIN

MAIN

J9J9J9

J4

J4

Unscrew

ANT case

Unsolder

ANT case

Flat cable

Disconnect

Disconnect

Black

Black

Black

Black

Red

Red

Red

Red

W4

W4

Unsolder 2 points

Unsolder 4 points

Unscrew

Clip

15 screws

w Unsolder 2 points at the ANT cases.

e Unscrew 4 screws from the ANT cases,

and remove them.

r Disconnect the flat cabe from J4 and the

speaker cable from J9.

t Unsolder 2 points at the bottom of ANT connectors.

y Unsolder 4 points at the PA module leads.

u Unscrew 2 screws from W4.

i Remove the clip from the side of chassis.

o Unscrew 15 screws from the MAIN UNIT, then take off

the MAIN UNIT PCB from the chassis.

Page 10

4 - 1

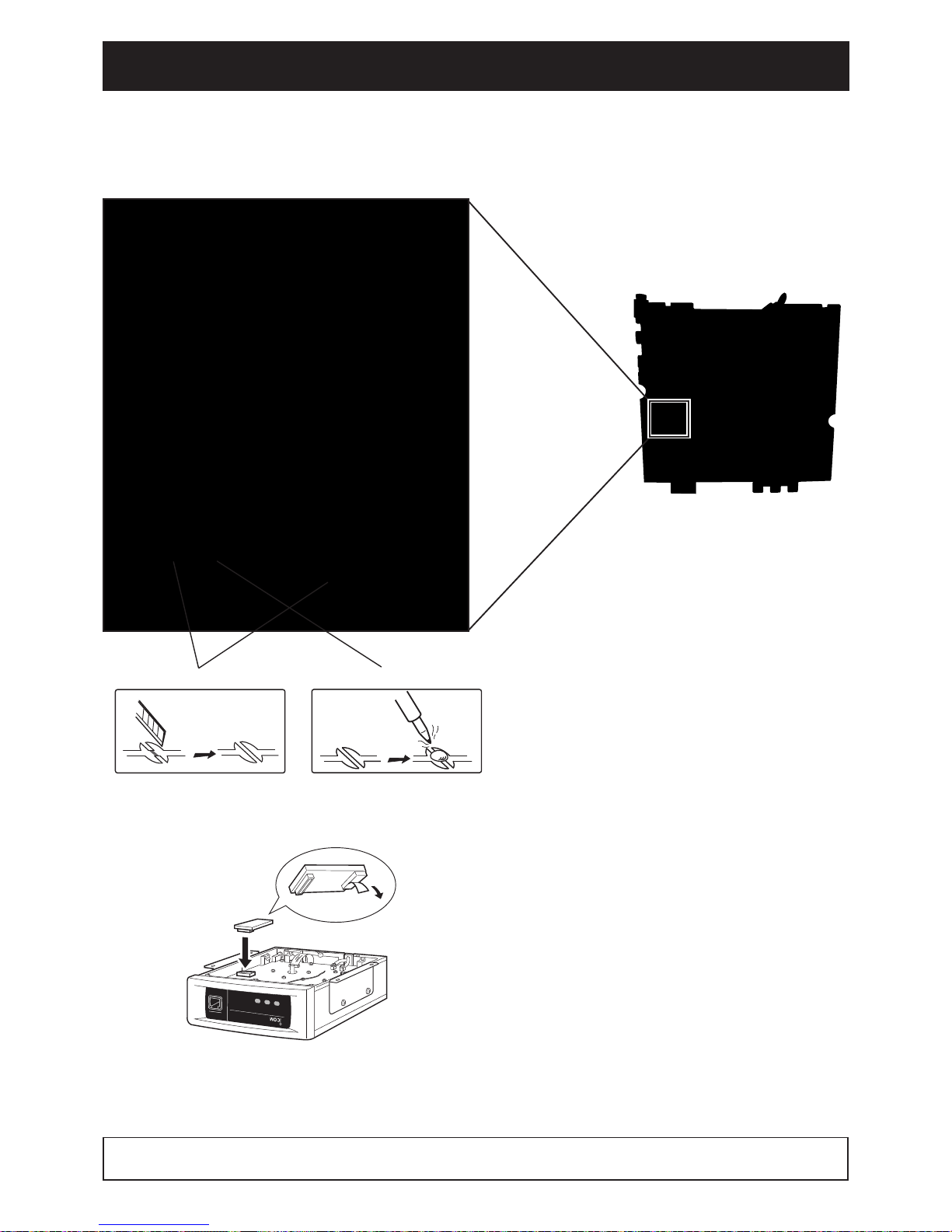

SECTION 4 OPTIONAL UNIT INSTALLATION

PWR TX RX

q Disassembly the repeater until the MAIN UNIT is exposed. (See the page 3-1)

w Modify the patter ns on the MAIN UNIT as below.

e Remove the protective paper of optional unit, and install it to the J1 as below.

A and F; Cut the pattern

B; Short the pattern

r Replace the cover, screws, etc. to recover the whole assembly.

NOTE: When uninstalling the scrambler unit

Be sure to recover the disconnected or connected points, otherwise no TX modulation or AF output is available.

Install UT-109R or UT-110R as follows.

<MAIN UNIT (bottom side)>

Page 11

5 - 1

SECTION 5 CIRCUIT DESCRIPTION

5-1 RECEIVER CIRCUITS

RF BPF CIRCUITS

RX signals from the RX antenna connector (J11) are passed

through the 1st stage of BPF (D28, 29, 31, 32, L44, 47) then

amplified by the RF AMP (Q36). The amplified RX signals

are passed through the 2nd stage of BPF (D28, 29, 31,

32, L44, 47) to remove unwanted signals for good image

response then applied to the 1st mixer (L27, 32, D62).

Being mixed with 1st LO signals from the RX VCO, the RX

signals are converted into the 46.35 MHz 1st IF signal.

The 1st and 2nd stage of the BPFs are tuned to the pass

band frequency by tracking voltage “T1” and “T2” from

the DAC (IC17). The gain of low noise RF AMP (Q36) is

controlled by the AGC circuit (Q39, D27) according to the

RX signal strength.

IF FILTER/IF AMP CIRCUITS

The 1st IF signal from the 1st mixer (L27, 32, D62) is

amplifi ed by the buffer AMP (Q63, 64, 71) and 1st stage of

IF AMP (Q19) then fi ltered by crystal fi lter (FI3 or FI4), and

then applied to the IF IC (IC5).

The crystal fi lters (FI3 or FI4) are switched by the “NWC1”

signal from the CPU (IC20) according to the RX mode; Wide

(Middle), Narrow or Digital.

<ANALOG RX>

Being mixed with the 2nd LO, the 1st IF signal is converted

into the 450 kHz 2nd IF signal. The 2nd IF signal is passed

through the external ceramic filter (FI1 or FI2), then FMdemodulated by the internal quadrature detector with

discriminator (X3). The demodulated AF signals are

amplifi ed by the AF AMP (IC36), and applied to the LINER

CODEC (IC8). The AF signals are converted into the

digital audio signal then processed by the DSP (IC12) then

recovered to the analog audio signals.

The ceramic filter (FI1 or FI2) is switched by the “NWC2”

signal from the CPU (IC20) according to the RX mode; Wide

(Middle), Narrow or Digital.

<DIGITAL RX>

The 450 kHz 2nd IF signal is amplifi ed by IC7 then applied

to the DSP (IC12) via ADC (IC9), and digital-demodulated.

The processed digital signal is converted into the analog

audio signal by the LINEAR CODEC (IC8).

AF AMPLIFIER CIRCUITS

The AF signals from the LINEAR CODEC are amplifi ed by

the AF AMP (IC36) and level-adjusted by DAC (IC2), then

applied to IC28 via IC29 to be power-amplifi ed.

SIGNALING (DECODE)

The Continious Tone (CTCSS/DTCS), Single Tone (5-Tone/

DTMF/CW_ID) signals in the demodulated AF signals are

decoded in the DSP (IC8).

5-2 TRANSMITTER CIRCUITS

MODULATION CIRCUITS

The demodulated signals are applied to the MIC AMP (IC25).

The amplified Demodulated signals are passed through the

SW IC (IC35) which selects the source of Demodulated signals

from J5 (from MIC) and from D-SUB connector (DEXM).

The Demodulated signals from the SW IC are amplifi ed by

an AMP (IC1) then applied to the LINEAR CODEC IC (IC8)

where the Demodulated signals are converted in to the

digital audio signals.

The converted digital audio signals are processed (preemphasis, limit, etc.) by the DSP (IC12), then recovered to

the analog audio signals by LINER CODEC IC (IC8). The AF

signals are amplifi ed by IC1 and level-adjusted by Electronic

VR (IC2), then applied to the TX VCO and TCXO (X1) as the

modulation signals.

SIGNALING (ENCODE)

The Continious Tone (CTCSS/DTCS), Single Tone (5-Tone/

DTMF/CW_ID) signals are encoded, and mixed with

Demodulated signals in the DSP (IC12).

YGR/PA CIRCUITS

The output signals from TX VCOs are amplified to the level

required for the PA module by pre-AMPs (Q37, 38), then

amplifi ed b y the PA module (IC22) to obtain TX output power. The

power-amplifi ed TX signal is passed through the ANT SW (D44)

and LPF (for harmonics removal) then applied to the TX antenna.

APC CIRCUIT

D45, D48 and D49 detect the TX power, and the detected

voltage is applied to the IC23 in APC circuit. Comparing the

detected voltage which is in proportion to the TX power and

power setting voltage as the reference voltage, IC23 adjusts

the bias voltage of PA module (pin 2: VGG terminal) and preAMP (Q38) to control the TX power.

Page 12

5 - 2

5-3 FREQUENCY SYNTHESIZER CIRCUITS

RX PLL CIRCUIT

The RX PLL IC (IC4) outputs resulting signal; phase-comparison

of reference signal (15.3 MHz) from the TCXO (X2) and fedback

OSC signal from the RX VCO. The phase-difference signal is

passed through the active loop fi lter (Q11, 14) and applied to the

RX VCO as the lock voltage. The voltage of RX LV (lock voltage)

is adjusted to appropriate one by “RX LVA” signal.

A portion of reference frequency signal (15.3 MHz) from the

TCXO (X2) is passed through the tripler (Q2) to extract 3rd

harmonic, then applied to the IF IC (IC5).

RX VCO

There are 2 VCOs; VCO for lower band (Q21, D8, 16, L17) and

higher band (Q20, D7, 15, L20), and these VCOs (=OSC freq.)

are switched by the VCO SW (Q26, 30). The OSC frequencies

of these VCOs are adjusted (=Locked) to desired one by the

RX LV signal (Lock Voltage). The output signals of these VCOs

are applied to the 1st mixer (L27, 32, D62) via buffer (Q25).

A portion of output signal from the buffer (Q25) is applied to

the doubler (Q32) to extract 2nd harmonic, then applied to

the PLL IC (IC4) via the LPF.

TX PLL CIRCUIT

TX PLL IC (IC3) outputs resulting signal; phase-comparison

of reference signal (15.3 MHz) from the TCXO (X1) and

fedback OSC signal from the TX VCO. The phase-difference

signal from the PLL IC (IC3) is passed through the active

loop fi lter (Q10, 13) and applied to the TX VCO as the lock

voltage. The rock voltage “TX LV” is adjusted to appropriate

one by the LVA signal. The OSC signal of TCXO (X1) is FMmodulated by applied modulation signals.

TX VCO CIRCUITS

There are 2 VCOs; VCO for lower band (Q23, D10, 14, L62)

and higher band (Q22, D9, 13, L14), and these VCOs (=OSC

frequencies) are switched by the VCO SW (Q27, 28). The

OSC frequencies of these VCO are adjusted (=Locked) to

desired one by the TX LV signal (Lock Voltage).

The modulation signals applied to the Var iable Capacitor

(VD; D18 or D30) vary the capacitor reactance of it for FM

modulation. The output signals of these VCOs are applied to

the YGR/PA circuits via buffers (Q24, 35).

A portion of these output signal is passed through the

doubler (Q33) to extract 2nd harmonic, then applied to the

PLL IC (IC3) via the LPF.

5-4 OTHER CIRCUITS

POWER SUPPLY

The power supply is switched by Q57 (ON/OFF). 5V (REF5)

from the regulator (IC30) is passed through L58 to supply to

CPU. The 5V also supplies to other sections of the repeater

via Q41 as “+5V.”

8V from the regulator (IC27) are supplies to various circuits,

and also supplies to TX circuits as “T8V” and RX circuits as

“8V.”

5V from the regulator (IC39) supplies DSP as “DSP5” and

supplies logic circuits; CPU, DSP, etc. via regulators (IC13,

14, 15).

The regulator “F8V” (IC41) provides the supply for FRONT

UNIT.

COMPANDER

The compander in the DSP (IC12) compresses the

amplitude of Demodulated signals in TX, and expands in RX

to provide high quality, high S/N ratio recovered sounds.

LEDs

DS1 (BUSY), DS2(PWR) and DS3 (TX) indicate the

repeater’s status: Power ON, T/RX and Cloning.

Page 13

5 - 3

Pin

No.

LINE NAME DESCRIPTION

IN/

OUT

CONDITION

1–11 D5–D15 DSP data bus line. I/O –

15–28 A1–A14 DSP data bus line. I/O –

29 HRW DSP data line. I/O –

32 FANS Cooling fan (CH: MF1) rotation detect. I "H"=While the cooling fan is rotating.

33 TLED TX indicator LED control signal. O "H"=TX

34 LEDR RX indicator LED control signal. O "H"=Squelch open.

35 PLSCK PLL (M: IC4) serial clock. O –

36 PLSSO PLL (M:IC4) serial data. O –

41 PWON Power line "VCC" control signal. O "H"=Power ON.

42 AFON2 AF power AMP. (M: IC28) control signal. O "H"=AF power AMP ON.

43 AFON AF output select signal. O

"H= AF signals are output from the

[ACCESSORY CONNECTOR].

44 ESCL Serial clock to the EEPROM (M: IC21). O –

45 ESDA Serial data to the EEPROM (M: IC21). O –

46 TXC TX power line "T8V" control signal. O "H"=TX

47 RXC RX power line "R8V" control signal. O "H"=RX

48 RPLST RX PLL (M: IC4) strobe. O –

49 TPLST TX PLL (M: IC3) strobe. O –

50 RUNLK RX PLL (M: IC4) unlock signal. I "L"=Unlocked

51 TUNLK TX PLL (M: IC3) unlock signal. I "L"=Unlocked

52 XCTS Serial data from the RS-232 line driver (M: IC26). I –

53 XRTS Serial data to the RS-232 line driver (M: IC26). O –

55 EXDA External D/A port. O –

56 BEEP Beep sounds (square waves). O –

57–59 OPV3–OPV1 Optional unit detect. I –

60 MMUT MIC mute signal to the installed optional unit. O "H"=MIC mute

61 HANG Microphone hang-up detect. I "L"=Hang-up

62 PTT [PTT] key input. (pull up) I –

63 RMUT RX mute signal to the installed optional unit. O "H"=RX mute

64 EXAD External A/D port. I –

65 TEMP Temperature detect. I –

68 RLVIN RX PLL lock voltage. I –

69 BATV Voltage monitor (divided voltage of "VCC"). I –

70 TLVIN TX PLL lock voltage. I –

71 RSSI RSSI signal from the IF IC (M: 5). I –

74 XTXD External data to the RS-232 driver (M: IC26). O –

75 XRXD External data from the RS-232 driver (M: IC26). I –

76 TMUT TX mute signal. O "H"=TX mute

77 HINT DSP IC control signal. O –

78 INT1 DSP IC control signal. O –

79 HRDY DSP IC control signal. O –

81 HDS1 DSP IC control signal. O –

82 HDS2 DSP IC control signal. O –

100 RES CPU reset signal from the reset IC (F: IC501). O –

101–108 EXIO1–EXIO8 External data bus line. I/O +5 V pull-up

112 POSW [PWR] key input. (pull-up) I –

113 NOIS Noise detect. I "H"=RX signal is absent (squelch close).

114 CSFT Clock frequency shift signal. O –

119 SSO Serial data to the seri-para converter (M: IC31). O –

120 SCK Clock signal to the seri-para converter (M: IC31). O –

121 EXIO9 External data bus line. I/O +5 V pull-up

122 DSDA Serial data to the DAC (M: IC17). O –

5-5 CPU (M: IC20) PORT ALLOCATION

Page 14

5 - 4

Pin

No.

LINE NAME DESCRIPTION

IN/

OUT

CONDITION

123 DAST Strobe to the DAC (M: IC2). O –

125 FMDA Data from the FRONT CPU (F: IC502). I –

126 MFDA Data to the FRONT CPU (F: IC502). O –

127 OPT2 Port for optional unit. O –

128 OPT1 Port for optional unit. I –

129 OPT3 Port for optional unit. I –

131 CSO Port for optional unit. O –

132 CSI Port for optional unit. I –

133 EXOE Output enable signal to the seri-para converter (M: IC31). O –

134 EXST Strobe to the seri-para converter (M: IC31). O –

135 DRES Reset signal to the DSP IC (M: IC12). O –

136 HCS DSP data line. I/O –

138 GPIO2 DSP data line. I/O –

139 GPIO1 DSP data line. I/O –

140–144 D0–D4 DSP data bus line. I/O –

5-5 CPU (M: IC20) PORT ALLOCATION (continued)

Page 15

6 - 1

SECTION 6 ADJUSTMENT PROCEDURE

6-1 PREPARATION

¤ REQUIRED EQUIPMENTS

EQUIPMENT

SPECIFICATION

EQUIPMENT SPECIFICATION

Adjustment

Software

"CS-FR5000" (Revision 1.0 or later) JIG cable

Modifi ed OPC-1122U (USB type)

(see the illust below)

Power Supply

Output voltage :

13.6 V DC

[FR5000]

13.2 V DC

[FR5100]

Current capacity : More than 20 A

[FR5000]

More than 10 A

[FR5100]

Attenuator

Power attenuation : 40 dB

Capacity : More than 60 W

[FR5000]

More than 30 W

[FR5100]

RF Power Meter

(terminated type)

Measuring range :

1–60 W

[FR5000]

1–30 W

[FR5100]

Frequency range : 100–300 MHz

Impedance : 50

Ω

SWR : Less than 1.2 : 1

Standard Signal

Generator (SSG)

Frequency range : 0.1–300 MHz

Output level : 0.1 mV to 32 mV

(–127 to –17 dBm)

Audio Generator

Frequency range : 300–3000 Hz

Output level : 1–500 mV

Frequency Counter

Frequency range : 0.1–300 MHz

Frequency accuracy

: ±1 ppm or better

Input level : Less than 1 mW

AC Millivoltmeter Measuring range : 10 mV to 10 V

Oscilloscope

Frequency range : DC–20 MHz

Measuring range : 0.01–20 V

Modulation

Analyzer

Frequency range : 30–300 MHz

Measuring range : 0 to ±10 kHz

External Speaker

Input impedance : 4

Ω

Capacity : More than 5 W

¤ JIG CABLE

Add a jumper wire here

OPC-1122U

(USB type Cloning cable)

+

GND

MIC

PTT

GND

PTT

4.7 µF

+−

AC MILLIVOLT METER

(10 mV to 10 V)

AUDIO GENERATOR

(300–3000 Hz/1–100 mV)

+−

GND

SP

+−

EXT. SPEAKER

(5 W/4 Ω)

Page 16

6 - 2

¤ CONNECTION

(Loose Coupling)

FREQUENCY COUNTER

(0.1–300 MHz)

MODULATION ANALYZER

(0.1–300 MHz)

STANDARD SIGNAL GENERATOR

(0.1–300 MHz)

OSCILLOSCOPE

(DC to 10 kHz)

ATTENUATOR

(30 dB/60 W)

RF POWER METER

Black

Red

20 A

fuses

DC power supply

DC power cable

<Rear view>

(Detect output)

Page 17

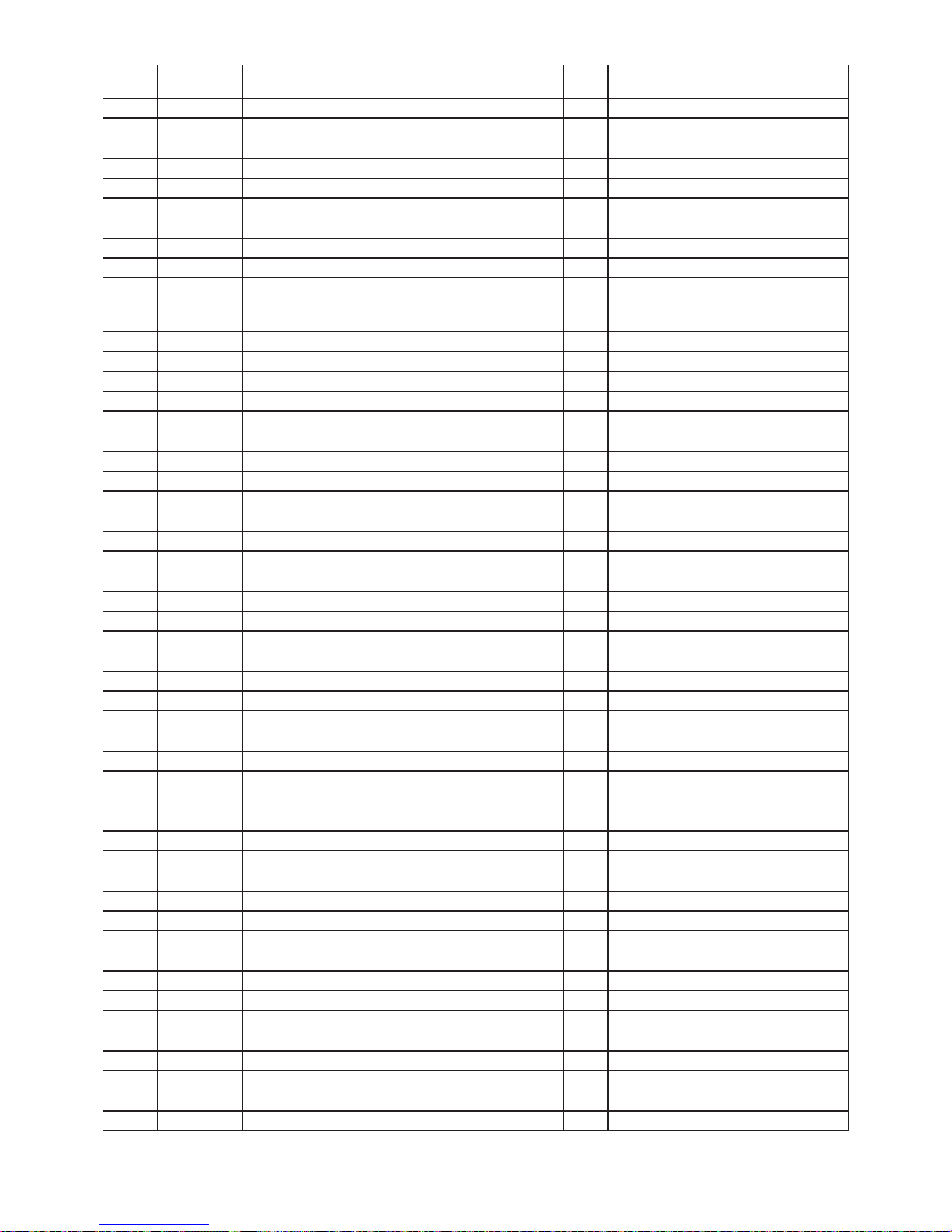

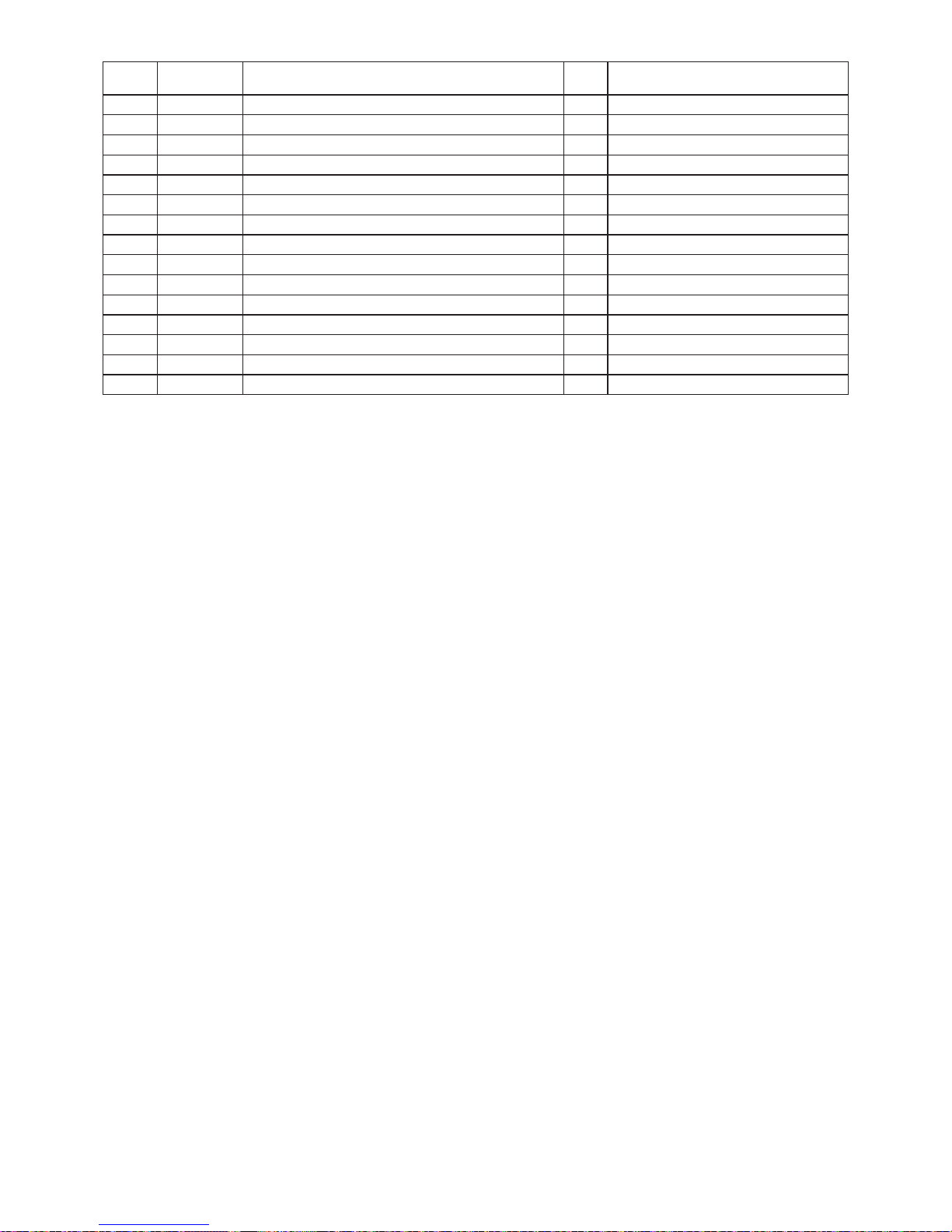

¤ ADJUSTMENT CHANNEL LISTS

Clone the adjust channels into the repeater before starting adjustment. Each channel must be assigned [Frequency], [RF

PWR], [CH Type], [TX C. Tone] and [W/N] as below.

• Channel list

6 - 3

Page 18

6 - 4

¤ WHOLE PROCEDURE OF THE ADJUSTMENT

q Connect the repeater and PC with the JIG cable (see the page 6-2).

w

Tur n the repeater power ON.

e

Boot up 'CS-FR5000.'

r

Set the [Digital Function] to "Enable."

y Set or modify adjustment values as specifi ed in the guidances on the pages 6-6 to 6-9.

t

Click or [Read <– TR] in the [Adjust] menu, then the "Adjust Utility" window (see the page 6-5) appears.

*For [FR5100]:

Set the [Wide Band Width] to "Middle" when adjust "ANALOG DEVIATION" in Middle mode.

Page 19

Mode setting

TX output power

Analog deviation

Digital deviation

Receive sensitivity (Band center)

Receive sensitivity (Band high)

CTCSS/DTCS deviation

Squelch

TX frequency

Lock volatge

(Preset)

Lock volatge

(Adjustment)

S-meter

Modulation balance

Modulation balance (High)

¤ ADJUST UTILITY WINDOW

6 - 5

Page 20

6-2 FREQUENCY ADJUSTMENT

1) Select an adjustment item using cursor or [↑] / [↓] keys of the PC’s keyboard.

2) Set or modify the adjustment value as specifi ed using [←] / [→] keys of the PC’s keyboard, then push the [ENTER] ke y.

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

ADJUSTMENT

ITEM

VALUE

PLL LOCK

VOLTAGE

-Preparation-

1

–

1) Connect an RF power meter to the

TX antenna.

2) Set the preset adjustment value on

the adjustment utility window.

[LV (RX L)] 161 [3.15V]

[LV (RX H)] 153 [3.00V]

[LV (TX L)] 51 [1.0V]

[LV (TX H)] 36 [0.7V]

-AdjustRX

(Band center)

2 • CH. : 1-1

• Receiving

• Select the item [RX LVA L], then

push the [ENTER] key. [RX LVA L]

(Automatic

adjustment)

RX

(Band high)

3 • CH. : 1-2

• Receiving

•

Select the item [RX LVA H], then

push the [ENTER] key.

[RX LVA H]

TX

(Band low)

4 • CH. : 1-3

• T r ansmitting

• Select the item [TX LVA L], then push

the [ENTER] key.

[TX LVA L]

TX

(Band center)

5 • CH. : 1-4

• T r ansmitting

• Select the item [TX LVA H], then

push the [ENTER] key.

[TX LVA H]

LOCK

VOLTAGE

VERIFY

RX

(Band low)

1 • CH. : 1-5

• Receiving

• Verify the lock voltage at each

channels on the [RX LIVIN] item on

the "I/O Check window" as below.

[RX LIVIN]

(I/O Check

window)

0.5–1.5 V

(Verify)

RX

(Band center)

2 • CH. : 1-6

• Receiving

TX

(Band center)

3 • CH. : 1-7

• T r ansmitting

• Verify the lock voltage at each

channels on the [TX LIVIN] item on

the "I/O Check window" as below.

[TX LIVIN]

(I/O Check

window)

3.0–4.5 V

(Verify)

TX

(Band high)

4 • CH. : 1-8

• T r ansmitting

2.0–3.5 V

(Verify)

TX

FREQUENCY

1

–

1) Set the item [TX Mode] to "1."

2) Connect an RF power meter to the

TX antenna.

[TX Mode]

"1"

2 • CH. : 1-9

• T r ansmitting

1) Adjust the frequency using [←] / [→]

keys of the PC’s keyboard.

2) Push the [ENTER] key to store the

adjust value.

[TX REF]

173.9000 MHz

6 - 6

• I/O CHECK WINDOW

*The above voltages are just an example.

Lock voltage verify

Page 21

6-3 TRANSMIT ADJUSTMENT

1) Select an adjustment item using cursor or [↑] / [↓] keys of the PC’s keyboard.

2) Set or modify the adjustment value as specifi ed using [←] / [→] keys of the PC’s keyboard, then push the [ENTER] ke y.

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

ADJUSTMENT

ITEM

VALUE

TX

Output Power

-Preparation-

1

–

• Connect an RF power meter to the

TX antenna connector.

––

-Adjust(Hi Power)

2 • CH. : 1-10

• T r ansmitting

1)

Adjust the TX output power using [←]

/ [→] keys of the PC’s keyboard.

2) Push the [ENTER] key to store the

adjust value.

[Power(Hi)]

50 W

[FR5000]

25 W

[FR5100]

(L2 Power) 3 • CH. : 1-11

• T r ansmitting

[Power(L2)]

25 W

[FR5000]

10 W

[FR5100]

(L1 Power) 4 • CH. : 1-12

• T r ansmitting

[Power(L1)]

5 W

[FR5000]

2.5 W

[FR5100]

MODULATION

BALANCE

-Preparation-

1• Connect a Modulation Analyzer

to the TX antenna connector

through an attenuator.

• Set the Modulation Analyzer as;

HPF : OFF

LPF : 20 kHz

De-emphasis : OFF

Detector : (P-P)/2

––

2 – • Set the item [TX Mode] to "2." [TX Mode]

"2"

-Adjust(TX VCO 1)

3 • CH. : 1-13

• T r ansmitting

1) Adjust the wave form using [←] / [→]

keys of the PC’s keyboard.

2) Push the [ENTER] key to store the

adjust value.

[BAL]

(square wave

form)

(TX VCO 2) 4 • CH. : 1-14

• T r ansmitting

[BAL Offset

(High]

DIGITAL

DEVIATION

-Preparation-

1 – • Set the item [TX Mode] to "16." [TX Mode]

"16"

2• Connect a Modulation Analyzer

to the TX antenna connector

through an attenuator.

• Set the Modulation Analyzer as;

HPF : OFF

LPF : 20 kHz

De-emphasis : OFF

Detector : (P-P)/2

––

-Adjust(Band 1)

3 • CH. : 1-15

• T r ansmitting

1) Adjust the deviation using [←] / [→]

keys of the PC’s keyboard.

2) Push the [ENTER] key to store the

adjust value.

[MOD (Digital)]

±1.39–1.43

kHz

(Band 2) 4 • CH. : 1-16

• T r ansmitting

[MOD Slant

Band 0]

(Band 3) 5 • CH. : 1-17

• T r ansmitting

[MOD Slant

Band 1]

(Band 4) 6 • CH. : 1-18

• T r ansmitting

[MOD Slant

Band 2]

(Band 5) 7 • CH. : 1-19

• T r ansmitting

[MOD Offset

(High)]

(Band 6) 8 • CH. : 1-20

• T r ansmitting

[MOD Slant

Band 3]

(Band 7) 9 • CH. : 1-21

• T r ansmitting

[MOD Slant

Band 4]

(Band 8) 10 • CH. : 1-22

• T r ansmitting

[MOD Slant

Band 5]

6 - 7

Page 22

6-3 TRANSMIT ADJUSTMENT (continued)

1) Select an adjustment item using cursor or [↑] / [↓] keys of the PC’s keyboard.

2) Set or modify the adjustment value as specifi ed using [←] / [→] keys of the PC’s keyboard, then push the [ENTER] ke y.

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

ADJUSTMENT

ITEM

VALUE

ANALOG

DEVIATION

-Preparation-

1 – • Set the item [TX Mode] to "1." [TX Mode]

"1"

2• Connect a Modulation Analyzer

to the TX antenna connector

through an attenuator.

• Set the Modulation Analyzer as;

HPF : OFF

LPF : 20 kHz

De-emphasis : OFF

Detector : (P-P)/2

––

3• Connect an Audio Generator

to the MIC line through the JIG

cable.

• Set the Audio Generator as;

Modulation : 1050 Hz

Level : 40 mVrms

Waveform : Sine wave

––

-Adjust(Wide)

4 • CH. : 1-23

• T r ansmitting

1) Adjust the deviation using [←] / [→]

keys of the PC’s keyboard.

2) Push the [ENTER] key to store the

adjust value.

[MOD (Wide)]

±4.05–4.15

kHz

(Middle)

<[FR5100] only>

5 • CH. : 1-24

• [Wide Band Width]

: "Middle" (see the page 6-4)

• T r ansmitting

[MOD (Middle)]

±3.15–3.25

kHz

(Narrow) 6 • CH. : 1-25

• T r ansmitting

[MOD (Narrow)]

±2.05–2.15

kHz

CTCSS/DTCS

DEVIATION

-Preparation-

1

–

• Set the item [TX Mode] to "3."

[TX Mode]

"3"

-Adjust- 2 • CH. : 1-26

• T r ansmitting

1) Adjust the deviation using [←] / [→]

keys of the PC’s keyboard.

2) Push the [ENTER] key to store the

adjust value.

[CTCSS]

±0.68–0.72

kHz

6-4 RECEIVE ADJUSTMENT

1) Select an adjustment item using cursor or [↑] / [↓] keys of the PC’s keyboard.

2) Set or modify the adjustment value as specifi ed using [←] / [→] keys of the PC’s keyboard, then push the [ENTER] ke y.

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

ADJUSTMENT

ITEM/POINT

VALUE

RECEIVE

SENSITIVITY

-Preparation-

1 – • Set the item [RX Mode] to "1." [RX Mode]

"1"

2• Connect an SSG to the RX

antenna connector.

• Set the SSG as;

Level : +20 dB

μ

Modulation : 1 kHz

Deviation : 3.5 kHz

––

-Adjust(Band center)

3 • CH. : 1-27

• Receiving

1) Set the SSG as;

Frequency : 136.100 MHz

2) Select the item [BPF C ALL], then

push the [ENTER] key.

[BPF C ALL]

(Automatic

adjustment)

(Band high)

<[FR5000] only>

4 • CH. : 1-28

• Receiving

1) Set the SSG as;

Frequency : 173.900 MHz

2) Select the item [BPF H ALL], then

push the [ENTER] key.

[BPF H ALL]

6 - 8

Page 23

6-4 RECEIVE ADJUSTMENT (continued)

1) Select an adjustment item using cursor or [↑] / [↓] keys of the PC’s keyboard.

2) Set or modify the adjustment value as specifi ed using [←] / [→] keys of the PC’s keyboard, then push the [ENTER] ke y.

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

ADJUSTMENT

ITEM/POINT

VALUE

S-METER

-Preparation-

NOTE: "RECEIVE SENSITIVITY" MUST be adjusted before "S-METER." When "RECEIVE SENSITIVITY" is re-

adjusted, "S-METER" MUST be re-adjusted too.

1• Connect an SSG to the RX

antenna connector.

• Set the SSG as;

Frequency : 173.900 MHz

Modulation : 1 kHz

Deviation : 3.5 kHz

––

-Adjust(S3 level)

2 • CH. : 1-29

• Receiving

1) Set the SSG as;

Level : +23 dB

μ

2) Select the item [RSSI S3 Level],

then push the [ENTER] key to store

the adjust value.

[RSSI S3 Level]

(Automatic

adjustment)

(S1 level) 3 • CH. : 1-29

• Receiving

1) Set the SSG as;

Level : –7 dB

μ

2) Select the item [RSSI S1 Level],

then push the [ENTER] key, to store

the adjust value.

[RSSI S1 Level]

(Automatic

adjustment)

SQUELCH

-Preparation-

1

–

• Set the item [SQL Level] to "2." [SQL Level] "2"

2• Connect an SSG to the RX

antenna connector.

• Set the SSG as;

Frequency : 173.900 MHz

Modulation : 1 kHz

Deviation : 3.5 kHz

Level : –14 dB

μ

––

-Adjust- 3 • CH. : 1-30

• Receiving

1)

Decrease the adjustment value

[SQL] to close the squelch once,

then increase the value to open the

squelch.

2) Select the item [SQL], then push

the [ENTER] key to store the adjust

value.

[SQL]

(Automatic

adjustment)

6 - 9

Page 24

7 - 1

SECTION 7 PARTS LIST

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

[FRONT UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

IC500 1130009121 S.IC S1D15206F00A200 B 69.4/35.9

IC501 1110005771 S.IC S-80942CNMC-G9CT2G B 105.3/24

IC502 1140014580 S.IC uPD78F1153GK-GAK-AX B 101.3/38.7

IC503 1110005350 S.IC NJM2870F05-TE1-#FZZB B 47.2/30.5

IC506 1140013200 S.IC CD4053BPWR B 39.1/31.7

IC508 1110002751 S.IC TA75S01F (TE85R,F) B 143/18

IC509 1110006770 S.IC TDA8547TS/N B 28.4/55.8

Q500 1590001050 S.TR DTC114TUA T106 B 148.4/41.4

Q501 1590001050 S.TR DTC114TUA T106 B 161.8/34.6

Q502 1590001050 S.TR DTC114TUA T106 B 161.8/41.4

Q503 1590001050 S.TR DTC114TUA T106 B 148.4/34.6

Q504 1590001050 S.TR DTC114TUA T106 B 91.4/45.6

Q506 1590001190 S.TR XP6501-(TX) .AB B 32.9/48.1

Q508 1520000460 S.TR 2SB1132 T100 R B 36.9/52.6

Q510 1590001050 S.TR DTC114TUA T106 B 152.8/53.2

Q511 1590001050 S.TR DTC114TUA T106 B 166.2/53

Q513 1590001060 S.TR DTA114TUA T106 B 168.7/53

Q514 1590001060 S.TR DTA114TUA T106 B 160.1/49.6

Q515 1590001060 S.TR DTA114TUA T106 B 155.3/53.2

Q516 1590001060 S.TR DTA114TUA T106 B 145.3/49.9

Q517 1590001050 S.TR DTC114TUA T106 B 160.1/46.9

Q518 1590001050 S.TR DTC114TUA T106 B 145.3/47

D503 1790001260 S.DIO MA2S077-(TX) B 112.3/33.9

D504 1790001250 S.DIO MA2S111-(TX) B 95/45.8

D505 1790001450 S.DIO RB160L-40 TE-25 B 41.8/26.6

D506 1790001450 S.DIO RB160L-40 TE-25 B 63.2/6.6

D507 1790000950 S.ZEN MA8056-M (TX) B 160.8/29.9

D508 1750000370 S.DIO DA221 TL B 153.2/27.7

D509 1750000370 S.DIO DA221 TL B 166.4/28.1

D510 1790001250 S.DIO MA2S111-(TX) B 43.2/51.5

D511 1790001250 S.DIO MA2S111-(TX) B 115.8/44.9

D512 1790001250 S.DIO MA2S111-(TX) B 65.3/10.2

D513 1790001250 S.DIO MA2S111-(TX) B 36.3/24.4

X501 6050012680 S.XTL CR-858 (SMD-49/18.432MHZ) B 113.1/28.2

L500 6200002861 S.COL NLV25T-4R7J B 106/17.9

L501 6200003640 S.COL MLF1608E 100K-T B 161.5/17.9

L502 6200002861 S.COL NLV25T-4R7J B 85.9/39.3

R500 7030003810 S.RES ERJ3GEYJ 125 V (1.2 M) B 83.5/43.7

R501 7030003810 S.RES ERJ3GEYJ 125 V (1.2 M) B 87.4/47.5

R506 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 157.7/36.3

R507 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 167.9/44.3

R508 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 167.9/37.7

R509 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 155.4/44.5

R510 7030005530 S.RES ERJ2GEJ 100 X (10) B 106.8/30.5

R511 7030005160 S.RES ERJ2GEJ 105 X (1 M) B 105.8/30.5

R512 7510001730 S.TMR ERTJOEP 473J B 103.1/48.9

R513 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 102.2/49.8

R514 7030008010 S.RES ERJ2GEJ 123 X (12 k) B 113.1/32.2

R515 7030008010 S.RES ERJ2GEJ 123 X (12 k) B 112.3/35.9

R516 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 103.2/26.4

R517 7030008010 S.RES ERJ2GEJ 123 X (12 k) B 110.3/33

R518 7410001140 S.ARY EXB28V104JX B 106.9/47.1

R519 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 105.4/48.4

R520 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 96.1/30.7

R523 7030005710 S.RES ERJ2GEJ 121 X (120) B 114.1/37.6

R524 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 104.4/48.4

R525 7030005710 S.RES ERJ2GEJ 121 X (120) B 113.2/37.6

R526 7030005710 S.RES ERJ2GEJ 121 X (120) B 112.3/37.6

R532 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 33.2/45.5

R533 7030009140 S.RES ERJ2GEJ 272 X (2.7 k) B 31.2/47.7

R534 7030008290 S.RES ERJ2GEJ 183 X (18 k) B 32.2/45.7

R536 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 158.7/30.8

R538 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 155.7/29.3

R539 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 27.6/51.1

R540 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 26.6/49.9

R541 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 139.1/31.9

R542 7030005080 S.RES ERJ2GEJ 823 X (82 k) B 26.1/51.1

R543 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 137.3/31.5

R544 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 164.9/29.3

R545 7030004980 S.RES ERJ2GEJ 101 X (100) B 140.3/19.9

R546 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 164.8/27.7

R547 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 155.7/27.7

R548 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 159.8/28

R549 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 32/51.3

R551 7210003050 VAR EVU-F2KFK3 B14 (10KB)

R552 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 142.3/20.3

R553 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 144.6/20.1

R554 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 32.6/53.4

R556 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 161.1/19

R557 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 29.2/51.3

R558 7030008370 S.RES ERJ2GEJ 561 X (560) B 169.1/51.1

R559 7030008370 S.RES ERJ2GEJ 561 X (560) B 155.7/51

R560 7030010040 S.RES ERJ2GEJ-JPW B 139.4/17.1

R562 7030003720 S.RES ERJ3GEYJ 224 V (220 k) B 86.2/43.7

R563 7030003720 S.RES ERJ3GEYJ 224 V (220 k) B 88.2/44.9

R564 7030009320 S.RES ERJ2GEJ 4R7 X (4.7) B 153/19.8

R566 7030008370 S.RES ERJ2GEJ 561 X (560) B 161.9/49.1

R567 7030008370 S.RES ERJ2GEJ 561 X (560) B 148.3/49.9

S.=Surface mount

[FRONT UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

R568 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 87.4/16.9

R570 7030005220 S.RES ERJ2GEJ 223 X (22 k) B 103/24.8

R571 7030005070 S.RES ERJ2GEJ 683 X (68 k) B 45.8/51.5

R572 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 46.2/50.3

R573 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 108.3/33

R574 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 108.3/32.1

R575 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 34.7/24.6

R576 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 62.6/12.8

C500 4030016930 S.CER ECJ0EB1A104K B 79.3/47.9

C501 4030016930 S.CER ECJ0EB1A104K B 80.8/47.4

C502 4030016930 S.CER ECJ0EB1A104K B 80.8/46.5

C503 4030016930 S.CER ECJ0EB1A104K B 80.4/45.3

C504 4030016930 S.CER ECJ0EB1A104K B 81.3/45.3

C505 4030017490 S.CER C1608 JB 1A 105K-T B 80.9/41

C506 4030017460 S.CER ECJ0EB1E102K B 83.9/39.8

C507 4030017490 S.CER C1608 JB 1A 105K-T B 80.9/39.5

C508 4030017730 S.CER ECJ0EB1E471K B 146.4/41.2

C509 4030017730 S.CER ECJ0EB1E471K B 159.8/34.4

C510 4030017730 S.CER ECJ0EB1E471K B 159.9/41.2

C511 4030017730 S.CER ECJ0EB1E471K B 146.4/34.4

C512 4030017030 S.CER ECJ0EB1A273K B 104.7/21.7

C513 4030017630 S.CER ECJ0EC1H120J B 106.4/29.3

C514 4030017420 S.CER ECJ0EC1H470J B 157.7/44.5

C515 4030016790 S.CER ECJ0EB1C103K B 103.5/50.2

C516 4030017580 S.CER ECJ0EC1H060C B 113.1/31.3

C517 4030016930 S.CER ECJ0EB1A104K B 102.2/50.7

C518 4030016790 S.CER ECJ0EB1C103K B 113.3/35.1

C519 4030017640 S.CER ECJ0EC1H150J B 111.3/31.8

C520 4030016930 S.CER ECJ0EB1A104K B 105.1/27.1

C521 4030018900 S.CER ECJ0EB0J474K B 104.9/30

C522 4550006480 S.TAN TEESVA 1C 475M8R B 46.7/33.2

C523 4030017330 S.CER ECJ0EF1C104Z B 44.9/31

C524 4030016790 S.CER ECJ0EB1C103K B 49.9/29.5

C525 4550006250 S.TAN TEESVA 1A 106M8R B 49/27.7

C526 4030016930 S.CER ECJ0EB1A104K B 48.9/26.1

C527 4030016930 S.CER ECJ0EB1A104K B 34.3/30

C530 4030017460 S.CER ECJ0EB1E102K B 34.5/55.4

C531 4550006250 S.TAN TEESVA 1A 106M8R B 106.6/20.2

C532 4030017460 S.CER ECJ0EB1E102K B 31.3/45.7

C533 4030017460 S.CER ECJ0EB1E102K B 45.3/27

C534 4030016930 S.CER ECJ0EB1A104K B 62.1/14.2

C535 4030016930 S.CER ECJ0EB1A104K B 30.7/49

C536 4030017460 S.CER ECJ0EB1E102K B 161/28.5

C537 4030017460 S.CER ECJ0EB1E102K B 33.6/53.4

C538 4030018860 S.CER ECJ0EB0J105K B 26.6/49

C539 4030017420 S.CER ECJ0EC1H470J B 154.8/27.7

C540 4510008590 S.ELE EEE1AA101SP B 36.9/59.4

C541 4030017330 S.CER ECJ0EF1C104Z B 150.1/20

C542 4030017460 S.CER ECJ0EB1E102K B 139.3/19.9

C544 4550006250 S.TAN TEESVA 1A 106M8R B 29.7/60.8

C545 4030017420 S.CER ECJ0EC1H470J B 168.1/28.1

C546 4030017420 S.CER ECJ0EC1H470J B 137.3/32.4

C547 4030017420 S.CER ECJ0EC1H470J B 134.2/32.4

C548 4030017460 S.CER ECJ0EB1E102K B 161/27.5

C549 4030017460 S.CER ECJ0EB1E102K B 44.1/47.4

C551 4030017420 S.CER ECJ0EC1H470J B 158.1/19.3

C553 4030017420 S.CER ECJ0EC1H470J B 140.6/17.6

C555 4030018860 S.CER ECJ0EB0J105K B 148.5/17.9

C556 4030016790 S.CER ECJ0EB1C103K B 143.1/23.6

C558 4550006480 S.TAN TEESVA 1C 475M8R B 143.5/22

C559 4030017730 S.CER ECJ0EB1E471K B 166.3/51.1

C560 4030017730 S.CER ECJ0EB1E471K B 153.1/51.1

C561 4030017730 S.CER ECJ0EB1E471K B 161.9/46.9

C562 4030017730 S.CER ECJ0EB1E471K B 147.4/46.6

C563 4030016930 S.CER ECJ0EB1A104K B 105.1/28

C564 4030016930 S.CER ECJ0EB1A104K B 103.2/28

C565 4030016930 S.CER ECJ0EB1A104K B 44/29.9

C566 4030017460 S.CER ECJ0EB1E102K B 42.8/49.5

C567 4030016930 S.CER ECJ0EB1A104K B 42.8/50.4

C568 4030017460 S.CER ECJ0EB1E102K B 67.3/6.6

C569 4550006250 S.TAN TEESVA 1A 106M8R B 89.6/40.7

C573 4030016930 S.CER ECJ0EB1A104K B 34.7/23.7

C574 4030016930 S.CER ECJ0EB1A104K B 62.6/11.9

C575 4510009020 S.ELE EEE0JA331P B 106/11.4

J501 6510019121 S.CNR S8B-PH-SM4-TB (LF) (SN) B 26.9/27.5

J502 6510019121 S.CNR S8B-PH-SM4-TB (LF) (SN) B 52.9/15.1

J503 6450002210 CNR 3017-8821 <KIN>

J504 6510014961 S.CNR B2B-ZR-SM4-TF (LF) (SN) B 18.4/57

DS500 5030002811 LCD L4-0013TVY-2

DS501 5040002710 LED EMPG3338S

DS502 5040002720 LED EMVR3338S

DS503 5040002710 LED EMPG3338S

DS504 5040002720 LED EMVR3338S

DS505 5040002310 S.LED SML-311YTT86 T 111.2/43.2

DS506 5040002310 S.LED SML-311YTT86 T 101.3/43.2

DS507 5040002310 S.LED SML-311YTT86 T 91.3/43.2

DS508 5040002310 S.LED SML-311YTT86 T 81.2/43.1

DS509 5040002310 S.LED SML-311YTT86 T 71.3/43.2

DS510 5040002310 S.LED SML-311YTT86 T 61.3/43.2

DS511 5040002150 LED VRPG3349S-734

DS512 5040002150 LED VRPG3349S-734

Page 25

6 - 2

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

[FRONT UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

S506 2250000511 ECR RH70N1037E20-13F-2781

SP501 2510001221 SP C052SB500-14

W501 8900011800 CBL OPC-1199

W502 8900017540 CBL OPC-1785

EP501 8930065150 LCT SRCN-2781-SP-N-W (SHJ)

EP503 6910019600 SCR LM-5

EP504 6910019610 SCR LM-7 (SPACER)

S.=Surface mount

[MAIN UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

IC1 1110005330 S.IC NJM12904V-TE1-#ZZZB T 58.1/71.4

IC2 1110007290 S.IC AK2330P-L T 58.7/56.1

IC3 1130010100 S.IC LMX2352TMX/NOPB B 120.2/43.9

IC4 1130010100 S.IC LMX2352TMX/NOPB B 28/78.8

IC5 1110003491 S.IC TA31136FNG (D,EL) B 70.4/82.5

IC7 1110007280 S.IC NJM2716F-TE1-#ZZZB B 56.8/46.4

IC8 1130012910 S.IC AK4554VTP-E2/P B 36.2/59.9

IC9 1190002080 S.IC AD7476ARTZ-500RL7 B 49.6/46.4

IC10 1130013040 S.IC TC7WBD125AFK (T5L,F) B 46.6/49.2

IC11 1110006230 S.IC NJM2711F-TE1-#ZZZB B 53.1/35

IC12 1140013290 S.IC TMS320VC5509AZHH B 33.3/37.8

IC13 1180002590 S.REG XC6204B332MR T 80.9/21.3

IC14 1180003270 S.REG R1114Q161D-TR-F T 84.4/21.4

IC15 1180002590 S.REG XC6204B332MR T 87.8/21.3

IC17 1190001340 S.IC M62334FP 600C T 67.3/61.7

IC18 1110005771 S.IC S-80942CNMC-G9CT2G T 41.2/52.8

IC19 1180003210 S.REG NJM2831F10 B 111/26.2

IC20 1140014550 S.IC HD64F2506RFC26DV T 33.5/37.6

IC21 1140012950 S.IC 24LC512T-I/SM T 59.1/21.8

IC22 1150002042 IC RA30H1317M-121 [EUR-01]

1150002073 IC RA60H1317M-125

[USA-01], [EXP-01]

IC23 1110002751 S.IC TA75S01F (TE85R,F) T 141.7/125.1

IC25 1130008561 S.IC TC75S51F (TE85L,F) B 29/16.3

IC26 1120003070 S.IC MAX3232EIPWR T 42.7/70

IC27 1180001251 S.IC TA7808F (TE16L,Q) T 114.4/85

IC28 1110003091 IC LA4425A-E

IC29 1110002751 S.IC TA75S01F (TE85R,F) T 12/123.1

IC30 1110003390 S.IC AN8005M-(E1) T 98.3/91.4

IC31 1130011760 S.IC CD4094BPWR T 8.1/45.2

IC32 1130013360 S.IC AT25F2048N-10SU-2.7SL383 B 8.9/36.1

IC34 1110005340 S.IC NJM12902V-TE1-#ZZZB B 12.2/58.2

IC35 1140013200 S.IC CD4053BPWR B 20.6/58.2

IC36 1110005330 S.IC NJM12904V-TE1-#ZZZB B 27.8/55.4

IC37 1120002830 S.IC NJM2125F-TE1-#FZZB T 56.6/66.7

IC38 1110006380 S.IC LM2904PWR T 114.1/23.8

IC39 1180001071 S.IC TA7805F (TE16L,Q) T 101.2/24.3

IC40 1110005330 S.IC NJM12904V-TE1-#ZZZB B 50.6/57.2

IC41 1180001251 S.IC TA7808F (TE16L,Q) B 132/16.7

Q1 1590003230 S.TR UNR9113J-(TX) B 53.4/79.7

Q2 1530002851 S.TR 2SC4116-BL (TE85R,F) B 34.9/77.7

Q3 1560001360 S.FET 2SK3019 TL B 66.4/76.3

Q5 1560000541 S.FET 2SK880-Y (T5RICOM,F) B 35.7/107.1

Q7 1530002601 S.TR 2SC4215-O (TE85R,F) B 73/92.9

Q8 1560000541 S.FET 2SK880-Y (T5RICOM,F) B 89.5/46

Q9 1560001360 S.FET 2SK3019 TL B 39.6/103.6

Q10 1530002851 S.TR 2SC4116-BL (TE85R,F) B 89.5/43.5

Q11 1530002851 S.TR 2SC4116-BL (TE85R,F) B 30.6/104.2

Q12 1590003230 S.TR UNR9113J-(TX) B 66.1/100.3

Q13 1530002851 S.TR 2SC4116-BL (TE85R,F) B 84.7/43.5

Q14 1530002851 S.TR 2SC4116-BL (TE85R,F) B 30.6/107.1

Q15 1530002851 S.TR 2SC4116-BL (TE85R,F) B 96.9/44.4

Q16 1530002851 S.TR 2SC4116-BL (TE85R,F) T 35.2/108.3

Q19 1530002601 S.TR 2SC4215-O (TE85R,F) B 63.2/106.8

Q20 1530002920 S.TR 2SC4226-T1 R25 B 39.9/123.1

Q21 1530002920 S.TR 2SC4226-T1 R25 B 39.6/114.5

Q22 1530002920 S.TR 2SC4226-T1 R25 B 95.2/64.3

Q23 1530002920 S.TR 2SC4226-T1 R25 B 95.2/54.5

Q24 1530003311 S.TR 2SC5107-O (TE85R,F) B 100.6/58.6

Q25 1530003311 S.TR 2SC5107-O (TE85R,F) B 44.9/117.4

Q26 1590001400 S.TR XP1214 (TX) B 40.5/117.8

Q27 1590001400 S.TR XP1214 (TX) B 96/59.6

Q28 1590003290 S.TR UNR9213J-(TX) B 93.3/59.6

Q29 1590003290 S.TR UNR9213J-(TX) T 57.2/41.9

Q30 1590003290 S.TR UNR9213J-(TX) B 37.8/117.8

Q31 1590003230 S.TR UNR9113J-(TX) T 57.2/39.8

Q32 1530003311 S.TR 2SC5107-O (TE85R,F) B 46.2/111.7

Q33 1530003311 S.TR 2SC5107-O (TE85R,F) B 101.9/53

Q34 1530003311 S.TR 2SC5107-O (TE85R,F) B 46.2/123.1

Q35 1530003311 S.TR 2SC5107-O (TE85R,F) B 101.9/64.4

Q36 1580000731 S.FET 3SK293 (TE85L,F) B 48.3/136.6

Q37 1530003311 S.TR 2SC5107-O (TE85R,F) B 132.4/84.5

Q38 1530002680 S.TR 2SC3357-T1 B 139.5/86

Q39 1560000841 S.FET 2SK1829 (TE85R,F) B 54.2/142.5

Q40 1590001190 S.TR XP6501-(TX) .AB T 101.6/87.4

Q41 1520000460 S.TR 2SB1132 T100 R T 101.6/82.8

Q42 1590003290 S.TR UNR9213J-(TX) T 13.3/67.6

Q43 1590003290 S.TR UNR9213J-(TX) T 137.3/125

Q44 1590003290 S.TR UNR9213J-(TX) T 114.3/80.1

Q45 1540000550 S.TR 2SD1664 T100Q T 118.4/75.2

Q46 1530002851 S.TR 2SC4116-BL (TE85R,F) T 137.3/120.2

Q48 1510000920 S.TR 2SA1577 T106 Q T 101.5/77.8

Q49 1590003290 S.TR UNR9213J-(TX) T 102.2/73.7

Q52 1590003290 S.TR UNR9213J-(TX) T 10.9/131.6

Q53 1590003290 S.TR UNR9213J-(TX) T 10.9/129.6

Q56 1590003321 S.FET TPC6103 (TE85L,F) T 7.6/132.6

Q57 1550000100 S.FET 2SJ377 (TE16L1,NQ) T 123.3/99.6

Q58 1590003290 S.TR UNR9213J-(TX) T 129.4/102.2

Q59 1590000990 S.TR DTC363EK T146 T 7.6/127.6

Q61 1530002851 S.TR 2SC4116-BL (TE85R,F) T 6.8/118.4

Q62 1540000441 S.TR 2SD1619T-TD-E T 118.4/18.6

Q63 1560000990 S.FET PMBFJ310 B 66.3/110

Q64 1560000990 S.FET PMBFJ310 B 63.4/110

Q65 1530003311 S.TR 2SC5107-O (TE85R,F) B 59.6/123.7

Q66 1590003290 S.TR UNR9213J-(TX) B 94.9/4.7

Q67 1590003290 S.TR UNR9213J-(TX) B 124.9/4.7

Q68 1590003290 S.TR UNR9213J-(TX) B 109.9/4.7

Q69 1590003290 S.TR UNR9213J-(TX) T 9.5/53.3

Q70 1590003230 S.TR UNR9113J-(TX) T 9.5/51

Q71 1560000990 S.FET PMBFJ310 B 60.5/110

Q72 1530002851 S.TR 2SC4116-BL (TE85R,F) B 107/26.3

Page 26

6 - 3

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

[MAIN UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

D1 1750001070 S.DIO DAN235ETL B 57.3/78.6

D2 1750001070 S.DIO DAN235ETL B 50/79.7

D3 1790001621 S.DIO 1SV308 (TPL3,F) B 69.3/94.8

D4 1790001621 S.DIO 1SV308 (TPL3,F) B 69.3/92.2

D5 1720000641 S.VCP 1SV284 (TPH3,F) B 29.9/120.1

D7 1720000791 S.VCP HVC321B1TRF-E B 28.6/125.1

D8 1720000791 S.VCP HVC321B1TRF-E B 26.5/113.3

D9 1720000791 S.VCP HVC321B1TRF-E B 84.7/59.8

D10 1720000791 S.VCP HVC321B1TRF-E B 86.4/51.2

D11 1790001621 S.DIO 1SV308 (TPL3,F) B 63.5/103.1

D12 1790001621 S.DIO 1SV308 (TPL3,F) B 62.4/101.1

D13 1720000791 S.VCP HVC321B1TRF-E B 84.9/61.8

D14 1720000791 S.VCP HVC321B1TRF-E B 84.4/52

D15 1720000791 S.VCP HVC321B1TRF-E B 28.6/122.6

D16 1720000791 S.VCP HVC321B1TRF-E B 26.5/114.6

D17 1720000641 S.VCP 1SV284 (TPH3,F) B 83.5/63.5

D18 1720000471 S.VCP 1SV239 (TPH3,F) B 96.3/66.7

D19 1750000520 S.DIO DAN222TL T 59.6/39.8

D20 1790001260 S.DIO MA2S077-(TX) T 39.5/57.9

D21 1750001610 S.VCP HVC365TRF-E B 63/139.4

D22 1750001610 S.VCP HVC365TRF-E B 59.8/136.7

D23 1750001610 S.VCP HVC365TRF-E B 63/136.7

D24 1750001610 S.VCP HVC365TRF-E B 59.8/139.4

D25 1750000370 S.DIO DA221 TL B 46.5/142.5

D26 1790001250 S.DIO MA2S111-(TX) B 48.3/142.5

D27 1790001250 S.DIO MA2S111-(TX) B 58.3/142.5

D28 1750001610 S.VCP HVC365TRF-E

[USA-01], [EXP-01] B 37.6/138.4

D29 1750001610 S.VCP HVC365TRF-E

[USA-01], [EXP-01] B 37.6/135.7

D30 1720000471 S.VCP 1SV239 (TPH3,F) B 95.6/56.8

D31 1750001610 S.VCP HVC365TRF-E B 34.4/135.7

D32 1750001610 S.VCP HVC365TRF-E B 34.4/138.4

D35 1750000351 S.DIO 1SV252 (TE85L,F) B 143.7/92.9

D36 1750001080 S.DIO RB886G T2R T 144.4/120.2

D37 1750001080 S.DIO RB886G T2R T 145.6/120.2

D38 1750001360 S.DIO L709CER (9401) B 84.7/134

D39 1750000581 S.DIO 1SV307 (TPH3,F) B 36/144.8

D40 1750000370 S.DIO DA221 TL T 114.3/77.8

D42 1720000641 S.VCP 1SV284 (TPH3,F) B 26.5/112

D44 1710001061 DIO L407CDB

D45 1790001211 S.DIO 1SS375-TL-E B 83.8/128

D46 1750000520 S.DIO DAN222TL T 13.3/131.1

D47 1750000520 S.DIO DAN222TL T 13.2/129.1

D48 1790001211 S.DIO 1SS375-TL-E B 119.6/144.5

D49 1790001211 S.DIO 1SS375-TL-E B 139.5/133.2

D51 1790001250 S.DIO MA2S111-(TX) T 10.5/127.1

D53 1790001810 S.VSR AVR-M1005C080MTABB T 32.5/11.7

D55 1790001810 S.VSR AVR-M1005C080MTABB T 30.5/11.7

D56 1790001810 S.VSR AVR-M1005C080MTABB T 36.6/11.7

D59 1790000700 DIO DSA3A1

D61 1750000520 S.DIO DAN222TL T 118.4/14.7

D62 1750000431 S.DIO HSB88WSTR-E B 68.3/123.3

D63 1790001250 S.DIO MA2S111-(TX) B 34.2/20.8

D64 1750000370 S.DIO DA221 TL T 63.2/93.9

D65 1750000370 S.DIO DA221 TL T 65.2/93.9

D66 1750000370 S.DIO DA221 TL T 67.2/93.9

D67 1750000370 S.DIO DA221 TL T 61.9/105.9

D68 1750000370 S.DIO DA221 TL T 59.9/105.5

D69 1750000370 S.DIO DA221 TL T 69.2/93.9

D70 1750000370 S.DIO DA221 TL T 71.2/93.9

D71 1750000370 S.DIO DA221 TL T 69.1/109.5

D72 1750000370 S.DIO DA221 TL T 71.2/109.5

D73 1750000370 S.DIO DA221 TL T 73.3/109.5

D74 1750000370 S.DIO DA221 TL T 75.3/109.5

D75 1790001250 S.DIO MA2S111-(TX) B 41/38.6

D76 1790001250 S.DIO MA2S111-(TX) B 26.4/41.3

D77 1790001250 S.DIO MA2S111-(TX) B 49.2/29.9

D78 1730002360 S.ZEN MA8062-M (TX) B 52.3/29.9

D79 1720000641 S.VCP 1SV284 (TPH3,F) B 83.1/52

FI1 2020001520 CER CFWLA450KFFA-B0

FI2 2020001460 CER CFWLA450KHFA-B0

FI3 2030000500 S.MLH FL-401 (46.35 MHz) B 72/101

FI4 2030000670 S.MLH FL-420 (46.35 MHz) B 63.4/91.1

FI5 2040001440 S.LC NFE31PT152Z1E9L T 116.5/108.3

FI6 2040001440 S.LC NFE31PT152Z1E9L T 116.5/111.5

FI7 2040001440 S.LC NFE31PT152Z1E9L T 116.5/114.6

X1 6050012380 S.XTL CR-826 (15.3 MHz) B 128.6/45.3

X2 6050012380 S.XTL CR-826 (15.3 MHz) B 35.6/72.3

X3 6070000300 S.DCR JTBM450CX24 <JJE> B 63.5/83.5

X4 6050012350 S.XTL CR-817 (12.288 MHz) B 52.8/38.2

X5 6050012680 S.XTL CR-858 (SMD-49/18.432MHZ) T 46.9/52.7

L1 6200004660 S.COL MLF1608A 1R8K-T B 115.5/39.2

L2 6200004660 S.COL MLF1608A 1R8K-T B 23.6/82.4

L3 6200004480 S.COL MLF1608D R82K-T B 39.4/79.3

L4 6200003540 S.COL MLF1608D R22K-T B 36.9/76.9

L5 6200005691 S.COL ELJRE 18NGFA B 102.7/45.6

L6 6200005691 S.COL ELJRE 18NGFA B 47.3/101.1

L7 6200005661 S.COL ELJRE 10NGFA B 44/99.1

L8 6200007120 S.COL ELJND 1R0J B 27/124.1

L9 6200007120 S.COL ELJND 1R0J B 27/120.8

L10 6200007120 S.COL ELJND 1R0J B 25.9/116.8

L11 6200007120 S.COL ELJND 1R0J B 82.5/61.4

L12 6200007120 S.COL ELJND 1R0J B 83.1/49.9

L13 6200007120 S.COL ELJND 1R0J B 28.7/111.6

L14 6200007120 S.COL ELJND 1R0J B 85.3/66.4

L15 6200013220 S.COL C6342A-R13G-A B 88.6/54.6

L16 6200010600 S.COL C6342A-67NG-A B 33.8/122.7

S.=Surface mount

[MAIN UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

L17 6200007120 S.COL ELJND 1R0J B 28.7/116.8

L18 6200009910 S.COL C6342A-88NG-A B 88.8/63.9

L19 6200007120 S.COL ELJND 1R0J B 83.5/66.4

L20 6200007120 S.COL ELJND 1R0J B 30.2/124.7

L21 6200009910 S.COL C6342A-88NG-A B 33.1/114.4

L22 6200003550 S.COL MLF1608A 4R7K-T B 73.4/109.9

L23 6200005011 S.COL NLV25T-100J B 60.5/113.3

L24 6200010740 S.COL C2520C-R27G-A B 70/109.1

L25 6200007120 S.COL ELJND 1R0J B 97.4/62.5

L26 6200007120 S.COL ELJND 1R0J B 98/56.1

L27 6130002961 S.COL #617DB-1327=P3 B 68.3/117

L28 6200007001 S.COL ELJRE 82NGFA B 62.3/123.6

L29 6200006981 S.COL ELJRE R10GFA B 102.6/58.6

L30 6200006981 S.COL ELJRE R10GFA B 46.9/117.4

L31 6200002861 S.COL NLV25T-4R7J T 91.2/20

L32 6130002961 S.COL #617DB-1327=P3 B 68.3/128.7

L33 6200005691 S.COL ELJRE 18NGFA B 47.3/109.2

L34 6200005721 S.COL ELJRE 33NGFA B 61.1/117.5

L35 6200005691 S.COL ELJRE 18NGFA B 102.7/50.5

L36 6200007001 S.COL ELJRE 82NGFA B 44.3/123.1

L37 6200005721 S.COL ELJRE 33NGFA B 61.1/120.1

L38 6200007001 S.COL ELJRE 82NGFA B 100/64.4

L39 6200010610 S.COL C6342A-50NG-A B 67.4/138.5

L41 6200010610 S.COL C6342A-50NG-A B 53.7/136.7

L42 6200006981 S.COL ELJRE R10GFA B 134.5/84.5

L43 6200006671 S.COL ELJRE 68NGFA B 138.9/90.1

L44 6200010610 S.COL C6342A-50NG-A

[USA-01], [EXP-01] B 41.9/137.3

L45 6200005741 S.COL ELJRE 47NGFA B 142.8/87.4

L46 6200005741 S.COL ELJRE 47NGFA B 142.8/90.1

L47 6200010610 S.COL C6342A-50NG-A B 29.9/136.7

L48 6200007750 S.COL LQW2BHN56NJ03L

[USA-01], [EXP-01] B 33.3/141.2

6200010000 S.COL C2012C-56NG-A [EUR-01] B 33.3/141.2

L49 6200010050 S.COL AS080547-47N B 97.2/119.2

L50 6200007750 S.COL LQW2BHN56NJ03L B 85.5/137.4

L51 6200007750 S.COL LQW2BHN56NJ03L

[USA-01], [EXP-01] B 25.1/142.9

6200010000 S.COL C2012C-56NG-A [EUR-01] B 25.1/142.9

L52 6200010420 S.COL FHW1210HC 1R0JGT <JJE> B 86.6/122.3

L53 6200010050 S.COL AS080547-47N B 90.1/135.3

L55 6200010050 S.COL AS080547-47N B 107.6/135

L56 6200010050 S.COL AS080547-47N B 115.2/138.8

L57 6200010050 S.COL AS080547-47N B 143.7/140.9

L58 6200002861 S.COL NLV25T-4R7J T 55.4/37.5

L59 6200010420 S.COL FHW1210HC 1R0JGT <JJE> B 147.1/146.2

L60 6200010420 S.COL FHW1210HC 1R0JGT <JJE> B 24.5/147

L61 6200002961 S.COL NLV32T-4R7J T 118.4/23.8

L62 6200013530 S.COL MLF2012E 100K-T B 83.7/56.6

L63 6200010000 S.COL C2012C-56NG-A B 72.3/137.8

L64 6200007120 S.COL ELJND 1R0J B 81.8/54.9

L65 6200007120 S.COL ELJND 1R0J B 41.7/120.7

L66 6200007120 S.COL ELJND 1R0J B 42.4/115.2

L68 6200003960 S.COL MLF1608A 1R0K-T B 140.7/94.7

L69 6200005661 S.COL ELJRE 10NGFA B 102.7/42.3

R1 7030005310 S.RES ERJ2GEJ 124 X (120 k) T 54.9/64.1

R2 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 58.7/61.7

R3 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 62.4/69.6

R4 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 57.3/80.1

R6 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) T 9.5/57.1

R7 7030010040 S.RES ERJ2GEJ-JPW T 61.6/66.3

R8 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 24.9/70.4

R9 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 25.8/70.4

R10 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 26.7/70.4

R12 7510001730 S.TMR ERTJOEP 473J B 129.1/49.3

R13 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 130.8/49.3

R15 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 54.5/78.3

R17 7030004980 S.RES ERJ2GEJ 101 X (100) T 19.8/68.8

R18 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 55.3/79.2

R20 7030009150 S.RES ERJ2GEJ 824 X (820 k) T 56.1/63.5

R22 7410001130 S.ARY EXB28V102JX B 122.6/39

R23 7410001130 S.ARY EXB28V102JX B 23.1/76.3

R24 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 115.5/42.2

R25 7030004970 S.RES ERJ2GEJ 470 X (47) B 65.3/79.4

R26 7030010040 S.RES ERJ2GEJ-JPW T 57.7/64.5

R27 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 57.8/51

R29 7030007570 S.RES ERJ2GEJ 122 X (1.2 k) B 38.5/75.9

R30 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 52.8/81.1

R32 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 51.2/78.3

R33 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 48.4/78.2

R34 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 27.1/68.1

R35 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 28/68.1

R36 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 28.9/68.1

R38 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 27.6/70.4

R39 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 28.6/70.4

R40 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 29.5/70.4

R41 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 68.2/78.2

R42 7030006610 S.RES ERJ2GEJ 394 X (390 k) B 34.4/75.5

R43 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 62.8/77.3

R44 7030005030 S.RES ERJ2GEJ 152 X (1.5 k) B 71.4/78.2

R45 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 64.6/75.5

R46 7030005000 S.RES ERJ2GEJ 471 X (470) T 52.7/57.1

R47 7030005720 S.RES ERJ2GEJ 563 X (56 k) B 64.6/76.4

R48 7030005030 S.RES ERJ2GEJ 152 X (1.5 k) B 62.8/76.4

R49 7030010040 S.RES ERJ2GEJ-JPW T 55.6/57.3

R52 7030004980 S.RES ERJ2GEJ 101 X (100) B 34.1/56.4

R53 7030005210 S.RES ERJ2GEJ 822 X (8.2 k) B 16.8/57.6

R54 7030005000 S.RES ERJ2GEJ 471 X (470) B 19.4/64.3

R56 7030004970 S.RES ERJ2GEJ 470 X (47) B 121.9/50.4

R57 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 62.8/75.5

R58 7030008290 S.RES ERJ2GEJ 183 X (18 k) B 56.5/49

R59 7030008290 S.RES ERJ2GEJ 183 X (18 k) B 57.4/49

Page 27

7 - 4

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

[MAIN UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

R60 7030005000 S.RES ERJ2GEJ 471 X (470) B 32.3/74.3

R62 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 18.5/62.5

R63 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 55.6/60.5

R65 7030005000 S.RES ERJ2GEJ 471 X (470) B 125.1/47.3

R66 7030004980 S.RES ERJ2GEJ 101 X (100) B 56.5/50.6

R68 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 67.5/86.7

R69 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 32.7/83

R70 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 69.8/71.9

R71 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 31/62.6

R72 7030004980 S.RES ERJ2GEJ 101 X (100) B 57.6/44.2

R73 7030010040 S.RES ERJ2GEJ-JPW B 28.3/100.4

R74 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 25.8/83.5

R75 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 39.9/71.1

R76 7030010040 S.RES ERJ2GEJ-JPW B 93.7/41.6

R77 7030005580 S.RES ERJ2GEJ 560 X (56) B 119.7/48.8

R78 7030010040 S.RES ERJ2GEJ-JPW B 29.9/99.3

R79 7030005580 S.RES ERJ2GEJ 560 X (56) B 32.7/79.5

R80 7030004970 S.RES ERJ2GEJ 470 X (47) B 23.5/41.1

R81 7030007250 S.RES ERJ2GEJ 220 X (22) B 49.9/50.5

R82 7030008400 S.RES ERJ2GEJ 182 X (1.8 k) B 56/44.2

R83 7030010040 S.RES ERJ2GEJ-JPW B 32.4/106.5

R84 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 93.7/47.1

R85 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 37.8/107.1

R86 7030010040 S.RES ERJ2GEJ-JPW B 33.2/105.2

R87 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 73.7/81.1

R88 7030005530 S.RES ERJ2GEJ 100 X (10) B 39/71.1

R89 7030008400 S.RES ERJ2GEJ 182 X (1.8 k) B 67.1/83.2

R90 7030008010 S.RES ERJ2GEJ 123 X (12 k) T 54.5/73.3

R91 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 92.1/47.1

R92 7030009140 S.RES ERJ2GEJ 272 X (2.7 k) B 92.1/41.6

R93 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 37.8/106.1

R94 7030009140 S.RES ERJ2GEJ 272 X (2.7 k) B 28.3/98.3

R97 7410001170 S.ARY EXB28V470JX B 42.9/49.9

R98 7030005530 S.RES ERJ2GEJ 100 X (10) B 71/95.7

R99 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 71/92.9

R100 7030005600 S.RES ERJ2GEJ 273 X (27 k) B 67.9/93.8

R101 7030004980 S.RES ERJ2GEJ 101 X (100) B 92.1/42.6

R102 7030004980 S.RES ERJ2GEJ 101 X (100) B 34.8/105.2

R103 7030004980 S.RES ERJ2GEJ 101 X (100) B 28.3/101.3

R105 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 33.7/107.9

R107 7030004980 S.RES ERJ2GEJ 101 X (100) B 87.1/47.1

R109 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 64.8/98.2

R111 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 37.8/104.4

R112 7030005070 S.RES ERJ2GEJ 683 X (68 k) B 84.7/45.3

R113 7030005070 S.RES ERJ2GEJ 683 X (68 k) B 32.4/108.1

R114 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 67.4/96.2

R115 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 67.9/91.3

R116 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 87.1/45.3

R117 7030005810 S.RES RR0510P-152-D (1.5 k) B 87.1/46.2

R118 7030007280 S.RES ERJ2GEJ 331 X (330) B 72.8/94.8

R119 7030007270 S.RES ERJ2GEJ 151 X (150) B 68.1/89

R120 7030005810 S.RES RR0510P-152-D (1.5 k) B 33.7/107

R121 7030008280 S.RES ERJ2GEJ 271 X (270) B 27.3/108.7

R122 7030004970 S.RES ERJ2GEJ 470 X (47) B 56.6/33.9

R123 7030004970 S.RES ERJ2GEJ 470 X (47) B 49.5/38.5

R124 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 55.3/38.3

R125 7030008280 S.RES ERJ2GEJ 271 X (270) B 84.7/46.2

R126 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 96.5/42.6

R127 7030005720 S.RES ERJ2GEJ 563 X (56 k) T 88.4/58.4

R128 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) T 33.4/108.3

R129 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 55.3/35.1

R130 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 56.2/36.7

R131 7030004980 S.RES ERJ2GEJ 101 X (100) B 54.2/32.4

R132 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 50.8/34.9

R133 7030007280 S.RES ERJ2GEJ 331 X (330) B 67.5/104.4

R134 7030007270 S.RES ERJ2GEJ 151 X (150) B 62.4/97.1

R136 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 81.8/65.5

R137 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 81.8/57

R138 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 95.3/65.8

R139 7030005060 S.RES ERJ2GEJ 333 X (33 k) T 95.3/64.9

R140 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 63.9/100.3

R141 7030005060 S.RES ERJ2GEJ 333 X (33 k) T 95.3/64

R142 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 65.4/102.5

R143 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 48.6/38.5

R144 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 48.6/36.8

R145 7030010040 S.RES ERJ2GEJ-JPW B 47.3/37.3

R146 7030005060 S.RES ERJ2GEJ 333 X (33 k) T 93.1/54.8

R148 7030004980 S.RES ERJ2GEJ 101 X (100) B 59.6/107.1

R151 7030005310 S.RES ERJ2GEJ 124 X (120 k) B 93.1/57.7

R152 7030005070 S.RES ERJ2GEJ 683 X (68 k) B 65.2/107

R153 7030005000 S.RES ERJ2GEJ 471 X (470) B 61.4/104.4

R154 7030008340 S.RES RR0510P-182-D (1.8 k) B 37.9/122.2

R155 7030011000 S.RES RR0510P-392-D (3.9 k) B 36.7/120.7

R156 7030011000 S.RES RR0510P-392-D (3.9 k) B 37.6/112

R157 7030005310 S.RES ERJ2GEJ 124 X (120 k) B 93/67.3

R158 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 93.1/56.7

R159 7030005530 S.RES ERJ2GEJ 100 X (10) B 65.2/106.1

R160 7030010040 S.RES ERJ2GEJ-JPW B 37.9/124

R161 7030008340 S.RES RR0510P-182-D (1.8 k) B 37.6/112.9

R162 7030010040 S.RES ERJ2GEJ-JPW B 37.6/114.7

R163 7030011000 S.RES RR0510P-392-D (3.9 k) B 91.7/62

R164 7030011000 S.RES RR0510P-392-D (3.9 k) B 93.1/52.3

R165 7030010040 S.RES ERJ2GEJ-JPW B 93/64.6

R166 7030010040 S.RES ERJ2GEJ-JPW B 93.1/55

R167 7030005530 S.RES ERJ2GEJ 100 X (10) B 62.5/112.2

R168 7030008340 S.RES RR0510P-182-D (1.8 k) B 93/62.8

R169 7030008340 S.RES RR0510P-182-D (1.8 k) B 93.1/53.2

R171 7030011920 S.RES RR0510P-561-D (560) B 41.7/123.2

R172 7030009820 S.RES RR0510P-681-D (680) B 97.4/65

R173 7030009820 S.RES RR0510P-681-D (680) B 97.2/53.7

R174 7030009820 S.RES RR0510P-681-D (680) B 42.1/113.8

R175 7030005530 S.RES ERJ2GEJ 100 X (10) B 73.6/111

R176 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 100.6/56.8

R177 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 44.9/115.6

S.=Surface mount

[MAIN UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

R178 7030004980 S.RES ERJ2GEJ 101 X (100) B 100.6/55.9

R179 7030004980 S.RES ERJ2GEJ 101 X (100) B 44.9/114.7

R180 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 37/108.3

R181 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 96.4/49

R182 7030007300 S.RES ERJ2GEJ 332 X (3.3 k)

[USA-01], [EXP-01] B 68.5/107

R184 7030008280 S.RES ERJ2GEJ 271 X (270) B 63.2/119.1

R185 7030010090 S.RES ERJ2GEJ 180 X (18) B 62.3/117.5

R186 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 39.2/50.7

R187 7030008010 S.RES ERJ2GEJ 123 X (12 k) T 41.5/55.9

R188 7410001150 S.ARY EXB28V471JX T 48.5/41.1

R189 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 55.6/39.5

R190 7030008010 S.RES ERJ2GEJ 123 X (12 k) T 43.1/55.9

R191 7030005000 S.RES ERJ2GEJ 471 X (470) B 43.5/112.2

R192 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 44.4/112.2

R193 7030008280 S.RES ERJ2GEJ 271 X (270) B 59.6/116.8

R194 7030004980 S.RES ERJ2GEJ 101 X (100) B 99.2/53

R195 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 100.1/53

R196 7030009320 S.RES ERJ2GEJ 4R7 X (4.7) B 48/120.7

R197 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 40.5/50.6

R198 7030009320 S.RES ERJ2GEJ 4R7 X (4.7) B 103.7/62

R199 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 67.6/57.5

R200 7030004980 S.RES ERJ2GEJ 101 X (100) B 43.1/123.1

R201 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 48/122.6

R202 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 41.4/48.6

R204 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 54.7/39.5

R205 7030008010 S.RES ERJ2GEJ 123 X (12 k) T 36.5/57.9

R207 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 103.7/64

R208 7030010040 S.RES ERJ2GEJ-JPW B 46.2/120.7

R209 7030005000 S.RES ERJ2GEJ 471 X (470) T 67.6/56.5

R212 7410001140 S.ARY EXB28V104JX T 52.3/41.1

R213 7030005530 S.RES ERJ2GEJ 100 X (10) T 41.4/47.7

R214 7030004980 S.RES ERJ2GEJ 101 X (100) B 98.9/64

R215 7030010040 S.RES ERJ2GEJ-JPW B 100.9/62

R216 7410001140 S.ARY EXB28V104JX T 17.3/52.4

R217 7410001140 S.ARY EXB28V104JX T 38.6/56

R218 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 61.4/138.5

R220 7410001140 S.ARY EXB28V104JX T 15.2/50.7

R222 7410001140 S.ARY EXB28V104JX T 36.1/56

R223 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 61.4/137.6

R224 7410001150 S.ARY EXB28V471JX T 30.4/53.1

R225 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 61.4/139.4

R226 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 39.9/72.7

R227 7410001150 S.ARY EXB28V471JX T 42.9/28.9

R230 7410001150 S.ARY EXB28V471JX T 28.6/50.9

R231 7030007270 S.RES ERJ2GEJ 151 X (150)

[USA-01], [EXP-01] B 58.2/139.4

7030009280 S.RES ERJ2GEJ 391 X [EUR-01] B 58.2/139.4

R232 7410001150 S.ARY EXB28V471JX T 25.9/49.4

R233 7030004980 S.RES ERJ2GEJ 101 X (100) B 58.2/135.8

R234 7410001150 S.ARY EXB28V471JX T 42.5/25.7

R235 7410001150 S.ARY EXB28V471JX T 24.2/47.6

R236 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 132.4/82.7

R237 7030005530 S.RES ERJ2GEJ 100 X (10) B 49.4/138.8

R238 7410001150 S.ARY EXB28V471JX T 45.7/28.9

R239 7410001150 S.ARY EXB28V471JX T 22.4/45.8

R240 7030004980 S.RES ERJ2GEJ 101 X (100) B 134.7/86.7

R241 7030007270 S.RES ERJ2GEJ 151 X (150) B 49.4/134.3

R242 7030009320 S.RES ERJ2GEJ 4R7 X (4.7) B 48.4/138.8

R243 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 47.4/138.8

R244 7410001150 S.ARY EXB28V471JX T 39.7/25.8

R245 7410001150 S.ARY EXB28V471JX T 20.2/42.4

R246 7030005310 S.RES ERJ2GEJ 124 X (120 k) B 45.6/136.6

R247 7030005720 S.RES ERJ2GEJ 563 X (56 k) B 48.4/140.4

R249 7030008010 S.RES ERJ2GEJ 123 X (12 k) B 135.6/88.4

R250 7030004980 S.RES ERJ2GEJ 101 X (100) B 133.8/90.1

R251 7030006610 S.RES ERJ2GEJ 394 X (390 k) B 49.4/142.5

R252 7030010040 S.RES ERJ2GEJ-JPW B 132/86.7

R253 7030004970 S.RES ERJ2GEJ 470 X (47) B 136.5/90.1

R255 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 52.4/142.5

R256 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 137.7/90.1

R257 7410001140 S.ARY EXB28V104JX T 14.5/45.7

R259 7030005170 S.RES ERJ2GEJ 474 X (470 k) B 57.1/142.5

R260 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 108.8/25.3

R261 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 52.5/25.2

R262 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 51.9/22.8

R263 7410001140 S.ARY EXB28V104JX T 46.2/20

R264 7410001140 S.ARY EXB28V104JX T 50.2/24

R265 7030010040 S.RES ERJ2GEJ-JPW B 87.1/43.5

R266 7030005090 S.RES ERJ2GEJ 104 X (100 k)

[USA-01], [EXP-01] only B 36/138.4

R267 7410001140 S.ARY EXB28V104JX T 15/42.5

R268 7410001150 S.ARY EXB28V471JX T 45.7/31.8

R269 7030004980 S.RES ERJ2GEJ 101 X (100) B 143.2/94.7

R270 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 36/136.6

R271 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 23.8/26.7

R272 7410001150 S.ARY EXB28V471JX T 17.9/32.3

R273 7410001150 S.ARY EXB28V471JX T 17.9/35.1

R274 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 36/137.5

R275 7030005060 S.RES ERJ2GEJ 333 X (33 k) T 93.1/55.7

R276 7030010040 S.RES ERJ2GEJ-JPW B 87.1/44.4

R277 7030004980 S.RES ERJ2GEJ 101 X (100) T 145/126

R278 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 13.9/65.6

R279 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) T 102.4/90.1

R280 7030004990 S.RES ERJ2GEJ 221 X (220) T 141.3/127.7

R281 7410001150 S.ARY EXB28V471JX T 21.3/31.8

R282 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 37.8/20.3

R283 7030005100 S.RES ERJ2GEJ 154 X (150 k) T 144/124.4

R285 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 101.6/79.5

R286 7030005080 S.RES ERJ2GEJ 823 X (82 k) B 40.8/72.7

R287 7410001140 S.ARY EXB28V104JX T 49.7/27.7

R288 7030007340 S.RES ERJ2GEJ 153 X (15 k) T 139.5/122.5

R289 7030006070 S.RES ERJ12YJ101U (100) B 86.9/117.5

R290 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 138.6/122.5

Page 28

7 - 5

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

[MAIN UNIT]

REF ORDER

DESCRIPTION

M.

H/V

NO. NO.

LOCATION

R291 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 137.6/127.7

R292 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 144/126

R293 7030004980 S.RES ERJ2GEJ 101 X (100) B 136.5/83.3

R294 7030004980 S.RES ERJ2GEJ 101 X (100) B 136.5/85

R295 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 137.6/122.5

R296 7030000440 S.RES MCR10EZHJ 3.3 k T 118.4/79.6

R297 7030000440 S.RES MCR10EZHJ 3.3 k T 120.2/79.6

R298 7030000440 S.RES MCR10EZHJ 3.3 k T 116.6/79.6

R299 7030004980 S.RES ERJ2GEJ 101 X (100) B 29.1/19.4

R300 7030005530 S.RES ERJ2GEJ 100 X (10) T 47.6/73.1

R301 7030008300 S.RES ERJ2GEJ 184 X (180 k) B 85.6/105.6

R302 7030005590 S.RES ERJ2GEJ 680 X (68) B 135.6/85

R303 7410001150 S.ARY EXB28V471JX T 47.7/68.4

R304 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 84.3/130

R306 7520000260 S.POS PRF18BB471QB1RB B 84.4/104.4

R308 7030005060 S.RES ERJ2GEJ 333 X (33 k)

[USA-01], [EXP-01] T 144/127.7

7030005070 S.RES ERJ2GEJ 683 X (68 k) [EUR-01] T 144/127.7

R309 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 102.2/75.7