VHF FM REPEATER

iC-fr3000

iC-fr3100

INTRODUCTION

This service manual describes the latest service information for the IC-FR3000/IC-FR3100 VHF FM REPEATER.

To upgrade quality, all electrical or mechanical parts and

internal circuits are subject to change without notice or

obligation.

DANGER

USE ONLY the specified AC voltage described on the

AC power socket. Other voltages may causes repeater

damage or personal injury.

DO NOT expose the repeater to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when

connecting the repeater.

DO NOT apply an RF signal of more than 20 dBm (100

mW) to the antenna connector. This could damage the

repeater’s front end.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit order numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

1110003780 S.IC NJM2902V IC-FR3000 LOGIC UNIT 1 piece

8930056450 2368 6-key IC-FR3000 CHASSIS 5 pieces

Addresses are provided on the inside back cover for your

convenience.

REPAIR NOTES

Make sure a problem is internal before disassembling

the repeater.

DO NOT open the repeater until the repeater is disconnected from its power source.

DO NOT force any of the variable components. Turn

them slowly and smoothly.

DO NOT short any circuits or electronic parts. An insulated tuning tool MUST be used for all adjustments.

DO NOT keep power ON for a long time when the repeater is defective.

DO NOT transmit power into a signal generator or a

sweep generator.

ALWAYS connect a 40 dB or 50 dB attenuator between the repeater and a deviation meter or spectrum

analyser when using such test equipment.

READ the instructions of test equipment thoroughly

before connecting equipment to the repeater.

1.

2.

3.

4.

5.

6.

7.

8.

VersionModel

Europe

U.S.A.

Germany

Symbol Frequency range

AC supply

USA

FRG2

Power

50 [W]100 –120 [V]

150 –174 [MHz]

150 –174 [MHz]

148 –172 [MHz]

IC-FR3000

IC-FR3100

GEN2

220 –240 [V]

General GEN4

GEN74

50 [W]

220 –240 [V]

EUR2

25 [W]

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

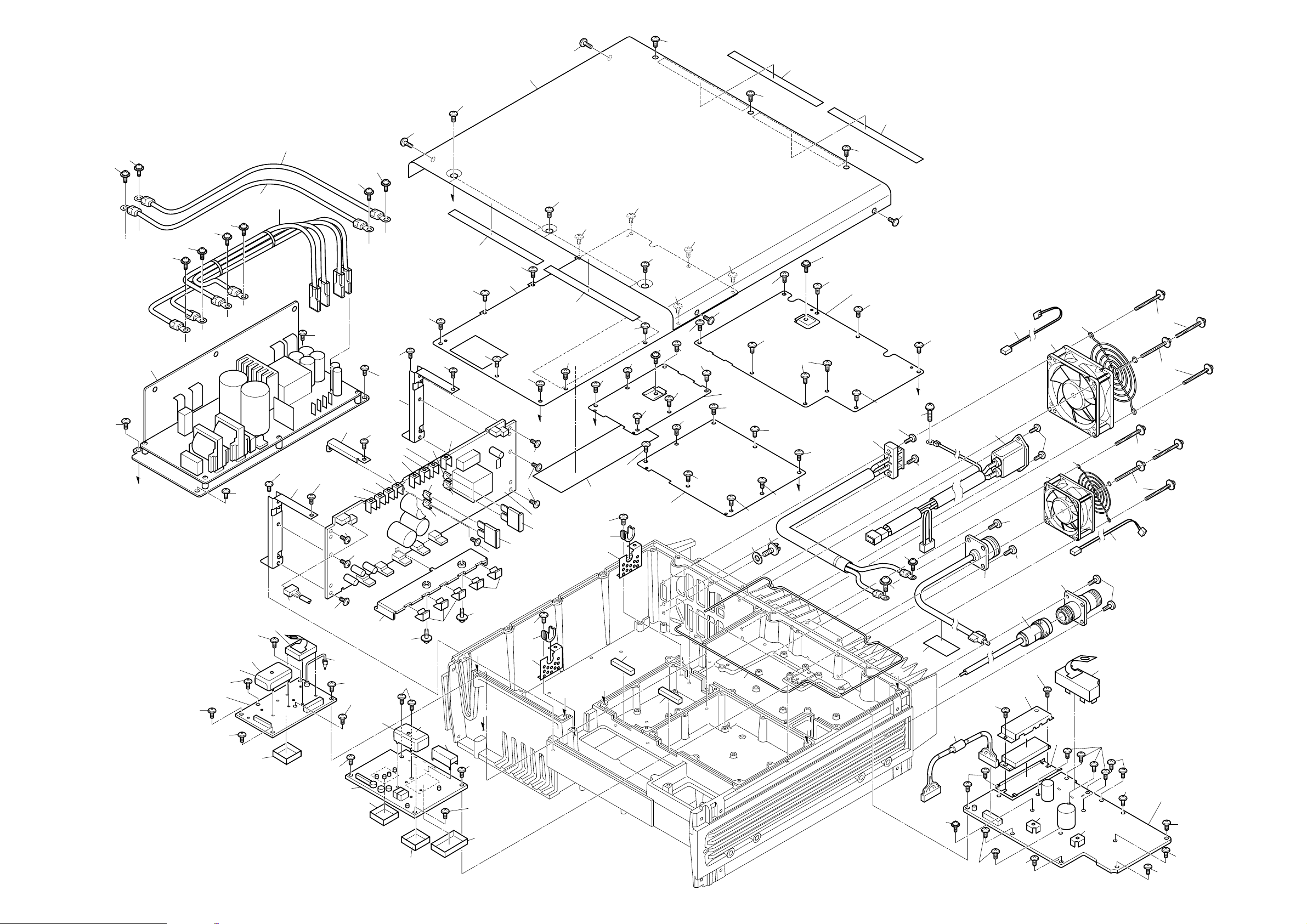

SECTION 2 INSIDE VIEWS

SECTION 3 CIRCUIT DESCRIPTION

3 - 1 RECEIVER CIRCUITS ................................................................................................... 3 - 1

3 - 2 TRANSMITTER CIRCUITS ............................................................................................ 3 - 2

3 - 3 PLL CIRCUITS................................................................................................................. 3 - 4

3 - 4 OTHER CIRCUITS .......................................................................................................... 3 - 5

3 - 5 POWER SUPPLY CIRCUITS ......................................................................................... 3 - 5

3 - 6 PORT ALLOCATIONS .................................................................................................... 3 - 6

SECTION 4 ADJUSTMENT PROCEDURES

4 - 1 PREPARATION................................................................................................................ 4 - 1

4 - 2 PLL ADJUSTMENT.......................................................................................................... 4 - 5

4 - 3 SOFTWARE ADJUSTMENT .......................................................................................... 4 - 6

SECTION 5 PARTS LIST

SECTION 6 OPTION UNIT INSTALLATION

SECTION 7 MECHANICAL PARTS AND DISASSEMBLY

SECTION 8 SEMI-CONDUCTOR INFORMATION

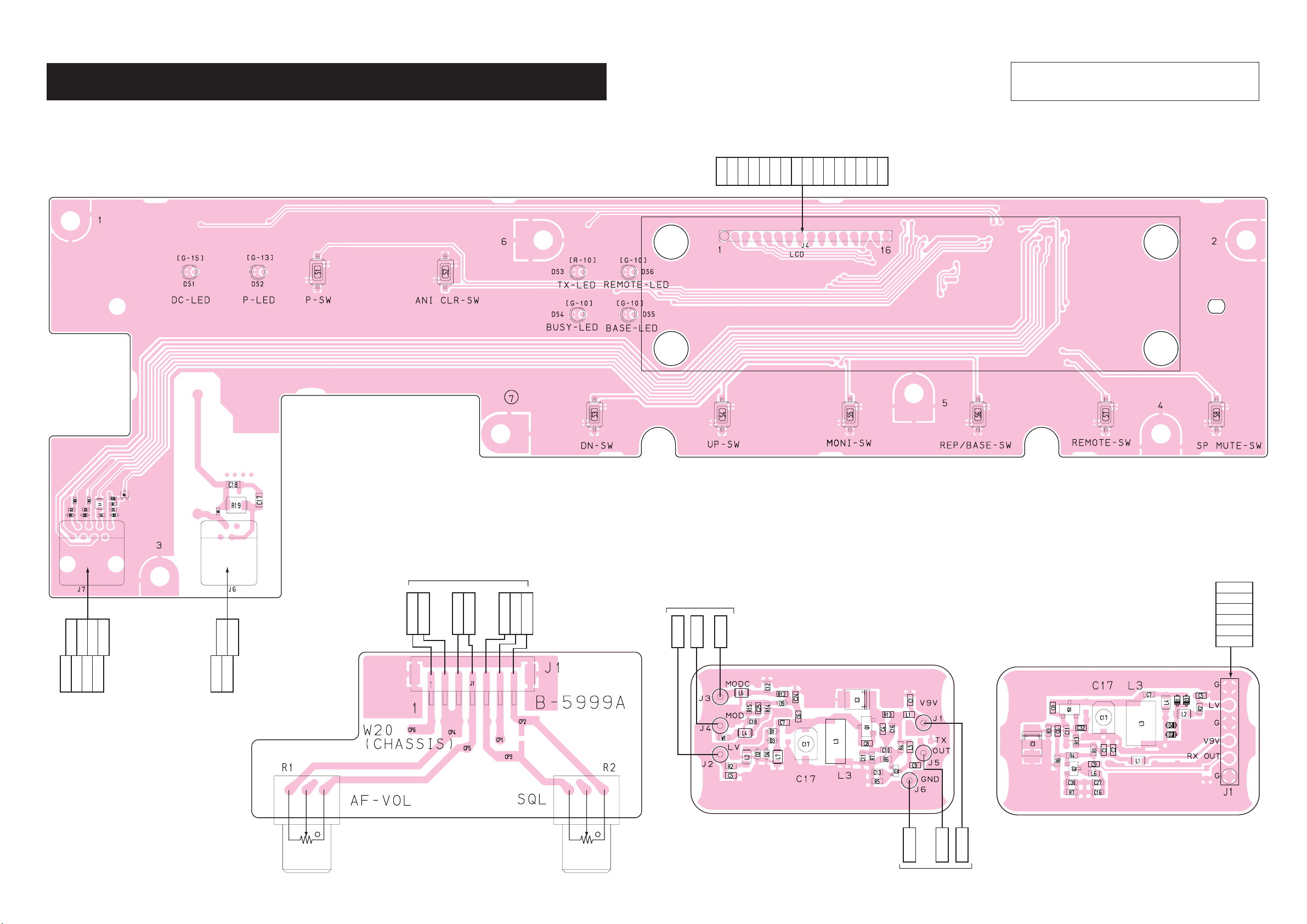

SECTION 9 BOARD LAYOUTS

9 - 1 FRONT UNIT..................................................................................................................9 - 1

9 - 2 VR UNIT ......................................................................................................................... 9 - 1

9 - 3 TVCO UNIT .................................................................................................................... 9 - 1

9 - 4 RVCO UNIT.................................................................................................................... 9 - 1

9 - 5 LOGIC UNIT................................................................................................................... 9 - 3

9 - 6 RX UNIT ......................................................................................................................... 9 - 5

9 - 7 TX UNIT ......................................................................................................................... 9 - 7

9 - 8 PA UNIT.......................................................................................................................... 9 - 9

9 - 9 REG UNIT ...................................................................................................................... 9 - 11

9 - 10 JACK1 UNIT................................................................................................................... 9 - 11

9 - 11 JACK2 UNIT................................................................................................................... 9 - 11

SECTION 10 BLOCK DIAGRAM

SECTION 11 WIRING DIAGRAM

SECTION 12 VOLTAGE DIAGRAM

Measurement method

Frequency range

Type of emission

Channel spacing

Frequency stability

Number of channels

Antenna connector

Power supply requirement

Current drain (approx.)

Operating temperature range

Dimensions (proj. not included)

Weight

(approx.)

RF output power (High/Low)

Modulation system

Maximum frequency deviation

Spurious emissions

Adjacent channel power

Input impedance

Receive system

Intermediate frequencies

Sensitivity (typical)

Adjacent channel selectivity (typical)

Spurious response

Intermodulation (typical)

Audio output power

Audio output impedance

IC-FR3000 IC-FR3100

SECTION 1 SPECIFICATIONS

1- 1

All stated specifications are subject to change without notice or obligation.

RECEIVER TRANSMITTER GENERAL

EIA / TIA-603 ETS 300 086

[USA2], [GEN2], [GEN4], [GEN74], [EUR2], [FRG2]: 150.000–174.000 MHz

[GEN74]: 148.000–172.000 MHz

Wide (25 kHz): 16K0F3E

Middle (20 kHz): 14K0F3E

Narrow (12.5 kHz): 8K50F3E

[USA2], [GEN2], [GEN4], [GEN74], [EUR2]: 25/12.5 kHz

[FRG2]: 20/12.5 kHz

±2.5 ppm ±1.0 kHz

Max. 32 channel

Type-N

× 2 (50 Ω)

[USA2], [GEN2]: 100–120 V

[GEN4], [GEN74], [EUR2], [FRG2]: 220–240 V

13.6 V DC (negative ground) 13.2 V DC (negative ground)

TX (at 50 W) 15.0 A TX (at 25 W) 10.0 A

RX (max. audio) 2 A

(stand-by) 1 A

–30˚C to +60˚C (–22˚F to +140˚F) –25˚C to +55˚C

410(W) × 110(H) × 360(D) mm; 16.1 (W)

×4.3 (H) × 14.1 (D) inch

12 kg; 26.5 lb

50/10 W 25/5 W

Variable reactance frequency modulation

[Wide]: ±5.0 kHz, [Middle]: ±4.0 kHz, [Narrow]: ±2.5 kHz

70 dBc typical 0.25 µW ≤ 1GHz, 1.0 µW > 1 GHz

[Wide], [Middle]: 70 dB, [Narrow]: 60 dB

600 Ω

Double-conversion superheterodyne system

1st: 31.65 MHz, 2nd: 455 kHz

0.5 µV at 12 dB SINAD 6 dBµV (emf) at 20 dB SINAD

[Wide], [Middle]: 70 dB, [Narrow]: 60 dB

70 dB

70 dB

2.5 W typical at 10% distortion with a 4 Ω load

4 Ω

AC

DC

TX

RX

2 - 1

JACK1 unit*

FRONT unit

JACK2 unit*

TX unit

RX unit

PA unit

REG unit

LOGIC unit*

SECTION 2 INSIDE VIEWS

• BOARD LAYOUT

*: Located under side of this point.

• PA UNIT

Top view

Pre-drive

(Q4: 2SK3475)

APC CTRL

(IC1: TA75S01F

Q9: DTC143ZU

Q10: DTC114EU)

+9 V switch

(Q7: DTC114EU

Q8: 2SA1362)

+5 V regulator

(IC7: TA78L05)

Power amplifier

(IC2:S-AV32 50 W type

S-AV33 25 W type)

2 - 2

• LOGIC UNIT

Top view

Bottom view

Splatter filter

(IC4: NJM2902V)

CTCSS decoder

(IC29: FX805LG)

D/A converter

(IC25: M62364)

Mic mix amplifier

(IC2: NJM2902V)

Mic amplifier

(IC1: NJM2902V)

AF amplifier

(IC17: LA4425A)

Mic mute

(IC13: BU4066)

LED current CTRL

(Q18, Q19, Q20: XP1114)

Temperature switching

circuit (IC32: TC4W53)

MIC amplifier, Limitter

(IC3: NJM2902V)

ON-HOOK signal output

(IC45: LM567M)

High-pass filter,

De-emphasis circuts

(IC9: NJM2902V)

RESET

(IC34: S-80842C)

CPU

(IC33: HD64F2238BF)

Ringer detect circuit

(IC48: TLP121)

EEPROM

(IC37: HN58X2464TI)

DTMF decoder

(IC30: TC4W53FU,

IC31: LC7387M)

2 - 3

• TX UNIT

Top view

*: Located under side of this point.

• RX UNIT

Top view

*: Located under side of this point.

PLL reference

oscillator

12.8 MHz

(X1: CR-759)

PLL IC*

(IC2: MB1511PFV)

TX VCO circuit

Mixer

(IC6: NJM2107F)

D/A converter*

(IC5: M62364FP)

RF amplifier

(Q1: 2SC5337)

PLL IC*

(IC4: MB1511PFV)

RX VCO circuit

IF amplifier

(Q3: 2SK1771)

2nd Lo oscillator

31.195 MHz

(X2: CR-757)

IF IC

(IC2: TA31136FN)

Noise amplifier

(IC8: NJM2902V)

Reference oscillator

12.8 MHz

(X3: CR-732)

1st Mixer

(IC1: GN2011)

Lo amplifier*

(Q8: 2SC4226,

Q9: 2SC4703)

SECTION 3 CIRCUIT DESCRIPTION

3 - 1

3-1 RECEIVER CIRCUITS

3-1-1 RF CIRCUIT

(RX

UNIT

)

Received signals from the RX antenna connector enter the

RX unit J1 and pass through a tuned bandpass filter (D3,

D4, L2, L3, C5–C8, C12, C13, C205, C206, C220, 221)

which is controlled by the D/A converter IC (LOGIC unit;

IC25). The filtered signals are applied to an RF amplifier

(Q1). The amplified signals are applied to a bandpass filter

(L6, L7, L12, L13, C9–C11, C14, C15, C21, C22, C24, C30,

C207, C208), and are then applied to the 1st mixer circuit.

3-1-2 1ST MIXER AND 1ST IF CIRCUITS (RX UNIT)

The 1st mixer circuit converts the received signals to a fixed

frequency of the 1st IF signal with the PLL output frequency.

By changing the PLL frequency, only the desired frequency

will pass through a crystal filter at the next stage of the 1st

mixer.

The filtered signals are applied to the 1st mixer circuit (L8,

L9, L10, IC1) and are then mixed with the 1st LO signal from

the PLL circuit to produce a 31.65 MHz 1st IF signal.

The 1st IF signal passes through a MCF (Monolithic Crystal

Filter; FI1) to suppress out-of-band signals. The filtered signal is applied to the 2nd mixer circuit (IC2, pin 16) via the

buffer amplifier (Q3).

3-1-3 2ND IF AND DEMODULATOR CIRCUITS

(RX UNIT)

The 2nd mixer circuit converts the 1st IF signal to a 2nd IF

signal. A double-conversion superheterodyne system

improves the image rejection ratio and obtains stable receiver gain.

The amplified signal is applied to the 2nd mixer section of

the FM IF IC (IC2, pin 16), and is then mixed with the 2nd

LO signal for conversion to a 455 kHz 2nd IF signal.

IC2 contains the 2nd mixer, limiter amplifier, quadrature

detector, active filter and noise amplifier circuits, etc. The

local oscillator section and X2 generate 31.195 MHz for the

2nd LO signal.

The 455 kHz 2nd IF signal is applied to a ceramic bandpass

filter (narrow; FI5, wide; FI6) where unwanted signals are

suppressed and are then applied to a limiter amplifier section in the system IC (IC2, pin 5).

The 2nd LO signal is then amplified at the limiter amplifier

section (IC2, pin 5) and applied to the quadrature detector

section (IC2, pins 10, 11 and X1) to demodulate the 2nd IF

signal into AF signals.

The AF signals are output from pin 9 (IC2) and are then

applied to the AF amplifier circuit on the LOGIC unit.

3-1-5 AF AMPLIFIER CIRCUIT (LOGIC UNIT)

The AF amplifier circuit amplifies the demodulated AF signals to drive a speaker.

The AF signals from the FM IF IC (RX unit; IC2, pin 9) are

applied to a buffer amplifier (IC9, pins 8, 9). The amplified

signals pass through the high-pass filter (IC9, pins 5, 7, 12,

14) which removes CTCSS or DTCS signals.

The filtered AF signals are output from pin 7 (IC9), and are

applied to the de-emphasis circuit (IC9, pins 1, 2) with frequency characteristics of –6 dB/octave, and then passed

through a low-pass filter (IC10, pins 1, 3, 5, 7). The filtered

signal is applied to a volume control (VR unit; R1) to control

the audio level.

IC2 contains the 2nd mixer, limiter amplifier, quadrature

detector, active filter and noise amplifier circuits, etc. The

local oscillator section and X2 generate 31.195 MHz for the

2nd LO signal.

The output AF signals from a volume control (VR unit; R1)

pass through the analog switch IC (IC16, pins 1, 7), and are

then applied to the AF power amplifier (IC17, pins 1, 4) to

drive a speaker.

• 2ND IF AND DEMODULATOR CIRCUITS (RX UNIT)

FI5

2nd IF filter

455 kHz

IF

amp.

QUAD.

detector

Active

filter

"DISC" signal to

LOGIC unit J1

X1

RSSI

2nd

Mixer

X2

1st IF from the IF amplifier (Q3)

"RSSI" signal to the CPU

8

7

531

16

13

11

109

IC2

TA31136FN

Noise

comp.

Noise

amp.

12

FI6

"N-DET" to the CPU

"SQL" signal to the

LOGIC unit J1

NARROW

WIDE

3 - 2

3-1-6 RECEIVER MUTE CIRCUITS (LOGIC UNIT)

• NOISE SQUELCH

The noise squelch circuit cuts out AF signals when no RF

signals are received. By detecting noise components in the

AF signals, the squelch circuit switches the AF mute switch.

Some noise components in the AF signals from the FM IF IC

(RX unit; IC2, pin 9) are passed through the SQL level controller (VR unit; R2). The level controlled signals are applied

to the active filter section in the FM IF IC (RX unit; IC2, pin

8). Noise components about 10 kHz are amplified and output from pin 7 (RX unit; IC2).

The filtered signals are converted to the pulse-type signals

at the noise detector section and output from pin 13 (RX

unit; IC2).

The NDET signal from the FM IF IC (RX unit; IC2) is applied

to the CPU (IC33, pin 40). The CPU analyses the noise condition and controls the AF mute signal via “AFMUTE1” line

(IC40, pin 4) to the AF mute switch (IC16, pin 5).

• TONE SIGNALS

The tone squelch circuit detects AF signals and opens the

squelch only when receiving a signal containing a matching

subaudible tone (CTCSS or DTCS).

The CTCSS signal passes through a low-pass filter circuit

(IC8, pins 1, 3, 5, 7, 8, 10), and is then applied to the signal

amplifier (IC8, pins 13, 14). The amplified signal is applied to

the CTCSS decoder IC (IC29, pin 16) and the detected sig-

nal is applied to the CPU (IC 33) via the serial signal line.

The DTCS signal passes through a low-pass filter circuit

(IC12, pins 1, 3, 8, 10), and is then applied to the signal

amplifier (IC12, pins 12, 14). the amplified signal is applied

to the DTCS decoder which is inside the CPU (IC33, pin 52)

via the “DTCSI” line.

The 2/5TONE signals are passes through a low-pass filter

circuit (IC12, pins 5, 7), and are then applied to the 2/5

TONE decoder which is inside the CPU (IC33, pin 51) via

“25TI” line.

The DTMF signal is pass through the DTMF switch IC (IC30

pin 7), and is then applied to the DTMF decoder(IC31). The

decoded signal is applied to the CPU (IC33, pins 82, 85, 86).

The CPU analyzes the DTMF signal.

The DTMF switch (IC30) selects the signal from telephone

line or RX unit.

3-2 TRANSMITTER CIRCUITS

3-2-1 AF AMPLIFIER CIRCUIT (LOGIC UNIT)

• IN CASE OF THE AF SIGNALS FROM THE MIC JACK

The AF signals from the MIC jack (FRONT unit; J7) are

amplified at the AF amplifier (IC1). The amplified signals are

mixed with the “E_MOD1”, “E_MOD2” and “TELAFO” signals at IC2. The mixed signals pass though the high-pass filter (IC2, pins 1, 2, 6, 7) via the pre-emphasis circuit (IC2,

pins 8, 9).

• TONE SIGNALS CIRCUITS (LOGIC UNIT)

DTMF

SW

LPF

LPF

LPF

AMP

AMP

CTCSS

DTCS

2/5TONE

DTMF

CTCSS

DETECTOR

DTMF

DECODER

CPU; IC33

DATA BU S

DATA BU S

DISC signal

from RX unit

To the AF amplifier

AMP

IC9

IC8

IC12

IC31

IC30

IC12

IC12

IC8

IC29

DTCSI

25TI

• AF AMPLIFIER CIRCUITS (LOGIC UNIT)

AMP

AMP

AMP

AMP

SW-D

SW-C

SW-B

SW-A

AMP

MIX

PRE

EMP

HPF

LIMIT

SIG

MIX

SPLAT

FIL

RPT AF

MUTE

LPF

E_MOD3

To TX unit

From the FRONT

unit

RPT AF signal

from IC25

From the telephone

circuit

From the REMOTE

connector

From the ACC

connector

From the REMOTE

connector

25TONE

BEEP

CW

DTMF

From CPU (IC33)

MIC

E_MOD

TELAFO

E_MODE2

IC13

MIC MUTE

AFATTO

IC2

IC3

IC3

IC4

IC26

IC14

3 - 3

The filtered signals are applied to the limiter amplifier (IC3),

and are then mixed with the DTMF signal from the CPU

(IC33, pin 43) via the TX-signal filter (IC3, pins 8, 10, 12, 14).

The mixed signals are applied to the splatter filter (IC4), and

are then applied to the PA unit.

• IN CASE OF THE AF SIGNALS FROM THE ANTENNA

CONNECTOR

The AF signals (received signals) from the antenna connector (RX unit; J1) are applied to the buffer amplifier (IC9),

CTCSS detector (IC29) and AF amplifier (IC6). The amplified signals are applied to the D/A converter IC (IC25, pins

8, 9) to adjust a repeater AF level. The adjusted AF signals

pass through the RPT AF mute switch (IC14), and are

applied to the limiter amplifier (IC3).

• IN CASE OF THE 2/5TONE SIGNALS

The 2/5TONE signals from the CPU (IC33, pin 43) are

applied to the mixer amplifier (IC3) via TX signal filter circuit

(IC3, pins 8, 10, 12, 14).

• IN CASE OF THE DTMF SIGNALS FROM

DIALER IC

The DTMF from dialer IC (IC47, pin 14) are applied to the

mixer amplifier (IC3) via the TX signal filter circuit (IC3, pins

8, 10, 12, 14).

• IN CASE OF THE CTCSS AND DTCS SIGNALS

FROM THE CPU

The CTCSS and DTCS signals from the CPU (IC33, pin 44)

are applied to the TX-tone filter (IC4, pins 12, 14). The filtered signal are applied to the D/A converter IC (TX unit; IC5

pin 9) to adjust a tone level needed, and are then mixed with

AF signal at the mixer amplifier IC (TX unit; IC6).

3-2-2 MODULATION CIRCUIT (TX UNIT)

The modulation circuit modulates the VCO oscillating signal

(RF signal) using the AF audio signals.

The filtered signals from the LOGIC unit are applied to the

D/A converter (IC5, pin 4) to adjust AF level. The adjusted

signals are applied to the mixer amplifier IC (IC6, pin 1) with

the CTCSS/DTCS signals.

The mixed signals are applied to the TX VCO circuit to mod-

ulate the oscillated signal (TVCO unit; D5) and modulate the

oscillated signal at VCO circuit (TVCO; Q1, D1–D4). The

modulated VCO output is amplified at the buffer amplifier

(Q1) and is then applied to the drive amplifier circuit on the

PA unit.

3-2-3 POWER AMPLIFIER CIRCUIT (PA UNIT)

The power amplifier circuit amplifies the driver signal to an

output power level.

The RF signal from the TX unit is applied to the pre-drive

(Q4) to amplify the level needed at the power amplifier. The

amplified signal passes through the attenuator circuit

(R29–R31) and is then applied to the power amplifier (IC2).

The RF signal from the pre-drive (Q4) is applied to the

power amplifier (IC2) to obtain 50 W ([IC-FR3100]: 25 W) of

RF power.

The amplified signal is passed through a low-pass filter circuit (L6, L7, L20, C1–C3, C48, C73, C98, C100) and APC

detector (D2, D4, R7, R8, R20, R21, R25, R26, 58, R36,

R37, C78, C79), and is then applied to the TX antenna connector (CHASSIS; J1).

Control voltage for the pre-drive (Q4) and power amplifier

(IC2) comes from the APC amplifier (IC1, Q9, Q10) to obtain

stable output power. The transmit mute switch (Q7, Q8) controls the pre-drive (Q4) and power amplifier (IC2) when

transmit mute is necessary.

3-2-4 APC CIRCUIT (PA UNIT)

The APC circuit protects the power amplifier from a mismatched output load and stabilizes the output power.

The APC detector circuit detects forward signals and reflection signals at D2 and D4 respectively. The combined voltage become minimum level when the antenna impedance is

matched at 50 Ω, and the voltage is increased when it is

mismatched.

The detected voltage is applied to the APC amplifier (IC1 pin

3), and the power setting “PCON” signal from the D/A converter (TX unit; IC5), controlled by the CPU (LOGIC unit;

IC33), is applied to the the APC amplifier (IC1 pin 1) for reference. When antenna impedance is mismatched, the

• APC CIRCUIT (PA UNIT)

DRIVE

AT T

DET

LPF

+9V

SW

APC

CTRL

FWSWR

RVSWR

POWER AMP

PCON

(TX UNIT; IC5)

Q4

VCC

TX UNIT

TMUTE2

Q7, Q8

To IC33; pin 46 (LOGIC UNIT)

To IC33; pin 47 (LOGIC UNIT)

IC2

IC1, Q9, Q10

3 - 4

detected voltage exceeds the power setting voltage. Then

the output voltage of the APC amplifier IC (IC1, pin 4) controls the input current of the drive amplifier (Q4) and power

amplifier IC (IC2, pin 2) to reduce the output power.

3-3 PLL CIRCUITS

3-3-1 GENERAL

Each receiver and transmitter circuit has an independent

PLL circuit for controlling frequencies. All PLL circuits are

shielded and installed on the RX and TX units.

PLL circuits steadily oscillate the transmit frequency and the

receive local frequency. The PLL output frequency is controlled by divided ratio (N-data) of the programmable divider.

3-3-2 RECEIVER PLL CIRCUIT (RX UNIT)

The PLL IC (IC4) which includes in the prescaler, the programmable counter and the phase comparator generates

the 1st LO frequency with the VCO circuit (RVCO unit; Q1,

D1–D4). The PLL IC sets the divided ratio which bases on

N-data from the CPU (LOGIC unit; IC33) to control the programmable counter. The PLL IC compares a phases of the

VCO signal with the reference oscillator frequency, and is

then applied to the VCO circuit (RVCO unit; Q1, D1–D4).

3-3-3 RECEIVER REFERENCE OSCILLATOR

CIRCUIT (RX UNIT)

The 12.8 MHz reference frequency is produced by the oscillator (X3). The frequency is adjusted by the D/A converter IC

(LOGIC unit; IC25). The reference frequency is applied to

the PLL IC (IC4, pin 1).

3-3-4 RECEIVER VCO CIRCUIT (RVCO UNIT)

The VCO circuit (Q1, D1–D4) generates the receive frequency. The signal is applied to the buffer amplifier (Q2) and

is then applied to the PLL IC (RX unit; IC4). The signal is

amplified at the amplifiers (RX unit; Q8, Q9) and then passes through the low-pass filter (RX unit; L23, L24, L39, L53,

C112–C114, C184, C216, C217) and attenuator (RX unit;

R81, R136, R137). The filtered signal is applied to the 1st

mixer circuit (RX unit; IC1) as 1st LO signal.

A part of the signal is applied to the PLL IC (RX unit; IC4) via

the amplifier (RX unit; Q14) as RX PLL lock voltage.

3-3-5 TRANSMITTER PLL CIRCUIT (TX UNIT)

The PLL IC (IC2) which includes in the prescaler, the programmable counter and the phase comparator. The PLL IC

sets the divided ratio which bases on N-data from the CPU

(LOGIC unit; IC33) to control the programmable counter.

The PLL IC compares a phases of the VCO signal with the

reference oscillator frequency, and is then applied to the

VCO circuit (TVCO unit; Q1, D1–D4).

3-3-6 TRANSMITTER REFERENCE OSCILLATOR

CIRCUIT (TX UNIT)

The 12.8 MHz reference frequency is produced by the oscillator (X1). The frequency is adjusted by the D/A converter IC

(IC5, pin 14). The reference frequency is applied to the PLL

IC (IC2, pin 1).

3-3-7 TRANSMITTER VCO CIRCUIT (TVCO UNIT)

The VCO circuit (Q1, D1–D4) generates the transmit frequency. The signal is applied to the buffer amplifier (Q2) and

is then applied to the amplifier (TX unit; Q1). The amplified

signal is applied to the PA unit.

A part of the signal is applied to the PLL IC (TX unit; IC2) via

the amplifier (TX unit; Q3) as TX PLL lock voltage.

• PLL CIRCUITS

To the PA unit

To the 1st mixer circuit

AMP

AMP

AMP

PLL IC

PLL IC

RVCO

TVCO

AMP

AMP

X1

X3

CPU; IC33

TX UNIT

RX UNIT

LOGIC UNIT

DATA BU S

DATA BU S

D1–D4

Q1

D1–D4

Q1

Q14

Q8

Q9

Q1

Q3

IC2

IC4

3 - 5

3-4 OTHER CIRCUITS

3-4-1 TELEPHONE IF CIRCUIT (LOGIC UNIT)

The signals from the telephone line (FRONT, J13) are

applied to the ringer detect circuit (IC48, D1, D5, R131,

R143, R145, C100, C103, C375). The detected signals are

applied to the CPU (IC33, pin 73) via “RING” line. The

“HOOKC” signal from the CPU (IC33, pin 72) and the “DP”

signal from IC47 are applied to the hook switch (RL1, RL2)

to off-hook.

Received AF signals from the RX unit pass through the highpass filter (IC9, pins 5, 7, 12, 14), de-emphasis (IC9, pins 1,

2) and low-pass filter circuits (IC10, pins 1, 3, 5, 7, 8, 9). The

filtered AF signals are amplified at IC7 (pins 12, 14) and are

then applied to the network IC (IC46, pin 16) via T6. The output signals from IC46 are applied to the J13 (FRONT unit)

via L1, L2.

AF signals from J13 (FRONT unit) are applied to the network

IC (IC46, pins 8, 9). The output signals from IC46 (pins 8, 9)

are applied to the AF amplifier IC (IC1, pins 1, 2) via T8.

Amplified signals pass through the MIC mute switch (IC1,

pins 3, 4), the MIC mixer amplifier (IC2, pins 13, 14), the preemphasis circuit (IC2, pins 8, 9), the high-pass filter circuit

(IC2, pins 1, 2, 6, 7), limiter amplifier circuit (IC3, pins 1, 2),

S-mixer circuit (IC3, , pins 6, 7), and splatter filter circuit (IC4,

pins 1, 3, 5, 7, 8, 10). The filtered signals are applied to the

TX unit.

After off-hook condition, DTMF signal from telephone line is

applied to the decoder IC (IC31) to decode the DTMF signal.

The DTMF signal is applied to the CPU (IC33) via serial signal line.

The clear down signal is detected at IC45 and is then

applied to the CPU (IC33). The “HOOKC” signal from the

CPU (IC33, pin 72) and the “DP” signal from IC47 are

applied to the hook switch (RL1, RL2) to on-hook.

3-4-2 EEPROM CIRCUIT (LOGIC UNIT)

The detector IC (IC34) detects power supply ON-OFF voltage. The signal from IC34 is applied to IC33 (CPU). IC35,

IC36 are reset signal circuit which stabilizes memory data

for the EEPROM (IC37).

EEPROM (IC37) memories clone data and adjust setting

condition data.

3-4-3 TEMPERATURE DETECT CIRCUIT

(LOGIC UNIT)

The temperature detect circuit protects the power amplifier

and power supply circuit from high temperature and stabilizes the output power.

Inside temperature of the PA unit is detected at D15 (PA unit)

and is then applied to the amplifier IC (PA unit; IC3). The

amplified signal is applied to the CPU (IC33) to analyze the

temperature via IC32.

Inside temperature of the REG unit is detected at D6 (REG

unit) and is then applied to the amplifier (REG unit; IC9). The

amplified signal applied to the CPU (IC33) to analyze the

temperature via IC32.

IC32 selects “PATEMP” or “REGTEMP” signals from the PA

or REG unit.

Description

The voltage from the DC power unit (CHASSIS;

EP1).

The same voltage as the PS 15V line which is

controlled by the power switch.

Common 9 V for converted from the VCC1 line

by the M9V regulator circuit (REG unit; IC1, Q8,

Q9). The voltage is applied to the TX and RX

units.

Common 9 V converted from the VCC1 line by

the L9V regulator circuit (REG unit; IC2).

Common 5 V converted from the L9V line by the

A5V regulator circuit (REG unit; IC3).

Common 5 V converted from the L9V line by the

L5V regulator circuit (LOGIC unit; IC38, Q48,

D43).

Common 5 V converted from the L9V line by the

C5V regulator circuit (LOGIC unit; IC38, Q45,

D13).

Common 5 V converted from the M9V line by the

TEL5V regulator circuit (LOGIC unit; IC11).

Line

PS 15V

VCC1

M9V

L9V

A5V

L5V

C5V

TEL5V

3-5 POWER SUPPLY CIRCUITS

3-5-1 LOGIC AND REG UNITS VOLTAGE LINES

Description

Transmit 5 V converted from the M9V line by the

T5V regulator circuit (TX unit; IC1).

Transmit 6 V converted from the M9V line by the

T6V regulator circuit (TX unit; IC4).

Common 9 V converted from the M9V line by the

V9V regulator circuit (TX unit; Q6).

Line

T5V

T6V

V9V

3-5-3 TX UNIT VOLTAGE LINES

Description

Common 5 V converted from the M9V line by the

+5V regulator circuit (RX unit; IC3).

Common 6 V converted from the M9V line by the

+6V regulator circuit (RX unit; IC7).

Receive 5 V converted from the R9V line by the

R5V regulator circuit (RX unit; IC6).

Receive 9 V controlled by the R9V regulator circuit (RX unit; Q15) using “R9C” signal from IC39

(LOGIC unit).

Common 9 V converted from the M9V line by the

V9V regulator circuit (RX unit; Q24).

Line

+5V

+6V

R5V

R9V

V9V

3-5-2 RX UNIT VOLTAGE LINES

Input port for the strobe signal.

Input port for the clock signal.

Outputs the serial data to the CPU

(LOGIC unit; IC33).

Input port for the received AF signal.

Outputs the adjusted AF signal for the

repeater output.

Outputs the adjustment signal for the

PLL reference frequency on the RX

unit.

Outputs the BPF tuning signal to the

RX unit.

6

7

8

9

10

14

15

DA2STB

SCK

SDTO

AFFTTI

AFATTO

RVCON

TUNE

Pin Port

Description

number name

3-6-4 D/A CONVERTER IC (LOGIC UNIT; IC25)

3 - 6

Outputs the switch control signal for

the received AF signal to the microphone amplifier.

Outputs the control signal for narrow/wide bands.

Outputs the control signal for the +9V

regulator on the RX unit.

Outputs the control signal for the M9V

regulator on the Rx unit and TX unit.

Output the detection signals whether

optional boards are installed or not.

Outputs the speaker mute signal for

the received AF.

Outputs the speaker mute signal for

the received 2/5TONE and DTMF

signals.

Outputs the MIC mute signal for the

hand microphone.

Outputs the MIC mute signal for the

REMOTE connector.

Outputs the pulse control signal for

the telephone dialer IC

Outputs the MOD mute signal for

AF signal from the telephone line.

Outputs the telephone mute signal for

the received AF signal.

Outputs the MIC mute signal for the

ACC connector.

AFMUTE1

AFMUTE2

MICMUTE1

MICMUTE2

TELBMR

TELMUTE2

TELMUTE1

MICMUTE3

4

5

6

7

11

12

13

14

Pin Port

Description

number name

R/BSW

W/NS

R9C

M9C

OPT1

OPT3

5

6

7

12

13

14

Pin Port

Description

number name

3-6-2 EXPANDER IC (LOGIC UNIT; IC40)

3-6-3 EXPANDER IC (LOGIC UNIT; IC41)

BASL

RMTL

BUSYL

TXL

D5C

PROGL

DCL

Outputs the control signal for “BASE”

LED on the FRONT unit.

Outputs the control signal for

“REMOTE” LED on the FRONT unit.

Outputs the control signal for “BUSY”

LED on the FRONT unit.

Outputs the control signal for “TX”

LED on the FRONT unit.

Outputs the control signal for the D5V

on the FRONT unit.

Outputs the control signal for “P” LED

on the FRONT unit.

Outputs the control signal for “DC”

LED on the FRONT unit.

4

5

6

7

12

13

14

Pin Port

Description

number name

3-6 PORT ALLOCATIONS

3-6-1 EXPANDER IC (LOGIC UNIT; IC39)

3 - 7

Outputs the strobe signal for the PLL

IC on the RX unit.

Outputs the strobe signal for the PLL

IC on the TX unit.

Input port for the unlock signal from

the PLL IC on the TX unit.

Outputs the TX mute signal for the TX

unit.

Outputs the TX mute signal for the PA

unit.

Input port for the PTT switch signal

from the microphone.

Input port for [SPMUTE] switch.

Input port for [REMOTE] switch.

Input port for [R/B] switch.

Outputs the BEEP signal for modulation.

Input port for [MONI] switch.

Input port for [CHUP] switch.

Input port for [CHDN] switch.

Input port for [DISP] switch.

Input port for [PROG] switch.

Outputs the antenna switching signal.

Outputs the CW signal for transmit.

Outputs the beep audio signals to the

speaker.

Outputs the master/slave switching

signal.

Input port for the master/slave switching signal.

Input port for the PTT signal form the

REMOTE connector.

Input port for PTT signal from the ACC

connector.

Input port for the memory channel

control signal.

Input port for the noise signal from the

FM IF IC (RX unit; IC2).

Outputs the temperature or PLL lock

voltage switching signal.

Outputs the 2/5TONE and DTMF signals.

Outputs the CTCSS/DTCS signals.

Input port for the detection signal from

the REG unit.

Input port for FW SWR signal from the

PA unit.

RPLSTB

TPLSTB

TUNLK

TMUTE

TMUTE2

M_PTT

SPMUTE

REMOTE

R/B

MBEEP

MONI

CHUP

CHDN

DISP

PROG

COAXSW

CWO

KBEEP

M/SO

M/SI

E_PTT

E_PT2

D0–D4

NDET

SW

2/5T

DTMFO

CTDTO

PSD

FWSWR

1

2

3

4

5

8

9

10

11

13

15

16

17

18

19

26

27

28

29

30

33

34

35–39

40

41

43

44

45

46

Pin Port

Description

number name

3-6-6 CPU (LOGIC UNIT; IC33)

Input port for the TONE signal from

the ACC connector.

Outputs the adjusted external TONE

signal.

Outputs the TX AF signal to the TX

modulation.

Input port for the AF signal.

Input port for the strobe signal.

Input port for the clock signal.

Outputs the serial data signal to the

CPU (LOGIC unit; IC33).

Input port for the TONE signal.

Outputs the adjusted TONE signal.

Outputs the TX power control signal.

Outputs the adjustment signal for the

TX unit PLL reference frequency.

Outputs the control signal for modulation balance.

Input port for the mixed signal with the

external signal, TX AF signal and

internal signals.

Outputs the adjustment signal for

TONE balance.

Outputs the adjusted AF signal for the

TX modulation.

Input port for the mixed signal with the

ETONE, TX AF and TONE signals.

ETONE

ETONEO

TXAFO

TXAF

DA1STB

SCK

SDTO

TONE

TONEO

PCON

TVCON

MODC

MIXO

REFMOD

MOD

MIXO

1

2

3

4

6

7

8

9

10

11

14

15

21

22

23

24

Pin Port

Description

number name

3-6-5 D/A CONVERTER IC (TX UNIT; IC5)

3 - 8

Outputs the strobe signal for the port

expander IC (LOGIC unit; IC41).

Outputs the strobe signal for the port

expander IC (LOGIC unit; IC40).

Outputs the strobe signal for the port

expander IC (LOGIC unit; IC39).

Outputs the strobe signal for the D/A

converter IC (LOGIC unit; IC25).

Outputs the strobe signal for the D/A

converter IC (TX unit; IC5).

Outputs the serial data signal for the

PLL IC (RX unit; IC4, TX unit; IC2),

dialer IC (LOGIC unit; IC47), port

expander IC (LOGIC unit; IC39–IC41)

and optional boards.

Outputs the clock signal for the PLL IC

(RX unit; IC4, TX unit; IC2), dialer IC

(LOGIC unit; IC47), port expander IC

(LOGIC unit; IC39–IC41) and optional

boards.

Input port for the unlock signal from

the PLL IC (RX unit; IC4).

Outputs the control signal for the TXTONE filter (LOGIC unit; IC4).

PE3STB

PE2STB

PE1STB

D2STB

D1STB

SDTO

SCK

RUNLK

C/DSW

89

90

91

95

96

97

98

99

100

Pin Port

Description

number name

CPU-Continued

Input port for the RV SWR signal from

the PA unit.

Input port for the temperature signals

of PA and REG units.

Input port for the VCO lock voltage to

the TX and RX unit.

Input port for the RSSI signal from the

FM IF IC (RX unit; IC2).

Input port for the 2/5TONE signals.

Input port for the DTCS signal.

Input port for the busy signal from the

pulse tone dialer IC (LOGIC unit;

IC47).

Outputs the serial clock signal for the

EEPROM (LOGIC unit; IC37).

I/O port for the serial data signal

from/to the EEPROM (LOGIC unit;

IC37).

Outputs strobe signal for the pulse

tone dialer IC (LOGIC unit; IC47).

Outputs the ON/OFF HOOK control

signal for the telephone line.

Input port for the ringer detecting signal from the telephone line.

Outputs the control signal for the clock

shift circuit.

Input port for the power supply detection signal.

Outputs the serial data signal to the

ACC connector.

Input port for the serial data signal

from the ACC connector.

Outputs the control signal for the

DTMF SW IC (LOGIC unit; IC50).

Outputs the clone data signal.

Input port for the clone data signal.

Outputs the control signal for the

DTMF SW IC (LOGIC unit; IC30).

Input port for the TONE detecting signal from the DTMF decoder IC

(LOGIC unit; IC31).

Input port for the data decoding signal

from the DTMF decoder IC (LOGIC

unit; IC31).

Outputs the clock signal for the DTMF

decoder IC (LOGIC unit; IC31).

Input port for the detection signal of

the ON-HOOK signal.

Outputs the control signal for the port

expander IC (LOGIC unit; IC39–IC41).

RVSWR

TEMP

T/RLV

RSSI

25TI

DTCSI

TEL-

BUSY

MCK

MDT

TELSTB

HOOKC

RING

SHIFT

INT

TXDTO

RXDTO

DTSEL1

TXDT1

RXDT1

DTSEL2

DTSTD

DTMFD

DTACK

ONHOOK

IOE

47

48

49

50

51

52

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

85

86

87

88

Pin Port

Description

number name

CPU-Continued

4 - 1

4-1 PREPARATION

Some adjustments must be performed on the “ADJUSTMENT MODE”. CS-FR3000 CLONING SOFTWARE, OPC-478 CLONING

CABLE and OPC-592 ADAPTOR CABLE are required when entering the adjustment mode. Refer to the next page in detail.

■ REQUIRED TEST EQUIPMENT

SECTION 4 ADJUSTMENT PROCEDURES

EQUIPMENT

DC power supply

RF power meter

(terminated type)

Frequency counter

FM deviation meter

GRADE AND RANGE

Output voltage : 13.6 V DC [FR3000]

13.2 V DC [FR3100]

Current capacity : 25 A or more

Measuring range : 1–100 W

Frequency range : 100–300 MHz

Impedance : 50 Ω

SWR : Less than 1.2 : 1

Frequency range : 0.1–600 MHz

Frequency accuracy : ±1 ppm or better

Sensitivity : 100 mV or better

Frequency range : DC–600 MHz

Measuring range : 0 to ±5 kHz

EQUIPMENT

Audio generator

Attenuator

Standard signal

generator (SSG)

AC millivoltmeter

Oscilloscope

Digital multimeter

GRADE AND RANGE

Frequency range : 300–3000 Hz

Output level : 1–500 mV

Power attenuation : 40 or 50 dB

Capacity : 100 W or more

Frequency range : 120–600 MHz

Output level : 0.1 µV–32 mV

(–127 to –17 dBm)

Measuring range : 10 mV–10 V

Frequency range : DC–20 MHz

Measuring range : 0.01–20 V

Input impedance : 10 MΩ/V DC or better

RF power meter

1–100 W / 50 Ω

Attenuator

40 dB or 50dB

FM deviation meter

(DC measurable)

Oscilloscope

DC power supply

13.6 V/25 A [FR3000]

13.2 V/25 A [FR3100]

Standard signal

generator

–127 to –17 dBm

Frequency

counter

JIG CABLE

[TX]

[RX]

[BATTERY]

[MIC]

OPC-478 + OPC-592

RS-232C

connector

Audio

generator

Microphone connector

MIC GND

MIC INPUT

–

+

PTT

18

GND

AC

millivoltmeter

Personal

computer

• CONNECTION

■ BEFORE ENTERING THE ADJUSTMENT MODE

CAUTION!: Need to back up the original memory data using CS-FR3000 before cloning the adjustment frequencies.

When program the adjustment frequencies into the repeater, the repeater’s memories channels will be overwritten

the data and deleted original memory data at the same time.

Need to do cloning “Adjustment Mode Access” permitting and adjustment frequency into the CPU using CS-FR3000 before

entering the adjustment mode. Otherwise, the repeater can not enter the adjustment mode.

■ PROCESS TO THE PERMIT “ADJUSTMENT MODE ACCESS”

1 Run the CS-FR3000 CLONING SOFTWARE.

2 Open the “Common Setting” folder .

3 Click the “Expert” card on the tree view window.

4 Double-click somewhere on the Common setting screen window, then appear the “Edit Expert” window.

5 Click the “Expert 2” tab, then click the “Adjustment Mode Access” check box.

6 Click “OK” button.

7 Click the “Memory CH” card on the tree view window.

8 Input adjustment frequencies as following page 4-4.

9 Cloning to the repeater then the repeater can be enter the adjustment mode.

Show the next page to enter the adjustment mode.

4 - 2

5

6

5

3

4

2

MEMORY CHANNEL SCREEN (Sample only)

4 - 3

■ ENTERING THE ADJUSTMENT MODE

1 Turn the power OFF.

2 While pushing and holding both [CH-DN] and [CH-UP],

turn ON. Never release [CH-DN] and [CH-UP] until 1

short beep sounds.

3 Push [CH-DN] button, then sounds 2 beep audio.

■ OPERATING IN THE ADJUSTMENT MODE

• Change the item (including frequency) (+1). : Push [CH-UP] button.

• Change the item (including frequency) (–1). : Push [CH-DN] button.

• Adjust the specified value (+1). : Push [PRT/BASE] button.

• Adjust the specified value (–1). : Push [MONI] button.

• Change the TX and RX’s condition. : Push [PROG] button.

Change the condition TX reference frequency to RX reference frequency.

Change the condition TX “HIGH POWER” to TX “LOW POWER”.

■ EXITING THE ADJUSTMENT MODE

1 Turn the power OFF.

2 While pushing and holding and [CH-UP], turn ON. Never release [CH-UP] until 1 short beep sounds.

3 Push [CH-UP] button, then sounds 2 beep audio.

■ AFTER FINISHING ADJUSTMENT

CAUTION!: When the adjustment is finished, the repeater need to be canceled adjustment mode.

Otherwise the repeater does not work properly.

1 Perform the step 1 to 4, described in the PROCESS TO PERMIT “ADJUSTMENT MODE ACCESS” (see page 4-2).

2 Click the “EXPERT 2” tag, then clear the check box for the “Adjustment Mode Access”.

3 Click “OK” button, then cloning with the original memory data.

[POWER]

[CH-UP]

[CH-DN]

[CH-UP]

[CH-DN]

[RPT/BASE]

[MONI]

[PROG]

2

3

2

4 - 4

171.925 (RX)

171.725 (TX)

171.925 (RX)

171.725 (TX)

160.075 (RX)

160.275 (TX)

148.075 (RX)

148.275 (TX)

148.075 (RX)

148.275 (TX)

160.075 (RX)

160.275 (TX)

160.075 (RX)

160.275 (TX)

148.075 (RX)

148.275 (TX)

171.925 (RX)

171.725 (TX)

160.075 (RX)

160.275 (TX)

160.075 (RX)

160.275 (TX)

160.075 (RX)

160.275 (TX)

158.275 (RX)

163.275 (TX)

158.275 (RX)

163.275 (TX)

■ ADJUSTMENT MODE CH LIST

A01

A02

A03

A04

A05

A06

A07

A08

A09

A10

A11

A12

A13

A14

A01 LW TXREF 127

A02 LW HRTUN 115

A03 LW MRTUN 088

A04 LW LRTUN 055

A05 LW RPTSQL 150

A06 HW POWER 166

A07 LW M DEV 143

A08 LW LMODC 073

A09 LW HMODC 191

A10 LW CTCDEV 134

A11 LW DTCADJ 159

A12 LN CTCDEV 062

A13 LW RPTAF 141

A14 LN RPTAF 126

W

W

W

W

W

W

W

W

W

N

W

N

W

N

TVCO/RVCO adjustment.

Reference frequency adjustment.

RX sensitivity adjustment.

RX sensitivity adjustment.

RX sensitivity adjustment.

RPT SQL adjustment.

TX power adjustment.

TX modulation adjustment.

TX modulation adjustment.

TX modulation adjustment.

CTCSS modulation adjustment.

DTCS modulation adjustment.

CTCSS modulation adjustment. (NARROW)

RPT modulation adjustment. (WIDE)

RPT modulation adjustment. (NARROW)

CH LCD DISPLAY

ADJUSTMENT

[Other] (MHz) [GEN74] (MHz)

W/N

173.925 (RX)

173.725 (TX)

173.925 (RX)

173.725 (TX)

162.075 (RX)

162.275 (TX)

150.075 (RX)

150.275 (TX)

150.075 (RX)

150.275 (TX)

162.075 (RX)

162.275 (TX)

162.075 (RX)

162.275 (TX)

150.075 (RX)

150.275 (TX)

173.925 (RX)

173.725 (TX)

162.075 (RX)

162.275 (TX)

162.075 (RX)

162.275 (TX)

162.075 (RX)

162.275 (TX)

160.275 (RX)

165.275 (TX)

160.275 (RX)

165.275 (TX)

A01 LW TXREF 127

Adjustment frequency channel

TX power (LOW)

Band width (WIDE)

Adjustment value

Adjustment item

■ EXPLANATION OF LCD DISPLAY IN THE ADJUSTMENT MODE

[Other]: 150–174 MHz version, [GEN74]: 148–172 MHz version

LCD display’s detail as shown below. A number of 3 figures is a adjustment value (sample).

4 - 5

4-2 PLL ADJUSTMENT

TX VCO LOCK

VOLTAGE

RX VCO LOCK

VOLTAGE

REFERENCE

FREQUENCY

1

1

1

2

• LCD display :

A01 LW TXREF 127

• Transmitting

• LCD display :

A01 LW TXREF 127

• Receiving

• Wait for 5 minutes after power ON.

• LCD display :

A01 LW TXREF

Connect the RF power meter or 50 Ω

dummy load to the [TX] antenna connector.

• Transmitting

• Push the [PROG] button

• LCD display :

A01 LW RXREF

• Receiving

TX

RX

REAR

panel

RX

Connect the digital

multi meter or oscilloscope to check point

CP4.

Connect the digital

multi meter or oscilloscope to check point

CP3.

Loosely couple a frequency counter to the

[TX] antenna connector.

Connect the frequency

counter to check point

CP2.

4.0 V

4.0 V

171.7250 MHz

[GEN74]

173.7250 MHz

[Other]

140.2750 MHz

[GEN74]

142.2750 MHz

[Other]

TVCO

RVCO

FRONT

FRONT

C17

C17

[PRT/BASE]

/[MONI]

[PRT/BASE]

/[MONI]

ADJUSTMENT ADJUSTMENT CONDITIONS

UNIT LOCATION

VALUE

UNIT ADJUST

MEASUREMENT ADJUSTMENT

CP4

C17 (TVCO unit)

TX VCO lock voltage

adjustment

CP4

TX VCO lock voltage

check point

CP4

CP18

CP2

CP1

CP3

LV

C17 (RVCO unit)

RX VCO lock voltage

adjustment

CP2

Reference frequency

check point

CP3

RX VCO lock voltage

chack point

CP2

L10

RX UNIT

TX UNIT

• RX UNIT TOP VIEW

• TX UNIT TOP VIEW

• IC-FR3000 TOP VIEW

4 - 6

*The output level of the standard signal generator (SSG) is indicated as the SSG’s open circuit.

4-3 SOFTWARE ADJUSTMENT

Select an item using [CH-UP] / [CH-DN] buttons, then set specified value using [RPT/BASE] / [MONI] buttons on the

FRONT PANEL.

Maximum

voltage

Maximum

voltage

Maximum

voltage

Squelch open

1

2

3

• LCD display :

A02 LW HRTUN

• Connect the standard signal generator

to the [RX] antenna connector and set

as:

Frequency : 171.9250 MHz

[GEN74]

173.9250 MHz [Other]

Level : 32 µV* (–77 dBm)

Modulation : 1 kHz

Deviation : ±3 kHz

• Receiving

• LCD display :

A03 LW MRTUN

• Connect the standard signal generator

to the [RX] antenna connector and set

as:

Frequency : 160.0750 MHz

[GEN74]

162.0750 MHz [Other]

• Receiving

• LCD display :

A04 LW LRTUN

• Connect the standard signal generator

to the [RX] antenna connector and set

as:

Frequency : 148.0750 MHz

[GEN74]

150.0750 MHz [Other]

• Receiving

• LCD display :

A05 LW RPTSQL

• Connect a standard signal generator to

the [RX] antenna connector and set as:

• Connect the RF power meter or 50 Ω

dummy load to the [TX] antenna connector.

Frequency : 148.0750 MHz

[GEN74]

150.0750 MHz [Other]

Level : 0.2 µV* (–121 dBm)

[Other]

: 0.32 µV* (–117 dBm)

[EUR2], [FRG2]

Modulation : 1 kHz

Deviation : ±3 kHz [Other]

: ±2.4 kHz [FRG2]

• Receiving

RX

SENSITIVITY

(HIGH FRQ.)

(MID FRQ.)

(LOW FRQ.)

REPEATER

SENSITIVITY

RX

FRONT

Connect the digital multi meter or

oscilloscope to check point

CP18.

Speaker

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

UNIT

LOCATION

CP18

CP1

CP18

RX sensitivity chack point

• RX UNIT TOP VIEW

4 - 7

SOFTWARE ADJUSTMENT – continued

Select an item using [CH-UP] / [CH-DN] buttons, then set specified value using [RPT/BASE] / [MONI] buttons on the

FRONT PANEL.

1

2

1

2

• LCD display :

A06 HW POWER

• Operating freq. : 160.2750 MHz

[GEN74]

162.2750 MHz [Other]

• Connect the RF power meter to the [TX]

antenna connector.

• Transmitting

• Push the [PROG] button

• LCD display :

A06 LW POWER

• Operating freq. : 160.2750 MHz

[GEN74]

162.2750 MHz [Other]

• Transmitting

• LCD display :

A07 LW M DEV

• Operating freq. : 160.2750 MHz

[GEN74]

162.2750 MHz [Other]

• IF bandwidth : Wide

• Connect the audio generator to the

[MIC] jack through the JIG cable and set

as:

1.0 kHz/40 mVrms

• Set an FM deviation meter as:

HPF : OFF

LPF : 20 kHz

De-emphasis: OFF

Detector : (P–P)/2

• Transmitting

• LCD display :

A08 LW LMODC

• Operating freq. : 148.2750 MHz

[GEN74]

150.2750 MHz [Other]

• IF bandwidth : Wide

• Connect the audio generator to the

[MIC] jack through the JIG cable and set

as:

1.0 kHz/40 mVrms

• Set an FM deviation meter as:

HPF : OFF

LPF : 20 kHz

De-emphasis: OFF

Detector : (P–P)/2

• Transmitting

• LCD display :

A09 LW HMODC

• Operating freq. : 171.7250 MHz

[GEN74]

173.7250 MHz [Other]

• Transmitting

Rear

panel

Rear

panel

Rear

panel

Connect the RF power meter to

the [TX] antenna connector.

Connect the FM deviation meter

to the [TX] antenna connector

through the attenuator.

Connect the FM deviation meter

to the [TX] antenna connector

through the attenuator.

50.0 W

[Other]

25.0 W

[EUR2], [FRG2]

10.0 W

[Other]

5.0 W

[EUR2], [FRG2]

±4.4 kHz

[Other]

±3.5 kHz

[FRG2]

±4.4 kHz

[Other]

±3.5 kHz

[FRG2]

±4.4 kHz

[Other]

±3.5 kHz

[FRG2]

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

UNIT LOCATION

*The output level of the standard signal generator (SSG) is indicated as the SSG’s open circuit.

OUTPUT

POWER

(HI)

(LOW)

DEVIATION

MODULATION

BALANCE

(LOW FRQ.)

(HIGH FRQ.)

4 - 8

*The output level of the standard signal generator (SSG) is indicated as the SSG’s open circuit.

SOFTWARE ADJUSTMENT – continued

Select an item using [CH-UP] / [CH-DN] buttons, then set specified value using [RPT/BASE] / [MONI] buttons on the

FRONT PANEL.

±0.65 kHz

[Other]

±0.52 kHz

[FRG2]

±0.35 kHz

±3.0 kHz

[Other]

±2.4 kHz

[FRG2]

±1.5 kHz

1

2

1

2

• LCD display :

A10 LW CDCDEV

• Operating freq. : 160.2750 MHz

[GEN74]

162.2750 MHz [Other]

• Set the FM deviation meter as:

HPF : OFF

LPF : 20 kHz

De-emphasis: OFF

Detector : (P–P)/2

• No audio applied to the [MIC] connector.

• Transmitting

• LCD display :

A12 LN CTCDEV

• Operating freq : 160.2750 MHz

[GEN74]

162.2750 MHz [Other]

• No audio applied to the [MIC] connector.

• Transmitting

• LCD display :

A11 LW DTCADJ

• Operating freq. : 160.2750 MHz

[GEN74]

162.2750 MHz [Other]

• No audio applied to the [MIC] connector.

• Transmitting.

• LCD display :

A13 LW RPTAF

• Operating freq : 158.2750 MHz (RX)

[GEN74]

160.2750 MHz (TX)

[GEN74]

160.2750 MHz (RX)

[Other]

162.2750 MHz (TX)

[Other]

• Connect the standard signal generator

to the RX antenna connector and set

as:

Level : 1 mV* (–47 dBm)

Modulation : 1 kHz

Deviation : ±3 kHz [Other]

: ±2.4 kHz [FRG2]

• Transmitting

• LCD display :

A14 LN RPTAF

• Operating freq : 158.2750 MHz (RX)

[GEN74]

160.2750 MHz (TX)

[GEN74]

160.2750 MHz (RX)

[Other]

162.2750 MHz (TX)

[Other]

• Transmitting

CTCSS

DEVIATION

(WIDE)

(NARROW)

DTCS

MODULATION

BALANCE

REPEATER

DEVIATION

(WIDE)

(NARROW)

Rear

panel

Rear

panel

Rear

panel

Connect the FM deviation meter

to the [TX] antenna connector

through the attenuator.

Connect the FM deviation meter

with an oscilloscope to the [TX]

antenna connector through the

attenuator.

Connect the FM deviation meter

to the [TX] antenna connector

through the attenuator.

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

UNIT LOCATION

Set to flat wave

form

[REG UNIT][REG UNIT]

IC1 1180001320 IC NJM7809FA T

IC2 1180002290 S.IC NJM7809DL1A-TE B

IC3 1180001860 S.IC TA78M05F (TE16L) B

IC4 1180002480 S.REG TA78DL12AF (TE16L) T

IC6 1180001540 S.IC TA78L08F (TE12R) B

IC7 1110002860 S.IC TA75S393F (TE85R) T

IC9 1110002400 S.IC NJM2107F-TE1 T

IC11 1110002750 S.IC TA75S01F (TE85R) T

Q1 1590003110 FET 2SJ533 T

Q4 1590003110 FET 2SJ533 T

Q5 1540000550 S.TRANSISTOR 2SD1664 T100Q T

Q7 1590001940 S.TRANSISTOR DTC144EE TL B

Q8 1590003030 S.FET 2SJ553STR B

Q9 1590001940 S.TRANSISTOR DTC144EE TL B

D2 1750000550 S.DIODE 1SS355 TE-17 B

D3 1790000700 DIODE DSA3A1 T

D4 1710001170 DIODE FCH30A03L T

D6 1790000720 DIODE MA29W-B T

D7 1710001170 DIODE FCH30A03L T

D8 1730002340 S.ZENER MA8047-M (TX) B

R3 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) B

R14 7100000830 RESISTOR 5SG 3.3 Ω T

R16 7030003240 S.RESISTOR ERJ3GEYJ 220 V (22 Ω) B

R17 7030003240 S.RESISTOR ERJ3GEYJ 220 V (22 Ω) B

R18 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R19 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R23 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ) T

R24 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ) B

R27 7030003420 S.RESISTOR ERJ3GEYJ 681 V (680 Ω) B

R30 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ) T

R31 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω) T

R32 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R33 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ) T

R34 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R35 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ) T

R36 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R37 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω) T

R38 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R39 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R40 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R41 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ) T

R42 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω) T

R58 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) B

R59 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ) B

R60 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ) T

R61 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) T

R62 7030010510 S.RESISTOR ERJ1TYJ 8R2U (8.2 Ω) B

R64 7030003240 S.RESISTOR ERJ3GEYJ 220 V (22 Ω) B

R65 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) B

R66 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ) T

R67 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω) T

R68 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω) T

C4 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C5 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C6 4510007690 ELECTROLYTIC LXZ25VB2200 T

C7 4510007690 ELECTROLYTIC LXZ25VB2200 T

C9 4510007690 ELECTROLYTIC LXZ25VB2200 T

C11 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C15 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C17 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C19 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C20 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C22 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C23 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C24 4550006770 S.TANTALUM TEESVD2 1C 476M-12R T

C25 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C26 4510007660 ELECTROLYTIC LXZ25VB100 T

C27 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C28 4510007650

S.ELECTROLYTIC

EEVHB1C470P T

C29 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C31 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C33 4030006900 S.CERAMIC C1608 JB 1H 103K-T B

C34 4510007570

S.ELECTROLYTIC

EEVHB1C220UR T

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

S.=Surface mount

C35 4030006900 S.CERAMIC C1608 JB 1H 103K-T B

C36 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C37 4510007660 ELECTROLYTIC LXZ25VB100 T

C38 4510007660 ELECTROLYTIC LXZ25VB100 T

C41 4510007570

S.ELECTROLYTIC

EEVHB1C220UR T

C42 4030006900 S.CERAMIC C1608 JB 1H 103K-T T

C43 4030006900 S.CERAMIC C1608 JB 1H 103K-T T

C45 4030006900 S.CERAMIC C1608 JB 1H 103K-T T

C47 4510007660 ELECTROLYTIC LXZ25VB100 T

C48 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C49 4510007570

S.ELECTROLYTIC

EEVHB1C220UR T

C50 4030006900 S.CERAMIC C1608 JB 1H 103K-T T

C51 4030006900 S.CERAMIC C1608 JB 1H 103K-T T

C52 4030017490 S.CERAMIC C1608 JB 1A 105K-T T

RL2 6330001680 RELAY ACB32101 T

J13 6510018970 S.CONNECTOR B4B-PH-SM3-TB T

J14 6510022620 S.CONNECTOR 10FMN-BMTTR-A-TBT T

J16 6510018960 S.CONNECTOR B2B-PH-SM3-TB T

J17 6510018960 S.CONNECTOR B2B-PH-SM3-TB T

J18 6510018960 S.CONNECTOR B2B-PH-SM3-TB T

F1 5220000300 HOLDER 1A5600 T

F2 5220000300 HOLDER 1A5600 T

F3 5210000850 FUSE ATC-20 T

F4 5220000300 HOLDER 1A5600 T

F5 5220000300 HOLDER 1A5600 T

F6 5210000850 FUSE ATC-20 T

S1 2260001510 SWITCH RXE160 T

W1 7120000490 JUMPER ERD25T0 T

W2 7120000490 JUMPER ERD25T0 T

W3 7120000490 JUMPER ERD25T0 T

W4 7120000490 JUMPER ERD25T0 T

EP1 0910056242 PCB B 5998B

EP2 6910012350 S.BEAD MMZ1608Y 102BT T

EP3 6910011340 TERMINAL OT-010 M3 T

EP4 6910011340 TERMINAL OT-010 M3 T

EP5 6910011340 TERMINAL OT-010 M3 T

EP6 6910011340 TERMINAL OT-010 M3 T

EP7 6910011340 TERMINAL OT-010 M3 T

EP8 6910011340 TERMINAL OT-010 M3 T

EP9 6910011340 TERMINAL OT-010 M3 T

EP10 6910011340 TERMINAL OT-010 M3 T

5 - 1

SECTION 5 PARTS LIST

REF ORDER

DESCRIPTION M.

NO. NO.

REF ORDER

DESCRIPTION M.

NO. NO.

[FR3000]: IC-FR3000, [FR3100]: IC-FR3100

[FRONT UNIT]

Q1 1530002060 S.TRANSISTOR 2SC4081 T106 R T

D1 1750000930 S.DIODE NNCD8.2C-T1 T

D2 1750000930 S.DIODE NNCD8.2C-T1 T

D3 1750000930 S.DIODE NNCD8.2C-T1 T

L1 6200001620 S.COIL ELJFC 1R0K-F T

R1 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω) T

R2 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω) T

R3 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω) T

R8 7030001150 S.RESISTOR MCR50JZHJ 150 Ω (151) B

R9 7030001150 S.RESISTOR MCR50JZHJ 150 Ω (151) B

R10 7030001160 S.RESISTOR MCR50JZHJ 180 Ω (181) B

R11 7030001150 S.RESISTOR MCR50JZHJ 150 Ω (151) B

R12 7030001150 S.RESISTOR MCR50JZHJ 150 Ω (151) B

R13 7030001150 S.RESISTOR MCR50JZHJ 150 Ω (151) B

R15 7030003460 S.RESISTOR ERJ3GEYJ 152 V (1.5 kΩ) B

R17 7030008220 S.RESISTOR MCR100JZHJ 47 Ω (470) B

R18 7030008220 S.RESISTOR MCR100JZHJ 47 Ω (470) B

R19 7540000240 S.ABSORBER KU10R29N-4063 T

R21 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) B

R22 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) B

R23 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) B

R24 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) B

R26 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) T

R27 7030010910 S.RESISTOR ERJ1TYJ 150U (15 Ω) B

R28 7030010910 S.RESISTOR ERJ1TYJ 150U (15 Ω) B

C1 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C2 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C3 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C4 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C5 4030006860 S.CERAMIC C1608 JB 1H 102K-T T

C12 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C13 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C14 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C15 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C16 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C17 4030017200 S.CERAMIC GRM31BR32J102KY01L T

C18 4030017200 S.CERAMIC GRM31BR32J102KY01L T

C19 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

C20 4030006860 S.CERAMIC C1608 JB 1H 102K-T B

J1 6510022620 S.CONNECTOR 10FMN-BMTTR-A-TBT B

J2 6510022580 S.CONNECTOR 24FMN-BMTTR-A-TBT B

J3 6510021600 S.CONNECTOR S2B-PH-SM3-TB B

J4 6510022910 CONNECTOR IMSA9201B-1-16Z012Z T

J6 6510022790 CONNECTOR 95003-2641 T

J7 6450001470 CONNECTOR 95003-2881 T

J8 6510023250 S.CONNECTOR S3B-PH-SM3-TB B

J9 6510021600 S.CONNECTOR S2B-PH-SM3-TB B

F1 5210000890 FUSE SBR-1A [USA2] B

DS1 5040001820 LED BG3889S T

DS2 5040001820 LED BG3889S T

DS3 5040001330 LED BR3889S T

DS4 5040001820 LED BG3889S T

DS5 5040001820 LED BG3889S T

DS6 5040001820 LED BG3889S T

DS7 5030002190 LCD MSC-C161UYLY-4W T

S1 2260001680 S.SWITCH SKQDPB T

S2 2260001680 S.SWITCH SKQDPB T

S3 2260001680 S.SWITCH SKQDPB T

S4 2260001680 S.SWITCH SKQDPB T

S5 2260001680 S.SWITCH SKQDPB T

S6 2260001680 S.SWITCH SKQDPB T

S7 2260001680 S.SWITCH SKQDPB T

S8 2260001680 S.SWITCH SKQDPB T

W1 7030003860 S.RESISTOR ERJ3GE JPW V

[GEN2], [GEN4], [GEN74], [EUR2], [FRG2] T

EP1 0910056251 PCB B 5997A

EP2 6910014560 SPACER LM-15 T

EP3 6910014550 SPACER LM-13 T

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

S.=Surface mount

5 - 2

REF ORDER

DESCRIPTION M.

NO. NO.

[FR3000]: IC-FR3000, [FR3100]: IC-FR3100

[FRONT UNIT]

EP4 6910014540 SPACER LM-10 T

EP5 6910014540 SPACER LM-10 T

EP6 6910014540 SPACER LM-10 T

EP7 6910014540 SPACER LM-10 T

IC1 1110003780 S.IC NJM2902V-TE1 T

IC2 1110003780 S.IC NJM2902V-TE1 T

IC3 1110003780 S.IC NJM2902V-TE1 B

IC4 1110003780 S.IC NJM2902V-TE1 T

IC6 1110002400 S.IC NJM2107F-TE1 T

IC7 1110003780 S.IC NJM2902V-TE1 B

IC8 1110003780 S.IC NJM2902V-TE1 B

IC9 1110003780 S.IC NJM2902V-TE1 B

IC10 1110003780 S.IC NJM2902V-TE1 T

IC11 1180000420 S.IC TA78L05F (TE12R) B

IC12 1110003780 S.IC NJM2902V-TE1 T

IC13 1130008090 S.IC BU4066BCFV-E1 T

IC14 1130004200 S.IC TC4S66F (TE85R) T

IC16 1130006220 S.IC TC4W53FU (TE12L) B

IC17 1110003090 IC LA4425A T

IC20 1130006220 S.IC TC4W53FU (TE12L) T

IC21 1130006220 S.IC TC4W53FU (TE12L) T

IC25 1190001350 S.IC M62364FP 600D T

IC26 1110003800 S.IC NJM2904V-TE1 B

IC28 1110002400 S.IC NJM2107F-TE1 B

IC29 1190001720 S.IC FX805LG T

IC30 1130006220 S.IC TC4W53FU (TE12L) T

IC31 1130007400 S.IC LC7387M-TRM T

IC32 1130006220 S.IC TC4W53FU (TE12L) T

IC33 1140010140 S.IC HD64F2238BFA13 T

IC34 1110005710 S.IC S-80842CLUA-B63-T2 B

IC35 1130009320 S.IC BU4011BFV-E2 B

IC36 1130009320 S.IC BU4011BFV-E2 B

IC37 1140008650 S.IC HN58X2464TI T

IC38 1180002250 S.IC S-812C50AMC-C3E-T2 B

IC39 1130007570 S.IC BU4094BCFV-E2 T

IC40 1130007570 S.IC BU4094BCFV-E2 B

IC41 1130007570 S.IC BU4094BCFV-E2 T

IC42 1170000280 S.IC TLP121 (GB-TPL) B

IC43 1170000280 S.IC TLP121 (GB-TPL) B

IC44 1120002830 S.IC NJM2125F-TE1 T

IC45 1110005000 S.IC LMC567CM B

IC46 1190001740 S.IC BA6566F-E2 B

IC47 1190001730 S.IC LC73701M-TLM T

IC48 1170000280 S.IC TLP121 (GB-TPL) T

IC49 1170000280 S.IC TLP121 (GB-TPL) T

IC50 1130006220 S.IC TC4W53FU (TE12L) T

IC51 1110002400 S.IC NJM2107F-TE1 T

IC52 1110005690 S.IC NJM2520V-TE1 T

IC53 1130006220 S.IC TC4W53FU (TE12L) T

Q1 1590001400 S.TRANSISTOR XP1214 (TX) B

Q2 1530002060 S.TRANSISTOR 2SC4081 T106 R B

Q3 1590001940 S.TRANSISTOR DTC144EE TL B

Q4 1530002060 S.TRANSISTOR 2SC4081 T106 R T

Q5 1510000510 S.TRANSISTOR 2SA1576A T106R T

Q6 1530002060 S.TRANSISTOR 2SC4081 T106 R T

Q7 1590001400 S.TRANSISTOR XP1214 (TX) B

Q8 1590003210 S.TRANSISTOR XP1111 (TX) B

Q9 1590003210 S.TRANSISTOR XP1111 (TX) B

Q10 1590003210 S.TRANSISTOR XP1111 (TX) B

Q11 1590003210 S.TRANSISTOR XP1111 (TX) B

Q17 1590001940 S.TRANSISTOR DTC144EE TL T

Q18 1590002010 S.TRANSISTOR XP1114 (TX) T

Q19 1590002010 S.TRANSISTOR XP1114 (TX) T

Q20 1590002010 S.TRANSISTOR XP1114 (TX) T

Q24 1550000020 S.FET 2SJ377 (TE16R) T

Q25 1530002060 S.TRANSISTOR 2SC4081 T106 R T

Q26 1590001960 S.TRANSISTOR XP4311 (TX) T

Q27 1590001960 S.TRANSISTOR XP4311 (TX) T

Q28 1590001960 S.TRANSISTOR XP4311 (TX) T

Q29 1590001960 S.TRANSISTOR XP4311 (TX) T

Q37 1590001940 S.TRANSISTOR DTC144EE TL B

Q38 1590001400 S.TRANSISTOR XP1214 (TX) B

Q40 1590001940 S.TRANSISTOR DTC144EE TL B

Q44 1590002430 S.TRANSISTOR DTA144EE TL B

Q45 1510000590 S.TRANSISTOR 2SA1362-Y (TE85L) B

REF ORDER

DESCRIPTION M.

NO. NO.

REF ORDER

DESCRIPTION M.

NO. NO.

[LOGIC UNIT]

[LOGIC UNIT][LOGIC UNIT]

Q48 1160000150 S.TRANSISTOR IMZ4 T108 B

Q49 1590001960 S.TRANSISTOR XP4311 (TX) T

Q50 1590001960 S.TRANSISTOR XP4311 (TX) T

Q51 1540000570 S.TRANSISTOR 2SD1760 TLQ [FR3100] B

Q52 1530001950 S.TRANSISTOR 2SC2712-GR (TE85R) [FR3100] B

D1 1730002650 S.ZENER PTZ TE25 36B B

D4 1710001180 S.BRIDGE D1UBA80-4062 B

D5 1710001180 S.BRIDGE D1UBA80-4062 B

D6 1790001250 S.DIODE MA2S111-(TX) B

D7 1790001250 S.DIODE MA2S111-(TX) T

D8 1790001250 S.DIODE MA2S111-(TX) B

D9 1790001250 S.DIODE MA2S111-(TX) B

D10 1790001250 S.DIODE MA2S111-(TX) B

D11 1790001250 S.DIODE MA2S111-(TX) B

D12 1790001250 S.DIODE MA2S111-(TX) B

D13 1790000670 S.DIODE SB07-03C-TB B

D14 1790001260 S.DIODE MA2S077-(TX) B

D15 1790001250 S.DIODE MA2S111-(TX) B

D16 1790001250 S.DIODE MA2S111-(TX) B

D17 1790001250 S.DIODE MA2S111-(TX) B

D18 1790001250 S.DIODE MA2S111-(TX) B

D19 1790001250 S.DIODE MA2S111-(TX) T

D20 1790001250 S.DIODE MA2S111-(TX) T

D21 1790001250 S.DIODE MA2S111-(TX) T

D22 1790001250 S.DIODE MA2S111-(TX) T

D23 1790001250 S.DIODE MA2S111-(TX) B

D24 1790001250 S.DIODE MA2S111-(TX) B

D25 1790001250 S.DIODE MA2S111-(TX) B

D26 1790001250 S.DIODE MA2S111-(TX) B

D27 1790001250 S.DIODE MA2S111-(TX) B

D28 1750000550 S.DIODE 1SS355 TE-17 B

D29 1750000550 S.DIODE 1SS355 TE-17 B

D33 1790001250 S.DIODE MA2S111-(TX) B

D38 1730002640 S.ZENER PTZ TE25 13B T

D43 1790001250 S.DIODE MA2S111-(TX) B

D44 1790001250 S.DIODE MA2S111-(TX) B

D45 1790001250 S.DIODE MA2S111-(TX) B

D46 1790001250 S.DIODE MA2S111-(TX) B

X1 6050011490 S.XTAL CR-733 (4.194304 MHz) T

X2 6050011000 S.XTAL CR-681 (12.288 MHz) T

X3 6050009300 S.XTAL CR-505 (4 MHz) T

L1 6200009790 S.COIL BLM31PG121SN1 T

L2 6200009790 S.COIL BLM31PG121SN1 T

L3 6200009790 S.COIL BLM31PG121SN1 T

L4 6200009790 S.COIL BLM31PG121SN1 T

L5 6200009790 S.COIL BLM31PG121SN1 B

L6 6200009790 S.COIL BLM31PG121SN1 T

L7 6200009790 S.COIL BLM31PG121SN1 T

L8 6200009790 S.COIL BLM31PG121SN1 T

L9 6200009790 S.COIL BLM31PG121SN1 T

L10 6200009790 S.COIL BLM31PG121SN1 B

L11 6200009790 S.COIL BLM31PG121SN1 B

R2 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R3 7030003750 S.RESISTOR ERJ3GEYJ 394 V (390 kΩ) T

R5 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ) T

R6 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ) T

R7 7310004790 S.TRIMMER EVM-3YSX50 B14 (103) B

R8 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) T

R9 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) T

R10 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R12 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) T

R13 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) T

R14 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R15 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R16 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R17 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R18 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R19 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R22 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) B

R23 7030003740 S.RESISTOR ERJ3GEYJ 334 V (330 kΩ) B

R24 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) B

R25 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) B

R26 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ) T

R27 7030003530 S.RESISTOR ERJ3GEYJ 562 V (5.6 kΩ) T

R28 7030003420 S.RESISTOR ERJ3GEYJ 681 V (680 Ω) T

R29 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ) T

R30 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ) T

R31 7030003370 S.RESISTOR ERJ3GEYJ 271 V (270 Ω) T

R32 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ) T

R33 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

S.=Surface mount

R34 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R35 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R36 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R37 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R40 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R48 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) B

R50 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ) B

R51 7310004790 S.TRIMMER EVM-3YSX50 B14 (103) T

R52 7030003670 S.RESISTOR ERJ3GEYJ 823 V (82 kΩ) T

R53 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ) T

R54 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R55 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R56 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R57 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R58 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R59 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R60 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R61 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R62 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R63 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R64 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R65 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) B

R66 7030003550 S.RESISTOR ERJ3GEYJ 822 V (8.2 kΩ) B

R67 7030003530 S.RESISTOR ERJ3GEYJ 562 V (5.6 kΩ) B

R68 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω) B

R69 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ) B

R70 7030003490 S.RESISTOR ERJ3GEYJ 272 V (2.7 kΩ) B

R71 7030003410 S.RESISTOR ERJ3GEYJ 561 V (560 Ω) B

R72 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ) B

R74 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ) B

R75 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ) B

R77 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) B

R78 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ) B

R79 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ) T

R80 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ) T

R81 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R82 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ) T

R83 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ) T

R84 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R85 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) T

R86 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R87 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R88 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) B

R89 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) B

R90 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R91 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) T

R92 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) T

R94 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R95 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ) T

R96 7030003690 S.RESISTOR ERJ3GEYJ 124 V (120 kΩ) B

R97 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ) B

R98 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ) B

R99 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ) B