Icom IC-F22SR, IC-F22S, IC-F22, IC-F21GM, IC-F21BR Service Manual

...

SERVICE

MANUAL

UHF TRANSCEIVERS

INTRODUCTION

DANGER

ORDERING PARTS

REPAIR NOTES

This service manual describes the latest service information

for the

IC-F21/IC-F21S/IC-F21BR/IC-F21GM/IC-F22/IC-

F22S/IC-F22SR

at the time of publication.

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than 8.6 V. Such a connection

could cause a fire hazard and/or electric shock.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when con-

necting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100mW)

to the antenna connector. This could damage the transceiver’s front end.

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit order numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

1130007020 S.IC TC7S66FU IC-F21 MAIN UNIT 1 piece

8810004860 Screw PH M 2 x 6 ZK IC-F21 Chassis 10 pieces

Addresses are provided on the inside back cover for your

convenience.

1. Make sure a problem is internal before disassembling the transceiver.

2. DO NOT open the transceiver until the transceiver is disconnected from its power source.

3. DO NOT force any of the variable components. Turn them slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An insulated turning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the transceiver is defective.

6. DO NOT transmit power into a signal generator or a sweep generator.

7. ALWAYS connect a 40 dB to 50 dB attenuator between the transceiver and a deviation meter or spectrum analyzer when

using such test equipment.

8. READ the instructions of test equipment thoroughly before connecting equipment to the transceiver.

To upgrade quality, all electrical or mechanical parts and

internal circuits are subject to change without notice or obligation.

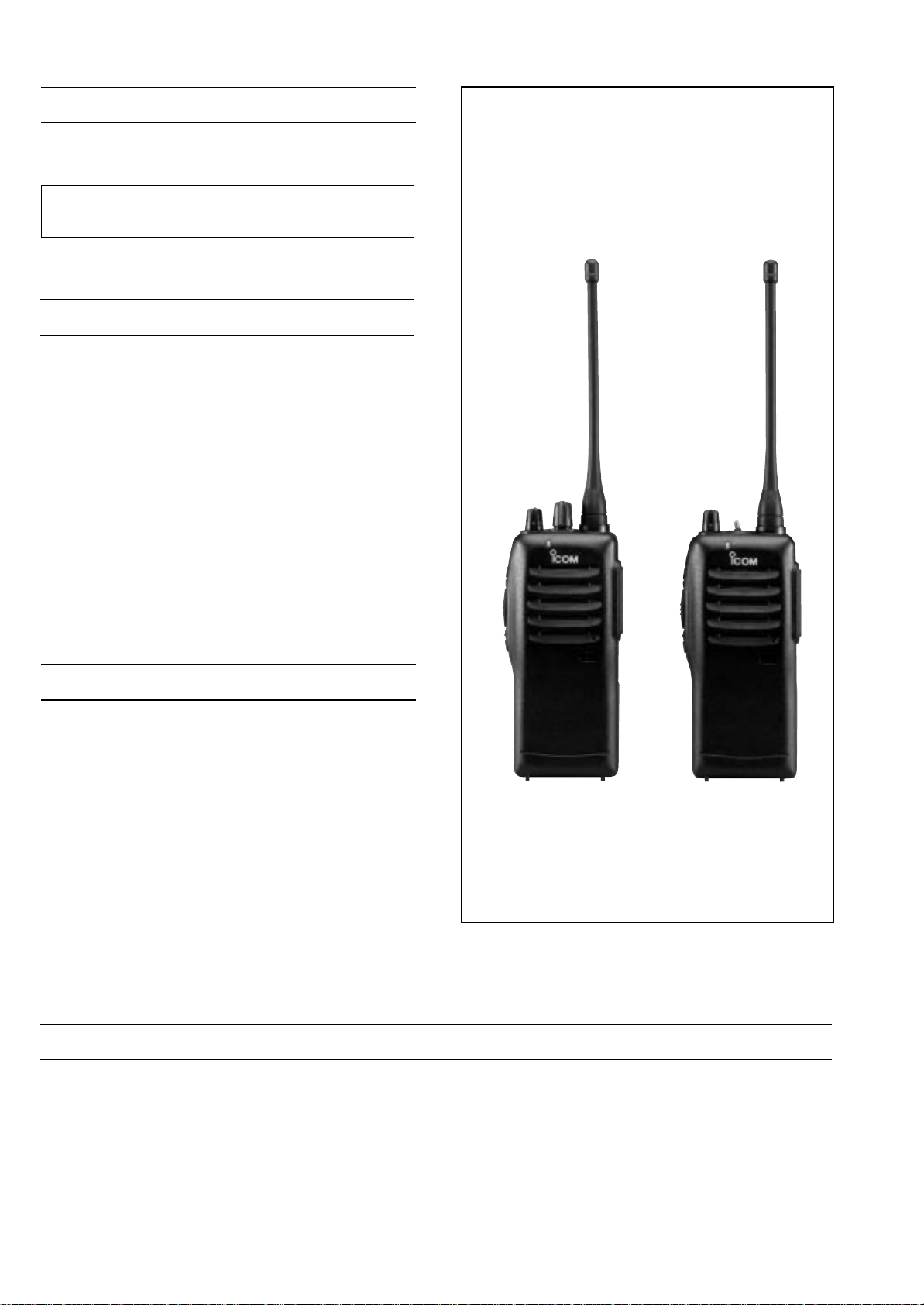

IC-F21/IC-F21GM/

IC-F22/IC-F22SR

IC-F21S/IC-F21BR/

IC-F22S

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 DISASSEMBLY INSTRUCTIONS

SECTION 4 CIRCUIT DESCRIPTION

4-1 RECEIVER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4-2 TRANSMITTER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

4-3 PLL CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4-4 POWER SUPPLY CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4-5 PORT ALLOCATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

SECTION 5 ADJUSTMENT PROCEDURES

5-1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5-2 PLL ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

5-3 SOFTWARE ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5

SECTION 6 PARTS LIST

SECTION 7 MECHANICAL PARTS AND DISASSEMBLY

SECTION 8 SEMI-CONDUCTOR INFORMATION

SECTION 9 BOARD LAYOUTS

9-1 IC-F22/F22S/F22SR MAIN UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

9-2 IC-F21/F21S/F21BR/F21GM MAIN UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-3

9-3 SW-AAND SW-B UNITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-5

SECTION 10 BC-146 OPTIONAL DESKTOP CHARGER INFORMATION

10-1 PARTS LIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10-2 DISASSEMBLY INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10-3 VOLTAGE DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

10-4 BOARD LAYOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

SECTION 11 BLOCK DIAGRAM

SECTION 12 VOLTAGE DIAGRAM

12-1 MAIN UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

12-2 SW-A AND SW-B UNITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

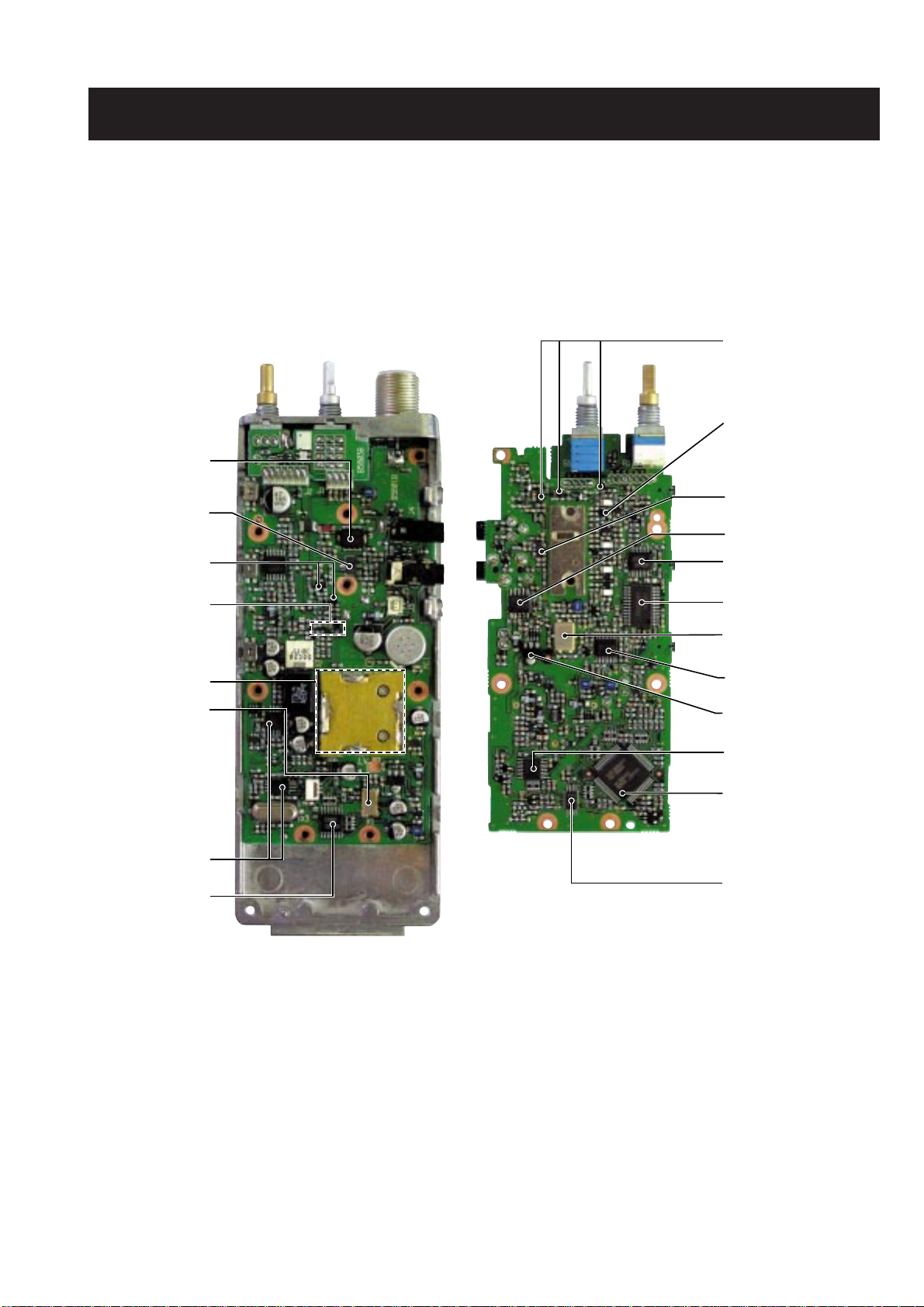

1 - 1

SECTION 1 SPECIFICATIONS

All stated specifications are subject to change without notice or obligation.

Frequency coverage

Type of emission

Number of channels

Power supply requirement

Antenna impedance

Input impedance (Mic)

Output impedance (Audio)

Intermediate frequency

Operating temperature range

High power

Low power

stand-by

Rated audio

Dimensions

(Projections not included)

Weight

RF output power (at 7.2 V DC)

Modulation system

Max. permissible deviation

External mic.connector

Frequency error

Spurious emissions

Adjacent channel power

Audio harmonics distortion

FM Hum and noise

Residual modulation

Limiting charact of modulator

Receive system

Intermediate frequencies

Sensitivity

Audio output power (at 7.2 V)

Adjacent channel selectivity

Spurious response

Intermodulation

FM Hum and noise (Typical)

Squelch sensitivity

EIA-152-C/204D or TIA-603 ETS 300 086/300 296

RECEIVER TRANSMITTER GENERAL

440.000 MHz–470.000 MHz 440.000 MHz–470.000 MHz

462.550 MHz–469.550 MHz A 446.00625 MHz–446.09375 MHz C

462.550 MHz–467.725 MHz B

16K0F3E/8K50F3E (at 25 / 12.5 kHz: W/N-type), 8K50F3E (at 12.5 kHz: N-type)

2 ch. (IC-F21BR / F21S / F22S), 15 ch. (IC-F21GM / F22SR), 16 ch. (IC-F21 / F22)

7.2 V (negative ground)

50 Ω normal

2.2 kΩ normal

8 Ω normal

1st: 46.350 MHz, 2nd: 450 kHz

–30 ˚C to +60 ˚C (–22˚F to +140˚F) –25 ˚C to +55 ˚C (–13˚F to +131˚F)

1.6 A(4 W) except

A, C; 1.2 A (2 W) except C; 0.5 A (0.5 W ERP) C only

0.8 A (1 W)

70 mA

250 mA

54(W)

× 128(H) × 37(D) mm; 2

1

⁄8(W) × 51⁄25(H) × 115⁄32(D) inch

310 g; 10.1 oz (with BP-209), 300 g; 10.6 oz (with BP-222)

High: 4.0 W (A: 2.0 W, C: 0.5 W), Low1: 2.0 W (except A, C), low2: 1.0 W (except C)

Variable reactance frequency modulation

± 5.0 kHz (25 kHz), ± 2.5 kHz (12.5 kHz) (

C: ± 2.5 kHz (12.5 kHz) only)

3-conductor 2.5 mm (

1

⁄10 in) (2 kΩ)

±2.5 ppm ±1.5 kHz

73 dBc (typical) 0.25 µW <= 1 GHz, 1.00 µW > 1 GHz

70 dB*

1

(25 kHz), 60 dB*1(12.5 kHz)

3 % typical at 1 kHz, 40 % deviation 5 % typical at 1 kHz 60 % deviation

46 dB typ. (25 kHz), 40 dB typ. (12.5 kHz) –

– 45 dB typ. (25 kHz), 43 dB typ. (12.5 kHz)

70 % – 100 % of max. deviation

Double-conversion super heterodyne

1st: 46.350 MHz, 2nd: 450 kHz

0.25 µV (typical) for 12 dB SINAD

0.25 µV (typical) for 12 dB SINAD 0.63 µV EMF (typical) for 20 dB SINAD

(

C: 26.5 dBµV/m for 20 dB SINAD)

0.5 W at 5 % distortion with an 8 Ω load, 0.6 W at 5 % distortion with 6 Ω load

70 dB typ. (25 kHz), 65 dB typ. (12.5 kHz) 70 dB (25 kHz), 60 dB (12.5 kHz)

81.29 dBµV/m

70 dB*

1

(C: 91.29 dBµV/m)

70 dB 65 dB (

C: 86.29 dBµV/m)

46 dB*2(25 kHz), 40 dB*2(12.5 kHz) 45 dB typ.*3(25 kHz), 43 dB typ.*3(12.5 kHz)

0.3 µV typical at threshold (C: 26.5 dBµV/m at threshold)

Current drain

(at 7.2 V)

Tx

Rx

*1EIA-152-C/204D or TIA-603 is typical value, *2EIA-152-C/204D only, *3With CCITT filter

A: [F21BR], B: [F21GM]], C: [F22SR]

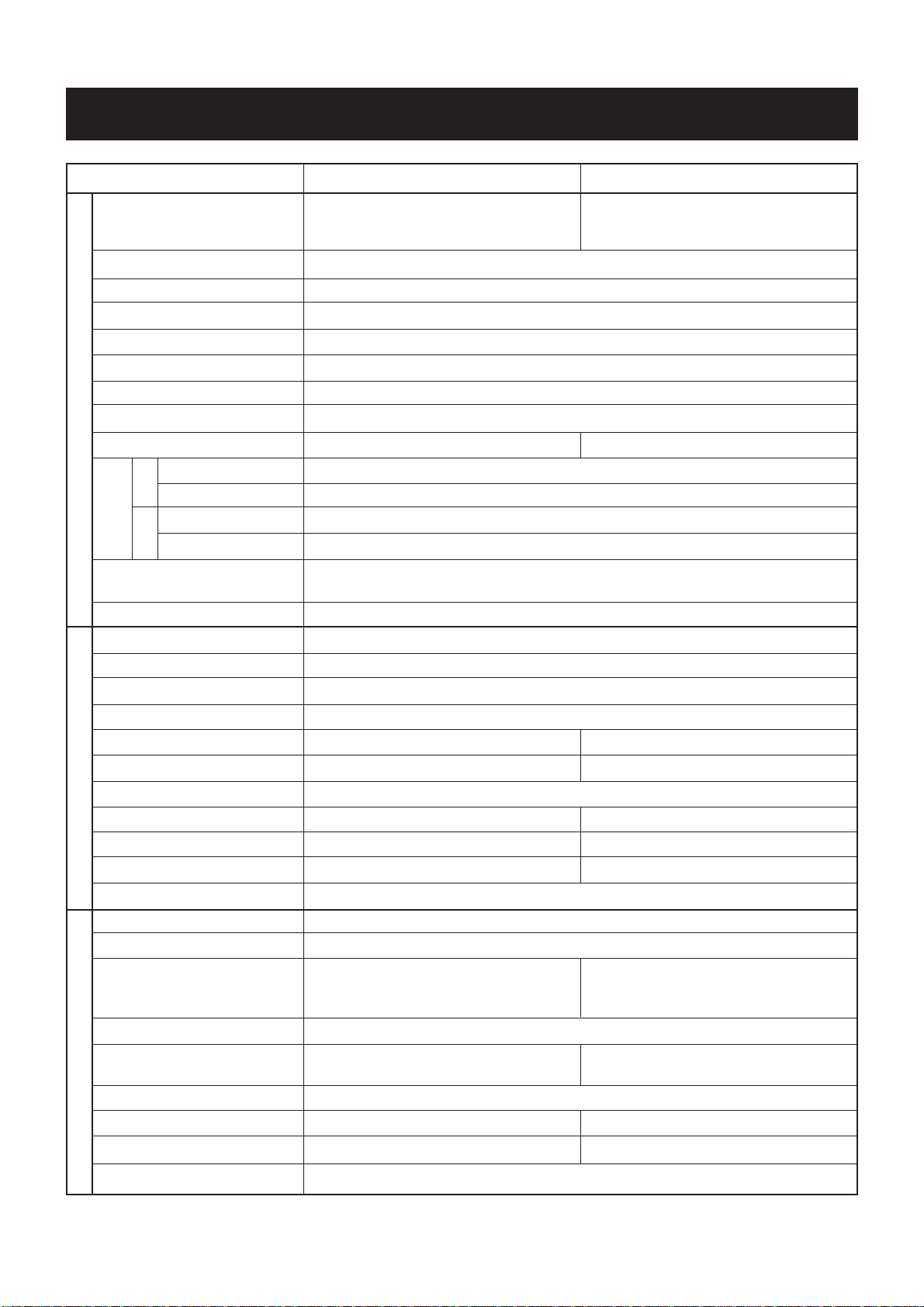

2 - 1

SECTION 2 INSIDE VIEWS

• MAIN UNIT

Power amplifier

(Q1: 2SK2974)

Antenna switching circuit

D1: 1SV307

D9, D10: MA77

TOP VIEW BOTT OM VIEW

RF amplifier

(Q15: 3SK293)

VCO circuit

FM IF IC

(IC3: TA31136FN)

Low-pass filter circuit

(IC12,16: NJM12904V)

Expander IC

(IC15: BU4094BCFV)

TX/RX switch

(D3, D4: MA77)

Analog switch

(IC6: BU4066BCFV)

APC

(IC2: TA75S01F)

AF amplifier

(IC4: TA7368F)

1st mixer

(Q19: 2SB1132 R)

CPU

IC7: HD6433664A24FP

(F21/F21S/F21BR/

F21GM/F22/F22S)

: HD64F3664FP

(F22SR)

EEPROM

(IC11: HN58X2416TI)

D/A converter

(IC9: M62363FP-650C)

PLL reference oscillator

(X1: CR-671A)

Crystal filter

(FI1: FL-335)

PLL IC

(IC1: MB15A02PFV-1)

YGR amplifier

Q3: 2SC3585 R44

Q4: 2SC5107 O

Pre-drive

(Q2 : 2SK2973)

()

()

()

3 - 1

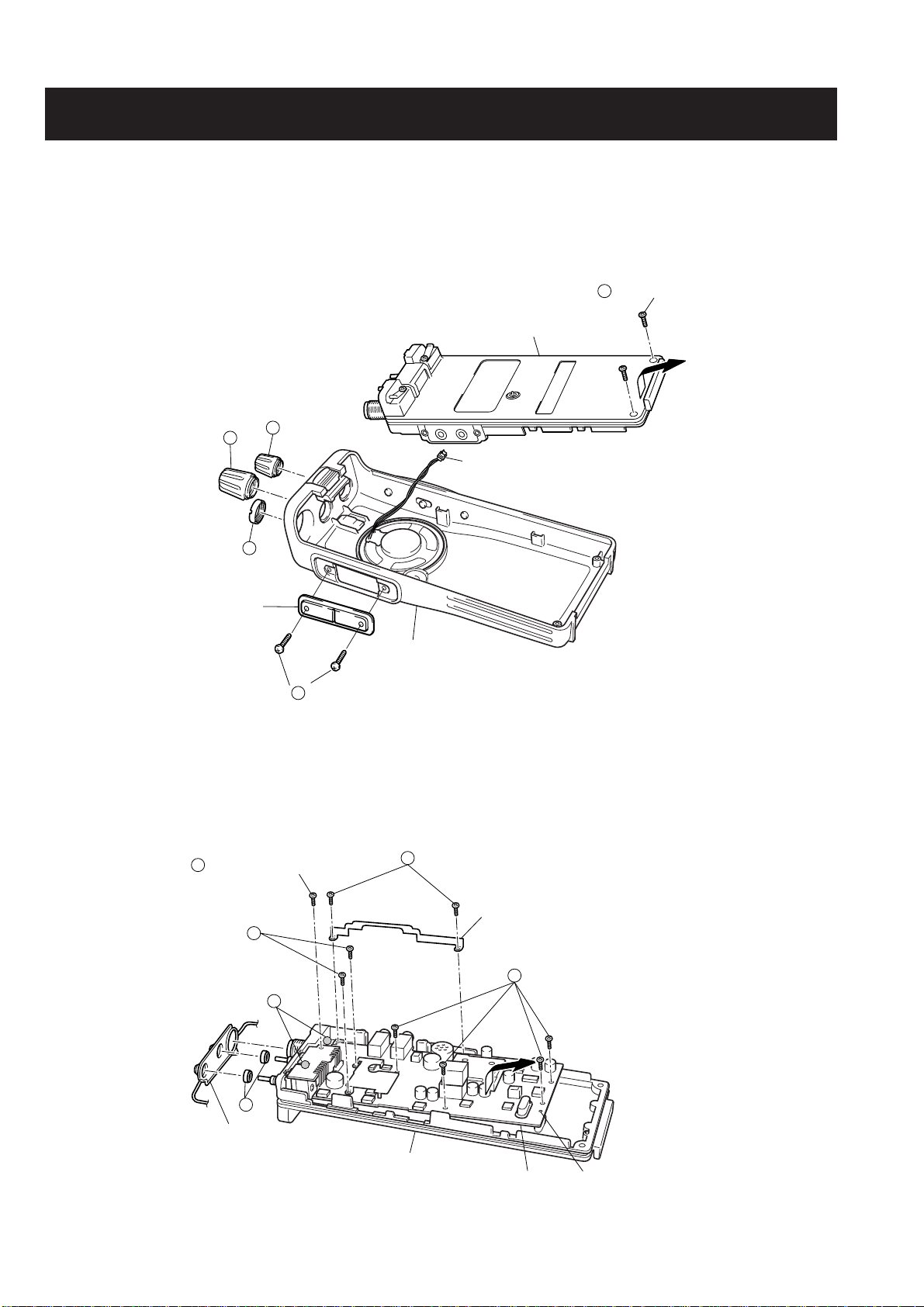

SECTION 3 DISASSEMBLY INSTRUCTIONS

• REMOVING THE CHASSIS

¡ Unscrew 1 nut, A, and remove 2 knobs, B, C.

™ Unscrew 2 screws, D.

£ Unscrew 2 screws, H, to separate the Jack panel and the

Front panel.

¢ Take off the chassis in the direction of the arrow.

∞ Unplug J6 to separate the front panel and the chassis.

• REMOVING THE MAIN UNIT

¡ Remove the searing rubber.

™ Unsolder 2 points, E, and unscrew 2 nuts, F.

£ Unscrew 9 screws, G, (silver, 2mm) to separate the chassis and the MAIN unit.

¢ Take off the MAIN unit in the direction of the arrow.

Front panel

J6 (Speaker connector)

Jack panel

Chassis

C

B

(Black, 2mm) x 2

D

A

(Black, 2mm) x 2

H

Guide holes

MAIN unit

Sealing rubber

Chassis

E

F

Side plate

([F21S], [F21BR], [F22S] only)

G

G

G

G

4 - 1

SECTION 4 CIRCUIT DESCRIPTION

4-1 RECEIVER CIRCUITS

4-1-1 ANTENNA SWITCHING CIRCUIT

The antenna switching circuit functions as a low-pass filter

while receiving. However, its impedance becomes very high

while D9 and D10 are turned ON. Thus transmit signals are

blocked from entering the receiver circuits. The antenna

switching circuit employs a λ⁄4 type diode switching system.

Received signals are passed through the low-pass filter (L1,

L2, C3, C5, C6). The filtered signals are applied to the λ⁄4

type antenna switching circuit (D9, D10).

The passed signals are then applied to the RF amplifier circuit.

4-1-2 RF CIRCUIT

The RF circuit amplifies signals within the range of frequency coverage and filters out-of-band signals.

The signals from the antenna switching circuit are amplified

at the RF amplifier (Q15) after passing through the tunable

bandpass filter (D12, L21, C104, C105). The amplified signals are applied to the 1st mixer circuit (Q16) after out-ofband signals are suppressed at the 3 stages tunable bandpass filter (D13, L22, C111, C113, D14, L23, C116, C117,

D15, L24, C120, C122).

Varactor diodes are employed at the bandpass filters that

track the filters and are controlled by the CPU (IC7) via the

D/A convertor (IC9) using T1–T4 signals. These diodes tune

the center frequency of an RF passband for wide bandwidth

receiving and good image response rejection.

4-1-3 1ST MIXER AND 1ST IF CIRCUITS

The 1st mixer circuit converts the received signal into a fixed

frequency of the 1st IF signal with a PLL output frequency.

By changing the PLL frequency, only the desired frequency

will pass through a crystal filter at the next stage of the 1st

mixer.

The signals from the RF circuit are mixed at the 1st mixer

(Q16) with a 1st LO signal (393.65–423.65 MHz) coming

from the VCO circuit to produce a 46.35 MHz 1st IF signal.

The 1st IF signal is applied to a crystal filter (FI1) to suppress out-of-band signals. The filtered 1st IF signal is

applied to the IF amplifier (Q17), then applied to the 2nd

mixer circuit (IC3, pin 16).

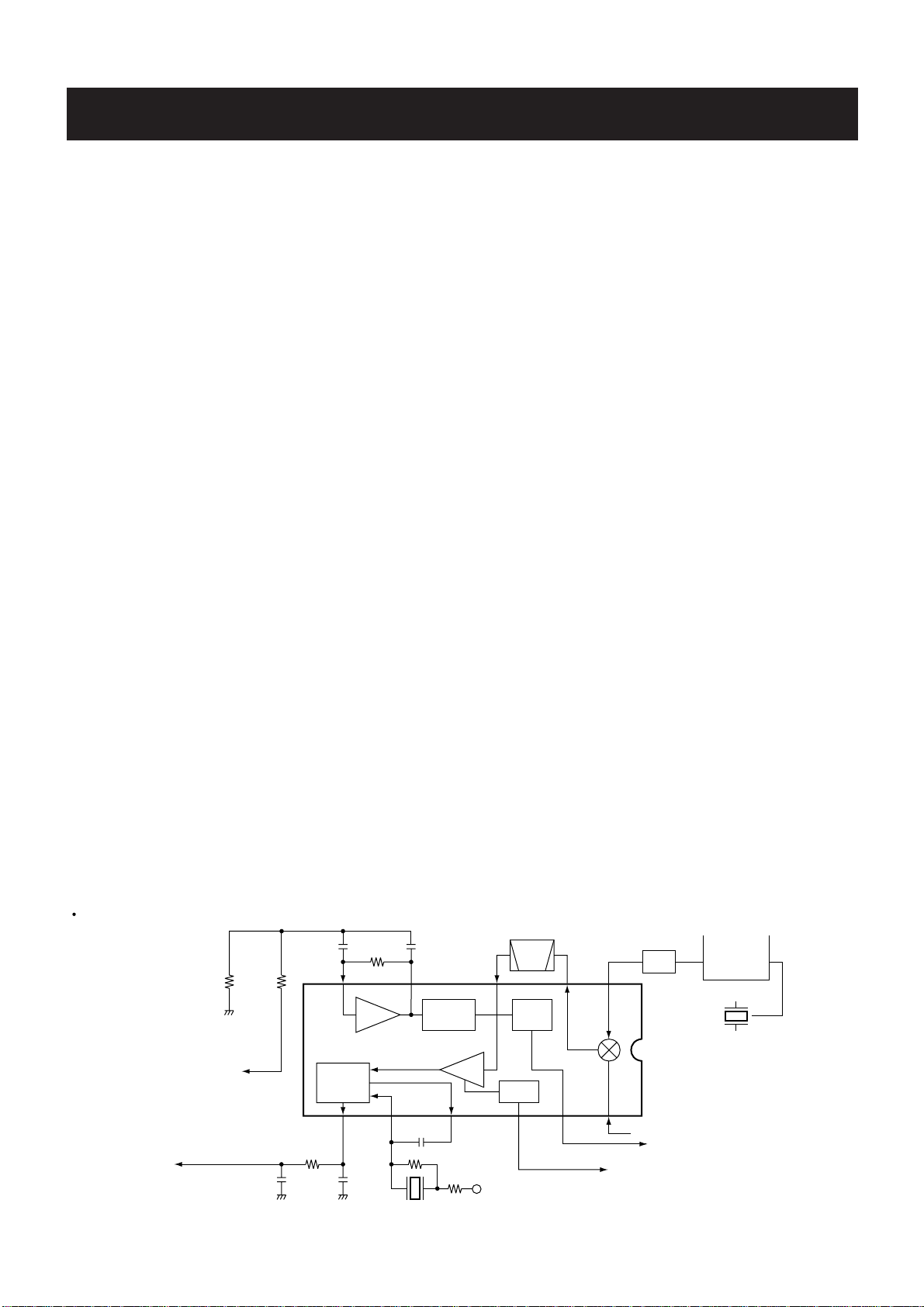

4-1-4 2ND IF AND DEMODULATOR CIRCUITS

The 2nd mixer circuit converts the 1st IF signal into a 2nd IF

signal. Adouble conversion superheterodyne system (which

converts receive signals twice) improves the image rejection

ratio and obtains stable receiver gain.

The 1st IF signal from the IF amplifier is applied to the 2nd

mixer section of the FM IF IC (IC3, pin 16), and is mixed with

the 2nd LO signal to be converted into a 450 kHz 2nd IF signal.

The FM IF IC contains the 2nd mixer, limiter amplifier, quadrature detector and active filter circuits. A 2nd LO signal

(45.9 MHz) is produced at the PLL circuit by tripling it’s reference frequency.

The 2nd IF signal from the 2nd mixer (IC3, pin 3) passes

through a ceramic filter (FI2) to remove unwanted heterodyned frequencies. It is then amplified at the limiter amplifier (IC3, pin 5) and applied to the quadrature detector (IC3,

pins 10, 11) to demodulate the 2nd IF signal into AF signals.

4-1-5 AF CIRCUIT

AF signals from the FM IF IC (IC3, pin 9) are applied to the

analog switch (IC6, pin 1) after being passed through the

high-pass filter (IC5B, pins 5, 7) via the “DET” signal. The

signals pass through the low-pass filter (IC5D, pins 13, 14),

and then applied to the analog switch (IC6, pins 9, 10) again.

The output signals from the analog swtich (IC6, pin 11) are

applied to the AF power amplifier (IC4, pin 4) after being

passed through the [VOL] control (SW-A/SW-B unit; R143)

via the “VOLIN” and “VOLOUT” signals.

2ND IF AND DEMODULATOR CIRCUITS

Mixer

16

Limiter

amp.

2nd IF filter

450 kHz

PLL IC

IC1

X1

15.3 MHz

IC3 TA31136F

12

1st IF from the IF amplifier (Q17)

"RSSI" signal to the CPU pin 59

11109

87 5 3

AF signal "DET"

R5V

X2

R98

C155

C154

R100R99

R93

"SQLIN" signal to the

D/A convertor (IC9, pin 23)

R92

C138 C139

C140

2

21

Active

filter

FI2

Noise

detector

FM

detector

13

"NOIS" signal to the CPU pin 53

RSSI

Noise

comp.

×3

R94

Q18

4 - 2

The applied AF signals are amplified at the AF power amplifier circuit (IC4, pin 4) to obtain the specified audio level. The

amplified AF signals output from pin 10 as “AFOUT”signal

are applied to the internal speaker (SP1) as the “SP” signal

via the [SP] jack when no plug is connected to the jack.

4-1-6 SQUELCH CIRCUIT

Asquelch circuit cuts out AF signals when no RF signals are

received. By detecting noise components in the AF signals,

the squelch switches the AF mute switch.

A portion of the AF signals from the FM IF IC (IC3, pin 9) as

“DET” signal are applied to the D/A convertor IC (IC9, pin

24). The signals from the D/A convertor (IC9, pin 23) as

“SQLIN” signals are applied to the active filter section (IC3,

pin 8) where noise components are amplified and detected

with an internal noise detector.

The active filter section amplifies noise components. The filtered signals are rectified at the noise detector section and

converted into “NOIS” (pulse type) signals at the noise comparator section. The “NOIS” signal output from IC3, pin 13,

and is applied to the CPU (IC7, pin 53).

The CPU detects the receiving signal strength from the

number of the pulses, and outputs “EXST”, “SO”, “SCK” signals. The signals are applied to the expander IC (IC15, pins

1, 2, 3), and then outputs “RMUT” signal from pin 4. This

signal controls the analog switch (IC6, pin 13) to cut the AF

signal line.

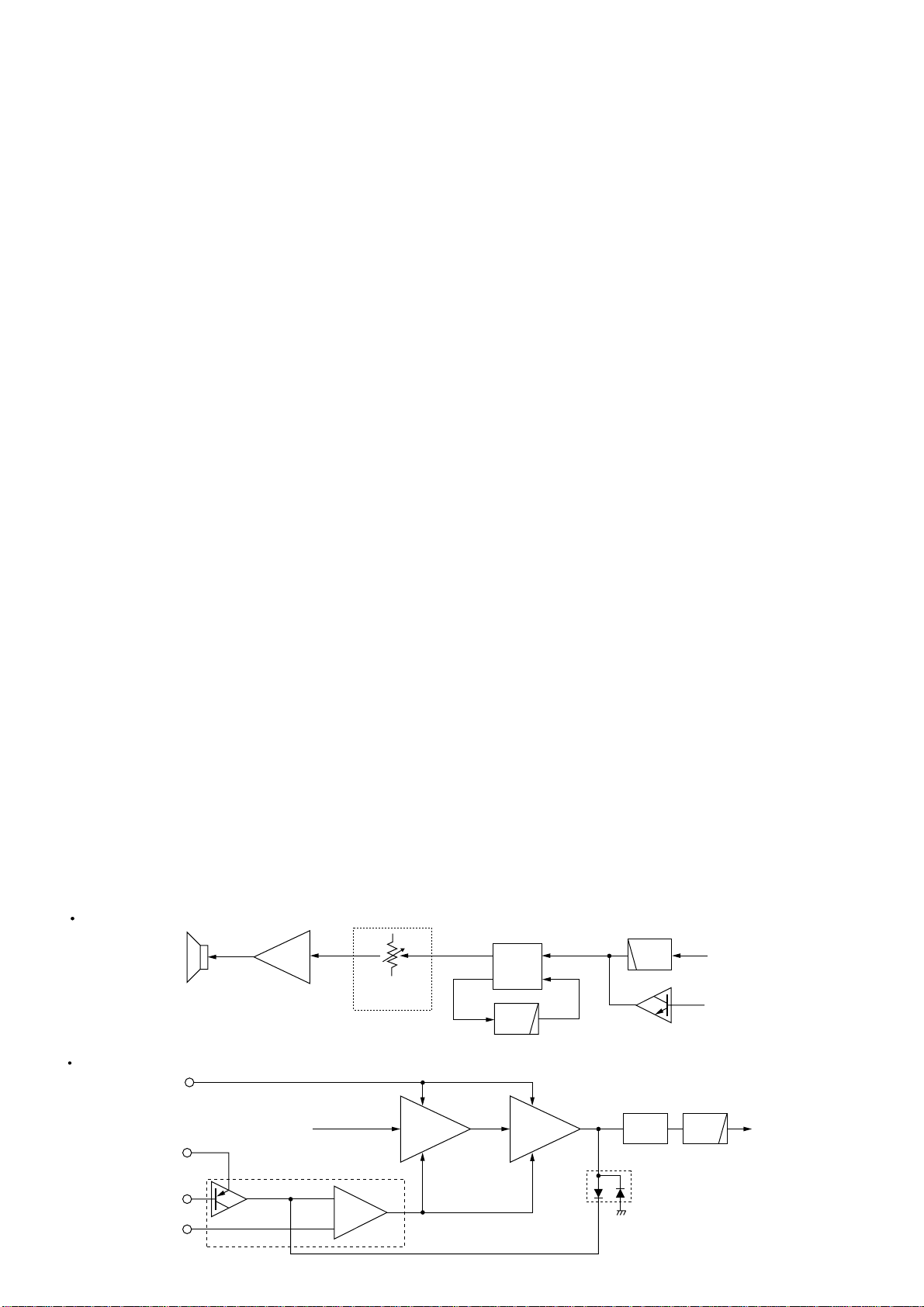

4-2 TRANSMITTER CIRCUITS

4-2-1 MICROPHONE AMPLIFIER CIRCUIT

The microphone amplifier circuit amplifies audio signals with

+6 dB/octave pre-emphasis characteristics from the microphone to a level needed for the modulation circuit.

The AF signals from the microphone are applied to the

microphone amplifier circuit (IC5c, pin 10) after being pass

through the high-pass filter (C186, C187). The amplified AF

signals are passed through the low-pass filter circuit (IC5d,

pins 13, 14) via the mute switch (IC6, pins 2, 3, 4). The filtered AF signals are applied to the modulator circuit after

being passed through the mute switch (IC6, pins 8, 9, 10).

4-2-2 MODULATION CIRCUIT

The modulation circuit modulates the VCO oscillating signal

(RF signal) using the microphone audio signal.

The audio signals change the reactance of a diode (D6) to

modulate an oscillated signal at the TX-VCO circuit (Q11).

The oscillated signal is amplified at the buffer-amplifiers (Q5,

Q7), then applied to the T/R switching circuit (D3, D4).

4-2-3 DRIVE/POWER AMPLIFIER CIRCUITS

The signal from the VCO circuit passes through the T/R

switching circuit (D3) and is amplified at the YGR (Q4, Q3),

pre-drive (Q2) and power amplifier (Q1) to obtain 4 W of RF

power (at 7.2 V DC). The amplified signal passes through

the antenna switching circuit (D1) via the power detector

(D2), and low-pass filter and is then applied to the antenna

connector.

The bias current of the pre-drive (Q2) and the power amplifier (Q1) is controlled by the APC circuit.

4-2-5 APC CIRCUIT

The APC circuit (IC2) protects the drive and the power

amplifiers from excessive current drive, and selects HIGH or

LOW output power.

The signal output from the power detector circuit (D2) is

applied to the differential amplifier (IC2, pin 3), and the “T4”

signal from the expander (IC9, pin 11), controlled by the

CPU (IC7), is applied to the other input for reference.

When the driving current is increased, input voltage of the

differential amplifier (pin 3) will be increased. In such cases,

the differential amplifier output voltage (pin 4) is decreased

to reduce the driving current.

APC CIRCUIT

Q1

Power

amp.

Q2

Pre-driver

amp.

IC2

+

—

VCC

RF signal

from PLL

to antenna

T4

T5V

Q14

S5V

APC control circuit

Power detector

circuit (D2)

D2

LPF

D1

ANT

SW

AF

amp.

LPF

HPF

"DET" signal

from IC3, pin 9

"NWC" signal

from IC15, pin 14

Q21

Analog

switch

IC6

IC5B

IC5D

AF VOL.

R1

SW-A/SW-B

unit

IC4

SP

111

9, 102, 3

AF CIRCUIT

4 - 3

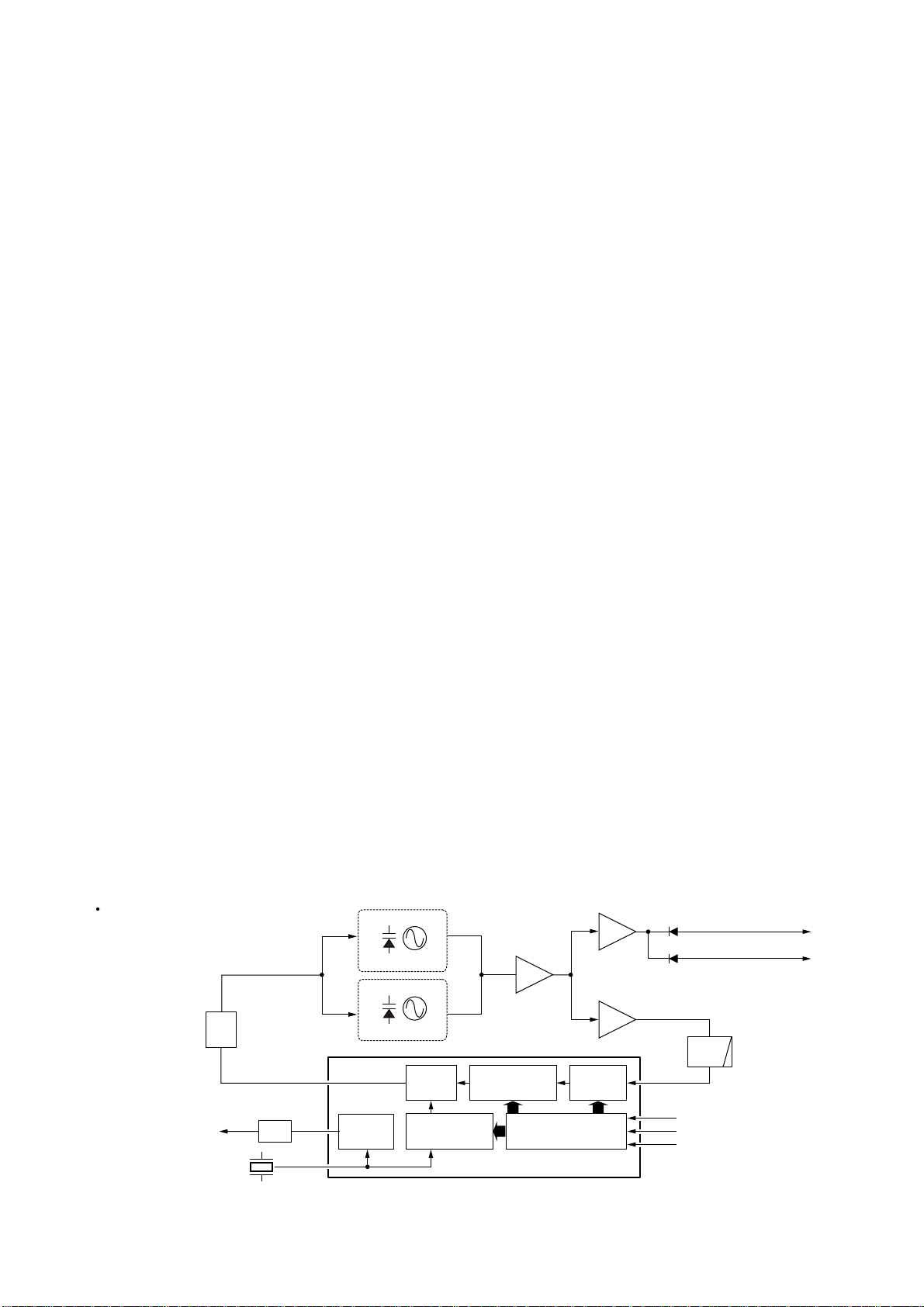

4-3 PLL CIRCUIT

4-3-1 GENERAL

A PLL circuit provides stable oscillation of the transmit frequency and receive 1st LO frequency. The PLL output compares the phase of the divided VCO frequency to the reference frequency. The PLL output frequency is controlled by a

crystal oscillator and the divided ratio (N-data) of a programmable divider.

The PLL circuit, using a one chip PLL IC (IC1), directly generates the transmit frequency and divided ratio based on

serial data from the CPU and compares the phases of VCO

signals with the reference oscillator frequency. The PLL IC

detects the out-of-step phase and output from pin 5.The reference frequency (15.3 MHz) is oscillated by X1.

4-3-2 TX LOOP

The generated signal at the TX-VCO (Q11, D7) enters the

PLL IC (IC1, pin 8) and is divided at the programmable

divider section and is then applied to the phase detector

section.

The phase detector compares the input signal with a reference frequency, and then outputs the out-of-phase signal

(pulse-type signal) from pin 5.

The pulse-type signal is converted into DC voltage (lock

voltage) at the loop filter (R40–R42, C75–C77), and then

applied to varactor diodes (D6) of the TX-VCO to stabilize

the oscillated frequency.

4-3-3 RX LOOP

The generated signal at the RX-VCO (Q10, D5) enters the

PLL IC (IC1, pin 8) and is divided at the programmable

divider section and is then applied to the phase detector

section.

The phase detector compares the input signal with a reference frequency, and then outputs the out-of-phase signal

(pulse-type signal) from pin 5.

The pulse-type signal is converted into DC voltage (lock

voltage) at the loop filter (R40–R42, C74–C77), and then

applied to varactor diodes (D5) of the RX-VCO to stabilize

the oscillated frequency. The lock voltage is also used for

the receiver circuit for the bandpass filter center frequency.

The lock voltage from the loop filter is amplified at the buffer

amplifier (Q13) and then applied to the CPU (IC7, pin 60).

The signal is analyzed at the CPU, and then applied to the

D/A convertor (IC9). The D/A convertor outputs “T1”, “T2”,

“T3”, “T4” signals to RF bandpass filters D12–D15 to suppress harmonic components.

4-3-4 VCO CIRCUIT

The VCO outputs from Q11 (TX) and Q10 (RX) are buffer

amplified at Q7 and Q6, and are then sent to the T/R switch

(D3, D4). The receive LO signal is applied to the 1st mixer

circuit (Q16) through an attenuator, and the tramsmit signal

is applied to the YGR amplifier (Q4). A portion of the VCO

output is reapplied to the PLL IC (IC1, pin 8) via the buffer

amplifier (Q6) and low-pass filter (L18, R53, C89–C91).

Shift register

Prescaler

Phase

detector

Loop

filter

Programmable

counter

Programmable

divider

X1

15.2 MHz

45.9 MHz signal

to the FM IF IC

Q11, D7

TX VCO

RX VCO

Buffer

Buffer

Buffer

Q5

Q6

Q7

11

9

10

P.STB

IC1 (PLL IC)

CK

DATA

to transmitter circuit

to 1st mixer circuit

D3

D4

2

1

5

8

Q10, D5

Crystal

oscillator

×3

Q18

LPF

PLL CIRCUIT

4 - 4

4-4 POWER SUPPLY CIRCUITS

VOLTAGE LINE

LINE

HV

VCC

CPU5V

T5V

R5V

S5V

+5V

VCO5V

DESCRIPTION

The voltage from the attached battery pack.

The same voltage as the HV line (battery volt-

age) which is controlled by the power swtich

([VOL] control).

Common 5 V converted from the VCC line by the

+5 regulator circuit (IC10). The output voltage is

applied to the CPU (IC7), reset circuit (IC8) and

etc.

5 V for transmitter circuits regulated by the T5

regulator circuit (Q27).

5 V for receiver circuits regulated by the R5 regulator circuit (Q26).

Common 5 V converted from the VCC line by the

S5 regulator circuit (Q24, Q19).

The same voltage as the CPU5V line for the analog swtich (IC6), buffer amplifier (Q13), etc.

The same voltage as the +5V line for the TXVCO (Q11), RX-VCO (Q10) and buffer amplifiers

(Q5–Q7).

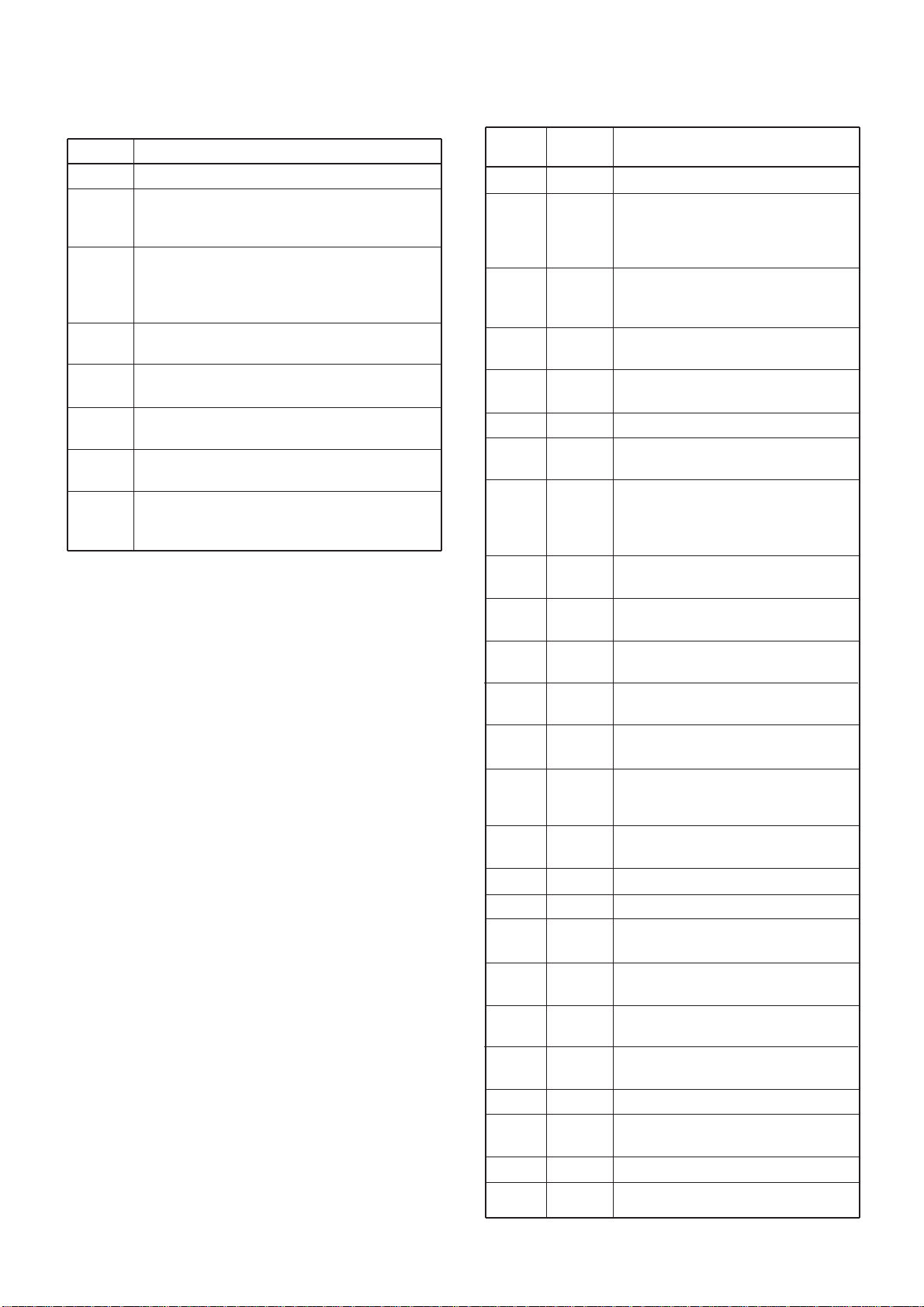

4-5 PORT ALLOCATIONS

4-5-1 CPU (IC7)

Pin

number

7

13

14

19

20

23

24

25

28

29

30

36

37

38

39

40

41

42

43

44

45

46

51

52

53

54

55

57

58

59

60

Port

name

RES

SENC0

SENC1

SENC2

SENC3

CENC0

CENC1

CENC2

SCK

SO

BEEP

PLST

DAST

EXST

PTT

TXC

RLED

TLED

AFON

ESDA

CLI

CLO

F1

F2

NOIS

UNLK

TEMP

CDEC

SDEC

RSSI

LVIN

Description

Input port for RESET signal.

Outputs single tone encode signal.

Outputs CTCSS/DTCS data signal.

Outputs serial clock signal to the PLL

IC (IC1), EEPROM (IC11), etc.

Outputs data signal to the PLL IC

(IC1) and D/A convertor (IC9).

Outputs beep audio signal.

I/O port for strobe signal from/to PLL

IC (IC9).

• Outputs strobe signal to the D/A convertor (IC9).

• Input port for the initial version signal.

Outputs strobe signal for the expander

IC (IC15).

Input port for [PTT] swtich signal.

High:While [PTT] switch is pushed.

Outputs TX mute control signal.

High:While transmitting

Outputs BUSY LED control signal.

High:While receiving.

Outputs TX LED control signal.

high: While transmitting.

Outputs control signal for the regulator

circuit of AF power amplifier.

High:While squelch is open, etc.

I/O port for data signal from/to the

EEPROM (IC11).

Input port for cloning signal.

Outputs the cloning signal.

Input ports for the customization key

signals.

Input port for the noise pulse signal for

the squelch function.

Input port for PLL unlock signal.

High:PLL is locked.

Input port for the transceiver’s internal

tempereture detection.

Input port for CTCSS/DTCS signals.

Input port for single tone decode sig-

nal.

Input port for the RSSI voltage.

Input port for the PLL lock voltage.

4 - 5

Pin

number

61

62

Port

name

BDET

BATV

Description

Input port for the battery’s type detection.

Input port for battely voltage detection.

4-5-3 D/A CONVERTOR IC (IC9)

Pin

number

2, 3,

10, 11

14

15

22

Port

name

T1–T4

REF

BAL

DEV

Description

Output tunable bandpass filters control signals.

Outputs differential voltage for the reference oscillator (Q31, D19, X1).

Outputs DTCS balance control signal.

Outputs modulating signal for the

modulator circuit (D6).

CPU (IC7)–continued

4-5-2 OUTPUT EXPANDER IC (IC15)

Pin

number

4

5

6

7

11

12

13

14

Port

name

CSFT

RMUT

MMUT

DUSE

T5C

R5C

S5C

NWC

Description

Outputs clock shift control signal for

CPU.

Outputs RX mute control signal.

Outputs TX mute control signal.

Outputs low-pass filter cut-off frequen-

cy control signal when DTCS is activated.

Outputs T5 regulator control signal.

Low: While transmitting.

Outputs R5 regulator control signal.

Low: While receiving.

Outputs S5 regulator control signal.

Low: While power is ON.

Outputs Narrow/Wide of channel

spacing control signal.

Low: While Narrow is selected.

5 - 1

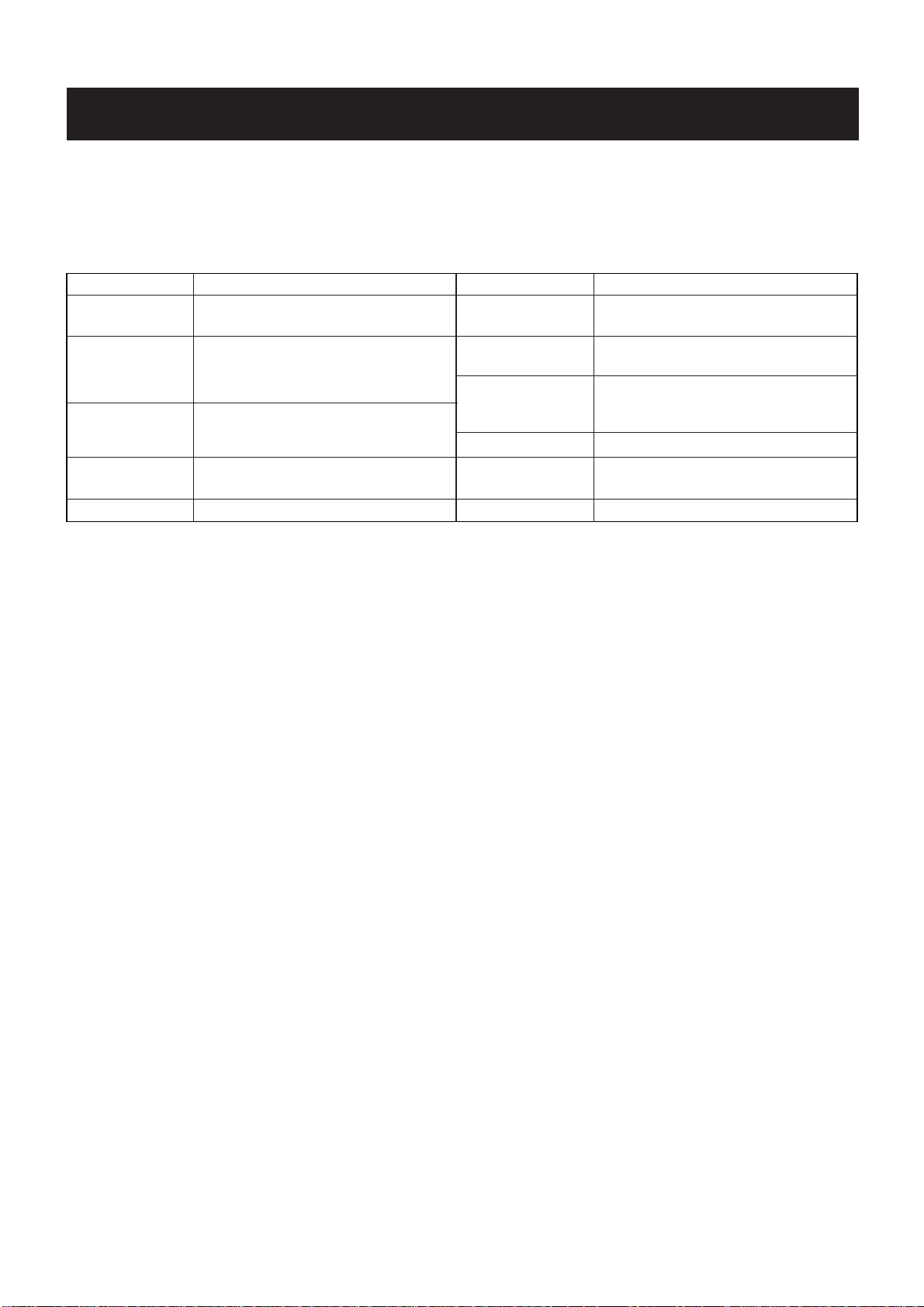

5-1 PREPARATION

When you adjust the contents on page 5-5 or 5-6, SOFTWARE ADJUSTMENT, the optional CS-F21 ADJ ADJUSTMENTSOFTWARE

(Rev. 1.0 or later), OPC-478 CLONING CABLE and a JIG CABLE (see illustration at page 5-2) are required.

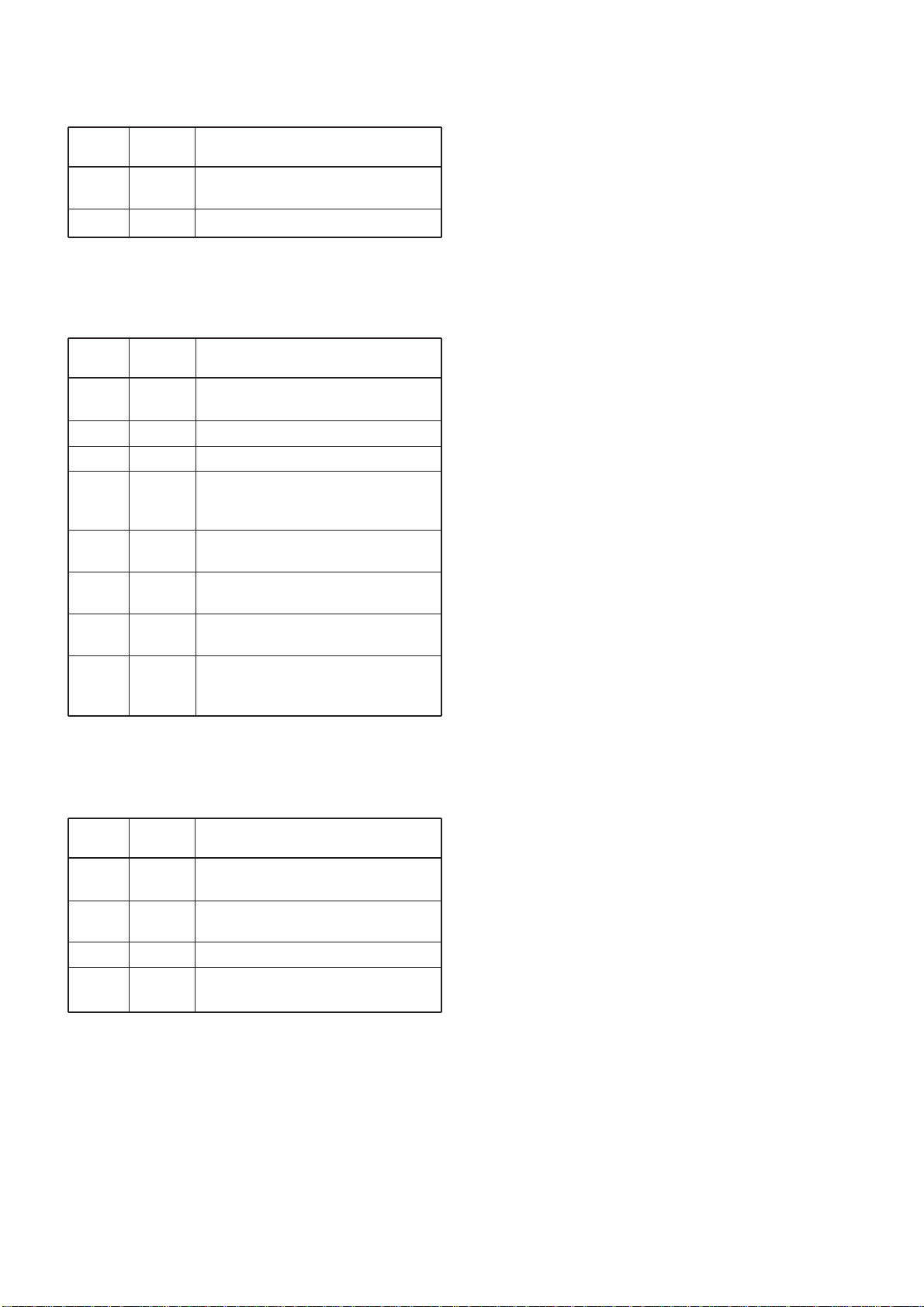

■ REQUIRED TEST EQUIPMENT

SECTION 5 ADJUSTMENT PROCEDURES

EQUIPMENT

DC power supply

RF power meter

(terminated type)

Frequency counter

FM deviation meter

Digital multimeter

GRADE AND RANGE

Output voltage : 7.2 V DC

Current capacity : 5 Aor more

Measuring range : 1–10 W

Frequency range : 300–600 MHz

Impedance : 50 Ω

SWR : Less than 1.2 : 1

Frequency range : 0.1–600 MHz

Frequency accuracy : ±1 ppm or better

Sensitivity : 100 mV or better

Frequency range : DC–600 MHz

Measuring range : 0 to ±5 kHz

Input impedance : 10 MΩ/V DC or better

EQUIPMENT

Audio generator

Attenuator

Standard signal

generator (SSG)

DC voltmeter

Oscilloscope

AC millivoltmeter

GRADE AND RANGE

Frequency range : 300–3000 Hz

Output level : 1–500 mV

Power attenuation : 40 or 50 dB

Capacity : 10 W or more

Frequency range : 120–600 MHz

Output level : 0.1 µV–32 mV

(–127 to –17 dBm)

Input impedance : 50 kΩ/V DC or better

Frequency range : DC–20 MHz

Measuring range : 0.01–20 V

Measuring range : 10 mV–10 V

■ SYSTEM REQUIREMENTS

• IBM PC compatible computer with an RS -232C serial port

(38400 bps or faster)

• Microsoft Windows 95 or Windows 98

• Intel i486DX processor or faster (Pentium 100 MHz or

faster recommended)

• At least 16 MB RAM and 10 MB of hard disk space

• 640×480 pixel display (800×600 pixel display recommended)

■ ADJUSTMENT SOFTWARE INSTALLATION

q Boot up Windows.

- Quit all applications when Windows is running.

w Insert the cloning software CD-ROM into the appropriate

CD-ROM drive.

e Select ‘Run’ from the [Start] menu.

r Type the setup program name using the full path name,

then push the [Enter] key. (For example; D:\ setup)

t Follow the prompts.

y Program group ‘CS-F21’ appears in the ‘Programs’ folder

of the [Start] menu.

■ STARTING SOFTWARE ADJUSTMENT

q Connect the transceiver and PC with the optional OPC-

478 and the JIG cable.

w Boot up Windows, and turn the transceiver power ON.

e Click the program group ‘CS-F21 ADJ’ in the ‘Programs’

folder of the [Start] menu, then CS-21G ADJ’s window is

appeared.

r Click ‘Connect’ on the CS-F21’s window, then appears

the transceiver’s up-to-date condition.

t Set or modify adjustment data as desired.

IBM is a registered trademark of International Bussiness

Machines Corporation in the U.S.A. and other countries.

Microsoft and Windows are registered trademarks of

Microsoft Corporation in the U.S.A. and other countries.

Screen shots produced with permission from Microsoft

Corporation. All other products or brands are registered

trademarks or trademarks of their respective holders.

Loading...

Loading...