Page 1

Please read this information, so you'll know how to help me, and make this site better.

If you have any new modifications that are not listed on this site, please mail the modification to me.

Any technical information like manuals, service notes, service manual, diagrams or other stuff, I will be very happy if you

will send it to me. If the information is on paper and you have access to a scanner or camera, then scan or photograph

the information and send the picture to me. I have a good connection to the internet, so the size is no problem.

KB2LJJ Privacy Guarantee

I will not give any guaranty on the radio modification.

Remember it is Illegal to transmit out of band.

The Radio Modification is for Informational purposes ONLY.

Doing such modifications on your radio may void any warranty and damage your equipment.

All mods found on this database are offered by other amateur radio hams or captured by the Packet system.

KB2LJJ takes no responsibility or liability for any damage done resulting from any modification.

For more information please email to support@kb2ljj.com

KB2LJJ Radio Mods Database and Manuals

Page 1

Page 2

SERVICE

MANUAL

HF/VHF/UHF ALL MODE TRANSCEIVER

i706MK™G

Page 3

INTRODUCTION

DANGER

This service manual describes the latest service information

for the IC-706MKIIG HF/VHF/UHF ALL MODE TRANSCEIVER at the time of publication.

VERSION NO.

#02, #12

#03, #13

#04, #14

#05, #15

#08, #18

VERSION

Europe

France

Spain

U.S.A.

Other

SYMBOL

EUR

FRA

ESP

USA

OTH

To upgrade quality, any electrical or mechanical parts and

internal circuits are subject to change without notice or

obligation.

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than 16 V. This will ruin the

transceiver.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOTreverse the polarities of the power supply when con-

necting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW)

to the antenna connector. This could damage the transceiver’s front end.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit order numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

1110004080 S.IC µPC2709T IC-706MKIIG MAIN UNIT 05 pieces

8810009020 Screw FH M2.6 x 5 ZK IC-706MKIIG Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

REPAIR NOTES

1. Make sure a problem is internal before disassembling the

transceiver.

2. DO NOT open the transceiver until the transceiver is

disconnected from its power source.

3. DO NOT force any of the variable components. Turn

them slowly and smoothly.

4. DO NOT short any circuits or electronic par ts. An insu-

lated tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the trans-

ceiver is defective.

6. DO NOT transmit power into a signal generator or a

sweep generator.

7. ALWAYS connect a 50 dB to 60 dB attenuator between

the transceiver and a deviation meter or spectrum analyzer when using such test equipment.

8. READ the instructions of test equipment thoroughly

before connecting equipment to the transceiver.

Page 4

TABLE OF CONTENTS

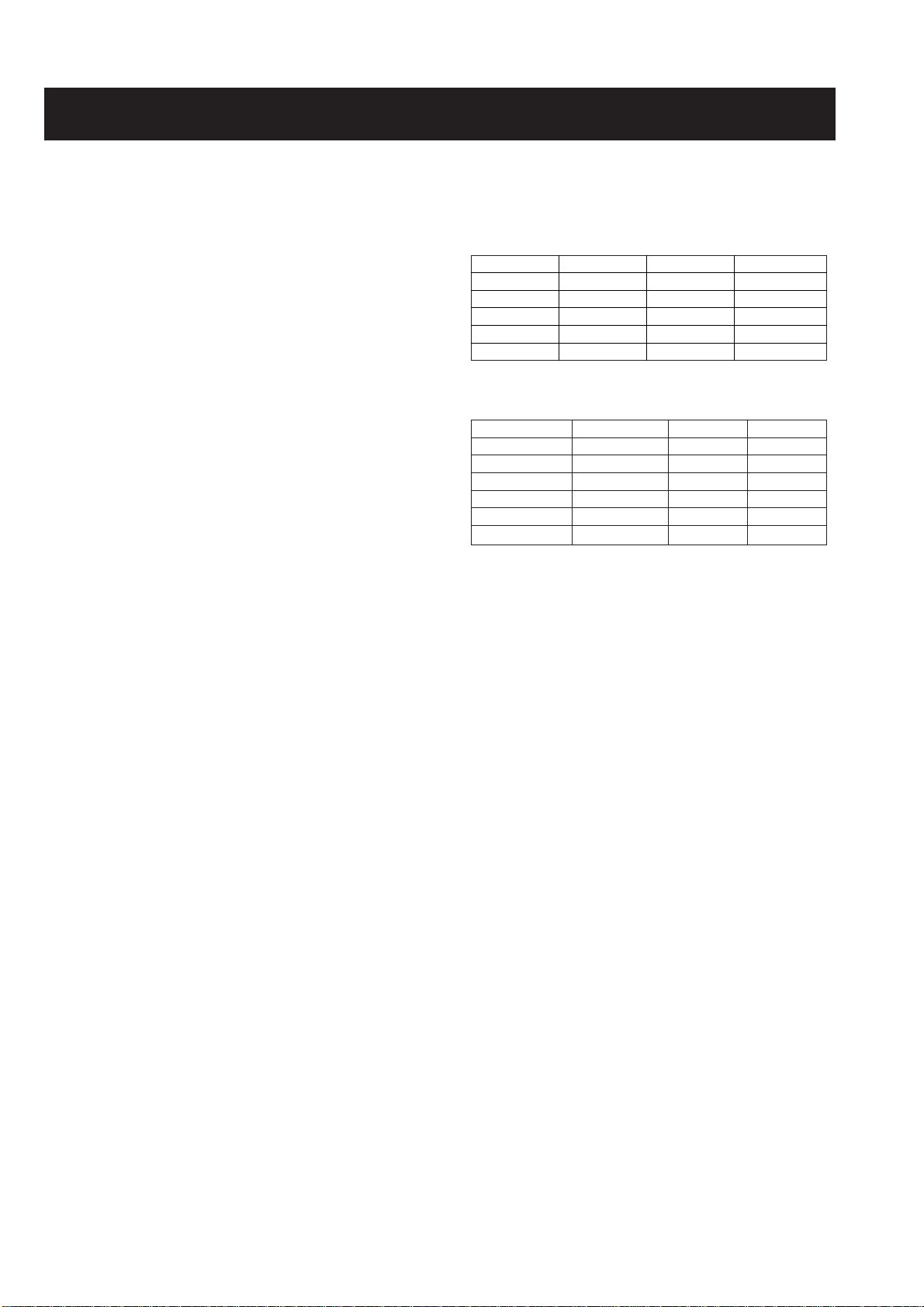

SECTION 1 SPECIFICATIONS

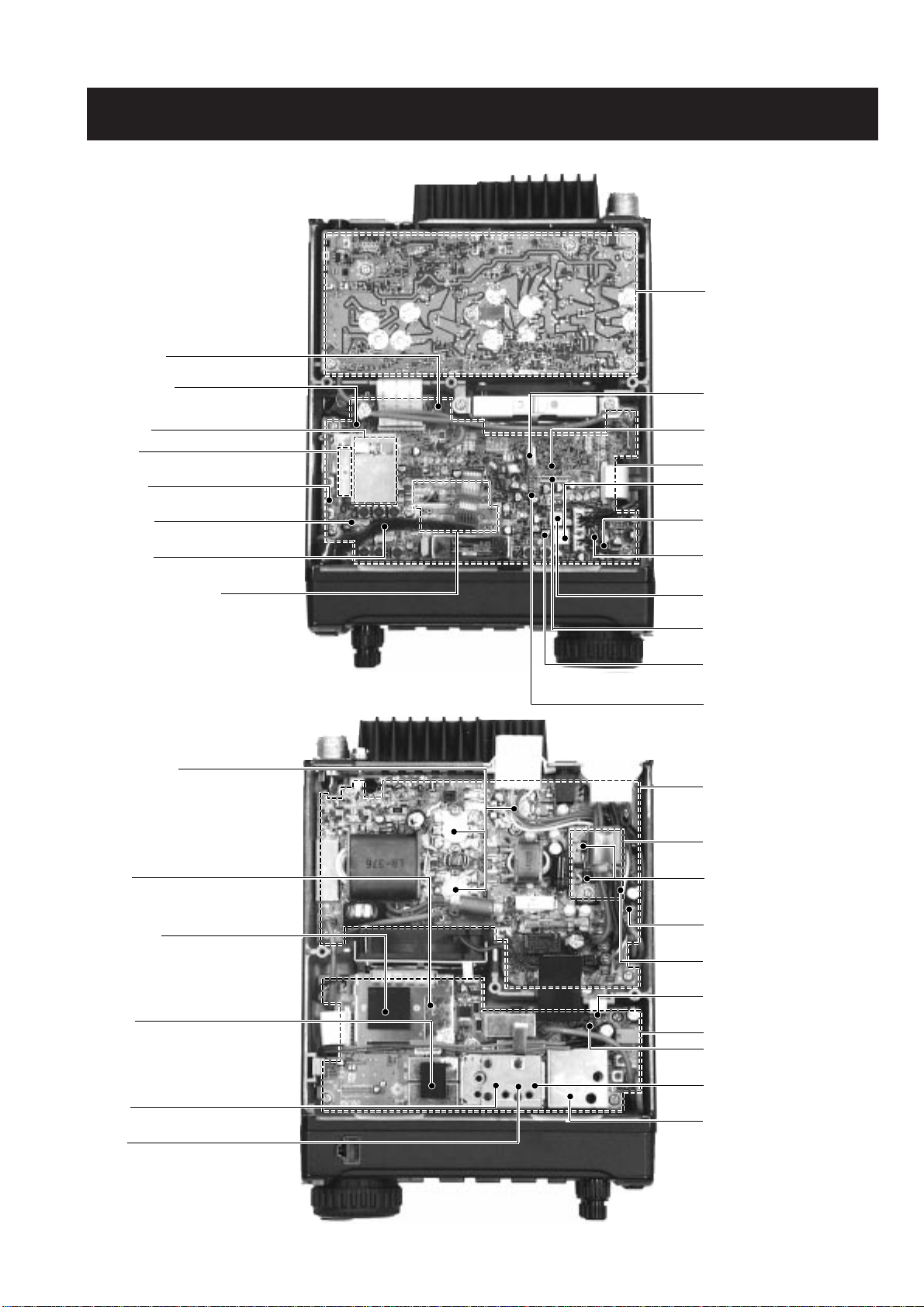

SECTION 2 INSIDE VIEWS

SECTION 3 CIRCUIT DESCRIPTION

3 - 1 RECEIVER CIRCUITS................................................................................................................................ 3 - 1

3 - 2 TRANSMITTER CIRCUITS ......................................................................................................................... 3 - 4

3 - 3 PLL CIRCUITS............................................................................................................................................ 3 - 6

3 - 4 LOGIC CIRCUITS....................................................................................................................................... 3 - 8

SECTION 4 ADJUSTMENT PROCEDURES

4 - 1 PREPARATION BEFORE SERVICING ...................................................................................................... 4 - 1

4 - 2 PLL ADJUSTMENTS................................................................................................................................... 4 - 2

4 - 3 TRANSMITTER ADJUSTMENTS............................................................................................................... 4 - 2

4 - 4 RECEIVER ADJUSTMENTS....................................................................................................................... 4 - 8

4 - 5 SET MODE ADJUSTMENT....................................................................................................................... 4 - 10

SECTION 5 PARTS LIST

SECTION 6 MECHANICAL PARTS AND DISASSEMBL Y

SECTION 7 SEMI-CONDUCTOR INFORMATION

SECTION 8 BOARD LAYOUTS

8 - 1 DISPLAY BOARD........................................................................................................................................ 8 - 1

8 - 2 MAIN BOARD.............................................................................................................................................. 8 - 3

8 - 3 HPF AND DRIVER BOARD........................................................................................................................ 8 - 5

8 - 4 PAUNIT....................................................................................................................................................... 8 - 7

8 - 5 PLL UNIT..................................................................................................................................................... 8 - 9

8 - 6 FILTER BOARD......................................................................................................................................... 8 - 11

SECTION 9 BLOCK DIAGRAM

SECTION 10 VOLTAGE DIAGRAM

Page 5

■ GENERAL

• Frequency coverage :

Receive 0.030 – 200.000 MHz*

430.000 – 470.000 MHz*

Transmit 1.800 – 1.999 MHz*

3.500 – 3.999 MHz*

7.000 – 7.300 MHz*

10.100 – 10.150 MHz

14.000 – 14.350 MHz

18.068 – 18.168 MHz

21.000 – 21.450 MHz

24.890 – 24.990 MHz

28.000 – 29.700 MHz

50.000 – 54.000 MHz*

144.000 – 148.000 MHz*

430.000 – 450.000 MHz*

*Depending on version.

• Mode : USB, LSB, CW, RTTY(FSK), AM, FM,

WFM (WFM is for receiver only)

• Number of memory ch. : 107 (99 regular, 6 scan edges,1 call)

• Antenna connector : SO-239 ✕ 2

(for HF/50 MHz and 144/440 MHz)/50 Ω

• Power supply requirement : 13.8 V DC ±15% (negative ground)

• Frequency stability : Less than ± 7 ppm from 1 min. to 60

min. after power ON. After that, rate of

stability less than ±1 ppm/hr. at +25˚C

(+77˚F). Temperature fluctuations 0˚C

to +50˚C (+32˚F to +122˚F) less than

± 5 ppm.

• Current consumption :

Transmit max. power 20 A

Receive standby 1.8 A

max. audio 2.0 A

• Usable temperature range : –10˚C to +60˚C (+14˚F to +140˚F)

• Dimensions : 167(W)

✕ 58(H) ✕ 200(D) mm

(projections not included) 69⁄16(W) ✕ 29⁄32(H) ✕ 77⁄8(D) inch

• Weight : 2.45 kg (5 lb 6 oz)

• CI-V connector : 2-conductor 3.5 (d) mm (

1

/8")/8 Ω

• ACC connector : 13-pin

■ TRANSMITTER

• Output power :

1.8–50 MHz band SSB/CW/RTTY/FM 5–100 W

AM 2–40 W

144 MHz band SSB/CW/RTTY/FM 5–50 W

AM 2–20 W

440 MHz band SSB/CW/RTTY/FM 2–20 W

AM 2–8 W

• Modulation system :

SSB Balanced modulation

AM Low level modulation

FM Variable reactance modulation

• Spurious emissions :

Below 47.5 MHz Less than –50 dB (typical)

Above 47.5 MHz Less than –60 dB

• Carrier suppression : More than 40 dB

• Unwanted sideband supp. : More than 50 dB

• Microphone connector : 8-pin modular jack (600 Ω)

• KEY connector : 3-conductor 6.35 (d) mm (

1

/4")

• RTTY connector : 3-conductor 3.5 (d) mm (

1

/8")

■ RECEIVER

• Receive system :

SSB/CW/AM/WFM Double superheterodyne

FM Triple superheterodyne

• Intermediate frequencies :

*FM or FM-N mode only

• Receive sensitivity : (pre-amp ON)

Note: SSB, CW and AM modes are measured at 10 dB S/N; FM mode at

12 dB SINAD.

*Except 4–4.5 MHz, 8–9 MHz.

• Squelch Sensitivity : (pre-amp ON)

SSB Less than 5.6 µV

FM Less than 0.32 µV

• Selectivity* :

SSB, CW, RTTY More than 2.4 kHz/–6 dB

Less than 4.8 kHz/–60 dB

AM/FM-N More than 8.0 kHz/–6 dB

Less than 30 kHz/–40 dB

FM More than 12 kHz/–6 dB

Less than 30 kHz/–60 dB

*Without an optional filter unit and with mid bandwidth selected.

• Spurious and image rejection ratio:

HF band 70dB

50 MHz band 65 dB (except IF through)

144/440 MHz band 65 dB

• Audio output power : More than 2.0 W at 10% distortion

(at 13.8 V DC) with an 8 Ω load

• RIT variable range : ± 9.99 kHz

• PHONES connector : 3-conductor 3.5 (d) mm (1/8")/8 Ω

• EXT SP connector : 2-conductor 3.5 (d) mm (

1

/8")/8 Ω

3rd IF

455 kHz*

455 kHz*

—

—

—

MODE

SSB/AM-N/FM

AM/FM-N

CW

RTTY

WFM

1st IF

69.0115 MHz

69.0100 MHz

69.0106 MHz

69.0105 MHz

70.7000 MHz

2nd IF

9.0115 MHz

9.0100 MHz

9.0106 MHz

9.0105 MHz

10.7000 MHz

1 - 1

SECTION 1 SPECIFICATIONS

FM

—

—

0.5 µV

0.25 µV

0.18 µV

0.18 µV

FREQUENCY

0.5 – 1.8 MHz

1.8 – 28 MHz*

28 – 29.999 MHz

50 MHz band

144 MHz band

440 MHz band

SSB/CW/RTTY

—

0.16 µV

0.16 µV

0.13 µV

0.11 µV

0.11 µV

AM

13 µV

2 µV

2 µV

1 µV

1 µV

1 µV

All stated specifications are subject to change without notice or obligation.

Page 6

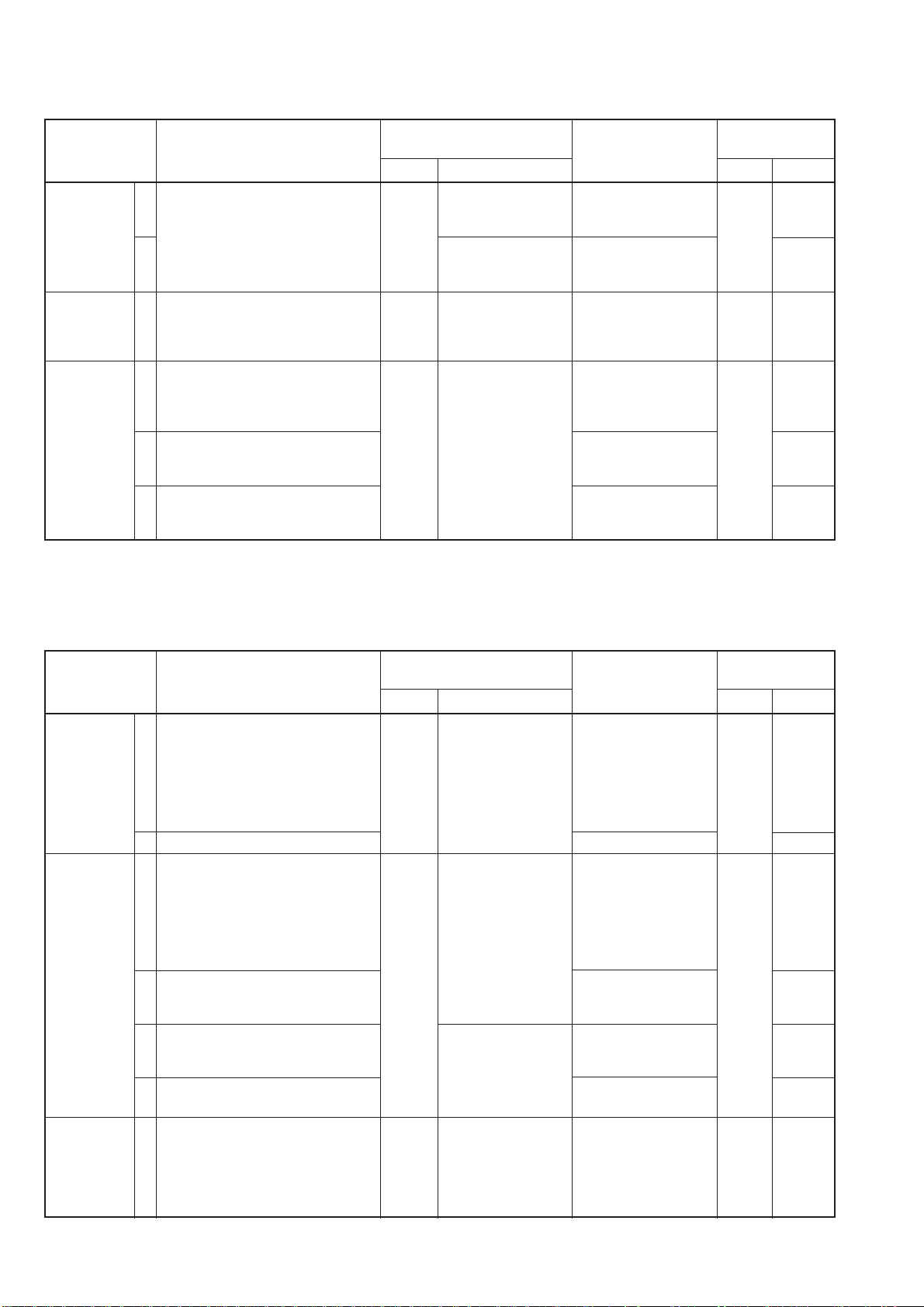

Predrive amplifier

(Q101: 2SK2854)

HPF board

D/A converter

(IC2201: M62352GP)

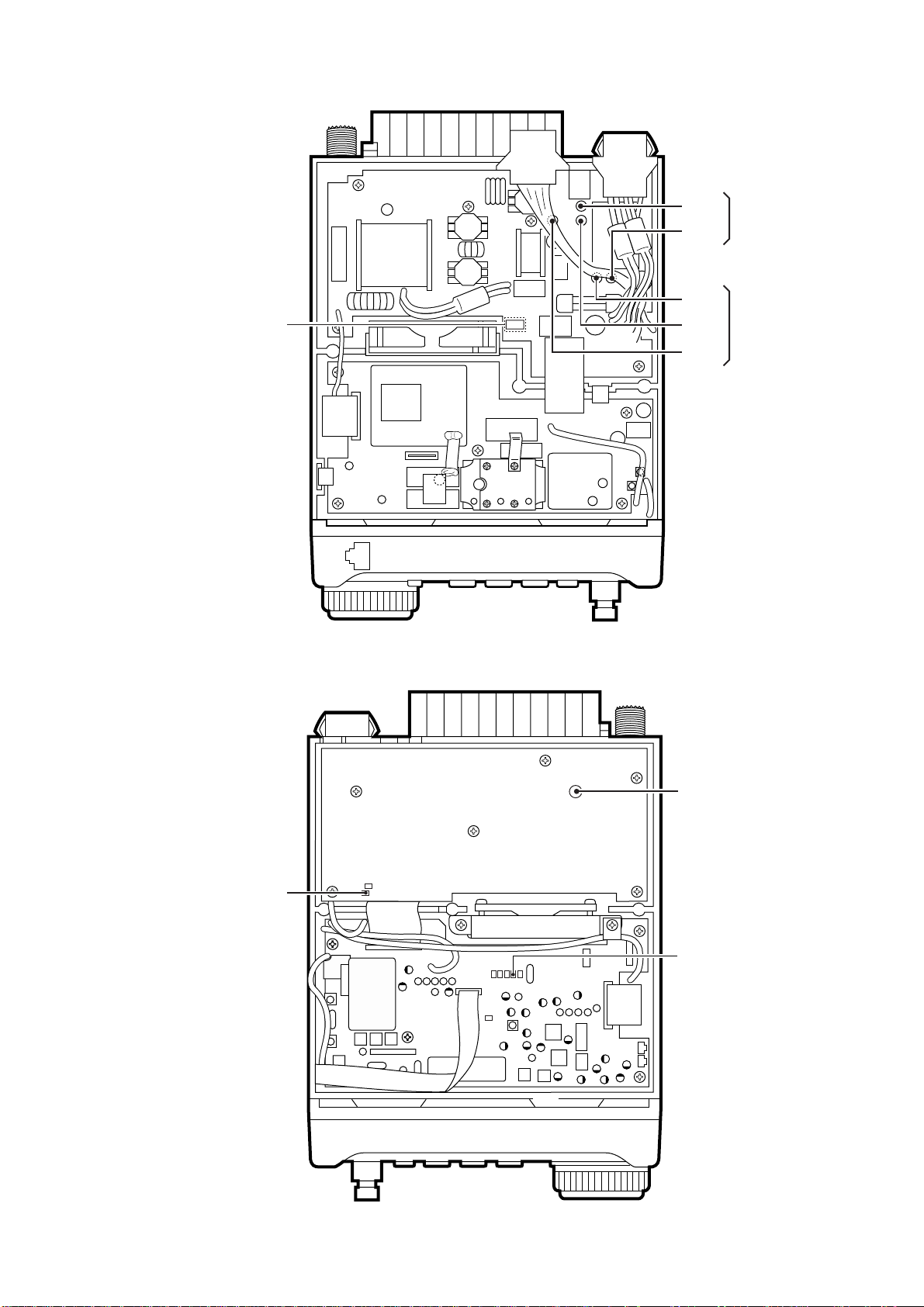

¡PA AND PLL UNITS

FILTER board

MAIN CPU clock

(X2161: CR-636)

MAIN CPU *

(IC 2001: HD6433337YA56F)

MAIN board

3rd IF filter for FM *

(FI791: SFPC455E-TC01)

MIC amplifier

(IC931: µPC5023GS-077-E1)

AF selector switch *

(IC861: BU4052BCFV-E2)

Tx FM PLL IC *

(IC1011: LC7153M-TLM)

Balanced modulator *

(IC1041: NJM1496V)

Discriminator

(X791: CDB455CX24)

FM IF IC *

(IC791: TA31136FN)

RX preamplifier

(IC151: µPC1658G)

1st mixer

(D271: HSB88WSTR)

1st IF filter

(FI511: FI-261)

2nd mixer *

(D551: HSB88WSTR)

2nd IF filter

(FI561: FL-23)

Space for optional filters

FL-100, FL-101, FL-103

FL-233, FL-232

Power amplifers

(Q171, Q172, Q231: SRFJ7044)

DDS IC

(IC101: SC-1246)

BFO DDS IC

(IC901: SC-1287)

PLL IC *

(IC461: LMX2306TMX)

VCO1 *

(Q301: 2SK508)

VCO2 *

(Q331: 2SK508)

PA unit

DRIVER board

Drive amplifers

(Q161, Q211: MRF1508TI)

Predrive amplifer

(Q121: MXR9745)

AF power amplifer

(IC231: LA4425A)

PLL unit

AF volume controller

(IC201: M5282FP)

VCO3 *

(Q361: 2SK508)

Reference oscillator

(X621: CR-275A 30.00000 MHz)

*Located under side of the point

¡MAIN AND FILTER BOARDS

2 - 1

SECTION 2 INSIDE VIEWS

Page 7

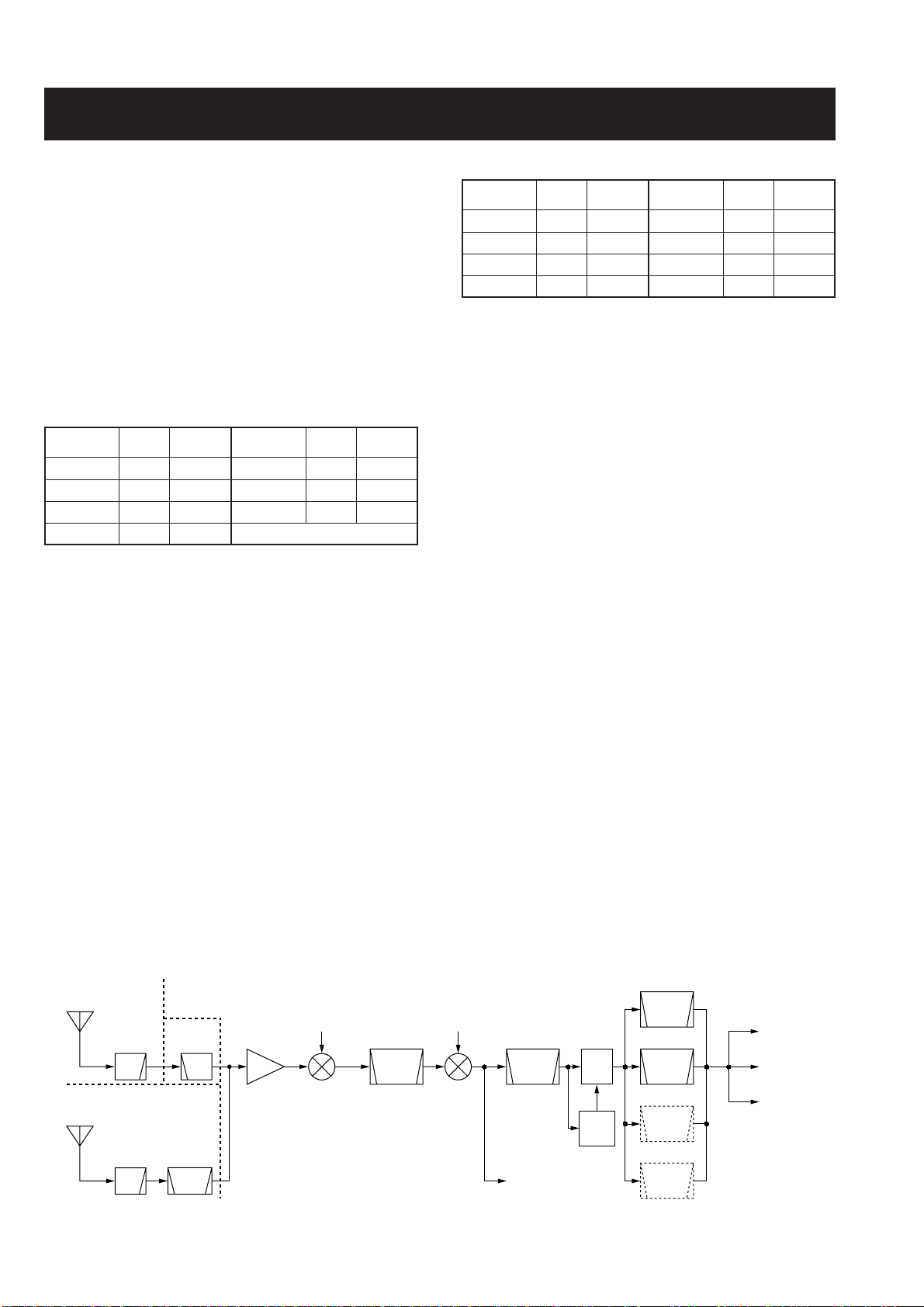

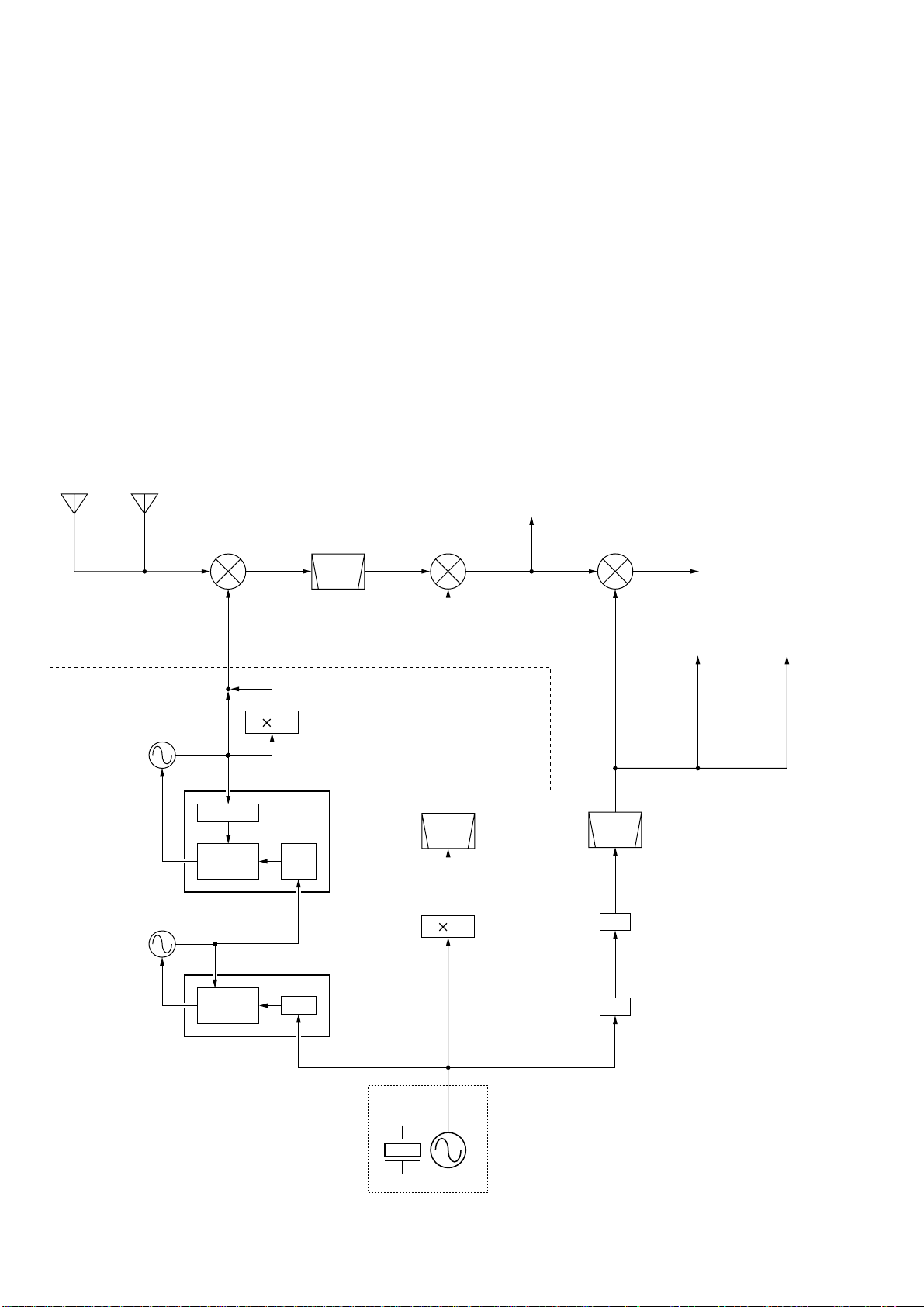

3-1 RECEIVER CIRCUITS

3-1-1 HF/50 MHz RF CIRCUIT

(FILTER, MAIN AND HPF BOARDS)

HF/50 MHz RF filters pass only the desired band signals

and suppress any undesired band signals. The HF/50 MHz

RF circuit has 7 low-pass filters and 8 high-pass filters for

specified band use.

HF/50 MHz RF signals from the [ANT1] connector, pass

through one of 7 low-pass filters as below, the transmit/

receive switching relay (FILTER board; RL1) and low-pass

filter (FILTER board; L1, L2, C1–C5), and are then applied

to the MAIN board via J1 (FILTER board).

The signals from the FILTER board are applied to or bypass

the 20 dB attenuator (R122, R125, R126). The signals pass

through the high-pass filter (L132, L133, C132–C137) to

suppress strong signals below 1.6 MHz and are then applied

to the HPF board via the “SAF” terminal.

(1) 0.03–2 MHz and 30–40 MHz

The signals pass through a low-pass filter (L101, L102,

C101–C105), and then applied to the preamplifier circuit on

the MAIN board.

(2) 2–30 MHz

The signals from the low-pass filter (L101, L102,

C101–C105) are applied to one of 6 high-pass filters as at

right above and are then applied to the preamplifier circuit

on the MAIN board.

(3) 40–60 MHz

The signals pass through the low-pass filter (L172, L173,

C172–C176) and the high-pass filter (L174, L175,

C177–C181) via D171 and are then applied to the preamplifier circuit on the MAIN board.

3-1-2 VHF AND UHF RF CIRCUITS (PA UNIT)

The VHF and UHF RF circuits pass and amplify only the

desired band signals and suppresses any undesired band

signals. The both RF circuits have a preamplifier and bandpass filters respectively.

• VHF RF CIRCUIT

The VHF RF signals from the [ANT2] connector pass

through the low-pass filter (L263–L265, C274–C276) and

antenna switching circuit (D291–D293). The signals are

applied to the bandpass filter (D403, D409, D408), and are

then amplified at the preamplifier circuit (Q403). The amplified signals are then applied to the another bandpass filter

(D407, D406, D410).

• UHF RF CIRCUIT

The UHF RF signals from the [ANT2] connector pass

through the high-pass filter (L316, L317, C326–C327), lowpass filter (L313–L315, C322–C324) and antenna switching

circuit (D341, D342, D343). The signals are amplified at the

preamplifier circuit (Q453) between the 2 bandpass filters

(D454, D453 and D454, D456).

The filtered signals are applied to the MAIN board via J481

(PAunit) and are then applied to the preamplifier circuit.

D403, D408, D409, D406, D407, D410, D454, D453, D454

and D456 are varactor diodes that tune the ceinter frequency of an RF passband for wide bandwidth receiving and

good image response rejection. On the VHF band, receiving

signals are above 129 MHz, the switching diodes (D404,

D405) are turned off by the control signal “2MBL” from PLL

unit, then the varactor diodes (D408, D407) are disconnected.

• Used RF high-pass filter (HPF board)

• Used RF low-pass filter (FILTER board)

3 - 1

SECTION 3 CIRCUIT DESCRIPTION

• RECEIVER CONSTRUCTION

1st LO:

69.0415 MHz–

530.0115 MHz

BPF

LPF

HPF

1st mixer

D271

2nd LO:

60.0 MHz

2nd

mixer

D511

to AM demod.

circuit (D761)

to FM demod.

circuit (IC791)

[ANT1]

0.03–60 MHz

LPF

[ANT2]

60–470 MHz

Crystal

filter

FI511

69.0115 MHz

Crystal

filter

NB

gate

FI561

to WFM detector

circuit (IC631)

to BFO circuit

(IC1041)

9.0115MHz

NB

circuit

FILTER BOARD

PA UNIT

HPF

BOARD

MAIN BOARD

SSB, CW

filter

FI671

AM, FM-N

filter

FI681

Optional

filter-1

Optional

filter-2

amp.

Pre-amp.

IC151

Frequency

(MHz)

0.03–2 MHz

2–4 MHz

4–8 MHz

8–15 MHz

Frequency

(MHz)

15–22 MHz

22–30 MHz

30–60 MHz

Control

signal

L5

L6

L7

Control

signal

L1

L2

L3

L4

Entrance

coil

RL15

RL13

RL5

RL9

Entrance

coil

RL11

RL7

RL3

Frequency

(MHz)

0.03–2 MHz

2–4 MHz

4–8 MHz

8–15 MHz

Frequency

(MHz)

15–22 MHz

22–30 MHz

30–40 MHz

40–60 MHz

Control

signal

L5H

L6H

THH

B7H

Control

signal

THH

L2H

L3H

L4H

Entrance

coil

D111

D121

D131

D141

Entrance

coil

D151

D161

D111

D171

Page 8

3-1-3 PREAMPLIFIER CIRCUIT (MAIN BOARD)

The preamplifier circuit in the IC-706MKIIG has approx.

15dB gain over a wide-band frequency range.

When the preamplifier is turned ON, the signals from the RF

circuit are applied to the preamplifier (IC151) via D2182.

Amplified or bypassed signals are applied to the 1st mixer

circuit (D271).

3-1-4 1ST MIXER CIRCUIT (MAIN BOARD)

The 1st mixer circuit mixes the receive signals with the 1st

LO signal to convert the receive signal frequencies to a 69

or 70.7 MHz 1st IF signal.

The signals from the preamplifier circuit, or signals which

bypass the preamplifier, are passed through a low-pass filter and then applied to the 1st mixer (D271).

The 1st LO signals

(69.0415–539.0115 MHz)

enter the MAIN board from

the PLL unit via J281. The

LO signal is amplified at

IC281, filtered by a lowpass filter, and then,

applied to the 1st mixer.

3-1-5 1ST IF CIRCUIT (MAIN BOARD)

The 1st IF circuit filters and amplifies the 1st IF signals. The

1st IF signals are applied to a Crystal Filter (FI511) to suppress out-of-band signals.

The 69 MHz 1st IF signals (except WFM) pass through the

crystal filter (FI511), however, the 70.7 MHz 1st IF signal

(WFM) passes through a bandpass filter (L501–L505,

C501–C506). Then the filtered signals are applied to the IF

amplifier (IC521).

The AGC voltage is supplied to the transmit/receive switching circuit (D521, D522) and D521/D522 function as PIN

attenuators for AGC operation.

The amplified signals are then applied to the 2nd mixer circuit (D551) via the bandpass filter (L542–L546,

C542–C545).

3-1-6 2ND MIXER CIRCUIT (MAIN BOARD)

The 2nd mixer circuit mixes the 1st IF signals and 2nd LO

signal (60.00 MHz) to convert the 1st IF to a 2nd IF.

The 1st IF signals from the band pass filter (L542–L546,

C542–C545) are converted to 9 MHz or 10.7 MHz 2nd IF

signals at the 2nd mixer (D551).

The 2nd IF signals are

applied to the bandpass filter (FI561) to suppress

undesired signals, such as

the 2nd LO signal, and are

then applied to the noise

blanker gate (D561,

D562).

While in WFM mode, the IF signals pass through the lowpass filter (L601, C601–C603), IF amplifiers (Q601, Q611),

ceramic filter (FI611). The signals are then applied to the

WFM demodulator circuit (IC631).

3-1-7 NOISE BLANKER CIRCUIT (MAIN BOARD)

The noise blanker circuit detects pulse type noise, and turns

OFF the signal line when noise appears.

Aportion of the signals from FI561 are amplified at the noise

amplifiers (Q621, Q632, amplifier section of IC631), then

detected at the noise detector (D632) to convert the noise

components to DC voltages.

The converted voltages are then applied to the noise

blanker switch (Q634, Q635). At the moment the detected

voltage exceeds Q634’s threshold level, Q635 outputs a

blanking signal to close the noise blanker gate (D561, D562)

by applying reverse-biased voltage.

The detected voltage from D632 is also applied to the noise

blanker AGC circuit (Q631, Q633) and is then fed back to

the noise amplifier (IC631) as a bias voltage. The noise AGC

circuit prevents closure of the noise blanker gate for long

periods by non-pulse-type noise. The time constant of the

noise blanker AGC circuit is determined by R637.

The 2nd IF signals from the noise blanker gate are then

applied to the 2nd IF circuit.

3-1-8 2ND IF CIRCUIT

The 2nd IF circuit amplifies and filters the 2nd IF signals.

The 2nd IF signals from the noise blanker gate (D561,

D562) are amplified at the IF amplifier (IC571) via the Tx/Rx

switch (D572) and applied to a 2nd IF filter as shown below.

The filtered or bypassed signals are applied to the buffer

amplifier (Q721), IF amplifiers (Q731, Q741) and buffer

amplifier (Q751) to obtain a detectable level at the demodulator circuit

The amplified signals from the buffer amplifier (Q751) are

shared between the SSB/CW/RTTY detector (IC841), AM

detector (D761) and AGC detector (D771). Output signals

from the buffer amplifier (Q721) are applied to the FM IF IC

(IC791).

3 - 2

• 1st IF frequency

• 2nd IF frequency

• Used 2nd IF filter

Mode Used filter Control signal

SSB, CW, RTTY

AM nar.

AM, FM nar.

FM

SSB nar.

CW nar., RTTY nar.

SSB wide, CW wide,

RTTY wide

FL-272 (FI671)

FL-94 (FI681)

Bypassed

Optional FL-223

Optional FL-100,

FL101, FL-223,

FL-232

Optional FL-103

2F23

2F80

2FTH

OP1 or OP2

OP1 or OP2

OP1 or OP2

1st IF

69.0115 MHz

69.0100 MHz

69.0106 MHz

69.0105 MHz

70.7000 MHz

Mode

SSB/AM-N/FM

AM/FM-N

CW

RTTY

WFM

2nd IF

9.0115 MHz

9.0100 MHz

9.0106 MHz

9.0105 MHz

10.7000 MHz

Mode

SSB/AM-N/FM

AM/FM-N

CW

RTTY

WFM

Page 9

3 - 3

3-1-9 IF SHIFT CIRCUIT (MAIN BOARD)

The IF shift circuit shifts the center frequency of IF signals to

electronically shift the center frequency.

The IF shift circuit shifts the 1st LO and BFO within ±1.2 kHz

in SSB/CW/RTTY modes or ±250 Hz in CW-N/RTTY-N

modes. As a result, the 2nd IF (also 1st IF) is shifted from

the center frequency of the 2nd IF filter (FI671, FI681 or

optional IF filters). This means 2nd IF signals do not pass

through the center of the 2nd IF filter. Therefore, the higher

or lower frequency components of the IF are cut out. Since

the BFO frequency is also shifted the same value as the 1st

IF, frequency is corrected at the detector.

In the IC-706MKIIG, the 1st LO frequency is shifted to

change the 2nd IF because a fixed 2nd LO frequency (60

MHz) is used. The 1st IF filter (FI671) and crystal filter

(FI561) have 15 kHz pass-band widths, and do not affect IF

shift operation.

3-1-10 AGC CIRCUIT (MAIN BOARD)

The AGC (Automatic Gain Control) circuit reduces IF amplifier gain to keep the audio output at a constant level. The

receiver gain is determined by the voltage on the AGC line

(Q776 collector).

The 2nd IF signal from the buffer amplifier (Q751) is detected at the AGC detector (D771) and applied to the AGC

amplifier (IC811b). IC811b sets the receiver gain with the

[RF/SQL] control via the “RFGV” signal line.

When receiving strong signals, the detected voltage increases and the AGC voltage decreases via the DC amplifier

(Q776). The AGC voltage is used for the bias voltage of the

transmit/receive switching PIN diodes (D521, D522, D572,

D573) to attenuate the received signals.

When AGC slow is selected, C775 and R778 are connected

in parallel to obtain appropriate AGC characteristics.

3-1-11 S-METER CIRCUIT (MAIN BOARD)

The S-meter circuit indicates the relative received signal

strength while receiving by utilizing the AGC voltage which

changes depending on the received signal strength.

The output voltage of the AGC amplifier (IC811b, pin 7) is

applied to the main CPU (IC2001, pin 36) as an S-meter signal via the analog switch (IC2101, pins 5, 3) as the “SML”

signal. The FM S-meter signal from the FM IF IC (IC791, pin

12) is also applied to the analog switch (IC2101, pin 5) via

the meter amplifier (Q774).

The S-meter signal from the main CPU (IC2001) is applied

to the sub CPU and is then displayed on the S-meter readout.

3-1-12 SQUELCH CIRCUIT (MAIN BOARD)

The squelch circuit mutes audio output when the S-meter

signal is lower than the [RF/SQL] control setting level.

The S-meter signal is applied to the main CPU (IC2001, pin

36) in SSB/CW/RTTY modes and is compared with the

threshold level set by the [RF/SQL] control. The [RF/SQL]

setting is picked up at the sub CPU (DISPLAY board; IC1,

pin 99). The main CPU compares the S-meter signal and

[RF/SQL] setting, and controls the AF selector switch

(IC861) to cut out AF signals via IC2122a.

In FM mode, a portion of the AF signals from the FM IF IC

(IC791, pin 9) are applied to the active filter section (pin 8)

where noise components above 20 kHz are amplified. The

signals are rectified at the noise detector section and then

output from pin 14. The noise squelch signal from pin 14 is

applied to the main CPU (IC2001, pin 31) via the analog

switch (IC2101, pins 14, 13) as the “NSQL” signal. The CPU

then controls the AF selector switch (IC861).

3-1-13 DEMODULATOR CIRCUITS (MAIN BOARD)

(1) SSB/CW/RTTY modes

The 2nd IF signals from the buffer amplifier (Q751) are

mixed with the BFO signal from the PLL unit at the product

detector (IC841, pin 6). The detected AF signals from IC841

(pin 1) are applied to the AF selector switch (IC861, pin 12).

(2) AM mode

The 2nd IF signals from the buffer amplifier (Q751) are

detected at the AM detector (D761). The detected AF signal

is applied to the AF selector switch (IC861, pin 15).

(3) FM/FM NARROW modes

The 2nd IF signals from the buffer amplifier (Q721) are

applied to the FM IF IC (IC791, pin 16) where the IF signals

are converted into 455 kHz IF signals. The signals pass

through FI791 and are applied to the quadrature detector

section. X791 is used for quadrature detector. The detected

AF signals from pin 9 are then applied to the AF selector

switch (IC861, pin 14) via the de-emphasis circuit (IC811a).

(4) WFM mode

The 2nd IF signals from the IF amplifier (Q611) are applied

to the WFM demodulator circuit (IC631, pins 2, 3) where the

IF signals are converted into AF signals. The detected AF

signals from pin 8 are then applied to the AF selector switch

(IC861, pin 11).

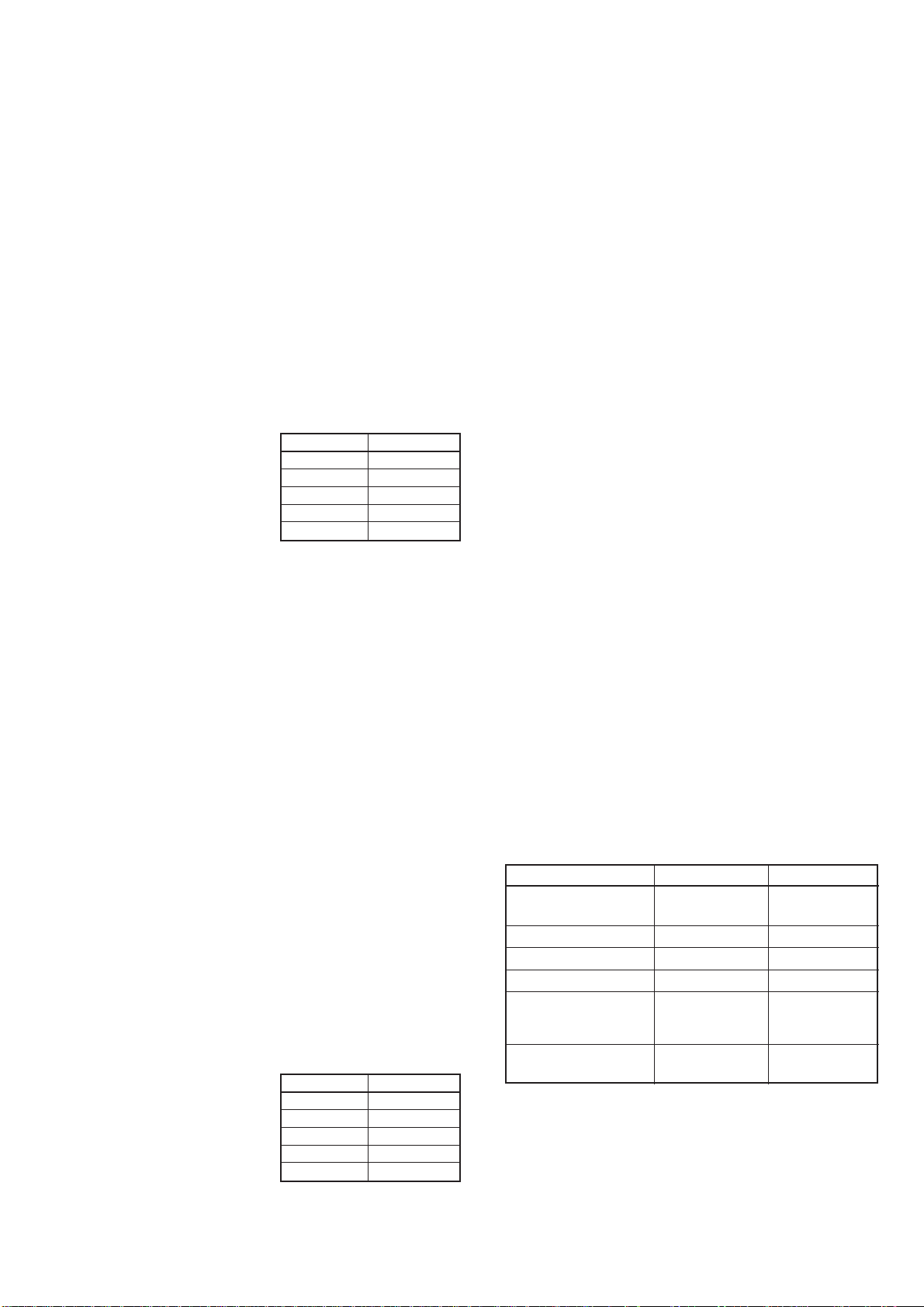

• AGC CIRCUIT

AGC line

RFGV

(RF gain control)

AGC

FAST

Q771

8 V

D771

C771

C772

2nd IF

signal

C775 R778Q773

C774 R777Q772

C773 R776

R775

D772

R772

R773

R774

Amp.

AGC

amp.

Q776, Q777

IC811b

“SML”

AGC det.

S-meter signal

Page 10

3 - 4

3-1-14 AF SELECTOR SWITCH (MAIN BOARD)

The AF signals from one of the detector circuits are applied

to the AF selector switch (IC861). IC861 consists of dual 4channel analog switches which are selected with a mode

signal and the squelch control signal.

3-1-15 AF AMPLIFIER CIRCUIT (PLL UNIT)

The AF amplifier amplifies the demodulated signal to a suitable driving level for the speaker.

The AF signals from the AF selector switch (MAIN board;

IC861) are applied to the PLL unit via the “AFI” signal line.

The CW side tone/beep tone and optional synthesized voice

are also applied to the PLL unit via the “AFBP” signal line.

The AF signals from the MAIN board are applied to the VCA

(Voltage Controlled Amplifier) circuit (IC201). The AF gain

setting from the main CPU is converted to DC voltage at the

D/A converter (MAIN board IC2201) and applied to the VCA

control terminal (IC201, pin 8) via the “AFGC” signal line.

The output AF signal from IC201 (pin 9) is power-amplified

at IC231 to drive the speaker.

3-2 TRANSMITTER CIRCUITS

3-2-1 MICROPHONE AMPLIFIER CIRCUIT

(MAIN BOARD)

The microphone amplifier circuit amplifies microphone input

signals and outputs the amplified signals to the balanced

modulator or FM modulation circuit.

Audio signals from the front or rear panel [MIC] connector

enter the microphone amplifier IC (IC931, pin 22) and are

then amplified at the microphone amplifier or speech compressor section. Compression level is adjusted with the

[COMP GAIN] control (R945).

The amplified or compressed signals are applied to the VCA

section of IC931. The microphone gain setting from the D/A

converter (IC2201, pin 2) is applied to the VCA control terminal (IC931, pin 10). The resulting signals from pin 9 are

then applied to the buffer amplifier (Q961) via the analog

switch (IC1141). External modulation input from the [ACC]

socket (pin 11) is also applied to Q961.

While in SSB mode, the amplified signals from the buffer

amplifier (Q961) are passed through the AF selector switch

(IC971) and are then applied to the balanced modulator

(IC1041).

While in AM/FM mode, the amplified signals from the buffer

amplifier (Q961) are applied to the limiter amplifier (IC981a)

and splatter filter (IC981b). The signals are then applied to

the AF selector switch (IC971) in AM mode or to the varactor diode (D1012) in FM mode.

3-2-2 VOX CIRCUIT (MAIN BOARD)

The VOX (Voice-Operated-Transmission) circuit sets transmitting conditions according to voice input.

When the VOX function is activated, the microphone signals

from IC931 (pin 19) are applied to the VOX comparator section in the main CPU (IC2001, pin 32) via the VOXL line.

A portion of the power amplified AF signals from the AF

power amplifier (PLL unit; IC231) are amplified at the buffer

amplifier (IC931, pins 14, 15) and applied to the anti-VOX

comparator section in the main CPU (IC2001, pin 33) via the

AVXLline.

Then the main CPU compares these and controls the transmitter circuit.

3-2-3 BALANCED MODULATOR (MAIN BOARD)

The balanced modulator converts the AF signals from the

microphone amplifier to a 9 MHz IF signal with a BFO (Beat

Frequency Oscillator) signal.

Microphone signals from the AF selector switch (IC971) are

applied to the balanced modulator (IC1041, pin 1). The BFO

signal from the PLL unit is applied to IC1041 (pin 10) as a

carrier signal.

IC1041 is a double balanced mixer IC and outputs a double

side band (DSB) signal with –40 dB of carrier suppression.

R1045 adjusts the balanced level of IC1041 for maximum

carrier suppression. The resulting signal passes through a 9

MHz IF filter (FI671 in SSB/CW/RTTY modes) to suppress

unwanted side-band signals.

In AM mode, R1042 is connected to upset the balance of

IC1041 via Q1041 for leaking the BFO signal as a carrier

signal. The CW keying/RTTY TX signal is applied to IC1041

pin 1.

• AF selector switch

11

13

INH

15

12

9, 10

14

X3

X2

X0

X

X1

SSB/CW/

RTTY

IC861

FM

WFM

AM

6

AFS1, AFS2

SQL

AFI signal

to PLL unit

• Microphone amplifier

11 2, 3 10

19

22

9

1415

MIC

signal

IC931

[

COMP GAIN

]

(R945)

MIGV from D/A

convertor (IC35)

VOXL

to CPU

AVOXL

to CPU

AFO signal

Amp.

COMP

Buffer

Buffer

Buffer

COMS

from CPU

AMOD

to IC1141

VCA

Buffer

Page 11

3 - 5

3-2-4 FM MODULATION CIRCUIT (MAIN BOARD)

The microphone signals from Q961 are applied to the limiter

amplifier (IC981a) and the splatter filter (IC981b). The 1750

Hz European tone signal from the main CPU (IC2001 pin

40) is also applied to IC981a pin 2 for European repeaters.

The sub-audible tone signal (67.0–254.1 Hz) from the main

CPU (IC2001 pin 37) is also applied to IC981b pin 5 for

repeater use.

The resulting signals are applied to the VCO circuit (Q1011,

D1012) via R1002 to change the reactance of the varactor

diode (D1012) for FM modulation. The modulated signal is

amplified at the buffer amplifier (Q1013) and bypasses the 9

MHz IF filter.

3-2-5 TRANSMITTER IF CIRCUIT (MAIN BOARD)

The 9 MHz IF signal from the modulation circuit passes

through the 9 MHz IF filter (FI671 in SSB/CW/RTTY modes;

FI681 in AM/FM-N modes; through in FM mode). The signal

is amplified at IC571, and then passes through the total gain

adjustment volume (R579), and the crystal filter (FI561). The

signal is then applied to the 2nd mixer (D551).

The signal is mixed with the 2nd LO signal (60 MHz) and

converted to a 69 MHz IF signal at the 2nd mixer (D551).

The 69 MHz IF signal passes through a bandpass filter, IF

amplifier (IC521) and 69 MHz IF filter (FI511), and is then

converted to the displayed frequency at the 1st mixer (D271)

with the 1st LO signal. The mixers (D271, D551) and IF

amplifiers (IC521, IC571) are used commonly for both

receiving and transmitting.

The ALC voltage is supplied to the transmit/receive switching circuit (D521/D522 and D572/D573). D521/D522 and

D572/D573 function as PIN attenuators for ALC operation.

3-2-6 RF CIRCUIT

(PA UNIT, MAIN AND HPF BOARD)

The RF circuit amplifies the displayed frequency signal to

obtain 100 W of RF output power for HF/50 MHz bands and

50 W for the 144 MHz band, 20 W for the 440 MHz band.

The HF/50 MHz RF signals from the 1st mixer (D271) via the

low-pass filter enter the HPF board and then pass through

one of 8 high-pass filters (Refer to 3-1 for used RF high-pass

filter). The 50 MHz RF signals pass through a low-pass filter

additionally. The filtered signals return to the MAIN board,

are amplified at the YGR amplifier (IC231), and are then

applied to the PAunit.

The 144 MHz RF signals from the 1st mixer (D271) via the

low-pass filter (L251–253, C253–259) bypass the filters and

pass through the bandpass filter (L182–L184, L195, L196,

C181–C186, C195–C197) in the MAIN board. The signals

are amplified at the RF amplifier (IC221) and YGR amplifer

(IC231) and are then applied to the PAunit.

The 440 MHz RF signals from the 1st mixer (D271) via the

low-pass filter (L251–253, C253–259) are amplified at RF

amplifier (IC222) and passed through the bandpass filter

(FI371–FI373) in the MAIN board. The filtered signal is

amplified at the YGR amplifer (IC231) and is applied to the

PA unit.

The signals from IC231 enter the PA unit and is amplified at

the drive amplifiers (Q101, Q121) in sequence. The amplified signals are applied to the band switch (RL1).

The HF/50 MHz RF signals from the band switch (RL1) are

amplified at the drive (DRIVER board; Q161) and power

(Q171, Q172) amplifiers to obtain a stable 100 W of RF output power. The power-amplified signals are then applied to

the [ANT1] connector via one of the 7 low-pass filters in the

FILTER board.

For the 144/440 MHz RF signals from the band switch

(RL1), 50 W for 144 MHz band or 20 W for 440 MHz band

of RF output power is obtained at the drive (DRIVER board;

Q211) and power amplifier (Q231). The power-amplified signals are applied to the [ANT2] connector via the antenna

switching circuit and low-pass (144 MHz band) or high pass

(440 MHz band) filters.

3-2-7 ALC CIRCUIT (MAIN BOARD)

The ALC (Automatic Level Control) circuit reduces the gain

of IF amplifiers in order for the transceiver to output a constant RF power set by the RF power setting even when the

supplied voltage shifts, etc.

The HF/50 MHz RF power signal level is detected at the

power detector (FIL TER board; D9), buffer-amplified at IC1b

and applied to the MAIN board as the “HFOR” voltage.

The 144 MHz and 440 MHz RF power signals are detected

at the power detectors (PA unit; D262, D263) and (PA unit;

D312, D313) respectively. The detected signals are applied

to the MAIN board as the “VFOR” or “UFOR” voltages.

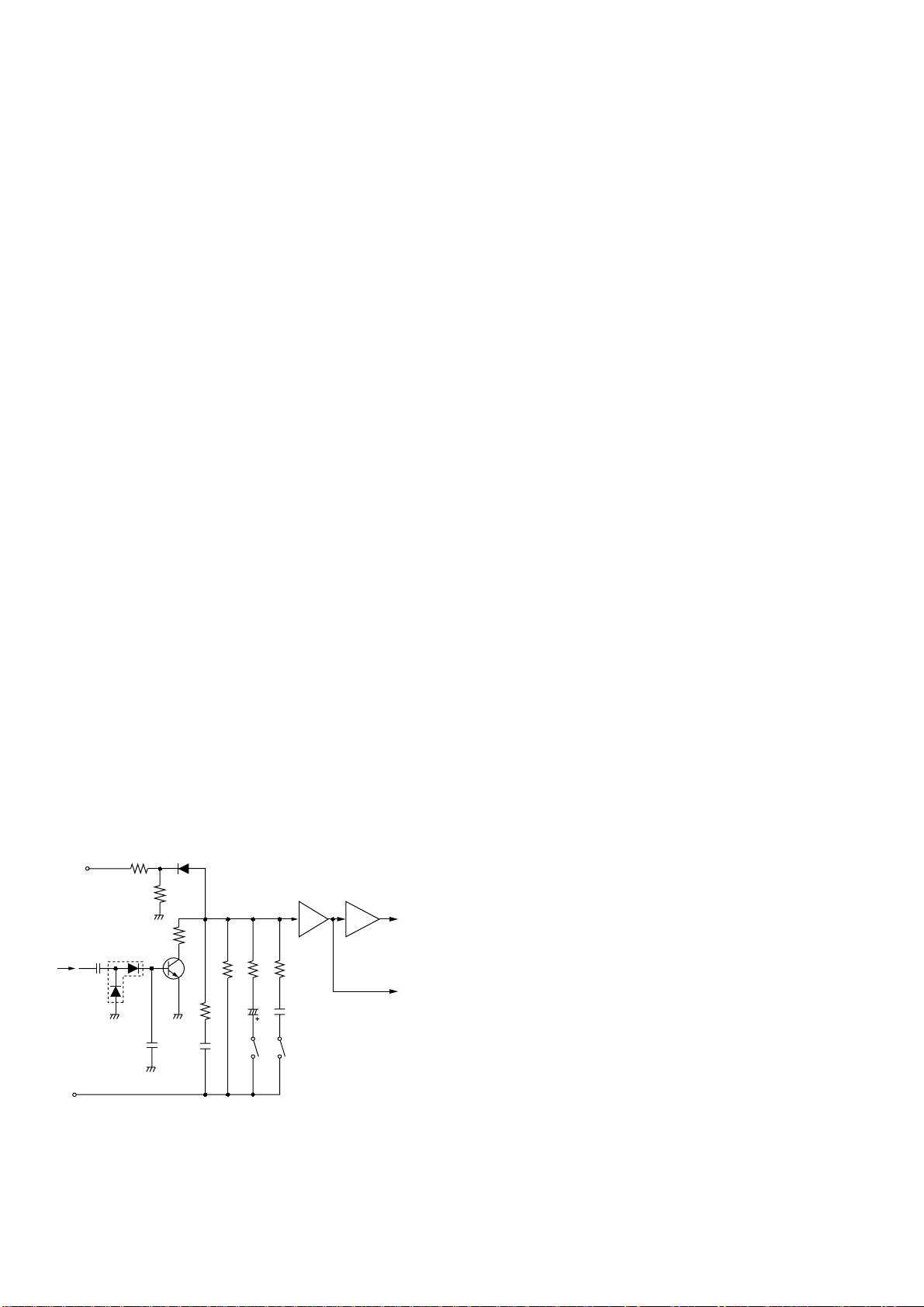

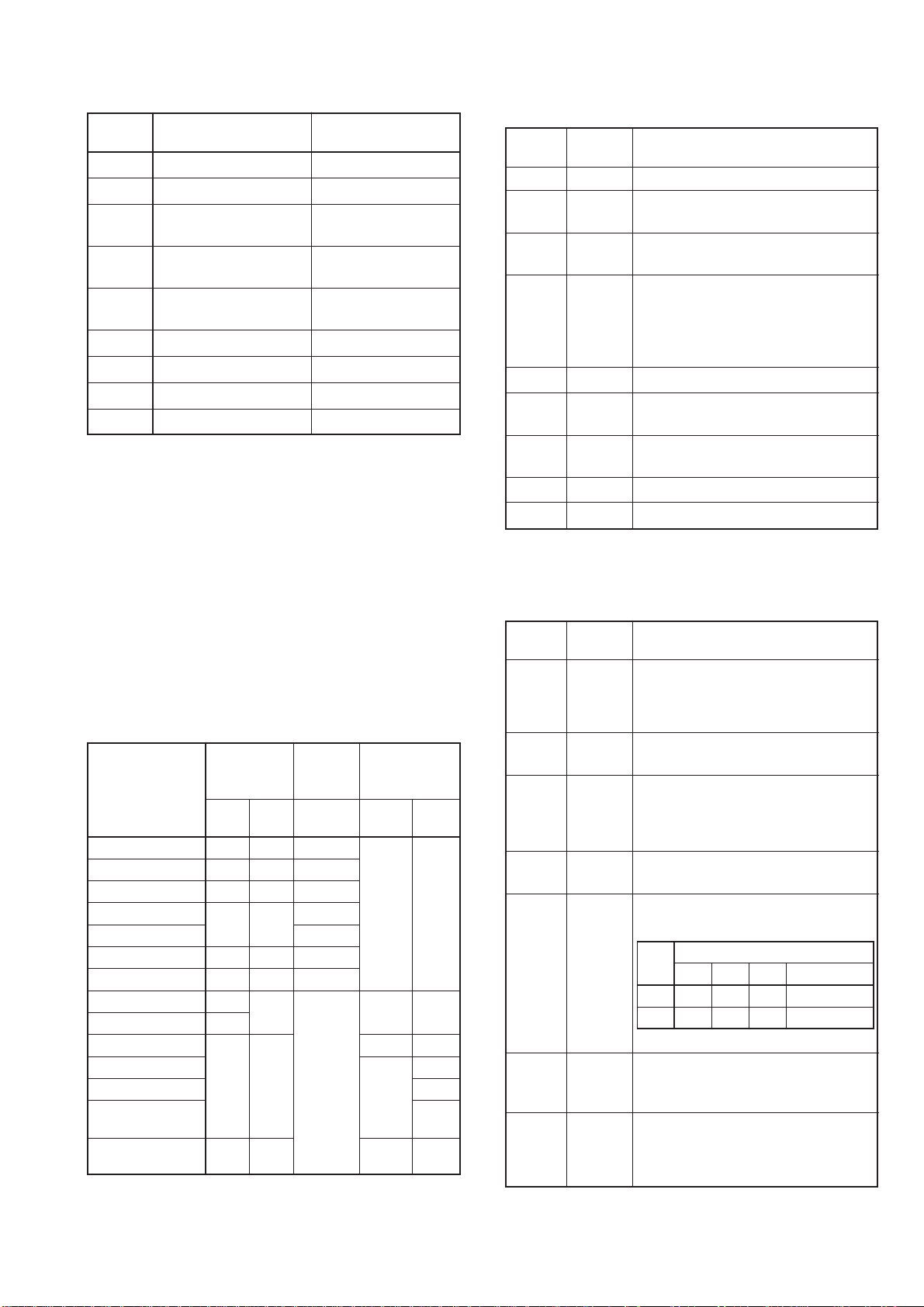

• TRANSMITTER CONSTRUCTION

1st LO

60.0 MHz

BFO

FM tone

D551

IC231

[ANT1]

HF+50 MHz

[ANT2]

144/440 MHz

144 MHz

440 MHz

Q101

Q121

Q171

Q172

Q231

Q1011

D231

IC1041

IC931

Crystal

filter

FI1

FI671, FI681,

or optional filter

MIC

except FM

9.0115 MHz

Crystal

filter

BPF

BPF

LPF

LPF

HPF

BPF

HPF

HPF

PA UNIT

HPF

BOARD

FILTER

BOARD

MAIN BOARD

Amp. Amp. Amp.

Amp.

Q161

Amp.

Amp.

Q211

Amp.

IDC

FM, AM

AM

FM

FM only

50 MHz

144 MHz

SSB

•

•

•

BPF

440 MHz

Page 12

3 - 6

The “FOR”, “VFOR” and “UFOR” voltages are combined to

the “FORL” voltage and then applied to IC1091b (pin 6). The

“POCV” voltage from the D/A converter (IC2201, pin 3),

determined by the RF power setting, is applied to IC1091b

(pin 5) as the reference voltage.

When the “FORL” voltage exceeds the “POCV” voltage, ALC

bias voltage from IC1091a (pin 1) controls the PIN diodes

(D521, D522, D572, D573) using Q1092. This adjusts the

output power to the level determined by the RF power setting until the “FORL” and “POCV” voltages are equalized.

In AM mode, IC1091a operates as an averaging ALC amplifier with Q1091 and C1091. Q1071 turns ON and the

“POCV” voltage is shifted for 40 W AM output power (maximum, 20 W for 144 MHz band, 8 W for 440 MHz band)

through R1080.

The ALC bias voltage from IC1091a is also applied to the

main CPU (IC2001 pin 34) as the “ALCL” voltage for ALC

meter indication.

An external ALC input (minus voltage) from the [ACC] socket (pin 6) is shifted to plus voltage at D1131 and is applied

to the buffer amplifier (Q1131). External ALC operation is

identical to that of the internal ALC.

3-2-8 APC CIRCUIT (MAIN BOARD)

The APC (Automatic Power Control) circuit protects the

power amplifiers on the PAunit from high SWR and excessive current for the HF/50 MHz band.

The reflected wave signal appears and increases on the

antenna connector when the antenna is mismatched. The

HF/50 MHz reflected signal level is detected at D10 (FILTER

board), and is amplified at the APC amplifier (IC1091c) and

applied to the ALC circuit as the reference voltage.

For the current APC, the driving current at the power amplifier is detected in the voltages (“ICH” and “ICL”) which

appear at both terminals of a 0.012 Ω resistor (R201) on the

PAunit. The detected voltages are applied to the differential

amplifier (IC1091d, pins 13, 12). When the current of the

power amplifier exceeds 22 A, IC1091d controls the ALC

line via IC1091a to prevent excessive current flow.

3-2-9 RF, ALC, SWR METER CIRCUITS

(MAIN BOARD)

While transmitting, RF, ALC or SWR meter readings are

available and can be selected with the [MET] switch.

(1) Power meter

The “FOR”, “VFOR” and “UFOR” voltages are combined to

the “FORL” voltage, and it is then applied to the main CPU

(IC2001, pin 35) via the analog switch (IC2101, pins 11, 13)

for indicating the output power.

(2) ALC meter

The ALC bias voltage from IC1091a pin 1 is applied to the

main CPU (IC2001, pin 34) via the “ALCV” signal line for

indicating the ALC level.

(3) SWR meter

The “FORL” and “REFL” voltages are applied to the main

CPU (IC2001, pins 32 and 36) via the analog switch

(IC2101, pins 11, 13 and 4, 3) respectively. The main CPU

compares the ratio of “FORV” to “REFV” voltage and indicates the SWR for the [ANT1] connector.

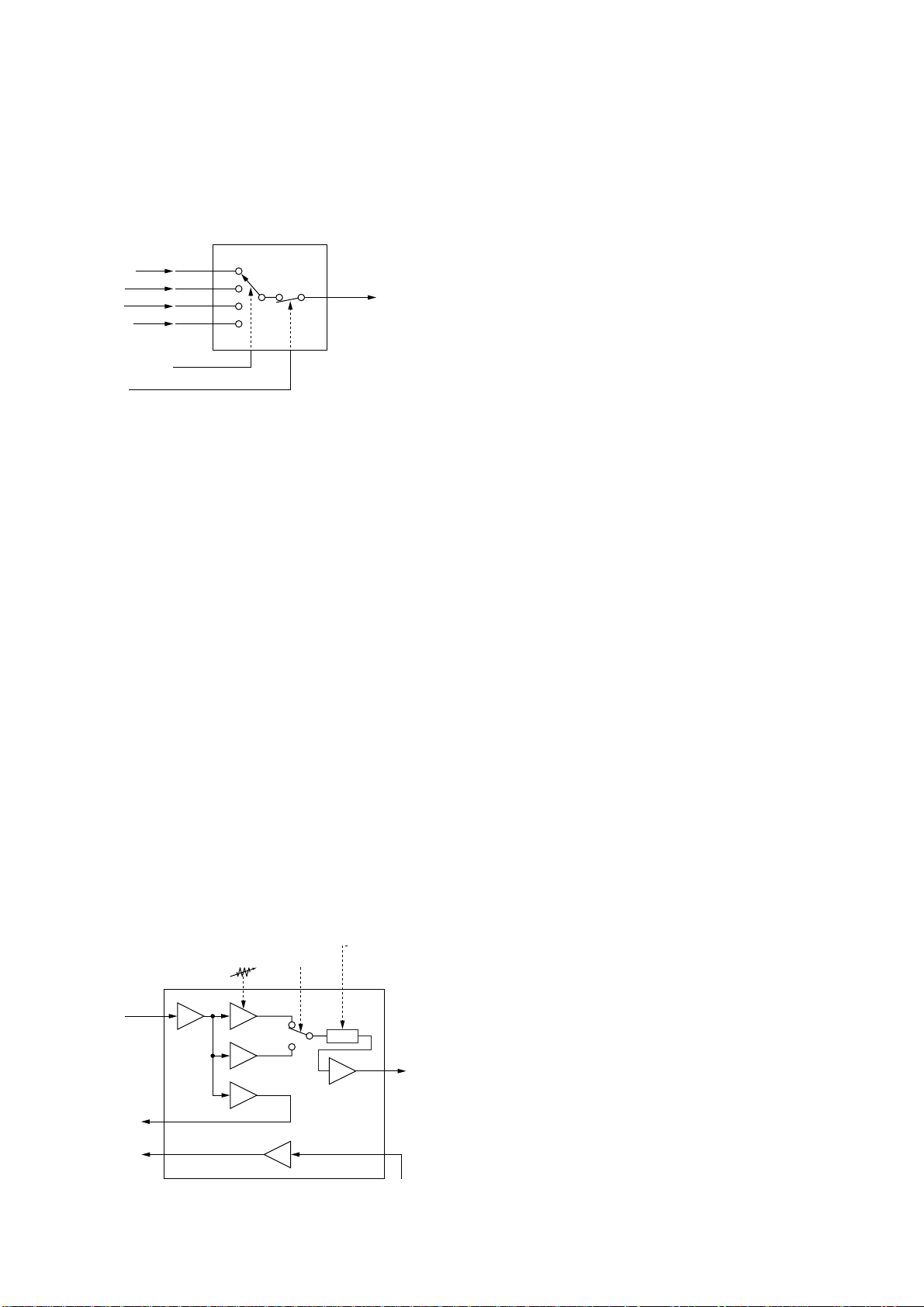

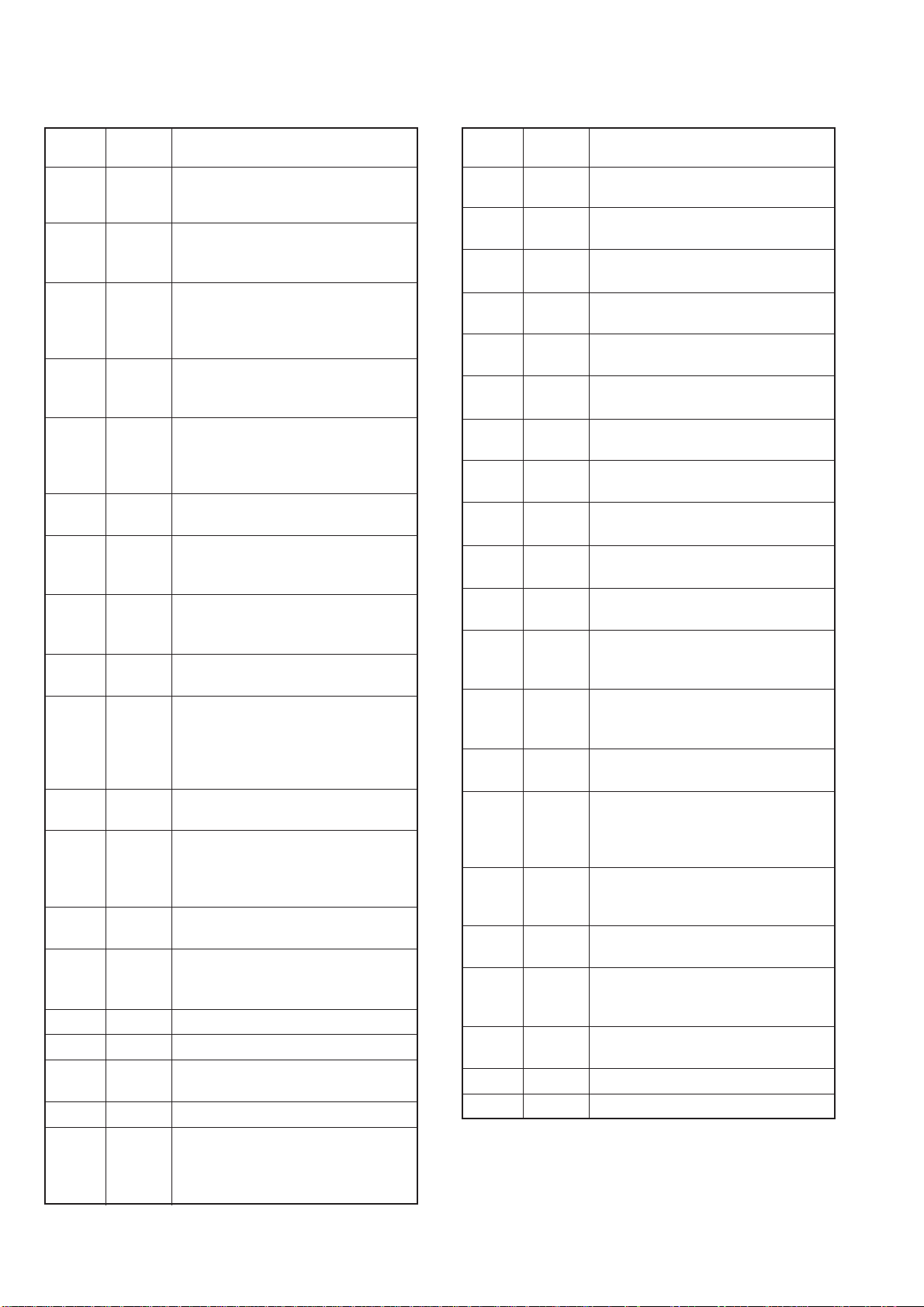

3-3 PLL CIRCUITS

3-3-1 GENERAL

The PLL unit generates a 1st LO frequency

(69.0415–530.0115 MHz), a 2nd LO frequency (60 MHz), a

BFO frequency (9.01 MHz), an FM 3rd LO frequency

(9.4665/9.4650 MHz) and a TX FM PLL reference frequency (9.0115/9.0100 MHz).

The 1st LO PLL adopts a mixer-less dual loop PLL system

and has 3 VCO circuits. The BFO uses a DDS and the 2nd

LO uses a fixed frequency double that of the crystal oscillator.

3-3-2 1ST LO PLL CIRCUIT

The 1st LO PLL contains a main loop and reference loop

forming a dual loop system.

The reference loop generates a 10.6605 to 10.683 MHz frequency using a DDS circuit, and the main loop generates a

69.0415 to 269.50575 MHz frequency using the reference

loop frequency.

While operating on 60 MHz and above, the output is doubled

at D531 for oscillating a wide frequency range.

(1) REFERENCE LOOP PLL

The oscillated signal at the reference VCO (Q1, D1) is

amplified at the amplifiers (Q21, Q51) and is then applied to

the DDS IC (IC101, pin 46). The signal is then divided and

detected on phase with the DDS generated frequency.

The detected signals output from IC101 (pin 56) is converted into a DC voltage (lock voltage) at the loop filter (R133,

R134, C133) and then fed back to the varactor diode (D1) in

the VCO circuit.

(2) MAIN LOOP PLL

The oscillated signal at one of the main loop VCOs (Q301,

Q331, Q361) is amplified at the buffer amplifiers (Q10) and

is then applied to the PLL IC (IC461, pin 6). The signal is

then divided and detected on phase with the reference loop

output frequency.

The detected signal output from the PLL IC (IC461, pin 2) is

converted into a DC voltage (lock voltage) at the active loop

filter and then fed back to one of the varactor diodes (D301,

D331, D361) in the VCO circuits. While operating on 60 MHz

and above, the VCO output is doubled at the doubler circuit

(D531) and amplified at the ampolifier (IC541).

The oscillated signal passes through a low-pass or bandpass filter and is then applied to the MAIN board as a 1st LO

signal.

Page 13

3 - 7

3-3-3 2ND LO AND REFERENCE OSCILLATOR

CIRCUITS

The reference oscillator (X621, Q621) generates a 30.0

MHz frequency used for the 1st LO and BFO circuits as a

system clock and for the 2nd LO signal.

The oscillated signal is amplified at the buffer amplifier

(Q661), and is doubled at Q681 and the 60 MHz frequency

is picked up at the bandpass filter (L681, L682). The 60 MHz

signal is applied to the MAIN board as a 2nd LO signal.

3-3-4 BFO CIRCUIT

The DDS IC (IC901) generates a 10-bit digital signal. The

signal is converted into an analog wave signal at the D/A

converter (R951–R970). The analog wave is passed

through the high-pass filter and low-pass filter. The 9 MHz

BFO signal is then applied to the MAIN board via the “BFO”

signal line.

While transmitting in RTTY mode, the RTTY keying signal is

applied to IC901 pin 3 to shift the generated frequency and

to obtain 2 frequencies for FSK operation.

While receiving in FM or FM narrow mode, the BFO circuit

generates a 9.4665 MHz frequency as the 3rd LO signal.

While transmitting in FM or FM narrow mode, the BFO circuit generates a 9.0115 MHz or 9.0100 MHz frequency as

the TX FM PLL reference frequency, respectively.

69.0415–

539.0115 MHz

(1st LO)

10.665–

10.683 MHz

129.0115–

539.0115 MHz

69.0415–

129.0115 MHz

60.0 MHz

(2nd LO)

[ANT1] [ANT2]

1st mixer

D271

0.03–

60 MHz

60–

470 MHz

9.01 MHz

(BFO)

9.4665 MHz (FM)

9.4650 MHz (FM nar.)

9.0115 MHz (FM)

9.0100 MHz (FM nar.)

to FM IF IC

(IC791)

to TX FM

PLL IC

(IC1011)

IC901

IC101

IC461

Q681

PLL UNIT

MAIN BOARD

Q301

Q331

Q361

Q1

Phase

detector

1

⁄N divider

1

⁄

86

Phase

detector

Main loop PLL

Ref. loop PLL

DDS

2

2

DDS

D/A

BPF

BPF

2nd mixer

D551

Product

detector

IC841

69.0115 MHz

(WFM: 70.7 MHz)

to AF selector switch

Ref. Osc.

30.0 MHz

X621

BPF

1st IF 2nd IF

AF signals

Q621

to WFM detector

(IC631)

• FREQUENCY CONSTRUCTION

Page 14

• BFO frequency

IF shift: Center, RTTY: Normal polarity

3-4 LOGIC CIRCUITS

3-4-1 BAND SELECTION DATA

(MAIN BOARD AND PLL UNIT)

To select the correct RF low-pass filter, high-pass filter and

VCOs on the PLL unit, the CPU outputs the following band

selection data from the I/O expander (MAIN board; IC2231,

IC2232), the D/Aconverter (MAIN board; IC2201) or DDS IC

(PLL unit; IC101) depending on the display frequency.

The D/A convertor output from IC2201 (pin 18) is doubled at

IC891d to obtain the band voltage for external equipment.

• Band selection data

3-4-2 SUB CPU PORT ALLOCATIONS

(DISPLAY board; IC1)

3 - 8

USB

LSB

CW

CW-R

RTTY

AM

FM

FM nar.

WFM

9.0130

9.0100

9.0106

(–CW pitch frequency)

9.0106

(+CW pitch frequency)

9.008375 (2125 Hz tone)

9.008885 (1615 Hz tone)

No output

9.4665 (3rd LO)

9.4650 (3rd LO)

No output

9.0130

9.0100

9.0106

(–CW pitch frequency)

9.0106

(+CW pitch freqency)

9.0105 (MARK)

9.0100

9.0115 (PLLref.)

9.0100 (PLL ref.)

No output

Mode

RX BFO/3rd LO TX BFO/FM PLL ref.

frequency [MHz] frequency [MHz]

0.03– 1.999999

2.0– 3.999999

4.0– 7.999999

8.0– 10.999999

11.0– 14.999999

15.0– 21.999999

22.0– 29.999999

30.0– 39.999999

40.0– 59.999999

60.0–128.999999

129.0–143.999999

144.0–148.000000

148.000001–

199.999999

400.000000–

470.000000

IC2231,

IC2201 IC101

IC2232

(MAIN) (PLL)

Frequency (MAIN)

[MHz]

HPF LPF 1/2 band

VCO

LPF

BPF LPF voltage BPF

L1

L2

L3

L4

L5

L6

B7W

B7

B8

B9

L1

L2

L3

L4

L5

L6

L7

L8

B9

3.70 V

3.19 V

2.68 V

0 V

2.18 V

1.69 V

1.19 V

0.96 V

VCO1

VCO2

VCO1

VCO2

VCO3

LOF1

LOF2

LOF3

LOF4

LOF5

LOF4

LOF6

1

18

19, 20

80

81

96

97

98

99

Input port for the [SHIFT] control.

Outputs a PTT signal.

Low : While transmitting.

Outputs displaly backlight control signal.

Input port for the [PHONES] jack connection detection.

High : When the headphone or

external speaker is connected

to the [PHONES] jack.

Input port for the [RIT] switch.

Input port for the [PTT] switch on the

microphone.

Input port for the microphone up/down

signal.

Input port for the [AF] control.

Input port for the [RF/SQL] control.

SFTL

PTTS

BU1S,

BU2S

PHNK

RSK

PTTL

FUDL

AFGL

SQLL

Pin Port

Description

number name

3-4-3 I/O EXPANDER PORT ALLOCATIONS

(MAIN board; IC2221)

4

5

6

7

11, 12

13

14

Outputs select signal for the Tx AF

selector switch (IC1141).

Hign : When AM and SSB modes

are selected.

Outputs AM mode select signal.

High : When AM mode is selected.

Outputs FM and FM-N modes select

signal.

High : When FM and FM-N modes

are selected.

Outputs WFM mode select signal.

High : When WFM mode is selected.

Output select signals for the Rx AF

selector switch (IC861).

Outputs non-FM mode select signal.

High : When SSB/CW/RTTY/AM

modes are selected.

Outputs an audio mute signal for the

analog switch (IC971).

High : While transmitting in

CW/RTTY modes.

MODS

AMS

FMS

WFMS

AFS1,

AFS2

UNFM

MINH

Pin Port

Description

number name

PORT

MODE

WFM FM AM SSB/CW/RTTY

AFS1 High High Low Low

AFS2 High High Low Low

Page 15

40

41

42

43

44

45

46

48

49–51

52

53

54

55

61

62

63

71

74

75

78

79

Outputs 1750 Hz European tone signal.

Outputs a strobe signal for the optional UT-102 (Voice synthesizer unit).

Outputs serial data for the I/O

expanders, optional AT-180/UT-102.

Outputs a clock signal for the I/O

expanders, optional AT-180/ UT-102.

Outputs a strobe signal for the I/O

expander ICs (IC2231, IC2232).

Outputs a strobe signal for the I/O

expander ICs (IC2221, IC2222).

Outputs a strobe signal for the D/A

converter IC (IC2201).

Outputs a strobe signal for the BFO

DDS IC (PLL unit; IC901).

Output mode control signals for the 1st

LO DDS IC (PLL unit; IC101).

Outputs a strobe signal for the 1st LO

DDS IC (PLL unit; IC101).

Outputs a strobe signal for the 1st LO

PLL IC (PLL unit; IC461).

Outputs serial data for the DDS ICs

(PLL unit; IC101, IC901) and PLL IC

(PLL unit; IC461).

Outputs a clock signal for the DDS ICs

(PLL unit; IC101, IC901) and PLL IC

(PLL unit; IC461).

Outputs AGC rate select signal

Low : When AGC fast is selected.

Outputs the NB switch (Q635) control

slignal.

High : When the [NB] is turned ON,

except FM/WFM modes.

Outputs the attenuator circuit control

slignal.

High : When the [ATT] is turned ON.

Outputs a strobe signal for the TX FM

PLL IC (IC1011).

Input port for transmit/receive switching signals for the [ACC] connector.

Low : While transmitting.

Outputs a CW keying signal or RTTY

TX signal.

Output port for CI-V bus line.

Input port for CI-V bus line.

3 - 9

ETON

MSST

MDT

MCK

BSTB

DSST

ASTB

PBST

CON2–

CON0

PDST

PMST

PDT

PCK

AFGS

NBS

ATTS

FMST

SNDS

KDS

LTXD

LRXD

(MAIN unit; IC2001)–Continued

Pin Port

Description

number name

13

14

15

16

17

18

19

20

21

22

23

24

30

31

32

33

34

37

39

Input port for the external paddle

(DASH).

Low : During key down

Input port for the external paddle

(DOT) or straight key.

Low : During key down

Input port for the PLL unlock signal

from the DDS IC (PLL unit; IC101) and

PLL IC (PLL unit; IC461).

Low : while PLL unlock

Input port for transmit control signal

from the optional AT-180/AH-4 antenna tuners.

Input port for the optional antenna

tuner connection detection.

High : When the optional antenna

tuner is connected.

Outputs a squelch control signal for

the external unit.

Input port for the [POWER] switch.

Low : When the [POWER] switch is

pushed.

Outputs the switching relay (PA unit;

RL591) control signal.

High : While power is ON.

Outputs start signal for the optional

AT-180 antenna tuner.

Output port

: Beep audio signals while

receiving.

: CW side tone signals while

transmitting.

Outputs start signal for the optional

AH-4

Outputs squelch mute control signal,

applied to the AF mute switch (MAIN

board; Q772).

Low : While squelch is closed.

Input port for the CTCSS decode signal from the low-pass filter (IC811C).

Input port from the [RTTY] or [MIC]

connector.

High : While transmitting.

Input port for the VOX voltage.

Input port for the anti-VOX voltage.

ALC level input port for the ALC meter

indication.

Outputs subaudible tone signals.

Input port for the optional UT-102

(Voice synthesizer unit) activation signal.

High : During speech synthesis.

3-4-4 MAIN CPU PORT ALLOCATIONS

(MAIN unit; IC2001)

DASK

DOTK

UNLK

TKEY

TCON

SQSS

PWK

POWS

ATST

BEEP

AHST

AFMS

CTCV

SNDL

VOXL

AVXL

ALCV

TONE

SPBK

Pin Port

Description

number name

Page 16

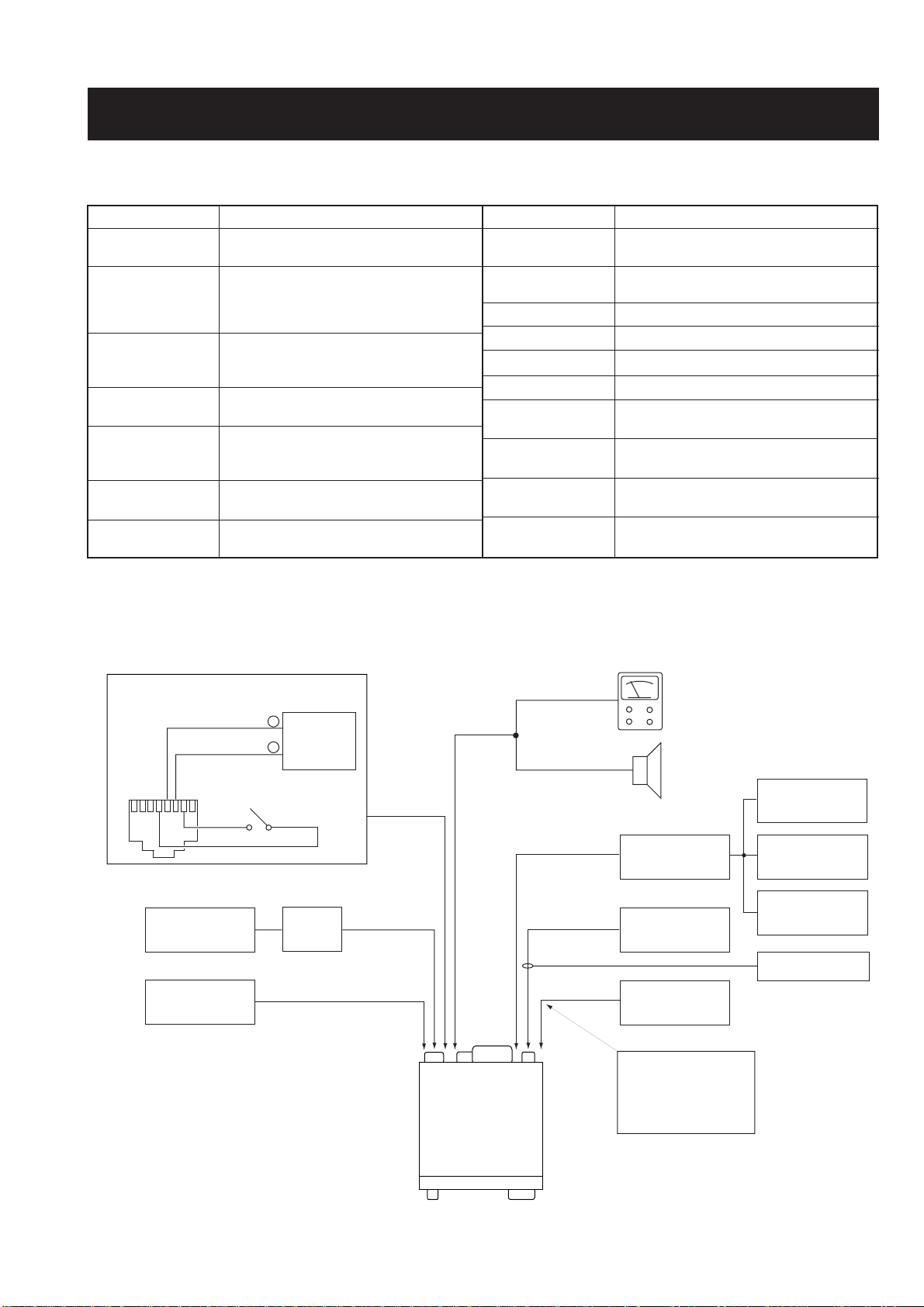

4-1 PREPARATION BEFORE SARVICING

■ REQUIRED TEST EQUIPMENT

DC power supply

RF power meter

(terminated type)

Frequency counter

RF voltmeter

Standard signal

generator (SSG)

FM deviation meter

Modulation analyzer

Distortion meter

Oscilloscope

Digital multimeter

AC millivoltmeter

DC voltmeter

DC ammeter

Audio generator

Spectram analyzer

Attenuator

External speaker

EQUIPMENT GREDE AND RANGE EQUIPMENT GREDE AND RENGE

4 - 1

SECTION 4 ADJUSTMENT PROCEDURES

Output voltage : 13.8 V DC

Current capacity : 30 A or more

Measuring range : 10–200 W

Frequency range : 1.8–500 MHz

Impedance : 50 Ω

SWR : Less than 1.2 : 1

Frequency range : 0.1–500 MHz

Frequency accuracy : ±1 ppm or better

Sensitivity : 100 mV or better

Frequency range : 0.1–500 MHz

Measuring range : 0.01–10 V

Frequency range : 0.1–30 MHz

Output level : 0.1 µV–32 mV

(–127 to –17 dBm)

Frequency range : 0–500 MHz

Measuring range : 0 to ±5 kHz

Frequency range : At least 500 MHz

Measuring range : 0–100 %

Frequency range : 1 kHz ±10 %

Measuring range : 1–100 %

Frequency range : DC–100 MHz

Measuring range : 0.01–10 V

Imput impeadance : 10 MΩ/DC or beter

Measuring range : 10 mV–10 V

Input impedance :

50 kΩ/V DC or better

Measurement capability: 1 A/50 A

Frequency range : 300–3000 Hz

Measuring range : 1–500 mV

Frequency range : At least 1000 MHz

Spectraum bandwidth : 100 kHz or more

Power attenuation : 50 or 60 dB

Capacity : 150 W or more

Input impedance : 8 Ω

Capacity : 5 W or more

‘‘

CONNECTIONS

Attenuator

50 or 60 dB

Audio

generator

RF power meter

A200 W/50 Ω

DC power supply

AA13.8 V/30 A

Standard signal

aagenerator

FM deviation

AAmeter

Spectrum

analyzer

AC

millivoltmeter

Modulation

aanalyzer

CAUTION:

DO NOT connect the

signal generator while

transmitting.

Speaker

to [EXT SP]

i706MKIIG

to [MIC]

to [DC 13.8 V]

to [ELEC KEY]

to [ANT 1/2]

Keyer

• Microphone connector

• (Rear panel view)

Frequency counter

AM meter

1 A, 30 A

Pin 5

MIC GND

Pin 6

MIC INPUT

–

+

Pin 4

PTT

18

Pin 7

GND

Page 17

4-2 PLL ADJUSTMENTS

4 - 2

REFERENCE

FREQUENCY

REFERENCE

LOOP LOCK

VOLTAGE

MAIN LOOP

LOCK

VOLTAGE

ADJUSTMENT

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

POINT

UNIT LOCATION UNIT ADJUST

1

2

1

1

2

3

• Display frequency: Any

• L623 (PLL unit) : Center

• Receiving

• Display frequency: 0.0300 MHz

• Mode : USB

• Receiving

• Display frequency

: 128.99999 MHz

• Mode : USB

• Receiving

• Display frequency

: 199.99999 MHz

• Mode : USB

• Receiving

• Display frequency

: 470.00000 MHz

• Mode : USB

• Receiving

PLL

PLL

PLL

Connect an RF voltmeter to check point

P681.

Connect a frequency

counter to check

point P681.

Connect a digital

multimeter or oscilloscope to check point

CP131.

Connect a digital

multimeter or oscilloscope to check point

CP401.

Maximum level

(0 dB or more)

60.000000 MHz

2.0 V

4.0 V

4.0 V

4.0 V

PLL

PLL

PLL

L681,

L682

L601

L623

R602

C4

C306

C335

C367

4-3 TRANSMITTER ADJUSTMENTS

TRANSMIT

TOTAL GAIN

OUTPUT

POWER

CARRIER

SUPPRESSION

ADJUSTMENT

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

POINT

UNIT LOCATION UNIT ADJUST

1

2

1

2

3

4

1

• Display frequency: 14.10000 MHz

• Mode : USB

• [Q1 RF POWER] : H

• Connect an audio generator to

[MIC] connector and set as:

1.5 kHz/3 mV

• Transmitting

• Transmitting

• Display frequency: 14.10000 MHz

• Mode : USB

• [Q2 MIC GAIN] : 5

• Connect an audio generator to

[MIC] connector and set as:

1.5 kHz/30 mV

• Transmitting

• Display frequency

: 52.00000 MHz

• Transmitting

• Display frequency

: 145.00000 MHz

• Transmitting

• Display frequency

: 435.00000 MHz

• Transmitting

• Display frequency

: 14.10000 MHz

• Mode : USB and LSB

• Apply no signal to [MIC] connector.

• Transmitting

Rear

Panel

Rear

Panel

Rear

Panel

Connect an RF

power meter to

[ANT1] connector.

Connect an RF

power meter to

[ANT1] connector.

Connect an RF

power meter to

[ANT2] connector.

Connect a spectrum

analyzer to [ANT1]

connector via an

attenuator.

Maximum RF power

50 W

100 W

100 W

50 W

20 W

Minimum carrier level

MAIN

MAIN

MAIN

L511,

L512,

L562,

L563,

L566

R579

R1082

R1084

R1086

R1088

R1045

Page 18

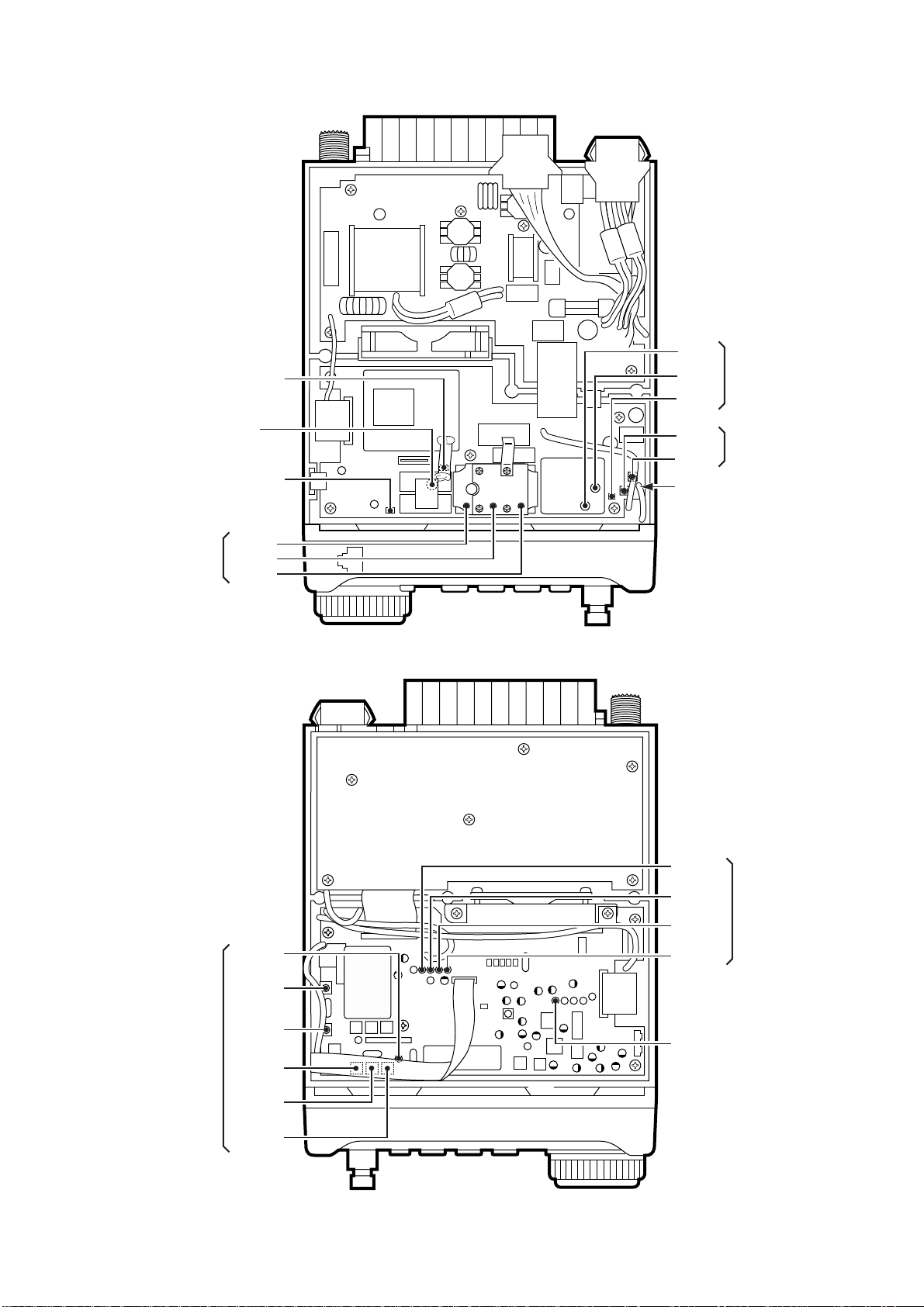

4 - 3

• MAIN UNIT

• PLL AND PA UNITS

CP131

CP401

Reference loop lock

voltage check point

Reference frequency

adjustment

C4

P681

L682

L681

C335

C306

C367

Main loop lock

voltage adjustment

Main loop lock

voltage check point

Reference loop lock

voltage adjustment

Reference frequency

check point

2nd LO level

adjustment

R1082

R1084

R1086

R1088

R1045

L511

L512

L562

L563

L566

R579

L623

R602

L601

Transmit total gain

Output power

adjustment

Carrier suppression

adjustment

Page 19

4 - 4

TRANSMITTER ADJUSTMENTS (continued)

FM VCO

FM

DEVIATION

RESIDUAL

AM

AM

MODULATION

CW

CARRIER

LEVEL

ADJUSTMENT

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

POINT

UNIT LOCATION UNIT ADJUST

1

1

1

2

1

2

3

1

• Display frequency: 29.10000 MHz

• Mode : FM

• [Q1 RF POWER] : H

• [M4 TON] : OFF

• Apply no signal to [MIC] connector.

• Transmitting

• Display frequency: 29.10000 MHz

• Mode : FM

• [Q1 RF POWER] : H

• [M4 TON] : OFF

• [Q2 MIC GAIN] : 5

• Connect an audio generator to

[MIC] connector and set as:

1 kHz/30 mV

• Transmitting

• Display frequency: 29.10000 MHz

• Mode : FM

• [Q1 RF POWER] : H

• [M4 TON] : OFF

• [Q2 MIC GAIN] : 5

• Connect an audio generator to

[MIC] connector and set as:

1 kHz/30 mV and OFF

• Transmitting

• Display frequency

: 14.10000 MHz

• Mode : AM

• [Q1 RF POWER] : H

• [Q2 MIC GAIN] : 5

• Disconnect the plug from J281 on

the MAIN board.

• Apply no signal to [MIC] connector.

• Transmitting

• Connect the plug to J281 on the

MAIN board.

• Apply no signal to [MIC] connector.

• Transmitting

• Connect an audio generator to

[MIC] connector and set as:

1 kHz/30 mV

• Transmitting

• Display frequency: 14.10000 MHz

• Mode : CW

• [Q1 RF POWER] : H

• [Q5 KEY SPEED]: 60

• [M4 BRK] : BK

(semi break-in)

• CW paddle : n

• Connect an RF power meter to

[ANT1] connector.

• Transmit dots for a while using a

paddle.

MAIN

Rear

Panel

MAIN

Rear

Panel

Connect a digital

multimeter to check

point CP1011.

Connect an FM deviation meter to [ANT1]

connector via an

attenuator.

Connect an RF

power meter to

[ANT1] connector.

Connect an osilloscope to check point

CP1041.

Connect an RF

power meter to

[ANT1] connector.

Connect a modulation analyzer to

[ANT1] connector via

an attenuator.

Connect an osilloscope to check point

CP921 and [ANT1]

connector.

1.8 V

±4.5 kHz

Minimum power difference with modulation

and unmodulation.

100 mVp-p

35 W

90 % modulation

At the point where the

CW carrier completely

comes up in a 10

msec. delay after

CP921 voltage comes

up.

MAIN

MAIN

MAIN

MAIN

MAIN

C1022

R1002

adjust in

sequence

L511, L512,

then adjust

L562, L563,

L566.

R1042

R1080

R999

R921

After adjustment, varify the TRANSMIT TOTAL GAIN and OUTPUT POWER adjustments.

10 msec.

Keying (CP921)

Page 20

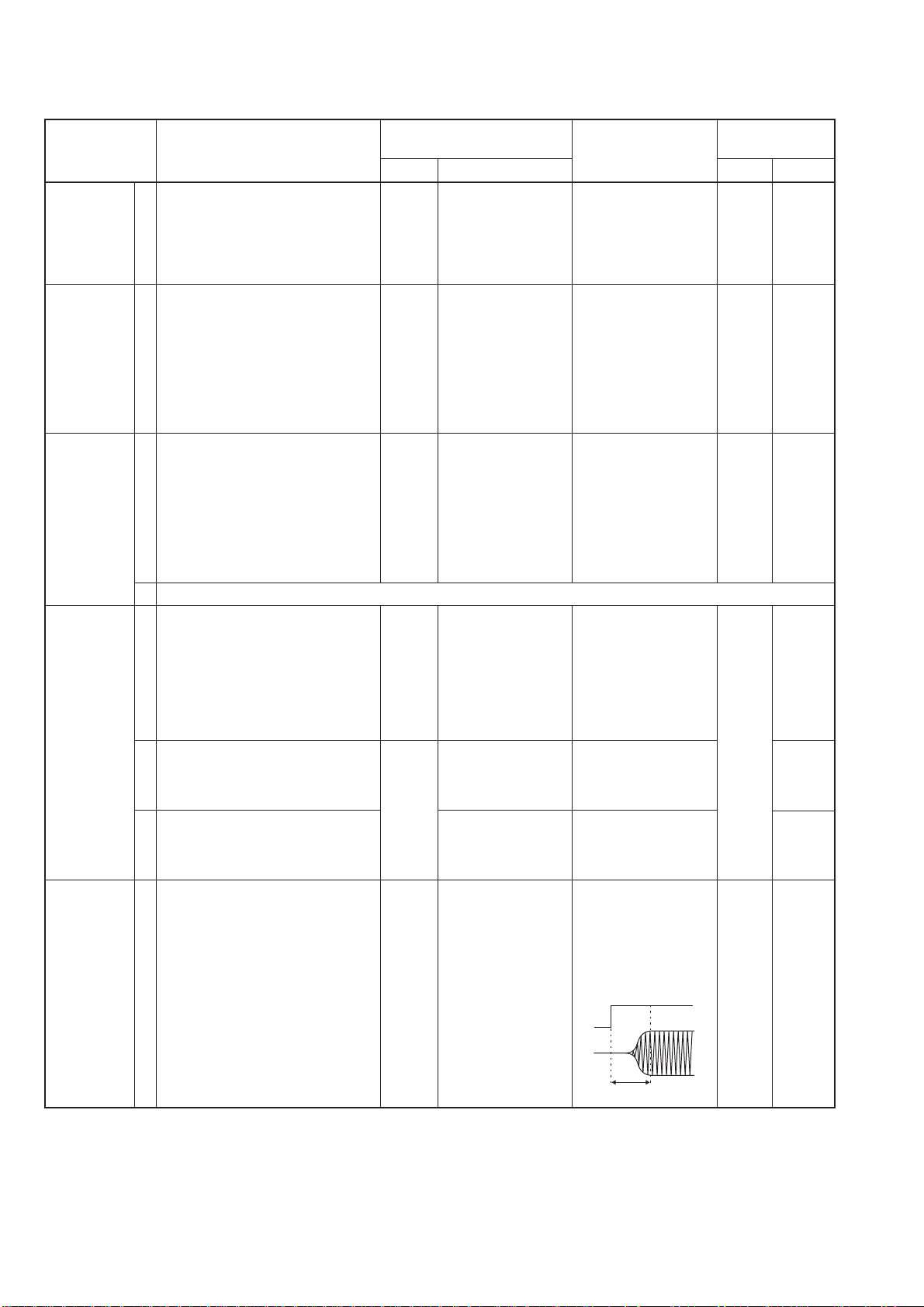

4 - 5

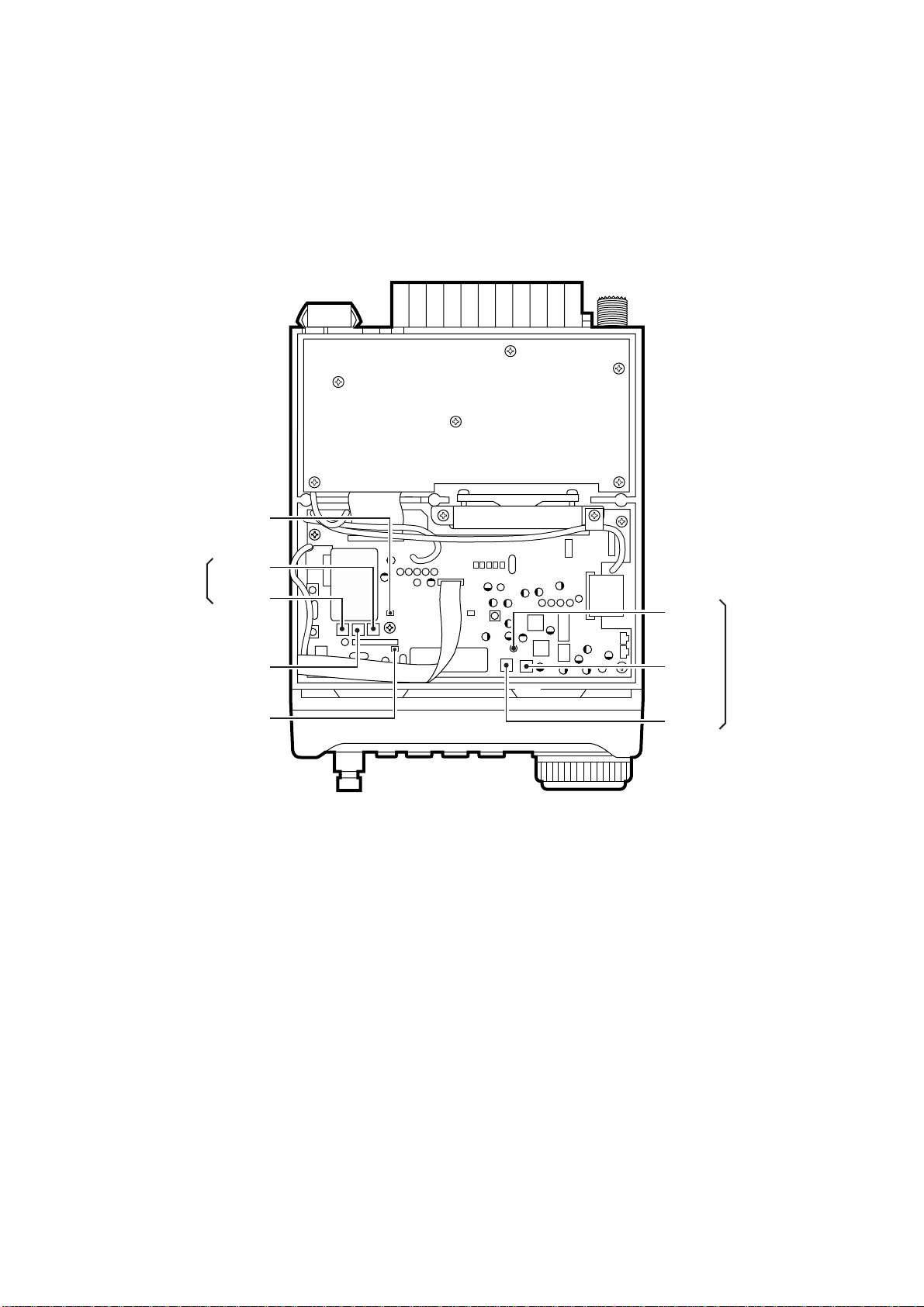

• MAIN UNIT

R921

R1042

R1002

R999

R1080

L511

L512

CP1011

CP1041

L562

L563

L566

Residual AM

adjustment

FM VCO

check point

CP921

CW carrier level

check point

AM modulation

check point

AM modulation

pre-setting

FM deviation

adjustment

C1022

FM VCO

adjustment

AM modulation

adjustment

CW carrier level

adjustment

J281

Page 21

4 - 6

TRANSMITTER ADJUSTMENTS (continued)

IDLING

CURRENT

(for drive

amplifiers)

(for final

amplifiers)

SWR

DETECTION

ADJUSTMENT

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

POINT

UNIT LOCATION UNIT ADJUST

1

2

3

4

5

1

2

3

• Display frequency: 14.10000 MHz

• Mode : USB

• [Q2 MIC GAIN] : 1 (minimum)

• turn R162, R174, R175, R214,

R231 (on the PA unit) to maximum

counterclockwise position.

• Disconnect the plug from J571 on

the PAunit.

• Transmitting

• Display frequency: 145.10000 MHz

• Mode : USB

• [Q2 MIC GAIN] : 1 (minimum)

• Transmitting

• Display frequency: 14.10000 MHz

• Mode : USB

• [Q2 MIC GAIN] : 1 (minimum)

• Transmitting

• Transmitting

• Display frequency: 145.10000 MHz

• Mode : USB

• [Q2 MIC GAIN] : 1 (minimum)

• Transmitting

• Display frequency: 14.10000 MHz

• Mode : USB

• Ground CP1071 on the MAIN board.

• Connect an audio generator to

[MIC] connector and set as:

1.5 kHz/30 mV

• Transmitting

• Transmitting

PA

Rear

Panel

FILTER

Connect a DC

ammeter between

the DC power supply

and transceiver’s DC

power socket (P601

on the PAunit).

Connect an RF

power meter to

[ANT1] connector.

Connect a digital

multimeter to check

point W16.

0.5 Aincrease from that

R162 is in maximum

counterclockwise position.

1.0 A increase from

step 1.

1.0 Aincrease from that

R174 is in maximum

counterclockwise position.

1.0 A increase from

step 3.

2.0 A increase from

step 4.

100 W

Minimum voltage

PA

Quick

set

mode

FILTER

R162

R214

R174

R175

R231

Q2 MIC

GAIN

C58

After remove the jumper wire from CP1071 on the MAIN board.

Page 22

4 - 7

• MAIN AND FILTER UNITS

• PA UNIT

C58

R162

R214

R174

R175

R231

J571

CP1071

Drive idling

adjustment

Final idling

adjustment

SWR detection

pre-setting

Idling current

pre-setting

W16

SWR detection

check point

SWR detection

adjustment

Page 23

4-4 RECEIVER ADJUSTMENTS

*This output level of the standard signal generator (SSG) is indicated as SSG’s open circuit.

RECEIVER

TOTAL GAIN

WFM

RECEIVING

NOISE

BLANKER

Muximum AF output

level

30 dB of AF level difference

4.0 V

Adjust the maximum

noise wave displayed

on the oscilloscope.

At the point where the

noise just reduces.

1

2

1

1

2

• Display freq. : 14.10000 MHz

• Mode : USB

• [RIT] : OFF

• [M4 AGC] : Fast (F AGC)

• [M3 NB] : OFF

• [P.AMP/ATT] : Preamp ON

• Connect a standard signal generator to the [ANT1] connector and set

as:

Frequency : 14.10150 MHz

Level :

0.5 µV* (–113 dBm)

Modulation : OFF

• Receiving

• [P.AMP/ATT] : Preamp OFF

• Set an SSG as:

Frequency : 14.10150 MHz

Level :

500 µV* (–53 dBm)

and OFF

Modulation : OFF

• Receiving

• Display freq. : 14.10000 MHz

• Mode : WFM

• Set an SSG as:

Frequency : 14.10000 MHz

Level :

500 µV* (–53 dBm)

Modulation : OFF

• Receiving

• Display freq. : 14.10000 MHz

• Mode : USB

• [P.AMP/ATT] : Preamp ON

• [M3 NB] : OFF

• R623 (MAIN) : Center

• Connect an SSG to the [ANT1] connector and set as:

Frequency : 14.1015 MHz

Level : 18 µV* (–82 dBm)

Modulation : OFF

and apply the following signal to

the [ANT1] connector.

• Receiving

• [M3 NB] : ON

• Set an SSG as:

Level : 10 µV* (–87 dBm)

Modulation : OFF

• Receiving

L731,

L741

R741

L632

L621,

L633

R623

Connect an AC millivoltmeter to the [EXT

SP] jack with an 8 Ω

dummy load.

Connect an AC millivoltmeter to the [EXT

SP] jack with a 8 Ω

dummy load.

Connect a digital

multimeter or oscilloscope to check point

CP631.

Connect an oscilloscope to check point

CP632.

MAIN

MAIN

MAIN

MAIN

MAIN

Rear

Panel

Rear

Panel

MAIN

MAIN

ADJUSTMENT

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

POINT

UNIT LOCATION UNIT ADJUST

4 - 8

1 msec.

100 msec.

Page 24

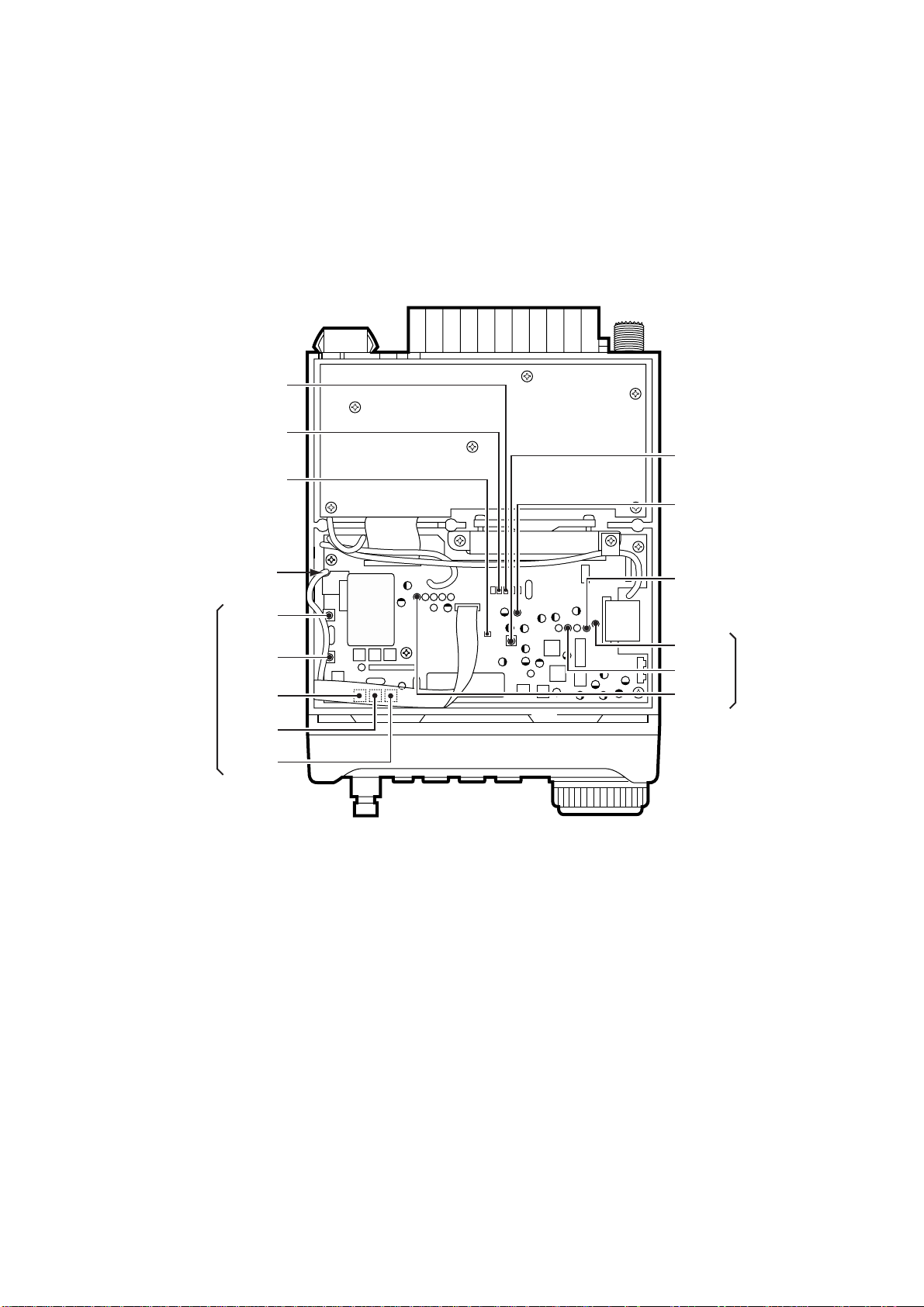

4 - 9

• MAIN UNIT

CP631

L632

R741

L741

L731

L621

L633

CP632

Receiver total gain

adjustment

Noise blanler

check point

Noise blanler

adjustment

WFM receiving

adjustment

WFM receiving

check point

Page 25

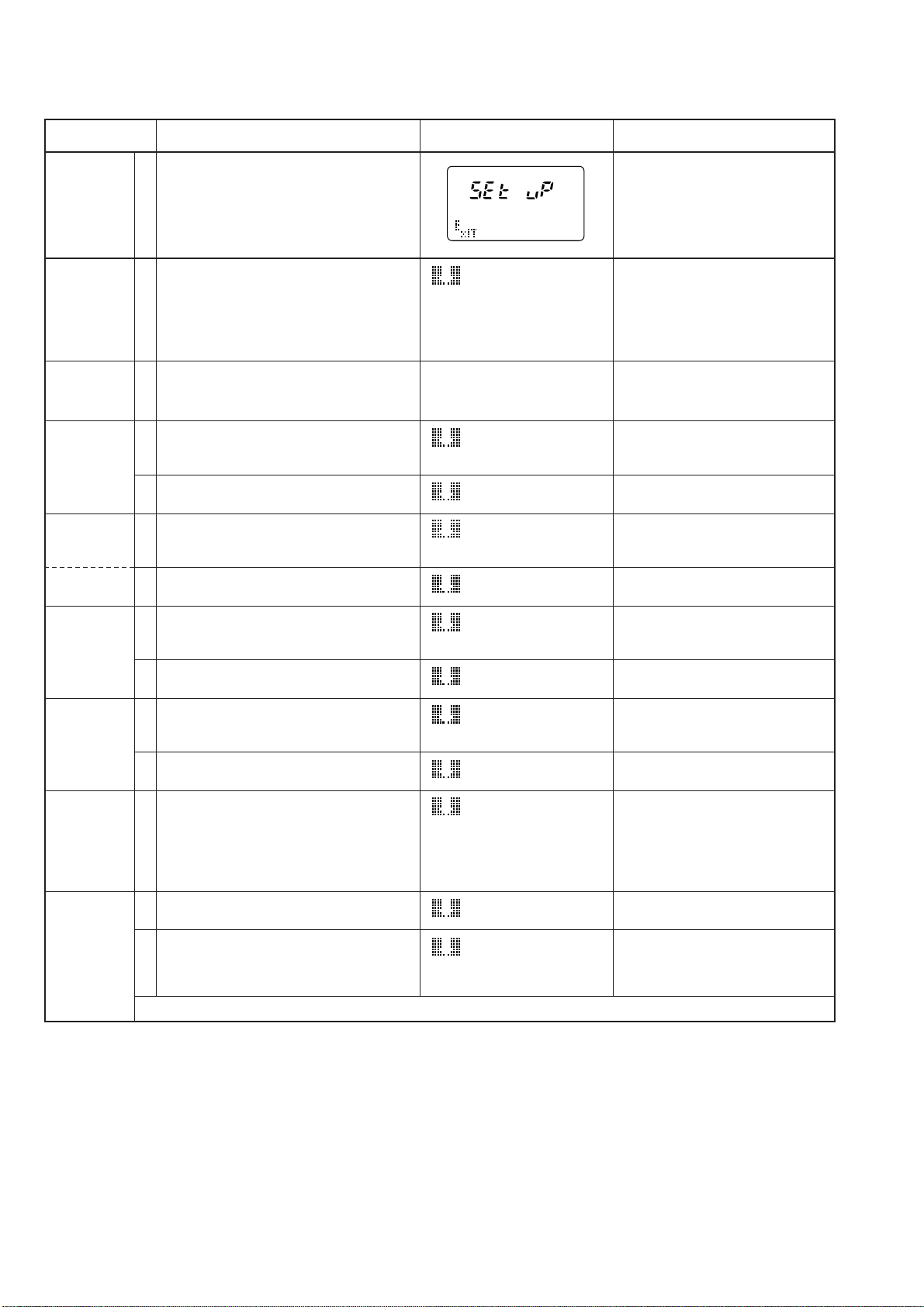

4-5 SET MODE ADJUSTMENT

4 - 10

ENTERING

ADJUSTMENT

SET MODE

Id APC

FILTER

CALIBRATION

POWER

METER

(14 MHz)

TUNING

POWER

(14 MHz)

(50 MHz)

POWER

METER

(145 MHz)

POWER

METER

(430 MHz)

ALC METER

SWR METER

ADJUSTMENT ADJUSTMENT CONDITION DISPLAY OPERATION

• Enter adjustment set mode:

1 Turn power OFF.

2 Terminate the [REMOTE] jack with a

3.5(d) mm mini-plug.

3 While pushing [P.AMP/ATT] and

[TUNE/CALL], turn power ON.

• Connect an RF power meter to [ANT1]

connector.

• Connect a DC ammeter between the DC

power supply and transceiver’s DC power

socket (P601 on the PAunit).

• Transmit using an external PTT switch.

• Connect an RF power meter to [ANT1]

connector.

• Connect an RF power meter to [ANT1]

connector.

• Transmit using an external PTT switch.

• Transmit using an external PTT switch.

• Connect an RF power meter to [ANT1]

connector.

• Transmit using an external PTT switch.

• Transmit using an external PTT switch.

• Connect an RF power meter to [ANT2]

connector.

• Transmit using an external PTT switch.

• Transmit using an external PTT switch.

• Connect an RF power meter to [ANT2]

connector.

• Transmit using an external PTT switch.

• Transmit using an external PTT switch.

• Connect an RF power meter to [ANT1]

connector.

• Connect an audio generator to [MIC] con-

nector and set as :

Level : 1.5 kHz/30mV

• Transmit using an external PTT switch.

• Connect a 50 Ω dummy load or power

meter to [ANT1] connector.

• Connect a 50 Ω dummy load or power

meter to [ANT1] connector.

1

1

1

1

2

1

2

1

2

1

2

1

1

2

SET IdAPC

GO FILTER CAL

SET 90 %

SET 50 %

SET TUNE Po

SET TUNE Po

SET 90 %

SET 50 %

SET 90 %

SET 50 %

ALC START

SWR 1 LOAD

SWR 2 LOAD

Push [F-3 (TX)] to enter the TX

adjustment setting mode.

Then advance to the following setting, or push [UP]/[DN] to scroll the

display.

Set a total current at 15 Aby adjusting R1125 on the MAIN board.

Push [MENU] to set the "SET

IdAPC" after returning receiving condition.

Push and hold [MENU (GO)] to

make the calibration.

• Transceiver transmits for a while.

Set to 90 W using [MAIN DIAL], then

push [MENU] while transmitting.

Set to 50 W using [MAIN DIAL], then

push [MENU] while transmitting.

Set to 10 W using [MAIN DIAL], then

push [MENU] while transmitting.

Set to 10 W using [MAIN DIAL], then

push [MENU] while transmitting.

Set to 45 W using [MAIN DIAL], then

push [MENU] while transmitting.

Set to 25 W using [MAIN DIAL], then

push [MENU] while transmitting.

Set to 18 W using [MAIN DIAL], then

push [MENU] while transmitting.

Set to 10 W using [MAIN DIAL], then

push [MENU] while transmitting.

Push and hold [MENU] to set ALC

reference level while transmitting.

Push [MENU] to set SWR reference

level.

Push [MENU] to set SWR2 level.

• The display returns to the same as

the ADUSTMENT SET MODE above.

USB

RX TX

Push [F-1 (EXIT)] to exit adjustment set mode.

Page 26

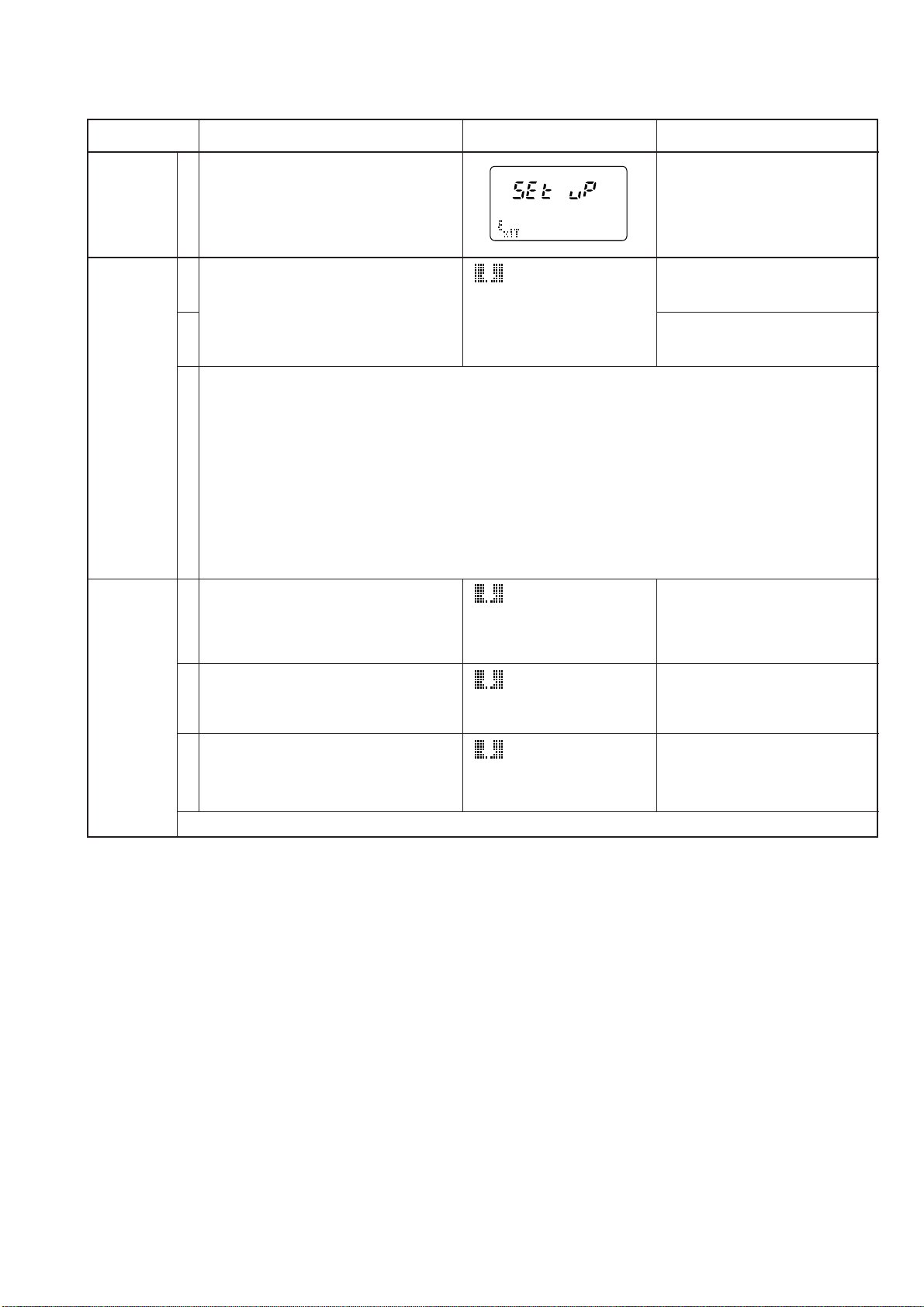

SET MODE ADJUSTMENT (continued)

ENTERING

ADJUSTMENT

SET MODE

SENSITIVITY

S-METER

• Enter adjustment set mode:

1 Turn power OFF.

2 Terminate the [REMOTE] jack with a

3.5(d) mm mini-plug.

3 While pushing [P.AMP/ATT] and

[TUNE/CALL], turn power ON.

• Connect a standard signal generator to

[ANT2] and set as :

Frequency : 60.05150 MHz

Modulation : OFF

• Receiving

• Connect an SSG to [ANT1] connector and

set as:

Frequency : 14.1515 MHz

Level : OFF

• Receiving

• Set an SSG as :

Level : 50 µV (–73 dBm)

Modulation : OFF

• Receiving

• Set an SSG as :

Level : 50 mV (–13 dBm)

Modulation : OFF

• Receiving

VHF1 BPF1 L

S0 LEVEL

S9 LEVEL

+60dB LEVEL

Push [F-2 (RX)] to enter the RX

adjustment setting mode.

Then advance to the following setting, or push [UP]/[DN] to scroll the

display.

Set a connected SSG’s level at 10

dB of S/N ratio with AC millivoltmeter.

Set maximum AF level using the

[MAIN DIAL], then push [MENU] to

set the "VHF1 BPF1 L".

Push [MENU] to set the "S0 level".

Push [MENU] to set the "S9 level".

Push [MENU] to set the "+60 dB

level".

• The display returns to the same as

the ADUSTMENT SET MODE above.

Push [F-1 (EXIT)] to exit adjustment set mode.

4 - 11

ADJUSTMENT ADJUSTMENT CONDITION DISPLAY OPERATION

1

1

2

3

1

2

3

USB

RX TX

• Same operation as step 2 for the listed BPFs.

• Set an SSG as:

Modulation : OFF

VHF1 BPF2 L : 60.05150 MHz

VHF1 BPF1 M : 90.50150 MHz VHF1 BPF2 M : Same as left

VHF1 BPF1 H : 128.9515 MHz VHF1 BPF2 H : Same as left

VHF2 BPF1 L : 129.1015 MHz VHF2 BPF2 L : Same as left

VHF2 BPF1 M : 145.1515 MHz VHF2 BPF2 M : Same as left

VHF2 BPF1 H : 170.0015 MHz VHF2 BPF2 H : Same as left

UHF BPF1 L : 400.0015 MHz UHF BPF2 L : Same as left

UHF BPF1 M : 435.1515 MHz UHF BPF2 M : Same as left

UHF BPF1 H : 470.0015 MHz UHF BPF2 H : Same as left

• Receiving

Page 27

S.=Surface mount

S1 2250000290 ENCODER SW-159 (EC24B50B)

W1 8900006040 CABLE OPC-593

W2 8900006250 CABLE OPC-610

IC1 1140008050 S.IC HD6433832SD47H

IC2 1130007960 S.IC SED1522F0C (QFP15-100PIN)

IC3 1130002660 S.IC µPD4030BG-T1

IC4 1110004750 S.IC S-80945ALMP-DA9-T2

IC5 1180001080 S.IC S-81250PG-PD-T1

IC6 1140003630 S.IC X24C01S-2.7T6

Q1 1590002310 S.TRANSISTOR DTC114EE TL

Q2 1520000460 S.TRANSISTOR 2SB1132 T100 R

Q3 1530002060 S.TRANSISTOR 2SC4081 T107 R

Q4 1540000440 S.TRANSISTOR 2SD1619-T-TD

Q8 1590002370 S.TRANSISTOR XP4111 (TX)

Q9 1590001870 S.TRANSISTOR DTA114EE TL

Q10 1530002060 S.TRANSISTOR 2SC4081 T107 R

Q11 1520000380 TRANSISTOR 2SB1143 S

Q12 1590002370 S.TRANSISTOR XP4111 (TX)

Q13 1520000460 S.TRANSISTOR 2SB1132 T100 R

Q14 1530002060 S.TRANSISTOR 2SC4081 T107 R

Q15 1590001870 S.TRANSISTOR DTA114EE TL

Q16 1590002770 S.FET CPH3404

D1 1750000370 S.DIODE DA221 TL

D2 1750000370 S.DIODE DA221 TL

D3 1750000370 S.DIODE DA221 TL

D5 1790001250 S.DIODE MA2S111-(TX)

D6 1790001250 S.DIODE MA2S111-(TX)

D7 1160000140 S.DIODE DAP222 TL

D9 1790001250 S.DIODE MA2S111-(TX)

D10 1790001250 S.DIODE MA2S111-(TX)

D11 1160000060 S.DIODE DAN202U T107

D12 1790001250 S.DIODE MA2S111-(TX)

D13 1160000060 S.DIODE DAN202U T107

D14 1160000140 S.DIODE DAP222 TL

D15 1160000140 S.DIODE DAP222 TL

D16 1160000140 S.DIODE DAP222 TL

X1 6050009660 S.XTAL MA-406 (9.8304 MHz)

L1 6200003260 S.COIL NL 322522T-101J

L2 6200003950 S.COIL HF50ACC 322513-T

L3 6200003950 S.COIL HF50ACC 322513-T

L4 6200003950 S.COIL HF50ACC 322513-T

L5 6200003950 S.COIL HF50ACC 322513-T

R1 7030003340 S.RESISTOR ERJ3GEYJ 151 V (150 Ω)

R2 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R3 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R4 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R5 7030003340 S.RESISTOR ERJ3GEYJ 151 V (150 Ω)

R6 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R7 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)