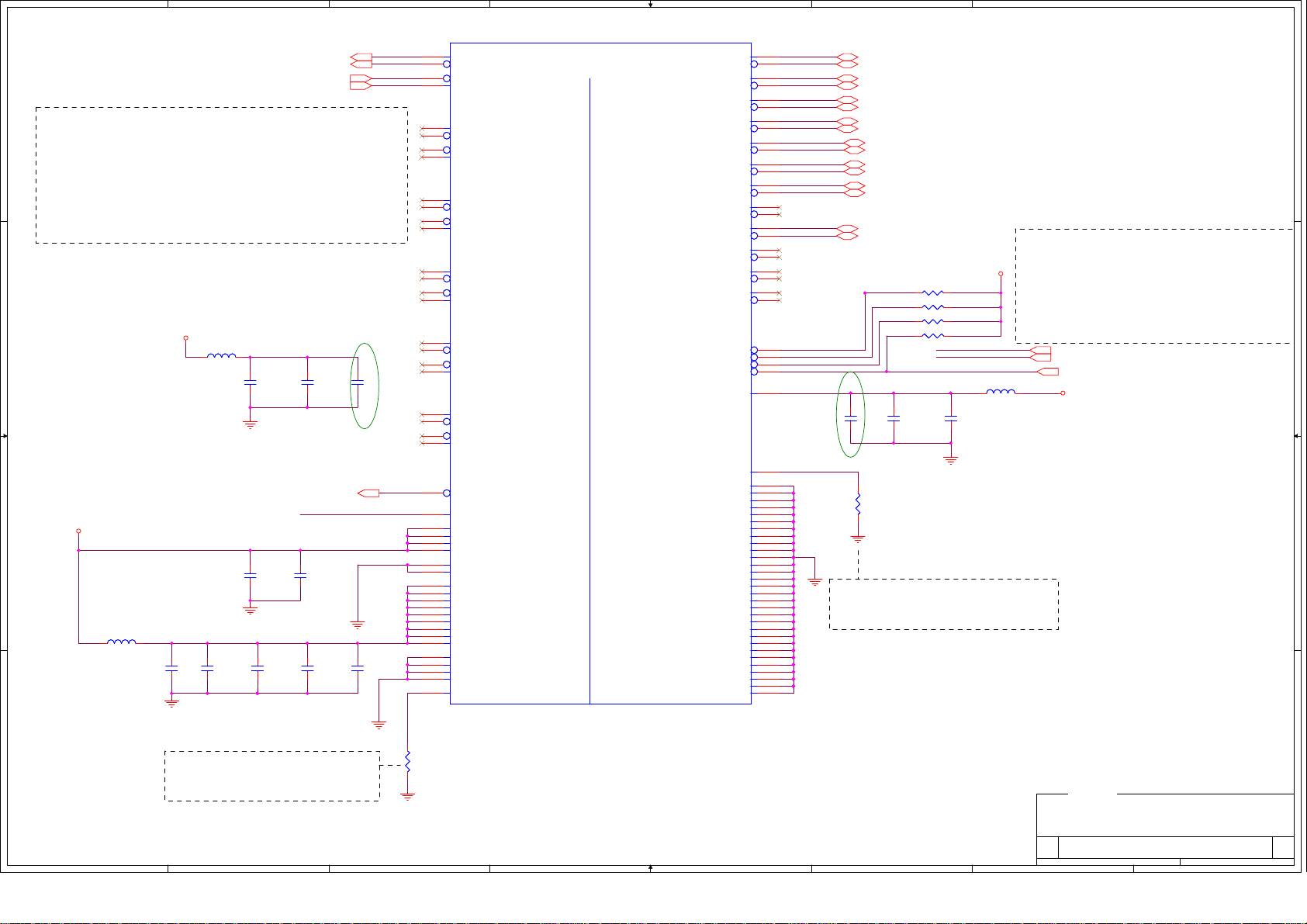

Page 1

5

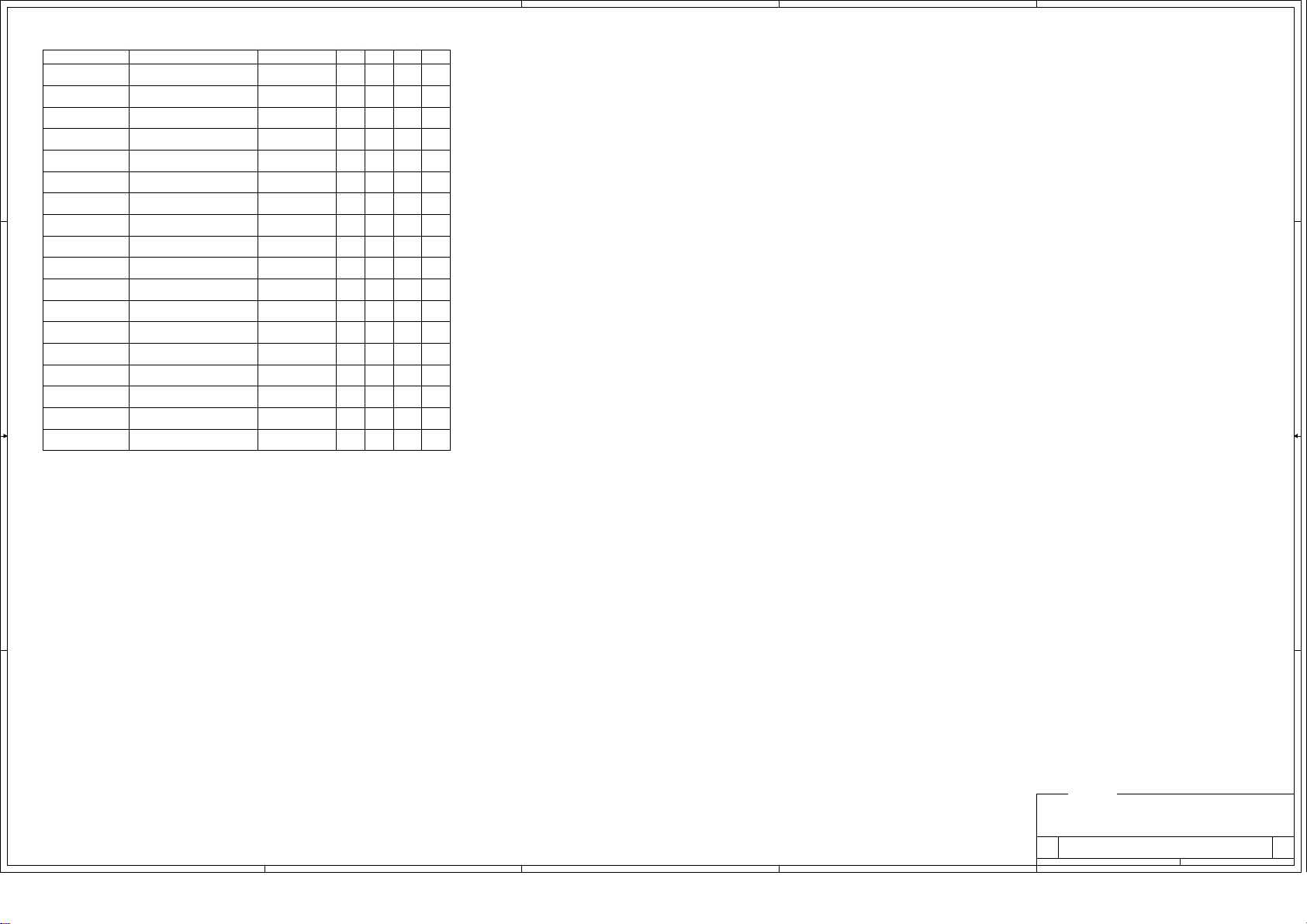

PCB STACK UP6L

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1

D D

LAYER 4 : IN2

LAYER 5 : SVCC

LAYER 6 : BOT

4

3

2

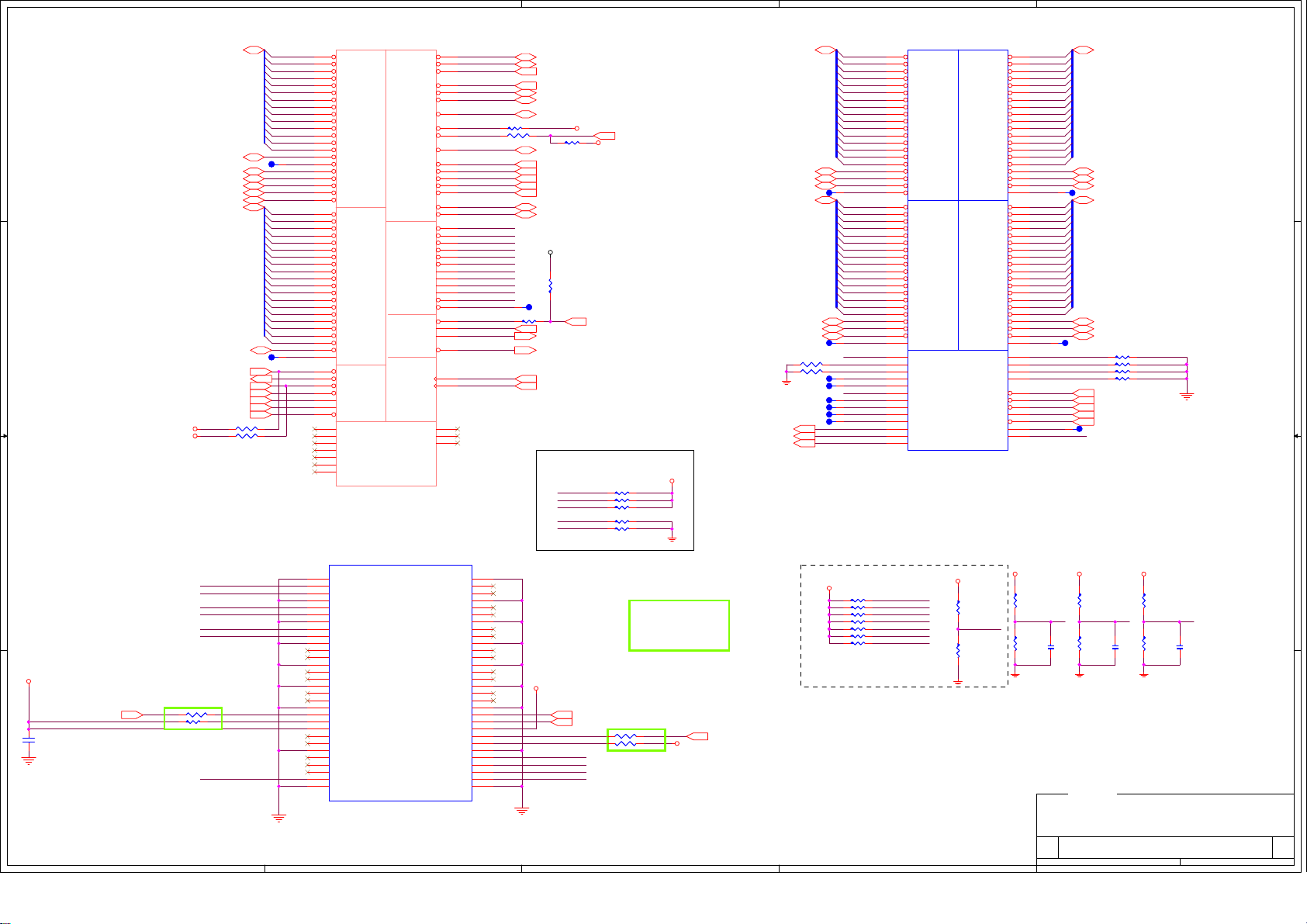

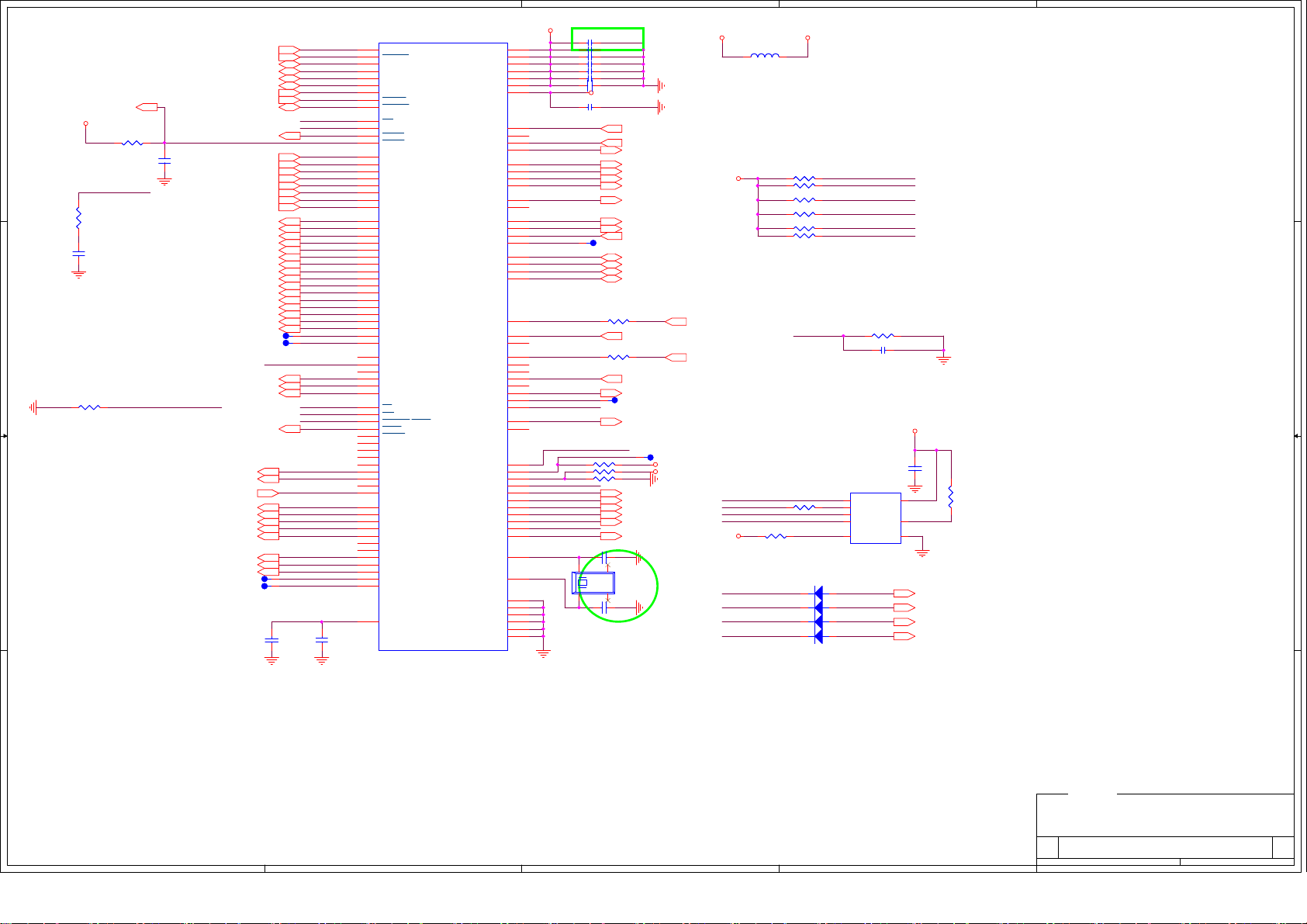

FP6_Prescott Block Diagram

Intel Diamondville

FCBGA8

22 x 22 mm 437 Balls

1

SYSTEM POWER RT8206B

VCCP 1.05V / 1.5v(RT8204)

CPU CORE RT8152B

MCPCORE (RT8208)

DDR III SMDDR_VTERM

1.5V/1.5VSUS(RT8207)

30

31

34

36

32

01

TDP~2.5W

3,4

SYSTEM CHARGER (ISL6251A)

34

FSB 533/667MHz

C C

11.6" LED Panel

CRT

HDMI

Max 4GB

20

22

24

LVDS

RGB

HDMI

DDR3 1066MHz

DDR3 SO-DIMM

B B

DDR3 8x1Rx8 1G

USB CONN X 3

CCD CONN

BT CONN

A A

Card Reader

15

16,17

27

20

28

DDR3 1066MHz

Port0,1,2

Port5

Port4

Port6

USB 2.0

25MHz 32.768MHz

NVIDIA

M

CP79MH_B03

35 x 35 mm

GA 1437 Balls

B

TDP~15W

32.768KHz

KB3926 D2

EC

LPC

29

5~14

MII

PCIE

SATA0

2.5"HDD&SSD

HDA

AUDIO CODEC IDT 92HD80

HP/MIC

10/100M PHY

RTL8201EL

WLAN

26

24

MIC

DigitalCOMBO JACK

21

23

Int SPK

21

21

21

RTS5159

5

25

WWANSIM Card

Port7

4

Touch Pad Con. SPI FlashK/B Con.

28 29282626

3

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date: Sheet of

Date: Sheet of

Date: Sheet of

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

Prescott

Prescott

Prescott

1 36Wednesday, April 15, 2009

1 36Wednesday, April 15, 2009

1 36Wednesday, April 15, 2009

1B

1B

1B

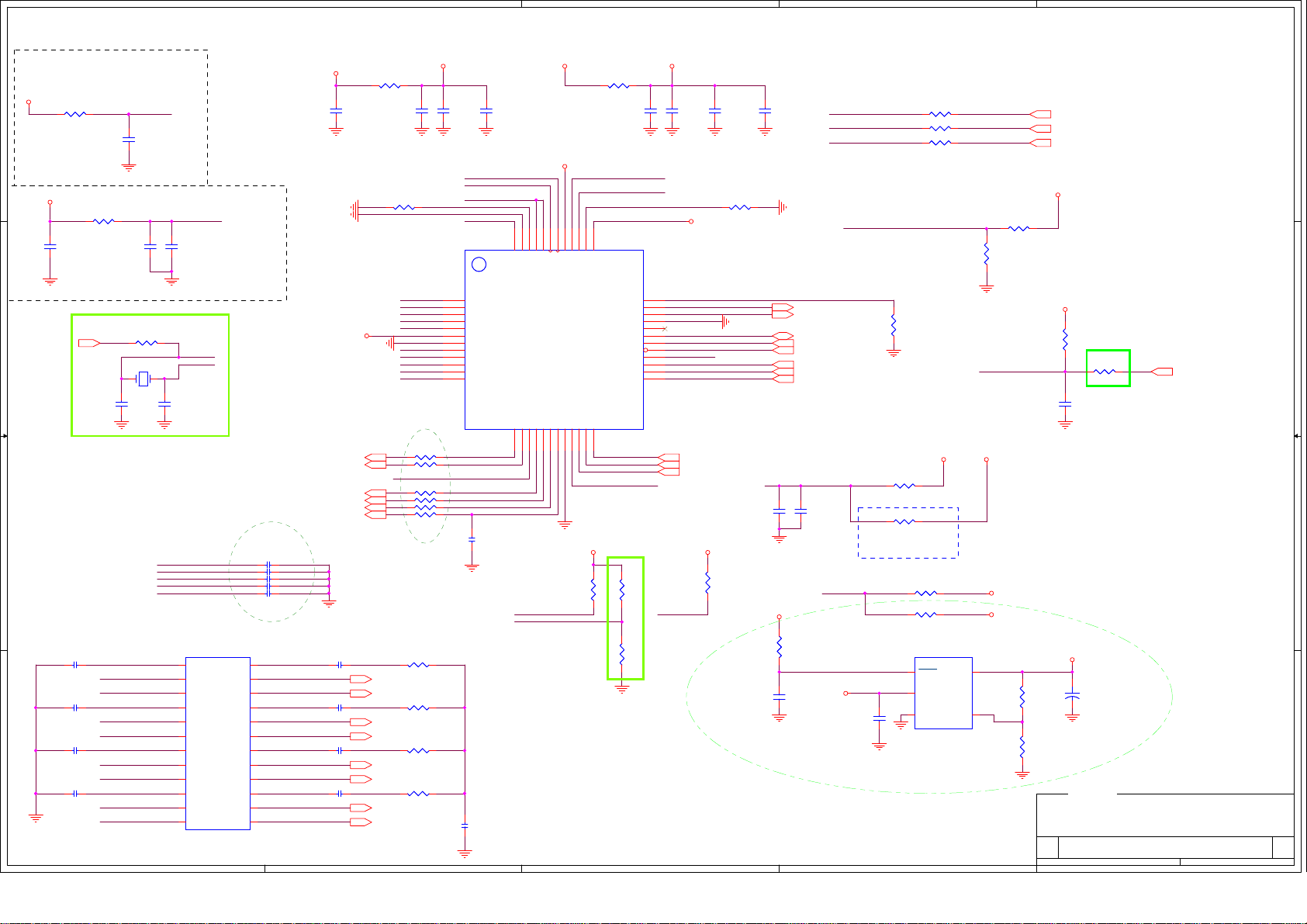

Page 2

5

4

3

2

1

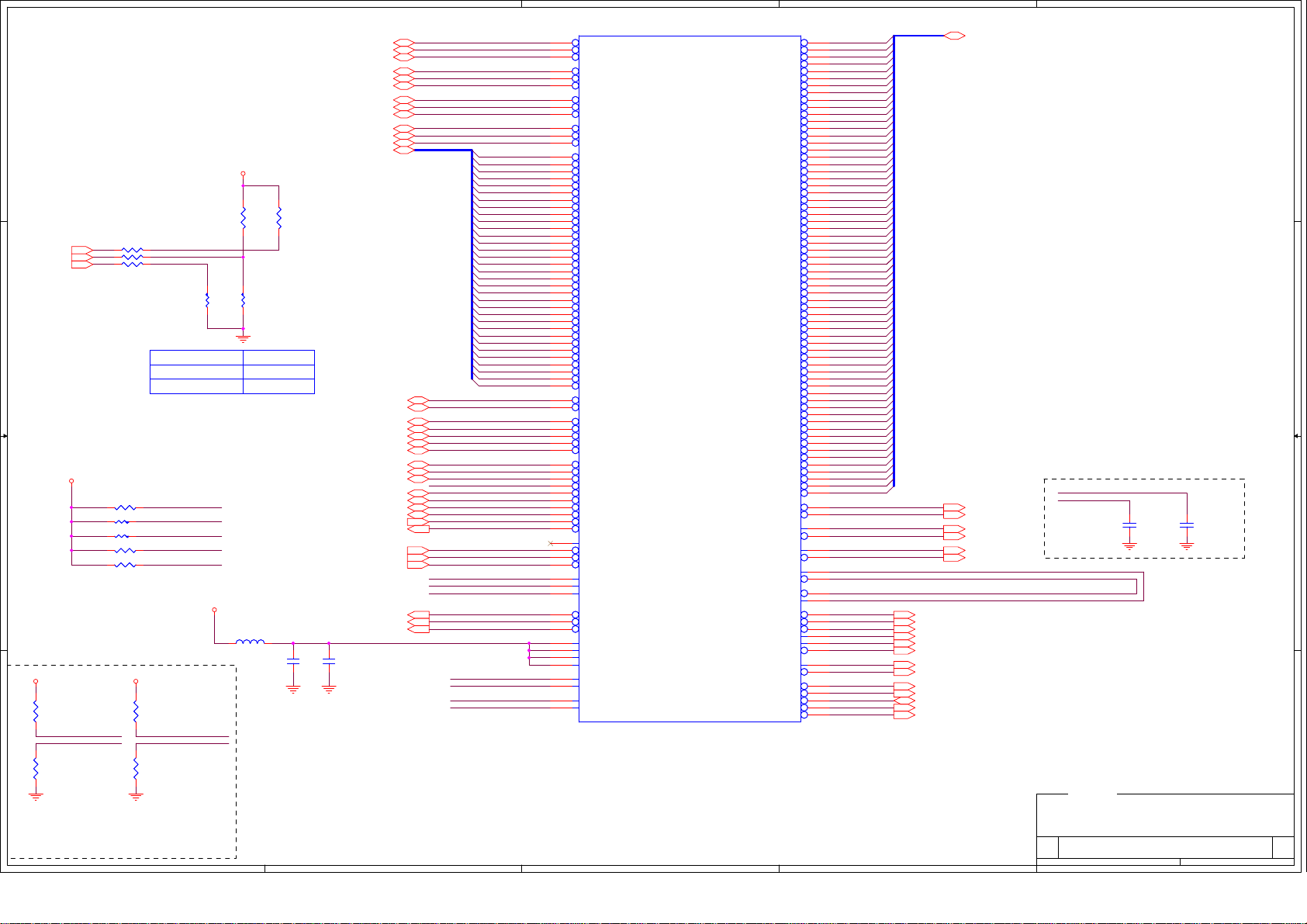

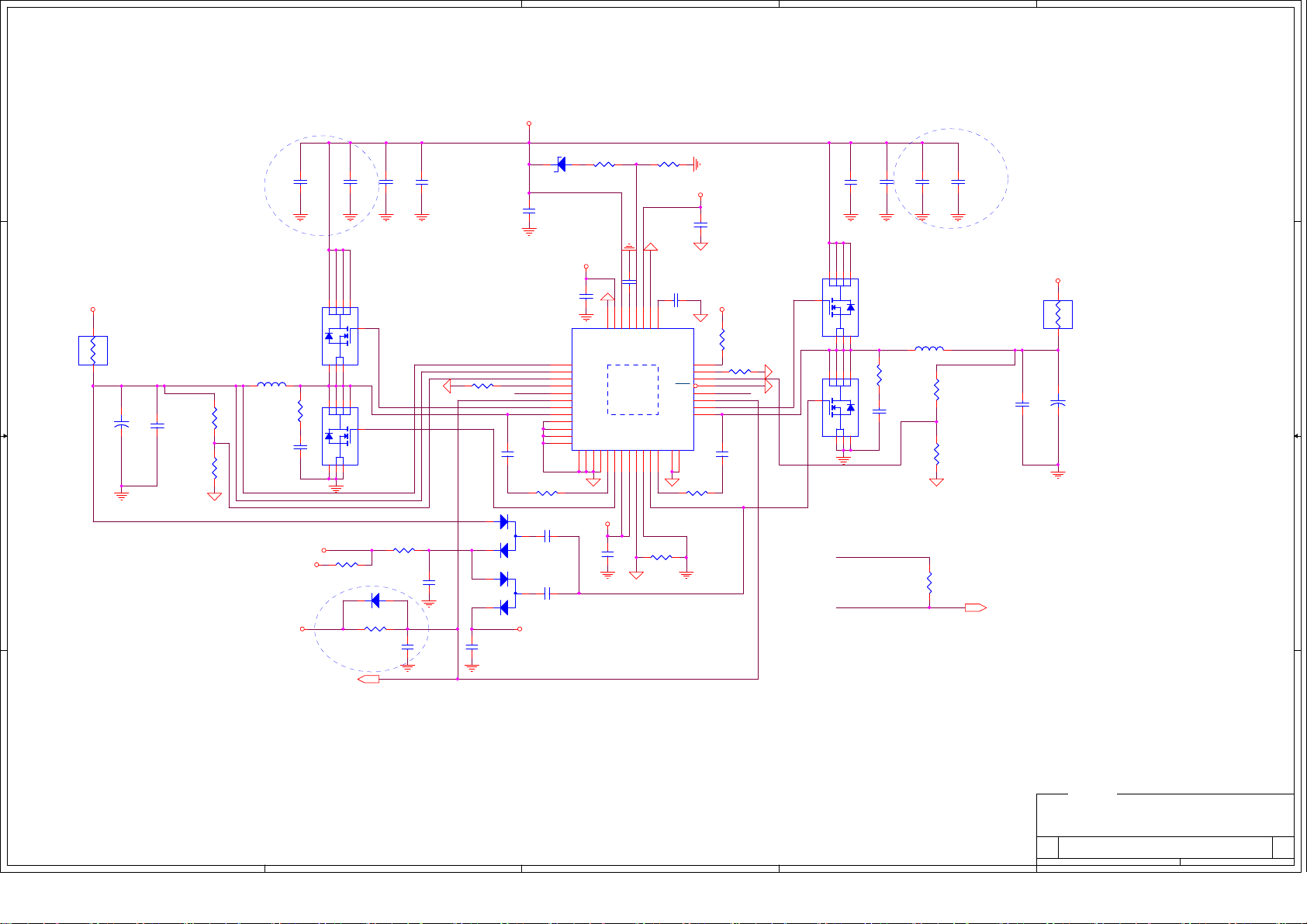

Power Rails

02

Power Net Description Voltage S0 S3 S4 S5

+MCP_CORE

+VCC_CORE

D D

+5VSUS

+3VSUS

+1.5VSUS 1.5V

+5V

+3V 3.3V

+1.8V 1.8V

+1.5V

+1.05V

+1.05V_S5

C C

+3VPCU

+5VPCU

+3VLANVCC

+1.05V_LAN

MCP79 Vcore

CPU Vcore

Memory

0.9~1.0V

N270-1.2V

N280-1.1V

5V

3.3V

5V

1.5V

1.05V

1.05V

3.3V+3V_S5

3.3V

5V

3.3V

1.05V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V V

V

V

V V

V

V

V V

V

V

V V

V

V

V V

V

V

V V

B B

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Index

Index

Index

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

1

Prescott

Prescott

Prescott

2 36Wednesday, April 15, 2009

2 36Wednesday, April 15, 2009

2 36Wednesday, April 15, 2009

1A

1A

1A

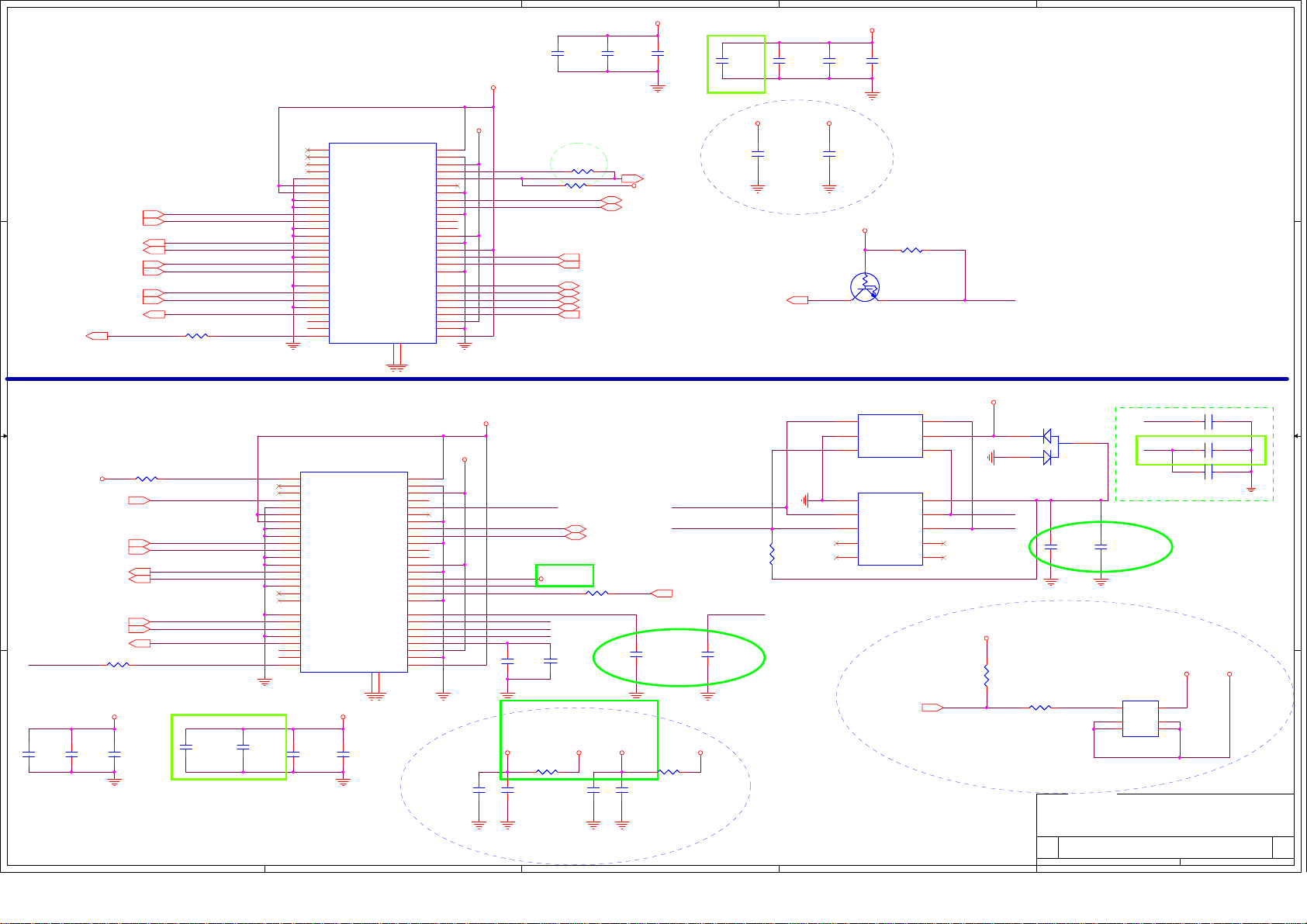

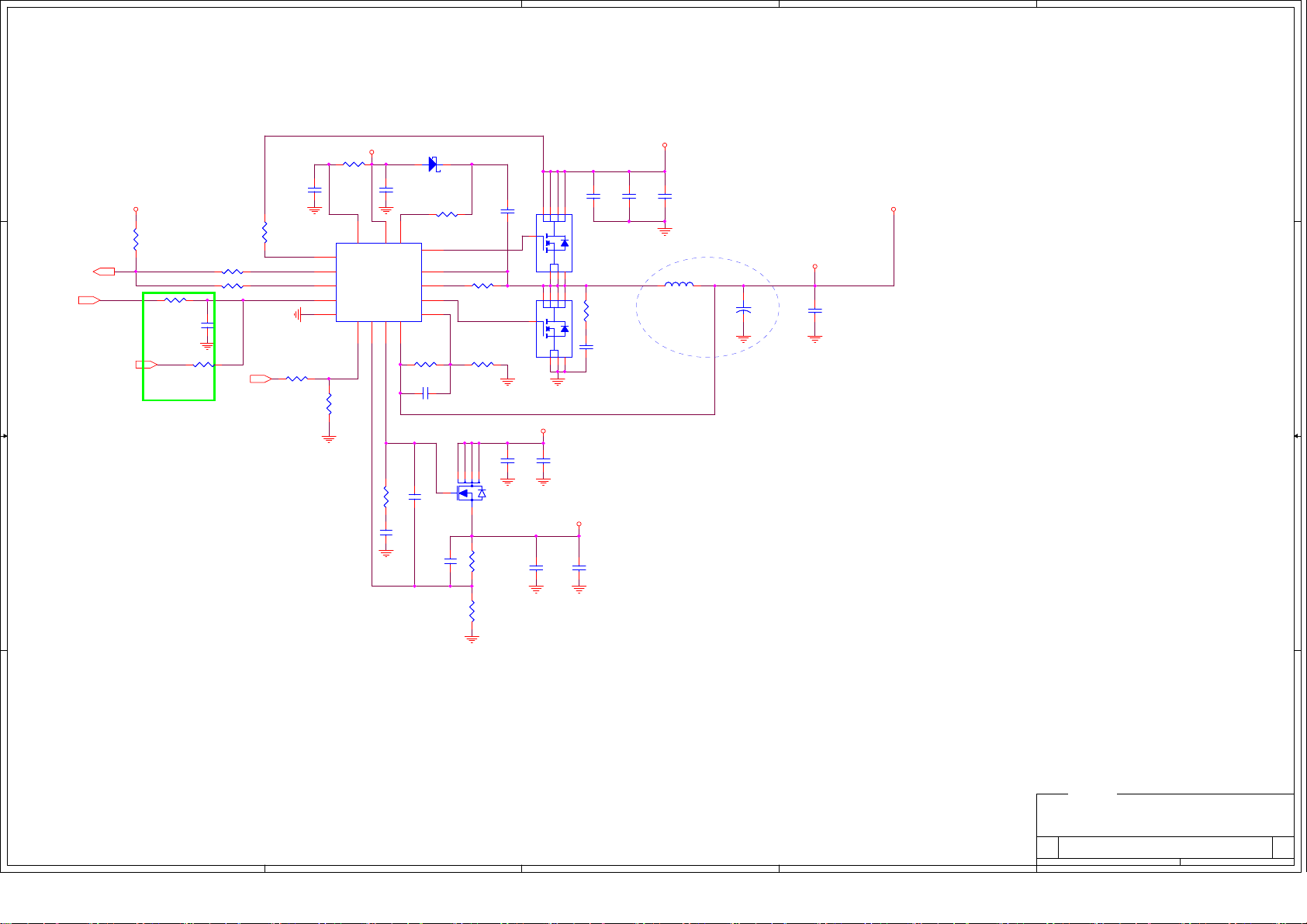

Page 3

5

4

3

2

1

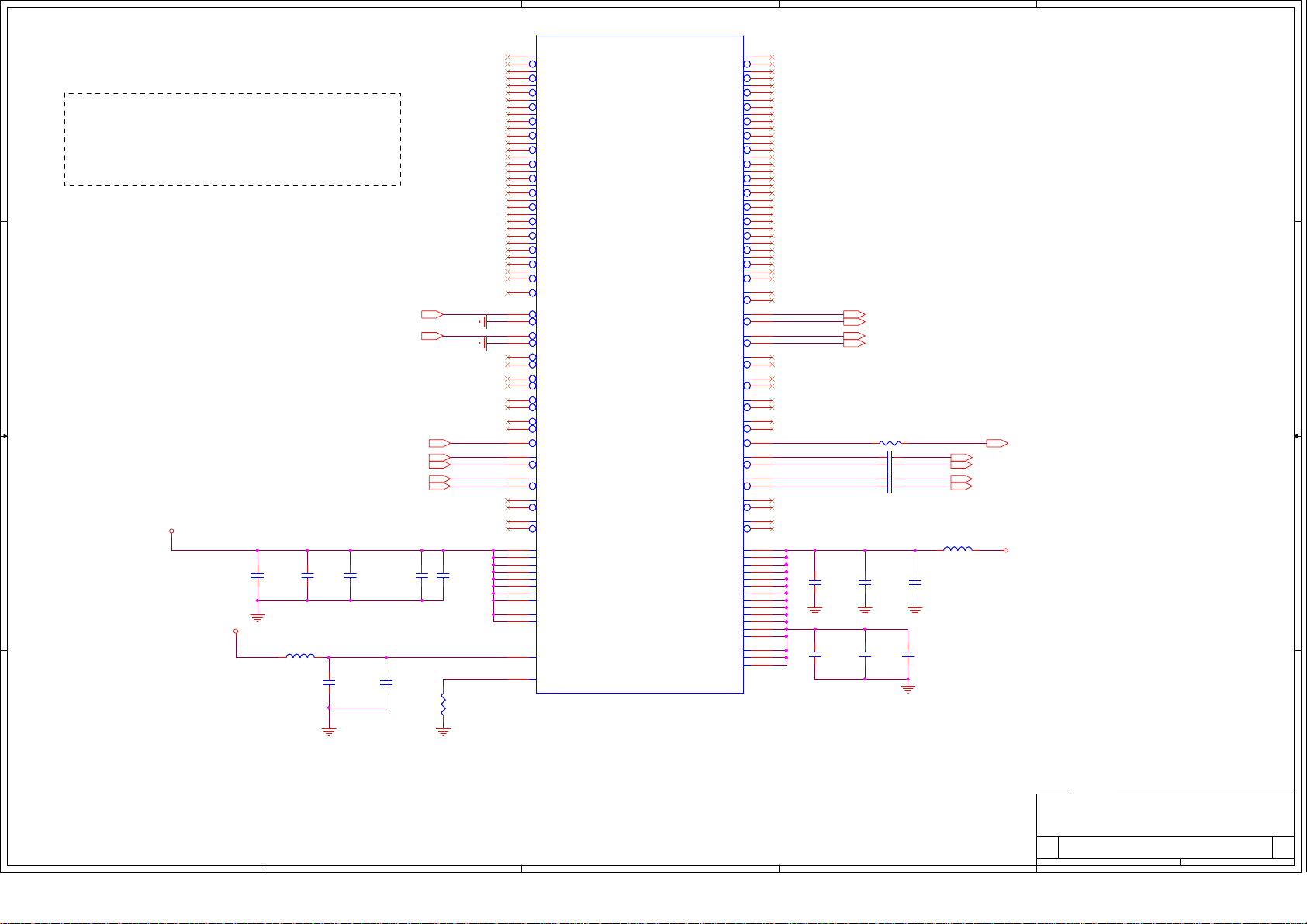

U22B

U22A

H_A#[3..35]5

D D

H_ADSTB#05

H_REQ#05

H_REQ#15

H_REQ#25

H_REQ#35

H_REQ#45

H_A#[3..35]5

C C

H_ADSTB#15

H_A20M#5

H_FERR#5

H_IGNNE#5

H_STPCLK#5

H_INTR5

H_NMI5

H_SMI#5

+1.05V

+1.05V

B B

+1.05V

HWPG4,12,20,29,30,31,32,36 CLK_ITP_BCLK 5

C325

C325

*.1U/10V_4

*.1U/10V_4

A A

R205 *1K/F_4R205 *1K/F_4

R204 *54.9/F_4R204 *54.9/F_4

del R204,R205 in BOM

5

R150 *1K/F_4R150 *1K/F_4

R194 *1K/F_4R194 *1K/F_4

CAD Note: Place near CPU

XDP_BPM#5

XDP_BPM#4

XDP_BPM#3

XDP_BPM#2

XDP_BPM#1

XDP_BPM#0

H_CPUPWRGD_XDP

XDP_HOOK1

XDP_TCK

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_AP0

T22T22

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_AP1

T16T16

H_IGNNE#

U22A

P21

A[3]#

H20

A[4]#

N20

A[5]#

R20

A[6]#

J19

A[7]#

N19

A[8]#

G20

A[9]#

M19

A[10]#

H21

A[11]#

L20

A[12]#

M20

A[13]#

K19

A[14]#

J20

A[15]#

L21

A[16]#

K20

ADSTB[0]#

D17

AP0

N21

REQ[0]#

J21

REQ[1]#

G19

REQ[2]#

P20

REQ[3]#

R19

REQ[4]#

C19

A[17]#

F19

A[18]#

E21

A[19]#

A16

A[20]#

D19

A[21]#

C14

ADDR GROUP 1

ADDR GROUP 1

A[22]#

C18

A[23]#

C20

A[24]#

E20

A[25]#

D20

A[26]#

B18

A[27]#

C15

A[28]#

B16

A[29]#

B17

A[30]#

C16

A[31]#

A17

A[32]#

B14

A[33]#

B15

A[34]#

A14

A[35]#

B19

ADSTB[1]#

M18

AP1

U18

A20M#

T16

FERR#

J4

IGNNE#

R16

STPCLK#

T15

LINT0

R15

LINT1

U17

SMI#

D6

NC1

G6

NC2

H6

NC3

K4

NC4

K5

NC5

M15

NC6

L16

NC7

Diamondville_SC_Rev1

Diamondville_SC_Rev1

CN21

CN21

CPU XDP Conn.

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

PWRGOOD/HOOK039ITPCLK/HOOK4

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

*Samtec BSH-030-01

*Samtec BSH-030-01

GROUP

0

GROUP

0

NC

NC

ADS#

BNR#

BPRI#

ADDR

ADDR

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROLXDP/ITP SIGNALS

CONTROLXDP/ITP SIGNALS

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

BR1#

PROCHOT#

THRMDA

THRMDC

THERM

THERM

THERMTRIP#

BCLK[0]

BCLK[1]

H CLK

H CLK

RSVD3

RSVD2

RSVD1

ITPCLK#/HOOK5

RESET#/HOOK6

4

TDI

V19

Y19

U21

T21

T19

Y18

T20

F16

V16

W20

D15

W18

Y17

U20

W19

AA17

V20

K17

J18

H15

J15

K18

J16

M17

N16

M16

L17

K16

V15

G17

E4

E5

H17

V11

V12

C21

C1

A3

.

.

GND1

OBSFN_C0

OBSFN_C1

GND3

OBSDATA_C0

OBSDATA_C1

GND5

OBSDATA_C2

OBSDATA_C3

GND7

OBSFN_D0

OBSFN_D1

GND9

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

VCC_OBS_CD

DBR#/HOOK7

GND15

TDO

TRSTN

TMS

GND17

H_BR0#

IERR#

R176 56_4R176 56_4

H_INIT#R

R135 1K/F_4R135 1K/F_4

H_RESET#

H_RS#0

H_RS#1

H_RS#2

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_BR1#

H_PROCHOT#_R

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

TDI

58

60

H_ADS# 5

H_BNR# 5

H_BPRI# 5

H_DEFER# 5

H_DRDY# 5

H_DBSY# 5

H_BR0# 5

+1.05V

H_LOCK# 5

H_RESET# 5

H_RS#0 5

H_RS#1 5

H_RS#2 5

H_TRDY# 5

H_HIT# 5

H_HITM# 5

+1.05V

T12T12

R170

R170

22_4

22_4

H_THERMDA 4

H_THERMDC 4

H_THRMTRIP# 4

CLK_CPU_BCLK 5

CLK_CPU_BCLK# 5

R128 330_4R128 330_4

R171

R171

68_4

68_4

H_INIT# 5

+1.05V

H_PROCHOT# 5,33

Must stuff/Close to CPU

XDP_TMS

R182 56_4R182 56_4

XDP_TDI

R180 56_4R180 56_4

XDP_BPM#5

R210 56_4R210 56_4

XDP_TCK

R215 56_4R215 56_4

XDP_TRST#

R183 56_4R183 56_4

del R230,R231,R232,R233 in BOM & SCH

+1.05V

CLK_ITP_BCLK# 5

XDP_RST#_R

XDP_DBRST#

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

R221 *1K/F_4R221 *1K/F_4

R207 *150/F_4R207 *150/F_4

del R221,R207 in BOM

+1.05V

+3V

3

H_RESET# 5

CPU_BSEL05

CPU_BSEL15

CPU_BSEL25

H_D#[63:0]5

H_DSTBN#05

H_DSTBP#05

H_DINV#05

T11T11

H_D#[63:0]5

H_DSTBN#15

H_DSTBP#15

H_DINV#15

T13T13

R136 *1K/F_4R136 *1K/F_4

R137 *1K/F_4R137 *1K/F_4

T14T14

T15T15

T18T18

T20T20

T17T17

T10T10

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DP#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DP#1

H_GTLREF

ACLKPH

DCLKPH

H_BINIT#

EDM

EXTGBREF

FORCEPR#

H_HFPLL

H_MCERR

H_RSP#

+1.05V

R168 *1K_4R168 *1K_4

R149 *1K_4R149 *1K_4

R157 *1K_4R157 *1K_4

R173 *1K_4R173 *1K_4

R159 *1K_4R159 *1K_4

R160 *1K_4R160 *1K_4

R122 *1K_4R122 *1K_4

For defensive design

reservation only in this

initial release

U22B

Y11

D[0]#

W10

D[1]#

Y12

D[2]#

AA14

D[3]#

AA11

D[4]#

W12

D[5]#

AA16

D[6]#

Y10

D[7]#

Y9

D[8]#

Y13

D[9]#

W15

D[10]#

AA13

D[11]#

Y16

D[12]#

W13

D[13]#

AA9

D[14]#

W9

D[15]#

Y14

DSTBN[0]#

Y15

DSTBP[0]#

W16

DINV[0]#

V9

DP#0

AA5

D[16]#

Y8

D[17]#

W3

D[18]#

U1

D[19]#

W7

D[20]#

W6

D[21]#

Y7

D[22]#

AA6

D[23]#

Y3

D[24]#

W2

D[25]#

V3

D[26]#

U2

D[27]#

T3

D[28]#

AA8

D[29]#

V2

D[30]#

W4

D[31]#

Y4

DSTBN[1]#

Y5

DSTBP[1]#

Y6

DINV[1]#

R4

DP#1

A7

GTLREF

U5

ACLKPH

V5

DCLKPH

T17

BINIT#

R6

EDM

M6

EXTBGREF

N15

FORCEPR#

N6

HFPLL

P17

MCERR#

T6

RSP#

J6

BSEL[0]

H5

BSEL[1]

G5

BSEL[2]

Diamondville_SC_Rev1

Diamondville_SC_Rev1

H_NMI

H_SMI#

H_INTR

H_STPCLK#

H_DPSLP#

H_DPRSTP#

H_PWRGOOD

2

H_D#32

R3

D[32]#

H_D#33

R2

D[33]#

H_D#34

P1

D[34]#

H_D#35

N1

D[35]#

H_D#36

M2

D[36]#

H_D#37

P2

D[37]#

H_D#38

J3

D[38]#

H_D#39

N3

D[39]#

H_D#40

G3

D[40]#

H_D#41

H2

D[41]#

H_D#42

N2

D[42]#

H_D#43

L2

D[43]#

M3

D[44]#

J2

D[45]#

H1

D[46]#

J1

D[47]#

K2

K3

L1

M4

DP#2

C2

D[48]#

G2

D[49]#

F1

D[50]#

D3

D[51]#

B4

D[52]#

E1

D[53]#

A5

D[54]#

C3

D[55]#

A6

D[56]#

F2

D[57]#

C6

D[58]#

B6

D[59]#

B3

D[60]#

C4

D[61]#

C7

D[62]#

D2

D[63]#

E2

F3

C5

D4

DP#3

T1

T2

F20

F21

R18

R17

U4

V17

N18

SLP#

A13

B7

.

.

+1.05V

Layout note:

Zo=55ohm, 0.5" max

for GTLREF

H_D#44

H_D#45

H_D#46

H_D#47

H_DP#2

T19T19

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DP#3

T24T24

COMP0

COMP1

COMP2

COMP3

CORE_DET

CPU_CMREF

Layout note:

+1.05V

R237

R237

1K/F_4

1K/F_4

H_GTLREF

C334

C334

R229

R229

2K/F_4

2K/F_4

0.1u/10V_4

0.1u/10V_4

Layout note:

Zo=55ohm, 0.5"

max for EXTGBREF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Diamondville CPU(01_HOST)

Diamondville CPU(01_HOST)

Diamondville CPU(01_HOST)

Date: Sheet of

Date: Sheet of

Date: Sheet of

DATA GRP 2

DATA GRP 2

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DATA GRP 3

DATA GRP 3

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

CORE_DET

CMREF[1]

Comp0,2 connect with Zo=27.4ohm, make

trace length shorter than 0.5"

Comp1,3 connect with Zo=55ohm, make

trace length shorter than 0.5"

R177

R177

*1K_4

*1K_4

R178

R178

*1K_4

*1K_4

MISC

MISC

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

+1.05V

H_DPWR#

H_D#[63:0] 5

H_DSTBN#2 5

H_DSTBP#2 5

H_DINV#2 5

H_D#[63:0] 5

H_DSTBN#3 5

H_DSTBP#3 5

H_DINV#3 5

R163 27.4/F_4R163 27.4/F_4

R153 54.9/F_4R153 54.9/F_4

R186 27.4/F_4R186 27.4/F_4

R190 54.9/F_4R190 54.9/F_4

H_DPRSTP# 5

H_DPSLP# 5

H_DPWR# 5

H_PWRGOOD 5

H_CPUSLP# 5

T34T34

R172

R172

1K/F_4

1K/F_4

EXTGBREF

R185

R185

2K/F_4

2K/F_4

1u/10V_4

1u/10V_4

03

+1.05V

R238

R238

1K/F_4

1K/F_4

CPU_CMREF

R234

R234

C330

2K/F_4

2K/F_4

Layout note:

Zo=55ohm, 0.5"

max for GTLREF

1

C330

0.1u/10V_4

0.1u/10V_4

Prescott

Prescott

Prescott

3 36Wednesday, April 15, 2009

3 36Wednesday, April 15, 2009

3 36Wednesday, April 15, 2009

C291

C291

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1A

1A

1A

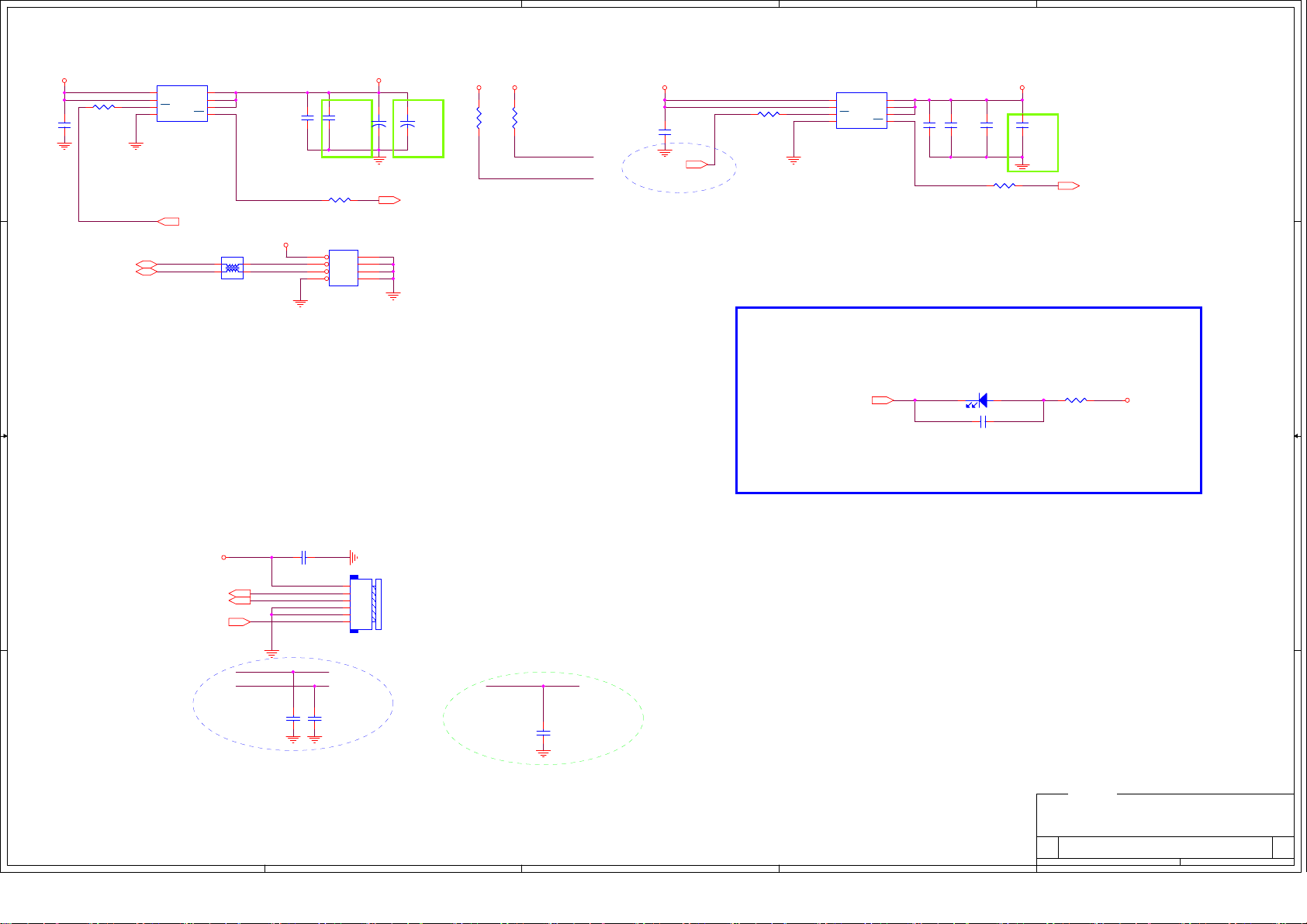

Page 4

5

4

3

2

1

CPU-2

U22D

U22D

A2

VSS1

A4

VSS2

A8

VSS4

A15

VSS5

A18

VSS6

A19

VSS7

A20

VSS8

B1

VSS9

B2

D D

C C

B B

VSS10

B5

VSS11

B8

VSS12

B13

VSS13

B20

VSS14

B21

VSS15

C8

VSS16

C17

VSS17

D1

VSS18

D5

VSS19

D8

VSS20

D14

VSS21

D18

VSS22

D21

VSS23

E3

VSS24

E6

VSS25

E7

VSS26

E8

VSS27

E15

VSS28

E16

VSS29

E19

VSS30

F4

VSS31

F5

VSS32

F6

VSS33

F7

VSS34

F17

VSS35

F18

VSS36

G1

VSS37

G4

VSS38

G7

VSS39

G9

VSS41

G13

VSS42

G21

VSS45

H3

VSS46

H4

VSS48

H7

VSS49

H9

VSS51

H13

VSS52

H16

VSS53

H18

VSS54

H19

VSS55

J5

VSS56

J7

VSS57

J9

VSS58

J13

VSS59

J17

VSS60

K1

VSS61

K6

VSS62

K7

VSS63

K9

VSS64

K13

VSS65

K15

VSS66

K21

VSS67

L3

VSS68

L4

VSS69

L5

VSS70

L6

VSS71

L7

VSS72

L9

VSS73

L13

VSS74

L15

VSS75

L18

VSS76

L19

VSS77

M1

VSS78

M5

VSS79

M7

VSS80

M9

VSS81

M13

VSS82

M21

VSS83

N4

VSS84

Diamondville_SC_Rev1

Diamondville_SC_Rev1

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

N5

N7

N9

N13

N17

P3

P4

P5

P6

P7

P9

P13

P15

P16

P18

P19

R1

R5

R7

R9

R13

R21

T4

T5

T7

T9

T10

T11

T12

T13

T18

U3

U6

U7

U15

U16

U19

V1

V4

V6

V7

V8

V13

V14

V18

V21

W1

W5

W8

W11

W14

W17

W21

Y1

Y2

Y20

Y21

AA2

AA3

AA4

AA7

AA10

AA12

.

.

AA15

AA18

AA19

AA20

<NO_STUFF>

<NO_STUFF>

+1.05V

V10

3A

+VCC_CORE

A10

A11

A12

B10

B11

B12

C10

C11

C12

D10

D11

D12

E10

E11

E12

F10

F11

F12

G10

G11

G12

H10

H11

H12

J10

J11

J12

K10

K11

K12

L10

L11

L12

M10

M11

M12

N10

N11

N12

P10

P11

P12

R10

R11

R12

U22C

U22C

VCCF

A9

VCCQ1

B9

VCCQ2

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VCCP27

VCCP28

VCCP29

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

VCCP35

VCCP36

VCCP37

VCCP38

VCCP39

VCCP40

VCCP41

VCCP42

VCCP43

VCCP44

VCCP45

Diamondville_SC_Rev1

Diamondville_SC_Rev1

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VCCPC64

VCCPC63

VCCPC62

VCCPC61

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

C9

D9

E9

F8

F9

G8

G14

H8

H14

J8

J14

K8

K14

L8

L14

M8

M14

N8

N14

P8

P14

R8

R14

T8

T14

U8

U9

U10

U11

U12

U13

U14

F14

F13

E14

E13

D7

F15

D16

E18

G15

G16

E17

G18

C13

D13

+VCC_CORE

130mA

+V1.5S_VCCA

C313

C313

0.1u/10V_4

0.1u/10V_4

.

.

C292

C292

0.1u/10V_4

0.1u/10V_4

C296

C296

1u/10V_4

1u/10V_4

ATOM

N280

N270

R315

R315

100/F_4

100/F_4

R316

R316

100/F_4

100/F_4

C276

C276

0.1u/10V_4

0.1u/10V_4

C344

C344

10u/6.3V_6

10u/6.3V_6

C312

C312

1u/10V_4

1u/10V_4

R226 *0_4/SR226 *0_4/S

C338

C338

10U/6.3V_6/S

10U/6.3V_6/S

2.5A

C339

C339

10u/6.3V_6

10u/6.3V_6

C271

C271

1u/10V_4

1u/10V_4

Vcore

+1.1V

+1.2V

+1.5V

VID0 33

VID1 33

VID2 33

VID3 33

VID4 33

VID5 33

VID6 33

+VCC_CORE

VCC_SENSE 33

VSS_SENSE 33

From CPU

H_THRMTRIP#3

C219

C219

1u/10V_4

1u/10V_4

PLACE IN CAVITY

C216

C216

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

C281

C281

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

C303

C248

C248

1u/10V_4

1u/10V_4

C303

1u/10V_4

1u/10V_4

C305

C305

1u/10V_4

1u/10V_4

PLACE IN CORRIDOR AND CLOSE TO CPU

C343

C218

C218

C286

C286

C337

C337

10u/6.3V_6

10u/6.3V_6

C293

C293

1u/10V_4

1u/10V_4

C331

C331

10u/6.3V_6

10u/6.3V_6

C306

C306

1u/10V_4

1u/10V_4

C343

10u/6.3V_6

10u/6.3V_6

C279

C279

1u/10V_4

1u/10V_4

C425

C425

10u/6.3V_6

10u/6.3V_6

C302

C302

1u/10V_4

1u/10V_4

PLACE IN CAVITY

HWPG3,12,20,29,30,31,32,36

+1.05V

R158

R158

56_4

56_4

R_THERMTRIP_PWR#

R165 33_4R165 33_4

R166 0_4R166 0_4

C308

C308

10u/6.3V_6

10u/6.3V_6

C217

C217

10u/6.3V_6

10u/6.3V_6

C290

C290

1u/10V_4

1u/10V_4

+1.05V

2

R179

R179

*1K_4

*1K_4

Q17

Q17

1 3

*MMBT3904

*MMBT3904

MBCLK218,29

MBDATA218,29

+1.05V

C272

C272

10u/6.3V_6

10u/6.3V_6

C332

C332

C426

C426

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

C275

C275

C304

C304

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

+5V

FAN_ON#28

3

Q18

Q18

*2N7002E

*2N7002E

1

2

To SYS 3/5V SHDN#

SI: C433 leave empty

+

+

C433

C433

*330u/2.5V_7343

*330u/2.5V_7343

C215

C215

10u/6.3V_6

10u/6.3V_6

C311

C311

C307

1u/10V_4

1u/10V_4

R248

R248

10K/F_4

10K/F_4

C307

1u/10V_4

1u/10V_4

R245

R245

10K/F_4

10K/F_4

C309

C309

1u/10V_4

1u/10V_4

R244 10K_4R244 10K_4

FAN_ON#

SYS_SHDN# 30

MCP_THERMTRIP# 5

+1.05V

C502

C502

10u/6.3V_6

10u/6.3V_6

SI add C502,C503 close C433

C314

C314

1u/10V_4

1u/10V_4

+3V

25mils

R256

R256

10K/F_4

10K/F_4

U14

U14

8

7

6

4

SYS_SHDN-1#

SCLK

SDA

ALERT#

OVERT#

G780P81U

G780P81U

ADDRESS: 98H

VCC

DXP

DXN

GND

C503

C503

0.1u/10V_4

0.1u/10V_4

1

2

3

5

1 3

C340

C340

.1U/10V_4

.1U/10V_4

C350

C350

*100P/50V_4

*100P/50V_4

Q12

Q12

MMBT3904-7-F

MMBT3904-7-F

2

H_THERMDA 3

H_THERMDC 3

D9

D9

2 1

RB501V-40

RB501V-40

R236 10K/F_4R236 10K/F_4

04

3920_RST# 29

ECPWROK 12,29

+3V

thermal shutdown circuit

del Q18,R179,Q17 in BOM for SI & add R166

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Diamondville CPU(POWER/GND THM)

Diamondville CPU(POWER/GND THM)

Diamondville CPU(POWER/GND THM)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

1

Prescott

Prescott

Prescott

4 36Wednesday, April 15, 2009

4 36Wednesday, April 15, 2009

4 36Wednesday, April 15, 2009

1A

1A

1A

Page 5

5

H_DSTBP#03

H_DSTBN#03

H_DINV#03

H_DSTBP#13

H_DSTBN#13

H_DINV#13

H_DSTBP#23

H_DSTBN#23

D D

+1.05V

R130

R130

R1171KR117

*1K

*1K

1K

CPU_BSEL03

CPU_BSEL13

CPU_BSEL23

C C

R131 *0_4R131 *0_4

R138 *0_4R138 *0_4

R125 *0_4R125 *0_4

H_BSEL0

H_BSEL1

H_BSEL2

R121

R121

100/F_4

100/F_4

2

R126

R126

100/F_4

100/F_4

ATOM CPU

N280(166MHZ)

Default

+1.05V

R119 62R119 62

R123 56_4R123 56_4

B B

+1.05V +1.05V

12

R118

R118

49.9/F

49.9/F

BCLK_VML_COMP_VDD

BCLK_VML_COMP_GND

12

A A

R133

R133

49.9/F

49.9/F

R127 56_4R127 56_4

R101 1KR101 1K

R164 62R164 62

N270(133MHZ)

H_RESET#

H_FERR#

MCP_THERMTRIP#

H_BR1#

H_BR0#

12

12

R120

R120

49.9/F

49.9/F

CPU_COMP_VCC

CPU_COMP_GND

12

R129

R129

49.9/F

49.9/F

+1.05V

1 2

0

1

BSEL[2..0]

0 1 1

0 0 1

L10

L10

BLM18PG181SN1D

BLM18PG181SN1D

RC0603

RC0603

C153

C153

4.7U/6.3V_6

4.7U/6.3V_6

H_DINV#23

H_DSTBP#33

H_DSTBN#33

H_DINV#33

H_A#[3..35]3

MCP_THERMTRIP#4

C154

C154

2.2U/6.3V_6

2.2U/6.3V_6

4

T40

CPU_DSTBP0*

U40

CPU_DSTBN0*

V41

CPU_DBI0*

W39

CPU_DSTBP1*

W37

CPU_DSTBN1*

V35

CPU_DBI1*

N37

CPU_DSTBP2*

L36

CPU_DSTBN2*

N35

CPU_DBI2*

M39

CPU_DSTBP3*

M41

CPU_DSTBN3*

J41

H_A#[3..35]

H_ADSTB#03

H_ADSTB#13

H_REQ#03

H_REQ#13

H_REQ#23

H_REQ#33

H_REQ#43

H_ADS#3

H_BNR#3

H_BR0#3

H_DBSY#3

H_DRDY#3

H_HIT#3

H_HITM#3

H_LOCK#3

H_TRDY#3

H_PROCHOT#3,33

H_FERR#3

H_RS#03

H_RS#13

H_RS#23

MCP_THERMTRIP#

H_FERR#

H_BSEL2

H_BSEL1

H_BSEL0

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_BR0#

H_BR1#

+V_PLL_CPU+V_PLL_CPU

BCLK_VML_COMP_VDD

BCLK_VML_COMP_GND

CPU_COMP_VCC

CPU_COMP_GND

+V_PLL_MCLK

20mA with RUN rail

CPU_DBI3*

AC34

CPU_A3*

AE38

CPU_A4*

AE34

CPU_A5*

AC37

CPU_A6*

AE37

CPU_A7*

AE35

CPU_A8*

AB35

CPU_A9*

AF35

CPU_A10*

AG35

CPU_A11*

AG39

CPU_A12*

AE33

CPU_A13*

AG37

CPU_A14*

AG38

CPU_A15*

AG34

CPU_A16*

AN38

CPU_A17*

AL39

CPU_A18*

AG33

CPU_A19*

AL33

CPU_A20*

AJ33

CPU_A21*

AN36

CPU_A22*

AJ35

CPU_A23*

AJ37

CPU_A24*

AJ36

CPU_A25*

AJ38

CPU_A26*

AL37

CPU_A27*

AL34

CPU_A28*

AN37

CPU_A29*

AJ34

CPU_A30*

AL38

CPU_A31*

AL35

CPU_A32*

AN34

CPU_A33*

AR39

CPU_A34*

AN35

CPU_A35*

AE36

CPU_ADSTB0*

AK35

CPU_ADSTB1*

AC38

CPU_REQ0*

AA33

CPU_REQ1*

AC39

CPU_REQ2*

AC33

CPU_REQ3*

AC35

CPU_REQ4*

AD42

CPU_ADS*

AD43

CPU_BNR*

AE40

CPU_BR0*

AL32

CPU_BR1*

AD39

CPU_DBSY*

AD41

CPU_DRDY*

AB42

CPU_HIT*

AD40

CPU_HITM*

AC43

CPU_LOCK*

AE41

CPU_TRDY*

E41

CPU_PECI

AJ41

CPU_PROCHOT*

AG43

CPU_THERMTRIP*

AH40

CPU_FERR*

F42

CPU_BSEL2

D42

CPU_BSEL1

F41

CPU_BSEL0

AC41

CPU_RS0*

AB41

CPU_RS1*

AC42

CPU_RS2*

AG27

+V_DLL_DLCELL_AVDD

AH27

+V_PLL_MCLK

AG28

+V_PLL_FSB

AH28

+V_PLL_CPU

AM39

BCLK_VML_COMP_VDD

AM40

BCLK_VML_COMP_GND

AM43

CPU_COMP_VCC

AM42

CPU_COMP_GND

I348

I348

+V_PLL_FSB

29mA with RUN rail

3

MCP79_MOBILE_BGA1437

MCP79_MOBILE_BGA1437

1 OF 11

1 OF 11

FSB

FSB

S

S

EC

EC

+V_PLL_CPU

15mA with RUN rail

SOCKETU19A

SOCKETU19A

CPU_D0*

CPU_D1*

CPU_D2*

CPU_D3*

CPU_D4*

CPU_D5*

CPU_D6*

CPU_D7*

CPU_D8*

CPU_D9*

CPU_D10*

CPU_D11*

CPU_D12*

CPU_D13*

CPU_D14*

CPU_D15*

CPU_D16*

CPU_D17*

CPU_D18*

CPU_D19*

CPU_D20*

CPU_D21*

CPU_D22*

CPU_D23*

CPU_D24*

CPU_D25*

CPU_D26*

CPU_D27*

CPU_D28*

CPU_D29*

CPU_D30*

CPU_D31*

CPU_D32*

CPU_D33*

CPU_D34*

CPU_D35*

CPU_D36*

CPU_D37*

CPU_D38*

CPU_D39*

CPU_D40*

CPU_D41*

CPU_D42*

CPU_D43*

CPU_D44*

CPU_D45*

CPU_D46*

CPU_D47*

CPU_D48*

CPU_D49*

CPU_D50*

CPU_D51*

CPU_D52*

CPU_D53*

CPU_D54*

CPU_D55*

CPU_D56*

CPU_D57*

CPU_D58*

CPU_D59*

CPU_D60*

CPU_D61*

CPU_D62*

CPU_D63*

CPU_BPRI*

CPU_DEFER*

BCLK_OUT_CPU_P

BCLK_OUT_CPU_N

BCLK_OUT_ITP_P

BCLK_OUT_ITP_N

BCLK_OUT_NB_P

BCLK_OUT_NB_N

BCLK_IN_N

BCLK_IN_P

CPU_A20M*

CPU_IGNNE*

CPU_INIT*

CPU_INTR

CPU_NMI

CPU_SMI*

CPU_PWRGD

CPU_RESET*

CPU_SLP*

CPU_DPSLP*

CPU_DPWR*

CPU_STPCLK*

CPU_DPRSTP*

2

H_D#0

Y43

H_D#1

W42

H_D#2

Y40

H_D#3

W41

H_D#4

Y39

H_D#5

V42

H_D#6

Y41

H_D#7

Y42

H_D#8

P42

H_D#9

U41

H_D#10

R42

H_D#11

T39

H_D#12

T42

H_D#13

T41

H_D#14

R41

H_D#15

T43

H_D#16

W35

H_D#17

AA37

H_D#18

W33

H_D#19

W34

H_D#20

AA36

H_D#21

AA34

H_D#22

AA38

H_D#23

AA35

H_D#24

U38

H_D#25

U36

H_D#26

U35

H_D#27

U33

H_D#28

U34

H_D#29

W38

H_D#30

R33

H_D#31

U37

H_D#32

N34

H_D#33

N33

H_D#34

R34

H_D#35

R35

H_D#36

P35

H_D#37

R39

H_D#38

R37

H_D#39

R38

H_D#40

L37

H_D#41

L39

H_D#42

L38

H_D#43

N36

H_D#44

N38

H_D#45

J39

H_D#46

J38

H_D#47

J37

H_D#48

L42

H_D#49

M42

H_D#50

P41

H_D#51

N41

H_D#52

N40

H_D#53

M40

H_D#54

H40

H_D#55

K42

H_D#56

H41

H_D#57

L41

H_D#58

H43

H_D#59

H42

H_D#60

K41

H_D#61

J40

H_D#62

H39

H_D#63

M43

AA41

AA40

CLK_CPU_BCLK

G42

CLK_CPU_BCLK#

G41

CLK_ITP_BCLK

AL43

CLK_ITP_BCLK#

AL42

BCLK_FEEDBACK_P

AL41

BCLK_FEEDBACK_N

AK42

Length must matching w/CLK_CPU_BCLK+220ps

AK41

AJ40

AF41

AH39

AH42

H_INTR

AF42

H_NMI

AG41

AH41

H_PWRGOOD

AH43

H_RESET#

H38

H_CPUSLP#

AM33

AN33

AM32

AG42

AN32

H_D#[0..63]

H_A20M# 3

H_IGNNE# 3

H_INIT# 3

H_INTR 3

H_NMI 3

H_SMI# 3

H_PWRGOOD 3

H_RESET# 3

H_CPUSLP# 3

H_DPSLP# 3

H_DPWR# 3

H_STPCLK# 3

H_DPRSTP# 3

H_D#[0..63] 3

H_BPRI# 3

H_DEFER# 3

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

CLK_ITP_BCLK 3

CLK_ITP_BCLK# 3

CLK_CPU_BCLK

CLK_CPU_BCLK#

12

C209

C209

*12P/50V_4

*12P/50V_4

1

05

12

C208

C208

*12P/50V_4

*12P/50V_4

+V_DLL_DLCELL_AVDD

1. Route at normal impedance and 8 mils

spacing to resistor.

2. 49.9 ohm to GND or VTT_CPU less than 1 inch

from MCP79.

5

4

150mA with RUN rail

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP79(HOST)

MCP79(HOST)

MCP79(HOST)

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

PROJECT :

1

Prescott

Prescott

Prescott

5 36Wednesday, April 15, 2009

5 36Wednesday, April 15, 2009

5 36Wednesday, April 15, 2009

1B

1B

1B

Page 6

5

D D

C C

PCIE Layout Notice:

M

CP79 BGA Breakout (<27ps):

Route at 50 ohm impedance and 1.5x dielectric height spacing.

After Breakout:

Route at 50 Signal end and 90 ohm differential.

Inter-pair spacing 4x (Microstrip) dielectric height spacing 3x (Stripline)

dielectric height spacing.

WLAN

WLAN

WWAN

+1.05V

B B

+1.05V

430mA with RUN rail 1200mA with RUN rail

C171

1U/6.3V_4

1U/6.3V_4

L5

L5

BLM18PG181SN1D

BLM18PG181SN1D

RC0603

RC0603

1 2

C171

C97

C97

4.7U/6.3V_6

4.7U/6.3V_6

C117

C117

2.2U/6.3V_6

2.2U/6.3V_6

4

PCIE_CLK_REQ0#26

PCIE_CLK_REQ1#26

PE_WAKE#(Internal PU)

PCIE_WAKE#26

PCIE_RXP026

PCIE_RXP126

PCIE_RXN126

C179

C179

C119

1U/6.3V_4

1U/6.3V_4

C119

.1U/10V_4

.1U/10V_4

161mA with RUN rail

+1.1V_PE_PLL

C78

C78

2.2U/6.3V_6

2.2U/6.3V_6

12

C101

C101

.1U/10V_4

.1U/10V_4

PE_CLK_COMP

R60

R60

*2.37K/F_4

*2.37K/F_4

3

U19E SOCKET

U19E SOCKET

F7

PE0_RX0_P

E7

PE0_RX0_N

D7

PE0_RX1_P

C7

PE0_RX1_N

E6

PE0_RX2_P

F6

PE0_RX2_N

E5

PE0_RX3_P

F5

PE0_RX3_N

E4

PE0_RX4_P

E3

PE0_RX4_N

C3

PE0_RX5_P

D3

PE0_RX5_N

G5

PE0_RX6_P

H5

PE0_RX6_N

J7

PE0_RX7_P

J6

PE0_RX7_N

J5

PE0_RX8_P

J4

PE0_RX8_N

L11

PE0_RX9_P

L10

PE0_RX9_N

L9

PE0_RX10_P

L8

PE0_RX10_N

L7

PE0_RX11_P

L6

PE0_RX11_N

N11

PE0_RX12_P

N10

PE0_RX12_N

N9

PE0_RX13_P

P9

PE0_RX13_N

N7

PE0_RX14_P

N6

PE0_RX14_N

N5

PE0_RX15_P

N4

PE0_RX15_N

C9

PE0_PRSNT_16#

D5

PEB_CLKREQ#/GPIO_49

D9

PEB_PRSNT#

E8

PEC_CLKREQ#/GPIO_50

C10

PEC_PRSNT#

M15

PED_CLKREQ#/GPIO_51

B10

PED_PRSNT#

L16

PEE_CLKREQ#/GPIO_16

L18

PEE_PRSNT#/GPIO_46

M16

PEF_CLKREQ#/GPIO_17

M18

PEF_PRSNT#/GPIO_47

M17

PEG_CLKREQ#/GPIO_18

M19

PEG_PRSNT#/GPIO_48

F17

PE_WAKE#

K9

PE1_RX0_P

J9

PE1_RX0_N

H9

PE1_RX1_P

G9

PE1_RX1_N

F9

PE1_RX2_P

E9

PE1_RX2_N

H7

PE1_RX3_P

G7

PE1_RX3_N

T17

+DVDD0_PEX

W19

+DVDD0_PEX

U17

+DVDD0_PEX

V19

+DVDD0_PEX

W16

+DVDD0_PEX

W17

+DVDD0_PEX

W18

+DVDD0_PEX

U16

+DVDD0_PEX

T19

+DVDD1_PEX

U19

+DVDD1_PEX

T16

+V_PLL_PEX

A11

PE_CLK_COMP

I165

I165

MCP79_MOBILE_BGA1437

MCP79_MOBILE_BGA1437

SEC 5 OF 11

SEC 5 OF 11

PCIE

PCIE

PE0_TX0_P

PE0_TX0_N

PE0_TX1_P

PE0_TX1_N

PE0_TX2_P

PE0_TX2_N

PE0_TX3_P

PE0_TX3_N

PE0_TX4_P

PE0_TX4_N

PE0_TX5_P

PE0_TX5_N

PE0_TX6_P

PE0_TX6_N

PE0_TX7_P

PE0_TX7_N

PE0_TX8_P

PE0_TX8_N

PE0_TX9_P

PE0_TX9_N

PE0_TX10_P

PE0_TX10_N

PE0_TX11_P

PE0_TX11_N

PE0_TX12_P

PE0_TX12_N

PE0_TX13_P

PE0_TX13_N

PE0_TX14_P

PE0_TX14_N

PE0_TX15_P

PE0_TX15_N

PE0_REFCLK_P

PE0_REFCLK_N

PE1_REFCLK_P

PE1_REFCLK_N

PE2_REFCLK_P

PE2_REFCLK_N

PE3_REFCLK_P

PE3_REFCLK_N

PE4_REFCLK_P

PE4_REFCLK_N

PE5_REFCLK_P

PE5_REFCLK_N

PE6_REFCLK_P

PE6_REFCLK_N

PE_RST0#

PE1_TX0_P

PE1_TX0_N

PE1_TX1_P

PE1_TX1_N

PE1_TX2_P

PE1_TX2_N

PE1_TX3_P

PE1_TX3_N

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD0_PEX

+AVDD1_PEX

+AVDD1_PEX

+AVDD1_PEX

C5

D4

C4

B4

A4

A3

B3

B2

C1

D1

D2

E1

E2

F2

F3

F4

G3

H4

H3

H2

H1

J1

J2

J3

K2

K3

L4

L3

M4

M3

M2

M1

E11

D11

G11

F11

J11

J10

G13

F13

J13

H13

L14

K14

N14

M14

K11

D8

C8

B8

A8

A7

B7

B6

C6

Y12

AA12

AB12

M12

P12

R12

N12

T12

U12

AC12

AD12

V12

W12

M13

N13

P13

PE_RESET#_C

PCIE_TX0_P_C

PCIE_TX0_N_C

PCIE_TX1_P_C

PCIE_TX1_N_C

+AVDD_PEX

C60

C60

.1U/10V_4

.1U/10V_4

C63

C63

1U/6.3V_4

1U/6.3V_4

.1U/10V_4

.1U/10V_4

C62

C62

2

CLK_PCIE_WLAN 26

CLK_PCIE_WLAN# 26

CLK_PCIE_WWAN 26

CLK_PCIE_WWAN# 26

R53 0_4R53 0_4

C39 0.1U/10VC39 0.1U/10V

1 2

C38 0.1U/10VC38 0.1U/10V

1 2

C37 0.1U/10VC37 0.1U/10V

1 2

C36 0.1U/10VC36 0.1U/10V

1 2

C61

C61

1U/6.3V_4

1U/6.3V_4

C71

C71

2.2U/6.3V_6

2.2U/6.3V_6

PE_RESET#

L8

L8

1 2

BLM21PG600SN1D

BLM21PG600SN1D

C77

C77

10U/6.3V_6/S

10U/6.3V_6/S

PCIE_TXP0 26

PCIE_TXN0 26PCIE_RXN026

PCIE_TXP1 26

PCIE_TXN1 26

1

06

PE_RESET# 26

WLAN

WWAN

+1.05V

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP79(PCIE)

MCP79(PCIE)

MCP79(PCIE)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

1

Prescott

Prescott

Prescott

6 36Wednesday, April 15, 2009

6 36Wednesday, April 15, 2009

6 36Wednesday, April 15, 2009

1B

1B

1B

Page 7

5

4

3

2

1

R104

R104

1.47K/F

1.47K/F

C182

C182

.1U/10V_4

.1U/10V_4

RGMII_PWRDWN

PHY_RST#

12

R82

R82

*4.7K

*4.7K

C184

C184

.1U/10V_4

.1U/10V_4

12

R295

R295

150/F

150/F

07

+3VLANVCC

+3V

12

C202

C202

4.7U/6.3V_6

4.7U/6.3V_6

R85

R85

10K_4

10K_4

MII_RXER23

Unstuff for MII mode

MII_RXD[0..3]23

D D

+1.05V_LAN

12

L9

L9

BLM18PG181SN1D

BLM18PG181SN1D

RC0603

RC0603

MII_COL23

MII_CRS23

SI changed to short PAD. R92, R89, R98, R287

Reservation by EMI

MII_RXD0

MII_RXD1

MII_RXD2

MII_RXCLK23

MII_RXCTL23 MII_TXD[0..3] 23

MII_RXD3

R286 *47K_4R286 *47K_4

9mA with RUN rail

C159

C159

4.7U/6.3V_6

4.7U/6.3V_6

Layout Notice:

124 ohm +-1% to GND and within 750 mils

of MCP79.

C C

B B

0.01uF to GND and within 500 mils of

MCP79.

+1.8V

C152

C152

2.2U/6.3V_6

2.2U/6.3V_6

190mA with RUN rail

+3VLANVCC

C172

C172

2.2U/6.3V_6

2.2U/6.3V_6

+1.05V

2.2U/6.3V_6

2.2U/6.3V_6

R293 49.9/FR293 49.9/F

R291 49.9/FR291 49.9/F

R303 124/FR303 124/F

C421 0.01U/16VC421 0.01U/16V

HDMI_CEC24

LCD_BKL_CTL20

LCD_BKL_ON20

LCD_ENVDD20

HDMI_TXC_P24

HDMI_TXC_N24

HDMI_TX_P024

HDMI_TX_N024

HDMI_TX_P124

HDMI_TX_N124

HDMI_TX_P224

HDMI_TX_N224

R111 22K/F_4R111 22K/F_4

C168

C168

.1U/10V_4

.1U/10V_4

R96 0_4R96 0_4

95mA with RUN rail

C102

C102

C94

C94

2.2U/6.3V_6

2.2U/6.3V_6

HDMI_HPLUG_DET24

MII_RXER

MII_COL

MII_CRS

R92 *0_4/SR92 *0_4/S

R89 *0_4/SR89 *0_4/S

R98 *0_4/SR98 *0_4/S

R287 *0_4/SR287 *0_4/S

R88 *0_4/SR88 *0_4/S

R285 *0_4R285 *0_4

R289 *0_4R289 *0_4

R284 *0_4R284 *0_4

1 2

1 2

1 2

1 2

1 2

+VDD_IFPB can

be connect to

GND if IFPB not

used.

12

MII_RXD0_MCP

MII_RXD1_MCP

MII_RXD2_MCP

MII_RXD3_MCP

MII_RXCLK_MCP

MII_RXER

MII_COL

MII_CRS

R80 10K_4R80 10K_4

+1.05V_DUAL_PLL_MAC

MII_COMP_VDD

MII_COMP_GND

RGB_DAC_RSET

RGB_DAC_VREF

HDMI_TXC_P

HDMI_TXC_N

HDMI_TX_P0

HDMI_TX_N0

HDMI_TX_P1

HDMI_TX_N1

HDMI_TX_P2

HDMI_TX_N2

HPLUG_DET2

+VDD_IFPB

+V_PLL_IFPAB

HDMI_REST

HDMI_VPROBE

C169

C169

R106

R106

1K_4

1K_4

*.1U/10V_4

*.1U/10V_4

U19F

U19F

C23

RGMII_RXD0/MII_RXD0

B23

RGMII_RXD1/MII_RXD1

E24

RGMII_RXD2/MII_RXD2

A24

RGMII_RXD3/MII_RXD3

A23

RGMII_RXC/MII_RXCLK

C22

RGMII_RXCTL/MII_RXDV

F23

MII_RXER/GPIO_36

B26

MII_COL/GPIO_20/MSMB_DATA

B22

MII_CRS/GPIO_21/MSMB_CLK

J22

RGMII/MII_INTR/GPIO_35

T23

+V_DUAL_MACPLL

C27

MII_COMP_VDD

B27

MII_COMP_GND

C39

RGB_DAC_RSET

B38

RGB_DAC_VREF

E36

TV_DAC_RSET

A35

TV_DAC_VREF

C38

XTALIN_TV

D38

XTALOUT_TV

E16

GPIO_6/FERR/IGPU_GPIO_6#

B15

GPIO_7/NFERR/IGPU_GPIO_7#

G39

LCD_BKL_CTL/GPIO_57

E37

LCD_BKL_ON/GPIO_59

F40

LCD_PANEL_PWR/GPIO_58

D35

HDMI_TXC_P/ML0_LANE3_P

E35

HDMI_TXC_N/ML0_LANE3_N

G35

HDMI_TXD0_P/ML0_LANE2_P

F35

HDMI_TXD0_N/ML0_LANE2_N

F33

HDMI_TXD1_P/ML0_LANE1_P

G33

HDMI_TXD1_N/ML0_LANE1_N

J33

HDMI_TXD2_P/ML0_LANE0_P

H33

HDMI_TXD2_N/ML0_LANE0_N

D43

DP_AUX_CH0_P

C43

DP_AUX_CH0_N

C31

HPLUG_DET2/GPIO_22

F31

HPLUG_DET3

M27

+VDD_IFPA

M26

+VDD_IFPB

M28

+V_PLL_IFPAB

M29

+V_PLL_HDMI

T25

+VDD_HDMI

J31

HDMI_RSET

J30

HDMI_VPROBE

I202

I202

MCP79_MOBILE_BGA1437

MCP79_MOBILE_BGA1437

SEC 6 OF 11

SEC 6 OF 11

LAN

LAN

DACS

DACS

FLAT

FLAT

PANEL

PANEL

SOCKET

SOCKET

+3.3V_DUAL_RMGT

+3.3V_DUAL_RMGT

+V_DUAL_RMGT

+V_DUAL_RMGT

MII_VREF

RGMII_TXD0/MII_TXD0

RGMII_TXD1/MII_TXD1

RGMII_TXD2/MII_TXD2

RGMII_TXD3/MII_TXD3

RGMII_TXCLK/MII_TXCLK

RGMII_TXCTL/MII_TXEN

RGMII/MII_MDC

RGMII/MII_MDIO

RGMII/MII_PWRDWN#/GPIO_37

BUF_25MHZ

MII_RESET#

+V_RGB_DAC

+V_TV_DAC

DDC_CLK0

DDC_DATA0

RGB_DAC_RED

RGB_DAC_GREEN

RGB_DAC_BLUE

RGB_DAC_HSYNC

RGB_DAC_VSYNC

TV_DAC_RED

TV_DAC_GREEN

TV_DAC_BLUE

TV_DAC_HSYNC/GPIO_44

TV_DAC_VSYNC/GPIO_45

IFPA_TXC_P

IFPA_TXC_N

IFPA_TXD0_P

IFPA_TXD0_N

IFPA_TXD1_P

IFPA_TXD1_N

IFPA_TXD2_P

IFPA_TXD2_N

IFPA_TXD3_P

IFPA_TXD3_N

IFPB_TXC_P

IFPB_TXC_N

IFPB_TXD4_P

IFPB_TXD4_N

IFPB_TXD5_P

IFPB_TXD5_N

IFPB_TXD6_P

IFPB_TXD6_N

IFPB_TXD7_P

IFPB_TXD7_N

DDC_CLK2/GPIO_23

DDC_DATA2/GPIO_24

DDC_CLK3

DDC_DATA3

IFPAB_RSET

IFPAB_VPROBE

+3V

J24

K24

U23

V23

MII_VREF

E28

MII_TXD0_MCP

B24

MII_TXD1_MCP

C24

MII_TXD2_MCP

C25

MII_TXD3_MCP

D25

MII_TXCLK_R

D24

MII_TXCTRL_R

C26

Add R501 in SI BOM & SCH

D21

MII_MDIO

C21

RGMII_PWRDWN

G23

RGMII_25M_R

E23

PHY_RST#

J23

+V_RGB_DAC+V_RGB_DAC+V_RGB_DAC

J32

K32

B31

A31

CRT_R_R

B39

CRT_G_R

A39

CRT_B_R

B40

DAC_HSY

A40

DAC_VSY

A41

A36

B36

C36

D36

C37

SI add C~ for EMI

B35

C35

B32

A32

D32

C32

D33

C33

B34

C34

L31

K31

J29

H29

L29

K29

L30

K30

N30

M30

LCD_DDCCLK

C30

LCD_DDCDAT

B30

HDMI_DDCCLK_MCP

D31

HDMI_DDCDATA_MCP

E31

E32

G31

IFPAB_VPROBE

C130

C130

C413

C413

4.7U/6.3V_6

4.7U/6.3V_6

.1U/10V_4

.1U/10V_4

R288 22_4R288 22_4

R290 22_4R290 22_4

R95 22_4R95 22_4

R97 22_4R97 22_4

R91 22_4R91 22_4

R501 22_4R501 22_4

R93 *22_4R93 *22_4

SI del R93 for EMI

R296 0_4R296 0_4

R297 0_4R297 0_4

R299 0_4R299 0_4

R301 22_4R301 22_4

R302 22_4R302 22_4

Reserved by EMI

TXLCLKOUT+ 20

TXLCLKOUT- 20

TXLOUT0+ 20

TXLOUT0- 20

TXLOUT1+ 20

TXLOUT1- 20

TXLOUT2+ 20

TXLOUT2- 20

R110 0_4R110 0_4

T9T9

R108 0_4R108 0_4

264mA with ALW rail264mA with ALW rail

C139

C139

.1U/10V_4

.1U/10V_4

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

MII_TXCLK

MII_TXCTL

MII_MDC 23

MII_MDIO 23

MII_25M 23

PHY_RST# 23

DDCCLK 25

DDCDATA 25

CRT_R 25

CRT_G 25

CRT_B 25

HSYNC_COM 25

VSYNC_COM 25

Reserved by EMI

MII_TXD0

C149 22P/50V_4C149 22P/50V_4

MII_TXD1

C166 22P/50V_4C166 22P/50V_4

MII_TXD2

C155 22P/50V_4C155 22P/50V_4

MII_TXD3

C412 22P/50V_4C412 22P/50V_4

MII_TXCLK

C411 22P/50V_4C411 22P/50V_4

MII_TXCTL

C501 22P/50V_4C501 22P/50V_4

Add C501 in SI BOM & SCH

Reserved by EMI

C193

C193

*22P/50V_4

*22P/50V_4

12

R112

R112

*1K_4

*1K_4

+1.05V_LAN+3VLANVCC

C137

C137

2.2U/6.3V_6

2.2U/6.3V_6

MII_TXCLK 23

MII_TXCTL 23

MCP79 Strapping

MII_TXD0

Networking Select

MII(100M)

RGMII(GIGA)01

CRT_R_R

CRT_G_R

CRT_B_R

Layout Note:

Place 150 ohm

termination resistors

close to MCP79.

HDMI_DDCCLK 24

HDMI_DDCDATA 24

C194

C194

*22P/50V_4

*22P/50V_4

+3VLANVCC

12

MII_VREF

12

R105

R105

1.47K/F

1.47K/F

+3VLANVCC

R90

R90

*10K_4

*10K_4

R94

R94

10K_4

10K_4

206mA with RUN rail

+V_RGB_DAC

C185

C185

.1U/10V_4

.1U/10V_4

12

R300

R300

150/F

150/F

L14

L14

BLM18PG181SN1D

BLM18PG181SN1D

RC0603

RC0603

12

R298

R298

150/F

150/F

12

12

R99

R99

R100

A A

+3V

R304 0_6R304 0_6

5

8mA with RUN rail

+V_PLL_IFPAB

C183

C424

C424

4.7U/6.3V_6

4.7U/6.3V_6

C183

.1U/10V_4

.1U/10V_4

C180

C180

.1U/10V_4

.1U/10V_4

LCD_DDCCLK

LCD_DDCDAT

4

3

2.7K/F

2.7K/F

R100

2.7K/F

2.7K/F

LCD_DDCCLK 20

LCD_DDCDAT 20

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP79(MII/LVDS/HDMI)

MCP79(MII/LVDS/HDMI)

MCP79(MII/LVDS/HDMI)

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

1

Prescott

Prescott

Prescott

7 36Wednesday, April 15, 2009

7 36Wednesday, April 15, 2009

7 36Wednesday, April 15, 2009

1B

1B

1B

Page 8

5

MCP79_MOBILE_BGA1437

MCP79_MOBILE_BGA1437

SEC 2 OF 11

DDR_A_D63

AL8

AW5

AN10

AW9

AP11

AW6

AU11

AV11

AV13

AW13

AR11

AT11

AR14

AU13

AR26

AU25

AT27

AU27

AP25

AR25

AP27

AR27

AP29

AR29

AP31

AR31

AV27

AN29

AV29

AN31

AU31

AR33

AV37

AW37

AT31

AV31

AT37

AU37

AW39

AV39

AR37

AR38

AV38

AW38

AR35

AP35

AR10

AN13

AN27

AW29

AV35

AR34

AL9

AP9

AN9

AL6

AL7

AN6

AN7

AR6

AR7

AV6

AR5

AU6

AV5

AU7

AU8

AY5

AU9

AV9

AN5

AU5

MDQ0_63

MDQ0_62

MDQ0_61

MDQ0_60

MDQ0_59

MDQ0_58

MDQ0_57

MDQ0_56

MDQ0_55

MDQ0_54

MDQ0_53

MDQ0_52

MDQ0_51

MDQ0_50

MDQ0_49

MDQ0_48

MDQ0_47

MDQ0_46

MDQ0_45

MDQ0_44

MDQ0_43

MDQ0_42

MDQ0_41

MDQ0_40

MDQ0_39

MDQ0_38

MDQ0_37

MDQ0_36

MDQ0_35

MDQ0_34

MDQ0_33

MDQ0_32

MDQ0_31

MDQ0_30

MDQ0_29

MDQ0_28

MDQ0_27

MDQ0_26

MDQ0_25

MDQ0_24

MDQ0_23

MDQ0_22

MDQ0_21

MDQ0_20

MDQ0_19

MDQ0_18

MDQ0_17

MDQ0_16

MDQ0_15

MDQ0_14

MDQ0_13

MDQ0_12

MDQ0_11

MDQ0_10

MDQ0_9

MDQ0_8

MDQ0_7

MDQ0_6

MDQ0_5

MDQ0_4

MDQ0_3

MDQ0_2

MDQ0_1

MDQ0_0

MDQM0_7

MDQM0_6

MDQM0_5

MDQM0_4

MDQM0_3

MDQM0_2

MDQM0_1

MDQM0_0

I704

I704

DDR_A_D62 DDR_B_D62

DDR_A_D61

DDR_A_D60

DDR_A_D59

DDR_A_D58

D D

C C

DDR_A_DM[0..7]16,17

B B

DDR_A_D57

DDR_A_D56

DDR_A_D55

DDR_A_D54

DDR_A_D53

DDR_A_D52

DDR_A_D51

DDR_A_D50

DDR_A_D49

DDR_A_D48

DDR_A_D47

DDR_A_D46

DDR_A_D45

DDR_A_D44

DDR_A_D43

DDR_A_D42

DDR_A_D41

DDR_A_D40

DDR_A_D39

DDR_A_D38

DDR_A_D37

DDR_A_D36

DDR_A_D35

DDR_A_D34

DDR_A_D33

DDR_A_D32

DDR_A_D31

DDR_A_D30

DDR_A_D29

DDR_A_D28

DDR_A_D27

DDR_A_D26

DDR_A_D25

DDR_A_D24

DDR_A_D23

DDR_A_D22

DDR_A_D21

DDR_A_D20

DDR_A_D19

DDR_A_D18

DDR_A_D17

DDR_A_D16

DDR_A_D15

DDR_A_D14

DDR_A_D13

DDR_A_D12

DDR_A_D11

DDR_A_D10

DDR_A_D9

DDR_A_D8

DDR_A_D7

DDR_A_D6

DDR_A_D5

DDR_A_D4

DDR_A_D3

DDR_A_D2

DDR_A_D1

DDR_A_D0

DDR_A_DM7

DDR_A_DM6

DDR_A_DM5

DDR_A_DM4

DDR_A_DM3

DDR_A_DM2

DDR_A_DM1

DDR_A_DM0

SEC 2 OF 11

MEMORY

MEMORY

PARTITION 0

PARTITION 0

MEMORY CONTROL 0A

MEMORY CONTROL 0A

SOCKETU19B

SOCKETU19B

MDQS0_7_N

MDQS0_6_N

MDQS0_5_N

MDQS0_4_N

MDQS0_3_N

MDQS0_2_N

MDQS0_1_N

MDQS0_0_N

MCLK0A_2_P

MCLK0A_2_N

MCLK0A_1_P

MCLK0A_1_N

MCLK0A_0_P

MCLK0A_0_N

MDQS0_7_P

MDQS0_6_P

MDQS0_5_P

MDQS0_4_P

MDQS0_3_P

MDQS0_2_P

MDQS0_1_P

MDQS0_0_P

MRAS0*

MCAS0*

MWE0*

MBA0_2

MBA0_1

MBA0_0

MA0_14

MA0_13

MA0_12

MA0_11

MA0_10

MA0_9

MA0_8

MA0_7

MA0_6

MA0_5

MA0_4

MA0_3

MA0_2

MA0_1

MA0_0

MCS0A_1*

MCS0A_0*

MODT0A_1

MODT0A_0

MCKE0A_1

MCKE0A_0

4

DDR_A_DQS[0..7] 16,17

DDR_A_DQS#[0..7] 16,17

DDR_A_DQS7

AL10

DDR_A_DQS#7

AL11

DDR_A_DQS6

AR8

DDR_A_DQS#6

AR9

DDR_A_DQS5

AW7

DDR_A_DQS#5

AW8

DDR_A_DQS4

AP13

DDR_A_DQS#4

AR13

DDR_A_DQS3

AV25

DDR_A_DQS#3

AW25

DDR_A_DQS2

AU30

DDR_A_DQS#2

AU29

DDR_A_DQS1

AT35

DDR_A_DQS#1

AU35

DDR_A_DQS0

AU39

DDR_A_DQS#0

AT39

AV17

AP17

AR17

AP23

AP19

AW17

AR23

AU15

AN23

AW21

AN19

AV21

AR22

AU21

AP21

AR21

AN21

AV19

AU19

AT19

AR19

AW33

AV33

BA24

AY24

BB20

BC20

AT15

AR18

AP15

AV15

AU23

AT23

DDR_A_BS2

DDR_A_BS1

DDR_A_BS0

DDR_A_MA14

DDR_A_MA13

DDR_A_MA12

DDR_A_MA11

DDR_A_MA10

DDR_A_MA9

DDR_A_MA8

DDR_A_MA7

DDR_A_MA6

DDR_A_MA5

DDR_A_MA4

DDR_A_MA3

DDR_A_MA2

DDR_A_MA1

DDR_A_MA0

DDR_A_RAS# 16,17,18

DDR_A_CAS# 16,17,18

DDR_A_WE# 16,17,18 DDR_B_WE# 15

DDR_A_BS[0..2] 16,17,18

DDR_A_MA[0..14] 16,17,18

DDR_A_CLK_1 18

DDR_A_CLK_1# 18

DDR_A_CLK_0 16,17,18

DDR_A_CLK_0# 16,17,18

DDR_CS1_DIMMA# 18

DDR_CS0_DIMMA# 16,17,18

DDR_ODT1_DIMMA 18

DDR_ODT0_DIMMA 16,17,18

DDR_CKE0_DIMMA 16,17,18

3

U19C

U19C

MCP79_MOBILE_BGA1437

MDQ1_63

MDQ1_62

MDQ1_61

MDQ1_60

MDQ1_59

MDQ1_58

MDQ1_57

MDQ1_56

MDQ1_55

MDQ1_54

MDQ1_53

MDQ1_52

MDQ1_51

MDQ1_50

MDQ1_49

MDQ1_48

MDQ1_47

MDQ1_46

MDQ1_45

MDQ1_44

MDQ1_43

MDQ1_42

MDQ1_41

MDQ1_40

MDQ1_39

MDQ1_38

MDQ1_37

MDQ1_36

MDQ1_35

MDQ1_34

MDQ1_33

MDQ1_32

MDQ1_31

MDQ1_30

MDQ1_29

MDQ1_28

MDQ1_27

MDQ1_26

MDQ1_25

MDQ1_24

MDQ1_23

MDQ1_22

MDQ1_21

MDQ1_20

MDQ1_19

MDQ1_18

MDQ1_17

MDQ1_16

MDQ1_15

MDQ1_14

MDQ1_13

MDQ1_12

MDQ1_11

MDQ1_10

MDQ1_9

MDQ1_8

MDQ1_7

MDQ1_6

MDQ1_5

MDQ1_4

MDQ1_3

MDQ1_2

MDQ1_1

MDQ1_0

MDQM1_7

MDQM1_6

MDQM1_5

MDQM1_4

MDQM1_3

MDQM1_2

MDQM1_1

MDQM1_0

I705

I705

MCP79_MOBILE_BGA1437

SEC 3 OF 11

SEC 3 OF 11

DDR_B_D[0..63]15DDR_A_D[0..63]16,17

DDR_B_D63

AT4

AT3

DDR_B_D61

AV2

DDR_B_D60

AV3

DDR_B_D59

AR4

DDR_B_D58

AR3

DDR_B_D57

AU2

DDR_B_D56

AU3

DDR_B_D55

AY4

DDR_B_D54

AY3

DDR_B_D53

BB3

DDR_B_D52

BC3

DDR_B_D51

AW4

DDR_B_D50

AW3

DDR_B_D49

BA3

DDR_B_D48

BB2

DDR_B_D47

BB5

DDR_B_D46

BA5

DDR_B_D45

BA8

DDR_B_D44

BC8

DDR_B_D43

BB4

DDR_B_D42

BC4

DDR_B_D41

BA7

DDR_B_D40

AY8

DDR_B_D39

BA9

DDR_B_D38

BB10

DDR_B_D37

BB12

DDR_B_D36

AW12

DDR_B_D35

BB8

DDR_B_D34

BB9

DDR_B_D33

AY12

DDR_B_D32

BA12

DDR_B_D31

BC32

DDR_B_D30

AW32

DDR_B_D29

BA35

DDR_B_D28

AY36

DDR_B_D27

BA32

DDR_B_D26

BB32

DDR_B_D25

BA34

DDR_B_D24

AY35

DDR_B_D23

BC36

DDR_B_D22

AW36

DDR_B_D21

BA39

DDR_B_D20

AY40

DDR_B_D19

BA36

DDR_B_D18

BB36

DDR_B_D17

BA38

DDR_B_D16

AY39

DDR_B_D15

BB40

DDR_B_D14

AW40

DDR_B_D13

AV42

DDR_B_D12

AV41

DDR_B_D11

BA40

DDR_B_D10

BC40

DDR_B_D9

AW42

DDR_B_D8

AW41

DDR_B_D7

AT40

DDR_B_D6

AT41

DDR_B_D5

AP41

DDR_B_D4

AN40

DDR_B_D3

AU40

DDR_B_D2

AU41

DDR_B_D1

AR41

DDR_B_D0

AP42

DDR_B_DM7

AT5

DDR_B_DM6

BA2

DDR_B_DM5

AY7

DDR_B_DM4

BA11

DDR_B_DM3

BB34

DDR_B_DM2

BB38

DDR_B_DM1

AY43

DDR_B_DM0

AR42

DDR_B_DM[0..7]15

MEMORY

MEMORY

PARTITION 1

PARTITION 1

MEMORY CONTROL 1A

MEMORY CONTROL 1A

2

SOCKET

SOCKET

MDQS1_7_P

MDQS1_7_N

MDQS1_6_P

MDQS1_6_N

MDQS1_5_P

MDQS1_5_N

MDQS1_4_P

MDQS1_4_N

MDQS1_3_P

MDQS1_3_N

MDQS1_2_P

MDQS1_2_N

MDQS1_1_P

MDQS1_1_N

MDQS1_0_P

MDQS1_0_N

MRAS1*

MCAS1*

MWE1*

MBA1_2

MBA1_1

MBA1_0

MA1_14

MA1_13

MA1_12

MA1_11

MA1_10

MA1_9

MA1_8

MA1_7

MA1_6

MA1_5

MA1_4

MA1_3

MA1_2

MA1_1

MA1_0

MCLK1A_2_P

MCLK1A_2_N

MCLK1A_1_P

MCLK1A_1_N

MCLK1A_0_P

MCLK1A_0_N

MCS1A_1*

MCS1A_0*

MODT1A_1

MODT1A_0

MCKE1A_1

MCKE1A_0

AT2

AT1

AY2

AY1

BB6

BA6

BA10

AY11

BB33

BA33

BB37

BA37

BA43

AY42

AT42

AT43

AW16

BA15

BA16

BB29

BB18

BB17

BA29

BA14

AW28

BC28

BA17

BB28

AY28

BA28

AY27

BA27

BA26

BB26

BA25

BB25

BA18

BA42

BB42

BB22

BA22

BA19

AY19

BB14

BB16

BB13

AY15

AY31

BB30

DDR_B_DQS7

DDR_B_DQS#7

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_BS2

DDR_B_BS1

DDR_B_BS0

DDR_B_MA14

DDR_B_MA13

DDR_B_MA12

DDR_B_MA11

DDR_B_MA10

DDR_B_MA9

DDR_B_MA8

DDR_B_MA7

DDR_B_MA6

DDR_B_MA5

DDR_B_MA4

DDR_B_MA3

DDR_B_MA2

DDR_B_MA1

DDR_B_MA0

DDR_B_DQS[0..7] 15

DDR_B_DQS#[0..7] 15

DDR_B_RAS# 15

DDR_B_CAS# 15

DDR_B_BS[0..2] 15

DDR_B_MA[0..14] 15

DDR_B_CLK_1 15

DDR_B_CLK_1# 15

DDR_B_CLK_0 15

DDR_B_CLK_0# 15

DDR_CS1_DIMMB# 15

DDR_CS0_DIMMB# 15

DDR_ODT1_DIMMB 15

DDR_ODT0_DIMMB 15

DDR_CKE1_DIMMB 15DDR_CKE1_DIMMA 18

DDR_CKE0_DIMMB 15

1

08

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP79(MEM)

MCP79(MEM)

MCP79(MEM)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

1

Prescott

Prescott

Prescott

8 36Wednesday, April 15, 2009

8 36Wednesday, April 15, 2009

8 36Wednesday, April 15, 2009

1B

1B

1B

Page 9

5

4

3

2

1

C98

C98

.1U/10V_4

.1U/10V_4

C107

C107

.1U/10V_4

.1U/10V_4

09

+1.5VSUS

4.77A with ALW rail for S0

318mA for S0 Idle

U19D

U19D

MCP79_MOBILE_BGA1437

MCP79_MOBILE_BGA1437

SEC 4 OF 11

SEC 4 OF 11

AU33

D D

+V_VPLL

39mA with RUN rail

+V_PLL_DP

12mA with RUN rail

+1.05V

C C

Route "MEM_COMP_VDD" &

" MEM_COMP_GND" as 8mil

width

*47P/50V_4

*47P/50V_4

+V_PLL_XREF_XS

17mA with RUN rail

+V_PLL_CORE

19mA with RUN rail

L11

L11

BLM18PG181SN1D

BLM18PG181SN1D

RC0603

RC0603

1 2

+1.5VSUS

C161

C161

.1U/10V_4

.1U/10V_4

+V_PLL_XREF

*47P/50V_4

*47P/50V_4

C225

C225

C163

C163

+V_PLL_XREF

C176

C176

4.7U/6.3V_6

4.7U/6.3V_6

R134 40.2/FR134 40.2/F

1 2

1 2

R132 40.2/FR132 40.2/F

C175

C175

4.7U/6.3V_6

4.7U/6.3V_6

C174

C174

2.2U/6.3V_6

2.2U/6.3V_6

MEM_COMP_VDD

MEM_COMP_GND

Request by HP RF

B B

AU34

BB24

BC24

BA21

BB21

AU17

AR15

AN17

AN15

AV23

AN25

U28

U27

AN41

AM41

AA22

AP12

G30

P10

V10

V34

AA39

AB22

AB7

AD22

AE20

AF24

AG24

AH35

AK7

AM28

AT25

AP30

AR36

AU10

BC21

AY9

BC9

D34

G32

H31

M38

N39

P33

P34

P37

P40

R36

R40

R43

AK11

T27

T28

T10

T6

W5

F28

F24

K7

M5

M6

M7

M9

N8

P4

P7

R5

T18

T20

T24

T26

MCLK0B_2_P

MCLK0B_2_N

MCLK0B_1_P

MCLK0B_1_N

MCLK0B_0_P

MCLK0B_0_N

MCS0B_0*

MCS0B_1*

MODT0B_0

MODT0B_1

MCKE0B_0

MCKE0B_1

+V_PLL_XREF_XS

+V_PLL_DP

+V_PLL_CORE

+V_VPLL

MEM_COMP_VDD

MEM_COMP_GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

I195

I195

SOCKET

SOCKET

MCLK1B_2_P

MCLK1B_2_N

MCLK1B_1_P

MCLK1B_1_N

MCLK1B_0_P

MCLK1B_0_N

MCS1B_0*

MCS1B_1*

MODT1B_0

MODT1B_1

MEMORY CONTROL 1B

MEMORY CONTROL 0B

MEMORY CONTROL 1B

MEMORY CONTROL 0B

MCKE1B_0

MCKE1B_1

MRESET0*

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

+VDD_MEM

BA41

BB41

AY23

BA23

BA20

AY20

BC16

BA13

AY16

BC13

BA30

BA31

AY32

AM17

AM19

AM21

AM23

AM25

AM27

AM29

AN16

BC29

AN20

AN24

AT17

AP16

AN22

AP20

AP24

AV16

AR16

AR20

AR24

AW15

AP22

AP18

AU16

AN18

AU24

AT21

AY29

AV24

AU20

AU22

AW27

BC17

AV20

AY17

AY18

AM15

AU18

AY25

AY26

AW19

AW24

BC25

AL30

AM31

T33

GND

T34

GND

T35

GND

T37

GND

T38

GND

T7

GND

T9

GND

U18

GND

U20

GND

U22

GND

MEM_RESET#

C120

C120

2.2U/6.3V_6

2.2U/6.3V_6

.1U/10V_4

.1U/10V_4

C133

C133

.1U/10V_4

.1U/10V_4

+1.5VSUS

C142

C142

R1031KR103

1K

C89

C89

.1U/10V_4

.1U/10V_4

MEM_RESET# 15,16

C93

C93

.1U/10V_4

.1U/10V_4

.1U/10V_4

.1U/10V_4

C100

C100

C151

C151

.1U/10V_4

.1U/10V_4

.1U/10V_4

.1U/10V_4

C106

C106

C178

C178

.1U/10V_4

.1U/10V_4

.1U/10V_4

.1U/10V_4

C165

C165

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP79(MEM_Power)

MCP79(MEM_Power)

MCP79(MEM_Power)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

1

Prescott

Prescott

Prescott

9 36Wednesday, April 15, 2009

9 36Wednesday, April 15, 2009

9 36Wednesday, April 15, 2009

1B

1B

1B

Page 10

5

4

3

2

1

5

4

3

2

1

5

4

3

2

1

10

+3V

PCI_DEVSEL#

PCI_INTY#

PCI_INTX#

PCI_REQ1#

+3V

PCI_TRDY#

PCI_FRAME#

PCI_REQ0#

U19G

U19G

PCI_REQ0#

PCI_REQ1#

BOID_414

BOID_514

D D

CLKRUN#

C C

B B

BOID_614

R277 10K_4R277 10K_4

CLKRUN#29

LPC_SERIRQ29

MCP89 AE2 is NC

BOID_4

BOID_5

BOID_6

+3V

PCI_INTW#

PCI_INTX#

PCI_INTY#

PCI_INTZ#

PCI_TRDY#

CLKRUN#

T2

PCI_REQ0#

V9

PCI_REQ1#/FANRPM2

T3

PCI_REQ2#/GPIO_40/RS232_DSR#

U9

PCI_REQ3#/GPIO_38/RS232_CTS#

T4

PCI_REQ4#/GPIO_52/RS232_SIN#

AC3

PCI_AD0

AE10

PCI_AD1

AC4

PCI_AD2

AE11

PCI_AD3

AB3

PCI_AD4

AC6

PCI_AD5

AB2

PCI_AD6

AC7

PCI_AD7

AC8

PCI_AD8

AA2

PCI_AD9

AC9

PCI_AD10

AC10

PCI_AD11

AC11

PCI_AD12

AA1

PCI_AD13

AA5

PCI_AD14

Y5

PCI_AD15

W3

PCI_AD16

W6

PCI_AD17

W4

PCI_AD18

W7

PCI_AD19

V3

PCI_AD20

W8

PCI_AD21

V2

PCI_AD22

W9

PCI_AD23

U3

PCI_AD24

W11

PCI_AD25

U2

PCI_AD26

U5

PCI_AD27

U1

PCI_AD28

U6

PCI_AD29

T5

PCI_AD30

U7

PCI_AD31

P2

PCI_INTW#

N3

PCI_INTX#

N2

PCI_INTY#

N1

PCI_INTZ#

Y3

PCI_TRDY#

AD11

PCI_CLKRUN#/GPIO_42

AE2

LPC_DRQ1#/GPIO_19

AE1

LPC_DRQ0#

AE6

LPC_SERIRQ

U24

GND

U26

GND

U39

GND

U4

GND

U8

GND

V16

GND

V17

GND

V18

GND

V20

GND

V22

GND

V24

GND

V26

GND

V27

GND

V28

GND

V33

GND

V37

GND

V4

GND

V40

GND

V7

GND

W20

GND

W22

GND

W24

GND

W36

GND

W40

GND

W43

GND

Y16

GND

Y17

GND

Y18

GND

Y19

GND

Y20

GND

Y22

GND

Y24

GND

Y25

GND

I120

I120

MCP79_MOBILE_BGA1437

MCP79_MOBILE_BGA1437

SEC 7 OF 11

SEC 7 OF 11

PCI

PCI

GND

GND

LPC

LPC

PCI_GNT4#/GPIO_53/RS232_SOUT#

LPC_PWRDWN#/GPIO_54/EXT_NMI#

SOCKET

SOCKET

PCI_GNT0#

PCI_GNT1#/FANCTL2

PCI_GNT2#/GPIO_41/RS232_DTR#

PCI_GNT3#/GPIO_39/RS232_RTS#

PCI_CBE0#

PCI_CBE1#

PCI_CBE2#

PCI_CBE3#

PCI_DEVSEL#

PCI_FRAME#

PCI_IRDY#

PCI_PERR#/GPIO_43/RS232_DCD#

PCI_PAR

PCI_SERR#

PCI_STOP#

PCI_PME#/GPIO_30

PCI_RESET0#

PCI_RESET1#

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLKIN

LPC_FRAME#

LPC_RESET0#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_CLK0

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

R3

U10

WWAN_OFF#

R4

RF_OFF#

U11

BT_OFF#

P3

AA3

AA6

AA11

W10

PCI_DEVSEL#

AA9

PCI_FRAME#

Y4

PCI_IRDY#

AA10

Y1

PCI_PERR#

AB9

PCI_SERR#

AA7

PCI_STOP#

Y2

PCI_PME#

T1

STR_EN#

R10

PCI_RESET1#

R11

PCI_CLK0

R6

R7

PCI_CLK2

R8

PCI_CLKIN

R9

Layout Notice:

Serise resistor placed within 500 mil of MCP79.

CP89 AE12 is NC

M

AD4

AE12

AE5

AD3

AD2

AD1

AD5

AE9

Y26

Y27

AB18

H34

AB20

AB21

AB23

AB24

AB25

AB26

AB27

AB28

AB34

AB37

AB4

AB40

AC22

AC36

AC40

AB33

AC5

AD16

AD17

AD18