Page 1

1

www.schematic-x.blogspot.com

2

3

4

5

6

7

8

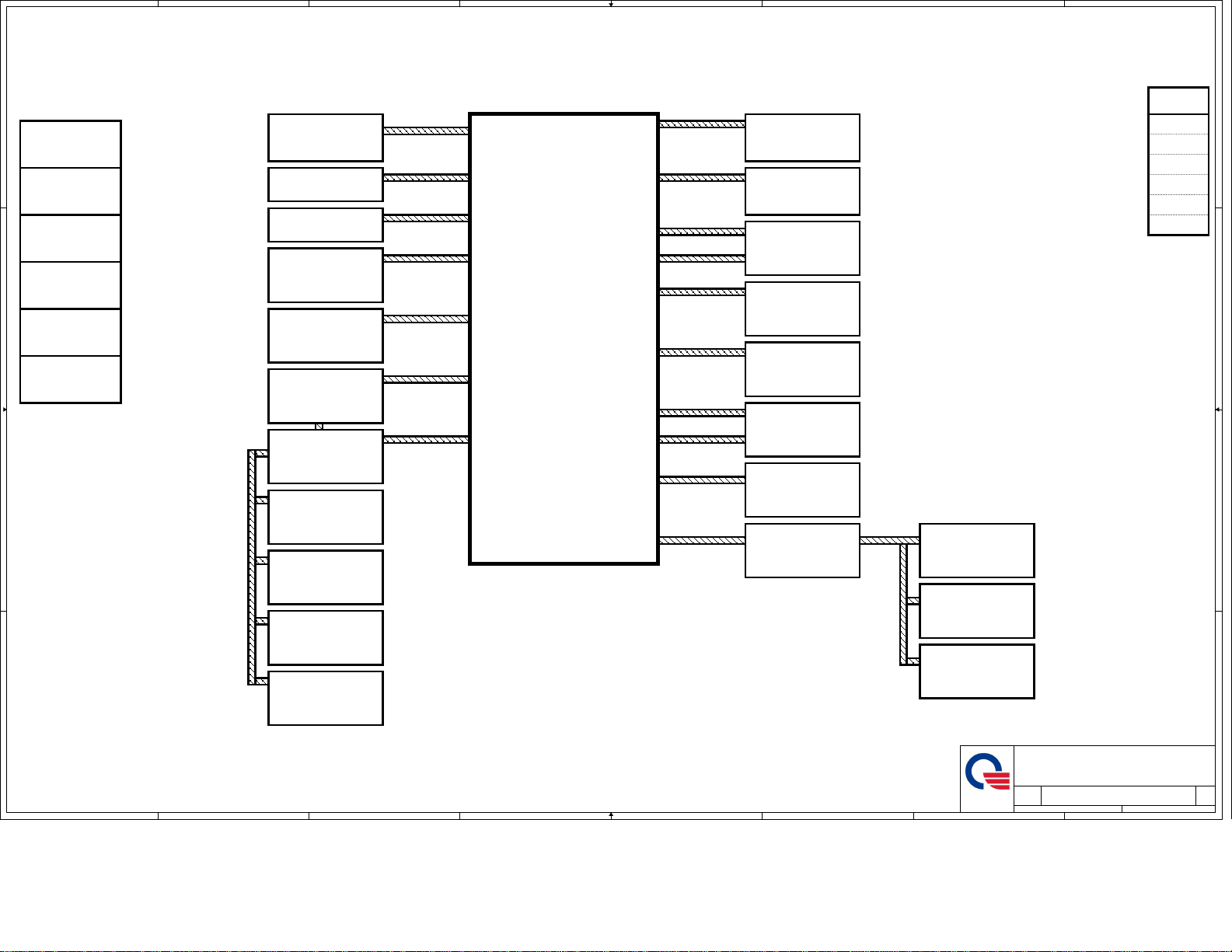

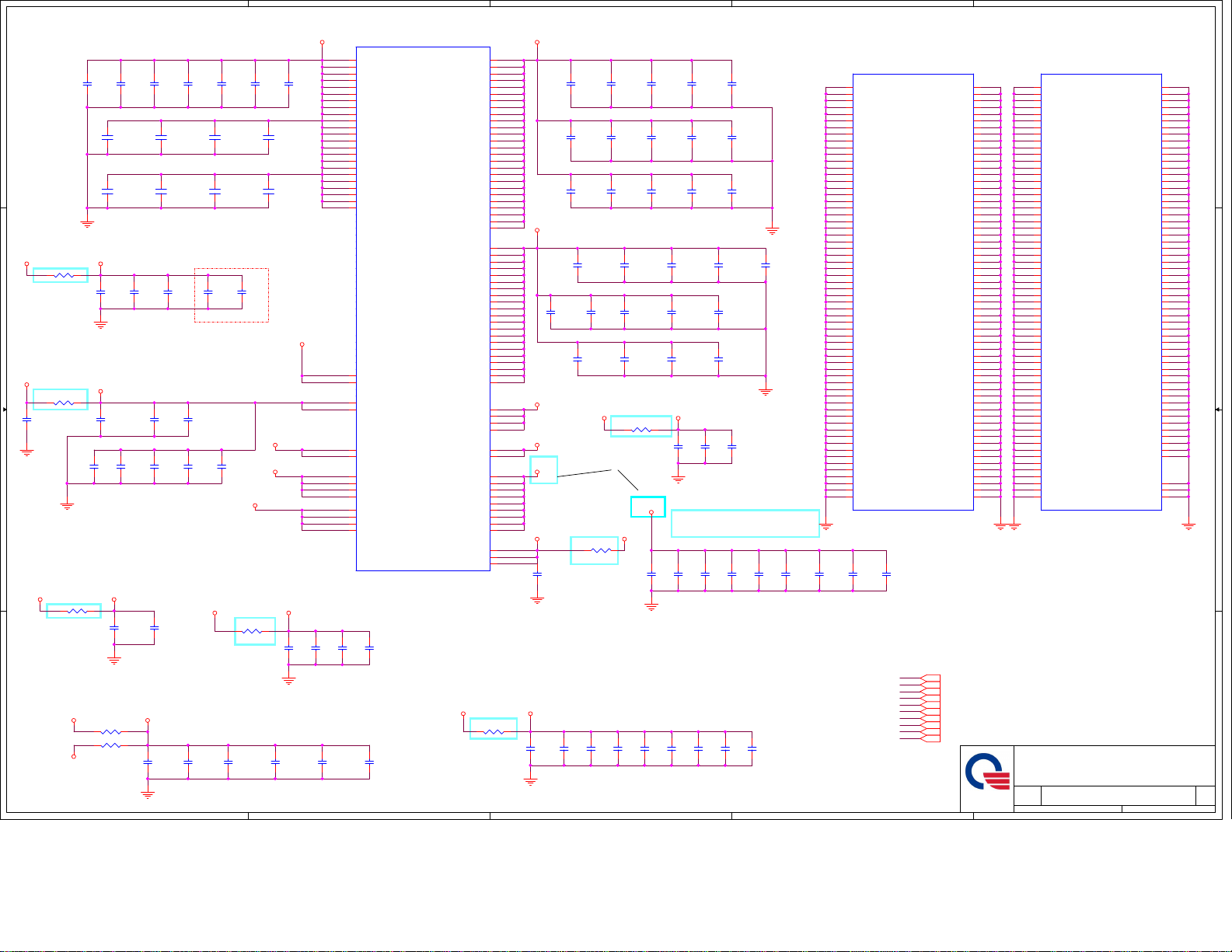

Y02 (HP Mario) AMD Temash Platform Block Diagram

A A

Charge

PG.23

DDR3L-1066 Memory Down

FBGA96 10*14mm

PG.8~9

DDR3L 1066MT/s

AMD Temash FT3

LVDS Interface

Port 0

24.5 X 24.5 (mm)

+3V/+5V S5

PG.24

+0.95V +1.5VS5

PG.25

DDR3L

PG.26

B B

CPU Core

PG.27~28

Dis-Charge

PG.29

C C

D D

TPM

PG.10

SATA HDD

PG.20

LAN Controller

RTL8166EH

10/100

PG.18

Card Reader

RTS5239GRT

SD/MMC

PG.14

System BIOS

APU SPI ROM

PG.5

KBC

ITE8528E/EX

PG.22

CPU FAN con.

PG.20

Keyboard con.

PG.19

Touch Pad con.

PG.19

SPI EC ROM

PG.22

LPC Interface

SATA0 6GB/s

PCI-E

Port 1

PCI-E

Port 3

SPI Interface

LPC Interface

769 BALL BGA

MAX 8.4W

PG.2~7

DDI (5.4Gb/s)

Port 1

USB 3.0

Port 0

USB 2.0

Port 8

USB 2.0

Port 0 ,Port 1

USB 2.0

Port 5

USB 2.0

Port 2

PCI-E

Port 0

Port 3

Azalia

LVDS single

PG.11

HDMI

PG.13

USB3.0/2.0 Combo

PG.17

USB2.0 Ports

PG.17

Camera

PG.11

WLAN Min-Card

BT COMBO

PG.21

Touch Screen

PG.14USB 2.0

Audio codec

ALC3227-CG

PG.15

Speaker

PG.15

DIGITAL MIC

PG.15

COMBO JACK

HP/MIC

PG.16

01

Stackup

TOP

GND

I

N1

IN2

VCC

BOT

1

2

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

BLOCK DIAGRAM

BLOCK DIAGRAM

NB5

NB5

3

4

5

6

NB5

7

BLOCK DIAGRAM

Date: Sheet of

Date: Sheet of

Date: Sheet of

1 30Tuesday, July 02, 2013

1 30Tuesday, July 02, 2013

1 30Tuesday, July 02, 2013

8

1A

1A

1A

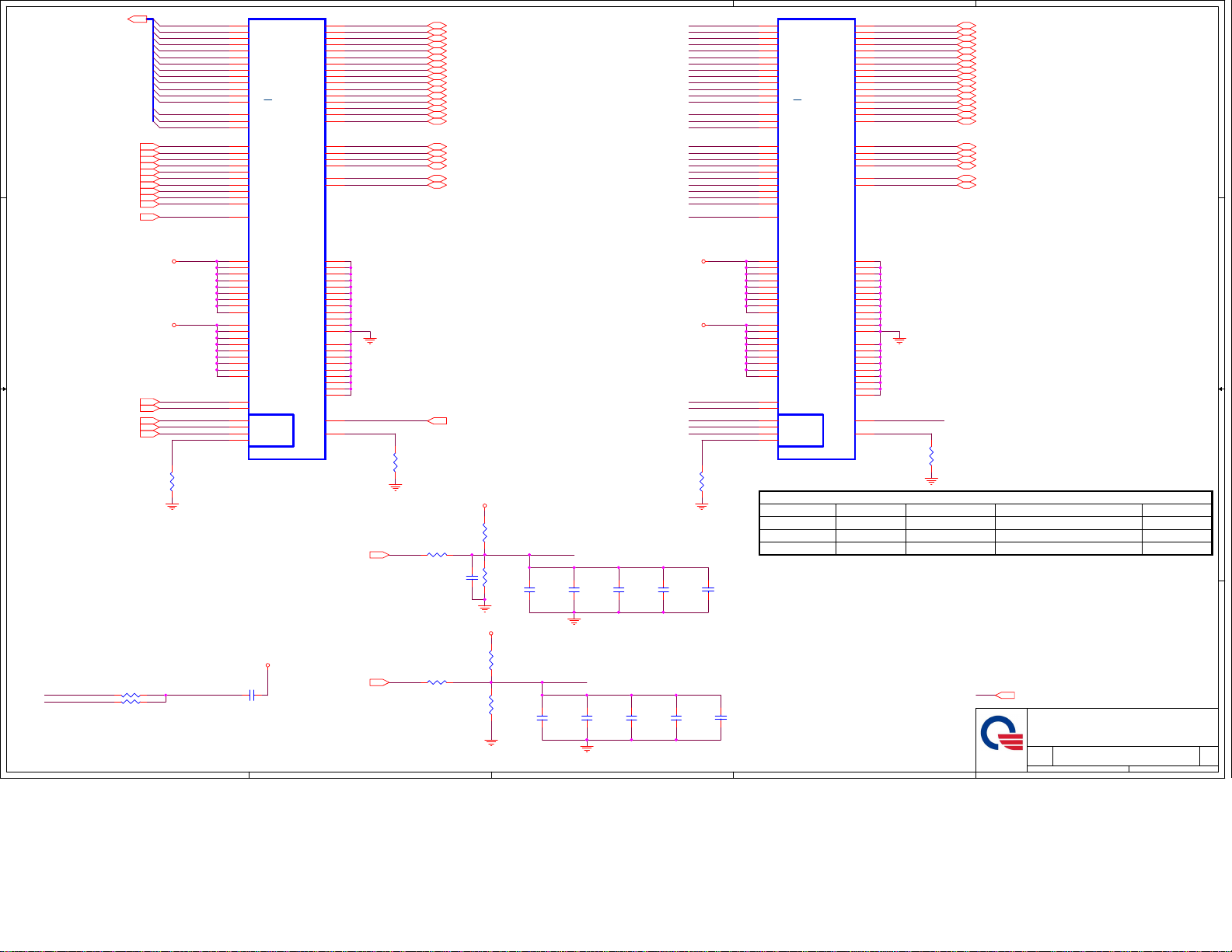

Page 2

5

4

3

2

1

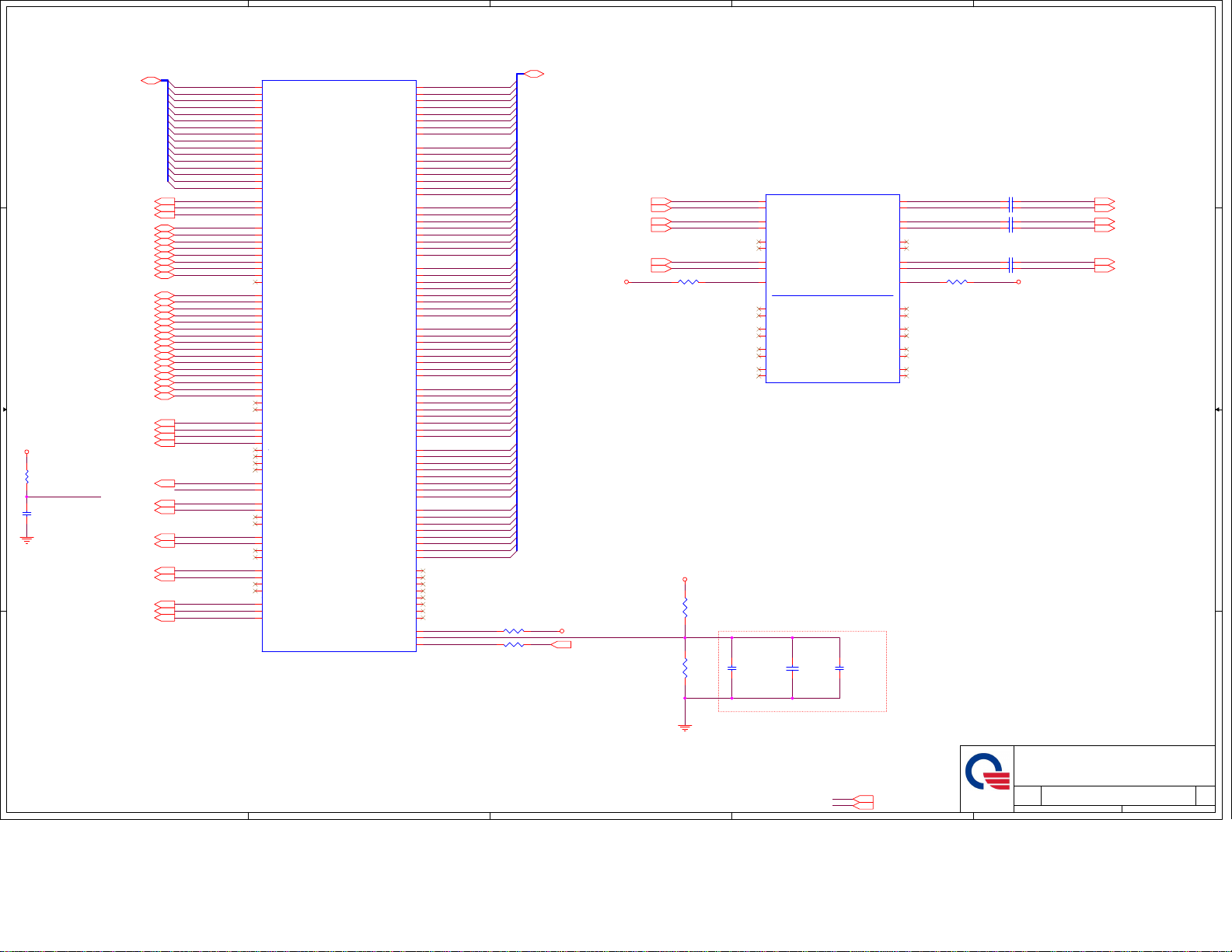

02

U23B

M_A_A[15:0](8,9)

D D

M_A_BS#0(8,9)

M_A_BS#1(8,9)

M_A_BS#2(8,9)

M_A_DM0(8)

M_A_DM1(8)

M_A_DM2(8)

M_A_DM3(8)

M_A_DM4(9)

M_A_DM5(9)

M_A_DM6(9)

M_A_DM7(9)

M_A_DQSP0(8)

M_A_DQSN0(8)

C C

+1.35VSUS

R140

1K_4

M_A_EVENT#

C123

B B

0.1U/10V/X7R_4

M_A_DQSP1(8)

M_A_DQSN1(8)

M_A_DQSP2(8)

M_A_DQSN2(8)

M_A_DQSP3(8)

M_A_DQSN3(8)

M_A_DQSP4(9)

M_A_DQSN4(9)

M_A_DQSP5(9)

M_A_DQSN5(9)

M_A_DQSP6(9)

M_A_DQSN6(9)

M_A_DQSP7(9)

M_A_DQSN7(9)

M_A_CLKP0(8)

M_A_CLKN0(8)

M_A_CLKP1(9)

M_A_CLKN1(9)

DDR3_DRAMRST#(8,9)

M_A_CKE0(8,9)

M_A_CKE1(8,9)

M_A_ODT0(8,9)

M_A_ODT1(8,9)

M_A_CS#0(8,9)

M_A_CS#1(8,9)

M_A_RAS#(8,9)

M_A_CAS#(8,9)

M_A_WE#(8,9)

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_EVENT#

AG38

W35

W38

W34

AG34

AN34

AJ38

AG35

AG40

AN41

AY40

AY34

AH41

AH40

AP41

AP40

BA40

AY41

AY33

BA34

AA40

AC35

AC34

AA34

AA32

AE38

AE37

AA37

AA38

AE34

AN38

AU38

AN37

AR37

AJ34

AR38

AL38

AN35

AJ37

AL34

AL35

U38

U37

U34

R35

R38

N38

R34

N37

L38

L35

N34

B32

B38

G40

N41

Y40

B33

A33

B40

A40

H41

H40

P41

P40

Y41

G38

L34

J38

J37

J34

Kabini

M_ADD0

M_ADD1

M_ADD2

M_ADD3

M_ADD4

M_ADD5

M_ADD6

M_ADD7

M_ADD8

M_ADD9

M_ADD10

M_ADD11

M_ADD12

M_ADD13

M_ADD14

M_ADD15

M_BANK0

M_BANK1

M_BANK2

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_DM8

M_DQS_H0

M_DQS_L0

M_DQS_H1

M_DQS_L1

M_DQS_H2

M_DQS_L2

M_DQS_H3

M_DQS_L3

M_DQS_H4

M_DQS_L4

M_DQS_H5

M_DQS_L5

M_DQS_H6

M_DQS_L6

M_DQS_H7

M_DQS_L7

M_DQS_H8

M_DQS_L8

M_CLK_H0

M_CLK_L0

M_CLK_H1

M_CLK_L1

M_CLK_H2

M_CLK_L2

M_CLK_H3

M_CLK_L3

M_RESET_L

M_EVENT_L

M0_CKE0

M0_CKE1

M1_CKE0

M1_CKE1

M0_ODT0

M0_ODT1

M1_ODT0

M1_ODT1

M0_CS_L0

M0_CS_L1

M1_CS_L0

M1_CS_L1

M_RAS_L

M_CAS_L

M_WE_L

KABINI

PART 2 OF 9

MEMORY I/F

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_CHECK0

M_CHECK1

M_CHECK2

M_CHECK3

M_CHECK4

M_CHECK5

M_CHECK6

M_CHECK7

M_ZVDDIO_MEM_S

M_VREF

M_VREFDQ

B30

A32

B35

A36

B29

A30

A34

B34

B37

A38

D40

D41

B36

A37

B41

C40

F40

F41

K40

K41

E40

E41

J40

J41

M41

N40

T41

U40

L40

M40

R40

T40

AF40

AF41

AK40

AK41

AE40

AE41

AJ40

AJ41

AM41

AN40

AT41

AU40

AL40

AM40

AR40

AT40

AV41

AW40

BA38

AY37

AU41

AV40

AY39

AY38

BA36

AY35

BA32

AY31

BA37

AY36

BA33

AY32

V41

W40

AB40

AC40

U41

V40

AA41

AB41

AD41

AD40

AC38

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

+M_ZVDDIO

M_VREF

M_VREFDQ_R

R325 39.2/J_4

R152 *0_4

M_A_DQ[0..63] (8,9)

PCIE_RXP0_WLAN(21)

PCIE_RXN0_WLAN(21)

PCIE_RXP1_LAN(18)

PCIE_RXN1_LAN(18)

PCIE_RXP3_CARD(14)

PCIE_RXN3_CARD(14)

+1.1V_CLK +1.1V_CLK

Temash use 0.95V

+1.35VSUS

SMDDR_VREF_DQ0_M1 (8,9)

0521 :

Change net name

from +M_VREFDQ to SMDDR_VREF_DQ0_M1

R150 1.69K/F_4 R155 1K

U23A

Kabini

PCIE_RXP0_WLAN

PCIE_RXN0_WLAN

PCIE_RXP1_LAN

PCIE_RXN1_LAN

PCIE_RXP3_CARD PCIE_TXP3_CARD_L

PCIE_RXN3_CARD

+1.35VSUS

R146

1K_4

R145

1K_4

R10

P_GPP_RXP0

R8

P_GPP_RXN0

R5

P_GPP_RXP1

R4

P_GPP_RXN1

N5

P_GPP_RXP2

N4

P_GPP_RXN2

N10

P_GPP_RXP3

N8

P_GPP_RXN3

W8

P_TX_ZVDD_095

L5

P_GFX_RXP0

L4

P_GFX_RXN0

J5

P_GFX_RXP1

J4

P_GFX_RXN1

G5

P_GFX_RXP2

G4

P_GFX_RXN2

D7

P_GFX_RXP3

E7

P_GFX_RXN3

C118

0.1U/10V/X7R_4

1 2

C117

1U/6.3V_4

KABINI

PART 1 OF 9

PCIE I/F

P_RX_ZVDD_095

GFX

C119

*1U/6.3V_4

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

L2

PCIE_TXP0_WLAN_L

L1

PCIE_TXN0_WLAN_L

K2

PCIE_TXP1_LAN_L

K1

PCIE_TXN1_LAN_L

J2

J1

H2

H1

PCIE_TXN3_CARD_L

W7

G2

G1

F2

F1

E2

E1

D2

D1

C368 0.1U/10V/X7R_4

C370 0.1U/10V/X7R_4

C373 0.1U/10V/X7R_4

C371 0.1U/10V/X7R_4

C375 0.1U/10V/X7R_4

C374 0.1U/10V/X7R_4

Temash use 0.95V

PCIE_TXP0_WLAN (21)

PCIE_TXN0_WLAN (21)

PCIE_TXP1_LAN (18)

PCIE_TXN1_LAN (18)

PCIE_TXP3_CARD (14)

PCIE_TXN3_CARD (14)

A A

5

4

3

Place within 1000mil of the APU

2

+1.35VSUS (6,8,9,26)

+1.1V_CLK (6)

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

NB5

NB5

NB5

Date: Sheet of

Tuesday, July 02, 2013 2 30

Date: Sheet of

Tuesday, July 02, 2013 2 30

Date: Sheet of

Tuesday, July 02, 2013 2 30

MEM/PCIE (1/6)

MEM/PCIE (1/6)

MEM/PCIE (1/6)

1

1A

1A

1A

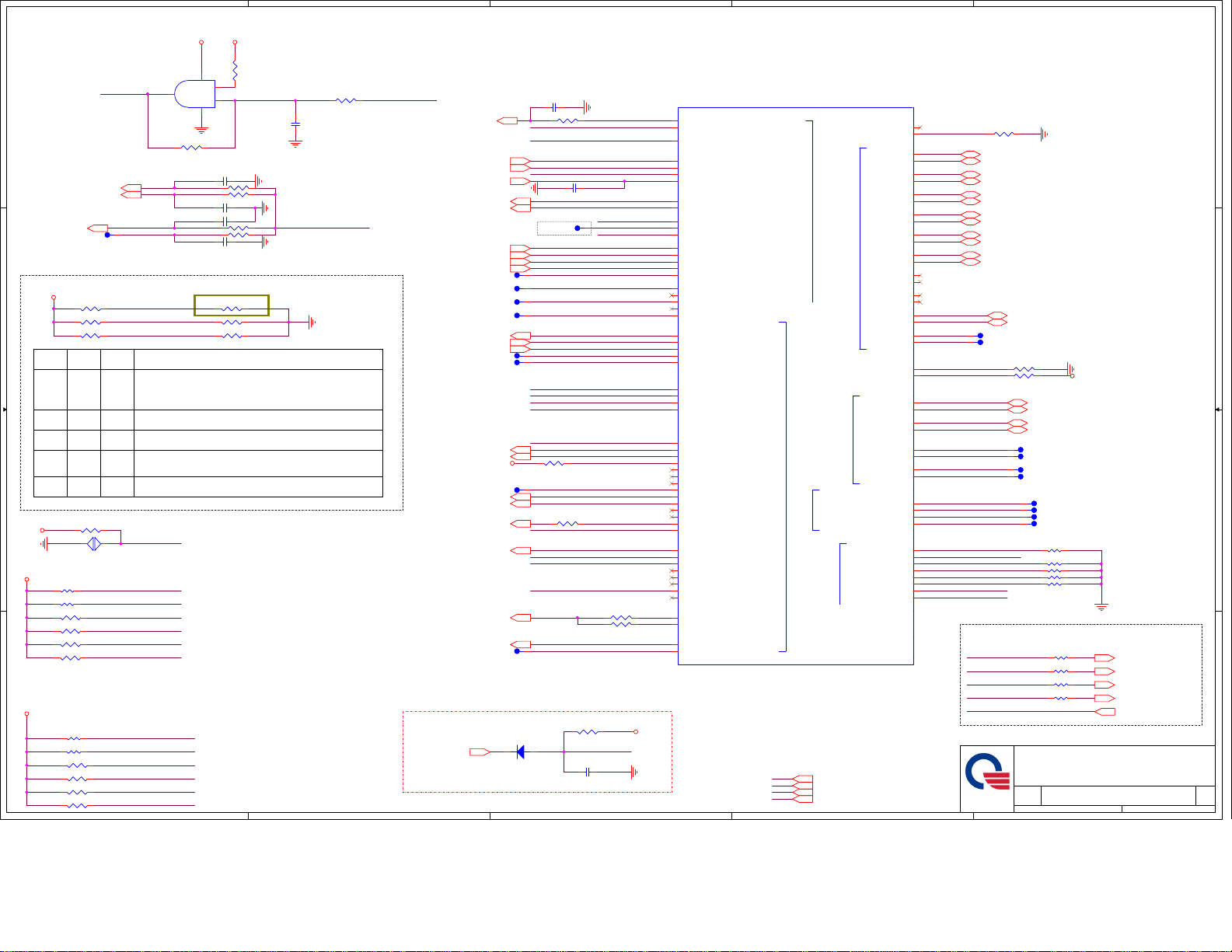

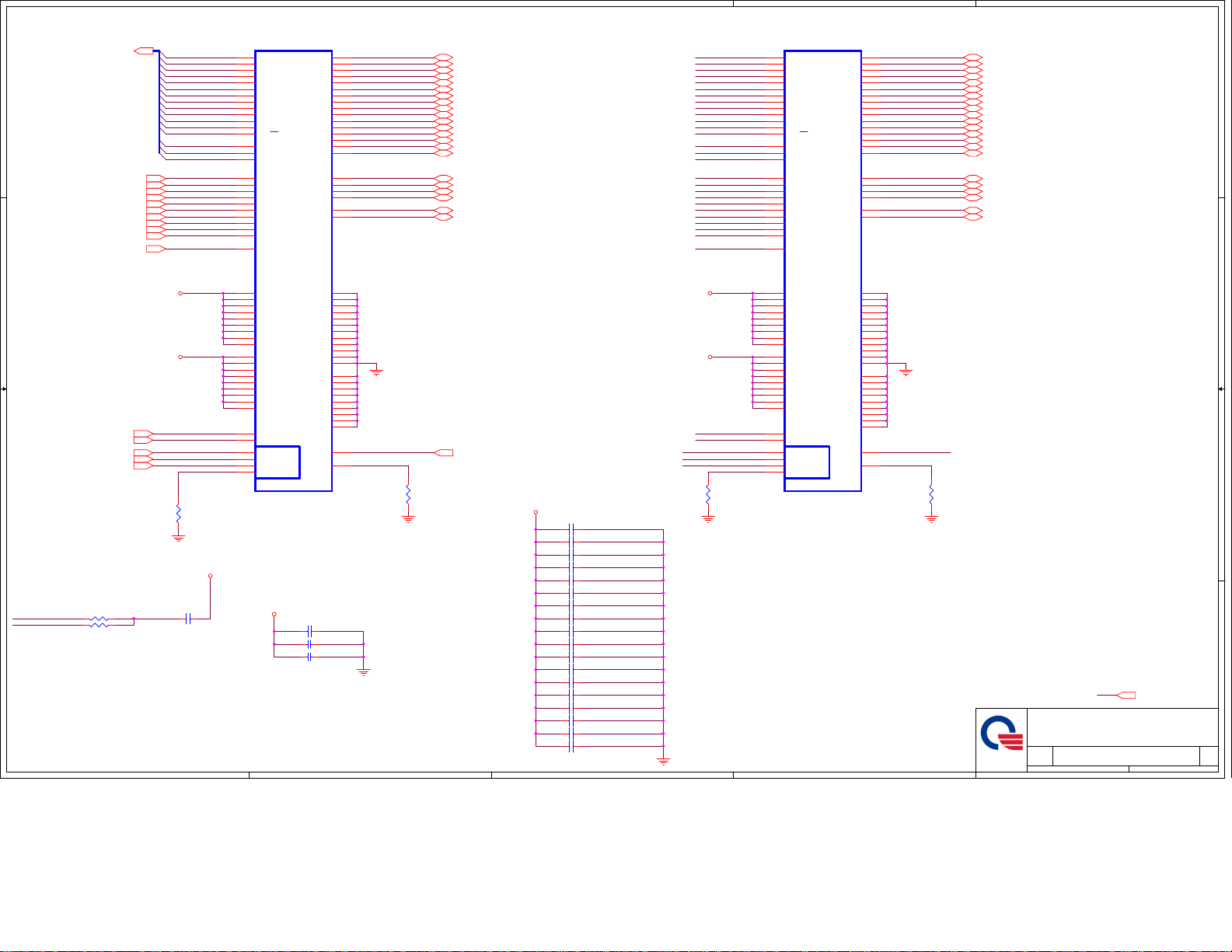

Page 3

5

4

3

2

1

Close to HDMI CONN

+3V

R344 1K_4

R178 1K_4

R173 1K_4

R185 1K_4

D D

APU_VDD_18

R363 300R

R336 300R

APU_PROCHOT#

APU_SIC

APU_SID

APU_ALERT

APU_RST#

APU_PWRGD

HDMI

IN_D0(13)

IN_D0#(13)

IN_D1(13)

IN_D1#(13)

IN_D2(13)

IN_D2#(13)

IN_CLK(13)

IN_CLK#(13)

LVDS

VRHOT(27)

H_PROCHOT#(22)

R345 0_4

APU_PROCHOT#

EC new option

MBCLK2(21)

MBDATA2(21)

C C

C387

*150P/50V_4

C386

*150P/50V_4

0527 :

Change net name from VDDIO_FB_H to TP

LDT_RST#

LDT_PWRGD

H_PROCHOT#

C389

220P/50V_4

TP41

TP40

TP31

PV Change to Short Pad

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

VDDIO_SUS_SENSE

DIFFERENTIAL ROUTING

CPU_VDDNB_RUN_FB_H(27)

CPU_VDD0_RUN_FB_H(27)

CPU_VDD0_RUN_FB_L(27)

TP77

TP76

TP33

R348 0_4

R347 0_4

APU_PROCHOT#(4)

CPU_VDDNB_RUN_FB_H

CPU_VDD0_RUN_FB_H

VDDIO_FB_H

CPU_VDD0_RUN_FB_L

VDD_095_FB(25)

TP13

C194 0.1U/10V/X7R_4

C191 0.1U/10V/X7R_4

C188 0.1U/10V/X7R_4

C186 0.1U/10V/X7R_4

C179 0.1U/10V/X7R_4

C176 0.1U/10V/X7R_4

C185 0.1U/10V/X7R_4

C183 0.1U/10V/X7R_4

LVDS_TXP0_R(11)

LVDS_TXN0_R(11)

LVDS_TXP1_R(11)

LVDS_TXN1_R(11)

LVDS_DATAP2(11)

LVDS_DATAN2(11)

LVDS_CLK(11)

LVDS_CLK#(11)

R182 0_4

R170 0_4

R179 0_4

R181 0_4

R160 0_4

R180 0_4

VDD_095_FB

VDD_095_FB_L

DPB_LANE0_P

DPB_LANE0_N

DPB_LANE1_P

DPB_LANE1_N

DPB_LANE2_P

DPB_LANE2_N

DPB_LANE3_P

DPB_LANE3_N

LVDS_TXP0

LVDS_TXN0

LVDS_TXP1

LVDS_TXN1

LVDS_DATAP2

LVDS_DATAN2

LVDS_CLK

LVDS_CLK#

SVT

SVC

SVD

APU_SIC

APU_SID

APU_RST#

LDT_RST#

APU_PWRGD

LDT_PWRGD

APU_PROCHOT#

APU_ALERT

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

VDDIO_SUS_SENSE

VSS_SENSE

U23D

Kabini

A9

TDP1_TXP0

B9

TDP1_TXN0

A10

TDP1_TXP1

B10

TDP1_TXN1

A11

TDP1_TXP2

B11

TDP1_TXN2

A12

TDP1_TXP3

B12

TDP1_TXN3

A4

LTDP0_TXP0

B4

LTDP0_TXN0

A5

LTDP0_TXP1

B5

LTDP0_TXN1

A6

LTDP0_TXP2

B6

LTDP0_TXN2

A7

LTDP0_TXP3

B7

LTDP0_TXN3

K15

DISP_CLKIN_H

H15

DISP_CLKIN_L

G31

SVT

D27

SVC

E29

SVD

B22

SIC

B21

SID

B20

APU_RST_L

A20

LDT_RST_L

B19

APU_PWROK

A19

LDT_PWROK

A22

PROCHOT_L

B18

ALERT_L

D29

TDI

D31

TDO

D35

TCK

D33

TMS

G27

TRST_L

B25

DBRDY

A25

DBREQ_L

D23

VDDCR_NB_SENSE

G23

VDDCR_CPU_SENSE

E25

VDDIO_MEM_S_SENSE

E23

VSS_SENSE

AV33

VDD_095_FB_H

AU33

VDD_095_FB_L

ANALOG/DISPLAY/MISC

DP MISC

DISPLAYPORT 0 DISPLAYPORT 1

CLK

SER

JTAG CTRL

KABINI

PART 4 OF 9

DP_150_ZVSS

DP_2K_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

TDP1_AUXP

TDP1_AUXN

TDP1_HPD

LTDP0_AUXP

LTDP0_AUXN

LTDP0_HPD

DAC_RED

DAC_GREEN

DAC_BLUE

DAC_HSYNC

DAC_VSYNC

DAC_SCL

VGA DAC

DAC_SDA

DAC_ZVSS

THERMDA

THERMDC

DIECRACKMON

PLLTEST1

PLLTEST0

BYPASSCLK_H

BYPASSCLK_L

PLLCHRZ_H

PLLCHRZ_L

TEST

GIO_TSTDTM0_SERIALCLK

HDMI_EN/DP_STEREOSYNC

M_TEST

FREE_2

GIO_TSTDTM0_CLKINIT

USB_ATEST0

USB_ATEST1

M_ANALOGIN

M_ANALOGOUT

TMON_CAL

B16

DP_150_ZVSS

A21

DP_2K_ZVSS

B17

APU_LVDS_BLON

A17

APU_DISP_ON

A18

APU_DPST_PWM

D17

SDVO_CLK

E17

SDVO_DATA

H19

HDMI_HPD_CON

D15

EDP_AUXP

E15

EDP_AUXN

H17

EDP_HPD

B14

FCH_CRT_R

A14

FCH_CRT_G

B15

FCH_CRT_B

G19

HSYNC_COM

E19

VSYNC_COM

D19

DDCCLK

D21

DDCDATA

A16

DAC_ZVSS

H27

APU_THERMDA_R

H29

APU_THERMDC_R

D25

DIECRACKMON

A27

BP0

BP1

BP2

BP3

BP0

B27

BP1

A26

BP2

B26

BP3

B28

PLLTEST1

A28

PLLTEST0

B24

BYPASSCLK_H

A24

BYPASSCLK_L

AV35

PLLCHRZ_H

AU35

PLLCHRZ_L

E33

M_TEST

A29

FREE_2

H21

GIO_TSTDTMO_SERIALCLK

H25

GIO_TSTDTM0_CLKINIT

AJ10

USB_ATEST0

AJ8

USB_ATEST1

R32

M_ANALOGIN

N32

M_ANALOGOUT

AP29

TMON_CAL

E21

HDMI_EN/DP_STEREOSYNC

R191 150/F_4

R171 2K/F_4

R376 75/F_4

R377 75/F_4

R195 75/F_4

R375 0_4

R360 0_4

R361 0_4

R362 0_4R343 0_4

R186 499/F_4

TP30

TP75

TP12

TP9

TP38

TP74

TP16

TP17

TP25

TP39

TP8

R359 *1K_4

R371 *1K_4

APU_LVDS_BLON (11)

APU_DISP_ON (11)

APU_DPST_PWM (11)

SDVO_CLK (13)

SDVO_DATA (13)

HDMI_HPD_CON (13)

LVDS_AUXP_CLK (11)

LVDS_AUXN_DATA (11)

CRT_R

CRT_G

CRT_B

TP78

TP79

TP80

TP81

TP32

TP37

R340 *1K_4

R339 *1K_4

R353 *1K_4

R355 1K_4

R354 1K_4

R333 511_4

R337 511_4

BYPASS CLK AND

PLLCHRZ NEED

DIFFERENTIAL ROUTING

R358 *1K_4

R379 *1K_4

R177 *1K_4

R172 *1K_4

EDP_AUXP

EDP_AUXN

R338 1.8K_4

R332 1.8K_4

SI Add

EDP_HPD

+1.8V

HSYNC_COM

NOTE:

DP_STEREOSYNC & APU_HSYNC PU FOR INTERNAL,

DP_STEREOSYNC & APU_HSYNC PD FOR CUSTOMER

03

+3V

R373

100k/F_4

R356

*100k/F_4

R374 1K_4

R357 *1K_4

+3V

MV AMD Request(for HDMI 3D need pull-high +3V)

B B

HDT(Hardware Debug Tool ) Connector

+3V

+1.8V

R216

R213

*1K_4

*1K_4

C226

*0.1U/10V/X7R_4

U14

*SN74LVC2G07DCKR

1

APU_RST#

APU_PWRGD APU_PWRGD_BUF

A A

Serial VID

SVT

SVC

SVD

APU_PWRGD

1A

2

GND

3

2A

R350 0_4

R366 0_4

R367 0_4

R346 0_4

PV Change to Short Pad

VCC

1Y

2Y

6

5

4

+1.8V

5

APU_LDT_RST_HTPA#

R351 *1K_4

R365 *1K_4

R368 *1K_4

SI Add

Can remove on MP

APU_LDT_RST_HTPA#

APU_PWRGD_BUF

SVT

SVC

SVD

CPU_SVT (27)

CPU_SVC (27)

CPU_SVD (27)

CPU_PWRGD_SVID_REG (27)

+1.8V

R233

R227

*1K_4

*1K_4

CPU_LDT_RST_HTPA#

VFIX MODE

VID Override table (VDD)

SVDSVC

0

0

0

110 0.9V

11

4

U11

*TC7SH08FU

4

Boot Voltage

1.1V

1.0V

0.8V

+3V

C229

*0.1U/10V/X7R_4

2

APU_RST#

1

3 5

+1.8V

R232 1K_4

R231 1K_4

R230 1K_4

R229 1K_4

R228 1K_4

+1.8V

TP46

APU_DBREQ#

APU_TCK

APU_TMS

APU_TDI

APU_TRST#

PLLTEST1

PLLTEST0

APU_LDT_RST_HTPA#

CPU_LDT_RST_HTPA#

APU_DBREQ#

APU_DBRDY

APU_TCK

APU_TMS

APU_TDI

APU_TRST#

APU_TDO

APU_PWRGD_BUF

3

CN5

*HDT CONN

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

88511-2001-20p-l

Local Thermal Sensor

+3V

U12

*G781-1P8EV

MBCLK2

MBDATA2

+3V

R200 *0_4

R201 *0_4

R226 *10K_4

2

8

VCC

SCLK

7

DXP

SDA

6

DXN

ALERT#

4

GND

OVERT#

MSOP

I2C ADDRESS: 9AH

C244

*0.01U/25V_4

NB5

NB5

NB5

1

2

3

5

IO_THERMDA_IO

C245 *2200P/50V_4

IO_THERMDC_IO

+3V (4,5,6,10,11,13,14,15,18,19,20,21,22,27,29)

+1.8V (6,27,29)

APU_VDD_18 (6)

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, July 02, 2013 3 30

Date: Sheet of

Tuesday, July 02, 2013 3 30

Date: Sheet of

Tuesday, July 02, 2013 3 30

DIS/MI (2/6)

DIS/MI (2/6)

DIS/MI (2/6)

1

2

Q10

*3904-G

1 3

1A

1A

1A

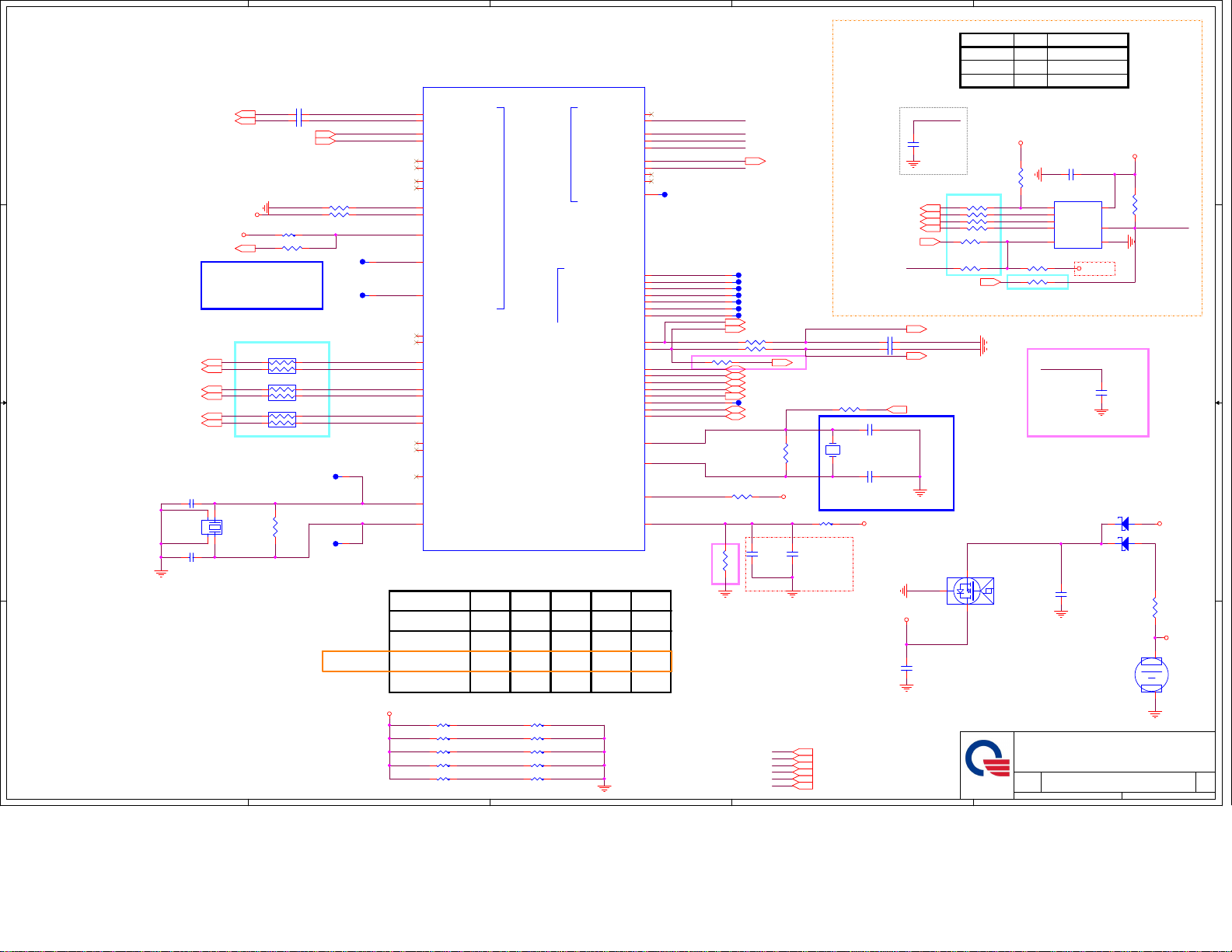

Page 4

5

4

3

2

1

+3VS5+3VS5

04

U10

*MC74VHC1G08DFT2G

PCIE_RST#_R1

D D

CARD_PCIE_RST#(14)

MINI_PCIE_RST#(10,21)

LAN_PCIE_RST#(18)

TP45

0522 :

Change net name from GPU_RST# to TP

+3VS5

NC,no install by default

C C

R113 *1K_4

R306 *1K_4

R303 *1K_4

4

R222 0_4

GPU_RST#

MV AMD Request (RTC Clock Issue)

APU_TEST0

APU_TEST1

APU_TEST2

TEST2 TEST1 TEST0 Description

FCH TAP accessible from APU when TAPEN is asserted

0

0 0

0

0

0

1

1

TMS

1 TMS

B B

A A

+3VS5

+3V

R105 2.2K_4

R104 2.2K_4

R79 10K/F_4

R134 10K/F_4

R132 10K/F_4

R78 10K/F_4

+3VS5

R304 *1K_4

1 2

J1

*SOLDERJUMPER-2

R316 2.2K_4

R315 2.2K_4

R314 10K/F_4

R130 *10K/F_4

R92 *10K/F_4

R86 10K/F_4

FCH JTAG pins are overloaded for multiple

functions, in this configuration the FCH JTAG are

used as non-JTAG pins

1

Reserved

X

Reserved

FCH JTAG multi-function pins are configured as

JTAG pins, in this configuration the FCH TAP

0

can be accessed from FCH JTAG pins

Use on ATE only

1

Yuba JTAG enabled

SYS_RST#

SYS_RST# internal

10K pull up

SMB_RUN_CLK

SMB_RUN_DAT

GEVENT4#

GEVENT7#

GPIO49

DGPU_PWROK

SMB_PCH_CLK

SMB_PCH_DAT

DNBSWON#

CLK_PCIE_REQ2#

ODD_DA#_FCH

PCIE_WAKE#

5

R204

*4.7K/F_4

35

1

2

PCIE_RST#

C240150P/50V_4

R218 33_4

R217 33_4

C239150P/50V_4

C233150P/50V_4

R220 33_4

R219 33_4

C236150P/50V_4

R114 15K_4

R305 *15K_4

R313 *15K_4

R212 33_4

C220

150P/50V_4

PCIE_RST#_R1

PCIE_RST#_R

KBC_RST#(22)

DNBSWON#(22)

SYS_PWRGD(7)

PCIE_WAKE#(18,21)

SUSB#(22)

SUSC#(22)

EC_RCIN#(22)

EC_A20GATE(22)

SIO_EXT_SCI#(22)

SIO_EXT_SMI#(22)

0522 :

Change net name from ODD_PLUGIN# to TP

CLK_PCIE_REQ2#(14)

PCIE_CLKREQ_LAN#(18)

PCIE_CLKREQ_WLAN#(21)

BT_COMBO_OFF#(21)

BT_COMBO_EN#(21)

0522 :

Change net name from VGA_RSTB to TP

ACZ_SPKR(15)

VGA_ON_SB(22)

APU_PROCHOT#(3)

GEVENT2#(7,22)

ACCEL_INTH#(21)

RF_OFF#(21)

RSMRST#(22)

Kabini reference current

4

C345150P/50V_4

R312 33_4

C61 *100P/50V_4

TP66

TP64

TP15

TP62

TP7

CLK_PCIE_REQ2#

PCIE_CLKREQ_LAN#

TP10

TP67

R295 *10K/F_4

+3V

TP70

TP11

0522 :

Change net name from ODD_PWR to TP

D7 RB501V-40

PCIE_CLKREQ_WLAN#

GPIO_23_CLKREQb

R103 *0_4

ODD_DA#_FCH

R111 47K/F_4

21

C77 1U/6.3V_4

R297 0_4

R296 *0_4

RSMRST#_R

LPC_RST#_R

PCIE_RST#_R

RSMRST#_R

DNBSWON#

SYS_PWRGD

SYS_RST#

PCIE_WAKE#

SUSB#

SUSC#

APU_TEST0

APU_TEST1

APU_TEST2

EC_RCIN#

EC_A20GATE

SIO_EXT_SCI#

SIO_EXT_SMI#

GEVENT5#

ODD_PLUGIN#

PM_THERM#

LLB#

SMB_RUN_CLK

SMB_RUN_DAT

SMB_PCH_CLK

SMB_PCH_DAT

GPIO49

BT_COMBO_OFF#

BT_COMBO_EN#

APU_GPIO55

VGA_RSTB

ACZ_SPKR

VGA_ON_SB

PROCHOT#_CTRL

DGPU_PWROK

GEVENT2#

GEVENT4#

GEVENT7#

RF_OFF#

ODD_PWR

+1.8VS5

3

U23C

Kabini

AY4

LPC_RST_L

AY9

PCIE_RST_L

AY5

RSMRST_L

BA8

PWR_BTN_L

AM19

PWR_GOOD

AY7

SYS_RESET_L/GEVENT19_L

AW11

WAKE_L/GEVENT8_L

AY3

SLP_S3_L

BA5

SLP_S5_L

AU13

TEST0

AY10

TEST1/TMS

AY6

TEST2

AR23

KBRST_L

AR31

GA20IN/GEVENT0_L

AN5

LPC_PME_L/GEVENT3_L

AL7

LPC_SMI_L/GEVENT23_L

AV2

LPC_PD_L/GEVENT5_L/SPI_TPM_CS_L

AP15

AC_PRES/IR_RX0/GEVENT16_L

AV13

IR_TX0/GEVENT21_L

BA9

IR_TX1/GEVENT6_L

BA10

IR_RX1/GEVENT20_L

AV15

IR_LED_L/LLB_L/GPIO184

AU29

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/GPIO60

AW29

CLK_REQ1_L/GPIO61

AR27

CLK_REQ2_L/GPIO62

AV27

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/GPIO63

AY29

CLK_REQG_L/GPIO65/OSCIN

AU25

SCL0/GPIO43

AV25

SDA0/GPIO47

AY11

SCL1/GPIO227

BA11

SDA1/GPIO228

AP27

GPIO49

AY28

GPIO50

BA28

GPIO51

AV23

GPIO55

AP21

GPIO57

BA26

GPIO58

AV19

GPIO59

AY27

GPIO64

BA27

SPKR/GPIO66

AU21

GPIO68

AY26

GPIO69

AV21

GPIO70

AM21

GPIO71

BA3

GPIO174

AV17

GEVENT2_L

BA4

GEVENT4_L

AR15

GEVENT7_L

AP17

GEVENT10_L

AP11

GEVENT11_L

AN8

GEVENT17_L

AU17

BLINK/GEVENT18_L

BA6

GEVENT22_L

BA29

GENINT1_L/GPIO32

AP23

GENINT2_L/GPIO33

AV31

FANOUT0/GPIO52

AU31

FANIN0/GPIO56

USBCLK/14M_25M_48M_OSC

ACPI / WAKE UP

EVENTS

USB_SS_ZVDD_095_USB3_DUAL

GPIO

USB_OC0_L/SPI_TPM_CS_L/TRST_L/GEVENT12_L

USB_OC1_L/TDI/GEVENT13_L

USB_OC2_L/TCK/GEVENT14_L

USB_OC3_L/TDO/GEVENT15_L

USB

OC

HD

AUDIO

KABINI

PART 3 OF 9

+3V (3,5,6,10,11,13,14,15,18,19,20,21,22,27,29)

+3VS5 (5,6,7,10,12,13,21,22,24,25,29)

+1.8VS5 (6,7,26,27,29)

+0.95V_DUAL (6)

USB

MISC

USB

1.1

USB

2.0

USB

3.0

AZ_SDIN0/GPIO167

AZ_SDIN1/GPIO168

AZ_SDIN2/GPIO169

AZ_SDIN3/GPIO170

2

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_HSD8P

USB_HSD8N

USB_HSD9P

USB_HSD9N

USB_SS_ZVSS

USB_SS_TX0P

USB_SS_TX0N

USB_SS_RX0P

USB_SS_RX0N

USB_SS_TX1P

USB_SS_TX1N

USB_SS_RX1P

USB_SS_RX1N

AZ_BITCLK

AZ_SDOUT

AZ_SYNC

AZ_RST_L

W4

AG4

AL4

AL5

AJ4

AJ5

AG7

AG8

AG1

AG2

AF1

AF2

AE1

AE2

AD1

AD2

AC1

AC2

AB1

AB2

AA1

AA2

AE10

AE8

T2

T1

V2

V1

R1

R2

W1

W2

AY8

AW1

AV1

AY1

AN2

AN1

AK2

AK1

AM1

AL2

AM2

AL1

USB_RCOMP

R137 11.8K

USBP0+ (17)

USBN0- (17)

USBP1+ (17)

USBN1- (17)

USBP2+ (21)

USBN2- (21)

USBP3+ (14)

USBN3- (14)

USBP4+ (12)

USBN4- (12)

USBP5+ (11)

USBN5- (11)

USBP8+

USBN8-

USBP9+

USBN9-

USB30_TX1+

USB30_TX1-

USB30_RX1+

USB30_RX1-

TP23

TP24

USBSS_CALRN

USBSS_CALRP

JTAG_TRST#

JTAG_TDI

JTAG_TCK

JTAG_TDO

ACZ_BCLK_R

ACZ_SDOUT_R

ACZ_SDIN0

ACZ_SDIN1

ACZ_SDIN2_R

ACZ_SDIN3_R

ACZ_SYNC_R

ACZ_RST#_R

AZ_SDIN[3:0]/

GPIO[170:167] 13.6K - PD

ACZ_SDOUT_R

ACZ_SYNC_R

ACZ_BCLK_R

ACZ_RST#_R

ACZ_SDIN0

NB5

NB5

NB5

Right side USB2.0 Connector

Right side USB2.0 Connector

WLAN Min-Card

TOUCH SCREEN

Touch PAD I2C

Camera USB

USBP8+ (17)

Left side USB3.0/2.0 Combo

USBN8- (17)

0525 :

Change net name from USBP9+ to TP

Change net name from USBN9- to TP

R147 1K

R131 1K

TP36

TP35

TP22

TP21

R124 *10K/F_4

R323 *10K/F_4

R324 *10K/F_4

R321 *10K/F_4

R126 *10K/F_4

+0.95V_DUAL

USB30_TX0+ (17)

USB30_TX0- (17)

USB30_RX0+ (17)

USB30_RX0- (17)

0525 :

Change net name from USB30_TX1+ to TP

Change net name from USB30_TX1- to TP

Change net name from USB30_RX1+ to TP

Change net name from USB30_RX1- to TP

TP65

TP68

TP61

TP69

HD audio

interface is

+3V_S5 voltage

To Azalia

R122 33_4

R127 33_4

R119 33_4

R322 33_4

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, July 02, 2013 4 30

Date: Sheet of

Tuesday, July 02, 2013 4 30

Date: Sheet of

Tuesday, July 02, 2013 4 30

Date: Sheet

ACZ_SDOUT_AUDIO (15)

ACZ_SYNC_AUDIO (15)

BIT_CLK_AUDIO (15)

ACZ_RST#_AUDIO (15)

ACZ_SDIN0 (15)

GPIO/USB/AZ (3/6)

GPIO/USB/AZ (3/6)

GPIO/USB/AZ (3/6)

1

1A

1A

1A

of

Page 5

5

4

3

2

1

APU SPI ROM

U23E

Kabini

D D

SATA_TXP0_C(20)

SATA_TXN0_C(20)

SATA HDD

SATA_LED#(19)

Use with external clock

generator only

Integrated Clock Mode:

C143

C159

10P/50V/C0G_4

10P/50V/C0G_4

Leave unconnected.

1

2

Y4

48MHZ +-10PPM

4

3

C C

CLK_PCIE_CARDP(14)

CLK_PCIE_CARDN(14)

CLK_PCIE_LANP(18)

CLK_PCIE_LANN(18)

CLK_PCIE_WLAN(21)

CLK_PCIE_WLAN#(21)

Integrated Clock Mode:

Le

ave unconnected.

B B

C413 0.01U/25V_4

C414 0.01U/25V_4

SATA_RXN0(20)

SATA_RXP0(20)

+0.95V

R298 *560_4/F

+3V

R299 0_4

2

RP9 0_4P2R_4

RP7 0_4P2R_4

RP8 0_4P2R_4

1

4

3

4

3

2

1

4

3

2

1

PV Change to Short Pad

R165

1M/F_4

0522 :

Del ODD HDD net

R136 1K

R133 1K

TP71

TP72

0522 :

Del DGPU CLK net

CLK_PCIE_CARDP_R

CLK_PCIE_CARDN_R

CLK_PCIE_LANP_R

CLK_PCIE_LANN_R

CLK_PCIE_WLAN_R

CLK_PCIE_WLAN#_R

TP27

TP34

SATA_TXP0

SATA_TXN0

SB_SATA_LED#

SATA_RXN0

SATA_RXP0

48M_X1

48M_X2

BA14

SATA_TX0P

AY14

SATA_TX0N

BA16

SATA_RX0N

AY16

SATA_RX0P

AY19

SATA_TX1P

BA19

SATA_TX1N

AY17

SATA_RX1N

BA17

SATA_RX1P

AR19

SATA_ZVSS

AP19

SATA_ZVDD_095

BA30

SATA_ACT_L/GPIO67

AY12

SATA_X1

BA12

SATA_X2

U4

GFX_CLKP

U5

GFX_CLKN

AC8

GPP_CLK0P

AC10

GPP_CLK0N

AE4

GPP_CLK1P

AE5

GPP_CLK1N

AC4

GPP_CLK2P

AC5

GPP_CLK2N

AA5

GPP_CLK3P

AA4

GPP_CLK3N

AP13

X14M_25M_48M_OSC

N2

X48M_X1

N1

X48M_X2

BOARD ID SETTING

Model

10.1'' UMA

lpida (TN)

E

Hynix (default)

Hynix (TG)

Micron (TF)

A A

5

+3V

R294 10K_4

R307 *10K_4

R308 *10K_4

R311 *10K_4

R319 *10K_4

4

BOARD_ID0

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

KABINI

PART 5 OF 9

SERIAL

ATA

SPI

BOARD_ID1 BOARD_ID2 BOARD_ID30BOARD_ID4

SD_DATA0/GPIO77

SD_DATA1/GPIO78

SD_DATA2/GPIO79

SD_DATA3/GPIO80

SD

CARD

SPI_CS1_L/GPIO165

SPI_CS2_L/GPIO166

SPI_HOLD_L/GEVENT9_L

SPI_WP_L/GPIO161

ROM

SD__PWR_CTRL

SD_CLK/GPIO73

SD_CMD/GPIO74

SD_CD/GPIO75

SD_WP/GPIO76

SD_LED/GPIO45

SPI_CLK/GPIO162

SPI_DO/GPIO163

SPI_DI/GPIO164

LPCCLK0

LPCCLK1

LAD0

LAD1

LAD2

LAD3

LFRAME_L

LDRQ0_L

SERIRQ/GPIO48

LPC_CLKRUN_L

32K_X1

32K_X2

RTCCLK

VDDBT_RTC_G

0 0 0 0 0

0

0

0

0

0

0

0

1

0

0

1

0

R310 *10K_4

R317 10K_4

R320 10K_4

R293 10K_4

R318 10K_4

3

BA23

AY22

AY23

AY20

BA20

BA22

AY21

AY24

BA24

AY25

AU7

AW9

AR4

AR11

AR7

AU11

AU9

AY2

AW2

AT2

AT1

AR2

AR1

AP2

AP1

AV29

AP25

AJ2

AJ1

AV11

AN4

TP73

SPI_CLK

SPI_CS0#

MEM_1V35

SPI_SO

SPI_SI

SPI_HOLD

SPI_WP

LPC_CLK0

LPC_CLK1

LAD0

LAD1

LAD2

LAD3

LFRAME#

LDRQ#0

SERIRQ

CLKRUN#

CLK_RTC

20MIL

BOARD_ID3

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID4

R108 33_4

R91 33_4

R99 *22_4

32K_X1

32K_X2

R123 10K_4

R129

*0_4

SI Modify

ACC_LED# (19)

TP28

TP18

TP57

TP29

TP19

TP26

TP20

LPC_CLK0 (7)

LPC_CLK1 (7)

R153

20M_4

C89

0.22U/10V_4

CLK_PCI_TPM (10)

+3VS5

R128 10K_4

C88

0.1U/10V/X7R_4

LAD0 (10,21,22)

LAD1 (10,21,22)

LAD2 (10,21,22)

LAD3 (10,21,22)

LFRAME# (7,10,21,22)

TP14

SERIRQ (10,22)

CLKRUN# (10,22)

AMD reference circuit

C113

*22P/50V_4

EC_BIOS_CS#(22)

EC_BIOS_SPI_CLK_I(22)

EC_BIOS_WR#(22)

EC_BIOS_RD#(22)

HMISO2(22)

SPI_WP

un-mount

C76 15P/50V_4

C67 15P/50V_4

SI Add

R139 *0_4

C115 18P/50V_4

21

Y3

32.768KHZ

C125 18P/50V_4

USE GROUND GUARD FOR 32K_X1 AND 32K_X2

CLKGEN_RTC_X1 (13)

+1.5V_RTC

AP2138N-1.5TRG1

+1.5V_RTC

20MIL

0

0

+3VRTC (13)

+3V (3,4,6,10,11,13,14,15,18,19,20,21,22,27,29)

+BAT (13)

+3VS5 (4,6,7,10,12,13,21,22,24,25,29)

+0.95V (6,25)

+3VPCU (13,19,21,22,23,24)

2

C391

1u/10V_4

Vender

Socket

SPI_CLK

EMI

R151 *0_4

R142 *0_4

R141 *0_4

R154 *0_4

R157 *0_4

R158 *0_4

HMISO3(22)

PV Modify to ShortPad

CLK_33M_DEBUG (21)

CLK_33M_KBC (22)

3

Q16

2

1

NB5

NB5

NB5

Size P/N

2M

2

M

DFHS08FS023

+3VS5

R148

*10K/F_4

SPI_CS0#

SPI_CLK

SPI_SO

SPI_SI

R159 *10K/F_4

R143 *0_4

C114 *0.1U/10V/X7R_4

U6

1

CE#

6

SCK

5

SI

2

SO

HOLD#

3

WP#

*MX25L1605DM2I-12G

+3VS5

VDD

VSS

+3VS5

8

R144

*10K/F_4

7

4

AMD reference circuit

CLK_PCI_TPM

EC5

*10P/50V_4

SI EMI Request

D12

RB500V-40

+3VRTC

20MIL

20MIL

+3VRTC

C400

1u/10V_4

D11

RB500V-40

20MIL

21

21

R369

1K/F_4

20MIL

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, July 02, 2013 5 30

Date: Sheet of

Tuesday, July 02, 2013 5 30

Date: Sheet of

Tuesday, July 02, 2013 5 30

SATA/CLK (4/6)

SATA/CLK (4/6)

SATA/CLK (4/6)

1

05

SPI_HOLD

+3VPCU

+VCCRTC_2

+BAT

+BAT

12

CN19

RTC SOCKET

1A

1A

1A

Page 6

5

1.35VSUS (2.9A)

C104

180P/50V_4

180P/50V_4

D D

GND

+1.5VS5 APU_VDDIO_AZ

R135 0_8

PV Change to Short Pad

C C

PV Change to Short Pad

+1.8VS5

R176 0_8

C172

180P/50V_4

GND

B B

C180

180P/50V_4

GND

+3VS5 APU_VDD33_ALW

R121 0_8

PV Change to Short Pad

S5 DOMAIN

A A

+0.95VS5 +0.95V_DUAL

R164 0_8

R163 *0_8

+0.95V

S0 DOMAIN

C142

180P/50V_4

C91

0.1U/10V/X7R_4

C156

0.1U/10V/X7R_4

C94

4.7U/6.3V_6

GND

APU_VDD18_ALW

C184

4.7U/6.3V_6

VDD_18_ALW_R

C174

1U/10V_4

C81

1U/10V_4

GND

5

C109

C103

10U/6.3V_8

180P/50V_4

C131

0.1U/10V/X7R_4

C106

0.1U/10V/X7R_4

PLACE ON TOP LAYER

C95

C98

180P/50V_4

1U/10V_4

C175

C170

1U/10V_4

1U/10V_4

C169

C171

1U/10V_4

1U/10V_4

C80

1U/10V_4

PV Change to Short Pad

C137

C134

10U/6.3V_8

10U/6.3V_8

GND

C85

10U/6.3V_6

C105

0.1U/10V/X7R_4

C155

0.1U/10V/X7R_4

C96

1U/10V_4

VDD_18_ALW_R

C177

1U/10V_4

R169 0_8

1U/10V_4

C153

10U/6.3V_8

C97

1U/10V_4

VDD_0.95V_ALW

C86

C87

0.1U/10V/X7R_4

C154

0.1U/10V/X7R_4

APU_VDD33_ALW

+0.95V_DUAL

+1.35VSUS +VCC_CORE

APU_VDDIO_AZ

0.1A

0.5A

0.2A

1A

0.5A

VDD_0.95V_ALW+0.95VS5

C110

C162

1U/10V_4

1U/10V_4

GND

C149

1U/10V_4

C150

1U/10V_4

U23F

Kabini

J35

VDDIO_MEM_S_1

L32

VDDIO_MEM_S_2

L37

VDDIO_MEM_S_3

N35

VDDIO_MEM_S_4

R31

VDDIO_MEM_S_5

R37

VDDIO_MEM_S_6

U32

VDDIO_MEM_S_7

U35

VDDIO_MEM_S_8

W31

VDDIO_MEM_S_9

W32

VDDIO_MEM_S_10

W37

VDDIO_MEM_S_11

AA31

VDDIO_MEM_S_12

AA35

VDDIO_MEM_S_13

AC32

VDDIO_MEM_S_14

AC37

VDDIO_MEM_S_15

AE31

VDDIO_MEM_S_16

AE35

VDDIO_MEM_S_17

AG32

VDDIO_MEM_S_18

AG37

VDDIO_MEM_S_19

AJ35

VDDIO_MEM_S_20

AL32

VDDIO_MEM_S_21

AL37

VDDIO_MEM_S_22

AR35

VDDIO_MEM_S_23

AL10

VDDIO_AZ_ALW_1

AL11

VDDIO_AZ_ALW_2

B1

VDD_18_ALW_1

B2

VDD_18_ALW_2

AL13

VDD_33_ALW_1

AM13

VDD_33_ALW_2

AR5

VDD_095_USB3_DUAL1

AU4

VDD_095_USB3_DUAL2

AV7

VDD_095_USB3_DUAL3

AW5

VDD_095_USB3_DUAL4

AE11

VDD_095_ALW_1

AE13

VDD_095_ALW_2

AJ11

VDD_095_ALW_3

AJ13

VDD_095_ALW_4

C163

1U/10V_4

4

C116

1U/10V_4

C151

180P/50V_4

4

VDDCR_CPU_1

VDDCR_CPU_2

VDDCR_CPU_3

VDDCR_CPU_4

VDDCR_CPU_5

VDDCR_CPU_6

VDDCR_CPU_7

VDDCR_CPU_8

VDDCR_CPU_9

VDDCR_CPU_10

VDDCR_CPU_11

VDDCR_CPU_12

VDDCR_CPU_13

VDDCR_CPU_14

VDDCR_CPU_15

VDDCR_CPU_16

VDDCR_CPU_17

VDDCR_CPU_18

VDDCR_CPU_19

VDDCR_CPU_20

VDDCR_CPU_21

VDDCR_CPU_22

VDDCR_CPU_23

VDDCR_CPU_24

VDDCR_CPU_25

VDDCR_CPU_26

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

POWER

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDCR_NB_10

VDDCR_NB_11

VDDCR_NB_12

VDDCR_NB_13

VDDCR_NB_14

VDDCR_NB_15

VDDCR_NB_16

VDDCR_NB_17

VDDCR_NB_18

VDDCR_NB_19

VDDCR_NB_20

VDDCR_NB_21

VDD_18_1

VDD_18_2

VDD_18_3

VDD_18_4

KABINI

PART 7 OF 9

VDD_33_1

VDD_33_2

VDD_095_1

VDD_095_2

VDD_095_3

VDD_095_4

VDD_095_5

VDD_095_6

VDD_095_7

VDD_095_8

VDD_095_9

VDD_095_GFX_1

VDD_095_GFX_2

VDD_095_GFX_3

+1.8V APU_VDD_18

R335 0_8

PV Change to Short Pad

L21

L23

L25

L27

L29

N21

N23

N27

R21

R23

R27

U21

U23

U27

W21

W23

W27

AA21

AA23

AA27

AC21

AC23

AC27

AE21

AE23

AE27

L13

L17

N11

N13

N17

R11

R13

R17

U13

U17

W13

W17

AA13

AA17

AC13

AC17

AE15

AE17

AE19

AG17

AG21

1.5A

A2

A3

B3

C3

0.2A

AM15

AM17

AG23

AG27

AJ21

AJ27

AL21

AL23

AL27

AM23

AM25

0.6A

U10

W10

AA10

10A+

C312

10U/6.3V_8

C135

1U/10V_4

C112

1U/10V_4

+VDDNB_CORE

6.5A

C298

10U/6.3V_8

C158

C139

1U/10V_4

1U/10V_4

C136

1U/10V_4

5A

APU_VDD_18

APU_VDD_33

+0.95V

+1.1V_CLK

GND

C385

10U/6.3V_8

GND

PV Change to Short Pad

PV Change APU_VDD_0.95 to +0.95v plan

R138 *0_6

C133

*1U/10V_4

PV Change to Short Pad

+1.1V_CLK will be 1.1V for TV

but it will be 0.95V for Temash

C378

C376

1U/10V_4

1U/10V_4C152

3

C310

C311

10U/6.3V_8

C111

1U/10V_4

C126

1U/10V_4

C43

10U/6.3V_6

C147

1U/10V_4

C141

1U/10V_4

+3V APU_VDD_33

R97 0_8

+0.95V

+0.95V

C383

C379

1U/10V_4

1U/10V_4

3

C138

10U/6.3V_8

180P/50V_4

C130

1U/10V_4

C132

1U/10V_4

C40

10U/6.3V_6

C128

1U/10V_4

C129

1U/10V_4

C75

1U/10V_4

GND

PV Del R61,R79 & APU_VDD_0.95

C100

C99

1U/10V_4

1U/10V_4

GND

C384

1U/10V_4

C122

1U/10V_4

C121

1U/10V_4

C101

1U/10V_4

C108

1U/10V_4

C382

1U/10V_4

C46

10U/6.3V_6

C145

1U/10V_4

C120

1U/10V_4

C102

180P/50V_4

C93

1U/10V_4

C377

1U/10V_4

C148

1U/10V_4

C140

1U/10V_4

C127

1U/10V_4

C380

180P/50V_4

GND

C124

180P/50V_4

GND

C90

1U/10V_4

C395

10U/6.3V_8

A13

A23

A31

A35

A39

B13

B23

B31

B39

C11

C13

C15

C17

C19

C21

C23

C25

C27

C29

C31

C33

C35

C37

C39

C41

D11

D13

E11

E13

E27

E31

E35

E38

E39

G11

G13

G15

G17

G21

G25

G29

G35

G37

G39

G41

H11

H13

H23

H31

C398

10U/6.3V_8

A8

B8

C1

C2

C5

C7

C9

D9

E3

E4

E9

G3

G7

2

U23G

Kabini

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

C92

1U/10V_4

2

KABINI

PART 8 OF 9

C107

180P/50V_4

J3

VSS_63

J7

VSS_64

J8

VSS_65

J39

VSS_66

K11

VSS_67

K13

VSS_68

K17

VSS_69

K19

VSS_70

K21

VSS_71

K23

VSS_72

K25

VSS_73

K27

VSS_74

K29

VSS_75

K31

VSS_76

L3

VSS_77

L7

VSS_78

L8

VSS_79

L10

VSS_80

L11

VSS_81

L15

VSS_82

L19

VSS_83

L31

VSS_84

L39

VSS_85

L41

VSS_86

M1

VSS_87

M2

VSS_88

N3

VSS_89

N7

VSS_90

N15

VSS_91

GROUND

N19

VSS_92

N25

VSS_93

N29

VSS_94

N31

VSS_95

N39

VSS_96

P1

VSS_97

P2

VSS_98

R3

VSS_99

R7

VSS_100

R15

VSS_101

R19

VSS_102

R25

VSS_103

R29

VSS_104

R39

VSS_105

R41

VSS_106

U1

VSS_107

U2

VSS_108

U3

VSS_109

U7

VSS_110

U8

VSS_111

U11

VSS_112

U15

VSS_113

U19

VSS_114

U25

VSS_115

U29

VSS_116

U31

VSS_117

U39

VSS_118

W3

VSS_119

W5

VSS_120

W11

VSS_121

W15

VSS_122

W19

VSS_123

W25

VSS_124

GNDGND GNDGND

+3V (3,4,5,10,11,13,14,15,18,19,20,21,22,27,29)

+1.8V (3,27,29)

+3VS5 (4,5,7,10,12,13,21,22,24,25,29)

+0.95V (5,25)

+1.5VS5 (25,29)

+1.8VS5 (4,7,26,27,29)

+0.95VS5 (25)

+1.35VSUS (2,8,9,26)

+1.1V_CLK (2)

+VCC_CORE (27,28)

NB5

NB5

NB5

1

06

U23H

Kabini

W29

VSS_125

W39

VSS_126

W41

VSS_127

Y1

VSS_128

Y2

VSS_129

AA3

VSS_130

AA7

VSS_131

AA8

VSS_132

AA11

VSS_133

AA15

VSS_1134

AA19

VSS_135

AA25

VSS_136

AA29

VSS_137

AA39

VSS_138

AC3

VSS_139

AC7

VSS_140

AC11

VSS_141

AC15

VSS_142

AC19

VSS_143

AC25

VSS_144

AC29

VSS_145

AC31

VSS_146

AC39

VSS_147

AC41

VSS_148

AE3

VSS_149

AE7

VSS_150

AE25

VSS_151

AE29

VSS_152

AE32

VSS_153

AE39

VSS_154

AG3

VSS_155

AG5

VSS_156

AG10

VSS_157

AG11

VSS_158

AG13

VSS_159

AG15

VSS_160

AG19

VSS_161

AG25

VSS_162

AG29

VSS_163

AG31

VSS_164

AG39

VSS_165

AG41

VSS_166

AH1

VSS_167

AH2

VSS_168

AJ3

VSS_169

AJ7

VSS_170

AJ15

VSS_171

AJ17

VSS_172

AJ19

VSS_173

AJ23

VSS_174

AJ25

VSS_175

AJ29

VSS_176

AJ31

VSS_177

AJ32

VSS_178

AJ39

VSS_179

AL3

VSS_180

AL8

VSS_181

AL15

VSS_182

AL17

VSS_183

AL19

VSS_184

AL25

VSS_185

AL29

VSS_186

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, July 02, 2013 6 30

Date: Sheet of

Tuesday, July 02, 2013 6 30

Date: Sheet of

Tuesday, July 02, 2013 6 30

Date: Sheet

KABINI

PART 9 OF 9

GROUND

POWER/GND(5/6)

POWER/GND(5/6)

POWER/GND(5/6)

1

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSSBG_DAC

VBURN

PSEN

AL39

AL41

AM11

AM27

AM31

AN3

AN7

AN39

AP31

AR3

AR13

AR17

AR21

AR25

AR29

AR39

AR41

AU1

AU2

AU3

AU15

AU19

AU23

AU27

AU39

AV9

AW3

AW7

AW13

AW15

AW17

AW19

AW21

AW23

AW25

AW27

AW31

AW33

AW35

AW37

AW39

AW41

AY13

AY15

AY18

AY30

BA2

BA7

BA13

BA15

BA18

BA21

BA25

BA31

BA35

BA39

A15

AL31

AM29

of

1A

1A

1A

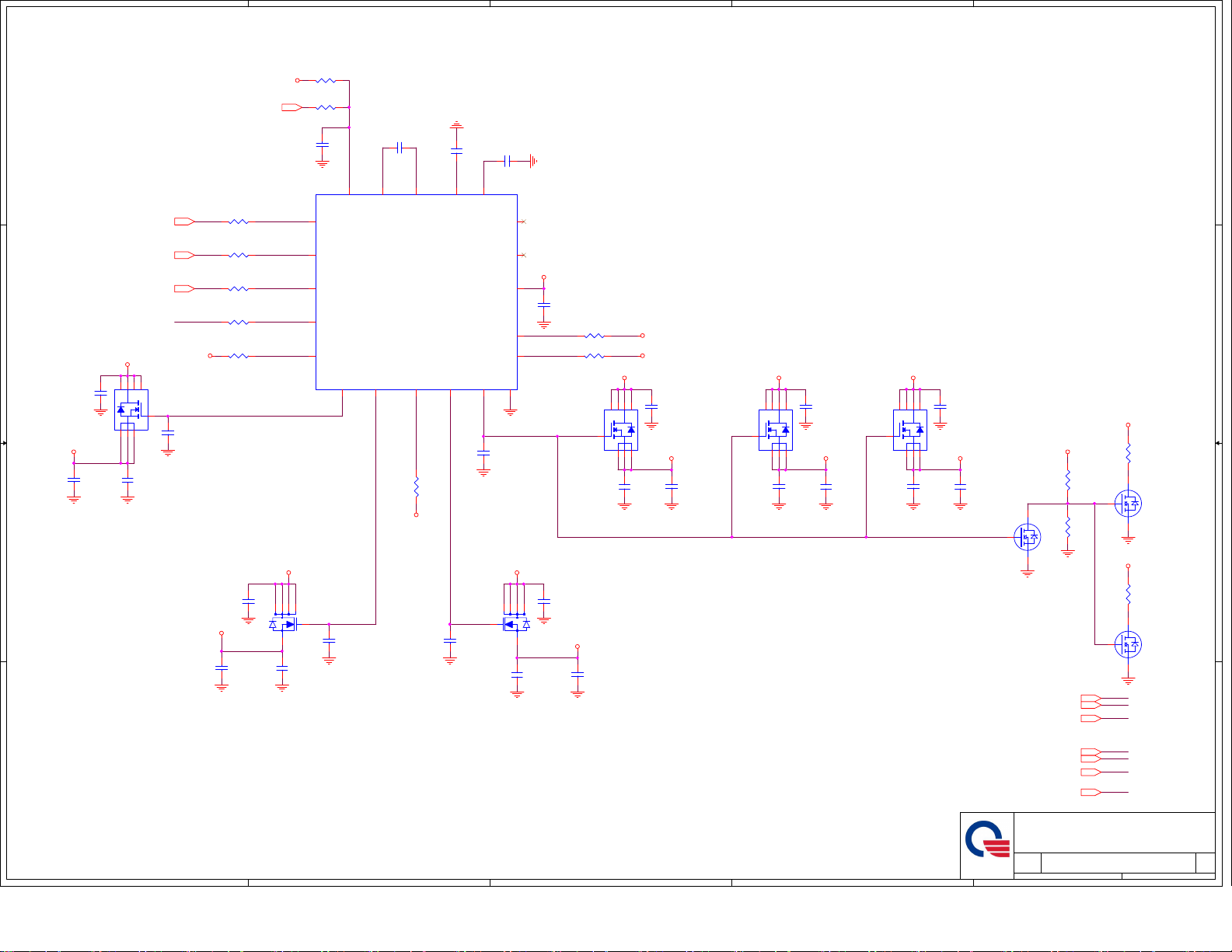

Page 7

5

4

3

2

1

STRAPS PINS

OVERLAP COMMON PADS WHERE

D D

C C

POSSIBLE FOR DUAL-OP RESISTORS.

R109

*10K/F_4

LPC_CLK0(5)

LPC_CLK1(5)

LFRAME#(5,10,21,22)

GEVENT2#(4,22)

LPC_CLK0

LPC_CLK1

LFRAME#

GEVENT2#

R110

2K_4

+3VS5 +3VS5 +3VS5+3VS5

R120

10K/F_4

R125

*2K_4

R88

*10K/F_4

R87

2K_4

R100

10K/F_4

R101

*2K_4

07

REQUIRED STRAPS

PULL

HIGH

PULL

LOW

LPC_CLK0

BOOT FAIL TIMER

ENABLED

BOOT FAIL TIMER

DISABLED

DEFAULT

LPC_CLK1

CLKGEN

ENABLED

DEFAULT

CLKGEN

DISABLED

LFRAME#

SPI ROM

DEFAULT

LPC ROM

GEVENT2#

1.8V SPI ROM

3.3V SPI ROM

DEFAULT

B B

SYS PWRGD

+1.8VS5

R116

D8 BAT54A

CPU_VRM8380_PG(27)

ECPWROK(22)

A A

2

3

1

5

10K/F_4

C78

*2.2U/6.3V_4

Modify for cost down

R112 0_4

4

SYS_PWRGD (4)

+3V (3,4,5,6,10,11,13,14,15,18,19,20,21,22,27,29)

+3VS5 (4,5,6,10,12,13,21,22,24,25,29)

+1.8VS5 (4,6,26,27,29)

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

STRAP (6/6)

STRAP (6/6)

NB5

NB5

3

2

NB5

STRAP (6/6)

Tuesday, July 02, 2013 7 30

Date: Sheet of

Tuesday, July 02, 2013 7 30

Date: Sheet of

Tuesday, July 02, 2013 7 30

Date: Sheet

1

1A

1A

1A

of

Page 8

5

M_A_A[15:0](2,9)

D D

0521 :

Change net name from M_A_BS0 to M_A_BS#0

Change net name from M_A_BS1 to M_A_BS#1

Change net name from M_A_BS2 to M_A_BS#2

M_A_BS#0(2,9)

M_A_BS#1(2,9)

M_A_BS#2(2,9)

M_A_CS#0(2,9)

M_A_CLKP0(2)

M_A_CLKN0(2)

M_A_CKE0(2,9)

M_A_CAS#(2,9)

M_A_RAS#(2,9)

M_A_WE#(2,9)

M_A_ODT0(2,9)

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_CS#0

M_A_CLKP0

M_A_CKE0

M_A_CAS#

M_A_RAS#

M_A_WE#

M_A_ODT0

U25

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

L2

CS#

J7

CK

K7

CK#

K9

CKE

K3

CAS#

J3

RAS#

L3

WE#

K1

ODT

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

DQSU

DQSL

DQSU#

DQSL#

DMU

DML

4

E3

M_A_DQ3

F7

M_A_DQ7

F2

M_A_DQ2

F8

M_A_DQ6

H3

M_A_DQ5

H8

M_A_DQ1

G2

M_A_DQ4

H7

M_A_DQ0

D7

M_A_DQ9

C3

M_A_DQ11

C8

M_A_DQ8

C2

M_A_DQ15

A7

M_A_DQ12

A2

M_A_DQ10

B8

M_A_DQ13

A3

M_A_DQ14

C7

M_A_DQSP1

F3

M_A_DQSP0

B7

M_A_DQSN1

G3

M_A_DQSN0

D3

M_A_DM1

E7

M_A_DM0

M_A_DQ3 (2)

M_A_DQ7 (2)

M_A_DQ2 (2)

M_A_DQ6 (2)

M_A_DQ5 (2)

M_A_DQ1 (2)

M_A_DQ4 (2)

M_A_DQ0 (2)

M_A_DQ9 (2)

M_A_DQ11 (2)

M_A_DQ8 (2)

M_A_DQ15 (2)

M_A_DQ12 (2)

M_A_DQ10 (2)

M_A_DQ13 (2)

M_A_DQ14 (2)

M_A_DQSP1 (2)

M_A_DQSP0 (2)

M_A_DQSN1 (2)

M_A_DQSN0 (2)

M_A_DM1 (2)

M_A_DM0 (2)

3

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_CS#0

M_A_CLKP0

M_A_CLKN0

M_A_CKE0

M_A_CAS#

M_A_RAS#

M_A_WE#

M_A_ODT0

U24

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

L2

CS#

J7

CK

K7

CK#

K9

CKE

K3

CAS#

J3

RAS#

L3

WE#

K1

ODT

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

DQSU

DQSL

DQSU#

DQSL#

DMU

DML

2

E3

M_A_DQ18

F7

M_A_DQ23

F2

M_A_DQ19

F8

M_A_DQ22

H3

M_A_DQ17

H8

M_A_DQ21

G2

M_A_DQ16

H7

M_A_DQ20

D7

M_A_DQ28

C3

M_A_DQ26

C8

M_A_DQ25

C2

M_A_DQ31

A7

M_A_DQ24

A2

M_A_DQ30

B8

M_A_DQ29

A3

M_A_DQ27

C7

M_A_DQSP3

F3

M_A_DQSP2

B7

M_A_DQSN3

G3

M_A_DQSN2

D3

M_A_DM3M_A_CLKN0

E7

M_A_DM2

M_A_DQ18 (2)

M_A_DQ23 (2)

M_A_DQ19 (2)

M_A_DQ22 (2)

M_A_DQ17 (2)

M_A_DQ21 (2)

M_A_DQ16 (2)

M_A_DQ20 (2)

M_A_DQ28 (2)

M_A_DQ26 (2)

M_A_DQ25 (2)

M_A_DQ31 (2)

M_A_DQ24 (2)

M_A_DQ30 (2)

M_A_DQ29 (2)

M_A_DQ27 (2)

M_A_DQSP3 (2)

M_A_DQSP2 (2)

M_A_DQSN3 (2)

M_A_DQSN2 (2)

M_A_DM3 (2)

M_A_DM2 (2)

1

08

+1.35VSUS

C C

+1.35VSUS

SMDDR_VREF_DQ0_M1(2,9)

+SMDDR_VREF_DIMM(9)

M_A_ODT1(2,9)

M_A_CS#1(2,9)

M_A_CKE1(2,9)

B B

A A

M_A_CLKP0 DRMA_CLK0_CT

M_A_CLKN0

R189 36_4

R190 36_4

SMDDR_VREF_DQ0_M1

+SMDDR_VREF_DIMM

DDRA_ZQ1 DDRA_ZQ2

R384

240_4

GND GND

5

B2

VDD#B2

D9

VDD#D9

G7

VDD#G7

K2

VDD#K2

K8

VDD#K8

N1

VDD#N1

N9

VDD#N9

R1

VDD#R1

R9

VDD#R9

A1

VDDQ#A1

A8

VDDQ#A8

C1

VDDQ#C1

C9

VDDQ#C9

D2

VDDQ#D2

E9

VDDQ#E9

F1

VDDQ#F1

H2

VDDQ#H2

H9

VDDQ#H9

H1

VREFDQ

M8

VREFCA

J1

ODT1#J1

L1

CS1#L1

J9

CKE1#J9

L9

ZQ1#L9

Memory-Down _DDRL3

+1.35VSUS

C178

0.1U/10V_4

8Gb

SDRAM DDR3

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

VSSQ#G1

VSSQ#G9

RESET#

96-BALL

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

GND GND

D1

D8

E2

E8

F9

G1

G9

T2

DDR3_DRAMRST#

L8

DDR_ZQ1 DDR_ZQ2

ZQ

DDR_VTTREF(8,26)

DDR_VTTREF(8,26)

4

0521 :

Change net name

from M_A_DRAMRST# to DDR3_DRAMRST#

DDR3_DRAMRST# (2,9)

R383

240_4

GND

R282 *0_6

C348

0.47U/10V_4

R286 *0_6

+1.35VSUS

R352

1K_4

SMDDR_VREF_DQ0_M1

R328

1K_4

1 2

GND

+1.35VSUS

R382

1K_4

+SMDDR_VREF_DIMM

R329

1K_4

GND Size Document Number Rev

C303

0.1u/10V_4

C372

0.1u/10V_4

GND

C388

0.1u/10V_4

GND

C404

0.1u/10V_4

3

C347

0.1u/10V_4

C353

0.1u/10V_4

+1.35VSUS

+1.35VSUS

SMDDR_VREF_DQ0_M1

+SMDDR_VREF_DIMM

C390

0.1u/10V_4

C354

0.1u/10V_4

M_A_ODT1

M_A_CS#1

M_A_CKE1

R330

240_4

C306

*1U/6.3V_4

B2

VDD#B2

D9

VDD#D9

G7

VDD#G7

K2

VDD#K2

K8

VDD#K8

N1

VDD#N1

N9

VDD#N9

R1

VDD#R1

R9

VDD#R9

A1

VDDQ#A1

A8

VDDQ#A8

C1

VDDQ#C1

C9

VDDQ#C9

D2

VDDQ#D2

E9

VDDQ#E9

F1

VDDQ#F1

H2

VDDQ#H2

H9

VDDQ#H9

H1

VREFDQ

M8

VREFCA

J1

ODT1#J1

L1

CS1#L1

J9

8Gb

CKE1#J9

L9

ZQ1#L9

SDRAM DDR3

Memory-Down _DDRL3

DDR3L

TOPBS PN

AKD5JGETW07

AKD5JGST412

AKD5JGSTL06 AKD5JGSTL07 MT41K256M16HA-125:E IC SDRAM (96P) MT41K256M16HA-125:E Micron

C341

*1U/6.3V_4

A9

VSS#A9

B3

VSS#B3

E1

VSS#E1

G8

VSS#G8

J2

VSS#J2

J8

VSS#J8

M1

VSS#M1

M9

VSS#M9

P1

VSS#P1

P9

VSS#P9

T1

VSS#T1

T9

VSS#T9

B1

VSSQ#B1

B9

VSSQ#B9

D1

VSSQ#D1

D8

VSSQ#D8

E2

VSSQ#E2

E8

VSSQ#E8

F9

VSSQ#F9

G1

VSSQ#G1

G9

VSSQ#G9

RESET#

ZQ

96-BALL

0521 :

Change net name

from M_A_DRAMRST# to DDR3_DRAMRST#

T2

DDR3_DRAMRST#

L8

GND

R331

240_4

QBCON DescriptionVender PN

AKD5JGETW08 H5TC4G63AFR-PBA IC SDRAM (96P) H5TC4G63AFR-PBA Hynix (default)

IC SDRAM (96P) EDJ4216EFBG-GN-FAKD5JGST413 EDJ4216EFBG-GN-F

+1.35VSUS (2,6,9,26)

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

DDR3L - A1

DDR3L - A1

NB5

NB5

2

NB5

DDR3L - A1

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Elpida

1A

1A

8 30Tuesday, July 02, 2013

8 30Tuesday, July 02, 2013

8 30Tuesday, July 02, 2013

1A

Page 9

5

4

3

2

1

M_A_A[15:0](2,8)

D D

0521 :

Change net name from M_A_BS0 to M_A_BS#0

Change net name from M_A_BS1 to M_A_BS#1

Change net name from M_A_BS2 to M_A_BS#2

C C

B B

M_A_CLKP1 DRMA_CLK1_CT

M_A_CLKN1

A A

M_A_BS#0(2,8)

M_A_BS#1(2,8)

M_A_BS#2(2,8)

M_A_CS#0(2,8)

M_A_CLKP1(2)

M_A_CLKN1(2)

M_A_CKE0(2,8)

M_A_CAS#(2,8)

M_A_RAS#(2,8)

M_A_WE#(2,8)

M_A_ODT0(2,8)

SMDDR_VREF_DQ0_M1(2,8)

+SMDDR_VREF_DIMM(8)

M_A_ODT1(2,8)

M_A_CS#1(2,8)

M_A_CKE1(2,8)

R106 36_4

R107 36_4

5

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_CS#0

M_A_CLKP1

M_A_CLKN1

M_A_CKE0

M_A_CAS#

M_A_RAS#

M_A_WE#

M_A_ODT0

+1.35VSUS

+1.35VSUS

SMDDR_VREF_DQ0_M1

+SMDDR_VREF_DIMM

DDRA_ZQ3 DDRA_ZQ4

R326

240_4

GND

+1.35VSUS

C68

0.1U/10V_4

U22

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

L2

CS#

J7

CK

K7

CK#

K9

CKE

K3

CAS#

J3

RAS#

L3

WE#

K1

ODT

B2

VDD#B2

D9

VDD#D9

G7

VDD#G7

K2

VDD#K2

K8

VDD#K8

N1

VDD#N1

N9

VDD#N9

R1

VDD#R1

R9

VDD#R9

A1

VDDQ#A1

A8

VDDQ#A8

C1

VDDQ#C1

C9

VDDQ#C9

D2

VDDQ#D2

E9

VDDQ#E9

F1

VDDQ#F1

H2

VDDQ#H2

H9

VDDQ#H9

H1

VREFDQ

M8

VREFCA

J1

ODT1#J1

L1

CS1#L1

J9

8Gb

CKE1#J9

L9

ZQ1#L9

SDRAM DDR3

Memory-Down _DDRL3

+1.35VSUS

C367 1U/6.3V_4 C356 0.22U/6.3V_4

C359 180P/50V_4

C358 180P/50V_4

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

DQSU

DQSL

DQSU#

DQSL#

DMU

DML

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

VSSQ#G1

VSSQ#G9

RESET#

96-BALL

E3

M_A_DQ35

F7

M_A_DQ34

F2

M_A_DQ38

F8

M_A_DQ39

H3

M_A_DQ33

H8

M_A_DQ37

G2

M_A_DQ32

H7

M_A_DQ36

D7

M_A_DQ45

C3

M_A_DQ47

C8

M_A_DQ44

C2

M_A_DQ42

A7

M_A_DQ40

A2

M_A_DQ46

B8

M_A_DQ41

A3

M_A_DQ43

C7

M_A_DQSP5

F3

M_A_DQSP4

B7

M_A_DQSN5

G3

M_A_DQSN4

D3

M_A_DM5

E7

M_A_DM4

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

GND GND

D1

D8

E2

E8

F9

G1

G9

T2

DDR3_DRAMRST#

L8

ZQ

DDR_ZQ3 DDR_ZQ4

GND GND

GND

4

M_A_DQ35 (2)

M_A_DQ34 (2)

M_A_DQ38 (2)

M_A_DQ39 (2)

M_A_DQ33 (2)

M_A_DQ37 (2)

M_A_DQ32 (2)

M_A_DQ36 (2)

M_A_DQ45 (2)

M_A_DQ47 (2)

M_A_DQ44 (2)

M_A_DQ42 (2)

M_A_DQ40 (2)

M_A_DQ46 (2)

M_A_DQ41 (2)

M_A_DQ43 (2)

M_A_DQSP5 (2)

M_A_DQSP4 (2)

M_A_DQSN5 (2)

M_A_DQSN4 (2)

M_A_DM5 (2)

M_A_DM4 (2)

0521 :

Change net name

from M_A_DRAMRST# to DDR3_DRAMRST#

DDR3_DRAMRST# (2,8)

R327

240_4

+1.35VSUS

1 2

C366 0.22U/6.3V_4

1 2

C381 0.22U/6.3V_4

1 2

C350 0.22U/6.3V_4

1 2

C365 0.22U/6.3V_4

1 2

C360 0.22U/6.3V_4

1 2

C361 0.22U/6.3V_4

1 2

C352 0.22U/6.3V_4

1 2

C351 0.22U/6.3V_4

1 2

1 2

C363 0.22U/6.3V_4

1 2

C364 0.22U/6.3V_4

1 2

C362 0.22U/6.3V_4

1 2

C397 0.22U/6.3V_4

1 2

C401 0.22U/6.3V_4

1 2

C399 0.22U/6.3V_4

1 2

C402 0.22U/6.3V_4

1 2

C357 0.22U/6.3V_4

1 2

C355 0.22U/6.3V_4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_CS#0

M_A_CLKP1

M_A_CLKN1

M_A_CKE0

M_A_CAS#

M_A_RAS#

M_A_WE#

M_A_ODT0

+1.35VSUS

+1.35VSUS

SMDDR_VREF_DQ0_M1

+SMDDR_VREF_DIMM

M_A_ODT1

M_A_CS#1

M_A_CKE1

R302

240_4

GND

3

U20

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

L2

CS#

J7

CK

K7

CK#

K9

CKE

K3

CAS#

J3

RAS#

L3

WE#

K1

ODT

B2

VDD#B2

D9

VDD#D9

G7

VDD#G7

K2

VDD#K2

K8

VDD#K8

N1

VDD#N1

N9

VDD#N9

R1

VDD#R1

R9

VDD#R9

A1

VDDQ#A1

A8

VDDQ#A8

C1

VDDQ#C1

C9

VDDQ#C9

D2

VDDQ#D2

E9

VDDQ#E9

F1

VDDQ#F1

H2

VDDQ#H2

H9

VDDQ#H9

H1

VREFDQ

M8

VREFCA

J1

ODT1#J1

L1

CS1#L1

J9

CKE1#J9

L9

ZQ1#L9

Memory-Down _DDRL3

DQSU#

DQSL#

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

VSSQ#G1

VSSQ#G9

RESET#

8Gb

96-BALL

SDRAM DDR3

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

DQSU

DQSL

DMU

DML

E3

M_A_DQ51

F7

M_A_DQ55

F2

M_A_DQ50

F8

M_A_DQ48

H3

M_A_DQ49

H8

M_A_DQ53

G2

M_A_DQ54

H7

M_A_DQ52

D7

M_A_DQ57

C3

M_A_DQ58

C8

M_A_DQ56

C2

M_A_DQ63

A7

M_A_DQ61

A2

M_A_DQ59

B8

M_A_DQ60

A3

M_A_DQ62

C7

M_A_DQSP7

F3

M_A_DQSP6

B7

M_A_DQSN7

G3

M_A_DQSN6

D3

M_A_DM7

E7

M_A_DM6

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

0521 :

Change net name

from M_A_DRAMRST# to DDR3_DRAMRST#

T2

DDR3_DRAMRST#

L8

ZQ

2

R309

240_4

M_A_DQ51 (2)

M_A_DQ55 (2)

M_A_DQ50 (2)

M_A_DQ48 (2)

M_A_DQ49 (2)

M_A_DQ53 (2)

M_A_DQ54 (2)

M_A_DQ52 (2)

M_A_DQ57 (2)

M_A_DQ58 (2)

M_A_DQ56 (2)

M_A_DQ63 (2)

M_A_DQ61 (2)

M_A_DQ59 (2)

M_A_DQ60 (2)

M_A_DQ62 (2)

M_A_DQSP7 (2)

M_A_DQSP6 (2)

M_A_DQSN7 (2)

M_A_DQSN6 (2)

M_A_DM7 (2)

M_A_DM6 (2)

NB5

NB5

NB5

09

+1.35VSUS (2,6,8,26)

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

DDR3L - A2

DDR3L - A2

DDR3L - A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

9 30Tuesday, July 02, 2013

9 30Tuesday, July 02, 2013

9 30Tuesday, July 02, 2013

1A

1A

1A

Page 10

1

2

3

4

5

6

7

8

10

A A

TPM_TESTB1

+3V rail for SLB9656

+3VS5 rail for SLB9635

+3VS5+3V

C42

*0.1U/10V_4

R48*4.7K/F_4

Install for SLB9635

No install for SLB9656

R44

*0_4

C28

*0.1U/10V_4

C33

*0.1U/10V_4

+3V

+3V

C39

*0.1U/10V_4

R54*0_4

R46

*0_4

+3V_TPM_PWR

No install for SLB9635

TPM (1.2)

B B

CLK_PCI_TPM

R57

*33_4

C41

*10P/50V_4

FOR EMI

LAD0(5,21,22)

LAD1(5,21,22)

LAD2(5,21,22)

LAD3(5,21,22)

CLK_PCI_TPM(5)

LFRAME#(5,7,21,22)

MINI_PCIE_RST#(4,21)

SERIRQ(5,22)

CLKRUN#(5,22)

LAD0

LAD1

LAD2

LAD3

CLK_PCI_TPM

LFRAME#

MINI_PCIE_RST#

LPCPD#_TPM

SERIRQ

TPM_TESTB1

R71*0_4

Install for SLB9635

No install for SLB9656

Install for SLB9656

U3

*SLB9656TT1.2-FW4.32

26

LAD0

23

LAD1

20

LAD2

17

LAD3

21

LCLK

22

LFRAME#

16

LRESET#

28

LPCPD#

27

SERIRQ

9

TEST/BADD

15

CLKRUN#

1

NC

3

NC

12

NC

VDD

VDD

VDD

VSB

GND

GND

GND

GND

GPIO

GPIO2

TESTI

XTALI/32K IN

XTALO

R65

*0_4

10

19

24

5

4

11

18

25

6

2

7

PP

TPM_PP

8

13

TPM_XIN

14

TPM_XOUT

LPCPD#_TPM

TPM_PP

Install for SLB9635

No install for SLB9656

No install for SLB9635

Install for SLB9656

R59*4.7K/F_4

R47*4.7K/F_4

R64*0_4

R49*4.7K/F_4

R51*4.7K/F_4

+3V

MINI_PCIE_RST#TPM_TESTB1

+3V

Address

C C

SLB9635 SLB9656

R71 Install No install

R46

R44

No install

Install

(default)

BADD

HIGH

4EH/4F

Install

No install

Y1

*32.768KHZ

C52

*12P/50V_4

H=2.54mm

Install for SLB9635

No install for SLB9656

21

C53

*12P/50V_4

R48 Install No install

Y1,C52,C53

R59

D D

R47

Install No install

Install

Install

No install

No install

+3V(3,4,5,6,11,13,14,15,18,19,20,21,22,27,29)

+3VS5(4,5,6,7,12,13,21,22,24,25,29)

R64 No install Install

R65 No install Install

1

2

NB5

NB5

3

4

5

6

NB5

PROJECT : Y02

PROJECT : Y02

PROJECT : Y02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet

TPM SLB9656/SLB9635

TPM SLB9656/SLB9635

TPM SLB9656/SLB9635

7

of

10 30Tuesday, July 02, 2013

10 30Tuesday, July 02, 2013

10 30Tuesday, July 02, 2013

8

1A

1A

1A

Page 11

1

LID Switch

EMU_LID(22)

LVDS_BLON1

+VIN

+VIN

LVDS_BLON1

C282

4.7U/25V_8

EC12

0.1U/25V_4

A A

B B

R13 0_4

R15 1K/F_4

R18 100K/F_4

L20 0_8

L21 0_8

MI suggestion

E

C279

4.7U/25V_8

EC6

0.1U/25V_4

EC18 0.1U/25V_4

EMI suggestion

C2

1U/6.3V_4

C C

DISP_ON_L

DISP_ON_L need 80 mil trace

2

PN_BLON

D1 MEK500V-40

100mA

+VIN_BLIGHT

C275 0.1U/25V_4

C274 0.01U/25V_4

C276

0.1U/25V_4

EC1

0.1U/25V_4

+3V

Power Switch

U1

5

IN

4

IN

3

ON/OFF

IC(5P) G5243AT11U

AL005243001 GMT:G5243AT11U

AL002821000 BCD:AP2821KTR-G1

+VIN_BLIGHT

C277

0.1U/25V_4

EC14

0.1U/25V_4

BLON_CON

C281

0.1U/25V_4

EC3

0.1U/25V_4

OUT

GND

1

2

R8 100K/F_4

BRIGHT

C278

0.1U/25V_4

EC2

0.1U/25V_4

L3

TI160808U600

3

C10 22P/50V_4

R10

R14

100K/F_4

C283

0.1U/25V_4

C5

0.01U/16V_4

2 1

1K/F_4

C6

0.1U/10V_4

2 1

+3VLCD_CON

2 1

VADJ1

C9

33P/50V_4

C8

10U/6.3V_6

4

LVDS SINGLE

LVDS_DATAN2(3)

LVDS_DATAP2(3)

LVDS_AUXP_CLK(3)

LVDS_AUXN_DATA(3)

LVDS_TXN1_R(3)

LVDS_TXP1_R(3)