HP IFD-53110, IFD-53010 Datasheet

Silicon Bipolar MMIC

3.5 and 5.5 GHz Divide-by-4

Static Prescalers

Technical Data

IFD-53010

IFD-53110

Features

• Wide Operating Frequency

Range:

IFD-53010: 0.15 to 5.5 GHz

IFD-53110: 0.15 to 3.5 GHz

• Low Phase Noise:

-143 dBc/Hz @ 1 kHz Offset

• Output Power: -5 dBm Typ.

• Single Supply Voltage

Vcc = 5 V or Vee = -5 V

• On-Chip Terminations

Provide Good Input and

Output VSWRs

• Hermetic Gold-Ceramic

Surface Mount Package

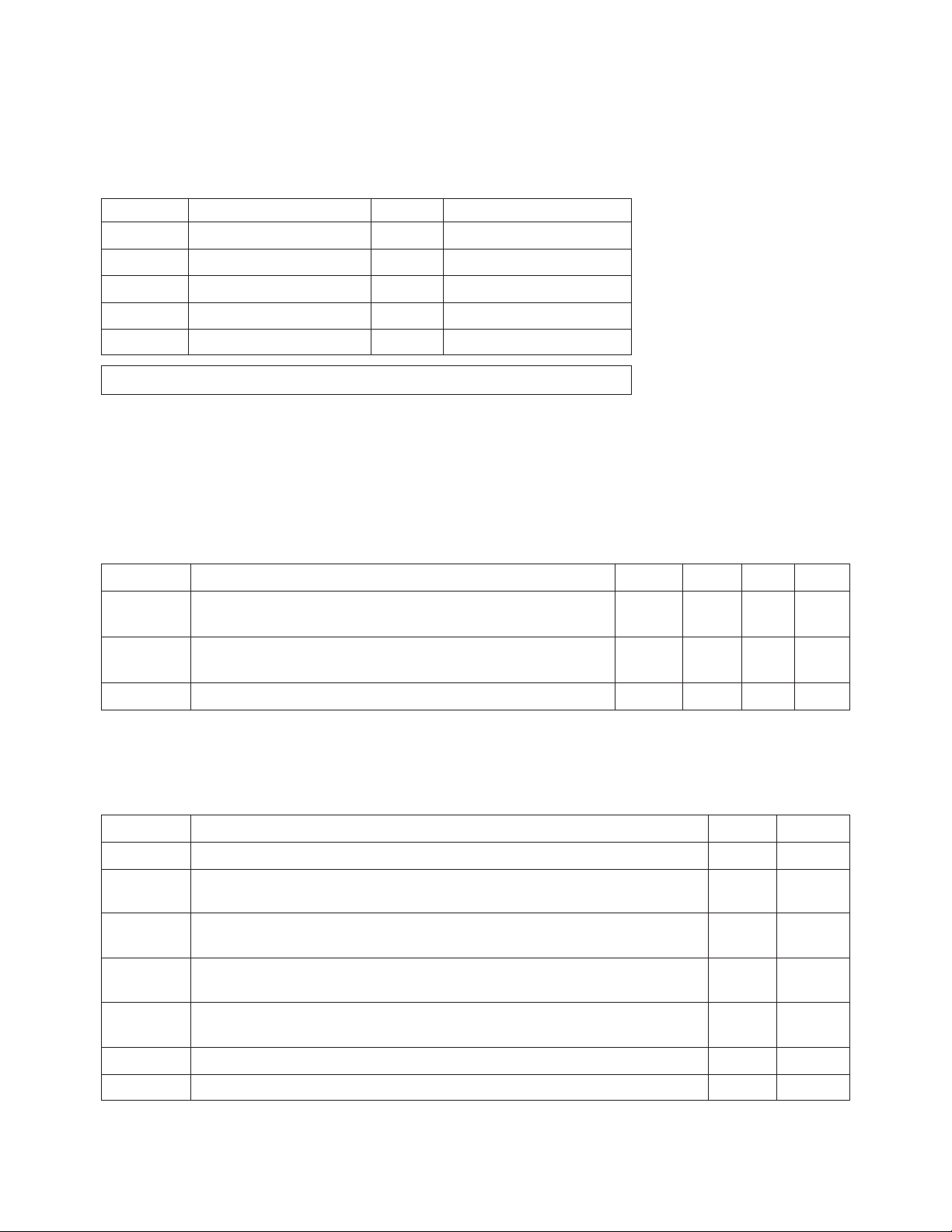

Functional Block Diagram

1

V

CC

RF INPUT

4

CQ CQ

CQ CQ

3

100 mil Stripline Package Description

Hewlett-Packard's IFD-53010 and

IFD-53110 are low phase noise

silicon bipolar static digital

frequency dividers using two

scaled Emitter-Coupled-Logic

(ECL) master-slave D flip-flops

and buffer amplifiers. They are

housed in hermetic high reliability

surface mount packages suitable

Pin Configuration

V

3

EE

4

RF INPUT RF OUTPUT

V

1

CC

V

EE

2

RF OUTPUT

2

for commercial, industrial, and

military applications. Typical

applications include stabilized or

digitally controlled local oscillators for GPS, SATCOM or

military receivers, and frequency

synthesizers and counters in

instrumentation systems. The

IFD-53110 is a lower cost selected

version of the IFD-53010, and is

distinguished by a reduced

operating frequency range.

The IFD series of frequency

dividers is fabricated using

Hewlett-Packard's 18 GHz, ft,

ISOSAT™-2 silicon bipolar

process which uses nitride selfalignment, submicrometer

lithography, trench isolation, ionimplantation, gold metallization

and polyimide intermetal

dielectric and scratch protection

to achieve excellent device

uniformity, performance, and

reliability.

7-151

5965-9115E

Absolute Maximum Ratings

Symbol Parameter Units Absolute Maximum

[1]

Vcc - V

P

diss

P

in

T

j

T

STG

Thermal Resistance

Notes:

1, Operation of this device above any one of these parameters may cause permanent damage.

2. T

= 25°C.

case

3. Derate at 9.3 mW/°C for TC ≥ 130°C.

Device Voltage V 8

ee

Power Dissipation

[2,3]

m W 650

RF Input Power dBm +15

Junction Temperature °C 200

Storage Temperature °C -65 to +200

[2]

: θjc = 107° C/W

Guaranteed Electrical Specifications, IFD-53010 and IFD-53110

T

= 25° C, ZO = 50 Ω, V

A

Symbol Parameters and Test Conditions Units Min. Typ. Max.

IFD-53010:

F

MAX

Maximum Clock Frequency Pin = -10 dBm (200 mVpp) GHz 5.5 6.0

IFD-53110:

F

MAX

I

CC

Maximum Clock Frequency Pin = -10 dBm (200 mVpp) GHz 3.5 5.0

IFD-53010 and IFD-53110: Supply Current mA 35 43 50

- Vee = 5.0 V

cc

Typical Design Information, T

All values apply to both IFD-53010 and IFD-53110. f

= 25° C, Z0 = 50 Ω, V

A

is 5 GHz for IFD-53010 and 3 GHz for IFD-53110 (unless

test

- Vee = 5.0 V, Pin = -10 dBm.

cc

otherwise noted).

Symbol Parameters and Test Conditions Units Value

F

MIN

P

Minimum Clock Frequency

in

Input Sensitivity f = f

[1]

test

MHz 150

dBm -22

mVpp 50

P

out

Output Power f = 0.15 to f

test

dBm -5

mVpp 355

VSWR Input VSWR f = 0.15 to f

Output VSWR f = 0.15 to f

test

test

2.0:1

2.5:1

PN SSB Phase Noise f = 3 GHz, 1 kHz offset dBc/Hz -143

f = 5 GHz, 1 kHz offset (IFD-53010 only) -138

T

r

T

f

Note:

1. Minimum clock frequency when driven from a sinusoidal input. Operation to lower frequencies is possible when using input signals

with faster rise times, such as occurs in the case of a cascade of two or more IFDs.

Output Rise Time, 20% - 80% f = f

Output Fall Time, 20% - 80% f = f

test

test

psec 145

psec 85

7-152

Loading...

Loading...