Fibre Channel Transceiver Chip

Technical Data

HDMP-1536 Transceiver

HDMP-1546 Transceiver

Features

• ANSI X3.230-1994 Fibre

Channel Compatible (FC-0)

• Supports Full Speed

(1062.5 MBd) Fibre Channel

• Compatible with “Fibre

Channel 10-Bit Interface”

Specification

• Low Power Consumption,

630 mW

• Transmitter and Receiver

Functions Incorporated onto

a Single IC

• Auto Frequency Lock

• Small Package Profile

HDMP-1536, 10x10 mm QFP

HDMP-1546, 14x14 mm QFP

• 10-Bit Wide Parallel TTL

Compatible I/Os

• Single +3.3 V Power Supply

Applications

• 1062.5 MBd Fibre Channel

Interface

• FC Interface for Disk Drives

and Arrays

• Mass Storage System I/O

Channel

• Work Station/Server I/O

Channel

• High Speed Proprietary

Interface

• High Speed Backplane

Interface

Description

The HDMP-1536/46 transceiver

is a single silicon bipolar

integrated circuit packaged in a

plastic QFP package. It provides

a low-cost, low-power physical

layer solution for 1062.5 MBd

Fibre Channel or proprietary link

interfaces. It provides complete

FC-0 functionality for copper

transmission, incorporating both

the Fibre Channel FC-0 transmit

and receive functions into a

single device.

This chip is used to build a highspeed interface (as shown in

Figure 1) while minimizing board

space, power, and cost. It is

compatible with both the ANSI

X3.230-1994/AM 1 - 1996

document and the “Fibre Channel

10-bit Interface” specification.

The transmitter section accepts

10-bit wide parallel TTL data and

multiplexes this data into a highspeed serial data stream. The

parallel data is expected to be

8B/10B encoded data, or

equivalent. This parallel data is

latched into the input register of

the transmitter section on the

rising edge of the 106.25 MHz

reference clock (used as the

transmit byte clock).

The transmitter section’s PLL

locks to this user supplied 106.25

MHz byte clock. This clock is

then multiplied by 10, to generate

the 1062.5 MHz serial signal

clock used to generate the highspeed output. The high-speed

outputs are capable of interfacing

directly to copper cables for

electrical transmission or to a

separate fiber-optic module for

optical transmission.

The receiver section accepts a

serial electrical data stream at

1062.5 MBd and recovers the

original 10-bit wide parallel data.

The receiver PLL locks onto the

incoming serial signal and

recovers the high-speed serial

clock and data. The serial data is

696

5965-8113E (4/97)

HDMP-15x6

PROTOCOL DEVICE

BYTSYNC

REFCLK

ENBYTSYNC

-LCKREF

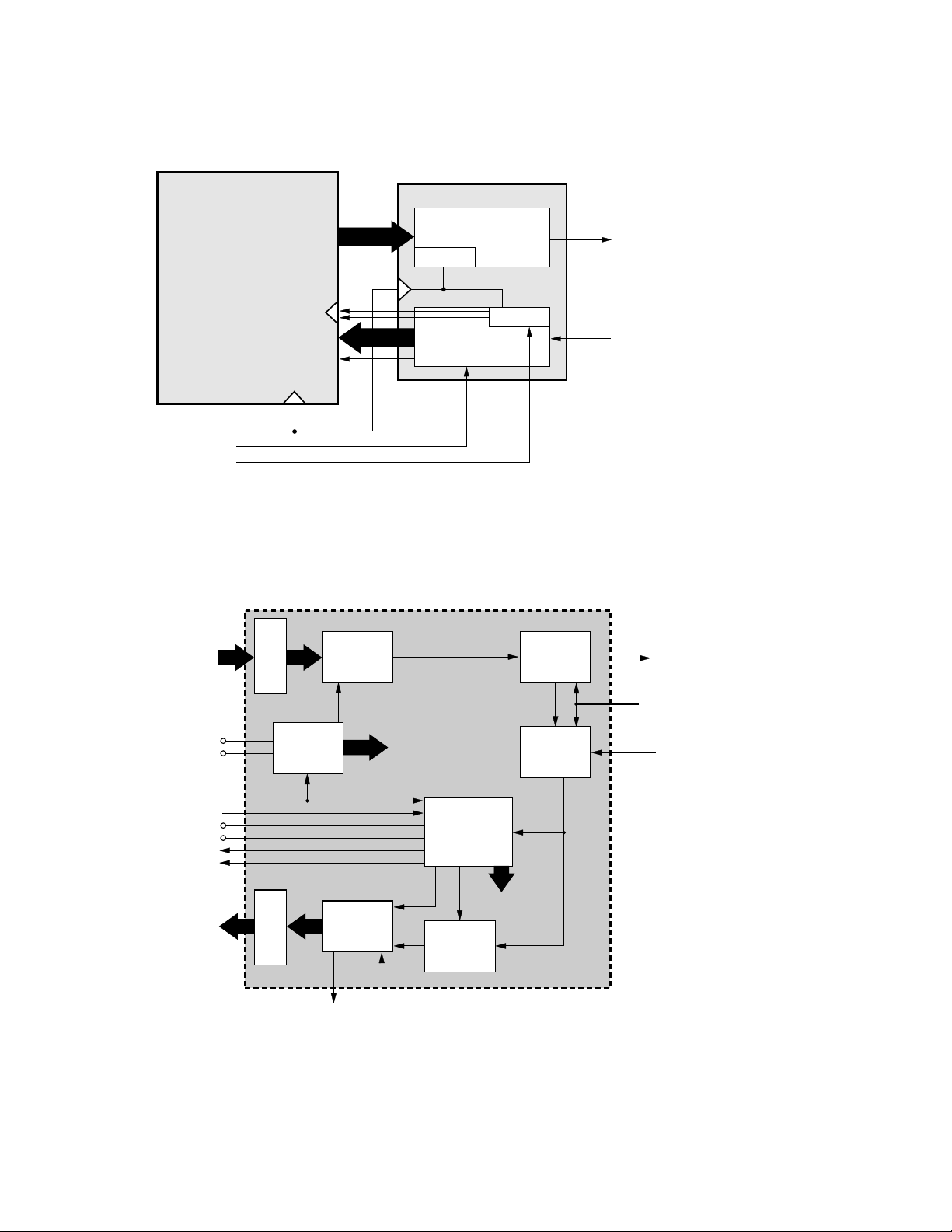

Figure 1. Typical Application Using the HDMP-15x6.

DATA BYTE

TX[0-9]

INPUT

LATCH

FRAME

MUX

TRANSMITTER SECTION

PLL

PLL

RECEIVER SECTION

OUTPUT

SELECT

SERIAL DATA OUT

SERIAL DATA IN

± DOUT

TXCAP0

TXCAP1

REFCLK

-LCKREF

RXCAP0

RXCAP1

RBC0

RBC1

DATA BYTE

RX[0-9]

TX

PLL/CLOCK

GENERATOR

FRAME

DEMUX

DRIVER

OUTPUT

BYTE SYNC

BYTSYNC ENBYTSYNC

AND

INTERNAL

TX CLOCKS

Figure 2. HDMP-15x6 Transceiver Block Diagram.

RX

PLL/CLOCK

RECOVERY

RX CLOCKS

INPUT

SAMPLER

INTERNAL

LOOPBACK

INTERNAL

INPUT

SELECT

LOOPEN

± DIN

697

converted back into 10-bit

parallel data, recognizing the

8B/10B comma character to

establish byte alignment.

The recovered parallel data is

presented to the user at TTL

compatible outputs. The receiver

section also recovers two

53.125 MHz receiver byte clocks

that are 180 degrees out of phase

with each other. The parallel data

is properly aligned with the rising

edge of alternating clocks.

The transceiver provides for onchip local loop-back functionality,

controlled through an external

input pin. Additionally, the byte

synchronization feature may be

disabled. This may be useful in

proprietary applications which

use alternative methods to align

the parallel data.

HDMP-1536/46 Block Diagram

The HDMP-1536/46 was designed

to transmit and receive 10-bit

wide parallel data over a single

high-speed line, as specified for

the FC-0 layer of the Fibre

Channel standard. The parallel

data applied to the transmitter is

expected to be encoded per the

Fibre Channel specification,

which uses an 8B/10B encoding

scheme with special reserve

characters for link management

purposes. In order to accomplish

this task, the HDMP-1536/46

incorporates the following:

• TTL Parallel I/Os

• High Speed Phase Lock Loops

• Clock Generation/Recovery

Circuitry

• Parallel to Serial Converter

• High-Speed Serial Clock and

Data Recovery Circuitry

• Comma Character Recognition

Circuitry

• Byte Alignment Circuitry

• Serial to Parallel Converter

INPUT LATCH

The transmitter accepts 10-bit

wide TTL parallel data at inputs

TX[0..9]. The user-provided

reference clock signal, REFCLK,

is also used as the transmit byte

clock. The TX[0..9] and REFCLK

signals must be properly aligned,

as shown in Figure 3.

TX PLL/CLOCK GENERATOR

The transmitter Phase Lock Loop

and Clock Generator (TX PLL/

CLOCK GENERATOR) block is

responsible for generating all

internal clocks needed by the

transmitter section to perform its

functions. These clocks are based

on the supplied reference byte

clock (REFCLK). REFCLK is used

as both the frequency reference

clock for the PLL and the transmit byte clock for the incoming

data latches. It is expected to be

106.25 MHz and properly aligned

to the incoming parallel data (see

Figure 3). This clock is multiplied

by 10 to generate the 1062.5

MHz clock necessary for the high

speed serial outputs.

FRAME MUX

The FRAME MUX accepts the 10bit wide parallel data from the

INPUT LATCH. Using internally

generated high speed clocks, this

parallel data is multiplexed into

the 1062.5 MBd serial data

stream. The data bits are transmitted sequentially, from the

least significant bit (TX[0]) to the

most significant bit (TX[9]).

OUTPUT SELECT

The OUTPUT SELECT block

provides for an optional internal

loopback of the high speed serial

signal, for testing purposes.

In normal operation, LOOPEN is

set low and the serial data stream

is placed at ± DOUT. When wrapmode is activated by setting

LOOPEN high, the ± DOUT pins

are held static and the serial

output signal is internally

wrapped to the INPUT SELECT

box of the receiver section.

INPUT SELECT

The INPUT SELECT block determines whether the signal at ± DIN

or the internal loop-back serial

signal is used. In normal operation, LOOPEN is set low and the

serial data is accepted at ± DIN.

When LOOPEN is set high, the

high-speed serial signal is

internally looped-back from the

transmitter section to the receiver

section. This feature allows for

loop-back testing exclusive of the

transmission medium.

RX PLL/CLOCK RECOVERY

The RX PLL/CLOCK RECOVERY

block is responsible for frequency

and phase locking onto the

incoming serial data stream and

recovering the bit and byte

clocks. An automatic locking

feature allows the Rx PLL to lock

onto the input data stream

without external controls. It does

this by continually frequency

locking onto the 106.25 MHz

clock, and then phase locking

onto the input data stream. An

internal signal detection circuit

monitors the presence of the

input, and invokes the phase

detection as the data stream

appears. Once bit locked, the

receiver generates the high speed

sampling clock at 1062.5 MHz

for the input sampler, and

recovers the two 53.125 MHz

receiver byte clocks (RBC1/

RBC0). These clocks are 180° out

of phase with each other, and are

698

alternately used to clock the 10bit parallel output data.

An optional -LCKREF pin is

available for users who want to

gain full control during the

frequency acquisition process.

Asserting this pin will force the

Rx PLL to fully phase and

frequency lock onto the reference

clock, disregarding the serial

stream completely.

To enable the auto-locking

feature, the -LCKREF pin should

be tied to VCC. The receiver will

detect the absence of high-speed

serial data into +DIN (pin 54)

and -DIN (pin 52) and lock onto

the reference clock (REFCLK).

RBC0 and RBC1 will remain

frequency locked to 53.125 MHz.

The receiver will frequency and

phase lock onto the incoming

valid data once it is reapplied.

INPUT SAMPLER

The INPUT SAMPLER is

responsible for converting the

serial input signal into a re-timed

serial bit stream. In order to

accomplish this, it uses the high

speed serial clock recovered from

the RX PLL/CLOCK RECOVERY

block. This serial bit stream is

sent to the FRAME DEMUX and

BYTE SYNC block.

FRAME DEMUX AND BYTE SYNC

The FRAME DEMUX AND BYTE

SYNC block is responsible for

restoring the 10-bit parallel data

from the high speed serial bit

stream. This block is also

responsible for recognizing the

comma character (or a K28.5

character) of positive disparity

(0011111xxx). When recognized,

the FRAME DEMUX AND BYTE

SYNC block works with the RX

PLL/CLOCK RECOVERY block to

properly align the receive byte

clocks to the parallel data. When

a comma character is detected

and realignment of the receiver

byte clocks (RBC1/RBC0) is

necessary, these clocks are

stretched, not slivered, to the

next possible correct alignment

position. These clocks will be

fully aligned by the start of the

second 4-byte ordered set. The

second comma character received

shall be aligned with the rising

edge of RBC1. Comma characters

should not be transmitted in

consecutive bytes to allow the

receiver byte clocks to maintain

their proper recovered

frequencies.

OUTPUT DRIVERS

The OUTPUT DRIVERS present

the 10-bit parallel recovered data

byte properly aligned to the

receiver byte clocks

(RBC1/RBC0), as shown in

Figure 5. These output data

buffers provide TTL compatible

signals.

Recommended Handling Precautions

Additional circuitry is built into

the various input and output pins

on this chip to protect against

low level electrostatic discharge;

however, they are still ESD

sensitive. Standard procedures

for static sensitive devices should

be used in the handling and

assembly of this product.

699

HDMP-1536/46 (Transmitter Section)

Timing Characteristics

[1]

T

= 0°C to +60°C, VCC = 3.15 V to 3.45 V

A

Symbol Parameter Units Min. Typ. Max.

t

setup

t

hold

[2]

t_txlat

Notes:

1. Device tested and characterized under TA conditions specified, with TC monitored at approximately 20° higher than TA.

2. The transmitter latency, as shown in Figure 4, is defined as the time between the latching in of the parallel data word (as triggered

by the rising edge of the transmit byte clock, REFCLK) and the transmission of the first serial bit of that parallel word (defined by

the rising edge of the first bit transmitted).

Setup Time nsec 2

Hold Time nsec 1.5

Transmitter Latency nsec 7.5

bits 8.0

REFCLK

TX[0]-TX[9]

DATA

t

setup

Figure 3. Transmitter Section Timing.

± DOUT

TX[0]-TX[9]

T5 T6 T7 T8 T9 T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T0 T1 T2 T3 T4 T5

DATA DATA

t

hold

DATA BYTE A

t_txlat

DATA BYTE B DATA BYTE C

DATA DATA

1.4 V

2.0 V

0.8 V

DATA BYTE B

REFCLK

Figure 4. Transmitter Latency.

700

1.4 V

Loading...

Loading...