HP HCPL-0710 Datasheet

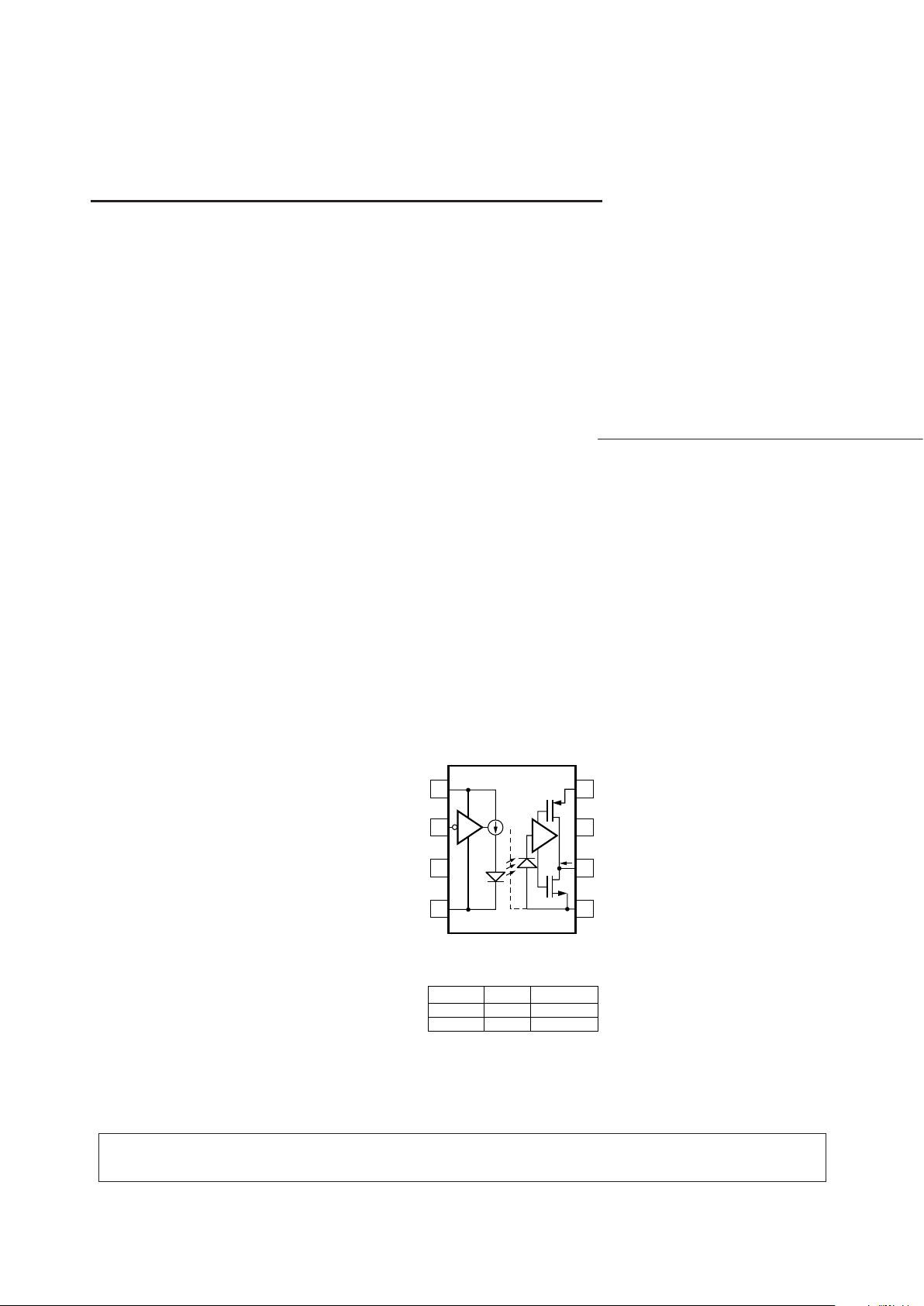

8

7

6

1

3

SHIELD

5

2

4

**V

DD1

V

I

*

GND

1

V

DD2

**

V

O

GND

2

VI, INPUT LED1

H

L

OFF

ON

TRUTH TABLE

(POSITIVE LOGIC)

NC*

I

O

LED1

V

O

, OUTPUT

H

L

H

40 ns Prop. Delay,

SO-8 Optocoupler

Technical Data

HCPL-0710

Functional Diagram

*Pin 3 is the anode of the internal LED and must be left unconnected for guaranteed data sheet performance.

Pin 7 is not connected internally. External connections to pin 7 are not recommended.

**A 0.1 µF bypass capacitor must be connected between pins 1 and 4, and 5 and 8.

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component

to prevent damage and/or degradation which may be induced by ESD.

Features

• +5 V CMOS Compatibility

• 8 ns max. Pulse Width

Distortion

• 20 ns max. Prop. Delay Skew

• High Speed: 12 Mbd

• 40 ns max. Prop. Delay

• 10 kV/µs Minimum Common

Mode Rejection

• 0°C to 85°C Temp. Range

• Safety and Regulatory

Approvals

UL Recognized

2500 V rms for 1 min. per

UL 1577

CSA Component Acceptance

Notice #5

Applications

• Digital Fieldbus Isolation:

DeviceNet, SDS, Profibus

• AC Plasma Display Panel

Level Shifting

• Multiplexed Data

Transmission

• Computer Peripheral

Interface

• Microprocessor System

Interface

Description

Available in the SO-8 package

style, the HCPL-0710 optocoupler

utilizes the latest CMOS IC

technology to achieve outstanding

performance with very low power

consumption. The HCPL-0710

requires only two bypass

capacitors for complete CMOS

compatability.

Basic building blocks of the

HCPL-0710 are a CMOS LED

driver IC, a high speed LED and a

CMOS detector IC. A CMOS logic

input signal controls the LED

driver IC which supplies current

to the LED. The detector IC

incorporates an integrated

photodiode, a high-speed

transimpedance amplifier, and a

voltage comparator with an

output driver.

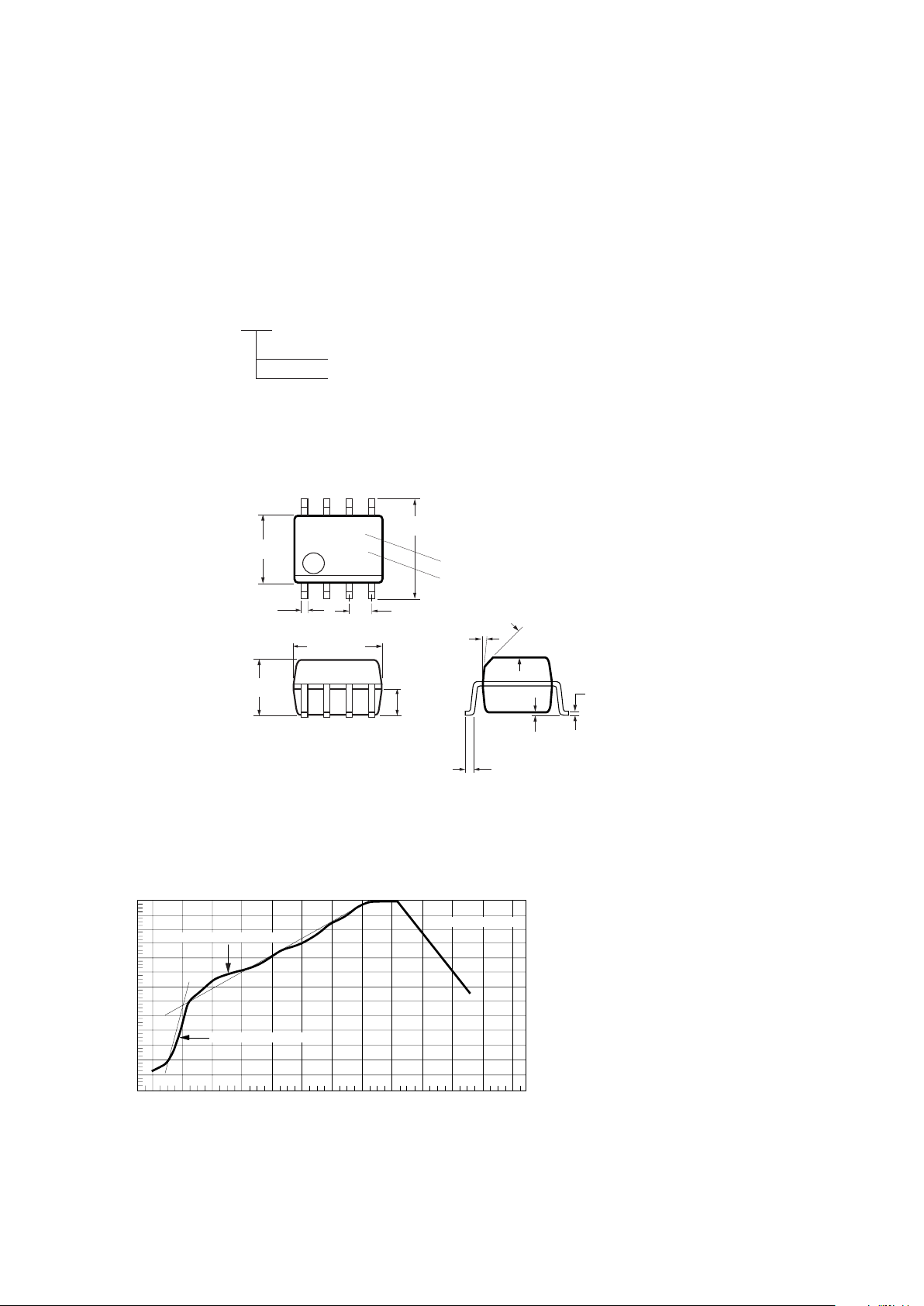

710

YWW

87

65

4

3

2

1

PIN

ONE

7°

5.842 ± 0.203

(0.236 ± 0.008)

3.937 ± 0.127

(0.155 ± 0.005)

0.381 ± 0.076

(0.016 ± 0.003)

1.270

(0.050)

BSG

5.080 ± 0.005

(0.200 ± 0.005)

3.175 ± 0.127

(0.125 ± 0.005)

1.524

(0.060)

45° X

0.432

(0.017)

0.228 ± 0.025

(0.009 ± 0.001)

0.152 ± 0.051

(0.006 ± 0.002)

TYPE NUMBER (LAST 3 DIGITS)

DATE CODE

DIMENSIONS IN MILLIMETERS AND (INCHES).

LEAD COPLANARITY = 0.10 mm (0.004 INCHES).

0.305

(0.012)

MIN.

Ordering Information

Specify Part Number followed by Option Number (if desired)

Example

HCPL-0710#XXX

No Option = Standard SO-8 package, 100 per tube.

500 = Tape and Reel Packaging Option, 1500 per reel.

Option data sheets available. Contact Hewlett-Packard sales representative or authorized distributor.

Package Outline Drawing

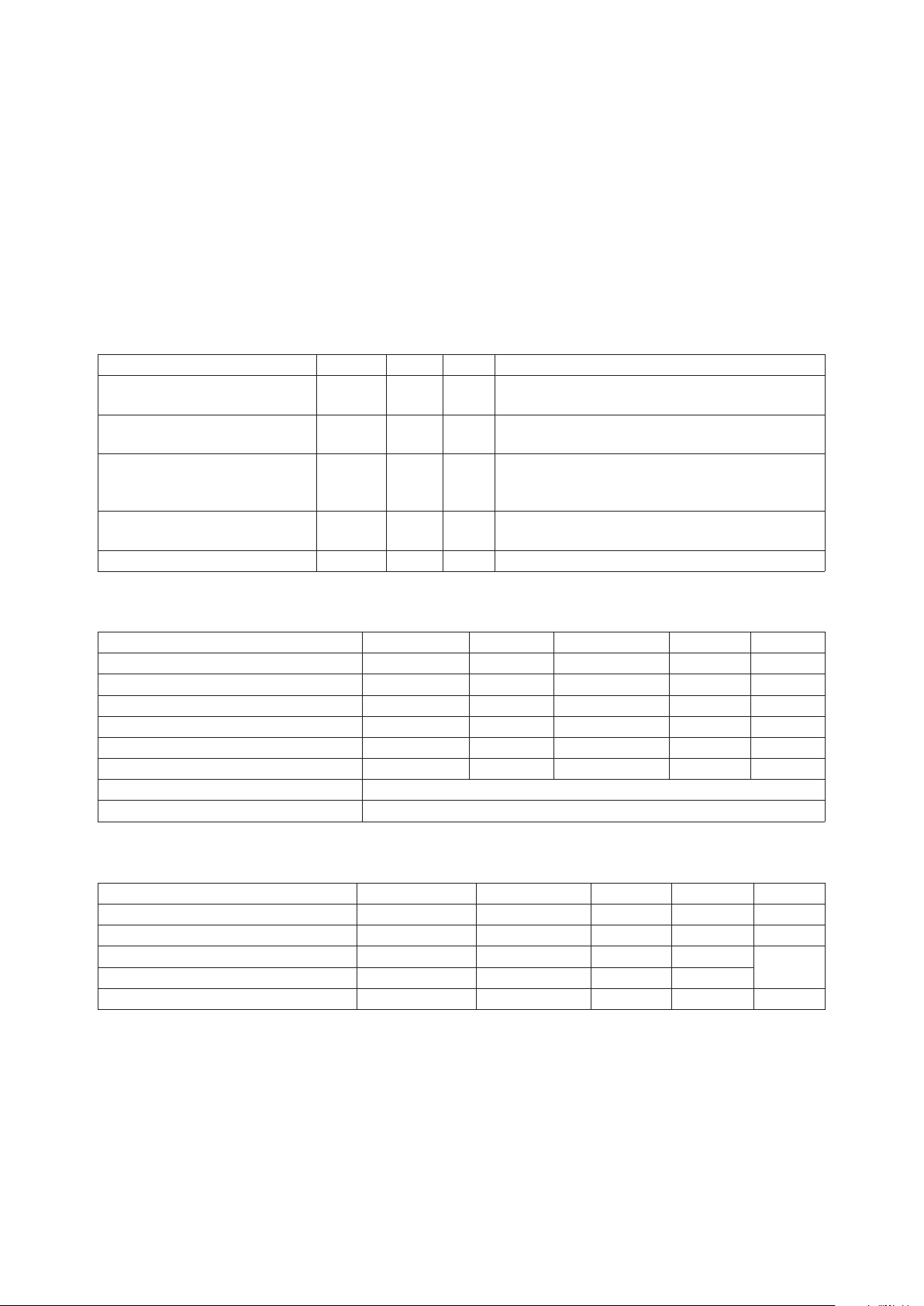

Solder Reflow Thermal Profile

240

∆T = 115°C, 0.3°C/SEC

0

∆T = 100°C, 1.5°C/SEC

∆T = 145°C, 1°C/SEC

TIME – MINUTES

TEMPERATURE – °C

220

200

180

160

140

120

100

80

60

40

20

0

260

123456789101112

(NOTE: USE OF NON-CHLORINE ACTIVATED FLUXES IS RECOMMENDED.)

Recommended Operating Conditions

Parameter Symbol Min. Max. Units Figure

Ambient Operating Temperature T

A

0 +85 °C

Supply Voltages V

DD1

, V

DD2

4.5 5.5 V

Logic High Input Voltage V

IH

0.8 * V

DD1

V

DD1

V 1, 2

Logic Low Input Voltage V

IL

0.0 0.8 V

Input Signal Rise and Fall Times tr, t

f

1.0 ms

Regulatory Information

The HCPL-0710 has been

approved by the following

organizations:

UL

Recognized under UL 1577,

component recognition program,

File E55361.

Absolute Maximum Ratings

Parameter Symbol Min. Max. Units Figure

Storage Temperature T

S

-55 125 °C

Ambient Operating Temperature

[1]

T

A

-40 +100 °C

Supply Voltages V

DD1

, V

DD2

0 5.5 Volts

Input Voltage V

I

-0.5 V

DD1

+0.5 Volts

Output Voltage V

O

-0.5 V

DD2

+0.5 Volts

Average Output Current I

O

10 mA

Lead Solder Temperature 260°C for 10 sec., 1.6 mm below seating plane

Solder Reflow Temperature Profile See Solder Reflow Temperature Profile Section

Insulation and Safety Related Specifications

Parameter Symbol Value Units Conditions

Minimum External Air Gap L(I01) 4.9 mm Measured from input terminals to output

(Clearance) terminals, shortest distance through air.

Minimum External Tracking L(I02) 4.8 mm Measured from input terminals to output

(Creepage) terminals, shortest distance path along body.

Minimum Internal Plastic Gap 0.08 mm Insulation thickness between emitter and

(Internal Clearance) detector; also known as distance through

insulation.

Tracking Resistance CTI 200 Volts DIN IEC 112/VDE 0303 Part 1

(Comparative Tracking Index)

Isolation Group IIIa Material Group (DIN VDE 0110, 1/89, Table 1)

CSA

Approved under CSA Component

Acceptance Notice #5, File CA

88324.

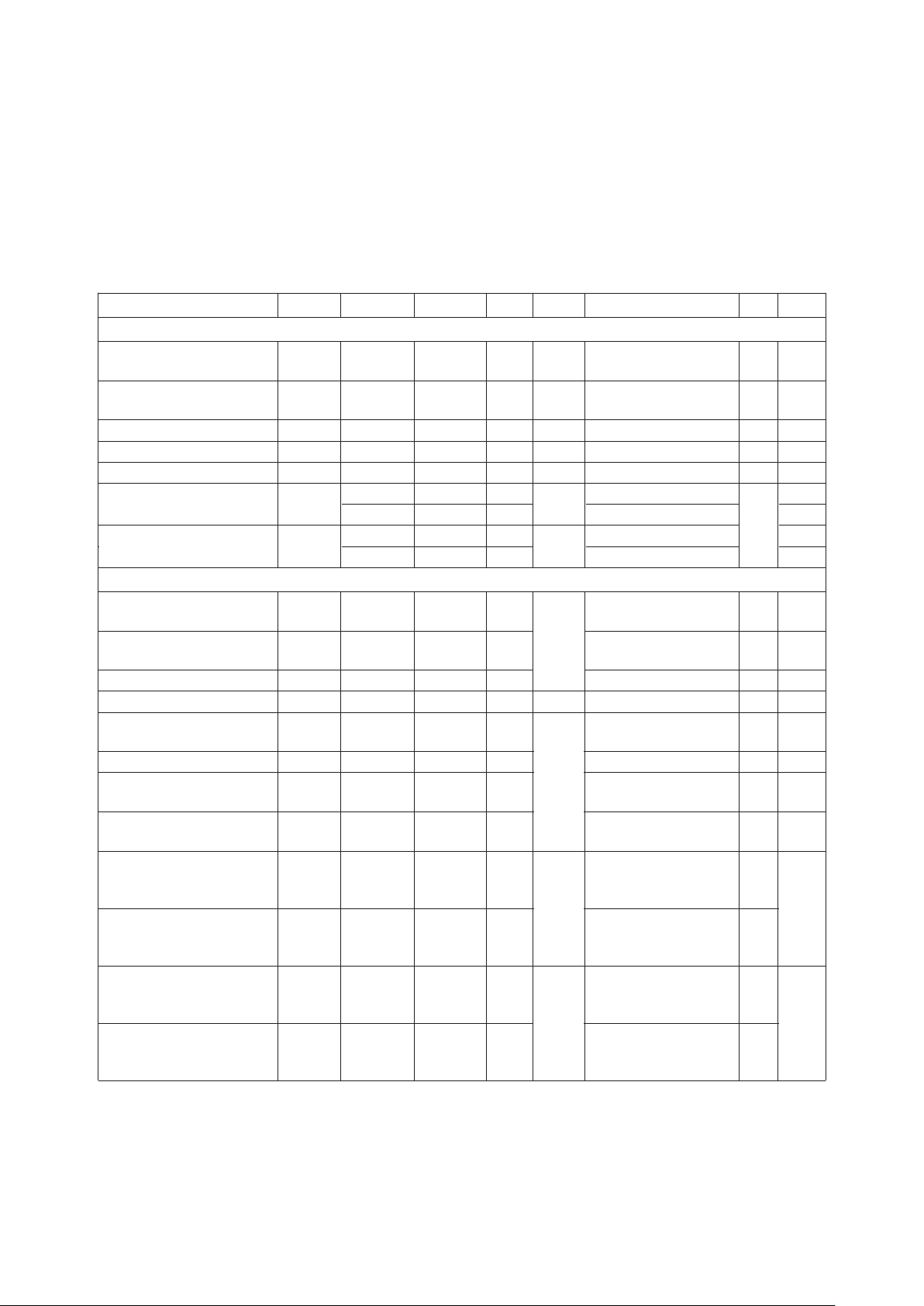

Electrical Specifications

Test conditions that are not specified can be anywhere within the recommended operating range. All typical

specifications are at TA = +25°C, V

DD1

= V

DD2

= +5 V.

Parameter Symbol Min. Typ. Max. Units Test Conditions Fig. Note

DC Specifications

Logic Low Input I

DD1L

6.0 10.0 mA VI = 0 V 2

Supply Current

Logic High Input I

DD1H

1.5 3.0 mA VI = V

DDI

Supply Current

Input Supply Current I

DD1

13.0 mA

Output Supply Current I

DD2

5.5 11.0 mA

Input Current I

I

-10 10 µA

Logic High Output V

OH

V

DD2

- 0.1 V

DD2

VIO = -20 µA, VI = VIH1, 2

0.8 *V

DD2VDD2

- 0.5 IO = -4 mA, VI = V

IH

Logic Low Output V

OL

0 0.1 V IO = 20 µA, VI = V

IL

0.5 1.0 IO = 4 mA, VI = V

IL

Switching

Propagation Delay Time t

PHL

20 40 ns CL = 15 pF 3, 7 3

to Logic Low Output CMOS Signal Levels

Propagation Delay Time t

PLH

23 40

to Logic High Output

Pulse Width PW 80 4

Data Rate 12.5 MBd

Pulse Width Distortion PWD 3 8 ns CL = 15 pF 4, 8 5

|t

PHL

- t

PLH

| CMOS Signal Levels

Propagation Delay Skew t

PSK

20 6

Output Rise Time t

R

9C

L

= 15 pF 5, 9

(10 - 90%) CMOS Signal Levels

Output Fall Time t

F

86,

(90 - 10%) 10

Common Mode |CMH| 10 20 kV/µsVI = V

DD1

, VO >7

Transient Immunity at 0.8 V

DD1

,

Logic High Output VCM = 1000 V

Common Mode |CML|10 20 V

I

= 0 V, VO > 0.8 V,

Transient Immunity at VCM = 1000 V

Logic Low Output

Input Dynamic Power C

PD1

60 pF 8

Dissipation

Capacitance

Output Dynamic Power C

PD2

10

Dissipation

Capacitance

Voltage

Voltage

Specifications

Package Characteristics

Parameter Symbol Min. Typ. Max. Units Test Conditions Fig. Note

Input-Output Momentary V

ISO

2500 Vrms RH ≤ 50%, t = 1 min., 9, 10,

Withstand Voltage TA = 25°C11

Resistance R

I-O

10

12

Ω V

I-O

= 500 Vdc 9

(Input-Output)

Capacitance C

I-O

0.6 pF f = 1 MHz

(Input-Output)

Input Capacitance C

I

3.0 12

Input IC Junction-to-Case θ

jci

160 °C/W Thermocouple

Thermal Resistance located at center

Output IC Junction-to-Case θ

jco

135

Thermal Resistance

Package Power Dissipation P

PD

150 mW

Notes:

1. Absolute Maximum ambient operating

temperature means the device will not

be damaged if operated under these

conditions. It does not guarantee

functionality.

2. The LED is ON when VI is low and OFF

when VI is high.

3. t

PHL

propagation delay is measured

from the 50% level on the falling edge

of the VI signal to the 50% level of the

falling edge of the VO signal. t

PLH

propagation delay is measured from

the 50% level on the rising edge of the

VI signal to the 50% level of the rising

edge of the VO signal.

4. Mimimum Pulse Width is the shortest

pulse width at which 10% maximum,

Pulse Width Distortion can be guaranteed. Maximum Data Rate is the

inverse of Minimum Pulse Width.

Operating the HCPL-0710 at data rates

above 12.5 MBd is possible provided

PWD and data dependent jitter

increases and relaxed noise margins

underside of

package

are tolerable within the application.

For instance, if the maximum

allowable variation of bit width is 30%,

the maximum data rate becomes 37.5

MBd. Please note that HCPL-0710

performance above 12.5 MBd is not

guaranteed by Hewlett-Packard.

5. PWD is defined as |t

PHL

- t

PLH

|.

%PWD (percent pulse width distortion)

is equal to the PWD divided by pulse

width.

6. t

PSK

is equal to the magnitude of the

worst case difference in t

PHL

and/or

t

PLH

that will be seen between units at

any given temperature within the

recommended operating conditions.

7. CMH is the maximum common mode

voltage slew rate that can be sustained

while maintaining VO > 0.8 V

DD2

. CM

L

is the maximum common mode voltage

slew rate that can be sustained while

maintaining VO < 0.8 V. The common

mode voltage slew rates apply to both

rising and falling common mode

voltage edges.

8. Unloaded dynamic power dissipation is

calculated as follows: CPD * V

DD2

* f +

IDD * VDD, where f is switching

frequency in MHz.

9. Device considered a two-terminal

device: pins 1, 2, 3, and 4 shorted

together and pins 5, 6, 7, and 8

shorted together.

10. In accordance with UL1577, each

optocoupler is proof tested by

applying an insulation test voltage

≥ 3000 V

RMS

for 1 second (leakage

detection current limit, I

I-O

≤ 5 µA).

11. The Input-Output Momentary Withstand Voltage is a dielectric voltage

rating that should not be interpreted as

an input-output continuous voltage

rating. For the continuous voltage

rating refer to your equipment level

safety specification or HP Application

Note 1074 entitled “Optocoupler

Input-Output Endurance Voltage.”

12. CI is the capacitance measured at pin

2 (VI).

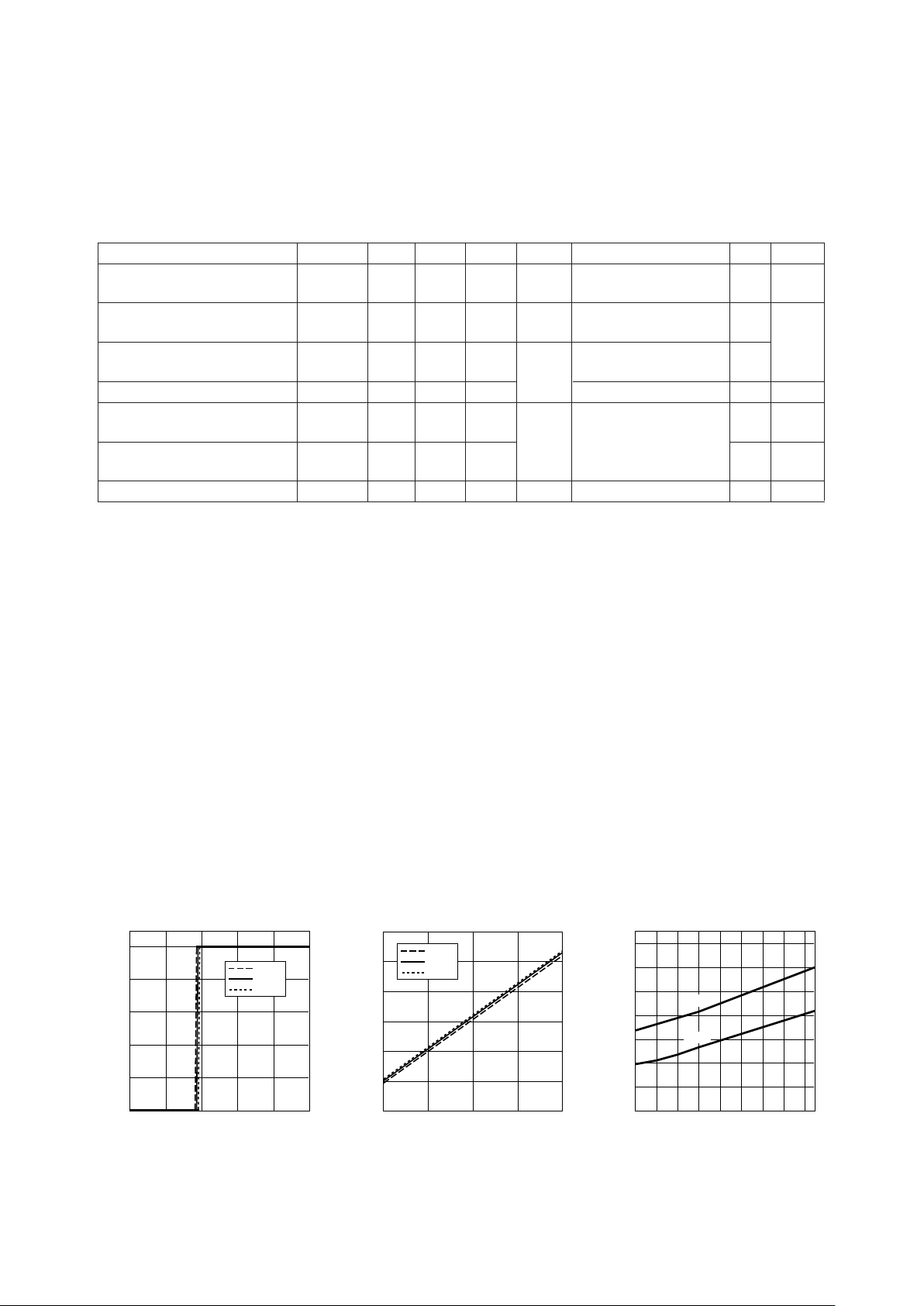

Figure 1. Typical Output Voltage vs.

Input Voltage.

Figure 2. Typical Input Voltage

Switching Threshold vs. Input Supply

Voltage.

Figure 3. Typical Propagation Delays

vs. Temperature.

V

O

(V)

0

0

VI (V)

5

4

1

4123

5

3

2

0 °C

25 °C

85 °C

V

ITH

(V)

4.5

1.6

V

DD1

(V)

5.5

2.1

1.7

5.254.75 5

2.2

2.0

1.8

1.9

0 °C

25 °C

85 °C

T

PLH

, T

PHL

(ns)

0

15

TA (C)

80

27

17

6020 30

29

25

19

21

10 40 50 70

23

T

PLH

T

PHL

Loading...

Loading...