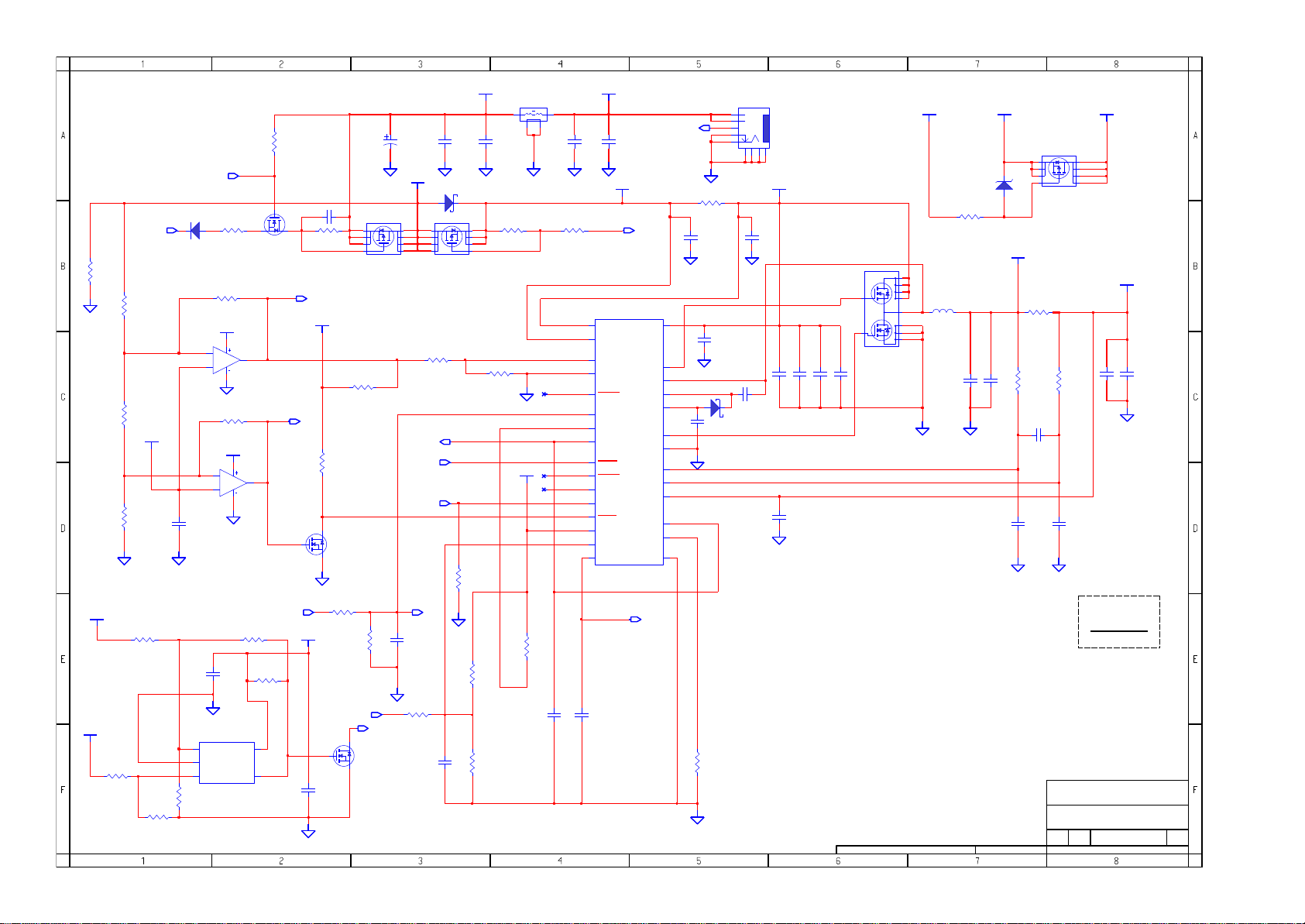

Page 1

S-CLASS

Prince/Pearl

SI2 Build

2008/02/14

DATE

DRAWER

DESIGN

CHECK

RESPONSIBLE

3SIZE =

XXXX-XXXXXX-XXFILE NAME :

REVCHANGE NO.

XXXXXXXXXXXXP/N

POWERDATEEE

DATE

TITLE

VER : REVDOC. NUMBERCODESIZE

A3

INVENTEC

Prince/Pearl

SI 1 X02

CS

SHEET

OF

531

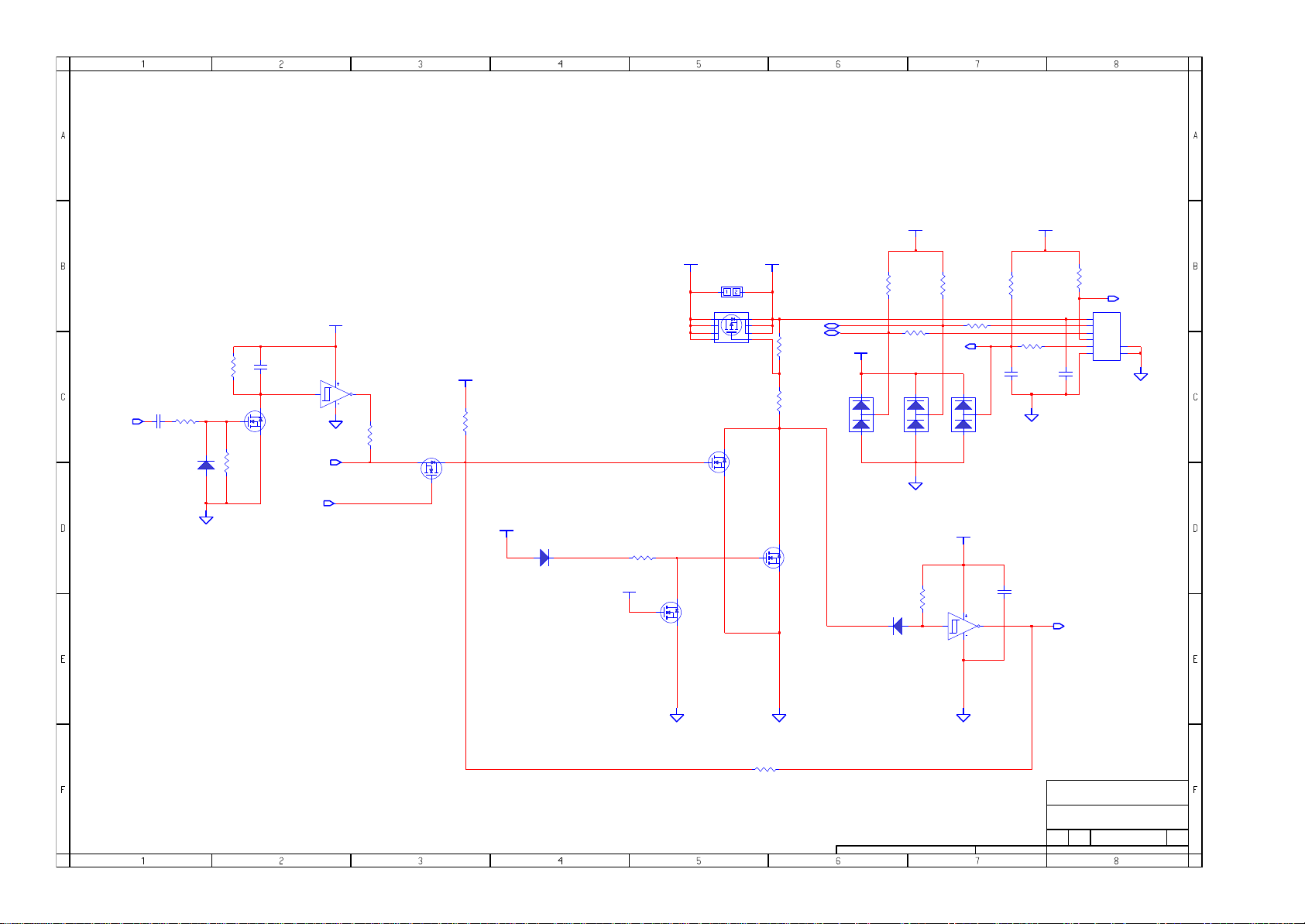

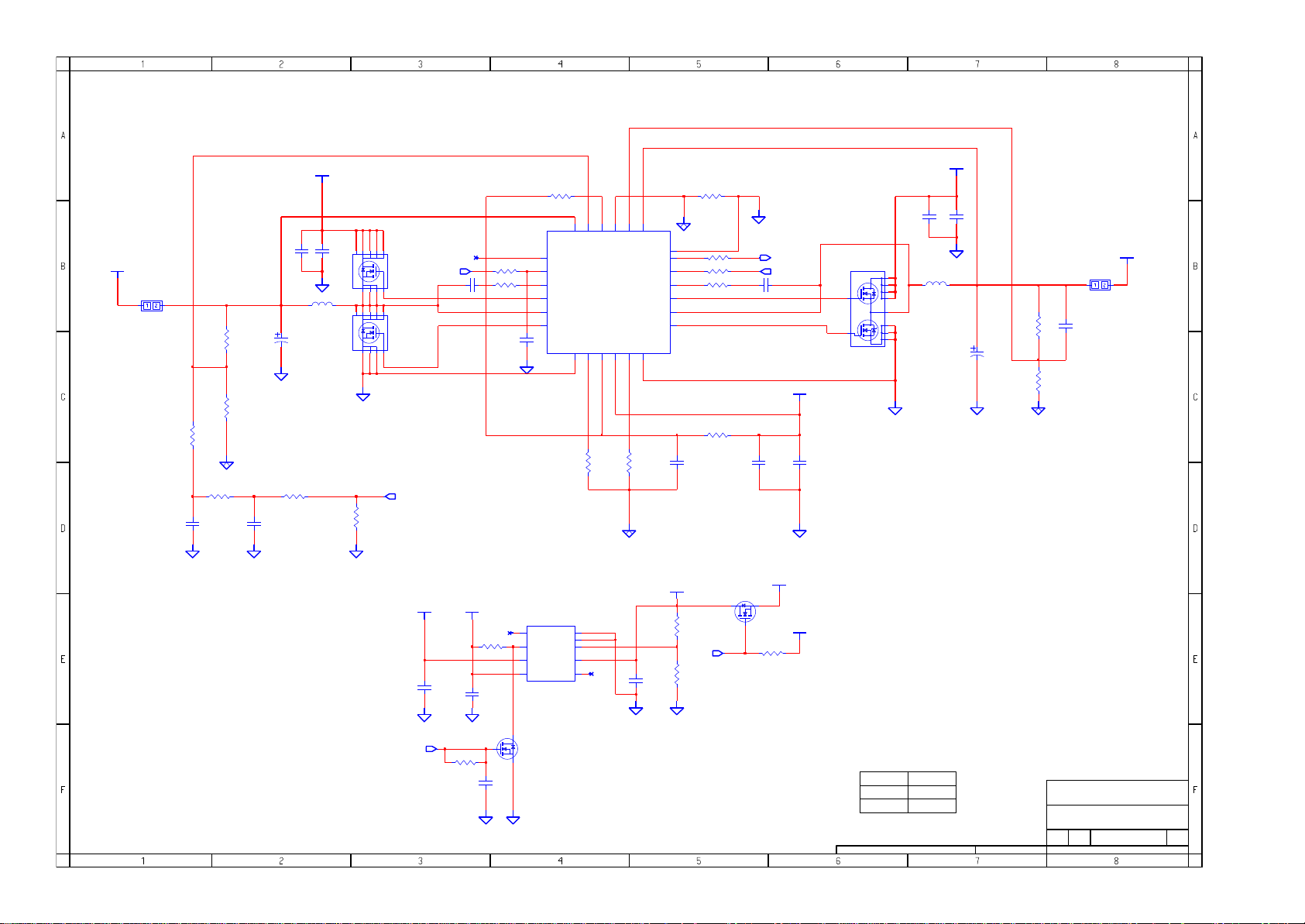

Page 2

TABLE OF CONTENTS

PAGE

5- DC& BATTERY CHARGER

6- SELECT & BATTERY CONN

7- +V5A,+V3A & +V2.5S

8- OCP

9- +VCC_NB & +V1.2A

10- +VCC_CORE

11- POWER

12- DDR2 POWER

13- POWER(SLEEP)

14- POWER(SEQUENCE)

PAGE

15- CLOCK_GENERATOR

16- CPU-1

17- CPU-2

18- CPU-3

19- CPU-4

20- THERMAL&FAN CONTROLLER

21- RS780-1

22- RS780-2

23- RS780-3

24- RS780-4

25- DDR2-DIMM0

26- DDR2-DIMM1

27- DDR2-DAMPING

28- CRT

29- LCD CONN

30- SB700-1

31- SB700-2

32- SB700-3

33- SB700-4

34- KBC

PAGE

35- KB & TP CONN

36- SPI & ACCELEROMETER

37- HDD & ODD CONN

38- USB CONN

39- USB WEBCAM CONN

40- FLASH MEDIA CARD

41- AZALIA CODEC

42- Earphone & MIC JACK

43- AUDIO AMP & HP JACK

44- MDC CNTR

45- NIC 10/100- CONTROLLER

46- NIC 10/100- RJ45 CONN

47- MINICARD & BT CONN

48- NEW CARD

49- UWB CONN

50- BUTTON & LED

51- SCREW

52- 15" ODD Extend Board

53- SWITCH Board

INVENTEC

TITLE

Prince/Pearl

Table OF Content

CS

SHEETCHANGE by

DOC. NUMBER

253

21-Nov-2007Andy Liu

A3

REVSIZE CODE

X02SI 1

OF

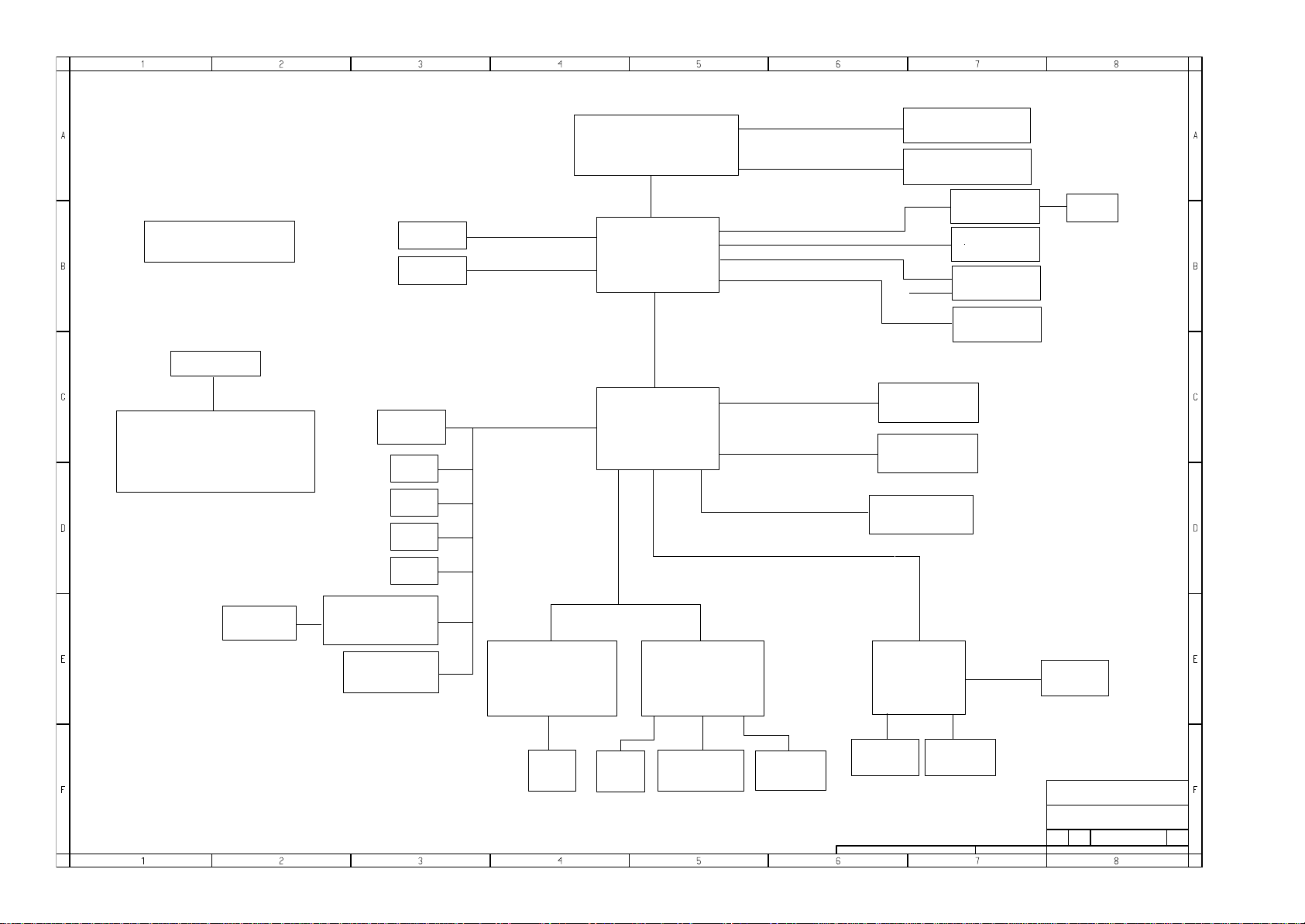

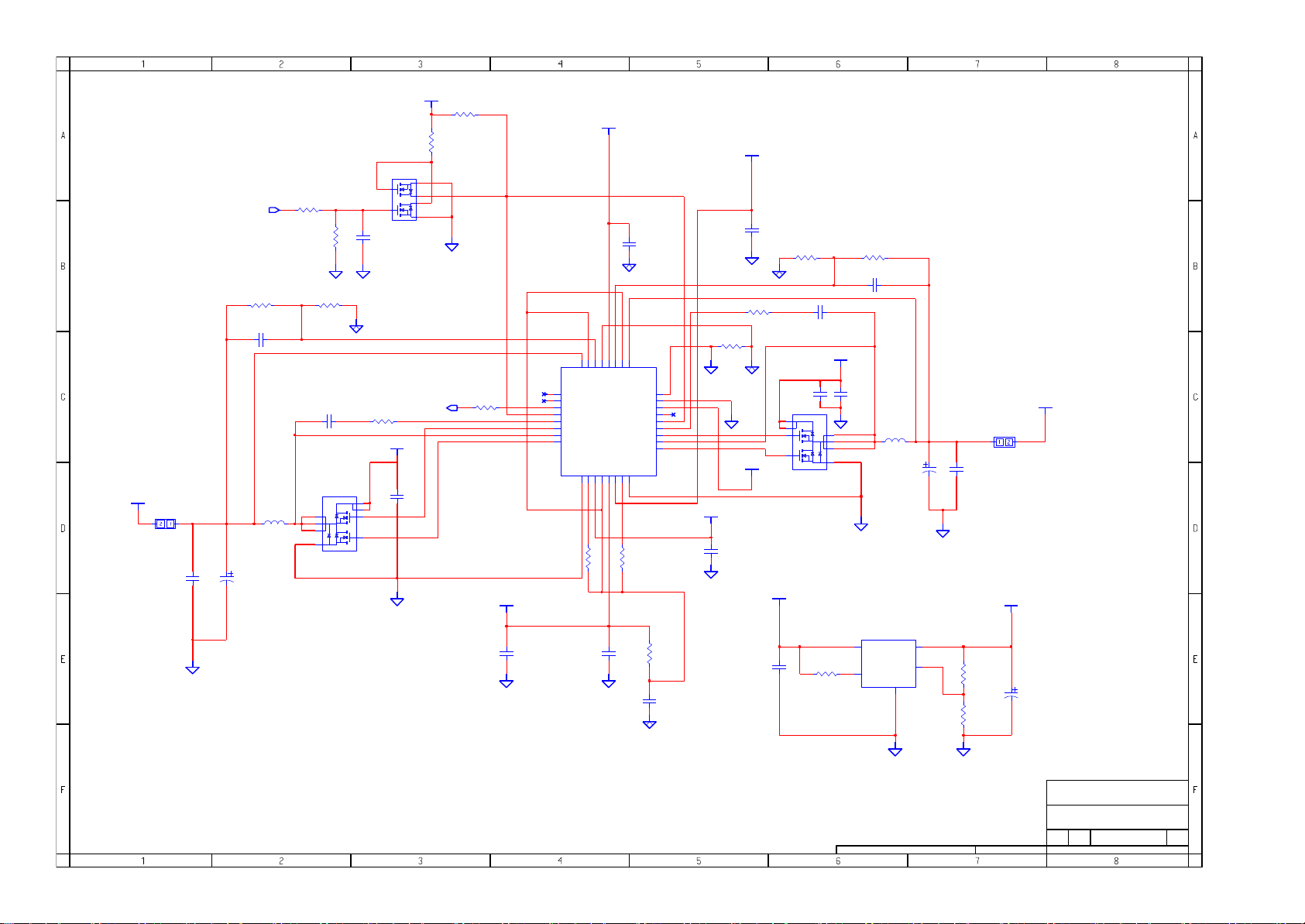

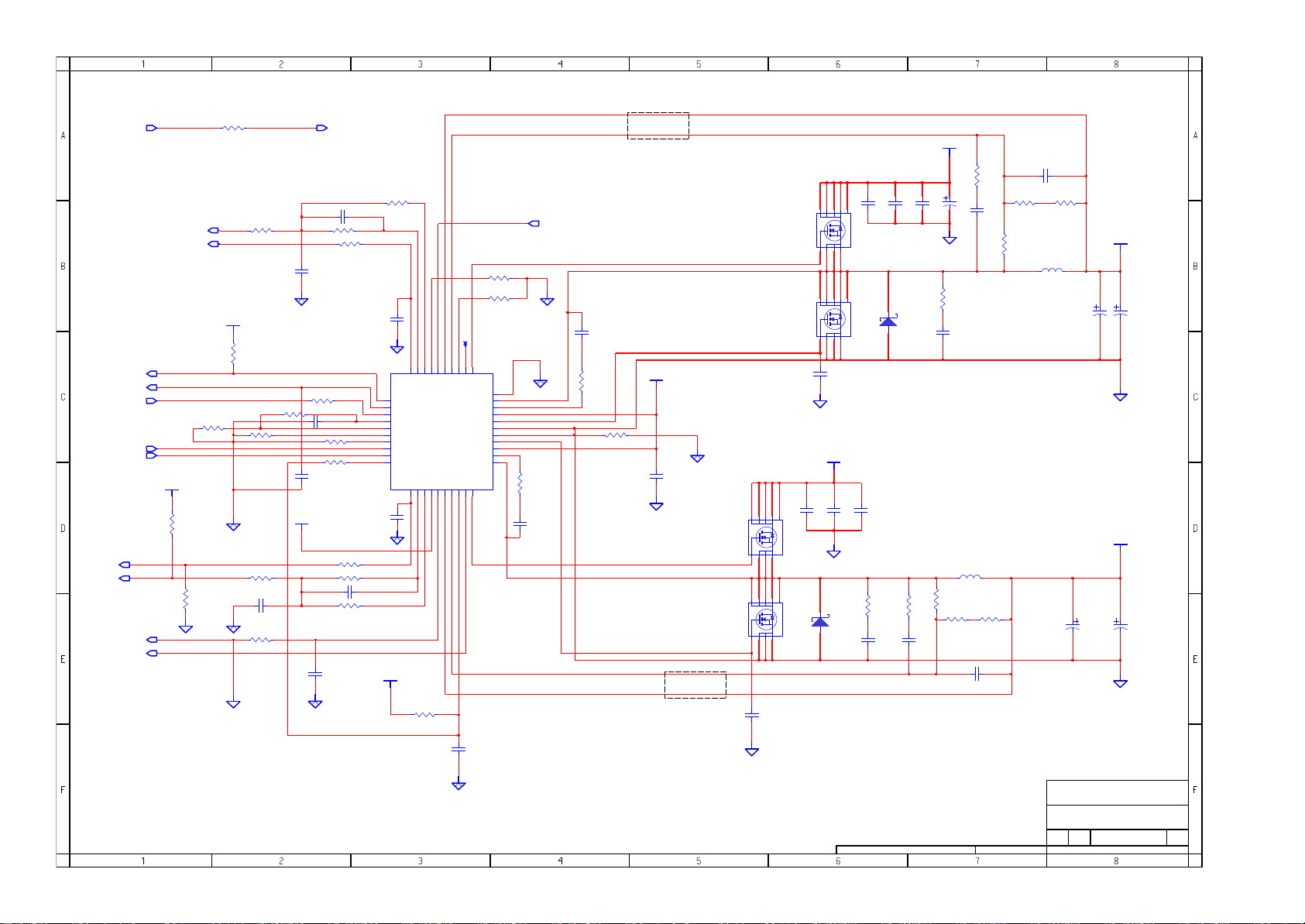

Page 3

AMD Griffin

Turion/Sempron

SIG2 Socket/638pin

DDR2

DDR2

DDR II _SODIMM0

DDR II _SODIMM1

Clock Generator

ICS9LPR476KLFT

MAIN BATT

System Charger &

DC/DC System power

4 in 1

Slot

USB11

Bluetooth

USB0

Conn

USB2

Conn

USB4

Conn

USB5

Conn

USB3

Flash media

ALCOR AU6371

LCM

CRT

LVDS

CRT

USB2.0

Azalia interface

Hyper Transport

AMD

RS780

(FCBGA)

A-LINK

AMD

SB700

(FCBGA)

PCIE0

PCIE2

PCIE3

PCIE4

SATA1

SATA0

SM Bus

LPC interface

USB1

FIXED ODD

HDD

Accelerometer

NIC 10/100

Marvell 8039

MINI CARD

CONN

(WLAN)

NEW CARD

CONN

UWB

RJ45

USB7

CAMERA

MDC V1.5/V3

CONNECTOR

RJ11

Mic IN

AUDIO CODEC

ADI_1984A

Headphone

Speaker

KBC

SMSC KBC1091

SPI

SYSTEM

BIOS

Keyboard TouchPad

INVENTEC

TITLE

Prince/Pearl

Block Diagram

SIZE CODE

A3

CHANGE by SHEET

21-Nov-2007Andy Liu

CS

DOC. NUMBER

OF

353

REV

X02SI 1

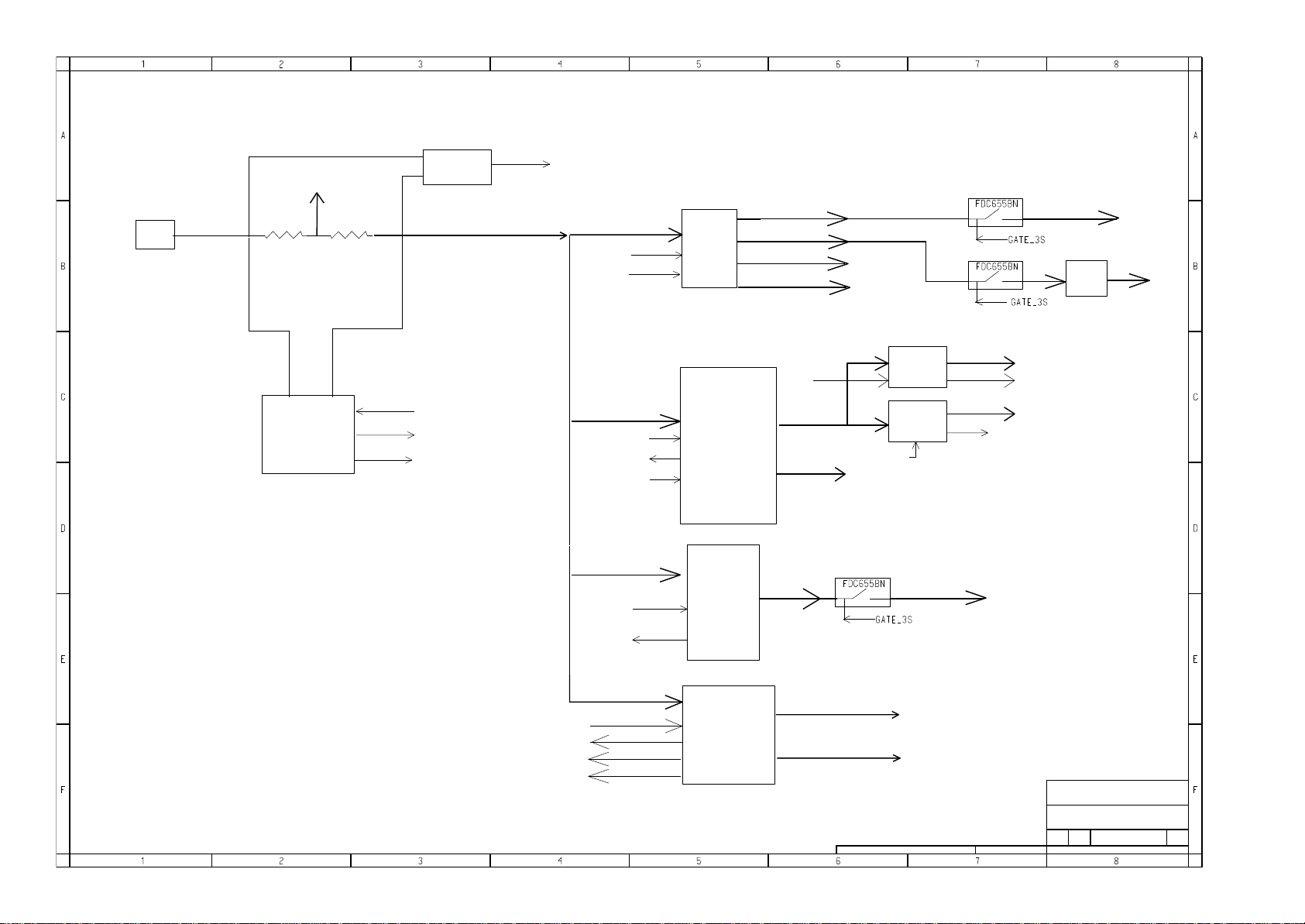

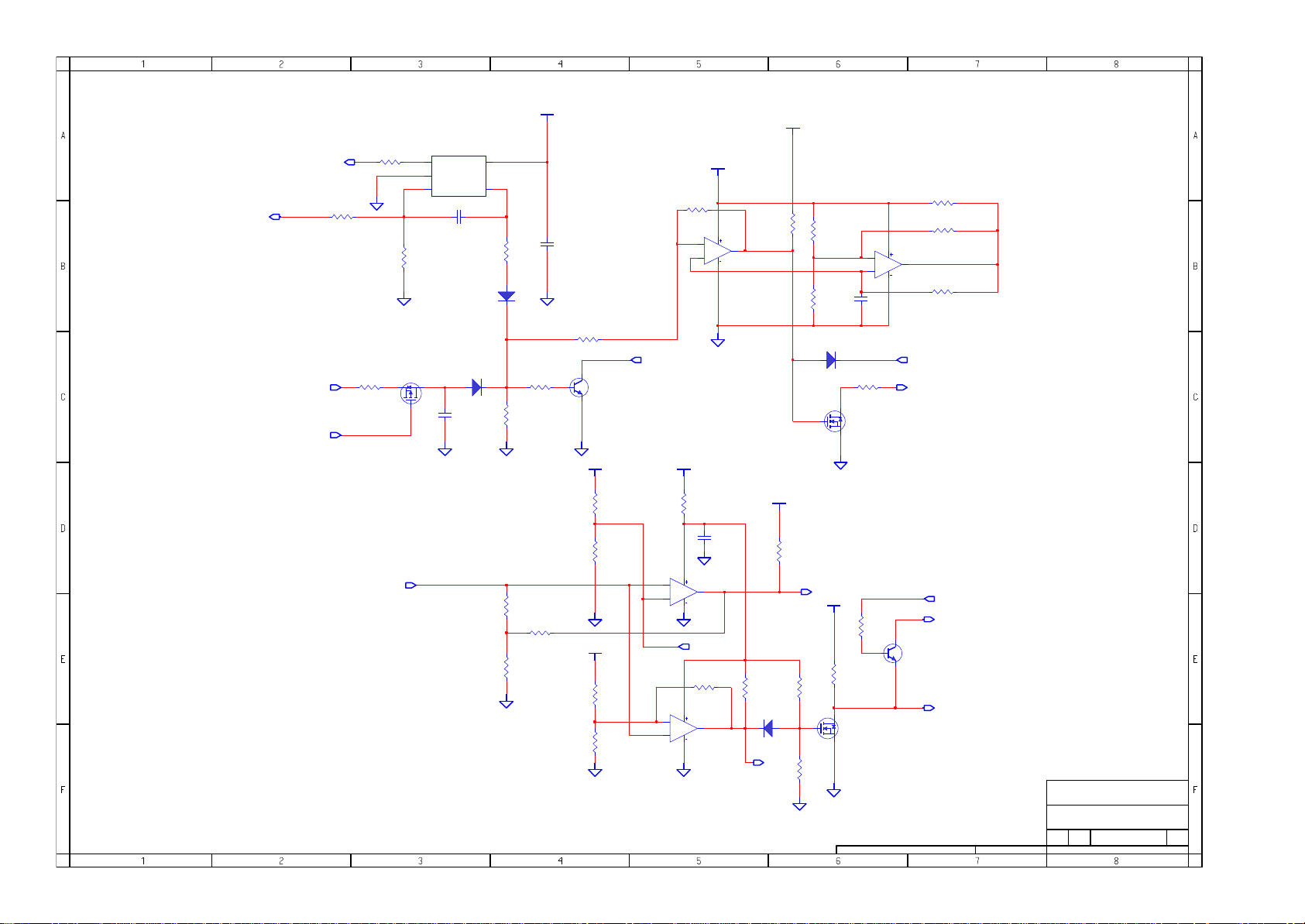

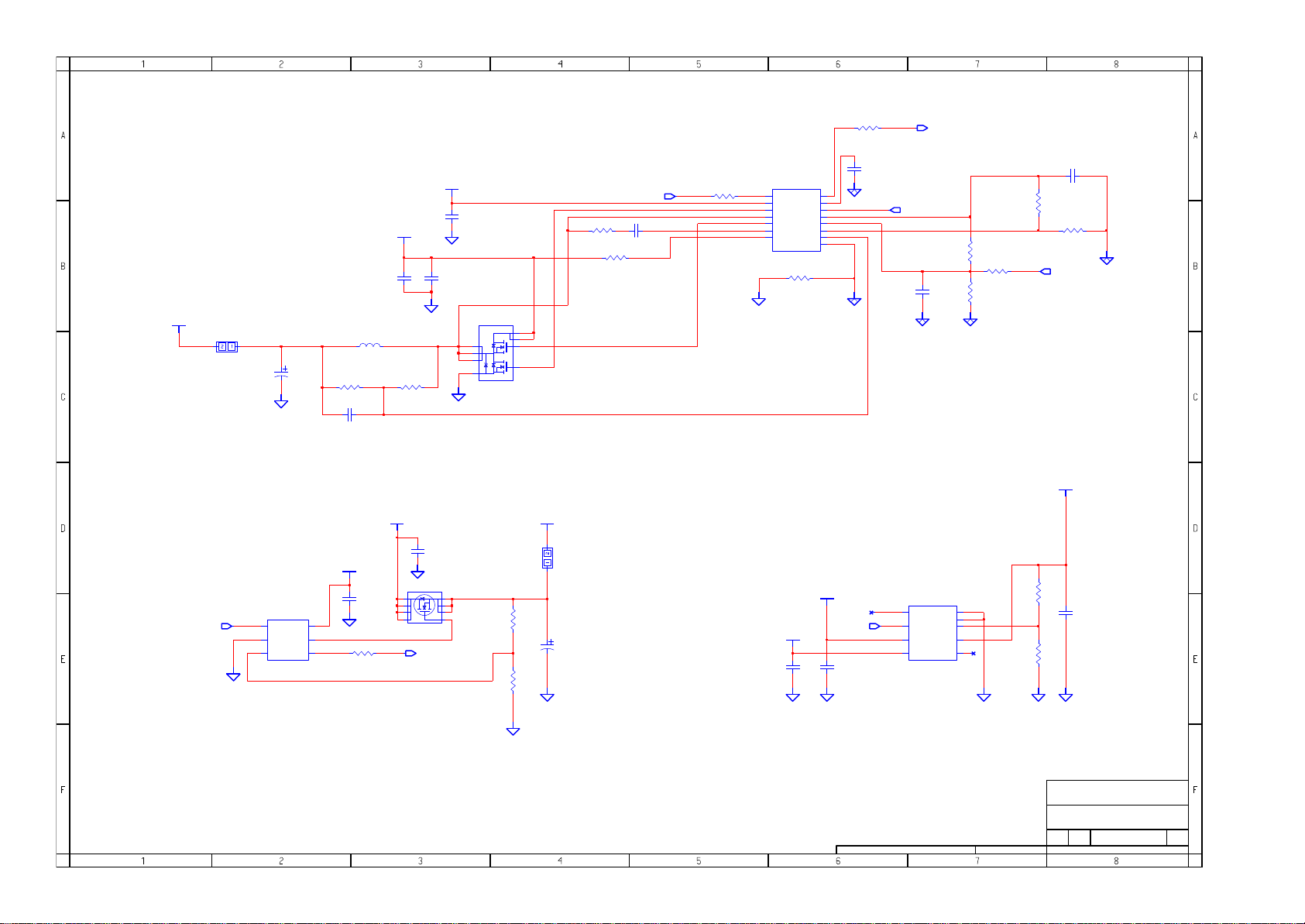

Page 4

Adapter

+VBAT

OCP

OCP_OC#

+VBATR

KBC_PW_ON

ADP_PRES

5/3.3V

(TPS51120)

+V5A

+V3A

+V5AL

+V3AL

+V3S

+V5S

GMT

(G916)

+V2.5S

Charger

(BQ24740)

CHGCTRL_3

ADP_PRES

AC_AND_CHG

POWER_GOOD_3

POWER_GOOD_3

PWR_GOOD_3

NB_SKIP

NBV_BUF

SYS_PWRGD

SYS_PWRGD

SLP_S5#_5R

V18_GOOD

+VCC_NB&+V1.2

(TPS51124)

DDR2 POWER

(TPS51117)

VCC_CORE

(MAX17009)

SLP_S3#_3R

+V1.8

+V1.8

+V1.25S

CHANGE by

LR

(G2997)

LR

(APL5913)

+VCCP

+V1.8S

+VCC_CORE

+VCC_CORE_VDD1

+V0.9S

V1.5S_PG

21-Nov-2007Andy Liu

M_VREF

+V1.5S

INVENTEC

TITLE

Prince/Pearl

SIZE

CODE

A3

CS

DOC. NUMBER

SHEET

REV

X02SI 1

OF

453

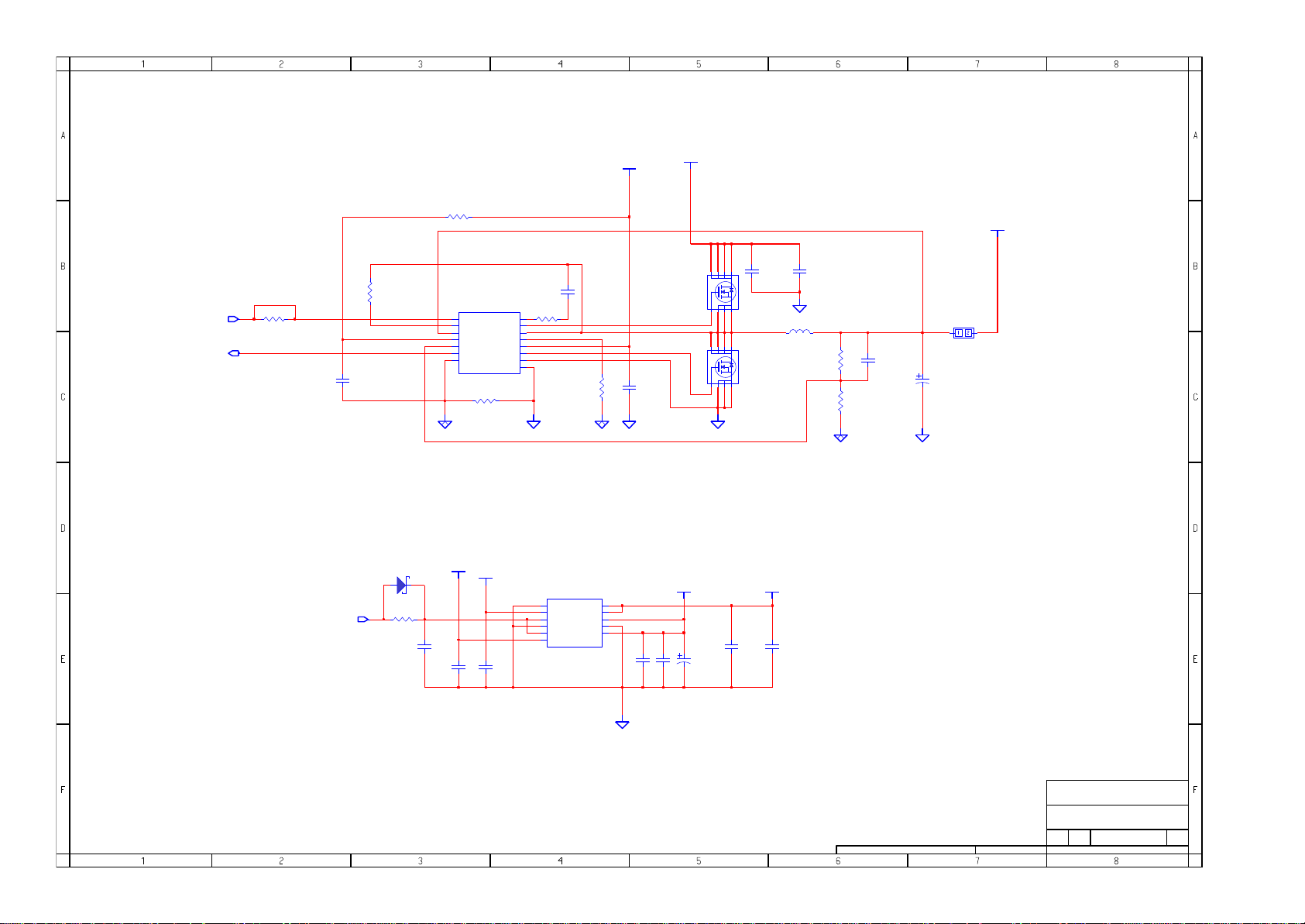

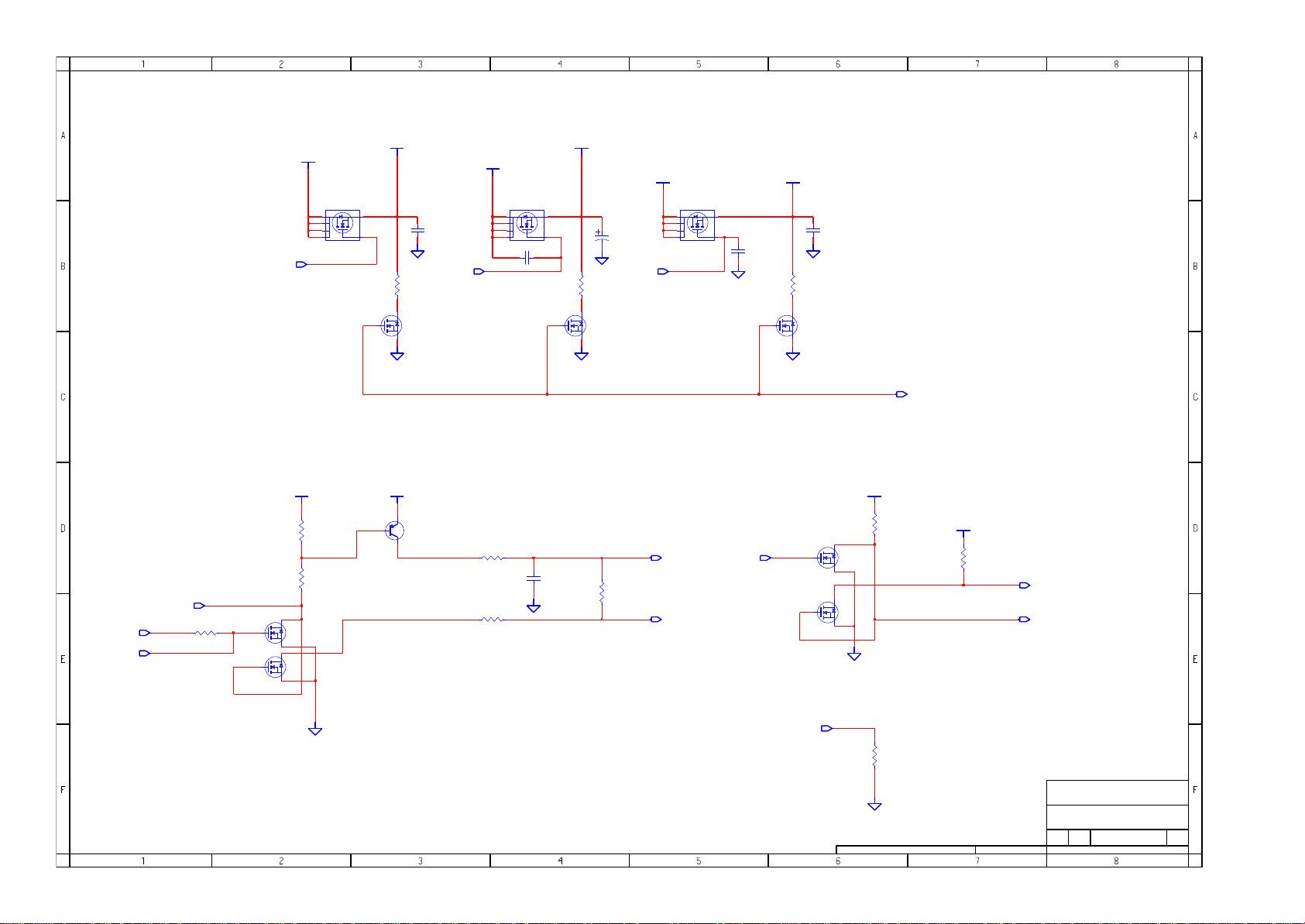

Page 5

1

R123

15K_5%

2

+VADPBL

+VBDC

5-,6-

100K_1%

1

R78

14.3K_1%

2

5-

R1255

12

100K_1%

ADP_EN#

12

R74

1

R76

8.25K_1%

2

2VREF

R1249

1

100K_1%

12

24K_1%

BATCAL#

8-

D1006

1SS355W

7-,14-

C70

1

2

0.022uF_16v

2

1

TI_LMV321IDBVR_SOT23_5P

R1247

2

23.7K_1%

R1256

21

3

2

1

2

1

1IN+

2

GND

3

1IN-

8-

R1275

12

100K_5%

R75

12

270K_5%

+V5AL

5-,7-

8

+

1

OUT

-

AS393MTR_E1

U5-A

4

R77

1M_5%

12

+V5AL

5-,7-

8

5

+

OUT

6

-

AS393MTR_E1

U5-B

4

R1248

12

1M_5%

C1226

0.1uF_16v

U1018

Vcc+

OUT

1

2

1

G

S

2

Q1022

2N7002W

6-,32-,34-,45-

7

CHGCTRL_3

R1257

12

100K_5%

5

4

R1278

220K_5%

D

3

6-

2N7002W

33uF_25v_OPEN

C1249

0.1uF_25v

12

12

R1277

220K_5%

ADP_PRES

+V3AL

6-,7-,8-,30-,32-,34-,35-,36-,50-

AC_AND_CHG

1

R80

10K_5%

2

Q20

3

D

1

G

S

2

12

6-,34-

280K_1%

+V5AL

5-,7-

Q1020

1

2N7002W

C1221

1

2

0.1uF_10v

R1269

200K_1%

VCTRL_3

G

C1248

1

2

3

AM4825P_AP

22K_5%

R1276

R1266

5-

3

D

S

2

1

2

Q1031

S

G

12

1

2

34-

ADPDRV#

+VADPBL

5-

8

D

7

6

54

BQREF

SLP_S3#_3R

7-,9-,13-,14-,31-,32-,33-,45-,50-

CELLS

8-

I_SET

C1242

1

1uF_6.3v

2

R1271

12

422K_1%

C1243

1uF_6.3v

+VADP

1

C1264

2

10pF_50v

D1011

SSM14_1A40V

1

S

2

3

G

8-

8-,13-,32-,34-,43-,45-,48-

34-

1

R1260

100K_5%

2

1

R1267

453K_1%

2

1

R1270

1

1M_1%

2

2

8-

C1263

R1272

12

300K_5%

3.3A_150mil

1

2

21

Q1025

8

D

7

6

54

AM4825P_AP

R1273

12

47K_5%

L1041

NFM60R30T222

12

0.1uF_25v

R1289

12

47K_5%

+V3A

1uF_6.3v

4

12

R1274

20K_5%

C1247

+VADPTR

C1262

1

0.1uF_25v

2

5A

LIMITsignal

+VADPTR

3

C1261

1

2

10pF_50v

+VBAT +VBATR

5-

R1290

1

2

5-

1

2

4.7K_5%

U1021

2

ACN

3

ACP

5

ACDET

9

AGND

13

EXTPWR

16

SRSET

6

ACSET

10

VREF

8

IADSLP

21

DPMDET

4

LPMD

20

CELLS

1

CHGEN

11

VDAC

12

VADJ

15

IADAPT

TI_BQ24740_QFN_28P

1

C1244

2

100pF_50v

ADPDRV#

ISYNSET

PowerPad

8-

PVCC

HIDRV

REGN

LODRV

PGND

LPREF

ICS

BTST

SRP

SRN

BAT

PH

28

26

25

27

24

C1236

1uF_10v

23

22

19

18

17

7

14

29

R1268

33K_5%

1

2

DC JACK

8-

R10

12

0.01_1%_1W

C1246

1uF_25v

C1256

1

2

1uF_25v

3

1

D1005

1

CHENMKO_BAT54_3P

2

1

2

JACK1003

1

2

3

4

5

6789

FOX_JPD113D_LBA21_7F_9P

C1245

1

2

1uF_25v

C1266

1

2

C1237

0.1uF_25v

12

0.1uF_16v

1

2

7-,9-,10-,11-,12-,13-,29-,34-

C1268

C1267

1

1

2

2

C1241

0.1uF_25v

Q1032

2

3

Q1

4

9

1

10

Q2

5

6

8

FAIR_FDMS9620S_MLP_8P

C1269

1

2

4.7uF_25v

4.7uF_25v

4.7uF_25v

CHANGE by

7

CELLSEL#=0,Vcharger=12.6V

CELLSEL#=1,Vcharger=16.8V

Andy Liu 29-Jan-2008

5-

5-

R52

12

3K_5%

L1042

12

PCMB0603T_8R2MS

C1259

1

2

4.7uF_25v

4.7uF_25v

Icharger=3A

C1270

+VBDC+VBAT+VADPBL

5-,6-

Q5

1

8

S

D

7

2

6

3

D3

1

RLZ18C2

4

G

AM4825P_AP

5

+VBDCR

+VBDC

C1260

1

2

4.7uF_25v

5-,6-

1

2

C1271

4.7uF_25v

R1308

0.01_1%_1W

12

1

R1259

0_5%

2

C1239

0.033uF_16v

2

1

1

R1261

0_5%

2

1

2

Kevin sense

C1238

1uF_25v

1

2

C1240

1uF_25v

1

2

Note:

high power trace

INVENTEC

TITLE

Prince/Pearl

DC & BATTERY CHARGER

SIZE CODE

A3

CS

SHEET

DOC. NUMBER

SI 1 X02

REV

OF

535

Page 6

CHGCTRL_3

C1257

5-,34-

12

1000pF_50v

R1291

12

1K_5%

D1008

1SS355W

R1293

470K_5%

1

2

1

2

1

G

1

R1292

470K_5%

2

1

C1258

0.047uF_16v

2

3

D

2N7002W

S

2

Q1026

AC_AND_CHG

ADP_PRES

+V3AL

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

5

U1023

2

74HC1G14GV

3

5-

5-,32-,34-,45-

1

R14

2

R12

12

1K_5%

1

C15

470pF_50v

2

C3010

1

2

0.1uF_10v_OPEN

+V3AL

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

1

2

SYN_200046MR006G100ZU_6P

1

2

C14

0.1uF_25v

34-

BATCON

R13

10K_5%

1

1

2

2

3

3

4

4

5

5

6

6

CN1016

6CELLSEL#

7

7

8

8

+V3AL

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

+VBDC +VBATA

5-

PAD3005

POWERPAD_2_0610

Q1051

8

D

7

6

5

G

AM4825P_AP_OPEN

+V3AL

Q1027

S

3

D

G

1

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

1

R1295

220K_5%

2

+VBATA

6-

CHENKO_LL4148_2P_OPEN

21

D2014

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

SSM3K7002F_OPEN

R2018

12

0_5%_OPEN

+V3AL

Q1054

G

1

SSM3K7002F_OPEN

3

D

S

2

Q1053

3

D

1

G

S

2

SSM3K7002F_OPEN

4

1

R1294

10K_5%

2

2

2N7002W

6-

1

S

2

3

4

SDA_MAIN

SCL_MAIN

1

R2015

470K_5%_OPEN

2

1

R2016

4.7K_5%_OPEN

2

3434-

1

R15

10K_5%

2

+V3AL

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

1

3

D5

DIODE_BAV99

2

R16

12

100_5%

1

3

D6

DIODE_BAV99

2

1

R17

10K_5%

2

R18

12

100_5%

THM_MAIN#

1

DIODE_BAV99

2

100K_5%

34-

3

D4

+V3AL

1

2

2

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

5

U1026

4

74HC1G14GV_OPEN

3

Q1052

1

3

D

G

S

2

R2017

220K_5%_OPEN

21

D2013

CHENKO_LL4148_2P_OPEN

R1750

12

0_5%

INVENTEC

TITLE

Prince/Pearl

SELECT & BATTERY CONN

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

Andy Liu 29-Jan-2008

A3

SI 1 X02

CS

536

Page 7

7A

+V3A

PAD1002

POWERPAD_2_0610

5-,9-,13-,14-,31-,32-,33-,45-,50-

C1111

1

1uF_6.3v

2

KBC_PWR_ON

R461

17.4K_1%

C463

12

OPEN

PCMB104E_4R7MS

1

C1124

330uF_4v

R2012

12

34-

30K_5%

R2008

200K_5%

12

L1016

12

R463

7.32K_1%

C462

12

0.1uF_16v

5

S1_D2

6

7

4

S2

FDS6900AS

1

2

12

51120GND

Q65

1

2

1

D1

2

G1

8

3

G2

Q1041

2

G1

5

G2

2N7002DW

C3004

0.1uF_16v

R458

12

0_5%

+VBATR

5-,7-,9-,10-,11-,12-,13-,29-,34-

C410

1

2

4.7uF_25v

+V5AL

1

S1

6

D1

3

D2

4

S2

RSMRST#

5-,7-

12

100K_5%

1

R2011

100K_5%

2

R2010

12

32-,34-

R2007

33_5%

+V5AL

1

2

5-,7-

C458

10uF_6.3v

8

VO2

9

TI_TPS51120_QFN_32P

EN5

10

EN3

11

PGOOD2

12

EN2

13

VBST2

14

DRVH2

15

LL2

16

DRVL2

PGND2

U34

17

R456

11.3K_1%

2VREF

5-,7-,14-

7

6

GND

VFB2

COMP2

V5FILT

CS2

VREG319VREG5

18

1

2

1

2

51120GND

5

4

VFB1

VREF2

VIN

20

21

C461

0.1uF_10v

3

22

2

COMP1

CS1

1

2

2

23

C511

1000pF_50v1

1

VO1

SKIPSEL

TONSEL

PGOOD1

EN1

VBST1

DRVH1

LL1

DRVL1

PGND1

24

R457

11.3K_1%

1

2

51120GND

33

32

31

30

29

28

27

26

25

1

R500

5.1_5%

2

C509

1uF_6.3v

+VBATR

C460

4.7uF_25v

R502

12

0_5%

51120GND

+V3AL

5-,6-,8-,30-,32-,34-,35-,36-,50-

1

C459

2

10uF_6.3v

5-,7-,9-,10-,11-,12-,13-,29-,34-

1

2

R501

12

0_5%

51120GND

R462

12

7.32K_1%

C510

12

0.1uF_16v

R460

12

30K_1%

C464

12

OPEN

+VBATR

5-,7-,9-,10-,11-,12-,13-,29-,34-

C506

1

1

C507

4.7uF_25v

2

2

4.7uF_25v

Q67

1

D1

2

5

S1_D2

G1

8

6

7

3

G2

4

2VREF

5-,7-,14-

C413

10uF_6.3v

+V3S

1

2

S2

FDS6900AS

8-,10-,13-,14-,15-,20-,23-,24-,25-,26-,28-,29-,30-,31-,32-,33-,34-,36-,40-,41-,44-,45-,47-,48-,49-,50-

R420

12

10K_5%

L1006

12

CYNTEC_PCMC063_4R7

C1063

220uF_6.3v

U29

GMT_G916T1Uf_SOT23_5_5P

1

IN

OUT

SHDN#

SET

GND

2

3

5A

+V5A

9-,10-,11-,12-,13-,38-

PAD1001

1

2

1uF_6.3v

C1064

1

2

1

2

R418

10K_1%

R419

10K_1%

POWERPAD_2_0610

200mA

+V2.5S

18-

12

22uF_10v

C412

1

2

5

4

CHANGE by

Andy Liu 21-Nov-2007

INVENTEC

TITLE

Prince/Pearl

+V5A,+V3A&+V2.5S

SIZE

A3

DOC. NUMBER

CODE

SI 1 X02

CS

SHEET

REV

OF

537

Page 8

BQREF

5-

LIMITsignal

VBIAS

ICS

5-

12

R237

73.2K_1%

R177

12

5-,8-

100_5%

8-

R238

12

10K_5%

BSS84_3P

1

2

3

TI_LMV321IDBVR_SOT23_5P

1

R186

178K_1%

2

Q30

3

2

D

S

G

1

U13

1IN+

GND

1IN-

1

2

Vcc+

OUT

12

C185

0.22uF_10v

1SS355W 2

D23

2

1SS355W

C137

3900pF_16v

+V5S

8-,13-,14-,20-,28-,31-,32-,35-,37-,39-,42-,43-,47-

7-,10-,13-,14-,15-,20-,23-,24-,25-,26-,28-,29-,30-,31-,32-,33-,34-,36-,40-,41-,44-,45-,47-,48-,49-,50-

5

4

1

1

R184

2K_1%

2

C138

0.1uF_10v

2

1

D19

R172

12

3.9K_5%

1

12

100K_5%

1

R175

3.9K_1%

2

R174

B

1

3

C

Q29

E

D_MMST3904

2

5-

I_SET

+V5S

8-,13-,14-,20-,28-,31-,32-,35-,37-,39-,42-,43-,47-

R173

12

330K_5%

8

U8-A

3

+

1

OUT

2

-

AS393MTR_E1

4

R145

10K_5%

+V3S

1

1

2

2

1

2

1SS355W D15

2N7002W

R146

133K_1%

R179

80.6K_1%

21

Q24

1

G

1

2

12

3

D

S

2

5

+

6

-

C133

0.027uF_10v

9-,10-,11-,14-

R185

0_5%

8

OUT

AS393MTR_E1

4

18-,20-

10K_5%

2

U8-B

7

12

604K_1%

PWR_GOOD_3

PROCHOT#

R144

2

R143

100K_5%

R176

1

1

LIMITsignal

+VADP +VADP

5-,8-

2

R1283

22.6K_1%

1

1

R1281

10K_1%

2

5-,8-

1

R1301

182K_1%

2

12

1M_5%

1

R1300

10K_1%

2

R1299

+VADP

5-,8-

1

R1287

29.4K_1%

2

1

2

R1286

10K_1%

3

+

2

-

5

+

6

-

5-,8-

1

R2006

1_5%

2

8

OUT

4

8-

VBIAS

1

8

OUT

4

C1265

1

2

1uF_25v

U1024-A

1

AS393MTR_E1

R1303

2

1M_5%

U1024-B

7

AS393MTR_E1

+V3AL

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

1

R1304

47K_5%

2

R1288

220K_5%

D1010

21

1SS355W

5-

ADP_EN#

5-,6-,7-,8-,30-,32-,34-,35-,36-,50-

1

R1302

10K_5%

2

ADP_PWRID

34-

+V3AL

1

R1305

1

10K_5%

2

2

3

D

G

1

Q1029

S

2

1

R1306

220K_5%

2

5-,13-,32-,34-,43-,45-,48-

1

R1307

100K_5%

2

1

2N7002W

3

C

B

E

2

SLP_S3#_3R

5-

Q1030

D_MMST3904

34-

BATCAL#

ADP_EN

INVENTEC

TITLE

Prince/Pearl

OCP

Andy Liu 22-Jan-2008

SIZE CODE DOC. NUMBER REV

A3

SI 1 X02

CS

SHEETCHANGE by OF

538

Page 9

+VCC_NB

24-

PAD1005

POWERPAD_2_0610

1

R264

309K_1%

2

16.2K_1%

1

C219

2

1500pF_50v

1

R262

10K_1%

2

1

R265

22.6K_1%

2

51124GND

R268

12

C182

1

4.7uF_25v

2

12

PCMB104E_2R2MS

1

C1203

2

220uF_2v_9mR_Panasonic

R270

12

5.1K_1%

1

C220

2

4700pF_25v

+VBATR

5-,7-,9-,10-,11-,12-,13-,29-,34-

C183

1

4.7uF_25v

2

L1028

9

9

8D765

S

8D765

S

2

1

1

123

R269

23

23-

10K_5%

G

FDMS8690

4

G

4

Q37

Q36

FDMS8660S

PWR_GOOD_3

STRP_DATA

8-,9-,10-,11-,14-

C181

12

0.1uF_16v

R2005

10K_5%

2

1

R226

12

0_5%

1

2

R256

12

0_5%_OPEN

7

PGOOD2

8

EN2

9

VBST2

10

DRVH2

11

LL2

12

DRVL2

C3002

1000pF_50v

6

VO2

PGND2

13

VFB2

TRIP2

1

2

5.1K_1%

5

14

R224

4

TONSEL

U19

V5FILT

15

2

3

1

VO1

GND

VFB1

GND

PGOOD1

EN1

VBST1

DRVH1

LL1

DRVL1

PGND1

TRIP1

V5IN

18

17

16

TI_TPS51124RGER_QFN_24P

1

R257

2

15.4K_1%

51124GND

51124GND

25

24

23

22

21

20

19

C216

1

2

1uF_6.3v

R266

0_5%

R260

R259

R258

12

12

10_5%

R255

+VBATR

5-,7-,9-,10-,11-,12-,13-,29-,34-

12

C297

4.7uF_25v12

0_5%

0_5%

0_5%

9-

V1.2S_PG

8-,9-,10-,11-,14-

PWR_GOOD_3

C217

12

0.1uF_16v

Q47

2

3

Q1

4

1

9

10

Q2

5

6

8

FAIR_FDMS9620S_MLP_8P

7

220uF_2v_9mR_Panasonic

12

12

+V5A

7-,9-,10-,11-,12-,13-,38-

C215

4.7uF_6.3v

1

2

C214

0.1uF_10v

1

2

C298

1

2

4.7uF_25v

L1021

12

PCMB104E_2R2MS

C1125

+V1.2S

9-,11-,15-,18-,19-,24-,30-,31-

PAD1003

POWERPAD_2_0610

1

C218

1

R261

2

OPEN

2

6.49K_1%

1

2

51124GND

1

R263

10K_1%

2

5-,7-,13-,14-,31-,32-,33-,45-,50-

V1.2S_PG

1000pF_50v_OPEN

1

2

9-

C371

10uF_6.3v

+V5A+V3A

7-,9-,10-,11-,12-,13-,38-

1

C370

2

0.1uF_10v

R2009

2

1

10K_5%_OPEN

C3003

U25

19

PGOOD

TML-PAD

R374

12

10K_5%

RICHTEK_RT9018A25PSP_SOP8_8P

3

D

G

1

S

2

1

2

GND

ADJ

EN

36

VIN

VOUT

4

VDD

NC

Q55

2N7002W

+V1.2A

31-

1

R371

C368

10uF_6.3v

5.1K_1%

2

V1.2S_PG

1

R372

2

10K_1%

9-

8

72

5

1

2

+V1.2S

9-,11-,15-,18-,19-,24-,30-,31-

Q54

3

2

D

S

G

FDV305N

1

R373

10K_5%

+V5A

7-,9-,10-,11-,12-,13-,38-

12

STRP_DATA

CHANGE by

+VCC_NB

0

1.1

1

1.0

Andy Liu 30-Nov-2007

INVENTEC

TITLE

Prince/Pearl

+VCC_NB & +V1.2A

CODE

SIZE

A3

DOC. NUMBER

SI 1 X02

CS

SHEET

REV

OF

539

Page 10

PWR_GOOD_3

VDD1_FB#

VDD1_FB

SYS_PWRGD

NBV_BUF

CPU_SVC_R

CPU_SVD_R

18-

18-

NB_GNDS

NB_SKIP#

18-,30-

COREFB

COREFB#

11-,34-

11-

8-,9-,11-,14-

1818-

+VCC_CORE_VDD1

10-,19-

1

R253

51_5%

2

1

2

11-

R1220

12

100_1%

1818-

+V3S

R1241

12

100K_1%

MAX17009

R1226

51_5%

MAX17009

10-

0_5%

R1237

1

2

7-,8-,13-,14-,15-,20-,23-,24-,25-,26-,28-,29-,30-,31-,32-,33-,34-,36-,40-,41-,44-,45-,47-,48-,49-,50-

1

R209

4.7K_5%

2

R1240 36.5K_1%

12

12

R1242

154K_1%

C1216

1000pF_50v

R217

2

1

100_1%

C211

12

0.0047uF_50v

R1245

12

10_1%

CPU_PWRGD_SVID_REGLDT_PG

C1192

2

1

R1238

2

2

R1239

C1213

1

2

0.0047uF_50v

MAX17009

0.0047uF_50v

MAX_MAX17009GTL+_TQFN_40P

100_1%R210

12

C1215

0.22uF_6.3v

12

12

12

1

2

+V1.8

0.0047uF_50v

12-,13-,18-,19-,20-,25-,26-,27-

R1246

2

R215 1.2K_1%

2

C173

12

2

R251

1

C1199

1000pF_50v

2

MAX17009

R1219

1000pF_50v

1.2K_1%

1

1

100_1%

C1214

R1243

121K_1%

R1244

10K_1%

C1217

100_1%

1

1

1000pF_50v

1.5K_1%

1

2

1

2

MAX17009

1

PERGD

2

NV_BUF

3

SHDN#

4

REF

5

ILIM

6

OSC

7

TIME

8

SVC

9

SVD

10

THRM

1

2

MAX17009

+V5A

7-,9-,10-,11-,12-,13-,38-

1.5K_1%

1

39

38

37

36

4011

CSN1CSN2

FBDC1FBDC2

FBAC1FBAC2

GNDS1

PGD_IN

OPTION

U1016

GNDS_NB

VDDIO

GNDS2

13

12

14

15

R252

12

10_5%

35

CSP1

CSP2

16

1

2

3417

33

PRO#

VCC

18

1uF_6.3v

3120

32

DH1

TMLPAD

VRHOT#

BST1

VDD1

GND1

GND2

VDD2

BST2

NBSKP#

DH2

19

C209

LX1

DL1

DL2

LX2

10-

R1221

12

0_5%

R1222

12

0_5%

41

30

29

28

27

26

25

24

23

22

21

1

2

CPU_PWRGD_SVID_REG

MAX17009

MAX17009

1

R1225

4.7_5%

2

C1196

0.1uF_16v

(Should routed in 5/5/5 pair and need to

have 10mil clearance to other traces.)

2

C1195

0.1uF_16v

1

1

R1224

4.7_5%

2

+V5A

7-,9-,10-,11-,12-,13-,38-

R250

12

0_5%

C206

1

2

4.7uF_6.3v

(Should routed in 5/5/5 pair and need to

have 10mil clearance to other traces.)

MAX17009

Q45

FDMS8660S

FDMS8690

8765

D

G

S

23

41

8D765

4G1S23

C3008

1

2

4700pF_25v

FDMS8660S

9

Q46

FDMS8690

9

Q44

Q52

C292

1

2

1

2

8765

9

D

G

41S23

8765

9

D

G

41S23

C3007

1

2

4700pF_25v

+VBATR

5-,7-,9-,10-,11-,12-,13-,29-,34-

C288

1

2

D2006

40V_3A_1W

5-,7-,9-,10-,11-,12-,13-,29-,34-

1

C293

1

2

2

4.7uF_25v

4.7uF_25v

4.7uF_25v

D2007

1

40V_3A_1W

2

C287

1

2

4.7uF_25v

4.7uF_25v

4.7uF_25v

1

R1205

22_5%

2

C1173

1

2

1000pF_50v

C291

1

2

1

C286

2

1

R1206

1K_5%

2

C1197

220pF_50v

+VBATR

1

C1200

2

100uF_25v

1

R1204

22_5%

2

C1172

1

2

1000pF_50v

ETQP4LR45XFC

12

1

R1207

2.4K_1%

2

R1183

12

4.02K_1%

C1198

1

R1223

1K_5%

2

C1194

1

2

220pF_50v

L1027

R1184

12

10K_1%_THER_NTC

12

0.22uF_10v

C1193

0.22uF_10v

12

R1201

R1203

12

12

10K_1%_THER_NTC

4.02K_1%

1

R1202

2.4K_1%

2

L1024

12

ETQP4LR45XFC

330uF_2v_9mR_Panasonic

C351

+VCC_CORE

C349

1

2

+VCC_CORE_VDD1

1

1

2

2

330uF_2v_9mR_Panasonic

18-,19-

C114312

330uF_2v_7mR

10-,19-

C1144

330uF_2v_7mR

MAX17009

CHANGE by

INVENTEC

TITLE

Prince/Pearl

+VCC_CORE

CODE

CS

SHEET

DOC. NUMBER

OF

10 53

REV

X02SI 1

SIZE

1-Feb-2008Andy Liu

A3

Page 11

+VCC_CORE_NB

19-

PWR_GOOD_3

PAD1006

POWERPAD_2_0610

C148

220uF_2.5v_R35

8-,9-,10-,11-,14-

RICH_RT9194PE_05P_SOT23_6P

1

2

3

U1013

EN

GND

FB

1

2

7-,9-,10-,11-,12-,13-,38-

6

VCC

5

DRI

4

PGOOD

5-,7-,9-,10-,12-,13-,29-,34-

+VBATR

C147

4.7uF_25v

L1039

CYNTEC_PCMC063_3R3

1.5K_1%

0.22uF_16v

12

R1234

12

C1209

12

9-,15-,18-,19-,24-,30-,31-

+V1.2S

+V5A

1

C1145

0.1uF_10v

2

R1161

12

10-,11-,34-

0_5%

7-,9-,10-,11-,12-,13-,38-

C146

1

1

2

2

4.7uF_25v

R1233

12

5.76K_1%

1

C1126

4.7uF_10v

2

Q1014

8

D

S

7

6

5

G

FDM6296_POWERPAK1212_8

SYS_PWRGD

+V5A

1

2

3

4

1

2

C1211

1uF_6.3v

5

6

7

4

S1_D2

S2

FDS6900AS

Q32

D1

G1

G2

1

2

8

3

21-,22-,23-,24-

1

R1162

4.12K_1%

2

1

R1163

10K_1%

2

+V1.1S

POWERPAD_2_0610

1

220uF_2.5v_R35

2

C1146

PAD1004

2

R1236

0_5%

PWR_GOOD_3

1

0.22uF_16v

R1235

100K_1%

R1250

2

1

10-,11-,34-

0_5%

C1224

1

2

8-,9-,10-,11-,14-

C1210

12

12

R1252

12

0_5%

U1017

1

EN

PGOOD

VCC

VDD

3

DL

SKIP

4

LX

REF

5

DH

REFIN

6

ILIM

BST

7

TON

TML-PAD

MAX_MAX8792ETD+T_DFN_14P

R1251

12

0_5%

13-,14-,15-,18-,21-,23-,24-,32-

C330

0.1uF_10v

+V5A

1

2

7-,9-,10-,11-,12-,13-,38-

14

132

12

11

10

9

8

FB

15

+V1.8S

PWR_GOOD_3

1

2

1uF_6.3v

8792GND

10-

8792GND

8-,9-,10-,11-,14-

C300

GMT_G966_25ADJF1Uf_SOP_8P

10uF_10v

SYS_PWRGD

8792GND

8

7

5

1

R1228

OPEN

2

R1230

12

0_5%

1

R1229

OPEN

2

80.6K_1%

NB_SKIP#

C1223

1

2

100pF_50v

8792GND

U22

1

POK9TML

GND

2

ADJ

VEN

36

VIN

VO

4

NC

VPP

R1231

1

2

10-

1000pF_50v

1

NBV_BUF

+V1.5S

48-,49-

1

R304

9.1K_1%

2

1

R331

10K_1%

2

R1232

OPEN

1

2

C1222

12

C302

2

8792GND

10uF_10v

CHANGE by

Andy Liu 22-Nov-2007

INVENTEC

TITLE

Prince/Pearl

POWER

SIZE CODE

A3

DOC. NUMBER

SI 1 X02

CS

SHEET

11

REV

OF

53

Page 12

R86

12

10_5%

7-,9-,10-,11-,12-,13-,38-

+V5A

+VBATR

5-,7-,9-,10-,11-,13-,29-,34-

10-,12-,13-,18-,19-,20-,25-,26-,27-

+V1.8

SLP_S5#_5R

V18_GOOD

12-,13-

13-

R87

12

0_5%_OPEN

C64

1uF_6.3v

SLP_S5#_5R

1

2

1

2

BAT54_30V_0.2A

12-,13-

3300pF_50v

R88

330K_1%

13

D12

R127

12

200K_5%

C86

0.033uF_16v

1

2

51117GND

M_VREF

C87

U6

1

EN_PSV

TON

VOUT

V5FILT

VFB

PGOOD

GND

VBST

DRVH

TRIP

V5DRV

DRVL

PGND

LL

TML

2

3

4

5

6

7

TI_TPS51117_QFN_14P

R107

12

0_5%

+V5A

25-,26-

7-,9-,10-,11-,12-,13-,38-

1

1

C85

2

2

1uF_6.3v

1

C72

0.1uF_16v

2

R108

12

14

13

0_5%

12

11

10

9

8

15

15K_1%

11

VDDQSNS

GND

10

VIN VLDOIN

9

S5

8

GND

7

S3

6

VTTREF

TI_TPS51100_DGQ_10P

R106

PGND

VTTSNS

51117GND

U9

VTT

1

1

2

2

1

2

3

4

5

C128

4.7uF_6.3v

C71

1uF_6.3v

1

2

+V0.9S

C3009

1

2

4.7uF_6.3v

Q23

FDS8884

19-,27-

C127

1

2

220uF_2.5v

C84

1

8765

2

4.7uF_25v

D

G

41S23

765

8

D

Q22

G

FDS6690AS

S

4

123

C83

1

2

4.7uF_25v

L1040

12

PCMC063T_2R2MN

44.2K_1%

R82

30.1K_1%

R83

51117GND

PAD1007

1

C62

OPEN12

2

1

2

POWERPAD_2_0610

1

C1225

330uF_2v_15mR_Panasonic

2

+V1.8

10-,12-,13-,18-,19-,20-,25-,26-,27-

C126

C125

1

1

2

2

1uF_6.3v

10uF_6.3v_OPEN

NOTE: DDR2 REGULATOR

CHANGE by

Andy Liu 21-Nov-2007

INVENTEC

TITLE

Prince/Pearl

DDR2 POWER

CODE DOC. NUMBER

SIZE

A3

SI 1 X02

CS

SHEET

REV

OF

5312

Page 13

GATE_5S

+V5A

7-,9-,10-,11-,12-,13-,38-

6

5

2

1

13-

Q70

D

G

FDC655BN

+V5S

8-,14-,20-,28-,31-,32-,35-,37-,39-,42-,43-,47- 7-,8-,10-,14-,15-,20-,23-,24-,25-,26-,28-,29-,30-,31-,32-,33-,34-,36-,40-,41-,44-,45-,47-,48-,49-,50-

4

S

3

47_5%

R547

1

Q72

G

1

2

1

2

3

D

S

2

SSM3K7002F

C531

10uF_6.3v

+V3A

5-,7-,9-,14-,31-,32-,33-,45-,50-

Q56

6

D

5

2

1

G

FDC655BN

C700

12

13- 13-

GATE_5S

2200pF_50v

+V3S

+V1.8

4

S

3

R375

47_5%

1

Q57

G

1

2

1

2

3

D

S

2

SSM3K7002F

C372

100uF_6.3v

GATE_3S

6

5

2

1

Q33

D

G

FDC655BN

+V1.8S

11-,14-,15-,18-,21-,23-,24-,32-10-,12-,18-,19-,20-,25-,26-,27-

4

S

3

C145

1

2

1000pF_50v

1

Q41

G

1

2

1

R196

47_5%

2

3

D

S

2

SSM3K7002F

C149

10uF_6.3v

13-,14-

SLP_S3_5R

SLP_S3#_3R

V18_GOOD

SLP_S3_5R

5-,8-,13-,32-,34-,43-,45-,48-

12-

13-,14-

R239

12

4.7K_5%

Q39

1

G

SSM3K7002F

Q40

G

1

SSM3K7002F

+VBATR +VBATR

5-,7-,9-,10-,11-,12-,13-,29-,34-

1

R190

100K_5%

2

1

R189

470K_5%

2

3

D

S

2

3

D

S

2

5-,7-,9-,10-,11-,12-,13-,29-,34-

E

E

B

B

C

C

Q31

D-MMST3906

R193

12

100K_5%

R194

12

470_5%

1

C144

2200pF_50v

2

1

R195

20K_5%

2

13-

GATE_5S SLP_S5#_3R

13-

GATE_3S

32-,38-

SSM3K7002F

SSM3K7002F

SLP_S3#_3R

+V5A

7-,9-,10-,11-,12-,13-,38-

1

R546

10K_5%

Q73

1

G

Q71

G

1

2

3

D

S

2

3

D

S

2

5-,8-,13-,32-,34-,43-,45-,48-

1

R240

100K_5%

2

CHANGE by SHEET

Andy Liu 26-Dec-2007

+V5A

7-,9-,10-,11-,12-,13-,38-

1

R545

3K_5%

2

12-

45-

SLP_S5#_5R

SLP_S5_FPR

INVENTEC

TITLE

Prince/Pearl

POWER(Sleep)

SIZE

CODE DOC. NUMBER

A3

CS

SI 1 X02

REV

OF

5313

Page 14

+V1.8S

11-,13-,15-,18-,21-,23-,24-,32-

8-,13-,20-,28-,31-,32-,35-,37-,39-,42-,43-,47-

+V5S

R198

12

100K_1%

R197

12

280K_1%

C150

1000pF_50v

SLP_S3_5R

+V3S

R199

12

1M_5%

5-,7-,9-,13-,31-,32-,33-,45-,50-

R203

U15

1

+

3

-

R200

20K_5%

12

1

1

R201

2

54.9K_1%

2

13-

SSM3K7002F

2VREF

5-,7-

R204

12

Q34

1

G

100K_1%

3

D

S

2

1

2

12

100K_1%

C153

4700pF_25v

+V3A

5

4

OUT

TI_LMV331IDBVR_SOT23_5P

2

C151

1

2

0.1uF_16v

7-,8-,10-,13-,15-,20-,23-,24-,25-,26-,28-,29-,30-,31-,32-,33-,34-,36-,40-,41-,44-,45-,47-,48-,49-,50-

1

R202

3K_5%

2

8-,9-,10-,11-

PWR_GOOD_3

INVENTEC

TITLE

Prince/Pearl

POWER(Sequence)

CODE

CHANGE by

SIZE REV

21-Nov-2007Andy Liu

A3

DOC. NUMBER

CS

SHEET OF

14 53

X02SI 1

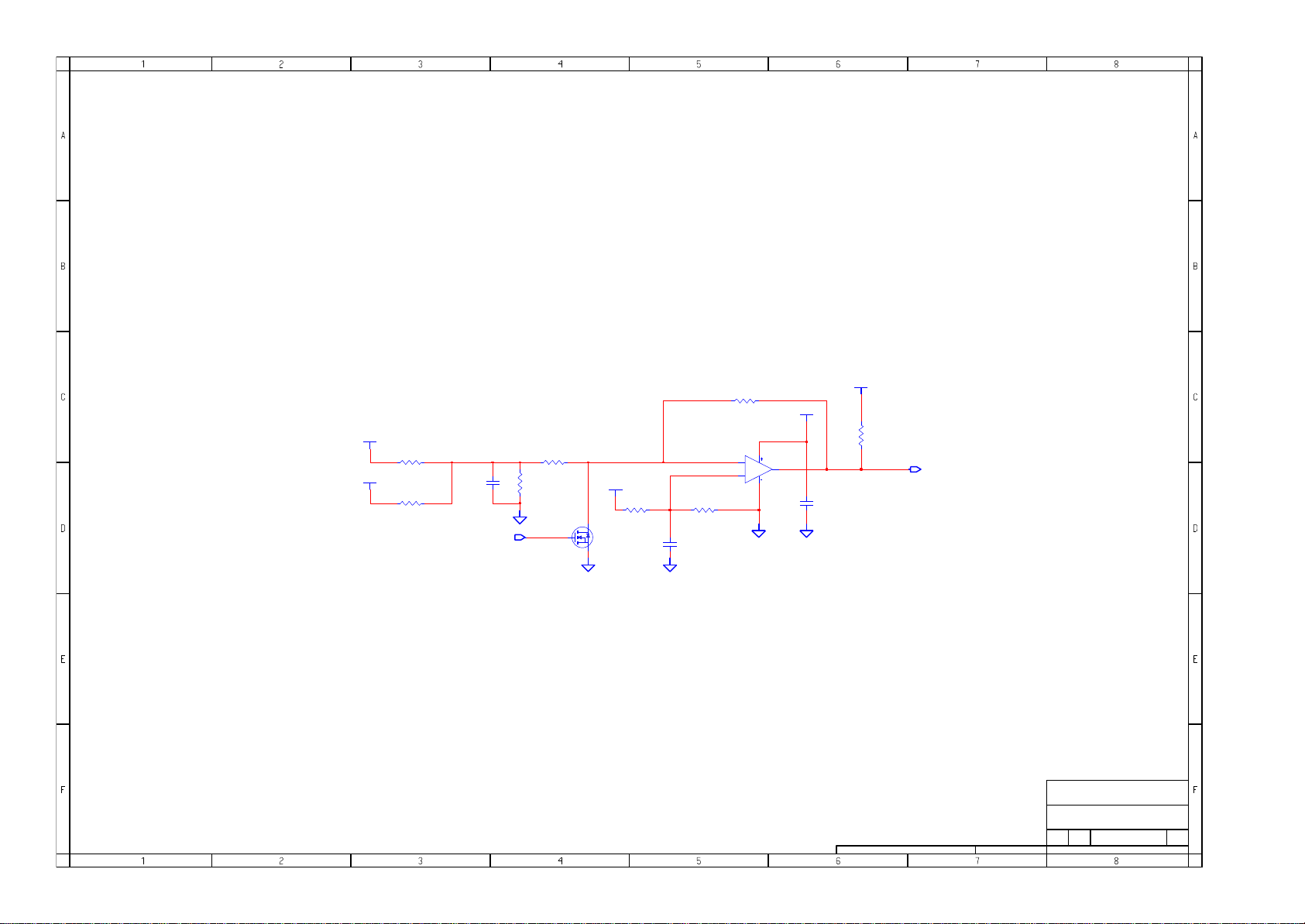

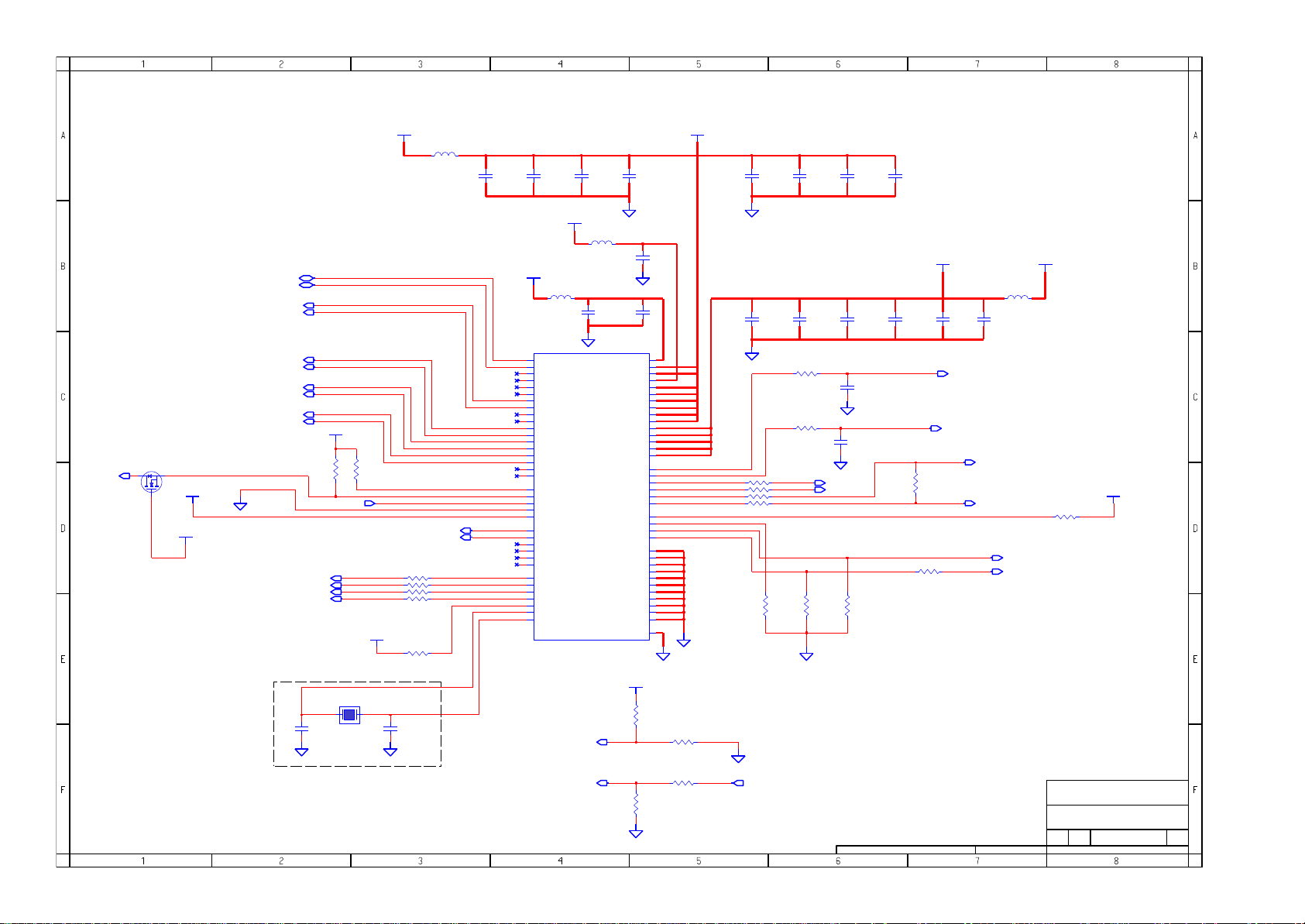

Page 15

CPPE_NC#

SSM3K7002F

CLK_R_PCIE_NEWCARD#

CLK_R_PCIE_NEWCARD

CLK_R_PCIE_MINICARD1#

CLK_R_PCIE_MINICARD1

7-,8-,10-,13-,14-,15-,20-,23-,24-,25-,26-,28-,29-,30-,31-,32-,33-,34-,36-,40-,41-,44-,45-,47-,48-,49-,50-

Q1050

3

2

32-,48-

D

S

G

+V3S_CLK

1

15-

+V3S

7-,8-,10-,13-,14-,15-,20-,23-,24-,25-,26-,28-,29-,30-,31-,32-,33-,34-,36-,40-,41-,44-,45-,47-,48-,49-,50-

7-,8-,10-,13-,14-,15-,20-,23-,24-,25-,26-,28-,29-,30-,31-,32-,33-,34-,36-,40-,41-,44-,45-,47-,48-,49-,50-

SB_3S_SMCLK

SB_3S_SMDATA

CLK_R_PCIE_UWB#

CLK_R_PCIE_UWB

CLK_R_PCIE_LAN#

CLK_R_PCIE_LAN

20-,25-,26-,32-,3620-,25-,26-,32-,36-

4949-

4848-

4747-

4545-

R1361

10K_5%

+V3S

1

1

R1360

10K_5%

2

2

WL_OFF

CLK_R_PCIE_ALINK#

CLK_R_PCIE_ALINK

CLK_R_PCIE_SB#

CLK_R_PCIE_SB

23233030-

+V3S_CLK

X1

12

C332

1

14.31818MHZ

30PPM

2

33pF_50v

47-

15-

R1138

R1139

R1146

R1145

+V3S

12

12

12

12

12

10K_5%

C353

1

2

33pF_50v

ICB_1206_3.0A

CLK_DVI#

R1143

L1020

12

CLK_DVI

CLK_PCIE_ALINK#

0_5%

CLK_PCIE_ALINK

0_5%

0_5%

CLK_PCIE_SB#

CLK_PCIE_SB

0_5%

1

2

2323-

CLKGEN_X1

CLKGEN_X2

C1113

C1114

1

2

22uF_6.3v

0.1uF_16v

+V3S_CLK

L1018

15-

U1012

1

SMBCLK

2

SMBDAT

4

SRC7C_LPRS_27MHZ_NS

5

SRC7T_LPRS_27MHZ_SS

45

SRC6C_SATAC_LPRS

46

SRC6T_SATAT_LPRS

7

SRC5C_LPRS

8

SRC5T_LPRS

9

SRC4C_LPRS

10

SRC4T_LPRS

13

SRC3C_LPRS

14

SRC3T_LPRS

15

SRC2C_LPRS

16

SRC2T_LPRS

20

SRC1C_LPRS

21

SRC1T_LPRS

22

SRC0C_LPRS

23

SRC0T_LPRS

42

CLKREQ4#

43

CLKREQ3#

50

CLKREQ2#

51

CLKREQ1#

24

CLKREQ0#

25

ATIG2C_LPRS

26

ATIG2T_LPRS

30

ATIG1C_LPRS

31

ATIG1T_LPRS

32

ATIG0C_LPRS

33

ATIG0T_LPRS

34

SB_SRC1C_LPRS

35

SB_SRC1T_LPRS

39

SB_SRC0C_LPRS

40

SB_SRC0T_LPRS

41

SB_SRC_SLOW#

67

X1

68

X2

ICS_ICS9LPRS476KLFT_MLF_72P

1

2

0.047uF_10v

+V3S_CLK

15-

BLM11A121S

12

C1119

0.1uF_16v

NBGFX_CLK#

C1135

1

2

L1017

BLM11A121S

12

C1115

2.2uF_16v

+V3S_CLK_VDDA

C1120

1

2

22uF_6.3v

VDDSB_SRC

VDDATIG

VDDSATA

VDDCPU_IO

VDDSB_SRC_IO

VDDATIG_IO

VDDSRC_IO

VDDSRC_IO

HTT0T_LPRS_66M

HTT0C_LPRS_66M

CPUKG0T_LPRS

CPUKG0C_LPRS

REF0_SEL_HTT66

REF1_SEL_SATA

REF2_SEL_27

GNDSATA

GNDSB_SRC

GNDATIG

THERMAL-PAD

23-

C1127

0.047uF_10v

+V3S_CLK_VDDREF

1

2

1

2

49

VDDA

69

VDD48

3

VDDDOT

62

VDDREF

61

VDDHTT

54

VDDCPU

38

29

17

VDDSRC

44

53

37

28

18

12

71

48MHZ_0

70

48MHZ_1

GNDREF

GNDCPU

GNDSRC

GNDSRC

GNDDOT

+V1.8S

HT_CLK

60

HT_CLK#

59

CPUBCLK

56

55

CPUBCLK#

57

PD#

65

64

63

72

GND48

66

58

GNDHTT

52

48

GNDA

47

36

27

19

11

6

73

11-,13-,14-,18-,21-,23-,24-,32-

1

R1144

4.7K_5%

2

12

2.2K_5%

R1140

+V3S_CLK

15-

R1130

R1131

R1133

R1134

C1147

1

2

0.1uF_16v

C1132

1

2

0.1uF_16v

CLK_48M

CLK_48M_1

0_5%

2

1

0_5%

12

0_5%

12

0_5%

12

1

R362

8.2K_5%

2

C1134

1

2

0.1uF_16v

C1129

1

2

0.1uF_16v

R1126

12

22_5%

R1390

12

22_5%_OPEN

2323-

1

R1129

8.2K_5%

2

C1121

1

2

0.1uF_16v

+V1.2S_CLK_IO

C1133

1

2

0.047uF_10v

1

C1112

2

4.7pF_50v

C1280

1

4.7pF_50v_OPEN

2

NBHT_CLK

NBHT_CLK#

CLK_KBC&SB14

1

R1127

8.2K_5%_OPEN

2

CLK_R3S_NB14

C1116

1

2

0.1uF_16v

C1130

1

2

0.047uF_10v

R1128

+V1.2S_CLK_IO

C1128

1

2

1uF_10v

32-

CLK_R3S_SB48

40-

CLK_R3S_FM48

1

R1135

261_1%_OPEN

2

33_5%

12

1

2

18-

CLK_R_CPUBCLK

18-

CLK_R_CPUBCLK#

15-

34-

L1019

BLM11A121S

2

C1131

22uF_6.3v

CLK_R3S_NB14

CLK_R3S_KBC14

+V1.2S

9-,11-,18-,19-,24-,30-,31-

1

R1132

1K_5%

2

1

+V3S_CLK

15-

Place close to CLKGEN within 500mils

NBGFX_CLK

R1142

1

R1141

90.9_1%

2

12

158_1%

15-

CLK_R3S_NB14

CHANGE by

Andy Liu

26-Dec-2007

INVENTEC

TITLE

Prince/Pearl

CLOCK_GENERATOR

SIZE

CODE DOC. NUMBER

A3

SI 1 X02

CS

SHEET

REV

OF

5315

23-

Page 16

L0_CLKIN1

L0_CLKIN1#

L0_CLKIN0

L0_CLKIN0#

L0_CTLIN1

L0_CTLIN1#

L0_CTLIN0

L0_CTLIN0#

L0_CADIN15

L0_CADIN15#

L0_CADIN14

L0_CADIN14#

L0_CADIN13

L0_CADIN13#

L0_CADIN12

L0_CADIN12#

L0_CADIN11

L0_CADIN11#

L0_CADIN10

L0_CADIN10#

L0_CADIN9

L0_CADIN9#

L0_CADIN8

L0_CADIN8#

L0_CADIN7

L0_CADIN7#

L0_CADIN6

L0_CADIN6#

L0_CADIN5

L0_CADIN5#

L0_CADIN4

L0_CADIN4#

L0_CADIN3

L0_CADIN3#

L0_CADIN2

L0_CADIN2#

L0_CADIN1

L0_CADIN1#

L0_CADIN0

L0_CADIN0#

21212121-

21212121-

21212121212121212121212121212121-

21212121212121- 212121212121212121- 2121-

CN1011-1

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

HYPERTRANSPORT

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

Y4

Y3

Y1

W1

T5

R5

R2

R3

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

FOX_PZ63823_284S_41F_TEMP_638P

21-

L0_CLKOUT1

21-

L0_CLKOUT1#

21-

L0_CLKOUT0

21-

L0_CLKOUT0#

21-

L0_CTLOUT1

21-

L0_CTLOUT1#

21-

L0_CTLOUT0

21-

L0_CTLOUT0#

21-

L0_CADOUT15

21-

L0_CADOUT15#

21-

L0_CADOUT14

21-

L0_CADOUT14#

21-

L0_CADOUT13

21-

L0_CADOUT13#

21-

L0_CADOUT12

21-

L0_CADOUT12#

21-

L0_CADOUT11

21-

L0_CADOUT11#

21-

L0_CADOUT10

21-

L0_CADOUT10#

21-

L0_CADOUT9

21-

L0_CADOUT9#

21-

L0_CADOUT8

21-

L0_CADOUT8#

21-

L0_CADOUT7

21-

L0_CADOUT7#

21-

L0_CADOUT6

21-

L0_CADOUT6#

21-

L0_CADOUT5

21-

L0_CADOUT5#

L0_CADOUT4

21-

L0_CADOUT4#

21-

L0_CADOUT3

21-

L0_CADOUT3#

21-

L0_CADOUT2

21-

L0_CADOUT2#

21-

L0_CADOUT1

21-

L0_CADOUT1#

L0_CADOUT0

21-

L0_CADOUT0#

A1

AF1

S1

Top View

A26

Layout: Add stitching caps if crossing plane split.

INVENTEC

TITLE

Prince/Pearl

CPU-1

CODE

SIZE

CHANGE by OF

21-Nov-2007Andy Liu

A3

DOC. NUMBER REV

CS

SHEET

16 53

X02SI 1

Page 17

MA_CLK_DDR2

MA_CLK_DDR2#

MA_CLK_DDR1

MA_CLK_DDR1#

MA_CS1#

MA_CS0#

MA_ODT1

MA_ODT0

MA_CAS#

MA_WE#

MA_RAS#

MA_BA2

MA_BA1

MA_BA0

MA_CKE1

MA_CKE0

MA_A(15:0)

MA_DQS(7)

MA_DQS#(7)

MA_DQS(6)

MA_DQS#(6)

MA_DQS(5)

MA_DQS#(5)

MA_DQS(4)

MA_DQS#(4)

MA_DQS(3)

MA_DQS#(3)

MA_DQS(2)

MA_DQS#(2)

MA_DQS(1)

MA_DQS#(1)

MA_DQS(0)

MA_DQS#(0)

MA_DM(7:0)

CN1011-2

P19

MA_CLK_H3

N19

MA_CLK_H0

N20

MA_CLK_L0

P20

MA_CLK_L3

25252525-

25-,2725-,27-

25-,2725-,27-

25-,2725-,2725-,27-

25-,2725-,2725-,27-

25-,2725-,2725-,27- 26-,27-

MA_A(15)

MA_A(14)

MA_A(13)

MA_A(12)

MA_A(11)

MA_A(10)

MA_A(9)

MA_A(8)

MA_A(7)

MA_A(6)

MA_A(5)

MA_A(4)

MA_A(3)

MA_A(2)

MA_A(1)

MA_A(0)

25-

MA_DQS(7)

25-

MA_DQS#(7)

25-

MA_DQS(6)

25-

MA_DQS#(6)

25-

MA_DQS(5)

25-

MA_DQS#(5)

25-

MA_DQS(4)

25-

MA_DQS#(4)

25-

MA_DQS(3)

25-

MA_DQS#(3)

25-

MA_DQS(2)

25-

MA_DQS#(2)

25-

MA_DQS(1)

25-

MA_DQS#(1)

25-

MA_DQS(0)

25-

MA_DQS#(0)

25-

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

Y16

MA_CLK_H2

AA16

MA_CLK_L2

E16

MA_CLK_H1

F16

MA_CLK_L1

V20

MA1_CS_L1

U20

MA1_CS_L0

U19

MA0_CS_L1

T20

MA0_CS_L0

V22

MA0_ODT1

T19

MA0_ODT0

V19

MA1_ODT1

U21

MA1_ODT0

T22

MA_CAS_L

T24

MA_WE_L

R19

MA_RAS_L

J21

MA_BANK2

R23

MA_BANK1

R20

MA_BANK0

J20

MA_CKE1

J22

MA_CKE0

K19

MA_ADD15

K24

MA_ADD14

V24

MA_ADD13

K20

MA_ADD12

L22

MA_ADD11

R21

MA_ADD10

K22

MA_ADD9

L19

MA_ADD8

L21

MA_ADD7

M24

MA_ADD6

L20

MA_ADD5

M22

MA_ADD4

M19

MA_ADD3

N22

MA_ADD2

M20

MA_ADD1

N21

MA_ADD0

W12

MA_DQS_H7

W13

MA_DQS_L7

Y15

MA_DQS_H6

W15

MA_DQS_L6

AB19

MA_DQS_H5

AB20

MA_DQS_L5

AD23

MA_DQS_H4

AC23

MA_DQS_L4

G22

MA_DQS_H3

G21

MA_DQS_L3

C22

MA_DQS_H2

C21

MA_DQS_L2

G16

MA_DQS_H1

G15

MA_DQS_L1

G13

MA_DQS_H0

H13

MA_DQS_L0

Y13

MA_DM7

AB16

MA_DM6

Y19

MA_DM5

AC24

MA_DM4

F24

MA_DM3

E19

MA_DM2

C15

MA_DM1

E12

MA_DM0

FOX_PZ63823_284S_41F_TEMP_638P

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MEMORY INTERFACE

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

25-

MA_DATA(63:0)

MB_CLK_DDR2

MB_CLK_DDR2#

MB_CLK_DDR1

MB_CLK_DDR1#

MB_CS1#

MB_CS0#

MB_ODT1

MB_ODT0

MB_CAS#

MB_WE#

MB_RAS#

MB_BA2

MB_BA1

MB_BA0

MB_CKE1

MB_CKE0

MB_A(15:0)

MB_DQS(7)

MB_DQS#(7)

MB_DQS(6)

MB_DQS#(6)

MB_DQS(5)

MB_DQS#(5)

MB_DQS(4)

MB_DQS#(4)

MB_DQS(3)

MB_DQS#(3)

MB_DQS(2)

MB_DQS#(2)

MB_DQS(1)

MB_DQS#(1)

MB_DQS(0)

MB_DQS#(0)

MB_DM(7:0)

26262626-

26-,2726-,27-

26-,2726-,27-

26-,2726-,2726-,27-

26-,2726-,2726-,27-

26-,2726-,27-

2626262626262626262626262626262626-

MB_A(15)

MB_A(14)

MB_A(13)

MB_A(12)

MB_A(11)

MB_A(10)

MB_A(9)

MB_A(8)

MB_A(7)

MB_A(6)

MB_A(5)

MB_A(4)

MB_A(3)

MB_A(2)

MB_A(1)

MB_A(0)

MB_DQS(7)

MB_DQS#(7)

MB_DQS(6)

MB_DQS#(6)

MB_DQS(5)

MB_DQS#(5)

MB_DQS(4)

MB_DQS#(4)

MB_DQS(3)

MB_DQS#(3)

MB_DQS(2)

MB_DQS#(2)

MB_DQS(1)

MB_DQS#(1)

MB_DQS(0)

MB_DQS#(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

CN1011-3

R26

MB_CLK_H3

P22

MB_CLK_H0

R22

MB_CLK_L0

R25

MB_CLK_L3

AF18

MB_CLK_H2

AF17

MB_CLK_L2

A17

MB_CLK_H1

A18

MB_CLK_L1

U22

MB1_CS_L0

W25

MB0_CS_L1

V26

MB0_CS_L0

W23

MB0_ODT1

W26

MB0_ODT0

Y26

MB1_ODT0

U24

MB_CAS_L

U23

MB_WE_L

U25

MB_RAS_L

J26

MB_BANK2

U26

MB_BANK1

R24

MB_BANK0

H26

MB_CKE1

J25

MB_CKE0

J24

MB_ADD15

J23

MB_ADD14

W24

MB_ADD13

L25

MB_ADD12

L26

MB_ADD11

T26

MB_ADD10

K26

MB_ADD9

M26

MB_ADD8

L24

MB_ADD7

N25

MB_ADD6

L23

MB_ADD5

N26

MB_ADD4

N23

MB_ADD3

P26

MB_ADD2

N24

MB_ADD1

P24

MB_ADD0

AF12

MB_DQS_H7

AE12

MB_DQS_L7

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AC25

MB_DQS_H4

AC26

MB_DQS_L4

F26

MB_DQS_H3

E26

MB_DQS_L3

A24

MB_DQS_H2

A23

MA_DQS_L2

D16

MB_DQS_H1

C16

MA_DQS_L1

C12

MB_DQS_H0

B12

MA_DQS_L0

AD12

MB_DM7

AC16

MB_DM6

AE22

MB_DM5

AB26

MB_DM4

E25

MB_DM3

A22

MB_DM2

B16

MB_DM1

A12

MB_DM0

FOX_PZ63823_284S_41F_TEMP_638P

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MEMORY INTERFACE

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

AD11

AF11

AF14

AE14

Y11

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

26-

MB_DATA(63:0)

INVENTEC

TITLE

Prince/Pearl

CPU-2

SIZE CODE DOC. NUMBER REV

CHANGE by SHEET OF

21-Nov-2007Andy Liu

A3

SI 1

CS

17 53

X02

Page 18

10-

COREFB

10-

COREFB#

Routing differential pair type

To put pull high resistors near switching power source

Keep trace to resistor less than 600mils from CPU pin

and trace to AC caps less than 1250mils.

CLK_R_CPUBCLK

CLK_R_CPUBCLK#

+V1.8

+VCC_CORE

CPU_SID

10-,19-

Routing differential pair type

1

R1177

51_5%

2

1

R1175

51_5%

2

10-,12-,13-,18-,19-,20-,25-,26-,27-

3232-

15-

15-

10-,12-,13-,18-,19-,20-,25-,26-,27-

C1152

12

3900pF_16v

R1176

169_1%

C1153

12

3900pF_16v

2

1

R1148 390_1%

12

390_1%R1174

+V1.8

Keep trace to resistors less

than 1" from CPU pin.

VDD1_FB

VDD1_FB#

Routing differential pair type

+V1.8S

11-,13-,14-,15-,18-,21-,23-,24-,32-

1

CPUBCLKIN_H

2

CPUBCLKIN_L

CPU_TRST#

12

12

LDT_PG

LDTSTOP#

LDT_RST#

CPU_TDI

CPU_TCK

CPU_TMS

39.2_1%R1192

39.2_1%R1194

1

R1154

0_5%

2

1010-

10-,18-,3018-,23-,3018-,23-,30-

1818181818-

CPU_MVREF

18-

R1180 510_5%

510_5%R1178

300_5%R1182

R1200 300_5%

R1199

R1181

R1169

+V1.8

10-,12-,13-,18-,19-,20-,25-,26-,27-

12

12

12

12

2

1

300_5%

300_5%

12

12

300_5%

CPU_VDDA

C324

1

2

TP19

TP20

TP3

TP7

TP13

TP12

TP21

TP10

FOX_PZ63823_284S_41F_TEMP_638P

C279

1

3300pF_50v

4.7uF_6.3v

2

CN1011-4

F8

VDDA

F9

VDDA

MISC

A9

CLKIN_H

A8

CLKIN_L

A7

PWROK

LDTSTOP_L

B7

RESET_L

AF4

SIC

AF5

SID

AF9 AE9

TDI

AD9

TRST_L

AC9

TCK

AA9

TMS

E10

DBREQ_L

F6

VDD_FB_H

E6

VDD_FB_L

H6

VDDNB_FB_H

G6

VDDNB_FB_L

Y10

VTT_SENSE

W17

M_VREF

AE10

M_ZN

AF10

M_ZP

AA8

MEMHOT_L

E9

TEST25_H

E8

TEST25_L

G9

TEST19

H10

TEST18

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

THERMDC

W8

THERMDA

Y6

VDD1_FB_H

AB6

VDD1_FB_L

LDTREQ_L

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

TEST29_H

TEST29_L

TEST28_H

TEST28_L

ALERT_L

1

2

DBRDY

HTREF1

HTREF0

TEST24

TEST23

TEST22

TEST21

TEST20

TEST27

TEST10

TEST8

SVC

SVD

TDO

BLM11A221S

1

C325

0.22uF_6.3v

+V1.8

C6F10

A6

A4

AF6

AC7

G10

W9

Y9

P6

R6

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

L33

+V2.5S

7-

2

10-,12-,13-,18-,19-,20-,25-,26-,27-

1

1

R1155

R1179

1K_1%

1K_1%

2

2

18-

TP4

TP6

12

TP14

TP15

TP9

TP8

TP17

TP18

Routing as differential as short as possible

CPU_THERM_SCI#

TP16

TP11

18-,23-,30-

LDT_REQ#

10-

CPU_SVC_R

10-

THERMTRIP#

CPU_SVD_R

CPU_DBRDYCPU_DBREQ#

44.2_1%

44.2_1% R351

12

2

1

R320

80.6_1%_OPEN

Route as 80 ohm differential impedance.

Keep trace to resistor less than 1" FROM CPU PIN.

12

12

12

1

R352

R1173

R1170

2

R1197

+V1.2S

300_5%

300_5%R1195

300_5%

300_5%

R1196

300_5%

12

+V1.8

10-,12-,13-,18-,19-,20-,25-,26-,27-

1

1

2

9-,11-,15-,19-,24-,30-,31-

Keep trace to resistors less

than 1" from CPU pin.

R1191

300_5%

2

R1172

300_5%

+V1.8

10-,12-,13-,18-,19-,20-,25-,26-,27-

1

R1218

1K_5%

2

1

2

R1171

1K_5%

Q1015

1

B

MMBT3904

C32E

+V1.8

1

B

Q1018

MMBT3904

10-,12-,13-,18-,19-,20-,25-,26-,27-

1

R1217

30K_5%

2

32-

C32E

20-,32-

H_THERMTRIP#CPU_SIC

8-,20-

PROCHOT#

18-

CPU_TDO

THERM_SCI#

+V1.8

R901

18-

18-

18-

18-

18-

18-

18-

18-,23-,30-

+V1.8S

1

1

2

2

10-,12-,13-,18-,19-,20-,25-,26-,27-

300_5%

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

LDT_RST#

HDT Header

11-,13-,14-,15-,18-,21-,23-,24-,32-

R902

604_1%

CN1009

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

SAMTEC_ASP_68200_26P

+V1.8

10-,12-,13-,18-,19-,20-,25-,26-,27-

1

R1193

1K_1%

2

1

R1198

1K_1%

2

1

C266

2

1000pF_50v

CPU_MVREF

18-

1

2

C267

0.22uF_6.3v

LDT_PG

LDT_RST#

LDTSTOP#

LDT_REQ#

CHANGE by

R345

10-,18-,30-

18-,23-,30-

18-,23-,30-

18-,23-,30-

12

300_5%

R1136

12

300_5%

R344

1

2

300_5%

R370

12

300_5%

Andy Liu 28-Jan-2008

+V1.8S

11-,13-,14-,15-,18-,21-,23-,24-,32-

INVENTEC

TITLE

Prince/Pearl

CPU-3

CODESIZE DOC. NUMBER

A3

CS

SHEET

SI 1 X02

REV

OF

5318

Page 19

+VCC_CORE

10-,18-,19-

C276

1

22uF_6.3v

2

+VCC_CORE_VDD1

10-,19-

C271

1

2

+VCC_CORE_NB

11-,19-

C277

1

2 22uF_6.3v

22uF_6.3v

Place under socket on bottom side.

1

2

1

222uF_6.3v

1

2

C273

22uF_6.3v

C270

22uF_6.3v

C268

+VCC_CORE_VDD1

10-,19-

+VCC_CORE

C321

1

22uF_6.3v

2

C318

1

2

22uF_6.3v

C269

1

2

4.7uF_6.3v

10-,18-,19+VCC_CORE_VDD1

10-,19-

CN1011-5

AC4

VDD1

AD2

VDD1

G4

VDD0

H2

VDD0

J9

VDD0

J11

VDD0

J13

VDD0

K6

VDD0

K10

VDD0

K12

VDD0

K14

VDD0

L4

VDD0

L7

VDD0

L9

VDD0

L11

VDD0

L13

VDD0

M2

VDD0

M6

VDD0

M8

VDD0

M10

VDD0

N7

VDD0

VDD

N9

VDD0

N11

VDD0

P8

VDD1

P10

VDD1

R4

VDD1

R7

VDD1

R9

VDD1

R11

VDD1

T2

VDD1

T6

VDD1

T8

VDD1

T10

VDD1

T12

VDD1

T14

VDD1

U7

VDD1

U9

VDD1

U11

VDD1

U13

VDD1

V6

VDD1

V8

VDD1

V10

VDD1

V12

VDD1

V14

VDD1

W4

VDD1

Y2

VDD1

FOX_PZ63823_284S_41F_TEMP_638P

C275

1

22uF_6.3v

2

C317

22uF_6.3v12

1

2

1

2

C322

0.22uF_16v

C319

0.22uF_16v

C278

1

2

0.01uF_16v

C316

1

2

0.01uF_16v

+V1.2S +V1.2S

9-,11-,15-,18-,19-,24-,30-,31- 9-,11-,15-,18-,19-,24-,30-,31-

CN1011-6

D4

VLDT_A

D3

VLDT_A

D2

AD10

VLDT_A

D1

VLDT_A

D10

VTT

C10

VTT

B10

VTT

VTT

W10

VTT

H25

VDDIO

J17

VDDIO

K18

VDDIO

K21

VDDIO

K23

VDDIO

K25

VDDIO

L17

VDDIO

M18

VDDIO

M21

VDDIO

M23

VDDIO

M25

VDDIO

N17

VDDIO

P18

VDDIO

P21

VDDIO

P23

VDDIO

P25

VDDIO

R17

VDDIO

T18

VDDIO

T21

VDDIO

T23

VDDIO

T25

VDDIO

U17

VDDIO

V18

VDDIO

V21

VDDIO

V23

VDDIO

V25

VDDIO

Y25

VDDIO

AA4

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AB2

VSS

AB7

VSS

AB9

VSS

AB23

VSS

AB25

VSS

AC11

VSS

AC13

VSS

AC15

VSS

AC17

VSS

AC19

VSS

AC21

VSS

AD6

VSS

AD8

VSS

AD25

VSS

AE11

VSS

AE13

VSS

AE15

VSS

AE17

VSS

AE19

VSS

AE21

VSS

AE23

VSS

B4

VSS

B6

VSS

B8

VSS

B9

VSS

B11

VSS

B13

VSS

B15

VSS

B17

VSS

B19

VSS

B21

VSS

B23

VSS

B25

VSS

D6

VSS

D8

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

AC6

VSS

10-,12-,13-,18-,19-,20-,25-,26-,27-

+V0.9S

+V1.8

FOX_PZ63823_284S_41F_TEMP_638P

+V1.8

+V1.8

10-,12-,13-,18-,19-,20-,25-,26-,27-

C274

C323

1

180pF_50v

2

C320

1

180pF_50v

2

C154

1

1

2

2

+V1.8

10-,12-,13-,18-,19-,20-,25-,26-,27-

C166

1

4.7uF_6.3v

2

C156

1

2

0.01uF_16v

Place close to socket.

22uF_6.3v

Place under socket on bottom side.

C158

1

4.7uF_6.3v

2

C157

1

2

0.01uF_16v

C155

1

2

0.22uF_10v

C165

1

2

0.22uF_10v

C161

1

2

180pF_50v

C167

C168

1

1

2

2

0.22uF_10v22uF_6.3v

180pF_50v

C164

1

2

0.22uF_10v

C160

1

4.7uF_6.3v

2

IOPWR

C162

1

2

0.22uF_10v

1

2

VLDT_B

VLDT_B

VLDT_B

VLDT_B

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1

2

C159

4.7uF_6.3v

AE5

AE4

AE3

AE2

AC10

AB10

AA10

A10

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

C272

180pF_50v

C163

1

2

0.22uF_10v

+V0.9S

12-,19-,27-12-,19-,27-

+V1.2S

9-,11-,15-,18-,19-,24-,30-,31-

1

C1139

180pF_50v

2

C1138

1

2

0.22uF_10v

+V0.9S

12-,19-,27-

C44

1000pF_50v_OPEN

2

+VCC_CORE

10-,18-,19-

1

C1140

180pF_50v

2

C1141

1

2

0.22uF_10v

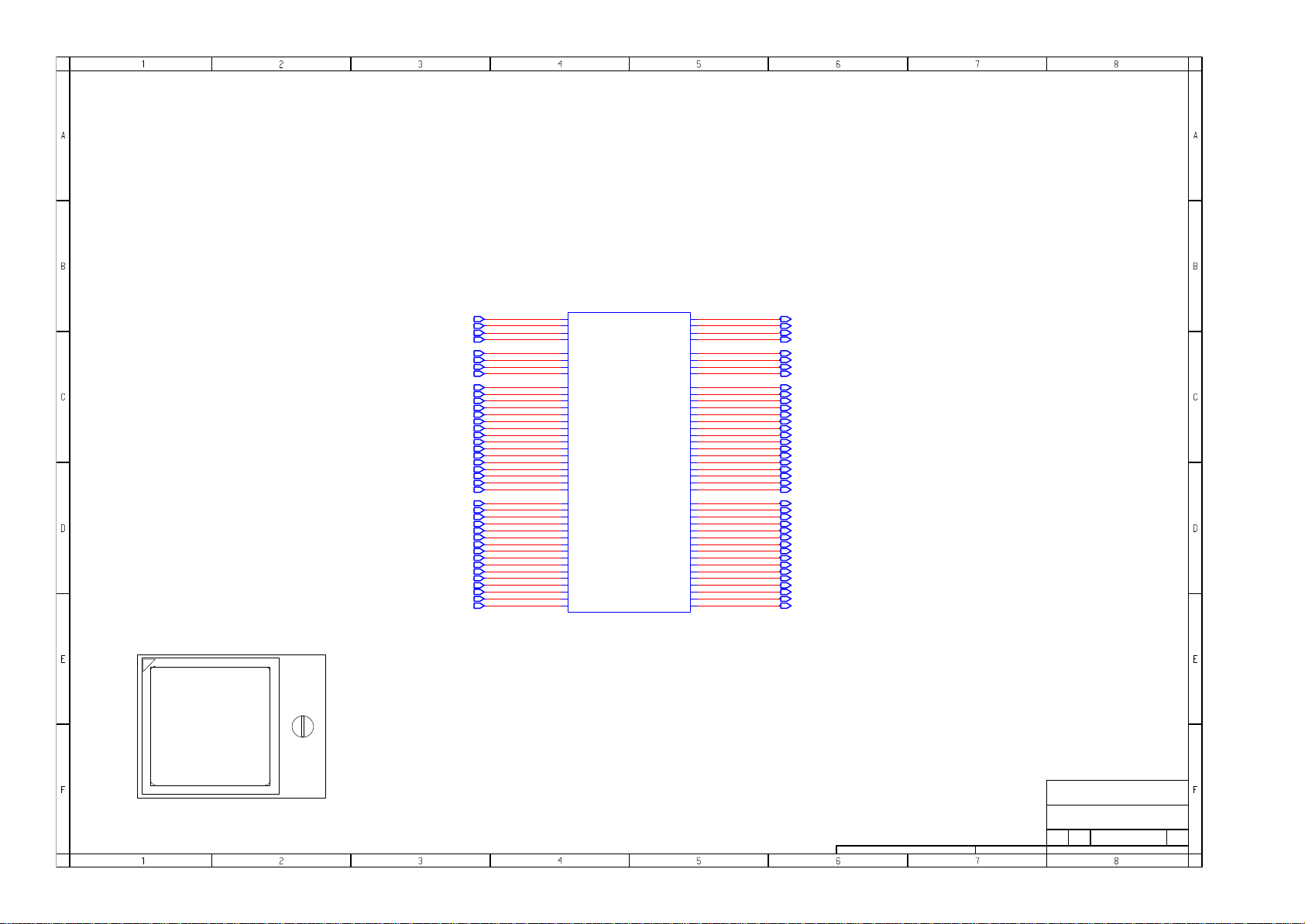

11

2

Place on DDR path

+VCC_CORE_NB

+VCC_CORE_VDD1

10-,19-

+V1.2S+VCC_CORE

C1137

1

4.7uF_6.3v

2

Place close to socket.

C47

1000pF_50v_OPEN

11-,19-

CN1011-7

M16

VDDNB

P16

VDDNB

T16

VDDNB

K16

VDDNB

U15

VDD1

V16

VDDNB

J15

VDD0

L15

VDD0

FOX_PZ63823_284S_41F_TEMP_638P

VDD

M17

VSS

N4

VSS

N8

VSS

N10

VSS

N16

VSS

N18

VSS

P2

VSS

P7

VSS

P9

VSS

P11

VSS

P17

VSS

R8

VSS

R10

VSS

R16

VSS

R18

VSS

T7

VSS

T9

VSS

T11

VSS

T13

VSS

T15

VSS

T17

VSS