Errata

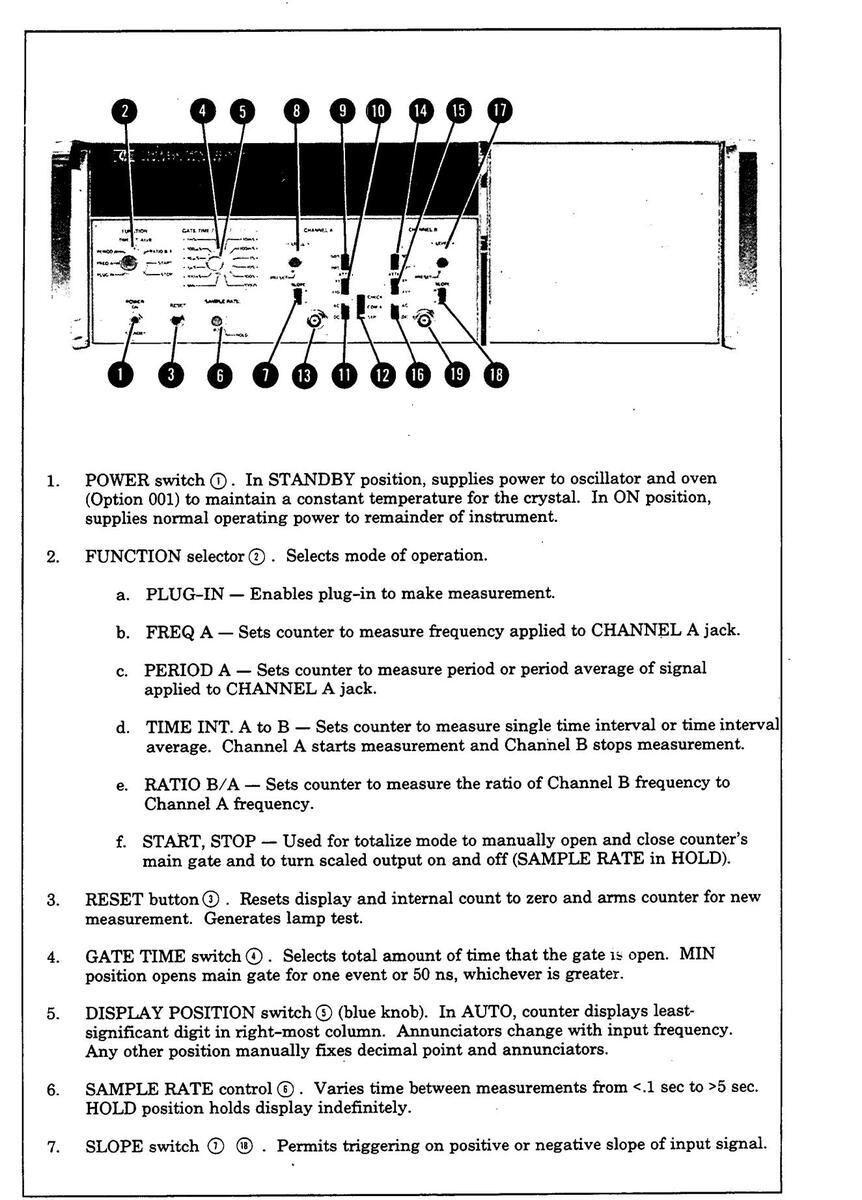

Title & Document Type: 5345A Operating & Service Manual

Manual Part Number: 05345-90060

Revision Date: May 1994

HP References in this Manual

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. The HP XXXX referred to in this document is now the Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

About this Manual

We've added this manual to the Agilent website in an effort to help you support your product. This manual provides the best information we could find. It may be incomplete or contain dated information, and the scan quality may not be ideal. If we find a better copy in the future, we will add it to the Agilent website.

Support for Your Product

Agilent no longer sells or supports this product. You will find any other available product information on the Agilent Test & Measurement website:

www.tm.agilent.com

Search for the model number of this product, and the resulting product page will guide you to any available information. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available.

Table 7-4. Adjustment Procedures

A3 INPUT ATTENUATOR

Equipment:

HP 3480A/3482A DVM Extender Cable 05345-60205 HP 180A Oscilloscope with 1810A Sampler HP 8640B Signal Generator

Setup:

- 1. Set LEVEL controls to PRESET.

- 2. Connect DVM between common and the cathode of diode A4CR1. Adjust A4R11 for an indication of 0 volts ±50 millivolts. Connect DVM between common and cathode of diode A4CR2. Adjust A4R13 for 0 volts ±50 millivolts.

NOTE

Allow a 5-minute warmup before performing adjustment procedure.

Bias Adjustment

- 1. Remove front panel display assembly, as outlined in Section III. Connect display assembly to counter, using extender cable. Place side of cable with "CINCH" on side of board with part number (05345-60004).

- 2. Connect DVM to U2 pin 15 (Channel B, U1 pin 15).

- 3. Adjust bias pot A4R44 (Channel B, A3R47) for a reading of 1.00V ±50 mV.

The following adjustments are done with the bottom cover and bottom air filter removed. The front panel display assembly is installed in the instrument.

Sensitivity Adjustment:

1. Set 5345A controls as follows:

| Input Impedance | 2 |

|---|---|

| ATTEN (A&B) X1 | Ĺ |

| Input Coupling DO | ) |

| Input Amplifier Control SEH | ) |

| SLOPE (A&B) | ۲ |

| LEVEL Control PRESET | ٦ |

- 2. Set 8640B Signal Generator output to 100 MHz at 100 mV rms into 50Ω.

- 3. Set 180A Oscilloscope controls as follows:

| AC/DC D | С |

|---|---|

| MAGNIFIER | ζ1 |

| DISPLAY IN | T |

4. Set 1810A Sampler controls as follows:

| DISPLAY FILTERED |

|---|

| MODE A |

| POLARITY + UP |

| mV/DIV |

| TIME/DIV (outer knob) 10 nSEC |

| TIME/DIV (inner knob) |

| CW SLOPE+ |

| SCAN SWEEP |

| DIRECT/EXPANDED EXPANDED |

| SCAN knob almost fully cw |

- 5. Disconnect the two white cables connected to the A9 board. Channel A output cable is the longer of the two. Connect these cables through an adapter connector (HP part number 1250–0831) to the oscilloscope's inputs.

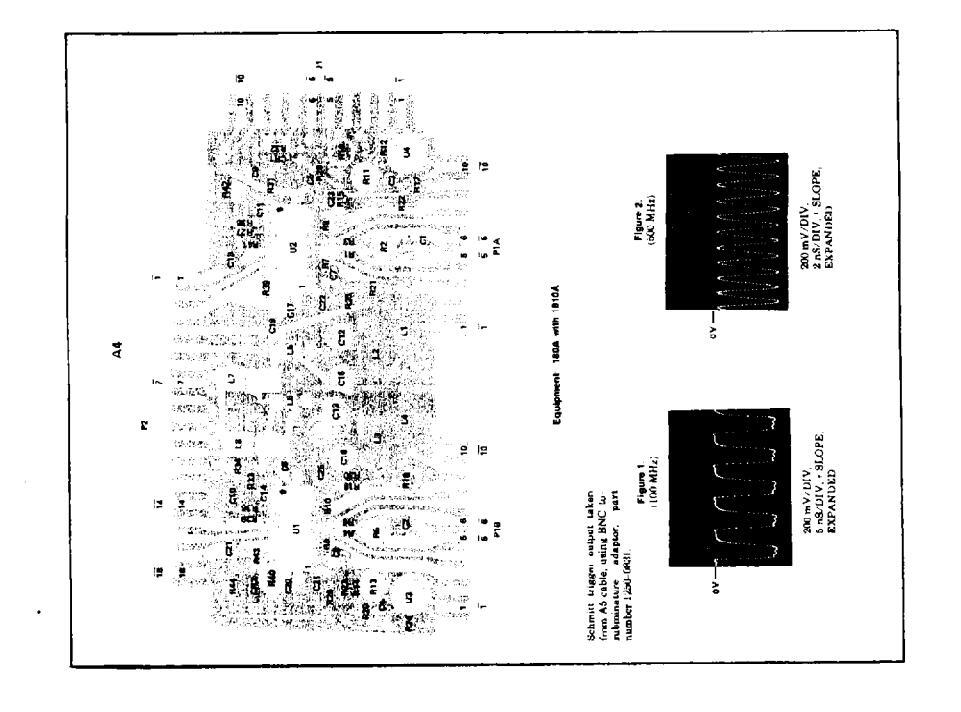

- 6. Adjust A4R2 and A4R11 (Channel B, A4R5 and A4R13) for a signal on oscilloscope.

- Adjust A4R11 (Channel B. A4R13) for no change in signal when SLOPE switch changes position

- 8. Aiust A4R2 (Channel B. A4R45) for 50% duty cycle.

- Set 8640B output to 20 mV rms. q

- 10. Adjust A4R11 (Channel B, A4R13) for no change in signal when SLOPE switch changes position. Readjust A4R2 (Channel B, A4R5) for 50% duty cycle if required.

A4 INPUT TRIGGER

Equipment:

HP 3480A/3482A DVM

- HP 180A Oscilloscope with 1810A Sampler

- HP 8640B Signal Generator

NOTE

Allow a 5-minute warmup before performing adjustment procedure.

The following adjustments are done with the bottom cover and bottom air filter removed. The front panel display assembly is installed in the instrument. See Section III for removal of air filter.

Bias Adjustm

- Adjust A4R2 (Channel B, A4R5) offset pot to midpoint. Connect 412A to A4U2 pin 3 (Channel B, A4U1 pin 3).

- 2 Adjust A4R16 (Channel B, A4R19) bias pot for a reading of +800 mV ±50 mV.

NOTE

NOTE - If A4U2 (Channel A) or A4U1 (Channel B) are replaced, the value of A4R15 (Channel A) or A4R18 (Channel B) may have to be increased in value to meet the 800 mV ±50 mV specifications. An increase of approximately 100 increases adjustment range of A4R16 or A4R19 approximately 100 mV.

Sensitivity Adjustment:

1. Set 5345A controls as follows:

| Input Impedance |

|---|

| ATTEN (A&B) X1 |

| Input Coupling DC |

| Input Amplifier Control SEP |

| SLOPE (A&B) + |

| LEVEL Control PRESET |

Table 5-6. Adjustment Procedures (Continued)

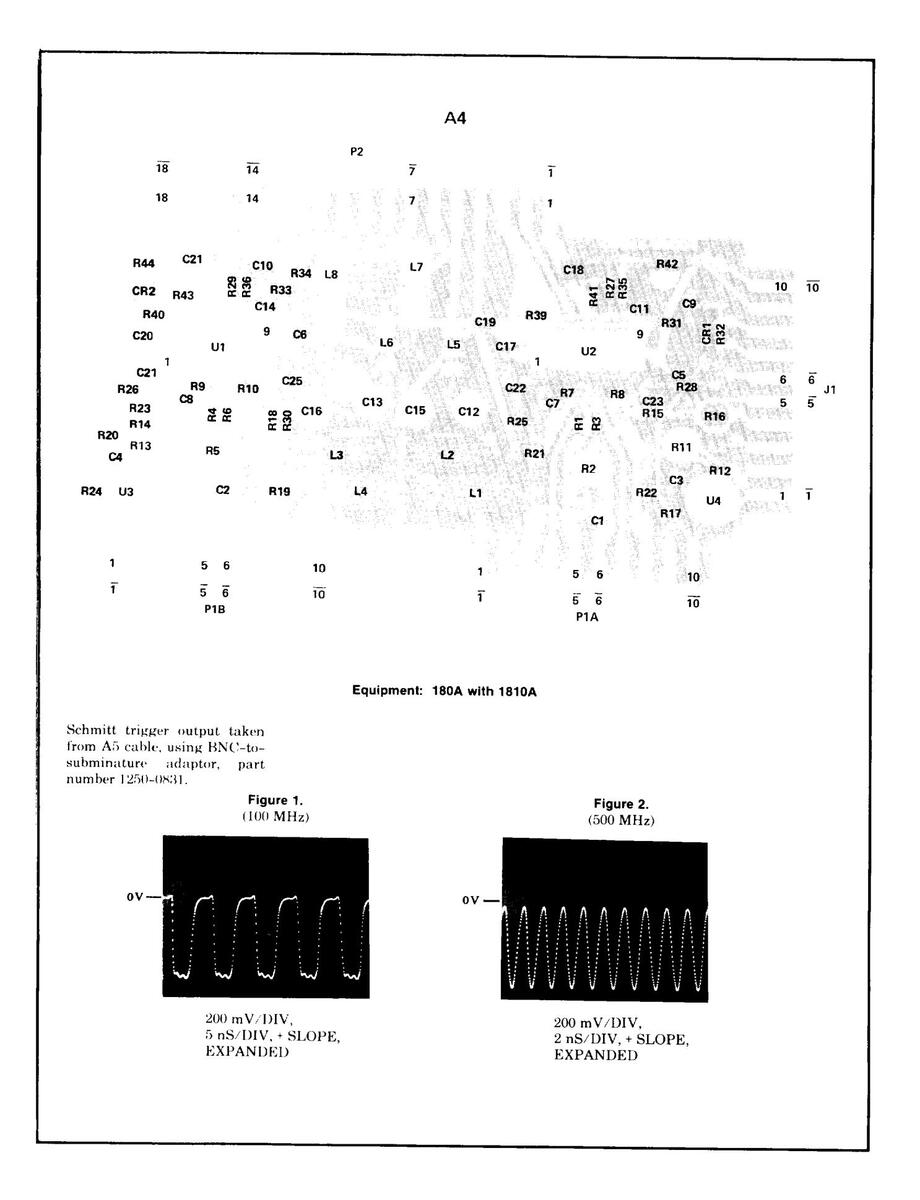

- 2. Set 8640B Signal Generator output to 100 MHz at 100 mV rms into 50Ω.

- 3. Set 180A Oscilloscope controls as follows:

| AC/DC | DC |

|---|---|

| MAGNIFIER | X1 |

| DISPLAY 1 | INT |

4. Set 1810 Sampler controls as follows:

| DISPLAY | FILTERED |

|---|---|

| MODE | A |

| POLARITY | + UP |

| mV/DIV | 200 |

| TIME/DIV (outer knob) | 10 nSEC |

| TIME/DIV (inner knob) | 2 nSEC |

| CW SLOPE | + |

| SCAN | SWEEP |

| DIRECT/EXPANDED | EXPANDED |

| SCAN knob | almost fully cw |

- 5. Disconnect the two white cables connected to the A9 board. Channel A output cable is the longer of the two. Connect these cables through an adapter connector (HP part number 1250-0831) to the oscilloscope's inputs.

- 6. Adjust A4R2 (Channel B, A4R5) for a signal on oscilloscope

- 7. Adjust A4R11 (Channel B, A4R13) for no change in signal when SLOPE switch changes position.

- 8. Set 8640B output to 10 mV rms.

- 9. Adjust A4R2 (Channel B, A4R5) for 50% duty cycle.

- 10. Adjust A4R11 (Channel B, A4R13) for no change in signal when SLOPE switch changes position. Readjust A4R2 (Channel B, A4R5) for 50% duty cycle if required.

Table 7-5, A3/A4 Parts List

|

Reference

Designation |

HP Part

Number |

Qty | Description |

Mfr

Code |

Mfr Part Number |

|---|---|---|---|---|---|

|

A3

A3 |

05345-60039

05345-60038 |

1 |

INPUT ATTENUATOR (OPTION 012)

INPUT ATTENUATOR ASSY (SERIES 1644) |

28480

28480 |

05345-60039

05345-60038 |

|

A3C1

A3C2 |

0160-0551

0160-0551 |

2 |

CAPACITOR-FXD .01UF +100-0% 400WVDC CER

CAPACITOR-FXD .01UF +100-0% 400WVDC CER |

28480

28480 |

0160-0551

0160-0551 |

|

A3C4

A3C5 |

0160-4531 | 2 |

CAPACITOR-FXD 2.2 ±.25PF 50WVDC CER CHIP

NOT ASSIGNED |

28480 | 0160-4531 |

|

A3C6

A3C7 |

0160-4531 |

STRAY CAPACITANCE

CAPACITOR-FXD 2.2 ±.25PF 50WVDC CER CHIP |

28480 | 0160-4531 | |

|

A 3C 9

A 3C 10 |

0160-0552

0150-0072 |

2

2 |

NUT ASSIGNED

CAPACITOR-FXD 100PF +-5% 400WVDC CER CAPACITOR-FXD 200PF +-5% 1000WVDC CER |

28480

28480 |

0160-0552

0150-0072 |

|

A3C11

A3C12 A3C13 A3C14 A3C15 |

0160-0552

0150-0072 0160-3879 0160-3879 0160-3879 |

55 |

CAPACITOR-FXD 100PF +-5% 400WVDC CEP

CAPACITOR-FXD 200PF +-5% 1003WVDC CER CAPACITOR-FXD -01UF +-20% 100WVDC CER CAPACITOR-FXD -01UF +-20% 100WVDC CER CAPACITOR-FXD -01UF +-20% 100WVDC CER |

28480

28480 28480 28480 28480 28480 |

0160-0552

0150-0072 0160-3879 0160-3879 0160-3879 |

|

A 3C 16

A 3C 17 |

0160-3879 |

CAPACITOR-FXD .01UF +-20% 100WVDC CER

NGT ASSIGNED |

28480 | 0160-3879 | |

|

A3C19

A3C20 |

0160-3876

0160-3878 |

11

41 |

NOT ASSIGNED

Capacitor-fxd 47PF +-203 200WVDC CER Capacitor-fxd 1000PF +-298 100WVDC CER |

28480

28460 |

0160-3876

0160-3878 |

|

A 3C 21

A 3C 22 A 3C 23 A 3C 24 A 3C 24 A 3C 25 A 3C 26 A 3C 26 A 3C 27 |

0160-3876

0160-3878 0160-3878 0160-3878 0160-3878 0160-3878 0160-3878 0160-3879 |

CAPACITOR-FXD 47PF +-201 2000VDC CER

CAPACITOR-FXD 1000PF +-201 1000VDC CER CAPACITOR-FXD 1003PF +-201 1000VDC CER CAPACITOR-FXD 1003PF +-201 1000VDC CER CAPACITOR-FXD 1000PF +-201 1000VDC CER CAPACITOR-FXD 1000PF +-20% 1000VDC CER CAPACITOR-FXD 0.01UF +-20% 1000VDC CER |

28480

28480 28480 28480 28480 28480 28480 28480 |

0160-3876

0160-3878 0160-3878 0160-3878 0160-3878 0160-3878 0160-3878 |

|

|

A 3CR1

A 3CR2 A 3CR3 A 3CR4 A 3CR4 A 3CR5 A 3CR6 A 3CP7 A 3CP8 |

1901-0376

1901-0376 1901-0376 1901-0376 1901-0376 1901-0040 1901-0040 1901-0040 |

4

32 |

DIODE-GEN PRP 35V 504A

DIODE-GEN PRP 35V 504A DIODE-GEN PRP 35V 504A DIODE-GEN PRP 35V 504A DIODE-SWITCHING 2NS 30V 504A DIODE-SWITCHING 2NS 30V 504A DIODE-SWITCHING 2NS 30V 504A |

28480

28480 28480 28480 28480 28480 28480 28480 23480 23480 |

1901-0376

1901-0376 1901-0376 1901-0376 1901-0376 1901-0040 1901-0040 1901-0040 |

|

A3J1A

A3J1B A3J2 A3J3 |

1251-2034

1251-2034 1250-1163 1250-1163 |

8

2 |

CONNECTOR; PC EDGE; 10-CONT; DIP SOLDER

CONNECTOR; PC EDGE; 10-CONT; DIP SOLDER CONNECTOR-RF BNC FEM SGL HOLE RR CONNECTOR-RF BNC FEM SGL HOLF RR |

71785

71785 28480 28480 |

252-10-30-300

252-10-30-300 1250-1163 1250-1163 |

|

A 301

A 302 A 303 A 304 A 305 |

1855-0225

1855-0225 1854-0215 1854-0215 1854-0215 |

2

9 |

TRANSISTOR, JFET, DUAL N-CHAN D-MODE SI

TRANSISTOR, JFET, DUAL N-CHAN D-MODE SI TRANSISTOR NPN SI PD=310MW FT=300MHZ TRANSISTOP NPN SI PD=310MW FT=300MHZ TRANSISTOR NPN SI PD=310MW FT=300MHZ |

28480

29480 04713 04713 04713 |

1855-0225

1855-0225 SPS 3611 SPS 3611 SPS 3611 |

| A 306 | 1854-0215 | TRANSISTOR NPN SI PD=310MW FT=3COMHZ | 04713 | SPS 3611 | |

|

A 3R 1

A 3R 2 |

0698-8382 | 1 |

RESISTOR 25 5% .25W C TC=0+-150

NOT ASSIGNED |

28480 | 0698-8382 |

| (FOR R3) |

1 25 1-22 29

0698-8881 |

22 |

RESISTOR 49.9 12 .5W F TC=0+-100

CONNECTOR;1+CONT SKT .033 DIA RESISTOR 900K5%.25W C TC=0+-150 |

19701

00779 28480 |

#F7C1/2-70-49R9-F

1-331677-3 0698-8881 |

|

A 3R 5

A 3R 6 (FOR R6) A 3P 7 A 3R 8 |

0698-8880

0757-0072 1251-2229 0698-8881 0698-8860 |

2 |

RESISTOR 100K 5% .15W C TC=0+-150

RESISTOR 49-9 1 3 -5W F TC=0+-100 CONNFCTOR;1CONT SKT -033 DIA RESISTOR 900K 5% .25W C TC=0+-150 RESISTOR 100K 5% .15W C TC=0+-150 |

28480

19701 00779 28480 28480 |

0698-8880

MF7C1/2-TD-4989-F 1-331677-3 0698-8881 0698-8880 |

|

A 3R 9

A 3R 10 A 3R 11 A 3R 12 A 3R 13 |

2100-0597

0683-2025 2100-0597 0683-2025 0698-8381 |

2

9 2 |

RESISTOR-VAR W/SW 100K 20% CC SPST-SW

RESISTOR 2K 5% 25% FC TC=-400/+700 RESISTOP-VAR W/SW 100K 20% CC SPST-SW RESISTOR 2K 5% 25% FC TC=-400/4700 RESISTOR 2K 5% 25% FC TC=-40/4700 |

28480

01121 28480 01121 28490 |

2100-0597

C82025 2100-0597 C82025 0698-8381 |

|

A 3R 14

A 3R 15 A 3R 16 A 3R 17 A 3R 18 |

0683-5115

0698-8381 0683-5115 0683-1055 0683-1055 |

14

2 |

RESISTOR 510 51 .25W FC TC=-400/+600

RESISTOR 50 51 .15W C TC=0+-150 RESISTOR 510 51 .25W FC TC=-400/+600 RESISTOR 1M 51 .25W FC TC=-800/+900 RESISTOR 1M 51 .25W FC TC=-800/+900 |

01121

28480 01121 01121 01121 |

C85115

O698-8381 C85115 C81055 C91055 |

|

A 3P 19

A 3P 20 A 3P 21 A 3P 22 A 3P 22 A 3P 23 |

0698-8615

0698-8615 0757-0420 0698-6241 0757-0420 |

4

6 2 |

RESISTOR 75K 1% 1/20W

RESISTOR 75K 1% 1/20W RESISTOR 75K 1% 1/20W RESISTOR 750 1% +125W F TC=0+-100 RESISTOR 750 1% +125W F TC=0+-100 |

28480

28480 24546 01121 24546 |

0698-8615

0698-8615 C4-1/R-T0-751-F 877515 C4-1/8-T0-751-F |

|

A 3F 24

A 3R 25 A 3R 26 ► A 3R 27 A 3R 28 |

0757-0420

0698-6241 0757-0420 0683-1125 0698-8615 |

RESISTUR 750 13 .125W F TC=0+-100

RESISTUR 750 53 .125W CC TC=0+882 RESISTUR 750 13 .125W F TC=0+-100 RESISTOR 1.1K 53 .25W FC TC=-400/+700 RESISTOR 75K 1% 1/20W |

24546

01121 24546 01121 28480 |

C4-1/8-T0-751-F

B87515 C4-1/8-T0-751-F C81125 0698-8615 |

NOT IN OPTION 012.

See introduction to this section for ordering information

| Table | 7-5 | A3/A4 | Parts 1 | List ( | (Continued) |

|---|

|

Reference

Designation |

HP Part

Number |

Qty | Description |

Mfr

Code |

Mfr Part Number |

|---|---|---|---|---|---|

|

A 3R 29

► A 3R 30 A 3R 31 A 3R 32 A 3R 33 |

0698-8615

0698-6283 0683-1525 0698-5178 0698-5178 |

2

1 5 4 |

RESISTOR 75K 1% 1/20W

RESISTOR 10 5% -125W CC TC=0+588 RESISTOR 1.5K 5% -25W FC TC=-400/+700 RESISTOR 1.5K 5% -125W CC TC=0+882 RESISTOR 100 5% -125W CC TC=0+588 |

28480

01121 01121 01121 01121 01121 |

0698-8615

881005 C21525 881525 881525 881015 |

|

A 3R 34

A 3R 35 A 3R 36 A 3R 37 A 3R 38 |

0757-0802

0698-3113 0757-0802 0698-3378 0683-1025 |

2

17 2 |

RESISTOR 162 1% -5W F TC=0+-100

RESISTOR 100 5% -125W CC TC=0+588 RESISTOR 162 1% -5W F TC=0+-100 RESISTOR 51 5% -125W CC TC=0+588 RESISTOR 1000 5% -25W CC TC=-400/+800 |

19701

01121 19701 01121 01121 |

MF7C-1/2-T0-162R-F

BB1015 MF7C-1/2-T0-162R-F BB5105 CB1025 |

|

► A 3P 39

A 3R 40 A 3R 41 A 3R 42 A 3R 43 |

0698-3378

0683-1025 0698-3113 0698-3113 0698-6984 |

2 |

RESISTOR 51 5% .25W CC TC=-400/+800

RESISTOR 1000 5% .25W CC TC=-400/+800 RESISTOR 100 5% .125W CC TC=-400/+808 RESISTOR 100 5% .125W CC TC=0+588 RESISTOR 470 5% .125W CC TC=0+882 |

01121

01121 01121 01121 01121 01121 |

BB5105

CB1025 B81015 B81015 B81015 B84715 |

|

A 3R 44

A 3R 45 A 3R 46 A 3R 47 A 3R 48 |

21001788

06832415 0698-6984 21001788 0698-5564 |

41 |

RESISTOR-VAR TRMR 500 DHM 10% C TOP ADJ

RESISTOR 240 5% .25% FC TC=-400/+609 RESISTOR 470 5% .125% CC TC=0+882 RESISTOR-VAR TKMR 500 DHM 10% C TOP ADJ RESISTOR 240 5% .125% CC TC=0+882 |

84048

01121 01121 84048 01121 |

170-501

CB2415 BB4715 170-501 BB2415 |

|

0698-6283

0683-1125 0683-1125 0698-3378 0683-4715 |

8

18 |

RESISTOR 10 5% .125W CC TC=0+588

RESISTOR 1.1K 5% .25W FC TC=-400/+700 RESISTOR 1.1K 5% .25W FC TC=-400/+700 RESISTOR 51 5% .125W CC TC=0+588 RESISTOR 470 5% .25W FC TC=-400/+600 |

01121

01121 01121 01121 01121 01121 |

881005

C81125 C81125 BR5105 CR4715 |

|

A 38.57

A 38.59 A 38.59 to A 38.62 A 35 1 (FOR S1) A 35 2 (FOR S2) A 35 3 (FOR S3) |

0698-3378

0683-4715 0683-5105 05345-60100 1460-0603 05345-60100 1450-0603 05345-60101 5022-3440 |

6

6 1 1 |

RESISTOR 51 51 .125W CC TC=0+588

RESISTOR 470 51 .25W FC TC=-400/+600 RESISTOR 51 OHM 5% WW CF LEVER/SLIDE ASSY SPRING WFRM .014-0D MUW LEVER/SLIDE ASSY SPRING WFRM .014-0D MUW SLIDE ASSY, P.C. SWITCH SPRING, DETENT |

01121

01121 01121 28480 28480 28480 28480 28480 28480 |

885105

C84715 C85105 05345=60100 1460-0603 05345-60100 1460-0603 C5345-60100 15070-3440 |

|

A 354

(FOR S4) A 355 (FOR S5) A 356 (FOR S6) |

05345-60100

1460-0603 05345-60100 1460-0603 05345-60100 1460-0603 |

LEVER/SLIDE ASSY

SPRING WEPM .014-OD MUW LEVER/SLIDE ASSY SPRING WERM .014-OD MUW LEVER/SLIDE ASSY SPRING WERM .014-OD MUW |

28480

26480 28480 28480 28480 26480 28480 |

UD34D-60100

1460-0603 05345-60100 1460-0603 05345-60100 1460-0603 |

|

|

A 35 7

(FOR 57) A 35 8 A 35 5 |

05345-60100

1460-0603 3101-1596 3101-1596 |

2 |

LEVER/SLIDE ASSY

Spring WERM .014-DD MUW Switch-Sl dpdt-ns Mintr 1A 125VAC Switch-Sl dpdt-ns Mintr 1A 125VAC |

28480

28480 28480 28480 28480 |

05345-60100

1460-0603 3101-1596 3101-1596 |

|

A 3U 1

A 3U 2 |

1 826~0088

1826-0088 |

Z |

IC, LIN 114-BIT WINE BAND AMPL

IC, LIN 114-BIT WIDE BAND AMPL |

28480

28480 |

1826-0088

1826-0088 |

| 05345-40002 | 4 | GUIDE (SWITCH TRACK) | 28480 | 05345-40002 | |

| A4 | 05345-60004 | 1 | INPUT TRIGGER ASSY (SERIES 1612) | 28480 | 05345-60004 |

|

A4C1

A4C2 A4C3 A4C4 A4C5 |

0160-3879

0160-3879 0160-3879 0160-3879 0160-3879 0160-3878 |

CAPACITOR-FXD .01UF +-20% 100WVDC CER

CAPACITOP-FXD .01UF +-20% 100WVDC CER CAPACITOR-FXD .01UF +-20% 100WVDC CER CAPACITOR-FXD .01UF +-20% 100WVDC CER CAPACITOR-FXD 1000PF +-20% 100WVDC CER |

28480

28480 28480 28480 28480 28480 |

0160-3879

0160-3879 0160-3879 0160-3879 0160-3878 |

|

|

A4C6

A4C7 A4C8 A4C9 A4C10 |

0160-3878

0160-3878 0160-3878 0160-3878 0160-3878 |

CAPACITOR-FXD 1000 PF +-20% 100WVDC CER

CAPACITOR-FXD 1000 PF +-20% 100WVDC CER CAPACITOR-FXD 1000 PF +-20% 100WVDC CER CAPACITOR-FXD 1000 PF +-20% 100WVDC CER CAPACITOR-FXD 1000 PF +-20% 100WVDC CER |

28480

28480 28480 28480 28480 28480 |

0160-3878

0160-3878 0160-3878 0160-3878 0160-3878 0160-3878 |

|

|

A4C 11

A4C 12 A4C 13 A4C 14 A4C 15 |

0160-3876

0180-0428 0180-0429 0160-3876 0180-0428 |

4 |

CAPACITOR-FXD 47PF +-20% 200WVOC CER

CAPACITOR-FXD; 68UF+-20% 6VDC TA-SOLID CAPACITOR-FXD; 68UF+-20% 6VDC TA-SOLID CAPACITOR-FXD 47PF +-20% 6VDC TA-SOLID CAPACITOR-FXD; 68UF+-20% 6VDC TA-SOLID |

28480

28480 28480 28480 28480 28480 |

0160-3876

0180-0428 0180-0428 0160-3876 0180-0428 |

|

A4C16

A4C17 A4C18 A4C19 A4C20 |

0 180-0428

0160-3876 0160-3878 0160-3879 0160-3879 0160-3876 |

CAPACITOR-FXD; 68UF+-20% 6VDC TA-SOLID

CAPACITOR-FXD 47PF +-20% 200WVDC CER CAPACITOR-FXD 1000PF +-20% 100WVDC CER CAPACITOR-FXD +01UF +-20% 100WVDC CER CAPACITOR-FXD 47PF +-20% 200WVDC CER |

28480

28480 28480 28480 28480 28480 |

0180-0428

0160-3876 0160-3878 0160-3879 0160-3876 |

|

|

A4C21

A4C22 A4C23 A4C24 A4C25 A4CR1 A4CR1 |

0160-3879

0160-3876 0160-3876 0160-3876 0160-3876 1902-0074 |

3 |

CAPACITOR-FXD 1000PF +-20% 100WVDC CER

CAPACITOR-FXD 47PF +-20% 200WVDC CER CAPACITOR-FXD 47PF +-20% 200WVDC CER CAPACITOR-FXD 47PF +-20% 200WVDC CER CAPACITOR-FXD 47PF +-20% 200WVDC CER DIODE-ZNR 7.15V 5% DO-7 PD=.4W TC=+.047% DIODE-ZNR 7.15V 5% DO-7 PD=.4W TC=+.047% |

28480

28480 28480 28490 28490 28480 04713 04713 |

0160-3878

0160-3876 0160-3876 0160-3876 0160-3876 0160-3876 SZ 10939-140 SZ 10939-140 |

NOT IN OPTION 01

See introduction to this section for ordering information

Table 7-5. A3/A4 Parts List (Continued)

| · | |||||

|---|---|---|---|---|---|

|

Reference

Designation |

HP Part

Number |

Qty | Description |

Mfr

Code |

Mfr Part Number |

|

A4CR3

A4CR4 |

1902-3036 | DIODE ZENER 3.16V 5% DO-7.4W | 04713 | SZ 10939-38 | |

| A4L1 | 9100-1788 | 5 | COLL: FXD: NON-MOLOED RE CHOKE: .750H | 04/13 | SZ 10939-38 |

| A4L2 | 9100-1788 | COIL: FXD; NON-MOLDED RF CHOKE: .750H | 02114 | VK200-20/48 | |

| A4L3 | 9100-1788 | COIL: FXD: NON-MOLDED RF CHOKE: .750H | 02114 | VK200-20/48 | |

| A4L5 | 9100-1620 | 2 |

COIL; FXD; NON-MOLDED RF CHOKE; .75UH

COIL-FXD MOLDED RF CHOKE 15UH 10% |

02114

24226 |

VK200-20/48

15/152 |

| A4L 6 | 9100-1620 | COIL-FXD MOLDED RE CHOKE 150H 10% | 76.226 | 15/152 | |

|

44L 7

84L 8 |

9100-0549

9100-0549 |

2 |

COIL-FXD MOLCED RF CHOKE 220H 10%

COIL-FXD MOLDED RF CHOKE 220H 10% |

06560

06560 |

4422-8K

4422-8K |

| A4R1 | 0698-5178 | RESISTOR 1.5K 5% .125W CC TC=0+882 | 01 1 2 1 | BB1525 | |

| A4R3 | 0698-5178 | RESISTOR-VAR TRMR 500 DHM 10% C TOP ADJ | 84048 | 170-501 | |

|

448 4

448 5 |

0698-5178

2100-1789 |

· |

RESISTOR 1.5K 5% .125W CC TC=0+882

RESISTOR-VAR TRMR 500 OHM 10% C TOP ADJ |

01121

84048 |

881525

881525 170-501 |

| A4R6 | 0698-5178 | RESISTOR 1.5K 5% .125W CC TC=0+882 | 01121 | RR1525 | |

| A4P 7 | 0698-3378 | RESISTOR 51 5% +125W CC TC=0+588 | 01121 | B85105 | |

| A4R9 | 0698-3378 | ĺ | RESISTOR 51 5% .125W CC TC=0+588 | 01121 | 885105 |

| A4R10 | 0698-3378 |

RESISTOR 51 5% +125W CC TC=0+588

RESISTOR 51 5% +125W CC TC=0+588 |

01121

01121 |

885105

885105 |

|

|

A 4R 11

A 4F 17 |

2100-3216 | 2 | RESISTOR-VAR TRMR 10KOHM 20% C TOP ADJ | 32997 | 3339H-1-103 |

| A 4P 13 | 2100-3216 | 2 | RESISTOR-VAR TRMP TOKOUN 200 C TOO ACT | 28480 | 0698-8623 |

|

A4R 14

A4R 15 |

0698-8623

0757-0913 |

з | RESISTOR 360 2% .125W F TC=0+-100 |

32997

28480 24546 |

5559H-1-103

0698-8623 C4-1/8-T0-361-G |

| A48 16 | 2100-1984 | 2 | RESISTOR-VAR TRMR 100 OHM 102 C TOP ADI | 84049 | 170=1.01 |

| A4R17 | 0698-5183 | 2 | RFSISTOR 4.3K 5% .125W CC TC=0+882 | 01121 | 884325 |

| A4R19 | 0/5/-0913 | RESISTOR 360 2% .125W F TC=0+-100 | 24546 | C4-1/8-TO-361-G | |

| 44R 20 | 0698-5183 |

RESISION-VAR TRMK 100 OHM 10% C TOP ADJ

RESISTOR 4.3K 5% .125W CC TC=0+882 |

84048

01121 |

170-101

BB4325 |

|

|

A 4 P 21

A 4 R 22 |

0686-6815 | 2 | RESISTOR 680 52 .5W CC TC=0+529 | 01121 | E86815 |

| 44R 23 | 0686-6815 | · ' | RESISTOR 680 5% -5% CC TC=0+529 | 24546 | C4-1/8-T0-201-F |

|

A4R 24

A4R 25 |

0757-0407

0683-1125 |

RESISTOR 200 1% .125W F TC=0+-100

RESISTOR 1.1K 5% - 25W FC TC=-600/+700 |

24546 | C4-1/8-T0-201-F | |

| A48.26 | 0693-1125 | 01121 | |||

| A46.27* | 0683-5105 | 9 | RESISTOR 51 51 52 +25W FC TC=+400/+700 |

01121

01121 |

C81125

C85105 |

| A4F 28 | 2683-1125 |

PESISTORY SELECTED PART

RESISTOR 1.1K 5% .25W FC TC=-400/+700 |

01121 | CB1125 | |

| A4R 29* | 0683-5105 |

RESISTOR 51 5% .25W FC TC=-400/+500

*FACTORY SELFCTED PART |

01121 | CB5105 | |

| A4F 30 | 0683-1125 | RESISTOR 1.1K 58 .25H FC TC=-400/+700 | 01121 | C81125 | |

| A 4R 32 | 0683-4715 |

RESISTOR 51 58 .125W CC TC=0+588

RESISTOR 470 58 .25W EC TC==400/4400 |

01121 | 885105 | |

| A 4P 33 | 0698-3378 | RESISTOR 51 5% .125W CC TC=0+583 | 01121 |

CB4715

BB5105 |

|

| A 4R 34 | 0683-4715 | RESISTOR 470 5% +25W FC TC=+400/+600 | 01121 | C84715 | |

|

A4R 35

A46 36 |

0683=2425 | 4 | RESISTOR 2.4K 5% .25W FC TC=-400/+700 | 01121 | CB2425 |

| A4P 39 | 0698-3111 | 2 | RESISTOR 30 5% +125W CC TC=0++850 | 01121 | |

|

48 40

449 41 |

0698-3111 | _ | RESISTOR 30 5% .125W CC TC=0+-850 | 01121 | BB3005 |

| #4R 42 | 0683-1615 | 2 | RESISTOR 160 52 -254 EC TC==400/4600 | 01121 | 682102 |

|

A 4R 43

A 4P 44 |

0698-3378

0683-1615 |

RESISTOR 51 57 .125W CC TC=0+588

RESISTOR 160 57 .25W FC TC=-400/4400 |

01121 |

885105

681415 |

|

| A401 | 1826-0290 | |,| | IC:AMPLIFIER | 20400 | |

| A4U2 | 1826-0290 | - L | IC:AMPLIFIER | 28480 | 1826-0290 |

|

A4U3

A4U4 |

1826-0021

1826-0021 |

2 |

IC:LM310H

IC:LM310H |

27014

27014 |

LM310H

LM310H |

See introduction to this section for ordering information

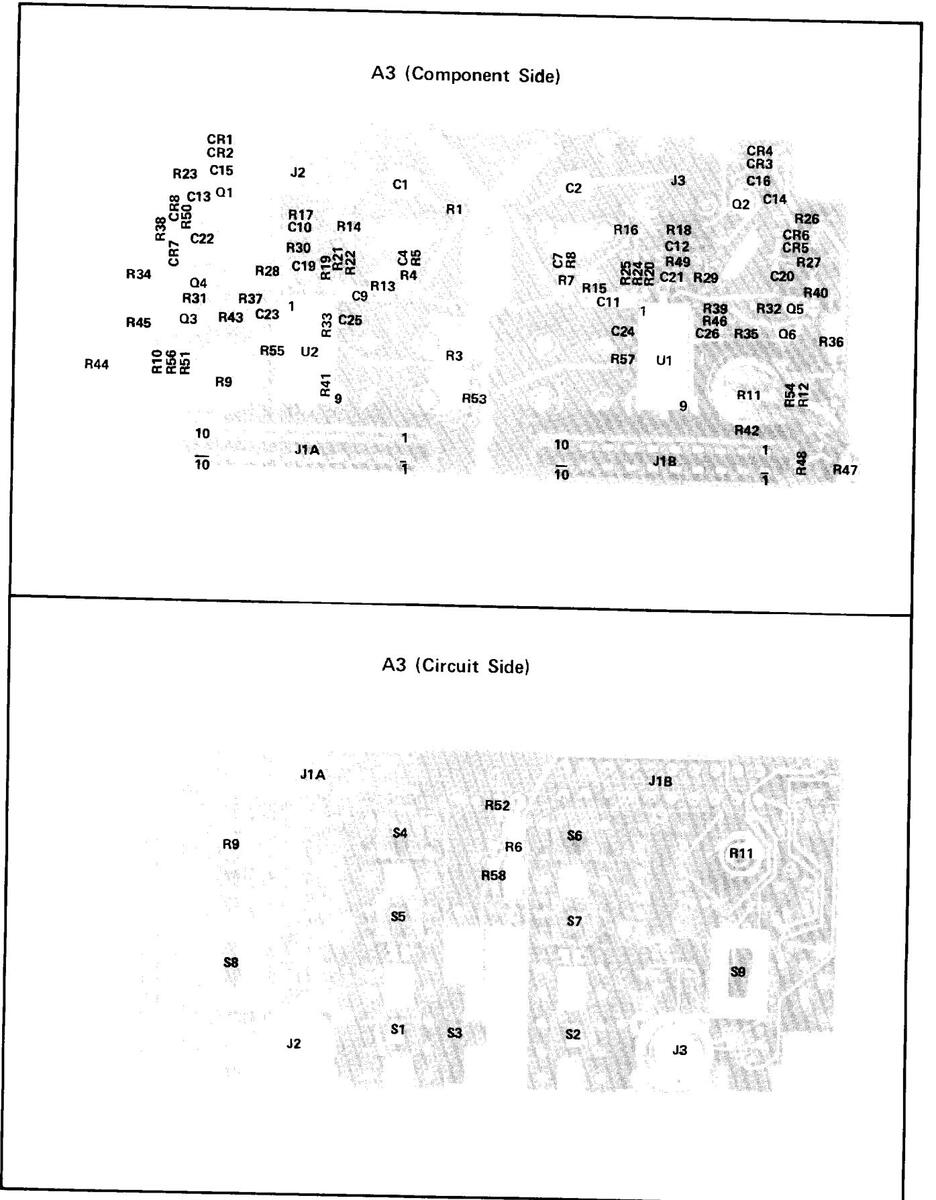

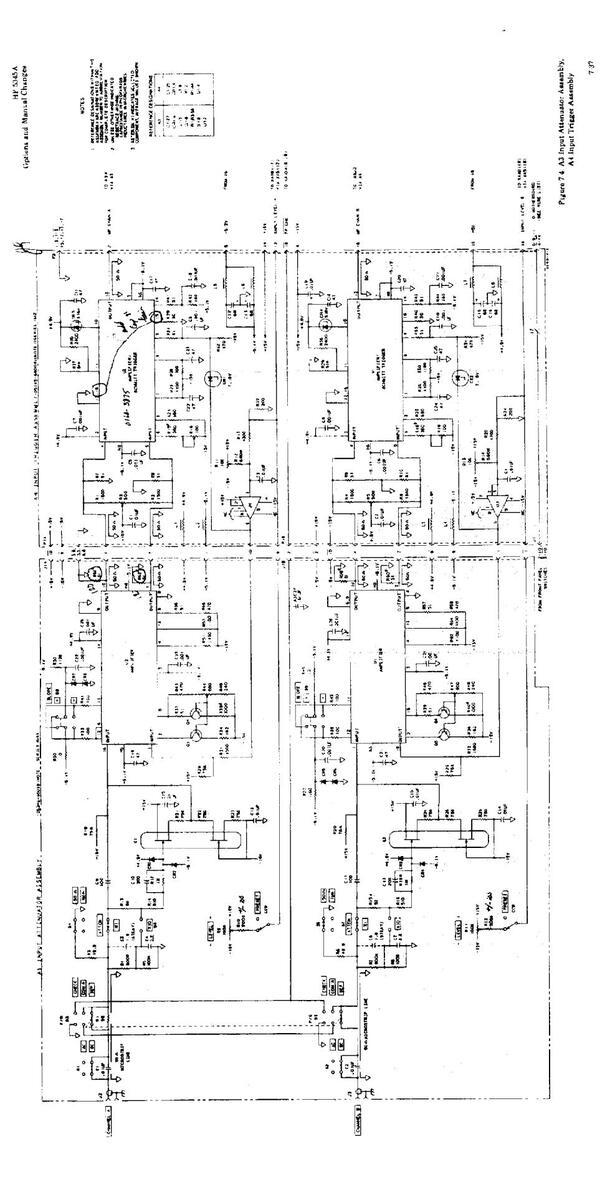

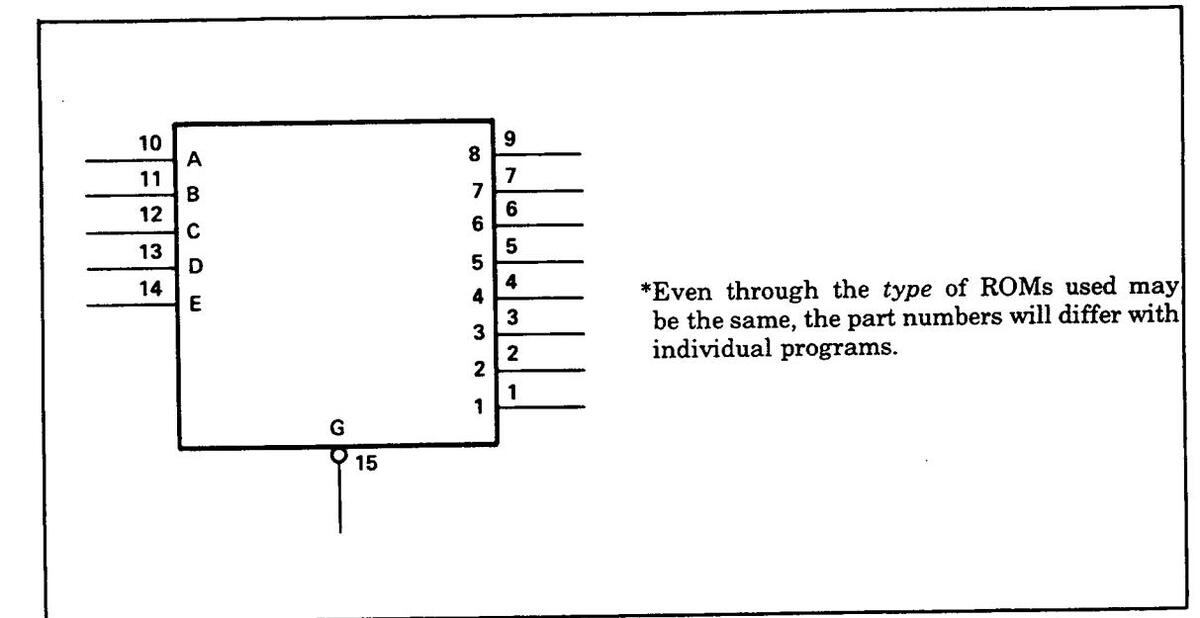

Figure 7-3. A3 Input Attenuator Assembly

VII

Operating and Service Manual

HP 5345A Electronic Counter

HP 5345A ELECTRONIC COUNTER

OPERATING AND SERVICE MANUAL

HP 5345A SERIAL PREFIX: 3103

This manual applies directly to HP 5345A Electronic Counters having serial number prefix 3103.

NEWER INSTRUMENTS

This manual, with enclosed "Manual Changes" sheet, applies to HP 5345A Electronic Counters having serial number prefixes as listed on the "Manual Changes" sheets.

OLDER INSTRUMENTS

For serial prefixes below 3103, refer to Section VII for manual backdating.

©HEWLETT-PACKARD COMPANY 1986, 1994 5301 STEVENS CREEK BLVD, SANTA CLARA, CA 95052-8059

MANUAL PART NUMBER : 05345-90060

Printed: MAY 1994

CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

WARRANTY

This Hewlett-Packard instrument product is warranted against defects in material and workmanship for a period of one year from date of shipment. During the warranty period, Hewlett-Packard Company will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by HP. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

EXCLUSIVE REMEDIES

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

ASSISTANCE

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

TABLE OF CONTENTS

| Section | Title | Page |

|---|---|---|

| I. GE | NERAL INFORMATION | 1-1 |

| - 1-1 | . Description | 1-1 |

| 1-4 | . Instrument Identification and Manual Changes | 1-1 |

| 1-6 | Options | 1-1 |

| 1-8 | . Accessories | 1-1 |

| II. IN | STALLATION | 2-1 |

| 2-1 | . Introduction | 2-1 |

| 2-3 | Unpacking and Inspection | 2-1 |

| 2-5 | Power Requirements | 2-1 |

| 2-7 | Line Voltage Selection | 2-1 |

| 2-1 | 3. Power Cable | 2-2 |

| 2-1 | 5. HP-IB Interface Connections | 2-3 |

| 2-1 | 9. HP-IB Talk/Listen and Address Switches | 2-4 |

| 2-2 | 2. HP-IB Descriptions | 2-4 |

| 2-2 | 4. Repacking for Shipment | 2-4 |

| 2-2 | 6. Environment During Storage and Shipment | 2-4 |

| III. OF | PERATION AND PROGRAMMING | 3-1 |

| 3-1 | . Introduction | 3-1 |

| 3-3 | . Measurement Technique | 3-1 |

| 3-5 | Operating Modes | 3-1 |

| 3-7 | 7. Frequency Mode | 3-1 |

| 3-1 | 0. Period Modes | 3-1 |

| 3-1 | 5. Time Interval Modes | 3-2 |

| 3-2 | 4. Ratio Measurements | 3-3 |

| 3-2 | 9. Totalize Mode | 3-4 |

| 3-3 | 4. Input Triggering | 3-4 |

| 3-3 | 6. Excessive Gate Time | |

| 3-3 | 8. External Arming and Gating | 3-5 |

| 3-4 | 0. External Arming | 3-5 |

| 3-4 | 2. External Gating | 3-6 |

| 3-4 | 7. Time Interval Measurements | 3-6 |

| 3-5 | 1. Display | 3-8 |

| 3-5 | 3. Display Position | 3-8 |

| 3-5 | 5. Asterisk | 3-8 |

| 3-5 | 9. Arm Light | 3-8 |

| . 3-6 | 61. Gate Light | 3-8 |

| 3-6 | 3. Lamp Test | 3-8 |

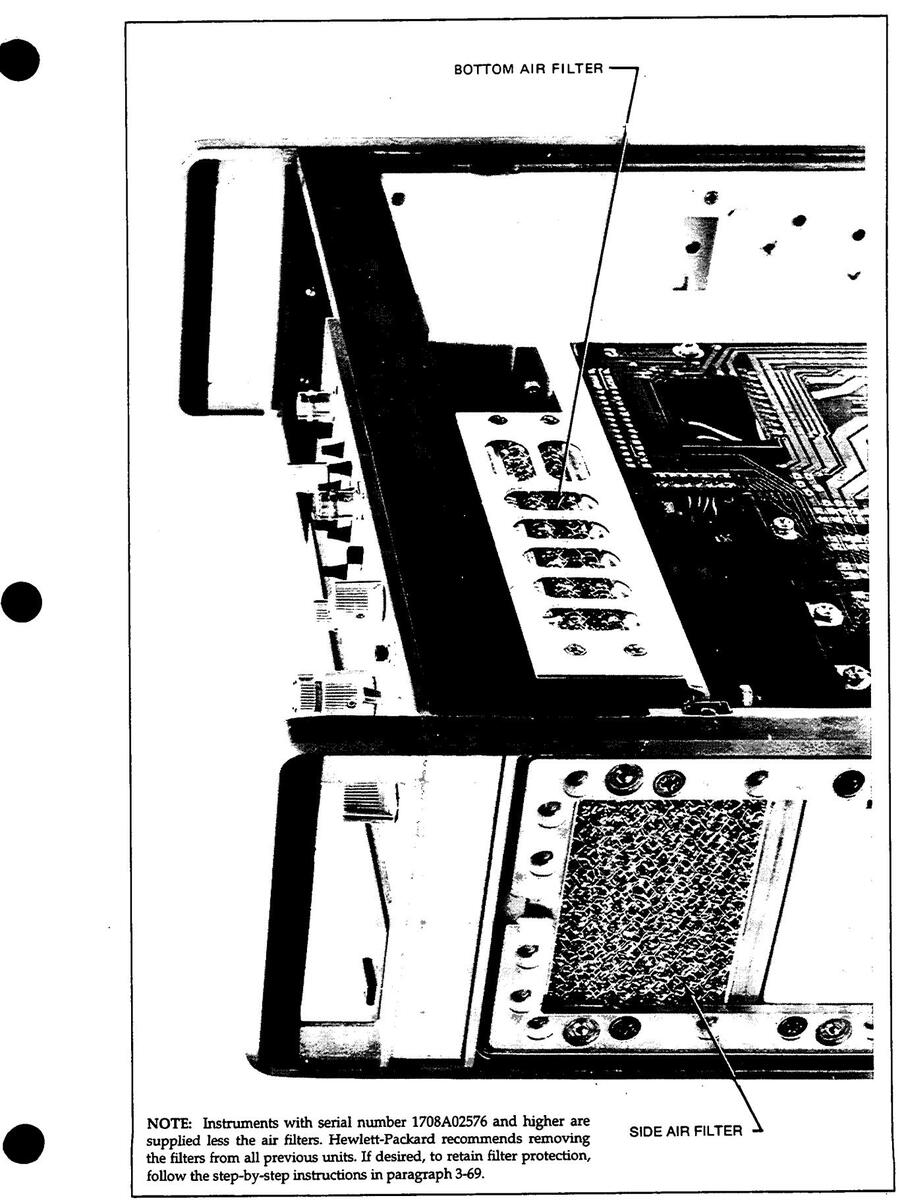

| 3-6 | 6. Cooling | 3-9 |

| 3-6 | Air Filter Cleaning | 3-9 |

| 3-7 | 70. Remote Programming via the Hewlett-Packard Interface Bus | 3-25 |

| 3-7 | 1. Introduction | 3-25 |

| 3-7 | 74. Interface System Terms | 3-25 |

| 3-7 | 6. HP-IB Description | 3-26 |

| 3-8 | 4. HP-IB Control Lines | 3-26 |

| 3-8 | 35. HP-IB Transfer Control Lines | 3-27 |

| 3-8 | 38. Address Selection | 3-27 |

| 3-9 | 01. Addressing the 5345A for Talk and Listen | 3-28 |

| 3-9 | 03. Output Modes | 3-28 |

| 3-9 | 95. Computer Dump | 3-28 |

| 3-9 | 99. Talk Output Mode | 3-29 |

| 3-1 | 01. Programming Commands | 3-29 |

| 3-1 | .04. Program Function Descriptions | 3-29 |

HP 5345A Table of Contents

TABLE OF CONTENTS (Continued)

| Section | Title | Page |

|---|---|---|

| 3-10 | 5. Program Codes and Universal Commands for Option 012 | |

| 3-107 | 7. Modes of Operation | 3-34 |

| 3-110 | ). Starting a Measurement Procedure | 3-35 |

| 3-112 | 2. Programming Examples | 3-35 |

| 3-115 | 5. Example Program 1: Triggering a Measurement | 3-35 |

| 3-117 | 7. Example Program 2: Start/Stop Totalize | 3-36 |

| 3-119 |

|

3-37 |

| 3-121 | Example Program 4: Computer Dump Mode | 3-38 |

| 3-123 | 8. Option 012 Factory Installed Remote Programming | 3-39 |

| 3-126 | 5. Features | 3-39 |

| 3-128 |

|

3-40 |

| 3-130 | ). Example Program: Time Interval Measurements of Pulse Width | 3-40 |

| IV. THE | ORY OF OPERATION | 4-1 |

| 4-1. | Introduction | |

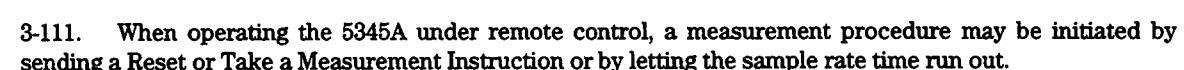

| 4-3 | Logic Elements | 4-1 |

| 4-5. | Logic Levels | |

| 4-7 | Wire-OR/Wire-AND Configuration | 4-2 |

| 4-10 | 4-2 | |

|

4_10.

4_12 |

Integrated Circuits — Theory of Operation |

4-2

4_2 |

|

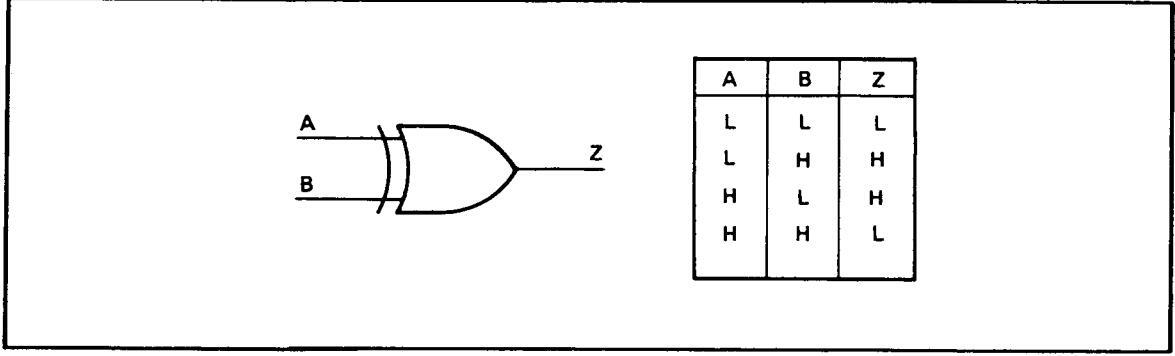

-12.

A_14 |

Synchronous 4-Bit Un/Down Counter 1820-0233 | 4-3 |

| 4-14. | Read-Only Memory (ROM) 1820-0200-0200 | |

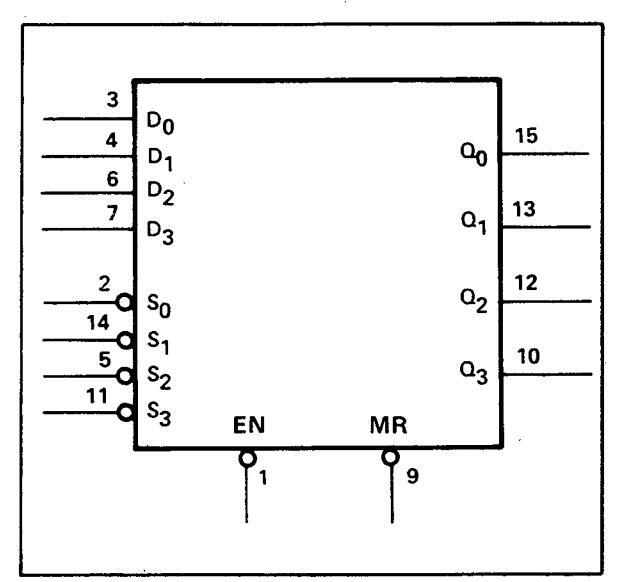

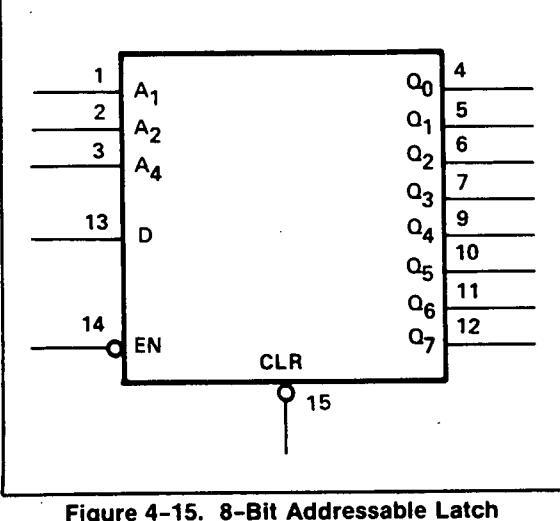

| 4 19 | A Bit Bistable Lateb 1890.0301 | |

| 4-10. | 4-Dit Distable Later, 1020-0501 | |

| 4-20. | Duel Four Input Multiplever 1820-0610 | |

|

4-22.

1.91 |

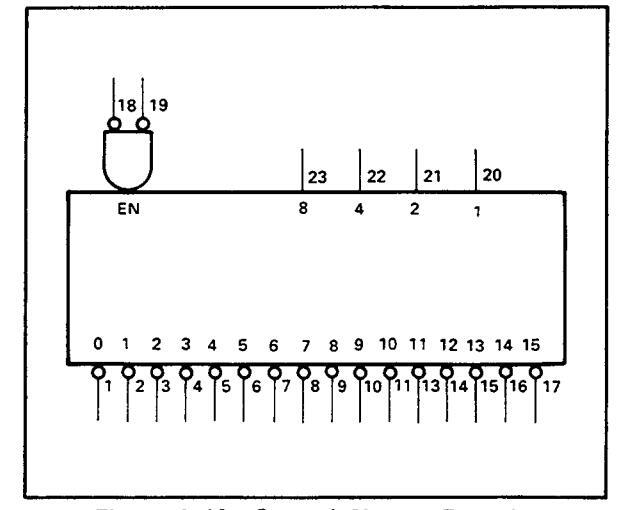

One of Tan Decoder 1820-0627 | |

| 4-24. | MOS Sir Decede Counter, 1820-0624 | |

| 4-20. | Fight Input Multiplever 1820-0658 | |

|

4-20.

4 20 |

Cued Leteh 1820 0701 | |

| 4-00. | Quad Later, 1020-0701 | |

| 4-32. | One-of-Sixteen Decoder, 1020-0702 | |

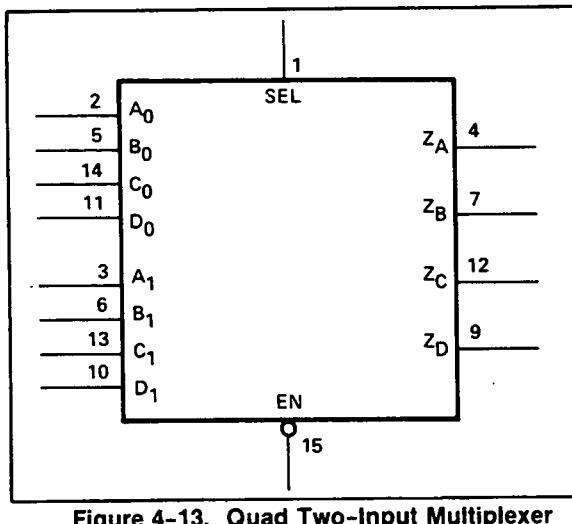

| 4-04. | Quad Two-Input Multiplexer, 1820-0716 | |

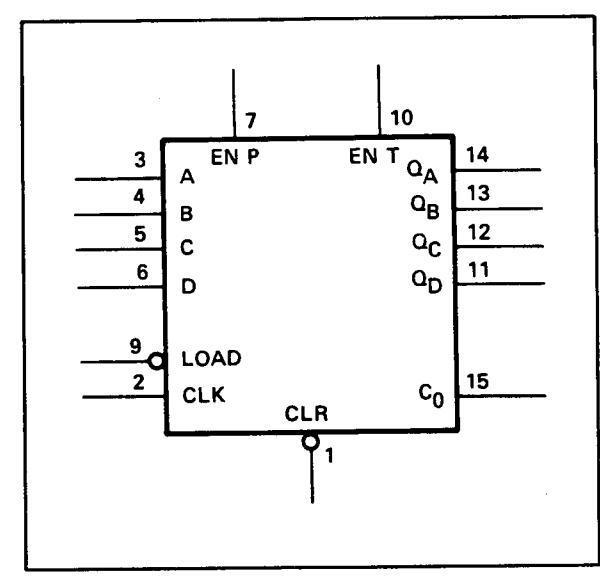

| 4-30. | Synchronous 4-Dit Counter, 1820-0710 | |

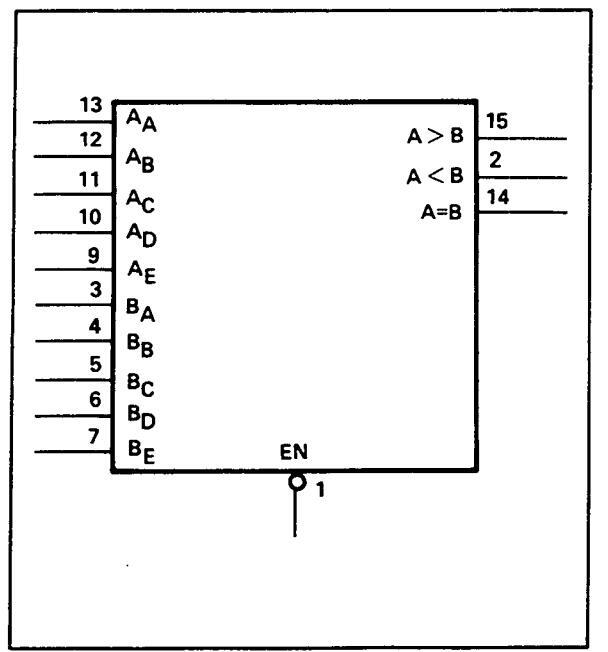

| 4-00. | 5 Bit Compositor 1990 0004 |

4-1

1 0 |

| 4-40. | D-Dit Comparator, 1620-0904 | |

| 4-42. | 04-Bit Read/ while Melliory, 1020-1020 | |

| 4-44. | ||

| 4-40. | ||

| 4-40. | Gale | |

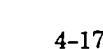

| 4-01. | Scalers | |

| 4-00. | Anulineur Floresson | |

| 4-01. | State Control Section | |

| 4-00. | Oscillator Officials | |

| 4-09 | Circuit Boord Theory | |

| 4-11. | Al and A2 Dimlay Accomplica | |

| 4-13. | A1 and A2 Display Assembles | |

| 4-04. | As input Attenuator | |

|

4-90.

4 00 |

A4 IIIput Ingger |

4-13

4 19 |

|

4-93.

4 05 |

AU FIORI Faller Interconnect | |

| 4-95. | AU DWILCIMING REGULATOR | |

| 4-105 | A DII Multiplice Noice Concenter | |

| 4-110 | AO Main Cata | |

| 4-132 | A 10 Cate Control | |

| 4-140 | ||

| 4-101 | A11 DCalci | |

| 4-170 | 4-40 |

TABLE OF CONTENTS (Continued)

| Section | Title | Page | |

|---|---|---|---|

| 4-196. | A13 Register, Adder/Subtracter | 4-32 | |

| 4-219. | A14 Qualifier | 4-37 | |

| 4-241. | A15 ROM | 4-40 | |

| 4-271. | A16 Motherboard | 4-46 | |

| 4-273. | A17 Plug-In Interconnection | 4-46 | |

| 4-275. | A18 10 MHz Oscillator (Oven) | 4-46 | |

| v. | MAINTE | ENANCE AND SERVICE | 5-1 |

| 5-1. | Introduction | 5-1 | |

| 5-3. | Assembly Designations | 5-1 | |

| 5-5. | Test Equipment | 5-2 | |

| 5-7. | Adjustments and In-Cabinet Performance Check | 5-2 | |

| 5-9. | Periodic Maintenance | 5-2 | |

| 5-11. | Overall Troubleshooting | 5-2 | |

| 5-13. | Trouble Isolation Method | 5-3 | |

| 5-17. | Troubleshooting Aids | 5-3 | |

| 5-21. | Extender Board Kit (10595A) | 5-3 | |

| 5-25. | 5345A Operational Verification | 5-23 | |

| VI. | REPLAC | CEABLE PARTS | 6-1 |

| 6-1. | Introduction | 6-1 | |

| 6-3. | Reference Designations | 6-1 | |

| 6-5. | Replaceable Parts | 6-1 | |

| 6-8. | How to Order a Part | 6-1 | |

| 6-10. | Parts Identification | 6-1 | |

| 6-14. | Contacting Hewlett-Packard | 6-2 | |

| 6-18. | Cabinet Parts and Hardware | 6-2 | |

| VII. | . OPTION | IS AND MANUAL CHANGES | 7-1 |

| 7-1. | Introduction | 7-1 | |

| 7-3. | Options | 7-1 | |

| 7-5. | Field Installation of Options | 7-1 | |

| 7-8. | Manual Changes | 7-1 | |

| 7-10. | Newer Instruments | 7-1 | |

| 7-12. | Older Instruments | 7-1 | |

| VII | I. SCHE | MATIC DIAGRAMS | 8-1 |

| 8.1 | Schematic Diagrams | 8-1 | |

| 8-3. | Schematic Diagram Notes, Assembly Numbers, and Reference Designations | 8-1 | |

| 8-5. | Reference Designations | 8-1 | |

| 8-7. | Identification Markings on Printed-Circuit Boards | 8-1 |

SAFETY CONSIDERATIONS

GENERAL

This is a Safety Class I instrument. This instrument has been designed and tested according to IEC Publication 348, "Safety Requirements for electronic Measuring Apparatus", and has been supplied in safe condition.

OPERATION

BEFORE APPLYING POWER verify that the power transformer primary is matched to the available line voltage and the correct fuse is installed (see Section II, Paragraph 2-6.) Make sure that only fuses with the required rated current and of the specified type (normal blow, time delay, etc.) are used for replacement. The use of repaired fuses and the short-circuiting of fuseholders must be avoided.

SERVICE

Although this instrument has been designed in accordance with international safety standards, this manual contains information, cautions, and warnings which must be followed to ensure safe operation and to retain the instrument in safe condition. Service and adjustments should be performed only be qualified service personnel.

Any adjustment, maintenance, and repair of the opened instrument under voltage should be avoided as much as possible, and when inevitable, should be carried out only by a skilled person who is aware of the hazard involved.

Capacitors inside the instrument may be charged even if the instrument has been disconnected from its source of supply.

Whenever it is likely that the protection has been impaired, the instrument must be made inoperative and be secured against any unintended operation.

ACCOUSTIC NOISE EMISSION:

LpA 56 dB at operator position, at normal operation, tested per EN27779. All data are the results from type test

GERAeUSCHEMISSION:

LpA 56 dB am Arbeitsplatz, normaler Betrieb, Geprueft nach EN277779 Teil 19. Die Angaben beruhen auf Ergenbnissen von Typpruefungen.

WARNING

IF THIS INSTRUMENT IS TO BE ENERGIZED VIA AN AUTO-TRANSFORMER (FOR VOLTAGE REDUCTION) MAKE SURE THE COMMON TERMINAL IS CONNECTED TO THE EARTHED POLE OF THE POWER SOURCE.

WARNING

BEFORE SWITCHING ON THE INSTRUMENT, THE PRO-TECTIVE EARTH TERMINALS OF THE INSTRUMENT MUST BE CONNECTED TO THE PROTECTIVE CONDUCTOR OF THE (MAINS) POWER CORD. THE MAINS PLUG SHALL ONLY BE INSERTED IN A SOCKET OUTLET PROVIDED WITH A PRO-TECTIVE EARTH CONTACT. THE PROTECTIVE ACTION MUST NOT BE NEGATED BY THE USE OF AN EXTENSION CORD (POWER CABLE) WITHOUT A PROTECTIVE CONDUCTOR (GROUNDING).

WARNING

THE SERVICE INFORMATION FOUND IN THIS MANUAL IS OFTEN USED WITH POWER SUPPLIED AND PROTECTIVE COVERS REMOVED FROM THE INSTRUMENT. ENERGY AVAIL-ABLE AT MANY POINTS MAY, IF CONTACTED, RESULT IN PERSONAL INJURY.

CAUTION

BEFORE SWITCHING ON THIS INSTRUMENT:

- 1. MAKE SURE THE INSTRUMENT IS SET TO THE VOLT-AGE OF THE POWER SOURCE.

- 2. ENSURE THAT ALL DEVICES CONNECTED TO THIS INSTRUMENT ARE CONNECTED TO THE PRO-TECTIVE (EARTH) GROUND.

- 3. ENSURE THAT THE LINE POWER (MAINS) PLUG IS CONNECTED TO A THREE-CONDUCTOR LINE POWER OUTLET THAT HAS A PROTECTIVE (EARTH) GROUND. (GROUNDING ONE CONDUCTOR OF A TWO-CONDUCTOR OUTLET IS NOT SUFFICIENT.)

- 4. MAKE SURE THAT ONLY FUSES WITH THE REQUIRED RATED CURRENT AND OF THE SPECIFIED TYPE (NORMAL BLOW, TIME DELAY, ETC.) ARE USED FOR REPLACEMENT. THE USE OF REPAIRED FUSES AND THE SHORT-CIRCUITING OF FUSE HOLDERS MUST BE AVOIDED.

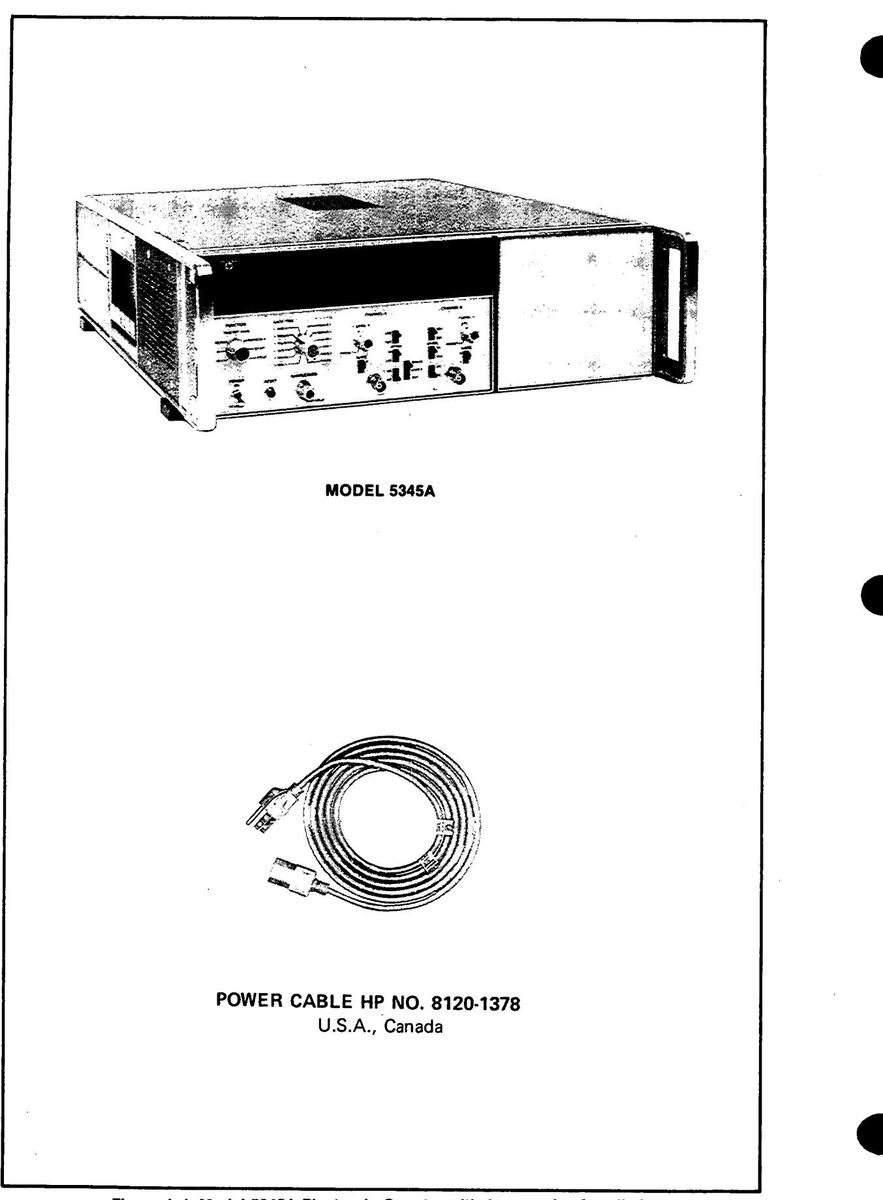

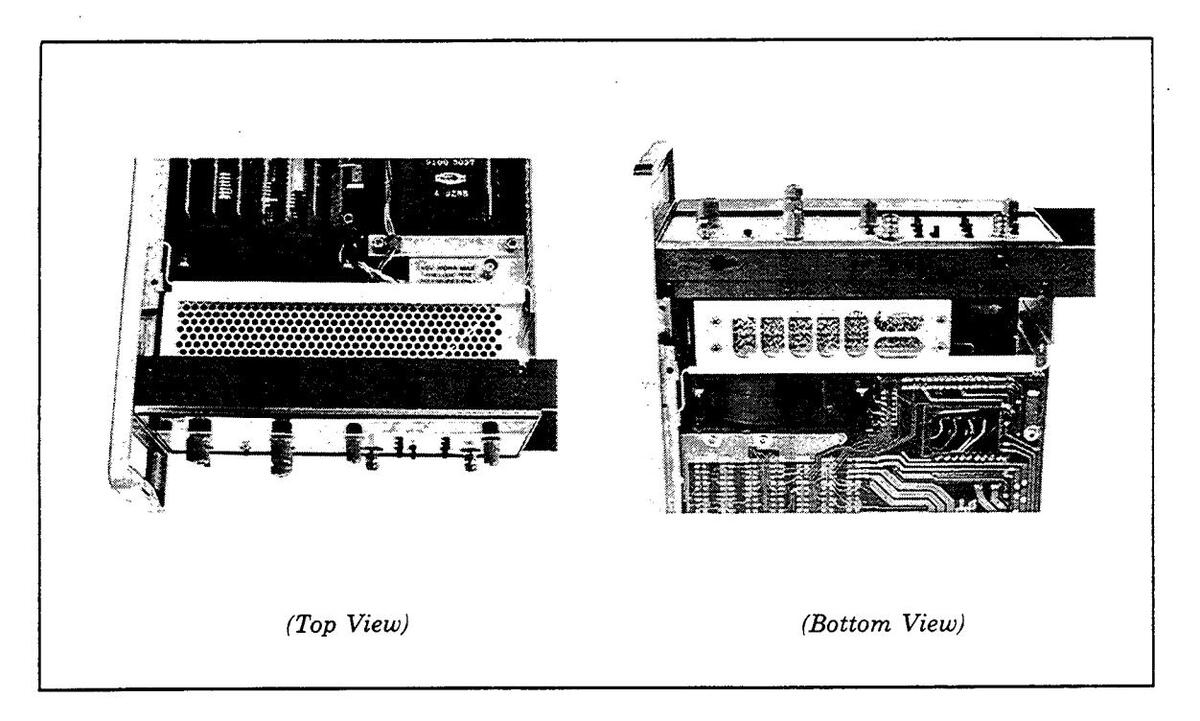

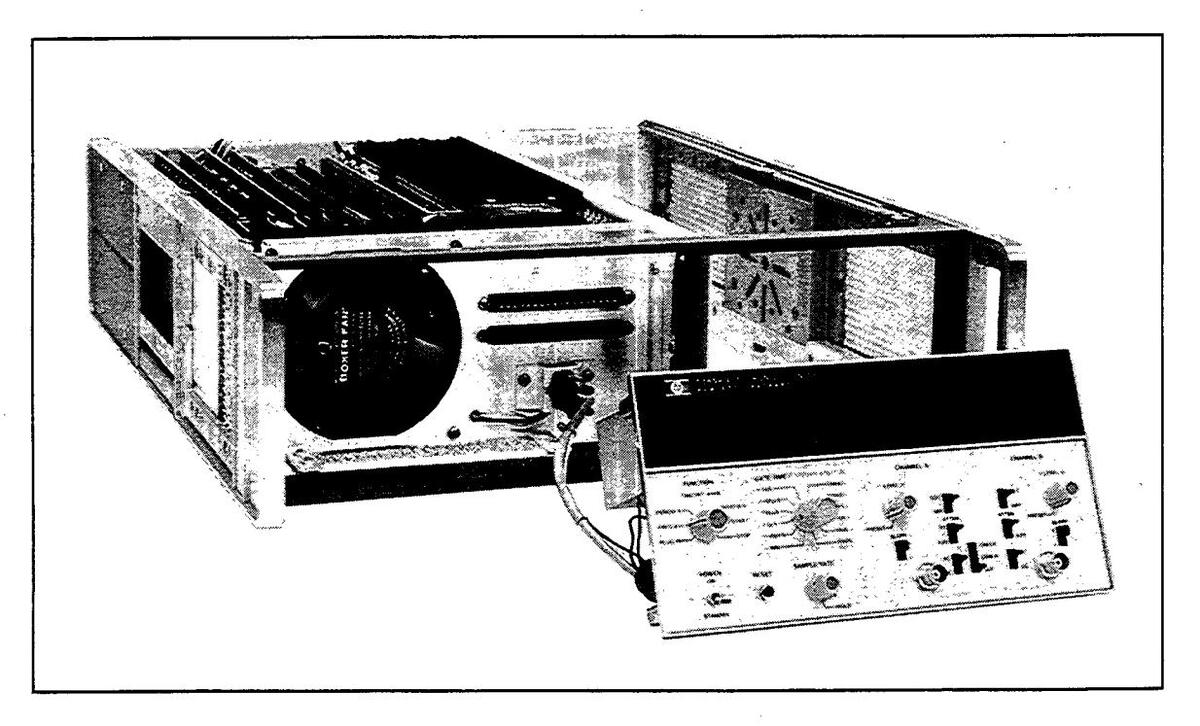

Figure 1-1. Model 5345A Electronic Counter with Accessories Supplied

SECTION I GENERAL INFORMATION

1-1. DESCRIPTION

1-2. The Hewlett-Packard Model 5345A Electronic Counter is a reciprocal counter capable of direct measurements to 500 MHz. The counter's ability to accept plug-in accessories extends its inherent capabilities and provides for a variety of additional measurements.

1-3. The instrument measures frequency, period, period average, single-shot time interval, time interval average, and ratio. It also provides a totalize function, whereby two signals can be simultaneously totalized with the displayed result being the sum of difference in the total number of counts.

1-4. INSTRUMENT IDENTIFICATION AND MANUAL CHANGES

1-5. Hewlett-Packard instruments have a 2-section, 10-character serial number (0000A00000), which is located on the rear panel. The 4-digit serial prefix identifies instrument changes. If the serial prefix of your instrument differs from that listed on the title page of this manual, there are differences between this manual and your instrument. instruments having lower serial prefixes than that listed on the title page are documented in Section VII, and higher serial prefixes are covered with manual change sheets included with the manual. If the manual change sheet is missing, contact the nearest Hewlett-Packard Sales office listed at the back of this manual.

1-6. OPTIONS

1-7. The following is a list of options: Option 011, General Purpose I/O (provides digital output and input control over all functions, except input amplifier); Option 012, similar to Option 011, but includes slope and level control. Option 908, Rack Mounting Kit, is available at an additional cost when ordered at the same time as the instrument.

1-8. ACCESSORIES

1-9. Table 1-1 lists equipment supplied and Table 1-2 list accessories available.

| Table 1-1. Equipment Supplie |

|---|

| DESCRIPTION | HP PART NO. |

|---|---|

| Detachable Power Cord, 231 cm (7½ ft. long) | 8120-1378 |

Table 1-2. Accessories Available

| DESCRIPTION | HP PART NO. |

|---|---|

| Rack Mounting Kit | 5060-8740 |

| Board Extender Kit | 10595A |

| Plug-In Adapter | 10590A |

| 10 MΩ Probe Kit | 10004D |

| 50Ω Probe Kit | 10020A |

1 ATTEXT

Input Characteristics Channel A and Channel R

SEPARATE INPUTS

Dange:

DC coupled: 0 to 500 MHz AC coupled: 1 MΩ. 200 Hz to 500 MHz 50Ω, 4 μ Hz to 500 MHz

Impedance : Switch selectable. 1 MQ (nominal) shunted by approximately 45 pF or 50Ω (nominal).

Sensitivity: (preset) 500 and 1 MO

50Ω DC coupled 0 to 300 MHz, 25 mV rms 300 MHz to 500 MHz, 50 mV rms The to 300 MHz, 25 mVrms 500 A AC couple

300 MHz to 500 MHz 50 mV rms X1: 25 mV rms sine wave 75 mV p-p pulse

X10: 300 mV rms sine wave, 900 mV p-p pulse

Dynamic Range: (preset) 50Ω and 1 MΩ X1: 25 mV to 300 mV rms sine wave 75 mV to 900 mV p-p pulse X10: 300 mV to 2.0V rms sine wave 900 mV to 6.0V p-p pulse

Linear Operating Range: -2.0 to +2.0V dc (nominal)

| Preset: | Centers trigger level to 0V dc (nominal) at 25°C |

|---|---|

| Drift: | ±10 mV dc max., 0°C to 50°C |

| Output: | Channel A & B trigger voltages (X ATTEN) |

| - | available t rear panel BNC connectors. |

| Accuracy: | X1: ±15 mV |

| - | X10: ±150mV (nominal) |

Slope: Independent selection of positive or negative slope.

Maximum Input: Damage may occur beyond specified level. For larger inputs, voltage divider probes 10020A for 50Ω and 10004D for 10MO are recommended

| 50Ω X1: | ±7V dc |

|---|---|

| 7V rms below 5 MHz | |

| 3.5V rms (+24 dBm) 5 MHz and above | |

| X10: | 7V dc, 7V rms (+30 dBm) |

| 1MΩ X1: | ±350V dc |

| 250V rms to 20 kHz, decreasing to 3.5V rms | |

| above 5 MHz | |

| X10: | ±350V dc |

| 250V rms to 20 kHz, decreasing to 35V rms | |

| above 5 MHz |

Cross Talk: No effects if inputs to Channel A and B are both above or below 100 MHz. With one signal above 100 MHz and the other below, there are no effects if the lower frequency has a slew rate of ≥10Vµs.

COMMON INPUT

In this mode the signal is applied to Channel A through a power splitter which equalizes impedances and delays to the input amplifiers. Channel B input is disabled. Both input impedance switches should be in the same position. All specifications are the same as for separate operation with the following differences.

Range

DC coupled: 0 to 400 MHz AC coupled: 1 MQ 300 Hz to 400 MHz AC coupled: 50Ω. 4 MHz to 400 MHz

Impedance: 1 MΩ becomes 500 kΩ shunted by approximately 80 pF. 50Ω no change.

Sensitivity (preset)

50Ω X1: 50 mV rms sine wave, 150mV p-p pulse

- X10. 600 mV rms sine wave, 1.8V p-p pulse

- 1MO DC coupled: 0 to 50 MHz 25 mVrms 50 MHz to 200 MHz. 75 mVrms 200 MHz to 400 MHz 120 mV rms AC coupled: 300 Hz to 50 MHz, 25 mV rms 50 MHz to 200 MHz 75 mV rms 200 MHz to 400 MHz, 120 mV rms

Dynamic Range

- 50Ω X1: 50 mV to 600 mV rms sine wave

-

500 X1 · 150 mV to 1.8V p-p pulse

- X10: 600 mV to 4.0V rms sine wave

- X10: 1.8V to 12V p-p pulse 1 MΩ Same as in SEPARATE

Maximum Input:

- 500: +5 0V dc or 5V ms

- 1 MΩ Same as in SEPARATE

Trigger Level: Adjustable over the range +4 0V dc (X ATTEN) in 50Ω or ±2.0V dc in MΩ (XATTEN).

Trigger Level Output: Channel A and B trigger voltages times 2 (X ATTEN) available at rear panel BNC connectors.

Ассигасу:

50Ω X1: ±30 mV (nominal) X10: +300 mV (nominal) 1 MΩ: Same as in SEPARATE

Frequency/Frequency Average. Period/Period Average

Both frequency and period are measured by measuring the total elapsed time, T, for the integral number of cycles, N of the input waveform. Computation, involving the quantities of N and T. provides direct readout of either frequency or period.

Range: 50µHz to 500 mHz; 2 ns to 20,000 s.

Measurement Time: Consists of GATE TIME plus the time required to reach the next STOP trigger level. When in MIN the GATE TIME is 50 ns or one period of the input signal, whichever is greater. when the GATE TIME is set to one of the decade steps, the counter will reset if a stop trigger is not reached within 3.5 times the GATE TIME setting. Decade GATE TIME settings range from 100 ns to 1000 s.

When using EXT GATE, the measurement cycle time consists of the GATE TIME divided by the duty cycle of the EXT GATE signal plus the time required to reach the next STOP trigger level after the end of the EXT GATE pulse.

Accuracy: Resolution is nine digits per second of measurement time. With the DISPLAY POSITION switch is AUTO the least significant digit error is ±1 count if the most significant digit is 1 through 4, and ±2 counts if the most significant digit is 5 through 9.

Accuracy is ± least significant digit (LSD) counts

± Time Base error × (Frequency or Period)

± Trigger Error * (Frequency or Period).

Time Interval/Time Interval Average

Range: 10 ns to 20.000 s

Minimum Dead Time: 10 ns (nominal)

Dead time is the time between the preceding time interval's STOP event and the current time interval's START event.

Minimum Trigger Pulse Width: 1 ns (typical) width input at minimum voltage input.

Accuracy:

Time Interval:

± Trigger error* ±2ns ± Time Base Error × Time Interval.

Time Interval Averaging:

± Trigger Error * ±2ns Jintervals averaged ±0.7ns ± Time Base Error × T.I. Average.

Not affected by harmonics of clock frequency.

Resolution:

Time Interval: 2 ns

Measurement Time: For single time interval measurement time the GATE TIME switch should be in MIN. Measurement time will be the displayed time interval.

ps

When a decade GATE TIME is selected, the counter will be in the TIME INTERVAL AVERAGE mode. The GATE TIME selected should be greater than the displayed time interval. The measurement time is now the GATE TIME divided by the duty cycle of the time interval waveform plus the time required to reach the next trigger stop level after the total GATE TIME has been accumulated.

seconds rms

*trigger error = Input Voltage slew rate at trigger point(V/s) second

where 150 µV is the typical rms input amplifier noise on the 5345A and en is the rms noise of the input signal for a 500 MHz bandwidth.

Ratio B/A

Range: Both channels accept dc to 500 MHz

Accuracy:

Measurement Time:

Start/Stop

Range: Both inputs may have repetition rates from dc to 500 MHz.

Modes: A. A+B. and A-B is determined by a rear panel switch.

Resolution: Not affected by GATE TIME setting. Resolution is one count up to 11 digits.

Accuracy: Coincident pulses may be applied to both inputs. One count is required to initiate each input, i.e., in Mode A add one count to display, in Mode A+B add two counts to display, in Mode A+B add no counts to display.

Scaling

Range: DC to 500 MHz

Scaling Factor: Selectable by GATE TIME setting. As GATE TIME is varried from the 100 ns position to the 1000 s position, scaling factor increases from 102 to 1012.

10-9SECONDS

Input: Input signal through Channel A

Output: Output frequency equals input frequency divided by scaling factor. Rear panel BNC supplies 80% duty cycle (typical) TTL compatible pulses.

GENERAL

- Display: Eleven-digit LED display and sign. Annunciator displays ks to ns, k to n, μHz to GHz. Decimal point is positioned with DISPLAY POSITION control or positioned after the first, second, or third most significant digit if DISPLAY POSITION is in AUTO. Leading zeros are suppressed.

- Overflow: Asterisk is illuminated when display is overflowed or underflowed.

- Sample Rate: Continuously variable from <0.1s to >5s with front panel control. In HOLD position the last reading is maintained until the counter is manually reset or an EXTERNAL ARM signal is applied. Number of readings per second will generally be limited by the output device, i.e., Printer or Computer.

Measurement Speed:

Normal operation (Max. Sample Rate): Up to 10 readings per second.

Table 1-3. HP 5345A Specifications (Continued)

Externally Armed or Gated: Up to 500 readings per second. Computer Dump: Up to 9000 readings per second.

- External Arm Input: Arming will be initiated by -1.0V (-5.0V max.) into 50Ω rear BNC input for greater than 500 ns. Minimum time between EXT ARM and acceptance of start pulse is <1 µs (typical).

- External Gate Input: EXT GATE feature will respond to a 0.0V pulse into 50Ω with 50 ns or faster rise and fall time pulse edges. Maximum pulse height (damage level) is -5V. Minimum pulse width is 20 ns. Time delay of the leading edge of EXT GATE to the acceptance of input signal is less than 20 ns.

Gate Output: ≥+1 volt into 50 Ω.

Reset: Counter resets at initial turn-on. Can be reset at any time with front panel pushbutton or through HP-IB control.

Operating Temperature: 0°C to 50°C.

Power Requirements: 100/120/220/240V rms +5% to -10%, 48 Hz to 66 Hz, maximum power 250 VA.

Weight: 17 kg (37 lbs.) net.

Size: 132.6 m H x 425 mm W x 495 mm D 5-7/32" x 16-3/4" x 19-1/2").

Time Base:

High Stability Time Base (Standard): 10 MHz (crystal frequency) oven oscillator.

Stability:

- Long Term (Aging Rate):

-

A. <5 x 10-10 per day after 24 -hour warm-up when:

- 1. oscillator off-time was less than 24 hours

- oscillator aging rate was <5 x 10-10 per day prior to turn off.

- B. <5 x 10-10 per day in less than 30 days of continuous operation for off-time greater than 24 hours.

- C. <1 x 10-7 per year for continuous operation.

Warmup:

-

Within 5 x 10-9 of final value (see below) 10 minutes after turnon when:

- oscillator is operated in a 25°C environment with 20 Vdc Oven supply voltage applied.

- 2. oscillator off-time was less than 24 hours.

- oscillator aging rate was <5 x 10-10 per day prior to turnoff

- Final value is defined as oscillator frequency 24 hours after turnon.

- Short Term: <1 x 10-11 for a 1 s average

Temperature: <7 x 10-9, 0°C to 50°C.

Line Voltage: <1 x 10-10, ±10% from nominal (15 min. after change).

- External Frequency Standard Input: 1, 2, 2.5 5, or 10 MHz ±5 x 10-8, with input voltage >1V rms into 1 KΩ.

- Frequency Standard Output: 10 MHz, >1V rms, high purity (<2 x 10-11 for a 1 s average) sine wave from 50Ω source.

- External Frequency Standard Input:, 1, 2, 2.5, 5, or 10 MHz ±5 x 10-5, with input voltage >1V rms into 1KΩ.

Options

- Option 011: Digital Input/Output. Full compatibility with HP interface Bus. Provides digital output as well as input for control over all functions except input amplifier.

- Option 012: Similar to Option 011, but includes slope and level control. Recommended for computer or dedicated calculator applications. Programming codes differ slightly from Option 011.

Option 908: Rack Mounting Kit (P/N 5060-8740).

Option W30: (Extended Hardware Support) provides two additional years of return-to-HP hardware-service support. Option W30 is available only at time of purchase. Service contracts are available from Hewlett-Packard for instruments which did not include Option W30 at time of purchase. For more information, contact your nearest Hewlett-Packard Sales office (offices are listed at the back of this manual).

SECTION II

2-1. INTRODUCTION

2-2. This section contains information for unpacking, inspection, and storage of the HP 5345A Electronic Counter.

2-3. UNPACKING AND INSPECTION

2-4. If the shipping carton is damaged, inspect the instrument for visible damage (scratches, dents, etc.). If the instrument is damaged, notify the carrier and the nearest Hewlett-Packard Sales and Service Office immediately (offices are listed at the back of this manual). Keep the shipping and packing material for the carrier's inspection. The Hewlett-Packard Sales and Service Office will arrange for repair or replacement of your instrument without waiting for the claim to be settled.

2-5. POWER REQUIREMENTS

2-6. The HP 5345A requires a power source of 100, 120, 220, or 240 volts ac at 48 to 66 Hz single phase.

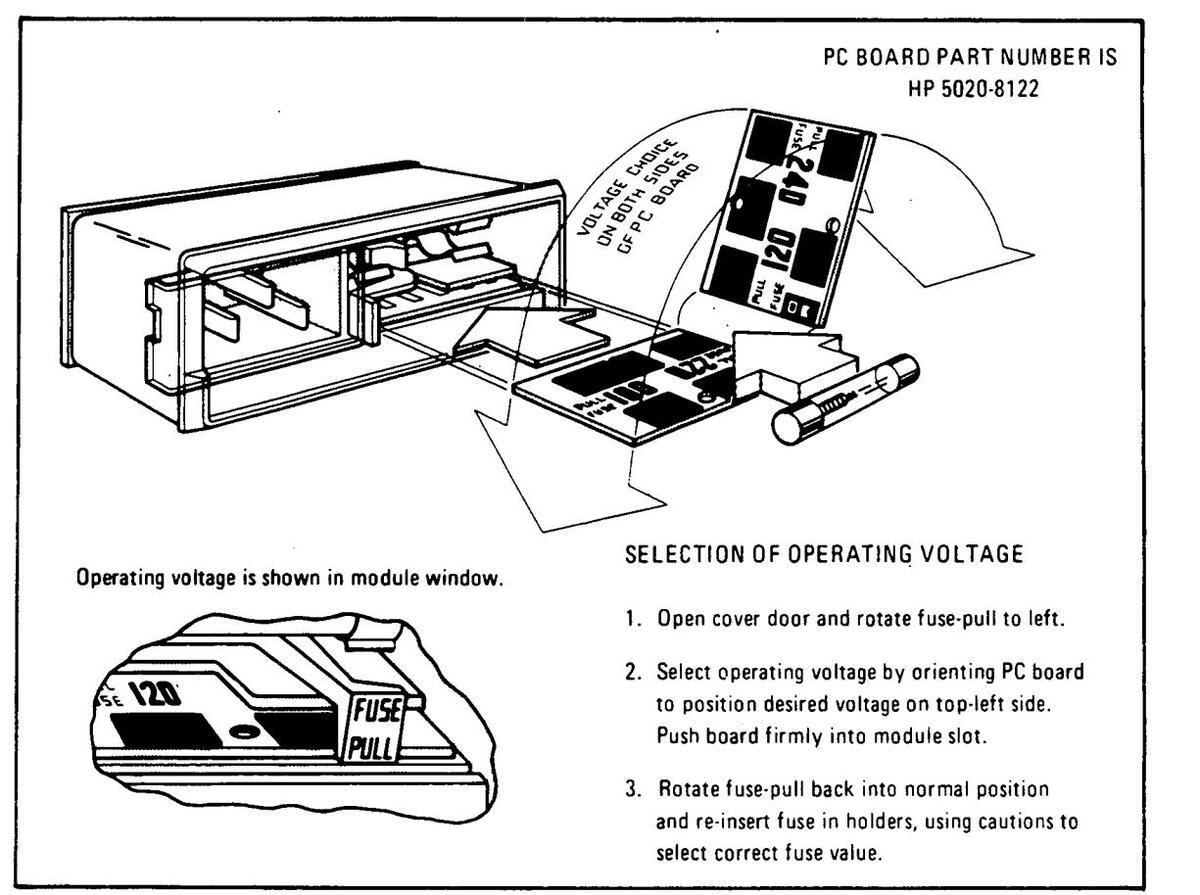

2-7. LINE VOLTAGE SELECTION

2-8. The instrument is equipped with an ac power module that contains a printed-circuit line voltage selector to select 100-, 120-, 220-, or 240-volt ac operation. Before applying power, the voltage selector must be set to the correct position and the correct fuse must be installed as described in paragraphs 2-8 and 2-9.

2-9. Power line connections are selected by the position of the plug-in circuit card in the module. When the card is plugged into the module, the only visible marking on the card indicates the line voltage to be used. The correct value of line fuse must be installed after the card is inserted. This instrument uses a 2.5A time delay fuse for 100/120V operation, and a 1.25A time delay fuse for 220/240V operation.

2-10. To convert from one line voltage to another, the power cord must first be disconnected from the power module. The sliding window covering the fuse compartment can then be moved to expose the fuse and circuit card. See Figure 2-1.

BEFORE CONNECTING THE UNIT TO AC POWER LINES, BE SURE THAT THE CORRECT FUSE IS INSTALLED AND THAT THE VOLTAGE SELECTOR IS PROPERLY POSITIONED AS DESCRIBED BELOW

Figure 2-1. Line Voltage Selection

2-11. Pull on the fuse lever to remove the fuse and then pull the card out of the module. The fuse lever must be held to one side to extract and insert the card. Insert the card so the marking that agrees with the line voltage to be used is visible.

2-12. Return the fuse lever to normal position, insert the correct fuse, slide the plastic window over the compartment, and connect the power cord to complete the conversion.

2-13. POWER CABLE

2-14. To protect the operator, the counter uses a grounded three-conductor power cable. The male connector end is a NEMA type connector, and the female connector end is a C.E.E. type connector that mates with the 5345A rear panel connector. Connect the power cable to a power source receptacle with a NEMA grounded third conductor. If the line power receptacle is a standard two-pin type instead of the NEMA three-pin receptacle, use a two-to-three pin adapter (HP PART No. 1251-0048) and connect the green pigtail on the adapter to ground.

BEFORE SWITCHING ON THIS INSTRUMENT, THE PRO-TECTIVE EARTH TERMINAL OF THIS INSTRUMENT MUST BE CONNECTED TO THE PROTECTIVE CONDUCTOR OF THE (MAINS) POWER CORD. THE PROTECTIVE ACTION MUST NOT BE NEGATED BY THE USE OF A POWER CORD EXTENSION CABLE WITHOUT A PROTECTIVE GROUNDING (EARTHING) CONDUCTOR.

2-15. HP-IB INTERFACE CONNECTIONS

2-16. HEWLETT-PACKARD INTERFACE BUS. The counter with HP-IB is compatible with the Hewlett-Packard Interface Bus. Interconnection data concerning the rear panel connector is provided in Figure 2-2. This connector is compatible with the HP 10833A/B/C/D cables. (See Table 2-1 for cable descriptions). The HP-IB system allows interconnection of up to 15 (including the controller) HP-IB compatible instruments.

| MODEL NUMBER | |

|---|---|

| 10833A | 1 metre (3.3 ft.) |

| 10833B | 2 metres (6.6 ft.) |

| 10833C | 4 metres (13.2 ft.) |

| 10833D | 0.5 metres (1.6 ft.) |

| Table | 2-1. | HP-IB | Cable | Descriptions | |

|---|---|---|---|---|---|

Figure 2-2. Hewlett-Packard Interface Bus Connection

2-17. The HP-IB cables have identical "piggy-back" connectors on both ends so that several cables can be connected to a single source without special adapters or switch boxes. System components and devices may be connected in virtually any configuration desired. There must, of course, be a path from the calculator (or controller) to every device operating on the bus. As a practical matter, avoid stacking more than three or four connectors on any one connector. If the stack gets too large, the force on the stack produces great leverage which can damage the connector mounting. Be sure each connector is firmly (finger tight) screwed in place to keep it from working loose during use.

2-18. CABLE LENGTH RESTRICTIONS. To achieve design performance with the HP-IB, the proper voltage levels and timing relationships must be maintained. If the system cable is too long, the lines cannot be driven properly, and the system will fail to perform properly. Therefore, when interconnecting an HP-IB system, it is important to observe the following rules:

- a. The total cable length for the system must be less than or equal to 20 metres (65.6 feet).

- b. The total cable length for the system must be less than or equal to 2 metres (6.6 feet) times the total number of devices connected to the bus.

- c. The total number of instruments connected to the bus must not exceed 15.

2-19. HP-IB TALK/LISTEN AND ADDRESS SWITCHES

2-20. The HP 5345A provides a rear panel HP-IB TALK/LISTEN selection switch. This switch determines the mode of remote operation as "Talk Only" or "Addressable".

2-21. The ADDRESS switches on the counter rear panel are used to manually set the remote control address of the counter. The addresses 20 and 21 are reserved for the controller, and only even numbered addresses may be programmed because the counter A1 bit has been internally tied low. Odd numbered addresses are used to access computer dump mode which will be discussed in Section III.

2-22. HP-IB DESCRIPTIONS

2-23. A description of the HP-IB is provided in Section III of this manual. A study of this information is necessary if the user is not familiar with the HP-IB concept. Additional information concerning the design criteria and operation of the bus is available in IEEE Standard 488-1978, titled "IEEE Standard Digital Interface for Programmable Instrumentation" .

2-24. REPACKING FOR SHIPMENT

2-25. If it becomes necessary to reship the counter, good commercial packing should be used. Contract packaging companies in many cities can provide dependable custom packaging on short notice. Instruments should be packed securely in a strong corrugated container (350 lb./sq. inch bursting test) with suitable filler pads between the instrument and container. The 4-corner support is not adequate, the counter must also have center support. Before returning instruments to Hewlett-Packard, contact the nearest Hewlett-Packard Sales and Service Office for instructions.

2-26. ENVIRONMENT DURING STORAGE AND SHIPMENT

2-27. Conditions during storage and shipment should normally be limited as follows:

- a. Maximum altitude: 25,000 feet.

- b. Minimum temperature: -40°FF (-40°C).

- c. Maximum temperature: +167°F (+75°C).

SECTION III OPERATION AND PROGRAMMING

3-1. INTRODUCTION

3-2. Section III contains operating and programming information that is helpful in realizing the best performance from the instrument. This includes a general description of the operating modes, the function of controls and indicators, operator's maintenance, a self-check procedure, setup procedures for making basic measurements, and remote programming instructions.

3-3. MEASUREMENT TECHNIQUE

3-4. The counter uses a period average technique to make measurements. The counts (or pulses) that are generated from the input and time base signals are collected in separate scalers during the measurement time. The counter compares these pulses arithmetically and displays the result on the front panel.

3-5. OPERATING MODES

3-6. The following paragraphs describe the operating modes for frequency, period, time interval, ratio, and totalize measurements.

3-7. Frequency Mode

3-8. Channel A accepts input frequencies from 50 µHz to 500 MHz with a minimum level of 25 mV rms sine wave. These frequencies are counted directly with no prescaling techniques applied. Extended frequency capability is available with the use of plug-ins. The counter is capable of measuring pulsed RF in either a single burst or an average of several bursts. The measurement time within the burst may be varied in length and position for detecting frequency variations within a burst.

3-9. The measurement time is the selected gate time plus the time until the next trigger pulse occurs. For example, if the selected gate time is 1 ms, the event gate will close on the next trigger after 1 ms has elapsed. If the input frequency were 20 kHz (.05 ms period), the measurement time would be 1 ms + .05 ms = 1.05 ms. The difference encountered does not affect the accuracy of the measurement.

3-10. Period Modes

3-11. Two modes of period measurements are available: single period and period average. These modes are described in the following paragraphs.

3-12. SINGLE PERIOD. Single period measurements are made with with the GATE TIME switch set to MIN. In this position, the gate time is one period or 50 ns, whichever is greater. Therefore, the input frequency range for a single period measurement is 50 µHz to 20 MHz. Frequencies greater than 20 MHz may be applied, but they will be averaged during a 50 ns gate time.

3-13. PERIOD AVERAGE. When the GATE TIME switch is set to any other position than MIN, the counter averages multiple periods. Averaging increases the accuracy and resolution of the measurement. Input frequencies are in the 50 µHz to 500 MHz range. The actual gate time is determined in the same manner as that described under Frequency Mode.

3-14. Number of Periods Averaged. To determine the number of periods averaged during a measurement, divide the displayed answer into the selected gate time.

Example: Gate Time setting (sec) =

The number of periods averaged will always be a whole number. Therefore, should the calculated answer contain any digits to the right of the decimal point, drop these digits and increment the remainder by one. This is due to the extended gate time. The answer for this example, then, is 49 periods averaged.

3-15. Time Interval Modes

3-16. The counter measures time intervals from Channel A to Channel B; that is, Channel A starts the measurement and Channel B stops the measurement. Time between points on a single waveform can be measured by connecting the input signal to CHANNEL A jack and placing the Input Amplifier Control switch to COM A. Under these conditions, the slope and level controls of Channel A and Channel B allow variable triggering on either the + or - slope. With the Input Amplifier Control switch set to SEP, measurements can be made between points on separate waveforms.

3-17. SINGLE TIME INTERVALS. Single time intervals down to 10 ns are measured with the GATE TIME switch set to MIN. The gate time is one time interval for repetition rates of less than 20 MHz. Thus, if two or more time intervals occur within 50 ns, they will be averaged.

3-18. TIME INTERVAL AVERAGE. The counter averages multiple time intervals when the GATE TIME switch is set to any position other than MIN. The maximum repetition rate is 50 MHz (10 ns time interval plus 10 ns deadtime = 20 ns period or 50 MHz). To average, the time interval must be less than the selected gate time.

NOTE

If the time interval is greater than the gate time, but not more than 3.5 times greater, a single period will be measured. The MIN gate time position is preferred for single periods.

3-19. When averaging, white noise modulates the internal clock signal to prevent any harmonic relationship between the input signal and the clock. This increases the measurement accuracy. The noise is not generated when the GATE TIME switch is set to MIN.

3-20. INITIATING A MEASUREMENT. The front-panel ARM and GATE lights and the rearpanel dc trigger levels are helpful when setting up a time interval measurement. Place the GATE TIME switch to 100 µs. The ARM light is an indication that Channel A is not triggering, possibly due to insufficient signal amplitude or misadjusted front-panel controls. A flashing GATE light indicates that Channel A is triggering. If the counter is gating and lamp test (paragraph 3-63) is flashing or appears to be steady, the counter has gone into excessive gate time (paragraph 3-36). This means the counter has reset because Channel B was not triggered with a stop signal. This could be caused by the stop pulse failing to arrive until after the maximum allowable time, which is 3.5 times the selected gate time. In this case, increase the gate time. Other causes could be insufficient signal amplitude or misadjusted front-panel controls.

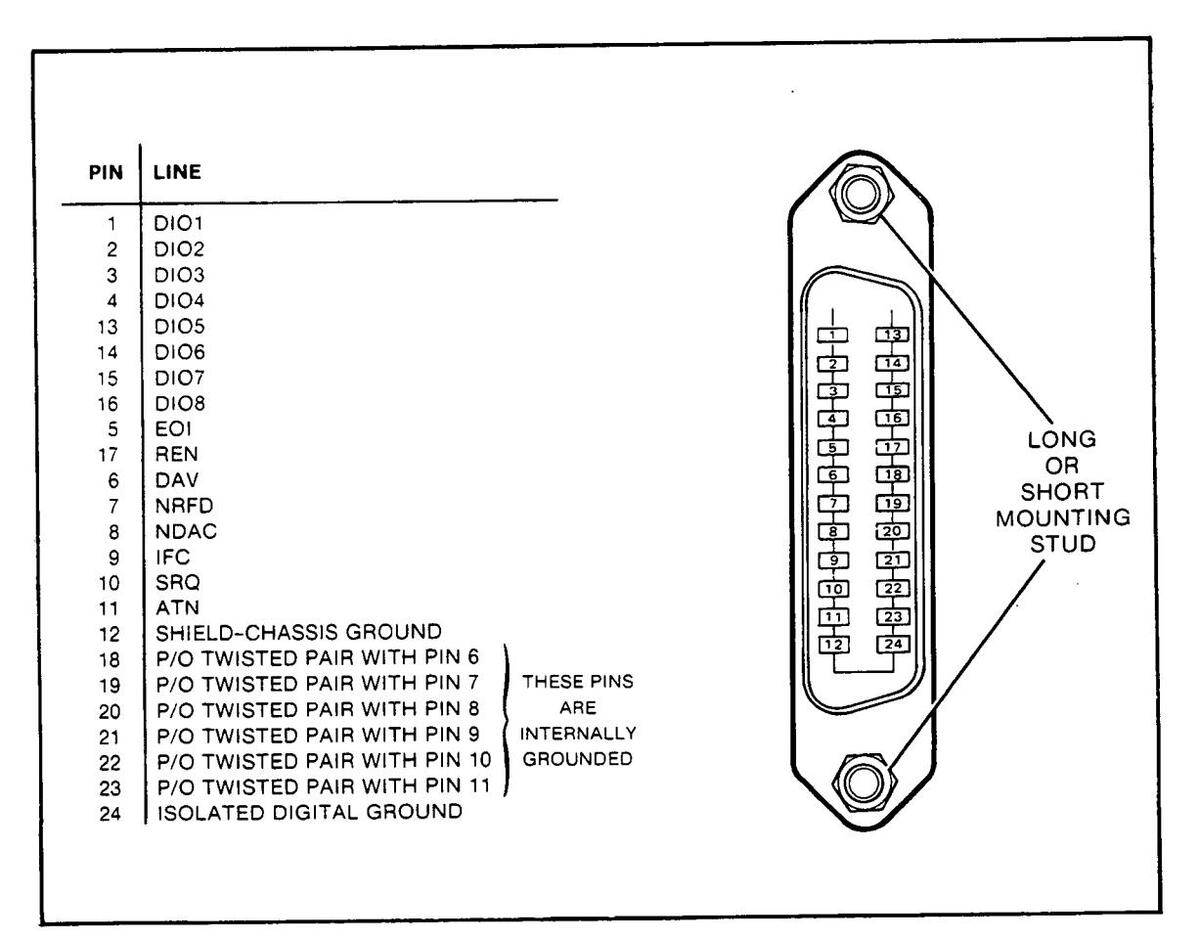

3-21. MEASUREMENT TIME. In time interval average, the time needed to complete a measurement may be much longer than the selected gate time. This is because the counter collects a gate time's worth of time intervals . The factors which would increase the measurement time are short time intervals and extended time between intervals (see Figure 3-1).

3-22. Occasionally, when increased resolution is needed, it may be convenient to estimate the total time of a measurement. To calculate this, use the equation below.

| Measurement | Time = | Gate Time (sec) | ||||

|---|---|---|---|---|---|---|

| Time Interval (sec) X Number of Time Intervals per sec | ||||||

| Example: | 1 msec | =_ | 1 X 10 -3 sec | = 12.5 seconds | ||

8 X 10-5

100 ns X 800/sec

Figure 3–1. Measurement Time for Time Interval Average

3-23. If the time interval used in the equation is unknown, it can be obtained from the counter by selecting MIN. The number of time intervals per second can be taken from an oscilloscope reading. For most purposes, these figures need be only approximate to give a reasonable indication of the waiting time involved.

3-24. Ratio Measurements

3-25. The ratio between two frequencies (FB/FA) is measured by connecting one signal to Channel A and the other to Channel B. Both channels operate in the 50 µHz to 500 MHz range. If the higher frequency is connected to Channel B, the ratio will be greater than one. The answer for a ratio measurement is a unitless figure.

3-26. MEASUREMENT TIME. The difference between the selected gate time and the total measurement time depends on the frequency applied to Channel B. In the Ratio mode, the Channel B signal substitutes for the internal 500 MHz time base.

3-27. With the GATE TIME switch set to 1 s, for example, 5 X 108 time base counts are needed to end the measurement. When the 500 MHz internal time base is used, the 5 X 108 counts are accumulated in 1 second. If, for example, 70 MHz were applied to Channel B and used as the time base, it would take about 7 times as long (7.14 seconds) to accumulate the 5 X 108 counts needed to disarm the gate.

3-28. To estimate the measurement time, use the equation below.

Measurement Time = 5 X 108 Hz X Gate Time Channel B Freq.

Example: 5 X 108 Hz X 1 ms = 5 X 108 X 1 X 10-3 sec = 20 ms

3–3

3-29. Totalize Mode

3-30. The START and STOP positions on the FUNCTION switch allow manual opening and closing of the counter's main gate. The Input Amplifier Control switch must be placed in SEP. When the switch is in the START position, the counter totalizes the number of times the input signal passes through the Channel A trigger point. The GATE TIME switch does not affect the displayed result in any way.

3-31. BOTH CHANNELS TOTALIZED. When the Input Amplifier Control switch is set to SEP, Channel A and Channel B signals can be totalized simultaneously. The displayed result is a function of the ACCUM MODE START/STOP switch, located on the rear panel. The two signals are added (A+B) or subtracted (A-B), depending on the switch position. When the Input Amplifier Control switch is set to CHECK, the counter always selects A+B.

3-32. A minus sign on the display indicates that during a subtraction (A-B) the B events have outnumbered the A events. With the switch in A-B, the instrument functions like an up-down or reversible counter. That is, the counter will count down from a previously-given positive number. As an example of this, assume that the A frequency is greater than the B frequency and the switch is in A-B. The display accumulates positive numbers at a rate equal to the difference between the two input frequencies. If the frequency of B now becomes greater than A, the displayed count will decrease towards zero, again, at a rate equal to the difference between the two frequencies. Once the declining number passes through zero, the minus sign lights and the display continues to accumulate.

3-33. SCALED OUTPUT. With the FUNCTION switch set to START and SAMPLE RATE to HOLD, the counter scales (divides) the Channel A input frequency by powers of 10. This scaled signal is available on the rear-panel CHAN A SCALER OUTPUT jack. Although the display is not functioning, the counter is accumulating. The GATE TIME switch controls the division factor, as shown in Table 3-1.

| GATE TIME SETTING | SCALING FACTOR | SCALED OUTPUT (100 MHz IN OR CHECK) |

|---|---|---|

|

100 ns

1 μs 10 μs 100 μs 1 ms 10 ms 100 ms 1 s 100 s 1000 s |

10

2

10 3 10 4 10 5 10 6 10 7 10 8 10 9 10 10 10 11 10 12 |

1 MHz

100 kHz 10 kHz 1 kHz 100 Hz 10 Hz 1 Hz 100 mHz 10 mHz 1 mHz 100 μHz |

Table 3-1. Scaler Output for Channel A

3-34. INPUT TRIGGERING

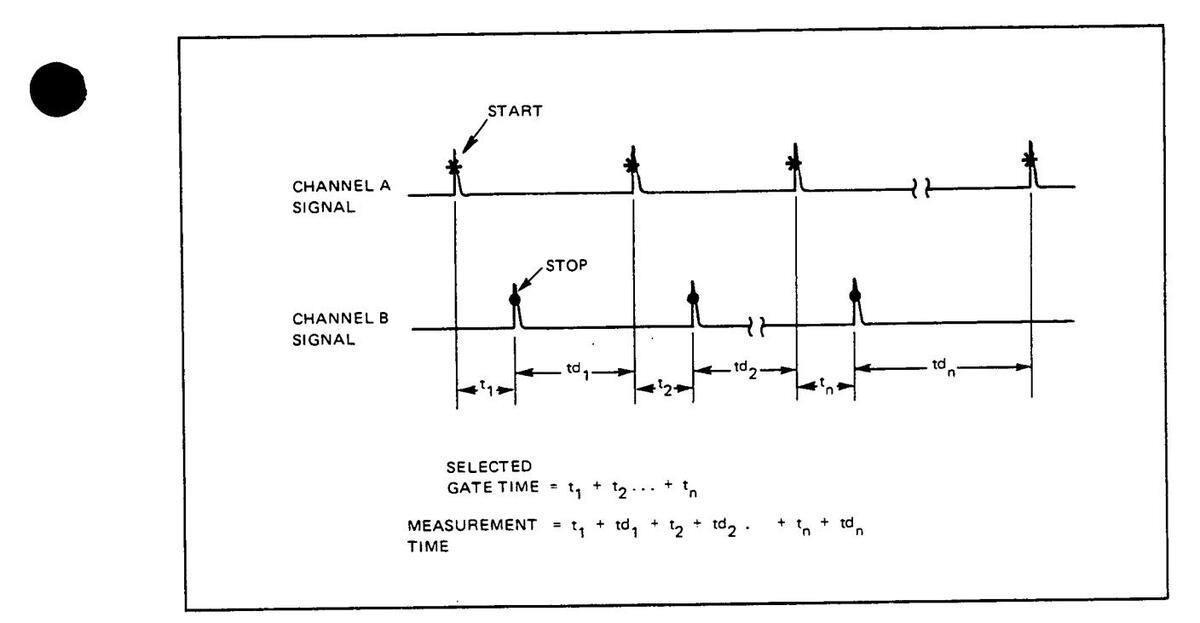

3-35. The input circuits provide triggering over a range of -2.0V to +2.0V. The point at which triggering occurs is adjustable with the front-panel LEVEL control. Each input channel has a small amount of hysteresis (about 10 mV). If the SLOPE switch is set to "+," the trigger pulse occurs at the top of the hysteresis window . If the SLOPE switch is set to "-," the pulse occurs on the bottom line of the window. In other words, the signal must pass through the entire hysteresis window before a trigger pulse is generated (see Figure 3-2). The LEVEL control must be placed to allow at least a 1 ns pulse width for the Schmitt Trigger.

Figure 3-2. Internal Triggering

3-36. EXCESSIVE GATE TIME

3-37. In every measurement involving a gate time, the counter depends on the input signal to terminate the measurement. The measurement concludes one clock pulse after the next input pulse following the end of the gate time, not with the gate time itself. If the period of the input signal is much longer than the gate time or if the signal is interrupted sometime during the gate time, the excessive gate time circuits prevent the counter from waiting indefinitely for the terminating pulse. The counter will wait for about 3.5 times the selected gate time before resetting. At the end of excessive gate time, the display will flash instantaneously to lamp test before displaying all zeros. Excessive gate time is especially useful during the time interval measurement; see paragraph 3-20 for a further description.

3-38. EXTERNAL ARMING AND GATING

3-39. The GATE CONTROL INPUT jack (rear panel) allows the counter to be externally armed and gated. The jack works in conjunction with the Gate Control switch, located directly below the jack.

3-40. External Arming

3-41. When externally arming, set the Gate Control switch to EXT ARM and the SAMPLE RATE switch to HOLD. The counter will ARM when the instrument is first turned on because of the internal arming of the sample rate circuits. After the first measurement, however, the counter's arming circuits are fully controlled by the external source. The counter is armed within 1 µs of receiving the arm pulse (500 ns to dc at -1V). Once the counter is armed, the measurement begins with the first Channel A trigger pulse. The counter makes only one measurement for each arm pulse.

3-42. External Gating

3-43. When the Gate Control switch is set to EXT GATE, the counter's arming and gating is under full external control. The gating can be accomplished in two ways: single gating or multiple gating.

3-44. SINGLE PULSE GATING. Single gating is accomplished with a single, external gate pulse. The width of this pulse can be varied from 20 ns to 20,000 seconds. When using a single gate, set the GATE TIME switch to MIN. This assures the measurement will always take place during a single, external gate pulse. This will not be true for other settings of the GATE TIME switch.

3-45. MULTIPLE PULSE GATING. This method requires an arming pulse, which is automatically taken from the external gate pulse train. When the GATE TIME switch is in any position other than MIN, the counter accumulates as many external gate pulses as are needed to equal or exceed the gate time selected by the switch. As an example, assume a GATE TIME setting of 10 ms and external gate pulses of 4 ms. The counter requires three of these pulses before a measurement can be completed. The total gate time is 12 ms.

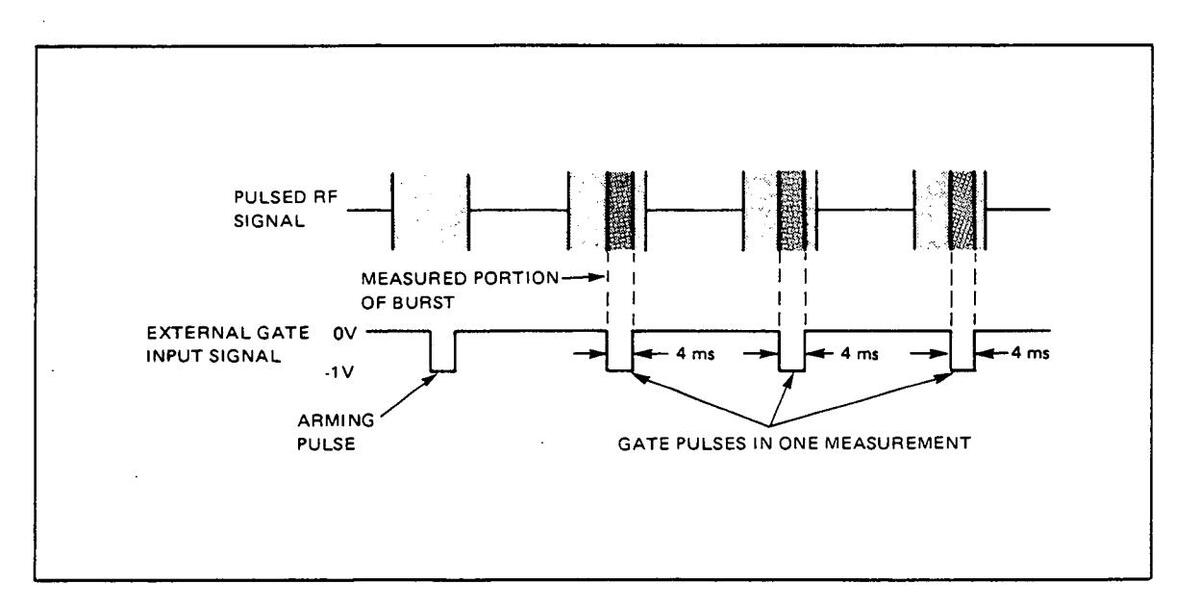

3-46. One of the uses of multiple gating is frequency averaging , i.e., an average of frequency measured over multiple bursts. Using the same values as above, Figure 3-3 shows the type of gating in frequency averaging.

Figure 3-3. Multiple Gating

3-47. Time Interval Measurements

3-48. External gating is valuable when measuring the time between two events while ignoring the events occurring between them. The external gate signal must go low (-1 V) before the start pulse and return high (0 V) before the stop pulse.

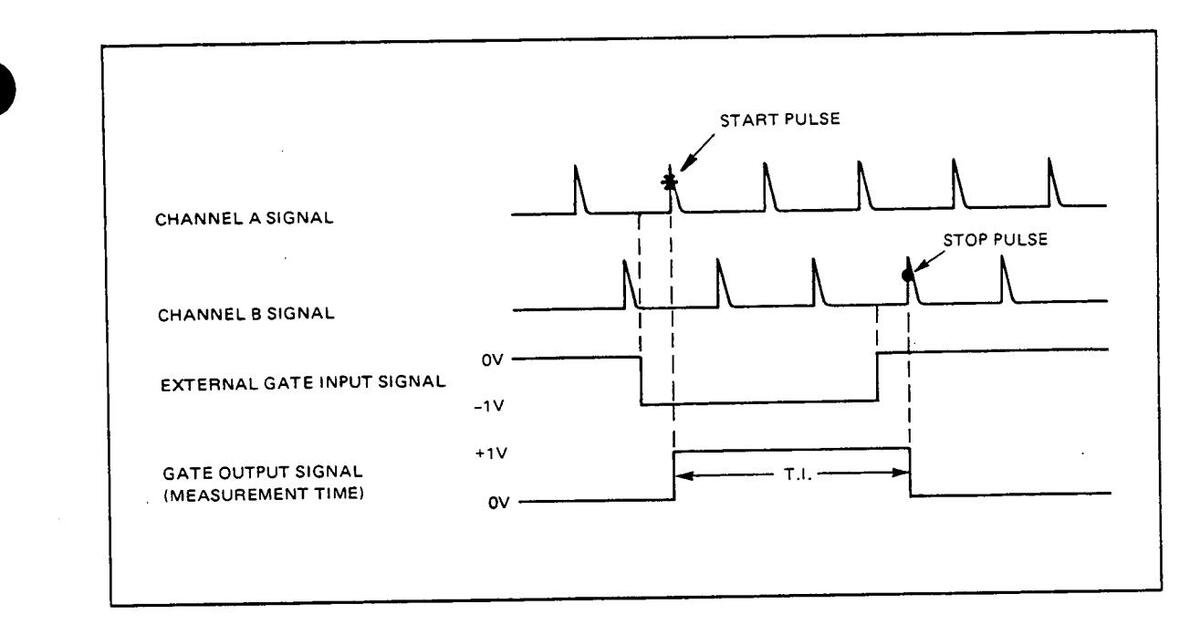

3-49. SINGLE TIME INTERVALS. As previously mentioned for external gating, a measurement using a single external gate requires the GATE TIME switch to be set to MIN. The counter arms automatically and the external gate pulse provides a control over the time interval measurement. Varying the width of the pulse determines which time interval is measured, as can be seen in Figure 3-4.

Figure 3-4. External Gating for Single Time Interval

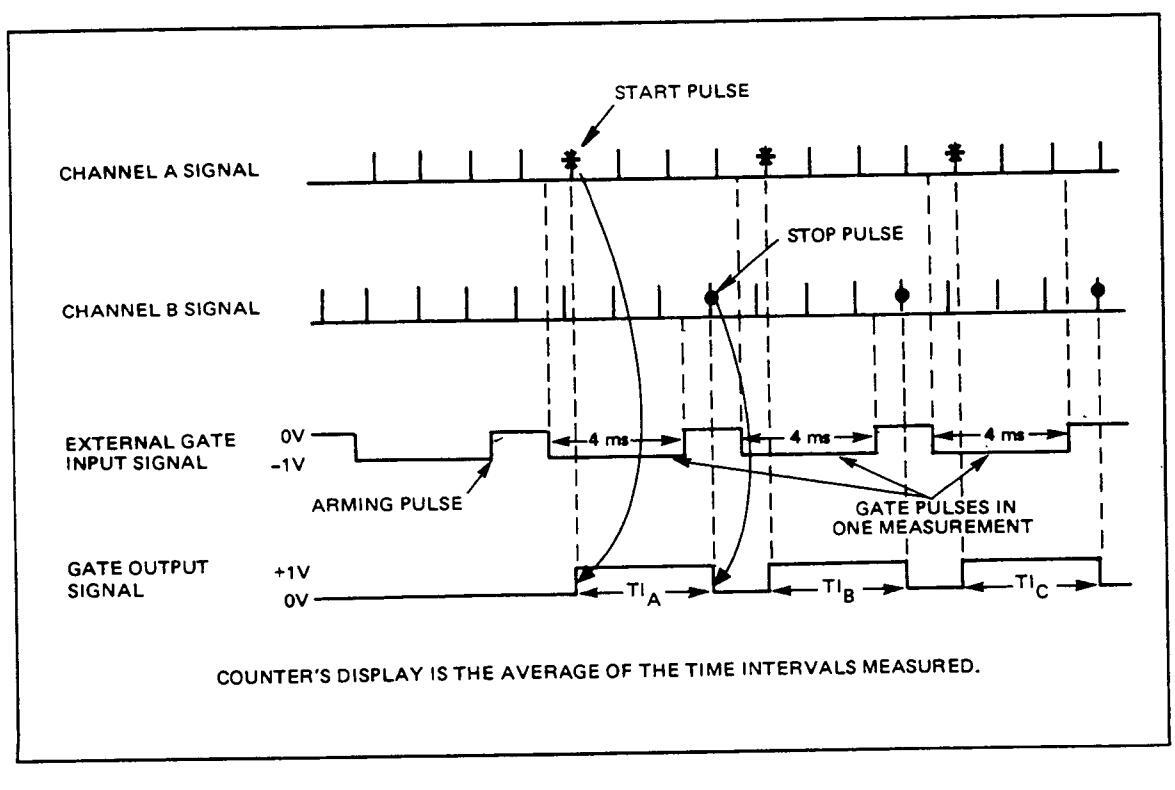

3-50. MULTIPLE TIME INTERVALS. An average of time intervals can be measured using the external gating method. This method, as in single time intervals, allows certain pulses of the waveform to be ignored. The GATE TIME switch must be set to any other position than MIN. See Figure 3-5 for an example of time interval averaging. This method does require an arming pulse for each measurement cycle.

Figure 3-5. External Gating for Time Interval Averaging

3-51. DISPLAY

3-52. The counter uses a 12-digit display: 11 digits of data and 1-digit for the minus sign. Unlike most counters, the number of digits displayed in a measurement is not a function of the input frequency and is not related to the FUNCTION switch. The number of digits is constant for each setting of the GATE TIME switch.

3-53. Display Position

3-54. When the DISPLAY POSITION switch is set to AUTO, the counter automatically positions the display's least-significant digit in the right-most column. Rotating the switch to each of its counterclockwise positions (blue dots) shifts the decimal point, hence the display, one place to the left. Once the switch is placed to any position other than AUTO, the annunciator (k, M, n, etc.) stays fixed, regardless of changing input frequency. The annunciator remains fixed until the RESET button is pushed or the FUNCTION switch setting is changed. Manually fixing the decimal point and the annunciator is convenient when collecting measurement data with a digital-to-analog converter. As an example, the DAC can continually record any 3 digits in a possible display of 11, regardless of changing input data.

3-55. Asterisk

3-56. The asterisk lamp will light under any one of four conditions: overfow, underflow, factitious zeros, or insuffucient oven temperature (standard only). Overflow occurs when the placement of the DISPLAY POSITION switch has positioned the display's most-significant digit(s) so far to the left that it is out of viewable range. Underflow occurs when the placement of the DISPLAY POSITION switch has positioned the display's least-significant digit(s) so far to the right that it is out of viewable range. If the counter is equipped with an oven-controlled oscillator (standard), the operating temperature of the oven must remain constant for the crystal to perform properly. Should the oven temperature drop below its normal operating range, the asterisk light will come on as an indication of this condition.

3-57. Factitious zeros occur when the settings of the GATE TIME switch and DISPLAY POSITION switch has been combined to give fewer significant digits than the DISPLAY POSITION demanded. In this combination, the display attempts to blank one or more of the significant digits located to left of decimal point. Instead of blanking the digit, the display substitutes an artificial and meaningless zero to keep that portion of the display filled.

3-58. Although the presence of factitious zeros is a rare occurrence, its appearance can be demonstrated with the counter set-up as follows: FUNCTION to FREQ A, connect input signal of 125 MHz, turn DISPLAY POSITION switch out of AUTO to about mid-range, turn GATE TIME switch ccw until the display is 125 MHz. The next switch position changes the display to 120 MHz and lights the asterisk. The zero now displayed is a factitious or filler zero.

3-59. Arm Light

3-60. An illuminated ARM light indicates that Channel A is not triggering. The condition of this indicator should be observed when adjusting the front-panel controls for a first-time measurement. Insufficient amplitude of the input signal or improper setting of the input controls (LEVEL, ATTEN, etc.) are common causes for the failure of the GATE light to turn on.

3-61. Gate Light

3-62. Once Channel A triggers, the ARM light turns off and the GATE light turns on. The GATE indicator lights during the time the counter's event gate is open. For short-duration gate times, the GATE light circuits include a 40 ms one-shot mV to allow a visible flash of the lgiht. The SAMPLE RATE control sets the time between flashes (or measurement cycles).

3-63. Lamp Test

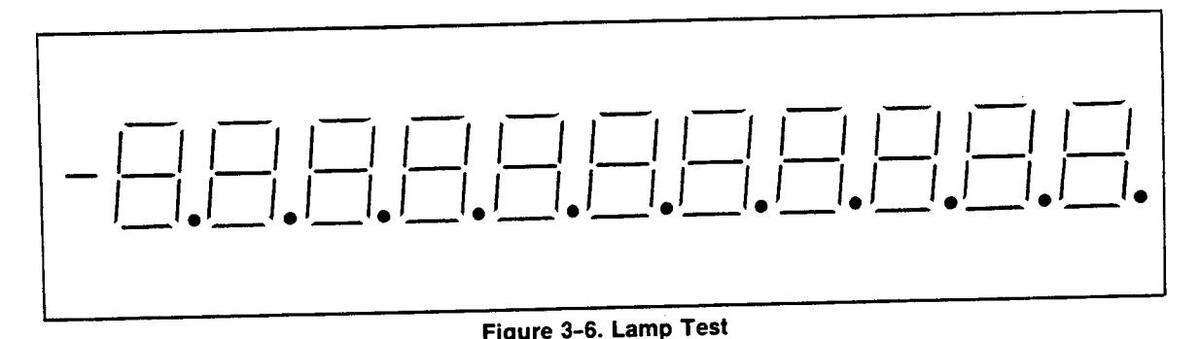

3-64. To ensure that all segments of the display are capable of lighting, the counter provides a lamp test. The display should appear like the representation shown on the next page (Figure 3-6).

3-65. Lamp test occurs under several conditions:

- a When the RESET button is pushed.

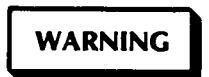

- b. When the POWER switch is placed to ON, lamp test will light for about 2 seconds.