Hitachi TV CP-2896 Schematic

CP2896TA

SERVICE MANUAL

VORSICHT:

Data contained within this Service

Verbesserungen

ä

ndern.

MANUEL D’ENTRETIEN

WARTUNGSHANDBUCH

CAUTION:

Before servicing this chassis, it is important that the service technician read

the “Safety Precautions” and “Product Safety Notices” in this service manual.

ATTENTION:

Avant d’effectuer l’entretien du châassis, le technicien doit lire les

«Précautions de sécurité» et les «Notices de sécurité du produit» présentés

dans le présent manuel.

No. 0103

CP2896TAN

CP2996TA

CP2996TAN

manual is subject to alteration for

improvement.

Les données fournies dans le

présent manuel d’entretien

peuvent faire l’objet de

modifications en vue de

perfectionner le produit.

Vor Öffnen des Gehäuses hat der Service-Ingenieur die „Sicherheitshinweise“

und „Hinweise zur Produktsicherheit“ in diesem Wartungshandbuch zu lesen.

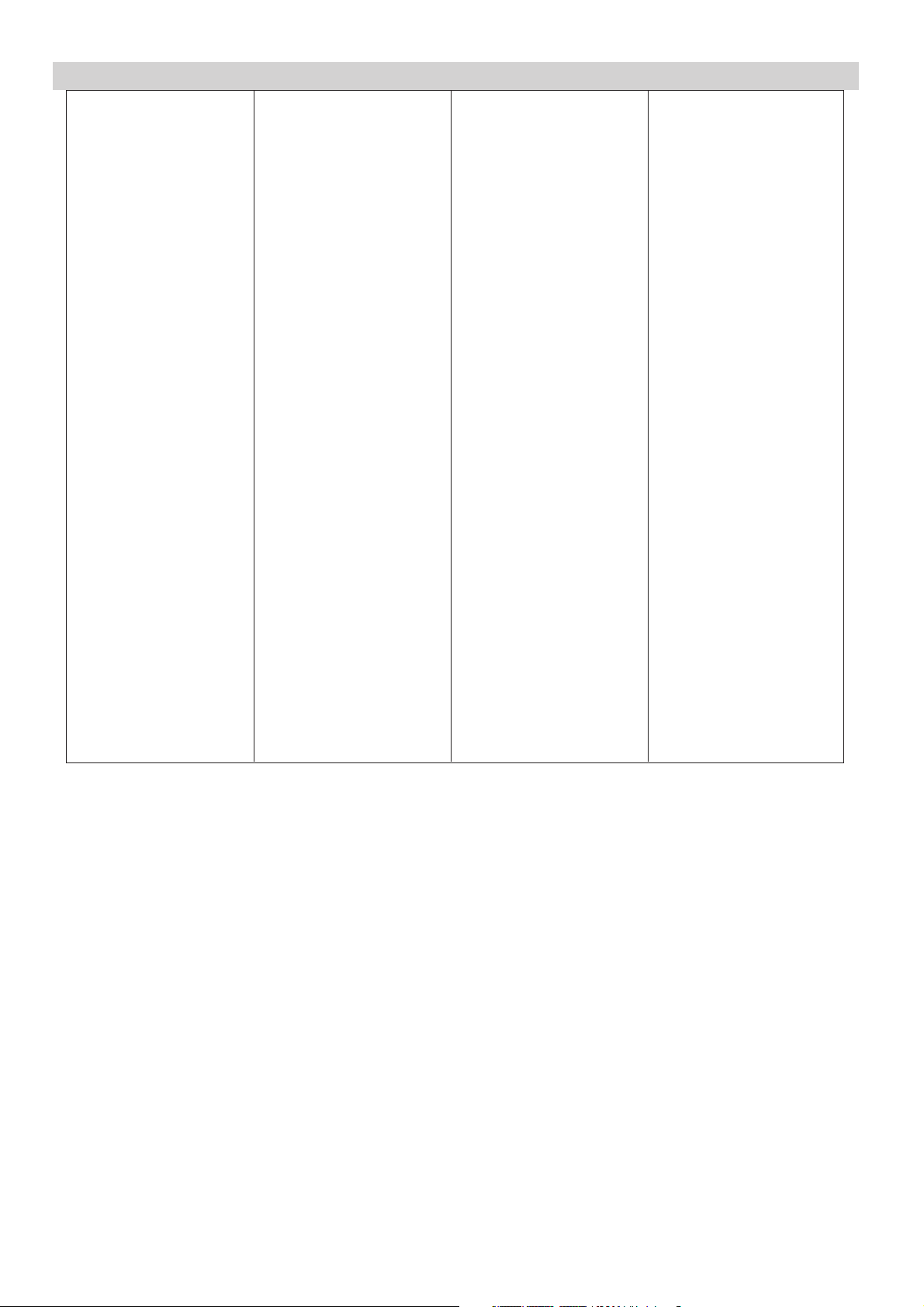

TECHNICAL SPECIFICATIONS

TV System.............................PAL/SECAM B,G

NTSC 3.58/4.43 MHz via Scart

Mains voltage........................210..240 V, 50Hz

Power consumption................................135W

Standby power consumption...................0.2W

Picture tube

2896 TAN,2896 TA 71cm

2996 TAN,2996 TA 74cm

Sound output (RMS) ..................... 2 x 10W/8Ω

Connections

Front panel

Headphones 32..600Ω, 3.5mm

Audio/Video Audio in: 0..2V (RMS)

Video in: 1V/75Ω

Y/C in (SVHS)

Rear panel

A/V Audio in: 0..2V (RMS)

Audio out: 0..2V/10k (RMS)

Video in/out: 1V/75Ω

RGB in: 0.7V/75Ω (E1)

Y/C in: (SVHS)(E2)

Loudspeakers min 10W/8Ω (RMS)

Aerial 75Ω

Audio output 0..2V/10k (RCA)

SPÉCIFICATIONS TECHNIQUES

Systéme TV...........................PAL/SECAM B,G

NTSC 3.58/4.43 MHz via Scart

Tension secteur.....................210..240 V, 50Hz

Consommation .......................................135W

Consommation en veille...........................0.2W

Tube-image

2896 TAN,2896 TA 71cm

2996 TAN,2996 TA 74cm

Sortie sonore (RMS).........................2 x 10W/8

Connexions

Sur le panneau avant

Ecouteurs 32..600Ω, 3.5mm

Audio/vidéo Entrée audio:0..2V(RMS)

Entrée video: 1V/75Ω

Entrée Y/C: (SVHS)

Sur le panneau arrière

Audio/video Entrée audio:0..2V(RMS)

Sortie audio: 0..2V/10k (RMS)

Entrée vidéo/out: 1V/75Ω

Entrée RGB: 0.7V/75Ω (E1)

Entrée Y/C: (SVHS)(E2)

Haut-parleurs min 10W/8Ω (RMS)

Antenne 75Ω

Sortie audio 0..2V/10k (RCA)

Die in diesem Wartungshandbuch

enthaltenen Spezifikationen

können sich zwecks

TECHNICAL SPECIFICATIONS

TV-Norm................................PAL/SECAM B,G

NTSC 3.58/4.43 MHz via Scart

Netzspannung.......................210..240 V, 50Hz

Leistungsaufnahme.................................135W

Leistungsaufnahme im standby-modus...0.2W

Bildröhre

2896 TAN,2896 TA 71cm

2996 TAN,2996 TA 74cm

Tonleistung (RMS)......................... 2 x 10W/8Ω

Anschlüsse

An der Vorderseite

Kopfhörer 32..600Ω, 3.5mm

Audio/Video Audio ein: 0..2V (RMS)

Video ein: 1V/75Ω

Y/C ein (SVHS)

An der Rückseite

Audio/video Audio ein: 0..2V (RMS)

Audio aus: 0..2V/10k (RMS)

Video ein/aus: 1V/75Ω

RGB ein: 0.7V/75Ω (E1)

Y/C ein: (SVHS)(E2)

Lautsprecher min 10W/8Ω (RMS)

Antenne 75Ω

Audio-Ausgang 0..2V/10k (RCA)

December 1998

2

Technical data

Technische Daten

Données téchniques

System

NTSC

Mains power

Consumption

1)

In stand-by

Frequency range

Sound output (RMS)

Subwoofer

2)

Connections on the front

panel

Headphones

Audio/Video

Connections on the rear

panel

Audio/Video

External loudspeakers

Antenna

Audio output

2)

Norm

NTSC

Netzanschluß

Leistungsaufnahme

Im Bereitschaft

Frequenzbereich

Tonendstufe (RMS)

Subwoofer

2)

Anschlüsse an der

Vorderseite

Kopfhöreranschluß

Audio/Video

Anschlüsse an der

Rückseite

Audio/Video

Externe Lautsprecher

Antennenanschluß

Audio Ausgang

2)

Systéme

NTSC

1)

Alimentation

Consommation

1)

En mode veille

Gamme de fréquences

Sortie sonore (RMS)

Subwoofer

2)

PAL/SECAM B, G

3.58/4.43 MHz via Scart

210...240 V, 50 Hz

135 W (normal)

0.2 W

48.25 - 855.25

2 x 10 W/8 Ω

14 W/16 Ω

Connexions sur le

panneau avant

Ecouteurs

Audio/Vidéo

32...600 Ω , 3.5 mm

Audio in: 0...2 V (RMS)

Video in: 1 V/75 Ω

Y/C in (SVHS)

Connexions sur le

panneau arrière

Audio/Vidéo

Audio in: 0...2 V (RMS)

Audio out: 0...2 V/10 kΩ

(RMS)

Video in/out: 1 V/75Ω

RGB in: 0.7 V/75Ω (E1)

Y/C in (SVHS) (E2)

Haut-parleurs externes

Antenne

Sortie audio

2)

min 10 W/8 Ω (RMS)

75 Ω

0...2 V/10 kΩ (RCA)

Specifications are subject

to change.

1)

Depends on option

modules and picture tube.

2)

Not in all models.

Änderungen vorbehalten

1)

Abhängig von

Optionsmodulen und

Bildröhre.

2)

Nicht in allen Modellen.

Les Spécifications

peuvent êt re modifiées

sans préavis.

1)

Dépend des modules

option-nels et du tube

cathodique.

2)

Pas sur tous les modèles.

15

20, 22, 24

19

10-12

13

fb

2-4

1

fb

bcl

BC

8

6

7

ICt1

ICr2

44-46

18-27

ICr1

47

BLAN

141312

Y

ICd1

25

26

V

U

ICd3

423

1

RGB + fb

1718161514

C

CVBS/Y

C

ICq1

OUT

OUT

13

3

11

IN

IN

CVBS/Y

5, 6

IN

8, 10

IN

2H

2V

14

sc

17

11

HA

VA

10

SSc

D1D0D2

D3

32

33

34

35

I/O2

I/O1

I/O3

I/O4

2

1

24

25

9

CVBS

3

2V

4

2H

A0-A9

RGB

ICs1

Mk1

DATA IN

DATA OUT

WS

L

R

CL

L, R

L, R

L, R

AM

SIF

R, L

R, L

L

R

3D/Pro Logic

module

AR7xx

4

6

1

7

ICa1

29

28

26

25

9

1

ICa2

2

6

33, 34

36, 37

46, 47

49, 50

52, 53

55

60

141312

11

5

6

7

8

SOUND BLOCK

CRT module

HH7xx

ICh3

ICh2

ICh1

R

G

B

6

5

4

9

7

BC

SVM

module

VMxxx

PIP

module

PP7xx

RGB

RGB

IQTV2

&

DPLL

DB7xx

Flyback

EW

Ver

Ver

Hor

sc

111412

16

Comb filter

module

CF7xx

V

Y

U

11

10

67

13

15

14

18-21

Scart 1

3435333738

Camera

Scart 2

Scart 1

RF BLOCK

PIP

module

109

C

CVBS/Y

11 12

Scart 2

Scart 2

RGB

2H

2V

27 26

24

TELETEXT

VIDEO BLOCK

Adjustable

audio

Scart 1

Camera

Scart 3

VGA

Scart 2

Scart 1

17

Y

Tk3

SWxxx

U1

12V

22

17

20

19

18

12

11

1

9

2

Scart 1

26

Y

SVM coil

Diode

modulation

Dk7, Dk8

Tk4,ts1,ts2

5

Vertical

deflection

yoke

Horizontal

deflection

yoke

Line

driver

Tk1, Tk2

Vertical

deflection

and

E-W driver

Horizontal

deflection

5,9-12,14-18

MSP3410D

Audio

processor

TDA9143

Colour

decoder

TDA4780

RGB processor

SDA5275S

Megatext

514400

Text memory

TEA6417

Video switch

TDA8354

Vertical output

TDA2616

Audio power

amplifier

TL082

Headphone

amplifier

TV-Frontend

Tuner+IF

19

18

20

PIP

CVBS

1

Scart 3

IN

IN

23

1

Fsc

clock

VGA

VGA/RGB

5

6

4

ICa4

1

9

TDA2616

Active subwoofer

amplifier

ICa3

31

SUB

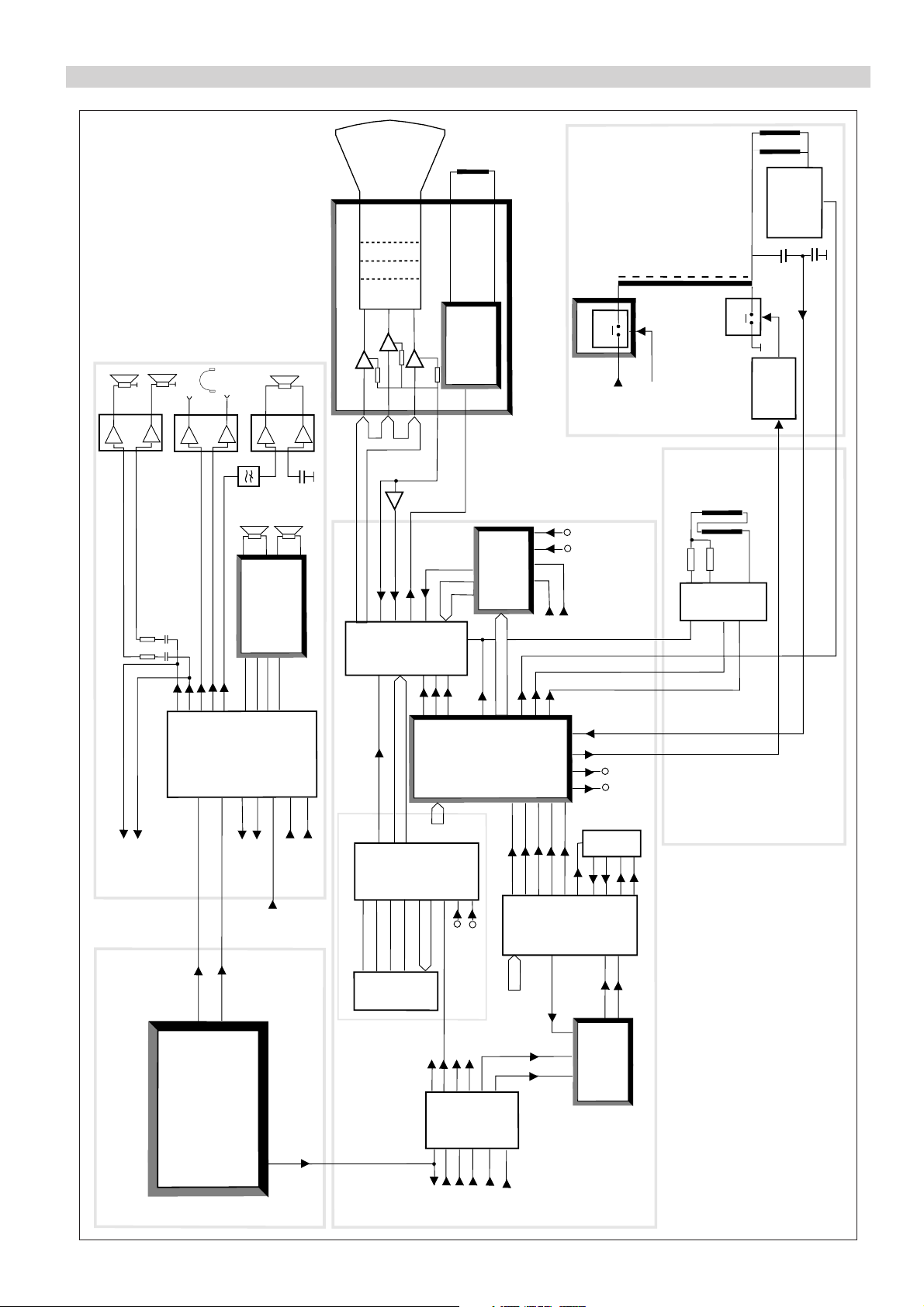

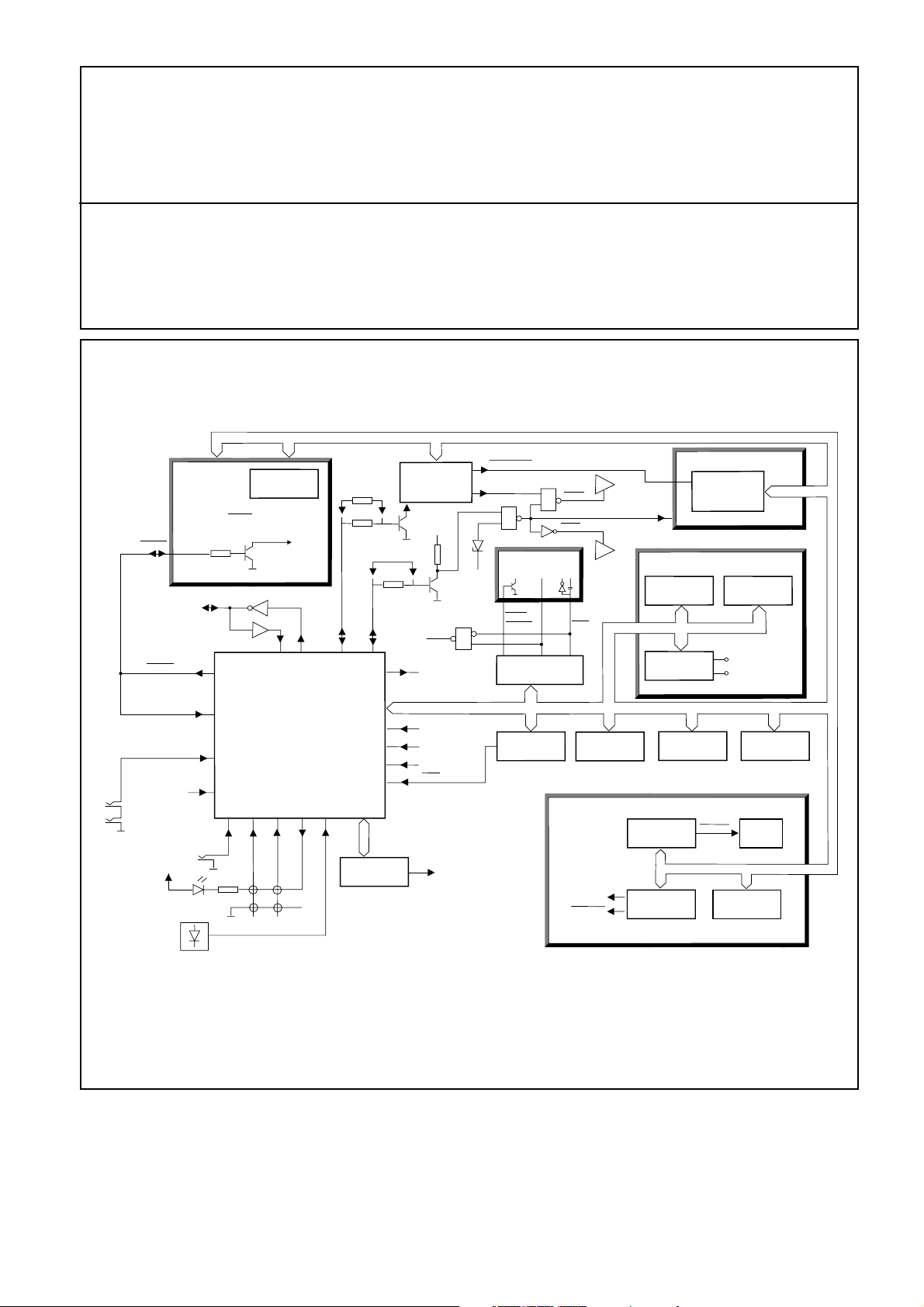

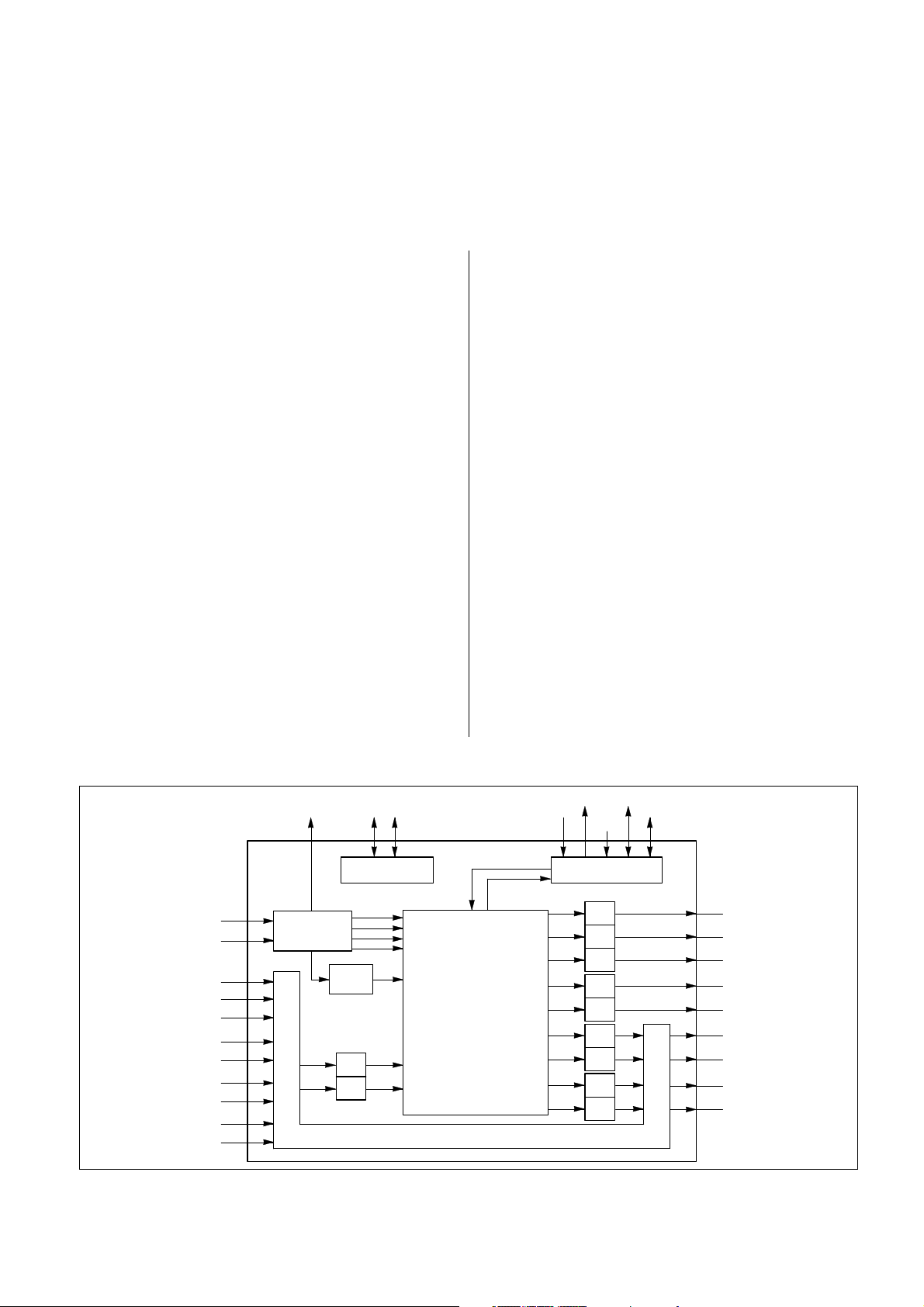

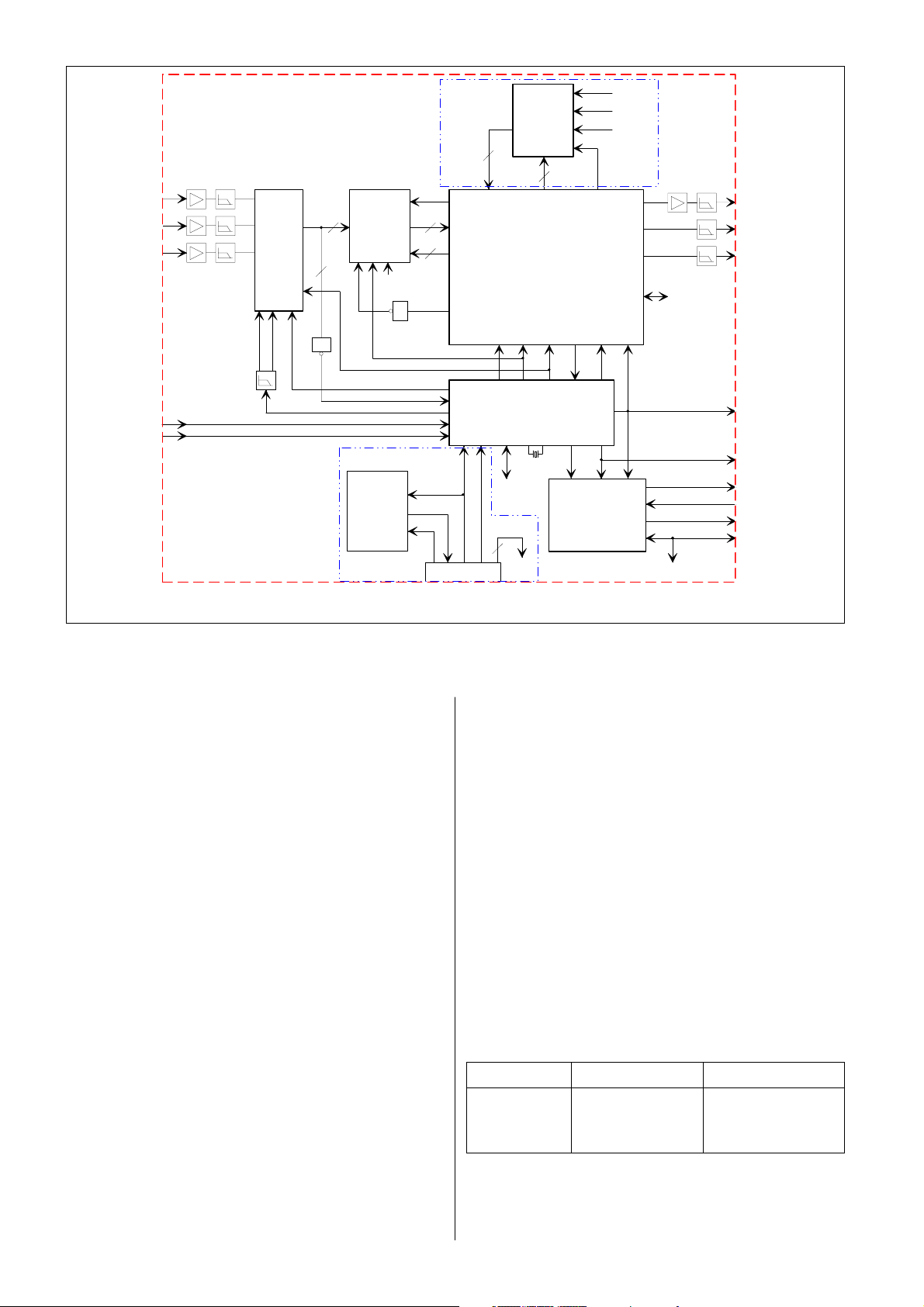

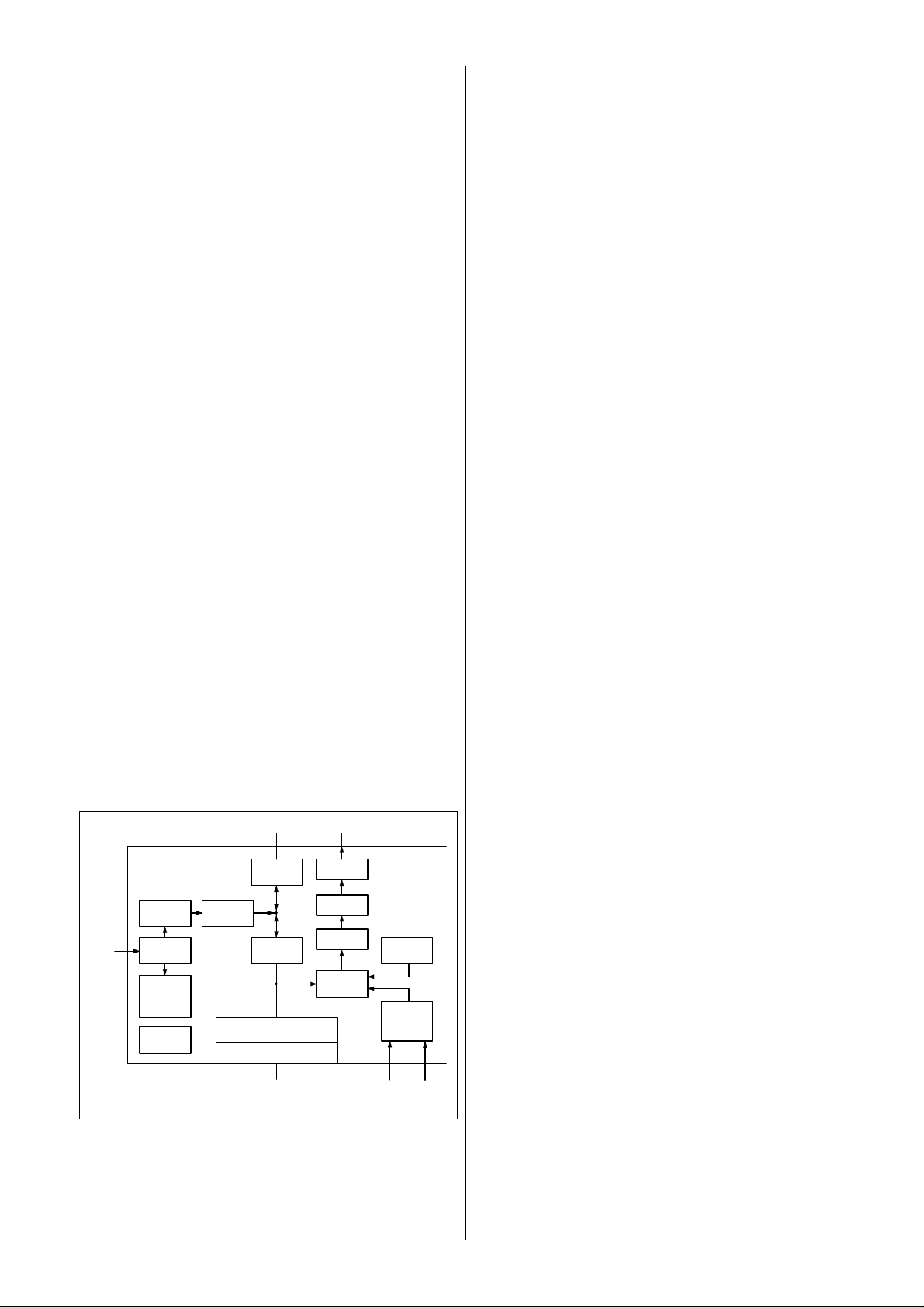

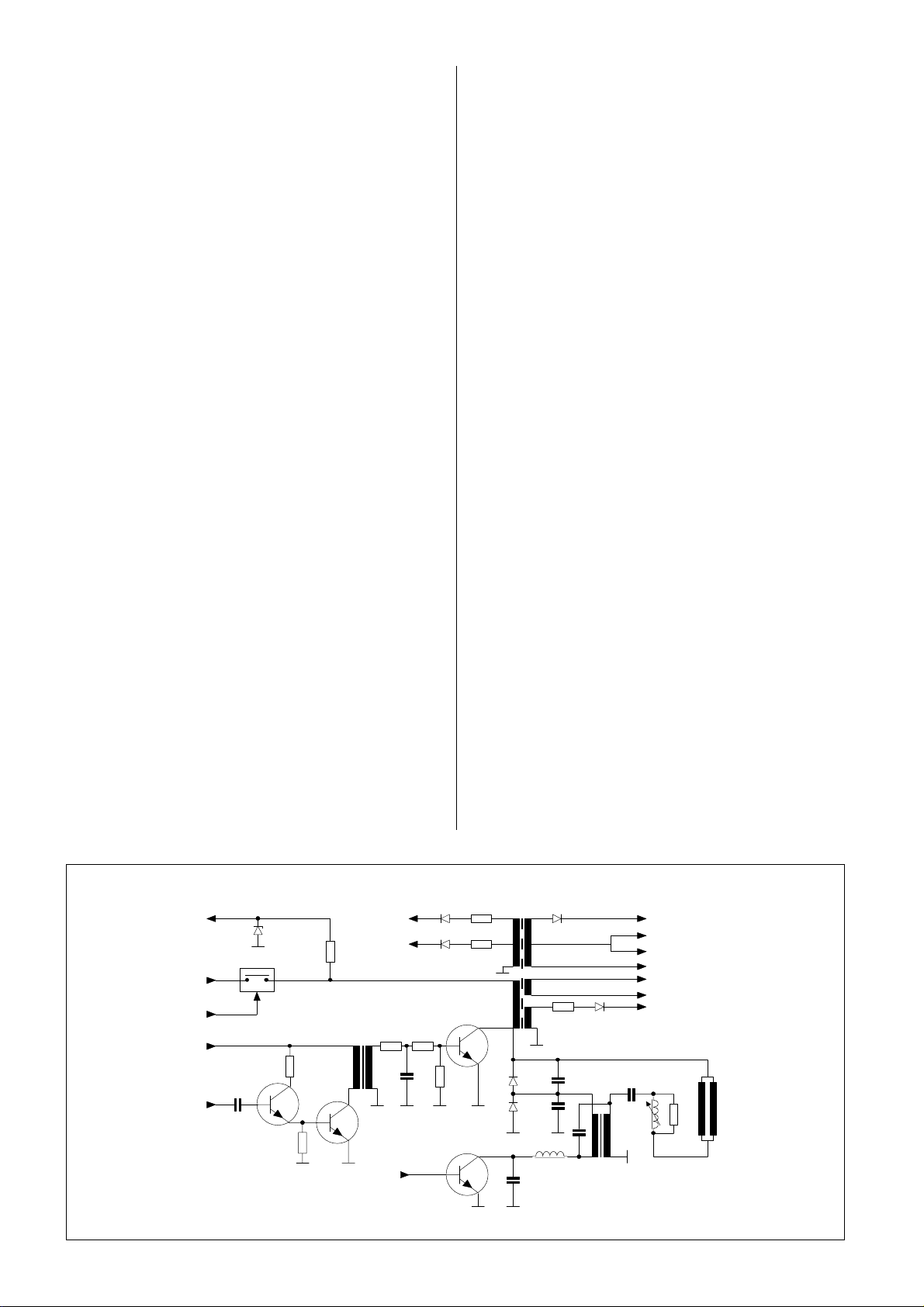

Block diagram, signal routes

3

Scart-

buffers

TXT

ICr1

RAM

ICr2

Delay

ICd3

Deco/Sync

ICd1

RGB-proc.

ICt1

ROM

ICf1

NVM

ICf2

µP

ICf3

Video Switch

ICq1

HP-Ampl.

ICa3

Service

conn. &

buffer

Sound

processor

ICa2

Frontend

PIF SIF

TV-

Tuner

ICo6

Rec

ICo3

Rec

5V-r

12V-r

To4

Pict

12V-p

SVM module

CRT-module

8V-p

FEATURE BOX

32

30

8V-p

Comb-Filter

3

4

PIP-module

Decoder

ICp3

µP, ICp6

&

A/D, ICp5

13

12V-p

7V-fb

8V-p

12V-p

7

28

5

5V-r

Amplifiers

Digital Sound

Processor

5V-r

12

1

28V

ICo4

12V-r

10V

5V-stb

Control module

IR-

receiver

8

10

6

12V-p

5V-stb

Loudspeaker

Amplifier

ICa1

PP7xx

Rq48

AR7xx

FC7xx

CF7xx

20

22

23

24

15

17

18

14

21

19

3

4

ICo2

3

2

11

5

ICo1

6

16

1

14

Ro8,

14

Do8

Co10

Do2

Do1

Do4

Do3

Ro4, 10

Ro15

Ro18, 19

21, 22

To1

Ro70

Co15

230V

50Hz

Ftc1

Fo1

Do12

Do11

Do9

Do13

U1

32

PWM

Line

sync.

Do17

Ro32

Fo3

Fo2

Do14

Do16

Ro42

Ro45

Ro50

Do20

8

2

5

!

!

Ro44, 46

ZDk1

7V

Mains non isolated

17V

7V-fb

Ro49

Ro48

!

Mo2

!

Mo3

!

Vert.deflection

& EW driver

ICs1

Mk1

Rk2

Dk1

8

10

11

12

1

7

Rk9

Dk2

Rk19

Dk3

6.3V RMS

30kV

500V

8 kV

Rk15

Rk45

200V

53V

Rk4

!

!

!

!

!

Tk3

Rk20

!

16V

SWxxx

Rk11, 12

13, 14

HH7xx

Line

driver

12V-p

12V-p

12V-p

!

7V

G2

Focus

Heater

5

4

3

6

12V-p

8V

Ra18

AUX

module

12V-p

TA700

And

ICf4

Reset

ICf5

Subwoofer

Amplifier

ICa4

I

2

C Switch

11

30V

2

30V

Rq54

Rq2

Tq5

8.5V

Rr18

Scart 3 module

TA710/711

4

10

Tuner

To15

To9

Cfc23

FC7xx

Control module

Start

ICfc1

ICfc2

2

1

47

14

Cfc24

Cfc26

Dfc11

Hfc2

3

Zdo1,To8

RGB

Switch

ICp7

I

2

C Switch

ttp5

IF

ICp1

Delay-line

ICp4

DB7xx

SR7xx

Cancellor

VMxxx

Defl. ctrl

IC17

Filters

5V

3V

IC1

DSP

IC4

IQTV

4

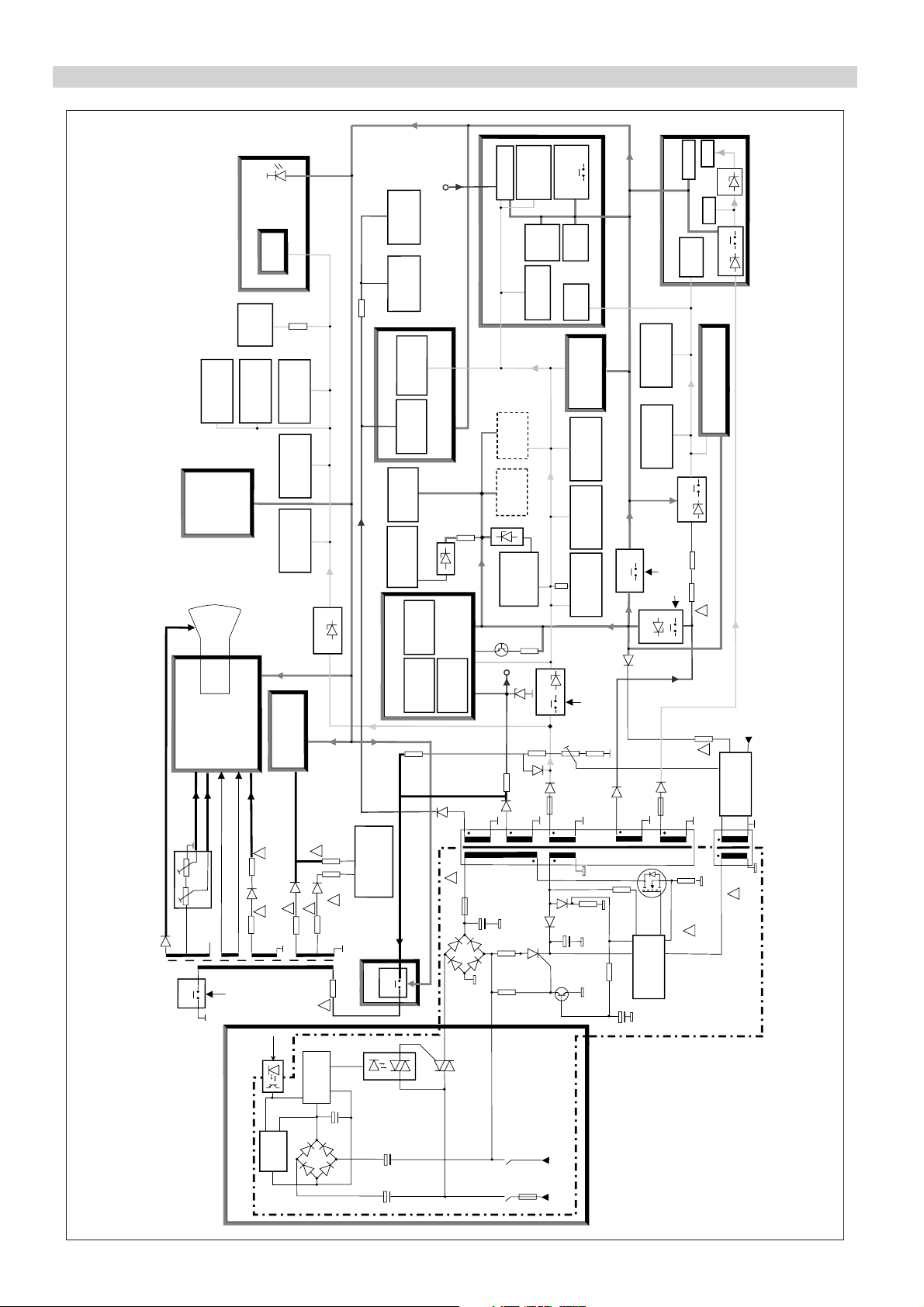

Block diagram, power supply

Block diagram, control signals

µP

ICf3

PIP-MODULE

FEATURE BOX DB7xx

Comb-Filter

module

TV tuner

SDA

SCL

+5V

Local control

HP ind

Rec / IR

IR Receiver

TXT

ICr1

M3L

Status 2

Status 1

Status 3

Hold

Surround

processor

ICar2

Sound

processor

ICa2

Deflection

IC 17

IQTV µP

IC 18

Deco/Sync

ICd1

Subwoofer

mute

5

MSP Reset

Bypass /

Comb-ID

NTSC

RGB processor

ICt1

Video Switch

ICq1

NVM

ICf2

PIP µP

ICp6

Deco/Sync

ICp3

Video switch

PIP/ext. RGB

Service

connector

545352

7

50

1

61 62

46

64

44, 45

4, 59, 60

AUDIO FEATURE BOX

17, 18

5, 6

8, 9

17, 18

5, 6 2, 4 27, 28

9, 10

49, 50, 51

51, 61

85

DPLL

IC 11

40, 41

9,10

24

40,41

3, 4

1, 2

3

PIP tuner

IF

ICp1

L-norm

15

16

37

38

VGA

1/2 FM

Bridges:

Mute

2

7

E3-control

(3-state)

&

APSi

test

Subwoofer

ident.

RGB

status

Line-out

status

6

3

FRONTEND

Multi: Strobe to write I/O-latch

Single: APSi control

IF ident.

resistor

APSi filter/Strobe

Strobe

APSi

(Single norm)

47

55

IF Ident.

15

16

23

13

2

1

5, 6

FSC /

SVHS

263

AV-link

PWM

Scart pin 10

16:9 ident.

51

12Vp

PA-mute

&

OR

28V

PA

PA

mute

mute

Subwoofer

Int-LS

15

4

I

2

C

I

2

C

DSP Reset

12V

4, 57, 8

10

A/D

Hor. shift

5

A/D

A/D

A/D

4, 5

8

8

ΤΑ700

8,9

Picture tilt

PWM

1

)

1

)

1

)

If no mux. and

picture tilt

mux.

ΤΑ710

Upict

Urec

U

49

48

Start

Rec-on

Pict-on

11 = Off

00 = TV

01 = Record

10 = Service

3

5

MULTI CONCEPT

MX/MZ-CHASSIS

G Functional description

2

C

I

4, 57, 8

APSi filter/Strobe

Scart pin 10

Strobe

APSi

RGB status

FRONTEND

Multi: Strobe to write I/O-latch

Single: APSi control

(Single norm)

IF Ident.

Line-out

status

Rec / IR

IF ident.

resistor

47

55

3

6

HP ind

10

+5V

A/D

1

TV tuner

AV-link

µP

ICf3

61 62

Local control

263

46

64

Subwoofer

ident.

16:9 ident.

MSP Reset

50

PWM

SDA

SCL

A/D

A/D

A/D

M3L

4, 59, 60

49, 50, 51

TXT

ICr1

PA-mute

51

5

44, 45

54

53

52

7

Sound

processor

ICa2

24

12Vp

APSi

test

Hor. shift

Status 2

Status 1

Status 3

Hold

7

E3-control

9, 10

&

(3-state)

4

5

12V

28V

DSP Reset

Subwoofer

mute

&

Comb-Filter

module

13

Bypass /

Comb-ID

15

Deco/Sync

Service

3

connector

OR

mute

2

NTSC

16

ICd1

5, 6

1, 2

PIP-MODULE

Video switch

PIP/ext. RGB

mute

1

FSC /

SVHS

23

T V

1997

AUDIO FEATURE BOX

15

85

PA

Subwoofer

Mute

Int-LS

PA

FEATURE BOX DB7xx

Deflection

40,41

2

I

C

5, 6 2, 4 27, 28

NVM

ICf2

PIP tuner

16

Deco/Sync

15

ICp3

Surround

processor

2

IC 17

17, 18

40, 41

DPLL

IC 11

Video Switch

ICq1

L-norm

8

4, 5

5, 6

ICar2

37

38

Bridges:

1/2 FM

VGA

8

PIP µP

IQTV µP

IC 18

RGB processor

ICp1

ICp6

51, 61

IF

17, 18

9,10

8, 9

ICt1

3, 4

IR Receiver

6611 72 76

Contents

MICROPOWER CONTROL.........................................................................................................................................................1

POWER SUPPLY ........................................................................................................................................................................ 2

RECEPTION ................................................................................................................................................................................4

AUDIO SECTION........................................................................................................................................................................5

Multistandard Sound Processor, ICa2................................................................................................................................ 5

Audio Power Amplifier, ICa1...............................................................................................................................................6

Headphone Amplifier, ICa3 .................................................................................................................................................6

VIDEO SECTION ........................................................................................................................................................................7

Video Matrix Switch, ICq1...................................................................................................................................................7

Colour Decoder / Sync Processor, ICd1 .............................................................................................................................7

Baseband Delay Line, ICd3 ................................................................................................................................................. 8

Feature boxes, DB7** .........................................................................................................................................................9

Feature box DB711 ..............................................................................................................................................................9

Analog to digital converter, ic9...........................................................................................................................................9

Field memory, ic14 ............................................................................................................................................................10

IQTV2 circuit, ic18 ..............................................................................................................................................................10

DPLL1 circuit, ic11 .............................................................................................................................................................11

Deflection Controller TDA9151, IC17 ...............................................................................................................................11

Feature box DB710 ............................................................................................................................................................ 12

Feature box DB700 ............................................................................................................................................................ 12

RGB Video Processor TDA4780, ICt1 ............................................................................................................................... 13

CRT module........................................................................................................................................................................14

Teletext ...............................................................................................................................................................................15

Megatext SDA5273, ICr1 ...................................................................................................................................................15

Megatext Plus SDA5275, ICr1 ...........................................................................................................................................15

Teletext memory DRAM, icr2 ............................................................................................................................................15

29

CONTROL SYSTEM ................................................................................................................................................................. 16

Program memory, ICf1...................................................................................................................................................... 16

NV RAM, ICf2 ..................................................................................................................................................................... 16

Microcontroller, icf3........................................................................................................................................................... 16

AND gate, icf4 ....................................................................................................................................................................17

Reset circuit, icf5................................................................................................................................................................ 17

DEFLECTION STAGES............................................................................................................................................................. 19

Vertical deflection ..............................................................................................................................................................19

Horizontal deflection ......................................................................................................................................................... 19

OPTIONS ..................................................................................................................................................................................21

Active Subwoofer ..............................................................................................................................................................21

Comb Filter module, CF700 .............................................................................................................................................. 21

Scan Velocity Modulation module, VM600 .....................................................................................................................22

Audio Feature modules, AR700 and AR701 .................................................................................................................... 23

Adjustable Audio Output module, TA700 ........................................................................................................................27

Scart 3 + VGA-audio module, TA710 ...............................................................................................................................27

Scart 3 module, TA711 ......................................................................................................................................................27

Picture in Picture module, PP700 ..................................................................................................................................... 27

Picture in Picture module, PP710 ..................................................................................................................................... 28

MICROPOWER CONTROL

1

General

The power supply is equipped with a micropower system

in order to reduce the standby power consumption to about

<200 mW (generally about 5 to 7W). To make this possible,

the power supply and degaussing circuitry must be totally

switched off in standby mode.

The only active part in standby mode is the micropower

circuitry which gets its supply voltage from a capacitive

coupled rectifier. This provides the supply voltage for required circuits, like a “primary” infrared receiver and a gate

circuit. When the TV set is switched on with the mains

switch or with a remote control command, the gate circuit

drives a triac switch to conduct, thereby supplying the

mains voltage to the power supply. At the same time, the

micropower circuit controls the main microcontroller via

optocouplers.

The micropower circuitry is not mains isolated.

Start up via the mains switch

The mains voltage is fed directly to the micropower circuit

which is located on the local control panel.

The circuitry gets its supply voltage from the capacitive

coupled rectifier consisting of capacitors Cfc24/26, resistors Rfc23/24 and diodes Dfc6...Dfc9. The supply voltage is

regulated to +5.1 V by zener diode DZfc1 and fed onwards

to the infrared receiver Hfc2, NAND gate ICfc1 and LED

Dfc16, that indicates the mains voltage is connected.

The TV set can be switched on by firmly pressing the mains

switch. An additional contact in the mains switch causes a

low level pulse on pins 12/13 of the NAND gate. Due to the

effect of the NAND gate, pin 11 as well pins 1/2 are high

and pin 3 is low. Moreover, pins 5/6 go low via diode dfc13

and pin 4 is high.

Transistor tfc1 conducts and grounds the cathode of the

internal LED of the optocoupler ICfc2. The optocoupler then

conducts, feeding the mains voltage via resistor Rfc27 to

the gate of triac Dfc11. The triac’s gate gets sufficient starting voltage via Rfc27, after which resistor Rfc26 is connected in parallel with Rfc27 to keep the triac in a conducting state. Thus the mains voltage is available for the power

supply.

Furthermore, when the TV set is started up with the mains

switch, a low level on pin 3 causes transistor tfc6 to conduct. Also the optocoupler ICfc4 conducts grounding the

cathode of diode dfc18. This indicates to the microcontroller

that the TV set is being powered on via the mains switch.

Because the additional contact causes only a momentary

low on pins 12/13, capacitor Cfc31 discharges and pins 12/

13 go high. Because of this, both transistor tfc6 and

optocoupler ICfc4 stop conducting.

The power supply then generates the supply voltages, the

microcontroller is reset, and its pins 48 (Pict_on) and 49

(Rec_on) go low. This causes optocoupler ICfc3 to conduct

holding pins 5/6 low in order to keep triac Dfc11 conducting.

If the mains switch is not pressed firmly, the additional

contact may not close for a long enough time and the TV

set may remain in standby mode.

Start up / switch off by the remote control

The TV set must, of course, be in standby mode. This means

the optocoupler Icfc3 does not conduct, voltage level on

pins 5/6 is high and capacitor Cfc28 is charged via rfc29.

When the remote control command is given, pulses on pin

3 of the “primary” IR receiver discharge capacitors Cfc28.

Thus pins 5/6 of the NAND circuit go low via diode Dfc12,

and the mains triac starts to conduct. The command must

be sufficiently long that the power supply has time to generate supply voltages, the microcontroller has time to be

reset and to receive the start command from the “secondary” IR receiver. After that, pins 48 (P_on) and 49 (Rec_on)

of the microcontroller go low and optocoupler ICfc3 conducts and holds pins 5/6 of the NAND gate low.

When the TV set is switched off by the remote control, pins

48 (P_on) and 49 (Rec_on) of the microcontroller go high.

Therefore all Vp and Vr voltages will be switched off (horizontal and vertical stages are switched off), the optocoupler

ICfc3 will not conduct causing pins 5/6 of the NAND gate

to go high. Optocoupler ICfc2 does not conduct and resistor Rfc27 will be disconnected from the gate of Dfc11.

Resistor Rfc26 alone is not able to feed enough holding

voltage to the mains triac, and so the power supply will be

disconnected from the mains.

2

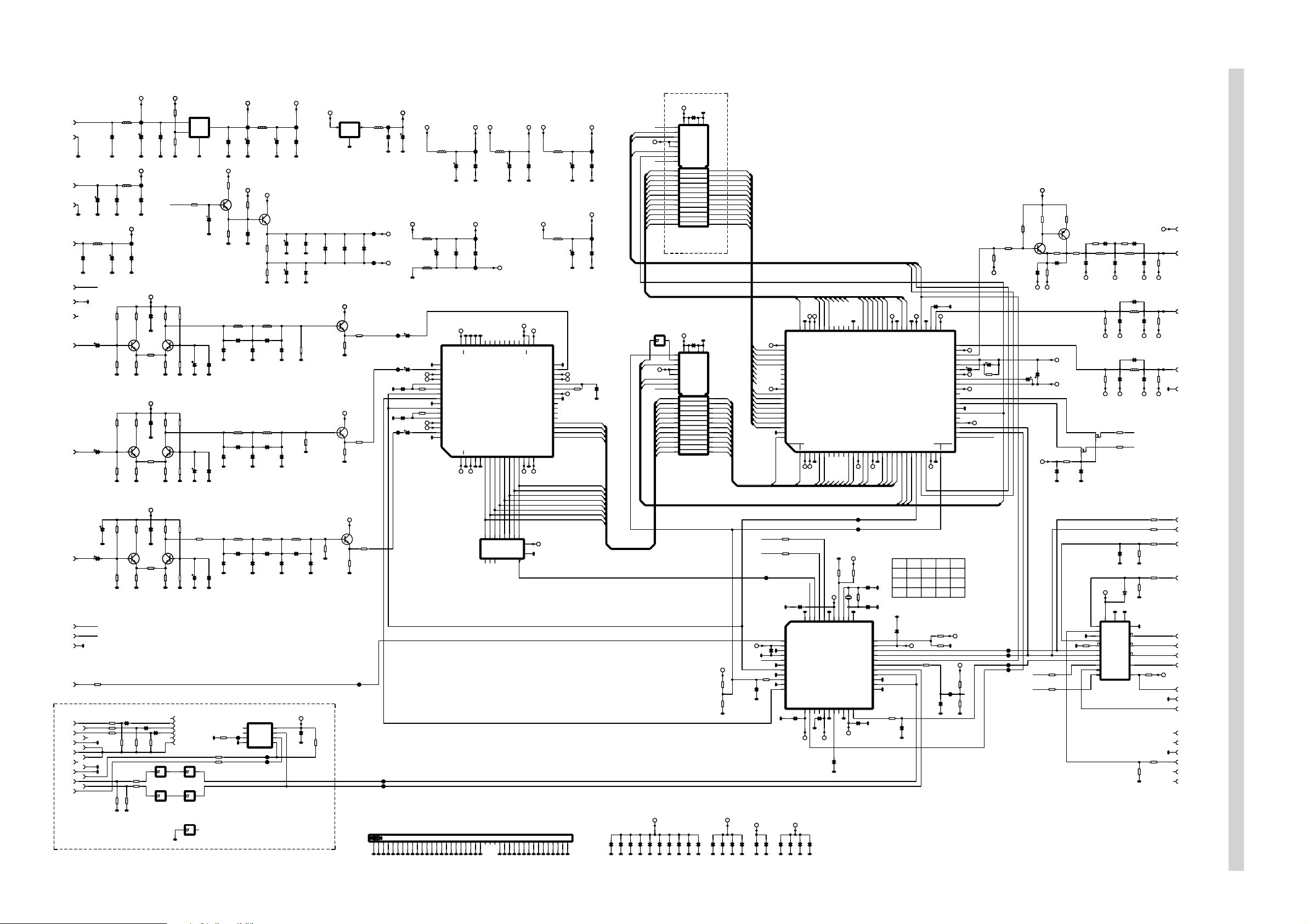

POWER SUPPLY

General

The power supply is a mains isolated Switched Mode Power

Supply (SMPS). Mains isolation is provided by transformer

Mo2. The mains voltage is full wave rectified by diodes

Do1...Do4 and filtered by capacitor Co10. This filtered voltage is fed to the switching transistor To1 (MOSFET) via the

primary winding 11 and 5 of the mains transformer. During the conduct period of To1, energy is stored in the primary winding 11 and 5. When transistor To1 is switched

off, energy flows to the secondary windings. These pulses

are rectified by secondary diodes Do11...14 and Do16.

The following supply voltages are available from the secondary diodes:

+130 V horizontal output stage

+28 V audio amplifier, subwoofer and audio feature

module

+17 V +12 V regulator IC, horizontal driver and +8 Vp

regulator transistor

+7 Vfb feature box

+7 V +5 Vr regulator IC, +5 Vstb regulator IC and +7 V

supply voltage

Note! The voltage levels may vary depending on the picture tube. More detailed values are given in the schematic

diagrams.

The power supply is designed to operate with a masterslave structure, where the power supply controller ICo1

operates as a slave and the secondary controller ICo2 as a

master. The power supply operates in the following ways

in different operation states:

Start up phase:

Power supply is in the primary regulation mode (burst

mode). Power supply controller ICo1 generates independent drive pulses for switching transistor.

Normal on mode:

Power supply is in the secondary regulation mode (master-slave mode). Secondary controller ICo2 generates drive

pulses for power supply controller ICo1. The secondary

controller is synchronized to the line flyback pulses.

Recording mode:

Power supply is in the secondary regulation mode (master-slave mode). Secondary controller ICo2 generates drive

pulses for power supply controller ICo1. The secondary

controller is synchronized to the free running frequency of

an internal oscillator.

Switching off to standby phase:

Power supply is in the primary regulation mode (burst

mode). Power supply controller ICo1 generates independent drive pulses for switching transistor.

Standby mode:

Due to the micropower control, the power supply is completely without voltage.

The power supply also has a so-called Service standby

mode. The receiver is in service standby mode when it is

set to the service mode by pressing the buttons -vol / menu,

TV and i, but has not yet been switched on by pushing the

TV button twice. In this mode, the power supply operates

(burst mode), but the Vr and Vp voltages are not available.

Start up

After switching on with the mains switch and when triac

Dfc11 (on the micropower control) conducts, capacitor Co15

is charged via resistors Ro9, Ro11, Ro70 and thyristor To15.

When the start up voltage on pin 16 of ICo1 reaches the

switch-on threshold level, that is typically +11.8 V, the IC

starts to operate.

The supply voltage of ICo1 is then taken from the secondary winding pin 3 via half wave rectifier diode Do8. The

same winding pin 3 supplies pulses to diode Do9. This

voltage drives transistor To9 to conduct putting the gate of

thyristor To15 to ground, and thus switching off the start

up voltage.

The same DC voltage that is taken from the cathode of diode Do9 is used for power supply regulation. The DC voltage is fed via the filter network Ro26, Co28 and Ro24 to the

error amplifier input pin 6. The error amplifier compares

the input voltage with the internal reference (+2.5 V) and

varies the burst time. Resistors ro4 and ro10 set the voltage to the proper level.

Furthermore, a possible magnetization state of the transformer can be checked by sensing the voltage across the

winding pins 3 and 2. This information is fed via resistor

Ro15 to pin 1 of ICo1, and if the specified level is exceeded,

the output pulses can not be generated.

To avoid magnetization during the start up phase, the operation will be started with the internal oscillator’s operating frequency divided by four, until voltage on soft start

pin 9 reaches a level of +2.5 V. The operating frequency of

the oscillator is set to 27 kHz by capacitor Co16 on pin 10

and resistor Ro3 on pin 11.

Drive of the switching transistor

Pin 14 outputs square wave pulses to the gate of switching

transistor To1. Resistors Ro2 and Ro13 limit the gate current. To1 conducts during the positive going pulse and drain

current flows through the primary winding pins 11 and 5.

The clamping circuit Do6, Co11 and Ro16 limits the voltage spikes, when To1 is switched off. The source of To1 is

connected to ground via current limiting resistors Ro18,

Ro19, Ro21 and Ro22. Information about the current is fed

to pin 3 of the power supply controller.

After the start up phase, when supply voltages are generated, the power supply moves from primary regulation

mode to secondary regulation mode. The microcontroller

will be reset and it’s pins 48 (P_on) and 49 (R_on) will go

low. The R_on line allows, via transistor to6, regulator ICo3

to feed +12 Vr out. This voltage is fed to the secondary

controller ICo2 (pin 2) and the IC starts operation.

The capacitor co58 on pin 1 operates as a soft-start capacitor causing the duration of soft-start to be around 20ms.

The free running frequency of an internal oscillator is set

to 32 kHz by capacitor co72 on pin 7 and resistor Ro37 on

pin 8. In normal operating mode, the oscillator is synchronized using the line flyback pulses via differentiator Ck6,

resistor ro38 and diode Do18.

In recording mode, the Vp voltages are switched off and

therefore the line flyback signal is not available. In this case,

the oscillator is in free running mode.

The internal pulse width modulator is controlled by comparing the input voltage level on pin 5 with the oscillator’s

sawtooth pulses. Pin 5 is connected to +140 V via resistor

network Ro46, Ro44, Ro50, Ro45 and Ro42. By adjusting

the trimmer potentiometer Ro45, the output voltages of

the power supply can be controlled.

In order to avoid excessive decreasing of +7 V during recording mode, diode Do20 is connected from the above

mentioned resistor network to +7 V. If the voltage level

drops too far below +7V, the diode conducts causing a lower

voltage level on pin 5. The controller then generates wider

pulses from the output pin 3 and the supply voltages of

the power supply will be increased.

The width modulated drive pulses are output from pin 3

via the pulse transformer Mo3 to power supply controller

pin 2. The rising edge of the drive pulse causes the switching transistor to conduct and the falling edge, which is synchronized to the line flyback pulse, switches off the transistor.

This arrangement prevents disturbances caused by the

switching-off time of the transistor from upsetting the

screen display.

Under / over voltage detection

The power supply controller has an internal monitor for

both under and over supply voltage on pin 16. The under

voltage threshold level is typically +8.5 V. Lower voltage

levels disable the output pulses.

The over voltage threshold is typically +15.7 V. Higher voltage levels disable the output pulses.

Restarting requires that the voltage level on pin 16 is first

decreased below +8.5 V and then increased to +11.8 V,

unless the voltage level across capacitor Co22 has reached

+2.5 V. In this case, circuit operation is completely stopped.

3

tor to7 conducts and transistor to4 is switched off.

The +12 Vp and +8 Vp voltages are absent, and therefore

the horizontal deflection stage will not operate.

ICo6 regulates +5 Vr, which is available in normal and recording modes, but not in service standby mode.

The tuning voltage +30 V for the tuner is regulated from

+130 V. The circuitry is located in the horizontal output stage

consisting of resistors Rk11...Rk114 and zener diode ZDk1.

Current limitation

As mentioned above, the source of the switching transistor is connected to ground via resistor network Ro18/19

and Ro21/22. The measured result is fed to input pin 3 of

ICo1. A double threshold system is used, first limitation

level (+0.6 V) against momentary overloads and a second

limitation level (+0.8 V) against very strong overloads.

When the first threshold level is reached, the switching transistor stops conducting until the end of the period, and a

new pulse is needed to start it conducting again. During

the first threshold period, capacitor Co22 is charged. If the

voltage level across Co22 reaches +2.5 V, the output will

be disabled. This system is called “repetitive overload protection”. However, if the overload subsides before +2.5 V

is reached, capacitor Co22 will be discharged and normal

operation will continue.

If a very powerful overload causes the second threshold

level to be reached, the output will immediately be disabled.

If the power supply stops because the first threshold has

been exceeded, it can be restarted by decreasing the supply voltage on pin 16 below +8.5 V and then increasing it

to +11.5 V.

If, however, the power supply stops due to exceeding the

second threshold, the circuit is stopped completely and can

only be restarted with mains switch.

Regulators / voltage switches

ICo4 regulates the +5 Vstby, which is always available when

the power supply is operating . Due to the micropower

system, there are no voltages available in standby mode.

ICo3 regulates the +12 Vr and +12Vp supply voltages. The

+12 Vr is available in normal and recording modes, but not

in service standby mode.

The +12 Vp can be switched off in recording mode by the

microcontroller. In this case the P_on line is high, transis-

4

RECEPTION

Tuner / IF

The tuner is known as a “front end” type tuner. This is

because the tuner block and IF block are both combined

into one complex module pack. Channel tuning is based

on a frequency synthesis system with a frequency range

of 48.25 MHz up to 855.25 MHz including cable and

hyperband channels.

In multistandard sets, both blocks are IIC-bus controlled.

The IIC-bus of the IF block has only one-way data traffic.

In BG standard sets, the IF block has no IIC-bus interface.

Multistandard IF block

The filter SAW501 operates as a picture signal filter. The

video IF signal is input to pins 28 and 29 of the Picture /

Sound Detector circuit, IC501.

The filters SAW502 (BG, DK, I, Nicam L) and SAW503

(Nicam L’, L/L’ AM) operate as sound signal filters. Standard selection takes place by diodes D501 and D502 and

transistors T502 and T503. Transistors are driven via pin 7

of the IIC-bus expander (IC502). Sound IF signals are input

to pins 31/32 (BG, DK, I, Nicam L), 1/2 (Nicam L’) and 4/5

(AM L/L’) of the detector circuit.

The AGC adjustment is implemented by potentiometer

P501 on pin 26. Pins 20 and 21 are inputs for standard

switches, which are controlled by the IIC-bus expander. The

AFC information is output from pin 11 to the tuner block

and onward to the IIC-bus. The AGC control is taken from

pin 27 to the tuner block. The tank coil of the FPLL-VCO is

connected between pins 14 and 19. This PLL reference coil

determines the stopping place of the found channel during the APSi. The VCO frequency is two times video carrier

frequency, 2 x 38.9 MHz = 77.8 MHz. For L’ standard requirements, the VCO frequency is switched to 67.8 MHz (2

x 33.9 MHz) using standard switches on pins 20 and 21,

and adjusted by the potentiometer P502 on pin 20.

The sound IF signal is output from pin 8 and the AM signal

from pin 7 onwards to the Multistandard Sound Processor, ICa2.

The CVBS signal is output from pin 23 to the group delay

correction circuitry and amplifiers consisting of transistors

T504...514 and associated components. The CVBS signal

is then fed to the Video Matrix Switch, ICq1.

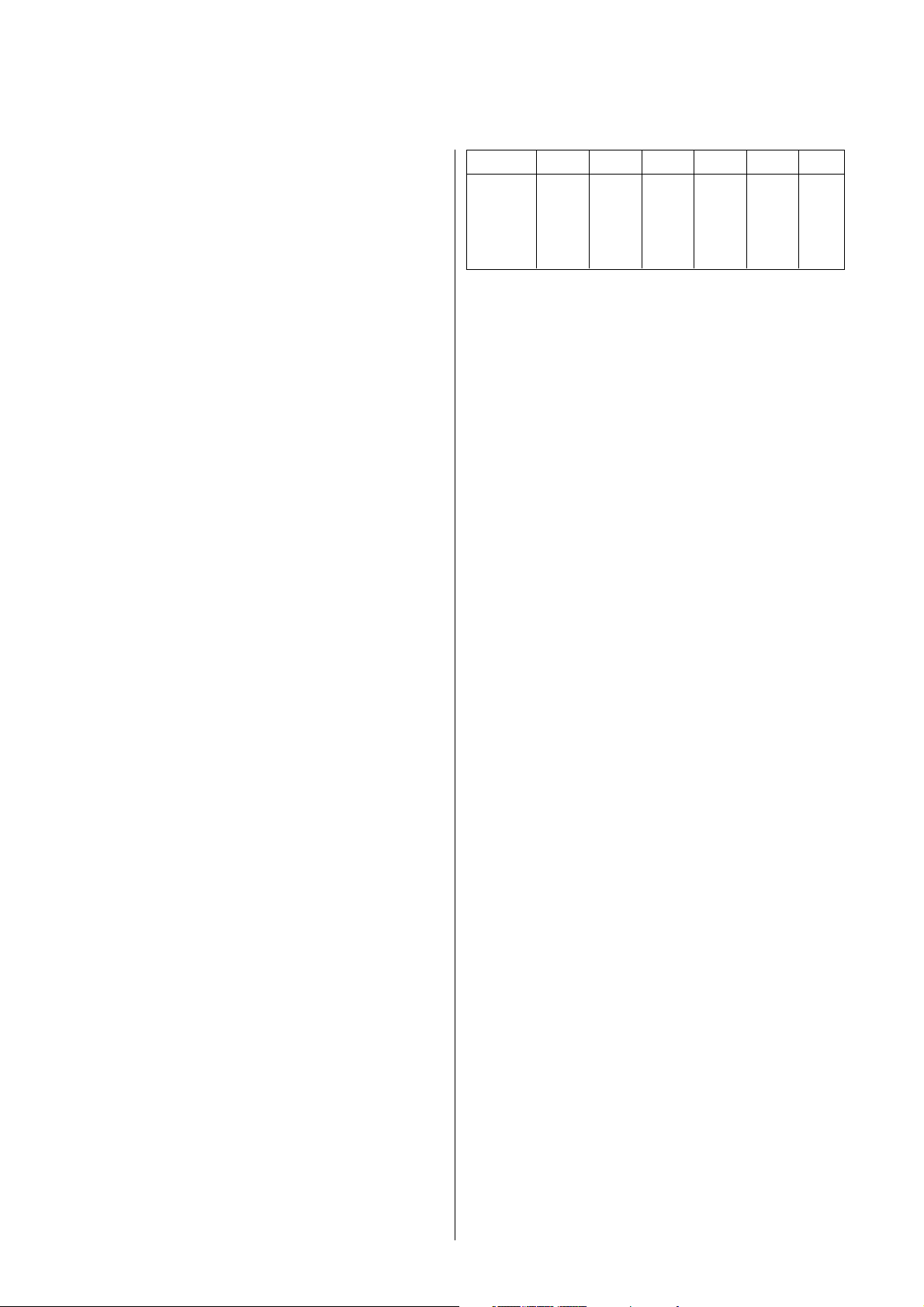

Standard pin 11 pin 13 pin 14 pin 7 pin 6 pin 5

B/G H L L L H H

I, K1 H L H H H H

D/K H H L H H H

L HHHLLL

Lí HHHHHL

Pin 11 drives input switches of IC501. Pin 11 is normally

high. During channel search (APSi), pin 11 goes

low. A low level on pins 27 and 28 of IC501

switches the video IF signal (instead of sound IF)

to the FPLL block. This is because the video band

is wider, and thus channel finding is more reliable.

Pin 13 drives the group delay correction circuitry

Pin 14 selects the output of the group delay correction

circuitry

Pin 7 selects the correct sound IF filter

Pin 6/5 drives input switches and AM demodulator, se-

lects right modulation and VCO frequency

BG standard IF block

The BG IF block is considerably simpler than the

multistandard IF block. Only one SAW filter is used and

the IIC-bus expander, group delay correction circuitry as

well as several switching transistors are omitted.

During channel search (APSi), the microcontroller (pin 47)

drives transistor T501 to conduct. A low level on pins 27

and 28 switches the video IF signal to the FPLL block in

order to make channel finding more reliable.

Tuning

Tuning is based on the APSi system (Automatic Program

search, Sorting and channel identification). The naming and

identification of the channels takes place using either the

PDC (Program Delivery Code), VPS (Video Programming

System), NI (Nation Identification) or Teletext header. Channel sorting is country dependant, and is therefore determined beforehand by the software.

The circuit IC502 operates as an IIC-bus expander (8-bit

shift register). Transistors T515 and T516 disconnect the

IIC-bus from pins 2 and 3 in order to eliminate possible

malfunctions on the IIC-bus when the TV set is switched

off. Standard definition takes place via the IIC-bus. The

microcontroller sends data to the shift register, the outputs change their state according to the data and strobe

pulse latches the outputs. The strobe pulse (high level) is

taken from the microcontroller (pin 47) to the base of transistor T517 and onward to pin 1. In addition, the base resistor (R556) of T517 operates as an indication of the installed IF module version. The value of this resistor depends on the module version. Pin 55 of the microcontroller

senses the voltage across this resistor and the base-emitter junction , and thus identifies the module version.

The data from the microcontroller determines the outputs

of IC502 according to the transmission standard as follows:

AUDIO SECTION

r

- Sound Processor

- Audio Power Amplifier

- Headphone Amplifier

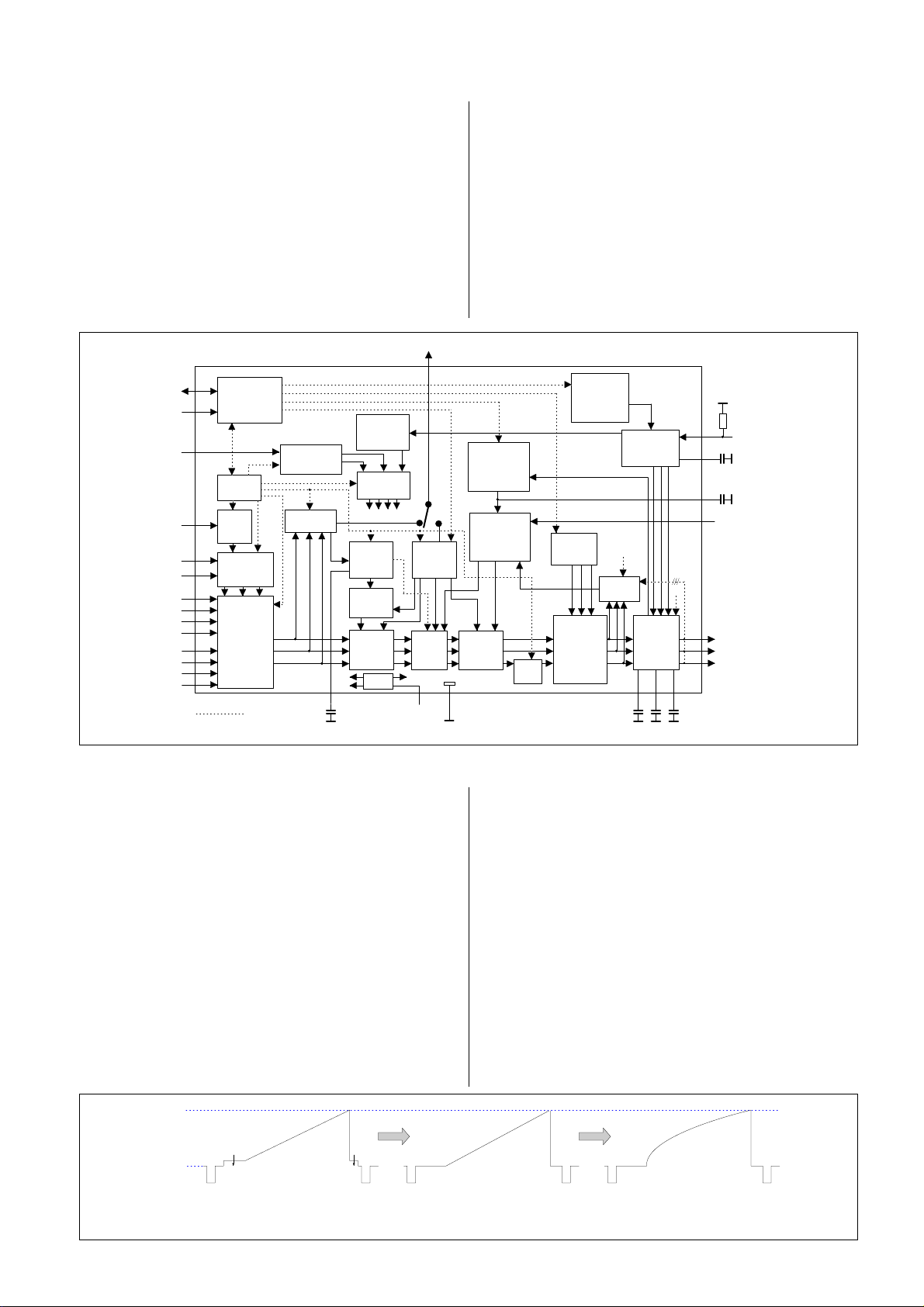

Multistandard Sound Processor, ICa2

5

General

The MSP3410D is a single-chip Multistandard Sound Processor which uses CMOS technology. The circuit is controlled by the microcontroller via the IIC-bus.

The sound processor performs simultaneous digital demodulation and decoding of NICAM-coded TV stereo

sound, as well as demodulation of FM-mono TV sound. As

an alternative, a two carrier FM system (according to the

German terrestrial specs, A2 stereo), or satellite specs can

be processed by the sound processor.

All FM modulated signals over the range 0.2 MHz to 9.0

MHz can be handled.

The sound processor can select the audio signal source,

convert analog audio signals into digital form, de-emphasize in several ways - including Wegener Panda 1, 50/75 µs

and J17, perform digital FM-identification decoding and

dematrixing, and perform digital baseband processing. It

can also control the volume separately for loudspeaker and

headphones, control bass, treble, graphic equalizer and

balance, perform pseudo stereo and basewidth enlargement, as well as convert digital audio signals into analog

form by using fourfold oversampled D/A-converters. This

provides an audio spectrum from 20 Hz to 16 kHz with a S/

N ratio of 85 dB.

The sound processor requires an 18.432 MHz crystal, whose

nominal free running frequency should be no more than

±1 kHz, which means a tolerance of ±0.005 %.

An audio signal to the sound processor can be taken from

the IF-section, scart 1, scart 2, or scart 3 / camera / VGA-

audio connector (or scart 4) sources. The source is internally selected in the sound processor. The processed audio signal is fed to several outputs such as loudspeaker

amplifier / adjustable audio output module, headphone

amplifier, scart 1 and scart 2 connectors (scart 3 optional).

The circuit also has a separate output for a subwoofer

amplifier including highpass filters for the loudspeaker

outputs and lowpass filters for the subwoofer output as

integrated into the chip. The upper barrier frequency is

programmable from 50 Hz to 400 Hz in 10 Hz steps. Depending on the programming of the upper barrier frequency, the lower barrier frequency for the loudspeaker

channels will also be changed automatically.

An IIS-bus interface with two data inputs is available for

optional audio feature purposes.

In some TV versions, the sound processor may be of type

MSP3400. The only difference is that MSP3400 cannot identify or process Nicam signals.

The sound processor is split into three functional blocks:

- Demodulator and decoder section

- Digital signal processing section performing audio

baseband processing

- Analog section containing two A/D-converters, nine D/

A-converters and channel selection

The simplified block diagram below shows the architecture of the MSP3410D.

Sound IF

ANA_IN 1+

ANA_IN 2+

Mono

Mono_in

SC1_IN_L

Scart 1

SC1_IN_R

SC2_IN_L

Scart 2

SC2_IN_R

SC3_IN_L

Scart 3

SC3_IN_R

SC4_IN_L

Scart 4

SC4_IN_R

ADR-bus

Demodulator

SDA SCL

2

I C-bus Interface

Ident

A/D

A/D

2

I S1/2L/R

2

I S1/2L/R

FM1 / AM

FM2

NICAM A

NICAM B

Ident

Digital

Function

Processing

SCART_L

SCART_R

SCART Switching Facilities

LOUDSPEAKER L

LOUDSPEAKER R

SUBWOOFER DACM_SUB

HEADPHONE L

HEADPHONE R

SCART1_L

SCART1_R

SCART2_L

SCART2_R

2

2

I S_DA_OUT

2

I S_DA_IN2

2

I S Interface

D/A

D/A

D/A

D/A

D/A

D/A

D/A

D/A

D/A

2

I S_CL

2

I S_WSI S_DA_IN1

DACM_L

Loudspeake

DACM_R

Subwoofer

DACA_L

Headphone

DACA_R

SC1_OUT_L

Scart 1

SC1_OUT_R

SC2_OUT_L

Scart 2

SC2_OUT_R

6

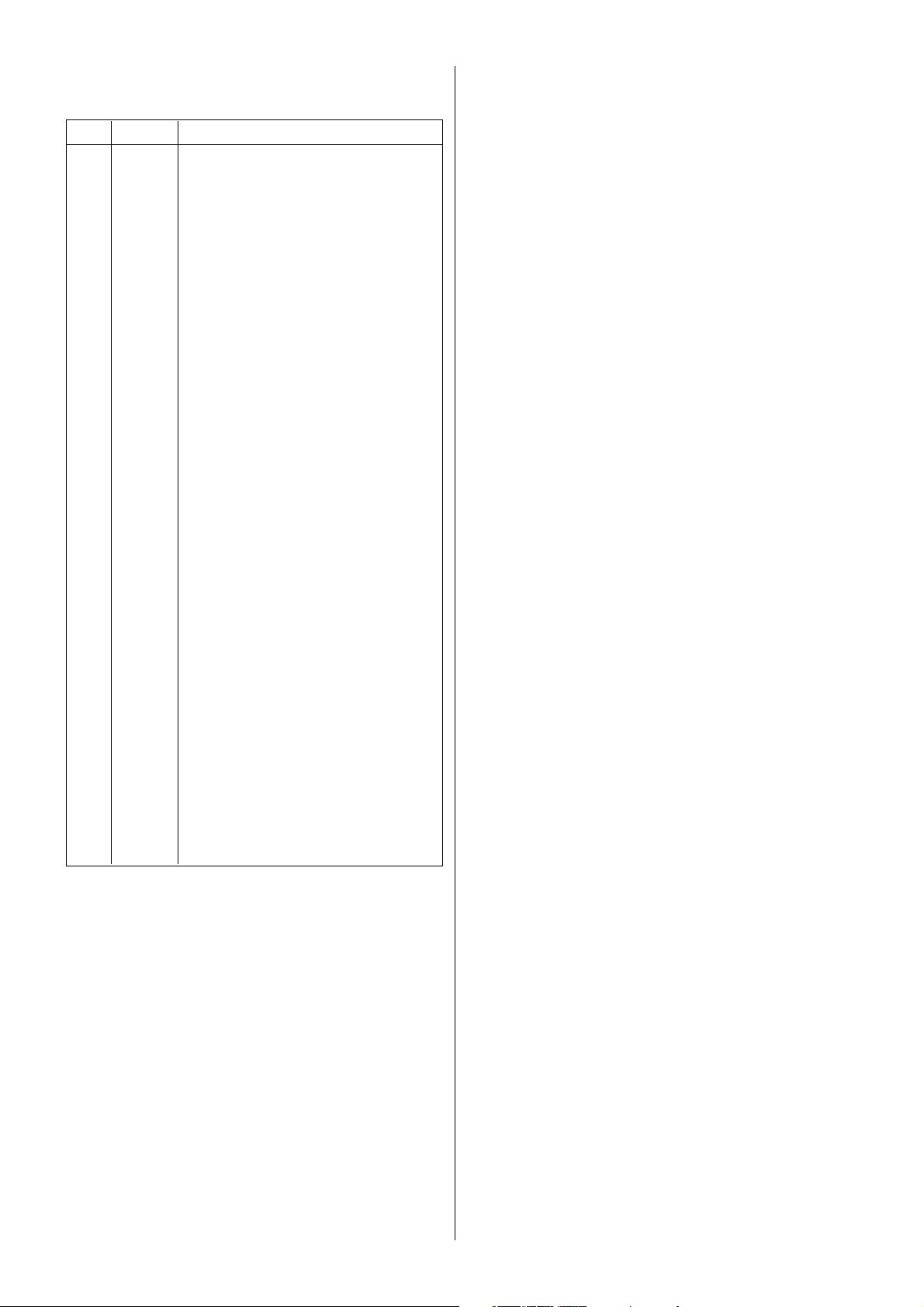

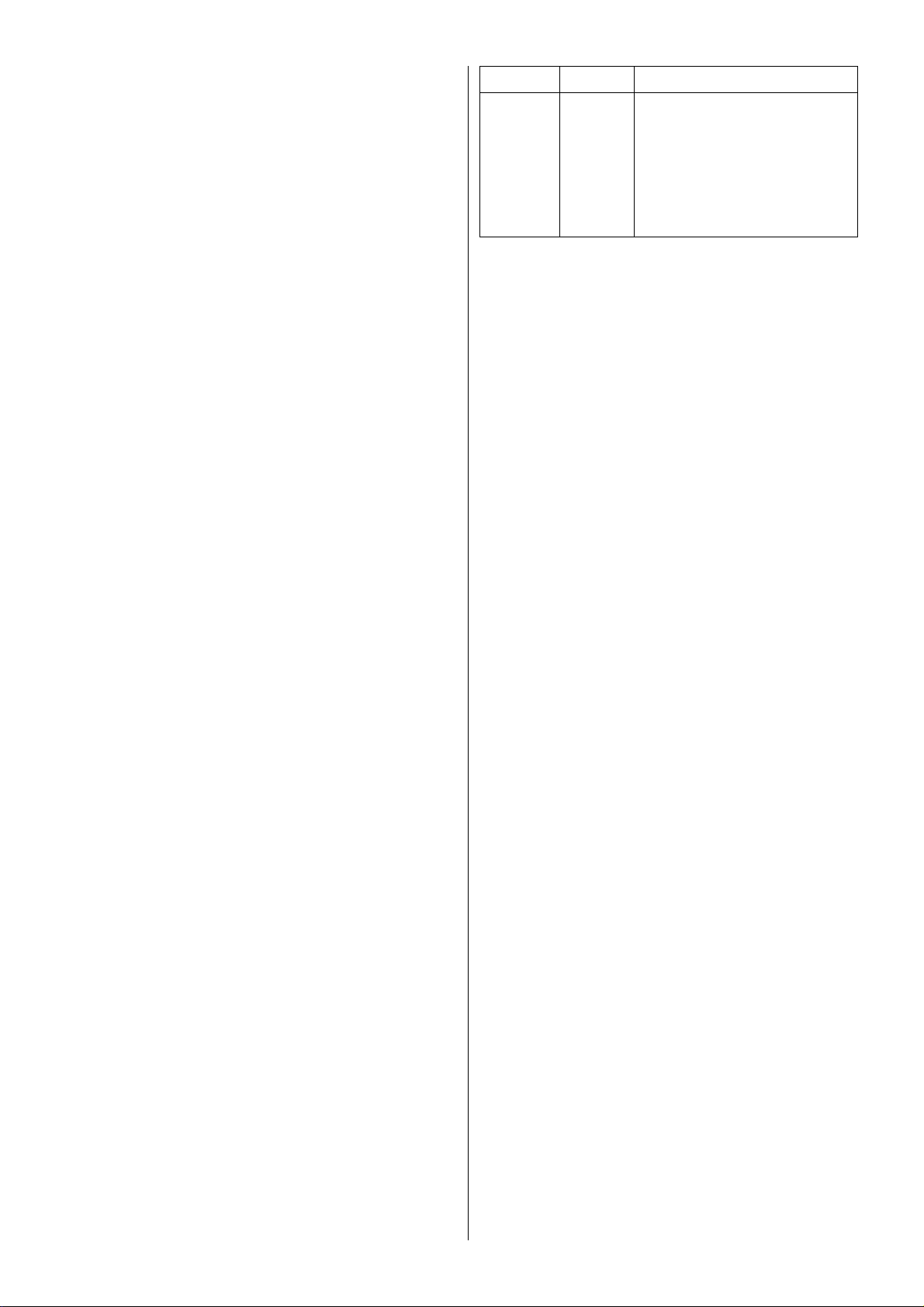

The pin functions of the Sound

Processor:

ance of external speakers is 8 Ohm. When an external

speaker is used, the internal speaker is muted by a switch

in the speaker connector.

Pin I / O Short description

04 O DSP reset and off by low

05 O Subwoofer off by high

07 I Supply voltage +5 Vr

09 I I2C clock (SCL)

10 I/O I2C data (SDA)

11 O I2S clock

12 I/O I2S word select

13 O I2S data output

14 I I2S1 data input

18 Digital power supply +5Vr

19 Digital ground

20 I I2S2 data input

24 I MSP power-on-reset by low

25 O Headphone output, R

26 O Headphone output, L

28 O Loudspeaker output, R

29 O Loudspeaker output, L

31 O Subwoofer output

33 O Scart output, R

34 O Scart output, L

36 O Scart output, R

37 O Scart output, L

38 Volume capacitor (Hp amp)

39 Analog power supply +8.0V

40 Volume capacitor (Ls amp)

42 Analog ref V, high V part

43 I Scart input, L

44 I Scart input, R

46 I Camera input, L

47 I Camera input, R

49 I Scart input, L

50 I Scart input, R

52 I Scart input, L

53 I Scart input, R

54 Ref voltage IF A/D conv

55 I Mono input

57 Analog power supply +5Vr

58 I IF input 1

59 I IF input common

60 I IF input 2 (Tuner SIF)

62 I Crystal osc 18.432 MHz

63 O Crystal osc

Headphone Amplifier, ICa3

Audio signals from the sound processor are fed to the inverting input pins 2 (L) and 6 (R). Outputs to the headphone

connector are from pins 1 (L) and 7 (R). There is a switch in

the headphone connector that informs the microcontroller

(pin 1), that headphones are connected. The headphone

volume control then appears in the OSD in addition to the

loudspeaker volume control.

Audio Power Amplifier, ICa1

The audio signal is amplified using the TDA2616 dual channel hi-fi Audio Power Amplifier. The amplifier has a builtin protection system against short circuits and thermal

overloads. It also has an internal input mute circuit that

silences unwanted signals at the inputs when the TV set is

switched on or off.

Audio signals from the audio processor are fed to pins 1

(L) and 9 (R). A logical low on pin 2 mutes the amplifier.

The mute control signal is taken from the microcontroller

(pin 51) via transistors ta10, ta4 and ta3. A high level on

microcontroller pin 51 causes a so-called “central mute”,

which means that each of the audio power amplifiers are

muted.

The supply voltage +28 V is taken from the power supply

to pin 7. The amplified audio signals for the loudspeakers

are output on pins 4 (L) and 6 (R). The impedance of the

internal loudspeakers is 8 ohm and the minimum imped-

VIDEO SECTION

7

The video section is divided into the following functional

blocks:

- Video Matrix Switch / Scarts

- Colour Decoder / Sync Processor

- Baseband Delay Line

- Feature Boxes

- RGB Video Processor

- CRT module

- Teletext

Video Matrix Switch, ICq1

The TEA6417 is an IIC-bus controlled signal switch, which

makes it possible to switch 8 input sources to 6 outputs.

Each output can be connected to only one input, but one

input may be connected to several outputs. The bandwidth

is 15 MHz and nominal gain from input to output is 6.5 dB.

All switching possibilities are controlled via the IIC-bus

using pins 2 (SDA) and 4 (SCL). The circuit operates with

+10 V supply voltage, that is fed to pins 9 and 12. The +10

V is regulated from +12Vr by zener diode Zdq1.

The inputs and outputs are connected as follows:

Input Signal Source

1 CVBS Scart 3

3 CVBS Scart 1

5 C Scart 2

6 CVBS / Y Scart 2

8 CVBS / Y Cam connector

10 C Cam connector

11 CVBS Tuner

20 CVBS PIP tuner

Output Signal Target

13 CVBS / Y Decoder / Comb filter

14 C Decoder / Comb filter

15 CVBS / Y PIP module

16 C PIP module

17 CVBS / Y Scart 2

18 CVBS Teletext

The system is based on the “P50” standard and enables,

for example, transferring of channel tuning information and

EPG (Electrical Program Guide) programming.

Scart 2

In addition to the S-VHS input possibility, scart 2 is designed

to output the S-VHS signals, which are taken from the camera connectors. Output of the luminance signal takes place

via transistor Tq1 and chrominance via tt3 and tt2.

Scart 2 also operates as an AV-link connector.

Scart 3 (option)

Scart 3 is an optional connector having the same characteristics as scart 1.

More detailed information can be found in the section entitled “Options, TA710”.

Colour Decoder / Sync Processor, ICd1

General

The TDA9143 is an IIC-bus controlled, alignment-free PAL /

NTSC / SECAM decoder / sync processor.

The colour decoder is able to process CVBS as well as Y / C

signals. The internal fast switch can select either the Y signal with the UV input signals, or YUV signals made up of

RGB input signals.

The sync processor provides a two level sandcastle pulse

(SC), a horizontal sync pulse (HA) and a vertical sync pulse

(VA).

Input switches

The circuit has a two pin input for the CVBS (pin 26) or Y / C

(pins 26 and 25) input signals. Selection between the signals is carried out using the IIC-bus.

RGB colour matrix

The RGB signals from scart 1 (or scart 3 ) connector are fed

to input pins 19 (B), 20 (G) and 21 (R). The RGB colour matrix converts RGB signals into the YUV signals. The desired

input signal, between the converted YUV and decoded YUV

signals, is selected by the fast switch. This switch is controlled by the fast blanking signal on pin 18.

Scart 1

Scart 1 is fully connected, thus RGB input is also available

from it . In RGB mode, the fast blanking signal from scart

pin 16 is fed to the colour decoder pin 18 and via tq3, tq4,

Cq32 (and NAND gate icf4-4) to the microcontroller pin 6.

The RGB status signal is fed to the microcontroller in order

to activate the correct H-shift setting. It also enables the

colour decoder to choose the input between the RGB signal and the processed YUV signals. Selection takes place

by a switch block in the colour decoder via the IIC-bus.

Scart 1 has a fixed output connection for the Tuner CVBS

from scart pin 19 via transistors tq9 and Tq2.

Scart 1 also operates as an AV-link connector. The AV-link

output is from microcontroller pin 2, onward via transistor

tq7 and scart pin 10. The AV-link input is from the same

scart pin, onward via diode dq4 and transistor tq8 to the

microcontroller pin 63. The AV-link system makes it possible to transfer data between the TV set and e.g. a video

recorder.

Luminance processing

From the input pin 26, the CVBS / Y signal is fed via the Y

clamp circuit to the gyrator-capacitor type notch filters, including adjustable luminance delay and chrominance trap.

The luminance delay compensates the delay, that is caused

by the external baseband delay line for the UV signals. The

chrominance trap can be switched to 4.43 MHz (PAL / NTSC),

4.28 MHz (SECAM) or 3.58 MHz (NTSC). Switching is con-

trolled by the standard identification circuit. PAL Y, NTSC

3.58 Y (from the comb filter ) and S-VHS Y signals bypass

the chrominance notch filters in order to preserve the signal bandwidth. The bypass function takes place automatically via the IIC-bus in S-VHS mode and in PAL / NTSC 3.58

reception, if the comb filter is installed. After the chroma

trap, the Y signal is fed to the switch stage and is output

from pin 12 to the feature box module.

8

Chrominance processing

From the input switch, the CVBS / C signal is fed through

the ACC amplifier to the chroma bandpass filters. PAL C,

NTSC 3.58 C (from the comb filter) and S-VHS C signals

bypass these bandpass filters in order to preserve the signal bandwidth. The chrominance is then fed to the standard identification and colour decoder stages.

The standard identification circuit is a digital circuit with

no external components. The crystals on pins 30 (reference crystal) and 31 (second crystal) specify the standards

which can be decoded. The IIC-bus is used to indicate which

crystals are connected in order to allow proper setting of

the calibration circuits. The components on pin 29 form

the colour PLL filter. Pin 23 drives the multiplexer circuit

on the comb filter module to bypass the S-VHS signals in

the multiplexer (“L”) or to feed signals onwards to the comb

filter IC (“H”). In addition, pin 23 feeds out the subcarrier

frequency (Fsc) of the active crystal to the comb filter IC.

After the PAL / NTSC demodulator and SECAM

demodulator, the signals are taken to the switch stage,

which is controlled by the standard identification circuit.

Finally, the colour difference signals are output to the

baseband delay line from pins 2 (U) and 1 (V).

From the delay line, the colour difference signals are input

to pins 3 (U) and 4 (V), then onward to the switch stage

and output from pins 14 (U) and 13 (V) to the feature box

module.

Sync processing

The CVBS / Y signal is fed through the sync separator to

the horizontal PLL and to the vertical sync separator.

The main part of the sync circuit is a 432 x fH (6.75 MHz)

oscillator. This frequency is divided by 432 to lock phase

discriminator 1 to the incoming signal. The time constant

of the loop can be selected to be either fast, auto or slow

mode using the IIC-bus. The free-running frequency of the

432 x fH oscillator is determined by a digital control circuit,

which is locked to the active crystal. Components on pin

24 form the horizontal PLL. The phase loop can be unlocked

using the IIC-bus. This is to facilitate On Screen Display

information. If there is no input signal or a very noisy signal, the phase loop can be unlocked to give a stable line

frequency and hence a stable OSD.

The horizontal sync pulse (HA) is fed from the timing generator via output pin 17 to the Feature box.

The vertical divider system has a fully integrated vertical

sync separator. The divider can handle both 50 Hz and 60

Hz systems. It can either determine the field frequency

automatically or it can be set to the desired frequency using the IIC-bus.

The divider system consists of a line counter, a norm counter , a timing generator, and a controller. The system operates at 432 times the horizontal line frequency. The line

counter receives enable pulses at twice the line frequency,

so that it counts two pulses per line. This count result is

fed to the controller. The controller can be in one of three

count states, norm, near-norm or no-norm. When the counter is in the norm state, it automatically generates a vertical sync pulse (VA) from the timing generator. The VA pulse

is fed via output pin 11 to the Feature box.

Noise detector

The decoder includes an internal S/N ratio detector, which

was originally designed to control the PALplus signal process. During PALplus transmission, the detector measures

the S/N ratio of the input signal on pin 26. When the S/N

ratio is over 20dB, the signal is accepted and the helper

signal is processed in the PALplus decoder. If the S/N ratio

is below 20dB, the PALplus process is disabled, and the

signal is handled as a normal signal. The detector can be

activated / deactivated via the IIC-bus.

In the Multi Concept, this detector is used to drive the APSi

system to accept or bypass tuned channels. The detector

controls the APSi system via the IIC-bus and it works only

during the automatic channel search.

However, the limit value of the bypass criteria (fixed 20dB)

seems to be too high for this purpose and therefore the

APSi may be too sensitive and bypass channels that it could

accept.

On the other hand, if the tuning system does not include

any signal level qualification, the APSi system accepts all

multiple and very noisy channels.

Utilizing an existing detector and avoiding both above

mentioned disadvantages, an external LPF filter is implemented. This filter is located at the luminance / CVBS input

(pin 26) and it consists of switching transistors tq10 / tq11,

and RC filter rq85 / cq45.

The RC-coupling is designed to filter high frequencies

(noise) from the luminance / CVBS signal.

When the S/N ratio of the tuned signal on pin 26 is over

20dB, the filter is not activated, but the channel is accepted

as such and it will be memorized and named.

If the S/N ratio is below 20dB, the detector causes a high

level on output pin 16. Transistor tq11 conducts and the

RC-coupling filters noise from the signal improving the S/

N ratio at the decoder input. When this noise-filtered signal is fed to the detector, it considers the S/N ratio to be

better than it actually is and accepts it. This channel will be

memorized, but not named.

In any case if the S/N ratio of the noise-filtered signal stays

below 10dB, it will be completely bypassed.

By tricking the detector in this way, the signal level qualification is reduced from an S/N ratio of 20dB to 10dB.

Sandcastle

The sync part also generates a two level sandcastle pulse

(SC) from pin 10. This pulse is used only for timing purposes in the baseband delay line.

IIC-bus

The decoder / sync processor is connected to the IIC-bus

via pins 5 (SCL) and 6 (SDA).The bus address is determined

by connecting pin 22 to +8 V.

The output pin 16 controls the filtering method of the comb

filter, either PAL 4.43 MHz (“L”) or NTSC 3.58 MHz (“H”).

The input / output pin 15 is primarily used to detect whether

the comb filter module is installed or not, by checking the

transistor tc3 (base-collector junction). In addition, pin 15

controls the comb filter IC to be in the filtering mode (“H”)

or in the internal bypass mode (“L”).

Baseband Delay Line, ICd3

General

The circuit TDA4665 is a delay line which requires no adjustments. It includes two colour difference comb filters

and uses switched capacitor techniques.

Each comb filter consists of an undelayed signal path and

a 64 µs delayed signal path.

In PAL mode, comb filters operate as a geometric adder to

carry out the requirements of PAL demodulation.

In NTSC mode, the comb filters suppress cross-colour interference.

In SECAM mode, the circuit repeats the colour difference

signal on consecutive horizontal scan lines.

Functional description

The colour difference signals are fed to input pins 14 (U)

and 16 (V). First the signals are clamped, and then they are

fed through pre-amplifiers to the undelayed / delayed signal paths. All the switching signals needed in the delay

process are generated from the 3 MHz master clock frequency. This frequency is divided from the internal 6 MHz

VCO, which is line-locked by the sandcastle pulse (SC). The

SC pulse taken from the sync processor is fed to pin 5.

Delay processed colour difference signals are fed through

the addition circuits to the output buffers and are finally

output on pins 12 (U) and 11 (V).

Feature boxes, DB7**

The feature box has two main functions, to perform the

conversion of the 50 (60) Hz scan to 100 (120) Hz scan format and to improve the picture quality. Depending on the

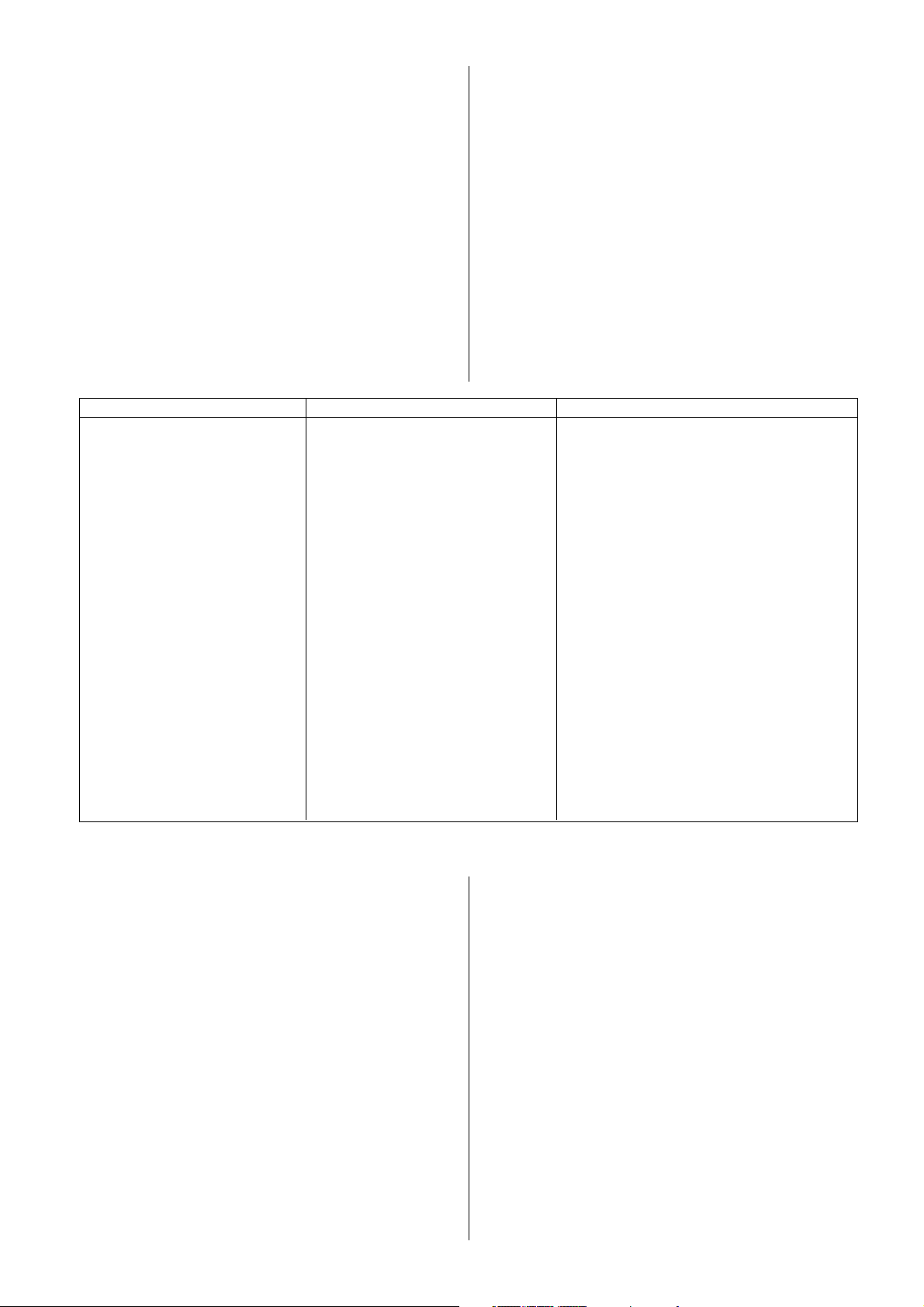

Feature DB711 DB710

100 Hz flicker reduction - field repetition - median interpolation

Line flicker reduction - no - median filter

Noise reduction (Y / C) - no - motion adapted

Aspect ratio conversions

- horizontally - ±12.5 and ±25 % - ±12.5 and ±25 %

- vertically - by deflection - +12.5 and +25 % (by DSP)

- hor picture position - fully programmable - fully programmable

- lift - no - yes

- side panels - programmable grey - programmable grey

Picture sharpening - vertical / horizontal peaking - vertical / horizontal peaking

- CTI, LTI - CTI, LTI

Histogram equalizing - yes - yes

Still picture - yes - yes

A/D conversion - YUV 4:1:1 signal format - YUV 4:1:1 signal format

- 8-bit per component - 8-bit per component

- input signal amplitude adapted - input signal amplitude adapted

- sampling rate - 13.5 MHz - 13.5 MHz

D/A conversion - Y-component 9-bit - Y-component 9-bit

- U- and V-component 8-bit - U- and V-component 8-bit

- sampling rate - 20.25 MHz ... 36 MHz - 20.25 MHz ... 36 MHz

Field memory - 3 Mbit (1 x 3 Mbit) - 6 Mbit (2 x 3 Mbit)

Synchronizing - line locked operation - line locked operation

- crystal based sync generation - crystal based sync generation

chassis version, there are few different feature boxes with

more or less variant features. The whole signal processing

takes place digitally and all functions are controlled using

the IIC-bus.

The basic version is DB711, that contains only one 3 Mb

field memory. The use of one field memory allows the conversion of 50 (60) Hz video to 100 (120) Hz video, but not

line flicker and noise reduction or vertical zooms. This

module is designed for TV sets with a 4:3 picture aspect

ratio.

The DB710 version contains two 3 Mb field memories, so

noise reduction and vertical zooms are also implemented.

The DB710 (and DB700) are designed for TV sets with both

a 4:3 and 16:9 picture aspect ratio.

The DB700 version is called a “full feature” version, that

includes in addition to the features of DB710, a signal interface in accordance with the VGA standard.

9

Feature box DB711

The main components of the DB711 are an A/D converter,

field memory (FM), picture quality improvement circuit

(IQTV2), digital phase locked loop (DPLL) and deflection

controller.

Y, U and V inputs

The luminance (Y) and colour difference signals (U and V)

are taken from the colour decoder to the module connector Q101, pins 6 (Y), 7 (U) and 8 (V). Each signal is first

amplified and then low pass filtered. After that the signals

are fed via buffer transistors to the A/D-converter, pins 63

(Y), 50 (U) and 31 (V).

Analog to digital converter, ic9

Analog to digital conversion is carried out using A/D-converter circuit TLC5733, which contains three separate 8-bit

A/D-converters. Each signal is clamped using the horizontal sync pulse (HOUT1) on pin 55 and then converted to

digital form. The converters sample the input signals at a

13.5 MHz sampling rate. The sampling frequency is taken

to pin 56. The converters are controlled by reference

voltages REFH (pins 61, 52 and 29) and REFL (pins 1, 48

and 33).

If an overflow is detected, the reference voltages will be

either increased or decreased. Information about a possible overflow is taken from the luminance output data (pins

6...13) and fed to the NAND gate ic28 and onward to the

DPLL circuit ic11 pin 42 (ADC_OVFL). The circuit detects

the overflow data and if necessary, it changes the width of

the pulses on pin 43 (PWM_REF). These width modulated

pulses are fed to the low pass filter consisting of transistors t1 and t9 and associated capacitor network. The low

pass filter generates both voltages, the REFH and REFL,

and these are fed to control the A/D-converters.

After converters the signals are fed to the output format

multiplexer, which is controlled by pins 45 (mode1) and 46

(mode0). The combination of a logical low on both pins

causes the output data format of the YUV signals to be

4:1:1. The U and V components have 1/4 of the signal

strength of the Y component.

The luminance data bus (pins 6...13) is eight bits wide and

the chrominance data bus (pins 17...20) four bits wide.

10

Field memory, ic14

Field Memory 1 (FM1) is a 3 Mb, high-speed Dynamic Random Access Memory (DRAM). The circuit is used as a

memory circuit in the 50 to 100 Hz upconversion and in

certain horizontal zoom functions.

The luminance and chrominance data are input from the

A/D-converter to pins 2...13.

The write operation is performed using the input control

signals RSTW (reset write) on pin 15, SWCK (serial write

clock) on pin 14 and ENW (enable write) on pin 16. The

write clock (SWCK / CLK27_1) frequency is 27 MHz. The

ENW signal enables memory writes only on every second

clock cycle.

The read operation is performed using the read output

control signals RSTR (reset read) on pin 22, SRCK (serial

read clock) on pin 23 and ENR (enable read) on pin 21.

The read clock (SRCK / CLK) frequency varies depending

on the picture format. The IQTV is able to generate the

following formats (implementation depends on the feature

box and software):

36.000 MHz = - 25.0 % hor compression

30.375 MHz = - 12.5 % hor compression

27.000 MHz = 0 no compression / no expansion

23.625 MHz = + 12.5 % hor expansion

20.250 MHz = + 25.0 % hor expansion

All vertical compression is carried out by the deflection

processor. Only the DB710 and DB700 comprise the vertical expansions (FM2 required).

The luminance and chrominance data are output to the

IQTV2 circuit from pins 24...35.

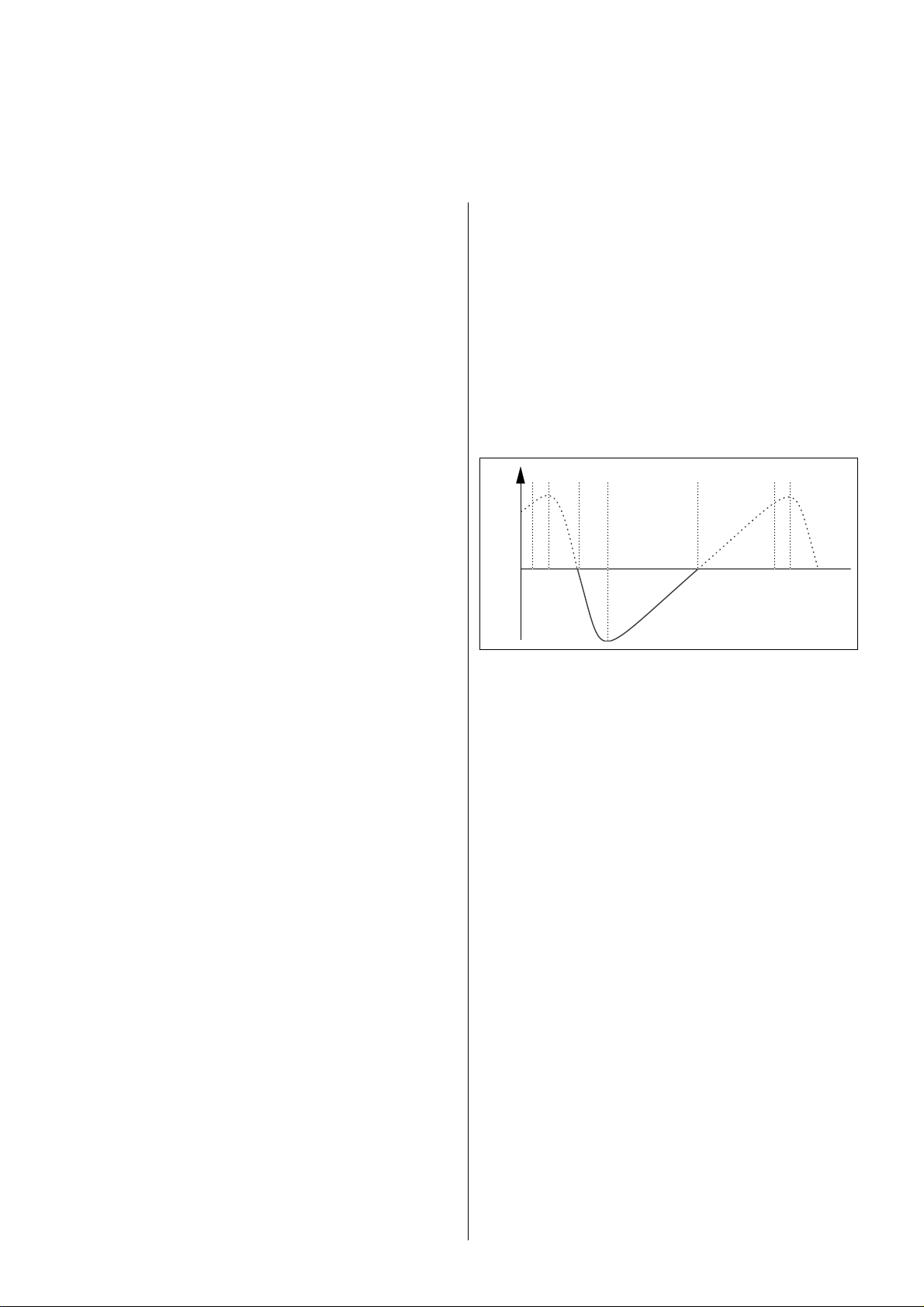

IQTV2 circuit, ic18

The main function of the IQTV2 (Improved Quality TV) circuit is to perform the upconversion, which reduces the

flicker caused by interlacing. The idea of the upconversion

is that the interlaced 50 (60) Hz scan will be converted to a

100 (120) Hz scan format.

The flicker reduction (upconversion) in the DB711 module

is based on a field repetition algorithm for both luminance

and chrominance signals. The field repetition method uses

zero degree interpolation and displays the original field

twice.

The characteristics of the IQTV2 make it possible to utilize

both the horizontal and vertical zoom functions, but because there is only one field memory, only the horizontal

zoom can be utilized. Thus all vertical zoom functions are

performed using the deflection controller circuit.

Picture sharpening is implemented not only in the horizontal direction, but also in the vertical direction. The peaking stage consists of high pass and band pass filters which

emphasize the middle band frequency range where most

of the details and edges are located.

The colour transient improvement (CTI) makes the slopes

of colour edges steeper by controlling the inputs between

the delayed, look ahead and current chrominance signals.

A new feature in the CTI of the IQTV2 circuit is that the

center of the transient always stays at the same point in

comparison with input and output signal.

The luminance transient improvement (LTI) is performed

by taking the 3-point median of three intermediate signals,

peaked, maximum and minimum. As a result of the LTI

process the luminance transients are made steeper without any undershoots or overshoots.

The histogram equalization (HEQ) system is designed to

carry out an automatic contrast enhancement. The system

is designed to give a uniform histogram for the output picture signal, changing the original pixel values for new ones

using a non-linear mapping. As a result, both under and

over contrasted picture signals are equalized to have the

desired contrast and gray level distribution.

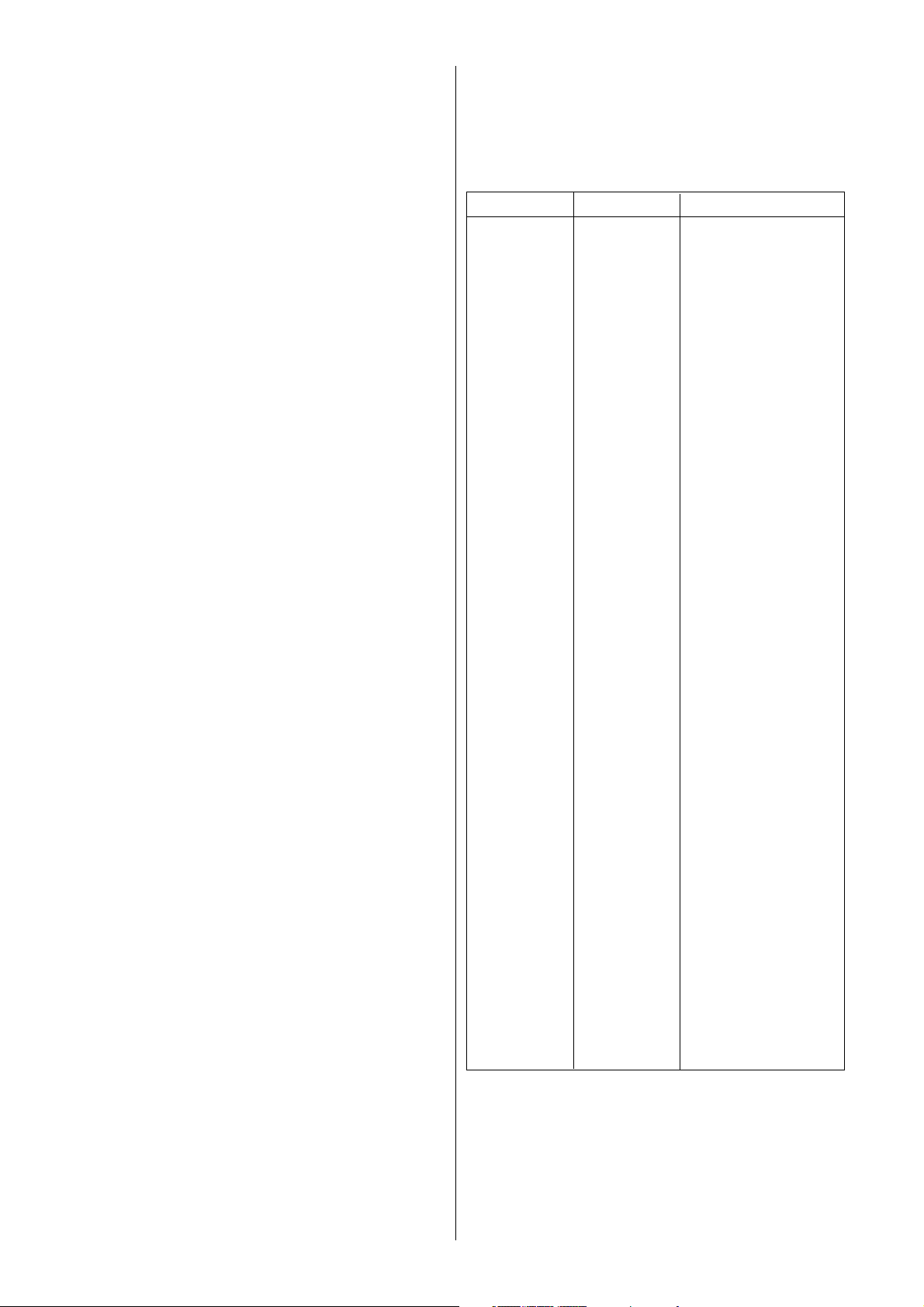

Pin description of ic18:

Pin Symbol Description

1, 5-12, 14-15,

18-21, 100 D0_FM1...

D15_FM1 Data input from FM1

2, 16, 41,

56, 81 +3.3V (core) Power supply for logic

3, 28, 61, 77 +5V (i/o, AC) Power supply for I/O

4, 29, 60, 69 GND (i/o, AC)

Ground for I/O

13, 34, 78 +5V (i/o, DC) Power supply for I/O

17, 37, 57,

79, 99 GND (CORE) Ground for CORE

22 FM1_ENR Read enable, FM1

23 FM1_ENW Write enable, FM1

24 FM1_RSTW Reset write, FM1

25 HS_IPLL Horizontal sync

26 FM2_ENW Write enable, FM2

27 FM2_ENR Read enable, FM2

30 CLK_IPLL

(CLK27_1) System input clock

(27 MHz)

31 CLK_OPLL

(CLK) System output clock

32 VS_50 Vertical sync

33 HS_OPLL Output horizontal sync

35 HS32 32 kHz horizontal sync

36 FM_RSTR Reset, FM2W/R, FM1R

38 SDA IIC-bus, serial data

39 SCL IIC-bus, serial clock

40 FSY Format sync for ADC

42 +5V (analog) Analog supply voltage

for DAC

43 VBIAS Analog

44, 47, 49, 51 GND (analog) Ground for DAC

45 VT Analog

46 Vref Current reference

for DAC

48 AY Analog Y output

50 AV Analog V output

52 AU Analog U output

53 RST System reset

54 TEST_EN Test mode enable

55 VS_50_100 Double frequency

vert sync

58-59, 62-67,

70-76, 80 Q0_FM2...

Q15_FM2 Data output to FM2

68 DIG_OUT8 9th bit in digital output

82-89, 91-98 D0_FM2...

D15_FM2 Data input from FM2

90 SYNC_SEL Selection of sync mode

After digital signal processing (DSP), the IQTV2 circuit converts the signals to analog form and outputs them from

pins 48 (Y), 52 (U) and 50 (V).

The colour difference signals are low pass filtered and output from module pins Q102-3 (U) and Q102-2 (V). The luminance signal is first amplified by transistors t18 and t19,

then the signal is low pass filtered and output from module pin Q102-4.

DPLL1 circuit, ic11

The DPLL (Digital Phase Locked Loop) circuit generates all

line locked clock and sync signals for the whole digital signal processing system. The circuit is IIC-bus controlled and

it needs only a few external components, one of them a 27

MHz crystal. The 27 MHz clock operates as a main clock,

from which the other clock frequencies are generated using suitable factors.

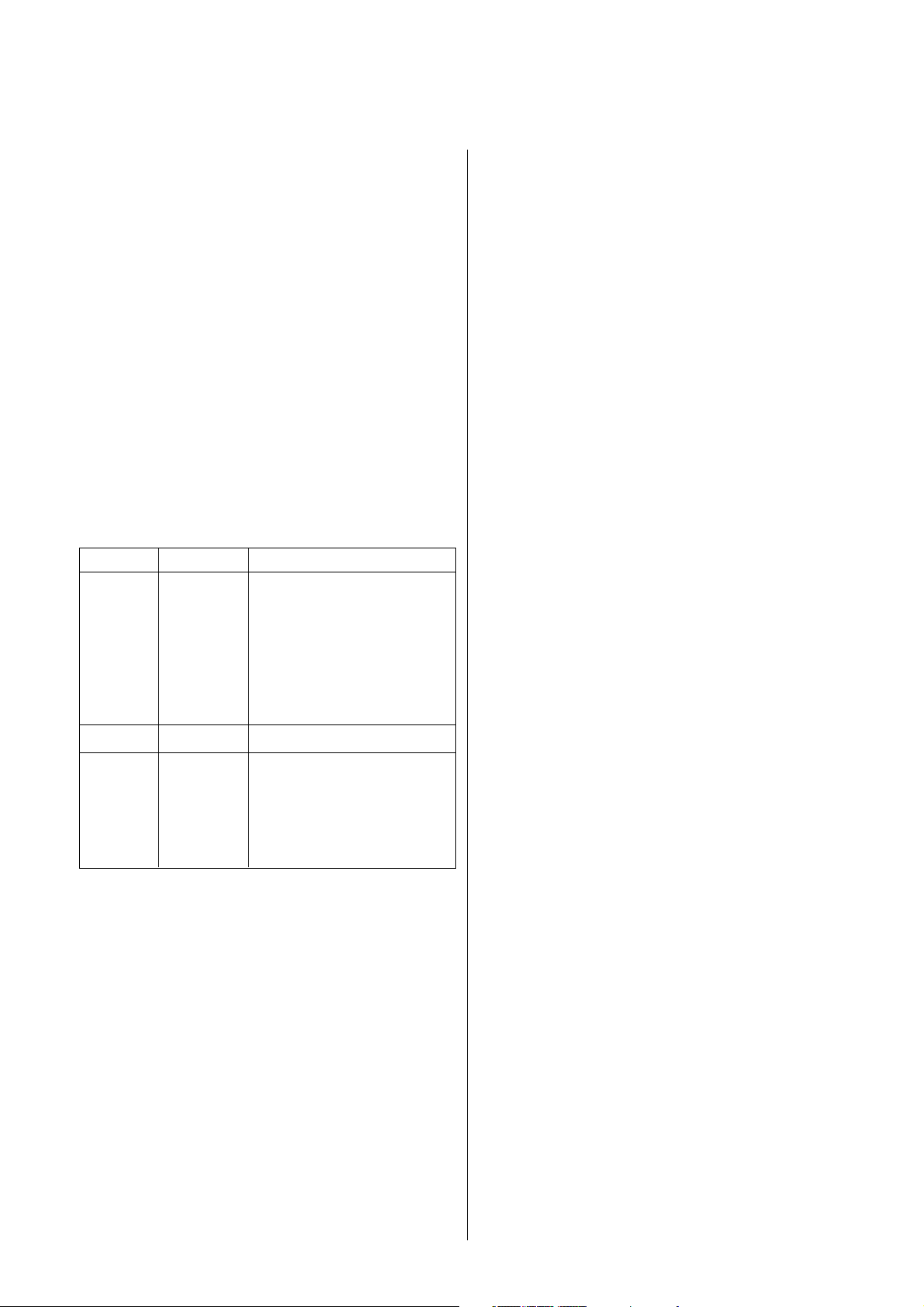

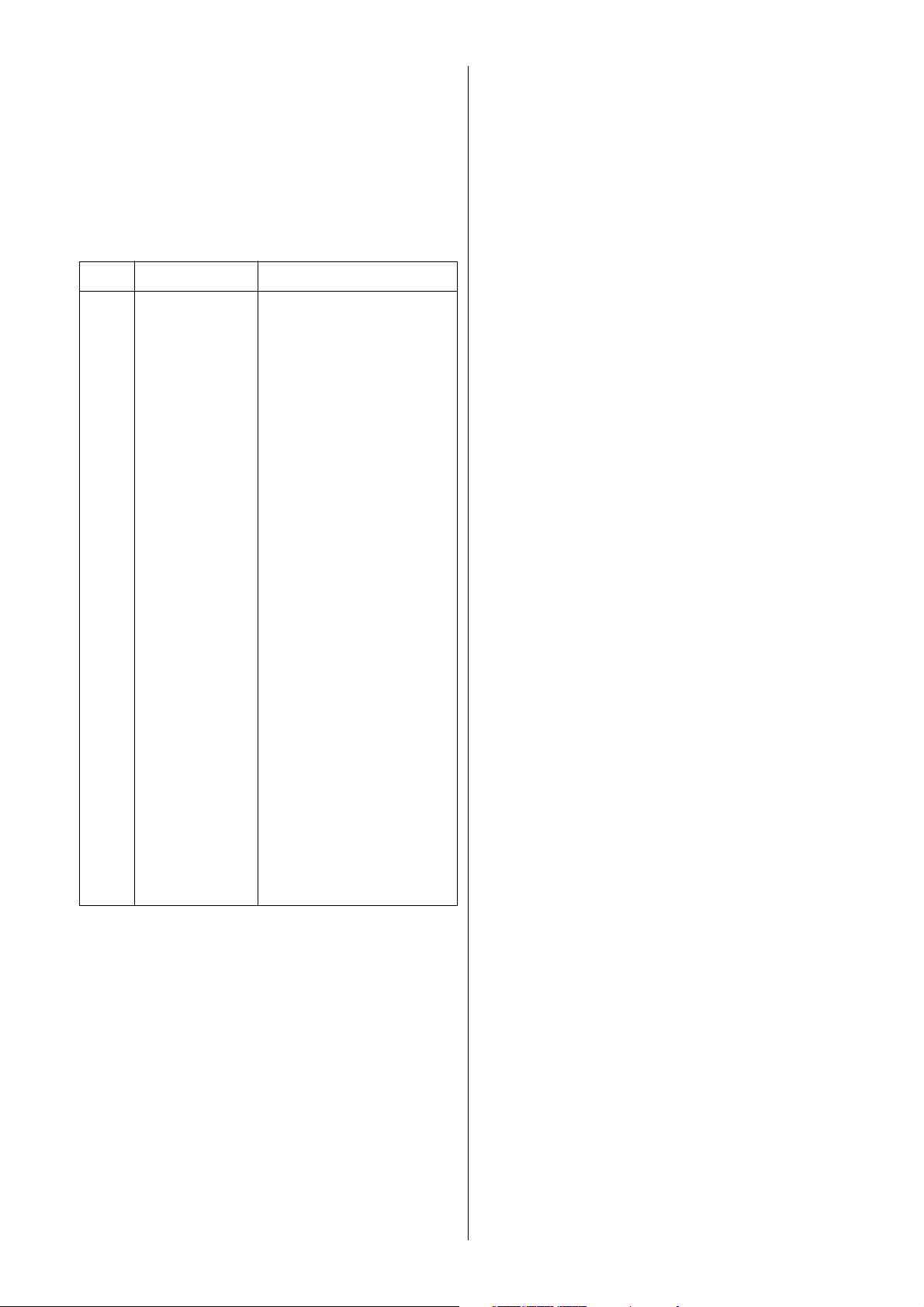

Pin description of ic11:

Pin Symbol Description

11

The horizontal (HDFL) and vertical (VDFL) sync signals from

the DPLL1 are fed to input pins 13 and 12 to synchronize

the circuit.

The horizontal flyback pulse is taken from the horizontal

output stage to input pin 1.

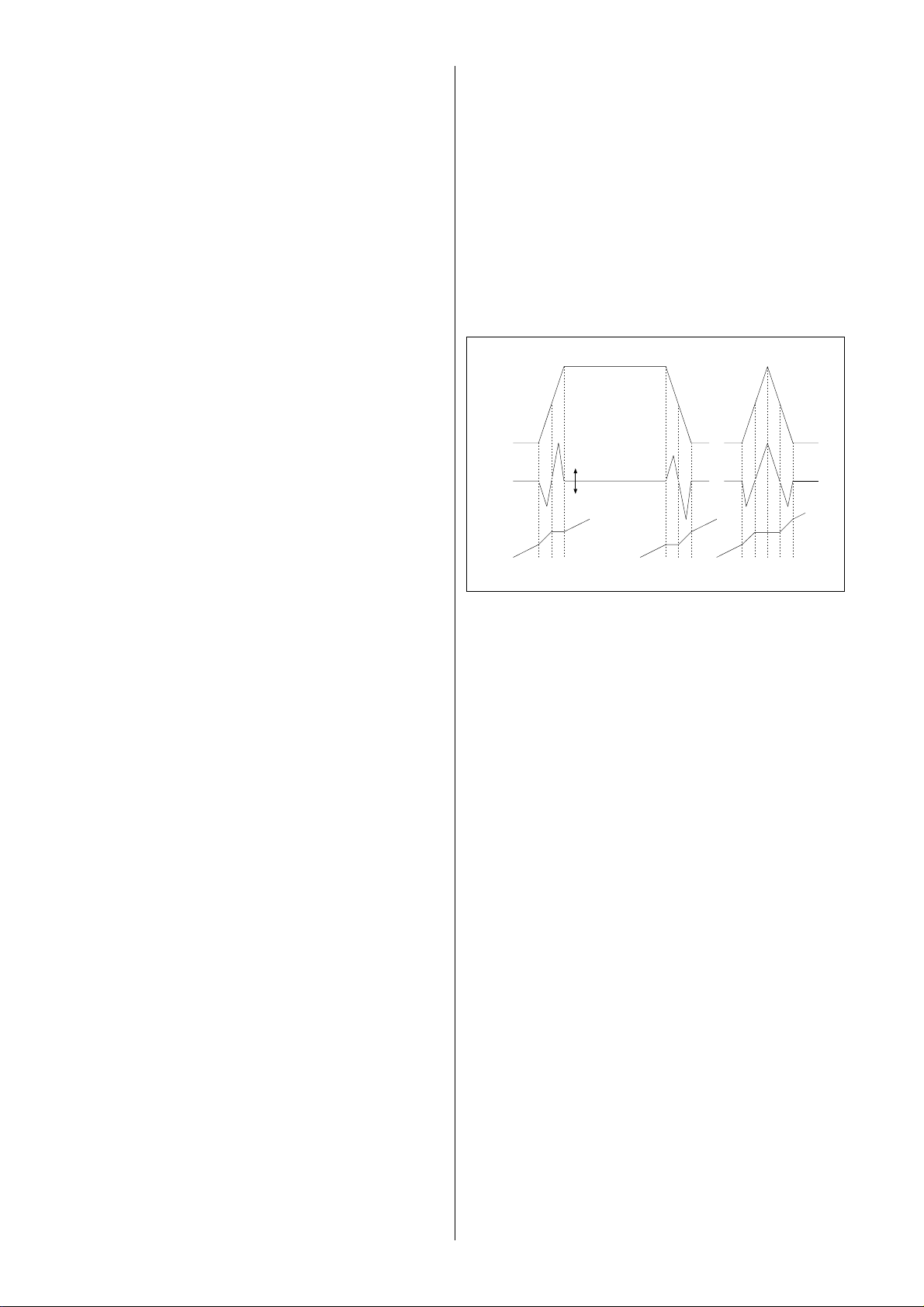

Horizontal drive signal

From the horizontal detector stage, the horizontal sync signal is fed to the horizontal counter, the horizontal place

control, the phase 2 loop, and finally output from pin 20 to

drive the horizontal driver stage. The H-phase adjustment

is performed in the horizontal position control stage using

the IIC-bus.

1 HSYNC1 Horizontal sync from sync

processor

5 VSYNC1 Vertical sync from sync

processor

7 HOUT1 Horizontal sync for ADC and

IQTV2

9 CLK27_1 27 MHz main clock for FM1

and IQTV1

11 CLK13_5_1 13.5 MHz clock for ADC

13 VOUT1 Vertical sync for IQTV2

22 CLK27_2 27 MHz main clock for

deflection controller

24 HS_GSCART Horizontal sync from VGA

(DB700)

26 HSYNC2 Horizontal sync from VGA

(DB700)

27 VS_GSCART Vertical sync from VGA

(DB700)

28 CLK Format dependant clock for

FM1/2 and IQTV2

29 VSYNC2 Double frequency vert sync

from IQTV2

30 HOUT2 (HDFL) Hor sync for IQTV2 and

deflection controller

31 VOUT2 (VDFL) Vert sync for IQTV2 and

deflection controller