Page 1

查询HD74HCT563供应商

HD74HCT563/HD74HCT573

Octal Transparent Latches (with 3-state outputs)

Description

When the latch enable (LE) input is high, the Q outputs of HD74HCT563 will follow the inversion of the D

inputs and the Q outputs of HD74HCT573 will follow the D inputs.

When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enabled

returns high again. When a high logic level is applied to the output control input, all outputs go to a high

impedance state, regardless of what signals are present at the other inputs and the state of the storage

elements.

Features

• LSTTL Output Logic Level Compatibility as well as CMOS Output Compatibility

• High Speed Operation: tpd (D to Q, Q) = 13 ns typ (CL = 50 pF)

• High Output Current: Fanout of 15 LSTTL Loads

• Wide Operating Voltage: VCC = 4.5 to 5.5 V

• Low Input Current: 1 µA max

• Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)

Function Table

Outputs

Output Control Latch Enable Data HD74HCT563 HD74HCT573

LH H L H

LH L H L

LL X Q

HX X Z Z

0

Q

0

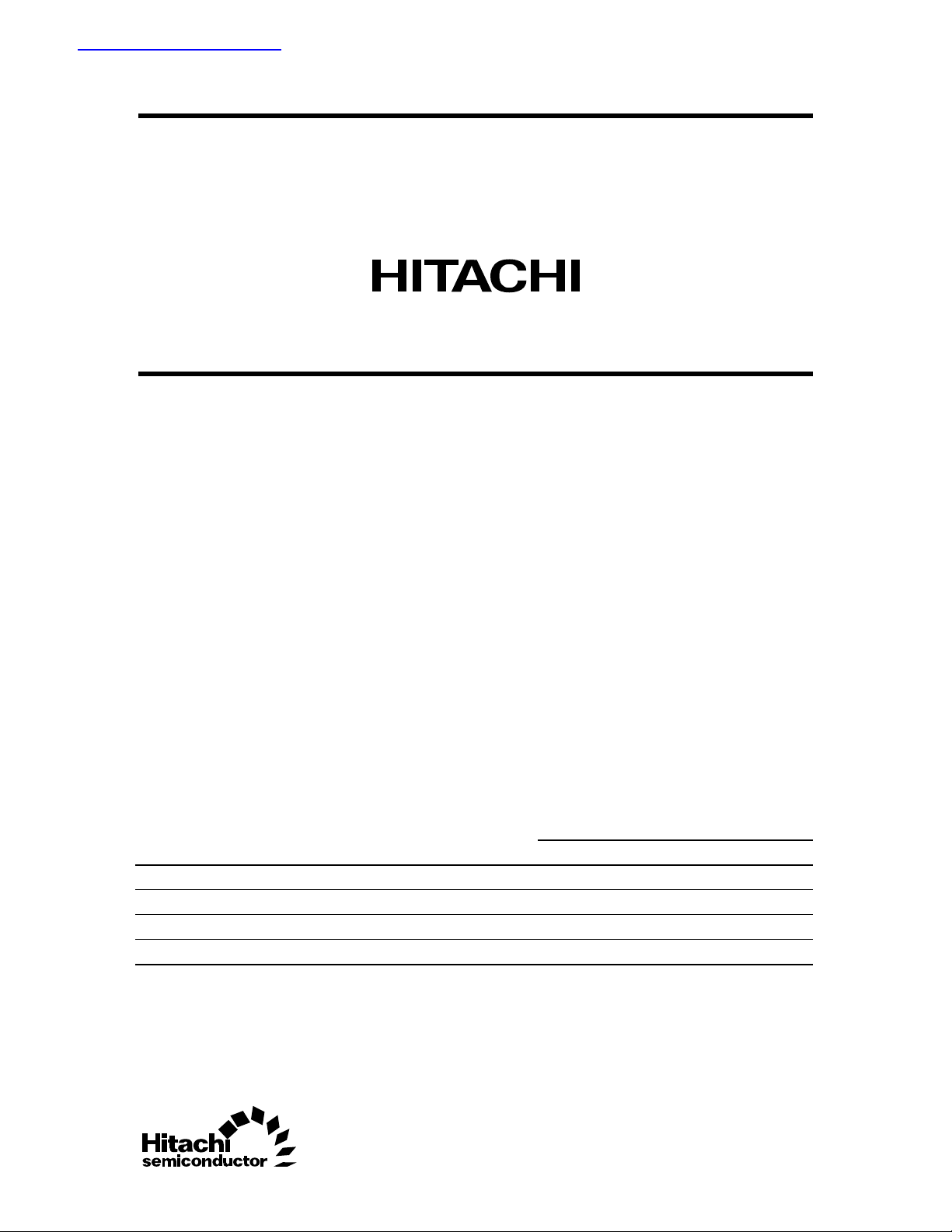

Page 2

HD74HCT563/HD74HCT573

Pin Arrangement

HD74HCT563

Output

Control

1D

2D

3D

4D

5D

6D

7D

8D

GND

10

V

OE

OE

OE

OE

20

CC

19

18

17

16

15

14

13

12

11

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

Latch

Enable

QD

QD

QD

QD

1

2

OE

3

QD

4

OE

5

QD

6

OE

7

QD

8

OE

9

QD

(Top view)

2

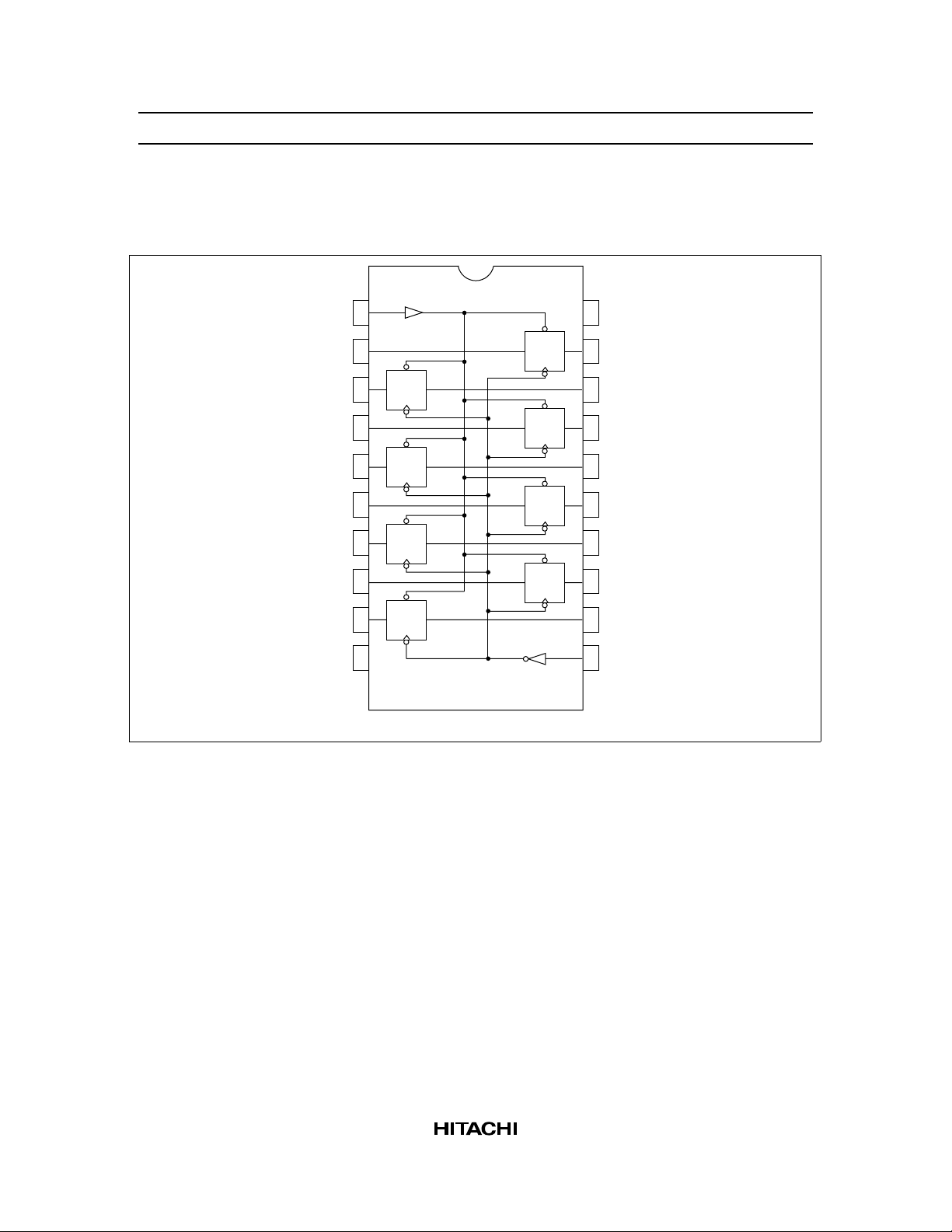

Page 3

HD74HCT573

HD74HCT563/HD74HCT573

Output

Control

1D

2D

3D

4D

5D

6D

7D

8D

GND

10

V

OE

OE

OE

OE

20

CC

19

18

17

16

15

14

13

12

11

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

Latch

Enable

QD

QD

QD

QD

1

2

OE

3

QD

4

OE

5

QD

6

OE

7

QD

8

OE

9

QD

(Top view)

3

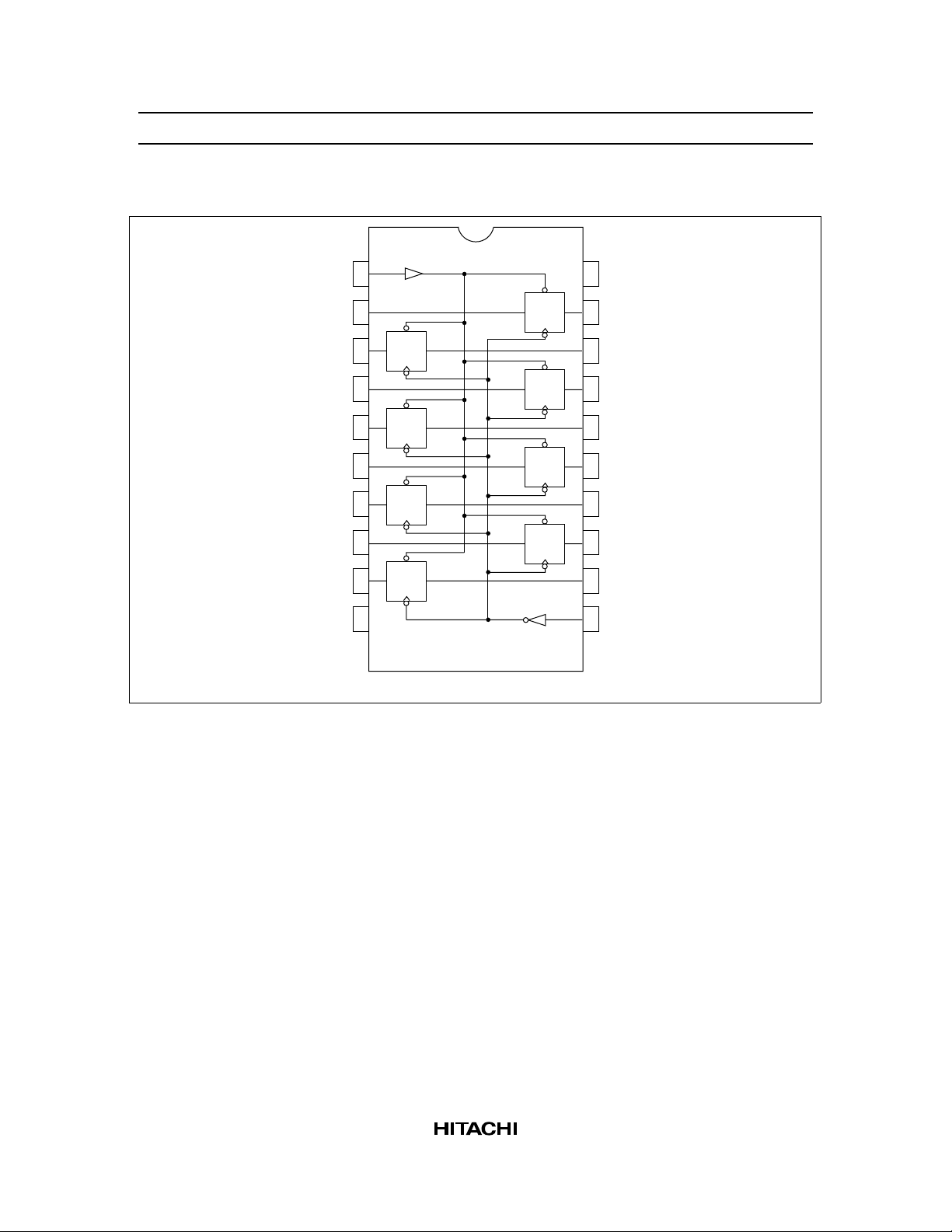

Page 4

HD74HCT563/HD74HCT573

Block Diagram

HD74HCT563

Enable C

OC

1D

2D

3D

4D

5D

6D

7D

8D

D

C Q

C

D

C Q

C

D

C Q

C

D

C Q

C

D

C Q

C

D

C Q

C

D

C Q

C

D

C Q

C

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

4

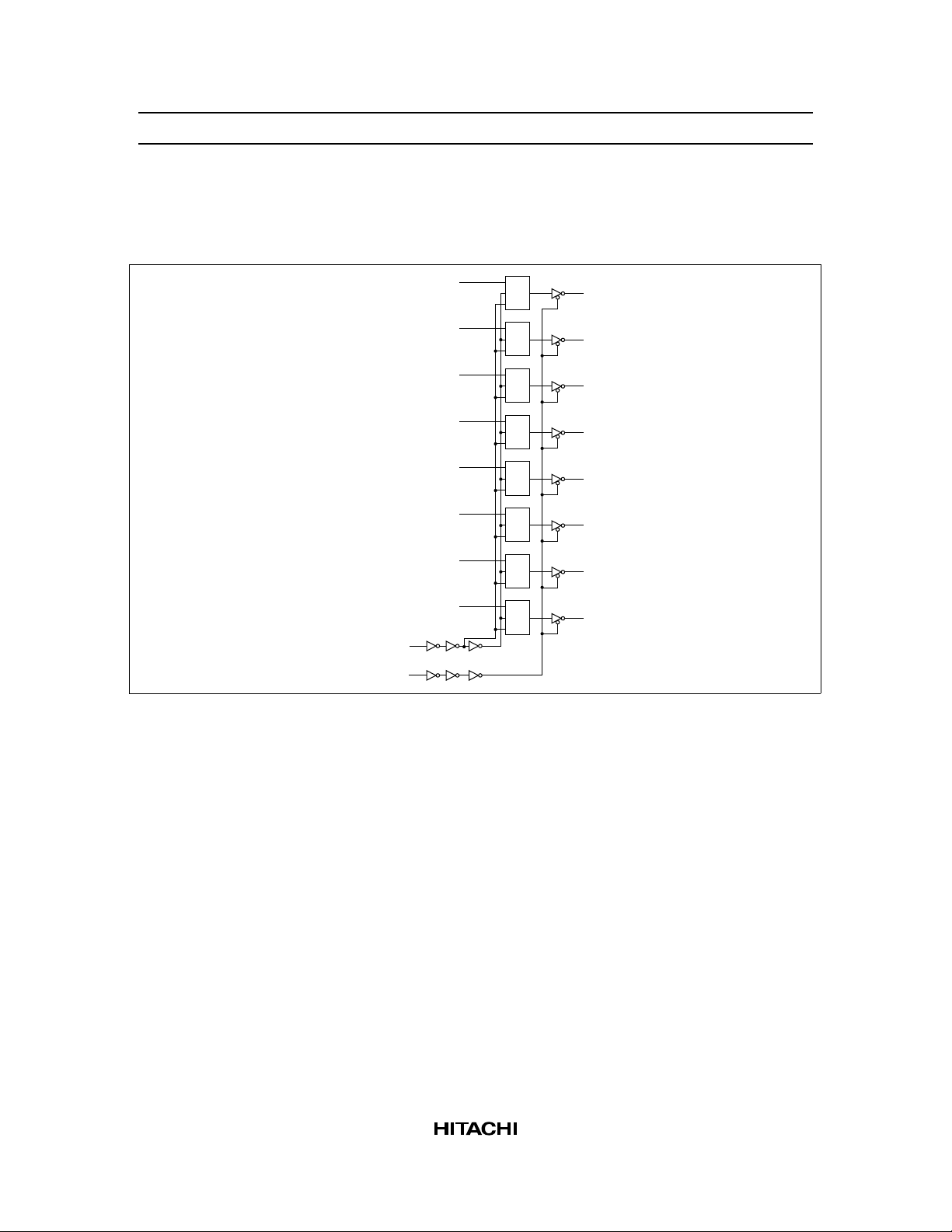

Page 5

HD74HCT573

HD74HCT563/HD74HCT573

Enable C

Absolute Maximum Ratings

OC

1D

2D

3D

4D

5D

6D

7D

8D

D

CQ

C

D

CQ

C

D

CQ

C

D

CQ

C

D

CQ

C

D

CQ

C

D

CQ

C

D

CQ

C

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

Item Symbol Rating Unit

Supply voltage range V

Input voltage V

Output voltage V

DC current drain per pin I

CC

IN

OUT

OUT

DC current drain per VCC, GND ICC, I

DC input diode current I

DC output diode current I

Power dissipation per package P

IK

OK

T

GND

–0.5 to +7.0 V

–0.5 to VCC + 0.5 V

–0.5 to VCC + 0.5 V

±35 mA

±75 mA

±20 mA

±20 mA

500 mW

Storage temperature Tstg –65 to +150 °C

5

Page 6

HD74HCT563/HD74HCT573

DC Characteristics

Ta = –40 to

Ta = 25°C

Item Symbol Min Typ Max Min Max Unit V

Input voltage V

Output voltage V

IH

V

IL

OH

2.0 — — 2.0 — V 4.5 to

— — 0.8 — 0.8 V 4.5 to

4.4 — — 4.4 — V 4.5 Vin = VIH or VILIOH = –20 µA

4.18 — — 4.13 — 4.5 IOH = –6 mA

V

OL

— — 0.1 — 0.1 V 4.5 Vin = VIH or VILIOL = 20 µA

— — 0.26 — 0.33 4.5 IOL = 6 mA

Off-state output

I

OZ

——±0.5 — ±5.0 µA 5.5 Vin = VIH or VIL,

current

Input current Iin — — ±0.1 — ±1.0 µA 5.5 Vin = VCC or GND

Quiescent current I

CC

— — 4.0 — 40 µA 5.5 Vin = VCC or GND, Iout = 0 µA

+85°C Test Conditions

(V)

CC

5.5

5.5

Vout = V

or GND

CC

AC Characteristics (CL = 50 pF, Input tr = tf = 6 ns)

Ta = –40 to

Ta = 25°C

Item Symbol Min Typ Max Min Max Unit V

Propagation delay t

time t

Output enable t

time t

Output disable t

time t

Setup time t

Hold time t

Pulse width t

Output rise/fall t

time t

PLH

PHL

t

PLH

t

PHL

ZL

ZH

LZ

HZ

su

h

w

TLH

THL

— 13 22 — 28 ns 4.5 Data to Q, Q

— 13 22 — 28 4.5

— 14 23 — 29 ns 4.5 Enable G to Q, Q

— 14 23 — 29 4.5

— 14 30 — 38 ns 4.5

— 15 30 — 38 4.5

— 16 30 — 38 ns 4.5

— 17 30 — 38 4.5

12 3 — 15 — ns 4.5

5 –1 — 5 — ns 4.5

16 4 — 20 — ns 4.5

— 4 12 — 15 ns 4.5

— 4 12 — 15 4.5

Input capacitance Cin — 5 10 — 10 pF —

+85°C Test Conditions

(V)

CC

6

Page 7

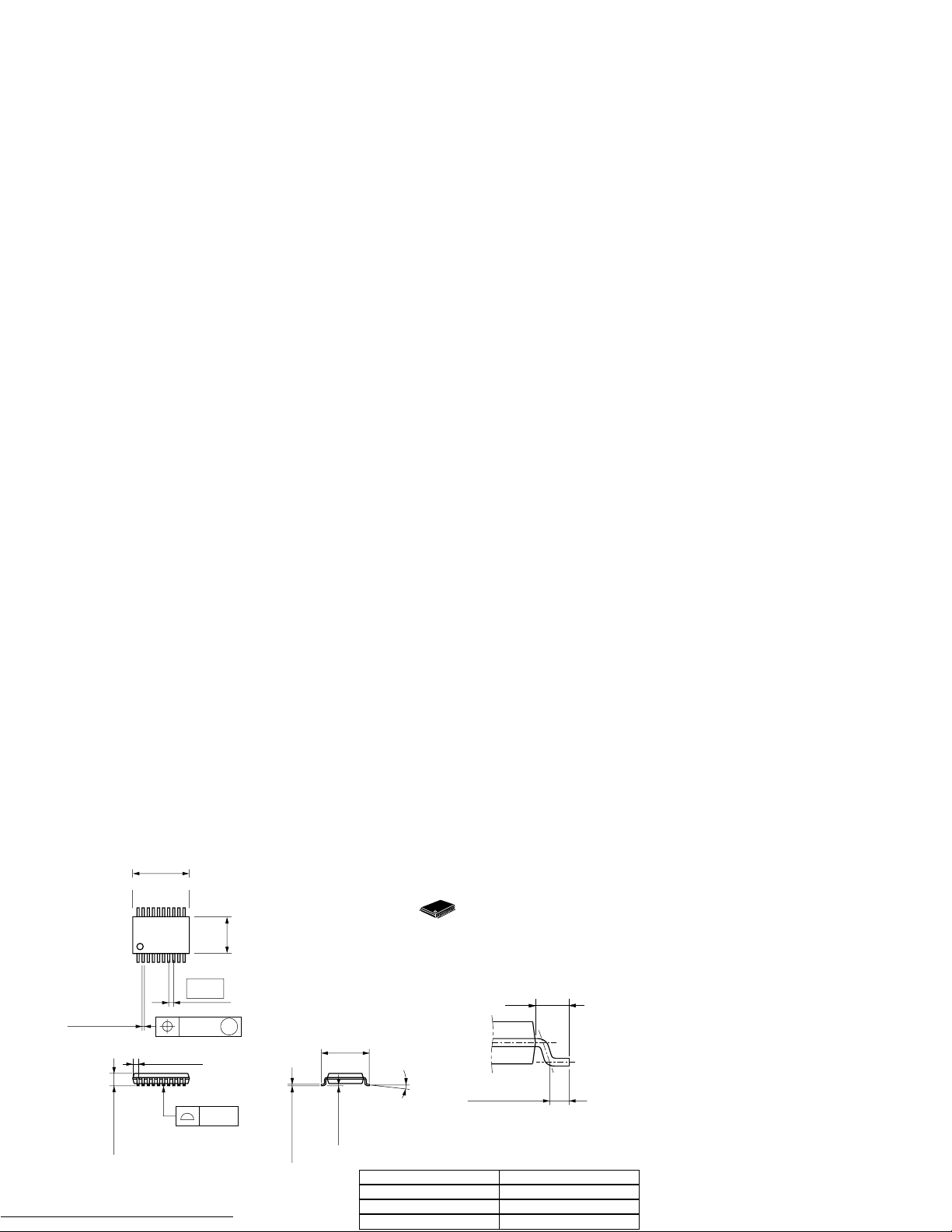

Hitachi Code

JEDEC

EIAJ

Weight

(reference value)

DP-20N

—

Conforms

1.26 g

Unit: mm

0.51 Min

2.54 Min 5.08 Max

7.62

0.25

+ 0.11

– 0.05

2.54 ± 0.25

0.48 ± 0.10

24.50

25.40 Max

0.89

1.30

6.30

7.00 Max

1

10

1120

0° – 15°

1.27 Max

Page 8

Hitachi Code

JEDEC

EIAJ

Weight

(reference value)

FP-20DA

—

Conforms

0.31 g

Unit: mm

*Dimension including the plating thickness

Base material dimension

*0.42 ± 0.08

0.12

0.15

M

20

10

1

*0.22 ± 0.05

0.80 Max

11

12.6

5.5

2.20 Max

13 Max

0° – 8°

0.70 ± 0.20

+ 0.20

– 0.30

7.80

1.27

0.10 ± 0.10

1.15

0.40 ± 0.06

0.20 ± 0.04

Page 9

Hitachi Code

JEDEC

EIAJ

Weight

(reference value)

FP-20DB

Conforms

—

0.52 g

Unit: mm

*Dimension including the plating thickness

Base material dimension

0.12

0.15

0° – 8°

M

20

11

0.20 ± 0.10

1

1.27

10

12.8

13.2 Max

7.50

2.65 Max

*0.27 ± 0.05

*0.42 ± 0.08

+ 0.57

– 0.30

0.70

+ 0.25

– 0.40

10.40

1.45

0.935 Max

0.40 ± 0.06

0.25 ± 0.04

Page 10

Hitachi Code

JEDEC

EIAJ

Weight

(reference value)

TTP-20DA

—

—

0.07 g

Unit: mm

*Dimension including the plating thickness

Base material dimension

0.50 ± 0.10

0° – 8°

*0.17 ± 0.05

6.40 ± 0.20

0.10

1.10 Max

0.13

M

0.65

110

20 11

4.40

6.50

6.80 Max

*0.22

+0.08

–0.07

0.07

+0.03

–0.04

1.0

0.65 Max

0.20 ± 0.06

0.15 ± 0.04

Page 11

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,

copyright, trademark, or other intellectual property rights for information contained in this document.

Hitachi bears no responsibility for problems that may arise with third party’s rights, including

intellectual property rights, in connection with use of the information contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you have

received the latest product standards or specifications before final design, purchase or use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,

contact Hitachi’s sales office before using the product in an application that demands especially high

quality and reliability or where its failure or malfunction may directly threaten human life or cause risk

of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,

traffic, safety equipment or medical equipment for life support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly

for maximum rating, operating supply voltage range, heat radiation characteristics, installation

conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used

beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable

failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other

consequential damage due to operation of the Hitachi product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without

written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor

products.

Hitachi, Ltd.

Semiconductor & Integrated Circuits.

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

URL NorthAmerica : http:semiconductor.hitachi.com/

For further information write to:

Hitachi Semiconductor

(America) Inc.

179 East Tasman Drive,

San Jose,CA 95134

Tel: <1> (408) 433-1990

Fax: <1>(408) 433-0223

Europe : http://www.hitachi-eu.com/hel/ecg

Asia (Singapore) : http://www.has.hitachi.com.sg/grp3/sicd/index.htm

Asia (Taiwan) : http://www.hitachi.com.tw/E/Product/SICD_Frame.htm

Asia (HongKong) : http://www.hitachi.com.hk/eng/bo/grp3/index.htm

Japan : http://www.hitachi.co.jp/Sicd/indx.htm

Hitachi Europe GmbH

Electronic components Group

Dornacher Stra§e 3

D-85622 Feldkirchen, Munich

Germany

Tel: <49> (89) 9 9180-0

Fax: <49> (89) 9 29 30 00

Hitachi Europe Ltd.

Electronic Components Group.

Whitebrook Park

Lower Cookham Road

Maidenhead

Berkshire SL6 8YA, United Kingdom

Tel: <44> (1628) 585000

Fax: <44> (1628) 778322

Hitachi Asia Pte. Ltd.

16 Collyer Quay #20-00

Hitachi Tower

Singapore 049318

Tel: 535-2100

Fax: 535-1533

Hitachi Asia Ltd.

Taipei Branch Office

3F, Hung Kuo Building. No.167,

Tun-Hwa North Road, Taipei (105)

Tel: <886> (2) 2718-3666

Fax: <886> (2) 2718-8180

Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.

Hitachi Asia (Hong Kong) Ltd.

Group III (Electronic Components)

7/F., North Tower, World Finance Centre,

Harbour City, Canton Road, Tsim Sha Tsui,

Kowloon, Hong Kong

Tel: <852> (2) 735 9218

Fax: <852> (2) 730 0281

Telex: 40815 HITEC HX

Page 12

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com

Loading...

Loading...