Page 1

MAS 101/102/111

Music system

Service Manual

CD

Page 2

CONTENTS

1. Specification ………………………………………………………………………………………………………….….1

2. Packing …………………………………………………………………………………………………………..………3

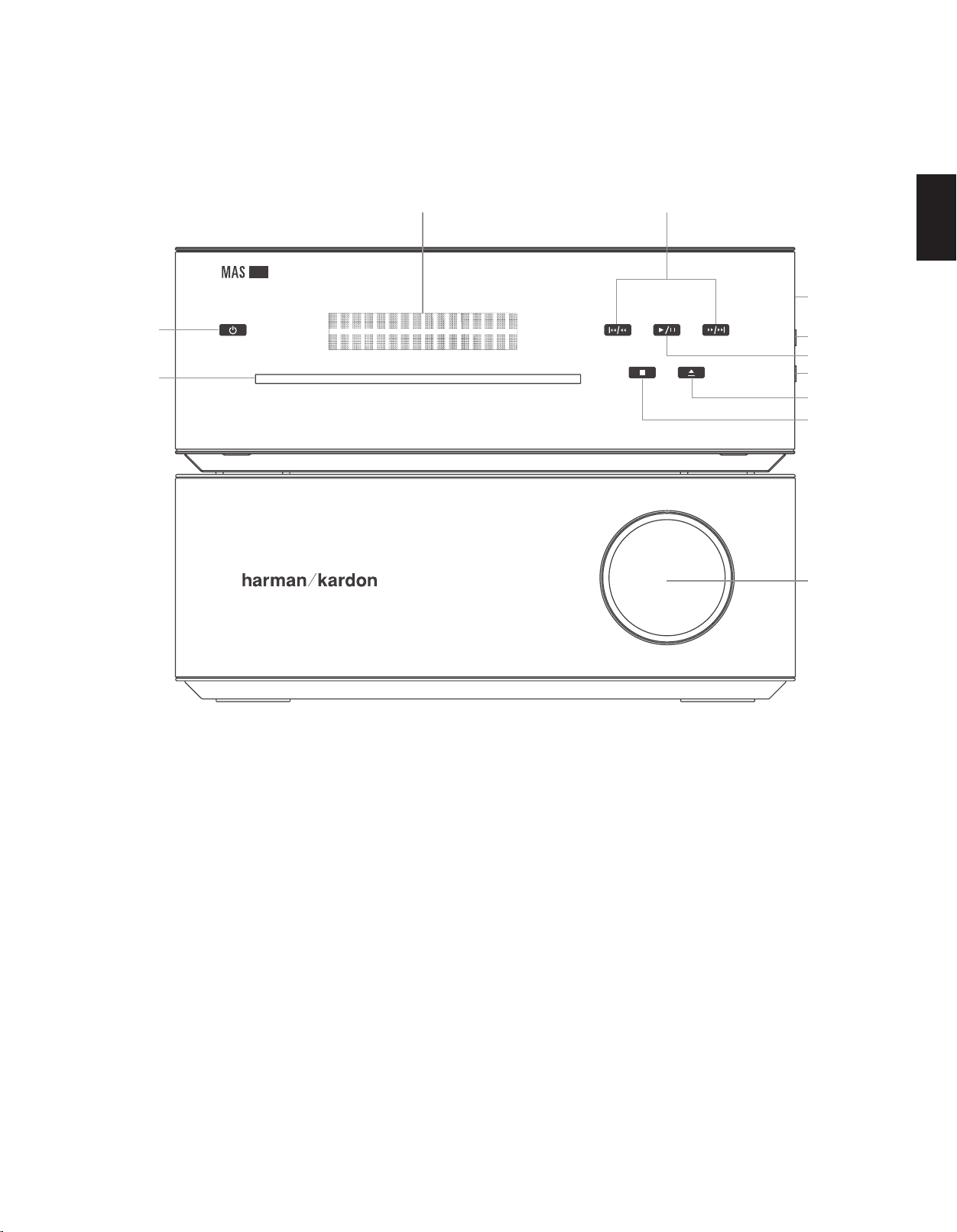

3. Front panel information ………………………………………………………………………………………………...4

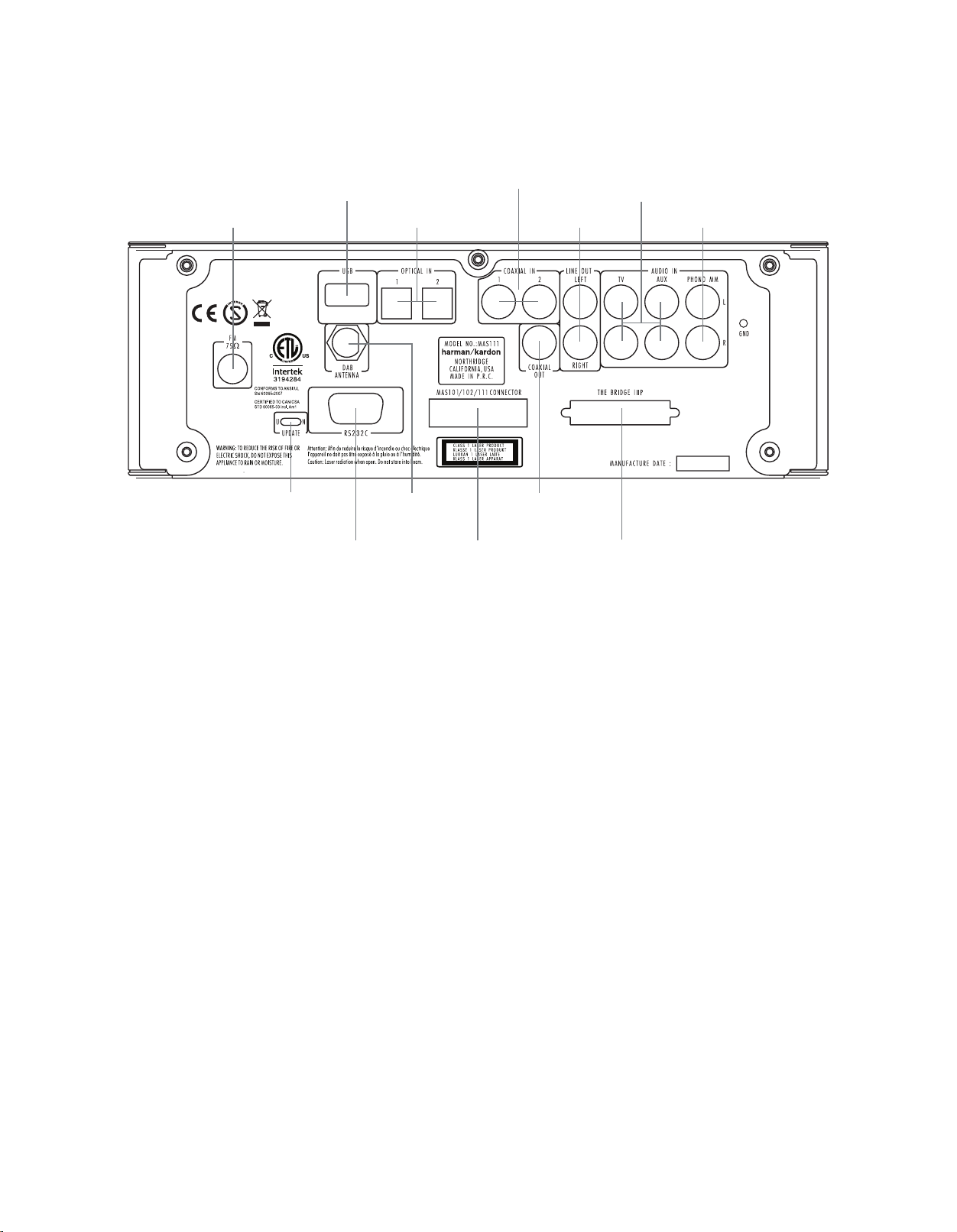

4. Rear panel information …………………………………………………………………………………………………5

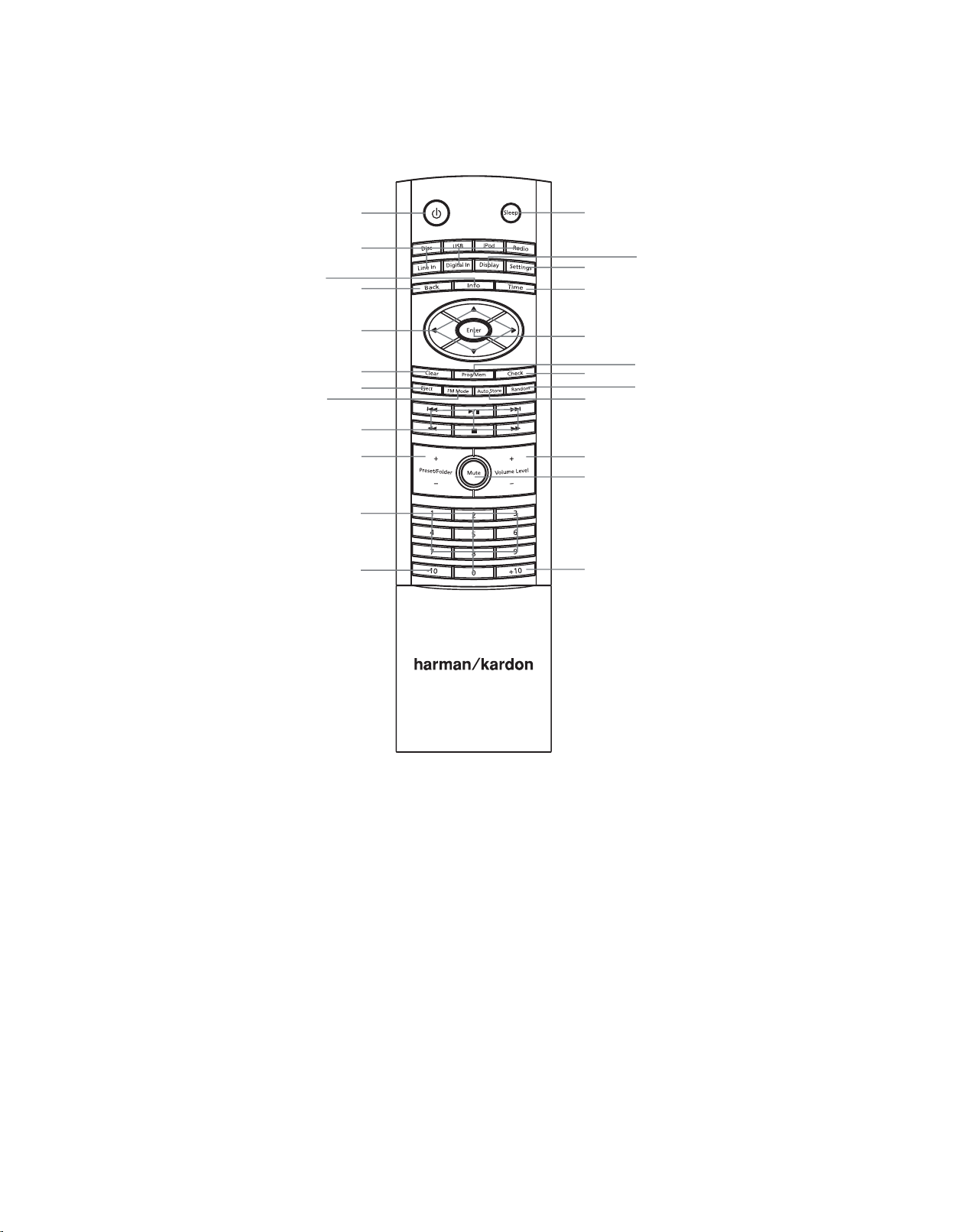

5. Remote control information ……………………………………………………………………………………………6

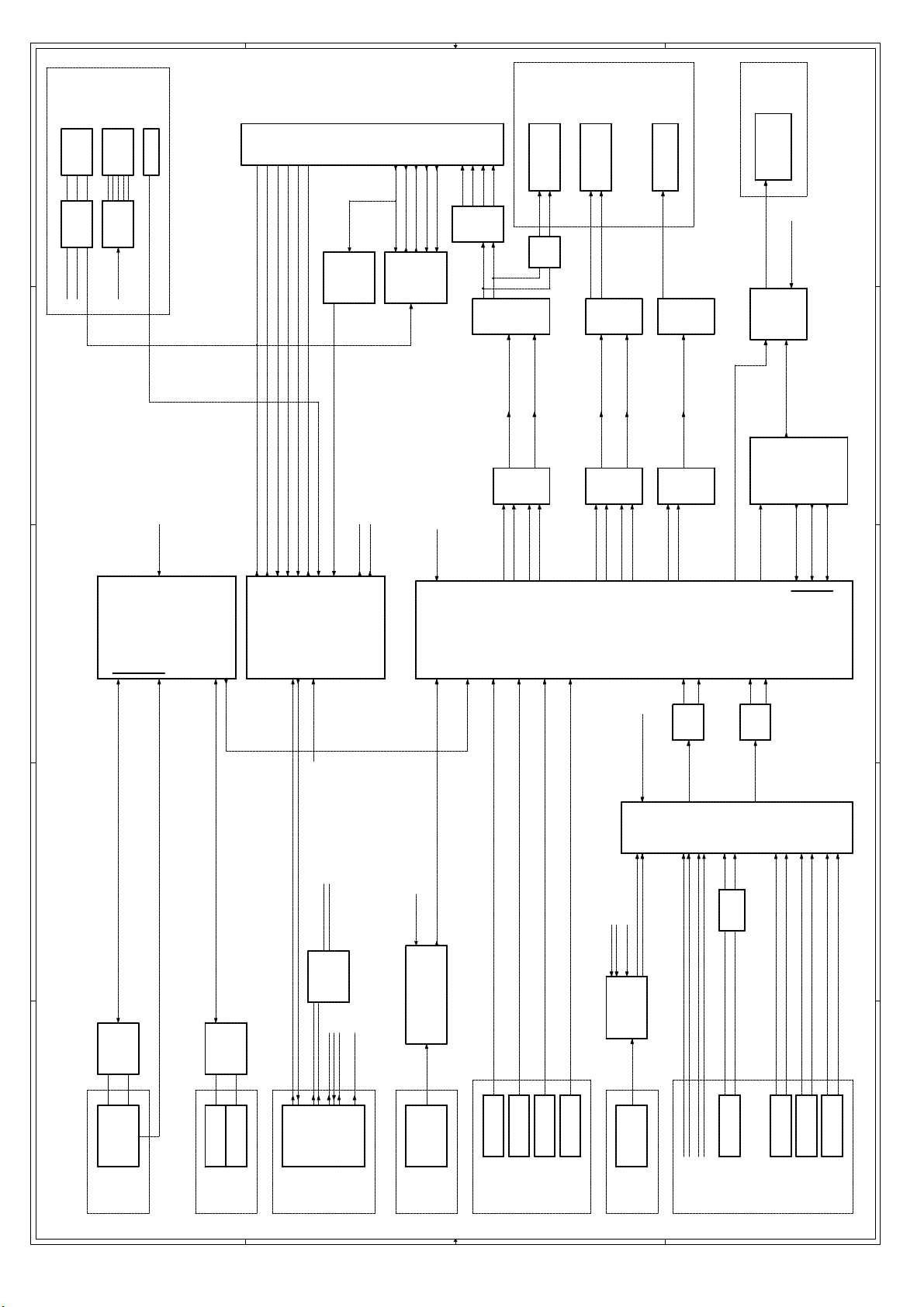

6. Block diagram …………………………………………………………………………………………………………...8

7. Wiring diagrams ………………………………………………………………………………………………………...9

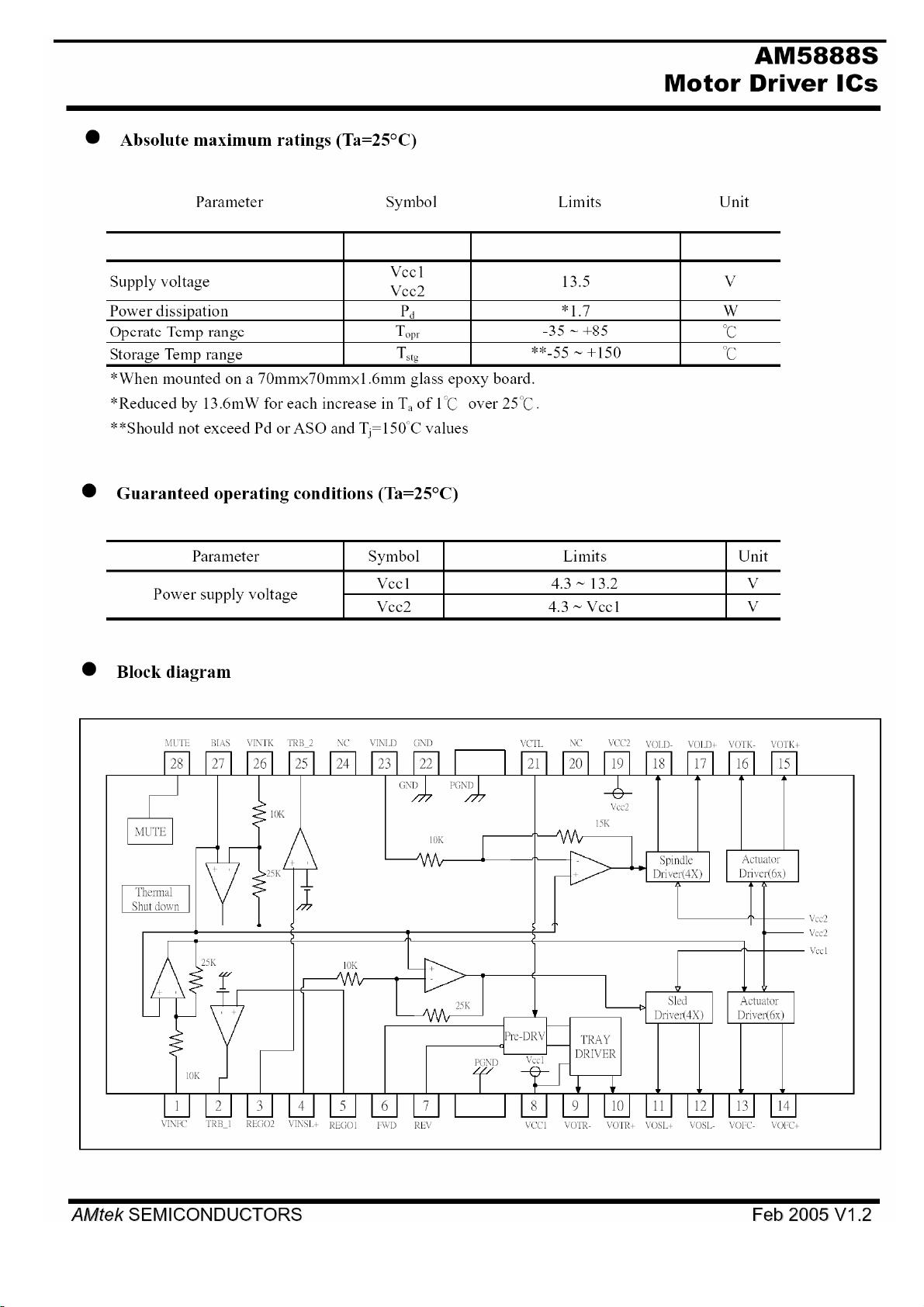

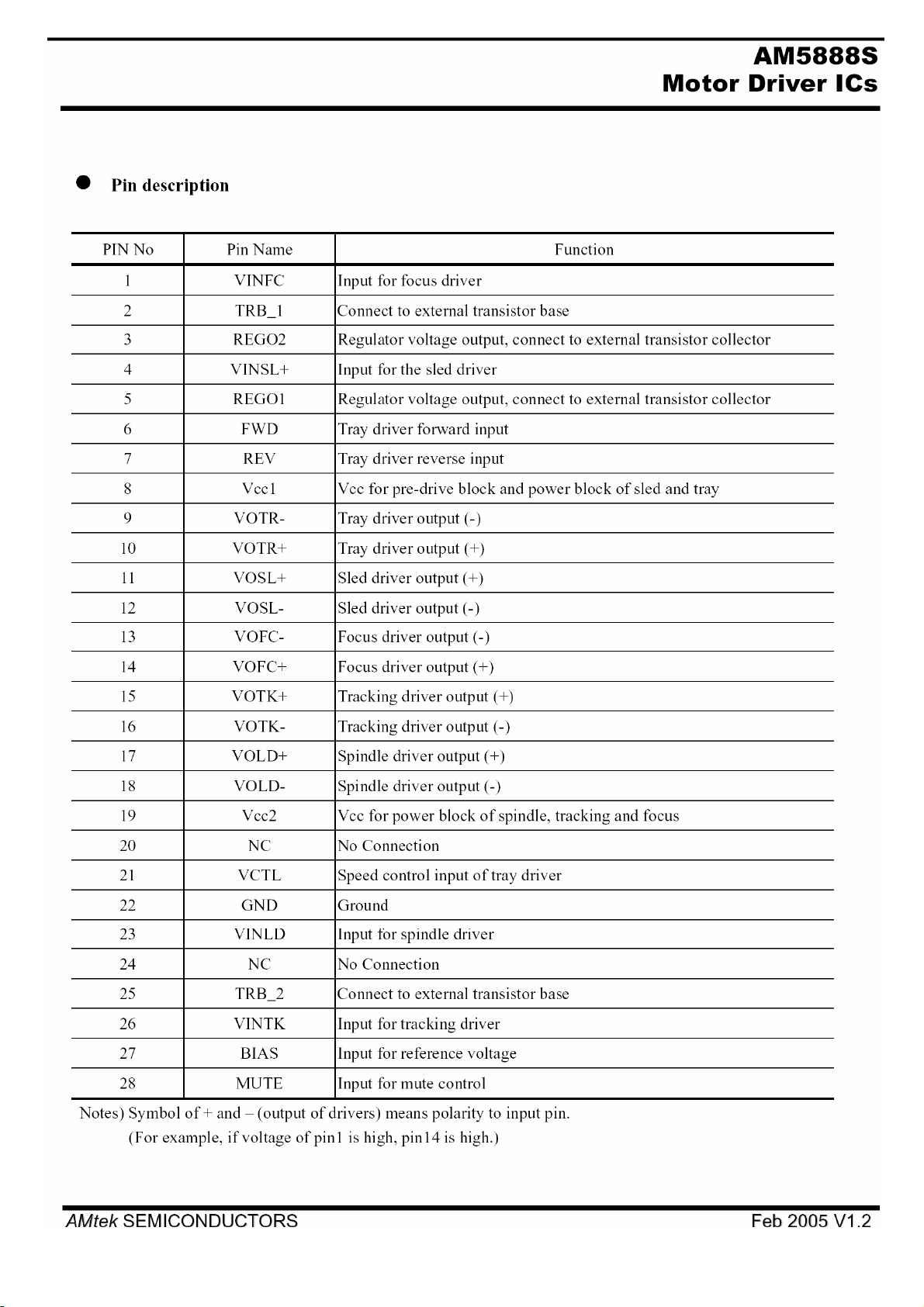

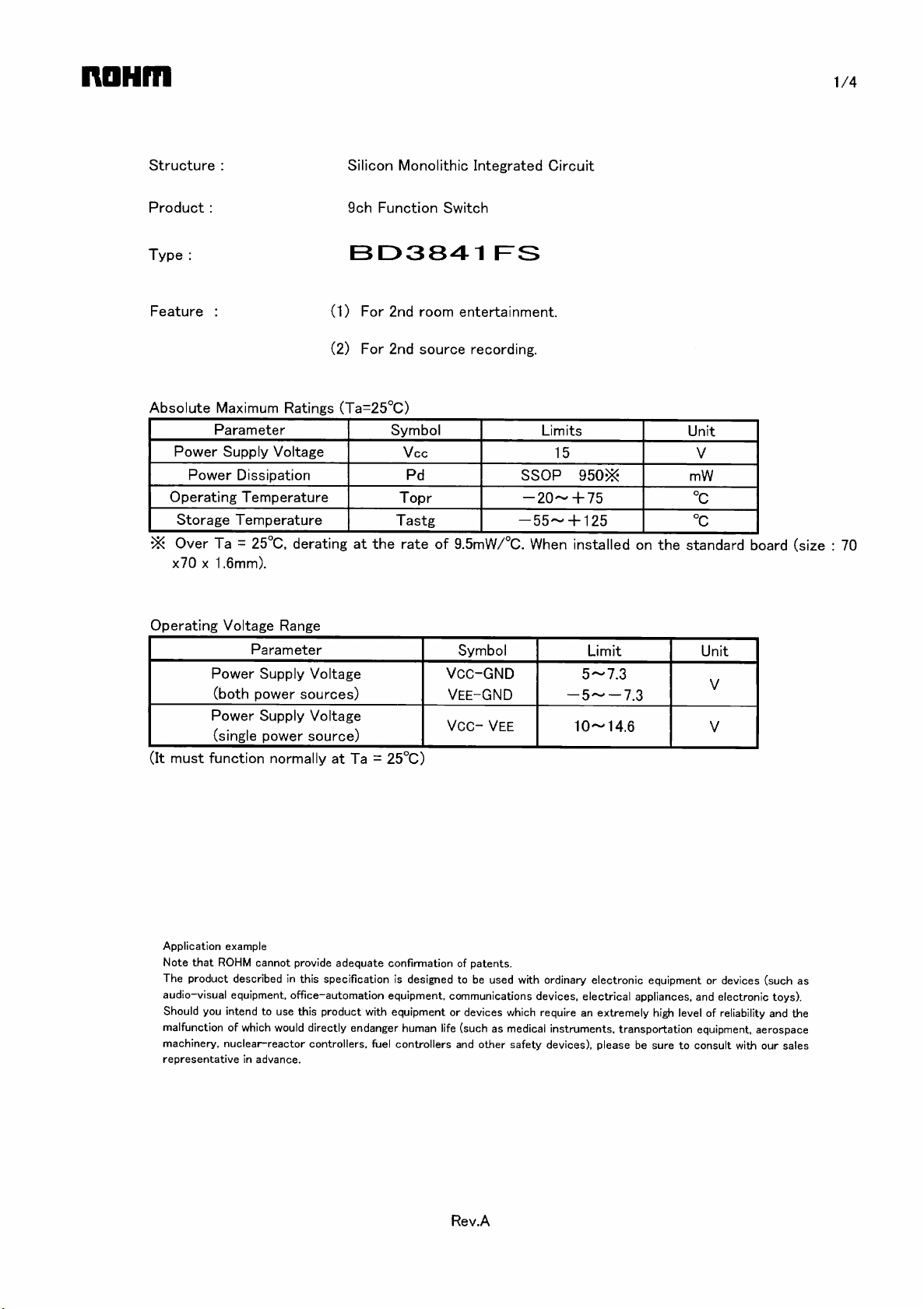

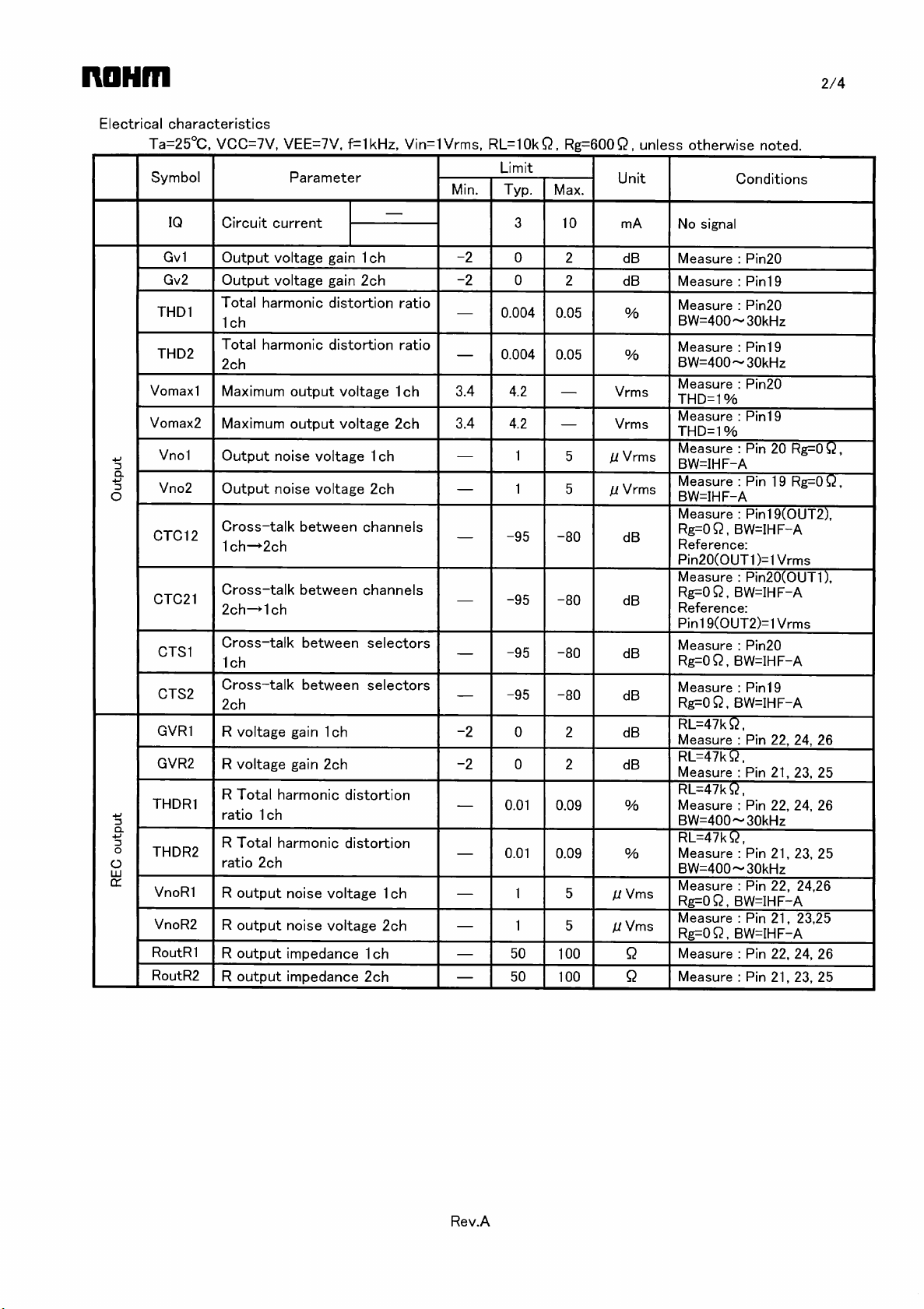

8. IC spec ……………………………………………………………………………………………………………..…..10

9. Printed circuit boards ……………………………………………………………………………………………..…..87

10. Schematic diagram ………………………………………………………………………………………………..….97

11. Exploded view …………………………………………………………………………………………………….…108

12. Electrical parts list ……………………………………………………………………………………………………110

Page 3

MAS SySteM

Specifications

System

Power output 65 watts per channel, 20Hz – 20kHz, THD <0.07%, into 6 ohms, both channels driven

Bandwidth 20Hz – 35kHz, –3dB

System frequency response 20Hz – 20kHz, ±0.5dB

Signal-to-noise ratio, A-weighted 90dB (Analog inputs), 96dB (Digital inputs)

Channel separation ≥65dB

Crosstalk between sources ≥70dB

Line-level input sensitivity at 1kHz 250mV RMS, ±1dB

Phono MM input sensitivity at 1kHz 7.5mV

Loudspeakers

Low-frequency transducers Two 130mm honeycomb composite drivers, ported

High-frequency transducers Two 25mm MMD

Nominal impedance 8 ohms

Sensitivity (2.83V/1m) 85dB

Frequency response 60Hz – 25kHz (–3dB)

Crossover frequency 2200Hz

®

domes, shielded

FM Tuner Section

Frequency range 87 – 108.0MHz

Usable sensitivity IHF 1.3µV/13.2dBf

Frequency response 10Hz to 15.3kHz

Signal-to-noise ratio mono/stereo 68/65dB

Distortion mono/stereo 0.15/0.3%

Stereo separation 35dB @ 1kHz, 100% deviation @ 65dBf

Selectivity ±300kHz; 65dBF

Image rejection 80dB

IF rejection 90dB

Tuner output level 1kHz, ±50kHz, Dev 500mV

Number of presets 30

RDS capability PS (program service), RT (dynamic radio text)

1

Page 4

ENGLISH

MAS SySteM

2

CD Section

Disc compatibility CD, CD-R, CD-RW, MP3, WMA

THD+N (20Hz – 20kHz) <0.025%

Frequency response 20Hz to 20kHz, 0dB ±0.5

Channel separation ≥65dB

Signal-to-noise ratio “A” WTG >96dBr; 22kHz filter > 94dBr

General

Power requirement AC 230V/50Hz (MAS 101/MAS 111); AC 120V/60Hz (MAS 102)

Power consumption <1W full standby (clock not activated); <2W standby (clock activated);

150W maximum (both channels driven)

Operating temperature 0°C to 40°C

Dimensions (H x W x D) Controller: 90mm x 240mm x 240mm (3-9/16" x 9-7/16" x 9-7/16")

Amplifier: 90mm x 240mm x 240mm (3-9/16" x 9-7/16" x 9-7/16")

Loudspeakers (each, with grille): 272mm x 181mm x 196mm

(10-23/32" x 7-1/8" x 7-3/4")

Weight System 13.9kg (30,5lb)

Controller 2.0kg (4,4lb)

Amplifier 2.8kg (6,3lb)

Loudspeakers (each): 4.4kg (9,8lb)

Specifications

Page 5

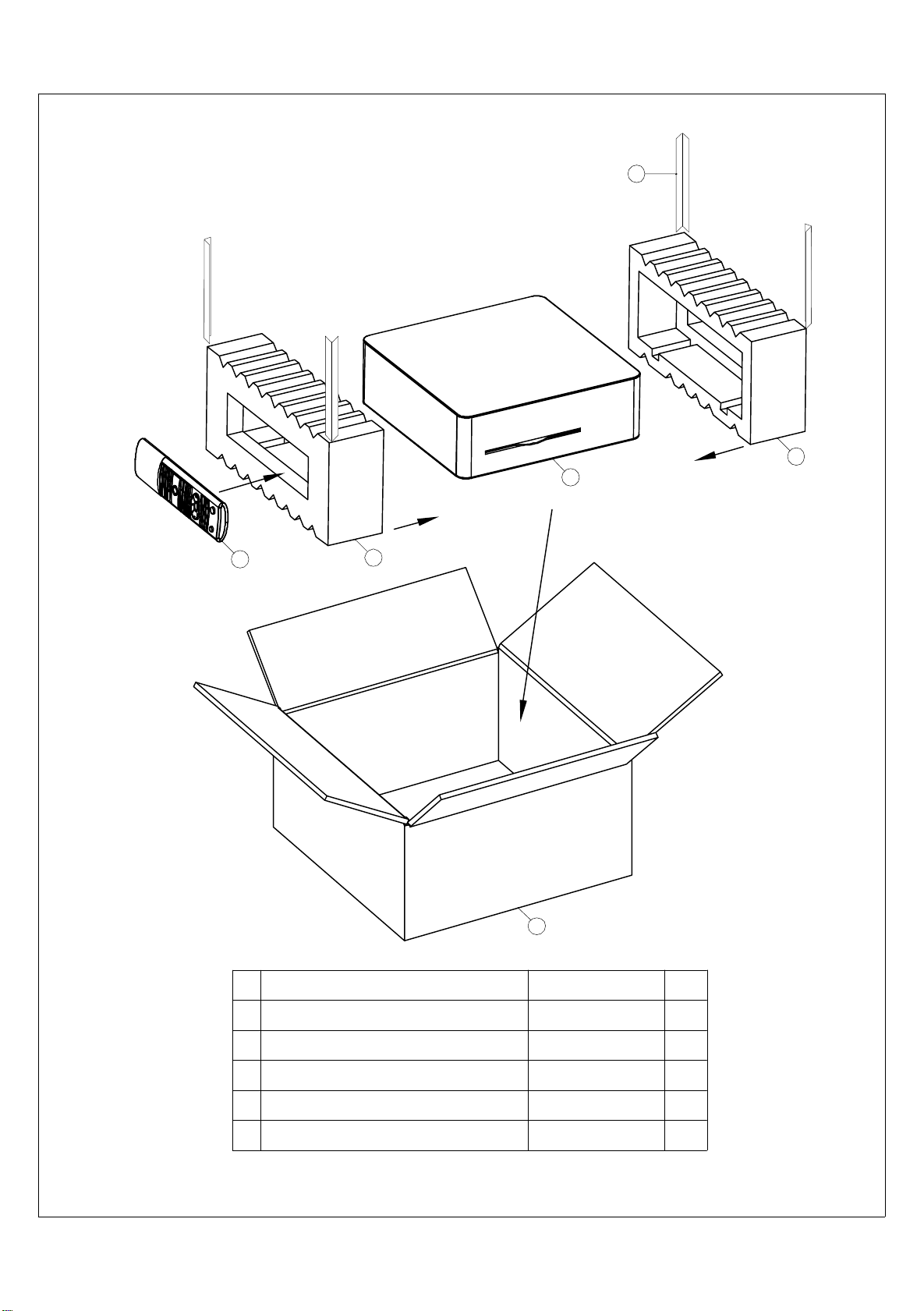

MAS101 MAS102 MAS111

3

harman/kardon

REMOTE CONTROL ASS'Y

CARDBOARD CORNER

1

EPE

3

2

SET

4

EPE

2

NO

SET

1

EPE

2

REMOTE CONTROL ASS'Y

3

CARDBOARD CORNER

4

BOX

5

5

BOX

DESCRIPTION PARTS NO. Q,ty

1

8250 503B 0 000

3320 0805 0 352

8150 5030 0 000

8150 5011 0000

2

1

4

1

Page 6

4

ENGLISH

MAS SySteM

Front-Panel Controls

Controller and Amplifier

1 3

Note: Controls are the same for all models.

0

2

7

8

4

9

6

5

A

The MAS systems use touch-sensitive controls. To use a control, tap gently on its lit icon.

NOTE: Controls are the same for all models.

0

Po wer: Turns the MAS system on or places it in Standby mode. To completely power

off the unit, unplug the power supply.

1

Message Display: The time and messages are displayed in this two-line text display.

2

CD Slot: Load compatible discs here.

3

Skip/S can Forward/Reverse: These buttons function differently, depending on the

current source:

iPod, CD or USB

•

button twice to skip to the previous track. Press and hold a button to scan

forward or reverse within a track.

•

: Press and release a button to select the next higher or lower programmed

Radio

preset station. Press and hold a button to scan to the next available higher or

lower station. When you release the button, the tuner continues to scan until it

finds a station of acceptably strong signal quality, and then it stops. To stop the

scan before a station is found, press the button while the tuner is scanning.

4

Play/Pause: Each tap toggles between the Play and Pause functions.

5

S top: Fully stops playback.

6

Ejec t: When a CD is loaded, tap here to eject it.

: Press and release to skip to the next track. Press the Reverse

7

USB Port A: Connect a compatible USB device here to enjoy playback of audio MP3

or WMA files. Although most USB flash and hard-disk drives in the FAT32 file format,

as well as many MP3 players, are compatible with the MAS system, due to the wide

variety of manufacturers, playback cannot be guaranteed. Do not connect an iPod

or iPhone to this port. Do not connect a personal computer or any peripherals to this

port.

8

Line -In Jack (Line Input): Connect a stereo 3.5mm male-to-male cable (not

included) to the headphone or line-level output on a portable player or other device.

9

Headphone Jack: Outputs a stereo signal for private listening through most

headphones that are equipped with a stereo 3.5mm plug.

A

Volume Control: Increases or decreases the volume.

Page 7

5

MAS SySteM

Rear-panel connections

Controller

c

a

l

k

0

FM Antenna Terminal: Connect the included FM antenna wire here.

1

DAB Antenna Terminal (MAS 111 Only): Connect the included DAB antenna wire

lead here to enjoy programm ing from digital DAB, DAB+ or T-DMB-Audio radio

stations available in your area.

2

USB Port B: Connect a compatible USB device here to enjoy playback of audio MP3

or WMA files. Although most USB flash and hard-disk drives in the FAT32 file format,

as well as many MP3 players, are compatible with the MAS system, due to the wide

variety of manufacturers, playback cannot be guaranteed. Do not connect an iPod

or iPhone to this port. Do not connect a personal computer or any peripherals to this

port.

3

Optic al 1/2 and Coaxial 1/2 Digital Audio Inputs: Connect a source device’s

optical or coaxial digital audio output to the corresponding input. Only the

uncompressed PCM format is supported.

4

T V and AUX Analog Audio Inputs: Connect the analog audio outputs of a tele-

vision or any source device to enjoy playback through the high-performance MAS

system.

5

Phono Input: Connect the outputs of a moving-magnet (MM) type turntable to this

input. Do not connect any other type of turntable to this input, and do not connect

the outputs of an MM-type turntable to any other analog audio inputs on the MAS

system without using a phono preamp, available separately from many electronics

stores.

6

The Bridge IIIP Input: To enjoy playback of audio materials stored on a compatible

iPod (see page 4), connect The Bridge IIIP. Make sure the insert for The Bridge IIIP is

installed, and install the appropriate dock adapter for your iPod within the insert, as

shown in Figure 1 on page 10.

d

b

d

h

i

j

7

Analog Audio O utputs: Connect these outputs to the analog audio inputs of an

audio recorder. When a source connected to the MAS system is playing, the signal will

be available at these outputs for recording. IMPORTANT: The Analog Audio Outputs

will mute when the Mute button on the remote is pressed. See page 9.

8

Coaxial Digital Audio O utput: Connect this output to the coaxial digital audio

input of a digital audio recorder. When the following sources are playing, the signal

will be available at this output for recording: CD, USB Ports A/B, Coaxial 1/2, Optical

1/2. The following sources are not available at this output: FM/DAB, TV, Aux, Phono,

The Bridge IIIP.

NOTES:

The MAS system can convert analog sources to the digital domain, or digital

•

sources to the analog domain for recording.

It is the user’s responsibility to comply with all laws pertaining to the

•

copying of audio materials.

9

O utput to Amplifier: Connect the incl uded ribbon cable to this connec tor and to

the corresponding connector on the MAS amplifier. This cable passes audio signals

from the controller to the amplifier, and it transfers DC power from the amplifier

to the controller. If this cable is ever damaged, do not use it, and contact Harman

Kardon for a replacement.

A

RS -232 Serial Port: This port is used only for system upgrades. Do not connect it to

any devices unless instructed to do so at the time a system upgrade is released.

B

Update Switch: This switch is used only for system upgrades. Leave it in the “N”

position for norm al operation unless instructed to sw itch it to the “U” pos ition to

install a system update.

e

f

g

Page 8

6

MAS SySteM

Remote control functions

Source Selectors

K/LM/N

FM Mode

Transport Controls

Preset/Folder +/–

–10 numeric Key

Power

Info

Back

Navigation

Clear

Eject

Numeric keys

Sleep

Settings

Time

Enter

Check

Auto Store

Volume +/–

Mute

+10 numeric Key

Display

Program/Memory

Random

Power: Turns the MAS system on or off. To completely power off the unit, unplug the

power supply.

Sleep: Each press increases the time until turn-off, from 10 to 90 minutes, in increments

of 10 minutes. The next press after the 90 minutes setting turns off the Sleep function.

Source Selectors: Selects a source input. Each press of the Line In or Digital In button

toggles among the available analog (L ine Input on right-side panel; TV, AUX or Phono

Input on rear panel) or digital audio inputs (Coaxial 1 or 2, Optical 1 or 2), respectively.

Press the iPod button to select an iPod docked in The Bridge IIIP.

Display: Adjusts the brightness of the message display. Each time the button is pressed

and held for one second, the message display brightness will cycle between full, half and

off. When the display is off while the system is turned on, the LEDs inside the Volume

knob and behind the front-panel function buttons will remain lit to remind you that the

system is still on.

Settings: Accesses menus for Speaker Setup (tone controls), Time Setup (clock), Alarm

Setup, System Version and System Reset. See the Operation section for more information.

Back: Returns to previous menu level.

Info: Displays the status of the current source:

Radio

•

: When FM band is in use, each press of the button toggles between the PS

(Program Service) and RT (Radio Text) RDS information, if available. When a DAB

radio station is playing (MAS 111 only), press this button to access the menu system

for the DAB tuner. See pages 13 and 14 for more information.

Audio CD

•

•

Time: Displays elapsed track time for the current Audio CD (no effect on data CDs or

other sources). Each additional press changes the display as follows: remaining track

time, elapsed disc time, remaining disc time then back to elapsed track time.

K/LM/N

through the Settin gs Menus, or through lists of content, and press the Enter button to

make selections. Press the Back button to return to the previous menu or content level.

Enter: Selects a menu item, or saves setting changes and returns to the previous menu

level.

: Displays CD Text information, if available. Each press of the button displays

the following items: Song, Artist, Album.

USB or Data CD

press of the button displays the individual items Song, Artist, Album, File type and

Folder, and then goes back to scrolling. If ID3 tags are not available, the file name will

appear.

: Scrolls all ID3 tag information for current source, if available. Each

Navigation buttons: Use the M and N buttons to scroll forward and reverse

Page 9

7

ENGLISH

MAS SySteM

Clear: Clears the current preset station or a playlist entry.

Radio

•

: To delete the current preset station, press the Clear button while it is playing.

Playlist

•

Program/Memory: Used to program playlists and radio presets.

•

•

Check: After a playlist has been programmed and play has been stopped, each press of

the Check button displays the tracks in the playlist.

Eject: When a CD is loaded, press this button to eject it.

FM Mode: Used with FM radio, each press toggles between Stereo and Monaural

playback.

Auto Store: Scans through all frequencies, searching for stations with acceptably strong

signal quality, and stores them as presets.

Random: Each press turns Random playback mode (shuffle) on or off. This mode plays

the tracks of the current disc or drive in random order.

: While programming a playlist, press the Clear button to delete the track just

entered. After the playlist has been saved by pressing the Stop button, press the Clear

button to delete the entire playlist. To delete a single track, stop play, press the Check

button repeatedly until the desired track appears and press the Clear button. Press

the Play or Stop button to exit the Check mode.

Radio

: If the current station has not been programmed into a preset, press Program/

Memory and press the Enter button to store the station at the current preset number,

or use the numeric keys to enter a different preset number. The new preset will

overwrite the existing one.

USB or CD (Audio or Data)

tracks to the playlist by using the Skip/Scan Transport Controls or the numeric keys

to select the t rack, then press the Program button to enter t he selection. Add up to

30 files. Press Play to play the playlist, or Stop to save the playlist without playing it.

During playback, the order of the track in the playlist will appear on the left, with the

disc’s track number to the right. See page 14 and 15.

: Press the Program button to begin Program Mode. Add

Remote control functions

Transport Controls

Track Skip Up/Down (iPod, CD or USB): Press and release the Next/Previous

skip buttons to skip to the next track, or the beginning of the current track. Press the

Previous Skip button twice to skip to the previous track.

Scan Forward/Reverse: These buttons function differently, depending on which

source has been selected:

iPod, CD or USB

•

track.

•

Radio:

by one increment/decrement. Press and hold a button to scan quickly through

the frequencies for next available station. Press the same button again to stop

scanning.

Play/Pause: Each tap toggles between the Play and Pause functions.

Stop: Fully stops playback.

Preset/Folder +/–: Selects a preset station or folder on a USB or data CD.

Radio

•

: Each press changes to the next or previous preset station, if any have been

programmed.

USB or Data CD

•

to the next or previous folder. After 3 seconds, the first track in the new folder will

begin playing.

Mute: Press to temporarily silence the speakers. Press again to restore audio. Muting is

also canceled if the MAS system is turned off.

NOTE: Pressing the Mute button also mutes the Analog Audio Outputs. See page 6.

Volume +/–: Increases or decreases the volume. Press and hold to change the volume

more quickly.

Numeric keys: Used to enter track numbers, radio stations or preset numbers, or while

adjusting the clock and alarm times.

–10 and +10 numeric Key: Used with a USB device or CD to quickly advance through a

large number of tracks. Each press of these keys changes to the next or previous track in

increments of 10.

: Press and hold a button to scan forward or reverse within a

Press and release a button to tune to the next higher or lower frequency

: Press once to open the current folder. Each additional press changes

Page 10

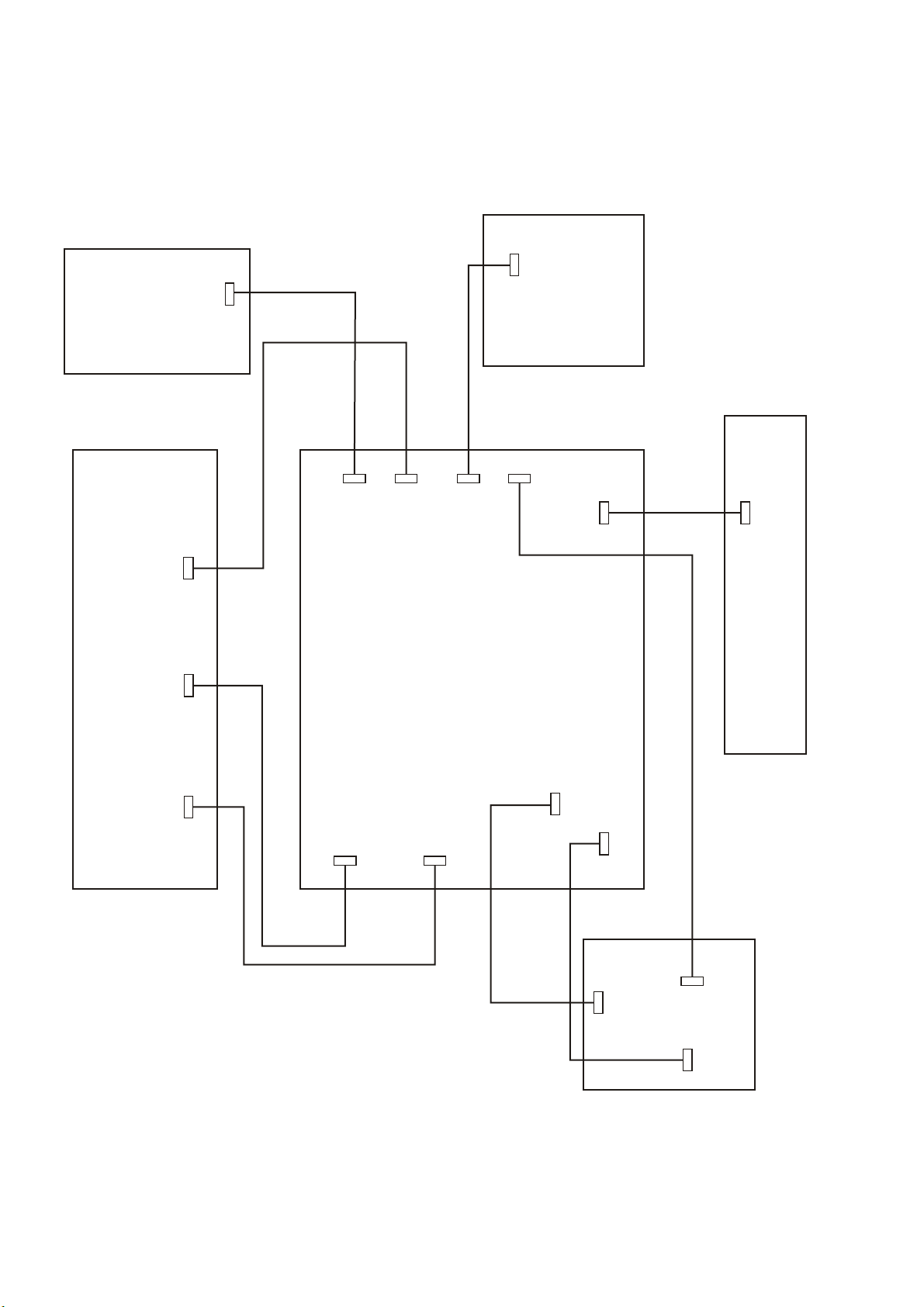

Line

8

Front

Panel

Control

Circuit

ConnectoionAmp

+5V

DGND

AGND

+3.3V

LDO

+1V

AMP_R-

AMP_L-

AMP_R+

AMP_L+

-15V

+15V

NJM

2608

Out_L

Out_R

+8V

MOLEX

IR

Sense

TOUCH

VFD

1

Sense

TOUCH

Driver

SPI

+5V

CPU

/SPI

2

I C

LDO

Out

Headphone

Out

Headphone

HP_Out_R

HP_Out_L

HP

AMP

Audio

Line

Line_Out_L

Out

Out

Line_Out_R

Subwoofer

Out

Subwoofer

Subwoofer_Out

Output

Main Digital

Coax

Out

SPDIF_SW

Coaxial_Out

1

2

3

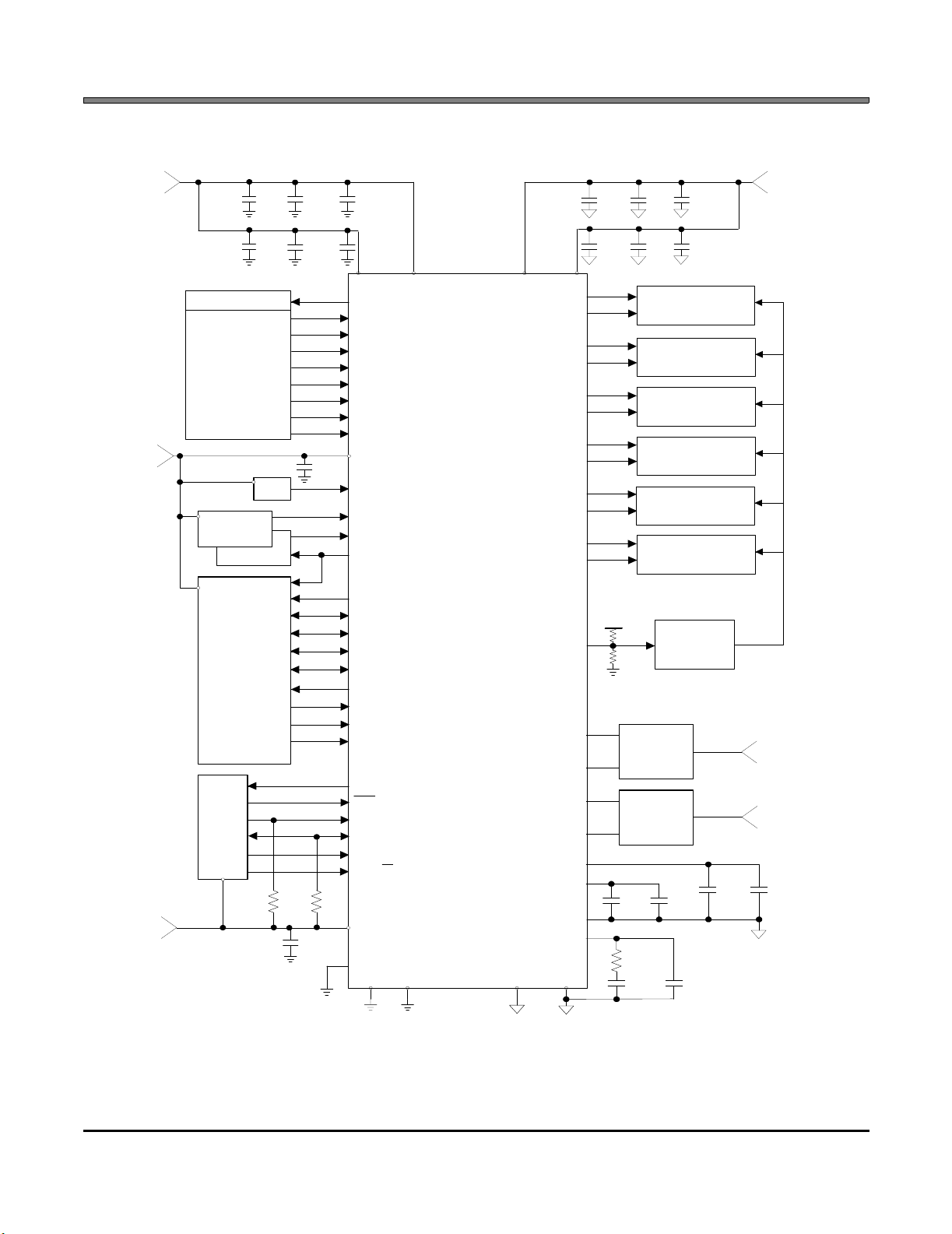

MAS111 Head Unit Block Diagram

Servo

Ali

SPI

M5673

USB 1.1

SPDIF_ALI_OUT

D/A

2

NJM

2608

Subwoofer_Out

NJM

2608

-

Dac3_L

AINL

+

-

2608

NJM

C

I

SPDIF_OUT_DIRECT

TXP

_Input_Out

SI

2

SAI

AINR

-

+

NJM

2608

SWITCH

74HC151

Tx

CS48540

_Iine_Out

S

2

I

DSP

_Main_Out

_Sub_Out

S

S

2

2

I

I

CX

2

3

Line_Out_L

++-

Dac2_L

NJM

NJM

2608

2608

+

Line_Out_R

-

Dac2_R

NJM

2608

Main_Out_R

Main_Out_L

Main_Out_R

Main_Out_L

NJM

2608

Relay_Control

Offset_detect

VOL-

VOL+

Mute_Audio

Standby

IR

Drop_detect

MM_MC_Sel

SPDIF_SW

Main

CPU

CI

2

+

-

Dac1_L

+

-

Dac1_R

CS42516

Spdif_In6

Spdif_In5

Spdif_In4

Spdif_In3

Spdif_In2

Spdif_In1

iPod CHECK

SPDIF_DAB_OUT

SPDIF_ALI_OUT

Coaxial_1

Coaxial_2

Optical_1

Optical_2

Line_In_1

Line_In_2

Line_In_3

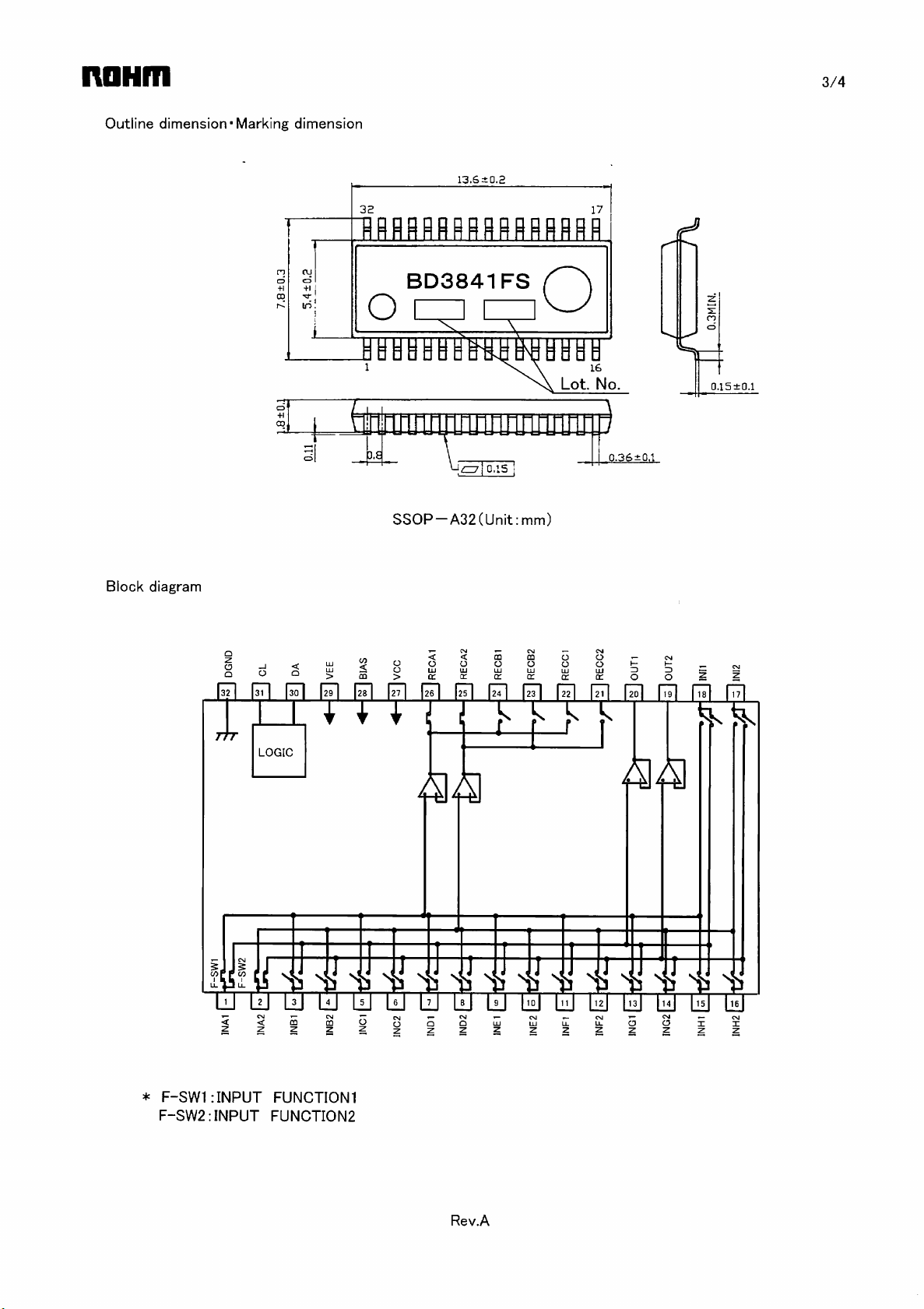

BD3841FS

4

Line_In_4

Line_In_5

Line_In_6

Line_In_7

4

dB30

2

iPod_In-L

iPod_In-R

LMV

832

DRIVER

MOTOR

5

OPU

LOADER

SLOT IN

Disc

Drive

D D

RELAYUSB Front

USB Back

USB

Inputs

UART iPod TX

UART iPod RX

In-R

In-L

Charger GND

Charger +8V

iPod CHECK

HW Identification

iPod

Connector

iPod

C C

I C

C

2

I

Tuner_L

Tuner_R

SPI RDS

SPI Tuner

CAN

DAB/DAB+/DMB

Venice 7.1

Frontier Silicon

RF

Coax 2

Antenna

RF

DAB

RF

Coax 1

Digital

Optical 1

Inputs

B B

Optical 2

Tuner

RF_FM

iPod_In-R

RF

RF Antenna

RIAA

5

TV

Line

AUX

Line In

Inputs

A A

Jack_In_R

Jack_In_L

iPod_In-L

Phono MM

Page 11

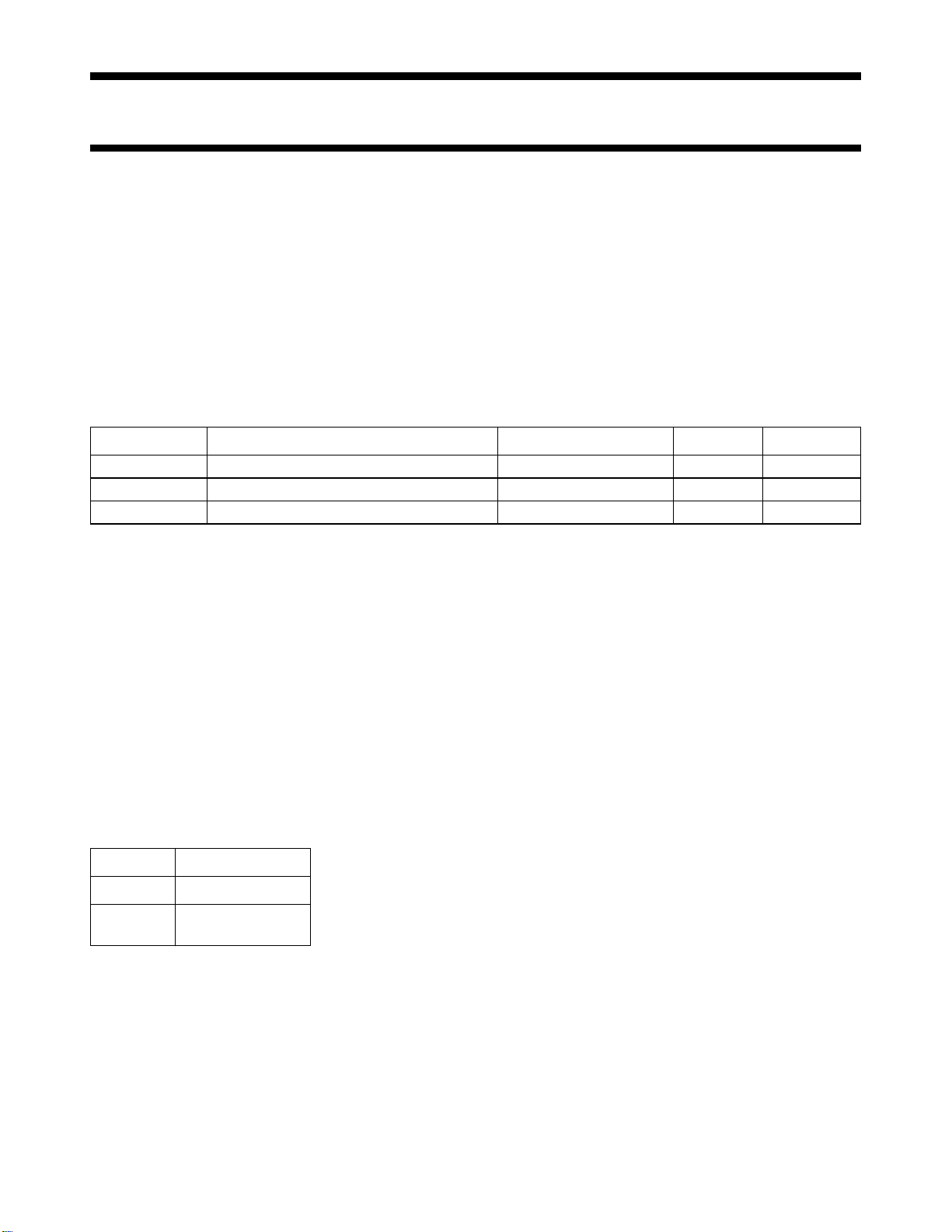

TUNER

9

WIRING DIAGRAM

BOARD

HEADPHONE

2P

CON8

16P

CN1

7P

CN1

RS232 BOARD

9P

CN2

10P

CN3

13P

CON1

9P

CON7

CON11

7P

CON5

CON10

10P

13P

6P

CON3

MAIN BOARD

CON9

16P

CON4

16P

DISPLAY BOARD

5P

CON2

CD CORE

Page 12

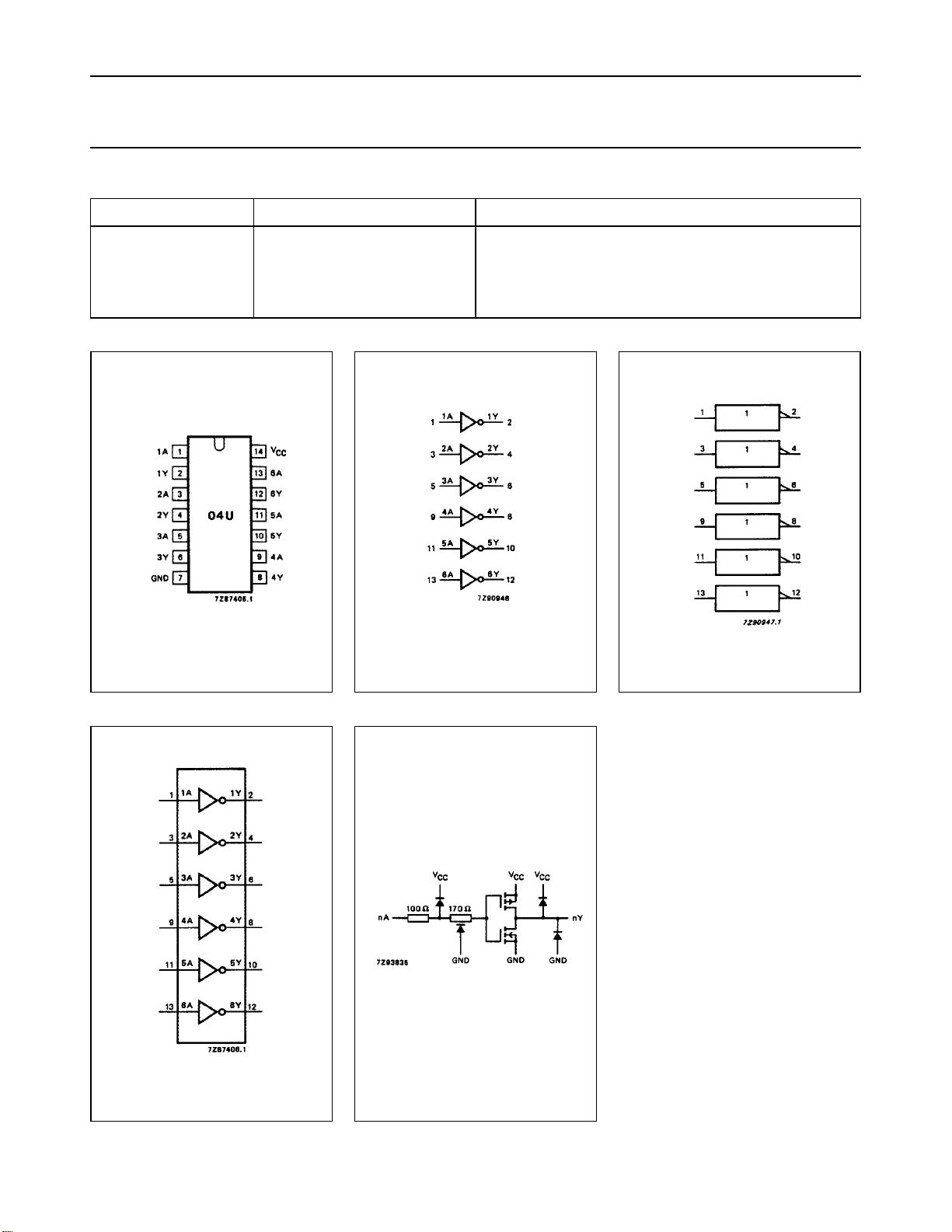

Philips Semiconductors Product specification

10

Hex inverter 74HCU04

FEATURES

• Output capability: standard

• ICC category: SSI

GENERAL DESCRIPTION

The 74HCU04 is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL).

It is specified in compliance with JEDEC standard no. 7A.

The 74HCU04 is a general purpose hex inverter. Each of the six inverters is a single stage

QUICK REFERENCE DATA

GND = 0 V; T

SYMBOL PARAMETER CONDITIONS TYP. UNIT

/ t

t

PHL

PLH

C

I

C

PD

=25°C; tr=tf=6ns

amb

propagation delay nA to nY CL= 15 pF; VCC=5V 5 ns

input capacitance 3.5 pF

power dissipation capacitance per inverter note 1 10 pF

Note

1. C

is used to determine the dynamic power dissipation (PD in µW):

PD

PD=CPD× V

2

× fi + ∑ (CL× V

CC

2

× fO) where:

CC

fi= input frequency in MHz

fo= output frequency in MHz

CL= output load capacitance in pF

VCC= supply voltage in V

∑ (CL× V

2

× fo) = sum of outputs

CC

ORDERING INFORMATION

“74HC/HCT/HCU/HCMOS Logic Package Information”

See

FUNCTION TABLE

INPUT OUTPUT

nA nY

L

H

H

L

Note

1. H = HIGH voltage level

L = LOW voltage level

.

Page 13

Philips Semiconductors Product specification

Hex inverter 74HCU04

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 3, 5, 9, 11, 13 1A to 6A data inputs

2, 4, 6, 8, 10, 12 1Y to 6Y data outputs

7 GND ground (0 V)

14 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

Fig.4 Functional diagram.

Fig.5 Schematic diagram

(one inverter).

11

Page 14

12

Page 15

13

Page 16

14

Page 17

Features

• Low-voltage and Standard-voltage Operation

– 1.8 (V

= 1.8V to 5.5V)

CC

• Internally Organized 256 x 8 (2K)

• Two-wire Serial Interface

• Schmitt Trigger, Filtered Inputs for Noise Suppression

• Bidirectional Data Transfer Protocol

• 1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) Compatibility

• Write Protect Pin for Hardware Data Protection

• 8-byte Page (2K) Write Modes

• Partial Page Writes Allowed

• Self-timed Write Cycle (5 ms max)

• High-reliability

– Endurance: 1 Million Write Cycles

– Data Retention: 100 Years

• 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3), 5-lead SOT23,

8-lead TSSOP and 8-ball dBGA2 Packages

• Lead-free/Halogen-free

• Available in Automotive

• Die Sales: Wafer Form, Tape and Reel and Bumped Wafers

Description

The AT24C02B provides 2048 bits of serial electrically erasable and programmable

read-only memory (EEPROM) organized as 256 words of 8 bits each. The device is

optimized for use in many industrial and commercial applications where low-power

and low-voltage operation are essential. The AT24C02B is available in space-saving

8-lead PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3)

SOT23, 8-lead TSSOP, and 8-ball dBGA2 packages and is accessed via a Two-wire

serial interface. In addition, the AT24C02B is available in 1.8V (1.8V to 5.5V) version.

, 5-lead

Two-wire

Serial EEPROM

2K (256 x 8)

AT24C02B

Table 0-1. Pin Configuration

Pin Name Function

A0 - A2 Address Inputs

SDA Serial Data

SCL Serial Clock Input

WP Write Protect

GND Ground

VCC Power Supply

Note: For use of 5-lead SOT23, the

software A2, A1, and A0 bits in

the device address word

must be set to zero to properly communicate.

8-lead Ultra-Thin

Mini-MAP (MLP 2x3)

VCC

WP

SCL

SDA

8

7

6

5

A0

1

A1

2

A2

3

GND

4

8-ball dBGA2

VCC

WP

SCL

SDA

Bottom View Bottom View

8-lead TSSOP

1

A0

2

A1

3

A2

GND

4

5-lead SOT23

SCL

GND

SDA

1

2

3

8

VCC

7

WP

6

SCL

5

SDA

WP

5

VCC

4

8-lead SOIC

A0

A1

A2

GND

8-lead PDIP

A0

A1

A2

GND

1

8

7

6

5

1

2

3

4

1

2

3

4

A0

2

A1

3

A2

4

GND

VCC

8

WP

7

SCL

6

SDA

5

8

VCC

7

WP

6

SCL

5

SDA

5126H–SEEPR–8/07

151718

Page 18

Page 19

Page 20

Page 21

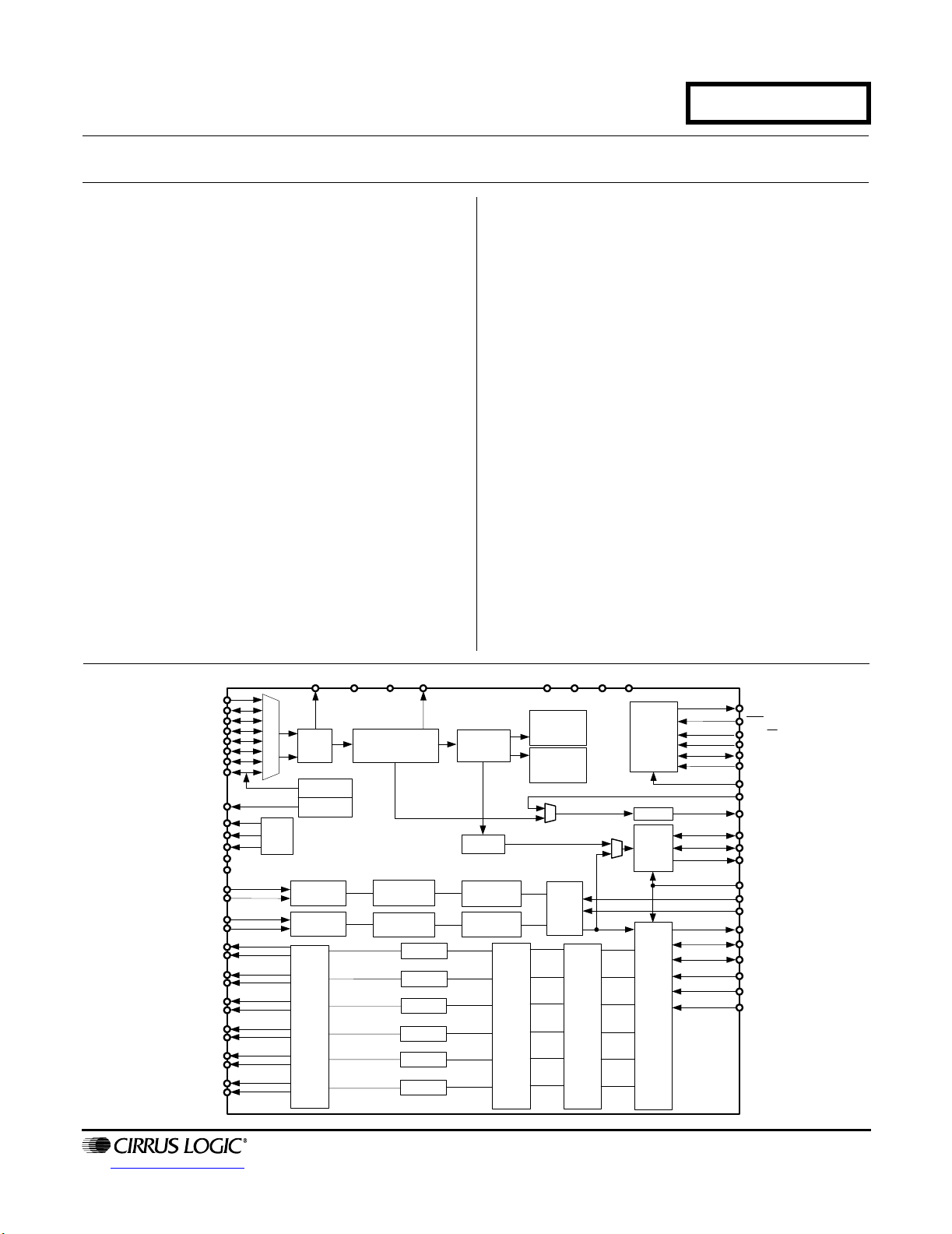

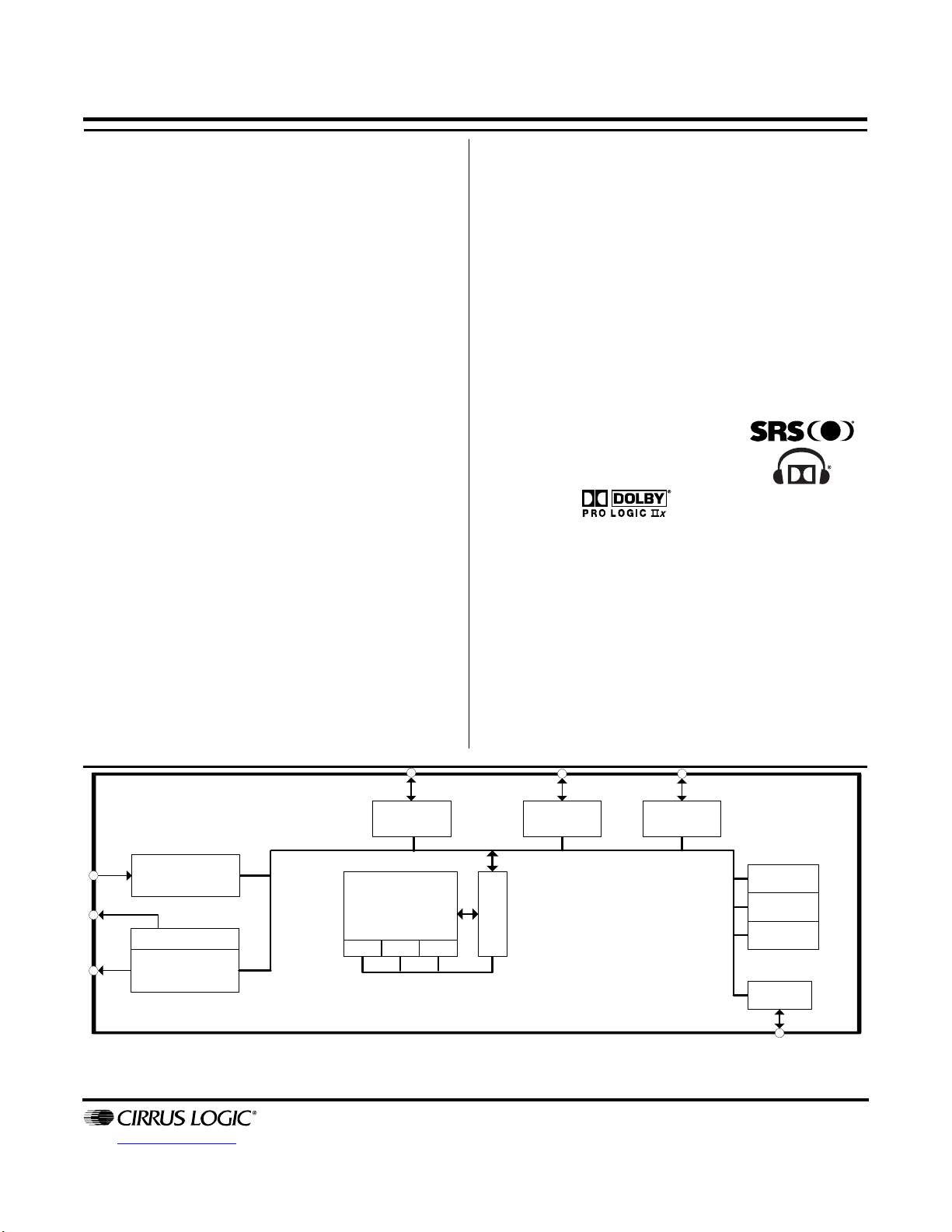

CS42516

110 dB, 192 kHz 6-Ch Codec with S/PDIF Receiver

Features

Six 24-bit D/A, two 24-bit A/D Converters

110 dB DAC / 114 dB ADC Dynamic Range

-100 dB THD+N

System Sampling Rates up to 192 kHz

S/PDIF Receiver Compatible with EIAJ

CP1201 and IEC-60958

Recovered S/PDIF Clock or System Clock

Selection

8:2 S/PDIF Input MUX

ADC High-Pass Filter for DC Offset Calibration

Expandable ADC Channels and One-Line

Mode Support

Digital Output Volume Control with Soft Ramp

Digital +/-15 dB Input Gain Adjust for ADC

Differential Analog Architecture

Supports Logic Levels between 1.8 V and 5 V

General Description

The CS42516 codec provides two analog-to-di gital and

six digital-to-analog delta-sigma converters, as well as

an integrated S/PDIF receiver.

The CS42516 integrated S/PDIF receiver supports up

to eight inputs, clock recovery circuitry and format autodetection. The internal stereo ADC is capable of independent channel gain control for single-ended or

differential analog inputs. All six channels of DAC provide digital volume control and differential analog

outputs. The general-purpose outputs may be driven

high or low, or mapped to a variety of DAC mute controls or ADC overflow indicators.

The CS42516 is ideal for audio systems requiring wide

dynamic range, negligible distortion and low noise, such

as A/V receivers, DVD receivers, digital speaker and

automotive audio systems.

The CS42516 is available in a 64-pin LQFP package in

both Commercial (-10° to 70° C) and Automotive

(-40° to 85° C) grades. The CDB42518 Customer Demonstration board is also available for device evaluation.

Refer to “Ordering Information” on page 89.

RXP0

RXP1/GPO1

RXP2/GPO2

RXP3/GPO3

RXP4/GPO4

RXP5/GPO5

RXP6/GPO6

RXP7/GPO7

MUTEC

FILT+

VQ

REFGND

VA

AGND

AINL+

AINLAINR+

AINR-

AOUTA1+

AOUTA1-

AOUTB1+

AOUTB1-

AOUTA2+

AOUTA2-

AOUTB2+

AOUTB2-

AOUTA3+

AOUTA3-

AOUTB3+

AOUTB3-

Ref

Rx

GPO

MUTE

ADC#1

ADC#2

Analog Filter

VARX AGND

Clock/Data

Recovery

Digital Filter

Digital Filter

DAC#1

DAC#2

DAC#3

DAC#4

DAC#5

DAC#6

S/PDIF

Decoder

DEM

Gain & Clip

Gain & Clip

Digital Filter

DGND

C&U Bit

Data Buffer

Format

Detector

Internal MCLK

ADC

Serial

Data

DGND VDLPFLTTXP

VD

INT

Control

Port

Mult/Div

Serial

Audio

Interface

Port

CODEC

Serial

Port

Volume Control

RST

AD0/CS

AD1/CDIN

SDA/CDOUT

SCL/CCLK

VLC

OMCK

RMCK

SAI_LRCK

SAI_SCLK

SAI_SDOUT

VLS

ADCIN1

ADCIN2

CX_SDOUT

CX_LRCK

CX_SCLK

CX_SDIN1

CX_SDIN2

CX_SDIN3

http://www.cirrus.com

NOVEMBER '05

DS583F1

19

Page 22

2. PIN DESCRIPTIONS

VLS

CX_SDIN2

TEST

CX_SDIN3

SAI_SCLK

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

SAI_LRCK

OMCK

ADCIN1

SAI_SDOUT

RMCK

CX_SDOUT

ADCIN2

DGND

VD

TXP

CS42516

RXP0

VD

DGND

VLC

INT

RST

AINR-

AINR+

AINL+

AINL-

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

CX_SDIN1

CX_SCLK

CX_LRCK

SCL/CCLK

SDA/CDOUT

AD1/CDIN

AD0/CS

Pin Name # Pin Description

CX_SDIN1

CX_SDIN2

CX_SDIN3

CX_SCLK

CX_LRCK

VD

DGND

VLC

SCL/CCLK

SDA/CDOUT

AD1/CDIN

AD0/CS

1

Codec Serial Audio Data Input (Input) - Input for two’s complement serial audio data.

64

63

CODEC Serial Clock (Input/Output) - Serial clock for the CODEC serial audio interface.

2

CODEC Left Right Clock (Input/Output) - Determines which channel, Left or Right, is currently active on

3

the CODEC serial audio data line.

4

Digital Power (Input) - Positive power supply for the digital section.

51

5

Digital Ground (Input) - Ground reference. Should be connected to digital ground.

52

6

Control Port Power (Input) - Determines the required signal level for the control port.

Serial Control Port Clock (Input) - Serial clock for the serial control port. Requires an external pull-up

7

resistor to the logic interface voltage in I²C mode as shown in the Typical Connection Diagram.

Serial Control Data (Input/Output) - SDA is a data I/O line in I²C mode and requires an external pull-up

8

resistor to the logic interface voltage, as shown in the Typical Connection Diagram. CDOUT is the output

data line for the control port interface in SPI mode.

Address Bit 1 (I²C)/Serial Control Data (SPI) (Input) - AD1 is a chip address pin in I²C mode; CDIN is

9

the input data line for the control port interface in SPI mode.

Address Bit 0 (I²C)/Control Port Chip Select (SPI) (Input) - AD0 is a chip address pin in I²C mode; CS

10

is the chip select signal in SPI mode.

CS42516

17 18 19 20 21 22 23 24 25 26 27 2 8 29 30 31 32

VQ

NCNCNC

FILT+

REFGND

NC

VA

AGND

AOUTB3-

AOUTB3+

AOUTB2-

AOUTA3-

AOUTA3+

AOUTB2+

AOUTA2+

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

RXP1/GPO1

RXP2/GPO2

RXP3/GPO3

RXP4/GPO4

RXP5/GPO5

RXP6/GPO6

RXP7/GPO7

VARX

AGND

LPFLT

MUTEC

AOUTA1AOUTA1+

AOUTB1+

AOUTB1AOUTA2-

DS583F1

20

Page 23

INT

RST

AINR-

AINR+

AINL+

AINLVQ

FILT+

REFGND

NC

AOUTA1 +,AOUTB1 +,AOUTA2 +,AOUTB2 +,AOUTA3 +,AOUTB3 +,-

VA

VARX

AGND

MUTEC

LPFLT

RXP7/GPO7

RXP6/GPO6

RXP5/GPO5

RXP4/GPO4

RXP3/GPO3

RXP2/GPO2

RXP1/GPO1

RXP0

TXP

VLS

SAI_SDOUT

RMCK

CX_SDOUT

Interrupt (Output) - The CS42516 will generate an interrupt condition as per the Interrupt Mask register.

11

See “Interrupts” on page 40 for more details.

Reset (Input) - The device enters a low power mode and all internal registers are reset to their default

12

settings when low.

13

Differential Right Channel Analog Input (Input) - Signals are presented differentially to the delta-sigma

14

modulators via the AINR+/- pins.

15

Differential Left Channel Analog Input (Input) - Signals are presented differentially to the delta-sigma

16

modulators via the AINL+/- pins.

17

Quiescent Voltage (Output) - Filter connection for internal quiescent reference voltage.

18

Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling circuits.

19

Reference Ground (Input) - Ground reference for the internal sampling circuits.

20

21

No Connect Pins - Do not make any connection to these pins.

22

23

36,37

35,34

32,33

Differential Analog Output (Output) - The full-scale differential analog output level is specified in the

31,30

Analog Characteristics specification table.

28,29

27,26

24

Analog Power (Input) - Positive power supply for the analog section.

41

25

Analog Ground (Input) - Ground reference. Should be connected to analog ground.

40

Mute Control (Output) - The Mute Control pin outputs high impedance following an initial power-on con-

dition or whenever the PDN bit is set to a ‘1’, forcing the codec into power-d own mode. The signal will

remain in a high impedance state as long as the part is in power-down mode. The Mute Control pin goes

38

to the selected “active” state during reset, muting, or if the master clock to left/right clock frequency ratio

is incorrect. This pin is intended to be used as a control for external mute circuits to prevent the clicks

and pops that can occur in any single supply system. The use of external mute circuits are not manda-

tory but may be desired for designs requiring the absolute minimum in extraneous clicks and pops.

39

PLL Loop Filter (Output) - An RC network should be connected between this pin and ground.

42

S/PDIF Receiver Input/ General Purpose Output (Input/Output) - Receiver inputs for S/PDIF encoded

43

data. The CS42516 has an internal 8:2 multiplexer to select the active receiver port, according to the

44

Receiver Mode Control 2 register. These pins can also be configured as general purpose output pins,

45

ADC Overflow indicators or Mute Control outputs accor din g to the RXP/Ge n eral Purp o se Pin C ontro l

46

registers.

47

48

S/PDIF Receiver Input (Input) - Dedicated receiver input for S/PDIF encoded data.

49

S/PDIF Transmitter Output (Output) - S/PDIF encoded data output, mapped directly from one of the

50

receiver inputs as indicated by the Receiver Mode Control 2 register.

53

Serial Port Interface Power (Input) - Determines the required signal level for the serial port interfaces.

Serial Audio Interface Serial Data Output (Output) - Output for two’s complement serial audio PCM

54

data from the S/PDIF incoming stream. This pin can also be configured to transmit the output of the inter-

nal and external ADCs.

Recovered Master Clock (Output) - Recovered master clock output from the External Clock Reference

55

(OMCK, pin 59) or the PLL which is locked to the incoming S/PDIF stream or CX_LRCK.

CODEC Serial Data Output (Output) - Output for two’s complement serial audio data from the internal

56

and external ADCs.

CS42516

DS583F1

21

Page 24

ADCIN1

ADCIN2

OMCK

TEST

SAI_LRCK

SAI_SCLK

CS42516

External ADC Serial Input (Input) - The CS42516 provides for up to two external stereo analog to digital

58

converter inputs to provide a maximum of six channels on one serial data output line when the CS42516

57

is placed in One-Line Mode.

External Reference Clock (Input) - External clock reference that must be within the ranges specified in

59

the register “OMCK Frequency (OMCK Freqx)” on page 53.

62

Test Pin (Input) - This pin must be connected to DGND.

Serial Audio Interface Left/Right Clock (Input/Output) - Determines which channel, Left or Right, is

60

currently active on the serial audio data line.

Serial Audio Interface Serial Clock (Input/Output) - Serial clock for the Serial Audio Interface.

61

DS583F1

22

Page 25

3. TYPICAL CONNECTION DIAGRAM

CS42516

+3.3 V to +5 V

+2.5 V

to + 5 V

+1.8 V

to + 5 V

** Resistors are required for

10 µF

10 µF

Driver

S/PDIF

Inte rfa c e

Up to 8

Sources

CS5361

A/D Converter

CS5361

A/D Converter

Digital Audio

Processor

Micro-

Controller

2

C control port operation

I

0.1 µF 0.01 µF

+

0.1 µF

+

OSC

** **

2 kΩ 2 kΩ

0.01 µF

0.1 µF

0.1 µF

50

49

48

47

46

45

44

43

42

53

59

58

57

55

54

60

61

3

2

56

1

64

63

11

12

7

8

9

10

6

62

4

VD

TXP

RXP0

RXP1/GPO1

RXP2/GPO2

RXP3/GPO3

RXP4/GPO4

RXP5/GPO5

RXP6/GPO6

RXP7/GPO7

VLS

OMCK

ADCIN1

ADCIN2

RMCK

51

CS42516

SAI_SDOUT

SAI_LRCK

SAI_SCLK

CX_LRCK

CX_SCLK

CX_SDOUT

CX_SDIN1

CX_SDIN2

CX_SDIN3

INT

RST

SCL/CCLK

SDA/CDOUT

AD1/CDIN

AD0/CS

VLC

TEST

DGND

DGND

52 40

5

25

41

VAVD

24

VA

AOUTA1+

AOUTA1-

AOUTB1+

AOUTB1-

AOUTA2+

AOUTA2-

AOUTB2+

AOUTB2-

AOUTA3+

AOUTA3-

AOUTB3+

AOUTB3-

MUTEC

AINL+

AINL-

AINR+

AINR-

VQ

FILT+

REFGND

LPFLT

AGNDAGND

0.01 µF

0.01 µF

36

37

35

34

32

33

31

30

28

29

27

26

+VA

38

15

16

14

13

17

18

19

39

*

*

0.1 µF

RFILT

CFILT

0.1 µF

+

10 µF

0.1 µF

+

10 µF

Analog Output Buffer

and

Mute Circuit (optional)

Analog Output Buffer

and

Mute Circuit (optional)

Analog Output Buffer

and

Mute Circuit (optional)

Analog Output Buffer

and

Mute Circuit (optional)

Analog Output Buffer

and

Mute Circuit (optional)

Analog Output Buffer

and

Mute Circuit (optional)

Mute

Drive

(optional)

* Pull up or down as

required on startup if the

M u te C o n tro l is u s e d .

Analog

2700 pF*

Input

1

Buffer

Analog

Input

2700 pF*

1

Buffer

+

100 µF

3

3

CRIP

0.1 µF

3

+5 V

2

2

2

2

2

2

Left Analog Input

Right Analog Input

+

4.7 µF

DS583F1

Connect DGN D and A G ND at single point near Codec

1. See the ADC Input Filter section in the Appendix.

2. See the DAC O utput Filter section in the Appendix.

3. See the PLL Filter section in the Appendix.

Figure 5. Typical Connection Diagram

23

Page 26

CS485xx Family Data Sheet

FEATURES

Cost-effective, High-performance 32-bit DSP

— 300,000,000 MAC/S (multiply accumulates per second)

— Dual MAC cycles per clock

— 72-bit accumulators are the most accurate in the industry

— 24k x 32 SRAM, 2k blocks - assignable to data or program

— Internal ROM contains a variety of configurable sound

enhancement feature sets

— 8-channel internal DMA

— Internal watch-dog DSP lock-up prevention

DSP Tool Set w/ Private Keys for Protecting Customer IP

Configurable Serial Audio Inputs/Outputs

— Configurable for all input/output types

— Maximum 32-bit @ 192 kHz

— Supports 32-bit audio sample I/O between DSP chips

— TDM input modes (multiple channels on same line)

— 192 k Hz SP DIF transmitter

— Multi-channel DSD direct stream digital SACD input

Supports Two Diff eren t Input Fs Sam ple Rates

— Output can be master or slave

— Dual processing path capability

— Input supports dual domain slave clocking

— Hardware assist time sampling for sample rate conversion

Integrated Clock Manager/PLL

— Can operate from external crystal, external oscillator

Input Fs Auto Detection

Host & Boot via Serial Interface

Configurable GPIOs and External Interrupt Input

1.8V Core and a 3.3V I/O that is tolerant to 5V input

Low-power Mode

— “Energy-Star Ready” via low-power mode, 268 µW in

standby

Differentiating from the legacy Cirrus multi-standard, multichannel decoders, this new CS485xx family is still based on

the same high-performance 32-bit fixed point Digital Signal

Processor core but instead is equipped with much less

memory, tailoring it for more cost-effective applications

associated with multi-channel and virtual-channel sound

enhancements. Target applications are:

— Digital Televisions

— Multimedia Peripherals

—iPod

— Automotive Head Units

— Automotive Outboard Amplifiers

— HD-DVD & Blu-ray Disc DVD Receivers

— PC Speakers

There are are also a wide variety of licensable DSP codes

available today as seen by the following examples:

Cirrus also ha s developed, or is developing their own royal tyfree versions of popular features sets like Cirrus Bass

Manager, Cirrus Dynamic Volume Leveler, Cirrus Original

Multichannel Surround, Cirrus Virtual Speaker & Cirrus 3DAudio.

The CS485xx family is programmed using the Cirrus

proprietary DSP Composer

Processing chains may be designed using a drag-and-drop

interface to place/utilize functional macro audio DSP

primitives. The end result is a software image that is downloaded to the DSP via serial host or serial boot modes.

Ordering Information:

See page 20 for ordering information

®

Docking Stations

L

A

FT

DRA

™

GUI development tool.

®

DELPHI

D

M

A

GPIO Debug

12 Ch. Audio In /

6 Ch. SACD In

S/PDIF

12 Ch PCM

Audio Out

Serial

Control 1

32-bit

DSP

P X Y

CONFIDENTI

http://www.cirrus.com

24

Watchdog

TMR1

TMR2

PLL

Page 27

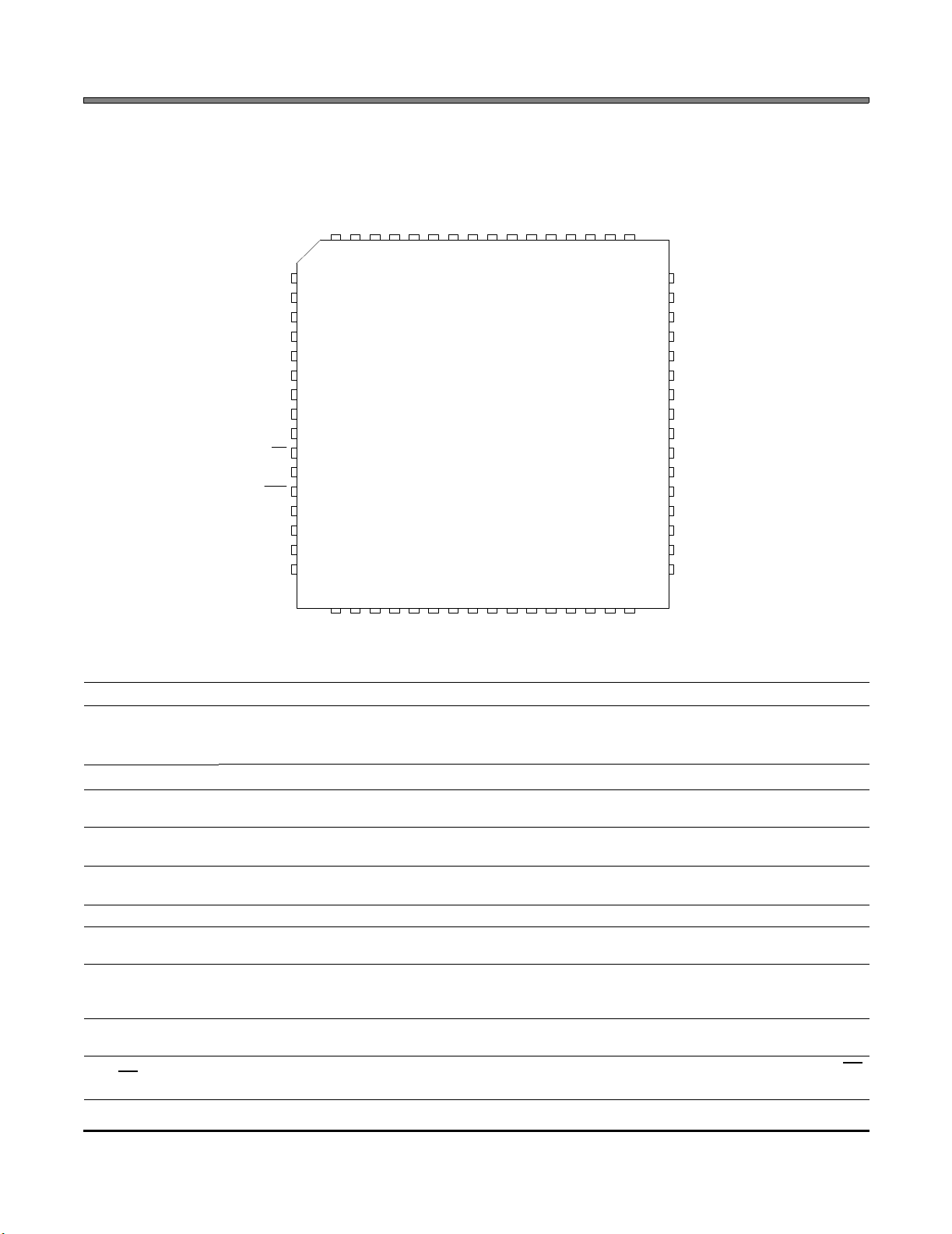

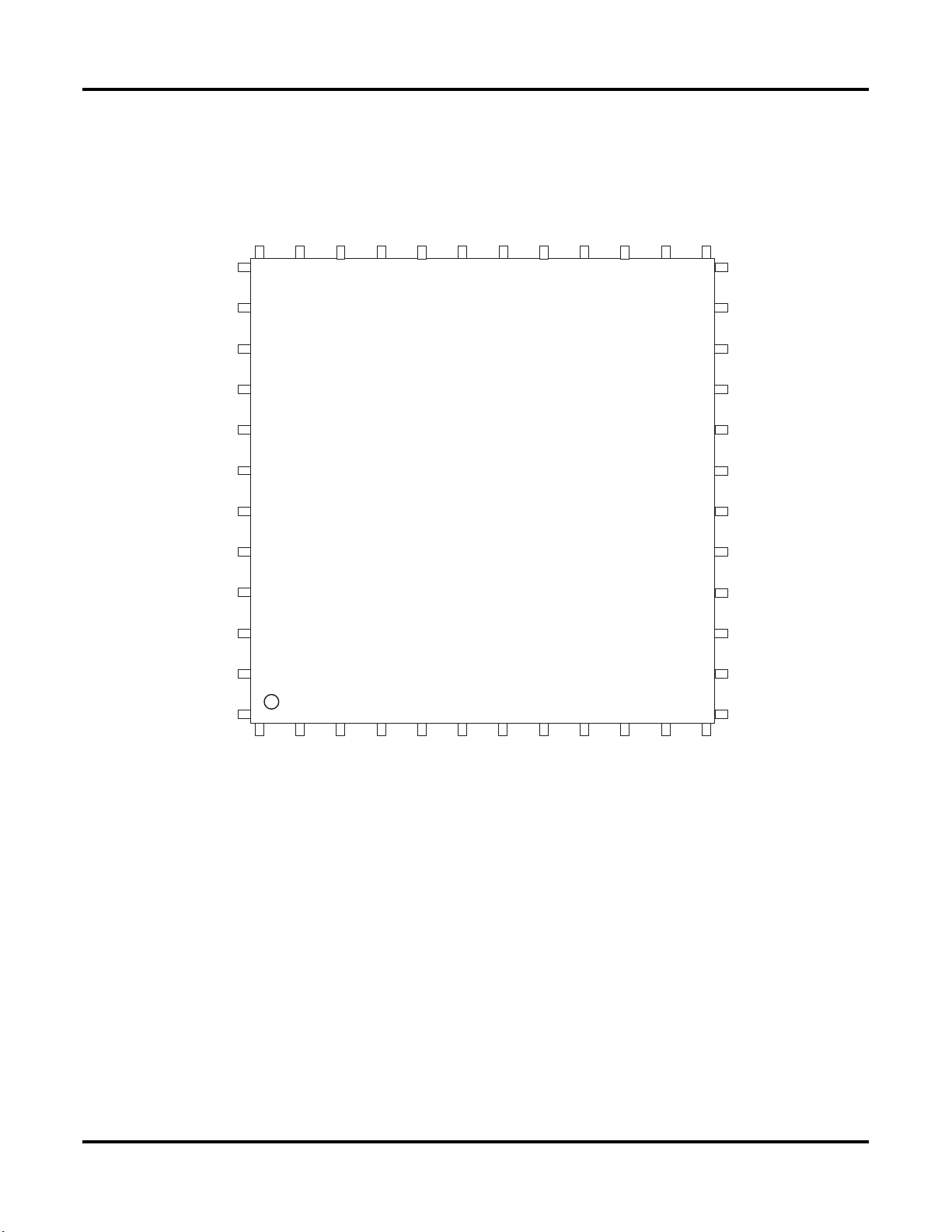

8.2 CS48540, 48-pin LQFP Pinout Diagram

GPIO10, SCP__MISO / SDA

GPIO9, SCP_MOSI

GND4

GPIO7, HS4

33

32

VDDIO3

37

GPIO11, SCP_CLK

36

35

34

GPIO6, DAO2_DATA0, HS3

31

CS485xx Family Data Sheet

32-bit Audio Decoder DSP Family

GPIO3, DAO1_ DATA1, HS1

VDD2GND2

GPIO5, XMTA

GNDIO3

30

28

29

GPIO4, DAO1_ DATA2, HS2

GPIO18, DAO_MCLK

26

27

25

VDDIO2

24

GPIO8, SCP_CS#

GPOI12, SCP_IRQ#

GNDIO4

GPIO13, SCP_BSY#, EE_CS#

VDD3

XTAL_OUT GPIO15, DAI2_SCLK

XTO

GNDA

PLL_REF_RES

VDDA (3.3V)

38

39

40

23

22

21

DAO_SCLK

GND3

DAO_LRCLK

FT

41

42

43

CS48540

48-Pin LQFP

DAO1_DATA0, HS0

20

19

GNDIO2

18

DRA

XTI

44

45

46

47

48

1

2

3

4

5

6

7

L

A

8

HI

9

10

11

GPIO14, DAI2_LRCLK

17

16

VDD1

GPIO17,

15

14

GPIO2

GPIO1, DAI1_DATA2

13

12

DAI2_DATA0

TEST

DBDA

RESET#

GND1

DBCK

GNDIO1

DAI1_LRCLK

DAI1_SCLK

DELP

GPIO16, DAI1_DATA0

GPIO0, DAI1_DATA1

Figure 12. CS48540, 48-Pin LQFP Pinout

CONFIDENTI

VDDIO1

25

Page 28

FAN1112

1A 1.2V Low Dropout Linear Regulator

Features

• Low dropout voltage

• Load regulation: 0.05% typical

• Trimmed current limit

• On-chip thermal limiting

• Standard SOT-223 and TO-252 packages

• Three-terminal fixed 1.2V

Applications

• Post regulator for switching supplies

• Supply for low-voltage processors

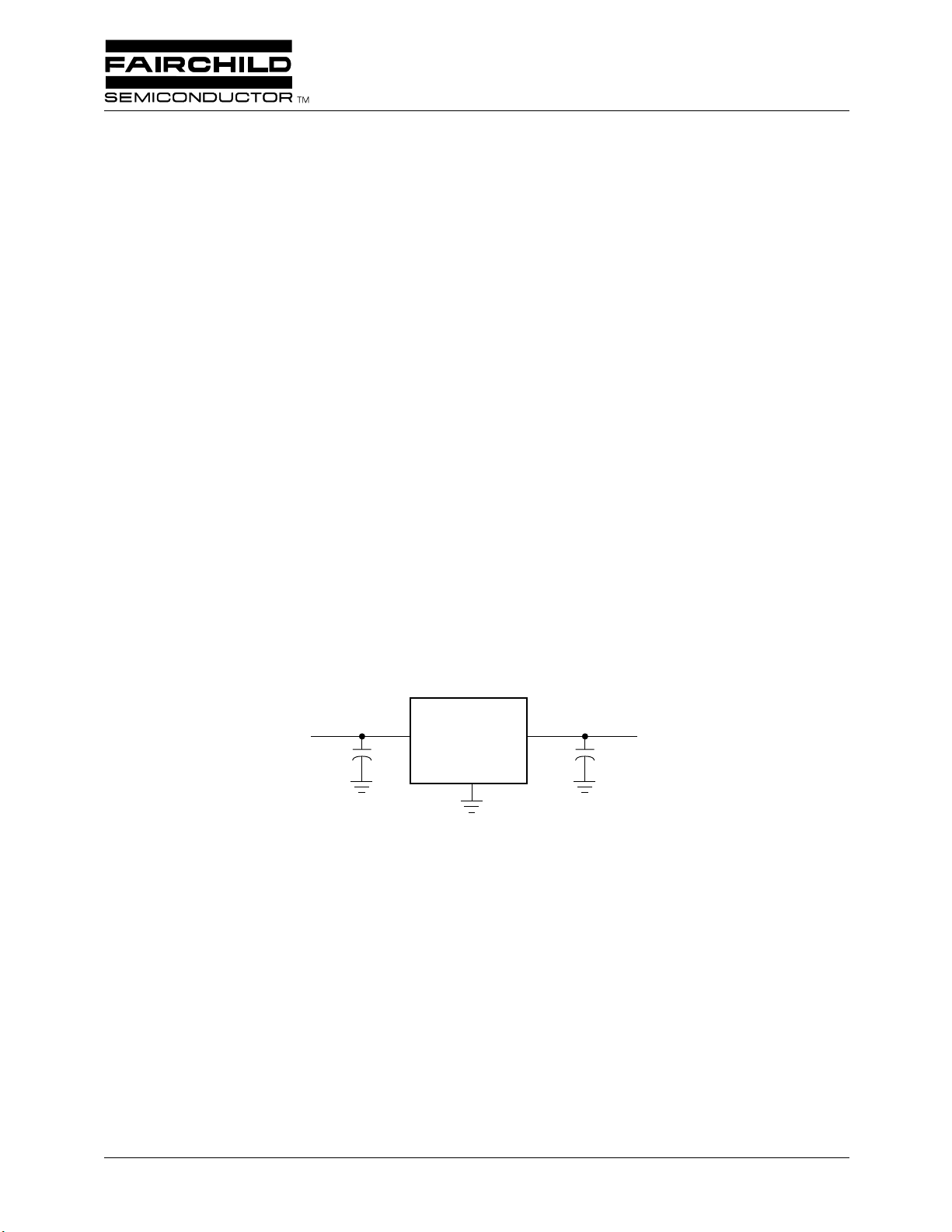

Typical Application

Description

The FAN1112 is a 1.2V low dropout three-terminal

regulator with 1A output current capability. The device has

been optimized for low voltage where transient response and

minimum input voltage are critical.

Current limit is trimmed to ensure specified output current

and controlled short-circuit current. On-chip thermal limiting

provides protection against any combination of overload and

ambient temperatures that would create excessive junction

temperatures.

Unlike PNP type regulators where up to 10% of the output

current is wasted as quiescent current, the quiescent current

of the FAN1112 flows into the load, increasing efficiency.

The FAN1112 regulator is available in the industry-standard

SOT-223 and TO-252 (DPAK) power packages.

FAN1112

V

= 3.3V V

IN

10µF

++

GND

V

OUT

IN

1.2V at 1A

22µF

26

Page 29

°

°

°

Pin Assignments

Tab is

V

OUT

Front View

Front View

Tab is V

OUT

3

IN

1

2

OUT

1

GND

GND OUT IN

23

4-Lead Plastic SOT-223

Θ

= 15°C/W*

JC

*With package soldered to 0.5 square inch copper area over backside ground plane or internal power plane., Θ

3-Lead Plastic TO-252

ΘJC = 3°C/W*

can vary from

JA

30°C/W to more than 50°C/W. Other mounting techniques may provide better thermal resistance than 30°C/W.

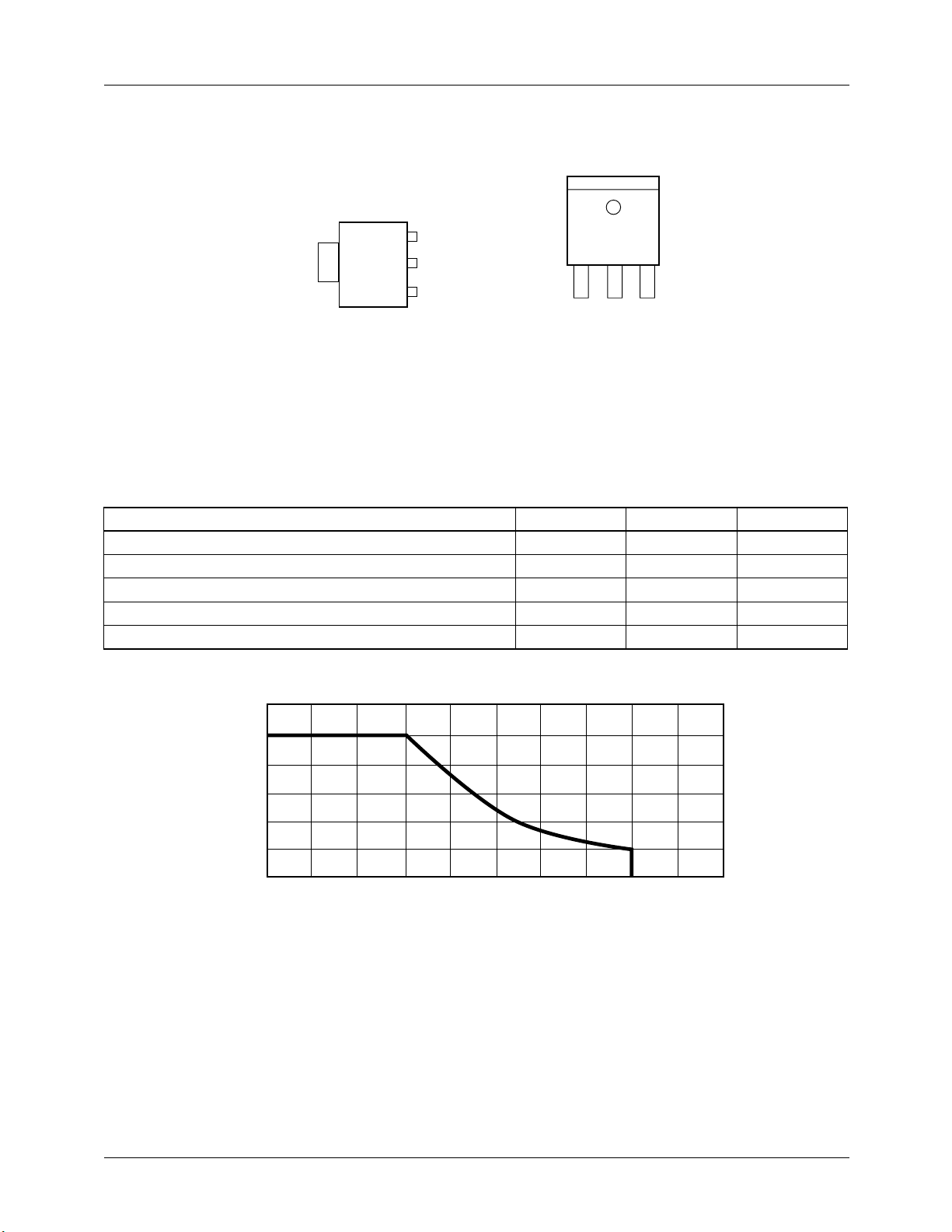

Absolute Maximum Ratings

Parameter Min. Max. Unit

V

IN

(V

IN

– V

OUT

) * I

OUT

Operating Junction Temperature Range 0 125

Storage Temperature Range -65 150

Lead Temperature (Soldering, 10 sec.) 300

1.2

1.0

0.8

(A)

0.6

OUT

I

0.4

18 V

See Figure 1

C

C

C

0.2

0

068

10 12 14 16 18 2042

V

– V

OUT

(V)

IN

Figure 1. Absolute Maximum Safe Operating Area

27

Page 30

HEF4094B

8-stage shift-and-store register

Rev. 08 — 2 April 2010 Product data sheet

1. General description

The HEF4094B is an 8-stage serial shift register. It has a storage latch associated with

each stage for strobing data from the serial input to par allel buffered 3-state outputs

QP0 to QP7. The parallel outputs may be connected directly to common bus lines. Data is

shifted on positive-going clock transitions. The data in each shift register stage is

transferred to the storage register when the strobe (STR) input is HIGH. Data in the

storage register appears at the outputs whenever the output enable (OE) signal is HIGH.

Two serial ou tputs (QS1 and QS2) are available for cascading a number of HEF4094B

devices. Serial data is available at QS1 on positive -going clock e dges to allow high -speed

operation in cascaded systems with a fast clock rise time. The same seri al data is

available at QS2 on the next negative going clock edge. This is used for cascading

HEF4094B devices when the clock has a slow rise time.

It operates over a recommended V

(usually ground). Unused inputs must be connected to V

also suitable for use over the industrial (−40 °C to +85 °C) and automotive (−40 °Cto

+125 °C) temperature ranges.

power supply range of 3 V to 15 V referenced to VSS

DD

, VSS, or another input. It is

DD

2. Features and benefits

Fully static operation

5 V, 10 V, and 15 V parametric ratings

Standardized symmetrical output characteristics

Operates across the automotive temperature range −40 °C to +125 °C

Complies with JEDEC standard JESD 13-B

3. Ordering information

Table 1. Ordering information

All types operate from

Type number Package

HEF4094BP DIP16 plastic dual in-line package; 16 leads (300 mil) SOT38-4

HEF4094BT SO16 plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

HEF4094BTS SSOP16 plastic shrink small outline package; 16 leads; body width 5.3 mm SOT338-1

−40°

C to +125°C.

Name Description Version

28

Page 31

NXP Semiconductors

001aaf119

001aaf111

4. Functional diagram

D

2

CP

3

STR

1

OE

15

QP0

8-STAGE SHIFT

REGISTER

8-BIT STORAGE

REGISTER

3-STATE OUTPUTS

QP1 QP2 QP3 QP4 QP5 QP6 QP7

QS2

QS1

HEF4094B

8-stage shift-and-store register

31

CP STR

QS1

QS2910

QP0

10

9

2OED

QP1

QP2

QP3

QP4

QP5

QP6

QP7

4

5

6

7

14

13

12

11

4 5 6 7 14 13 12 11

Fig 1. Functional diagram Fig 2. Logic symbol

STAGES 1 TO 6STAGE 0 STAGE 7

CP

STR

OE

DD

CP

FF 0

DLEQ

LATCH 0

Q

QP0

D

CP

QP1

QP2

QP3

QP4

QP5

QP6

Q

DCPQ

FF 7

DLEQ

LATCH 7

QP7

15

D QS2

Q

LE

LATCH

001aag799

QS1

Fig 3. Logic diagram

29

Page 32

NXP Semiconductors

5. Pinning information

5.1 Pinning

HEF4094B

8-stage shift-and-store register

HEF4094B

1

STR V

2

DOE

3

CP QP4

4

QP0 QP5

5

QP1 QP6

6

QP2 QP7

7

QP3 QS2

8

V

SS

001aae662

Fig 4. Pin configuration

5.2 Pin description

Table 2. Pin description

Symbol Pin Description

STR 1 strobe input

D 2 data input

CP 3 clock input

QP0 to QP7 4, 5, 6, 7, 14, 13, 12, 11 parallel output

V

SS

QS1 9 serial output

QS2 10 serial output

OE 15 output enable input

V

DD

8 ground supply voltage

16 supply voltage

16

DD

15

14

13

12

11

10

9

QS1

30

Page 33

NXP Semiconductors

001aaf117

HEF4094B

8-stage shift-and-store register

6. Functional description

Table 3. Function table

Inputs Parallel outputs Serial outputs

CP OE STR D QP0 QPn QS1 QS2

↑ LXXZZQ6SNC

↓ LXXZZNCQ7S

↑ HLXNCNCQ6SNC

↑ HHLL QPn −1Q6S NC

↑ HHHHQPn −1Q6S NC

↓ H H H NCNCNCQ7S

[1] At the positive clock edge, the information in the 7th register stage is transferred to the 8th register stage and the QSn outputs.

H = HIGH voltage level; L = LOW voltage level; X = don’t care;

↑ = positive-going transition; ↓ = negative-going transition;

Z = HIGH-impedance OFF-state; NC = no change;

Q6S = the data in register stage 6 before the LOW to HIGH clock transition;

Q7S = the data in register stage 7 before the HIGH to LOW clock transition.

[1]

CLOCK INPUT

STROBE INPUT

OUTPUT ENABLE INPUT

INTERNAL Q0S (FF 0)

INTERNAL Q6S (FF 6)

SERIAL OUTPUT QS1

SERIAL OUTPUT QS2

Fig 5. Timing diagram

DATA INPUT

OUTPUT QP0

OUTPUT QP6

Z-state

Z-state

31

Page 34

Features

·

Operating voltage: 2.0V~5.5V

·

Maximum input serial clock: 500kHz at VDD=2V,

2MHz at V

·

Operating current: less than 1mAat2V,

DD

=5V

less than 1.2mAat5V

·

TTL compatible

-

VIH: 2.0V~VDD+0.3V at VDD=5V

-

VIL: -0.3V~+0.8V at VDD=5V

Applications

·

Microcomputer serial clock

General Description

The HT1380/HT1381 is a serial timekeeper IC which

providesseconds,minutes,hours,day,date,monthand

year information. The number of days in each month

and leap years are automatically adjusted. The

HT1380/HT1381 is designed for low power consumption and can operate in two modes: one is the 12-hour

mode with an AM/PM indicator, the other is the 24-hour

mode.

HT1380/HT1381

Serial Timekeeper Chip

·

Two data transmission modes: single-byte,

or burst mode

·

Serial I/O transmission

·

All registers store BCD format

·

HT1380: 8-pin DIP package

HT1381: 8-pin SOP package

·

Clock and Calendar

The HT1380/HT1381 has several registers to store the

corresponding information with 8-bit data format. A

32768Hz crystal is required to provide the correct timing. In order to minimize the pin number, the

HT1380/HT1381 use a serial I/O transmission method

to interface with a microprocessor. Only three wires are

required: (1) REST

delivered 1 byte at a time or in a burst of up to 8 bytes.

, (2) SCLK and (3) I/O. Data can be

Block Diagram

Pin Assignment

S C L K

R E S T

N C

X 1

X 2

V S S

I / O

1

2

3

4

H T 1 3 8 0

8 D I P - A

D a t a S h i f t

R e g i s t e r

C o m m a n d

C o n t r o l L o g i c

V D D

8

7

S C L K

I / O

6

R E S T

5

R e a l T i m e

C l o c k

O s c i l l a t o r a n d

D i v i d e r C i r c u i t

1

N C

2

X 1

3

X 2

4

V S S

H T 1 3 8 1

8 S O P - A

X 1

X 2

V D D

8

7

S C L K

I / O

6

R E S T

5

9

32

Page 35

Pad Assignment

1

2

3

4

5

6

7

( 0 , 0 )

X 1

X 2

V S S

I / O

S C L K

V D D

R E S T

HT1380/HT1381

Chip size: 2010 ´ 1920 (mm)

2

* The IC substrate should be connected to VSS in the PCB layout artwork.

Pad Coordinates

Pad No. X Y

1

2

3

-851.40

-851.40

-844.40 -203.90

4 845.90

5 848.40

6 845.90 332.60

7 844.40 572.60

Pad Description

Pad No. Pad Name I/O

1 X1 I CMOS 32768Hz crystal input pad

2 X2 O CMOS Oscillator output pad

3 VSS

4 REST

¾

I CMOS Reset pin with serial transmission

5 I/O I/O CMOS Data input/output pin with serial transmission

6 SCLK I CMOS Serial clock pulse pin with serial transmission

7 VDD

¾

Internal

Connection

Description

CMOS Negative power supply, ground

CMOS Positive power supply

Unit: mm

775.00

494.60

-618.30

-4.30

33

Page 36

LM117/LM317A/LM317

3-Terminal Adjustable Regulator

General Description

The LM117 series of adjustable 3-terminal positive voltage

regulators is capable of supplying in excess of 1.5A over a

1.2V to 37V output range. They are exceptionally easy to

use and require only two external resistors to set the output

voltage. Further,both line and load regulation are better than

standard fixed regulators. Also, the LM117 is packaged in

standard transistor packages which are easily mounted and

handled.

In addition to higher performance than fixed regulators, the

LM117 series offers full overload protection available only in

IC’s. Included on the chip are current limit, thermal overload

protection and safe area protection. All overload protection

circuitry remains fully functional even if the adjustment terminal is disconnected.

Normally,no capacitors are needed unless the device is situated more than 6 inches from the input filter capacitors in

which case an input bypass is needed. An optional output

capacitor can be added to improve transient response. The

adjustment terminal can be bypassed to achieve very high

ripple rejection ratios which are difficult to achieve with standard 3-terminal regulators.

Besides replacing fixed regulators, the LM117 is useful in a

wide variety of other applications. Since the regulator is

“floating” and sees only the input-to-output differential volt-

age, supplies of several hundred volts can be regulated as

long as the maximum input to output differential is not exceeded, i.e., avoid short-circuiting the output.

Also, it makes an especially simple adjustable switching

regulator,a programmable output regulator, or by connecting

a fixed resistor between the adjustment pin and output, the

LM117 can be used as a precision current regulator. Supplies with electronic shutdown can be achieved by clamping

the adjustment terminal to ground which programs the output to 1.2V where most loads draw little current.

For applications requiring greater output current, see LM150

series (3A) and LM138 series (5A) data sheets. For the

negative complement, see LM137 series data sheet.

Features

n Guaranteed 1%output voltage tolerance (LM317A)

n Guaranteed max. 0.01%/V line regulation (LM317A)

n Guaranteed max. 0.3%load regulation (LM117)

n Guaranteed 1.5A output current

n Adjustable output down to 1.2V

n Current limit constant with temperature

n P

n 80 dB ripple rejection

n Output is short-circuit protected

+

Product Enhancement tested

LM117/LM317A/LM317 3-Terminal Adjustable Regulator

August 1999

Typical Applications LM117 Series Packages

1.2V–25V Adjustable Regulator

Full output current not available at high input-output voltages

*

Needed if device is more than 6 inches from filter capacitors.

†

Optional— improves transient response. Output capacitors in the range

of 1 µF to 1000 µF of aluminum or tantalum electrolytic are commonly

used to provide improved output impedance and rejection of transients.

DS009063-1

Part Number Design

Suffix Package Load

Current

K TO-3 1.5A

H TO-39 0.5A

T TO-220 1.5A

E LCC 0.5A

S TO-263 1.5A

EMP SOT-223 1A

MDT TO-252 0.5A

SOT-223 vs D-Pak (TO-252)

Packages

Scale 1:1

DS009063-54

34

Page 37

LM9022

Vacuum Fluorescent Display Filament Driver

LM9022 Vacuum Fluorescent Display Filament Driver

August 2005

General Description

The LM9022 is a bridged power amplifier capable of delivering typically 2W of continuous average power into a 10Ω

filament load when powered by a 5V power supply.

To conserve power in portable applications, the LM9022’s

micropower shutdown mode (I

when V

Additional LM9022 features include thermal shutdown protection, unity-gain stability, and external gain set.

is applied to the SHUTDOWN pin.

DD

Typical Application T

= 0.6µA, typ) is activated

Q

= 25˚C, VDD= 5V, unless otherwise specified.

A

Key Specifications

n IDDduring shutdown 0.6µA (typ)

n Thermal Shutdown Protection

Features

n No transformers required

n SO or DIP packaging

Applications

n VCR/DVD Displays

n RADIO/TUNER Displays

Connection Diagram

20021501

FIGURE 1. Typical Application Circuit

MSOP, Small Outline, and DIP Package

20021502

Top View

Order Number LM9022M or LM9022N

See NS Package Number M08A or N08E

35

Page 38

October 6, 2008

LMV831 Single/ LMV832 Dual/ LMV834 Quad

3.3 MHz Low Power CMOS, EMI Hardened Operational

Amplifiers

General Description

National’s LMV831, LMV832, and LMV834 are CMOS input,

low power op amp IC's, providing a low input bias current, a

wide temperature range of −40°C to 125°C and exceptional

performance making them robust general purpose parts. Additionally, the LMV831/LMV832/LMV834 are EMI hardened

to minimize any interference so they are ideal for EMI sensitive applications.

The unity gain stable LMV831/LMV832/LMV834 feature

3.3 MHz of bandwidth while consuming only 0.24 mA of current per channel. These parts also maintain stability for capacitive loads as large as 200 pF. The LMV831/LMV832/

LMV834 provide superior performance and economy in terms

of power and space usage.

This family of parts has a maximum input offset voltage of

1 mV, a rail-to-rail output stage and an input common-mode

voltage range that includes ground. Over an operating range

from 2.7V to 5.5V the LMV831/LMV832/LMV834 provide a

PSRR of 93 dB, and a CMRR of 91 dB. The LMV831 is offered

in the space saving 5-Pin SC70 package, the LMV832 in the

8-Pin MSOP and the LMV834 is offered in the 14-Pin TSSOP

package.

Features

Unless otherwise noted, typical values at TA= 25°C,

V+ = 3.3V

■

Supply voltage 2.7V to 5.5V

■

Supply current (per channel) 240 µA

■

Input offset voltage 1 mV max

■

Input bias current 0.1 pA

■

GBW 3.3 MHz

■

EMIRR at 1.8 GHz 120 dB

■

Input noise voltage at 1 kHz 12 nV/√Hz

■

Slew rate 2 V/µs

■

Output voltage swing Rail-to-Rail

■

Output current drive 30 mA

■

Operating ambient temperature range −40°C to 125°C

Applications

■

Photodiode preamp

■

Piezoelectric sensors

■

Portable/battery-powered electronic equipment

■

Filters/buffers

■

PDAs/phone accessories

Typical Application

EMI Hardened Sensor Application

30024101

LMV831 Single/ LMV832 Dual/ LMV834 Quad 3.3 MHz Low Power CMOS, EMI Hardened

Operational Amplifiers

36

Page 39

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

ESD Tolerance (Note 2)

Human Body Model 2 kV

Charge-Device Model 1 kV

Machine Model 200V

V

IN

Differential

± Supply Voltage

Supply Voltage (VS = V+ – V−)

6V

Voltage at Input/Output Pins V++0.4V,

V− −0.4V

Storage Temperature Range −65°C to 150°C

Junction Temperature (Note 3) 150°C

Soldering Information

Infrared or Convection (20 sec) 260°C

Operating Ratings (Note 1)

Temperature Range (Note 3) −40°C to 125°C

Supply Voltage (VS = V+ – V−)

2.7V to 5.5V

Package Thermal Resistance (θJA (Note 3))

5-Pin SC-70 302°C/W

8-Pin MSOP 217°C/W

14-Pin TSSOP 135°C/W

3.3V Electrical Characteristics (Note 4)

Unless otherwise specified, all limits are guaranteed for at TA = 25°C, V+ = 3.3V, V− = 0V, VCM = V+/2, and RL =10 kΩ to V+/2.

Boldface limits apply at the temperature extremes.

Symbol Parameter Conditions Min

(Note 6)

Typ

(Note 5)

Max

(Note 6)

Units

V

OS

Input Offset Voltage

(Note 9)

±0.25 ±1.00

±1.23

mV

TCV

OS

Input Offset Voltage Temperature Drift

(Notes 9, 10)

LMV831,

LMV832

±0.5 ±1.5

μV/°C

LMV834 ±0.5 ±1.7

I

B

Input Bias Current

(Note 10)

0.1 10

500

pA

I

OS

Input Offset Current 1

pA

CMRR Common-Mode Rejection Ratio

(Note 9)

0.2V ≤ VCM ≤ V+ - 1.2V

76

75

91

dB

PSRR Power Supply Rejection Ratio

(Note 9)

2.7V ≤ V+ ≤ 5.5V,

V

OUT

= 1V

76

75

93

dB

EMIRR EMI Rejection Ratio, IN+ and IN-

(Note 8)

V

RF_PEAK

=100 mVP (−20 dBP),

f = 400 MHz

80

dB

V

RF_PEAK

=100 mVP (−20 dBP),

f = 900 MHz

90

V

RF_PEAK

=100 mVP (−20 dBP),

f = 1800 MHz

110

V

RF_PEAK

=100 mVP (−20 dBP),

f = 2400 MHz

120

CMVR Input Common-Mode Voltage Range

CMRR ≥ 65 dB

−0.1 2.1

V

A

VOL

Large Signal Voltage Gain

(Note 11)

RL = 2 kΩ,

V

OUT

= 0.15V to 1.65V,

V

OUT

= 3.15V to 1.65V

LMV831,

LMV832

102

102

121

dB

LMV834 102

102

121

RL = 10 kΩ,

V

OUT

= 0.1V to 1.65V,

V

OUT

= 3.2V to 1.65V

LMV831,

LMV832

104

104

126

LMV834 104

103

123

LMV831 Single/ LMV832 Dual/ LMV834 Quad

37

Page 40

Symbol Parameter Conditions Min

(Note 6)

Typ

(Note 5)

Max

(Note 6)

Units

V

OUT

Output Voltage Swing High

RL = 2 kΩ to V+/2

LMV831,

LMV832

29 36

43

mV from

either rail

LMV834 31 38

44

RL = 10 kΩ to V+/2

LMV831,

LMV832

6 8

9

LMV834 7 9

10

Output Voltage Swing Low

R = 2 kΩ to V+/2

25 34

43

RL = 10 kΩ to V+/2

5 8

10

I

OUT

Output Short Circuit Current Sourcing, V

OUT

= VCM,

VIN = 100 mV

LMV831,

LMV832

27

22

28

mA

LMV834 24

19

28

Sinking, V

OUT

= VCM,

VIN = −100 mV

27

21

32

I

S

Supply Current LMV831 0.24 0.27

0.30

mA

LMV832 0.46 0.51

0.58

LMV834 0.90 1.00

1.16

SR Slew Rate (Note 7) AV = +1, V

OUT

= 1 VPP,

10% to 90%

2

V/μs

GBW Gain Bandwidth Product 3.3 MHz

Φ

m

Phase Margin 65

deg

e

n

Input Referred Voltage Noise Density f = 1 kHz 12

nV/

f = 10 kHz 10

i

n

Input Referred Current Noise Density f = 1 kHz 0.005

pA/

R

OUT

Closed Loop Output Impedance f = 2 MHz 500

Ω

C

IN

Common-mode Input Capacitance 15

pF

Differential-mode Input Capacitance 20

THD+N Total Harmonic Distortion + Noise

f = 1 kHz, AV = 1, BW ≥ 500 kHz

0.02

%

5V Electrical Characteristics (Note 4)

Unless otherwise specified, all limits are guaranteed for at TA = 25°C, V+ = 5V, V− = 0V, VCM = V+/2, and RL = 10 kΩ to V+/2.

Boldface limits apply at the temperature extremes.

Symbol Parameter Conditions Min

(Note 6)

Typ

(Note 5)

Max

(Note 6)

Units

V

OS

Input Offset Voltage

(Note 9)

±0.25 ±1.00

±1.23

mV

TCV

OS

Input Offset Voltage Temperature Drift

(Notes 9, 10)

LMV831,

LMV832

±0.5 ±1.5

μV/°C

LMV834 ±0.5 ±1.7

I

B

Input Bias Current

(Note 10)

0.1 10

500

pA

I

OS

Input Offset Current 1

pA

CMRR Common-Mode Rejection Ratio

(Note 9)

0V ≤ V

CM

≤ V+ −1.2V

77

77

93

dB

LMV831 Single/ LMV832 Dual/ LMV834 Quad

38

Page 41

Symbol Parameter Conditions Min

(Note 6)

Typ

(Note 5)

Max

(Note 6)

Units

PSRR Power Supply Rejection Ratio

(Note 9)

2.7V ≤ V+ ≤ 5.5V,

V

OUT

= 1V

76

75

93

dB

EMIRR EMI Rejection Ratio, IN+ and IN-

(Note 8)

V

RF_PEAK

=100 mVP (−20 dBP),

f = 400 MHz

80

dB

V

RF_PEAK

=100 mVP (−20 dBP),

f = 900 MHz

90

V

RF_PEAK

=100 mVP (−20 dBP),

f = 1800 MHz

110

V

RF_PEAK

=100 mVP (−20 dBP),

f = 2400 MHz

120

CMVR Input Common-Mode Voltage Range

CMRR ≥ 65 dB

–0.1 3.8

V

A

VOL

Large Signal Voltage Gain

(Note 11)

RL = 2 kΩ,

V

OUT

= 0.15V to 2.5V,

V

OUT

= 4.85V to 2.5V

LMV831,

LMV832

107

106

127

dB

LMV834 104

104

127

RL = 10 kΩ,

V

OUT

= 0.1V to 2.5V,

V

OUT

= 4.9V to 2.5V

LMV831,

LMV832

107

107

130

LMV834 105

104

127

V

OUT

Output Voltage Swing High

RL = 2 kΩ to V+/2

LMV831,

LMV832

32 42

49

mV from

either rail

LMV834 35 45

52

RL = 10 kΩ to V+/2

LMV831,

LMV832

6 9

10

LMV834 7 10

11

Output Voltage Swing Low

RL = 2 kΩ to V+/2

27 43

52

RL = 10 kΩ to V+/2

6 10

12

I

OUT

Output Short Circuit Current Sourcing V

OUT

= V

CM

VIN = 100 mV

LMV831,

LMV832

59

49

66

mA

LMV834 57

45

63

Sinking V

OUT

= V

CM

VIN = −100 mV

LMV831,

LMV832

50

41

64

LMV834 53

41

63

I

S

Supply Current LMV831 0.25 0.27

0.31

mA

LMV832 0.47 0.52

0.60

LMV834 0.92 1.02

1.18

SR Slew Rate (Note 7) AV = +1, V

OUT

= 2VPP,

10% to 90%

2

V/μs

GBW Gain Bandwidth Product 3.3 MHz

Φ

m

Phase Margin 65

deg

e

n

Input Referred Voltage Noise f = 1 kHz 12

nV/

f = 10 kHz 10

LMV831 Single/ LMV832 Dual/ LMV834 Quad

39

Page 42

Symbol Parameter Conditions Min

(Note 6)

Typ

(Note 5)

Max

(Note 6)

Units

i

n

Input Referred Current Noise f = 1 kHz 0.005

pA/

R

OUT

Closed Loop Output Impedance f = 2 MHz 500

Ω

C

IN

Common-mode Input Capacitance 14

pF

Differential-mode Input Capacitance 20

THD+N Total Harmonic Distortion + Noise

f = 1 kHz, AV = 1, BW ≥ 500 kHz

0.02

%

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics

Tables.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) FieldInduced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

Note 3: The maximum power dissipation is a function of T

J(MAX)

, θ

JA

, and TA. The maximum allowable power dissipation at any ambient temperature is

PD = (T

J(MAX)

- T

A

)/ θ

JA

. All numbers apply for packages soldered directly onto a PC board.

Note 4: Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating

of the device such that TJ = TA. No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where

TJ > TA.

Note 5: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will

also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 6: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlations using statistical quality

control (SQC) method.

Note 7: Number specified is the slower of positive and negative slew rates.

Note 8: The EMI Rejection Ratio is defined as EMIRR = 20log ( V

RF_PEAK

/ΔVOS).

Note 9: The typical value is calculated by applying absolute value transform to the distribution, then taking the statistical average of the resulting distribution.

Note 10: This parameter is guaranteed by design and/or characterization and is not tested in production.

Note 11: The specified limits represent the lower of the measured values for each output range condition.

Connection Diagrams

5-Pin SC-70

30024102

Top View

8-Pin MSOP

30024103

Top View

14-Pin TSSOP

30024104

Top View

Ordering Information

Package Part Number Package Marking Transport Media NSC Drawing

5-Pin SC-70

LMV831MG

AFA

1k Units Tape and Reel

MAA05ALMV831MGE 250 Units Tape and Reel

LMV831MGX 3k Units Tape and Reel

8-Pin MSOP

LMV832MM

AU5A

1k Units Tape and Reel

MUA08ALMV832MME 250 Units Tape and Reel

LMV832MMX 3.5k Units Tape and Reel

14-Pin TSSOP

LMV834MT

LMV834MT

94 Units/Rail

MTC14

LMV834MTX 2.5k Units Tape and Reel

LMV831 Single/ LMV832 Dual/ LMV834 Quad

40

Page 43

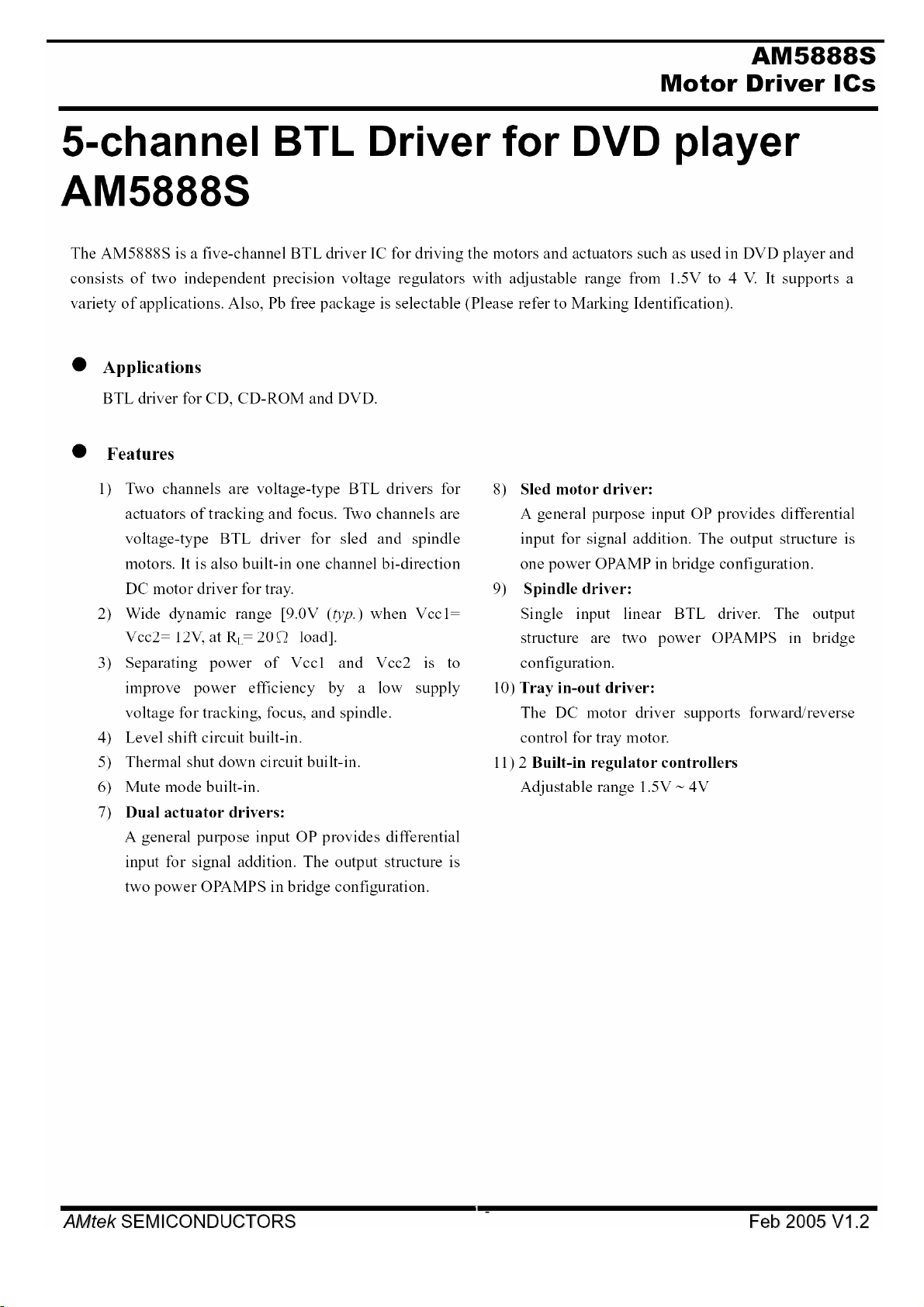

Features

1. Features

Ali’s M5673 pr

mass storage device.It built-in audio 24-bit Digital Signal Processor. With state-of-the-art technology and

cost-effective integration in mind, M5673 is developed to provide many leading features in a system-on-chip

solution, including CD RF PreAmp, CD Servo controller, EDC/ECC error detection and correction, full-speed

USB1.1 host controller, SD/MMC/MS memory card interface, high-performance caching micro-controller with

user-configurable I/Os, high-performance mixed-mode audio macros, etc.

ovides cost-e

CD Servo

■ Integrated RF Amp, Servo control, CD-DSP and CD-ROM decoder.

■ Support CD/CD-R/CD-RW physical format disc.

■ Support CDDA, CD-ROM(mode 1, mode2 form 1)logical format playback.

■ Support up to 4X speed optical pickup unit.

■ Embedded SRAM for ECC buffer, no need extra external DRAM.

USB1.1 Controller

■ on-chip USB transceiver compliant with USB Specification revision 1.1 Full-Speed(FS)

■ Support full-speed USB1.1 host mode for USB disc.

■ Built-in Configurable Four USB Endpoint FIF Os.

-Endpoint 0: 64-byte FIFO support for Control transfer.

-Endpoint A: 64-byte double-buffered bulk-In transfer.

-Endpoint B: 64-byte double-buffered bulk-Out transfer.

-Endpoint C: 8-byte interrupt transfer.

■ Support USB wakeup/suspend.

■ support DMA operation for bulk transfer.

ffective solutions for playback audio from disc, SD/MMC/MS flash card and USB

Data Storage Controller

■ Support

MS-Pro, etc.

■ Support DMA operation.

flash cards

including

Secure-Digital (SD)

and Multi-Media Card (MMC), Memory Stick (MS),

High performance Micro-controller

■ High-performance 8-bit 56MHz micro-controller with 8051 compatible instruction set.

■ Built-in 8KBytes 2-way i-cache SR

■ Support up to 256 KBytes external Serial-Flash.