www.DataSheet4U.com

To all our customers

Regarding the change of names mentioned in the document, such as Hitachi

Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas

Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog

and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.)

Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand

names are mentioned in the document, these names have in fact all been changed to Renesas

Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and

corporate statement, no changes whatsoever have been made to the contents of the document, and

these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp.

Customer Support Dept.

April 1, 2003

Cautions

Keep safety first in your circuit designs!

1. Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is al ways the possibility that t rouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in th e sel ection of the Renesas

Technology Corporation product best suited to the customer's application; they do not convey any

license under any intellectual property rights, or any other rights, belonging to Renesas Technology

Corporation or a third party.

2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any

third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or

circuit application examples contained in these materi als.

3. All information contained in these materials, including product data, diagrams, charts, programs and

algorithms represents information on products at the time of publication of these materials, and are

subject to change by Renesas Technology Corporation without notice due to product improvements or

other reasons. It is therefore recommended that customers contact Renesas Technology Corporation

or an authorized Renesas Technology Corporation product distributor for the latest product information

before purchasing a product listed herein.

The information described here may contain technical i naccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss

rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various

means, including the Renesas Technology Corporation Semiconductor home page

(http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams,

charts, programs, and algorithms, please be sure to evaluat e al l information as a total system before

making a final decision on the applicability of the information and products. Renesas Technology

Corporation assumes no responsibility for any damage, liability or other loss resulting from the

information contained herein.

5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device

or system that is used under circumstances in which human life is po t entially at stake. P l ease contact

Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor

when considering the use of a product contained herein for any specific purposes, such as apparatus or

systems for transportation, vehicular, medical, aerospace, n uclear, or undersea repeater use.

6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in

whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be

exported under a license from the Japanese government and cannot be imported into a country other

than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the

country of destination is prohibited.

8. Please contact Renesas Technology Corporation for further details on these materials or the products

contained therein.

H8S/2350 Series

H8S/2351, HD6432351,

H8S/2350, HD6412350

Hardware Manual

ADE-602-111A

Rev. 2.0

3/10/03

Hitachi, Ltd.

MC-Setsu

Notice

When using this document, keep the following in mind:

1. This document may, wholly or partially, be subject to change without notice.

2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole

or part of this document without Hitachi’s permission.

3. Hitachi will not be held responsible for any damage to the user that may result from accidents

or any other reasons during operation of the user’s unit according to this document.

4. Circuitry and other examples described herein are meant merely to indicate the characteristics

and performance of Hitachi’s semiconductor products. Hitachi assumes no responsibility for

any intellectual property claims or other problems that may result from applications based on

the examples described herein.

5. No license is granted by implication or otherwise under any patents or other rights of any third

party or Hitachi, Ltd.

6. MEDICAL APPLICATIONS: Hitachi’s products are not authorized for use in MEDICAL

APPLICATIONS without the written consent of the appropriate officer of Hitachi’s sales

company. Such use includes, but is not limited to, use in life support systems. Buyers of

Hitachi’s products are requested to notify the relevant Hitachi sales offices when planning to

use the products in MEDICAL APPLICATIONS.

Preface

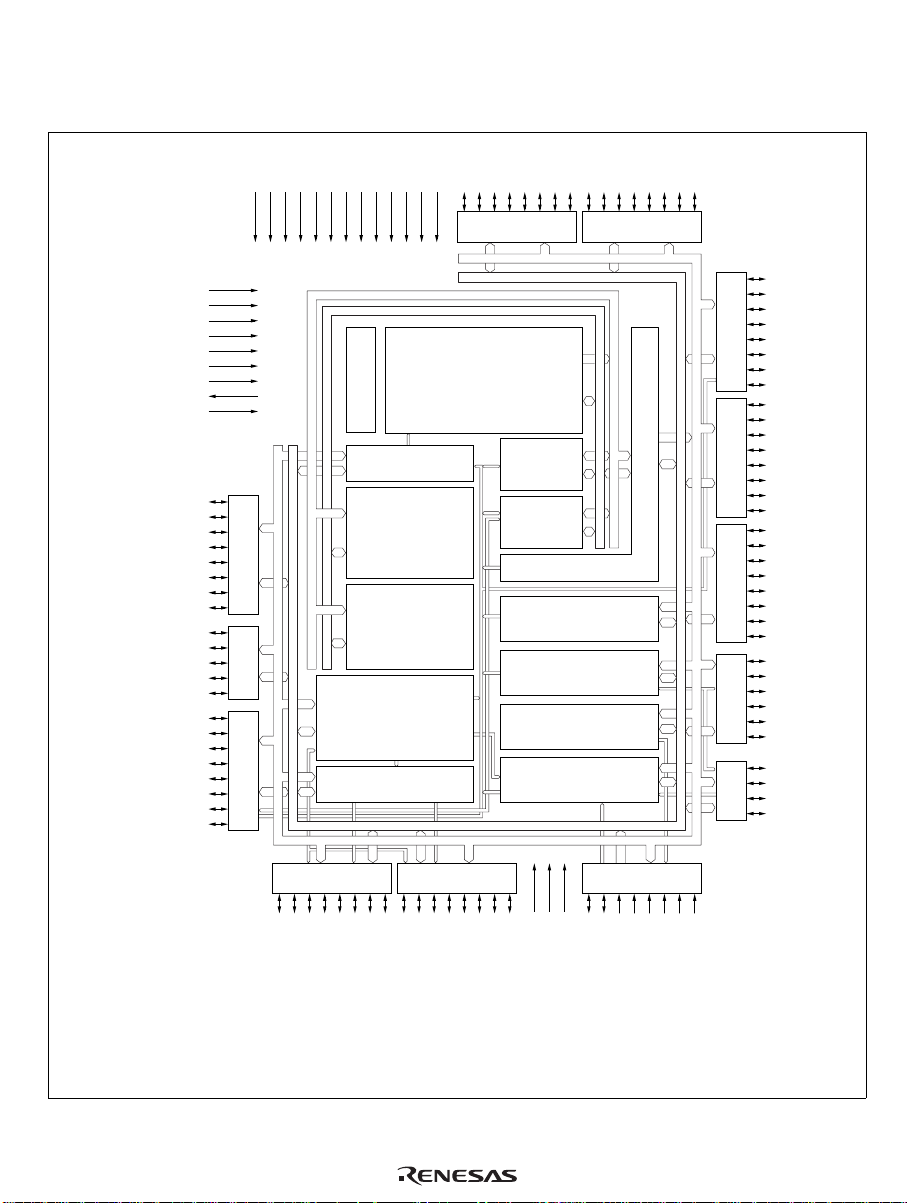

The H8S/2350 Series is a series of high-performance microcontrollers with a 32-bit H8S/2000

CPU core, and a set of on-chip supporting functions required for system configuration.

The H8S/2000 CPU can execute basic instructions in one state, and is provided with sixteen 16-bit

general registers with a 32-bit internal configuration, and a concise and optimized instruction set.

The CPU can handle a 16 Mbyte linear address space (architecturally 4 Gbytes). Programs based

on the high-level language C can also be run efficiently.

The address space is divided into eight areas. The data bus width and access states can be selected

for each of these areas, and various kinds of memory can be connected fast and easily.

On-chip memory consists of large-capacity ROM (H8S/2351 only) and RAM.

On-chip supporting functions include a 16-bit timer pulse unit (TPU), programmable pulse

generator (PPG), watchdog timer (WDT), serial communication interface (SCI), A/D converter,

D/A converter, and I/O ports.

In addition, an on-chip DMA controller (DMAC) and data transfer controller (DTC) are provided,

enabling high-speed data transfer without CPU intervention.

Use of the H8S/2350 Series enables easy implementation of compact, high-performance systems

capable of processing large volumes of data.

This manual describes the hardware of the H8S/2350 Series. Refer to the H8S/2600 Series and

H8S/2000 Series Programming Manual for a detailed description of the instruction set.

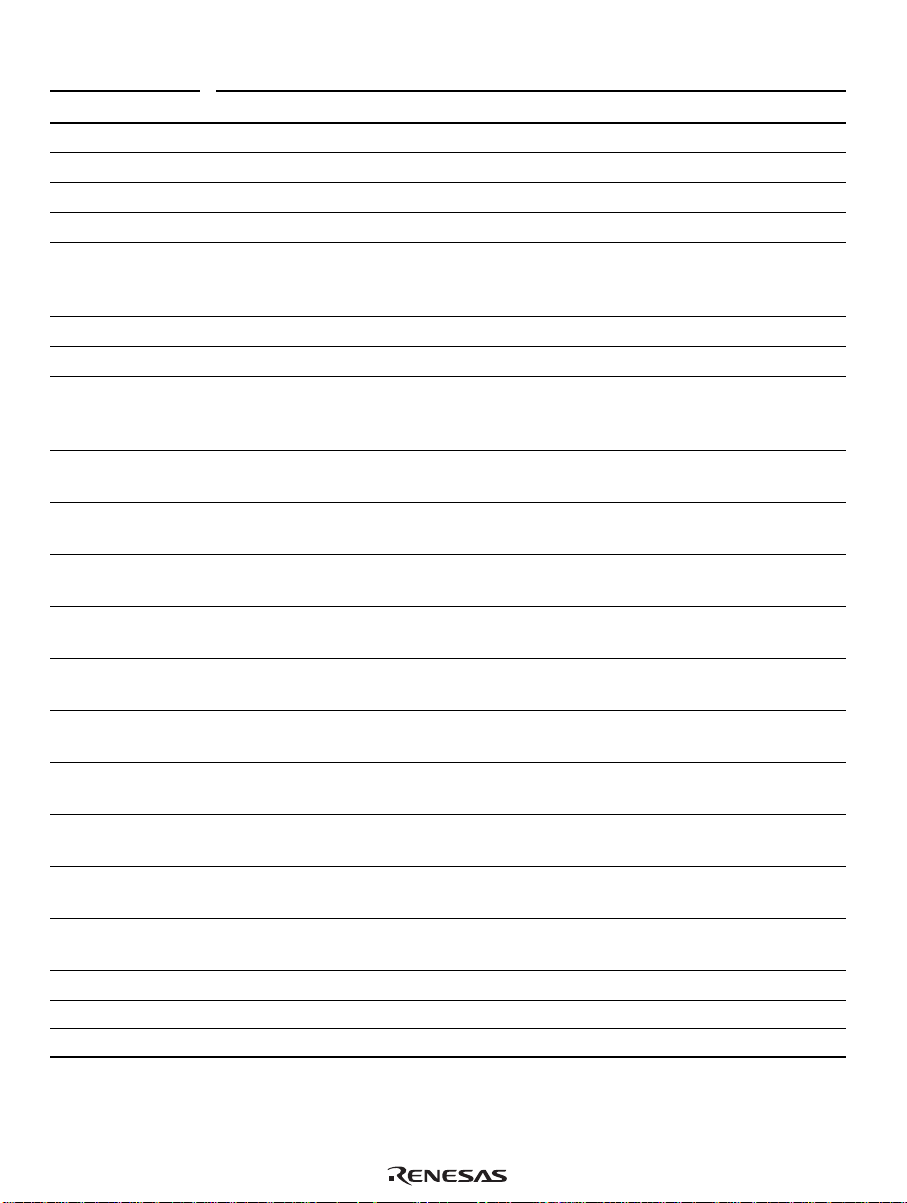

Contents

Section 1 Overview............................................................................................................ 1

1.1 Overview............................................................................................................................ 1

1.2 Block Diagram................................................................................................................... 5

1.3 Pin Description................................................................................................................... 6

1.3.1 Pin Arrangement................................................................................................... 6

1.3.2 Pin Functions in Each Operating Mode................................................................ 8

1.3.3 Pin Functions........................................................................................................ 13

Section 2 CPU..................................................................................................................... 21

2.1 Overview............................................................................................................................ 21

2.1.1 Features................................................................................................................. 21

2.1.2 Differences between H8S/2600 CPU and H8S/2000 CPU .................................. 22

2.1.3 Differences from H8/300 CPU ............................................................................. 23

2.1.4 Differences from H8/300H CPU.......................................................................... 23

2.2 CPU Operating Modes....................................................................................................... 24

2.3 Address Space.................................................................................................................... 29

2.4 Register Configuration....................................................................................................... 30

2.4.1 Overview............................................................................................................... 30

2.4.2 General Registers.................................................................................................. 31

2.4.3 Control Registers.................................................................................................. 32

2.4.4 Initial Register Values .......................................................................................... 34

2.5 Data Formats...................................................................................................................... 35

2.5.1 General Register Data Formats............................................................................. 35

2.5.2 Memory Data Formats.......................................................................................... 37

2.6 Instruction Set.................................................................................................................... 38

2.6.1 Overview............................................................................................................... 38

2.6.2 Instructions and Addressing Modes...................................................................... 39

2.6.3 Table of Instructions Classified by Function........................................................ 41

2.6.4 Basic Instruction Formats..................................................................................... 51

2.7 Addressing Modes and Effective Address Calculation...................................................... 52

2.7.1 Addressing Mode.................................................................................................. 52

2.7.2 Effective Address Calculation.............................................................................. 55

2.8 Processing States................................................................................................................ 59

2.8.1 Overview............................................................................................................... 59

2.8.2 Reset State ............................................................................................................ 60

2.8.3 Exception-Handling State..................................................................................... 61

2.8.4 Program Execution State ...................................................................................... 64

2.8.5 Bus-Released State................................................................................................ 64

2.8.6 Power-Down State................................................................................................ 64

i

2.9 Basic Timing...................................................................................................................... 65

2.9.1 Overview............................................................................................................... 65

2.9.2 On-Chip Memory (ROM, RAM).......................................................................... 65

2.9.3 On-Chip Supporting Module Access Timing....................................................... 67

2.9.4 External Address Space Access Timing............................................................... 68

Section 3 MCU Operating Modes................................................................................. 69

3.1 Overview............................................................................................................................ 69

3.1.1 H8S/2350 Operating Mode Selection................................................................... 69

3.1.2 H8S/2351 Operating Mode Selection................................................................... 70

3.1.3 Register Configuration.......................................................................................... 71

3.2 Register Descriptions......................................................................................................... 71

3.2.1 Mode Control Register (MDCR).......................................................................... 71

3.2.2 System Control Register (SYSCR)....................................................................... 72

3.3 Operating Mode Descriptions............................................................................................ 73

3.3.1 Mode 1.................................................................................................................. 73

3.3.2 Mode 2 (H8S/2351 Only) ..................................................................................... 73

3.3.3 Mode 3 (H8S/2351 Only) ..................................................................................... 73

3.3.4 Mode 4.................................................................................................................. 73

3.3.5 Mode 5.................................................................................................................. 74

3.3.6 Mode 6 (H8S/2351 Only) ..................................................................................... 74

3.3.7 Mode 7 (H8S/2351 Only) ..................................................................................... 74

3.4 Pin Functions in Each Operating Mode............................................................................. 75

3.5 Memory Map in Each Operating Mode............................................................................. 75

Section 4 Exception Handling........................................................................................ 79

4.1 Overview............................................................................................................................ 79

4.1.1 Exception Handling Types and Priority................................................................ 79

4.1.2 Exception Handling Operation ............................................................................. 80

4.1.3 Exception Vector Table........................................................................................ 80

4.2 Reset................................................................................................................................... 82

4.2.1 Overview............................................................................................................... 82

4.2.2 Reset Types........................................................................................................... 82

4.2.3 Reset Sequence ..................................................................................................... 83

4.2.4 Interrupts after Reset............................................................................................. 84

4.2.5 State of On-Chip Supporting Modules after Reset Release.................................. 84

4.3 Traces................................................................................................................................. 85

4.4 Interrupts............................................................................................................................ 86

4.5 Trap Instruction.................................................................................................................. 87

4.6 Stack Status after Exception Handling .............................................................................. 88

4.7 Notes on Use of the Stack.................................................................................................. 89

ii

Section 5 Interrupt Controller......................................................................................... 91

5.1 Overview............................................................................................................................ 91

5.1.1 Features................................................................................................................. 91

5.1.2 Block Diagram...................................................................................................... 92

5.1.3 Pin Configuration.................................................................................................. 93

5.1.4 Register Configuration.......................................................................................... 93

5.2 Register Descriptions......................................................................................................... 94

5.2.1 System Control Register (SYSCR)....................................................................... 94

5.2.2 Interrupt Priority Registers A to K (IPRA to IPRK) ............................................ 95

5.2.3 IRQ Enable Register (IER)................................................................................... 96

5.2.4 IRQ Sense Control Registers H and L (ISCRH, ISCRL) ..................................... 97

5.2.5 IRQ Status Register (ISR) .................................................................................... 98

5.3 Interrupt Sources................................................................................................................ 99

5.3.1 External Interrupts................................................................................................ 99

5.3.2 Internal Interrupts.................................................................................................. 100

5.3.3 Interrupt Exception Handling Vector Table ......................................................... 100

5.4 Interrupt Operation............................................................................................................. 104

5.4.1 Interrupt Control Modes and Interrupt Operation ................................................ 104

5.4.2 Interrupt Control Mode 0...................................................................................... 107

5.4.3 Interrupt Control Mode 2...................................................................................... 109

5.4.4 Interrupt Exception Handling Sequence............................................................... 111

5.4.5 Interrupt Response Times..................................................................................... 113

5.5 Usage Notes ....................................................................................................................... 114

5.5.1 Contention between Interrupt Generation and Disabling ..................................... 114

5.5.2 Instructions that Disable Interrupts....................................................................... 115

5.5.3 Times when Interrupts are Disabled..................................................................... 115

5.5.4 Interrupts during Execution of EEPMOV Instruction.......................................... 115

5.6 DTC and DMAC Activation by Interrupt.......................................................................... 116

5.6.1 Overview............................................................................................................... 116

5.6.2 Block Diagram...................................................................................................... 116

5.6.3 Operation .............................................................................................................. 117

Section 6 Bus Controller.................................................................................................. 119

6.1 Overview............................................................................................................................ 119

6.1.1 Features................................................................................................................. 119

6.1.2 Block Diagram...................................................................................................... 121

6.1.3 Pin Configuration.................................................................................................. 122

6.1.4 Register Configuration.......................................................................................... 123

6.2 Register Descriptions......................................................................................................... 124

6.2.1 Bus Width Control Register (ABWCR) ............................................................... 124

6.2.2 Access State Control Register (ASTCR).............................................................. 125

6.2.3 Wait Control Registers H and L (WCRH, WCRL).............................................. 126

6.2.4 Bus Control Register H (BCRH).......................................................................... 130

iii

6.2.5 Bus Control Register L (BCRL)........................................................................... 132

6.2.6 Memory Control Register (MCR) ........................................................................ 134

6.2.7 DRAM Control Register (DRAMCR).................................................................. 137

6.2.8 Refresh Timer/Counter (RTCNT) ........................................................................ 140

6.2.9 Refresh Time Constant Register (RTCOR).......................................................... 140

6.3 Overview of Bus Control................................................................................................... 141

6.3.1 Area Partitioning................................................................................................... 141

6.3.2 Bus Specifications ................................................................................................ 142

6.3.3 Memory Interfaces................................................................................................ 143

6.3.4 Advanced Mode.................................................................................................... 144

6.3.5 Areas in Normal Mode.......................................................................................... 145

6.3.6 Chip Select Signals............................................................................................... 146

6.4 Basic Bus Interface............................................................................................................ 147

6.4.1 Overview............................................................................................................... 147

6.4.2 Data Size and Data Alignment.............................................................................. 147

6.4.3 Valid Strobes........................................................................................................ 149

6.4.4 Basic Timing......................................................................................................... 150

6.4.5 Wait Control.......................................................................................................... 158

6.5 DRAM Interface ................................................................................................................ 160

6.5.1 Overview............................................................................................................... 160

6.5.2 Setting DRAM Space............................................................................................ 160

6.5.3 Address Multiplexing............................................................................................ 160

6.5.4 Data Bus................................................................................................................ 161

6.5.5 Pins Used for DRAM Interface ............................................................................ 161

6.5.6 Basic Timing......................................................................................................... 162

6.5.7 Precharge State Control........................................................................................ 163

6.5.8 Wait Control ......................................................................................................... 164

6.5.9 Byte Access Control ............................................................................................. 166

6.5.10 Burst Operation..................................................................................................... 168

6.5.11 Refresh Control..................................................................................................... 171

6.6 DMAC Single Address Mode and DRAM Interface......................................................... 174

6.6.1 When DDS = 1...................................................................................................... 174

6.6.2 When DDS = 0...................................................................................................... 175

6.7 Burst ROM Interface.......................................................................................................... 176

6.7.1 Overview............................................................................................................... 176

6.7.2 Basic Timing......................................................................................................... 176

6.7.3 Wait Control.......................................................................................................... 178

6.8 Idle Cycle........................................................................................................................... 179

6.8.1 Operation .............................................................................................................. 179

6.8.2 Pin States in Idle Cycle......................................................................................... 183

6.9 Write Data Buffer Function ............................................................................................... 184

6.10 Bus Release........................................................................................................................ 185

6.10.1 Overview............................................................................................................... 185

iv

6.10.2 Operation .............................................................................................................. 185

6.10.3 Pin States in External Bus Released State............................................................ 186

6.10.4 Transition Timing ................................................................................................. 187

6.10.5 Usage Note............................................................................................................ 188

6.11 Bus Arbitration................................................................................................................... 188

6.11.1 Overview............................................................................................................... 188

6.11.2 Operation .............................................................................................................. 188

6.11.3 Bus Transfer Timing............................................................................................. 189

6.11.4 External Bus Release Usage Note ........................................................................ 189

6.12 Resets and the Bus Controller............................................................................................ 190

Section 7 DMA Controller.............................................................................................. 191

7.1 Overview............................................................................................................................ 191

7.1.1 Features................................................................................................................. 191

7.1.2 Block Diagram...................................................................................................... 192

7.1.3 Overview of Functions.......................................................................................... 193

7.1.4 Pin Configuration.................................................................................................. 195

7.1.5 Register Configuration.......................................................................................... 196

7.2 Register Descriptions (1) (Short Address Mode) .............................................................. 197

7.2.1 Memory Address Registers (MAR)...................................................................... 198

7.2.2 I/O Address Register (IOAR) ............................................................................... 199

7.2.3 Execute Transfer Count Register (ETCR)............................................................ 199

7.2.4 DMA Control Register (DMACR) ....................................................................... 200

7.2.5 DMA Band Control Register (DMABCR)........................................................... 205

7.3 Register Descriptions (2) (Full Address Mode)................................................................. 211

7.3.1 Memory Address Register (MAR)........................................................................ 211

7.3.2 I/O Address Register (IOAR) ............................................................................... 211

7.3.3 Execute Transfer Count Register (ETCR)............................................................ 212

7.3.4 DMA Control Register (DMACR) ....................................................................... 213

7.3.5 DMA Band Control Register (DMABCR)........................................................... 217

7.4 Register Descriptions (3) ................................................................................................... 222

7.4.1 DMA Write Enable Register (DMAWER)........................................................... 222

7.4.2 DMA Terminal Control Register (DMATCR)..................................................... 225

7.4.3 Module Stop Control Register (MSTPCR)........................................................... 226

7.5 Operation............................................................................................................................ 227

7.5.1 Transfer Modes..................................................................................................... 227

7.5.2 Sequential Mode ................................................................................................... 230

7.5.3 Idle Mode.............................................................................................................. 233

7.5.4 Repeat Mode......................................................................................................... 236

7.5.5 Single Address Mode............................................................................................ 240

7.5.6 Normal Mode........................................................................................................ 243

7.5.7 Block Transfer Mode............................................................................................ 246

7.5.8 DMAC Activation Sources................................................................................... 252

v

7.5.9 Basic DMAC Bus Cycles...................................................................................... 255

7.5.10 DMAC Bus Cycles (Dual Address Mode) ........................................................... 256

7.5.11 DMAC Bus Cycles (Single Address Mode)......................................................... 264

7.5.12 Write Data Buffer Function.................................................................................. 270

7.5.13 DMAC Multi-Channel Operation......................................................................... 271

7.5.14 Relation Between External Bus Requests, Refresh Cycles, the DTC,

and the DMAC...................................................................................................... 273

7.5.15 NMI Interrupts and DMAC.................................................................................. 274

7.5.16 Forced Termination of DMAC Operation............................................................ 275

7.5.17 Clearing Full Address Mode................................................................................. 276

7.6 Interrupts............................................................................................................................ 277

7.7 Usage Notes ....................................................................................................................... 278

Section 8 Data Transfer Controller............................................................................... 283

8.1 Overview............................................................................................................................ 283

8.1.1 Features................................................................................................................. 283

8.1.2 Block Diagram...................................................................................................... 284

8.1.3 Register Configuration.......................................................................................... 285

8.2 Register Descriptions......................................................................................................... 286

8.2.1 DTC Mode Register A (MRA)............................................................................. 286

8.2.2 DTC Mode Register B (MRB).............................................................................. 288

8.2.3 DTC Source Address Register (SAR) .................................................................. 289

8.2.4 DTC Destination Address Register (DAR) .......................................................... 289

8.2.5 DTC Transfer Count Register A (CRA)............................................................... 289

8.2.6 DTC Transfer Count Register B (CRB)................................................................ 290

8.2.7 DTC Enable Registers (DTCER).......................................................................... 290

8.2.8 DTC Vector Register (DTVECR) ........................................................................ 291

8.2.9 Module Stop Control Register (MSTPCR)........................................................... 292

8.3 Operation............................................................................................................................ 293

8.3.1 Overview............................................................................................................... 293

8.3.2 Activation Sources................................................................................................ 295

8.3.3 DTC Vector Table ................................................................................................ 296

8.3.4 Location of Register Information in Address Space............................................. 299

8.3.5 Normal Mode........................................................................................................ 300

8.3.6 Repeat Mode......................................................................................................... 301

8.3.7 Block Transfer Mode............................................................................................ 302

8.3.8 Chain Transfer...................................................................................................... 304

8.3.9 Operation Timing.................................................................................................. 305

8.3.10 Number of DTC Execution States........................................................................ 306

8.3.11 Procedures for Using DTC.................................................................................... 308

8.3.12 Examples of Use of the DTC................................................................................ 309

8.4 Interrupts............................................................................................................................ 311

8.5 Usage Notes ....................................................................................................................... 312

vi

Section 9 I/O Ports............................................................................................................. 313

9.1 Overview............................................................................................................................ 313

9.2 Port 1.................................................................................................................................. 319

9.2.1 Overview............................................................................................................... 319

9.2.2 Register Configuration.......................................................................................... 320

9.2.3 Pin Functions........................................................................................................ 322

9.3 Port 2.................................................................................................................................. 330

9.3.1 Overview............................................................................................................... 330

9.3.2 Register Configuration.......................................................................................... 331

9.3.3 Pin Functions........................................................................................................ 333

9.4 Port 3.................................................................................................................................. 341

9.4.1 Overview............................................................................................................... 341

9.4.2 Register Configuration.......................................................................................... 341

9.4.3 Pin Functions........................................................................................................ 344

9.5 Port 4.................................................................................................................................. 346

9.5.1 Overview............................................................................................................... 346

9.5.2 Register Configuration.......................................................................................... 347

9.5.3 Pin Functions........................................................................................................ 347

9.6 Port 5.................................................................................................................................. 348

9.6.1 Overview............................................................................................................... 348

9.6.2 Register Configuration.......................................................................................... 348

9.6.3 Pin Functions........................................................................................................ 350

9.7 Port 6.................................................................................................................................. 351

9.7.1 Overview............................................................................................................... 351

9.7.2 Register Configuration.......................................................................................... 352

9.7.3 Pin Functions........................................................................................................ 354

9.8 Port A................................................................................................................................. 356

9.8.1 Overview............................................................................................................... 356

9.8.2 Register Configuration.......................................................................................... 357

9.8.3 Pin Functions........................................................................................................ 360

9.8.4 MOS Input Pull-Up Function [H8S/2351 Only] .................................................. 362

9.9 Port B ................................................................................................................................. 363

9.9.1 Overview............................................................................................................... 363

9.9.2 Register Configuration [H8S/2351 Only]............................................................. 364

9.9.3 Pin Functions........................................................................................................ 366

9.9.4 MOS Input Pull-Up Function [H8S/2351 Only] .................................................. 368

9.10 Port C ................................................................................................................................. 369

9.10.1 Overview............................................................................................................... 369

9.10.2 Register Configuration [H8S/2351 Only]............................................................. 370

9.10.3 Pin Functions........................................................................................................ 372

9.10.4 MOS Input Pull-Up Function [H8S/2351 Only] .................................................. 374

9.11 Port D................................................................................................................................. 375

9.11.1 Overview............................................................................................................... 375

vii

9.11.2 Register Configuration [H8S/2351 Only]............................................................. 376

9.11.3 Pin Functions........................................................................................................ 378

9.11.4 MOS Input Pull-Up Function [H8S/2351]............................................................ 379

9.12 Port E.................................................................................................................................. 380

9.12.1 Overview............................................................................................................... 380

9.12.2 Register Configuration.......................................................................................... 381

9.12.3 Pin Functions........................................................................................................ 383

9.12.4 MOS Input Pull-Up Function [H8S/2351 Only] .................................................. 384

9.13 Port F.................................................................................................................................. 385

9.13.1 Overview............................................................................................................... 385

9.13.2 Register Configuration.......................................................................................... 386

9.13.3 Pin Functions........................................................................................................ 388

9.14 Port G................................................................................................................................. 391

9.14.1 Overview............................................................................................................... 391

9.14.2 Register Configuration.......................................................................................... 392

9.14.3 Pin Functions........................................................................................................ 394

Section 10 16-Bit Timer Pulse Unit (TPU).................................................................. 397

10.1 Overview............................................................................................................................ 397

10.1.1 Features................................................................................................................. 397

10.1.2 Block Diagram...................................................................................................... 401

10.1.3 Pin Configuration.................................................................................................. 402

10.1.4 Register Configuration.......................................................................................... 404

10.2 Register Descriptions......................................................................................................... 406

10.2.1 Timer Control Register (TCR).............................................................................. 406

10.2.2 Timer Mode Register (TMDR)............................................................................. 411

10.2.3 Timer I/O Control Register (TIOR)...................................................................... 413

10.2.4 Timer Interrupt Enable Register (TIER)............................................................... 426

10.2.5 Timer Status Register (TSR) ................................................................................ 429

10.2.6 Timer Counter (TCNT)......................................................................................... 433

10.2.7 Timer General Register (TGR)............................................................................. 434

10.2.8 Timer Start Register (TSTR)................................................................................ 435

10.2.9 Timer Synchro Register (TSYR).......................................................................... 436

10.2.10 Module Stop Control Register (MSTPCR)........................................................... 437

10.3 Interface to Bus Master...................................................................................................... 438

10.3.1 16-Bit Registers.................................................................................................... 438

10.3.2 8-Bit Registers...................................................................................................... 438

10.4 Operation............................................................................................................................ 440

10.4.1 Overview............................................................................................................... 440

10.4.2 Basic Functions..................................................................................................... 441

10.4.3 Synchronous Operation ........................................................................................ 447

10.4.4 Buffer Operation................................................................................................... 449

10.4.5 Cascaded Operation.............................................................................................. 453

viii

10.4.6 PWM Modes......................................................................................................... 455

10.4.7 Phase Counting Mode........................................................................................... 460

10.5 Interrupts............................................................................................................................ 467

10.5.1 Interrupt Sources and Priorities............................................................................ 467

10.5.2 DTC/DMAC Activation........................................................................................ 469

10.5.3 A/D Converter Activation..................................................................................... 469

10.6 Operation Timing............................................................................................................... 470

10.6.1 Input/Output Timing............................................................................................. 470

10.6.2 Interrupt Signal Timing ........................................................................................ 474

10.7 Usage Notes ....................................................................................................................... 478

Section 11 Programmable Pulse Generator (PPG)..................................................... 489

11.1 Overview............................................................................................................................ 489

11.1.1 Features................................................................................................................. 489

11.1.2 Block Diagram...................................................................................................... 490

11.1.3 Pin Configuration.................................................................................................. 491

11.1.4 Registers................................................................................................................ 492

11.2 Register Descriptions......................................................................................................... 493

11.2.1 Next Data Enable Registers H and L (NDERH, NDERL) ................................... 493

11.2.2 Output Data Registers H and L (PODRH, PODRL) ............................................ 494

11.2.3 Next Data Registers H and L (NDRH, NDRL).................................................... 495

11.2.4 Notes on NDR Access.......................................................................................... 495

11.2.5 PPG Output Control Register (PCR).................................................................... 497

11.2.6 PPG Output Mode Register (PMR)...................................................................... 499

11.2.7 Port 1 Data Direction Register (P1DDR).............................................................. 502

11.2.8 Port 2 Data Direction Register (P2DDR).............................................................. 502

11.2.9 Module Stop Control Register (MSTPCR)........................................................... 503

11.3 Operation............................................................................................................................ 504

11.3.1 Overview............................................................................................................... 504

11.3.2 Output Timing ...................................................................................................... 505

11.3.3 Normal Pulse Output ............................................................................................ 506

11.3.4 Non-Overlapping Pulse Output ............................................................................ 508

11.3.5 Inverted Pulse Output ........................................................................................... 511

11.3.6 Pulse Output Triggered by Input Capture............................................................. 512

11.4 Usage Notes ....................................................................................................................... 513

Section 12 Watchdog Timer.............................................................................................. 515

12.1 Overview............................................................................................................................ 515

12.1.1 Features................................................................................................................. 515

12.1.2 Block Diagram...................................................................................................... 516

12.1.3 Pin Configuration.................................................................................................. 517

12.1.4 Register Configuration.......................................................................................... 517

12.2 Register Descriptions......................................................................................................... 518

ix

12.2.1 Timer Counter (TCNT)......................................................................................... 518

12.2.2 Timer Control/Status Register (TCSR) ................................................................ 518

12.2.3 Reset Control/Status Register (RSTCSR) ............................................................ 520

12.2.4 Notes on Register Access...................................................................................... 522

12.3 Operation............................................................................................................................ 524

12.3.1 Watchdog Timer Operation.................................................................................. 524

12.3.2 Interval Timer Operation...................................................................................... 525

12.3.3 Timing of Setting Overflow Flag (OVF).............................................................. 525

12.3.4 Timing of Setting of Watchdog Timer Overflow Flag (WOVF).......................... 526

12.4 Interrupts............................................................................................................................ 527

12.5 Usage Notes ....................................................................................................................... 527

12.5.1 Contention between Timer Counter (TCNT) Write and Increment...................... 527

12.5.2 Changing Value of CKS2 to CKS0...................................................................... 527

12.5.3 Switching between Watchdog Timer Mode and Interval Timer Mode................ 528

12.5.4 System Reset by WDTOVF Signal ...................................................................... 528

12.5.5 Internal Reset in Watchdog Timer Mode ............................................................. 528

Section 13 Serial Communication Interface (SCI)..................................................... 529

13.1 Overview............................................................................................................................ 529

13.1.1 Features................................................................................................................. 529

13.1.2 Block Diagram...................................................................................................... 531

13.1.3 Pin Configuration.................................................................................................. 532

13.1.4 Register Configuration.......................................................................................... 533

13.2 Register Descriptions......................................................................................................... 534

13.2.1 Receive Shift Register (RSR) ............................................................................... 534

13.2.2 Receive Data Register (RDR)............................................................................... 534

13.2.3 Transmit Shift Register (TSR).............................................................................. 535

13.2.4 Transmit Data Register (TDR).............................................................................. 535

13.2.5 Serial Mode Register (SMR)................................................................................ 536

13.2.6 Serial Control Register (SCR).............................................................................. 539

13.2.7 Serial Status Register (SSR) ................................................................................. 543

13.2.8 Bit Rate Register (BRR) ....................................................................................... 546

13.2.9 Smart Card Mode Register (SCMR)..................................................................... 555

13.2.10 Module Stop Control Register (MSTPCR)........................................................... 556

13.3 Operation............................................................................................................................ 557

13.3.1 Overview............................................................................................................... 557

13.3.2 Operation in Asynchronous Mode........................................................................ 559

13.3.3 Multiprocessor Communication Function............................................................ 570

13.3.4 Operation in Clocked Synchronous Mode............................................................ 578

13.4 SCI Interrupts..................................................................................................................... 586

13.5 Usage Notes ....................................................................................................................... 588

x

Section 14 Smart Card Interface...................................................................................... 593

14.1 Overview............................................................................................................................ 593

14.1.1 Features................................................................................................................. 593

14.1.2 Block Diagram...................................................................................................... 594

14.1.3 Pin Configuration.................................................................................................. 595

14.1.4 Register Configuration.......................................................................................... 596

14.2 Register Descriptions......................................................................................................... 597

14.2.1 Smart Card Mode Register (SCMR)..................................................................... 597

14.2.2 Serial Status Register (SSR) ................................................................................. 598

14.2.3 Serial Mode Register (SMR)................................................................................ 599

14.2.4 Serial Control Register (SCR).............................................................................. 600

14.3 Operation............................................................................................................................ 601

14.3.1 Overview............................................................................................................... 601

14.3.2 Pin Connections.................................................................................................... 602

14.3.3 Data Format.......................................................................................................... 603

14.3.4 Register Settings ................................................................................................... 605

14.3.5 Clock..................................................................................................................... 607

14.3.6 Data Transfer Operations...................................................................................... 609

14.3.7 Operation in GSM Mode...................................................................................... 616

14.4 Usage Notes ....................................................................................................................... 617

Section 15 A/D Converter.................................................................................................. 621

15.1 Overview............................................................................................................................ 621

15.1.1 Features................................................................................................................. 621

15.1.2 Block Diagram...................................................................................................... 622

15.1.3 Pin Configuration.................................................................................................. 623

15.1.4 Register Configuration.......................................................................................... 624

15.2 Register Descriptions......................................................................................................... 625

15.2.1 A/D Data Registers A to D (ADDRA to ADDRD).............................................. 625

15.2.2 A/D Control/Status Register (ADCSR)................................................................ 626

15.2.3 A/D Control Register (ADCR) ............................................................................. 628

15.2.4 Module Stop Control Register (MSTPCR)........................................................... 629

15.3 Interface to Bus Master...................................................................................................... 630

15.4 Operation............................................................................................................................ 631

15.4.1 Single Mode (SCAN = 0) ..................................................................................... 631

15.4.2 Scan Mode (SCAN = 1)........................................................................................ 633

15.4.3 Input Sampling and A/D Conversion Time.......................................................... 635

15.4.4 External Trigger Input Timing.............................................................................. 636

15.5 Interrupts............................................................................................................................ 637

15.6 Usage Notes ....................................................................................................................... 637

Section 16 D/A Converter.................................................................................................. 643

16.1 Overview............................................................................................................................ 643

xi

16.1.1 Features................................................................................................................. 643

16.1.2 Block Diagram...................................................................................................... 644

16.1.3 Pin Configuration.................................................................................................. 645

16.1.4 Register Configuration.......................................................................................... 645

16.2 Register Descriptions......................................................................................................... 646

16.2.1 D/A Data Registers 0 and 1 (DADR0, DADR1).................................................. 646

16.2.2 D/A Control Register (DACR) ............................................................................. 646

16.2.3 Module Stop Control Register (MSTPCR)........................................................... 648

16.3 Operation............................................................................................................................ 649

Section 17 RAM.................................................................................................................... 651

17.1 Overview............................................................................................................................ 651

17.1.1 Block Diagram...................................................................................................... 651

17.1.2 Register Configuration.......................................................................................... 652

17.2 Register Descriptions......................................................................................................... 652

17.2.1 System Control Register (SYSCR)....................................................................... 652

17.3 Operation............................................................................................................................ 653

17.4 Usage Note......................................................................................................................... 653

Section 18 ROM (H8S/2351 Only)................................................................................. 655

18.1 Overview............................................................................................................................ 655

18.1.1 Block Diagram...................................................................................................... 655

18.2 Operation............................................................................................................................ 656

Section 19 Clock Pulse Generator................................................................................... 657

19.1 Overview............................................................................................................................ 657

19.1.1 Block Diagram...................................................................................................... 657

19.1.2 Register Configuration.......................................................................................... 658

19.2 Register Descriptions......................................................................................................... 659

19.2.1 System Clock Control Register (SCKCR)............................................................ 659

19.3 Oscillator............................................................................................................................ 660

19.3.1 Connecting a Crystal Resonator............................................................................ 660

19.3.2 External Clock Input............................................................................................. 662

19.4 Duty Adjustment Circuit.................................................................................................... 664

19.5 Medium-Speed Clock Divider ........................................................................................... 664

19.6 Bus Master Clock Selection Circuit................................................................................... 664

Section 20 Power-Down Modes ...................................................................................... 665

20.1 Overview............................................................................................................................ 665

20.1.1 Register Configuration.......................................................................................... 666

20.2 Register Descriptions......................................................................................................... 667

20.2.1 Standby Control Register (SBYCR)..................................................................... 667

20.2.2 System Clock Control Register (SCKCR)............................................................ 668

xii

20.2.3 Module Stop Control Register (MSTPCR)........................................................... 669

20.3 Medium-Speed Mode......................................................................................................... 670

20.4 Sleep Mode ........................................................................................................................ 671

20.5 Module Stop Mode ............................................................................................................ 671

20.5.1 Module Stop Mode ............................................................................................... 671

20.5.2 Usage Notes.......................................................................................................... 672

20.6 Software Standby Mode..................................................................................................... 673

20.6.1 Software Standby Mode........................................................................................ 673

20.6.2 Clearing Software Standby Mode......................................................................... 673

20.6.3 Setting Oscillation Stabilization Time after Clearing Software Standby Mode... 674

20.6.4 Software Standby Mode Application Example .................................................... 674

20.6.5 Usage Notes.......................................................................................................... 675

20.7 Hardware Standby Mode ................................................................................................... 676

20.7.1 Hardware Standby Mode...................................................................................... 676

20.7.2 Hardware Standby Mode Timing ......................................................................... 676

20.8 ø Clock Output Disabling Function ................................................................................... 677

Section 21 Electrical Characteristics.............................................................................. 679

21.1 Absolute Maximum Ratings.............................................................................................. 679

21.2 DC Characteristics ............................................................................................................. 680

21.3 AC Characteristics ............................................................................................................. 685

21.3.1 Clock Timing........................................................................................................ 686

21.3.2 Control Signal Timing.......................................................................................... 688

21.3.3 Bus Timing ........................................................................................................... 690

21.3.4 DMAC Timing...................................................................................................... 700

21.3.5 Timing of On-Chip Supporting Modules.............................................................. 704

21.4 A/D Conversion Characteristics ........................................................................................ 709

21.5 D/A Convervion Characteristics........................................................................................ 710

21.6 Usage Note......................................................................................................................... 710

Appendix A Instruction Set............................................................................................... 711

A.1 Instruction List................................................................................................................... 711

A.2 Instruction Codes ............................................................................................................... 735

A.3 Operation Code Map.......................................................................................................... 750

A.4 Number of States Required for Instruction Execution....................................................... 754

A.5 Bus States During Instruction Execution........................................................................... 765

A.6 Condition Code Modification ............................................................................................ 779

Appendix B Internal I/O Register................................................................................... 785

B.1 Addresses ........................................................................................................................... 785

B.2 Functions............................................................................................................................ 794

xiii

Appendix C I/O Port Block Diagrams........................................................................... 913

C.1 Port 1 Block Diagram........................................................................................................ 913

C.2 Port 2 Block Diagram........................................................................................................ 916

C.3 Port 3 Block Diagram........................................................................................................ 917

C.4 Port 4 Block Diagram........................................................................................................ 920

C.5 Port 5 Block Diagram........................................................................................................ 921

C.6 Port 6 Block Diagram........................................................................................................ 923

C.7 Port A Block Diagram........................................................................................................ 929

C.8 Port B Block Diagram........................................................................................................ 935

C.9 Port C Block Diagram........................................................................................................ 937

C.10 Port D Block Diagram........................................................................................................ 939

C.11 Port E Block Diagram........................................................................................................ 941

C.12 Port F Block Diagram........................................................................................................ 943

C.13 Port G Block Diagram........................................................................................................ 951

Appendix D Pin States........................................................................................................ 955

D.1 Port States in Each Mode [H8S/2351] ............................................................................... 955

D.2 Port States in Each Mode [H8S/2350] ............................................................................... 959

Appendix E Pin States at Power-On.............................................................................. 962