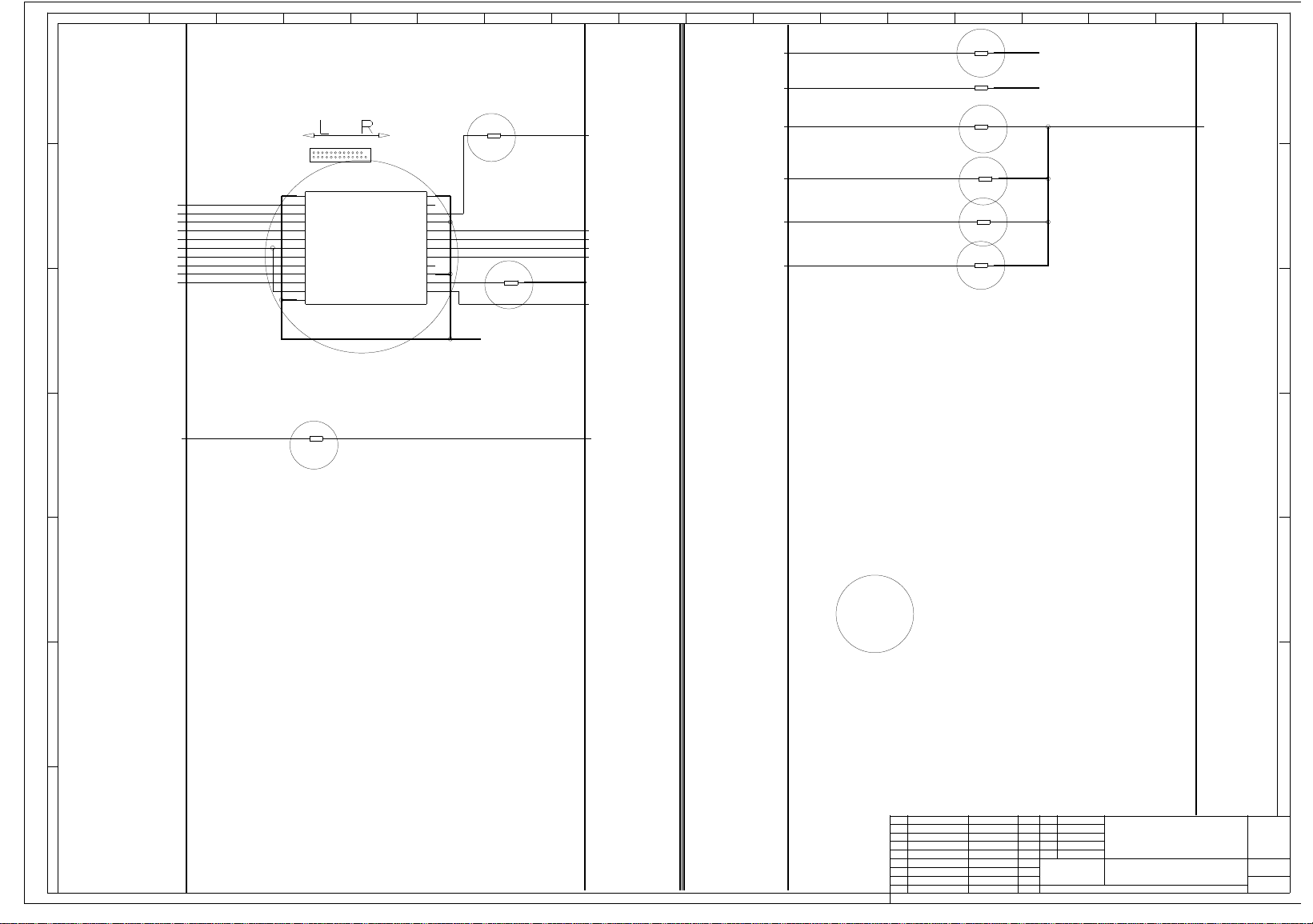

Gigabyte GA-8ISPK-FJ Schematic REV.1.0

ABBREV=D1534

TITLE=D1534

LAST_MODIFIED=Fri Jan 17 05:29:06 2003

DRAWING

SACHNUMMER

FUJITSU

SIEMENS

COMPUTERS

REG_PAGE

VORGANG

HIGHEST_LOGIC

CURRENT_LOGIC

FRAME1 VERSION 1

NAME

DATUM

ZUST

18

1716151110

98

76

5

4

1413

12

3

21

D

E

C

B

A

A

B

C

D

E

F

G

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

F

NAME

GEPR.

NORM

T-NR.

DATUM

S26361-D1534-X-*-11

02

02A3842

SCU

1

99

1+

FOR REPAIR ONLY

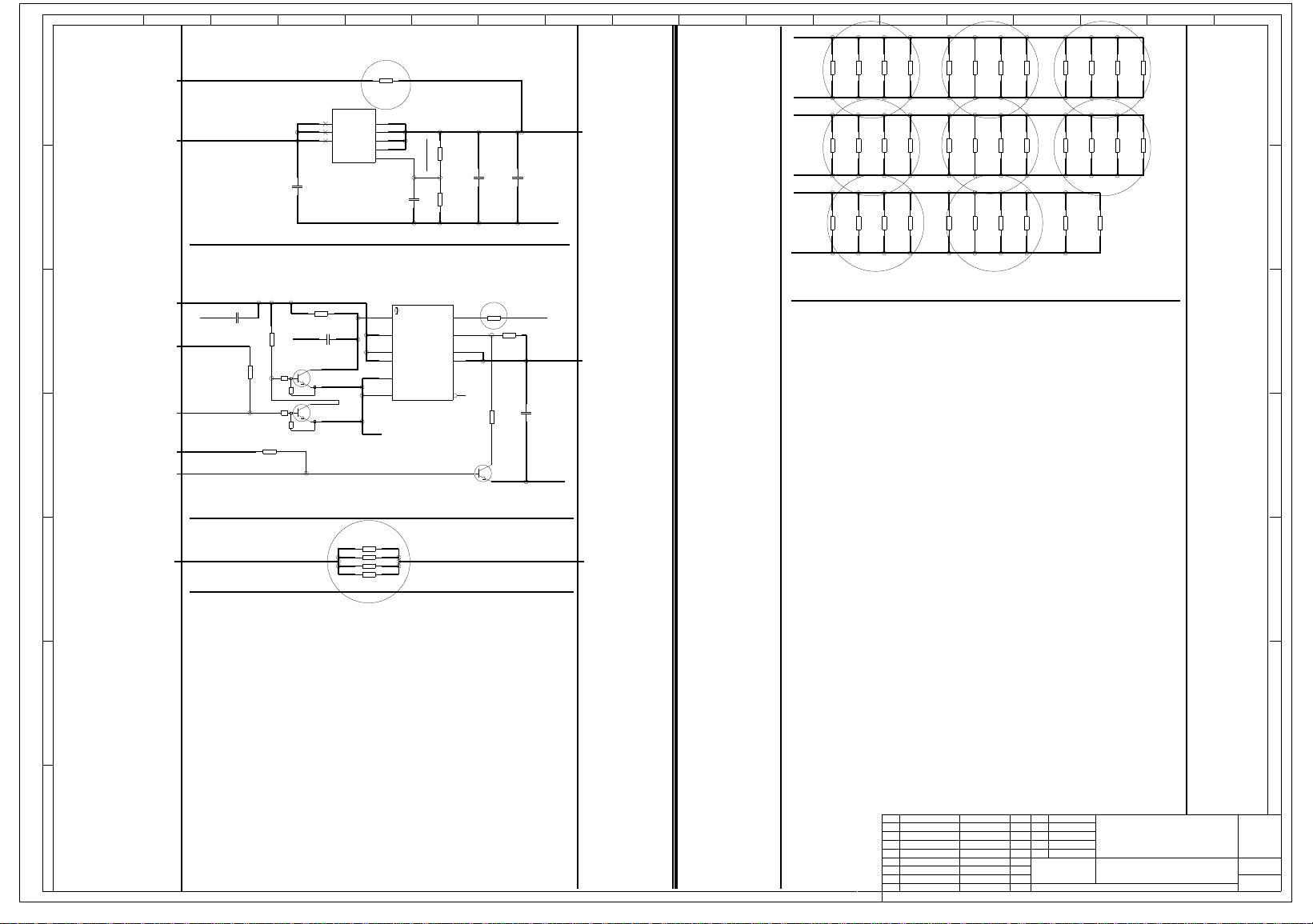

PAGE 99:

RJ-45 CONNECTOR

PAGE 94:

LAN_VREG / LAN_DECOUPLING

PAGE 92:

LAN POPULATION OPTIONS

PAGE 91:

LAN - CONTROLLER INTEL - KENAI II CSA

PAGE 90:

VGA CONNECT.,FILTER TRANSLATION / ISOLATION

PAGE 85:

AGP CONNECTOR PAGE 80:

MIC IN (REAR), LINE IN AND HEADPHONE OUT

PAGE 75:

CD IN, S/PDIF OUT,

PAGE 73:

MONO-AMPLIFIER

PAGE 72:

AC97 CODEC PAGE 71:

CPU/AUX FAN, EXT.SMB INTRUSION, PWR CONTROL

PAGE 66:

SYSTEMMONITORING PIC PIC SUPPORT, MAX1617

PAGE 65:

PCI-BUS RISER SLOT

PAGE 53:

PCI-BUS SLOT 1 + SLOT SUPPORT

PAGE 52:

POWER CONN./DECOUPL. RESET GENERATION

PAGE 48:

FRONTPANEL & SWITCH

PAGE 47:

FWH PAGE 46:

CONNECTOR KBD/MOUSE

PAGE 45:

CONNECTOR PARALLEL

PAGE 44:

CONNECTOR SER1 / SER2

PAGE 43:

CONNECTOR FLOPPY

PAGE 42:

47M967 SUPER-IO

PAGE 40:

USB CONNECTORS USB BLUETOOTH CONNECTOR

PAGE 38:

USB CONNECTORS

PAGE 37:

PCI PULLUPS / GAP C

PAGE 35:

ICH GPIO PULLUPS /2

PAGE 34:

ICH GPIO PULLUPS /1

PAGE 33:

PCI - IDE 1/2 + 3/4 SERIAL ATA CONN.

PAGE 32:

ICH SUPPORT BATTERY

PAGE 31:

ICH5 PAGE 30:

DDR TERMINATION B

PAGE 28:

DDR TERMINATION A

PAGE 27:

MEMORY MODUL 2

PAGE 25:

MEMORY MODUL 1

PAGE 24:

GMCH PAGE 22:

MCH SUPPORT PAGE 21:

GMCH PAGE 20:

CLKSYNTHESIZER

PAGE 19:

VOLTAGE REGULATORS

PAGE 15:

VOLTAGE REGULATORS

PAGE 14:

CPU CORE VOLTAGE REG.

PAGE 13:

CPU SUPPORT PAGE 12:

ITP PAGE 11:

PRESCOTT CPU PAGE 10:

HISTORY PAGE 9:

BUSPINS PAGE 6:

BUSPINS PAGE 5:

NC-PINS PAGE 4:

HIDDENPOWERPINS

PAGE 3:

HIDDENPOWERPINS

PAGE 2:

CONTENTS PAGE 1:

A_BRASILIA D1534 WGS2

BRASILIA

CONTENTS

DATUM

T-NR.

NORM

GEPR.

NAME

F

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

G

F

E

D

C

B

A

A

B

C

E

D

1 2

3

12

13 14

4

5

6 7

8 9

10 11 15 16 17

18

ZUST

DATUM

NAME

SACHNUMMER

FRAME1 VERSION 1

CURRENT_LOGIC

HIGHEST_LOGIC

VORGANG

REG_PAGE

FUJITSU

SIEMENS

COMPUTERS

S26361-D1534-X-*-11

02

02A3842

SCU

$

#

@

ABBREV=D1534

TITLE=D1534

LAST_MODIFIED=Fri Jan 17 05:28:55 2003

DRAWING

VTERM_GTL D2000 A4,A5,A6,B5,B6,C5,C6,D5,D6,D7,E6,E7,F7

,E8,F11,F13,F15,F17,F19,F9

VCC_CPUCORE D1000 A10,A12,A14,A16,A18,A20,A8,AA10,AA12,AA14,AA16,AA18,AA8,AB11,AB13,AB15,AB17,AB19,AB7,AB9,AC10,AC12,AC14,AC16,AC18,AC8,AD11,AD13,AD15,AD17,AD19,AD7,AD9,AE10,AE12,AE14,AE16,AE18,AE20,AE6,AE8

VCC D4851 5

VCC D4320 20

VCC D4310 20

SHIELD_GND_2 X4320 10,11

SHIELD_GND X4300 10,11

P3V3P_DUAL D9120 8

P3V3P_DUAL D9000 A11,A3,A7,E1,K13,K3,N6,N8,P12,P2

P3V3P_DUAL D4880 14

P3V3P D8500 8

P3V3P D6560 14

P3V3P D4850 14

P3V3P D4600 25,27,32

P3V3P D4000 121,19,80

P3V3P D3000 M10,N10,P6,R13,V19,W15,W17,W24

P3V3P D3000 AD13,AD20,B5,F6,G1,G19,G21,H6,K6,L6

P2V5P_DUAL X2400 X2500 104,108,112,120,128,136,143,148,15,156,164,168,172,180,22,30,38,46,54,62,7,70,77,85,96

P2V5P_DUAL D2000 AL6,AL7,AM1,AM2,AM3,AM5,AM6,AM7,AM8,AN2,AN4,AN5,AN6,AN7,AN8,AP3,AP4,AP5,AP6,AP7,AR4,AR5,AR7

P1V5P D3000 W6,W7,W8,W9

P1V5P D3000 M15,N15,N23,P19,R10,R12,R6,W10,W11,W19

P1V5P D3000 E15,F14,F15,H24,J19,K10,K12,K13,K19,L19

P1V5P D2000 J6,J7,J8,J9,K6,K7,K8,K9,L10,L11,L6,L7,L9,M10,M11,M8,M9,N10,N11,N9,P10,P11,R11,T16,T17,T18,T19,T20,U16,U17,U20,V16,V18,V20,W16,W19,W20,Y16,Y17,Y18,Y19,Y20

P12VP_CORE D4310 1

P12VP D4320 1

P12VN D4320 10

P12VN D4310 10

GND X2400 X2500 100,11,116,124,132,139,145,152,160,176,18,26,3,34,42,50,58,66,74,81,89,93

GND D9120 5

GND D9000 B3,B7,C10,C12,D13,D5,D7,D8,E2,E5,E6,E7,E8,E9,F10,F11,F4,F6,F7,F8,F9,G10,G11,G14,G7,G8,G9,H10,H9,K12,L11,L6,M6,N12,P8

GND D8500 4

GND D6560 7

GND D4880 7

GND D4851 3

GND D4850 7

GND D4600 16,26,28

GND D4320 11

GND D4310 11

GND D4000 32,57,6,87,99

GND D3000 V1,V21,W16,W18,Y10,Y3,Y6,Y7,Y8

GND D3000 P13,P14,P15,P21,R11,R14,T23,T3,T6,U19

GND D3000 M5,N11,N12,N13,N14,N20,P1,P10,P11,P12

GND D3000 L15,L21,L23,M1,M11,M12,M13,M14,M22,M24

GND D3000 K14,K20,K22,K24,K3,L10,L11,L12,L13,L14

GND D3000 G20,G24,G6,H1,H19,H22,J21,J23,J6,K11

GND D3000 D22,D24,D6,E17,E19,E20,E21,E23,F3,F9

GND D3000 C18,C20,C22,C3,C8,D1,D11,D16,D18,D20

GND D3000 AD21,AD4,AD6,AD8,B13,B17,B19,B21,B23,C16

GND D3000 AB9,AC10,AC13,AC2,AC23,AC4,AC6,AC8,AD12,AD17

GND D3000 AA21,AA24,AA5,AA7,AA9,AB11,AB15,AB18,AB5,AB7

GND D3000 A1,A10,A15,A17,A19,A21,A23,A7,AA11,AA13

,K11,K12,K14,K16,K18,K20,K22,K25,K27,K29,K33,L24,L25,L26,L31,L35,M26,M27,M28,M3,M30,M33,M6,N1,N32,N35,N4,P26,P27,P28,P3,P30,P33,P6,P8,P9,R1,R32,R4,T1,T10,T26,T27,T28,T3,T30,T33,T35,T6,T8,T9,U18,U19,U32,U4,V10,V17,V19,V26,V27,V28,V3,V30,V33,V6,V8,V9,W

M13,AM15,AM17,AM19,AM21,AM23,AM25,AM27,AM29,AM35,AM9,AN10,AN12,AN14,AN16,AN18,AN20,AN22,AN24,AN26,AN28,AN30,AN32,AR11,AR13,AR16,AR20,AR23,C10,C12,C14,C16,C18,C20,C22,C24,C26,C28,C4,C8,D1,D11,D13,D15,D17,D19,D21,D23,D25,D27,D29,D31,D33,D35,D9,E1,E3,F1

GND D2000 A11,AD10,AD28,AD3,AD30,AD33,AD6,AD8,AD9,AE1,AE10,AE11,AE12,AE13,AE25,AE26,AE32,AE35,AE4,AF11,AF14,AF16,AF18,AF20,AF22,AF24,AF25,AF3,AF30,AF33,AF6,AF9,AG14,AG16,AG18,AG20,AG22,AG24,AG26,AG2

18,B20,B23,B26,B4,B8,C11,C13,C15,C17,C19,C2,C22,C25,C5,C7,C9,D10,D12,D14,D16,D18,D20,D21,D24,D3,D6,D8,E1,E11,E13,E15,E17,E19,E23,E26,E4,E7,E9,F10,F12,F14,F16,F18,F2,F22,F25,F5,F8,G21,G24,G3,G6,H1,H23,H26,H4,J2,J22,J25,J5,K21,K24,K3,K6,L1,L23,L26,L4,M

GND D1000 A11,A13,A15,A17,A19,A21,A24,A26,A3,A9,AA1,AA11,AA13,AA15,AA17,AA19,AA23,AA26,AA4,AA7,AA9,AB10,AB12,AB14,AB16,AB18,AB20,AB21,AB24,AB3,AB6,AB8,AC11,AC13,AC15,AC17,AC19,AC2,AC22,AC25,AC5,AC7,

..............................................................................................................

Hidden_Power_Pins

BRASILIA

HIDDENPOWERPINS

DATUM

T-NR.

NORM

GEPR.

NAME

F

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

G

F

E

D

C

B

A

A

B

C

E

D

1 2

3

12

13 14

4

5

6 7

8 9

10 11 15 16 17

18

ZUST

DATUM

NAME

SACHNUMMER

FRAME1 VERSION 1

CURRENT_LOGIC

HIGHEST_LOGIC

VORGANG

REG_PAGE

FUJITSU

SIEMENS

COMPUTERS

S26361-D1534-X-*-11

02

02A3842

SCU

$

#

@

ABBREV=D1534

TITLE=D1534

LAST_MODIFIED=Fri Jan 17 05:29:06 2003

DRAWING

BRASILIA

HIDDENPOWERPINS

DATUM

T-NR.

NORM

GEPR.

NAME

F

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

G

F

E

D

C

B

A

A

B

C

E

D

1 2

3

12

13 14

4

5

6 7

8 9

10 11 15 16 17

18

ZUST

DATUM

NAME

SACHNUMMER

FRAME1 VERSION 1

CURRENT_LOGIC

HIGHEST_LOGIC

VORGANG

REG_PAGE

FUJITSU

SIEMENS

COMPUTERS

S26361-D1534-X-*-11

02

02A3842

SCU

$

#

@

ABBREV=D1534

TITLE=D1534

LAST_MODIFIED=Fri Jan 17 05:29:06 2003

DRAWING

X8000 125,126,127,128,129

X7310 5

X5302 121,122

X4800 21,22

X4750 4

X4400 28

X4200 5

X3820 1,11

X3240 X3241 8,9

X3200 X3201 20

X2400 X2500 191,192,193,194,195,71,9

X2400 X2500 101,102,163,173,185,186,187,188,189,190

X1300 5,6

X1100 26

N6530 4,5

N1500 8

N1430 N1431 N1520 1,13,16,3,6,9

D2000 M31,R25

D2000 AR3,AR33,AR35,B2,B25,B34,C1,C23,C35,E26

D2000 A35,AF13,AF23,AG9,AJ12,AN1,AN35,AP2,AP34,AR1

D2000 933,934,935,936,937,938,939,940,A3,A33

D1000 479,480,481,482,A22,A7,AE21,AF24,AF25

B2000 B2001 B2002 B2003 2

......................................................................................

NC_Pins

BRASILIA

NC-PINS

DATUM

T-NR.

NORM

GEPR.

NAME

F

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

G

F

E

D

C

B

A

A

B

C

E

D

1 2

3

12

13 14

4

5

6 7

8 9

10 11 15 16 17

18

ZUST

DATUM

NAME

SACHNUMMER

FRAME1 VERSION 1

CURRENT_LOGIC

HIGHEST_LOGIC

VORGANG

REG_PAGE

FUJITSU

SIEMENS

COMPUTERS

S26361-D1534-X-*-11

02

02A3842

SCU

$

#

@

ABBREV=D1534

TITLE=D1534

LAST_MODIFIED=Fri Jan 17 05:29:06 2003

DRAWING

PAGE: 10

LOCATION: D1000

PIN GTL_RESP_L

F4 2

G5 1

F1 0

PIN GTL_ADR_L

AB1 35

Y1 34

W2 33

V3 32

U4 31

T5 30

W1 29

R6 28

V2 27

T4 26

U3 25

P6 24

U1 23

T2 22

R3 21

P4 20

P3 19

R2 18

T1 17

N5 16

N4 15

N2 14

M1 13

N1 12

M4 11

M3 10

L2 9

M6 8

L3 7

K1 6

L6 5

K4 4

K2 3

PIN GTL_ADRSTB_L

R5 1

L5 0

PIN NC

V5 1

PIN NC

AC1 0

PIN GTL_CMD_L

H3 4

J3 3

J4 2

K5 1

J1 0

PIN GTL_DATA_L

AA24 63

AA22 62

AA25 61

Y21 60

Y24 59

Y23 58

W25 57

Y26 56

W26 55

V24 54

V22 53

U21 52

V25 51

U23 50

U24 49

U26 48

T23 47

T22 46

T25 45

T26 44

R24 43

R25 42

P24 41

R21 40

N25 39

N26 38

M26 37

N23 36

M24 35

P21 34

N22 33

M23 32

H25 31

K23 30

J24 29

L22 28

M21 27

H24 26

G26 25

L21 24

D26 23

F26 22

E25 21

F24 20

F23 19

G23 18

E24 17

H22 16

D25 15

J21 14

D23 13

C26 12

H21 11

G22 10

B25 9

C24 8

C23 7

B24 6

D22 5

C21 4

A25 3

A23 2

B22 1

B21 0

PIN GTL_DBI_L

V21 3

P26 2

G25 1

E21 0

PIN NC

L25 3

PIN NC

K26 2

PIN NC

K25 1

PIN NC

J26 0

PIN CPU_BPM_L

AB4 5

AA5 4

Y6 3

AC4 2

AB5 1

AC6 0

PIN CPU_VID_H

AD3 5

AE1 4

AE2 3

AE3 2

AE4 1

AE5 0

PAGE: 20

LOCATION: D2000

PIN GTL_ADR_L

G26 31

J26 30

G30 29

F31 28

E32 27

K24 26

H27 25

E28 24

F29 23

G27 22

J27 21

C34 20

F28 19

C32 18

D34 17

F25 16

J24 15

B33 14

E30 13

B31 12

J25 11

C31 10

C30 9

K23 8

B32 7

E29 6

L23 5

D30 4

D26 3

PIN GTL_CMD_L

J21 4

C29 3

L22 2

J23 1

B29 0

PIN AGP_SBA_H

T7 7

U5 6

U10 5

U9 4

R5 3

R3 2

P7 1

R6 0

PIN GTL_RESP_L

B27 2

C27 1

G22 0

PIN GTL_DATA_L

B8 63

D8 62

B9 61

C9 60

B10 59

E10 58

C11 57

D10 56

B11 55

C13 54

D14 53

B15 52

B12 51

B14 50

E14 49

B13 48

E9 47

G8 46

H10 45

J11 44

K13 43

E11 42

L15 41

G10 40

G12 39

K15 38

E13 37

F11 36

F13 35

J13 34

L16 33

J15 32

K17 31

E17 30

G14 29

J19 28

E21 27

E15 26

F15 25

F21 24

G18 23

G16 22

L18 21

J17 20

F19 19

E19 18

F17 17

G20 16

D18 15

E16 14

B17 13

B18 12

D16 11

B16 10

E20 9

E18 8

C21 7

B20 6

D22 5

B22 4

D20 3

B21 2

E22 1

B23 0

PIN ICH_HI_H

AJ3 10

AH2 9

AJ2 8

AL4 7

AL2 6

AL3 5

AK5 4

AG5 3

AK2 2

AG3 1

AF5 0

PIN LAN_CSA_H

AG6 10

AH9 9

AE9 8

AG7 7

AF8 6

AC10 5

AD7 4

AF7 3

AD11 2

AH7 1

AK7 0

PIN AGP_AD_H

M2 31

P4 30

P5 29

P2 28

R2 27

T5 26

T4 25

T2 24

U3 23

W3 22

V2 21

Y5 20

W2 19

Y2 18

Y4 17

AA2 16

V7 15

W9 14

W6 13

AA11 12

W10 11

AA5 10

AA6 9

AA9 8

AB7 7

AB11 6

AC9 5

AA10 4

AE5 3

AD5 2

AC11 1

AE6 0

PIN AGP_C_BE_L

U2 3

AA3 2

W5 1

Y7 0

PIN AGP_ST_H

N2 2

N5 1

N3 0

PIN SMEMA_DAT_H

F34 63

G34 62

J34 61

K31 60

F33 59

E33 58

H34 57

J33 56

L33 55

L34 54

P34 53

T31 52

K32 51

K34 50

T32 49

T34 48

U33 47

U34 46

AB32 45

AD31 44

V31 43

V32 42

AB31 41

AC34 40

AD34 39

AE34 38

AG33 37

AH31 36

AD32 35

AF32 34

AG34 33

AH32 32

AN34 31

AM31 30

AN29 29

AM28 28

AM33 27

AP33 26

AP29 25

AP28 24

AP27 23

AP25 22

AL22 21

AP21 20

AN27 19

AL24 18

AM22 17

AP22 16

AM18 15

AP18 14

AN15 13

AL14 12

AP19 11

AL18 10

AM14 9

AP14 8

AP13 7

AL12 6

AL10 5

AM10 4

AN13 3

AM12 2

AP11 1

AP10 0

PIN SMEMA_DM_H

H32 7

M34 6

W33 5

AF31 4

AP30 3

AM24 2

AP16 1

AP12 0

PIN SMEMA_DQS_H

H31 7

M32 6

V34 5

AF34 4

AM30 3

AP23 2

AP15 1

AN11 0

PIN SMEMB_DAT_H

G32 63

J29 62

M25 61

N25 60

G33 59

F32 58

H29 57

K30 56

L32 55

P25 54

R26 53

R31 52

L30 51

K28 50

R30 49

P29 48

R27 47

U25 46

V29 45

AA31 44

T25 43

U27 42

W30 41

AA30 40

AA27 39

AA26 38

AB29 37

AE31 36

Y29 35

AC30 34

AC27 33

AE30 32

AF28 31

AD25 30

AJ27 29

AJ26 28

AF27 27

AG27 26

AH26 25

AK25 24

AE22 23

AJ24 22

AK21 21

AL19 20

AK23 19

AG23 18

AE20 17

AE19 16

AJ18 15

AJ16 14

AJ14 13

AK13 12

AL17 11

AK17 10

AL13 9

AE17 8

AG12 7

AK11 6

AF12 5

AL8 4

AE16 3

AL11 2

AE15 1

AJ10 0

PIN SMEMB_DM_H

J31 7

M29 6

U31 5

AC31 4

AJ28 3

AE21 2

AG15 1

AG11 0

PIN SMEMB_DQS_H

J30 7

L27 6

U30 5

AD29 4

AH27 3

AG21 2

AG13 1

AF15 0

PIN CLK_SMEMA_H

P31 5

AM16 4

AK33 3

N33 2

AP17 1

AK32 0

PIN CLK_SMEMA_L

P32 5

AL16 4

AK34 3

N34 2

AN17 1

AK31 0

PIN SMEMA_ADR_H

AN21 12

AN23 11

AJ33 10

AP24 9

AP26 8

AN25 7

AL28 6

AL26 5

AL30 4

AN31 3

AK29 2

AL33 1

AJ34 0

PIN NC

AM26 5

PIN NC

AP31 4

PIN NC

AP32 3

PIN NC

AM34 2

PIN NC

AL34 1

PIN SMEMA_CS_L

W34 3

Y32 2

Y31 1

AA34 0

PIN SMEMA_CKE_H

AP20 3

AM20 2

AN19 1

AL20 0

PIN SMEMA_BA_H

AH34 1

AE33 0

PIN CLK_SMEMB_H

N31 5

AK15 4

AJ30 3

N27 2

AF17 1

AG29 0

PIN CLK_SMEMB_L

N30 5

AL15 4

AH29 3

N26 2

AG17 1

AG30 0

PIN SMEMB_ADR_H

AJ20 12

AL21 11

AF29 10

AJ22 9

AL23 8

AF21 7

AL25 6

AG25 5

AK27 4

AE24 3

AD27 2

AJ31 1

AG31 0

PIN NC

AE23 5

PIN NC

AL27 4

PIN NC

AL29 3

PIN NC

AD26 2

PIN NC

AE27 1

PIN SMEMB_CS_L

W25 3

V25 2

T29 1

U26 0

PIN SMEMB_CKE_H

AE18 3

AG19 2

AF19 1

AK19 0

PIN SMEMB_BA_H

AA25 1

Y25 0

PAGE: 24

LOCATION: X2400

PIN SMEMA_ADR_H

27 9

122 8

29 7

125 6

32 5

37 4

130 3

41 2

43 1

48 0

115 12

118 11

PIN SMEMA_DAT_H

99 7

98 6

95 5

94 4

8 3

6 2

4 1

2 0

110 15

109 14

106 13

105 12

20 11

19 10

13 9

12 8

123 23

121 22

117 21

114 20

31 19

28 18

24 17

23 16

133 31

131 30

127 29

126 28

40 27

39 26

35 25

33 24

151 39

150 38

147 37

146 36

60 35

57 34

55 33

53 32

162 47

161 46

155 45

153 44

69 43

68 42

64 41

61 40

171 55

170 54

166 53

165 52

80 51

79 50

73 49

72 48

179 63

178 62

175 61

174 60

88 59

87 58

84 57

83 56

PIN NC

144 7

PIN NC

142 6

PIN NC

135 5

PIN NC

134 4

PIN NC

51 3

PIN NC

49 2

PIN NC

45 1

PIN NC

44 0

PAGE: 25

LOCATION: X2500

PIN SMEMB_ADR_H

27 9

122 8

29 7

125 6

32 5

37 4

130 3

41 2

43 1

48 0

115 12

118 11

PIN SMEMB_DAT_H

99 7

98 6

95 5

94 4

8 3

6 2

4 1

2 0

110 15

109 14

106 13

105 12

20 11

19 10

13 9

12 8

123 23

121 22

117 21

114 20

31 19

28 18

24 17

23 16

133 31

131 30

127 29

126 28

40 27

39 26

35 25

33 24

151 39

150 38

147 37

146 36

60 35

57 34

55 33

53 32

162 47

161 46

155 45

153 44

69 43

68 42

64 41

61 40

171 55

170 54

166 53

165 52

80 51

79 50

73 49

72 48

179 63

178 62

175 61

174 60

88 59

87 58

84 57

83 56

PIN NC

144 7

PIN NC

142 6

PIN NC

135 5

PIN NC

134 4

PIN NC

51 3

PIN NC

49 2

PIN NC

45 1

PIN NC

44 0

PAGE: 30

LOCATION: D3000

PIN ICH_HI_H

G22 11

K21 10

J22 9

L22 8

M20 7

N21 6

M21 5

M23 4

H23 3

J20 2

H21 1

H20 0

PIN IDE_PRI_DAT_H

AB17 15

AA16 14

Y16 13

AC16 12

AA15 11

AD16 10

Y15 9

AD15 8

AB14 7

AD14 6

AC15 5

AA14 4

AC14 3

Y14 2

Y13 1

AB16 0

PIN IDE_SEC_DAT_H

AA23 15

AB24 14

AC24 13

AB22 12

AA20 11

AC22 10

AD22 9

Y19 8

AC20 7

AB20 6

AC21 5

AB21 4

AD24 3

AD23 2

AB23 1

AA22 0

PIN PCI_AD_H

P2 31

F4 30

P4 29

F5 28

N2 27

D3 26

P3 25

E6 24

N4 23

C4 22

N5 21

H3 20

P5 19

B2 18

L1 17

G4 16

G5 15

K1 14

G2 13

L5 12

H4 11

M4 10

F2 9

K5 8

J2 7

J3 6

H2 5

H5 4

K4 3

G3 2

J5 1

J4 0

PIN PCI_C_BE_L

M2 3

N3 2

J1 1

E3 0

PIN IDE_PRI_ADR_H

AC19 2

AD19 1

AA19 0

PIN IDE_SEC_ADR_H

W21 2

W23 1

W22 0

PIN LPC_LAD

U4 3

R3 2

R4 1

T5 0

PIN LAN_ICH_RXD

C11 2

C9 1

C10 0

PIN LAN_ICH_TXD

B12 2

E9 1

D9 0

PAGE: 40

LOCATION: D4000

PIN LPC_LAD

24 3

23 2

22 1

21 0

PIN LPT_DAT_H

91 7

90 6

89 5

88 4

86 3

85 2

84 1

83 0

PAGE: 46

LOCATION: D4600

PIN LPC_LAD

17 3

15 2

BRASILIA

BUSPINS

DATUM

T-NR.

NORM

GEPR.

NAME

F

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

G

F

E

D

C

B

A

A

B

C

E

D

1 2

3 12

13 144

5

6 7

8 9 10 11 15 16 17

18

ZUST

DATUM

NAME

SACHNUMMER

FRAME1 VERSION 1

CURRENT_LOGIC

HIGHEST_LOGIC

VORGANG

REG_PAGE

FUJITSU

SIEMENS

COMPUTERS

S26361-D1534-X-*-11

02

02A3842

SCU

$

#

@

ABBREV=D1534

TITLE=D1534

LAST_MODIFIED=Fri Jan 17 05:29:07 2003

DRAWING

14 1

13 0

PAGE: 90

LOCATION: D9000

PIN LAN_CSA_H

H1 10

G2 9

H3 8

N2 7

M1 6

M2 5

L3 4

K1 3

J3 2

J2 1

J1 0

D1534 D1534

BRASILIA

BUSPINS

ABBREV=D1534

D1534

LAST_MODIFIED=Fri Jan 17 05:29:05 2003

DRAWING

SACHNUMMER

FUJITSU

SIEMENS

COMPUTERS

REG_PAGE

VORGANG

HIGHEST_LOGIC

CURRENT_LOGIC

FRAME1 VERSION 1

NAME

DATUM

ZUST

18

1716151110

98

76

5

4

1413

12

3

21

D

E

C

B

A

A

B

C

D

E

F

G

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

F

NAME

GEPR.

NORM

T-NR.

DATUM

S26361-D1534-X-*-11

02

02A3842

SCU

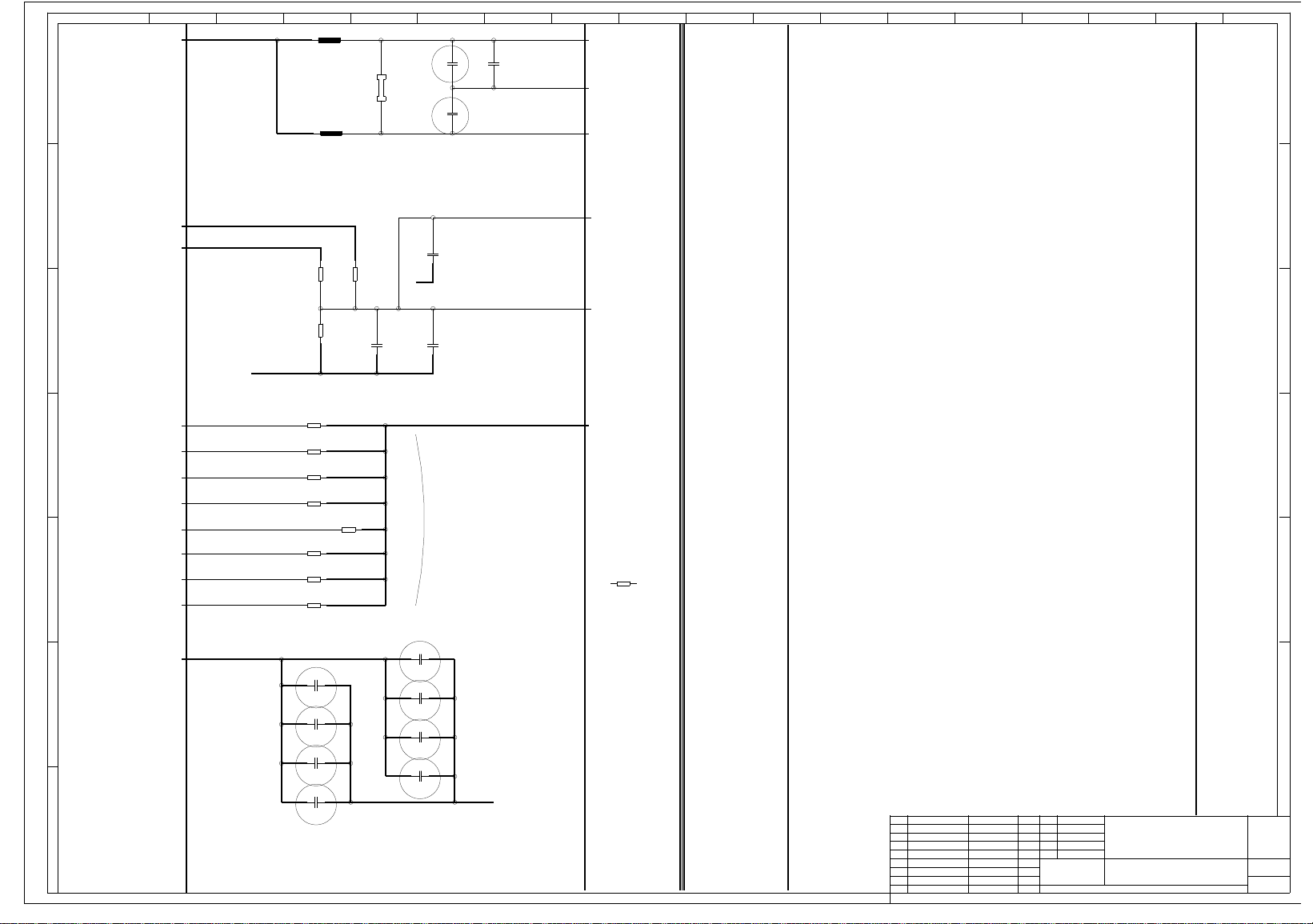

9

99

7+

CHANGE R9420-R9422,R9401 TO 0402

ADD R1090 (0R) TO SIGNAL CPU_BOOTSEL_H (POPULATE IF ONLY NWD)

CHANGE V1481 FROM IDP20N03L TO IDP12N03L (LOWER RDS

ADD X4750 HEADER + JUMPER

ADD V6560,A6560,R6560,R6561,R6562,D6560

NEW ICH SIGNALS: EN_PRESCOTT_L GPIO34(F21)

PROC_HOT CIRCUIT

DELETE D3180,R3181

ICH_SYNC CIRCUIT

ADD A6630/2 TO SIGNAL MON_ON_H (REDUCE H-LEVEL)

C2250 => B82-V8 (ALU)

38 CHANGE L3825,L3826 TO V26813-B356-V50 (NO L-SHORT !)

D1369 DDR TERM

NOTE SELECT FOR D7100: DEVICE AD1980 V26808-B7758-V30

DON’T POPULATE A7501

MODIFY C1900,C1901 FROM 6P8 TO 33P

DELETE C7100

20

30

MODIFY R1482 => 27K (P2V5P_DUAL STABILITY)

DON’T POPULATE K4310,K4311,K4320,K4321

RECONNECT A1580 PIN6 FROM P2V5P_DUAL TO VCC_DUAL (BETTER U )

99

85

14

10

19

ADD R7150 (0R) DON’T POPULATE

14

71

ADD R9118 (SELECT ASPI EEPROM)

CE

65

14

14

14

92

SECTION A1580

15,19

15

RECONNECT V1521

65

48

30

13

48

66

72

92

19

PAGE

08.07.02

SCHUTZ

22

22

D1382 FIRST COPY

D1451 AUDIO

91

MODIFY

CHANGE

MODIFY

MODIFY

MODIFY

31

30,65

47

15

91

71

10

80

13

14,21,22,30,31,35,80

14

19

14

15

DON’T POPULATE A1555-A1557

MODIFY C1005 FROM 100N TO 1U

REPLACE X8000 AGP CONNECTOR

14,15

91

91

48

DON’T POPULATE C4818

65

48

DEL A6520 (RAC)

22

RECONNECT A1580/3 TO V1521/3

CHANGE C1429 FROM 680U TO 22U

NEW SIGNAL P2V4P

SIGNALCHANGE P1V5P_AI --> P1V5P

DON’T POPULATE L1310,L1302,L1303

ADD L1320,L1322,L1323

(KOMBI-LAYOUT)

RECONNECT V1480 ANODE TO VCC_DUAL

14

45

DON’T POPULATE K4500

DON’T POPULATE C1020,C1023

43

44

DON’T POPULATE K4401,K4402

13

48

15

80

CHANGE R1423 FROM 24R9 TO 113R

75

)

LAN DISABLE CIRCUIT

DEL D9150 ,R9150

DEL A9201,A9203

33 CHANGE WGS-ID

C1992 => B51-V7 (0603)

C9111 => B51-V7 (0603)

C9267 => B51-V7 (0603)

MODIFY R1333,R1531 TO 6K8 NTC

ON

MODIFY R1485 => 10K (P2V5P_DUAL STABILITY)

CHANGE N1410 FROM EZ1085 TO IRU1030CD (DPAK)

15

47

DON’T POPULATE A1432,C1490

CHANGE R4851-R4854 INTO A4851 (RAC 33R)

CHANGE R9111 FROM 2K2K TO 1K

ADD R4856,C4851 (SIGNAL QUALITY)

ADD NEW SIGNAL : PCI_RST_IDE3V_L

ADD R6521 (470R, SIGNAL QUALITY)

ADD R1350-R1352 10R (DRIVER PERFORMANCE)

DEL A1330 (RAC), V1330 (SINGLE TR.)

CHANGE SIGNAL CPU_BOOTSEL_H --> _L

DEL V1421,V1422, A1400,A1401

CHANGE N1430,N1431,N1580 => LP2996 (V26811-B641-V40)

C2258 =>470U ALU V26803-B42-V53 (10MM)

71 DELETE C7100 (NOT REQUIRED)

REMOVE A4850/3 (PU ONLY 10MA, GOOD L-LEVEL)

85 CONNECT V8573,V8574 WITH THE CATHODE (PIN1) TO P3V3P (NOT 1V5)

SIGNAL-CHANGE AGND ->GND AT A7240/2/3/4 , C7241 (DIGITAL)

DON’T POPULATE R9900,R9901,V9900,R9915,R9918 (ONLY FOR REPAIR)

DON’T POPULATE ELKO C1451

MODIFY R1334 TO 1K62

DON’T POPULATE C4802

ADD A4700, R4702 AND RECONNECT (COST)

MODIFY R1522 FROM 1K5 5% TO 1K5 1%

91

PAR TO S4750

94

RECONNECT A4850/1 FROM P3V3P TO GND ( ENABLE BUFFER LVC125)

RECONNECT SIGNAL MON_ON_H FROM ICH GPO20(U22) TO GPO22(U20)

ADD A3180,V3180

(V26827-B470-V105)

CHANGE V1511 FROM IDP12N03L TO IDP20N03L (LOWER PRICE)

MODIFY A1550-A1557 FROM 47R TO 470R (WRONG VALUE)

EN_STPCLK_L GPO20(U22)

DELETE R6521

RECONNECT C1483/1,R1482/2,N1480/5 FROM VCC_DUAL TO L1480/2

MODIFY C1482 1U FROM Y5V TO X5R (VOLTAGE DERATING)

DEL THERMAL CONTROL CIRCUIT FOR THE CPU CORE REGULATOR

DEL GMCH-VTERM_GTL-REGULATOR REGULATOR (LP2996)

ADD CPU_BOOTSEL_L TO V1521/3

CHANGE D1900 FROM CK-409 TO CK-409-2 (REDUCE PIN-COUNT)

ADD A1901 ( NEW CPU_BSEL CONNECTION)

CHANGE R2260-R2262 TO RAC A2260

CHANGE D4850 FROM 74LVC125 TO 74LVC14 AND RECONNECT

CHANGE A4850 FROM 470R TO 220R AND RECONNECT

CHANGE R4855 FROM RSHORT TO 33R

CHANGE R4880,R4881 INTO RAC A4881

CHANGE R9152 FROM 10K TO 4K7

CHANGE V9150 FROM BCR133S TO BCR183S

ADD A9152 (470R), V9151 (BCR183S)

RECONNECT V9150,V9151,A9152

CHANGE D9110 TO EEPROM 2KX8 SPI

CONNECT D9110 PIN3 AND PIN7 WITH R9111 PIN2 (ONLY ONE PU)

CHANGE TEXT IN 10R/8=1R25 0.5W

ADD R6569 R-SHORT DON’T POPULATE

(ONLY FOR SHUTDOWN AND SOFTSTART)

MODIFY R1490 FROM 470R TO R-SHORT

MODIFY V1451 FROM SI4410 TOBSO4420 (RDSON=9MR)

DON’T POPULATE V6560,A6560,R6560,D6560 (NO PROC_HOT)

ADD R1330, V1330 (BCR119S) , SIGNAL CPU_BOOTSEL_H

NEW PCI RESET CIRCUIT

ADD D4851 74AHCT1G32 FOR IDE RESET 5V (DON’T POPULATE)

CHANGE N1020 TO V26811-B631-V40 (BETTER PERF.)

91 COMBINED R9105 AND R9106 INTO A9100

V8570-V8574, C8470-C8574

44 REPLACED R4410 WITH 2 ELEMENTS OF A4505

37 CHANGED L3826, L3856, L3855 TO L-SHORT

15 CHANGED N1500 TO LM1117-LGA8

AUDIO CHANGES

DON’T POPULATE R4700-R4702 (FOR ADJUSTMENT) ,C4700

MODIFY K7110 FROM 1N TO 270P

20 REMOVED SMEMA/B_C_ADR_H<5..1> SIGNALS

30,34 CONNECTED D3000/W4 AND A3440/7 TO LAN_CSA_PME_H

91 ADDED INVERTER FOR LAN_CSA_PME_L (V9120 AND R9120)

LAN WAKEUP FIX

DON’T POPULATE A1330,V1330,V1332 (NO CPU_BOOTSEL)

DON’T POPULATE V1521 (NO CPU_BOOTSEL)

POPULATE A7100,A7101,C7113,C7150,C7155,C7158

POPULATE R7500

MODIFY A1931 FROM 33R TO 22R , R1950 FROM 33R TO 10R

ADD SER RESISTOR 100R TO DUAL_OK_3V3_H (R3050)

MODIFY R1480,R1481 (113R,49R9) TO GET 2,61V (NEW MEMORY VOLTAGE)

REMOVED SIGNALS NECESSARY FOR THE 2DIMM/CHANNEL SOLUTION ONLY:

45 CHANGED A4505 TO 1K

47 REPLACED A4750 WITH 2 ELEMENTS OF A7250

48 CHANGED C4810 TO NOT POPULATED

91 COMBINED R9100, R9109 AND R9110 INTO A9101

91 COMBINED R9111 AND R9107 INTO A9102

71 ADDED PAPERGATE P7149 TO CONNECT AGND & GND BELOW AC97 COCEC

72 CHANGED TO NOT POPULATED: V7200, A7200, A7240, C7240-C7241

72 CHANGED TO POPULATED: R7230

72 REMOVED X7230 (SPEAKER IS ON E383 NOW)

DON’T POPULATE V1410,R1412,V1411,R1413 (NO P3V3P_DUAL SWITCH)

75 COMBINED R7500 AND R7501 INTO A7502

71 EXPANDED K7110 TO C7120-C7123; CHANGED C7120-C7121 TO NOT POP.

NOTE X8000 = V26827-B432-V225

DON’T POPULATE C8570-C8572,V8573,V8574

DON’T POPULATE R7100,C7110,C7151,C7156

ADD R7105 (100R)

ADD SER RESISTOR 100R TO POWER_OK_3V3_H (R2010)

ADD R9420-R9422 DON’T POPULATE R9421,R9422

CHANGE R9154 FROM 619R T0 590R. PERFORMANCE OF THE KINNERETH.

REMOVE OF UNNEEDED DDR SIGNALS/PARTS

27 REMOVED R2712

MODIFY C1483,C1484 FROM 100N TO 1U/X5R (TO INCR. BOOT PERF)

38 CHANGED C3829 AND C3859 TO NOT POPULATED

38 COMBINED R3821, R3822 TO A3820

38 CHANGED L3725, L3726, L3706, L3705 TO L-SHORT

37 CHANGED C3709 AND C3729 TO NOT POPULATED

14,24 CHANGED TO 1M0-M-6V3-R070: C1489, C1491, 2413

28 REMOVED R2812, A2870, R2815-R2817

10 COMBINED R1090 AND R1092 IN A1090

COST REDUCTION

14 CHANGED TO UNPOPULATED: N1430

14 CHANGED TO POPULATED: A1430 AND A1431

14 CONNECTED V_TERM_A/B_SENSE TOGETHER VIA A1431

14 CONNECTED V_TERM_A/B_SENSE TOGETHER VIA A1431 (SINGLE DDR TERM)

INTEGRATED GTL TERM REGULATOR

19 REPLACED A1580 WITH A1901 (PU FOR CPU_SOCET_OCC_L)

15 ADDED N1520, A1520, C1520-C1522, V1520, V1521, R1520-R1522

15 REMOVED C151*, C152*, R151*, R152*, N1510, V151*, V152*, A1580

SINGLE DDR TERM REGULATOR

VARIOUS CHANGES

37 REMOVED V3700

19 REMOVED C1984

91 REMOVED R9117

13 ADDED NOTE TO FOR THE RIGHT PART NUMBER OF V1300-V1311

13 CHANGED V1302, V1309 AND V1310 TO NOT POPULATED

13 CHANGED R1300, R1312, R1314 (R-SHORT) TO 5R1 (NEW FET SUPPORT)

13 CHANGED R1350, R1351, R1352 (10R) TO 5R1 (RELAYABILITY)

14 REMOVED UNNEEDED PADS: P1432-P1435, P1442 AND P1443

19 ADDED P190* TO CONNECT THE GND ISLAND BELOW THE CKLSYNT TO GND

30 REMOVED R3030 (WORKAROUND FOR EARLY ICH5 STEPPINGS)

65 CONNECTED A6550/8 TO A6550/2 INSTEAD OF A6550/7

66 ADDED V6692 AS PLACEMENT OPTION FOR V6690

80 ADDED P1V5P BULK DECOUPLING FOR AGP & ICH5 (C8027)

SCHEMATIC DATE

72 CHANGED TO NOT POPULATED: C8510, A8411, C8522, C8523,

94 REMOVED STUFFING OPTION FOR LED SIGNALLING (R9420-R9422)

16.01.03

13 ADDED C1301 (UNPOPULATED) BECAUSE OF LAYOUT RESTRICTIONS

BRASILIA

HISTORY

R1002

220R-J-W06

R1003

301R-F-W06

R1000

61R9-F-W06

R1009

61R9-F-W06

R1008

61R9-F-W06

A1080

AR2

4XS-1K0-J-W06

A1080

AR2

4XS-1K0-J-W06

A1080

AR2

4XS-1K0-J-W06

A1080

AR2

4XS-1K0-J-W06

C1011

10P-J-50V-COG-2

C1010

10P-J-50V-COG-2

C1020

1U0-Z-10V-Y5V

R1091

121R-F-W06

C1023

1U0-Z-10V-Y5V

C1005

1U0-Z-10V-Y5V

R1020

2K43-F-W06

A1060

4XS-56R-J-W06

A1060

4XS-56R-J-W06

A1060

4XS-56R-J-W06

A1060

4XS-56R-J-W06

A1061

4XS-56R-J-W06

A1061

4XS-56R-J-W06

A1061

4XS-56R-J-W06

A1061

4XS-56R-J-W06

2

3

4

5

6

7

8

9

10

VIDPWRGD

BOOTSELECT

OPTIMIZED/COMPAT

SKTOCC

12

11

ADDRESS/DATA

CONTROL

AGTL

TRANSFER

ARBITRATION

RESET

CLOCK/ERROR

VSS_SENSE

VCC_SENSE

VID<5:0>

TESTHI

TESTHI

VCC_IOPLL

VSS_A

COMP

VID GENERATION

CMOS (CPU_VCC)

DBR

PROC_HOT

BPM<5:0>

CMOS (CPU_VCC)

AP<1:0>

REQ<4:0>

ADSTB<1:0>

ADR<35:3>

DP<3:0>

D<63:0>

AGTL

RSP

TRDY

1

0

VCC_A

THRMTRIP

THERMDC

TEST

IERR

IGNNE

DRDY

DBSY

HITM

HIT

ADS

DEFER

RS<2:0>

DBI<3:0>

VCCVIDLB

A20M

RESET

STPCLK

FERR

TCK

TDOTDI

TMS

TRST

NMI/LINT1

INTR/LINT0

SMI

PWRGOOD

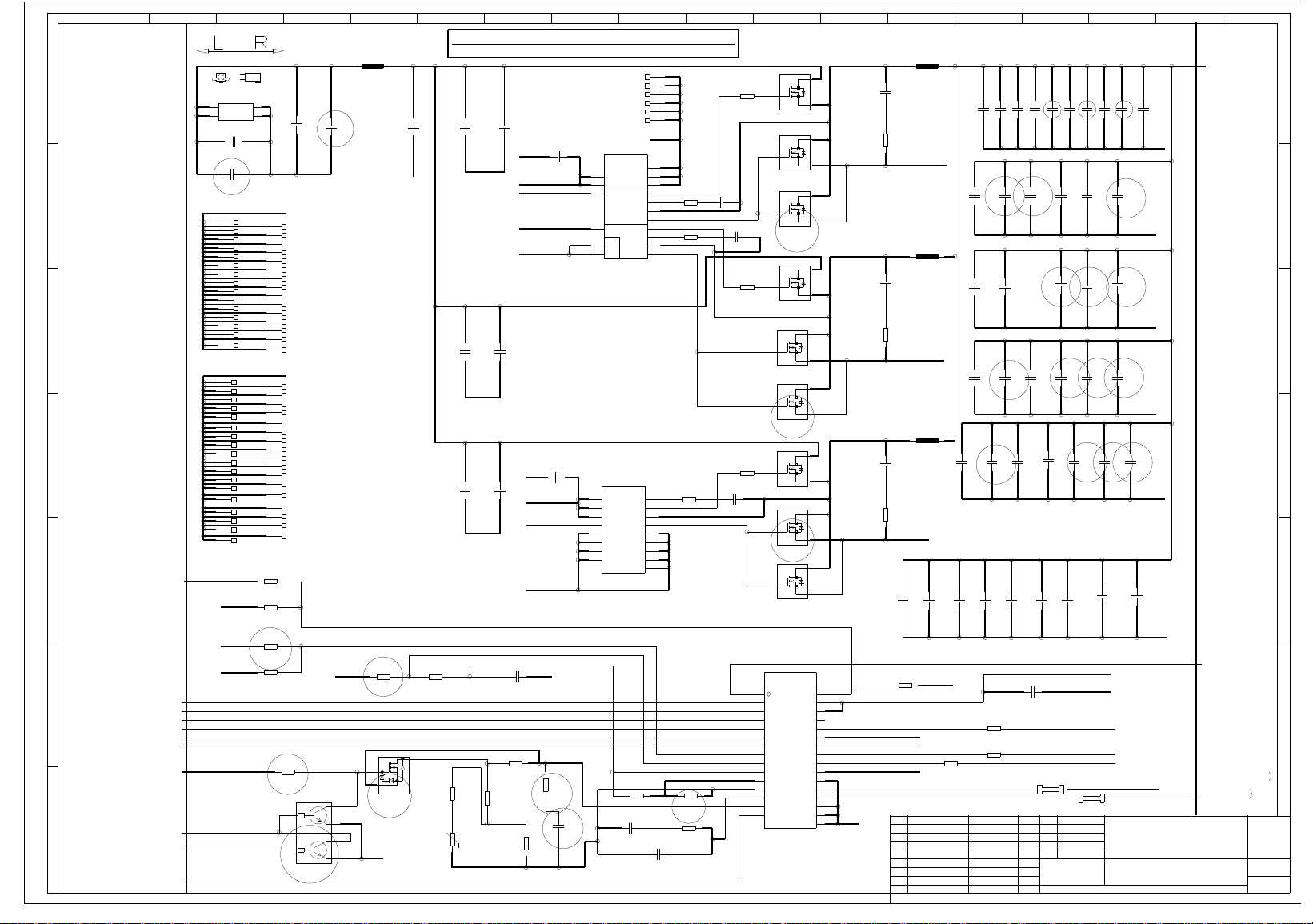

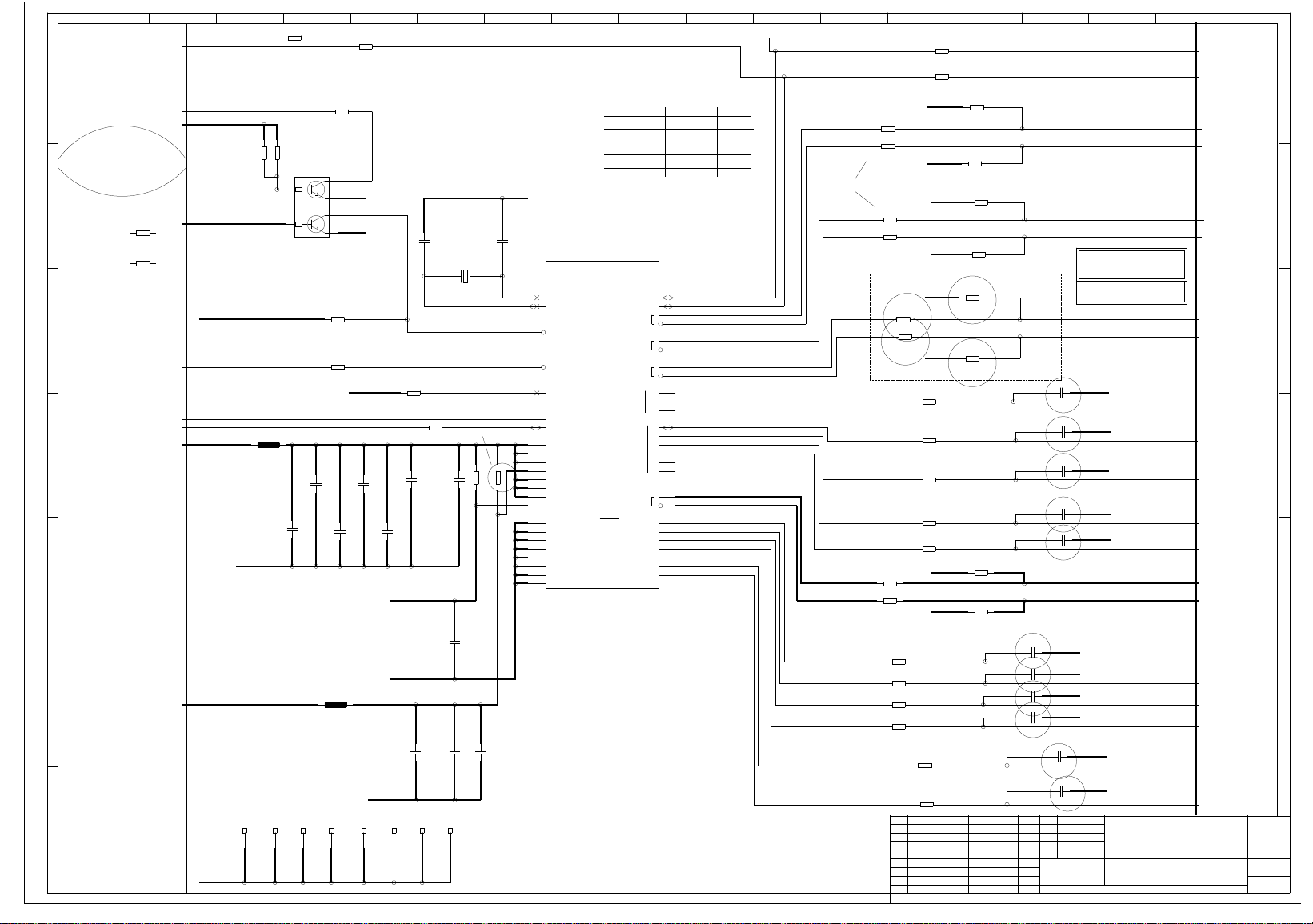

PRESCOTT

BCLK0

INIT

SLP

THERMDA

BPRI

BR0

MCERR

BINIT

BNR

LOCK

0

1

+

-

DSTB0

+

-

DSTB1

+

-

DSTB2

+

-

DSTB3

VCC_VID

ITP_CLK

0

1

0

1

BSEL

GTLREF

0

1

2

3

0

1

CV1,GND

PRESCOTT

D1000

PRESCOTT-BGA478

R1021

220R-J-W06

A1081

AR2

4XS-1K0-J-W06

A1081

AR2

4XS-1K0-J-W06

A1081

AR2

4XS-1K0-J-W06

A1081

AR2

4XS-1K0-J-W06

(1.2V)

VOUT

VIN

EN

GND

PWRGD

N1020

SN105125-SOT23

SN105125

R1095

R00-1A0

A1090

4XS-56R-J-W06

A1090

4XS-56R-J-W06

ABBREV=D1534

D1534

LAST_MODIFIED=Fri Jan 17 05:18:48 2003

DRAWING

FRAME1 VERSION 2

SACHNUMMER

NAME

DATUM

VORGANG

ZUST

18

1716151110

98

76

5

4

1413

12

3

21

D

E

C

B

A

A

B

C

D

E

F

G

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

F

NAME

GEPR.

NORM

T-NR.

DATUM

CURRENT_LOGIC

HIGHEST_LOGIC

REG_PAGE

FUJITSU

SIEMENS

COMPUTERS

S26361-D1534-X-*-11

02

02A3842

SCU

10

99

8+

POPULATE R1095 IF ONLY NWD, BECAUSE OF NO PSC SUPPORT

VID VR

30MA PEAK

1.20 V

CPU

N.C.

CPU

CPU

(0,8-1,6V)

DO NOT POPULATE R1000 IN CASE OF ONBOARD DEBUG CONNECTOR

N.C.

N.C.

N.C.

N.C.

N.C.

SCHUTZ

N.C.

CPU

ICH

CPU

N.C.

CRB0.7: F20

N.C.

PLACE NEAR CPU

PLACE AS NEAR TO THE CPU AS POSSIBLE

ICH

FOR TESTABILITY

02A3083

08.07.02

10.10.02

SCU01

08.07.02

SOCKET 478 PULLUPS

CPU

PLACE NEAR ICH5

PLACE NEAR ICH5

N.C.

N.C.

N.C.

N.C.

TP REQUIRED

TP REQUIRED

10 20

10 20 65

30 99

10 11 12 13 15 21

10 13

10 13

10 13

10 13

10 13

10

12 20

12

10

10 13 19

12

12

30

30

12

10 19 22

10 19 22

10

10

10 20

20

20

19

20

10 11 20

10 11 20

20

20

20

20

20

20

30

30

30

30

30

30

10 13

11

11

11

10

10

12

12

20

20

20

20

10 20 65

10 30

19

10 12

11

10 11

65

10 13

20

20

20

20

12

30 99

10 11 12 13 15 21

10 19 22

12

10 13

10 30

10 13

20

10 30

10 30

10 30

11

12

10 13 19

19

10 30

20

20

20

20

20

20

65

12

10 12

10 19 22

10 11

81

72

21

5

4

2

3

1

63

54

72

81

21

AD25

J6

A6

Y3

W4

U6

AB22

AA20

AC23

AD5

AD6

A4

AB2

A5

AE25

D5

AF26

C4

B3

A2

C3

B6

W22

W23

R22

P23

K22

J23

E22

E2

F21

E3

F3

H2

H5

G1

G4

G2

AA3

H6

V6

AC3

AC24

AC20

AC21

AA2

AD24

F6

F20

AA6

D2

AA21

AD20

AD22

AE23

P1

L24

AD2

AB23

AF3

AF4

AB25

AD26

AC26

C1

F7

E6

D4

AD1

Y4

AB26

B5

AF23

E5

D1

W5

B2

C6

AE26

AF22

81

72

54

63

54

63

72

81

21

21

21

21

21

21

21

63

54

72

81

21

21

21

21

21

CPU_BSEL0_H

CPU_TESTHI_G2D_H

CPU_TESTHI_G8U_H

CPU_TESTHI_G9U_H

CPU_VID_H<5..0>

CPU_BPM_L<5..0>

CPU_BSEL1_H

CPU_TESTHI_G10U_H

CPU_TDI_H

P3V3P

CPU_VID_H<0>

CPU_BSEL0_H

CPU_THERMTRIP_L

CPU_FPU_ERR_L

POWER_OK_CPU_H

GTL_BUSREQ_L

GTL_DSTB_P_L2

GND

CPU_BOOTSEL_H

GND

CPU_VID_H<1>

CPU_BOOTSEL_H

POWER_OK_CPU_H

CPU_VID_H<4>

CPU_VID_H<5>

BRASILIA

PRESCOTT CPU

CPU_VCC_A

V26811-B631-V40

VID_VCC_GD_H

GND

CPU_VCC_IOPLL

VREF_GTL

VCC_VID

CPU_BPM_L<5..0>

GTL_DBI_L<3..0>

GTL_HIT_L

GTL_HIT_MODI_L

GTL_DATA_L<63..0>

COMP0_GTL_CPU

THRM_DIODE_NEG

CPU_SOCKET_OCC_L

CPU_FPU_ERR_L

CPU_THERMTRIP_L

CLK_100_CPU_L

CLK_100_CPU_H

VCC_CPUCORE

GND

GND

VCC_CPUCORE

C

C

5

4

3

1

2

0

CPU_TESTHI_G2D_H

CPU_TESTHI_G4U_H

CPU_TDO_H

THRM_DIODE_POS

CPU_PROC_HOT_L

GTL_DSTB_N_L3

GTL_DSTB_P_L3

GTL_DSTB_N_L2

GTL_DSTB_N_L1

GTL_DSTB_P_L1

GTL_DSTB_N_L0

GTL_DSTB_P_L0

GTL_DATRDY_L

GTL_DATBSY_L

GTL_BUSLOCK_L

GTL_BLOCKNR_L

CPU_VSS_A

COMP1_GTL_CPU

VID_VCC_GD_H

CPU_TMS_H

CPU_TRST_L

CPU_TCK_H

CPU_STOPCLK_L

CPU_SMI_L

CPU_NMI_H

CPU_INTR_H

CPU_INIT_L

CPU_IGNNE_L

CPU_A20MASK_L

GTL_CMD_L<4..0>

GTL_ADRSTB_L<1..0>

GTL_ADR_L<35..3>

NO_SINGLE_CHECK=ON

GTL_TRDY_L

GTL_DEFER_L

GTL_RESET_L

CV1=VCC_CPUCORE

GTL_PRIREQ_L

GTL_BUSREQ_L

GTL_RESP_L<2..0>

GTL_ADS_L

CPU_VID_H<2>

CPU_SLEEP_L

GND

COMP0_GTL_CPU

COMP1_GTL_CPU

P3V3P

GND

VCC_VID

GTL_RESET_L

CPU_VID_H<3>

CPU_TESTHI_G4D_H

CPU_BSEL1_H

CPU_TESTHI_G1D_H

CPU_PROC_HOT_L

CPU_TESTHI_G1U_H

GND

R1110

R00-1A0

TDO

POWERON

GND

FBI

TCK

TRSTN

TMS

TDI

GND

DBRESET#

BSEN#

GND

BP[3]#/OA[3]#

BP[2]#/OA[2]#

PM[0]#/OA[0]#

GND

BCLK REF

PREQ0#

BCLK

FBO

RESET#

PREQ0#

PRDY#

PM[1]#/OA[1]#

GND

C

25

26

2

1

18

1

24

C

22

20

14

16

10

8

6

4

2

25

23

21

19

17

15

13

11

9

7

5

3

12

XB482-V26

X1100

STSMT11-026

R1100

27R-J-W06

R1102

39R2-F-W06

R1103

51R1-F-W06

R1101

680R-J-W06

R1104

150R-F-W06

R1105

39R2-F-W06

R1112

1K5-J-W06

R1113

150R-F-W06

FRAME1 VERSION 2

SACHNUMMER

NAME

DATUM

VORGANG

ZUST

18

1716151110

98

76

5

4

1413

12

3

21

D

E

C

B

A

A

B

C

D

E

F

G

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

F

NAME

GEPR.

NORM

T-NR.

DATUM

CURRENT_LOGIC

HIGHEST_LOGIC

REG_PAGE

FUJITSU

SIEMENS

COMPUTERS

S26361-D1534-X-*-11

02

02A3842

SCU

11

99

9+

ABBREV=D1534

TITLE=D1534

LAST_MODIFIED=Fri Jan 17 05:28:48 2003

DRAWING

PLACE NEAR CPU

R1100 REC. 27R4

PLACE NEAR CPU

ALWAYS POPULATE

TDO NOT REQUIRED WITHOUT ITP

N.C.

N.C.

= DON’T POPULATE

08.07.02

SCHUTZ

ITP700 TEST PORT

ROUTE TCK TO CPU AND BACK TO FBO PIN17 AT CONNECTOR

(5%)

BRASILIA

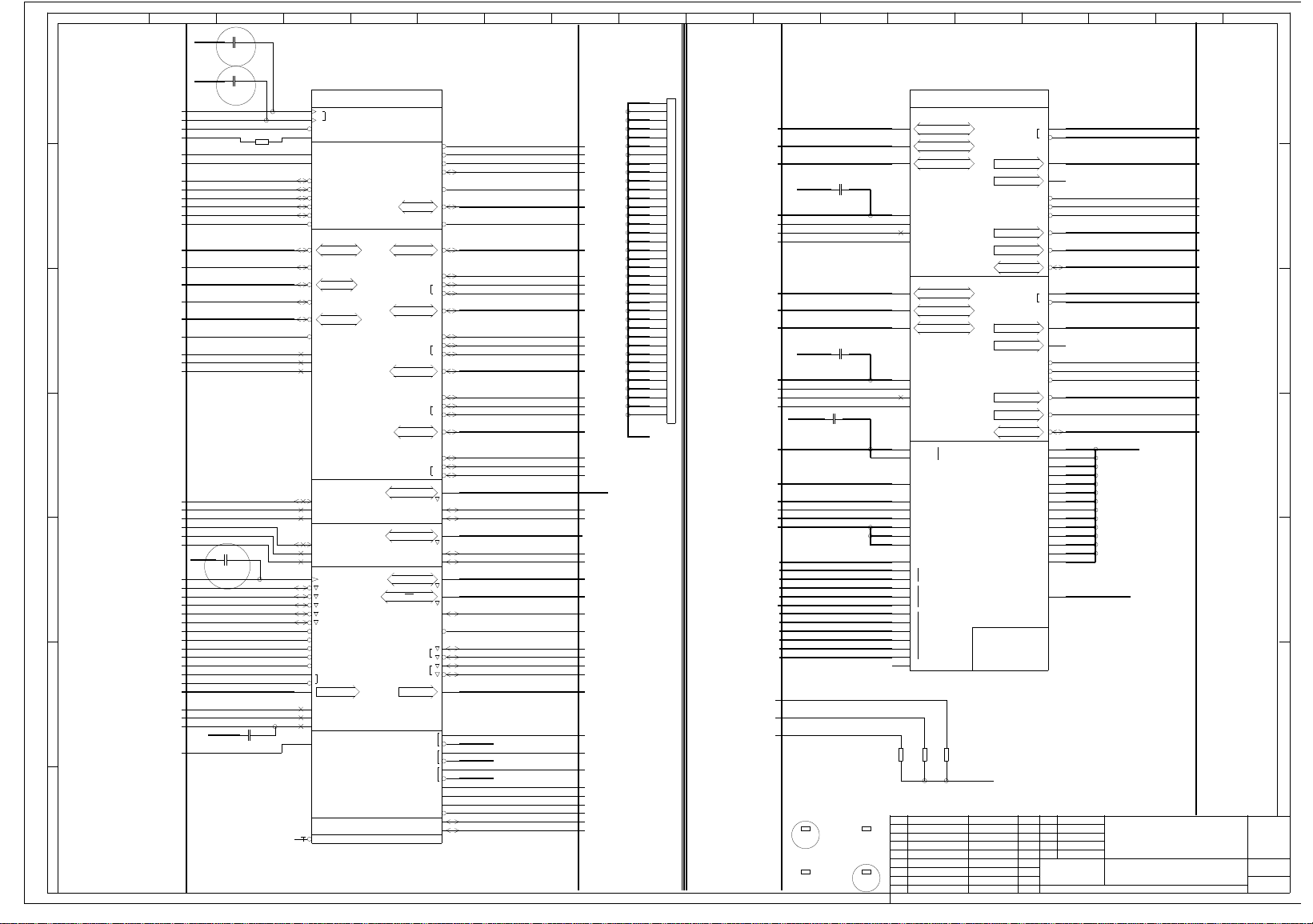

10 11

10 20

11

10 11

19

10

10

11

10

10

10

10

30 47 65

10 11

10 11

10 11

10 11

10 11

10 11

10 11 12 13 15 21 30 99

19

10 11

10 11

10 11

11

30 99

10 11 12 13 15 21

21

21

21

21

21

21

21

9

87

65

43

25

2423

2221

20

2

19

1817

1615

1413

1211

10

1

21

21

ITP

CPU_TCK_H

CPU_TMS_H

CPU_TDI_H

CPU_TDO_H

CLK_HOST_ITP_L

V26827-B482-V126

ITP_POWERGOOD_H

CPU_BPM_L<0>

CPU_BPM_L<1>

CPU_BPM_L<4>

CPU_BPM_L<5>

ITP_RESET_L

VCC_CPUCORE

GND

CPU_TDO_H

CPU_TDI_H

CPU_TMS_H

CPU_TRST_L

CPU_TCK_H

CPU_TCK_H

VCC_CPUCORE

GND

GND

R

R

CLK_HOST_ITP_H

BUTTON_RST_L

GTL_RESET_L ITP_RESET_L

CPU_TRST_L

NO_POWER_PINS

CPU_BPM_L<2>

CPU_BPM_L<3>

ITP_RESET_L

C1235

47P-J-50V-COG

C1232

22P-J-50V-COG

C1231

22P-J-50V-COG

C1238

47P-J-50V-COG

C1237

47P-J-50V-COG

C1236

47P-J-50V-COG

C1233

22P-J-50V-COG

R1211

169R-F-W06

A1220

AR2

4XS-56R-J-W06

A1220

AR2

4XS-56R-J-W06

A1220

AR2

4XS-56R-J-W06

A1220

AR2

4XS-56R-J-W06

A1221

AR2

4XS-56R-J-W06

A1221

AR2

4XS-56R-J-W06

A1221

AR2

4XS-56R-J-W06

A1221

AR2

4XS-56R-J-W06

C1212

100N-Z-25V-Y5V

L1200

10U-A06-R65

L1

L1201

10U-A06-R65

L1

R1210

200R-F-W06

C1230

22P-J-50V-COG

C1210

100N-Z-25V-Y5V

C1211

100N-Z-25V-Y5V

R1220

61R9-F-W06

C1200

1U0-Z-10V-Y5V

C1201

+

C1202

33U-M-6V3

ELKO

R1212

200R-F-W06

P1200

PAPERGATE

PAPERGATE

SACHNUMMER

FUJITSU

SIEMENS

COMPUTERS

REG_PAGE

VORGANG

HIGHEST_LOGIC

CURRENT_LOGIC

FRAME1 VERSION 1

NAME

DATUM

ZUST

18

1716151110

98

76

5

4

1413

12

3

21

D

E

C

B

A

A

B

C

D

E

F

G

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

F

NAME

GEPR.

NORM

T-NR.

DATUM

S26361-D1534-X-*-11

02

02A3842

SCU

12

99

10+

ABBREV=D1534

D1534

LAST_MODIFIED=Fri Jan 17 05:28:49 2003

DRAWING

EMI C’S

PLACE NEAR CPU PIN

08.07.02

SCHUTZ

REC. 62R

PDG: 220P

PLACE NEAR MCH PIN

100MA

ESR<0R3

ESL<5NH

10UH 60MA

BRASILIA

10

10 12 20

10 11 12 13 15 21 30 99

10

10 11 12 13 15 21 30 99

10 11 12 13 15 21 30 99

10

10

10

10

10

10

10

10

10 11 12 13 15 21 30 99

10 12 20

15 19 21

10

21

21

2 1

21 21

21

21

21

21

21

21

21

21

21

21

21

21

21

54

72

63

81

81

72

63

54

21

2

1

21

CPU SUPPORT

VTERM_GTL

0.7

CPU_TESTHI_G1D_H

CPU_TESTHI_G4D_H

GND

V26803-B73-V2V26803-B73-V2

VREF_GTL

VCC_CPUCORE

V26803-B54-V121

CPU_TESTHI_G1U_H

CPU_TESTHI_G8U_H

VCC_CPUCORE

CPU_TESTHI_G2D_H

CPU_TESTHI_G9U_H

GND

CPU_TESTHI_G10U_H

C

VCC_CPUCORE

VREF_GTL

CPU_TESTHI_G4U_H

CPU_VSS_A

CPU_VCC_A

CPU_VCC_IOPLL

GND

VCC_CPUCORE

C

C

C

C

C

C

C

C1306

1U0-Z-16V-Y5V

C1345

10U-M-6V3-X5R

C1344

10U-M-6V3-X5R

C1343

10U-M-6V3-X5R

C1342

10U-M-6V3-X5R

C1341

10U-M-6V3-X5R

C1340

10U-M-6V3-X5R

L1310

U86-23A-IO-258

L1

P48

P46

P44

P43

P49

P47

P45

P51

P50

P25

P27

P29

P31

P33

P37

P35

P24

P26

P32

P36

P34

P28

P30

L1302

U86-23A-IO-258

L1

C1328

1U0-Z-16V-Y5V

C1334

100N-K-16V-X7R

C1337

1U0-Z-16V-Y5V

L1303

U86-23A-IO-258

L1

C1321

1U0-Z-16V-Y5V

C1333

330P-J-50V-COG-2

C1331

10N-K-50V-X7R-2

R1303

49R9-F-W06

R1337

6K2-F-W06

R1308

130K-F-W06

C1332

1U-K-10V-X5R

C1364

10U-M-6V3-X5R

C1363

10U-M-6V3-X5R

C1362

10U-M-6V3-X5R

C1361

10U-M-6V3-X5R

C1360

10U-M-6V3-X5R

C1359

10U-M-6V3-X5R

C1358

10U-M-6V3-X5R

C1352

10U-M-6V3-X5R

C1353

10U-M-6V3-X5R

C1354

10U-M-6V3-X5R

C1355

10U-M-6V3-X5R

C1356

10U-M-6V3-X5R

C1357

10U-M-6V3-X5R

C1347

10U-M-6V3-X5R

C1346

10U-M-6V3-X5R

C1349

10U-M-6V3-X5R

C1350

10U-M-6V3-X5R

C1351

10U-M-6V3-X5R

C1336

1U0-Z-16V-Y5V

+

C1300

1M5-M-16V-R018

ELKO

P1309

P1307

P1310

P1329

P1327

P1328

P1308

P1306

P1305

P1325

P1326

P1304

P1303

P1302

P1321

P1323

P1322

P1324

P1318

P1337

P1336

P1317

P1335

P1316

P1313

P1315

P1314

P1312

P1311

P1332

P1333

P1334

P1331

P1330

+

C1384

2M2-M-6V3-R015

123

4

3

1 2

4

X1300

DIVST051-004

XB406-V104

C1398

C1399

100N-Z-25V-Y5V

+

C1317

2M2-M-6V3-R015

+

C1316

2M2-M-6V3-R015

+

C1315

2M2-M-6V3-R015

+

C1314

1M5-M-6V3-R026

+

C1318

1M5-M-6V3-R026

+

C1380

2M2-M-6V3-R015

+

C1383

1M5-M-6V3-R026

+

C1382

2M2-M-6V3-R015

+

C1381

1M5-M-6V3-R026

C1390

10U-M-6V3-X5R

C1391

10U-M-6V3-X5R

C1392

10U-M-6V3-X5R

C1393

10U-M-6V3-X5R

R1307

15K-J-W06

C1397

22N-K-25V-X7R

L1301

1U3-8A-IO-261

L1

C1396

10U-M-6V3-X5R

C1394

10U-M-6V3-X5R

C1395

10U-M-6V3-X5R

R1304

27K-F-W06

C1378

10U-M-6V3-X5R

C1376

10U-M-6V3-X5R

C1312

1N0-K-50V-X7R-2

R1315

3R3-J-W10

C1311

1N0-K-50V-X7R-2

R1318

3R3-J-W10

R1310

3R3-J-W10

C1310

1N0-K-50V-X7R-2

R1322

2K0-F-W06

R1323

2K0-F-W06

R1321

2K0-F-W06

P59

P56

P57

P58

P53

P54

P55

P52

C1325

100N-K-16V-X7R

D

S

G

V1306

IPD04N03L

FETN3P-3

D

S

G

V1308

IPD04N03L

FETN3P-3

D

S

G

V1300

IPD04N03L

FETN3P-3

D

S

G

V1311

IPD04N03L

FETN3P-3

D

S

G

V1309

IPD04N03L

FETN3P-3

D

S

G

V1310

IPD04N03L

FETN3P-3

D

S

G

V1302

IPD04N03L

FETN3P-3

D

S

G

V1301

IPD04N03L

FETN3P-3

D

S

G

V1307

IPD04N03L

FETN3P-3

+

C1329

1M5-M-16V-R018

ELKO

+

C1322

1M5-M-16V-R018

ELKO

+

C1304

1M5-M-16V-R018

ELKO

P1350

P1351

P1352

P1353

P1354

P1355

C1324

100N-K-16V-X7R

BOOT1

UGATE1

PVCC

VCC

PHASE1

LGATE1

PGND

NC

NC

HIP6602BCR

PGNDTAB

PWM2

BOOT2

UGATE2

PHASE2

LGATE2

GND

PWM1

N1305

HIP6602BCR-LGA16

HIP6602BCR

LVCC

NC

NC

NC

NC

PGND

NC

NC

GNDTAB

GND

LGATE

PHASE

VCC

PVCC

UGATE

BOOT

PWM

HIP6604

N1302

HIP6604BCR-LGA16

HIP6604BCR

GNDTAB

GND

GND

VSEN

ENLL

RGND

VDIFF

COMP

FB

VID2

VID3

ISEN3

ISEN1

ISEN4

VCC

PWM4

FS

DAC

VID4

PGOOD

EN

ISL6556ACR

VID1

OVP

PWM3

GND

OFSOUT

REF

VID0

OFS

ISEN2

VID12.5

PWM1

PWM2

ISL6556ACR

N1303

ISL6556-LGA32

R1336

750R-F-W06

R1334

1K62-F-W06

C1330

470P-J-50V-COG-2

R1335

2K43-F-W06

R1332

1K0-F-W06

R1309

1K0-F-W06

R1301

12K-F-W06

R1302

1K62-F-W06

R1333

R-RT

NTC-6K8-J

+

C1305

1M5-M-16V-R018

ELKO

R1338

750R-F-W06

D

S

G

V1332

BSH112-SOT23

FETN3P-5

R1339

R00-1A0

R1344

R00-1A0

R1350

5R1-J-W06

R1351

5R1-J-W06

R1352

5R1-J-W06

R1330

10K-J-W06

4K7

4K7

V1330

BCR119S-SOT363

T-NPN-BCR119S

+

C1301

47U-M-16V

ELKO

R1300

5R1-J-W10

R1312

5R1-J-W10

R1314

5R1-J-W10

P1340

PAPERGATE

P1341

PAPERGATE

SACHNUMMER

FUJITSU

SIEMENS

COMPUTERS

REG_PAGE

VORGANG

HIGHEST_LOGIC

CURRENT_LOGIC

FRAME1 VERSION 1

NAME

DATUM

ZUST

18

1716151110

98

76

5

4

1413

12

3

21

D

E

C

B

A

A

B

C

D

E

F

G

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

F

NAME

GEPR.

NORM

T-NR.

DATUM

S26361-D1534-X-*-11

02

02A3842

SCU

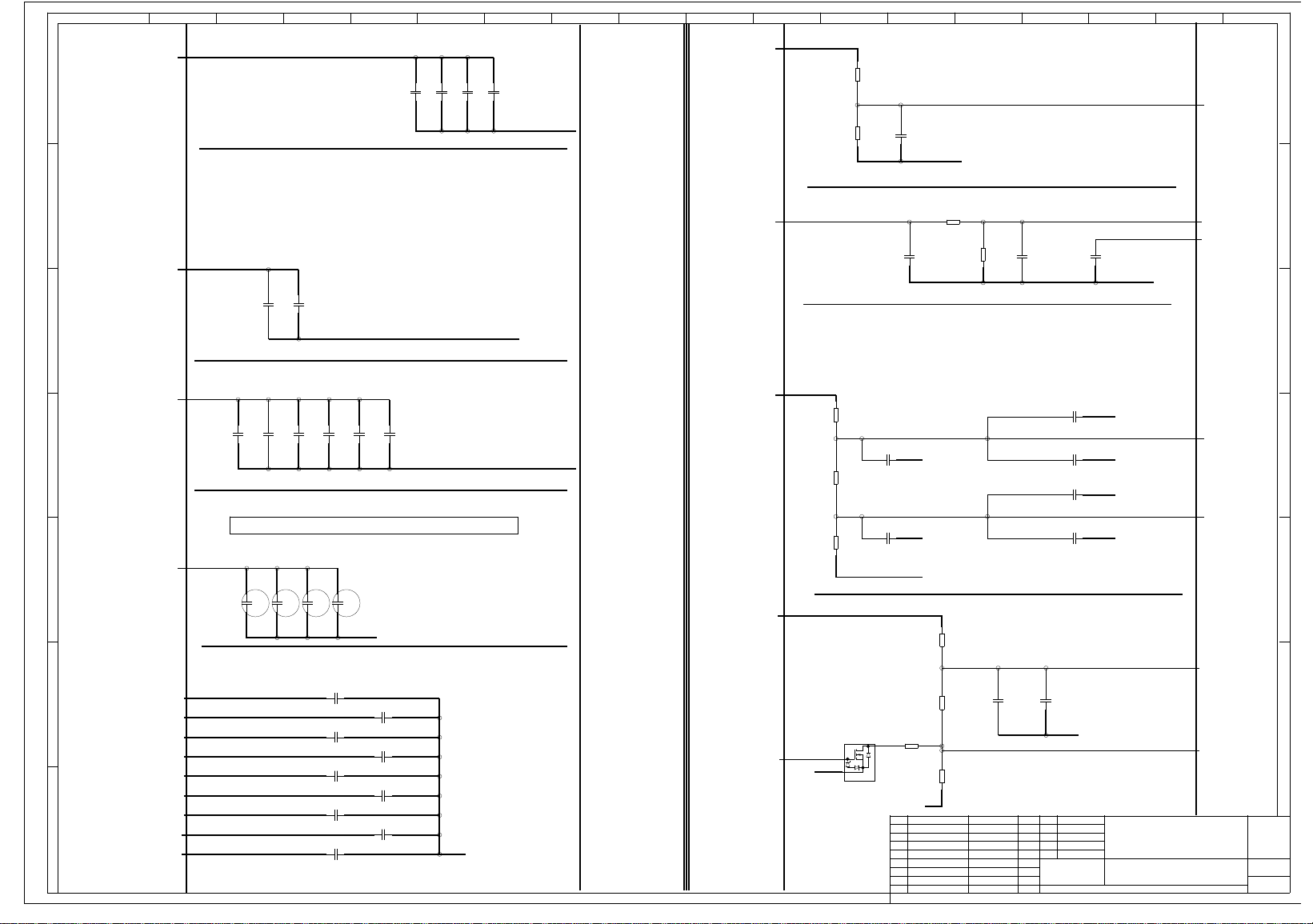

13

99

11+

D1534

Fri Jan 17 05:28:49 2003

DRAWING

C1313 REMOVED

FOR NWD-CPU= V26810-B789-V40

V1300, V1306, V1308:

V1301, V1307, V1311:

FOR NWD-CPU= V26810-B785-V40

NC

ALU ELKO

V1330, V1332 AND R1330 ONLY NECESSARY FOR PRESCOTT SUPPORT

(OUTPUT)

2K2 PU ON PG.15

FROM CPU

L=NW

H=PC

NC

20.09.02

68A/78A

LOW ESR NECESSARY

SOCKET

DIE

33MOHM

BRASILIA

13 43 53 66

15

10 19

10

10

10

13 43 53 66

15

10

10

10

10

30 99

10 11 12 13 15 21

30 99

10 11 12 13 15 21

21

21

21

21

21

2 1

4

3

1

6

5

2

21

21

21

21

21 21

D

S

G

2 1

2 1

21

21

21

21

21

21

21

21

21

6

4

5

3

2

1

33

29

26

2532

24

23

19

20

21

22

17

16

15

14

31

13

28

1827

12

11

10

9

8

7

30

2

12

8

6

1

3

9

10

17

15

13

5

4

7

14

16

11

13

11

12

1

4

16

15

14

5

8

17

6

7

10

9

2

3

21

1

1

1

1

1

1

2 12 12 1

S

D

G

S

D

G

S

D

G

S

D

G

S

D

G

S

D

G

S

D

G

S

D

G

S

D

G

21

1

1

1

1

1

1

1

1

21

21

21

21

2

1

21 2121 21

21

21

21

212121

21

2121

21

21

21

21

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

21

21

4

3

2

1

2 1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2 1

2 1

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

21

2 1

21

21

21

21

21

21

2 1

2 1

21

21

2 1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2 1

21

21

21

21

21

21

21

GND

GND

V26803-B42-V51

V26813-B1051-V1

V26803-B82-V5

V26801-B71-V7

V26803-B51-V8

V26813-B1055-V1

GND

V26803-B90-V1

GND

GND

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

C

V26803-B90-V1

C

V26803-B90-V1

C

C

V26803-B90-V1

C

V26810-B773-V40

0.7

0.7

VCC_CPUCORE

GND

SKORDEV

CPU CORE VOLTAGE REG.

GND

V26803-B42-V50V26803-B42-V50

CPU_BOOTSEL_L

CPU_BOOTSEL_H

GND

P12VP_CORE

GND

VCC_CPUCORE

P12VP_PHASE_1

P12VP_PHASE_2

P12VP_PHASE_3

P12VP_PHASE_3

GND

VCC

GND

GND

P12VP_FILTER

P12VP_CORE

GND

GND

PWM3_H

GND

PWM2_H

PWM1_H

GND

GND

GND

GND

GND

GND

P12VP_CORE

GND

GND

P12VP_PHASE_2

P12VP_PHASE_1

GND

GND

GND

PWM3_H

PWM2_H

PWM1_H

VCC

GND

VRM_PWR_OK_H

CPU_VID_H<4>

CPU_VID_H<3>

CPU_VID_H<2>

CPU_VID_H<1>

V26810-B583-V3

V26813-B1055-V1

C C

C

C

C

V26803-B90-V1

CCC

C

C

C

P12VP_FILTER

P12VP_CORE

VID_VCC_GD_H

CPU_VID_H<5>

CPU_VID_H<0>

V26813-B1055-V1

V26803-B42-V50

GND

P12VP_CORE

V26803-B42-V50

GND

V26803-B42-V50

A1441

AR2

4XS-4K7-J-W06

AR2

AR2

AR2

R1421

24R9-F-W06

R1420

121R-F-W06

C1422

1U0-Z-10V-Y5V

C1421

100N-Z-25V-Y5V

+

C1451

1M5-M-6V3-R026

ELKO

+

C1433

1M0-M-6V3-R070

ELKO

+

C1434

1M0-M-6V3-R070

ELKO

C1410

1U0-Z-16V-Y5V

C1411

1U0-Z-10V-Y5V

+

C1413

680U-M-6V3-R170

ELKO

R1410

200R-F-W06

C1417

100N-Z-25V-Y5V

R1411

121R-F-W06

P1413

P1415

P1414

P1412

P1411

P1410

PAD

PAD_0.70

P1431

P1430

PAD

PAD_0.70

P1439

P1438

P1437

P1436

PAD

PAD_0.70

SENSE

VOUT_TAB

VPWR

VOUT

VCTRL

ADJ

N1420

FAN1581M-DDPAK2

FAN1581M

C1423

1U0-Z-10V-Y5V

D

S

G

V1450

BSL211SP-TSO6

BSL211SP

V1410

SI4410DY-SO8

FETN8P

R1413

2K2-J-W06

R1412

10K-J-W06

V1411

BC846B

T-NPN

C1426

1U0-Z-10V-Y5V

R1422

121R-F-W06

R1423

113R-F-W06

SENSE

VOUT_TAB

VPWR

VOUT

VCTRL

ADJ

N1421

FAN1581M-DDPAK2

FAN1581M

C1427

1U0-Z-10V-Y5V

C1425

100N-Z-25V-Y5V

C1424

1U0-Z-10V-Y5V

P1423

PAD

P1424

PAD

P1441

P1440

A1430

AR2

4XS-0R-J-W06

R1430

R00-1A0

R1431

R00-1A0

R1432

R00-1A0

A1431

AR2

4XS-0R-J-W06

+

C1450

100U-M-6V3-R440

ELKO

A1432

A1432

AR2

4XS-10K-J-W06

C1436

1U0-Z-10V-Y5V

C1435

C1437

1U0-Z-10V-Y5V

C1438

1U0-Z-10V-Y5V

D

S

G

V1482

IPD20N03L

FETN3P-3

L1480

1U3-8A-IO-261

L1

L1481

IO-241-002

L1

VCC

ISL6520A

COMP/OCSET

FB GND

BOOT

UGATE

PHASE

LGATE

N1480

ISL6520A-SO8

ISL6520A

R1483

R00-1A0

C1486

470P-J-50V-COG-2

C1485

10N-K-50V-X7R-2

R1485

10K-J-W06

C1484

1U-K-10V-X5R

C1480

4U7-Z-16V-Y5V

C1483

1U-K-10V-X5R

C1487

1N0-K-50V-X7R-2

R1487

3R3-J-W10

+

C1481

2M2-M-6V3-R015

ELKO

R1482

27K-F-W06

R1481

1K8-F-W06

R1480

3K92-F-W06

R1484

1K0-J-W06

C1482

1U-K-10V-X5R

P1480

PAD_0.70

C1488

1U0-Z-10V-Y5V

P1482

P1483

P1487

P1486

P1485

P1484

PAD_0.70

P1493

P1492

P1491

P1490

PAD_0.70

V1480

D

BAT165

+

C1428

1M0-M-6V3-R070

ELKO

C1490

1U-K-10V-X5R

P1451

PAPERGATE

PAPERGATE

P1450

PAPERGATE

PAPERGATE

10K

10K

10K

10K

V1441

BCR133S-SOT363

T-NPN-BCR133S

10K

10K

10K

10K

V1483

BCR133S-SOT363

T-NPN-BCR133S

10K

10K

10K

10K

V1490

BCR133S-SOT363

T-NPN-BCR133S

D

S

G

V1481

IPD12N03L

FETN3P-3

+

C1429

22U-M-10V-2

ELKO

S

D

G

V1451

BSO4420-SO8

BSO4420

R1490

R-SHORT

R-SHORT-C0603

VDDQ

LP2996

AVIN

GND

VREF

VSENSE

VTT

PVIN

SD/NC

THRMPAD

VTT

PVIN

N1430

LP2996-LGA16

LP2996

VDDQ

LP2996

AVIN

GND

VREF

VSENSE

VTT

PVIN

SD/NC

THRMPAD

VTT

PVIN

N1431

LP2996-LGA16

LP2996

+VIN

ADJ

+VOUT

+VOLTAGE

REGULATOR

CASE

N1410

EZ1085CM

EZ1085

+

C1489

1M0-M-6V3-R070

ELKO

+

C1491

1M0-M-6V3-R070

ELKO

ABBREV=D1534

TITLE=D1534

LAST_MODIFIED=Fri Jan 17 05:28:50 2003

DRAWING

SACHNUMMER

FUJITSU

SIEMENS

COMPUTERS

REG_PAGE

VORGANG

HIGHEST_LOGIC

CURRENT_LOGIC

FRAME1 VERSION 1

NAME

DATUM

ZUST

18

1716151110

98

76

5

4

1413

12

3

21

D

E

C

B

A

A

B

C

D

E

F

G

WEITERGABE SOWIE VERVIELFAELTIGUNG DIESER UNTERLAGE, VERWERTUNG UND

MITTEILUNG IHRES INHALTS NICHT GESTATTET, SOWEIT NICHT AUSDRUECKLICH

ZUGESTANDEN. ZUWIDERHANDLUNGEN VERPFLICHTEN ZU SCHADENERSATZ. ALLE

RECHTE FUER DEN FALL DER PATENTERTEILUNG ODER GM-EINTRAGUNG VORBEHALTEN.

COPYING OF THIS DOCUMENT, AND GIVING IT TO OTHERS AND THE USE OR COMMUNICATION

OF THE CONTENTS THEREOF, ARE FORBIDDEN WITHOUT EXPRESS AUTHORITY. OFFENDERS

ARE LIABLE TO THE PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT

OF THE GRANT OF A PATENT OR THE REGISTRATION OF A UTILITY MODEL OR DESIGN.

F

NAME

GEPR.

NORM

T-NR.

DATUM

S26361-D1534-X-*-11

02

02A3842

SCU

14

99

12+

3.3 VOLT DUAL REGULATOR

=13MR

ON

RDS

MAX HEATSINK

POPULATE EITHER N1410 OR N1411

KUEHLFLAECHE MAXIMIEREN

KUEHLFLAECHE MAXIMIEREN

=9MR

5 VOLT

2.5 VOLT

MIN. LOAD

P3V3P: 0,3A

VCC: 0,3A

CH A

DUAL CONTROL

CH B

DUAL SWITCH

VIH=2,4V

10A NOM.

14A PEAK

RDS

SKORDEV

20.09.02

ON

DUAL REGULATOR

SOFT-START

470R

DON’T POPULATE IF LP2996

1.25 VOLT REGULATOR

1.5 VOLT MCH REGULATOR

VIH=2,4V

2,61V

BRASILIA

25

14 15 19 21 22 24

25

14

14 15 19 21 22 24 25

27

30 47

14

14 15 19 21 22 24 25

48

14 30 37 38 65

14

14

14 30 37 38 65

14 48

24

43 48 65 71 80

48

19 30

14

14

14 48

14 15 19 21 22 24 25

14 30 37 38 65

14

14 30 37 38 65

14

85

15 20 21 22 30 31 35 80

90 91 92

38 40 47 48 53 65 66 80

19 24 25 30 31 34 35 37

28

2 1

2 1

4

2

1

3

15

14

5

7

2

12

11

10

4

17

8

15

14

5

7

2

12

11

10

4

17

8

21

3

2

1

8

7

6

5

4

2 1

S

D

G

4

3

1

6

5

2

4

3

1

6

5

2

4

3

1

6

5

2

21

21

21

2 1

A K

111

1

111

1 1

1

1

2 1

1

21

21

212

1

2

1

21

21

2 1

21

21

21

21

2 1

2 1

21

8

7

6

5 4

3

2

1

21

21

S

D

G

2 1

2 1

2 1

2 1

54

72

8 1

63

2 1

816372

54

21

21

21

546372

81

1

1

1

1

2 1

21

2 1

2

1

6

3

5

4

21

2

1

2 1

C

B

E

21

21

8

7

6

5

3

2

1

4

6

5

2

1

4

3

2 1

2

1

6

3

5

4

111

1

1

1

111

111

21

2 1

21

2 1

2 1

2 1

2 1

2 1

2 1

21

2 1

2121

635472

81

V26803-B42-V37

REF_LP2995

V26803-B42-V52

V26803-B42-V52

V_TERM_B_1V25

0.3

V26810-B304-V40

EN_AUX_L

P3V3P

V26803-B42-V52

V26803-B42-V52

V_TERM_B_SENSE

V26810-B755-V50

P2V5P_DUAL

V_TERM_A_SENSE

0.3

SD_2996_L

VCC_DUAL

P3V3P

GND

P2V4P

VCC

V26803-B73-V8

V26803-B54-V112

V26811-B419-V40

P3V3P_DUAL

VCC

V26811-B641-V40

V26811-B641-V40

P2V5P_DUAL

VCC_DUAL_FILTER

V26803-B82-V9

GND

VCC_DUAL

V26810-B768-V50

V26803-B42-V52

V26803-B82-V8

V26810-B772-V40

GND

SLEEP_S3-S5_L

PWR_GD_3V3_L

GND

PS_ON_L

GND

EN_AUX_L

P12VP

GND

GND

VCC_DUAL

VCC_AUX

GND

P2V5P_DUAL

GND

P3V3P

GND

GND

GND

P1V5P

GND

VCC

GND

V_TERM_A_1V25

VREF_SMEMB

GND

REF_LP2995

GND

GND

GND

EN_P3V3P_DUAL_H

P2V4P

VREF_SMEMA

VCC_DUAL

V26803-B42-V51

VOLTAGE REGULATORS

EN_AUX_L

V26810-B774-V40

GND

GND

SLEEP_S4-S5_L

P2V5P_DUAL

PWR_GD_3V3_L

EN_AUX_L

GND

A1555

AR2

4XS-470R-J-W06

A1555

AR2

4XS-470R-J-W06

A1555

AR2

4XS-470R-J-W06

A1554

AR2

4XS-470R-J-W06

A1554

AR2

4XS-470R-J-W06

A1554

AR2

4XS-470R-J-W06

A1554

AR2

4XS-470R-J-W06

A1553

AR2

4XS-470R-J-W06

A1553

AR2

4XS-470R-J-W06

A1553

AR2

4XS-470R-J-W06

A1553

AR2

4XS-470R-J-W06

A1552

AR2

4XS-470R-J-W06

A1552

AR2

4XS-470R-J-W06

A1552

AR2

4XS-470R-J-W06

A1552

AR2

4XS-470R-J-W06

A1551

AR2

4XS-470R-J-W06

A1551

AR2

4XS-470R-J-W06

A1551

AR2

4XS-470R-J-W06

A1551

AR2

4XS-470R-J-W06

A1556

AR2

4XS-470R-J-W06

A1556

AR2

4XS-470R-J-W06

A1556

AR2

4XS-470R-J-W06

A1557

AR2

4XS-470R-J-W06

A1557

AR2

4XS-470R-J-W06

A1557

AR2

4XS-470R-J-W06

A1557

AR2

4XS-470R-J-W06

A1550

AR2

4XS-470R-J-W06

A1550

AR2

4XS-470R-J-W06

A1550

AR2

4XS-470R-J-W06

A1550

AR2

4XS-470R-J-W06

A1556

AR2

4XS-470R-J-W06

A1555

AR2

4XS-470R-J-W06

C1502

1U0-Z-10V-Y5V

R1500

121R-F-W06

C1500

1U0-Z-10V-Y5V

R1501

43R2-F-W06

C1501

100N-Z-25V-Y5V

+

C1503

22U-M-10V-2

ELKO

R1502

R00-1A0

R1521

2K0-F-W06

C1521

1U0-Z-16V-Y5V

A1560

AR2

4XS-0R-J-W06

A1520

AR2

4XS-2K2-J-W06

10K

10K

10K

10K

V1520

BCR133S-SOT363

T-NPN-BCR133S

A1520

AR2

4XS-2K2-J-W06

A1520

AR2

4XS-2K2-J-W06

VDDQ

LP2996

AVIN

GND

VREF

VSENSE

VTT

PVIN

SD/NC

THRMPAD

VTT

PVIN

N1520

LP2996-LGA16

LP2996

V1521

BC846B

T-NPN

A1520

AR2

4XS-2K2-J-W06

R1520

360R-F-W06

+

C1522

22U-M-10V-2

ELKO

C1520

1U0-Z-16V-Y5V

IN

OUT

LM1117

ADJ

OUT

IN

IN

OUTTAB

OUT

N1500

LM1117-LGA8

LM1117

R1550

33R-J-1W0

R1551

33R-J-1W0

R1522

1K0-J-W06

ABBREV=D1534

D1534