Page 1

Fujitsu SPARC M12

Quick Guide

Manual Code: C120-0050-06EN

March 2018

Page 2

Preface

This document describes the basic specifications and system configurations that users

need to be familiar with when using the Fujitsu SPARC M12 (hereinafter, referred to as

"SPARC M12").The document also provides an overview of the SPARC M12 and indicates

the reference manuals for different work phases or purposes.

Document configuration

1. Understanding an Overview of the System

This chapter describes the SPARC M12 lineup and features.

2. External Views of the Chassis

This chapter shows external views of the chassis for each model.

3. System Specifications

This chapter describes the server and processor hardware specifications.

For details on firmware and software, see "Chapter 1 Understanding an Overview of the SPARC

M12/M10" in the Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 System Operation and

Administration Guide.

4. Document Map Reference Guide (by Phase/Purpose)

This chapter shows the reference manuals for each work item from SPARC M12 installation to

operation/administration and system expansion.

5. Document List

This chapter shows a list of documents related to the SPARC M12.

- 1 -

Page 3

Text conventions

• This document uses the following fonts and symbols to express specific types of information.

Font/Symbol Meaning Example

Italic Indicates the name of a reference manual. See the Fujitsu SPARC M12-2S Installation Guide.

" " Indicates the name of a chapter, section,

item, button, or menu.

See "Chapter 2 Network Connection."

Related documentation

• Sun Oracle software-related documents (Oracle Solaris, etc.)

http://docs.oracle.com/en/

• For a list of documents related to the SPARC M12, see "5. Document List."

Document feedback

• If you have any comments or requests regarding this document, please take a moment to share

them with us by indicating the manual code, manual title, and page, and stating your points

specifically through the following sites:

• Global site

http://www.fujitsu.com/global/contact/

• Japanese site

http://www.fujitsu.com/jp/products/computing/servers/unix/sparc/contact/

Copyright © 2017, 2018 Fujitsu Limited. All rights reserved.

Oracle and/or its affiliates provided technical input and review on portions of this material.

- 2 -

Page 4

1. Understanding an Overview of the System

The SPARC M12 is a UNIX server system that is designed with the

high-performance, high-reliability SPARC64 XII processor and runs

the Oracle Solaris operating system.

The system can support system configurations that meet the

purpose and scale of business, by using CPU Activations and

server connections through the building block (BB) method.

The database server processing of the core system has been

accelerated, with the aim of streamlining tasks and suppressing

investment costs, revolutionizing the businesses of customers.

Page 5

1. Understanding an Overview of the System

1.1 Lineup

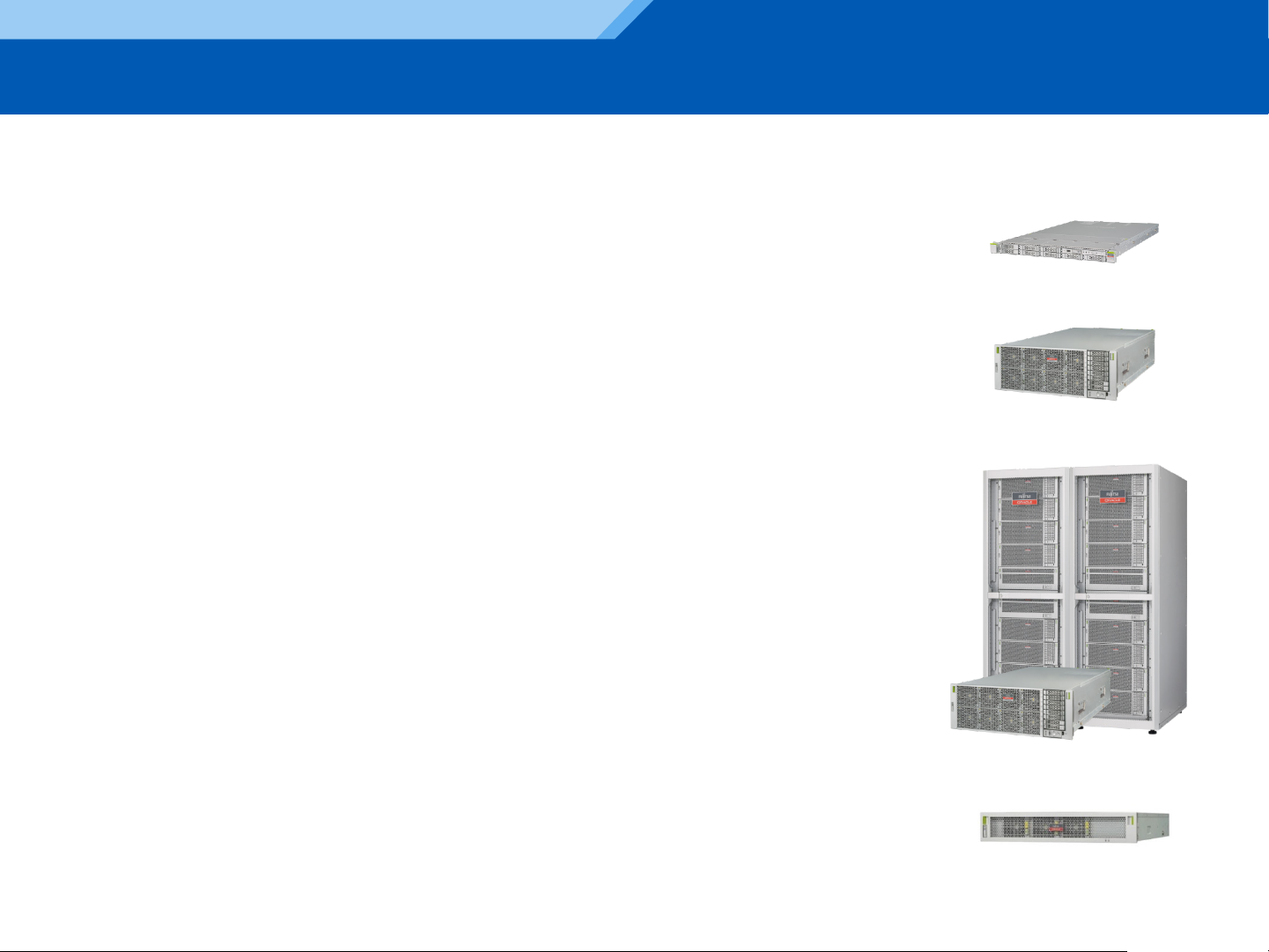

▍Server

SPARC M12-1

• This entry-level server packs high performance and high

reliability in a small 1 RU form factor, and is ideal for

any purpose.

SPARC M12-2

• The compact chassis of this mid-range server, optimal for data

center system integration, provides high performance and high

reliability along with flexible scalability.

SPARC M12-2S

• Providing excellent performance and high scalability, this flagship

server achieves high performance, high reliability, and world-class

scalability through building block connections.

▍Expansion Options

PCI expansion unit

• The SPARC M12 offers a PCI expansion unit for I/O slot expansion.

SPARC M12-1

SPARC M12-2

SPARC M12-2S

All the available server models support the PCI expansion unit,

which supports PCI Express (PCIe).

- 4 -

PCI expansion unit

Page 6

1. Understanding an Overview of the System

1.2 SPARC M12 Features

▍High Performance

• The SPARC M12 is equipped with a new processor, the SPARC64 XII with improved CPU core performance.

In addition to the adopted high-speed DDR4 memory improving memory access performance, the SPARC M12

has the Software On Chip function that incorporates part of software processing into the processor to

accelerate database processing.

▍Scalability

• CPU Activations and the building block method enable step-by-step expansion in units of one CPU core to up

to the maximum configuration of 384 CPU cores (16BB).

▍Flexibility

• You can flexibly configure a system, such as one emphasizing isolation or resource availability, by using

various virtualization functions.

▍Reliability

• Starting with a new processor, the SPARC64 XII with mainframe-class reliability, and through high-reliability

technologies such as data protection, redundancy, and dynamic degradation, the SPARC M12 thoroughly

pursues reliability.

Performance guarantee and continuous operation through alternative CPU cores are functions unique to the

SPARC M12.

▍Safety

• The adopted OS is Oracle Solaris, a UNIX OS compliant with international standards.

You can configure a highly reliable and secure system environment.

▍Ecology

• The SPARC M12 supports low power consumption to save energy through power-saving design and energy-

saving management.

- 5 -

Page 7

1. Understanding an Overview of the System

1.2.1 High Performance

The new processor, the SPARC64 XII, has substantially improved CPU core performance.

Business performance increases, which streamlines tasks, optimizing investment costs.

Acceleration of database server processing

• The improved CPU core performance can increase business performance and suppress

investment costs in the entire system.

• The SPARC M12 provides Software On Chip (SWoC) for accelerating the processing of

databases, such as Oracle Database.

• The SPARC M12 adopts high-speed DDR4 memory for accelerating in-memory processing,

and expands the memory bandwidth.

▍SPARC64 XII

• Designed with state-of-the-art 20 nm technology, the processor

is capable of highly parallel processing of 8 threads per CPU

core and up to 12 CPU cores/96 threads per CPU chip.

• Secondary cache memory is divided in units of CPU cores and

high-capacity tertiary cache memory is added, resulting in

accelerated data processing and an optimized balance

between the speed and capacity of all cache memory.

• The maximum frequency is 4.25 GHz.

- 6 -

Page 8

1. Understanding an Overview of the System

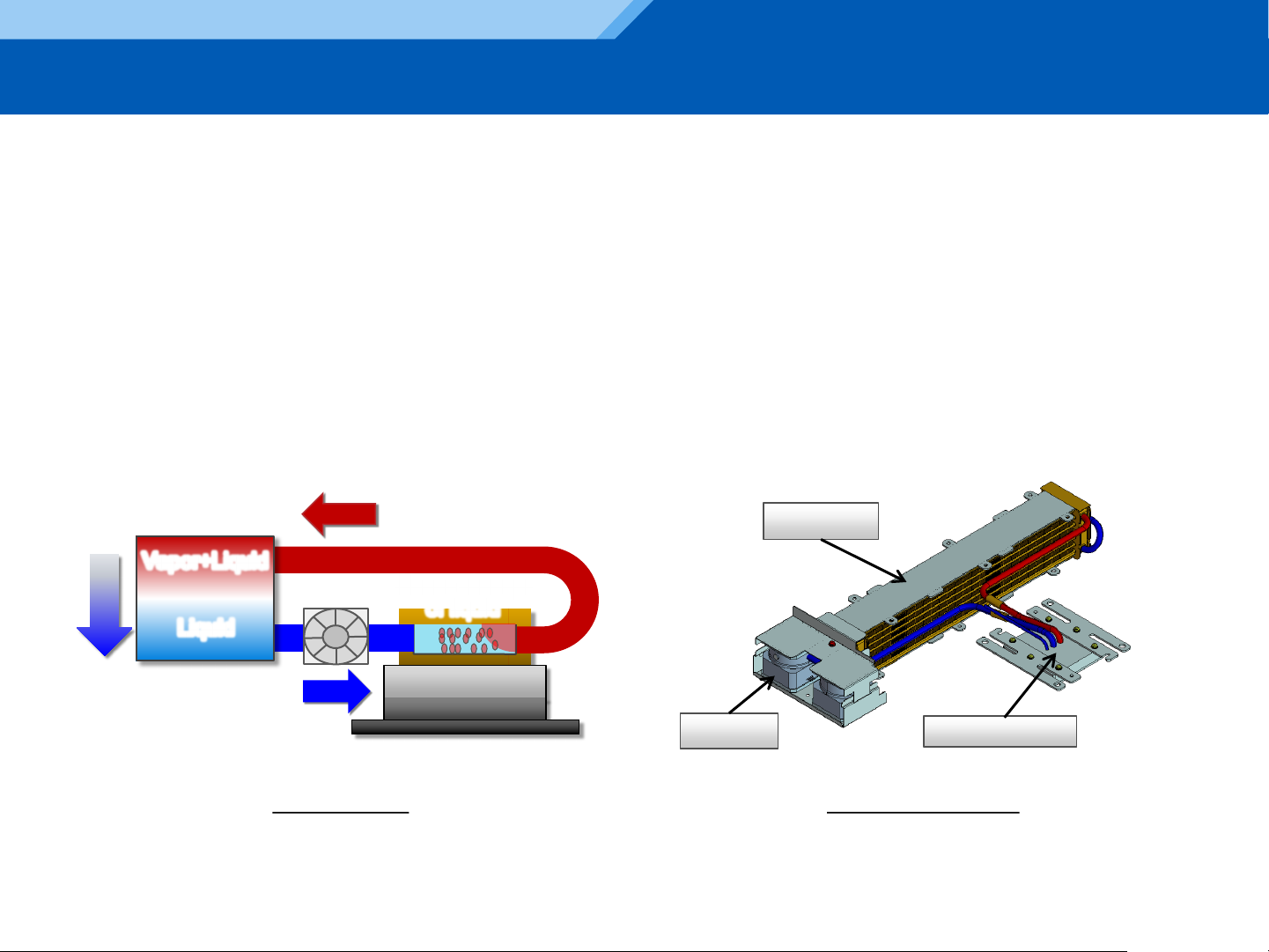

▍VLLC (Vapor and Liquid Loop Cooling)

Technology mounted in the SPARC M12-2/M12-2S to strongly cool the CPU in

order to achieve high CPU core performance

• Used in addition to hybrid cooling with LLC, evaporative cooling takes heat away when

liquid changes into vapor.

• VLLC can exhibit the maximum cooling capacity as a liquid-cooled module that forcibly

circulates refrigerant with a driving force, rather than using surface tension, natural

convection, or gravity to circulate refrigerant.

Radiator

Vapor+Liquid

Liquid

Radiator

Pump

Phase change

of liquid

CPU

Pump

Cooling plate

In principle Implementation

- 7 -

Page 9

1. Understanding an Overview of the System

1.2.2 Scalability

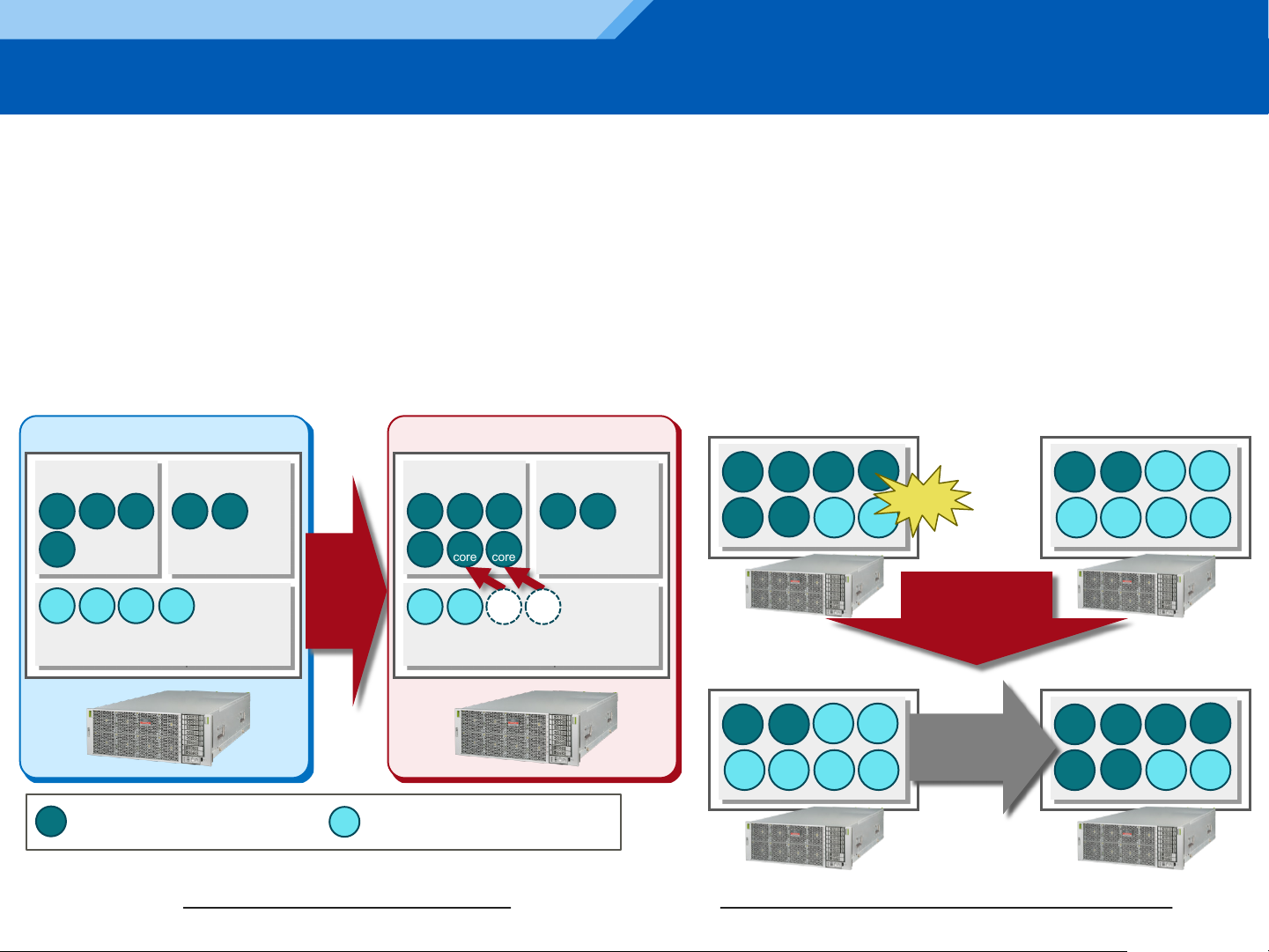

▍CPU Activation

• By using the CPU Activation function, you can add CPU resources in the unit of CPU

cores, which has finer granularity than the unit of CPU chips.

• You can add and register CPU core resources at any time.

• You can move resources by moving a CPU Activation key between SPARC M12 servers

of the same model type.

Normal times

Domain 1

CPU

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

core

CPU

CPU

core

core

CPU Activation

resource pool

CPU Activation assigned

Domain assigned

Operating site (Tokyo)

Backup site (Osaka)

Exceptional times

Domain 2

CPU

CPU

core

core

Domain 1

CPU

CPU

core

core

CPU

CPU

core

core

CPU

core

CPU

core

Domain 2

CPU

CPU

core

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

Sudden

CPU

core

load

increase

CPU

core

CPU

CPU

core

CPU

core

core

CPU Activation

resource pool

CPU Activation assigned

No domain assigned

CPU

core

Operating site (Tokyo)

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

Disaster occurs

at operating

CPU

core

Activation key

CPU

core

site

CPU

moved

Backup site (Osaka)

CPU

CPU

core

core

CPU

CPU

core

core

Resource shortage solved Resources moved between systems

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

- 8 -

Page 10

1. Understanding an Overview of the System

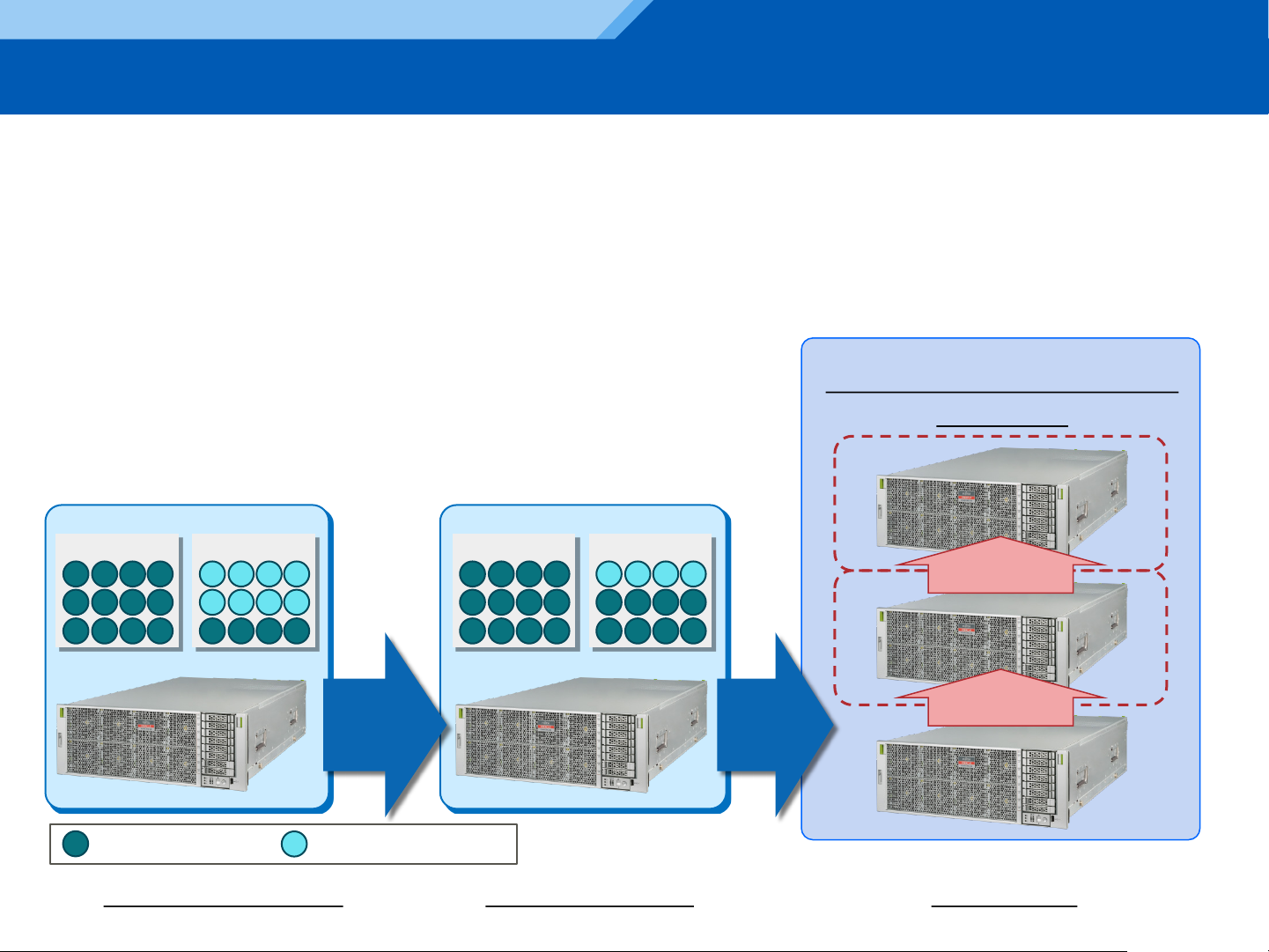

▍Building Block Configuration

• You can adjust the number of SPARC M12-2S connections according to the

performance required. The building block method enables expansion to up to the

16BB configuration/32 CPUs/384 cores.

• A physical partition (hardware partition) can consist

of multiple connected SPARC M12-2S units.

Can expand to up to 16 BBs

(32 CPUs)

12 CPU cores

CPU

CPU

CPU

core

CPU

core

CPU

core

core

CPU

core

CPU

core

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

4 CPU cores

CPU

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

12 CPU cores

CPU

CPU

CPU

core

CPU

core

CPU

core

core

CPU

core

CPU

core

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

8 CPU cores

CPU

core

CPU

core

CPU

core

Configured

cores

easily

added

CPU

Activated CPU core

core

CPU

Non-activated CPU core

core

At initial installation More CPUs More CPU cores

CPU

core

CPU

core

CPU

core

- 9 -

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

CPU

core

Continuous

Additional

expansion

Additional

expansion

use

Page 11

1. Understanding an Overview of the System

▍Dynamic Reconfiguration of Physical Partitions (PPAR DR)

• In the SPARC M12-2S, PPAR DR is a function that can add or remove hardware

resources including CPUs, memory, and I/O devices in a physical partition without

stopping a job.

• With this function, you can add resources (active addition) in a timely manner as required

to add a new job, expand a job, etc. You can also perform active maintenance on

hardware.

Physical partition #0

Job A

CPU

core

CPU

CPU

core

core

Memory

CPU

core

Dynamic

resource

addition

CPU

CPU

core

core

Memory

Addition of resources (active addition)

SPARC M12-2S dynamically disconnected and planned hardware maintenance performed

Disconnection

Job A

CPU

core

Job B Job C

CPU

CPU

core

CPU

core

core

Memory I/O

Activation assignment

CPU

Maintenance

CPU

CPU

core

core

Memory I/O

Active maintenance of hardware

- 10 -

Page 12

1. Understanding an Overview of the System

1.2.3 Flexibility

You can flexibly configure a system by selecting from the following

three choices for a virtual environment, according to your business:

physical partition, Oracle VM Server for SPARC, and Oracle Solaris Zone.

Physical partition (PPAR)

• A physical partition can be configured with the SPARC M12-2S connected using the

building block method.

So you can create a physically independent and highly reliable system environment

according to the scale of business.

Oracle VM Server for SPARC

• You can have an independent OS run on domains by configuring virtual hardware

environments (domains) in the firmware layer of a server.

Oracle Solaris Zone

• You can virtually divide the OS into zones and flexibly use the zones according to your

business.

- 11 -

Page 13

1. Understanding an Overview of the System

▍Types of Virtualization Functions

• A wide variety of virtualization functions can achieve high reliability and flexibility in an

optimal balance.

• You can flexibly configure a system, such as one emphasizing isolation or resource

availability.

Function

Name

(Target Model)

Divided

in Layers

Configuration

Diagram

Feature

Failure

Resistance

Physical partition

(SPARC M12-2S)

Oracle VM Server for SPARC

(All SPARC M12 models)

Hardware layer Hypervisor layer OS layer

Job A Job B Job A Job A Job B Job B

OS OS OS OS

Firmware Firmware

Hardware

resources

Hardware

resources

Firmware

Hardware resources

(Independent kernel)

Job A Job B

Kernel zone Kernel zone

OS

Firmware

Hardware resources

Oracle Solaris Zone

(All SPARC M12 models)

OS layer

Zone

Firmware

Hardware resources

(Shared kernel)

Zone

OS

Strong failure isolation High flexibility (Resource availability)

Can be isolated in units of application (*1)

Can be isolated in units of OS (*1)

Can be isolated in units of hardware (*1)

*1 This can limit the scope of a failure by stopping or isolating the respective unit where the failure occurred.

- 12 -

Page 14

1. Understanding an Overview of the System

1.2.4 Reliability

The SPARC M12 is equipped with data protection, redundancy,

dynamic degradation, and other such high-reliability technologies.

▍SPARC M12-1

CPU

■ Dynamic degradation of CPU

(in units of cache ways or CPU cores)

■● RAS functions (ECC, parity, retry, etc.)

Fan unit

■ Redundant configuration

● Active replacement

Built-in storage

■ Redundant configuration

(when RAID (*1) is configured)

● Active replacement (when

RAID (*1) is configured)

*1 For an HDD, it is when a software RAID/hardware RAID is configured. For an SSD, it is when a software RAID is configured.

Memory

■ Memory mirror

■ Memory patrol

■ Dynamic degradation of

memory (in units of pages)

■ Extended ECC

Power supply unit

■ Redundant configuration

● Active replacement

- 13 -

Hardware as whole

■ Dual power feed

■ Redundant configuration of LAN

(by Oracle Solaris functions)

PCIe card

■ Redundant configuration

(when in multipath configuration)

XSCF

■● Log collection

■● Monitoring function

Legend:

■ Technology minimizing

shutdowns due to failure

● Technology minimizing

maintenance shutdowns

Page 15

1. Understanding an Overview of the System

▍SPARC M12-2/M12-2S

Memory

■ Memory mirror

■ Memory patrol

■ Dynamic degradation of memory

(in units of pages)

■ Extended ECC

CPU

■ Dynamic degradation of CPU

(in units of cache ways or CPU cores)

■● RAS functions (ECC, parity, retry, etc.)

Hardware as whole

■ Protection between CPUs by CRC (*1)

■ Dual power feed

■ Redundant configuration of pump

■ XSCF unit, console path, and path between domain and XSCF:

Redundant configuration (in SPARC M12-2S 2BB configuration

or larger)

■ Redundant configuration of LAN (by Oracle Solaris functions)

■ Redundant configuration of SAS controller

● Active addition and removal of SPARC M12-2S

PCIe card

■ Redundant configuration

(when in multipath configuration)

● Active replacement

Fan unit

■ Redundant configuration

● Active replacement

Built-in storage

■ Redundant configuration

(when RAID (*2) is configured)

● Active replacement

(when RAID (*2) is configured)

*1 Stands for Cyclic Redundancy Check.

The function mainly checks for errors in serial interface access such as reading or writing.

*2 For an HDD, it is when a software RAID/hardware RAID is configured. For an SSD, it is when a software RAID is configured.

Power supply unit

■ Redundant configuration

● Active replacement

- 14 -

XSCF

■● Log collection

■● Monitoring function

● Active replacement

(XSCF unit in SPARC M12-2S

2BB configuration or larger)

NEW

NEW

Legend:

■ Technology minimizing

shutdowns due to failure

● Technology minimizing

maintenance shutdowns

Page 16

1. Understanding an Overview of the System

The SPARC M12 supports active addition and removal of hardware and newly supports

other methods, such as active replacement of the XSCF unit.

Active addition and removal of the SPARC M12-2S

• In a building block configuration connecting multiple SPARC M12-2S units, you can expand and

reduce hardware without stopping the system.

Active replacement of the XSCF unit (in the SPARC M12-2S 2BB configuration

or larger)

• In a building block configuration, you can replace the XSCF unit without stopping the system.

Redundant configuration of the SAS controller

• The SPARC M12-2/M12-2S further improves reliability by the duplication of disks via different SAS

controllers with a software RAID.

- 15 -

Page 17

1. Understanding an Overview of the System

1.2.5 Safety

You can configure a highly reliable and secure system environment

by using Oracle Solaris.

The SPARC64 XII processor is equipped with an encryption function.

Integrated security facility for system protection

• The SPARC M12 supports the security functions provided by Oracle Solaris, such as ZFS and

verified boot.

Data encryption function of the Oracle Solaris ZFS file system

• You can encrypt (encode) business data and file system metadata by using the encryption framework

of Oracle Solaris.

Encryption function of Software On Chip (SWoC) (*1)

• The function is capable of high-speed encryption without using a dedicated adapter for encryption

processing, so there is neither an additional cost nor performance degradation.

*1 The SPARC64 XII processor is equipped with SWoC.

Oracle Solaris

ZFS data encryption

Software On Chip encryption

- 16 -

Application

Secure system

environment

with Oracle Solaris

Page 18

1. Understanding an Overview of the System

1.2.6 Ecology

The power savings of the device have been achieved with a new implementation

technology. The SPARC M12 supports low power consumption to save energy through

power-saving design and energy-saving management.

Power Capping function that sets an upper limit on power consumption

• The function can set an upper limit on system power consumption according to the customer's electric

power conditions.

• After exceeding the set value and a certain period of time (grace period) has elapsed, the system is

suppressed to the maximum power consumption, with the frequency automatically controlled.

Electric

power

Grace period

Power Capping

setting value

Power consumption

at normal times

Power consumption when

Power Capping enabled

Time

Power Saving function that suppresses the power consumption of hardware that

has a low usage rate

• The function suppresses operation of hardware that has a low usage rate and reduces power

consumption by switching to power saving mode.

- 17 -

Page 19

2. External Views of the Chassis

This chapter shows external views of the chassis for each model.

Page 20

2. External Views of the Chassis

2.1 SPARC M12-1

Disk drive

Operation panel

Mode switch Power supply unit

USB port POWER switch

USB port

PCI Express slot

10GbE LAN port

Front view Rear view

- 19 -

XSCF USB port

SAS port

XSCF-LAN port

Page 21

2. External Views of the Chassis

2.2 SPARC M12-2

Fan unit (*1) Disk drive

Operation panel

USB port

Mode switch

*1 You can check the fan unit by removing the front cover.

POWER switch

Front view

- 20 -

XSCF USB port

Power supply unit

XSCF-LAN port

SAS port

PCI Express slot

10GbE LAN port

Rear view

USB port

Page 22

2. External Views of the Chassis

2.3 SPARC M12-2S

Fan unit (*1) Disk drive

Operation panel

BB-ID switch

*1 You can check the fan unit by removing the front cover.

Mode switch

POWER switch

Front view Rear view

USB port

XSCF USB port

XSCF DUAL

control port

XSCF BB

control port

XSCF-LAN port

- 21 -

PCI Express slot

Power supply unit

10GbE LAN port

SAS port

Crossbar

unit

USB port

Page 23

2. External Views of the Chassis

2.4 PCI Expansion Unit (Expansion Option)

Fan unit (*1)

LED

*1 You can check the fan unit by removing the front cover.

Front view Rear view

- 22 -

Link board

Power supply units

PCI Express slot

Page 24

3. System Specifications

This chapter describes the server and processor hardware

specifications.

For details on firmware and software, see "Chapter 1

Understanding an Overview of the SPARC M12/M10" in the Fujitsu

SPARC M12 and Fujitsu M10/SPARC M10 System Operation and

Administration Guide.

Page 25

3. System Specifications

3.1 Server Specifications

Item SPARC M12-1 SPARC M12-2 SPARC M12-2S

Type Rack mount (1U) Rack mount (4U)

Number of connected BBs

Processor name SPARC64 XII

Frequency 3.2 GHz 3.9 GHz 4.25 GHz

Number of CPUs 1 2, maximum

Processor

Memory

Built-in

storage

PCIe

slot

*1 To mount a 64 GB DIMM, see "Notes on Memory" in the Fujitsu SPARC M12 Product Notes.

*2 If the OS versions of the control domain, root domains, and I/O domains are all Oracle Solaris 11 and the firmware version of SPARC M12-2/M12-2S is XCP 3040 or later. For other

combinations, see the following table.

Number of CPU cores 6 12 (per processor)

Number of threads 8, maximum (per core)

Primary cache memory 128 KB (instruction 64 KB + data 64 KB) (per core)

Secondary cache memory 512 KB (per core)

Tertiary cache memory 16 MB 32 MB (per processor)

Type DDR4-DIMM

DIMM capacity/single unit 8/16/32/64 GB (*1)

Capacity type 1 TB, maximum (*1) 2 TB, maximum (*1)

Mounted quantity 8 units (SAS-HDD or SAS-SSD), maximum

Capacity 7.2 TB, maximum

Built-in PCI Express 3.0 (8 lanes): 3 slots PCI Express 3.0 (8 lanes): 11 slots PCI Express 3.0 (8 lanes): 8 slots

Max. number of

slots (number of

connected PCI

expansion units)

OS Versions of the Control Domain, Root

Domains, and I/O Domains

If they are all Oracle Solaris 11 and SPARC

M12-2/M12-2S firmware version is XCP

3030 or earlier

If any of them are Oracle Solaris 10

1 CPU

mounted

2 CPUs

mounted

33 slots (3 units) (*2)

CPU(s)

Mounted

1 CPU 33 slots (3 units) 41 slots (3 units) 38 slots (3 units)

2 CPU - 71 slots (6 units) 58 slots (5 units)

1 CPU 23 slots (2 units) 31 slots (2 units) 28 slots (2 units)

2 CPU - 71 slots (6 units) 58 slots (5 units)

-

91 slots (8 units) (*2) 88 slots (8 units) (*2)

-

SPARC M12-1 SPARC M12-2 SPARC M12-2S

51 slots (4 units) (*2) 48 slots (4 units) (*2)

16 BBs, maximum

-

- 24 -

Page 26

3. System Specifications

3.1 Server Specifications (Continued)

Item SPARC M12-1 SPARC M12-2 SPARC M12-2S

I/O

interface

Redundant facility

Active replacement facility

Supported OS Oracle Solaris 10/11 or later

*1 When memory is mirrored

*2 When the disk is mirrored by software or the built-in hard RAID

*3 When the disk is mirrored by software

*4 When in a multipath configuration (Replacement may not be possible depending on the card type.)

*5 When two or more building blocks are configured

LAN 4 ports (10GBASE-T)

SAS 1 port (6 Gb)

USB 2 ports (USB 3.0: Rear, USB 2.0: Front)

Memory (*1), built-in disk drive (*2),

SSD (*3), power supply unit, fan

unit, PCIe card (*4)

Built-in disk drive (*2), SSD (*3),

power supply unit, fan unit

Memory (*1), built-in disk drive (*2),

SSD (*3), power supply unit, fan unit,

PCIe card (*4), VLLC pump

Built-in disk drive (*2), SSD (*3),

power supply unit, fan unit, PCIe

card (*4)

Memory (*1), built-in disk drive (*2), SSD

supply unit, fan unit, PCIe card (*4), XSCF

(*3), power supply unit, fan unit, PCIe

card (*4), VLLC pump, XSCF unit (*5)

Built-in disk drive (*2), SSD (*3), power

unit (*5)

- 25 -

Page 27

3. System Specifications

3.2 Processor Specifications

Item SPARC64 XII

Operating frequency 4.25 GHz, maximum

Technology 20 nm

Number of CPU cores 12, maximum

Number of threads 8

SIMD 2

Primary cache memory 64 KB x 2

Secondary cache memory 512 KB

Tertiary cache memory 32 MB, maximum

Memory connection mode Directly connected to DIMM

DIMM type DDR4

DIMM speed 2,400 MHz

I/O bandwidth 64 GB/s (bidirectional)

PCIe PCI Express 3.0

Number of PCIe ports 4

DVFS Supported

CPU core degradation Supported

DIMM degradation Supported

FTL lane degradation Supported

Power supply noise measure Operation-rate modulation, frequency

modulation

SWoC SIMD (Single Instruction Multiple

Data)

Decimal floating-point arithmetic

unit mounted

Encryption computation unit

mounted

Can process up to 64 values of 4-bit data

simultaneously per core

Conforms to IEEE 754-2008, standard for

decimal floating-point arithmetic operations

Supports AES, DES, 3DES, DH, DSA, ECC,

RSA, and SHA

- 26 -

Page 28

3. System Specifications

3.3 PCI Expansion Unit Specifications

Item PCI Expansion Unit

Height

Number of PCIe slots

Redundant facility

Active replacement facility

*1 Active replacement may not be possible depending on the PCIe card type.

*2 You can replace the board after disconnecting the link card connected to the PCI expansion unit or the physical

partition containing this link card. Use PCI Hot Plug to disconnect the card, or dynamic reconfiguration (DR) to

disconnect the physical partition.

Power supply unit, fan unit

Power supply unit, fan unit,

PCIe card (*1), link board (*2)

2U

11

- 27 -

Page 29

4. Document Map

Reference Guide (by Phase/Purpose)

This chapter shows the reference manuals for each work item from

SPARC M12 installation to operation/administration and system

expansion.

For a list of the manuals and their formal names, see "5. Document

List."

Page 30

4. Document Map Reference Guide (by Phase/Purpose)

Document Map

Planning Installation

Quick Guide (this document)

Getting Started Guide

Important Legal and Safety

Information

Safety and Compliance Guide

Software License Conditions

Security Guide

Common Installation Planning Manual

Product Notes

Installation Guide Installation Guide

PCI Card Installation Guide PCI Card Installation Guide

System Operation and Administration Guide

Operation

Expansion

Domain Configuration Guide

RCIL User Guide

XSCF Reference Manual

XSCF MIB and Trap Lists

External USB-DVD Drive User Guide

Service Manual

- 29 -

Page 31

4. Document Map Reference Guide (by Phase/Purpose)

4.1 Planning

a. Understanding an overview

• Check the SPARC M12 overview.

▶ Quick Guide (this document)

b. Installation planning

• Check the specifications and software license conditions.

▶ Getting Started Guide ▶ Important Legal and Safety Information

▶ Safety and Compliance Guide ▶ Security Guide

▶ Software License Conditions

• Before installing the system, confirm that the installation location meets the requirements.

▶ Common Installation Planning Manual ▶ Installation Guide

c. System design

• During system design, confirm the flow for system settings and system configuration.

▶ Installation Guide ▶ PCI Card Installation Guide

▶ System Operation and Administration Guide ▶ Domain Configuration Guide

▶ Product Notes

- 30 -

Page 32

4. Document Map Reference Guide (by Phase/Purpose)

4.2 Installation

a. Installation and connection

• Install and connect servers and peripheral devices according to the system configuration.

▶ Installation Guide ▶ PCI Card Installation Guide

b. Initial settings

• Before starting the system, perform the initial setup of the eXtended System Control

Facility (XSCF).

• Configure the power control and other settings affecting the entire system.

• Make settings to improve reliability by using memory mirroring and the hardware RAID

function.

▶ System Operation and Administration Guide ▶ Product Notes

c. System configuration

• If you are not going to use the preinstalled Oracle Solaris as is, install Oracle Solaris.

• You can configure a virtual environment by dividing the system into physical partitions

and logical domains.

▶ Domain Configuration Guide

- 31 -

Page 33

4. Document Map Reference Guide (by Phase/Purpose)

4.3 Operation

a. Daily management

• You need to understand the basic operation/administration operations for daily

management work such as backup.

The basic operations include logging in/out from the management console and

starting/stopping the system.

▶ System Operation and Administration Guide

b. Updating firmware/software

• Update firmware, Oracle VM Server for SPARC, and Oracle Solaris to the latest versions.

The updates require a service contract with Fujitsu's Support Desk.

▶ System Operation and Administration Guide

c. Failure diagnosis/unit replacement

• If an error message appears on the console or the CHECK LED on the server or a

peripheral device goes on, diagnose whether a failure has occurred.

• After a failure occurs, replace the faulty unit. The maintenance method varies with the

unit. A service engineer performs the maintenance work.

▶ Service Manual

- 32 -

Page 34

4. Document Map Reference Guide (by Phase/Purpose)

4.4 Expansion

a. Expanding with a PCI expansion unit/optional unit

• You can expand the number of PCIe slots by using the PCI expansion unit.

• You can expand the system by adding an optional unit, such as a memory module or

PCIe card.

▶ Installation Guide ▶ PCI Card Installation Guide

▶ Service Manual

b. Expanding resources

• You can add CPUs in units of one CPU core according to load increases by using the

CPU Activation function.

▶ System Operation and Administration Guide

c. Expanding/Reducing the system with a building block configuration

• In the building block method, you can flexibly expand/downscale the system by

expanding/reducing the SPARC M12-2S.

▶ Installation Guide ▶ System Operation and Administration Guide

▶ Domain Configuration Guide ▶ Service Manual

d. Changing the resource configuration

• You can change the virtual CPU, virtual memory, and virtual I/O configuration by using

the dynamic reconfiguration function of Oracle VM Server for SPARC.

▶ Domain Configuration Guide

- 33 -

Page 35

5. Document List

This chapter shows a list of documents related to the SPARC M12.

• Global site

http://www.fujitsu.com/global/products/computing/servers/unix/sparc/downloads/manuals/

• Japanese site

http://www.fujitsu.com/jp/products/computing/servers/unix/sparc/downloads/manual/

Page 36

5. Document List

SPARC M12 Document List 1/3

▍ Fujitsu SPARC M12 Product Notes

Describes the important and latest information regarding hardware, software, and documents. Be sure to read this document

before installation.

▍ Fujitsu SPARC M12 Quick Guide (this document)

Provides an overview, including the system specifications and system configuration, and describes the manuals used with

each work item. The manuals cover the work from SPARC M12 installation to operation/administration and system expansion.

Check this document before reading the other documents.

▍ Fujitsu SPARC M12 Getting Started Guide

Describes notes regarding export control regulations and how to reference other documents.

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Important Legal and Safety Information

Describes software license agreements, user license agreements, and safety precautions.

Check this document before opening a software product package or installing the server.

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Safety and Compliance Guide

Describes notes on server installation. Check this document before installing the server.

▍ Software License Conditions for Fujitsu SPARC M12 and Fujitsu M10/SPARC M10

Describes the software license conditions used.

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Security Guide

Describes security guidelines for using the server.

▍ Fujitsu SPARC Servers/SPARC Enterprise/PRIMEQUEST Common Installation Planning Manual

Describes the requirements and concepts pertaining to installation planning and facility planning for the server.

- 35 -

Page 37

5. Document List

SPARC M12 Document List 2/3

▍ Fujitsu SPARC M12-1 Installation Guide

Describes the prerequisite environmental conditions for SPARC M12-1 installation, the installation and initial setting

procedures used during installation, and the procedures for expansion/reduction after operation has begun.

▍ Fujitsu SPARC M12-2 Installation Guide

Describes the prerequisite environmental conditions for SPARC M12-2 installation, the installation and initial setting

procedures used during installation, and the procedures for expansion/reduction after operation has begun.

▍ Fujitsu SPARC M12-2S Installation Guide

Describes the prerequisite environmental conditions for SPARC M12-2S installation, the installation and initial setting

procedures used during installation, and the procedures for expansion/reduction after operation has begun.

▍ Fujitsu SPARC M12 PCI Card Installation Guide

Describes the mounting rules for PCI cards mounted in the system.

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 System Operation and Administration Guide

Describes items related to the management and maintenance work after operation has begun.

For domain settings, see the Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Domain Configuration Guide. For the

maintenance procedures for each field replaceable unit (FRU), see the Fujitsu SPARC M12-2/2S Service Manual or the PCI

Expansion Unit for Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Service Manual.

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Domain Configuration Guide

Describes the knowledge and procedures required for configuring and managing physical partitions and logical domains,

among system operation and maintenance work.

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 RCIL User Guide

Describes the Remote Cabinet Interface over LAN (RCIL) function, used to manage the power of I/O devices such as the

Fujitsu storage system ETERNUS from the SPARC M12/M10.

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 XSCF Reference Manual

Describes how to use the commands provided with the mounted XSCF firmware.

- 36 -

Page 38

5. Document List

SPARC M12 Document List 3/3

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 XSCF MIB and Trap Lists

Describes, in lists, the Management Information Base (MIB) values and MIB Trap values used with the system.

▍ Fujitsu SPARC M12-1 Service Manual

Describes the information to be checked in system maintenance of the SPARC M12-1 and the maintenance procedures for

each field replaceable unit (FRU).

▍ Fujitsu SPARC M12-2/2S Service Manual

Describes the information to be checked in system maintenance of the SPARC M12-2/2S and the maintenance procedures for

each field replaceable unit (FRU).

▍ Crossbar Box for Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Service Manual

Describes the information to be checked in system maintenance of the crossbar box and the maintenance procedures for

each field replaceable unit (FRU).

▍ PCI Expansion Unit for Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Service Manual

Describes the information to be checked in system maintenance of the PCI expansion unit and the maintenance procedures

for each field replaceable unit (FRU).

▍ Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Glossary

Lists and explains the terms used in these documents.

▍ Safe Backup by Regularly Cleaning and Replacing Tape Units and Media!

Describes tape media management, the installation environment, and cleaning operations, all of which tend to be overlooked

after a backup environment is configured.

▍ External USB-DVD Drive User Guide

Describes how to use a USB-DVD drive connected to the SPARC M12/M10.

- 37 -

Loading...

Loading...