Page 1

Fujitsu Limited

4-1-1 Kamikodanak a

Nahahara-ku, Ka w as ak i, 211 -858 8

Japan

SPARC JPS1

Implementation Supplement:

Fujitsu SPARC64 V

Fujitsu Limited

Release 1.0, 1 July 2002

Part No. 806-6755-1.0

Page 2

Copyright 2002 Sun Microsystems, Inc., 901 San Antonio Road, Palo Alto, California 94303 U.S.A. All rights reserved.

Portions of this document are protected by copyright 1994 SPARC International, Inc.

This product or document is protected by copyright and distributed under lic enses restricting its use, copying, distributio n, and decompilation. No part of this

product or document may be reprod uced in any form by any means without prior written authorization of Sun and its lic ensors, if any. Thir d-party software,

including font technology, is copyrighted and license d from Sun suppliers.

Parts of the product may be derived fr om Berkeley BSD systems, licensed from the University of California. UNIX is a r egistered trademark in the U.S. and other

countries, exclusively licensed through X/Open C ompany, Ltd.

Sun, Sun Microsystems, the Sun logo, SunSoft, SunDocs, SunExpres s, and Solaris are trademarks, registered trademarks, or service marks of Sun Microsy stems,

Inc. in the U.S. and other countries. All SP ARC trademarks ar e used under license and are trademarks or r egistered trademarks of SPARC International, Inc. in the

U.S. and other countries. Products bearing SP ARC trademarks are based upon an architec ture developed by Sun Microsystems, Inc.

The OPEN LOOK and S un™ Graphi cal Use r Interfac e was devel oped by Su n Micr osystems, Inc. for its users a nd license es. Sun ac knowledges the pioneering

efforts of Xerox in r esearching and developing the con cept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from

Xerox to the Xerox Graphical User Interface, which lice nse also covers Sun’s licensees who implement OPEN LOOK GUIs and otherwise comply with Sun’s

written license agreements.

RESTRICTED RIGHTS: Use, duplication, or disclosure by the U.S. Government is subject to restrictions of F AR 52.227-14(g)(2)(6/87) and F AR 52.227-19(6/87),

or DFAR 252.227-7015(b)(6/95) and DF AR 227.7202-3(a).

DOCUMENTATION IS P ROVIDED “AS I S” AND ALL EXPR ESS OR IMPLIED CO NDITIONS, REP RESENTATIONS AND WARRANTIES, INCLUDING

ANY IMPLIED W ARRANTY OF MERCHANTABILITY , FITNESS FOR A P AR TICUL AR PURPOSE OR NON-INFRINGEMENT , ARE DISCL AIMED, EXCEPT

TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2002 Sun Microsystems, Inc., 901 San Antonio Road • Palo Alto, CA 94303-4900 Etats-Unis. Tous droits r éservés.

Ce produit ou document est protégé par un copy right et distribué avec des licences qui en r estreignent l’utilisation, la copie, la distribution, et la décompilation.

Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l’autorisation préalable et écrite de Sun

et de ses bailleurs de licence, s’il y en a. Le logiciel détenu par des tiers, et qu i comprend la technologie r elative aux polices de caractèr es, est protégé par un

copyright et licencié par des fournisseurs de Sun.

Des parties de ce produit pourront êtr e dérivées des systèmes Berkeley BS D licenciés par l’Université de Californie. UN IX est une marque déposée aux E tats-Unis

et dans d’autres pays et licenciée exclusivement par X/Open C ompany, Ltd. La notice suivante est applicable à Netscape Communicator™: Copyright 1995

Netscape Communications Corporation. T ous droi ts réservés.

Sun, Sun Microsystems , the Sun logo, Ans werBook2, docs.s un.com, et Sol aris sont des mar ques de fab rique ou des mar ques déposées, ou marques de service, de

Sun Microsystems, Inc. aux Etats-Unis et dans d’autr es pays. Toutes les marques SP ARC sont utilisées so us licence et sont des marques de fabrique ou des

marques déposées de SP ARC International, Inc. aux Etats-Unis et dans d ’autres pays. Les produits portant les mar ques SP ARC sont bas és sur une ar chitecture

développée par Sun Microsystems, Inc.

L ’interface d’utilisation graphique OPEN LOOK et Sun™ a été dévelo ppée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun r econnaît les eff orts

de pionniers de Xerox pour la r echerche et le développement d u concept des interfaces d’utilisation visuelle o u graphique pour l’industrie de l’informatique. Sun

détient une licence non exclusive de Xerox sur l’interface d’utilis ation graphique Xerox, ce tte licence couvrant également les licenciés d e Sun qui mettent en place

l’interface d’utilisation graphique OPEN LOOK et qui en outre se con forment aux licences écrites de Sun.

CETTE PUBLICATION EST FOURNIE "EN L’ETAT" ET AUCUNE GARANTIE, EXPRESSE OU IMPLICITE, N’EST ACCORDEE, Y COMPRIS DES

GARANTIES CONCERNANT LA VALEUR MARCHANDE, L ’APTITUDE DE LA PUBL ICA TION A REPOND RE A UNE UTILISA TI ON P AR TICUL IERE, OU

LE FAIT QU’ELLE NE SOIT PAS CONTREFAISA NTE DE PRO DUIT DE TIERS . CE DENI DE GARANTI E NE S’APPLIQU ERAIT PAS, DANS LA MESURE

OU IL SERAIT TENU JURIDIQUEMENT NUL ET NON AVENU.

Copyright© 2002 Fujitsu Limited, 4-1-1 Kamikodanaka, Nakahara-ku, Kawasaki, 211-8588, Japan. All rights reserved.

This product and related documentation ar e protected by copyright and distributed under licenses r estricting their use, copying, distribution, and decompilation.

No part of this product or related documentation may be r eproduced in any form by any means without prior written authorization of Fujits u Limited and its

licensors, if any.

Portions of this product may be derived from the UNIX and Berk eley 4.3 BSD Systems, licensed from UNIX System Laboratories, Inc., a wholly owned subsidiary

of Novell, Inc., and the University of California, respectively.

The product described in this book may be pro tected by one or more U.S. patents, f oreign patents, or pending applications.

Fujitsu and the Fujitsu logo are trademarks of Fujitsu Limited.

This publication is provided “as is” without warranty of any kind, either express or implied, including, but not limited to, the implied warranties of

merchantability, fitness for a particular purpose, or noninfringement.

This publication could include technical inaccuracies or typographical errors. changes are periodically added to the inf ormation herein; these chang es will be

incorporated in new editions of the publication. Fujitsu limited may make impr ovements and/or changes in the pr oduct(s) and/or the pr ogram(s) described in

this publication at any time.

Sun Microsystems, Inc. Fujitsu Limited

901 San Antonio 4-1-1 Kamikodanaka

Palo Alto, California, 94303 Nakahara-ku, Kawasaki, 211-8588

U.S.A. Japan

http://www.sun.com http://www.fujitsu.com/

Release 1.0, 1 July 2002 F. Chapter 2

Page 3

3 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 4

F.CHAPTER

Contents

1. Ove r v iew 1

Navigating the SPARC64 V Implementation Supplement 1

Fonts and Notational Conventions 1

The SPARC64 V processor 2

Component Overview 4

Instruction Control Unit (IU) 6

Execution Unit (EU) 6

Storage Unit (SU) 7

Secondary Cache and External Access Unit (SXU) 8

2. Def i n i t ions 9

3. Architectura l Ov e rvi ew 13

4. Data Formats 15

5. Registers 17

Nonprivileged Registers 17

Floating-Point State Register (FSR) 18

Ti ck (TICK) Reg ister 19

Privileged Registers 19

Trap State (TSTATE) Register 19

Ver sion (VER) Re g i ster 20

Ancillary State Registers (ASRs) 20

Registers Referenced Through ASIs 22

i

Page 5

Floating-Point Deferred-Trap Queue (FQ) 24

IU Deferred-Trap Queue 24

6. Instructions 25

Instruction Execution 25

Data Prefetch 25

Instruction Prefetch 26

Syncing Instructions 27

Instruction Formats and Fields 28

Instructi o n Categories 29

Control-Transfer Instructio ns (CTI s) 29

Floating-Point Operate (FPop) Instructio ns 30

Implementation-Dependent Instructions 30

Processor Pipeline 31

Instruction Fetch Stages 31

Issue Stages 33

Execution Stages 33

Completion Stages 34

7. Traps 35

Processor States, Normal and Sp ec ial Traps 35

RED_state 36

error_state 36

Trap Categories 37

Deferred Trap s 37

Reset Traps 37

Uses of the Trap Categories 37

Trap Control 38

PIL Control 38

Trap-Table Entry Addresses 38

Trap Type (TT) 38

Details of Supported Tr aps 39

Trap Processing 39

Exception and Interrupt Descriptions 39

SPARC V9 Implementation-Dependent, Optional Traps That Are

Mandatory in SPARC JPS1 39

ii SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 6

SPARC JPS1 Implementation-Dependent Traps 39

8. Mem ory Models 41

Overview 42

SPARC V9 M em or y Mo de l 42

Mode Control 42

Synchronizing Instruction and Data Memo ry 42

A. Instruction Definitions: SPARC64 V Extensions 45

Block Load and Store Instructions (VIS I) 47

Call and Link 49

Implementation-Dependent Instructions 49

Floating-Point Multiply-Add/Subtract 50

Jump and Link 53

Load Quadword, Atomic [Physical] 54

Memory Barrier 55

Partial Store (VIS I) 57

Prefetch Data 57

Read State Register 58

SHUTDOWN (VIS I) 58

Wr ite St at e Re gis t er 59

Deprecated I ns tru c ti on s 59

Store Barrier 59

B. IEEE S td 754 - 198 5 Re qu ir eme nt s fo r SPARC V9 61

Traps Inhibiting Results 61

Floating-Point Nonstandard Mode 6 1

fp_exception_other Exception (ftt=unfinished_FPop) 62

Operation Under FSR.NS = 1 65

C. Implementation Dependencies 69

Definition of an Implementation Depend ency 69

Hardware Characteristics 70

Implementation Dependency Categories 70

List of Implementation Dependencies 70

Release 1.0, 1 July 2002 F. Chapter Contents iii

Page 7

D. Forma l S pe cifi c atio n o f t he M emo ry M od els 81

E. Opc ode M ap s 8 3

F. Memory Management Unit 85

Virtual Address Translation 85

Translation Table Entry (TTE) 86

TSB Organization 88

TSB Pointer Formation 88

Faults and Traps 89

Reset, Disable, and RED_state Behavior 91

Internal Register s an d ASI ope rat ion s 92

Accessing MMU Registers 92

I/D TLB Data In, Data Access, and Tag Rea d Regis ters 93

I/D TSB Extension Registers 97

I/D Synchronous Fault Status Registers (I-SFSR , D-SF SR) 97

MMU Bypass 104

TLB Replacement Policy 105

G. Assembly Language Syntax 107

H. Software Considerations 109

I. Extending the SPARC V9 Architecture 111

J. Changes from SPARC V8 to SPARC V9 113

K. Programming with the Memory Models 115

L. Addre ss S pa ce Id enti fi er s 117

SPARC64 V ASI Assignments 117

Special Memory Ac ce ss AS Is 119

Barrier Assist for Parallel Processing 121

Interface Definition 121

ASI Registers 122

M. Cache Orga nizat io n 125

Cache Types 125

Level-1 Instruction Cache (L1I Cache) 126

iv SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 8

Level-1 Data Cac he (L1D C a ch e) 127

Level-2 Unified Cache (L2 Cache) 127

Cache Coherency Pro tocols 128

Cache Control/Status Instructions 128

Flush Level-1 Instruction Cache (ASI_FLUSH_L1I) 129

Level-2 Cache Control Register (ASI_L2_CTRL) 130

L2 Diagnostics Tag Read (ASI_L2_DIAG_ TAG_READ) 130

L2 Diagnostics Tag Read Registers (AS I_L 2_DI AG_TAG_READ_REG) 131

N. Interrupt Handling 133

Interrupt Dis p at c h 13 3

Interrupt Re ce iv e 1 35

Interrupt Global Registers 136

Interrupt-Related AS R Regis ter s 13 6

Interrupt Vector Dispatch Register 136

Interrupt Vector Dispatch Status Register 136

Interrupt Vector Receive Register 136

O. Rese t, RED_ s tate , and err or_st at e 137

Reset Types 137

Power-on Reset (POR) 137

Watchdog R eset (W DR) 138

Externally Initiated Reset (XIR) 138

Software-Initiat ed R ese t (S I R) 13 8

RED_state and error_st ate 139

RED_state 140

error_state 140

CPU Fatal Error state 141

Processor State after Reset and in RED_state 141

Operating Status Register (OPSR) 146

Hardw are Power-On Rese t Sequ ence 147

Firmware Initialization Sequence 147

P. Error Handling 14 9

Error Classification 149

Fatal Error 149

Release 1.0, 1 July 2002 F. Chapter Contents v

Page 9

error_state Transition Error 150

Urgent Error 150

Restrainable Error 152

Acti on an d Erro r Cont ro l 153

Registers Related to Error Handling 153

Summary of Actions Upon E rror Detection 154

Extent of Automatic Source Data Correction for Correctable Error 157

Error Marking for Cacheable Data Error 157

ASI_EIDR 161

Cont rol of E rror A c tion (ASI_ERROR_CONTROL) 161

Fatal Er ro r and e r ro r_s t a t e Tran s i tion Erro r 1 63

ASI_STCHG_ERROR_INFO 163

Fatal Error Types 164

Types of error_state Tra nsition Errors 164

Urgent Error 165

URGENT ERROR STATUS (ASI_UGESR) 165

Action of

async_data_error

(ADE) Trap 168

Instruction End-Method at ADE Trap 170

Expected Soft w are Hand ling of ADE Trap 171

Instruction Access Errors 173

Data Access Errors 173

Restrainable Errors 174

ASI_ASYNC_FAULT_STATUS (ASI_AFSR) 174

ASI_ASYNC_FAULT_ADDR_D1 177

ASI_ASYNC_FAULT_A DDR_U 2 17 8

Expected Software Handling of Restrainable Errors 179

Handling of Internal Register Errors 181

Register Error Handling (Excluding ASRs and ASI Registers) 181

ASR Error Handling 182

ASI Register Error Handling 183

Cache Error Handling 188

Handling of a Cache Tag Error 188

Handling of an I1 Cache Data Error 190

Handling of a D1 Cache Data Error 190

Handling of a U2 Cache Data Error 192

Automatic Way Reduction of I1 Cache, D1 Cache, and U2 Cache 193

vi SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 10

TLB Error Handling 195

Handling of TLB Entry Errors 195

Automatic Way Reduction of sTLB 196

Handling of Extended UPA Bus Interface Error 197

Handling of Extended UPA Address Bus Error 197

Handling of Extended UPA Data Bus Error 197

Q. Perform anc e Ins trume nt atio n 20 1

Performance Monitor Overview 201

Sample Pseudo co des 2 01

Performance Monitor Description 203

Instruction Statistics 204

Trap-R el at ed S tat istic s 2 06

MMU Event Counters 207

Cache Event Counters 208

UPA Event Counters 210

Miscellaneous Counters 211

R. UPA Programmer’s Model 213

Mapping of the CPU’s UPA Port Slave Area 213

UPA Por tID Re gist er 214

UPA Conf ig Re giste r 215

S. Summary of Differences between SPARC64 V and UltraSPARC-III 219

Bibliography 223

General References 223

Index 225

Release 1.0, 1 July 2002 F. Chapter Contents vii

Page 11

viii SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Rele a se 1. 0, 1 July 20 02

Page 12

F.CHAPTER

1

Overview

1.1 Navigating the SPARC64 V

Implementation Supplement

We sugg est that you approach this Impl ementation Suppl ement SPARC Joint

Programming Specification as follows.

1. Familiarize yourself with the SPARC64 V processor and its components by

reading these sections:

■

The SPARC64 V processor on page 2

■

Component Overview on page 4

■

Processor Pipel ine on page 31

2. Study the terminology in Chapter 2, Definitions:

3. For details of architectural changes, se e the remaining cha pters in this

Implementation Supplement as your interests direct.

For this revision, we added new appendixes: Appendix R,

and Appendix S, Summary of Differences between SPARC64 V and UltraSPARC-III.

UPA Programmer’s Model

1.2 Fonts and Notational Conventions

Please refer to Section 1.2 of Commonality for font a nd notational conventions.

,

1

Page 13

1.3 The SPARC64 V processor

The SPARC64 V processor is a high-performance, high-reliability, and high-integrity

processor that fully implements the instruction set architecture that conforms to

SPARC V9, as described in JPS1 Commonality. In addition, the SPARC64 V processor

implements the following features:

64-bit virtual a ddress space and 4 3-bit physical address space

■

Advanced RAS features that enable high-integrity error handling

■

Microarchitecture for High Performance

The SPARC6 4 V is an out-of-order execution superscala r processor that issues up to

four instructions per cycle. Instructions in the predicted path are issued in program

order and are stored temporarily in

of program order to appropriate execution units. Instructions commit in program

order when no exceptional conditions occur during execution and all prior

instructions commit (that is, the result of the instruction execution becomes visible).

Out-of-order execution in SPARC64 V contributes to high performance.

SPARC64 V implements a large branch history buffer to predict its instruction path.

The history buffer is large enough to sustain a good prediction rate for large-scale

programs such as DBMS and to support the advanced instruction fetch mechanism

of SPARC64 V. This instruction fetch scheme predicts the execution path beyond the

multiple conditional branches in accordance with the branch history. It then tries to

prefetch instructions on the predicted path as much as possible to reduce the effect

of the performance penalty caused by instruction cache misses.

reservation st ations

until they are dispatched out

High Integration

SPARC64 V integrates an on-board, associative, level-2 cache. The level-2 cache is

unified for instruction and data. It is the lowest layer in the cache hierarchy.

This integration contributes to both performance and reliability of SPARC64 V. It

enables shorter access time and more associativity and thus contributes to higher

performance. It contributes to higher reliability by eliminating the external

connections for level-2 cache.

High Reliability and High Integrity

SPARC64 V implements the following advanced RAS features for reliability and

integrity beyond that of ordinary microprocessors.

2 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 14

1. Advanced RAS features for caches

■

Strong cache error protection:

ECC protection for D1 (Data level 1) cache data, U2 (unified level 2) cache data,

■

and the U2 cache tag.

Parity protection for I1 (Instruction level 1) cache data.

■

Parity protection and duplication for the I1 cache tag and the D1 cache tag.

■

■

Automatic correction of all types of single-bit error:

Automatic single-bit error correction for the ECC protected data.

■

Invalidation and refilling of I1 cache data for the I1 cache data parity error.

■

Copying from duplicated tag for I1 cache tag and D1 cache tag parity errors.

■

■

Dynamic way reduction while cache consistency is maintained.

■

Error marking for cacheable data uncorrectable errors:

Special error-marking pattern for cacheable data with uncorrectable errors. The

■

identification of the module that first detects the error is embedded in the

special pattern.

Error-source isolation with faulty module identification in the special error-

■

marking. The identification information enables the processor to avoid

repetitive error logging for the same error cause.

2. Advanced RAS features for the core

■

Strong error protection:

Parity protection for all data paths.

■

Parity protection for most of software-visible registers and internal temporary

■

registers.

Parity predicti on or residue che cking for t he accumula tor output.

■

■

Hardware instruction retry

■

Support for software instruction retry (after failure of hardware instruction retry)

■

Error isolation for software recovery:

Error indication for each programmable register group.

■

Indication of retryability of the trapped instruction.

■

Use of different error traps to differentiate degrees of adverse effects on the

■

CPU and the system.

3. Extended RAS interface to software

■

Error classification according to the severity of the effect on program execution:

Urgent error (nonmaskable): Unable to continue execution without OS

■

intervention; reported through a trap.

Restrainable error (maskable): OS controls whether the error is reported

■

through a trap, so error does not directly affect program execution.

■

Isolated error indication to determine the effect on software

Release 1.0, 1 July 2002 F. Chapter 1 Overview 3

Page 15

■

Asynchronous data error (

Relaxed i nstruct ion en d method (precise , retryab le, not ret ryable ) for the

■

async_data_error

exception to indicate how the instruction should end; depends

ADE

) trap for additional errors:

on the executing instruction and the detected error.

ADE

Some

■

Simultaneous reporting of all detected

■

traps that are deferred but retryable.

handling of retryability.

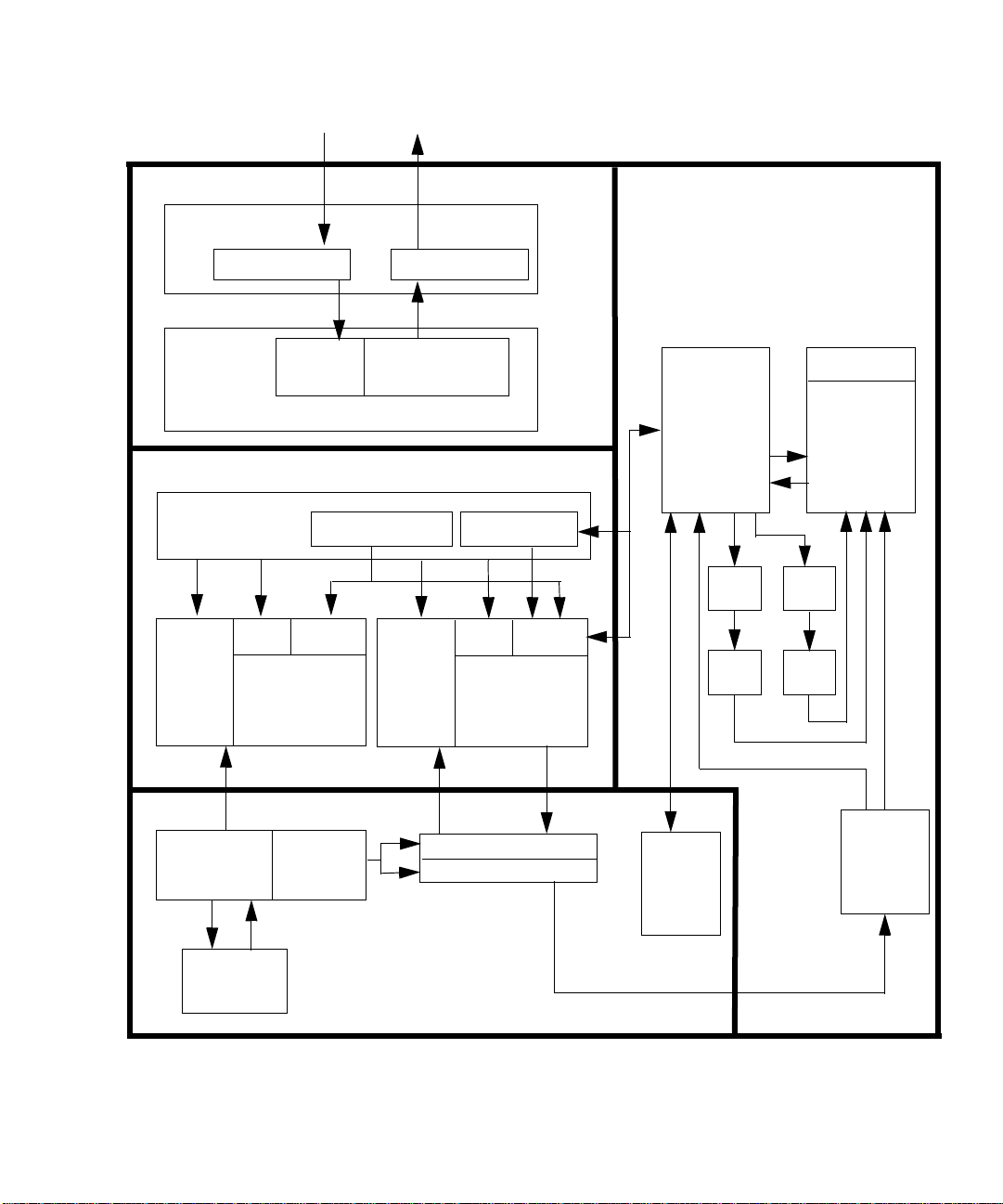

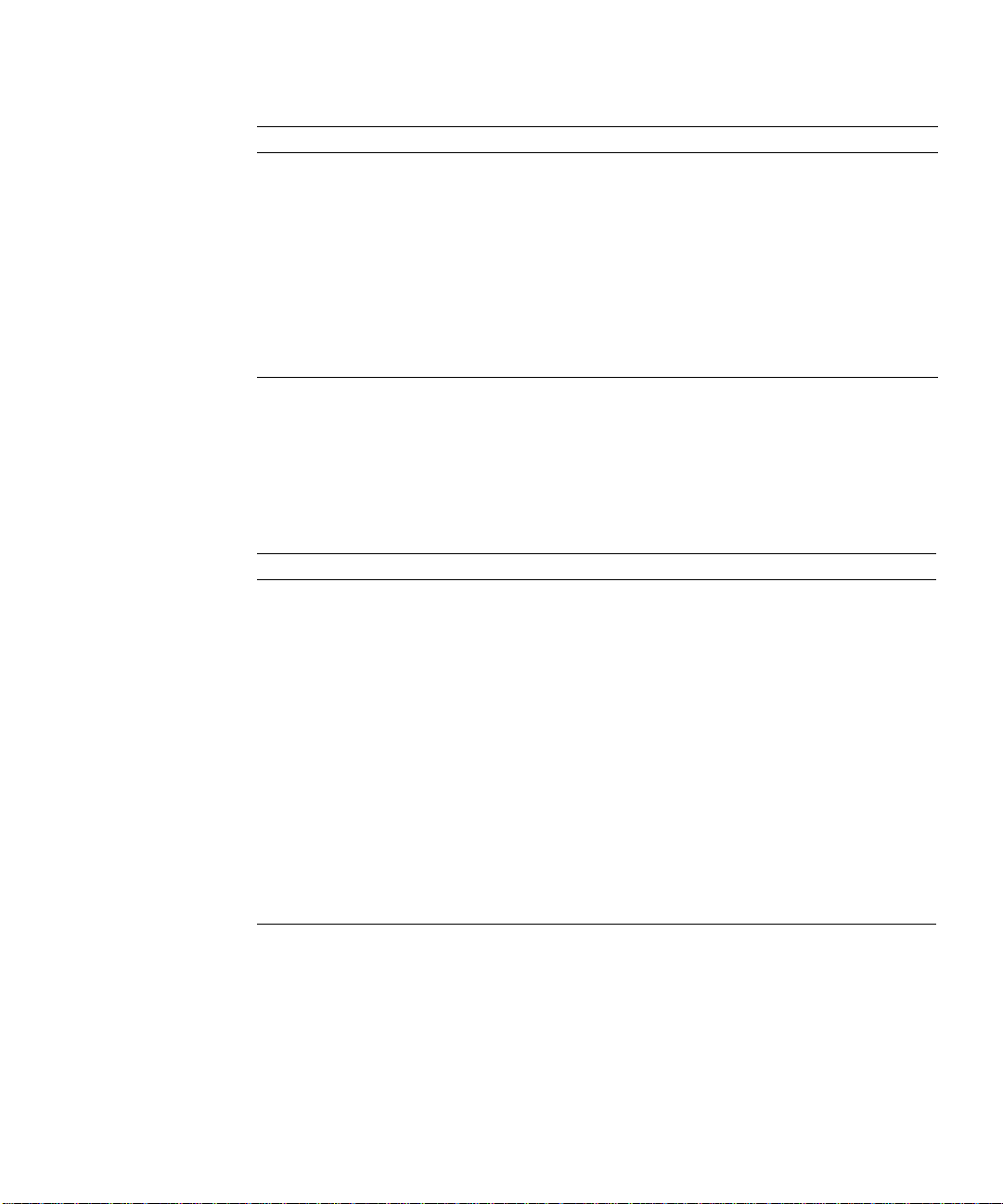

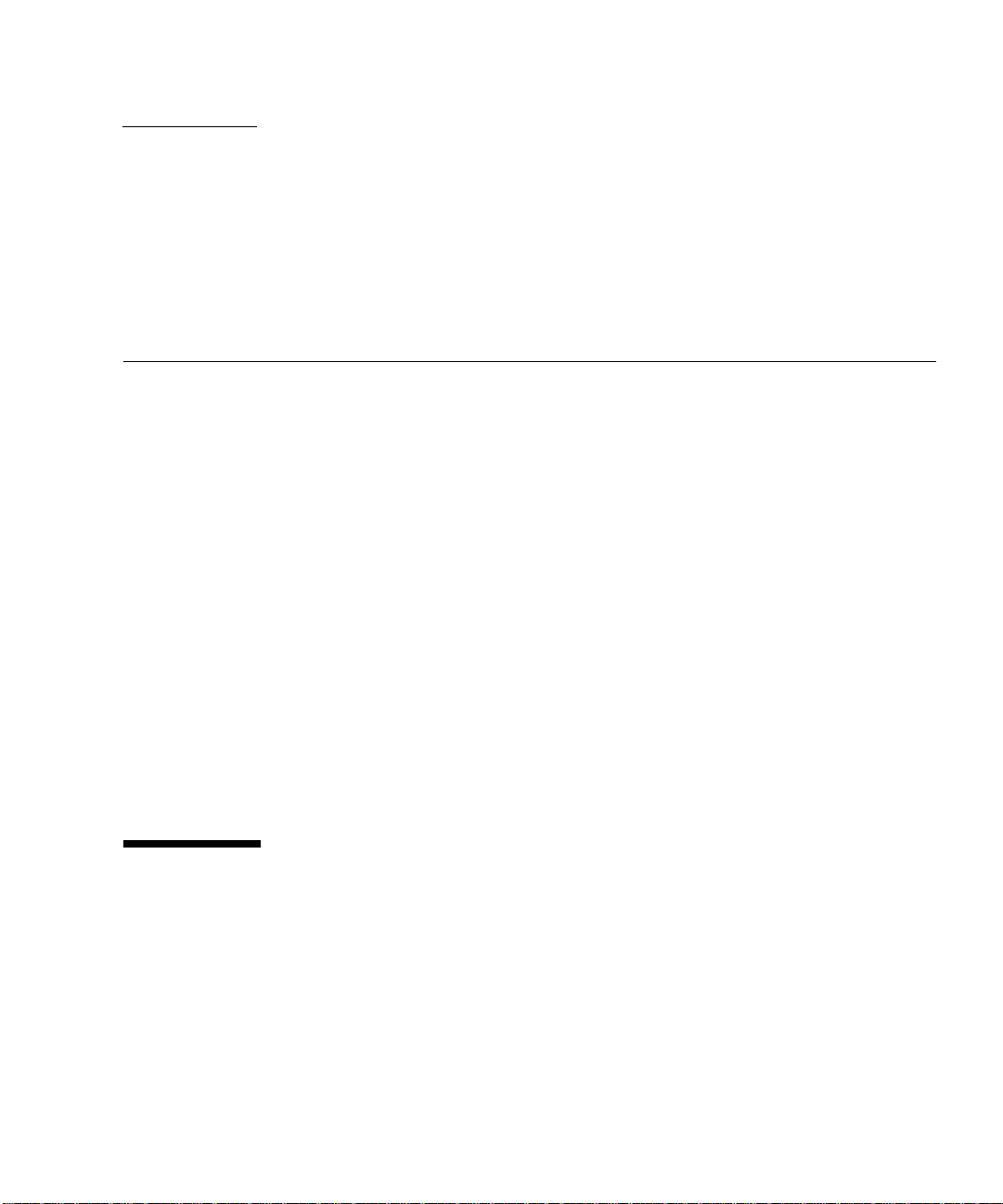

1.3.1 Component Overview

The SPARC64 V processor contains these components.

Instruction control Unit (IU)

■

Execution Unit (EU)

■

Storage Unit (SU)

■

Secondary cache and eXternal access Unit (SXU)

■

ADE

errors at the error barrier for correct

FIGURE 1-1

illustrates the major units; the following subsections describe them.

4 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 16

Extended UPA Bus

SX-Unit

UPA interface logic

MoveIn buffer

S-Unit interface

S-Unit

SX interface

I-TLB tag data

2048

+ 32

entry

Level-1 I cache

128 KB, 2-way

MoveOut buffer

U2$ U2$ data

tag 2M 4-way

SX order queue Store queue

D-TLB tag data

2048

+ 32

entry

Level-1 D cache

128 KB, 2-way

E-Unit

ALU

Input

Registers

and

Output

Registers

GUB FUB

GPR FPR

ALUs

EXA

EXB

FLA

FLB

EAGA

EAGB

I-Unit

Instruction Instruction

fetch buffer

pipeline

Commit stack entry

Reservation stations

PC

nPC

CCR

E-unit

control

logic

FSR

Branch

history

FIGURE 1-1

Release 1.0, 1 July 2002 F. Chapter 1 Overview 5

SPARC64 V Major Units

Page 17

1.3.2 Instruction Control Unit (IU)

The IU predicts the instruction execution path, fetches instructions on the predicted

path, distributes the fetched instructions to appropriate reservation stations, and

dispatches the instructions to the execution pipeline. The instructions are executed

out of order, and the IU commits the instructions in order. Major blocks are defined

TABLE 1-1

in

.

TABLE 1-1

Name Description

Instruction fetch pipeline Five stages: fetch address generation, iTLB access, iTLB match,

Branch history 16K entries, 4-way set associative.

Instruction buffer Six entries, 32 bytes/entry.

Reservation s tation Six reservation s tations to ho ld instructio ns until the y can

Commit stack entries Sixty-four ent ries; basica lly one inst ruction/ent ry, to hold

PC, nPC, CCR, FSR Program-vi sible regist ers for in structio n execu tion con trol.

Instruction Control Unit Major Blocks

I-Cache fetch, and a write to I-buffer.

execute: RSBR for branch and the other control-transfer

instructions; RSA for l oad/sto re instruction s; RSEA and RSEB for

integer arithmetic instructions; RSFA and RSFB for floating-point

arithmetic and V IS instructio ns.

information about instructions issued but not yet committed.

1.3.3 Execution Unit (EU)

The EU carries out execution of all integer arithmetic, logical, shift instructions, all

floating-point instructions, and all VIS graphic instructions.

EU major blocks.

TABLE 1-2

Execution Un it Major B locks

TABLE 1-2

describes the

Name Description

General register (gr) renaming

regis te r fi le (GUB: gr update

buffer)

Gr a rch ite ctu re re gis te r fi le ( GPR) 160 entries, 1 read port, 2 write ports

Floating-point (fr) renaming

regis te r fi le (FUB: fr update

buffer)

Fr arc hi tec ture reg is ter fil e (FPR )Thirty-two entries,

EU control logic Controls the in struction exe cution sta ges: instru ction

6 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Thirty-two entries, 8 read ports, 2 write ports

Thirty-two entries, 8 read ports, 2 write ports

6 read ports, 2 write ports

selection, register read, and execution.

Page 18

TABLE 1-2

Name Description

Execution Un it Major B locks (C o n tinued)

Interface registers Input/output registers to other units.

Tw o integer ex ecution pipelin es

(EXA, EXB)

Two floating-point and graphics

execution pipelines (FLA, FLB)

Two virtual address adders for

memory access pipeline (EAGA,

EAGB)

1.3.4 Storage Unit (SU)

The SU handles all sourcing and sinking of data for load and store instructions.

TABLE 1-3

describes the SU major blocks.

64-bit ALU and shifters.

Each floating-point execution pipeline can execute floating

point multiply, floating point add/sub, floa ting-point

multiply and add, floating point div/sqrt, and floatingpoint graphi cs instruction .

Two 64- bit virtual addresses for load/store.

TABLE 1-3

Name Description

Storage Unit Major Blocks

Instruction level-1 cache 128-Kbyte, 2-way associative, 64-byte line; provides low latency

instruction source

Data level-1 cache 128-Kbyte, 2-way associative, 64-byte line, writeback; provides

the low latency data source for loads and stores.

Instruction Translation

Buffer

1024 entries, 2-way associative TLB for 8-Kbyte pages,

1

1024 entries, 2-way associative TLB for 4-Mbyte pages

32 entries, fully associative TLB for unlocked 64-Kbyte, 512-

Kbyte, 4-Mbyte

1

pages and locked pages in all sizes.

,

Data Translation Buffer 1024 entries, 2-way associative TLB for 8- Kbyte pages,

1024 entries, 2-way associative TLB for 4-Mbyte pages

32 entries, fully associative TLB for unlocked 64-Kbyte, 512-

Kbyte, 4-Mbyte

1

pages and locked pages in all sizes.

1

,

Store queue Decouples the pipeline from the latency of store operations.

Allows the pipeline t o contin ue flowing while the store w aits for

data, and eventually writes into the data level 1 cache.

1. Unloced 4-Mbyte page entry is stored either in 2-way associative TLB or fully associative

TLB exclusively, depending on the setting.

Release 1.0, 1 July 2002 F. Chapter 1 Overview 7

Page 19

1.3.5 Secondary Cache and External Access Unit (SXU)

The SXU controls the operation of unified level-2 caches and the external data access

interface (extended UPA interface).

TABLE 1-4

describes the major blocks of the SXU.

TABLE 1-4

Name Description

Unified level-2 cache 2-Mbyte, 4-way associative, 64-byte line, writeback; provides low

Movein buffer Sixteen entries, 64-bytes/entry; catches returning data from

Moveout buffer Eight entries, 64-bytes/entry; holds writeback data. A maximum

Extended UPA interface

control logic

Secondary Cache and External Access Unit Major Blocks

latency data s ource for both instruction l evel-1 c ache and data

level-1 cache.

memory system in response to the cache line read request. A

maximum of 16 outstanding cache read operations can be issued.

of 8 outstanding writeback requests can be issued.

Send/receive transaction packets to/from Extended UPA

interface connected to the system.

8 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 20

F.CHAPTER

2

Definitions

This chapter defines concepts unique to the SPARC64 V, the Fujitsu implementation

of SPARC JPS1. For definition of terms that are common to all implementations,

please refer to Chapter 2 of Commonality.

committed Term applied to an instruction when it has completed w ithout error and all

prior instructions have completed without error and have been committed. When

an instruction is committ ed, the state of the machine is permanently change d

to reflect the result of the ins truction; the previously existing state is no longer

needed and can be disca rded.

completed Term applied to an instruction after it has finished, has sent a no nerror stat us to

the issue unit, and all of its source operands are nonspeculative. Note:

Although the state of the machine has been temporarily altered by completion

of an instruction, th e state has not y et been permanentl y changed and the old

state can be recovered until the instruction has been committed.

executed Te rm applied to an instru ction that ha s been proces sed by an execution u nit

such as a load unit. An instruction is in execution as long as it is still being

processed by an execution unit.

fetched Term applied to an instruction that is obtained from the I2 instruction cache or

from the on-chip internal cache an d sent to the i ssue unit.

finished Term applied to an instruction when it has completed execution in a functional

unit and has forwarded its result onto a result bus. Results on the result bus are

transferred to the register file, as are the waiting instructions in the instruction

queues.

initiated Term applied to an inst ruct ion wh en it ha s al l of t he resources that it nee ds (fo r

example, source operands) and has been selected for execution.

instruction dispatch Synonym: instruction initiation.

instruction issued Term applied to an instruction whe n it has bee n dispatched to a reservation

station.

9

Page 21

instruction retired Term applied to an instruct ion when all machine resources (s erial numbers,

renamed registers) have been reclaimed and are avai lable for use by o ther

instructions. An instruc tion can only be retired after it has been committed.

instruction stall Term applied to an instruc tion that is not allowed to be issu ed. Not every

instruction can be issued in a given cycle. The SPARC64 V implementation

imposes certain issue constraints bas ed on resource availability and program

requirements.

issue-stalling

instruction An instruction that prevents ne w instructions from being is sued until it has

committed.

machine sync The state of a machine when all previously executing instructions have

committed; that is, when no i ssued but uncommitted instructions are in the

machine.

Memory Manageme nt

Unit (MMU) Refers to the address translation h ardware in SPARC6 4 V that translates 64-bit

virtual address in to physica l address. The MMU is co mposed of the mITLB,

mDTLB, uITLB, uDTLB, and the ASI registers used to manage address

translation.

mTLB Main TLB. Sp lit into I and D, cal led m ITLB and mD TLB, respe ctive ly. Contains

address translations for the uITLB and uDTLB . When the uITLB o r uDTLB do

not contain a translatio n, they ask the mTLB for the translation. If the mTLB

contains the translation, it sends the tran slation to the respective uTLB. If the

mTLB does not contain the translation, it ge nerates a fast access exceptio n to a

software translation trap handler, which will load the translation information

(TTE) into the mTLB and retry the access. See also TLB.

uDTLB Micro Data TLB. A small, fully associative buffer that contains address

translations for data accesses. Misses in the uDTLB are handled by the mTLB.

uITLB Micro Instruction TLB. A small , fully associ ative buffer that contai ns address

translations for instruction accesses. Misses in the uTLB are han dled by th e

mTLB.

nonspeculative A distri bution syst em whereby a result i s guaranteed known cor rect or an

operand stat e is known to be valid . SPARC64 V employs sp eculative

distribution, meaning that results can be distributed from functional units

before the point at which guaranteed validity of the result is known.

reclaimed The status when all instruction-related resources that were held until commit

have been released and are availabl e for subsequent instructions. Instruct ion

resources are usually reclaimed a few cycles after they are committed.

rename registers A large set of hardware registers implemented by SPARC64 V that are invisible

to the programmer. Before instructions are issued, source and destination

registers are mapped on to this s et of rename registers. This al lows inst ructions

that normally would be blocked, waiting for an architected register, to proceed

10 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 22

in parallel . When i nstruction s are committed, results in renamed registers are

posted to the architected registers in the proper sequence to produce the correct

program results.

scan A method used to initialize all of the machine state within a chip. In a chip that

has been desi gned to be scann able, a ll of t he machin e state is conne cted i n one

or several loops c alled “scan ri ngs.” Initi alization data can be sca nned into the

chip through the scan rings. The state of the machine also can be s canned out

through the scan rings.

reservation station A holding location that b uffers di spatc h ed in struc ti ons u nt il al l i nput o pera nds

are available. SPARC64 V implements dataflow execution based on operand

availability. When opera nds are availabl e, the in structions in the reservation

station are scheduled for ex ecution. Reservati on stations also contai n special

tag-matching logic that captures the appropriate operand data. Reservation

stations are sometimes referred to as queues (for example, the integer queue).

speculative A distribution syst em whereby a result is not g uaranteed as kn own to be

correct or an operan d state is not known to be valid. SPARC64 V employs

speculative distribution, meaning results can be distributed from functional

units before the point at which guaranteed validity of the result is known.

superscalar An implementation that allows several instructions to be issued, executed, and

committed in one clock cycle. SPARC64 V issues up to 4 instructions per clock

cycle.

sync Synonym: machine sync.

syncing instruction An instruction that causes a machine sync. Thus, before a syncing instruction is

issued, all previo us instructions (in program order) must hav e been committed.

At that point, the syncing instruction is issued, executed, completed, and

committed by itself.

TLB Translation l ookaside b uffer.

Release 1.0, 1 July 2002 F. Chapter 2 Definitions 11

Page 23

12 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 24

F.CHAPTER

3

Architectural Overview

Please refer to Chapter 3 in the Commonality section of SPARC Joint Programming

Specification.

13

Page 25

14 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 26

F.CHAPTER

4

Data Formats

Please refer to Chapter 4, Data Formats in Commonality.

15

Page 27

16 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 28

F.CHAPTER

5

Registers

The SPARC64 V processor includes two types of registers: general-purpose—that is,

working, data, control/status—and ASI registers.

The SPARC V9 architecture also defines two implementation-dependent registers:

the IU Deferred-Trap Queue and the Floating-Point Deferred-Trap Queue (FQ);

SPARC64 V does not need or contain either queue. All processor traps caused by

instruction executio n are precise, and there are severa l disruptin g traps cause d by

asynchronous events, such as interrupts, asynchronous error conditions, and

RED_state entry traps.

For general information, please see parallel subsections of Chapter 5 in

Commonality. For easier referencing, this chapter follows the organization of

Chapter 5 in Commonality.

For information on MMU registers, please refer to Section F.10, Inte rnal Regist ers and

ASI operations, on page 9 2.

The chapter contains these sections:

■

Nonprivileged Regi sters on page 17

■

Privileged Registers on page 19

5.1 Nonprivileged Register s

Most of the definitions for the registers are as described in the corresponding

sections of Commonality. Only SPARC64 V-specific features are described in this

section.

17

Page 29

5.1.7 Floating-Point State Register (FSR)

Please refer to Section 5.1.7 of Commonality for the description of FSR.

The sections below describe SPARC64 V-specific features of the FSR regi st er.

FSR_nonstandard_fp (NS)

SPARC V 9 defines th e FSR.NS bit which, when set to 1, causes the FPU to produce

implementation-dependent results that may not conform to IEEE Std 754-1985.

SPARC 64 V implements th is bit.

When FSR.NS = 1, denormal input operands and denormal results that would

otherwise trap are flushed to 0 of the same sign and an inexact exception is signalled

(that may be masked by FSR.TEM.NXM). See Section B.6, Floating-Point Nonstandard

Mode, on page 61 for details.

When FSR.NS = 0, the normal IEEE Std 754-1985 behavi or is implemented.

FSR_version (

For each SPARC V9 IU implementation (as identified by its VER.impl field), there

may be one or more FPU implementations or none. This field identifies the

particular FPU implementation present. For the first SPARC64 V, FSR.ver =0 (impl.

dep. #19); however, future versions of the architecture may set FSR.ver to other

values. Consult the SPARC64 V Data Sheet for the setting of FSR.ver for your

chipset.

FSR_floating-point_trap_type (

The complete conditions under which SPARC64 V triggers

trap type

on page 61 (impl. de p. #248).

unfinished_FPop

)

ver

)

ftt

fp_exception_other

is described in Section B.6, Floating-Point Nonstandard Mode,

with

FSR_current_exception (cexc)

Bits 4 through 0 indicate that one or more IEEE_754 f loating-point exceptions were

generated b y the most recent ly execute d FPop inst ruction. Th e absence of an

exception causes the corresponding bit to be cleared.

In SPAR C64 V, the cexc bits are set according to the following pseudocode:

if (<LDFSR or LDXFSR commits>)

<update using data from LDFSR or LDXFSR>;

else if (<FPop commits with ftt = 0>)

<update using value from FPU>

18 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 30

else if (<FPop commits with IEEE_754_exception>)

<set one bit in the CEXC field as supplied by FPU>;

else if (<FPop commits with unfinished_FPop error>)

<no change>;

else if (<FPop commits with unimplemented_FPop error>)

<no change>;

else

<no change>;

FSR Conformance

SPARC V 9 allow s th e TEM, cexc, and aexc fields to be implemented in hardware in

either of two ways (both of which co mply with IEEE Std 754-1985) . SPAR C64 V

follows case (1); that is, it implements all t hree fields in conformance with IEEE Std

754-1985. See FSR Conform ance in Section 5.1.7 of Commonality for more

information about other implementation methods.

5.1.9 Tick (TICK) Register

SPARC64 V impl ements TICK.counter register as a 63-bit register (impl. dep.

#105).

Implementation Note –

when the TICK register is read is the value of TICK.counter when the RDTICK

instruction is executed. The difference between the counter values read from the

TICK register on two reads reflects the number of processor cycles executed between

the executions of the RDTICK instructions, not their commits. In longer code

sequences, the difference between this value and the value that would have been

obtained when the instructions are committed would have been small.

On SPARC64 V, the counter part of the value returned

5.2 Privileged Registers

Please refer to Section 5.2 of Commonality for the description of privileged registers.

5.2.6 Trap State (TSTATE) Register

SPARC64 V implem ents onl y bits 2: 0 of the TS TATE.CWP field. Writes to bits 4 and 3

are ignored, and reads of these bits always return zeroes.

Release 1.0, 1 July 2002 F. Chapter 5 Registers 19

Page 31

Note –

be performed, since it will take the SPARC64 V into RED_state withou t the

required sequencing.

Spurious set ting of t he PSTATE .RED bit by privileged software should not

5.2.9 Version (VER) Register

TABLE 5-1

TABLE 5-1

Bits Field Value

63:48 manuf 000416 (impl. dep. #104)

47:32 impl 5 (impl. dep. #13)

31:24 mask n (The value of n depends on the processor chip version)

15:8 maxtl 5

4:0 maxwin 7

The manuf field contains Fujitsu’s 8-bit JEDEC code in the lower 8 bits and zeroes in

the upper 8 bits. The manuf, impl, and mask fields are implemented so that they

may change in future SPARC64 V processor versions. The mask field is incremented

by 1 any time a programmer-visible revision is made to the processor. See the

SPARC64 V Data Sheet to determine the current setting of the mask field.

shows the values for the VER register for SPARC64 V.

VER

Register Encodings

5.2.11 Ancillary State Registers (ASRs)

Please refer to Section 5.2.11 of Commonality for details of the ASRs.

Performance Control Register (PCR) (ASR 16)

SPARC64 V implements the PCR register as described in SPARC JPS1 Commonality,

with additional features as described in this section.

In SPARC 64 V, the accessibili ty of PCR when PSTATE.PRIV = 0 is determined by

PCR.PRIV. If PSTATE.PRIV =0 and PCR.PRIV = 1, an attempt to execu te either

RDPCR or WRPCR will cause a

PCR.PRIV =0, RDPCR operates without privilege violation and WRPCR causes a

privileged_action

to) PCR.PRIV (impl. dep. #2 50).

See Appendix Q, Perf ormance Instr umentation , for a detailed discussion of the PCR

and PIC register usage and event count definitions.

20 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

exception only when an attempt is made to change (that is, write 1

privileged_action

exception. If PSTATE.PRIV =0 and

Page 32

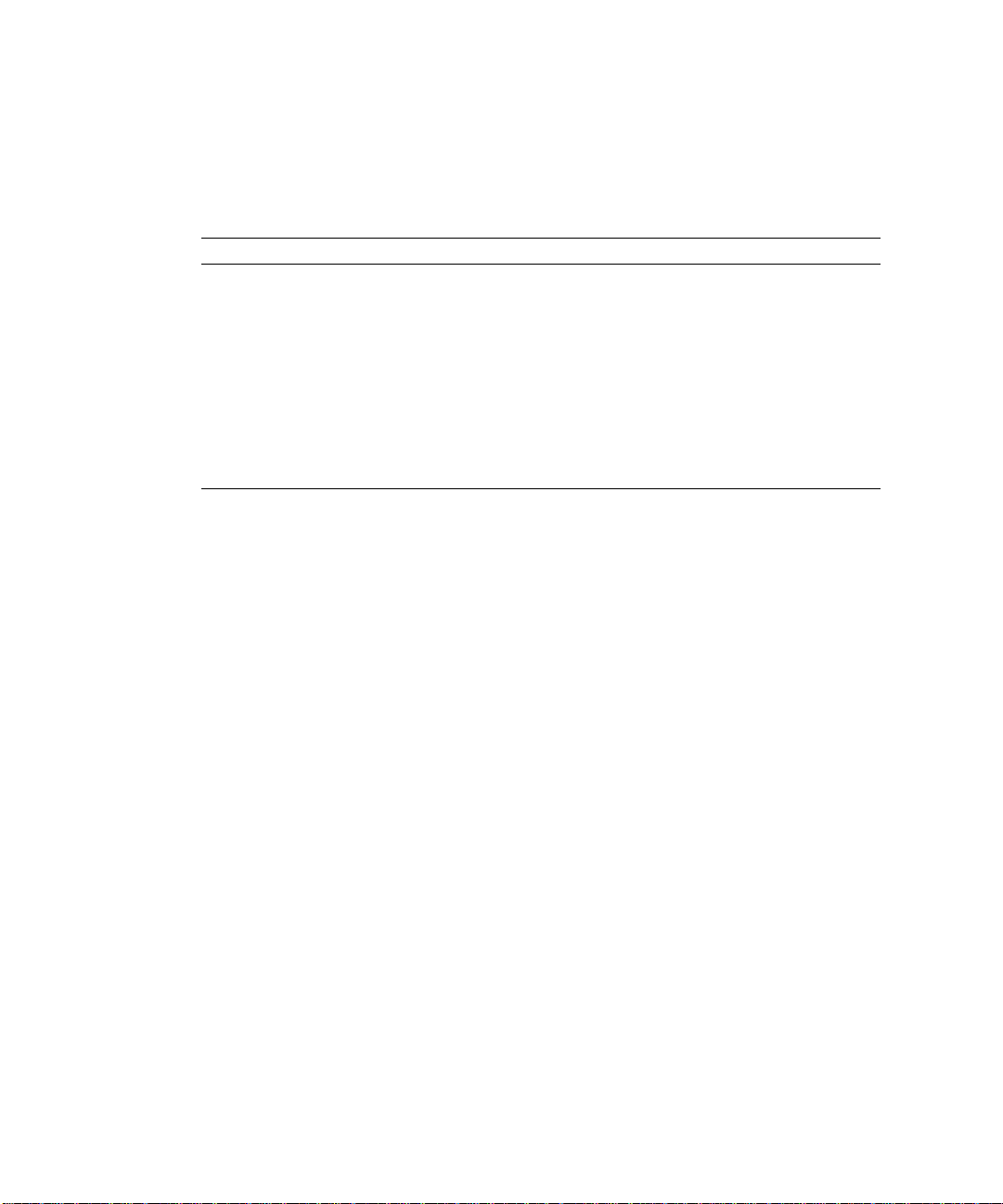

The Performance Control Register in SPARC64 V is illustrated in

described in

TABLE 5-2

.

FIGURE 5-1

and

0

63 16 10

TABLE 5-2

Bit Field Description

OVF 0 SLSU0SC

4748

FIGURE 5-1

PCR

Bit Description

0

26273132

SPARC64 V Performance Control Register (PCR) (ASR 16)

NC

0OVRO

25

0

21

2224

1718

20

9

ULRO UT ST PRIV

40

12311

47:32 OVF Overflow Clear/Set/Status. Used to read counter overflow status (via RDPCR) and cle ar

or set counter overflow status bits (via WRPCR). PCR.OVF is a SPARC64 V-specific f ield

(impl. dep. #207).

The following figure depicts the bit layout of SPARC64 V OVF field for four counter

pairs. Counter status bits are cleared on write of 0 to the appropriate OVF bit.

L2U2L3U3

15

L0U0L1U10

01234567

26 OVRO Overflow read-only. Write-only/read-as-zero field specifying PCR.OVF update behavior

for WRPCR. P CR. The OVRO field is implementation -dependent (impl. dep. #207).

WRPCR.PCR with PCR.OVRO = 1 inhibits updating of PCR.OVF for the current write

only. T he intention of PCR.OVRO is t o write PCR while preserving current PCR.OVF

value. PCR.OVF is maint ained inter nally by h ardware, so a sub sequent R DPCR .PCR

returns accurate overflow status at the time.

24:22 NC Number of c ounter pa irs. Three- bit, read-o nly field specifyi ng the n umber of counter

pairs, encoded as 0–7 for 1–8 counter pairs (impl. dep. #207).

For SPARC64 V, the hardcoded value of NC is 3 (indicating presence of 4 counter pairs).

20:18 SC Select PIC. In SPARC64 V, three-bit field specif ying which c ounter p air is currently

selected as PIC (ASR 17) and which SU/SL values are visible to software. On write,

PCR.SC selects which counter pair is updat ed (unless PCR. ULRO is set; see below). On

read, PCR.SC selects which counter pair is to be read through PIC (ASR 17).

16:11 SU Defined (as S1) in SPARC JPS1 Commonality.

9:4 SL Defined (as S0) in SPARC JPS1 Commonality.

3 ULRO Implementation-dependent field (impl. dep. #207) that specifies whether SU/SL are

read-only. In SPARC64 V, this field is write-only/read-as-zero, specifying update

behavior of SU/SL on write. When PC R.ULR O = 1, SU/SL are considered as read-only;

the values s et on PCR.SU/P CR.SL are not written into SU/SL. When PCR.ULRO = 0,

SU/SL are updated. PCR.ULRO is intended to switch visible PIC by writing PCR.SC,

without affecting current selection of SU/SL of that PIC. On PCR read, PCR.SU/PCR.SL

always shows the current setting of the PIC regardless of PCR.ULRO.

2 UT Defi ned in SPARC JPS1 Commonality.

1 ST Defi ned in SPARC JPS1 Commonality.

Release 1.0, 1 July 2002 F. Chapter 5 Registers 21

Page 33

TABLE 5-2

Bit Field Description

0 PRIV Defined in SPARC JPS1 Commonality, with the additional function of controlling PCR

PCR

Bit Description (Continued)

accessibility as described above (impl. de p. #250).

Performance Instrumentation Counter (PIC) Register (ASR

17)

The PI C register is implemented as described in SPARC JPS1 Commonality.

Four PICs are implemented in SPARC64 V. Each is accessed through ASR 17, using

PCR.SC as a select field . Read/write acce ss to the PIC will access the PICU/PIC L

counter pair selected by PCR. For PICU/PICL enc odings of sp ecific ev ent counte rs,

see

Appendix Q, Performance Instrumentation

.

Counter Overflow.

and an interrupt level-15 exception is generated. The counter overflow trap is

triggered on th e trans ition f rom value FFFF FFFF

are generated simultaneously, then multiple overflow status bits will be set. If

overflow status bits are already set, then they remain set on counter overflow.

Overflow status bits are cleared by software writing 0 to the appropriate bit of

PCR.OVF and may be set by writing 1 to the appropriate bit. Setting these bits by

software does not generate a level 15 inte rrupt.

On overflow, counters wrap to 0, SOFTINT register bit 15 i s set,

to value 0. If multiple overflows

16

Dispatch Control Register (DCR) (ASR 18)

The DC R is not implemented in SPARC64 V. Zero is returned on read, and writes to

the register are ignored. The DCR is a privileged register; attempted access by

nonprivileged (user) code generates a

privileged_opcode

exception.

5.2.12 Registers Referenced Thro ugh ASIs

Data Cache Unit Control Register (DCUCR)

ASI 4516 (ASI_DCU_CONTROL_REGISTER), VA = 016.

The Data Cache Unit Control Register contains fields that control several memory-

related hardware functions. The functions include Instruction, Prefetch, write and

data caches, MMUs, and watchpoint setting. SPARC64 V implements most of

DCUCUR’s functions described in Section 5.2.12 of Commonality.

22 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 34

Aft er a p ow er- on re se t ( POR), all fields of DCUCR, including implementationdependent fields, are set to 0. After a WDR, XIR, or SIR reset, all fields of DCUCR,

including i mplement ation-d ependen t fields, are set to 0.

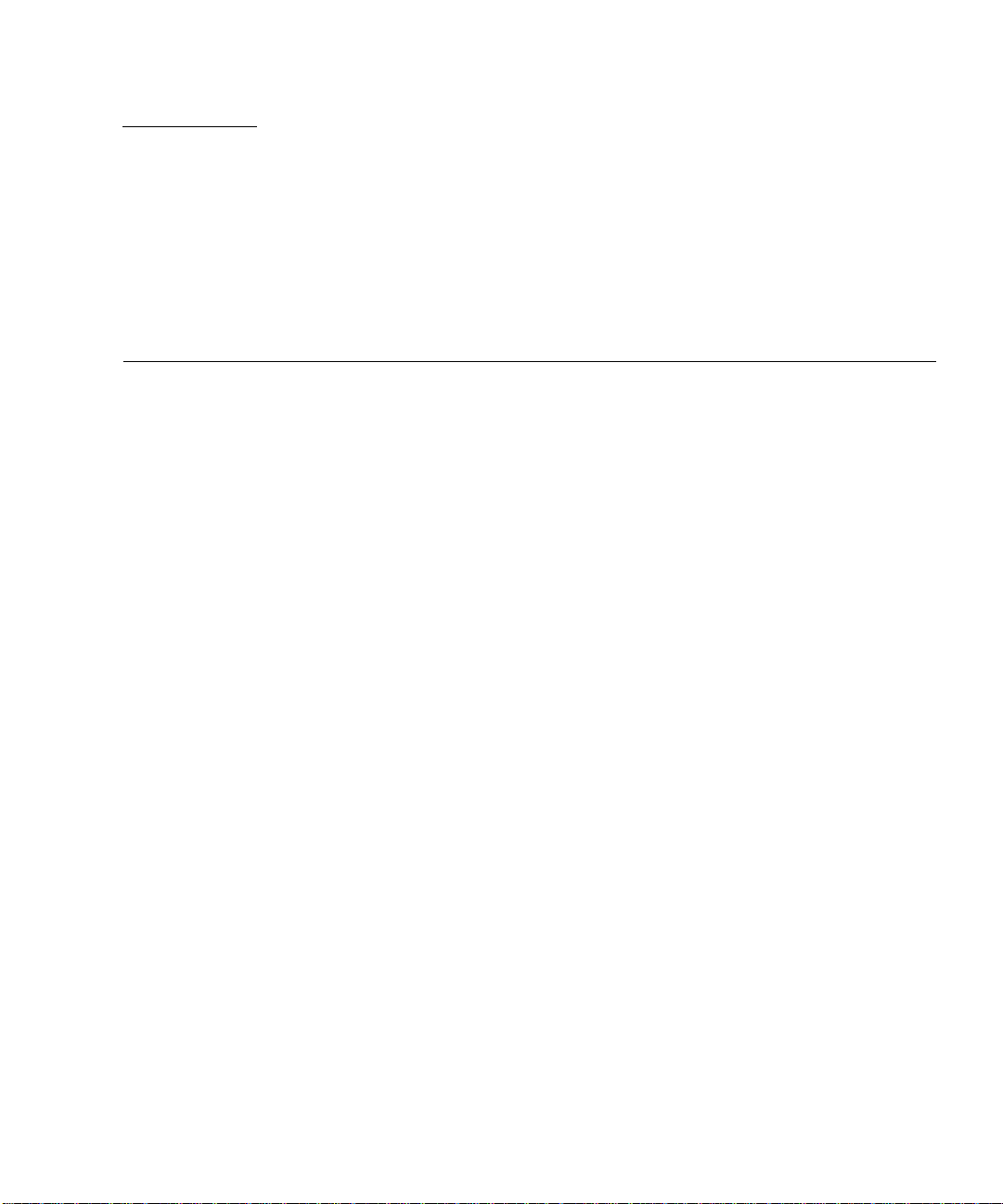

The Data Cache Unit Control Register is illustrated in

TABLE 5-3

—

5063

TABLE 5-3

Bits Field Type Use — Description

0

Implementation dependent PM VM PR PW VR DM 0

0

4849

FIGURE 5-2

DCUCR Description

. In the table, bits are grouped by function rather than by strict bit sequence.

WEAK_SPCA

41

DCU Control Register Access Data Format (ASI 4516)

2425323347

FIGURE 5-2

VW

and described in

—

IM 0

012342122234042 20

49:48 CP, CV RW No t implemented in SPARC64 V (impl. dep. #232). It reads as 0 and writes to

it are ignored.

47:42 impl. dep. Not used. It reads as 0 and writes to it are ignored.

41 WEAK_SPCA RW U sed for disabling speculative memory access (impl. dep. #240). When

DCUCR.WEAK_SPCA = 1, the branch history table is cleared and no longer

issues aggressive instruction prefetch.

During DCU CR.WE AK_SP CA = 1, aggressive in struction prefet ching is

disabled and any load and store instructions are considered presync

instructions that are executed w hen all previo us instruction s are committed .

Because all CTI are considered as not taken, instructions residing beyond 1

Kbyte of a CTI may be fetched and executed.

On entering aggressive instruction Prefetch disable mode, supervisor

software should issue membar #Sync, to make sure all in-flight instructions

in the pipeline are discarded.

During DCU CR.WE AK_SP CA = 1, an L2 cache flush by writing 1 to

ASI_L2_CTRL.U2_FLUSH remains pending internally until

DCUCR.WEAK_SPCA is set to 0. To wait for completion of the cache flush, a

member #Sync must be issued after DCUCR.WEAK_SPCA is set to 0.

Executing a membar #Sync while the DCUCR.WEAK_SPCA = 1 after writing 1

to ASI_L2_CTRL. U2_FL USH d oes not w ait for th e cache flush to co mplete .

40:33 PM<7:0> Defined in SPARC JPS1 Commonality.

32:25 VM<7:0> Defined in SPARC JPS1 Commonality.

24, 23 PR, PW Defined in SPARC JPS1 Commonality.

22, 21 VR, VW Defined in SPARC JPS1 Commonality.

20:4 — Reserved.

3 DM Defined in SPARC JPS1 Commonality.

2 IM Defined in SPARC JPS1 Commonality.

Release 1.0, 1 July 2002 F. Chapter 5 Registers 23

Page 35

TABLE 5-3

Bits Field Type Use — Description

1 DC RW Not implemented in SPARC64 V (impl. dep. #252). It reads as 0 and writes to

0 IC RW Not implemented in SPARC64 V (impl. dep. #253). It reads as 0 and writes to

DCUCR Description (Continued)

it are ignored.

it are ignored.

Data Watchpoint Registers

No implement ation-dep endent feature o f SPAR C64 V reduces the reli ability of da ta

watchpoints (imp l. dep. #244).

SPARC64 V employs conservative check of PA/VA watchpoint over partial store

instruction. See Section A.42, Partial Store (VIS I), on page 57 for details.

Instruction Trap Regist er

SPARC64 V implements the Inst ruction Trap Register (impl. dep. #20 5).

In SPARC64 V, the least significant 11 bits (bits 10:0) of a CALL or branch (BPcc,

FBPfcc, Bicc, BPr) instruction in an instruction cache are identical to their

architectural encoding (as it appe ars in main memory) (impl. dep. #245).

5.2.13 Floating-Point Deferred-Trap Queue (FQ)

SPARC64 V does not contain a Floating-Point Deferred-trap Queue (impl. dep. #24).

An attempt to read FQ with an RDPR instruction generates an

exception (impl. de p. #25).

illegal_instruction

5.2.14 IU Deferred-Trap Queue

SPARC64 V neither has nor needs an IU deferred-trap queue (impl. dep. #16)

24 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 36

F.CHAPTER

6

Instructions

This chapter presents SPARC64 V implementation-specific instruction details and the

processor pipeline information in these subsections:

■

Instruction Execution on page 25

■

Instructi on Format s and Field s on page 28

■

Instruction Categories on page 29

■

Processor Pipel ine on page 31

For additional, general information, please see parallel subsections of Chapter 6 in

Commonality. For easy referencing, we follo w the organization of Chapter 6 in

Commonality.

6.1 Instruction Execution

SPARC64 V is an advanced superscalar imp lementation of SPARC V9. Several

instructions may be issued and executed in parallel. Although SPARC64 V provides

serial program execution semanti cs, some of the implemen tation ch aracteri stics

described below are part of the architecture visible to software for correctness and

efficiency. The affected software includes optimizing compilers and supervisor code.

6.1.1 Data Prefetch

SPARC64 V employs speculative (out of program order) execution of instructions; in

most cases, the effect of these instructions can be undone if the speculation proves to

be incorrect.

prefetching. Formally, SPARC64 V employs the following rules regarding speculative

prefetching:

1. An async_data_error may be signalled during speculative data pref etching.

1

However, exceptions can occur because of speculative data

25

Page 37

1. If a memory operation y resolves to a volatile memory address (location[y]),

SPARC64 V will not speculatively prefetch location[y] for any re ason; location[y]

will be fetched or stored to only when operation y is commitable.

2. If a memory opera tion y resolves to a nonvolatile memory address (location[y]),

SPARC64 V may speculatively prefetch location[y] subject, adhering to the

following subrules:

a. If an operation y can be speculatively prefetched according to the prior rule,

operations with store semantics are speculatively prefetched for ownership

only if they are prefetched to cacheable locations. Operations without store

semantics are speculatively prefetched even if they are noncacheable as long as

they are not volatile.

b. Atomic operations (CAS(X)A, LDSTUB, SWAP) are never speculatively

prefetched.

SPARC64 V provides two mechanisms to avoid speculative execution of a load:

1. Avoid specul ation by disallowing speculative accesses to certain memory pages or

I/O spaces.

This can be done by setting the E (side-effect) bit in the PTE for all

memory pages that should not allow speculation. All accesses made to memory

pages that have th e E bit set in their PTE will be delayed until they are no longer

speculativ e or unt il the y are canc elle d

.

See Appendix F, Memory Mana geme nt Unit,

for details.

2. Alternate space load instructions that force program order, such as

ASI_PHYS_BYPASS_WITH_EBIT[_L] (AS I = 15

, 1D16), will not be speculatively

16

executed.

6.1.2 Instruction Prefetch

The processor prefetches instructions to minimize cases where the processor must

wait for instruction fetch. In combination with branch prediction, prefetching may

cause the processor to access instructions that are not subsequently executed. In

some cases, the specula tive instruction accesses w ill reference data pages.

SPARC64 V does not generate a trap for any exception that is caused by an

instruction fetch until all of the instructions before it (in program order) have been

committed.

1. Hardware errors and other asynchronous errors may generate a trap even if the instruction that caused the

trap is never committed.

26

SPARC JPS1 Implementation Supplement:

1

Fujitsu SPARC64 V

• Release 1.0, 1 July 2002

Page 38

6.1.3 Syncing Instructions

SPARC64 V has instructions, called syncing instructions, that stop execution for the

number of cycles it takes to clear the pipeline and to synchronize the processor.

There are two types of synchronization, pre and post. A presyncing instruction waits

for all previous instructions to commit, commits by itself, and then issues successive

instructions. A postsyncing instruction issues by itself and prevents the successive

instructions from issuing until it is committed. Some instructions have both pre- and

postsync attributes.

In SPARC64 V almost all instructions commit in order, but store instruction commit

before becoming globally visible. A few syncing instructions cause the processor to

discard prefetched instructions an d to refetch the successive i nstructions.

lists all pre-/postsync instructions and the effects of instruction execution.

TABLE 6-1

TABLE 6-1

Opcode

ALIGNADDRESS{_LITTLE} Yes

BMASK Yes

DONE Yes Yes

FCMP(GT,LE,NE,EQ)(16,32)Yes

FLUSH Yes Yes Yes

FMOV(s,d)icc Yes

FMOVr Yes

LDD Yes Yes

LDDA Yes Yes

LDDFA Yes

memory access with

ASI=ASI_PHYS_BYPASS_EC{_LI TTLE} ,

ASI_PHYS_BYPASS_EC_WITH_E_ BIT{_ LITTL E}

LDFSR, LDXFSR Yes

MEMBAR Yes Yes

MOVfcc Yes

MULScc Yes

PDIST Yes

RDASR Yes

RETRY Yes Yes

SIAM Yes

STBAR Yes

STD Yes

SPARC64 V Syncing Instructions

Presyncing Postsyncing

Sync?

Yes

Wai t fo r

store global

visibility?

1

Sync?

Yes

Discard

prefetched

instructions?

Release 1.0, 1 July 2002 F. Chapter 6 Instructions 27

Page 39

TABLE 6-1

Opcode

SPARC64 V Syncing Instructions (Conti nued)

Sync?

Presyncing Postsyncing

Wai t fo r

store global

visibility?

Sync?

Discard

prefetched

instructions?

STDA Yes

STDFA Yes

STFSR, STXFSR Yes

Tcc Yes Yes Yes

WRASR Yes

cmask !=0

1. When

WRGSR

2.

#

only.

.

2

Yes

6.2 Instruction Formats and Fields

Instructions are encoded in five major 32- bit formats and several mino r formats.

Please refer to Section 6.2 of Commonality for illustrations of four major formats.

FIGURE 6-1

Format 5 (op = 2, op3 = 3716): FMADD, FMSUB, FNMADD, and FNMSUB (in place of IMPDEP2B)

illustrates Format 5, unique to SPARC64 V.

op3rdop rs1 rs3 rs2var

31 141924 18 13 12 5 4 02530 29 11 10 9 7 617 8

FIGURE 6-1

Summary of Instruction Formats: Format 5

Instruction fields are those shown in Section 6.2 of Commonality. Three additional

fields are implemented in SPARC64 V. They are described in

TABLE 6-2

Bits Field Description

Instruction Fields Specific to

13:9 rs3 This 5-bit field is the address of the third f register source operand for

the floating-poin t multiply-a dd and multipl y-subtract in struction.

8.7 var This 2-bit field specifi es which s pecific op eration (variation) to perfor m

for the floating-po int multiply-ad d and multip ly-subtract instruc tions

6.5 size This 2-bit field specifies the size of the operands for the floating-point

multiply-add an d multiply-s ubtract ins tructions.

28 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

SPARC64 V

TABLE 6-2

size

.

Page 40

size

Since

= 00 is not

IMPDEP2B

and since

size

is not implemented in SPARC64 V, the instruction with

illegal_instruction

exception in SPARC64 V.

6.3 Instruction Categories

SPARC V9 instructions comprise the categories listed below. All categories are

described in Section 6.3 of Commonality. Subsections in bold face are SPARC64 V

implementation dependencies.

■

Memory access

■

Memory synchronization

■

Integer arithmetic

■

Control transfer (CTI)

■

Conditional moves

■

Register window management

■

State register access

■

Privileged register access

■

Floating-point operate (FPop)

■

Implementation-dependent

= 11 assumed quad operati ons but

= 00 or 11 generates an

size

6.3.3 Control-Transfer Instructions (CTIs)

These are the basic control-transfer instruction types:

■

Conditional branch (Bicc, BPcc, BPr, FBfcc, FBPfcc)

■

Unconditional branch

■

Call and link (CALL)

■

Jump and link (JMPL, RETURN)

■

Return from trap (DONE, RETRY)

■

Tr ap ( Tcc)

Instructions other than CALL and JMPL are described in their entirety in Section 6.3.2

of Commonality. SPARC64 V implements CALL and JMPL as described below.

CALL and JMPL Instructions

SPARC64 V writes all 64 bits of the PC into the destination register when

PSTATE.AM = 0. The upper 32 bits of r[15] (CALL) or of r[rd] (JMPL) are written

as zeroes when PSTATE.AM = 1 (impl. dep. #125).

Release 1.0, 1 July 2002 F. Chapter 6 Instructions 29

Page 41

SPARC64 V im plements JMPL and CALL return prediction hard ware in a form of

special stack, called the Return Address Stack (RAS). Whenever a CALL or JMPL that

writes to %o7 (r[15]) occurs, SPARC64 V “push es” the return address (PC+8) onto

the RAS. When either of the synthetic ins truct ions retl (JMPL [%o7+8]) and ret (JMPL

[%i7+8]) are subsequently executed, the return address is predicted to be the

address stored on the top of th e RAS and the RAS is “popped.” If the prediction in

the RAS is incorrect, SPARC64 V backs up and starts issuing instructions from the

correct target address. This backup takes a few extra cycles.

Programming Note –

take into account how the RAS works. For example, tricks that do nonstandard

returns in hopes of boosting performance may require more cycles if they cause the

wrong RAS value to be used for predicting the address of the return. Heavily nested

calls can also cause earlier entries in the RAS to be overwritten by newer entries,

since the RAS only has a limited number of entries. Eventually, some return

addresses will be mispredicted because of the overflow of the RAS.

For maximum performance, software and compilers must

6.3.7 Floating-Point Operate (FPop) Instructions

The complete conditions of generating an

FSR.ftt =

Mode on page 61.

The SPARC64 V-specific FMADD and FMSUB instructions (described below) are also

floating-point operations. They require the floating-point unit to be enabled;

otherwise, an

instructions. However, these instructions are not included in the FPop category and,

hence, reserved encodings in these opcodes generate an

defined in Section 6.3.9 of Commonality.

unfinished_FPop

fp_disabled

trap is generated. They also affect the FSR, like FPop

are described in Section B. 6, Floating-Point Nonstandard

fp_exception_other

illegal_instruction

excepti on with

6.3.8 Implementation-Dependent Instructions

exception, as

SPARC64 V uses the IMPDEP2 instruction to implement the Floating-Point MultiplyAdd/Subtract and Negative Multiply-Add/Subtract instructions; these have an op3

field = 37

definitions of these instructions. Opcode space is reserved in IMPDEP2 for the quadprecision forms of these instructions. However, SPARC64 V does not currently

implement the quad-precision forms, and the processor generates an

exception if a quad-precision form is specified. Since these instructions are not part

of the required SPARC V9 architecture, the operating system does not supply

software emulat ion routines f or the quad v ersions of these instruc tions.

SPARC64 V uses the IMPDEP1 instruction to implement the graphics acceleration

instructions.

30 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

(IMPDEP2). See Floating-Point Multiply-Add/Subtract on page 50 for fuller

16

illegal_instruction

Page 42

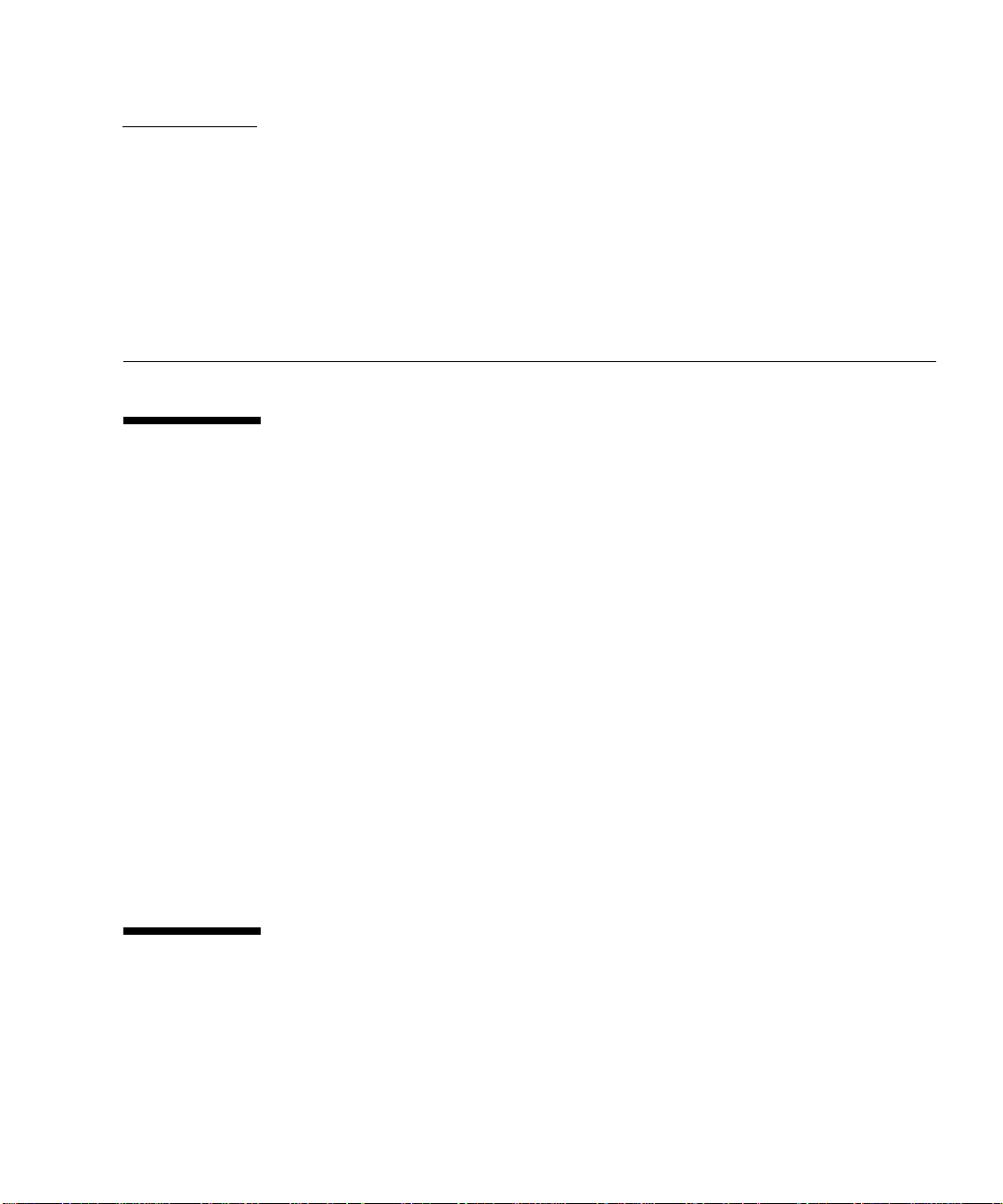

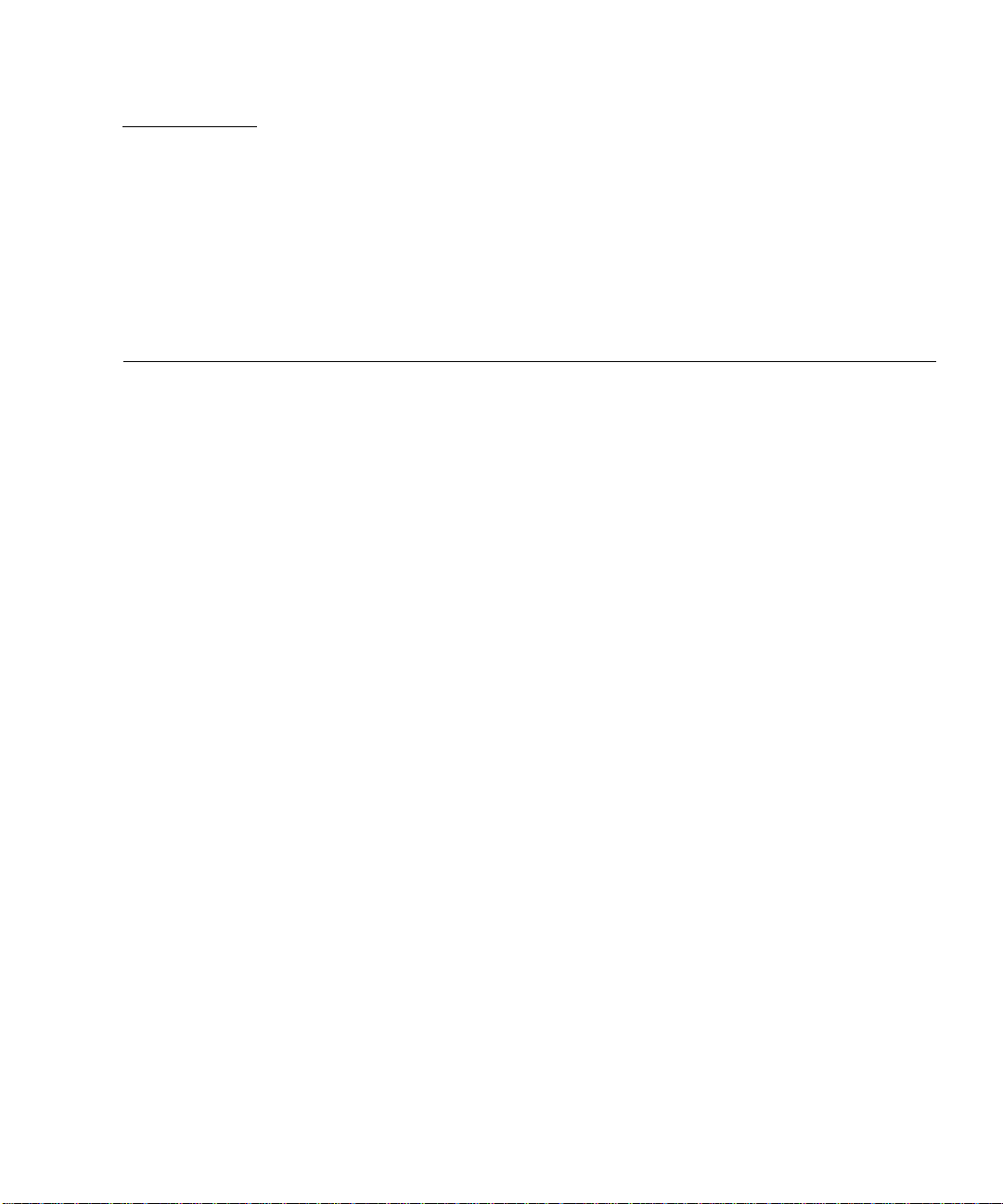

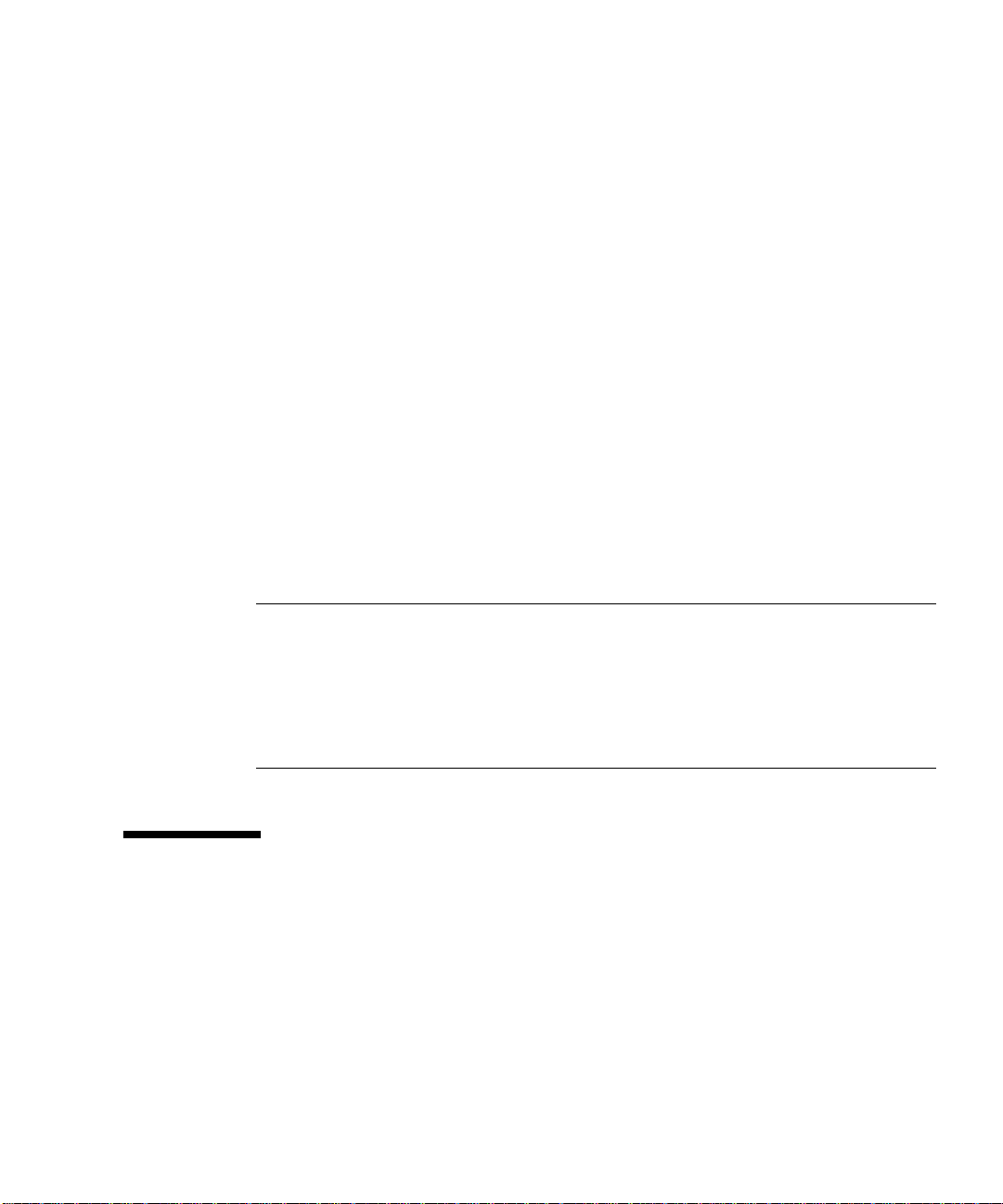

6.4 Processor Pipeline

The pipeline of SPARC64 V consists of fifteen stages, shown in FIGURE 6-2. Each

stage is referenced by one or two letters as follows:

IA IT IM IB IR

EDPBX UW

6.4.1 Instruction Fetch Stages

■

IA (Instruction Address generation) — Calculate fetch target address.

■

IT (Instruction TLB Tag access) — Instruction TLB tag search. Search of BRHIS

and RAS is also started.

■

IM (Instruction TLB tag Match) — Check TLB tag is matched.

The result of BRHIS and RAS search is also avail able at this stage and is

forwarded to IA stage for subsequent fetch.

■

IB (Instruction cache Buffer read) — Read L1 cache data if TLB is hit.

■

IR (Instruction read Result) — Writ e to I-Buffer.

IA through IR stages are dedicated to instruction fetch. These stages work in concert

with the cache access unit to supply instructions to subsequent stages. The

instructions fetched from memory or cache are stored in the Instruction Buffer (Ibuffer). The I-buffer has six entries, each of which can hold 32-byte-aligned 32-byte

data (eight instructions).

Ps Ts Ms Bs Rs

SPARC64 V has a bra nch prediction mechanism and resources named BRH IS

(BRanch HIStory) and RAS (Return Address Stack). Instruction fetch stages use these

resources to determine fetch a ddresses.

Instruction fetch stages are designed so that they work independently of subsequent

stages as much as possible. And they can fetch instructions even when execution

stages stall. These stages fetch until the I-Buffer is full; further fetches are possible by

requesting prefetches to the L1 cache.

Release 1.0, 1 July 2002 F. Chapter 6 Instructions 31

Page 43

BRHIS

IF EAG

iTLB

L1I

Instruction Buffer

IA

IT

IM

IB

IR

E

IWR

RSFA

FXB EXBFXA EXA EAGA EA GB

RSFB RSEBRSEA

FUB

RRRRRR

RR

GUB

RSA

dTLB

L1D

LB

LR

FPR

GPR

CSE

ccr fsr

RSBR

PCnPC

Ps

Ts

Ms

Bs

Rs

D

P

B

X

U

W

FIGURE 6-2

32 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

SPARC64 V Pipeline

Page 44

6.4.2 Issue Stages

■

E (Entry) — Instructions a re passed from fetc h stages.

■

D (Decode) — Assign resources and dispatch to reservation station (RS.)

SPARC64 V is an out-of-order execution CPU. It has six execution units (two of

arithmetic and logic unit, two of floating-point unit, two of load/store unit). Each

unit except the load/store unit has its own reservation station. E and D stages are

issue stages th at de code instr uction s and d isp atch th em to the target R S. SPARC64 V

can issue up to four instructions per cycle.

The resources needed to execute an instruction are assigned in the issue stages. The

resources to be allocated include the following:

■

Commit stack en try (CSE)

■

Renaming registers of integer (GUB) and floating-point (FUB)

■

Entries of reservations stations

■

Memory access ports

Resources needed for an instruction are specific to the instruction, but all resources

must be assigned at these stages. In normal execution, assigned resources are

released at the very last stage of the pipeline, W-stage.

stage and W-stage are considered to be in-flight. When an exception is signalled, all

in-flight instructions and the resources used by them are released immediately. This

behavior enables the decoder to restart issuing instructions as quickly as possible.

The number of in-flight instructions depends on how many resources are needed by

them. The maximu m number is 64.

1

Instructio ns betwe en the E-

6.4.3 Execution Stages

■

P (priority) — Select an instruction from those that have met the conditions for

execution.

■

B (buffer read) — Read register file, or receive forwarded data from another

pipelines.

■

X (execute) — Execution.

Instructions in reservation stations will be executed when certain conditions are met,

for example, the values of source registers are known, the execution unit is available.

Execution latency varies from one to many, depending on the instruction.

1. An entry in a reservation stat ion is rel eased at the X- stage.

Release 1.0, 1 July 2002 F. Chapter 6 Instructions 33

Page 45

Execution Stages for Cache Access

Memory access requests are passed to the cache access pipeline after the target

address is calculated. Cache ac cess stages work the sam e way as instruction fet ch

stages, except for the handl ing of bran ch prediction. See Section 6.4 .1, Instruction

Fetch Stages, for details. Stages in instruction fetch and cache access correspond as

follows:

Instruction Fetch Stages Cache Access

IA Ps

IT Ts

IM Ms

IB Bs

IR Rs

When an exception is signall ed, fetch ports and store ports used by memory access

instructions are released. The cache access pipeline itself remains working in order to

complete ou tgoing m emory acce sses. When data is return ed, it is the n stored to the

cache.

6.4.4 Completion Stages

■

U (Update) — Update of physical (renamed) register.

■

W (Writ e) — Update of architectural registers and retire; excep tion handli ng.

■

After an out-of-order execution, execution reverts to program order to complete.

Exception handling is done in the completion stages. Exceptions occurring in

execution stage s are not handled immedi ately but are signall ed when the

instruction is completed.

1

1. RAS-related except ion m ay be s igna lled b efor e co mplet ion.

34 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 46

F.CHAPTER

7

Traps

Please refer to Chapter 7 of Commonality. Section numbers in this chapter

correspond to those in Chapter 7 of Commonality.

This chapter adds SPARC64 V-specific information in the following sections:

■

Processor States, Normal and Special Traps on page 35

■

RED_state on page 36

■

error_state on page 36

■

Trap C a t e g o r i es on page 37

■

Deferred Traps on page 37

■

Reset Traps on page 37

■

Uses of the Trap Categories on page 37

■

Trap C o n t rol on page 38

■

PIL Control on page 38

■

Trap-Table Entry Addresses on page 38

■

Trap Typ e (TT) on page 38

■

Details of Supported Traps on page 39

■

Exception and Interrupt Descriptions on page 39

7.1 Processor States, Normal and Special Traps

Please refer to Section 7.1 of Commonality.

35

Page 47

7.1.1 RED_state

R ED_state Trap Table

The RE D_st ate trap vector is located at an implementation-dependent address

refe rre d t o as RSTVaddr. The value of RSTVaddr is a constant within each

implementation; in SPARC64 V this virtual address is FFFF FFFF F000 0000

which translates to physical address 0000 07FF F000 0000

dep. #114).

RED_state Execution Environment

In RED_state, the processor is forced to execute in a restricted environment by

overriding the values of some processor controls and state registers.

,

in RED_state (impl.

16

16

Note –

SPARC 64 V has the foll owing imp lementat ion-depen dent behav ior in RED_state

(impl. dep. #115):

■

■

■

Note –

should attempt to recover f rom potentially catastrophic error condition s or to disa ble

the failing c omponents . When RED_state i s entered after a reset, the software

should create the environment necessary to restore the system to a running state.

The values are overridden, not set, allowing them to be switched atomically.

While in RED_state, all inte rnal ITLB-bas ed translati on functions are disabled.

DTLB-based translations are disabled upon entry but may be reenabled by

software while in RED_state. However, ASI-based access functions to the TLBs

are still available.

While mTLBs and uTLBs are disabled, all accesses are assumed to be

noncacheable and strongly ordered for data access.

XIR errors are not masked and can cause a trap.

When RED_state is entered because of component failures, the handler

7.1.2 error_state

The processor enters error_state when a trap occurs while the processor is

already at its maximum su pported trap le vel (that is, when TL = MAXTL) (impl. dep.

#39).

36 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Page 48

Although the standard behavior of the CPU upon an entry into error_state is to

internally generate a

entry to error_state depending on a setting in the OPSR register (impl. dep #40,

#254).

watchdog_reset

7.2 Trap Categories

Please refer to Section 7.2 of Commonality.

An exception or interrupt request can cause any of the following trap types:

■

Precise trap

■

Deferred trap

■

Disrupting trap

■

Reset trap

7.2.2 Deferred Traps

Please refer to Section 7.2.2 of Commonality.

SPARC64 V implements a deferred trap to signal certain error conditions (impl. dep.

#32). Please refer to the description of

the instruction that caused the error” row i n

Instruction End-Method at ADE Trap on page 170.

(WDR), the CPU optionally stays halted upon an

I_UGE

error on “Rel ation b etween %tpc and

TABLE P-2

(page 156) for details. See also

7.2.4 Reset Traps

Please refer to Section 7.2.4 of Commonality.

In SPARC64 V, a watchdog reset (WDR) occurs when the processor has not

committed an instruction for 2

33

processor clocks.

7.2.5 Uses of the Trap Categories

Please refer to Section 7.2.5 of Commonality.

All exceptions that occur as the result of program execution are precise in

SPARC64 V (impl. dep. #33).

An exception caused after the initial access of a multiple-access load or store

instruction (LDD(A), STD(A), LDSTUB, CASA, CASXA, or SWAP) that causes a

catastrophic exception is precise in SPARC64 V.

Release 1.0, 1 July 2002 F. Chapter 7 Traps 37

Page 49

7.3 Trap Control

Please refer to Section 7.3 of Commonality.

7.3.1 PIL Control

SPARC64 V receives external interrupts from the UPA interconnect. They cause an

interrupt_vector_trap

information and then schedules SPARC V9-compatible interrupts by writing bits in

the SOFTINT register. Please refer to Section 5.2.11 of Commonality for details.

During handling of SPARC V9-compatible int errupts by SPAR C64 V, the PIL

register is checked. If an interrupt has sufficient priority, SPARC64 V will stop

issuing new instructions, will flush all uncommitted instructions, and then will

vector to the trap handler. The only exception to this process occurs when

SPARC64 V is processing a higher-priority trap.

SPARC 64 V takes a normal disrup ting trap upon receip t of an interrupt reques t.

(TT =6016). The interrupt vector trap handler reads the interrupt

7.4 Trap-Table Entry Addresses

Please refer to Section 7.4 of Commonality.

7.4.2 Trap Type (TT)