查询MB90561A供应商

FUJITSU SEMICONDUCTOR

DATA SHEET

16-bit Proprietary Microcontrollers

CMOS

F2MC-16LX MB90560/565 Series

MB90561/561A/562/562A/F562/F562B/V560

MB90567/568/F568

DESCRIPTION

■

The MB90560/565 series is a general-purpose 16-bit microcontroller designed for industrial, OA, and process

control applications that require high-speed real-time processing. The device f eatures a multi-function timer ab le

to output a programmable waveform.

The microcontroller instruction set is based on the same AT architecture as the F

with additional instructions for high-lev el languages, extended addressing modes, enhanced signed multiplication

and division instructions, and a complete range of bit manipulation instructions. The microcontroller has a

32-bit accumulator for processing long word (32-bit) data.

2

MC-8L and F2MC-16L families

DS07-13715-3E

FEATURES

■

•Clock

• Internal oscillator circuit and PLL clock multiplication circuit

• Oscillation clock

Clock speed selectable from either the machine cloc k, main clock, or PLL clock. The main clock is the oscillation

clock divided into 2 (0.5 MHz to 8 MHz for a 1 MHz to 16 MHz base oscillation) . The PLL cloc k is the oscillation

clock multiplied by one to four (4 MHz to 16 MHz for a 4 MHz base oscillation) .

• Minimum instruction execution time : 62.5 ns (for oscillation = 4 MHz, PLL clock setting = × 4, V

• Maximum CPU memory space : 16 MB

• 24-bit addressing

• Bank addressing

PACKAGES

■

64-pin plastic QFP 64-pin plastic LQFP 64-pin plastic SH-DIP

CC = 5.0 V)

(Continued)

(FPT-64P-M06) (FPT-64P-M09) (DIP-64P-M01)

MB90560/565 Series

(Continued)

• Instruction set

• Bit, byte, word, and long word data types

• 23 different addressing modes

• Enhanced calculation precision using a 32-bit accumulator

• Enhanced signed multiplication and division instructions and RETI instruction

• Instruction set designed for high level language (C) and multi-tasking

• Uses a system stack pointer

• Symmetric instruction set and barrel shift instructions

• Program patch function (2 address pointers) .

• 4-byte instruction queue

• Interrupt function

• Priority levels are programmable

• 32 interrupts

• Data transfer function

• Extended intelligent I/O service function : Up to 16 channels

• Low-power consumption modes

• Sleep mode (CPU operating clock stops.)

• Timebase timer mode (Only oscillation clock and timebase timer continue to operate.)

• Stop mode (Oscillation clock stops.)

• CPU intermittent operation mode (The CPU operates intermittently at the specified interval.)

• Package

• LQFP-64P (FTP-64P-M09 : 0.65 mm pin pitch)

• QFP-64P (FTP-64P-M06 : 1.00 mm pin pitch)

• SH-DIP (DIP-64P-M01 : 1.778 mm pin pitch)

• Process : CMOS technology

PERIPHERAL FUNCTIONS (RESOURCES)

■

• I/O ports : 51 ports (max.)

• Timebase timer : 1 channel

• Watchdog timer : 1 channel

• 16-bit reload timer : 2 channel 5

• Multi-function timer

• 16-bit free-run timer : 1 channel

• Output compare : 6 channels

Can output an interrupt request when a match occurs between the count in the 16-bit freerun timer and the

value set in the compare register.

• Input capture : 4 channels

On detecting an active edge on the input signal from an external input pin, copies the count value of the 16bit freerun timer to the input capture data register and generates an interrupt request.

• 8/16-bit PPG timer (8-bit × 6 channels or 16-bit × 3 channels) The period and duty of the output pulse can

be set by the program.

• Waveform generator (8-bit timer : 3 channels)

•

UART : 2 channels

• Full-duplex, double-buffered (8-bit)

• Can be set to asynchronous or clock synchronous serial transfer (I/O expansion serial) operation

• DTP/external interrupt circuit (8 channels)

• External interrupts can activate the extended intelligent I/O service.

• Generates interrupts in response to external interrupt inputs.

2

• Delayed interrupt generation module

• Generates an interrupt request for task switching.

• 8/10-bit A/D converter : 8 channels

• 8-bit or 10-bit resolution selectable

MB90560/565 Series

3

MB90560/565 Series

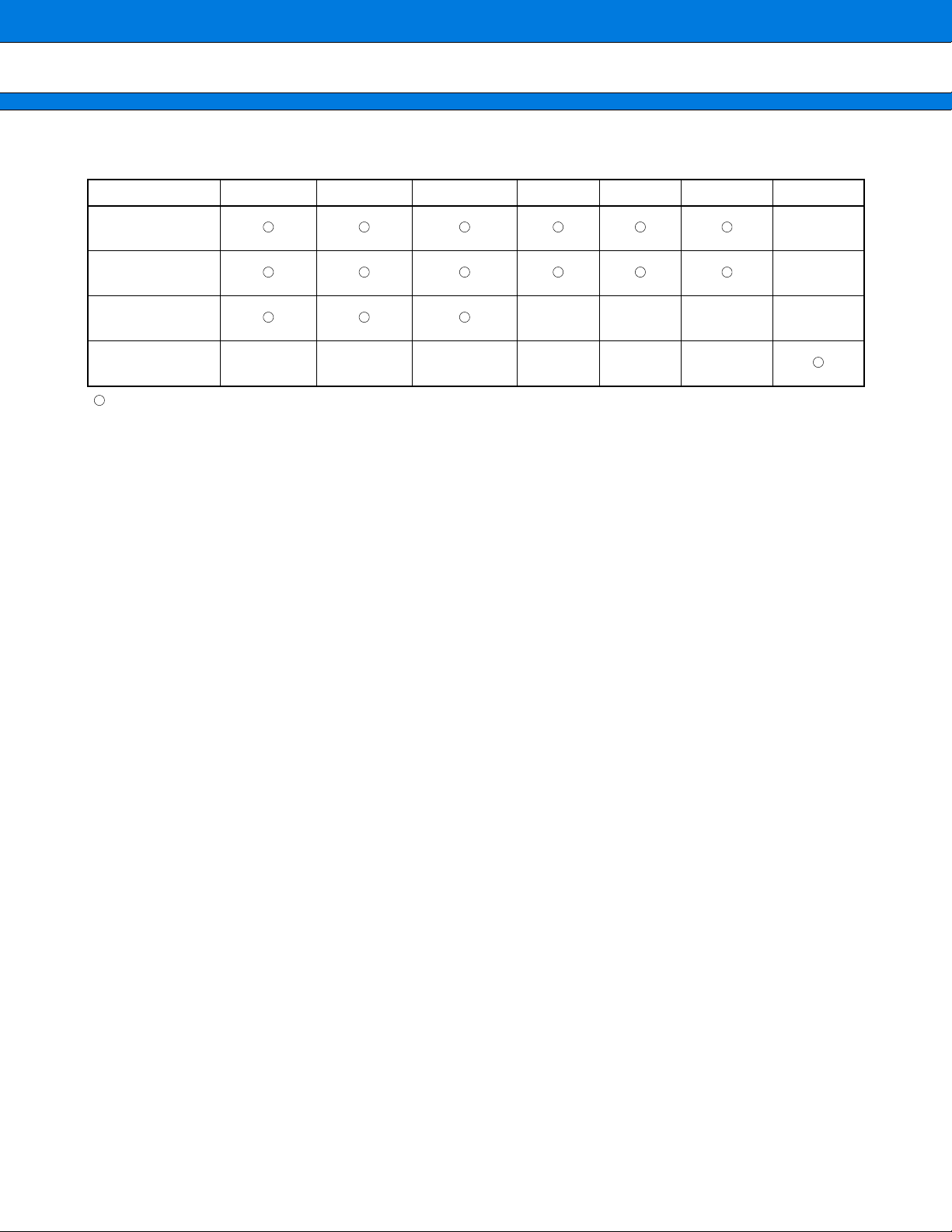

PRODUCT LINEUP

■

1. MB90560 Series

Part Number MB90F562/B MB90562/A MB90561/A MB90V560

Classification

ROM size 64 Kbytes 32 Kbytes No ROM

RAM size 2 Kbytes 1 Kbytes 4 Kbytes

Dedicated emula-

tor power supply

CPU functions

Ports I/O ports (CMOS) : 51

UART

16-bit reload timer

Multi-function

timer

Internal flash memory

product

*

Number of instructions : 351

Minimum instruction execution time : 62.5 ns for a 4 MHz oscillation (with ×4 multiplier)

Addressing modes : 23 modes

Program patch function : 2 address pointers

Maximum memory space : 16 Mbytes

Full-duplex, double-buffered

Clock synchronous or asynchronous operation selectable

Can be used as I/O serial

Internal dedicated baud rate generator

2 channels

16-bit reload timer operation

2 channels

16-bit free-run timer × 1 channel

Output compare × 6 channels

Input capture × 4 channels

8/16-bit PPG timer (8-bit × 6 channels or 16-bit × 3 channels)

Waveform generator (8-bit timer × 3 channels) 3-phase waveform output, deadtime output

No

Internal mask ROM product Evaluation product

8/10-bit

A/D converter

DTP/external

interrupts

Low power

consumption

modes

Process CMOS

Operating voltage 5 V ± 10%

* : DIP switch setting (S2) when using the emulation pod (MB2145-507) .

Refer to “2.7 Dedicated Emulator Power Supply” in the “MB2145-507 Hardware Manual” for details.

4

8 channels (multiplexed input)

8-bit or 10-bit resolution selectable

Conversion time : 6.13 µs (min.) (for maximum machine clock speed 16 MHz)

8 channels (8 channels available, shared with A/D input)

Interrupt triggers :

“L” → “H” edge, “H” → “L” edge, “L” level, “H” level (selectable)

Sleep mode, timebase timer mode, stop mode, and CPU intermittent operation mode

MB90560/565 Series

2. MB90565 Series

Part Number MB90F568 MB90568 MB90567

Classification Internal flash memory product Internal mask ROM product

ROM size 128 Kbytes 96 Kbytes

RAM size 4 Kbytes 4 Kbytes

Dedicated emula-

tor power supply

CPU functions

Ports I/O ports (CMOS) : 51

UART

16-bit reload timer

Multi-function

timer

8/10-bit A/D

converter

*

Number of instructions : 351

Minimum instruction execution time : 62.5 ns for a 4 MHz oscillation (with ×4 multiplier)

Addressing modes : 23 modes

Program patch function : 2 address pointers

Maximum memory space : 16 Mbytes

Full-duplex, double-buffered

Clock synchronous or asynchronous operation selectable

Can be used as I/O serial

Internal dedicated baud rate generator

2 channels

16-bit reload timer operation

2 channels

16-bit free-run timer × 1 channel

Output compare × 6 channels

Input capture × 4 channels

8/16-bit PPG timer (8-bit × 6 channels or 16-bit × 3 channels)

Waveform generator (8-bit timer × 3 channels) 3-phase waveform output, deadtime output

8 channels (multiplexed input)

8-bit or 10-bit resolution selectable

Conversion time : 6.13 µs (min.) (for maximum machine clock speed 16 MHz)

DTP/external

interrupts

Low power consumption modes

Process CMOS

Operating voltage 3.3 V ± 0.3 V

* : DIP switch setting (S2) when using the emulation pod (MB2145-507) .

Refer to “2.7 Dedicated Emulator Power Supply” in the “MB2145-507 Hardware Manual” for details.

8 channels (8 channels available, shared with A/D input)

Interrupt triggers :

“L” → “H” edge, “H” → “L” edge, “L” level, “H” level (selectable)

Sleep mode, timebase timer mode, stop mode, and CPU intermittent operation mode

5

MB90560/565 Series

PACKAGE AND CORRESPONDING PRODUCTS

■

Package MB90561/A MB90562/A MB90F562/B MB90567 MB90568 MB90F568 MB90V560

FPT-64P-M09

(LQFP-0.65 mm)

×

FPT-64P-M06

(QFP-1.00 mm)

DIP-64P-M01

(SH-DIP)

PGA-256C-A01

(PGA)

: Available : Not available

Note : See the “Package Dimensions” section for details of each package.

×

×× ××××

×× × ×

×

6

PIN ASSIGNMENTS

■

MB90560/565 Series

(TOP VIEW)

*

VCC

P35/RTO5

P34/RTO4

P33/RTO3

P32/RTO2

P43/PPG2

P42/PPG1

P41/PPG0

P40/SCK0

P37/SOT0

P36/SIN0

C

64636261605958575655545352

P31/RTO1

P44/PPG3

P45/PPG4

P46/PPG5

P50/AN0

P51/AN1

P52/AN2

P53/AN3

P54/AN4

P55/AN5

P56/AN6

P57/AN7

AV

CC

AVR

AVSS

P60/SIN1

P61/SOT1

P62/SCK1

P63/INT7/DTTI

MD0

10

11

12

13

14

15

16

17

18

19

1

2

3

4

5

6

7

8

9

20212223242526272829303132

SS

X0

X1

V

P00

P01

P02

P03

P04

P05

RST

MD1

MD2

P06

P30/RTO0

51

V

50

P27/IN3

49

P26/IN2

48

P25/IN1

47

P24/IN0

46

P23/TO1

45

P22/TIN1

44

P21/TO0

43

P20/TIN0

42

P17/FRCK

41

P16/INT6

40

P15/INT5

39

P14/INT4

38

P13/INT3

37

P12/INT2

36

P11/INT1

35

P10/INT0

34

P07

33

SS

(FPT-64P-M06)

* : N.C. on the MB90F568, MB90567, and MB90568.

(Continued)

7

MB90560/565 Series

(TOP VIEW)

P45/PPG4

P46/PPG5

P50/AN0

P51/AN1

P52/AN2

P53/AN3

P54/AN4

P55/AN5

P56/AN6

P57/AN7

AV

CC

AVR

AV

SS

P60/SIN1

P61/SOT1

P62/SCK1

10

11

12

13

14

15

16

*

VCC

P35/RTO5

P34/RTO4

P33/RTO3

P02

P03

P32/RTO2

P04

P44/PPG3

P43/PPG2

P42/PPG1

P41/PPG0

P40/SCK0

P37/SOT0

P36/SIN0

C

646362616059585756555453525150

1

2

3

4

5

6

7

8

9

171819202122232425262728293031

SS

X0

X1

V

P00

MD0

RST

MD1

MD2

P01

P31/RTO1

P05

P30/RTO0

P06

SS

V

49

32

P07

48

P27/IN3

47

P26/IN2

46

P25/IN1

45

P24/IN0

44

P23/TO1

43

P22/TIN1

42

P21/TO0

41

P20/TIN0

40

P17/FRCK

39

P16/INT6

38

P15/INT5

37

P14/INT4

36

P13/INT3

35

P12/INT2

34

P11/INT1

33

P10/INT0

P63/INT7/DTTI

* : N.C. on the MB90F568, MB90567, and MB90568.

8

(FPT-64P-M09)

(Continued)

(Continued)

C

P36/SIN0

P37/SOT0

P40/SCK0

P41/PPG0

P42/PPG1

P43/PPG2

P44/PPG3

P45/PPG4

P46/PPG5

P50/AN0

P51/AN1

P52/AN2

P53/AN3

P54/AN4

P55/AN5

P56/AN6

P57/AN7

AV

CC

AVR

AV

SS

P60/SIN1

P61/SOT1

P62/SCK1

P63/INT7/DTTI

MD0

RST

MD1

MD2

X0

X1

V

SS

MB90560/565 Series

(TOP VIEW)

*

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

V

63

P35/RTO5

62

P34/RTO4

61

P33/RTO3

60

P32/RTO2

59

P31/RTO1

58

P30/RTO0

57

V

56

P27/IN3

55

P26/IN2

54

P25/IN1

53

P24/IN0

52

P23/TO1

51

P22/TIN1

50

P21/TO0

49

P20/TIN0

48

P17/FRCK

47

P16/INT6

46

P15/INT5

45

P14/INT4

44

P13/INT3

43

P12/INT2

42

P11/INT1

41

P10/INT0

40

P07

39

P06

38

P05

37

P04

36

P03

35

P02

34

P01

33

P00

CC

SS

(DIP-64P-M01)

(Only support MB90F562/B, MB90561/A, and MB90562/A.)

* : Not support on the MB90F568, MB90567, and MB90568.

9

MB90560/565 Series

■ PIN DESCRIOTIONS

Pin No.

QFPM06 LQFPM09 SDIP

23, 24 22, 23 30, 31 X0, X1 A Oscillator

20 19 27 RST

26 to 33 25 to 32 33 to 40

34 to 40 33 to 39 41 to 47

41 40 48

42 41 49

43 42 50

Pin

Name

P00 to

P07

P10 to

P16

INT0 to

INT6

P17

FRCK

P20

TIN0

P21

TO0

Circuit

Type

B

C

C

C

D

D

State/

Function

*

at Reset

Reset

inputs

outputs)

input

Port

(Hi-Z

Description

Connect oscillator to these pins.

If using an external clock, leave X1 open.

External reset input pin

I/O ports

I/O ports

Can be used as interrupt request inputs ch0 to ch6.

In standby mode, these pins can operate as inputs

by setting the bits corresponding to EN0 to EN6 to

“1” and setting as input ports. When used as a port,

set the corresponding bits in the analog input

enable register (ADER) to “port”.

I/O port

External clock input pin for the freerun timer.

This pin can be used as an input when set as the

clock input for the freerun timer and set as an input

port. When used as a port, set the corresponding

bit in the analog input enable register (ADER) to

“port”.

I/O port

External clock input pin for reload timer ch0. This

pin can be used as an input when set as the external clock input and set as an input port.

I/O port

Event output pin for reload timer ch0. Output oper-

ates when event output is enabled.

P22

44 43 51

TIN1

P23

45 44 52

TO1

P24 to

P27

46 to 49 45 to 48 53 to 56

IN0 to

IN3

* : See “■ I/O CIRCUITS” for details of the circuit types.

10

D

D

D

I/O port

External clock input pin for reload timer ch1. This

pin can be used as an input when set as the external clock input and set as an input port.

I/O port

Event output pin for reload timer ch1. Output oper-

ates when event output is enabled.

I/O ports

Trigger input pins for input capture ch0 to ch3.

These pins can be used as an input when set as an

input capture trigger input and set as an input port.

(Continued)

MB90560/565 Series

Pin No.

QFPM06 LQFPM09 SDIP

51 to 56 50 to 55 58 to 63

59 58 2

60 59 3

Pin

Name

P30 to

P35

RTO0

to

RTO5

P36

SIN0

P37

SOT0

P40

Cir-

cuit

Type

E

D

D

State/

Function

*

at Reset

inputs

(Hi-Z)

Port

Description

I/O ports

Event output pins for the output compare and wave-

form generator output pins. The pins output the

specified waveform generated by the waveform

generator. If not using waveform generation, these

terminals enable output compare event output to

use as output compare outputs. When used as a

port, set the corresponding bits in the analog input

enable register (ADER) to “port”.

I/O port

Serial data input pin for UART ch0.

This pin is used continuously when input operation

is enabled for UART ch0. In this case, do not use as

a general input pin.

I/O port

Serial data output pin for UART ch0.

Output operates when UART ch0 output is enabled.

I/O port

61 60 4

SCK0

P41 to

P46

62 to 64,

1 to 3

61 to 64,

1, 2

5 to 10

PPG0

to

PPG5

P50 to

P57

4 to 11 3 to 10 11 to 18

AN0 to

AN7

12 11 19 AV

CC

13 12 20 AVR G

14 13 21 AV

SS

D

D

F

Analog

inputs

Power

supply

input

Reference voltage input

Power

supply

input

Serial clock I/O pin for UART ch0.

Output operates when UART ch0 clock output is

enabled.

I/O ports

Output pins for PPG ch0 to ch5.

The outputs operate when output is enabled for

PPG ch0 to ch5.

I/O ports

Analog input pins for the A/D converter. Input is

available when the corresponding analog input enable register bits are set. (ADER : bit0 to bit7)

VCC power supply input pin for A/D converter.

Reference voltage input pin for A/D converter.

Ensure that the voltage does not exceed V

CC.

VSS power supply input pin for A/D converter.

* : See “■ I/O CIRCUITS” for details of the circuit types.

(Continued)

11

MB90560/565 Series

(Continued)

Pin No.

QFPM06 LQFPM09 SDIP

Pin

Name

Circuit

Type

Function

*1

at Reset

State/

Description

15 14 22

16 15 23

17 16 24

18 17 25

P60

SIN1

P61

SOT1

P62

SCK1

P63

INT7

DTTI

D

D

D

D

Port input

(Hi-Z)

I/O port

Serial data input pin for UART ch1.

This pin is used continuously when input operation is enabled for UART ch1. In this case, do not

use as a general input pin.

I/O port

Serial data output pin for UART ch1.

Output operates when UART ch1 output is enabled.

I/O port

Serial clock I/O pin for UART ch1.

Output operates when UART ch1 clock output is

enabled.

I/O port

This pin can be used as interrupt request input

ch7. In standby mode, this pin can operate as an

input by setting the bit corresponding to EN7 to

“1” and setting as an input port.

Fixed pin level input pin when RTO0 to RTO5

pins are used. Input is enabled when “input enabled” set in the waveform generator.

Capacitor

58 57 1 C

*2

pin, power supply

input

19 18 26 MD0 B

21 20 28 MD1 B

Mode

input pins

22 21 29 MD2 B

25, 50 24, 49 32, 57 VSS

Power

supply

57 56 64 V

CC

inputs

*1 : See “■ I/O CIRCUITS” for details of the circuit types.

*2 : N.C. on the MB90F568, MB90567, and MB90568

Capacitor pin for stabilizing the power supply.

Connect an external ceramic capacitor of approximately 0.1 µF.

Input pin for setting the operation mode.

Connect directly to V

CC or VSS.

Input pin for setting the operation mode.

Connect directly to V

CC or VSS.

Input pin for setting the operation mode.

Connect directly to V

SS.

Power supply (GND) input pin

MB90560 series is power supply (5 V) input pin

MB90565 series is power supply (3.3 V) input pin

12

MB90560/565 Series

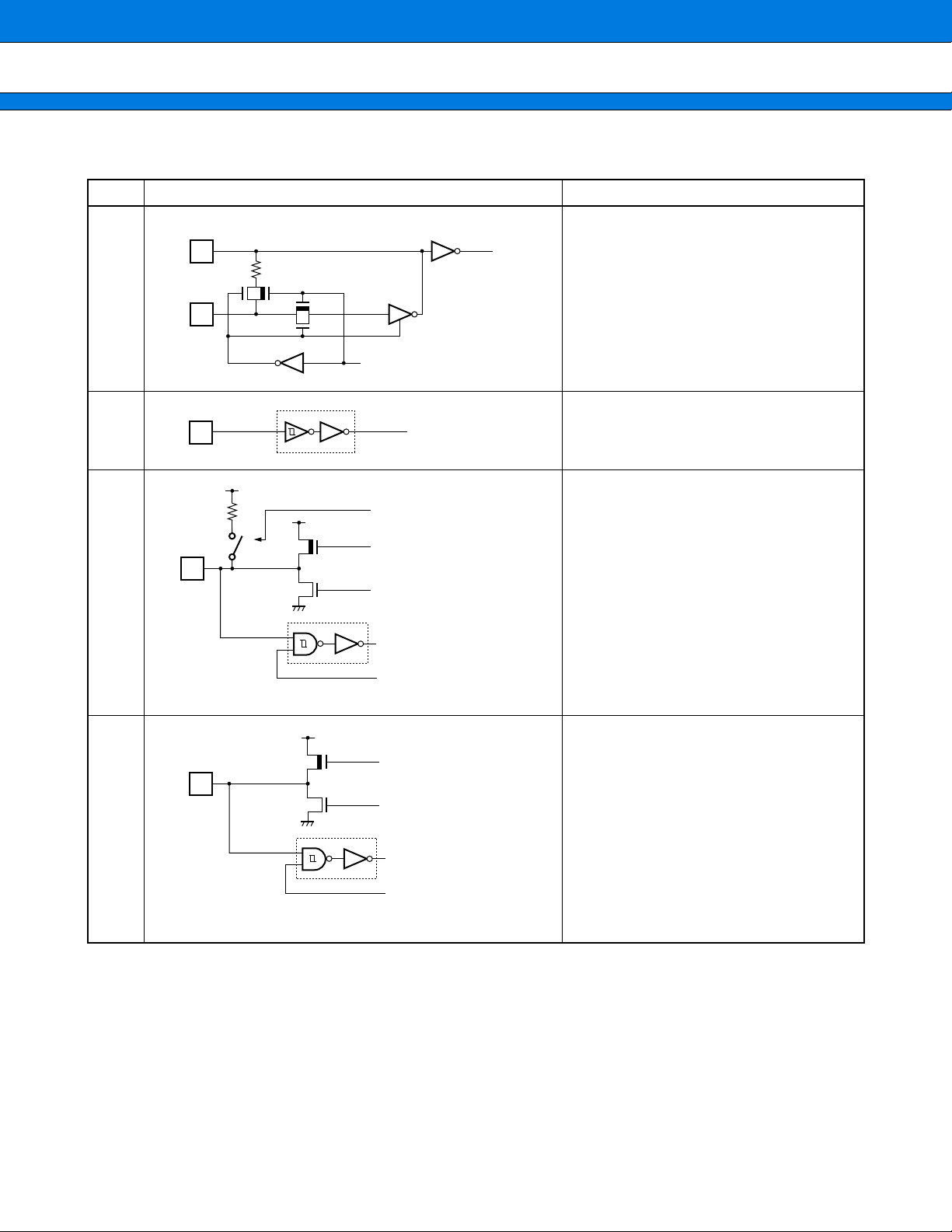

I/O CIRCUITS

■

Type Circuit Remarks

X1

R

Nch

A

X0

B

Rp

C

f

Pch

Nch

Pch

Nch

Pch

Standby control signal

Reset input

Pull-up control

Pout

Nout

Input signal

Xout

• Oscillation circuit

Internal oscillation feedback

resistor (R

f)

• CMOS hysteresis reset input pin

• CMOS hysteresis I/O pin with pull-up

control

CMOS output

CMOS hysteresis input (with input cutoff function in standby mode)

Internal pull-up resistor (R

< Note >

• The pull-up resistor is active when the

port is set as an input.

p)

Standby control signal

• CMOS hysteresis I/O pin

CMOS output

Pch

Pout

CMOS hysteresis input (with input cutoff function in standby mode)

Nch

D

Nout

Input signal

Standby control signal

< Notes >

• The I/O port output and internal

resource output share the same output buffer.

• The I/O port input and internal

resource input share the same input

buffer.

(Continued)

13

MB90560/565 Series

(Continued)

Type Circuit Remarks

•CMOS I/O pin

Pch

Nch

Pout

Nout

E

Hysteresis input

Standby control signal

Pch

Nch

F

Pout

Nout

Input signal

Standby control signal

A/D converter analog input

CMOS output

CMOS hysteresis input (with input cutoff function in standby mode)

< I

OL = 12 mA >

• Analog/CMOS hysteresis I/O pin

CMOS output

CMOS hysteresis input (with input cutoff function in standby mode)

Analog input (Analog input to A/D converter is enabled when “1” is set in the

corresponding bit in the analog input

enable register (ADER) .)

• The I/O port output and internal

resource output share the same output buffer.

• The I/O port input and internal

resource input share the same input

buffer.

• A/D converter (AVR) voltage input pin

14

Pch

G

Nch

Pch

Nch

AVR input

Analog input

enable signal

from A/D converter

MB90560/565 Series

HANDLING DEVICES

■

Take note of the following nine points when handling devices :

• Do not exceed maximum rated voltage (to prevent latch-up)

• Supply voltage stability

• Power-on precautions

• Treatment of unused pins

• Treatment of A/D converter power supply pins

• Notes on using an external clock

• Power supply pins

• Sequence for connecting and disconnecting the A/D converter power supply and analog input pins

• Notes on using the DIV A, Ri and DIVW A, RWi instructions

• Device Handling Precautions

(1) Do not exceed maximum rated voltage (to prevent latch-up)

Do not apply a voltage grater than V

ensure that the voltage between V

CC or less than VSS to the MB90560/565 series input or output pins. Also

CC and VSS does not exceed the rating. Applying a voltage in excess of the

ratings may result in latch-up causing thermal damage to circuit elements.

Similarly, when connecting or disconnecting the power to the analog power supply (AVCC, AVR) and analog

inputs (AN0 to AN7) , ensure that the analog power supply voltages do not exceed the digital voltage (V

(2) Supply voltage stability

Rapid changes in the V

CC supply voltage ma y cause the de vice to misoper ate . Accordingly, ensure that the VCC

power supply is stable. The standard for power supply voltage stability is a peak-to-peak VCC ripple voltage at

the supply frequency (50 to 60 Hz) of 10% or less of V

CC and a transient fluctuation in the voltage of 0.1 V/ms

or less when turning the power supply on or off.

(3) Power-on precautions

To prevent misoper ation of the internal regulator circuit, ensure that the voltage rise time at pow er-on is at least

50 µs (between 0.2 V to 2.7 V) .

(4) Treatment of unused pins

Leaving unused input pins unconnected can cause misoperation or permanent damage to the device due to

latchup. Always pull-up or pull-down unused pins using a 2 kΩ or larger resistor.

If some I/O pins are unused, either set as outputs and leave open circuit or set as inputs and treat in the same

way as input pins.

CC) .

(5) Treatment of A/D converter power supply pins

If not using the A/D converter, connect the analog power supply pins so that AV

CC = AVR = VCC and AVSS = VSS.

(6) Notes on using an external clock

Even if using an external clock, an oscillation stabilization delay time occurs after a power-on reset and when

recovering from stop mode in the same way as when an oscillator is connected. When using an external clock,

drive the X0 pin only and leave the X1 pin open.

15

MB90560/565 Series

X0

X1OPEN

MB90560/565 series

Example of using an external clock

(7) Power supply pins

The multiple V

such as latch-up. However, always connect all V

spurious radiation, prevent misoper ation of strobe signals due to increases in the ground le vel, and maintain the

overall output current rating.

CC and VSS pins are connected together in the internal device design so as to prevent misoper ation

CC and VSS pins to the same potential externally to minimize

Also, ensure that the impedance of the V

To minimize these problems, connect a b ypass capacitor of approximately 0.1 µF between V

the capacitor close to the V

CC and VSS pins.

CC and VSS connections to the power supply is as low as possible.

CC and VSS. Connect

(8) Sequence for connecting and disconnecting power supply

Do not apply voltage to the A/D converter power supply pins (AV

until the digital power supply (V

CC) is turned on. When turning the device off, turn off the digital power supply

CC, AVR, AVSS) or analog inputs (AN0 to AN7)

after disconnecting the A/D converter power supply and analog inputs. When turning the power on or off, ensure

that AVR does not exceed AV

CC.

When using the I/O ports that share pins with the analog inputs, ensure that the input voltage does not exceed

AVCC (turning the analog and digital power supplies on and off simultaneously is OK) .

(9) Conditions when output from ports 0 and 1 is undefined

After turning on the power supply, the outputs from ports 0 and 1 are undefined during the oscillation stabilization

delay time controlled by the regulator circuit (during the powe r-on reset) if the RST

RST

pin level is “L”, ports 0 and 1 go to high impedance.

pin level is “H”. When the

Figures 1 and 2 show the timing (for the MB90F562/B and MB90V560) .

Note that this undefined output period does not occur on products without an internal regulator circuit as these

products do not have an oscillation stabilization delay time.

(MB90561/A, MB90562/A, MB90F568, and MB90567/8)

16

MB90560/565 Series

•

Figure 1 Timing chart for undefined output from ports 0 and 1 (When RST

Oscillation stabilization delay time

Regulator circuit

stabilization delay time

VCC (Power supply pin)

PONR (Power-on reset) signal

RST (External asynchronous reset) signal

RST (Internal reset) signal

Oscillation clock signal

KA (Internal operating clock A) signal

KB (Internal operating clock B) signal

PORT (port output) signal Undefined output time

*1

*1 : Regulator circuit oscillation stabilization delay time :

17

2

/Oscillation clock frequency (approx. 8.19 ms for a 16 MHz oscillation clock frequency)

*2 : Oscillation stabilization delay time :

18

2

/Oscillation clock frequency (approx. 16.38 ms for a 16 MHz oscillation clock frequency)

pin level is “H”)

*2

17

MB90560/565 Series

•

Figure 2 Timing chart for ports 0 and 1 going to high impedance state (When RST

Oscillation stabilization delay time

Regulator circuit

stabilization delay time

VCC (Power supply pin)

PONR (Power-on reset) signal

RST (External asynchronous reset) signal

RST (Internal reset) signal

Oscillation clock signal

KA (Internal operating clock A) signal

KB (Internal operating clock B) signal

PORT (port output) signal

High impedance

*1

pin level is “L”)

*2

*1 : Regulator circuit oscillation stabilization delay time :

17

2

/Oscillation clock frequency (approx. 8.19 ms for a 16 MHz oscillation clock frequency)

*2 : Oscillation stabilization delay time :

18

2

/Oscillation clock frequency (approx. 16.38 ms for a 16 MHz oscillation clock frequency)

(10) Notes on using the DIV A, Ri and DIVW A, RWi instructions

The location in which the remainder value produced by the signed division instructions “DIV A, Ri” and “DIVW

A, RWi” is stored depends on the bank register. The remainder is stored in an address in the memor y bank

specified in the bank register.

Set the bank register to “00

H” when using the “DIV A, Ri” and “DIVW A, RWi” instructions.

(11) Notes on using REALOS

The extended intelligent I/O service (EI

2

OS) cannot be used when using REALOS.

(12) Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected in the microcontroller , it may attempt to continue the operation using the freerunning frequency of the self oscillation circuit in the PLL circuitry even if the oscillator is out of place or the clock

input is stopped. Performance of this operation, however, cannot be guaranteed.

18

BLOCK DIAGRAM

■

MB90560/565 Series

X0, X1

RST

MD0 to MD2

SIN0

SOT0

SCK0

SIN1

SOT1

SCK1

AV

AVR

AVSS

AN0 to AN7

TO0

TIN0

TO1

TIN1

CC

Clock

control circuit

Interrupt controller

RAM

ROM

UART

ch0

UART

ch1

8/10-bit

A/D converter

16-bit

reload timer

ch0

16-bit

reload timer

ch1

F2MC-16LX

CPU

Internal data bus

8/16-bit

PPG timer

ch0 to ch5

capture

ch0 to ch3

compare

ch0 to ch5

Waveform generator circuit

*

Input

16-bit

freerun

timer

Output

PPG0 to PPG5

IN0 to IN3

FRCK

RTO0

RTO1

RTO2

RTO3

RTO4

RTO5

DTTI

INT0 to INT7

DTP/

external interrupts

P00

P07

I/O ports (Ports 0, 1, 2, 3, 4, 5, and 6)

P10

P17

P20

P27

P30

P37

P40

P46

P50

P57

P60

P63

* : Channel numbers when used as 8-bit timers. Three channels (ch1, ch3, and ch5) are av ailable when used

as 16-bit timers.

Note: The I/O ports share pins with the various peripheral functions (resources) .

See the Pin Assignment and Pin Description sections for details.

Note that, if a pin is used by a peripheral function (resource) , it may not be used as an I/O port.

19

MB90560/565 Series

MEMORY MAP

■

Single chip mode

FFFFFFH

Address #1

FF0000H

010000H

Address #2

004000H

Address #3

000100H

0000C0H

000000H

(with ROM mirror function)

ROM area

ROM area

(image of FF bank)

RAM

area

Registers

Peripherals

Access prohibited

Part No. Address#1 Address#2 Address#3

MB90561/A FF8000

H 008000H 000500H

MB90562/A FF0000H 004000H 000900H

MB90F562/B FF0000H 004000H 000900H

MB90567 FE8000H 004000H 001100H

MB90568 FE0000H 004000H 001100H

MB90F568 FE0000H 004000H 001100H

MB90V560 FE0000H

*

004000H

*

001100H

* : “V” products do not contain internal ROM. Treat this address as the ROM decode area

used by the tools.

Memory map of MB90560/565 series

Notes : • When specified in the ROM mirror function register, the upper part of 00 bank (“004000

contains a mirror of the data in the upper part of FF bank (“FF4000

H to FFFFFFH”) .

H to 00FFFFH”)

• See “10. ROM Mirror Function Selection Module” in the Peripheral Functions section for details of the

ROM mirror function settings.

Remarks : • The ROM mirror function is provided so the C compiler’s small memory model can be used.

• The lower 16 bits of the FF bank and 00 bank addresses are the same. However, as the FF bank ROM

area exceeds 48 KBytes, the entire ROM data area cannot be mirrored in 00 bank.

• When using the C compiler’s small memory model, locating data tables in the area “FF4000

FFFFFF

H” makes the image of the data visible in the “004000H to 00FFFFH” area. This means that

data tables located in ROM can be referenced without needing to declare far pointers.

H to

20

I/O MAP

■

MB90560/565 Series

Address

000000

Abbreviat-

ed Register

Register name

Name

H PDR0 Port 0 data register R/W Port 0 XXXXXXXXB

Read/

Write

Resource Name Initial Value

000001H PDR1 Port 1 data register R/W Port 1 XXXXXXXXB

000002H PDR2 Port 2 data register R/W Port 2 XXXXXXXXB

000003H PDR3 Port 3 data register R/W Port 3 XXXXXXXXB

000004H PDR4 Port 4 data register R/W Port 4 XXXXXXXXB

000005H PDR5 Port 5 data register R/W Port 5 XXXXXXXXB

000006H PDR6 Port 6 data register R/W Port 6 XXXXXXXXB

000007H

to

00000F

H

Access prohibited

000010H DDR0 Port 0 direction register R/W Port 0 0 0 0 0 0 0 0 0B

000011H DDR1 Port 1 direction register R/W Port 1 0 0 0 0 0 0 0 0B

000012H DDR2 Port 2 direction register R/W Port 2 0 0 0 0 0 0 0 0B

000013H DDR3 Port 3 direction register R/W Port 3 0 0 0 0 0 0 0 0B

000014H DDR4 Port 4 direction register R/W Port 4 X 0 0 0 0 0 0 0B

000015H DDR5 Port 5 direction register R/W Port 5 0 0 0 0 0 0 0 0B

000016H DDR6 Port 6 direction register R/W Port 6 XXXX 0 0 0 0B

000017H ADER Analog input enable register R/W

Port 5,

A/D converter

1 1 1 1 1 1 1 1B

000018H

to

00001F

000020

H

H SMR0 Mode register ch0 R/W

Access prohibited

0 0 0 0 0 X 0 0B

000021H SCR0 Control register ch0 W, R/W 0 0 0 0 0 1 0 0B

000022H

SIDR0 Input data register ch0 R

UART0

XXXXXXXX

SODR0 Output data register ch0 W

000023H SSR0 Status register ch0 R, R/W 0 0 0 0 1 0 0 0B

000024H SMR1 Mode register ch1 R/W

0 0 0 0 0 X 0 0B

000025H SCR1 Control register ch1 W, R/W 0 0 0 0 0 1 0 0B

000026H

SIDR1 Input data register ch1 R

UART1

XXXXXXXX

SODR1 Output data register ch1 W

000027

H SSR1 Status register ch1 R, R/W 0 0 0 0 1 0 0 0B

000028H Access prohibited

000029H CDCR0

Communication prescaler

control register ch0

R/W

Communication

prescaler

0 XXX 0 0 0 0B

B

B

(Continued)

21

MB90560/565 Series

Address

00002A

00002B

Abbreviat-

ed Register

Register name

Name

H Access prohibited

H CDCR1

Communication prescaler

control register ch1

Read/

Write

R/W

Resource Name Initial Value

Communication

prescaler

0 XXX 0 0 0 0B

00002CH

to

00002F

000030

H

H ENIR DTP/external interrupt enable register R/W

000031H EIRR DTP/external interrupt request register R/W XXXXXXXXB

000032H

Request level setting register (lower) R/W 0 0 0 0 0 0 0 0

Access prohibited

0 0 0 0 0 0 0 0B

DTP/external

interrupts

ELVR

000033H Request level setting register (upper) R/W 0 0 0 0 0 0 0 0B

000034H ADCS0 A/D control status register (lower) R/W

000035H ADCS1 A/D control status register (upper) W, R/W 0 0 0 0 0 0 0 0B

000036H ADCR0 A/D data register (lower) R XXXXXXXXB

8/10-bit

A/D converter

0 0 0 0 0 0 0 0B

000037H ADCR1 A/D data register (upper) R, W 0 0 0 0 0 XXXB

000038H PRLL0 PPG reload register ch0 (lower) R/W

XXXXXXXXB

000039H PRLH0 PPG reload register ch0 (upper) R/W XXXXXXXXB

B

00003AH PRLL1 PPG reload register ch1 (lower) R/W XXXXXXXXB

00003BH PRLH1 PPG reload register ch1 (upper) R/W XXXXXXXXB

8/16-bit PPG timer

00003CH PPGC0 PPG control register ch0 (lower) R/W 0 0 0 0 0 0 0 1B

00003DH PPGC1 PPG control register ch1 (upper) R/W 0 0 0 0 0 0 0 1B

00003EH PCS01 PPG clock control register ch0, ch1 R/W 0 0 0 0 0 0 XXB

00003FH Access prohibited

000040

H PRLL2 PPG reload register ch2 (lower) R/W

XXXXXXXXB

000041H PRLH2 PPG reload register ch2 (upper) R/W XXXXXXXXB

000042H PRLL3 PPG reload register ch3 (lower) R/W XXXXXXXXB

000043H PRLH3 PPG reload register ch3 (upper) R/W XXXXXXXXB

8/16-bit PPG timer

000044H PPGC2 PPG control register ch2 (lower) R/W 0 0 0 0 0 0 0 1B

000045H PPGC3 PPG control register ch3 (upper) R/W 0 0 0 0 0 0 0 1B

000046H PCS23 PPG clock control register ch2, ch3 R/W 0 0 0 0 0 0 XXB

000047H Access prohibited

000048H PRLL4 PPG reload register ch4 (lower) R/W

XXXXXXXXB

000049H PRLH4 PPG reload register ch4 (upper) R/W XXXXXXXXB

00004AH PRLL5 PPG reload register ch5 (lower) R/W XXXXXXXXB

8/16-bit PPG timer

00004BH PRLH5 PPG reload register ch5 (upper) R/W XXXXXXXXB

00004CH PPGC4 PPG control register ch4 (lower) R/W 0 0 0 0 0 0 0 1B

(Continued)

22

MB90560/565 Series

Address

00004D

Abbreviat-

ed Register

Register name

Name

H PPGC5 PPG control register ch5 (upper) R/W

Read/

Write

Resource Name Initial Value

0 0 0 0 0 0 0 1B

8/16-bit PPG timer

00004EH PCS45 PPG clock control register ch4, ch5 R/W 0 0 0 0 0 0 XXB

00004FH Access prohibited

000050

H TMRR0 8-bit reload register ch0 R/W

XXXXXXXXB

000051H DTCR0 8-bit timer control register ch0 R/W 0 0 0 0 0 0 0 0B

000052H TMRR1 8-bit reload register ch1 R/W XXXXXXXXB

000053H DTCR1 8-bit timer control register ch1 R/W 0 0 0 0 0 0 0 0B

Waveform

generator

000054H TMRR2 8-bit reload register ch2 R/W XXXXXXXXB

000055H DTCR2 8-bit timer control register ch2 R/W 0 0 0 0 0 0 0 0B

000056H SIGCR Waveform control register R/W 0 0 0 0 0 0 0 0B

000057H Access prohibited

000058H

Compare clear register (lower) R/W

XXXXXXXX

CPCLR

000059H Compare clear register (upper) R/W XXXXXXXXB

00005AH

TCDT

00005BH Timer data register (upper) R/W 0 0 0 0 0 0 0 0B

Timer data register (lower) R/W 0 0 0 0 0 0 0 0

16-bit freerun

timer

B

B

00005CH

Timer control/status register (lower) R/W 0 0 0 0 0 0 0 0

TCCS

00005DH Timer control/status register (upper) R/W 0 XX 0 0 0 0 0B

00005EH

Access prohibited

00005F

000060H

H

Input capture data register ch0 (lower) R

XXXXXXXX

B

IPCP0

000061H Input capture data register ch0 (upper) R XXXXXXXXB

000062H

Input capture data register ch1 (lower) R XXXXXXXX

B

IPCP1

000063H Input capture data register ch1 (upper) R XXXXXXXXB

000064H

Input capture data register ch2 (lower) R XXXXXXXX

Input capture

B

IPCP2

000065H Input capture data register ch2 (upper) R XXXXXXXXB

000066H

Input capture data register ch3 (lower) R XXXXXXXX

B

IPCP3

000067H Input capture data register ch3 (upper) R XXXXXXXXB

000068H ICS01 Input capture control register 01 R/W 0 0 0 0 0 0 0 0B

000069H Access prohibited

00006A

H ICS23 Input capture control register 23 R/W Input capture 0 0 0 0 0 0 0 0B

00006BH

to

00006E

H

Access prohibited

(Continued)

B

23

MB90560/565 Series

Address

Abbreviat-

ed Register

Name

Register name

Read/

Write

Resource Name Initial Value

ROM mirror

00006F

H ROMM ROM mirror function selection register W

function selection

XXXXXXX 1B

module

000070H

Compare register ch0 (lower) R/W

XXXXXXXX

B

OCCP0

000071H Compare register ch0 (upper) R/W XXXXXXXXB

000072H

Compare register ch1 (lower) R/W XXXXXXXX

B

OCCP1

000073H Compare register ch1 (upper) R/W XXXXXXXXB

000074H

Compare register ch2 (lower) R/W XXXXXXXX

B

OCCP2

000075H Compare register ch2 (upper) R/W XXXXXXXXB

000076H

Compare register ch3 (lower) R/W XXXXXXXX

B

OCCP3

000077H Compare register ch3 (upper) R/W XXXXXXXXB

000078H

OCCP4

Compare register ch4 (lower) R/W XXXXXXXX

Output compare

B

000079H Compare register ch4 (upper) R/W XXXXXXXXB

00007AH

Compare register ch5 (lower) R/W XXXXXXXX

B

OCCP5

00007BH Compare register ch5 (upper) R/W XXXXXXXXB

00007CH OCS0 Compare control register ch0 (lower) R/W 0 0 0 0 XX 0 0B

00007DH OCS1 Compare control register ch1 (upper) R/W XXX 0 0 0 0 0B

00007EH OCS2 Compare control register ch2 (lower) R/W 0 0 0 0 XX 0 0B

00007FH OCS3 Compare control register ch3 (upper) R/W XXX 0 0 0 0 0B

000080H OCS4 Compare control register ch4 (lower) R/W 0 0 0 0 XX 0 0B

000081H OCS5 Compare control register ch5 (upper) R/W XXX 0 0 0 0 0B

000082H TMCSR0 : L Timer control status register ch0 (lower) R/W

0 0 0 0 0 0 0 0B

000083H TMCSR0 : H Timer control status register ch0 (upper) R/W XXXX 0 0 0 0B

TMR0 16-bit timer register ch0 (lower) R XXXXXXXXB

000084H

TMRLR0 16-bit reload register ch0 (lower) W XXXXXXXXB

TMR0 16-bit timer register ch0 (upper) R XXXXXXXXB

000085H

TMRHR0 16-bit reload register ch0 (upper) W XXXXXXXXB

16-bit reload timer

000086H TMCSR1 : L Timer control status register ch1 (lower) R/W 0 0 0 0 0 0 0 0B

000087H TMCSR1 : H Timer control status register ch1 (upper) R/W XXXX 0 0 0 0B

TMR1 16-bit timer register ch1 (lower) R XXXXXXXXB

000088H

TMRLR1 16-bit reload register ch1 (lower) W XXXXXXXXB

TMR1 16-bit timer register ch1 (upper) R XXXXXXXXB

000089H

TMRHR1 16-bit reload register ch1 (upper) W XXXXXXXXB

(Continued)

24

MB90560/565 Series

Address

00008A

to

00008B

00008C

Abbreviat-

ed Register

Register name

Name

H

Access prohibited

H

H RDR0 Port 0 pull-up resistor setting register R/W Port 0 0 0 0 0 0 0 0 0B

Read/

Write

Resource Name Initial Value

00008DH RDR1 Port 1 pull-up resistor setting register R/W Port 1 0 0 0 0 0 0 0 0B

00008EH

to

00009D

00009E

H

H PACSR

Program address detection

control status register

Access prohibited

R/W

Address match

detection

0 0 0 0 0 0 0 0B

00009FH DIRR Delayed interrupt request/clear register R/W Delayed interrupt XXXXXXX 0B

Low power

0000A0H LPMCR Low power consumption mode register W, R/W

consumption

0 0 0 1 1 0 0 0B

control circuit

0000A1H CKSCR Clock selection register R, R/W Clock 1 1 1 1 1 1 0 0B

0000A2H

to

0000A7

H

Access prohibited

0000A8

H WDTC Watchdog control register R/W Watchdog timer 1 XXXX 1 1 1B

0000A9H TBTC Timebase timer control register W, R/W Timebase timer 1 XX 0 0 1 0 0B

0000AAH

to

0000AD

0000AE

H

H FMCS Flash memory control status register

Access prohibited

R, W,

R/W

Flash memory 0 0 0 0 0 0 0 0B

0000AFH Access prohibited

0000B0

H ICR00

Interrupt control register 00 (for writing) W, R/W

XXXX 0 1 1 1

Interrupt control register 00 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 01 (for writing) W, R/W XXXX 0 1 1 1

0000B1H ICR01

Interrupt control register 01 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 02 (for writing) W, R/W XXXX 0 1 1 1

0000B2H ICR02

Interrupt control register 02 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupts

Interrupt control register 03 (for writing) W, R/W XXXX 0 1 1 1

0000B3H ICR03

Interrupt control register 03 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 04 (for writing) W, R/W XXXX 0 1 1 1

0000B4H ICR04

Interrupt control register 04 (for reading) R, R/W XX 0 0 0 1 1 1B

B

B

B

B

B

0000B5H ICR05

Interrupt control register 05 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 05 (for reading) R, R/W XX 0 0 0 1 1 1B

(Continued)

B

25

MB90560/565 Series

Abbreviat-

Address

ed Register

Name

0000B6

H ICR06

0000B7H ICR07

0000B8H ICR08

0000B9H ICR09

0000BAH ICR10

0000BBH ICR11

0000BCH ICR12

0000BDH ICR13

Register name

Read/

Write

Interrupt control register 06 (for writing) W, R/W

Resource Name Initial Value

XXXX 0 1 1 1

Interrupt control register 06 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 07 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 07 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 08 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 08 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 09 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 09 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 10 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 10 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupts

Interrupt control register 11 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 11 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 12 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 12 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 13 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 13 (for reading) R, R/W XX 0 0 0 1 1 1B

B

B

B

B

B

B

B

B

0000BEH ICR14

0000BFH ICR15

0000C0H

to

0000FF

H

000100H

to

#

H

#

H

to

001FEF

001FF0

001FF1H

H

H

PADR0

001FF2H

Interrupt control register 14 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 14 (for reading) R, R/W XX 0 0 0 1 1 1B

Interrupt control register 15 (for writing) W, R/W XXXX 0 1 1 1

Interrupt control register 15 (for reading) R, R/W XX 0 0 0 1 1 1B

Unused area

RAM area

Reserved area

Program address detection register ch0

(lower)

Program address detection register ch0

(middle)

Program address detection register ch0

(lower)

R/W

R/W XXXXXXXXB

Address match

detection

XXXXXXXXB

R/W XXXXXXXXB

(Continued)

B

B

26

(Continued)

Address

Abbreviat-

ed Register

Name

Register name

MB90560/565 Series

Read/

Write

Resource Name Initial Value

001FF3

001FF4H

001FF5H

H

PADR1

Program address detection register ch1

(lower)

Program address detection register ch1

(middle)

Program address detection register ch1

(lower)

001FF6H

to

001FFF

H

• Read/write notation

R/W : Reading and writing permitted

R : Read-only

W : Write-only

• Initial value notation

0 : Initial value is “0”.

1 : Initial value is “1”.

X : Initial value is undefined.

Unused area

R/W

R/W XXXXXXXXB

Address match

detection

XXXXXXXX

R/W XXXXXXXXB

B

27

MB90560/565 Series

INTERRUPTS, INTERRUT VECTORS, AND INTERRUPT CONTROL REGISTERS

■

2

EI

OS

Interrupt

Sup-

port

Reset #08 08

INT 9 instruction #09 09

Exception #10 0AH FFFFD4H

×

×

×

A/D converter conversion complete #11 0B

Interrupt Vector

No.

*

Address ICR Address

H FFFFDCH High

H FFFFD8H

H FFFFD0H ICR00 0000B0H

Interrupt Control

Register

Priori-

Output compare channel 0 match #13 0DH FFFFC8H

ICR01 0000B1H

8/16-bit PPG timer 0 counter borrow #14 0EH FFFFC4H

Output compare channel 1 match #15 0FH FFFFC0H

ICR02 0000B2H

8/16-bit PPG timer 1 counter borrow #16 10H FFFFBCH

Output compare channel 2 match #17 11H FFFFB8H

ICR03 0000B3H

8/16-bit PPG timer 2 counter borrow #18 12H FFFFB4H

Output compare channel 3 match #19 13H FFFFB0H

ICR04 0000B4H

8/16-bit PPG timer 3 counter borrow #20 14H FFFFACH

Output compare channel 4 match #21 15H FFFFA8H

ICR05 0000B5H

8/16-bit PPG timer 4 counter borrow #22 16H FFFFA4H

Output compare channel 5 match #23 17H FFFFA0H

ICR06 0000B6H

8/16-bit PPG timer 5 counter borrow #24 18H FFFF9CH

ty

DTP/external interrupt channel 0/1 detection #25 19H FFFF98H

ICR07 0000B7H

DTP/external interrupt channel 2/3 detection #26 1AH FFFF94H

DTP/external interrupt channel 4/5 detection #27 1BH FFFF90H

ICR08 0000B8H

DTP/external interrupt channel 6/7 detection #28 1CH FFFF8CH

8-bit timer 0/1/2 counter borrow #29 1DH FFFF88H

×

ICR09 0000B9H

16-bit reload timer 0 underflow #30 1EH FFFF84H

16-bit freerun timer overflow #31 1FH FFFF80H

×

ICR10 0000BAH

16-bit reload timer 1 underflow #32 20H FFFF7CH

Input capture channel 0/1 #33 21H FFFF78H

16-bit freerun timer clear #34 22H FFFF74H

×

ICR11 0000BBH

Input capture channel 2/3 #35 23H FFFF70H

Timebase timer #36 24H FFFF6CH

×

ICR12 0000BCH

UART1 receive #37 25H FFFF68H

ICR13 0000BDH

UART1 send #38 26H FFFF64H

UART0 receive #39 27H FFFF60H

ICR14 0000BEH

UART0 send #40 28H FFFF5CH

Flash memory status #41 29H FFFF58H

Delay interrupt output module #42 2AH FFFF54H Low

×

×

ICR15 0000BFH

28

Loading...

Loading...