查询MB90550A供应商

FUJITSU SEMICONDUCTOR

DATA SHEET

DS07-13706-2E

16-bit Proprietary Microcontroller

CMOS

F2MC-16LX MB90550A/550B Series

MB90552A/552B/553A/553B/T552A/T553A

MB90F553A/P553A

DESCRIPTION

■■■■

The MB90550A/550B series is a line of general-purpose, high-performance, 16-bit microcontrollers designed for

applications which require high-speed real-time processing, such as industrial machines, OA equipment, and

process control systems.

While inheriting the AT architecture of the F

incorporates additional instructions for high-level languages , supports extended addressing modes, and contains

enhanced multiplication and division instructions as well as a substantial collection of improved bit manipulation

instructions. In addition, the MB90550A/550B has an on-chip 32-bit accumulator which enables processing of

long-word data.

MB90552B and MB90553B are radiation noise decreased type. There are no change in the functional specification.

2

*: F

MC stands for FUJITSU Flexible Microcontroller, a registered trademark of FUJITSU LIMITED.

2

MC*-8 family, the instruction set for the MB90550A/550B series

FEATURES

■■■■

• Minimum instruction execution time: 62.5 ns (at oscillation of 4 MHz, × four times the PLL clock)

• Maximum memory space: 16 Mbytes

• Instruction set optimized for controller applications

Supported data types: Bit, byte, word and long word

Typical addressing mode: 23 types

Enhanced precision calculation realized by 32-bit accumulator

Enhanced signed multiplication/division instruction and RETI instruction functions

PACKAGES

■■■■

100-pin plastic QFP 100-pin plastic LQFP

(FPT-100P-M06) (FPT-100P-M05)

(Continued)

MB90550A/550B Series

(Continued)

• Instruction set designed for high level language (C) and multi-task operations

Adoption of system stack pointer

Symmetrical instruction set and barrel shift instructions

• Integrated address match detection function (for two address pointers)

• Faster execution speed: 4-byte queue

• Powerful interrupt functions (Eight priority levels programmable)

External interrupt inputs: 8 channels

• Data transfer functions (Intelligent I/O service): Up to 16 channels

DTP request inputs: 8 channels

• Embedded ROM size (EPROM, Flash: 128 Kbytes)

Mask ROM: 64 Kbytes/128 Kbytes

• Embedded RAM size (EPROM, Flash: 4 Kbytes)

Mask ROM: 2 Kbytes/4 Kbytes

• General-purpose por ts: Up to 83 channels

(Input pull-up resistor settable for: 16 channels; Open drain settable for: 8 channels; I/O open drains: 6 channels)

• A/D converter (RC successive approximation type): 8 channels

(Resolution: 8 or 10 bits selectable; Conversion time of 26.3 µs minimum)

• UART: 1 channel

• Extended I/O serial interface: 2 channels

2

•I

C interface: 2 channels

(Two channels, including one s witchable between terminal input and output)

• 16-bit reload timer: 2 channels

• 8/16-bit PPG timer: 3 channels

(8 bits × 2 channels; 16 bits x 1 channel: Mode switching function provided)

• 16-bit I/O timer

(Input capture × 4 channels, output compare × 4 channels, free run timer ×1 channel)

• Clock monitor function integrated (Delivering the oscillation clock divided by 21 to 28)

• Timebase timer/watchdog timer: 18 bits

• Low power consumption modes (sleep, stop, hardware standby, and CPU intermittent operation modes)

• Package: QFP-100, LQFP-100

•CMOS technology

2

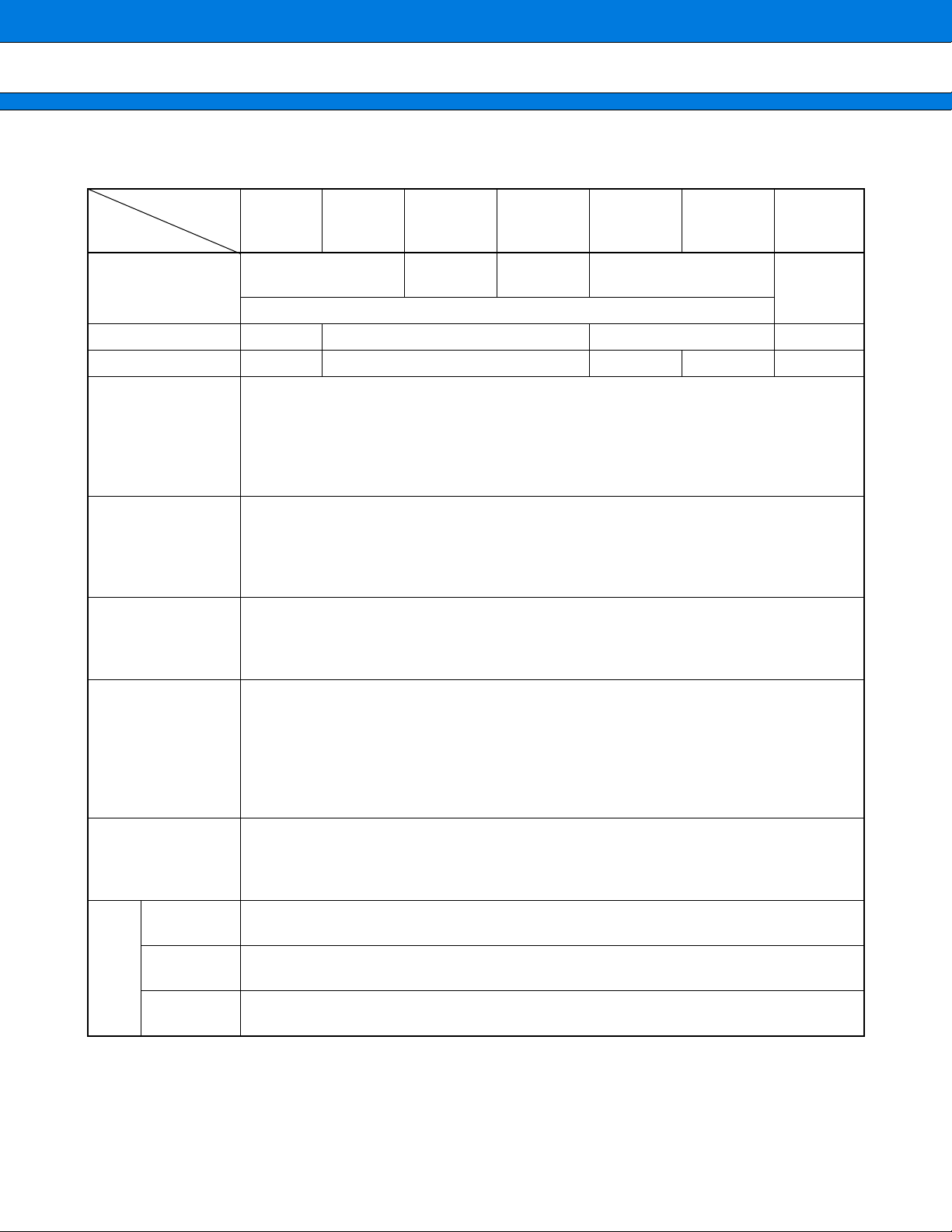

PRODUCT LINEUP

■■■■

MB90550A/550B Series

Part number

Item

Classification

ROM size 64 Kbytes 128 Kbytes None None

RAM size 2 Kbytes 4 Kbytes 2 Kbytes 4 Kbytes 6 Kbytes

CPU functions

Ports

UART (SCI)

MB90552A

MB90552B

Mask ROM products

Interrupt processing time: 1.5 ms (at machine clock of 16 MHz, minimum value)

MB90553A

MB90553B

Minimum execution time: 62.5 ns (at machine clock of 16 MHz)

General-purpose I/O ports (N-channel open-drain output): 6

General-purpose I/O ports (N-channel open-drain function selectable): 8

Clock synchronized transmission (62.5 Kbps to 2 Mbps)

Clock asynchronized transmission (62500 bps to 9615 bps)

Transmission can be performed by bi-directional serial transmission or by

MB90F553A MB90P553A MB90T552A MB90T553A MB90V550A

Flash ROM

products

Mass Product

The number of instructions: 340

Instruction bit length: 8 bits, 16 bits

Instruction length: 1 byte to 7 bytes

Data bit length: 1 bit, 8 bits, 16 bits

General-purpose I/O ports (CMOS output): 53

General-purpose I/O ports (with pull-up resistor): 16

master/slave connection.

OTP External ROM products

Total: 83

Evaluation

product

8/10-bit A/D

converter

8/16-bit PPG timer

16-bit

free run timer

16-bit

I/O

timer

Output compare (OCU)

Input capture

(ICU)

Conversion precision: 8/10-bit can be selectively used.

Number of inputs: 8

One-shot conversion mode (converts selected channel only once)

Scan conversion mode (converts two or more successive channels and can program up to

8 channels.)

Continuous conversion mode (converts selected channel continuously)

Stop conversion mode (converts selected channel and stop operation repeatedly)

Number of channels: 1 (8-bit × 2 channels)

PPG operation of 8-bit or 16-bit

A pulse wave of given intervals and given duty ratios can be output.

Pulse interval: 62.5 ns to 1 ms (at oscillation of 4 MHz, machine clock of 16 MHz)

Number of channels: 1

Overflow interrupts

Number of channels: 4

Pin input factor: A match signal of compare register

Number of channels: 4

Rewriting a register value upon a pin input (rising, falling or both edges)

(Continued)

3

MB90550A/550B Series

(Continued)

Part number

Item

MB90552A

MB90552B

MB90553A

MB90553B

MB90F553A MB90P553A MB90T552A MB90T553A MB90V550A

DTP/external

interrupt circuit

Extended I/O serial

Started by a rising edge, a falling edge, an “H” level input, or an “L” level input.

External interrupt circuit or extended intelligent I/O service (EI

Clock synchronized transmission (3125 bps to 1 Mbps)

interface

2

I

C interface Serial I/O port for supporting Inter IC BUS

Number of inputs: 8

LSB first/MSB first

2

OS) can be used.

18-bit counter

Timebase timer

Interrupt interval: 1.024 ms, 4.096 ms, 16.384 ms, 131.072 ms

(at oscillation of 4 MHz)

Watchdog timer

Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms

(at oscillation of 4 MHz, minimum value)

Process CMOS

Power supply volt-

age for operation*

4.5 V to 5.5 V

*:Varies with conditions such as the operating frequency. (See section “■ ELECTRICAL CHARA CTERISTICS”)

Assurance for the MB90V550A is given only for operation with a tool at a power voltage of 4.5 V to 5.5 V, an

operating temperature of 0°C to +25°C, and an operating frequency of 1 MHz to 16 MHz.

PACKAGE AND CORRESPONDING PRODUCTS

■■■■

Package

MB90552A

MB90552B

MB90553A

MB90553B

MB90F553A MB90P553A

FPT-100P-M05 ×

FPT-100P-M06

: Available ×: Not available

Note:For more info rmation about each package, see section “■ PACKAGE DIMENSIONS”

DIFFERENCES AMONG PRODUCTS

■■■■

Memory Size

In evaluation with an evaluation product, note the difference between the evaluation product and the product

actually used. The following items must be taken into consideration.

• The MB90V550A does not have an internal ROM. However, operations equivalent to those performed by a

chip with an internal ROM can be evaluated b y using a dedicated dev elopment tool, enabling selection of ROM

size by setting the development tool.

• In the MB90V550A, images from FF4000

H to FFFFFFH are mapped to bank 00, and FE0000H to FF3FFFH

are mapped to bank FE and FF only. (This setting can be changed by configuring the development tool.)

• In the MB90F553A/553A/553B/552A/552B, images from FF4000

H to FFFFFFH are mapped to bank 00, and

FF0000H to FF3FFFH to bank FF only.

4

PIN ASSIGNMENTS

■■■■

• FPT-100P-M06

MB90550A/550B Series

(Top View)

P20/A16

P21/A17

P22/A18

P23/A19

P24/A20

P25/A21

P26/A22

P27/A23

P30/ALE

P31/RD

V

P32/WRL

P33/WRH

P34/HRQ

P35/HAK

P36/RDY

P37/CLK

P40/SCK

P41/SOT

P42/SIN

P43/SCK1

P44/SOT1

V

P45/SIN1

P46/ADTG

P47/SCK0

P50/SDA0/SOT0

P51/SCL0/SIN0

P52/SDA1

P17/AD15

P16/AD14

P15/AD13

P14/AD12

P13/AD11

P12/AD10

P11/AD09

P10/AD08

P07/AD07

P06/AD06

P05/AD05

P04/AD04

P03/AD03

P02/AD02

P01/AD01

P00/AD00

VCCX1X0V

99989796959493929190898887868584838281

100

1

2

3

4

5

6

7

8

9

10

11

SS

12

13

14

15

16

17

18

19

20

21

22

CC

23

24

25

26

C

27

28

29

30

SS

80

PA4/CKOT

79

PA3

78

PA2

77

RST

76

PA1/OUT3

75

PA0/OUT2

74

P97/PPG5

73

P96/PPG4

72

P95/PPG3

71

P94/PPG2

70

P93/PPG1

69

P92/PPG0

68

P91/OUT1

67

P92/OUT0

66

P87/IN3

65

P86/IN2

64

P85/IN1

63

P84/IN0

62

P83/TOT1

61

P82/TOT0

60

P81/TIN1

59

P80/TIN0

58

P77/IRQ7

57

P76/IRQ6

56

P75/IRQ5

55

P74/IRQ4

54

P73/IRQ3

53

P72/IRQ2

52

HST

MD2

51

31323334353637383940414243444546474849

P53/SCL1

CC

AV

P55/SCL2

P54/SDA2

AVRL

AVRH

SS

AV

P60/AN0

P61/AN1

SS

V

P62/AN2

P63/AN3

P64/AN4

P65/AN5

P66/AN6

P67/AN7

P70/IRQ0

P71/IRQ1

MD0

(FPT-100P-M06)

50

MD1

5

MB90550A/550B Series

• FPT-100P-M05

P21/A17

P20/A16

P17/AD15

P16/AD14

P15/AD13

P14/AD12

P13/AD11

P12/AD10

P11/AD09

P10/AD08

100999897969594939291908988878685848382818079787776

(Top view)

P07/AD07

P06/AD06

P05/AD05

P04/AD04

P03/AD03

P02/AD02

P01/AD01

CC

X1X0VSSPA4/CKOT

P00/AD00

V

PA3

PA2

P22/A18

P23/A19

P24/A20

P25/A21

P26/A22

P27/A23

P30/ALE

P31/RD

V

P32/WRL

P33/WRH

P34/HRQ

P35/HAK

P36/RDY

P37/CLK

P40/SCK

P41/SOT

P42/SIN

P43/SCK1

P44/SOT1

V

P45/SIN1

P46/ADTG

P47/SCK0

1

2

3

4

5

6

7

8

9

SS

10

11

12

13

14

15

16

17

18

19

20

CC

21

22

23

24

25

C

26272829303132333435363738394041424344454647484950

CC

AV

P53/SCL1

P52/SDA1

P55/SCL2

P54/SDA2

AVRL

AVRH

SS

AV

P60/AN0

P61/AN1

P62/AN2

P63/AN3

SS

V

P64/AN4

P65/AN5

P66/AN6

P67/AN7

MD0

P70/IRQ0

P71/IRQ1

MD1

MD2

HST

75

RST

74

PA1/OUT3

73

PA0/OUT2

72

P97/PPG5

71

P96/PPG4

70

P95/PPG3

69

P94/PPG2

68

P93/PPG1

67

P92/PPG0

66

P91/OUT1

65

P90/OUT0

64

P87/IN3

63

P86/IN2

P85/IN1

62

61

P84/IN0

60

P83/TOT1

59

P82/TOT0

58

P81/TIN1

57

P80/TIN0

56

P77/IRQ7

55

P76/IRQ6

P75/IRQ5

54

53

P74/IRQ4

P73/IRQ3

52

51

P72/IRQ2

P51/SCL0/SIN0

P50/SDA0/SOT0

(FPT-100P-M05)

6

PIN DESCRIPTION

■■■■

MB90550A/550B Series

Pin no.

QFP LQFP

82 80 X0 A Oscillation pin

83 81 X1 A Oscillation pin

77 75 RST

52 50 HST C Hardware standby input pin

85 to 92 83 to 90

93 to

100

1 to 8

91 to 98

99,100,

1 to 6

97

Pin name Circuit type Function

B Reset input pin

General-purpose I/O ports.

P00 to P07

D

(CMOS)

AD00 to

AD07

P10 to P17

D

(CMOS)

AD08 to

AD15

P20 to P27

E

(CMOS)

A16 to A23

P30

E

(CMOS)

ALE

A pull-up resistor can be added (RD07 to RD00 = 1) by using

the pull-up resistor setting register (RDR0).

D07 to D00 = 1: Disabled when the port is set for output.

Serve as lower data I/O/lower address output (AD00 to AD07)

pins in the external bus mode.

General-purpose I/O ports.

A pull-up resistor can be added (RD17 to RD10 = 1) by using the

pull-up resistor setting register (RDR1).

D17 to D10 = 1: Disabled when the port is set for output.

Serve as upper data I/O/middle address output (AD08 to AD15)

pins in the 16-bit bus-width, external bus mode.

General-purpose I/O ports.

This function is enabled either in single-chip mode or with the

external address output control register set to “Port”.

External address bus A16 to A23 output pins.

This function is enabled in an external-bus enabled mode with

the external address output register set to “Address”.

General-purpose I/O port.

This function is enabled in single-chip mode.

Address latch enable output pin.

This function is enabled in an external-bus enabled mode.

10 8

12 10

13 11

P31

RD

P32

WRL

P33

WRH

E

(CMOS)

E

(CMOS)

E

(CMOS)

General-purpose I/O port.

This function is enabled in single-chip mode.

Read strobe output pin for the data bus.

This function is enabled in an external-bus enabled mode.

General-purpose I/O port.

This function is enabled in single-chip mode.

Write strobe output pin for the lower eight bits of the data bus.

This function is enabled in an external-bus enabled mode.

General-purpose I/O port.

This function is enabled in single-chip mode.

Write strobe output pin for the upper eight bits of the data bus.

This function is enabled in an external-bus enabled mode.

(Continued)

7

MB90550A/550B Series

Pin no.

QFP LQFP

14 12

15 13

16 14

17 15

18 16

Pin name Circuit type Function

P34

E

(CMOS)

HRQ

P35

E

(CMOS)

HAK

P36

E

(CMOS)

RDY

P37

E

(CMOS)

CLK

P40

F

(CMOS/H)

SCK

General-purpose I/O port.

This function is enabled in single-chip mode

Hold request input pin.

This function is enabled in an external-bus enabled mode.

General-purpose I/O port.

This function is enabled in single-chip mode.

Hold acknowledge output pin.

This function is enabled in an external-bus enabled mode.

General-purpose I/O port.

This function is enabled in single-chip mode.

Ready signal input pin.

This function is enabled in an external-bus enabled mode.

General-purpose I/O port.

This function is enabled in single-chip mode.

CLK output pin.

This function is enabled in an external-bus enabled mode.

General-purpose I/O port.

Serves as an open-drain output port (OD40 = 1) depending on the

setting of the open-drain control setting register (ODR4).

(D40 = 0: Disabled when the port is set for input.)

UART serial clock I/O pin.

This function is enabled with the UART clock output enabled.

19 17

20 18

21 19

P41

SOT

P42

SIN

P43

SCK1

F

(CMOS/H)

F

(CMOS/H)

F

(CMOS/H)

General-purpose I/O port.

Serves as an open-drain output port (OD41 = 1) depending on the

setting of the open-drain control setting register (ODR4).

(D41 = 0: Disabled when the port is set for input.)

UART serial data output pin.

This function is enabled with the UART serial data output enabled.

General-purpose I/O port.

Serves as an open-drain output port (OD42 = 1) depending on the

setting of the open-drain control setting register (ODR4).

(D42 = 0: Disabled when the port is set for input.)

UART serial data input pin. Since this input is used as required while

the UART is operating for input, the output by any other function

must be off unless used intentionally.

General-purpose I/O port.

Serves as an open-drain output port (OD43 = 1) depending on the

setting of the open-drain control setting register (ODR4).

(D43 = 0: Disabled when the port is set for input.)

Extended I/O serial clock I/O pin. This function is enabled with the

extended I/O serial clock output enabled.

(Continued)

8

MB90550A/550B Series

Pin no.

QFP LQFP

22 20

24 22

25 23

Pin name Circuit type Function

General-purpose I/O port.

P44

F

Serves as an open-drain output port (OD44 = 1) depending on

the setting of the open-drain control setting register (ODR4).

(D44 = 0: Disabled when the port is set for input.)

(CMOS/H)

Extended I/O serial data output pin.

SOT1

This function is enabled with the extended I/O serial data output

enabled.

General-purpose I/O port.

P45

F

(CMOS/H)

SIN1

Serves as an open-drain output port (OD45 = 1) depending on

the setting of the open-drain control setting register (ODR4).

(D45 = 0: Disabled when the port is set for input.)

Extended I/O serial data input pin.

Since this input is used as required while the extended I/O serial

interface is operating for input, the output by any other function

must be off unless used intentionally.

General-purpose I/O port.

P46

F

(CMOS/H)

ADTG

Serves as an open-drain output port (OD46 = 1) depending on

the setting of the open-drain control setting register (ODR4).

(D46 = 0: Disabled when the port is set for input.)

A/D converter external trigger input pin.

Since this input is used as required while the A/D converter is operating for input, the output by any other function must be off unless used intentionally.

P47

26 24

F

(CMOS/H)

SCK0

27 25 C —

P50

SDA0

28 26

G

(NchOD/H)

SOT0

General-purpose I/O port.

Serves as an open-drain output port (OD47 = 1) depending on

the setting of the open-drain control setting register (ODR4).

D47 = 0: Disabled when the port is set for input.

Extended I/O serial clock I/O pin. This function is enabled with

the extended I/O serial clock output enabled.

Capacitance pin for regulating the power supply.

Connect an external ceramic capacitor of about 0.1 µF.

N-channel open-drain I/O port.

2

I

C interface data I/O pin.

This function is enabled with the I

2

C interface enabled for

operation.

While the I

2

C interface is operating, place the port output in the

Hi-Z state (PDR = 1).

Extended I/O serial data output pin.

This function is enabled with the extended I/O serial data output

enabled.

(Continued)

9

MB90550A/550B Series

Pin no.

QFP LQFP

29 27

30,32 28,30

31,33 29,31

38 to 41,

43 to 46

36 to 39,

41 to 44

Pin name Circuit type Function

P51

SCL0

G

(NchOD/H)

N-channel open-drain I/O port.

2

I

C interface clock I/O pin. This function is enabled with the

2

I

C interface enabled for operation.

While the I

2

C interface is operating, place the port output in

the Hi-Z state (PDR = 1).

Extended I/O serial data input pin.

SIN0

Since this input is used as required while the extended I/O

serial interface is operating for input, the output by any other

function must be off unless used intentionally.

P52,P54

SDA1,SDA2

G

(NchOD/H)

N-channel open-drain I/O ports.

2

C interface data I/O pins. This function is enabled with the

I

2

I

C interface enabled for operation.

While the I

2

C interface is operating, place the port output in

the Hi-Z state (PDR = 1).

P53,P55

SCL1,SCL2

G

(NchOD/H)

N-channel open-drain I/O ports.

2

C interface clock I/O pins. This function is enabled with the

I

2

I

C interface enabled for operation.

While the I

2

C interface is operating, place the port output in

the Hi-Z state (PDR = 1).

P60 to P67

AN0 to AN7

H

(CMOS/H)

General-purpose I/O ports.

A/D converter analog input pin. This function is enabled with

the analog input enabled.

47,48,

53 to 58

45,46,

51 to 56

59,60 57,58

61,62 59,60

63 to 66 61 to 64

67,68 65,66

P70 to P77

IRQ0 to IRQ7

I

(CMOS/H)

General-purpose I/O ports.

External interrupt request input pins.

Since this input is used as required while external interrupts

remain enabled, the output by any other function must be off

unless used intentionally.

P80,P81

TIN0,TIN1

J

(CMOS/H)

General-purpose I/O ports.

Reload timer event input pins.

Since this input is used as required while the reload timer is

operating for input, the output by any other function must be

off unless used intentionally.

P82,P83

General-purpose I/O ports.

J

TOT0,TOT1

P84 to P87

IN0 to IN3

(CMOS/H)

J

(CMOS/H)

Reload timer output pins.This function is enabled with reroad

timer output enabled.

General-purpose I/O ports.

Input capture trigger input pins.

Since this input is used as required while the input capture

unit is operating for input, the output by any other function

must be off unless used intentionally.

P90,P91

OUT0,OUT1 Output compare event output pins.

J

(CMOS/H)

General-purpose I/O ports.

(Continued)

10

(Continued)

Pin no.

QFP LQFP

MB90550A/550B Series

Pin name Circuit type Function

P92 to P97

69 to 74 67 to 72

PPG0 to

PPG5

PA0,PA1

75,76 73,74

OUT2,OUT3 Output compare event output pins.

78,79 76,77 PA2,PA3

PA4

80 78

CKOT Serves as the CKOT output while the CKOT is operating.

34 32 AV

J

(CMOS/H)

J

(CMOS/H)

J

(CMOS/H)

J

(CMOS/H)

CC A/D converter power-supply pin.

General-purpose I/O ports.

PPG output pins. This function is enabled with the PPG output

enabled.

General-purpose I/O ports.

General-purpose I/O ports.

General-purpose I/O port.

35 33 AVRH A/D converter external reference voltage source pin.

36 34 AVRL A/D converter external reference voltage source pin.

37 35 AV

49,50 47,48 MD0,MD1 C

SS A/D converter power-supply pin.

Operation mode setting input pins.

Connect these pins directly to Vcc or Vss.

Operation mode setting input pin.

K

51 49 MD2

C

Connect this pin directly to Vcc or Vss. (MB90552A/552B/553A/

553B/V550A)

Operation mode setting input pin.

Connect this pin directly to Vcc or Vss. (MB90P553A/F553A)

23,84 21,82 V

11,42,819,40,

79

CC Power (5 V) input pins.

V

SS Power (0 V) input pins.

11

MB90550A/550B Series

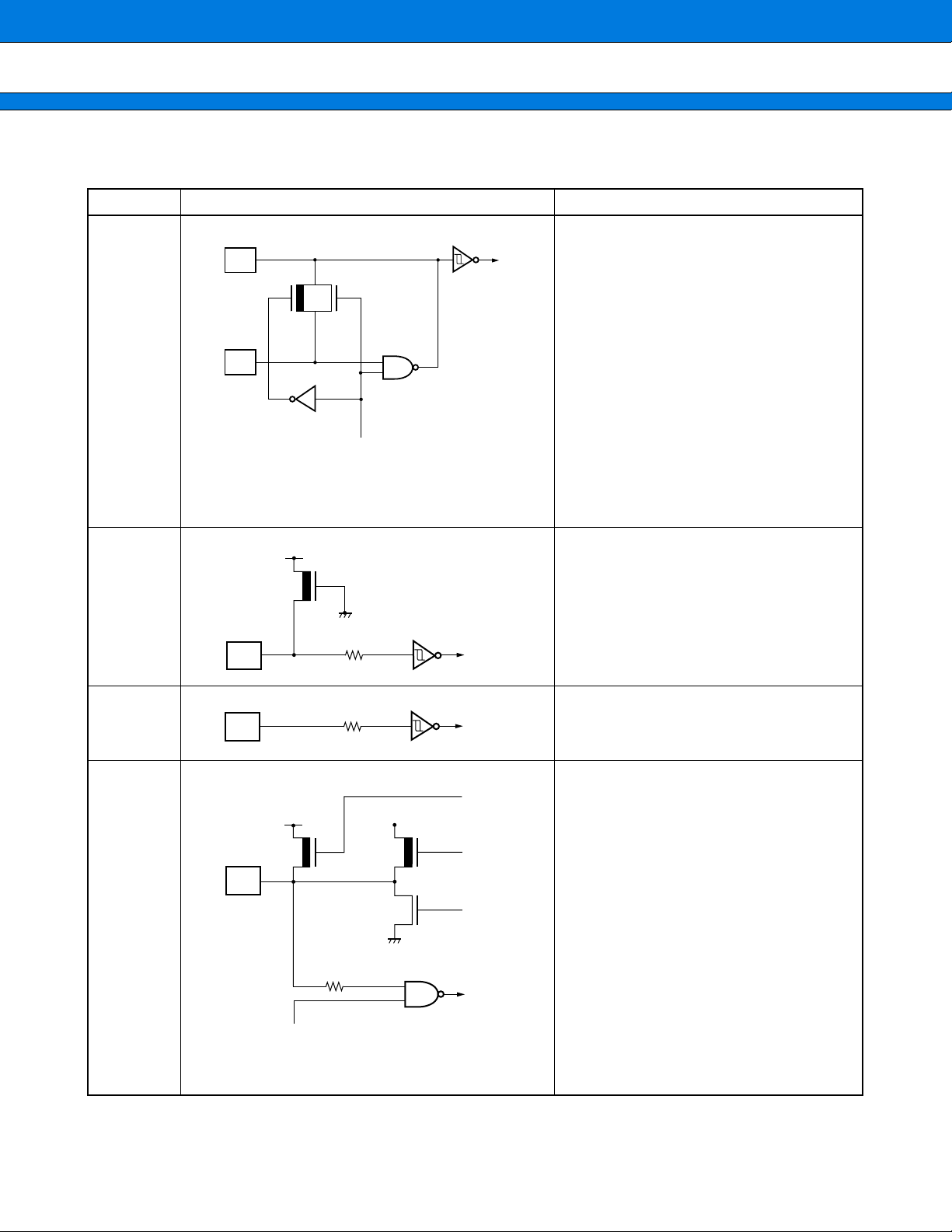

I/O CIRCUIT TYPE

■■■■

Type Circuit Remarks

Clock input

X1

• 3 MHz to 32 MHz

• Oscillator recovery resistor approx. 1MΩ

A

X0

HARD,SOFT

STANDBY

CONTROL

• CMOS level hysteresis input

• Pull-up resistor provided

Resistor: About 50 kΩ

B

• CMOS level hysteresis input

C

Pull-up resistor control

• CMOS level output

• CMOS level input

• Standby control provided

Digital output

• Input pull-up resistor control provided

Resistor: About 50 kΩ

12

Digital output

D

Digital input

HARD,SOFT

STANDBY

CONTROL

(Continued)

MB90550A/550B Series

Type Circuit Remarks

• CMOS level output

Digital output

Digital output

E

Digital input

HARD,SOFT

STANDBY

CONTROL

• CMOS level input

• Standby control provided

Open- drain

control

signal

Digital input

• CMOS level output

• CMOS level hysteresis input

• Open-drain control provided

F

Digital input

HARD,SOFT

STANDBY

CONTROL

• N-channel open-drain output

• CMOS level hysteresis input

Digital output

• Standby control provided

Note: Unlike normal CMOS I/O pins, this

pin is not provided with any P-channel

G

Digital input

transistor. Therefore the pin does not allow

a current to flow to the Vcc side even when

applied with a voltage from an external

HARD,SOFT

STANDBY

CONTROL

device with the IC’s power supply left off.

• CMOS level output

Digital output

• CMOS level hysteresis input

• Standby control provided

• Analog input

Digital output

H

HARD,SOFT

STANDBY

CONTROL

A/D

DISABLE

Analog input

Digital input

(Continued)

13

MB90550A/550B Series

(Continued)

Type Circuit Remarks

• CMOS level output

Digital output

Digital output

I

Digital input

HARD

STANDBY

CONTROL

Digital output

• CMOS level hysteresis input

• Standby control provided

• CMOS level output

• CMOS level hysteresis input

• Standby control provided

Digital output

J

Digital input

HARD,SOFT

STANDBY

CONTROL

• CMOS level hysteresis input

• Pull-up resistor provided

Resistor: About 50 kΩ

K

14

MB90550A/550B Series

HANDLING DEVICES

■■■■

1. Preventing Latchup

CMOS ICs may cause latchup in the following situations:

• When a voltage higher than Vcc or lower than Vss is applied to input or output pins.

• When a voltage exceeding the rating is applied between Vcc and Vss.

• When AVcc power is supplied prior to the Vcc voltage.

If latchup occurs, the power supply current increases rapidly, sometimes resulting in thermal breakdown of the

device. Use meticulous care not to let it occur.

For the same reason, also be careful not to let the analog power-supply v oltage e xceed the digital pow er-supply

voltage.

2. Handling unused input pins

Leaving unused input pins open ma y cause a malfunction or latch-up which leads to fatal damage to the de vice .

Therefore they must be pulled up or pulled down through at least 2 kΩ resistance. Also, unused input/output

pins should be left open in output state or handled in the same way as unused input pins.

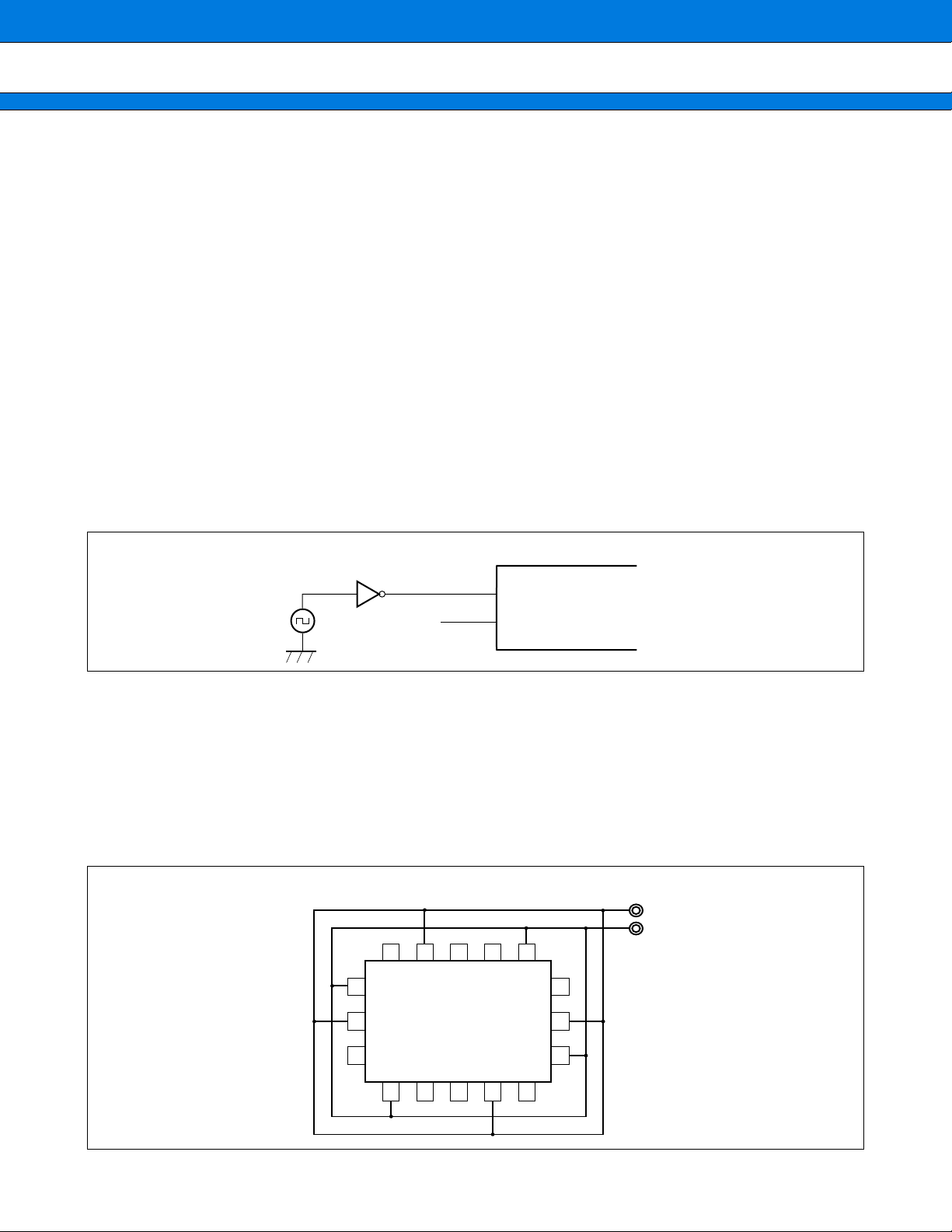

3. Notes on Using External Clock

In using the external clock, drive X0 pin only and leave X1 pin unconnected.

Using external clock

•

MB90550A/550B series

X0

Open

X1

4. Power Supply Pins (VCC/VSS)

In products with multiple VCC or VSS pins, the pins of a same potential are internally connected in the device to

avoid abnormal operations including latch-up. However, the pins should be connected to external power and

ground lines to lower the electro-magnetic emission level and abnormal operation of strobe signals caused by

the rise in the ground level, and to conform to the total current rating.

Make sure to connect V

It is recommended that a bypass capacitor of around 0.1 µF be placed between the V

device.

Using

•

power supply pins

CC and VSS pins via lowest impedance to power lines.

V

CC

V

SS

V

SS

MB90550A/550B

V

V

CC

series

CC

CC and VSS pins near the

V

CC

V

SS

V

SS

V

V

SS

CC

15

MB90550A/550B Series

5. Crystal Oscillator Circuit

Noises around X0 or X1 pins may cause abnormal operations. Make sure to provide bypass capacitors via

shortest distance from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure

that lines of oscillation circuit not cross the lines of other circuits.

A printed circuit board artwor k surrounding the X0 and X1 pins with grand area for stabilizing the operation is

highly recommended.

6. Turning-on Sequence of Power Supply to A/D Converter and Analog Inputs

Make sure to turn on the A/D converter power supply, D/A converter power supply (AVCC, AVRH, AVRL) and

analog inputs (AN0 to AN7) after turning-on the digital power supply (V

Turn-off the digital power after turning off the A/D converter supply and analog inputs. In this case, make sure

that the voltage does not exceed AVRH or AV

CC (turning on/off the analog and digital power supplies simulta-

neously is acceptable).

7. Connection of Unused Pins of A/D Converter

Connect unused pin of A/D converter to AVCC = VCC, AVSS = AVRH = AVRL = VSS.

8. N.C. Pin

The N.C. (internally connected) pin must be opened for use.

CC).

9. Notes on Energization

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at 50

µs or more.

10. Indeterminate outputs from ports 0 and 1

The outputs from ports 0 and 1 become indeterminate during oscillation setting time of step-down circuit (during

a power-on reset) after the power is turned on. (MB90552A, MB90552B, MB90553A, MB90553B , MB90F553A,

MB90V550A)

The series without built-in step-down circuit has no oscillation setting time of step-down circuit, so outputs should

not become indeterminate. (MB90P553A)

Timing chart of indeterminate outputs from ports 0 and 1

2

VCC (power-supply pin)

PONR (power-on reset) signal

RST (external asynchronous reset) signal

RST (internal reset) signal

Oscillation clock signal

Oscillation setting time *

Step-down circuit setting time *

1

KA (internal operating clock A) signal

KB (internal operating clock B) signal

PORT (port output) signal

Period of indeterminate

*1: Step-down circuit setting time 217/oscillation clock frequency (oscillation clock frequency of 16 MHz: 8.19 ms)

*2: Oscillation setting time 2

18

/oscillation clock frequency (oscillation clock frequency of 16 MHz: 16.38 ms)

16

MB90550A/550B Series

11. Initialization

In the device, there are internal registers which is initialized only by a po wer-on reset. To initialize these registers

turning on the power again.

12. Return from standby state

If the power-supply voltage goes below the standby RAM holding voltage in the standby state, the device may

fail to return from the standby state. In this case, reset the de vice via the external reset pin to return to the normal

state.

13. Precautions for Use of ’DIV A, Ri,’ and ’DIVW A, Ri’ Instructions

The signed multiplication-division instructions ’DIV A, Ri,’ and ’DIVW A, RWi’ should be used when the corresponding bank registers (DTB, ADB, USB , SSB) are set to value ’00h.’ If the corresponding bank registers (DTB,

ADB, USB, SSB) are set to a v alue other than ’00h,’ the remainder obtained after the ex ecution of the instruction

will not be placed in the instruction operand register.

14. Using of REALOS

The use of EI2OS is not possible the REALOS real time operating system.

17

MB90550A/550B Series

BLOCK DIAGRAM

■■■■

X0, X1

RST

HST

P00 to P07/

AD00 to AD07

P10 to P17/

AD08 to AD15

P20 to P27/

A16 to A23

P30/ALE

P31/RD

P32/WRL

P33/WRH

P34/HRQ

P35/HAK

P36/RDY

P37/CLK

P40/SCK

P41/SOT

P42/SIN

Clock control

4

circuit*

RAM

ROM

Port 0

Port 1

Port 2

Port 3

Port 4

Communication prescaler

UART

CPU

Core of F2MC-16LX

family

F

F

M

C

16

L

X

B

U

S

Interrupt controller

Port A

Clock monitor function

Port 9

8/16 PPG × 3c h

I/O timer

16-bit output compare

unit x 4 channels

16-bit input capture

unit x 4 channels

16-bit free-run timer

16-bit reload timer

x 2 channels

Port 8

CKOT/PA4

PA2, A3

OUT2, OUT3/

PA0, A1

PPG5/P97

PPG4/P96

PPG3/P95

PPG2/P94

PPG1/P93

PPG0/P92

OUT0, OUT1/

P90, P91

IN0 to IN3/

P84 to P87

TOT0, TOT1/

P82, P83

TIN0, TIN1/

P80, P81

18

P43/SCK1

P44/SOT1

P45/SIN1

P46/ADTG

P47/SCK0

P50/SDA0/SOT0

P51/SCL0/SIN0

P52/SDA1

P53/SCL1

P54/SDA2

P55/SCL2

Extended I/O

serial interface 1

Extended I/O

serial interface 0

I2C interface 0

2

C interface 1

I

Port 5

Port 7

External interrupt

A/D converter

(8/10 bits)

IRQ0 to IRQ7/

P70 to P77

AV

AVRH, AVRL

AV

AN0 to AN7/

P60 to P67

Port 6

pecifications of evaluation model

*: S

(MB90V550A)

Contains no internal ROM.

Contains 6 KB of internal RAM.

Contains the same internal resources as the

other products in the MB90550A/550B series.

CC

SS

Loading...

Loading...