Page 1

查询MB86293供应商

M

M

B

B

8

8

6

6

2

2

9

9

3

3

<

<

C

C

O

O

R

R

A

A

L

L

_

_

L

L

Q

Q

>

>

Grraapphhiiccss

G

SSppeecciiffiiccaattiioonnss

Revision 1.1

14th Jan, 2003

Coonnttrroolllleerr

C

Copyright © FUJITSU LIMITED 2001

ALL RIGHTS RESERVED

Page 2

• The specifications in this manual are subject to change without notice. Contact our Sales

Department before purchasing the product described in this manual.

• Information and circuit diagrams in this manual are only examples of device applications, they are

not intended to be used in actual equipment. Also, Fujitsu accepts no responsibility for

infringement of patents or other rights owned by third parties caused by use of the information and

circuit diagrams.

• The contents of this manual must not be reprinted or duplicated without permission of Fujitsu.

• Fujitsu’s semiconductor devices are intended for standard uses (such as office equipment

(computers and OA equipment), industrial/communications/measuring equipment, and

personal/home equipment). Customers using semiconductor devices for special applications

(including aerospace, nuclear, military and medical applications) in which a failure or malfunction

might endanger life or limb and which require extremely high reliability must contact our Sales

Department first. If damage is caused by such use of our semiconductor devices without first

consulting our Sales Department, Fujitsu will not assume any responsibility for the loss.

• Semiconductor devices fail with a known probability. Customers must use safety design (such as

redundant design, fireproof design, over-current prevention design, and malfunction prevention

design) so that failures will not cause accidents, injury or death).

• If the products described in this manual fall within the goods or technologies regulated by the

Foreign Exchange and Foreign Trade Law, permission must be obtained before exporting the goods

or technologies.

ii

Page 3

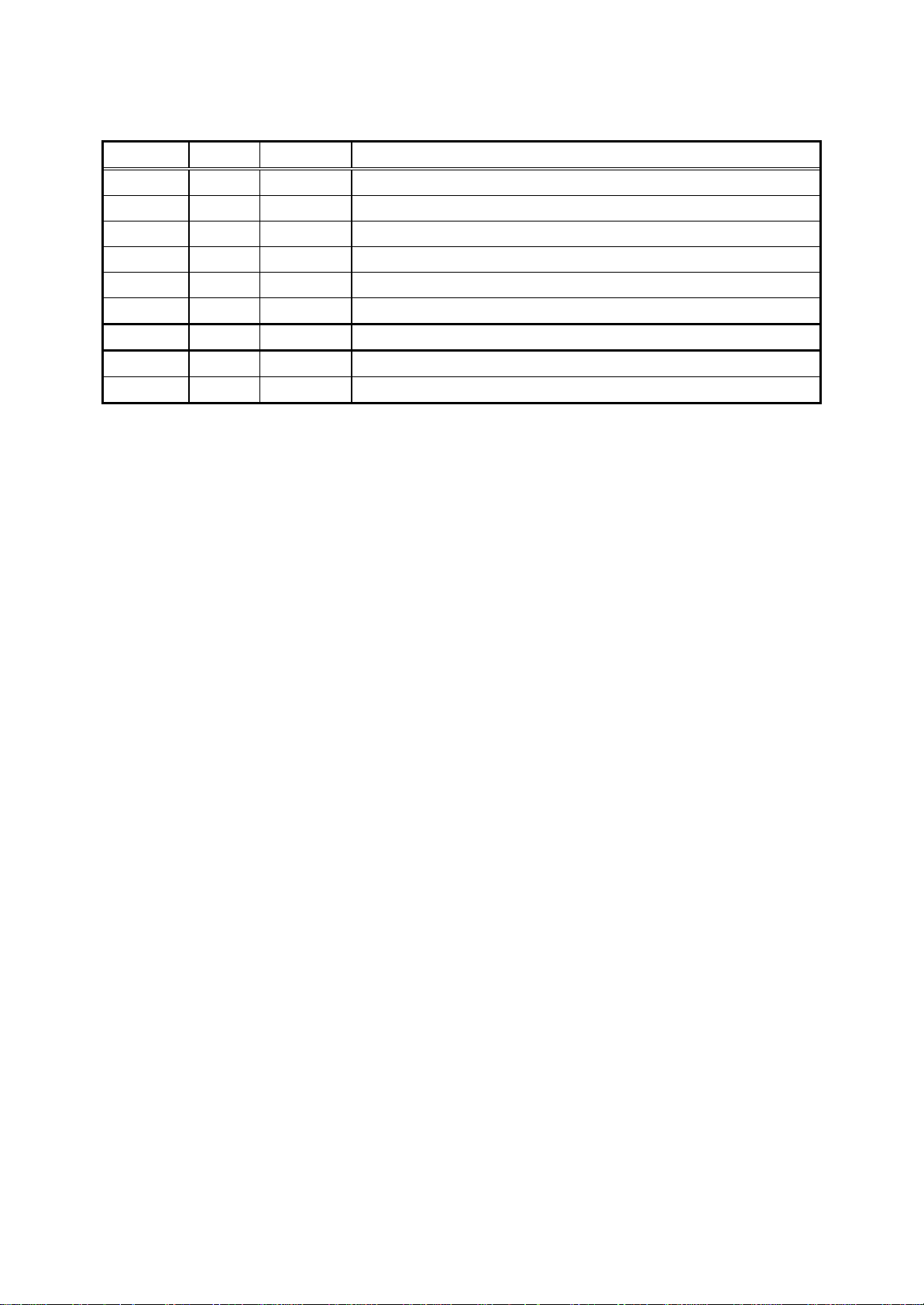

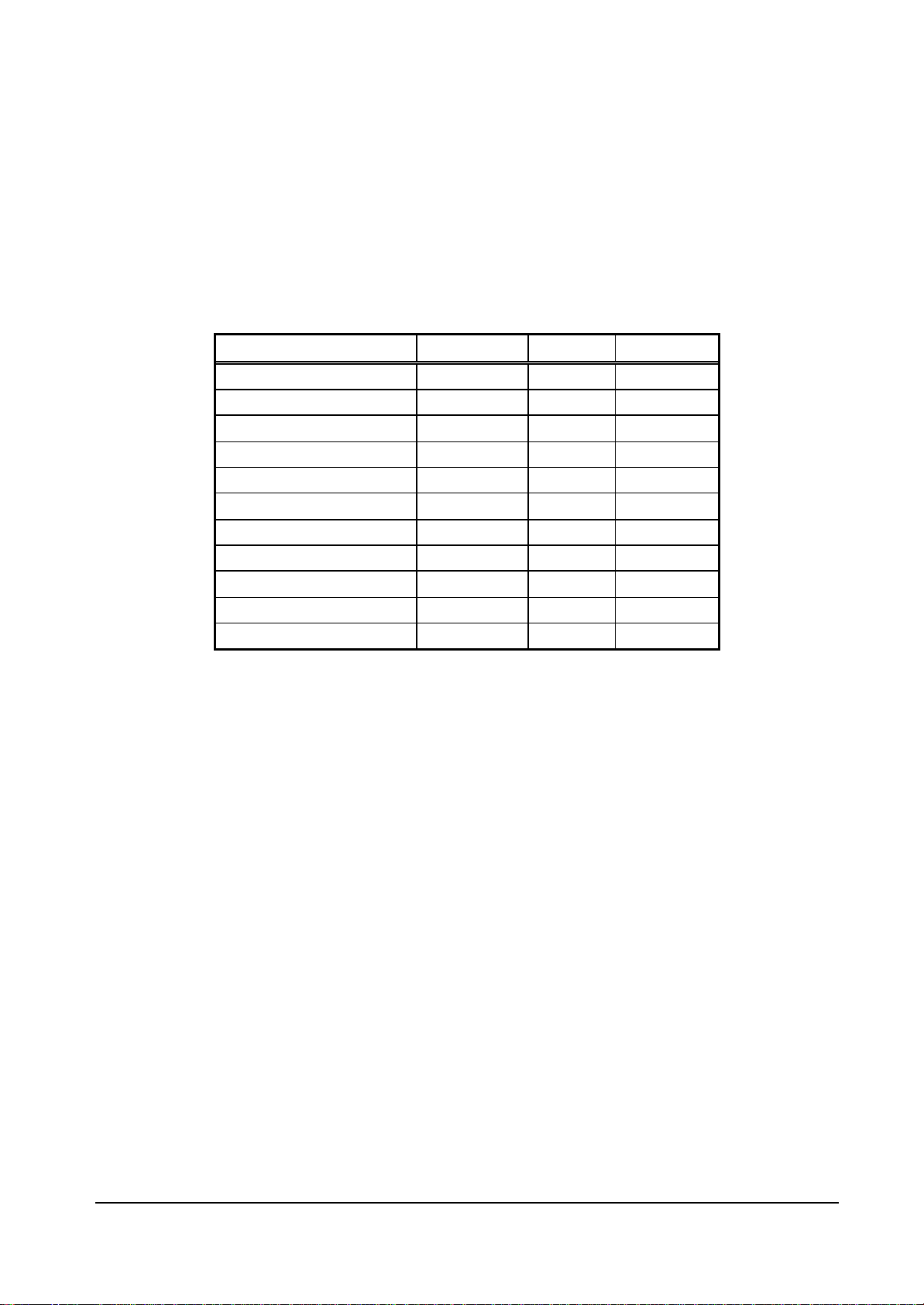

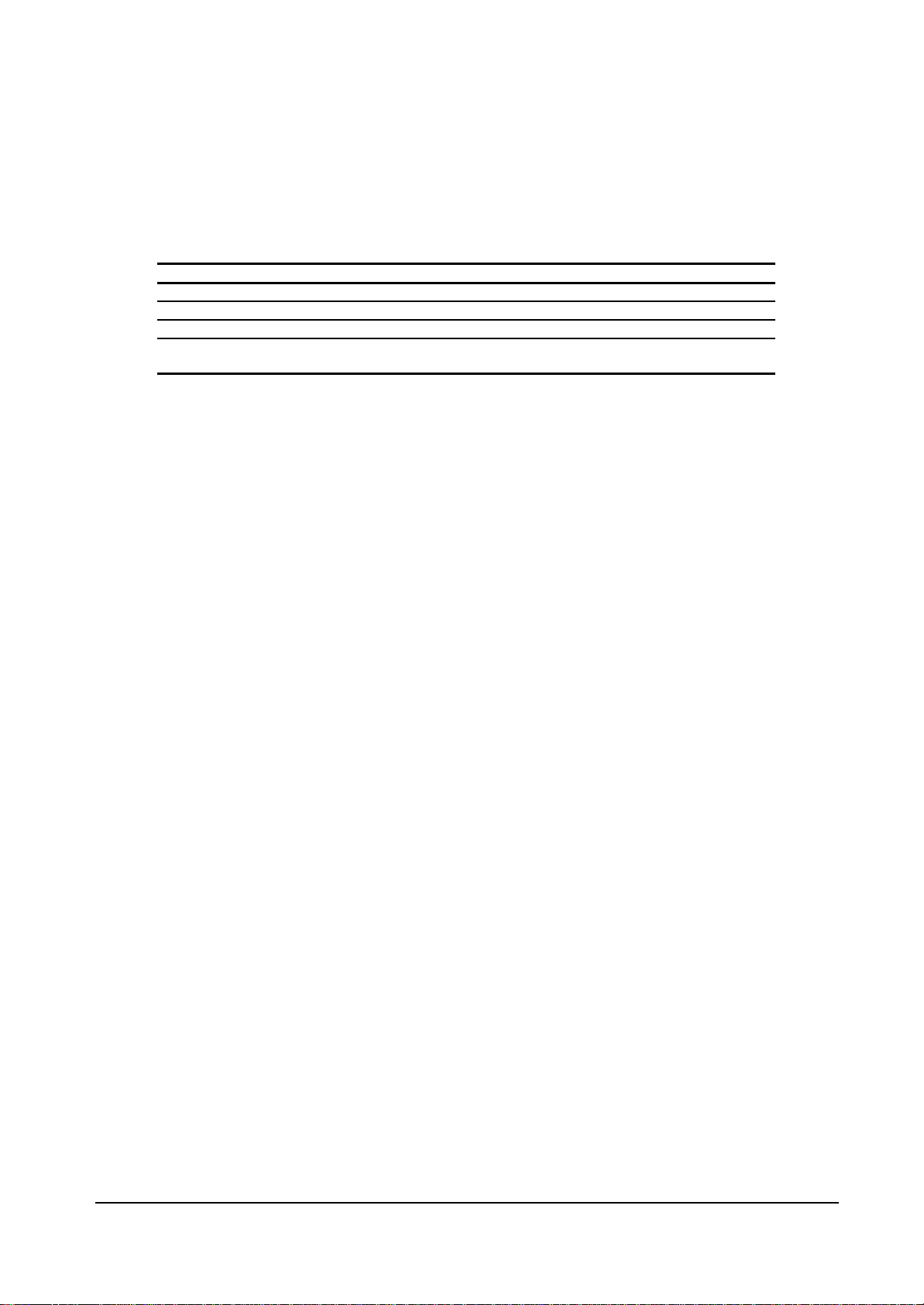

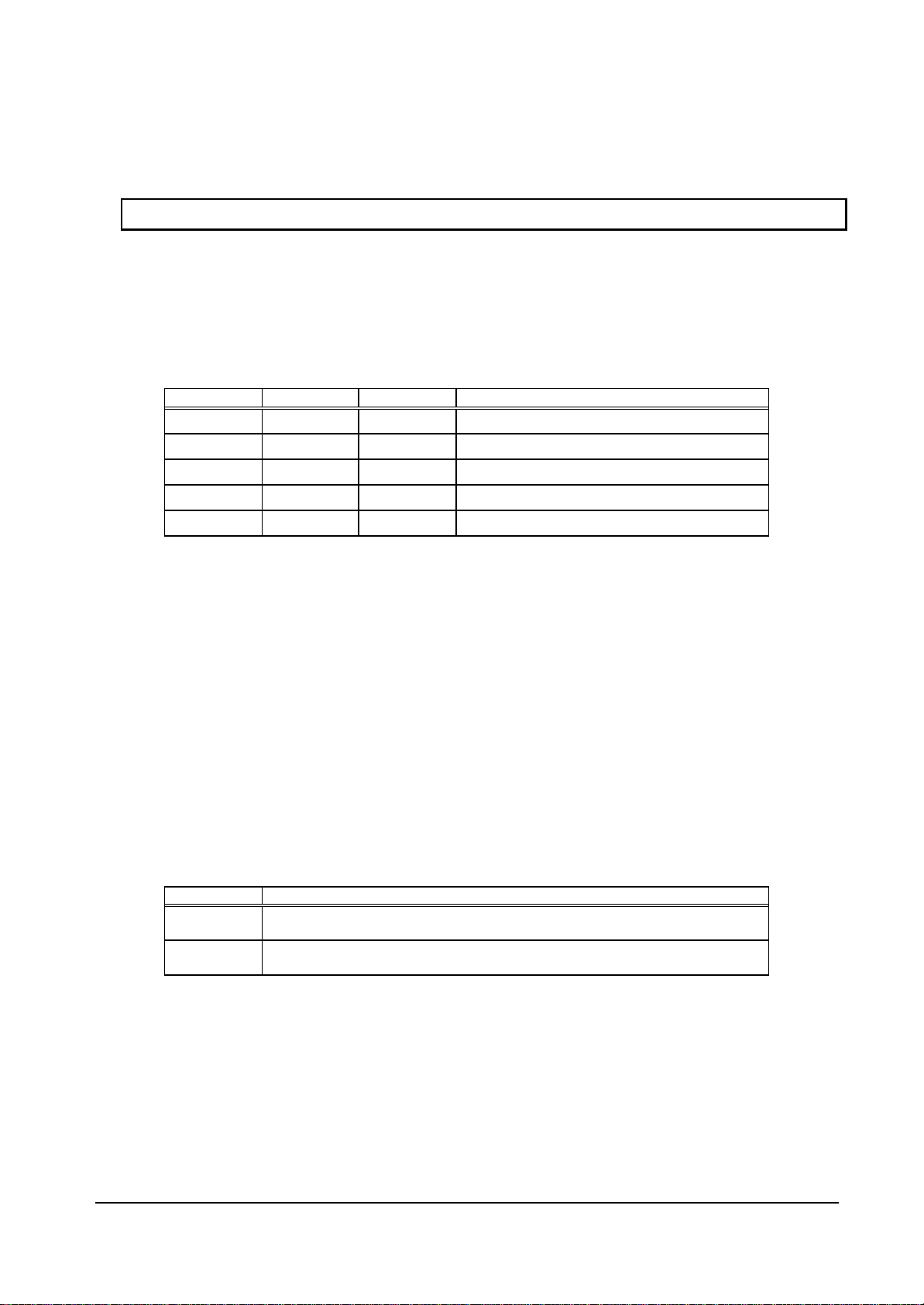

Update history

Date Version Page count Change

2001.2.22 0.1 31 First edition

2001.7.23 0.2 228 See separate paper (Page count difference between Orchid and Coral)

2001.8.23 0.3 238 See separate paper (Page count difference between Rev0.2 and Rev0.3)

2001.11.12 0.4 262 See separate paper (Page count difference between Rev0.3 and Rev0.4)

2001.12.8 0.5 266 See separate paper (Page count difference between Rev0.4 and Rev0.5)

2002.1.9 0.6 266 See separate paper (Page count difference between Rev0.5 and Rev0.6)

2002.4.15 0.7 274 See separate paper (Page count difference between Rev0.6 and Rev0.7)

2002.5.21 0.8 274 See separate paper (Page count difference between Rev0.7 and Rev0.8)

2003.1.14 1.1 284 See separate paper (Page count difference between Rev0.8 and Rev1.1)

Page 4

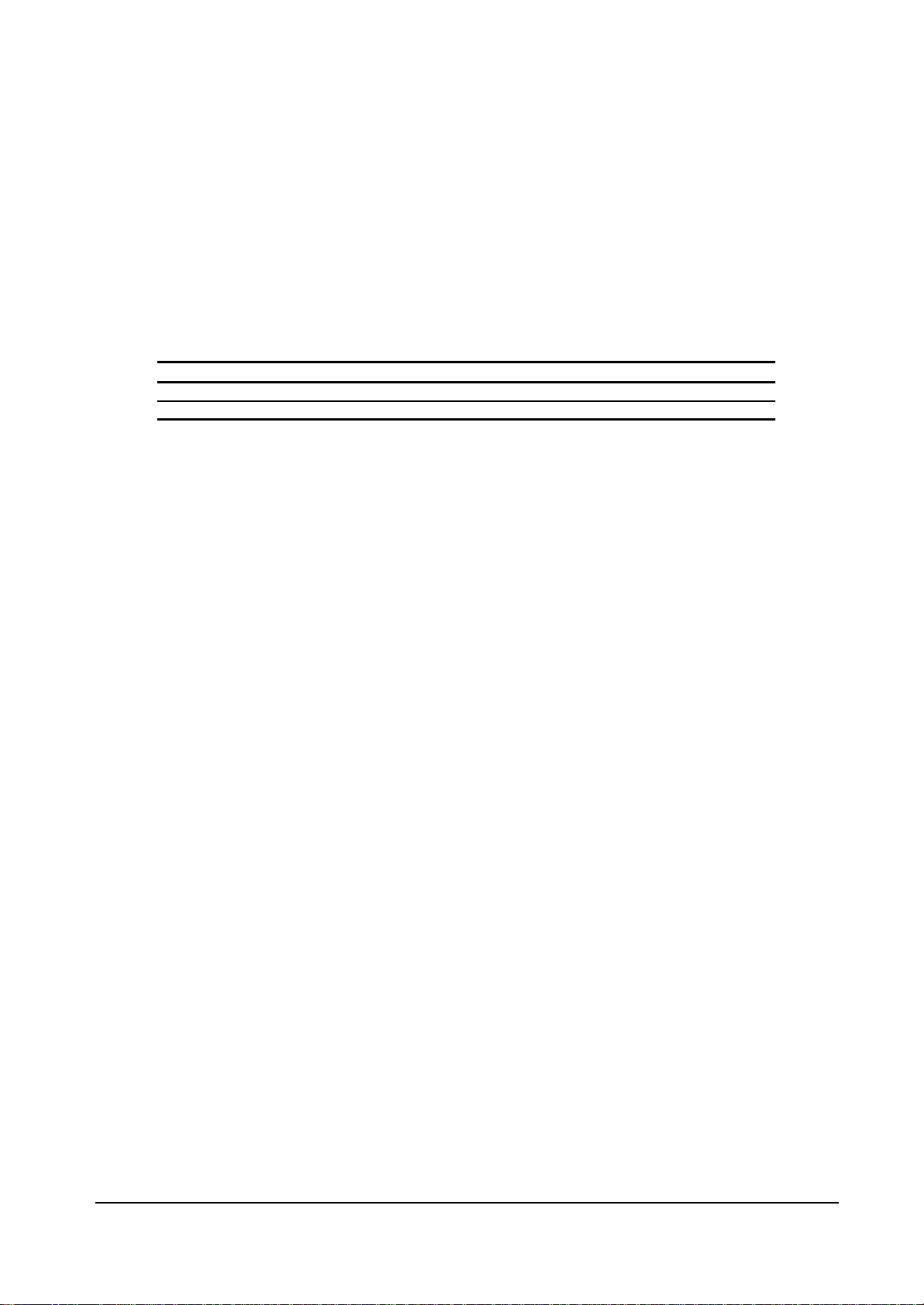

CONTENTS

1 GENERAL............................................................................................................................ 10

1.1 PREFACE......................................................................................................................... 10

1.2 FEATURES .......................................................................................................................11

1.3 BLOCK DIAGRAM.............................................................................................................. 12

1.4 FUNCTIONAL OVERVIEW..................................................................................................... 13

1.4.1 Host CPU interface .................................................................................................13

1.4.2 External memory interface ..................................................................................... 15

1.4.3 Display controller ................................................................................................... 16

1.4.4 Geometry processing............................................................................................... 18

1.4.5 2D Drawing ............................................................................................................ 19

1.4.6 3D Drawing ............................................................................................................ 21

1.4.7 Special effects......................................................................................................... 22

1.4.8 Others .................................................................................................................... 25

2 PINS .................................................................................................................................... 26

2.1 SIGNALS.......................................................................................................................... 26

2.1.1 Signal lines............................................................................................................. 26

2.2 PIN ASSIGNMENT ..............................................................................................................27

2.2.1 Pin assignment diagram ......................................................................................... 27

2.2.2 Pin assignment table .............................................................................................. 28

2.3 PIN FUNCTION.................................................................................................................. 30

2.3.1 Host CPU interface .................................................................................................30

2.3.2 Video output interface............................................................................................. 32

2.3.3 Graphics memory interface .....................................................................................33

2.3.4 Clock input ............................................................................................................. 34

2.3.5 Test pins................................................................................................................. 35

2.3.6 Reset sequence ....................................................................................................... 35

3 PROCEDURE OF THE HAR DWARE INITIALIZATION ...........................................................36

3.1 HARDWARE RESET ............................................................................................................ 36

3.2 RE -RESET .......................................................................................................................36

3.3 SOFTWARE RESET............................................................................................................. 36

4 HOST INTERFACE............................................................................................................... 37

4.1 OPERATION M ODE ............................................................................................................37

4.1.1 Host CPU mode ...................................................................................................... 37

4.1.2 Ready signal mode.................................................................................................. 37

4.1.3 BS signal mode ....................................................................................................... 38

Page 5

4.1.4 Endian.................................................................................................................... 38

4.2 ACCESS MODE................................................................................................................. 39

4.2.1 SRAM interface ...................................................................................................... 39

4.2.2 FIFO interface (fixed transfer destination address) .................................................39

4.3 DMA TRANSFER............................................................................................................... 40

4.3.1 Data transfer unit ...................................................................................................40

4.3.2 Address mode ......................................................................................................... 40

4.3.3 Bus mode................................................................................................................ 41

4.3.4 DMA transfer request............................................................................................. 41

4.3.5 Ending DMA transfer ............................................................................................. 41

4.4 TRANSFER OF LOCAL DISPLAY LIST ..................................................................................... 42

4.5 INTERRUPT ...................................................................................................................... 43

4.6 SH3 MODE...................................................................................................................... 43

4.7 WAIT .............................................................................................................................. 43

4.8 MEMORY MAP.................................................................................................................. 44

5 GRAPHICS MEMORY........................................................................................................... 46

5.1 CONFIGURATION............................................................................................................... 46

5.1.1 Data type................................................................................................................ 46

5.1.2 Memory Mapping ....................................................................................................47

5.1.3 Data Format........................................................................................................... 47

5.2 FRAME MANAGEMENT ....................................................................................................... 49

5.2.1 Single Buffer .......................................................................................................... 49

5.2.2 Double Buffer ......................................................................................................... 49

5.3 MEMORY ACCESS............................................................................................................. 49

5.3.1 Memory Access by host CPU................................................................................... 49

5.3.2 Priority of memory accessing .................................................................................. 49

5.4 CONNECTION WITH MEMORY............................................................................................... 50

5.4.1 Connection with memory........................................................................................ 50

6 DISPLAY CONTROLLER ......................................................................................................52

6.1 OVERVIEW ....................................................................................................................... 52

6.2 DISPLAY FUNCTION........................................................................................................... 52

6.2.1 Layer configuration ................................................................................................ 52

6.2.2 Overlay................................................................................................................... 54

6.2.3 Display parameters ................................................................................................ 56

6.2.4 Display position control.......................................................................................... 57

6.3 DISPLAY COLOR ............................................................................................................... 59

6.4 CURSOR.......................................................................................................................... 60

6.4.1 Cursor dis play function...........................................................................................60

6.4.2 Cursor control......................................................................................................... 60

Page 6

6.5 DISPLAY SCAN CONTROL ................................................................................................... 61

6.5.1 Applicable display ...................................................................................................61

6.5.2 Interlace display..................................................................................................... 62

6.6 THE EXTERNAL SYNCHRON OUS SIGNAL.................................................................................63

6.7 VIDEO INTERFACE , NTSC/PAL OUTPUT...............................................................................66

7 GEOMETRY ENGINE ........................................................................................................... 67

7.1 GEOMETRY PIPELINE......................................................................................................... 67

7.1.1 Processing flow .......................................................................................................67

7.1.2 Model-view-projection (MVP) transformation (OC→CC coordinate transformation) 68

7.1.3 3D-2D transformation (CC→NDC coordinate transformation) ................................ 68

7.1.4 View port transformation (NDC→DC coordinate transformation) ........................... 69

7.1.5 View volume clipping ..............................................................................................69

7.1.6 Back face curling .................................................................................................... 71

7.2 DATA FORMAT .................................................................................................................. 72

7.2.1 Data format ............................................................................................................72

7.3 SETUP E NGINE.................................................................................................................73

7.3.1 Setup processing..................................................................................................... 73

7.4 LOG OUTPUT OF DEVICE COORDINATES ............................................................................... 73

7.4.1 Log output mode..................................................................................................... 73

7.4.2 Log output destination address............................................................................... 73

8 DRAWING PROCESSING..................................................................................................... 74

8.1 COORDINATE SYSTEM ....................................................................................................... 74

8.1.1 Drawing coordinates ...............................................................................................74

8.1.2 Texture coordinates ................................................................................................ 75

8.1.3 Frame buffer .......................................................................................................... 76

8.2 FIGURE DRAWING ............................................................................................................. 77

8.2.1 Drawing primitives................................................................................................. 77

8.2.2 Polygon drawing function ....................................................................................... 77

8.2.3 Drawing parameters ...............................................................................................78

8.2.4 Anti-aliasing function ............................................................................................. 79

8.3 BIT MAP PROCESSING....................................................................................................... 80

8.3.1 BLT ........................................................................................................................ 80

8.3.2 Pattern data format................................................................................................ 80

8.4 TEXTURE MAPPING ........................................................................................................... 81

8.4.1 Texture size ............................................................................................................ 81

8.4.2 Texture color........................................................................................................... 81

8.4.3 Texture lapping ...................................................................................................... 82

8.4.4 Filtering ................................................................................................................. 83

8.4.5 Perspective correction............................................................................................. 83

Page 7

8.4.6 Texture blending .....................................................................................................84

8.4.7 Bi-linear high -speed mode ......................................................................................84

8.5 RENDERING ..................................................................................................................... 86

8.5.1 Tiling...................................................................................................................... 86

8.5.2 Alpha blending ....................................................................................................... 86

8.5.3 Logic operation....................................................................................................... 87

8.5.4 Hidden plane management..................................................................................... 87

8.6 DRAWING ATTRIBUTES ....................................................................................................... 88

8.6.1 Line drawing attributes ..........................................................................................88

8.6.2 Triangle drawing attributes .................................................................................... 88

8.6.3 Texture attributes................................................................................................... 89

8.6.4 BLT attributes ........................................................................................................90

8.6.5 Character pattern drawing attributes .....................................................................90

8.7 BOLD LINE....................................................................................................................... 91

8.7.1 Starting and ending points ..................................................................................... 91

8.7.2 Broken line pattern ................................................................................................ 92

8.7.3 Edging.................................................................................................................... 93

8.7.4 Interpolation of bold line joint .................................................................................94

9 DISPLAY LIST ......................................................................................................................95

9.1 OVERVIEW ....................................................................................................................... 95

9.1.1 Header format ........................................................................................................ 96

9.1.2 Parameter format................................................................................................... 96

9.2 GEOMETRY COMMANDS ..................................................................................................... 97

9.2.1 Geometry command list.......................................................................................... 97

9.2.2 Explanation of geometry commands......................................................................100

9.3 RENDERING COMMAND.................................................................................................... 110

9.3.1 Command list ....................................................................................................... 110

9.3.2 Details of rendering commands ............................................................................. 115

10 REGISTER .........................................................................................................................125

10.1 REGISTER LIST...............................................................................................................125

10.1.1 Host interface register list ....................................................................................125

10.1.2 Graphics memory interface register list................................................................127

10.1.3 Display controller register list ..............................................................................128

10.1.4 Drawing engine register list..................................................................................133

10.1.5 Geometry engine register list................................................................................139

10.2 EXPLANATION OF REGISTER .............................................................................................140

10.2.1 Host interface registers.........................................................................................141

10.2.2 Graphics memory interface registers ....................................................................148

10.2.3 Display control register.........................................................................................151

Page 8

10.2.4 Drawing control registers .....................................................................................199

10.2.5 Drawing mode registers ........................................................................................202

10.2.6 Triangle drawing registers....................................................................................220

10.2.7 Line drawing registers ..........................................................................................223

10.2.8 Pixel drawing registers.........................................................................................224

10.2.9 Rectangle drawing registers..................................................................................224

10.2.10 Blt registers ......................................................................................................225

10.2.11 High-speed 2D line drawing registers................................................................226

10.2.12 High-speed 2D triangle drawing registers..........................................................227

10.2.13 Geometry control register ..................................................................................228

10.2.14 Geometry mode registers ...................................................................................230

10.2.15 Display list FIFO registers ................................................................................237

11 TIMING DIAGRAM..............................................................................................................238

11.1 HOST I NTERFACE....................................................................................................238

11.1.1 CPU read/write timing diagram in SH3 mode (Normally Not Ready Mode)...........238

11.1.2 CPU read/write timing diagram in SH3 mode (Normally Ready Mode) .................239

11.1.3 CPU read/write timing diagram in SH4 mode (Normally Not Ready Mode)...........240

11.1.4 CPU read/write timing diagram in SH4 mode (Normally Ready Mode) .................241

11.1.5 CPU read/write timing diagram in V832 mode (Normally Not Ready Mode) .........242

11.1.6 CPU read/write timing diagram in V832 mode (Normally Ready Mode)................243

11.1.7 CPU read/write timing diagram in SPARClite (Normally Not Ready Mode)..........244

11.1.8 CPU read/write timing diagram in SPARClite (Normally Ready Mode) .................245

11.1.9 SH4 single -address DMA write (transfer of 1 long word).......................................246

11.1.10 SH4 single -address DMA write (transfer of 8 long words)..................................247

11.1.11 SH3/4 dual -address DMA (transfer of 1 long word)............................................248

11.1.12 SH3/4 dual -address DMA (transfer of 8 long words)...........................................248

11.1.13 V832 DMA transfer ...........................................................................................249

11.1.14 SH4 single -address DMA transfer end timing....................................................250

11.1.15 SH3/4 dual -address DMA transfer end timing ...................................................250

11.1.16 V832 DMA transfer end timing ..........................................................................251

11.1.17 SH4 dual DMA write without ACK ....................................................................252

11.1.18 Dual-address DMA (without ACK) end timing...................................................253

11.2 GRAPHICS M EMORY INTERFACE ........................................................................................ 254

11.2.1 Timing of read access to same row address ...........................................................254

11.2.2 Timing of read access to different row addresses ...................................................255

11.2.3 Timing of write access to same row address ..........................................................256

11.2.4 Timing of write access to different row addr esses..................................................257

11.2.5 Timing of read/write access to same row address ..................................................258

11.2.6 Delay between ACTV commands...........................................................................259

Page 9

11.2.7 Delay between Refresh command and next ACTV command.................................259

11.3 DISPLAY TIMING..............................................................................................................260

11.3.1 Non-interlace mode ...............................................................................................260

11.3.2 Interlace video mode.............................................................................................261

11.3.3 Composite synchronous signal ..............................................................................262

11.4 CPU CAUTIONS .............................................................................................................262

11.5 SH3 MODE....................................................................................................................263

11.6 SH4 MODE....................................................................................................................263

11.7 V832 MODE ..................................................................................................................264

11.8 SPARCLITE...................................................................................................................264

11.9 SUPPORTED DMA TRANSFER MODES................................................................................264

12 ELECTRICAL CHARACTERISTICS ....................................................................................265

12.1 INTRODUCTION...............................................................................................................265

12.2 MAXIMUM RATING ...........................................................................................................265

12.3 RECOMMENDED OPERATING CONDITIONS ...........................................................................266

12.3.1 Recommended operating conditions ......................................................................266

12.3.2 Note at po wer-on ..................................................................................................266

12.4 DC CHARACTERISTICS ....................................................................................................268

12.4.1 DC Characteristics ...............................................................................................268

12.4.2 V-I characteristics diagram...................................................................................269

12.5 AC CHARACTERISTICS ....................................................................................................270

12.5.1 Host interface.......................................................................................................270

12.5.2 Video interface ......................................................................................................271

12.5.3 Graphics memory interface ...................................................................................272

12.5.4 PLL specifications .................................................................................................276

12.6 AC CHARACTERISTICS M EASURING CONDITIONS ................................................................. 277

12.7 TIMING DIAGRAM............................................................................................................278

12.7.1 Host interface.......................................................................................................278

12.7.2 Video interface ......................................................................................................282

12.7.3 Graphics memory interface ...................................................................................283

Page 10

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1 GENERAL

1.1

Coral graphics controller has some functions and optional efficiency and is planned to be

serial-manufactured according to purposes .

For ES version, the specifications in which common descriptions to CORAL series are written are planned

to provide and for mass-production version, the specifications which are unique to each series are planed

to be provided. Therefore, please bear in mind that the contents for ES and mass-production versions

may be different form each other.

Preface

MB86293 CORAL_LQ

Graphics Controller 10

Specifications Rev. 1.1

Page 11

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1.2 Features

• Geometry engine

Geometry engine supports the geometry processing that is compatible with ORCHID (MB86292).

Using the display list created by ORCHID enables drawing. **(But Floating point setup command is

deleted.)

Heavy processing of geometric operations such as coordinates conversions or clipping performed by

this device can reduce the CPU loads dramatically.

• 2D and 3D Drawing

Coral has a drawing function that is compatible with the CREMSON (MB86290A). It can draw data

using the display list created for CREMSON. **(But Internal texture RAM is deleted.)

Coral also supports 3D rendering, such as texture mapping with perspective collection and Gouraud

shading, alpha blending, and anti-aliasing for drawing smooth lines.

• Display controller

Coral has a display controller that is compatible with ORCHID.

In addition to the traditional XGA (1024 × 768 pixels) display, 4-layer overlay, left/right split display,

wrap-around scrolling, double buffers, and translucent display, function of 6-layer overlay, 4-siding for

palette are expanded.

• Host CPU interface

Can be connected to SH3 and SH4 manufactured by Hitachi, to V832 microprocessor by NEC and to

SPARClite (MB86833) by Fujitsu without external circuits.

• External memory interface

SDRAM and FCRAM can be connected.

• Optional function

Final device can be selected either geometry high-/low-speed version.

• Others

CMOS technology with 0. 18-µm

HQFP256 Package (lead pitch 0. 4 mm)

Supply voltage: 1.8 V (internal operation) /3.3 V (I/O)

Current consumption ( TYPICAL )

1.8 V power supply : 500mA

3.3V power supply : 100mA

MB86293 CORAL_LQ

Graphics Controller 11

Specifications Rev. 1.1

Page 12

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

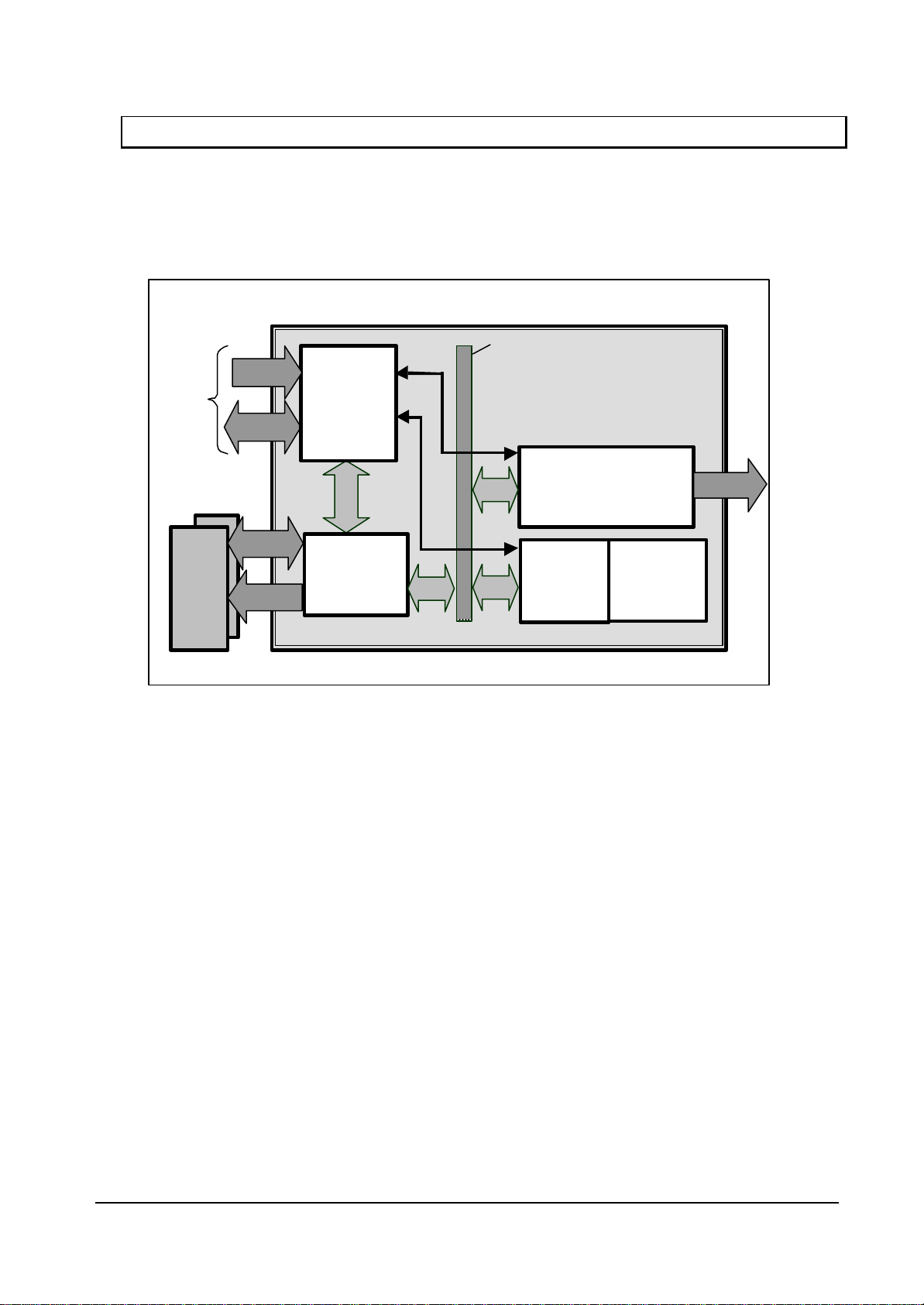

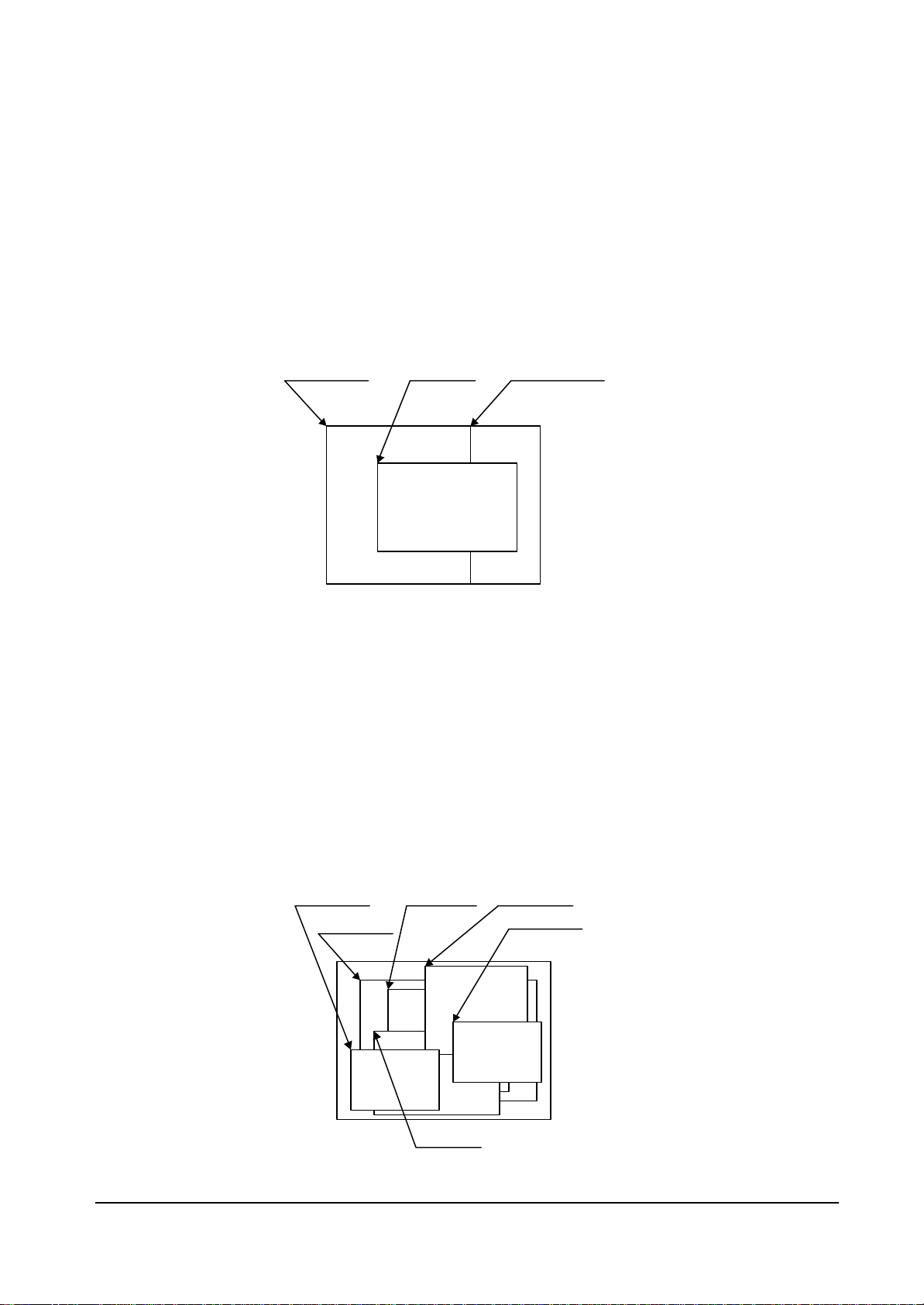

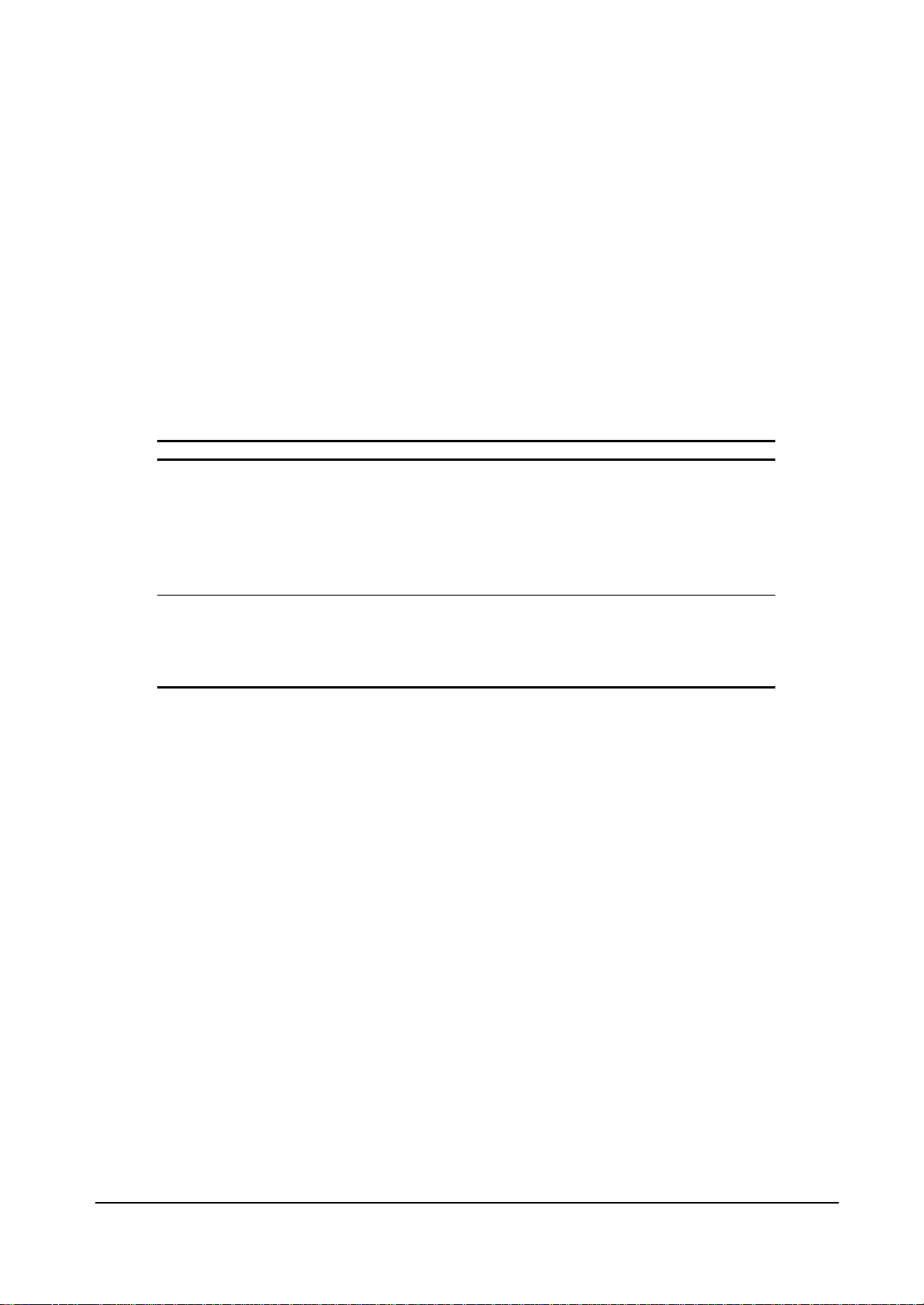

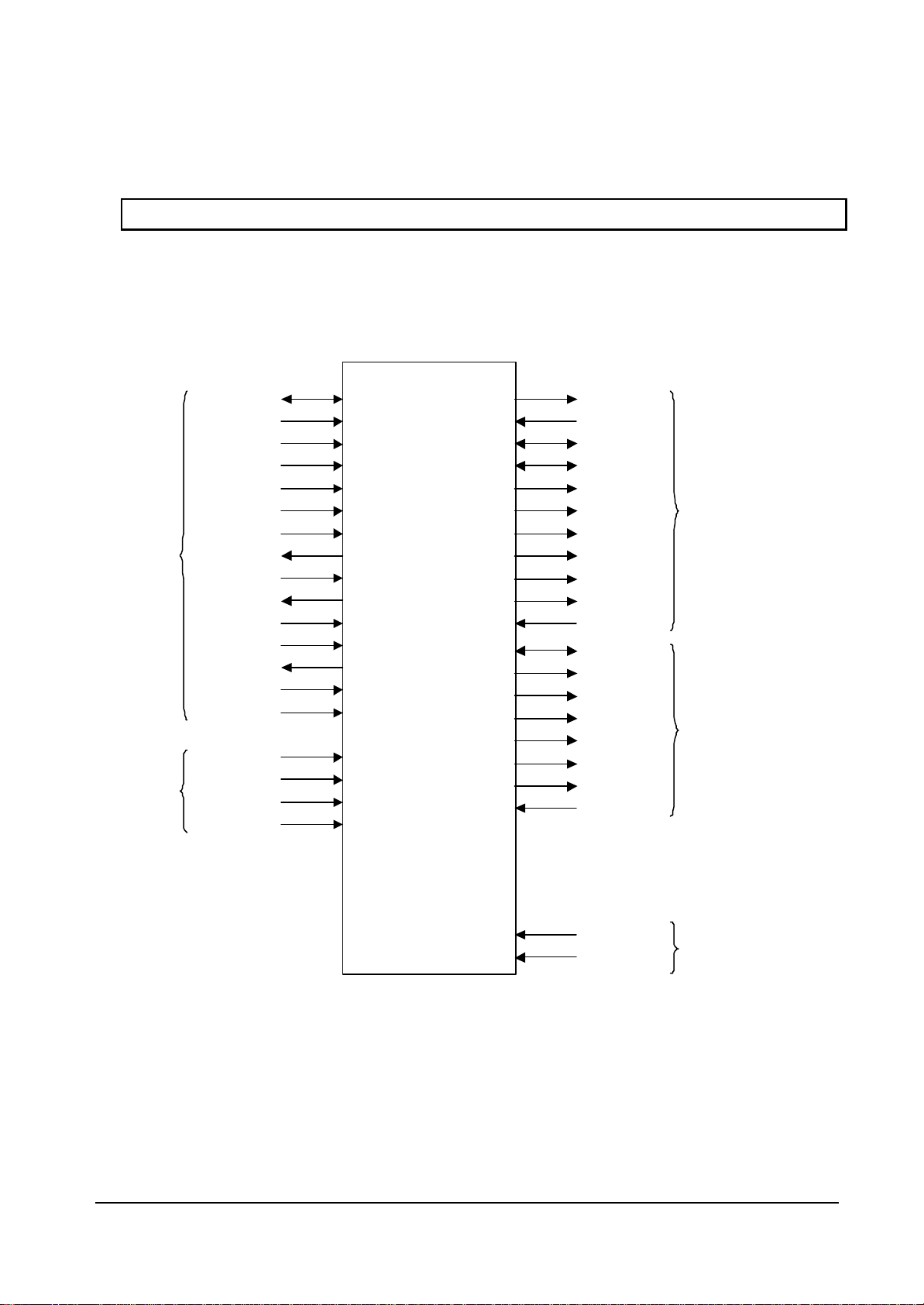

1.3 Block Diagram

CORAL general block diagram is shown below:

Please note that the capture controller is deleted from this figure in Coral-LQ.

External

Bus of

Host CPU

A2-25

Host

Interface

D0 -31

Pixel Bus

Display Controller

D RGB

or

MD0-31/63

MA0-14

External

Memory

Controller

Geometry

Engine

2D/3D

Rendering

Engine

SDRAM

FCRAM

Fig.1.1 CORAL Block Diagram

MB86293 CORAL_LQ

Graphics Controller 12

Specifications Rev. 1.1

Page 13

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1.4 Functional Overview

1.4.1 Host CPU interface

Supported CPU

Coral can be connected to SH3 and SH4 manufactured by HITACHI, V832 by NEC, SPARClite

(MB86833) by Fujitsu.

External Bus Clock

Can be connected at max. 100 MHz (when using SH4 interface)

Ready Mode

Supports normal ready/not ready.

Endian

Supports little endian.

Access Mode

SRAM interface

FIFO interface (transfer destination address fixed)

DMA transfer

Supports 1-double word (32 bits) /8-double word (32 bytes) (only SH4) for transfer unit.

ACK used/unused mode can be selected as protocol (only for DAM in dual address mode)

Supports dual address/mode single address mode (only SH4).

Supports cycle steel/burst.

Supports local display list transfer.

Interrupt

Vertical (frame) synchronous detection

Field synchronous detection

External synchronous error detection

Drawing command error

Drawing command execution end

MB86293 CORAL_LQ

Graphics Controller 13

Specifications Rev. 1.1

Page 14

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

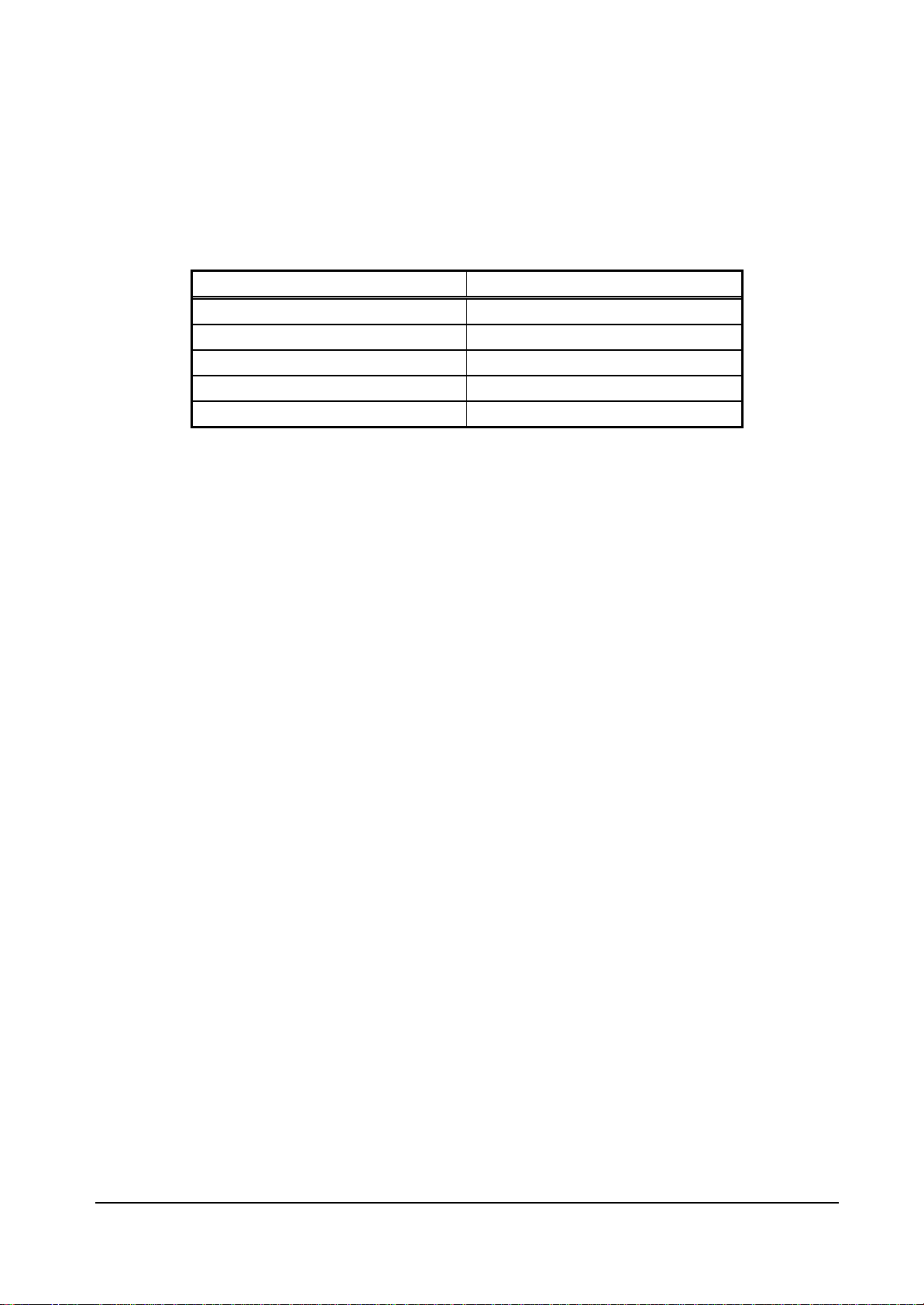

Switching internal operating frequency

Switch the operating frequency immediately after a reset (before rewriting MMR mode register of

external memory interface).

Any operating frequency can be selected from the five combinations shown in Table 2-6.

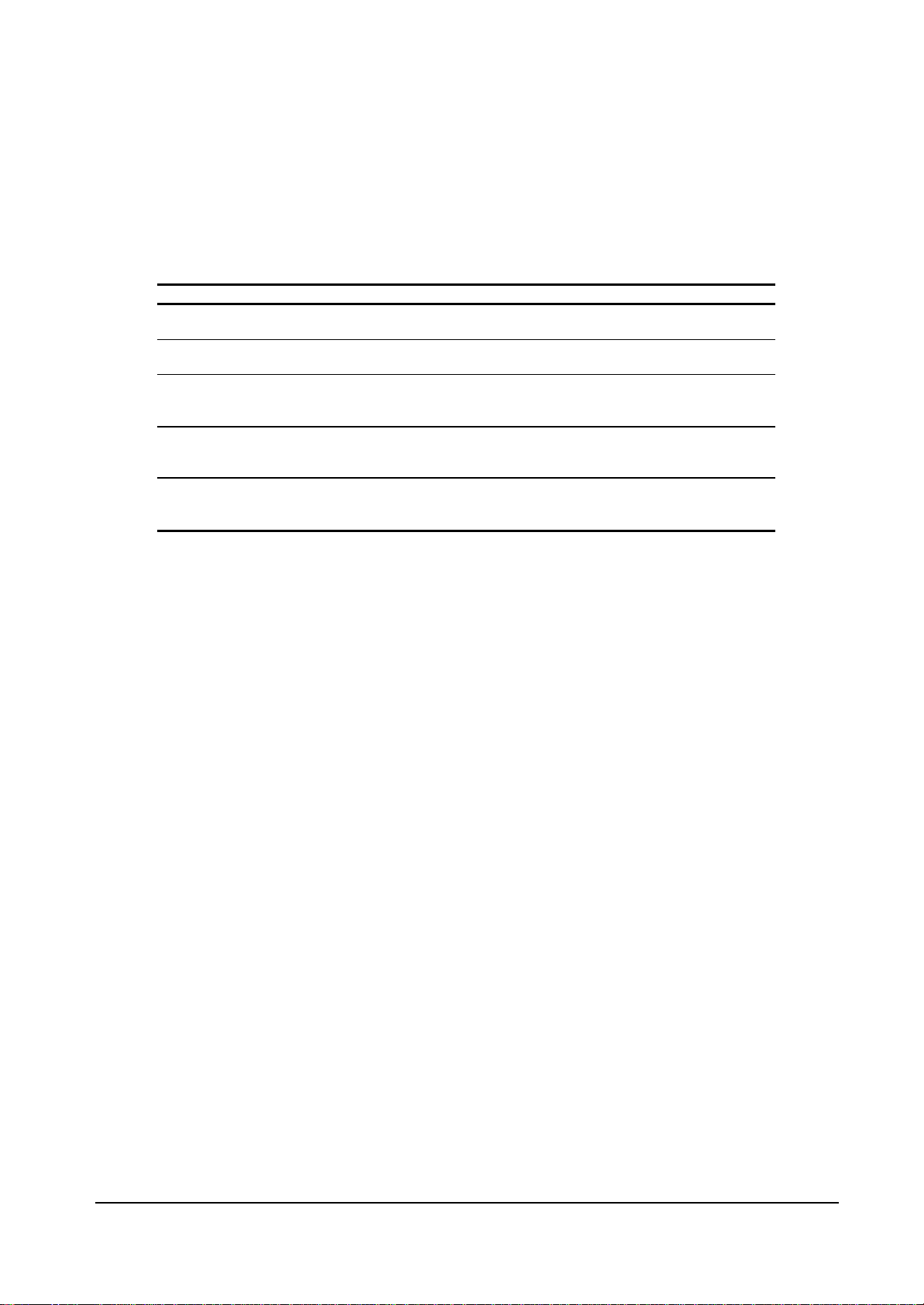

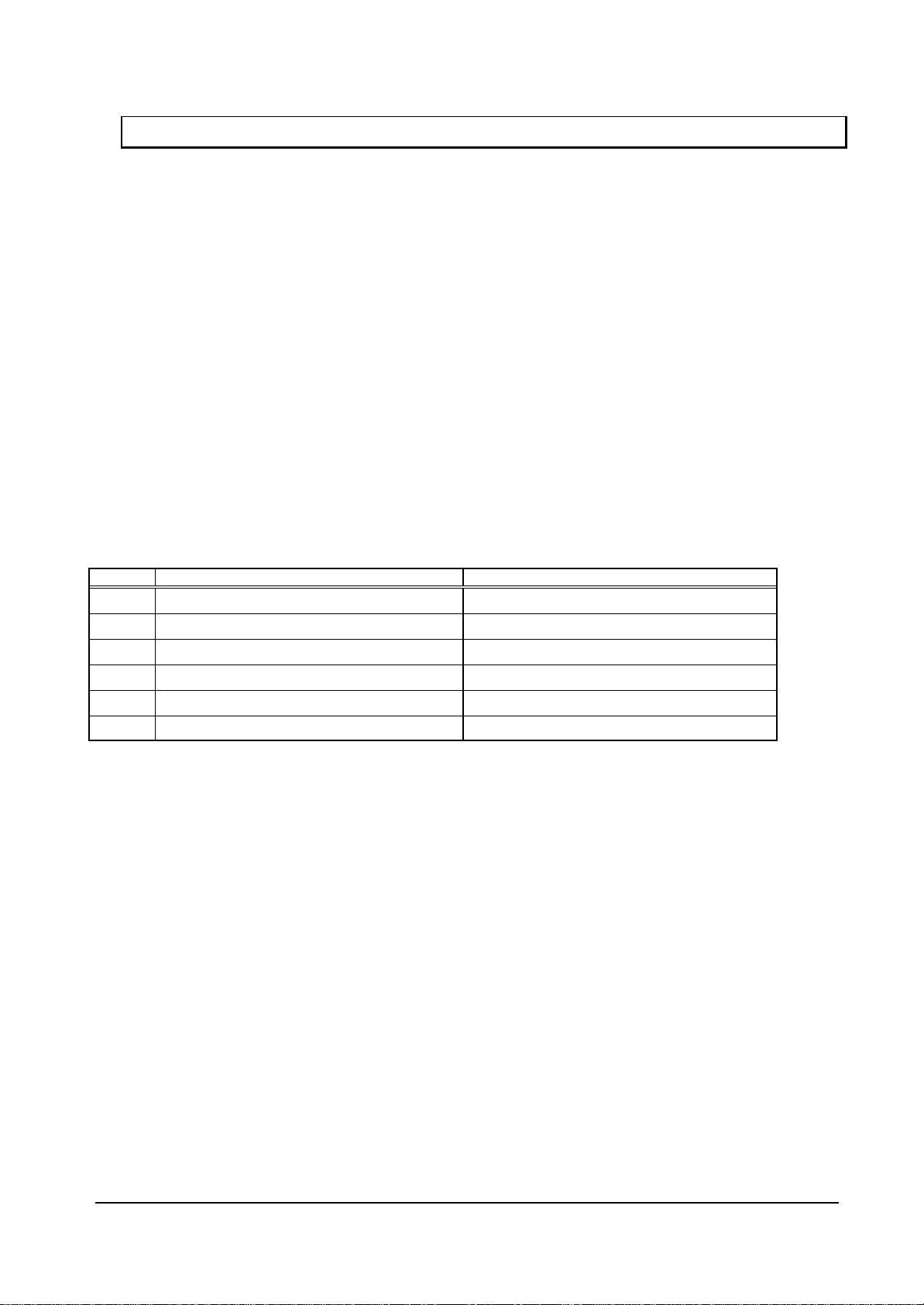

Table 1-1 Frequency Setting Combinations

Clock for geometry engine Clock for other than geometry engine

166 MHz 133 MHz

166 MHz 100 MHz

133 MHz 133 MHz

133 MHz 100 MHz

100 MHz 100 MHz

The following relationship is disabled: Clock for geometry engine < Clock for other than geometry

engine

MB86293 CORAL_LQ

Graphics Controller 14

Specifications Rev. 1.1

Page 15

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

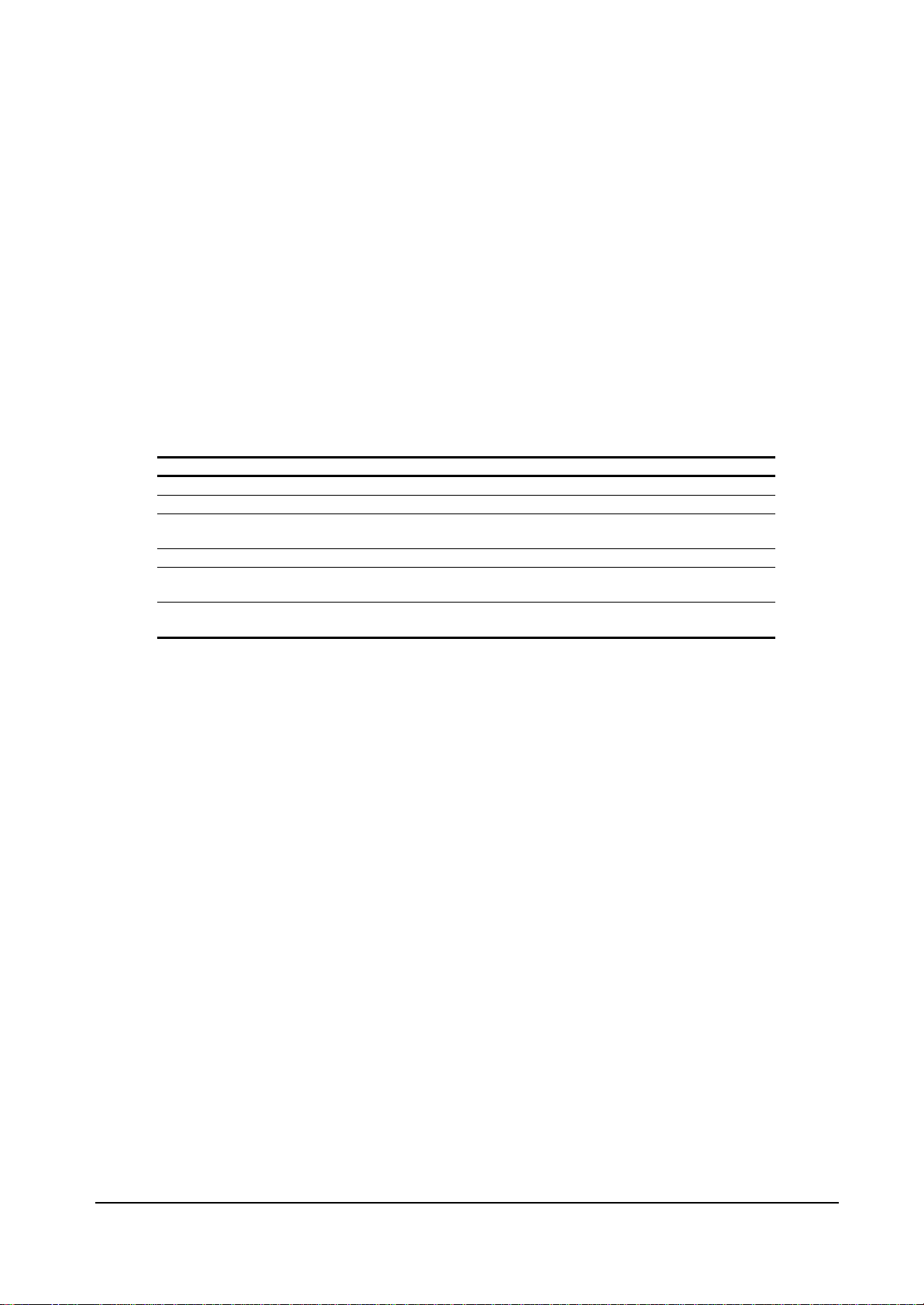

1.4.2 External memory interface

SDRAM or FCRAM can be connected.

64 bits or 32 bits can be selected for data bus.

Max. 133 MHz is available for operating frequency.

Connectable memory configuration is as shown below.

External Memory Configuration

Type Data bus width Use count Total capacity

FCRAM 16 Mbits (x 16 Bits) 32 Bits 2 4 Mbytes

FCRAM 16 Mbits (x16 Bits) 64 Bits 4 8 Mbytes

SDRAM 64 Mbits (x32 Bits) 32 Bits 1 8 Mbytes

SDRAM 64 Mbits (x32 Bits) 64 Bits 2 16 Mbytes

SDRAM 64 Mbits (x16 Bits) 32 Bits 2 16 Mbytes

SDRAM 64 Mbits (x16 Bits) 64 Bits 4 32 Mbytes

SDRAM 128 Mbits (x32 Bits) 32 Bits 1 16 Mbytes

SDRAM 128 Mbits (x32 Bits) 64 Bits 2 32 Mbytes

SDRAM 128 Mbits (x16 Bits) 32 Bits 2 32 Mbytes

SDRAM 128 Mbits (x16 Bits) 64 Bits 4 64 Mbytes

SDRAM 256 Mbits (x16 Bits) 32 Bits 2 64 Mbytes

MB86293 CORAL_LQ

Graphics Controller 15

Specifications Rev. 1.1

Page 16

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1.4.3 Display controller

Video data output

Each 6-bit digital video output is provided.

Screen resolution

LCD panels with wide range of resolutions are supported by using a programmable timing generator as

follows:

Screen Resolutions

Resolutions

1024 × 768

1024 × 600

800 × 600

854 × 480

640 × 480

480 × 234

400 × 234

320 × 234

Hardware cursor

Coral supports two hardware cursor functions. Each of these hardware cursors is specified as a 64 ×

64-pixel area. Each pixel of these hardware cursors is 8 bits and uses the same look-up table as

indirect color mode.

Double buffer method

Double buffer method in which drawing window and display window is switched in units of 1 frame

enables the smooth animation.

Flipping (switching of display window area) is performed in synchronization with the vertical blanking

period using program.

Scroll method

Independent setting of drawing and display windows and their starting position enables the smooth

scrolling.

Display colors

• Supports indirect color mode which uses the look-up table (color palette) in 8 bits/pixels.

• Entry for look -up table (color palette) corresponds to color code for 8 bits, in other words, 256. Color

data is each 6 bits of RGB. Consequently, 256 colors can be displayed out of 260,000 colors.

• Supports direct color mode which specifies RGB with 16 bits/pixels.

MB86293 CORAL_LQ

Graphics Controller 16

Specifications Rev. 1.1

Page 17

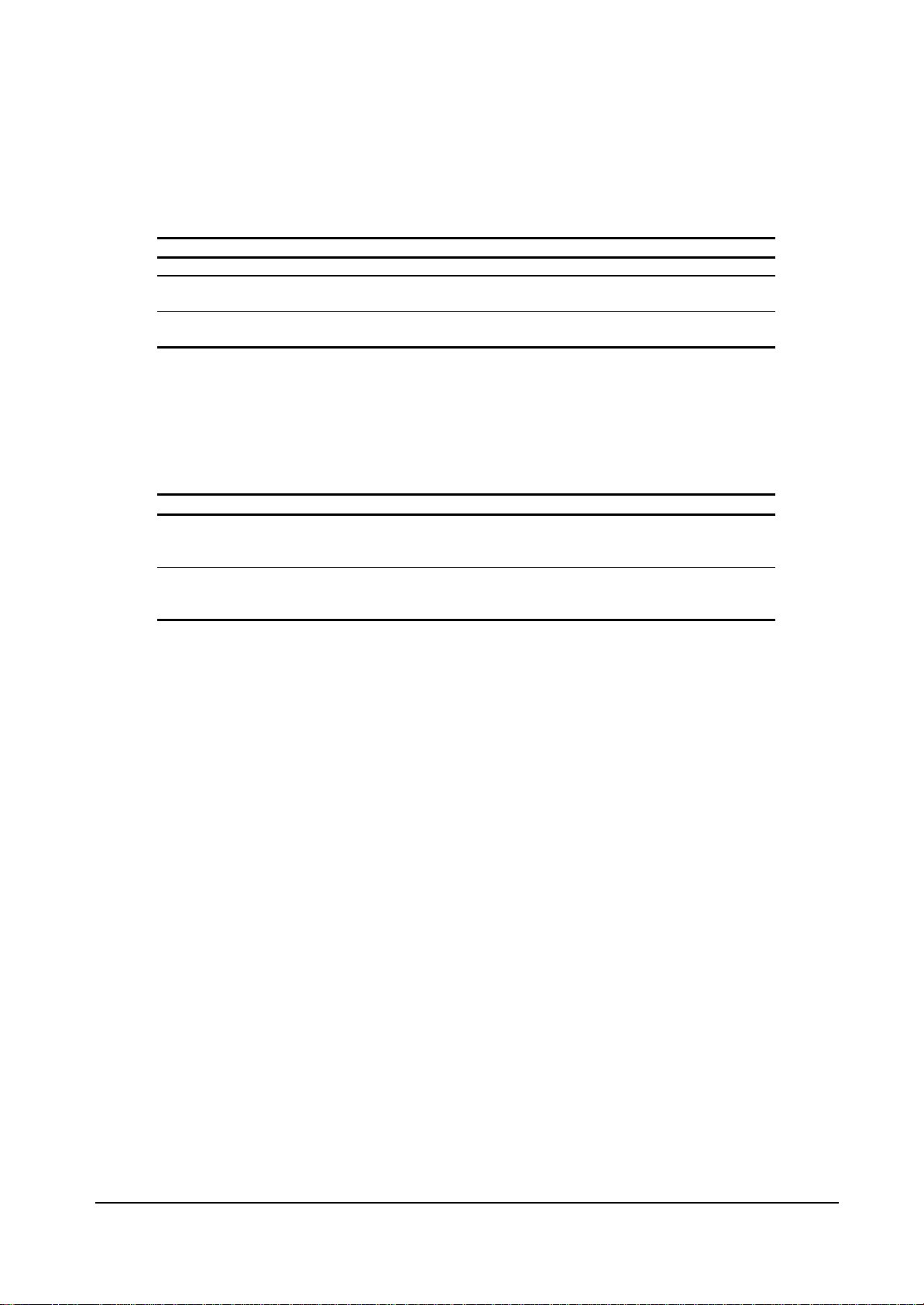

FUJITSU LIMITED

L1 (WX, WY)

PRELIMINARY and CONFIDENTIAL

Overlay

Compatibility mode

Up to four extra layers (C, W, M and B) can be displayed overlaid.

The overlay position for the hardware cursors is above/below the top layer (C).

The transparent mode or the blend mode can be selected for overlay.

The M- and B-layers can be split into separate windows.

Window display can be performed for the W-layer.

Two palettes are provided: C-layer and M-/B-layer.

The W-layer is used as the video input layer.

L0, L2, L4 (0,0)

L3, L5 (HDB+1, 0)

Window mode

• Up to six screens (L0 to 5) can be displayed overlaid.

• The overlay sequence of the L0- to L5-layers can be changed arbitrarily.

• The overlay position for the hardware cursors is above/below the L0-layer.

• The transparent mode or the blend mode can be selected for overlay.

• The L5-layer can be used as the blend coefficient plane (8 bits/pixel).

• Window display can be performed for all layers.

• Four palettes corresponded to L0 to 3 are provided.

• The L1-layer is used as the video input layer.

• Background color display is supported in window display for all layers.

L0 (L0WX, L0WY)

L5 (L5WX, L5WY)

L4 (L4WX, L4WY)

L2 (L2WX, L2WY)

L1 (L1WX, L1WY)

L3 (L3WX, L3WY)

MB86293 CORAL_LQ

Graphics Controller 17

Specifications Rev. 1.1

Page 18

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1.4.4 Geometry processing

Coral has a geometry engine for performing the numerical operations required for graphics processing.

The geometry engine uses the floating-point format for highly precise operations. It selects the required

geometry processing according to the set drawing mode and primitive type and executes processing to

the final drawing.

Primitives

Point, line, line strip, independent triangle, triangle strip, triangle fan, and arbitrary polygon are

supported.

MVP Transformation

MVP Transformation

Setting a 4 × 4 transformation matrix enables transformation of a 3D model view projection.

Two-dimensional affine transformation is also possible.

Clipping

Clipping stops drawing of figures outside the window (field of view). Polygons (including concave

shapes) can also be clipped.

Culling

Triangles on the back are not drawn.

3D-2D Transformation

This functions transforms 3D coordinates (normalization) into 2D coordinates in orthogonal or

perspective projections.

View port transformation

This function transforms normalized 2D coordinates into drawing (device) coordinates.

Primitive setup

This function automatically performs a variety of slope computations, etc., based on transforming

vertex data into coordinates and prepares for rendering (setup).

Log output of device coordinates

The view port conversion results are output to the local memory.

MB86293 CORAL_LQ

Graphics Controller 18

Specifications Rev. 1.1

Page 19

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1.4.5 2D Drawing

2D Primitives

Coral can perform 2D drawing for graphics memory (drawing plane) in direct color mode or indirect

color mode.

Bold lines with width and broken lines can be drawn. With anti-aliasing smooth diagonal lines also

can be drawn.

A triangle can be tiled in a single color or 2D pattern (tiling), or mapped with a texture pattern by

specifying coordinates of the 2D pattern at each vertex (texture mapping). At texture mapping,

drawing/non-drawing can be set in pixel units. Moreover, transparent processing can be performed

using alpha blending. When drawing in single color or tiling without Gouraud shading or texture

mapping, high-speed 2DLine and high -speed 2DTriangle can be used. Only vertex coordinates are

set for these primitives. High-speed 2DTriangle is also used to draw polygons.

2D Primitives

Primitive type Description

Point Plots point

Line Draws line

Bold line strip

(provisional name)

Triangle Draws triangle

High-speed 2DLine Draws lines

Arbitrary polygon Draws arbitrary closed polygon containing concave shapes

Draws continuous bold line

This primitive is used when interpolating the bold line joint.

Compared to line, this reduces the host CPU processing load.

consisting of vertices

Arbitrary polygon drawing

Using this function, arbitrary closed polygon containing concave shapes consisting of vertices can be

drawn. (There is no restriction on the count of vertices, however, the polygon with its sides crossed

are not supported.) In this case, as a work area for drawing, polygon drawing flag buffer is used on

the graphics memory. In drawing polygon, draw triangle for polygon drawing flag buffer using

high-speed 2DTriangle. Decide any vertex as a starting point to draw triangle along the periphery. It

enables you to draw final polygon form in single color or with tiling/texture mapping in a drawing frame.

MB86293 CORAL_LQ

Graphics Controller 19

Specifications Rev. 1.1

Page 20

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

BLT/Rectangle drawing

This function draws a rectangle using logic operations. It is used to draw pattern and copy the image

pattern within the drawing frame. It is also used for clearing drawing frame and Z buffer.

BLT Attributes

Attribute Description

Raster operation Selects two source logical operation mode

Transparent processing Performs BLT without drawing pixel consistent with the

transparent color.

Alpha blending The alpha map and source in the memory is subjected to alpha

blending and then copied to the destination.

Pattern (Text) drawing

This function draws a binary pattern (text) in a specified color.

Pattern (Text) Drawing Attributes

Attribute Description

Enlarge Vertically 2 × 2

Horizontally × 2

Vertically and Horizontally × 2

Shrink Vertically 1/2 × 1/2

Horizontally 1/2

Vertically and Horizontally 1/2

Drawing clipping

This function sets a rectangle frame in drawing frame to prohibit the drawing of the outside the frame.

MB86293 CORAL_LQ

Graphics Controller 20

Specifications Rev. 1.1

Page 21

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1.4.6 3D Drawing

3D Primitives

This function draws 3D objects in drawing memory in the direct color mode.

3D Primitives

Primitive Description

Point Plots 3D point

Line Draws 3D line

Triangle Draws 3D triangle

Arbitrary polygon Draws arbitrary closed polygon containing concave shapes

consisting of vertexes

3D Drawing attributes

Texture mapping with bi-linear filtering/automatic perspective correction and Gouraud shading provides

high-quality realistic 3D drawing. A built-in texture mapping unit performs fast pixel calculations.

This unit also delivers color blending between the shading color and texture color.

Hidden plane management

Coral supports the Z buffer for hidden plane management.

MB86293 CORAL_LQ

Graphics Controller 21

Specifications Rev. 1.1

Page 22

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1.4.7 Special effects

Anti-aliasing

Anti-aliasing manipulates line borders of polygons in sub-pixel units and blend the pre -drawing pixel

color with color to make the jaggies be seen smooth. It is used as a functional option for 2D drawing

(in direct color mode only).

Bold line and broken line drawing

This function draws lines of a specific width and a broken line.

Line Drawing Attributes

Attribute Description

Line width Selectable from 1 to 32 pixels

Broken line Set by 32 bit or 24 bit of broken line pattern

• Supports the verticality of starting and ending points.

• Supports the verticality of broken line pattern.

• Interpolation of bold line joint supports the following modes:

(1) Broken line pattern reference address fix mode

→ The same broken line pattern is kept referencing for the period of some pixels starting from the

joint and the starting point for the next line.

(2) No interpolation

• Supports the equalization of the width of bold lines.

• Supports the bold line edging.

• Not support the Anti-aliasing of dashed line patterns.

• For a part overlaid due to connection of bold lines, natural overlay can be represented by providing depth

information. (Z value).

Shading

Supports the shading primitive.

Drawing is performed to the body primitive coordinates (X, Y) with an offset as a shade. At this drawing,

the Z buffer is used in order to differentiate between the body and shade.

MB86293 CORAL_LQ

Graphics Controller 22

Specifications Rev. 1.1

Page 23

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

Alpha blending

Alpha blending blends two image colors to provide a transparent effect. CORAL supports two types

of blending; blending two different colors at drawing, and blending overlay planes at display.

Transparent color is not used for these blending options.

There are two ways of specifying alpha blending for drawing:

(1) Set a transparent coefficient to the register; the transparent coefficient is applied for transparency

processing of one plane.

(2) Set a transparent coefficient for each vertex of the plane; as with Gouraud shading, the transparent

coefficient is linear-interpolated to perform transparent processing in pixel units.

In addition to the above, the following settings can be performed at texture mapping. When the most

significant bit of each texture cell is 1, drawing or transparency can be set. When the most significant

bit of each texture cell is 0, non-drawing can be set.

Alpha Blending

Type Description

Drawing Transparent ratio set in particular register

While one primitive (polygon, pattern, etc.), being drawn,

registered transparent ratio applied

A transparent coefficient set for each vertex. A

linear-interpolated transparent coefficient applied.

This is possible only in direct color mode.

Overlay display Blends top layer pixel color with lower layer pixel color

Transparent coefficient set in particular register

Registered transparent coefficient applied during one frame

scan

Gouraud Shading

Gouraud shading can be used in the direct color mode to provide 3D object real shading and color

gradation.

Gray Scale Gouraud Shading

Gray scale gouraud shading can be used in the in-direct color(8bit/pixel) mode to draw a blend

coefficient layer.

MB86293 CORAL_LQ

Graphics Controller 23

Specifications Rev. 1.1

Page 24

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

Texture mapping

Coral supports texture mapping to map an image pattern onto the surface of plane. The texture

pattern can be laid out in the graphics memory. In this case, max. 4096 × 4096 pixels can be used.

For drawing 8-bit color, only point sampling can be specified for texture interpolation; only de -curl can

be specified for the blend mode.

Texture Mapping

Function Description

Filtering Point sample

Bi-linear filter

Coordinate s correction Linear

Perspective

Blend De-curl

Modulate

Stencil

Alpha blend Normal

Stencil

Stencil alpha

Wrap Repeat

Cramp

Border

MB86293 CORAL_LQ

Graphics Controller 24

Specifications Rev. 1.1

Page 25

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

1.4.8 Others

Drawing color

8-bit indirect color and 16-bit direct color are supported as a drawing input data.

Top-left rule non-applicable mode

In addition to the top-left rule applicable mode in which the triangle borders are compatible with

CREMSON, the top-left rule non-applicable mode can be used. (In case of non-top-left polygon

drawing, an object has to be in a geometry clipping area.)

Caution: Use perspective correct mode when use texture at the top-left rule non-applicable mode.

Top-left rule non-applicable primitives cannot use Geometry clip function.

Non-top-left-part’s pixel quality is less than body. (using approximate calculation)

MB86293 CORAL_LQ

Graphics Controller 25

Specifications Rev. 1.1

Page 26

FUJITSU LIMITED

XCS

XRD

Clock

CKM

PRELIMINARY and CONFIDENTIAL

2 PINS

2.1 Signals

2.1.1 Signal lines

Host CPU

interface

D0-31

A2-25

BCLKI

XRST

XWE0-3

XRDY

XBS

DREQ

DRACK

DTACK

XINT

RDY_MODE

BS_MODE

CLK

CLKSEL0-1

DCLKO

DCKLI

HSYNC

VSYNC

CSYNC

DISPE

GV

R2-7

CORAL

Graphics Controller

HQFP256

S

G2-7

B2-7

XRGBEN

MD0-63

MA0-14

MRAS

MCAS

MWE

MDQM0-7

MCLKO

MCLKI

TESTH

TRST

Video output

interface

Graphics memory

interface

Test

MB86293 CORAL_LQ

Graphics Controller 26

Specifications Rev. 1.1

Fig. 2.1 CORAL Signal Lines

Page 27

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

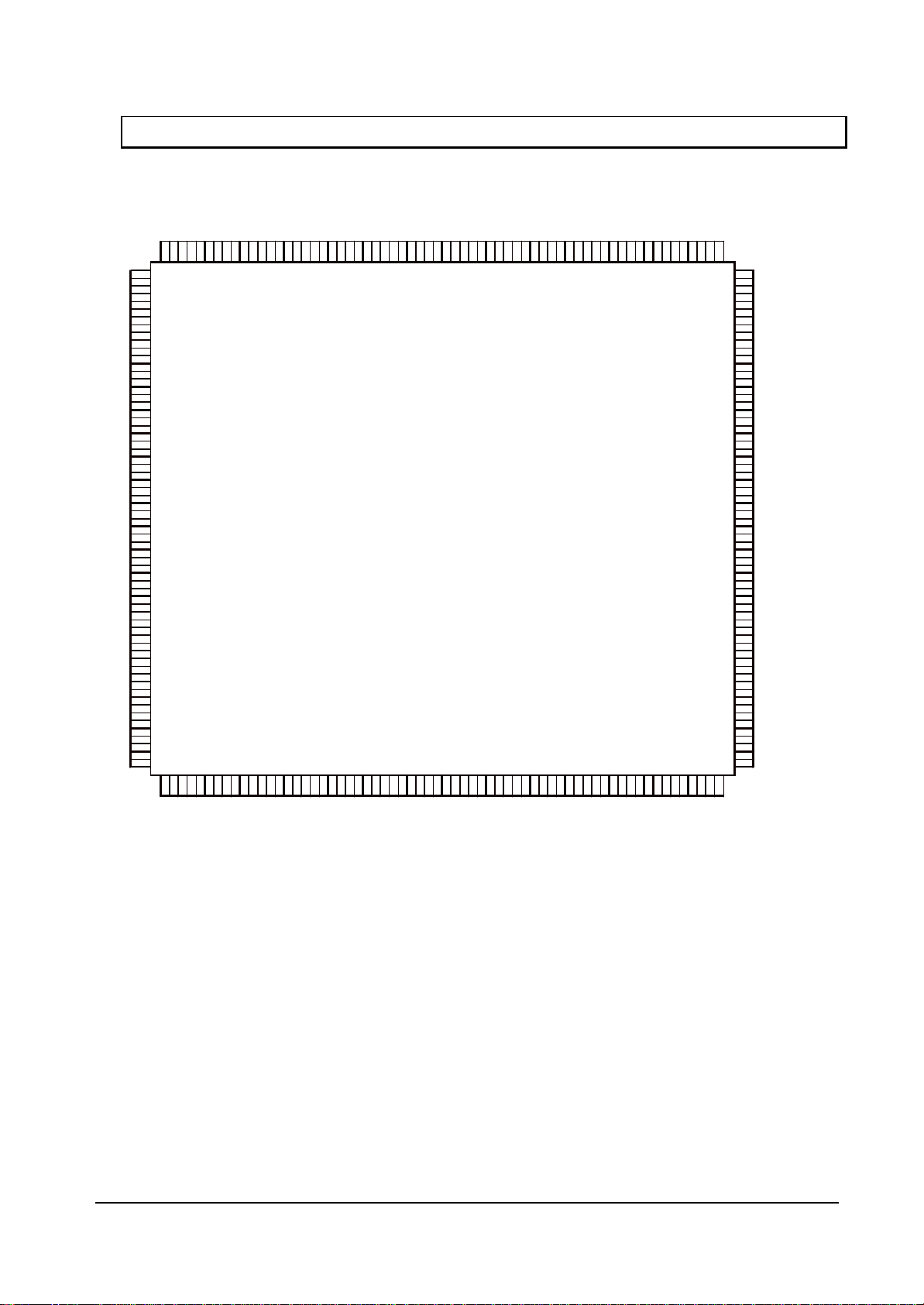

2.2 Pin Assignment

2.2.1 Pin assignment diagram

DTACK

XWE0

VDDL

XWE1

XWE2

XWE3

A25

A24

A23

A22

A21

A20

A19

A18

A17

A16

A15

VDDL

A14

A13

A12

A11

A10A9A8A7A6A5A4A3A2

256

255

254

253

252

251

250

249

248

247

246

245

244

243

242

241

240

239

238

237

236

235

234

233

232

231

DRACK 1

BS_MODE 2 191 DG7

3 190 DG6

4

XINT

DREQ 5 188 DG4

XRDY 6 187 DG3

VDDH 7

VDDL 8 185 DB7

BCLKI 9 184 VDDL

10

XCS

XRD 11 182 DB5

XBS 12 181 DB4

CKM 13 180 DB3

MODE0 14 179 DB2

MODE1 15 178 VDDH

MODE2 16 177 VSS

XRST 17 176 VSS

VSS 18 175 MD63/R1

VSS 19 174 MD62/R0

D0 20 173 MD61/G1

D1 21 172 MD60/G0

D2 22 171 MD59/B1

D3 23

VDDL 24 169 MD57

D4 25 168 VDDL

D5 26

VDDH 27 166 MD55

D6 28 165 MD54

D7 29

D8 30 163 MD52

D9 31 162 MD51

D10 32

D11 33 160 MD49

D12 34 159 MD48

D13 35

D14 36 157 TESTH

D15 37 156 MD47

D16 38 155 MD46

D17 39 154 MD45

VDDL 40 153 MD44

D18 41 152 VDDL

VDDH 42 151 MD43

D19 43 150 MD42

D20 44 149 MD41

D21 45

D22 46 147 VSS

D23 47 146 VSS

D24 48

D25 49 144 MD38

D26 50 143 MD37

D27 51

D28 52 141 MD35

D29 53 140 MD34

D30 54

D31 55 138 MD32

VDDL 56 137 XRGBEN

VDDH 57

VSS 58 135 VDDL

VSS 59 134 VSS

MD0 60 133 VSS

MD1 61 132 MCLKI

MD2 62 131 VDDH

MD3 63 130 VSS

MD4 64 129 VSS

6566676869707172737475767778798081828384858687888990919293949596979899

MD5

MD6

MD7

MD8

MD9

VDDL

MD10

MD11

MD12

MD13

MD14

MD15

VDDH

MD16

MD17

MD18

VDDL

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

230

MD28

229

MD29

228

MD30

227

MD31

226

VDDL

CLKSEL0

VDDL

225

224

VSS

VSS

CLKSEL1

VSS

223

222

VDDH

DQM0

VSS

221

100

DQM1

CLK

220

101

DQM2

PLLVDD

PLLVSSSTRST

219

218

102

103

MA0

DQM3

TESTH

TESTH

DCLKI

VSS

VSS

TESTH

VDDL

TESTH

VSYNC

HSYNC

VSS

VSS

CSYNCGVDE

DCLKO

VDDH

DR7

DR6

DR5

DR4

VDDL

DR3

217

216

215

214

213

212

211

210

209

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192 DR2

189 DG5

186 DG2

183 DB6

170 MD58/B0

167 MD56

164

161

158

148

145 MD39

142 MD36

139

136

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

VDDL

MA9

MA10

MA11

MA12

MA13

MA14

VDDH

MRAS

MCAS

MWE

DQM4

DQM5

DQM6

DQM7

VDDL

MCLKO

MD53

MD50

TESTH

MD40

MD33

TESTH

Note: The MODE2 signal used for Orchid is changed as shown below.

MODE2 signal for Orchid → RDY_MODE signal for Coral

MB86293 CORAL_LQ

Graphics Controller 27

Specifications Rev. 1.1

Page 28

FUJITSU LIMITED

64

MD4

128

MCLKO

192

DR2

256

DTACK

PRELIMINARY and CONFIDENTIAL

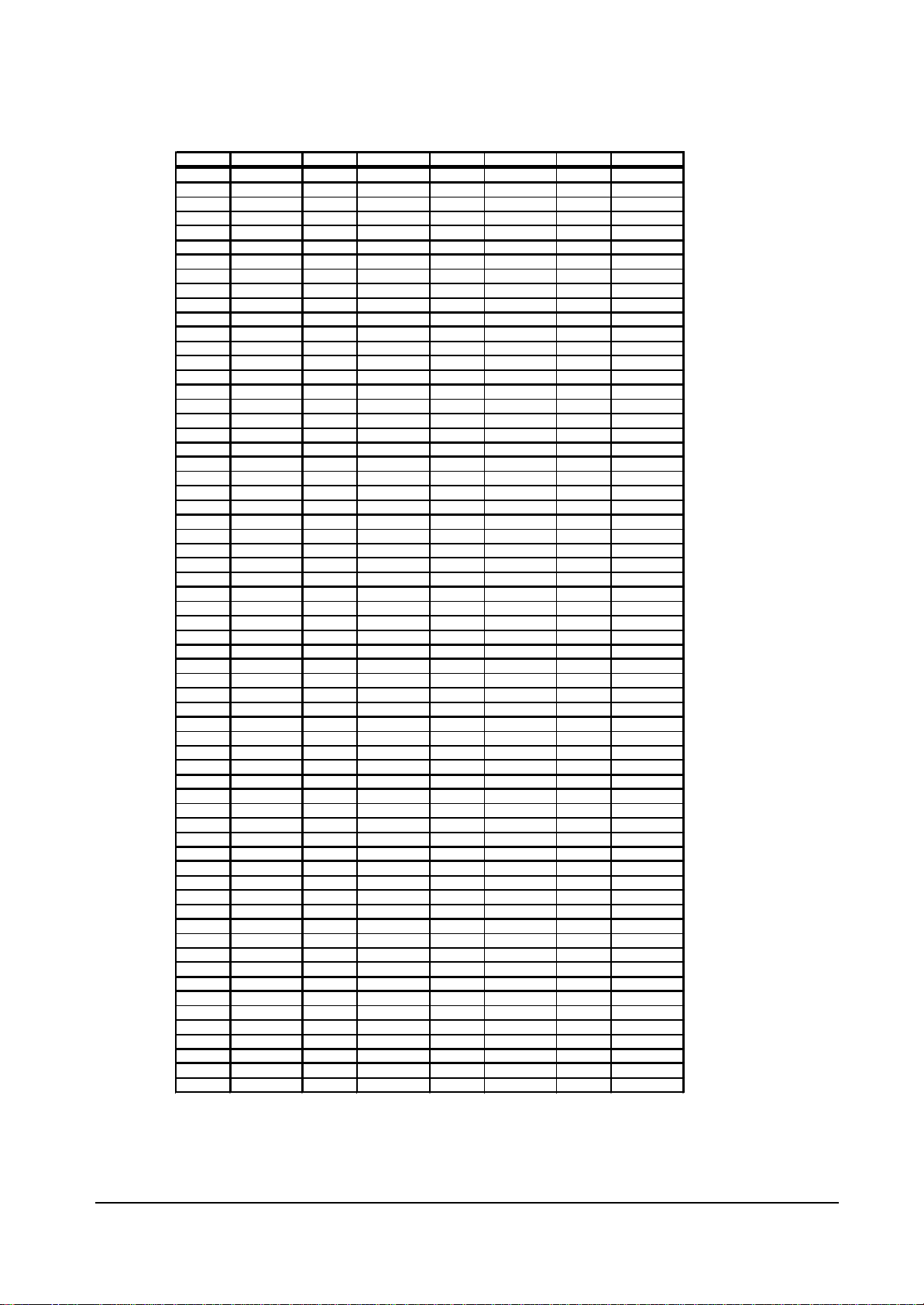

2.2.2 Pin assignment table

No. Name No. Name No. Name No. Name

1 DRACK 65 MD5 129 VSS 193 DR3

2 BS_MODE 66 VDDL 130 VSS 194 VDDL

3 RDY_MODE 67 MD6 131 VDDH 195 DR4

4 XINT 68 MD7 132 MCLKI 196 DR5

5 DREQ 69 MD8 133 VSS 197 DR6

6 XRDY 70 MD9 134 VSS 198 DR7

7 VDDH 71 MD10 135 VDDL 199 VDDH

8 VDDL 72 MD11 136 TESTH 200 DCLKO

9 BCLKI 73 MD12 137 XRGBEN 201 DE

10 XCS 74 MD13 138 MD32 202 GV

11 XRD 75 MD14 139 MD33 203 CSYNC

12 XBS 76 MD15 140 MD34 204 VSS

13 CKM 77 VDDH 141 MD35 205 VSS

14 MODE0 78 MD16 142 MD36 206 HSYNC

15 MODE1 79 MD17 143 MD37 207 VSYNC

16 MODE2 80 MD18 144 MD38 208 TESTH

17 XRST 81 VDDL 145 MD39 209 VDDL

18 VSS 82 MD19 146 VSS 210 TESTH

19 VSS 83 MD20 147 VSS 211 VSS

20 D0 84 MD21 148 MD40 212 VSS

21 D1 85 MD22 149 MD41 213 DCLKI

22 D2 86 MD23 150 MD42 214 TESTH

23 D3 87 MD24 151 MD43 215 TESTH

24 VDDL 88 MD25 152 VDDL 216 TRST

25 D4 89 MD26 153 MD44 217 S

26 D5 90 MD27 154 MD45 218 PLLVSS

27 VDDH 91 MD28 155 MD46 219 PLLVDD

28 D6 92 MD29 156 MD47 220 CLK

29 D7 93 MD30 157 TESTH 221 VSS

30 D8 94 MD31 158 TESTH 222 VSS

31 D9 95 VDDL 159 MD48 223 CLKSEL1

32 D10 96 VSS 160 MD49 224 VDDL

33 D11 97 VSS 161 MD50 225 CLKSEL0

34 D12 98 VDDH 162 MD51 226 A2

35 D13 99 DQM0 163 MD52 227 A3

36 D14 100 DQM1 164 MD53 228 A4

37 D15 101 DQM2 165 MD54 229 A5

38 D16 102 DQM3 166 MD55 230 A6

39 D17 103 MA0 167 MD56 231 A7

40 VDDL 104 MA1 168 VDDL 232 A8

41 D18 105 MA2 169 MD57 233 A9

42 VDDH 106 MA3 170 MD58/B0 234 A10

43 D19 107 MA4 171 MD59/B1 235 A11

44 D20 108 MA5 172 MD60/G0 236 A12

45 D21 109 MA6 173 MD61/G1 237 A13

46 D22 110 MA7 174 MD62/R0 238 A14

47 D23 111 VDDL 175 MD63/R1 239 VDDL

48 D24 112 MA8 176 VSS 240 A15

49 D25 113 MA9 177 VSS 241 A16

50 D26 114 MA10 178 VDDH 242 A17

51 D27 115 MA11 179 DB2 243 A18

52 D28 116 MA12 180 DB3 244 A19

53 D29 117 MA13 181 DB4 245 A20

54 D30 118 MA14 182 DB5 246 A21

55 D31 119 VDDH 183 DB6 247 A22

56 VDDL 120 MRAS 184 VDDL 248 A23

57 VDDH 121 MCAS 185 DB7 249 A24

58 VSS 122 MWE 186 DG2 250 A25

59 VSS 123 DQM4 187 DG3 251 XWE3

60 MD0 124 DQM5 188 DG4 252 XWE2

61 MD1 125 DQM6 189 DG5 253 XWE1

62 MD2 126 DQM7 190 DG6 254 VDDL

63 MD3 127 VDDL 191 DG7 255 XWE0

MB86293 CORAL_LQ

Graphics Controller 28

Specifications Rev. 1.1

Page 29

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

Notes

VSS/PLLVSS : Ground

V

: 3.3-V power supply

DDH

V

/PLLVDD : 1.8-V power supply

DDL

PLLVDD : PLL power supply

OPEN : Do not connect anything.

TESTH : Input a 3.3 V-power supply.

- It is recommended that PLLVDD should be isolated on the PCB.

- Insert a bypass capacitor with good high frequency characteristics between the power supply and

ground.

Place the capacitor as near as possible to the pin.

MB86293 CORAL_LQ

Graphics Controller 29

Specifications Rev. 1.1

Page 30

FUJITSU LIMITED

DMA transfer strobe signal (XTC is used in the V832 mode.

PRELIMINARY and CONFIDENTIAL

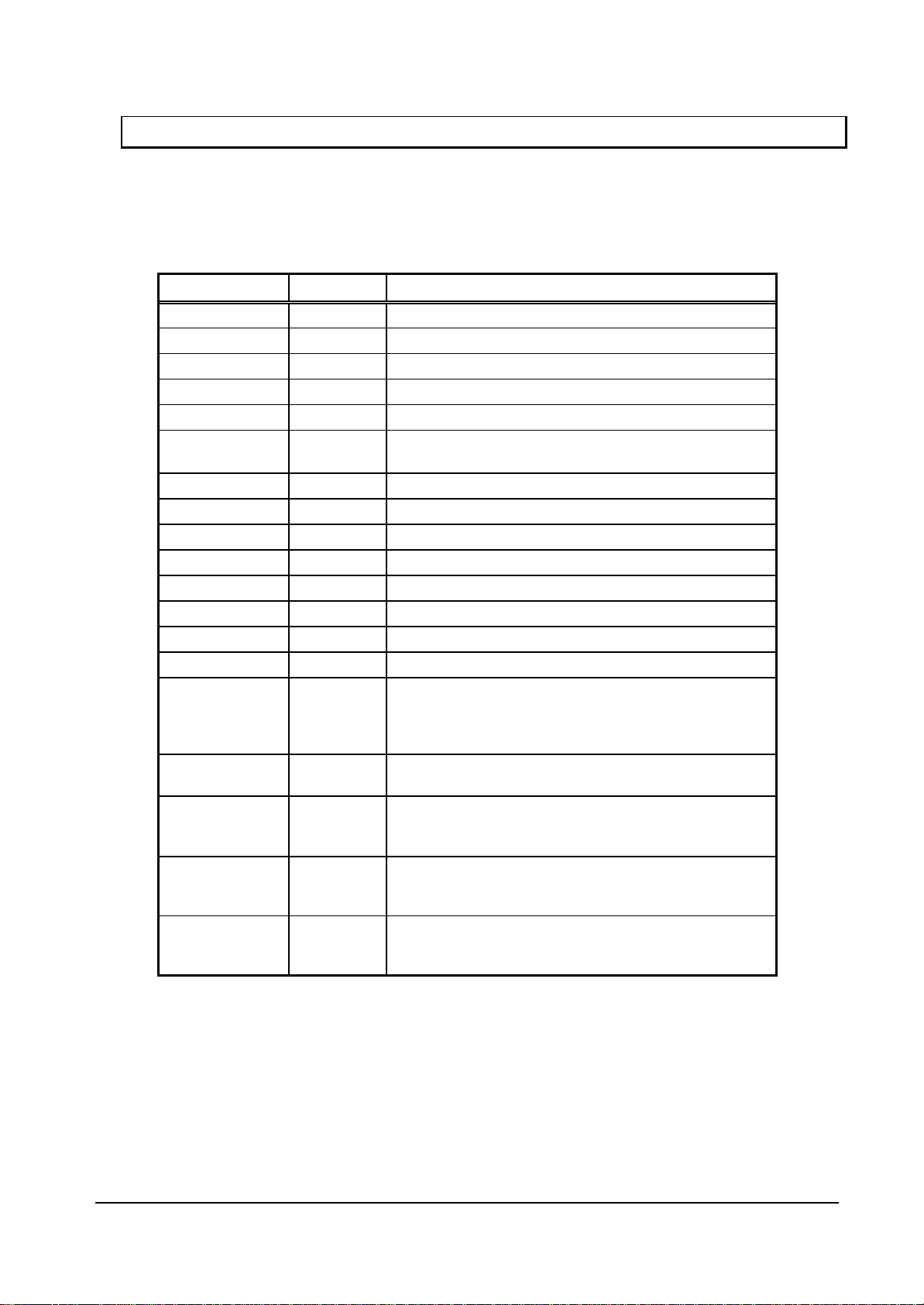

2.3 Pin Function

2.3.1 Host CPU interface

Table 2-1 Host CPU Interface Pins

Pin name I/O Description

MODE0-2 Input Host CPU mode select

RDY_MODE Input Normally ready, Not ready select

BS_MODE Input BS signal with/without select

XRST Input Hardware reset

D0-31 In/Out Host CPU bus data

A2-A25 Input Host CPU bus address (In the V832 mode, A[24] is

BCLKI Input Host CPU bus clock

XBS Input Bus cycle start signal

XCS Input Chip select signal

XRD Input Read strobe signal

XWE0 Input Write strobe for D0 to D7 signal

XWE1 Input Write strobe for D8 to D15 signal

XWE2 Input Write strobe for D16 to D23 signal

XWE3 Input Write strobe for D24 to D31 signal

XRDY Output

Tri-state

DREQ Output DMA request signal (This signal is low-active in both the SH

DRACK/DMAAK Input Acknowledge signal in response to DMA request (DMAAK is

DTACK/XTC Input

XINT Output Interrupt signal issued to host CPU (In the SH mode, and

connected to XMWR.)

Wait request signal (In the SH3 mode, when this signal is

“0”, it indicates the wait state; in the SH4, V832 and

SPARClite modes, when this signal is “1”, it indicates the

wait state.)

mode and V832 mode.)

used in the V832 mode; this signal is high-active in both the

SH mode and V832 mode.)

In the SH mode, this signal is high-active; in the V832 mode,

it is low-active.)

SPARClite this signal is low-active; in the V832 mode, it is

high-active)

MB86293 CORAL_LQ

Graphics Controller 30

Specifications Rev. 1.1

Page 31

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

• Coral can be connected to the Hitachi SH4 (SH7750), SH3 (SH7709) NEC V832 and Fujitsu SPARClite

(MB86833) without external circuit. In the SRA M interface mode, Coral can be used with any other CPU

as well. The host CPU is specified by the MODE0 to 2 pins.

MODE 2 MODE 1 MODE 0 CPU

L L

L L

L H

L H H SPARClite

H X X Reserved

L SH3

H SH4

L V832

When the bus cycle terminates, a ready signal level can be set . When using the RDY_MODE signal at

“High” level, set two cycles as the CPU software wait of the CPU. (When BS_MODE = “High” level, set

the CPU software wait to three cycles.)

RDY_MODE Ready signal mode

L When the bus cycle terminates, sets the XRDY signal to the ‘not ready’ level.

H When the bus cycle terminates, sets the XRDY signal to the ‘ready’ level.

A CPU with no BS (Bus Start) pin can be used. Setting can be performed in all CPU modes.

Connection can be made to a CPU with no BS signal by setting the BS_MODE signal to “High” level.

When not using the BS signal, fix the BS pin of CORAL at “High” level.

When using the BS_MODE signal as “High” level in the normally ready mode, set the CPU software wait

to three cycles.

BS_MODE BS signal mode

L Connect to a CPU with the BS signal

H Connect to a CPU without the BS signal

The data signal is 32 bits (fixed).

The address signal is 32 bits (per one double-word) × 24, and has a 64-Mbyte address field. (16-MByte

address space is provided for V832 and SPARClite.)

The external bus operating frequency is up to 100 MHz.

In the SH4, V832, and SPARClite modes, when the XRDY signal is low, it is in the ready state. However,

in the SH3 mode, when the XRDY signal is low, it is in the wait state. This signal is a tri -state output that

is synchronized with the rising edge of BCLKI.

DMA data transfer is supported using an external DMA controller.

An interrupt signal is generated to the host CPU.

The XRST input must be kept low for at least 300 µs after setting the S (PLL reset) signal to high.

In the V832 mode, Coral signals are connected to the V832 CPU as follows:

CORAL Pins V832 Signals

A24 XMWR

DTACK XTC

DRACK DMAAK

MB86293 CORAL_LQ

Graphics Controller 31

Specifications Rev. 1.1

Page 32

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

2.3.2 Video output interface

Pin name I/O Description

DCLKO Output Dot clock signal for display

DCLKI Input Dot clock signal input

HSYNC I/O Horizontal sync signal output

VSYNC I/O Vertical sync signal output

CSYNC Output Composite sync signal output

DISPE Output Display enable period signal

GV Output Graphics/video switch

R2-7 Output Digital picture (R) output

G2-7 Output Digital picture (G) output

B2-7 Output Digital picture (B) output

XRGBEN Input Signal to switch between RGB1 and 0 output/memory bus

Table 2-2 Video Output Interface Pins

Horizontal sync input <in external sync mode>

Vertical sync input <in external sync mode>

(MD 63 to 58)

6-bit display data is output as standard for R, G, and B. Depending on the condition, 8-bit display data

can also be output for R, G, and B. Fixing XRGBEN at 0, R0, 1, G0, 1, and B0, 1 can be output to MD62,

63, MD60, 61, and MD58, 59 respectively. When 8-bit output is selected for R, G, and B, only the 32-bit

mode can be used for the memory bus width mode.

Additional setting of external circuits can generate composite video signal.

Synchronous to external video signal display can be performed.

Either mode which is synchronous to DCLKI signal or one which is synchronous to dot clock, as for

normal display can be selected.

Since HSYNC and VSYNC signals are set to input state after reset, these signals must be pulled up LSI

externally.

The GV signal switches graphics and video at chroma key operation. When video is selected, the “Low”

level is output.

MB86293 CORAL_LQ

Graphics Controller 32

Specifications Rev. 1.1

Page 33

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

2.3.3 Graphics memory interface

Table 2-3 Graphics memory interface pins

Pin name I/O Description

MD0 to 57 I/O Graphics memory bus data

MD58 to 63/RGB I/O Graphics memory bus data or RGB0 to 1 output

MA0 to 14 Output Graphics memory bus data

MRAS Output Row address strobe

MCAS Output Column address strobe

MWE Output Write enable

MDQM0 to 7 Output Data mask

MCLK0 Output Graphics memory clock output

MCLK1 Input Graphics memory clock input

Connect the interface to the external memory used as memory for image data. The interface can be

connected to 64-/128-/256-Mbit SDRAM (16- or 32-bit length data bus) without using any external

circuit.

64 bits or 32 bits can be selected for the memory bus data. When 32 -bit memory bus data is used

and 6-bit output is used for R, G, and B (XRGBEN pin = 1), set MD32 to 63 and MDQM4 to 7 to the

open state. When 32 -bit memory bus data is used and 8-bit output is used for R, G, and B (XRGBEN

pin = 0), set MD32 to 39 to “High” level input and set MD40 to 57 and MDQM4 to 7 to the open state.

Connect MCLKI to MCLK0.

When XRGBEN is fixed at “1”, MD58 to 63 can be used as graphics memory bus data.

When XRGBEN is fixed at “0”, MD58 to 63 can be used as digital RGB0 to 1 outputs.

MB86293 CORAL_LQ

Graphics Controller 33

Specifications Rev. 1.1

Page 34

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

2.3.4 Clock input

Table 2-4 Clock Input Pins

Pin name I/O Description

CLK Input Clock input signal

S Input PLL reset signal

CKM Input Clock mode signal

CLKSEL [1:0] Input Clock rate select signal

Inputs source clock for internal operation clock and display dot clock. Normally, 4 Fsc (= 14.31818 MHz:

NTSC) is input. An internal PLL generates the internal operation clock of 166 MHz/133 MHz and the

display base clock of 400 MHz.

CKM Clock mode

L Output from internal PLL selected

H Host CPU bus clock (BCLK1) selected

• When CKM = L, selects input clock frequency when built-in PLL used according to setting of CLKSEL pins

CLKSEL1 CLKSEL0

L L Inputs 13.5-MHz

L H Inputs 14.32-MHz

H L Inputs 17.73-MHz

H H Reserved

Input clock

frequency

clock frequency

clock frequency

clock frequency

Multiplication

rate

× 29 391.5 MHz

× 28 400.96 MHz

× 22 390.06 MHz

Display

reference clock

MB86293 CORAL_LQ

Graphics Controller 34

Specifications Rev. 1.1

Page 35

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

2.3.5 Test pins

Pin name I/O Description

TESTH Input Input 3.3-V power.

TRST Input This is the test reset signal.

2.3.6 Reset sequence

See Section 10.3.2.

Table 2-5 Test Pins

Before performing reset via S/XRST, perform reset

via this signal (TRST).

MB86293 CORAL_LQ

Graphics Controller 35

Specifications Rev. 1.1

Page 36

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

3 PROCEDURE OF THE HARDWARE INITIALIZATION

3.1 Hardware reset

1.Do the hardware reset. (see section 11.3.2)

2.After the hardware reset, set the CCF(Change of Frequency) register (section 9.2.1).

In being unstable cycle after the hardware reset, keep 32 bus cycles open.

3.Set the graphics memory interface register, MMR (Memory I/F Mode Register).

After setting the CCF register, take 200 us to set the MMR register.

In being unstable memory access cycle, keep 32 bus cycles open.

4.Other registers, except for the CCF register and the MMR register, should be set after

setting the CCF register.

In case of not using memory access, the MMR register could be set in any order after

the CCF register is set.

3.2 Re-reset

1. Reset XRST signal.

2. See section 3.1 for registers setting after the procedure of re-reset.

3.3 Software reset

1. Set the value of the SRST register (see section 9.2.1) for re-reset.

2. It is not necessary to reset the CCF register and the MMR register again.

MB86293 CORAL_LQ

Graphics Controller 36

Specifications Rev. 1.1

Page 37

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

4 HOST INTERFACE

4.1 Operation Mode

4.1.1 Host CPU mode

Select the host CPU by setting the MODE0 to MODE 2 signals as follows:

Table 4-1 CPU Type Setting

MODE 2 MODE 1 MODE 0 CPU

L L

L L

L H

L H H SPARClite

H X X Reserved

L SH3

H SH4

L V832

4.1.2 Ready signal mode

The MODE2 pin can be used to set the ready signal level when the bus cycle of the host CPU terminates.

For the normally not ready mode, set the software wait to 0 or 1 cycles. When using this device in the

normally ready mode, set the software wait to 2 cycles. When using this device in the normally not ready

mode, set the software wait to one cycle. (When BS_MODE = H, three cycles are needed for the

software wait.)

The ‘normally not ready mode’ is the mode in which the CORAL XRDY signal is always in the wait state

and Ready is returned only when read/write is ready.

The ‘normal ready mode’ is the mode in which the CORAL XRDY signal is always in the Ready state and

it is put into the wait state only when read/write cannot be performed immediately.

Table 4-2 Ready Signal Mode

RDY_MODE Ready signal operation

L

H

Recognizes XRDY signal as ‘not ready level’ and terminates bus cycle

(normally not ready mode)

Recognizes XRDY signal as ‘ready level’ and terminates bus cycle (norma lly

ready mode)

MB86293 CORAL_LQ

Graphics Controller 37

Specifications Rev. 1.1

Page 38

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

4.1.3 BS signal mode

Connection to a CPU without the BS signal can be made via the BS_MODE signal. This setting can be

performed for all CPU modes. To connect to a CPU without the BS signal, set the BS_MODE signal to

“High” level.

When not using the BS signal, fix the BS pin of CORAL at “High” level.

When using the BS_MODE signal as “High” level, with the normally ready mode established, set the CPU

software wait to three cycles.

Table 4-3 BS Signal Mode

BS_MODE Operation of BS signal

L Connects to CPU with BS signal

H Connects to CPU without BS signal

4.1.4 Endian

CORAL operates in little-endian mode. All the register address descriptions in the specifications are byte

address in little endian. When using a big-endian CPU, note that the byte-or word-addresses are

different from these descriptions.

MB86293 CORAL_LQ

Graphics Controller 38

Specifications Rev. 1.1

Page 39

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

4.2 Access Mode

4.2.1 SRAM interface

Data can be transferred to/from CORAL using SRAM access protocol. CORAL internal registers and

graphics memory are all mapped to the physical address area of the host processor.

CORAL uses hardware wait based on the XRDY signal, enabling the hardware wait setting of the host

CPU. When using the normally not ready mode, set the software wait to “1”. When using the normally

ready mode, set the software wait to “2”. (When using the BS_MODE signal as “High” level, with the

normally ready mode established, set the CPU software wait to three cycles.) Switch the ready mode

using the RDY_MODE signal.

CPU Read

The host processor reads data from internal registers and memory of CORAL in double-word (32 bit)

units. Valid data is output continuously while XRD and XCS are being asserted at a “Low” level after

XRDY has been asserted.

CPU Write

The host CPU writes data to internal registers and memory of CORAL in byte, word(16 bit) and

double-word( 32 bit) units.

4.2.2 FIFO interface (fixed transfer destination address)

This interface transfers display lists stored in host memory. Display list information is transferred

efficiently using a single address mode DMA transfer. Data can be transferred to FIFO in relation to

FIFO buffer area mapped in memory area using SRAM interface or dual address mode.

MB86293 CORAL_LQ

Graphics Controller 39

Specifications Rev. 1.1

Page 40

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

4.3 DMA Transfer

4.3.1 Data transfer unit

DMA transfer is performed in double-word (32 bits) units or 8 double-word (32 bytes) units. Byte and

word access is not supported.

Note: 8 double-word transfer is supported only in the SH4 mode.

4.3.2 Address mode

Dual address mode (mode using ACK)

DMA is performed at memory-to-memory transfer between host memory and registers mapped in

memory space or graphics memory (destination). Both the host memory address and CORAL is used.

In the SH4 mode, the 1 double -word transfer (32 bits) and 8 double-word transfer (32 bytes) can be

used.

When the CPU transfer destination address is fixed, data can also be transferred to the FIFO interface.

However, in this case, even the SH4 mode supports only the 1 double-word transfer.

DREQ and DRACK pins and SRAM interface signals are used. In V832, the DREQ, DMAAK, and

XTC pins and SRAM interface signals are used.

Note: The SH3 mode supports the direct address mode; it does not support the indirect address

mode.

Dual address mode (mode not using ACK)

When not using the ACK signal with the dual address mode established, set bit3 at HostBase+0004h

(DNA: Dual address No Ack mode) to 1.

When the ACK is not used, the DREQ signal is in the edge mode and the DREQ signal is negated per

transfer and then reasserted it in the next cycle. If processing cannot be performed immediately

inside CORAL, the DREQ signal remains negated.

The transfer count register (DTC) of CORAL is not used, so in order to end DMA transfer, write “1” to

the DMA transfer stop register (DTS) from the CPU.

Note 1: In the dual DMA mode (mode without ACK), the destination address can be used only for the

FIFO.

In DMA transfer to the graphics memory, etc., use the dual DMA mode.

Note 2: DMA read is not supported.

Single address mode (FIFO interface)

Data is transferred between host memory (source) and FIFO (destination). Only the address output

from the host memory is used, and the data is transferred to the FIFO. This mode does not support

data write to the host memory. When the FIFO is full, the DMA transfer is suspended.

The 1 double-word transfer (32 bits) and the 8 double-word transfer (32 B) can be used.

DREQ, DTACK, and DRACK signal are used.

Note: The single-address mode is supported only in the SH4 mode.

MB86293 CORAL_LQ

Graphics Controller 40

Specifications Rev. 1.1

Page 41

FUJITSU LIMITED

PRELIMINARY and CONFIDENTIAL

4.3.3 Bus mode

Coral supports the DMA transfer cycle steal mode and burst mode according to setting of external DMA

mode.

Cycle steal mode (In the V832 mode, the burst mode is called the single transfer mode.)

In the cycle steal mode, the right to use the bus is obtained or released at every data transfer of 1 unit.

The DMA transfer unit can be selected from between the 1 double-word (32 bits) and 8 double-words

(32 B).