Page 1

FUJITSU SEMICONDUCTOR

DATA SHEET

DS04-27231-3E

ASSP For Power Management Applications

(General Purpose DC/DC Converter)

2-ch DC/DC Converter IC

with Overcurrent Protection

MB39A104

DESCRIPTION

■

The MB39A104 is a 2-channel DC/DC converter IC using pulse width modulation (PWM), incorporating an

overcurrent protection circuit (requiring no current sense resistor). This IC is ideal for down conversion.

Operating at high frequency reduces the value of coil.

This is ideal for built-in power supply such as LCD monitors and ADSL.

This product is covered by US Patent Number 6,147,477.

FEATURES

■

• Built-in timer-latch overcurrent protection circuit (requiring no current sense resistor)

• Power supply voltage range : 7 V to 19 V

• Reference voltage : 5.0 V ± 1 %

• Error amplifier threshold voltage : 1.24 V ± 1 %

• High-frequency operation capability : 1.5 MHz (Max)

• Built-in standby function: 0 µA (Typ)

• Built-in soft-start circuit independent of loads

• Built-in totem-pole type output for Pch MOS FET

PACKAGE

■

24-pin plastic SSOP

(FPT-24P-M03)

Page 2

MB39A104

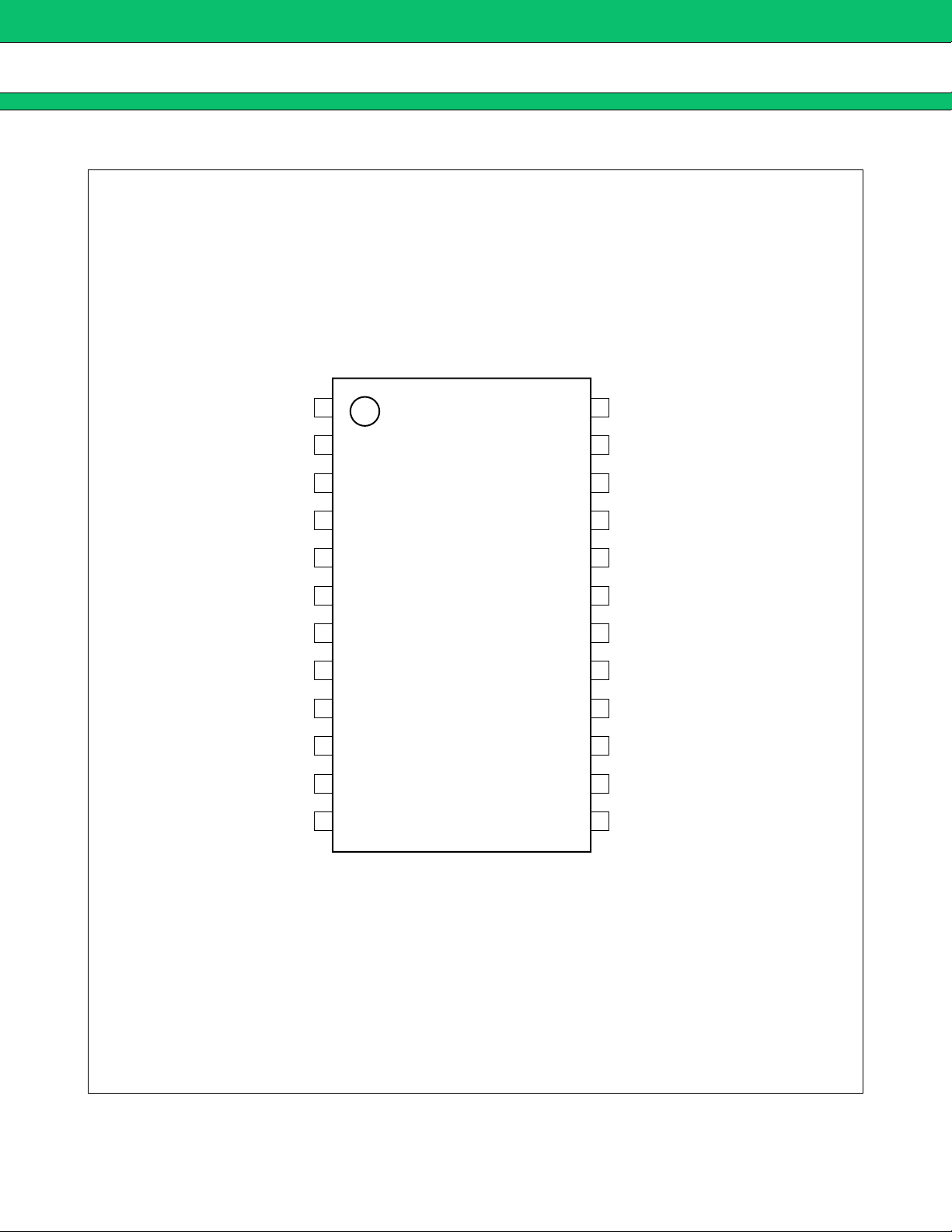

PIN ASSIGNMENTS

■

(TOP VIEW)

VCCO :

VH :

OUT1 :

VS1 :

ILIM1 :

DTC1 :

VCC :

CSCP :

FB1 :

−INE1 :

CS1 :

RT :

10

11

12

1

2

3

4

5

6

7

8

9

24

23

22

21

20

19

18

17

16

15

14

13

: CTL

: GNDO

: OUT2

: VS2

: ILIM2

: DTC2

: GND

: VREF

: FB2

: −INE2

: CS2

: CT

(FPT-24P-M03)

2

Page 3

MB39A104

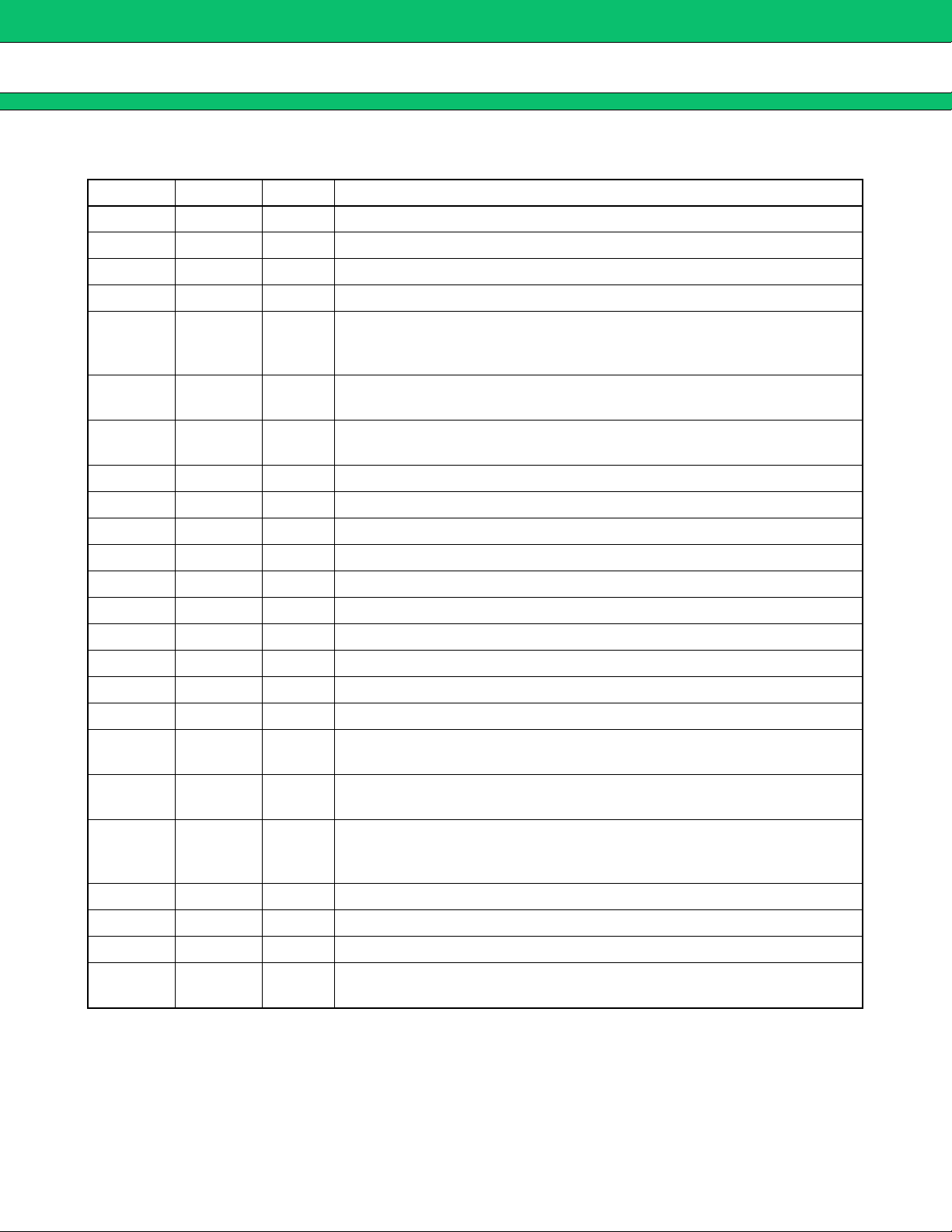

PIN DESCRIPTION

■

Pin No. Symbol I/O Descriptions

1VCCO Output circuit power supply terminal (Connect to same potential as VCC pin.)

2 VH O Power supply terminal for FET drive circuit (VH = V

3 OUT1 O External Pch MOS FET gate drive terminal

4 VS1 I Overcurrent protection circuit input terminal

Overcurrent protection circuit detection resistor connection terminal. Set

5ILIM1I

6DTC1I

7VCC

8CSCP Timer-latch short-circuit protection capacitor connection terminal

9 FB1 O Error amplifier (Error Amp 1) output terminal

10 −INE1 I Error amplifier (Error Amp 1) inverted input terminal

11 CS1 Soft-start capacitor connection terminal

12 RT Triangular wave oscillation frequency setting resistor connection terminal

13 CT Triangular wave oscillation frequency setting capacitor connection terminal

14 CS2 Soft-start capacitor connection terminal

15 −INE2 I Error amplifier (Error Amp 2) inverted input terminal

16 FB2 O Error amplifier (Error Amp 2) output terminal

overcurrent detection reference voltage depending on external resistor and

internal current resource (110 µA at RT = 24 kΩ)

PWM comparator block (PWM) input terminal. Compares the lowest voltage

among FB1 and DTC terminals with triangular wave and controls output.

Power supply terminal for reference power supply and control circuit

(Connect to same potential as the VCCO terminal)

CC − 5 V)

17 VREF O Reference voltage output terminal

18 GND

19 DTC2 I

20 ILIM2 I

21 VS2 I Overcurrent protection circuit input terminal

22 OUT2 O External Pch MOS FET gate drive terminal

23 GNDO Output circuit ground terminal (Connect to same potential as GND terminal.)

24 CTL I

Output circuit ground terminal (Connect to same potential as GNDO

terminal.)

PWM comparator block (PWM) input terminal. Compares the lowest voltage

among FB2 and DTC terminals with triangular wave and controls output.

Overcurrent protection circit detection resistor connection terminal. Set

overcurrent detection reference voltage depending on external resistor and

internal current resource (110 µA at RT = 24 kΩ)

Power supply control terminal. Setting the CTL terminal at “L” level places IC

in the standby mode.

3

Page 4

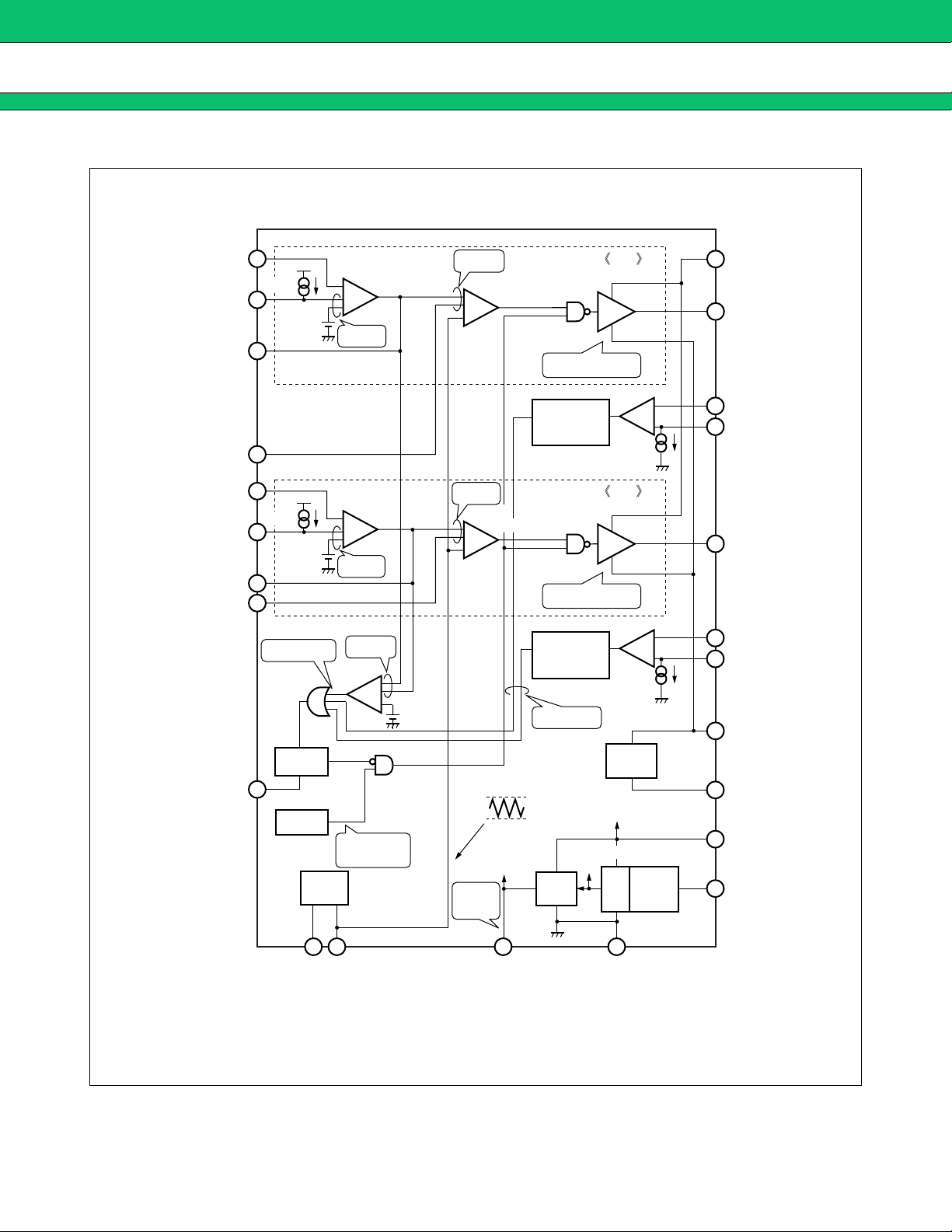

MB39A104

■ BLOCK DIA GRAM

10

−INE1

11

CS1

FB1

10 µA

9

VREF

1.24 V

Error

Amp1

−

+

+

L priority

L priority

PWM

Comp.1

+

+

−

CH1

Drive1

Pch

IO = 200 mA

at VCCO = 12 V

1

3

VCCO

OUT1

DTC1

−INE2

CS2

FB2

DTC2

CSCP

6

15

10 µA

14

16

19

H: at SCP

8

VREF

1.24 V

SCP

Logic

UVLO

OSC

12 13 1817

RT CT GNDVREF

−

+

+

L priority

H priority

SCP

Comp.

H:UVLO

release

Error

Amp2

+

+

−

(3.1 V)

L priority

2.5 V

1.5 V

Accuracy

±1%

PWM

Comp.2

+

+

−

5.0 V

bias

Current

Protection

Logic

CH2

Pch

I

O = 200 mA

at VCCO = 12 V

Current

Protection

Logic

H: at OCP

VH

Voltage

Error Amp Power Supply

Error Amp Reference

1.24 V

VREF

VR1

Drive2

V

Bias

Power

ON/OFF

−

+

−

+

CC − 5 V

CTL

4

5

22

21

20

2

23

7

24

VS1

ILIM1

OUT2

VS2

ILIM2

VH

GNDO

VCC

CTL

4

Page 5

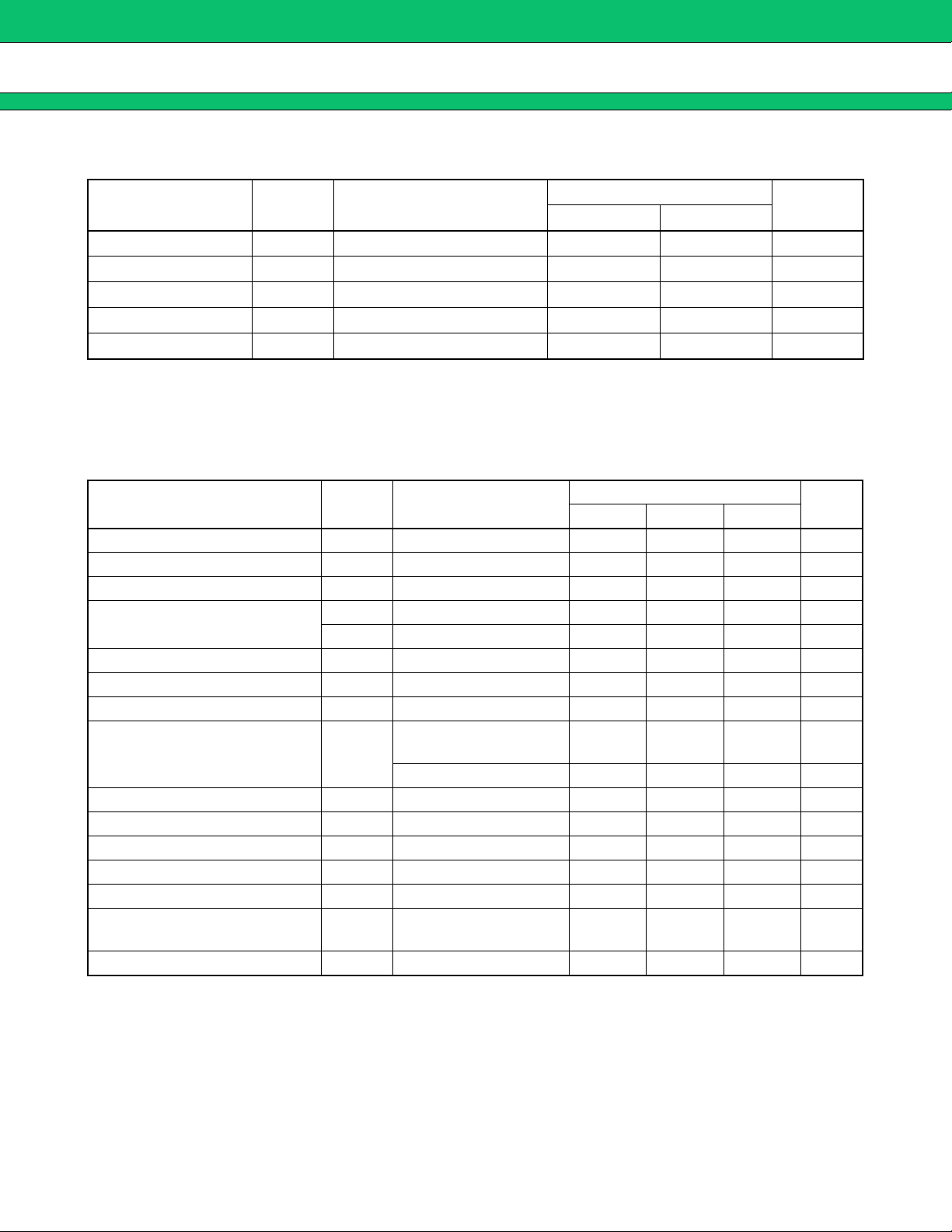

ABSOLUTE MAXIMUM RATINGS

■

MB39A104

Parameter Symbol Condition

Unit

Min Max

Rating

Power supply voltage V

Output current I

Output peak current I

Power dissipation P

Storage temperature T

CC VCC, VCCO terminal 20 V

O OUT1, OUT2 terminal 60 mA

OP Duty ≤ 5% (t = 1/fOSC×Duty) 700 mA

D Ta ≤ +25 °C 740* mW

STG −55 +125 °C

* : The packages are mounted on the epoxy board (10 cm × 10 cm).

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current,

temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

RECOMMENDED OPERATING CONDITIONS

■

Parameter Symbol Condition

Power supply voltage V

Reference voltage output current I

VH output current I

Input voltage

V

Control input voltage V

Output current I

Output Peak current I

Oscillation frequency f

Min Typ Max

CC VCC, VCCO terminal 7 12 19 V

REF VREF terminal −1 0mA

VH VH terminal 030 mA

V

INE −INE1, −INE2 terminal 0 VCC − 0.9 V

DTC DTC1, DTC2 terminal 0 VCC − 0.9 V

CTL CTL terminal 0 19 V

O OUT1, OUT2 terminal −45 +45 mA

Duty ≤ 5% (t = 1/fOSC×Duty)

OP

OSC

Overcurrent detection

by ON resistance of FET

−450 +450 mA

100 500 1000 kHz

Value

Unit

* 100 500 1500 kHz

Timing capacitor C

Timing resistor R

VH terminal capacitor C

Soft-start capacitor C

Short-circuit detection capacitor C

Reference voltage output

capacitor

T 39 100 560 pF

T 11 24 130 kΩ

VH VH terminal 0.1 1.0 µF

S CS1, CS2 terminal 0.1 1.0 µF

SCP CSCP terminal 0.1 1.0 µF

C

REF VREF terminal 0.1 1.0 µF

Operating ambient temperature Ta −30 +25 +85 °C

* : See“ ■ SETTING THE TRIANGULAR OSCILLATION FREQUENCY”.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the

semiconductor device. All of the device’s electrical characteristics are warranted when the device is

operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation

outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on

the data sheet. Users considering application outside the listed conditions are advised to contact their

FUJITSU representatives beforehand.

5

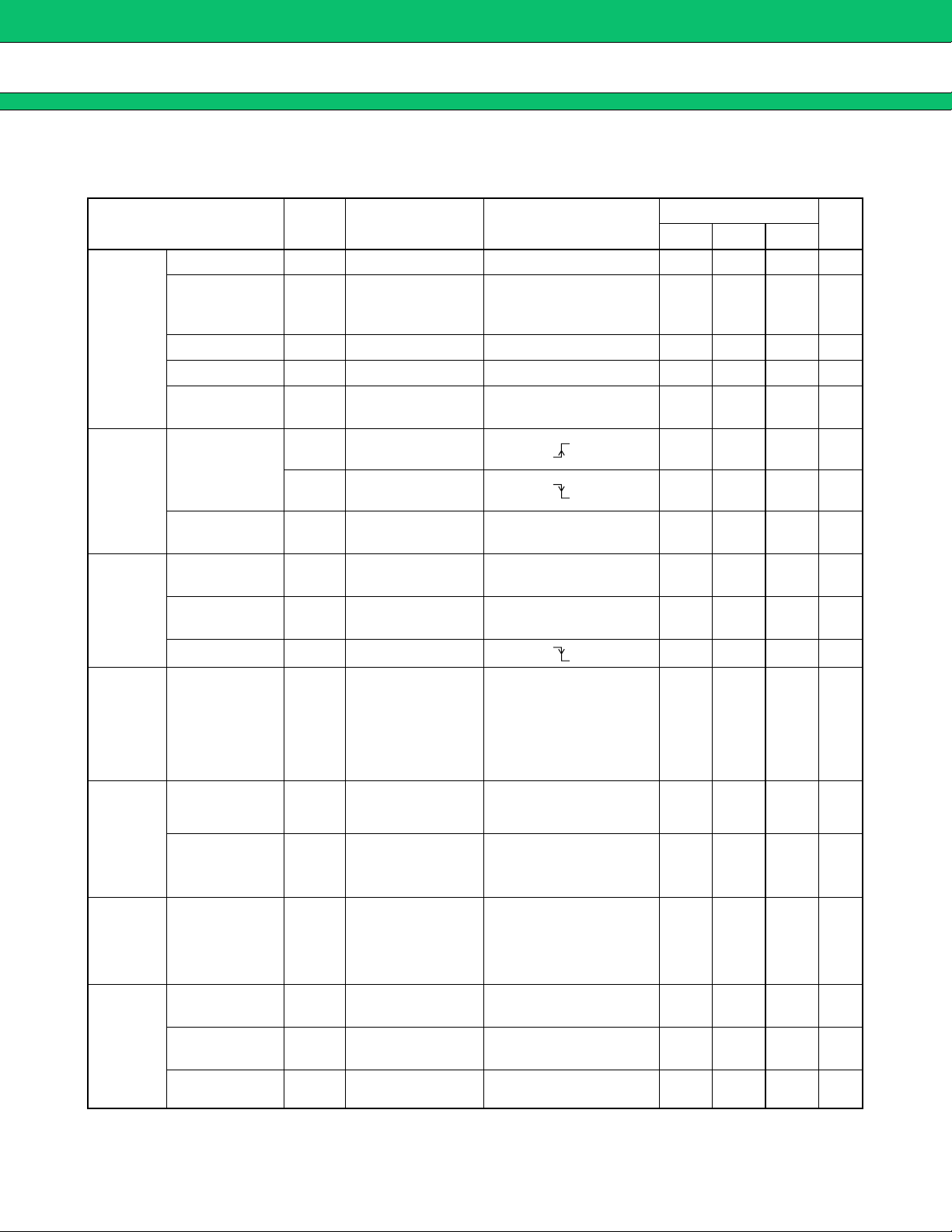

Page 6

MB39A104

ELECTRICAL CHARACTERISTICS

■

Parameter

Output voltage VREF 17 Ta = +25 °C 4.95 5.00 5.05 V

Output voltage

temperature

variation

Input stability Line 17 VCC = 7 V to 19 V 310mV

voltage

Load stability Load 17 VREF = 0 mA to −1 mA 110mV

block [REF]

1.Reference

Short-cuircuit

output current

Threshold

voltage

2.Under

voltage lockout

Hysteresis

block [UVLO]

width

protection circuit

Threshold

voltage

Input source

current

[SCP Logic]

3.Short-circuit

Reset voltage V

detection block

Symbol

REF/

∆V

V

REF

I

OS 17 VREF = 1 V −50 −25 −12 mA

V

TLH 17 VREF = 2.6 2.8 3.0 V

V

THL 17 VREF = 2.4 2.6 2.8 V

V

H 17 0.2 * V

TH 8 0.68 0.73 0.78 V

V

CSCP 8 −1.4 −1.0 −0.6 µA

I

RST 17 VREF = 2.4 2.6 2.8 V

(VCC = VCCO = 12 V, VREF = 0 mA, Ta = +25 °C)

Value

Pin No Conditions

Unit

Min Typ Max

17 Ta = 0 °C to +85 °C 0.5* %

Threshold

voltage

[SCP Comp]

4.Short-circuit

detection block

Oscillation

frequency

[OSC]

Frequency

5.Triangular

start

6.Soft-

variation

wave oscillator

Charge current ICS 11, 14 CS1 = CS2 = 0 V −14 −10 −6 µA

block

temperature

block

[CS1, CS2]

Threshold

voltage

Input bias

bolck

7.Error amplifier

current

[Error Amp1,

Error Amp2]

Voltage gain A

V

TH 8 2.8 3.1 3.4 V

f

OSC 13 CT = 100 pF, RT = 24 kΩ 450 500 550 kHz

OSC/

∆f

f

OSC

V

TH 9, 16 FB1 = FB2 = 2 V 1.227 1.240 1.253 V

I

B 10, 15 −INE1 = −INE2 = 0 V −120 −30 nA

V 9, 16 DC 100* dB

13 Ta = 0 °C to +85 °C 1* %

(Continued)

6

Page 7

(Continued)

(VCC = VCCO = 12 V, VREF = 0 mA, Ta = +25 °C)

Parameter Symbol Pin No. Conditions

MB39A104

Value

Unit

Min Typ Max

Frequency

bandwidth

Output voltage

Output source

[Error Amp1,

Error Amp2]

current

8.Error amplifier bolck

Output sink current I

Threshold voltage

block

Input current I

PWM Comp.2]

[PWM Comp.1,

9.PWM comparator

ILIM terminal input

current

block

Offset voltage V

10.Overcurrent

11.Bias

[OCP1, OCP2]

protection circuit

Output voltage VH 2

[VH]

block

voltage

Output source

current

Output sink current ISINK 3, 22

[Drive1, Drive2]

12.Output block

Output ON

resistor

CTL input voltage

BW 9, 16 A

V

OH 9, 16 4.7 4.9 V

V

OL 9, 16 40 200 mV

SOURCE 9, 16 FB1 = FB2 = 2 V −2 −1mA

I

SINK 9, 16 FB1 = FB2 = 2 V 150 200 µA

T0 6, 19 Duty cycle = 0 % 1.4 1.5 V

V

V

T100 6, 19 Duty cycle = Dtr 2.5 2.6 V

DTC 6, 19 DTC1 = DTC2 = 0.4 V −2.0 −0.6 µA

I

LIM 5, 20 RT = 24 kΩ, CT = 100 pF 99 110 121 µA

IO 5, 20 1 * mV

V = 0 dB 1.6* MHz

VCC = VCCO = 7 V to 19 V

VH = 0 mA to 30 mA

VCC−

5.5

VCC−

5.0

VCC−

4.5

V

OUT1 to OUT4 = 7 V,

ISOURCE 3, 22

Duty ≤ 5 %

(t = 1/f

OSC×Duty)

−300 mA

OUT1 to OUT4 = 12 V,

Duty ≤ 5 %

(t = 1/f

R

OH 3, 22 OUT1 = OUT2 = −45 mA 8.0 12.0 Ω

R

OL 3, 22 OUT1 = OUT2 = 45 mA 6.5 9.7 Ω

V

IH 24 IC Active mode 2 19 V

V

IL 24 IC Standby mode 0 0.8 V

OSC×Duty)

350 mA

[CTL]

Input current

13.Control block

Standby current ICCS 1, 17 CTL = 0 V 010µA

Power supply

current

14.General

*: Standard design value.

I

CTLH 24 CTL = 5 V 50 100 µA

I

CTLL 24 CTL = 0 V 1 µA

I

CC 1, 17 CTL = 5 V 4.0 6.0 mA

7

Page 8

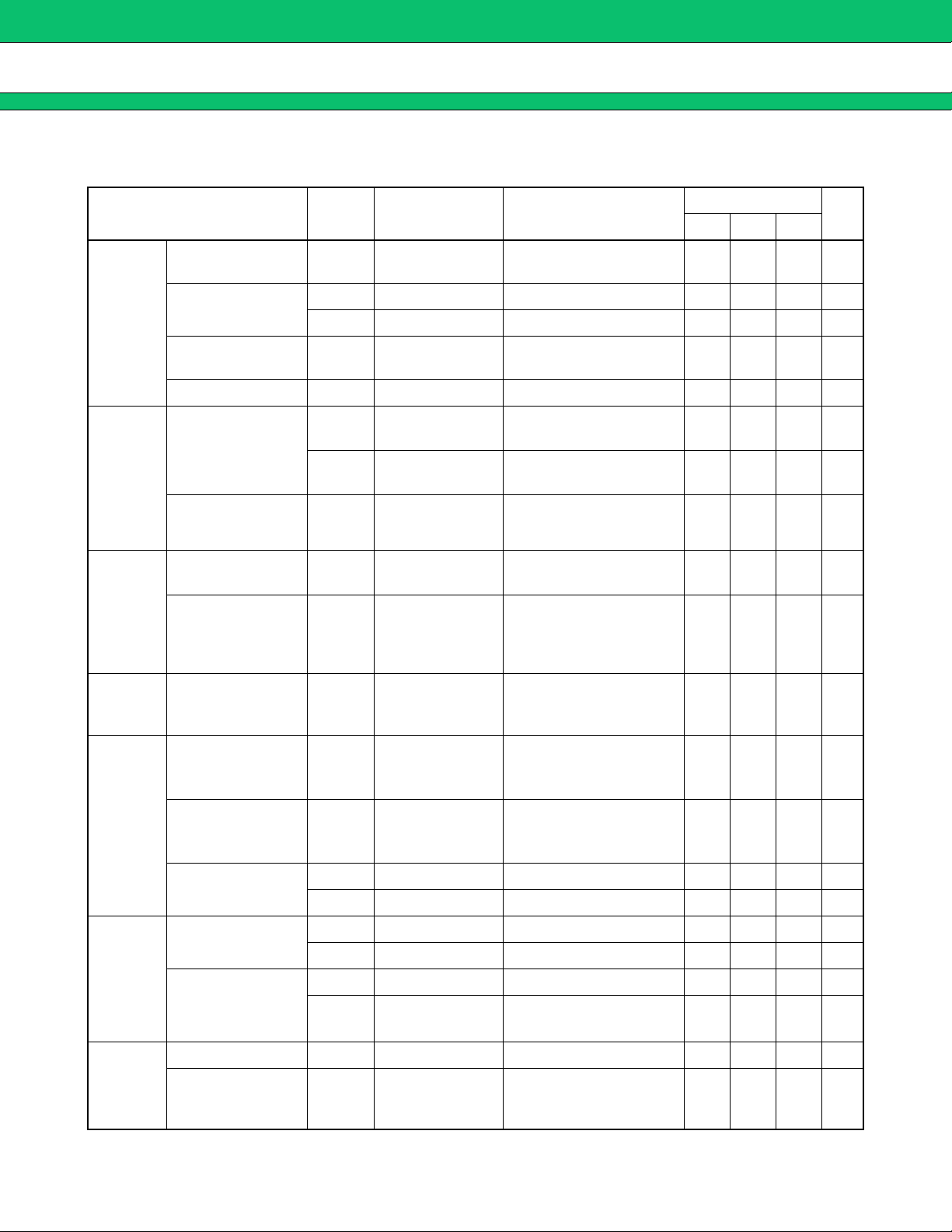

MB39A104

TYPICAL CHARACTERISTICS

■

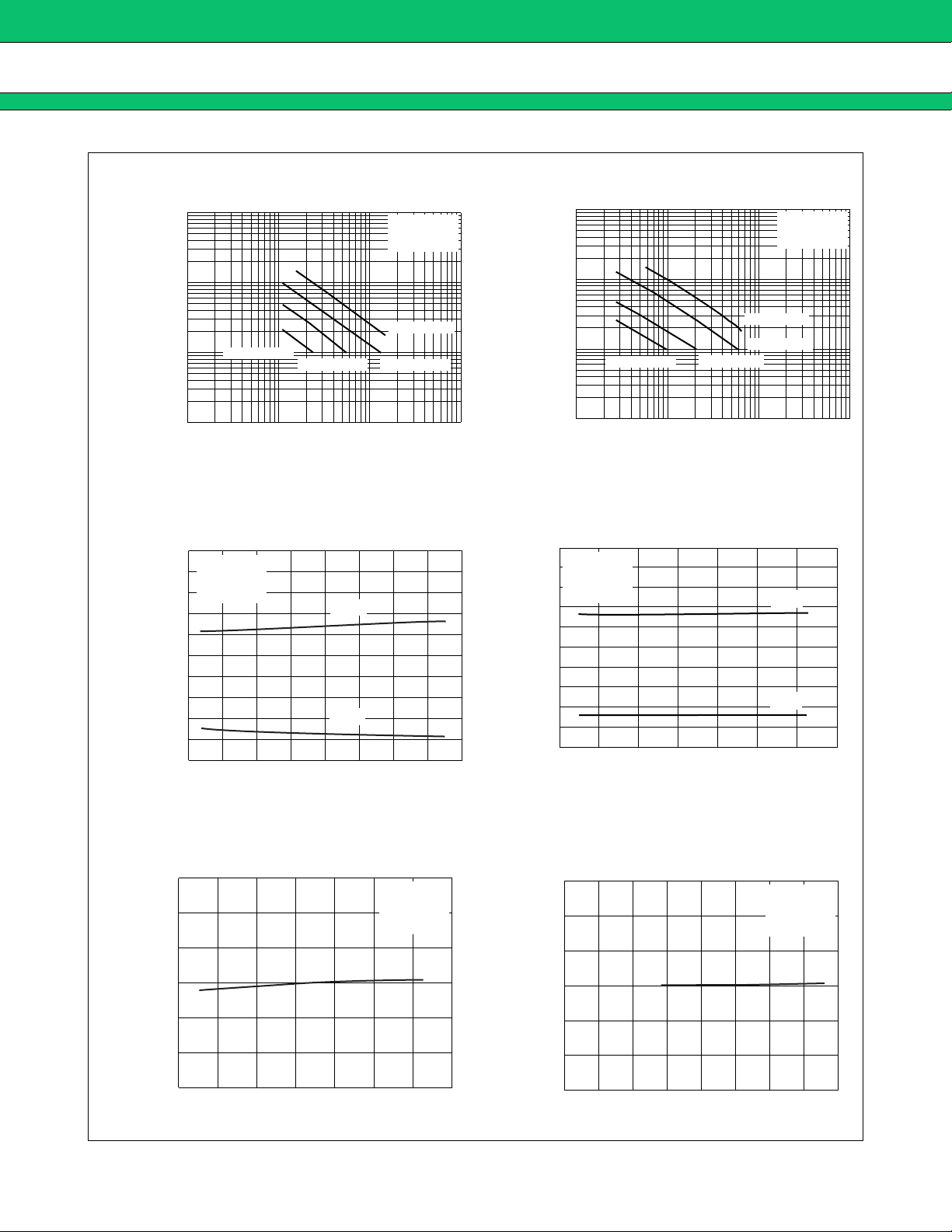

Power Supply Current vs. Power Supply Voltage

10

8

6

4

2

Power supply current ICC (mA)

0

0 5 10 15 20

Power supply voltage VCC (V)

Ta = +25 °C

CTL = 5 V

Reference Voltage vs. Ambient Temperature

10

8

6

4

Ta = +25 °C

VCC = 12 V

CTL = 5 V

Reference Voltage vs. Power Supply Voltage

10

8

REF (V)

6

4

2

Reference voltage V

0

0 5 10 15 20

Power supply voltage V

Ta = +25 °C

CTL = 5 V

VREF = 0 mA

CC (V)

Reference Voltage vs. Ambient Temperature

2.0

1.5

1.0

0.5

0.0

−0.5

VCC = 12 V

CTL = 5 V

VREF = 0 mA

2

Reference voltage VREF (V)

0

0 5 10 15 20 25 30 35

Ambient temperature Ta (°C)

CTL terminal Current vs. CTL terminal Voltage

500

400

300

200

100

CTL terminal current ICTL (µA)

0

0 5 10 15 20

VREF

ICTL

Ta = +25 °C

VCC = 12 V

VREF = 0 mA

CTL terminal voltage VCTL (V)

10

9

8

7

6

5

4

3

2

1

0

Reference voltage VREF (V)

−1.0

−1.5

Reference voltage ∆VREF (%)

−2.0

−40 −20 0 20 40 60 80 100

Ambient temperature Ta (°C)

(Continued)

8

Page 9

MB39A104

0

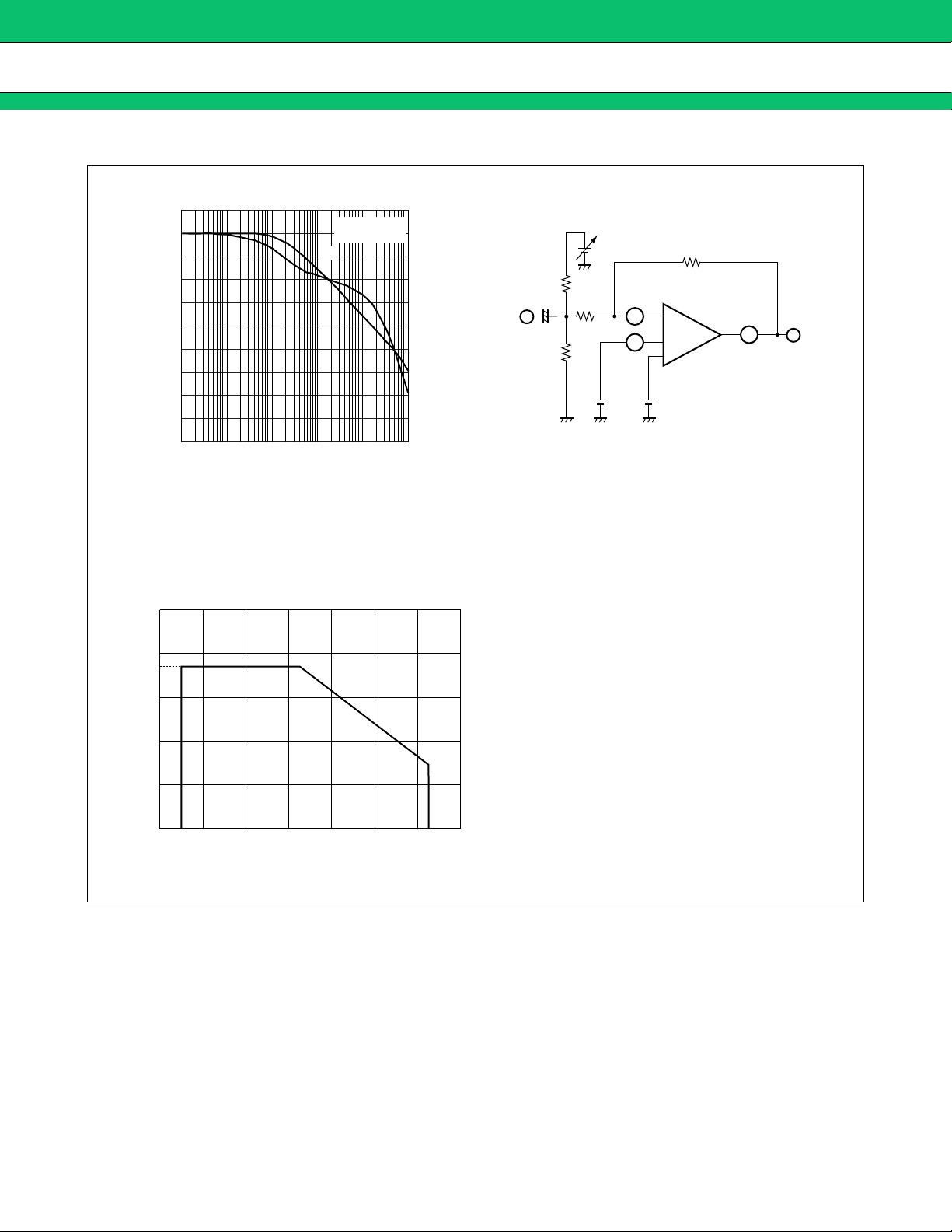

Triangular Wave Oscillation Frequency

vs. Timing Resistor

10000

1000

OSC (kHz)

100

CT = 560 pF

frequency f

Triangular wave oscillation

10

1 10 100 1000

Timing resistor RT (kΩ)

CT = 220 pF

Ta = +25 °C

VCC = 12 V

CTL = 5 V

CT = 39 pF

CT = 100 pF

Triangular Wave Upper and Lower Limit Voltage

vs. Triangular Wave Oscillation Frequency

3.2

Ta = +25 °C

3.0

VCC = 12 V

CTL = 5 V

2.8

CT (V)

lower limit voltage V

Triangular wave upper and

RT = 47 kΩ

2.6

2.4

2.2

2.0

1.8

1.6

1.4

1.2

0 200 400 600 800 1000 1200

Triangular wave oscillation frequency fOSC (kHz)

Upper

Lower

16001400

Triangular Wave Oscillation Frequency

vs. Timing Capacitor

10000

1000

OSC (kHz)

100

RT = 130 kΩ

frequency f

Triangular wave oscillattion

10

10 100 1000 1000

Timing capacitor CT (pF)

RT = 68 kΩ

Ta = +25 °C

VCC = 12 V

CTL = 5 V

RT = 11 kΩ

RT = 24 kΩ

Triangular Wave Upper and Lower Limit Voltage

vs. Ambient Temperature

3.2

VCC = 12 V

3.0

CTL = 5 V

RT = 24 kΩ

2.8

CT = 100 pF

CT (V)

2.6

2.4

2.2

2.0

1.8

1.6

1.4

lower limit voltage V

Triangular wave upper and

1.2

−40 −20 0 20 40 60 80 100

Ambient temperature Ta ( °C)

Upper

Lower

Triangular Wave Oscillation Frequency

vs. Ambient Temperature

560

540

520

OSC (kHz)

500

480

frequency f

460

Triangular wave oscillation

440

−40 −20 0 20 40 60 80 100

Ambient temperature Ta ( °C)

VCC = 12 V

CTL = 5 V

RT = 24 kΩ

CT = 100 pF

Triangular Wave Oscillation Frequency

vs. Power supply voltage

560

540

520

OSC (kHz)

500

480

frequency f

460

Triangular wave oscillation

440

0 5 10 15 20

Power supply voltage VCC (V)

Ta = +25 °C

CTL = 5 V

RT = 24 kΩ

CT = 100 pF

(Continued)

9

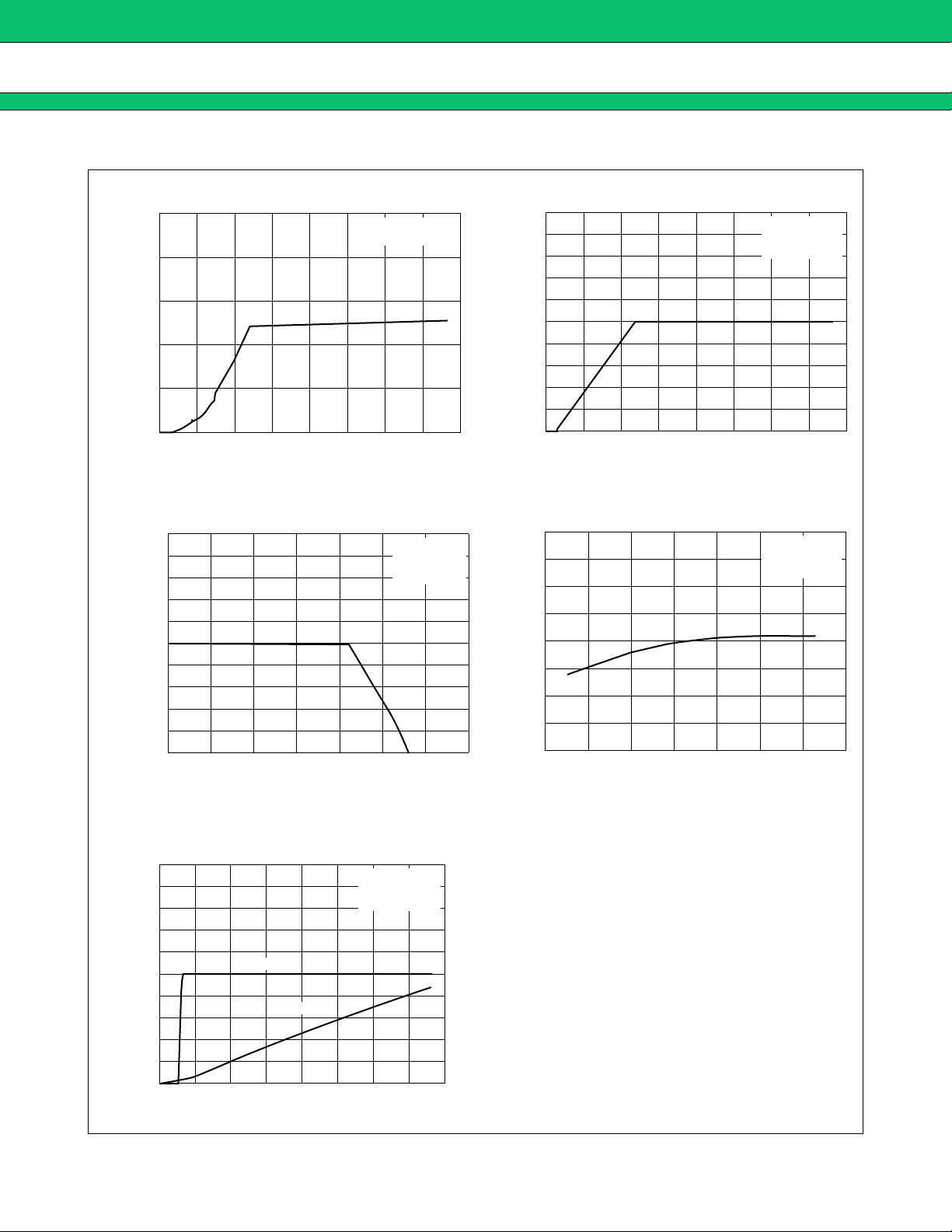

Page 10

MB39A104

(Continued)

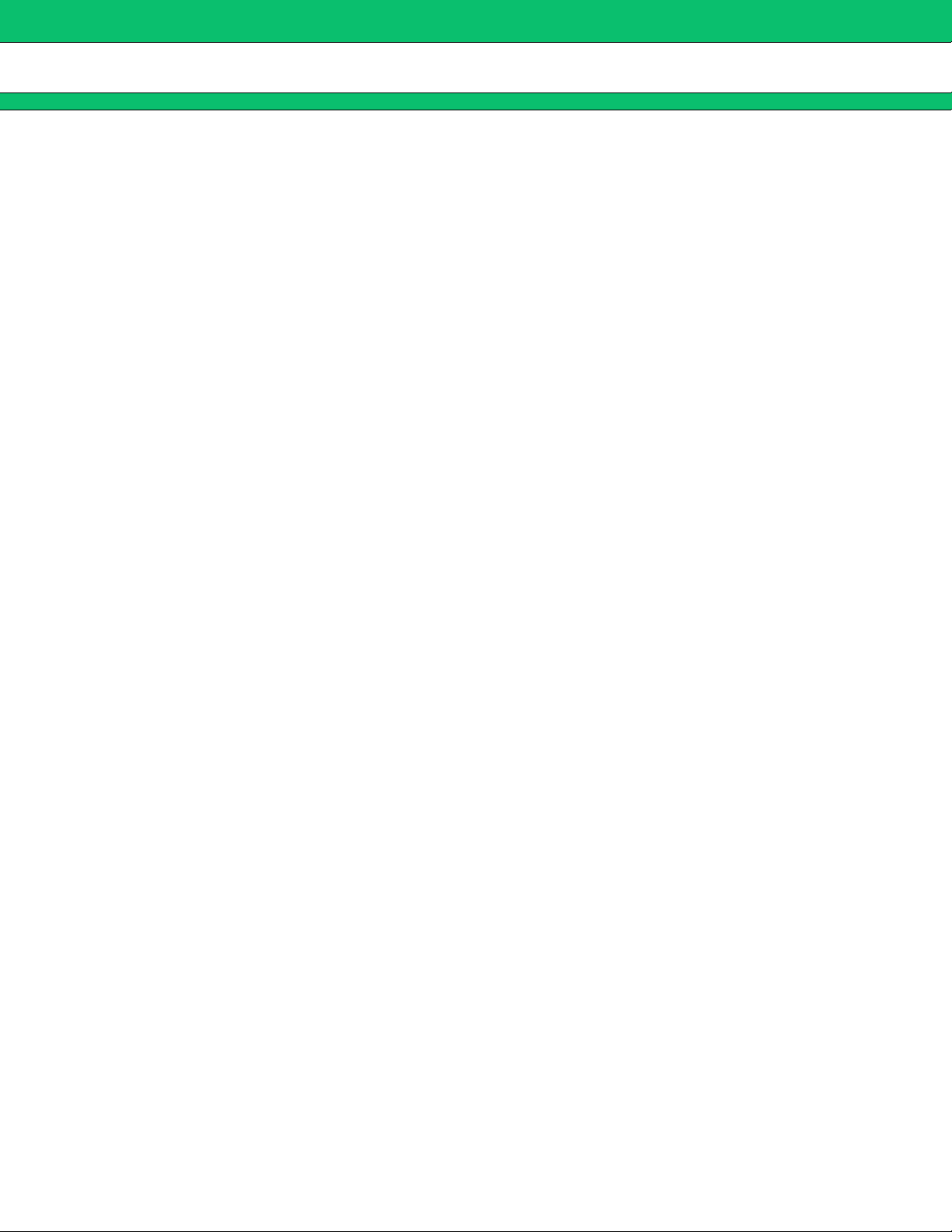

Error Amplifier, Gain, Phase vs. Frequency

Ta = +25 °C

VCC = 12 V

AV

Gain AV (dB)

40

30

20

10

0

−10

−20

−30

−40

100 1 k 10 k 100 k 1 M 10 M

ϕ

Frequency f (Hz)

Power Dissipation vs. Ambient Temperature

1000

800

740

180

90

0

−90

−180

Phase φ (deg)

10 kΩ

1 µF

+

IN

10 kΩ

2.4 kΩ

(15)

10

11

(14)

240 kΩ

−

+

+

1.24 V

9

(16)

Error Amp1

(Error Amp2)

OUT

600

400

200

Power dissipation PD (mW)

0

−40 −20 0 20 40 60 80 100

Ambient temperature Ta ( °C)

10

Page 11

MB39A104

FUNCTIONS

■

1. DC/DC Converter Functions

(1) Reference voltage block (REF)

The reference voltage circuit generates a temperature-compensated reference voltage (5.0 V Typ) from the

voltage supplied from the power supply terminal (pin 7). The voltage is used as the reference voltage for the

IC’s internal circuitry.

The reference voltage can supply a load current of up to 1 mA to an external device through the VREF terminal

(pin 17).

(2) Triangular-wave oscillator block (OSC)

The triangular wave oscillator incorporates a timing capacitor and a timing resistor connected respectively to

the CT terminal (pin 13) and RT terminal (pin 12) to generate triangular oscillation wavef orm amplitude of 1.5 V

to 2.5 V.

The triangular waveforms are input to the PWM comparator in the IC.

(3) Error amplifier block (Error Amp1, Error Amp2)

The error amplifier detects the DC/DC converter output voltage and outputs PWM control signals. In addition,

an arbitrary loop gain can be set by connecting a feedback resistor and capacitor from the output terminal to

inverted input terminal of the error amplifier, enabling stable phase compensation to the system.

Also, it is possib le to prevent rush current at power supply start-up by connecting a soft-start capacitor with the

CS1 terminal (pin 11) and CS2 terminal (pin 14) which are the non-inverted input ter minal for Error Amp. The

use of Error Amp for soft-start detection makes it possible for a system to oper ate on a fixed soft-start time that

is independent of the output load on the DC/DC converter.

(4) PWM comparator block (PWM Comp.)

The PWM comparator is a voltage-to-pulse width modulator that controls the output duty depending on the input/

output voltage.

The comparator keeps output transistor on while the error amplifier output voltage remain higher than the

triangular wave voltage.

(5) Output block

The output block is in the totem pole configuration, capable of driving an external P-channel MOS FET.

(6) Bias voltage block (VH)

This bias voltage circuit outputs V

circuit outputs the potential equal to V

CC − 5 V(Typ) as minimum potential of the output circuit. In standby mode , this

CC.

11

Page 12

MB39A104

2. Control Function

When CTL terminal (pin 24) is “L” level, IC becomes the standby mode . The power supply current is 10 µA (Max)

at the standby mode.

On/Off Setting Conditions

CTL Power

L OFF (Standby)

H ON (Operating)

3. Protective Functions

(1) Timer-latch overcurrent protection circuit block (OCP)

The timer-latch overcurrent protection circuit is actuated upon completion of the soft-start period. When an

overcurrent flows, the circuit detects the increase in the voltage between the FET’s drain and source using the

external FET ON resistor, actuates the timer circuit, and starts charging the capacitor C

CSCP terminal (pin 8). If the overcurrent remains flowing beyond the predetermined period of time, latch is set

and OUT terminlas (pin 3,22) of each channel are fixed at “H” lev el. And the circuit sets the latch to turn off the

external FET. The detection current value can be set by resistor R

the ILIM1 terminal (pin 5) and resistor R

LIM2 connected between the drain and the ILIM2 terminal (pin 20).

LIM1 connected between the FET’s drain and

SCP con-nected to the

Changing connection enables to detect overcurrent at current sense resistor.

To reset the actuated protection circuit, either the power supply turn off and on again or set the CTL terminal

(pin 6) to the “L” level to lo w er the VREF terminal (pin 17) voltage to 2.4 V (Min) or less . (See “1. Setting TimerLatch Overcurrent Protection Detection Current” in “■ABOUT TIMER-LATCH PROTECTION CIRCUIT”.)

(2) Timer-latch short-circuit protection circuit (SCP Logic, SCP Comp.)

The short-circuit detection comparator (SCP Comp.) detects the output voltage level of Error Amp, and if the

error amp output voltage of any channel falls below the shor t-circuit detection voltage (3.1 V Typ), the timer

circuits are actuated to start charging the external capacitor C

SCP connected to the CSCP terminal (pin 8).

When the capacitor voltage reaches about 0.73 V, the circuit is turned off the output transistor and sets the dead

time to 100 %.

To reset the actuated protection circuit, either the power supply turn off and on again or set the CTL terminal

(pin 24) to the “L” level to lower the VREF terminal (pin 17) voltage to 2.4 V (Min) or less. (See “2. Setting Time

Constant for Timer-Latch Short-Circuit Protection Circuit” in “■ABOUT TIMER-LATCH PROTECTION CIRCUIT”.)

(3) Under voltage lockout protection circuit (UVLO)

The transient state or a momentary decrease in supply voltage, which occurs when the power supply is turned

on, may cause the IC to malfunction, resulting in breakdown or degradation of the system. To prevent such

malfunctions, under voltage loc kout protection circuit detects a decrease in internal reference voltage with respect

to the power supply voltage, tur ns off the output transistor, and sets the dead time to 100% while holding the

CSCP terminal (pin 8) at the “L” level.

The circuit restores the output transistor to normal when the supply voltage reaches the threshold voltage of the

undervoltage lockout protection circuit.

(4) Protection circuit operating function table

This table refers to output condition when protection circuit is operating.

Operating circuit CS1 CS2 OUT1 OUT2

Overcurrent protection circuit L L H H

Short-circuit protection circuit L L H H

Under-voltage lockout L L H H

12

Page 13

SETTING THE OUTPUT VOLTAGE

■

• Output Voltage Setting Circuit

VO

MB39A104

R1

R2

SETTING THE TRIANGULAR OSCILLATION FREQUENCY

■

(−INE2)

−INE1

(CS2)

CS1

15

10

14

11

−

+

+

1.24 V

Error Amp

VO (V) =

1.24

R2

(R1 + R2)

The triangular oscillation frequency is determined by the timing capacitor (CT) connected to the CT terminal (pin

13), and the timing resistor (R

T) connected to the RT terminal (pin 12).

Moreover, it shifts more greatly than the caluculated v alues according to the constant of timing resistor (R

the triangular wave oscillation frequency e xceeds 1 MHz. Therefore, set it referring to “T riangular W ave Oscillation

Frequency vs . Timing Resistor” and “T riangular Wav e Oscillation Frequency vs. Timing Capacitor” in “■ TYPICAL

CHARACTERISTICS”.

T) when

Triangular oscillation frequency : f

fOSC (kHz) :=

1200000

C

T (pF) •RT (kΩ)

OSC

13

Page 14

MB39A104

SETTING THE SOFT-START AND DISCHARGE TIMES

■

To prevent r ush currents when the IC is tur ned on, you can set a soft-star t by connecting soft-star t capacitors

(C

S1 and CS2) to the CS1 terminal (pin 11) for channel 1 and the CS2 terminal (pin 14) for channel 2, respectively.

When CTL terminal (pin 24) goes to “H” level and IC starts (V

start capacitors (C

S1 and CS2) connected to CS1 and CS2 terminals are charged at 10 µA. The error amplifier

output (FB1 (pin 9) , FB2 (pin 16) ) is determined by comparison between the lower one of the potentials at two

non-inverted input terminals (1.24 V, CS1 terminal voltages) and the inverted input terminal voltage (−INE1 (pin

10) voltage, −INE2 (pin 15) voltage).

The FB1 (FB2) terminal voltage is decided for the soft-start period by the comparison between 1.24 V in an

internal reference voltage and the voltages of the CS1 (CS2) terminal. The DC/DC conver ter output voltage

rises in proportion to the CS1 (CS2) ter minal voltage as the soft-star t capacitor connected to the CS1 (CS2)

terminal is charged.

The soft-start time is obtained from the following formula:

Soft-start time: ts (time to output 100%)

ts (s) := 0.124 × C

S (µF)

CC ≥ UVLO threshold voltage), the external soft-

:= 5 V

:= 1.24 V

:= 0 V

CS1 (CS2) terminal voltage

Error Amp block −INE1 (−INE2) voltage

t

Soft-start time (ts)

14

Page 15

• Soft-Start Circuit

MB39A104

O

V

R1

R2

CH ON/OFF signal

L : ON, H : OFF

−INE1

(−INE2)

CS1

(CS2)

C

S1

(CS2)

FB1

(FB2)

10

15

11

14

16

VREF

10 µA

L priority

Error Amp

−

+

+

1.24 V

9

UVLO

15

Page 16

MB39A104

TREATMENT WITHOUT USING CS TERMINAL

■

When not using the soft-start function, open the CS1 terminal (pin 11) and the CS2 terminal (pin 14) .

•

Without Setting Soft-Start Time

“OPEN”

11

CS1

CS2

“OPEN”

14

16

Page 17

MB39A104

ABOUT TIMER-LATCH PROTECTION CIRCUIT

■

1. Setting Timer-Latch Overcurrent Protection Detection Current

The overcurrent protection circuit is actuated upon completion of the soft-start period. When an overcurrent

flows, the circuit detects the increase in the voltage betw een the FET’ s dr ain and source using the e xternal FET

ON resistor (R

terminal (pin 8). If the overcurrent remains flowing bey ond the predetermined period of time, the circuit sets the

latch to fix OUT terminals (pin 3, 22) at “H” level and turn off the external FET. The detection current value can

be set by the resistors (R

between the drain and the ILIM2 terminal (pin 20), respectively.

ON), actuates the timer circuit, and starts charging the capacitor CSCP connected to the CSCP

LIM1 and RLIM2) connected between the FET’s drain and the ILIM1 terminal (pin 5) and

The internal current (I

LIM) can be set by the timing resistor (RT) connected to the RT terminal (pin 12).

Time until activating timer circuit and setting latch is equal to short-circuit detection time in "2. Setting Time

Constant for Timer-Latch Short-Circuit Protection Circuit".

Internal current value: I

I

LIM (µA) :=

LIM

2700

R

T (kΩ)

Detection current value: IOCP

IOCP (A) :=

LIM(A) × RLIM(Ω)

R

ON (Ω)

−−−−

(VIN(V) − VO(V)) × VO(V)

2 × V

IN(V) × fOSC(Hz) × L(H)

I

RLIM : Overcurrent detection resistor

R

ON : External FET ON resistor

V

IN : Input voltage

V

O : DC/DC converter output voltage

f

OSC : Oscillation frequency

L : Coil inductance

To reset the actuated protection circuit, either the power supply turn off and on again or set the CTL terminal

(pin 24) to the "L" level to lower the VREF terminal (pin 17) voltage to 2.4 V (Min) or less.

• Overcurrent detection circuit

IN

V

Q1 L

CSCP

8

(1 µA)

S

Latch

(VS2)

21

VS1

4

(ILIM2)

Current

Protection

Logic

VREF

R

UVLO

−

+

Each

Channel

Drive

20

ILIM1

5

LIM)

(R

VO

17

Page 18

MB39A104

Overcurrent Protection Circuit: Range of Operation

When an overcurrent flow occurs , if the increased voltage between the drain and source of the FET is detected

by means of the external FET (Q1) resistor, operational stability is lost when the external FET (Q1) ON interv al

determined by the oscillation frequency, input voltage, and output voltage falls below 450 ns.

Therefore, the circuit should be used within a range that ensures that the ON interval does not f all belo w 450ns,

according to the following formula.

V

ON interval 450 (ns) ≥

V

If the ON interval of the external FET (Q1) is below 450ns, we recommend the use of an overcurrent detection

resistor RS to detect overcurrent, as shown below.

This example shows the range of operation of the overcurrent detection function with a setting of Vo = 3.3V.

•

Method to detect by current when external FET(Q1) is turned on

IN

V

(VS2)

21

VS1

4

O (V)

IN (V) × fOSC (Hz)

(Rs)

ErrAmp

Q1

Overcurrent Detection Function Operating Range

1600

1400

VO = set to 3.3 V

1200

1000

(ILIM2)

−+20

•

Method to detect by mean current

ILIM1

5

VIN

(VS2)

21

VS1

4

(ILIM2)

−

20

ILIM1

+

5

Connect to RS

Q1

when

using RS

ErrAmp

S

R

800

fOSC (kHz)

400

200

0

6 8 10 12 14

Operation Range

16 18 20

VCC (V)

Overcurrent Detection Function Operating Range

1600

1400

1200

1000

800

fOSC (kHz)

600

400

200

0

6 8 10 12 14

Operation Range

VO = set to 3.3 V

16 18 20

VCC (V)

18

Page 19

MB39A104

2. Setting Time Constant for Timer-Latch Short-Circuit Protection Circuit

Each channel uses the short-circuit detection comparator (SCP Comp.) to always compare the error amplifier′s

output level to the reference voltage (3.1 V Typ).

While DC/DC converter load conditions are stable on all channels, the short-circuit detection comparator output

remains at “L” level, and the CSCP terminal (pin 8) is held at “L” level.

If the load condition on a channel changes rapidly due to a short-circuit of the load, causing the output voltage

to drop, the output of the short-circuit detection comparator goes to “H” level. This causes the external shortcircuit protection capacitor C

Short-circuit detection time (t

t

SCP (s) := 0.73 × CSCP (µF)

When the capacitor C

FET is turned off (dead time is set to 100%). At this time, the latch input is closed and the CSCP terminal is

held at “L” level. If a short-circuit is detected on either of the two channels, both channels are shut off.

When the power supply is turned on back or VREF terminal (pin 17) voltage is less than 2.4 V (Min) by setting

CTL terminal (pin 24) to “L” level, the latch is released.

•

Timer-latch short-circuit protection circuit

SCP connected to the CSCP terminal to be charged at 1 µA.

SCP)

SCP is charged to the threshold voltage (VTH := 0.73 V), the latch is set and the external

R1

R2

(FB2)

V

O

FB1

(−INE2)

−INE1

16

15

10

9

Error

Amp

−

+

(1.24 V)

SCP

Comp.

(1 µA)

+

+

−

(3.1 V)

To each channel

Drive

CSCP

8

S

R

Latch

VREF

UVLO

19

Page 20

MB39A104

TREATMENT WITHOUT USING CSCP TERMINAL

■

When not using the timer-latch short-circuit protection circuit, connect the CSCP ter minal (pin 8) to GND with

the shortest distance.

• Treatment without using CSCP

18

GND

8

CSCP

RESETTING THE LATCH OF EACH PROTECTION CIRCUIT

■

When the overcurrent, or short-circuit protection circuit detects each abnormality , it sets the latch to fix the output

at the "L" level.

To reset the actuated protection circuit, either the power supply turn off and on again or set the CTL terminal

(pin 24) to the "L" level to lower the VREF terminal (pin 17) voltage to 2.4 V (Min) or less.

20

Page 21

MB39A104

O

I/O EQUIVALENT CIRCUIT

■

〈〈Reference voltage block〉〉 〈〈Control block〉〉 〈〈Soft-start block〉〉

VCC

GND

18

7

24

1.24 V

+

−

VREF

77.8

kΩ

24.8

kΩ

17

CTL

GND

72

kΩ

104

kΩ

VREF

(5.0 V)

GND

VCC

CSX

〈〈Short-circuit detection block〉〉

VREF

(5.0 V)

2 kΩ

GND

8

CSCP

〈〈Error amplifier block (CH1, CH2) 〉〉

VCC

VREF

(5.0 V)

−INEX CSX

1.24 V

GND

〈〈PWM comparator

block (CH1, CH2) 〉〉

VCC

〈〈Triangular wave oscillator

block (RT) 〉〉

(3.1 V)

1.35 V

GND

+

−

FBX

〈〈Bias voltage block〉〉

VCC

〈〈Triangular wave oscillator

(3.1 V)

CT

GND

(CT) block〉〉

13

12

VCC

RT

〈〈Overcurrent protection circuit block〉〉

VCC

ILIMX

GND

〈〈Output block (CH1, CH2) 〉〉

VCCO

VCCO

1

VCCO

VSX

GNDO

FBX CT

DTCX

GND

GND

2

GNDO

VH

GNDO

VH

23

X : Each channel No.

21

Page 22

MB39A104

APPLICATION EXAMPLE

■

Step-

down

O1

V

(5.0 V)

A

Q1 L1

VCCO

1

CH1

L priority

15 µF

OUT1

Drive1

PWM

Comp.1

+

+

+

Pch

D1

+

3

−

C4

82 µF

C310µF

C210µF

VS1

IO = 200 mA

at VCCO = 12 V

R4

5

4

−

+

Logic

Current

Protection

Step-

down

2.7 kΩ

ILIM1

O2

V

(3.3 V)

B

C11

0.1 µF

CH2

L priority

Q2 L2

PWM

D2

15 µF

+ +

OUT2

22

Drive2

Pch

Comp.2

+

+

−

C8

82 µF

C710µF

C610µF

VS2

O = 200 mA

at VCCO = 12 V

I

R5

20

21

−

+

Current

Protection

2.7 kΩ

ILIM2

Logic

VH

CC − 5 V

V

H:

at OCP

2

VH

GNDO

Bias

Voltage

23

Error Amp Power Supply

2.5 V

VCC

7

1.5 V

C10

0.1 µF

CTL

Error Amp Reference

1.24 V

bias

TH = 1.4 V

H : ON (Power ON)

L : OFF (Standby mode)

V

24

CTL

Power

ON/OFF

VR1

VREF

± 1%

accuracy

1817

5.0 V

GNDVREF

C20

0.1 µF

10

−INE1

R10R11

Error

Amp1

+

+

−

VREF

56 kΩ

10 µA

CS1

R9

1.24 V

11

R8

220

68 kΩ

0.1

C16

A

150 kΩ

CH1 ON/OFF signal

(Hiz : ON, L : OFF)

L priority

9

kΩ

C12

µF

FB1

1000 pF

6

DTC1

Error

Amp2

+

−

VREF

10 µA

15

14

CS2

−INE2

R14

68 kΩ

13 kΩ

R15R16

B

100 kΩ

CH2 ON/OFF signal

+

R13

220

0.1

C17

(Hiz : ON, L : OFF)

L priority

1.24 V

16

FB2

kΩ

C14

1000 pF

µF

VIN

(7 V to 19 V)

19

H priority

H:

DTC2

SCP

Comp.

at SCP

3.1 V

−

+

+

C1

SCP

Logic

H:

UVLO release

OSC

UVLO

8

12 13

RT CT

100 pF

R1

24 kΩ

CSCP

A)

C21

m

1000 pF

Charging

current (1

22

Page 23

MB39A104

PARTS LIST

■

COMPONENT ITEM SPECIFICATION VENDOR PARTS No.

Q1, Q2 Pch FET VDS = −30 V, ID = −6 A TOSHIBA TPC8102

D1, D2 Diode VF = 0.42 V (Max) , at IF = 3 A ROHM RB0530L-30

L1, L2 Inductor 15 µH 3.6 A, 50 mΩ SUMIDA CDRH104R-150

C1

C2, C6

C3, C7

C4, C8

C10, C11, C20

C12, C14, C21

C16, C17

R1

R4, R5

R8, R13

R9, R14

R10

R11

R15

R16

Ceramics Condenser

OS-CON

Ceramics Condenser

OS-CON

Ceramics Condenser

Ceramics Condenser

Ceramics Condenser

Resistor

Resistor

Resistor

Resistor

Resistor

Resistor

Resistor

Resistor

TM

TM

100 pF

10 µF

10 µF

82 µF

0.1 µF

1000 pF

0.1 µF

24 kΩ

2.7 kΩ

220 kΩ

68 kΩ

150 kΩ

56 kΩ

100 kΩ

13 kΩ

50 V

20 V

25 V

6.3 V

50 V

50 V

50 V

0.5 %

0.5 %

0.5 %

0.5 %

0.5 %

0.5 %

0.5 %

0.5 %

TDK

SANYO

TDK

SANYO

TDK

TDK

TDK

ssm

ssm

ssm

ssm

ssm

ssm

ssm

ssm

C1608CH1H101J

20SVP10M

C3225JF1E106Z

6SVP82M

C1608JB1H104K

C1608JB1H102K

C1608JB1H104K

RR0816P-243-D

RR0816P-272-D

RR0816P-224-D

RR0816P-683-D

RR0816P-154-D

RR0816P-563-D

RR0816P-104-D

RR0816P-133-D

Note : TOSHIBA : TOSHIBA Corporation

ROHM : ROHM Co., Ltd

SANYO : SANYO Electric Co., Ltd.

TDK : TDK Corporation

SUMIDA : SUMIDA Electric Co., Ltd.

ssm : SUSUMU Co., Ltd.

23

Page 24

MB39A104

SELECTION OF COMPONENTS

■

• Pch MOS FET

The P-ch MOSFET for s witching use should be rated f or at least 20% more than the maxim um input v oltage. To

minimize continuity loss, use a FET with low R

high frequency operation, on/off-cycle switching loss will be higher so that po wer dissipation must be considered.

In this application, the Toshiba TPC8102 is used. Continuity loss, on/off s witching loss , and total loss are determined by the follo wing formulas. The selection must ensure that peak drain current does not e xceed rated values,

and also must be in accordance with overcurrent detection levels.

DS(ON) between the drain and source. For high input voltage and

Continuity loss : P

C

PC = ID 2 × RDS (ON) × Duty

On-cycle switching loss : PS (ON)

P

S (ON) =

VD (Max) × ID × tr × fOSC

6

Off-cycle switching loss : PS (OFF)

P

S (OFF) =

VD (Max) × ID (Max) × tf × fOSC

6

Total loss : PT

PT = PC + PS (ON) + PS (OFF)

Example: Using the Toshiba TPC8102

CH1

Input voltage V

IN (Max) = 19 V, output v oltage VO = 5 V, drain current ID = 3 A, Oscillation frequency fOSC = 500 kHz,

L = 15 µH, drain-source on resistance R

Drain current (Max) : ID (Max)

I

D (Max) = IO +

= 3 +

VIN − VO

2L

19 − 5

2 × 15 × 10

ton

−6

×

500 × 10

DS (ON) := 50 mΩ, tr = tf := 100 ns.

1

× 0.263

3

:= 3.25 (A)

Drain current (Min) : ID (Min)

ID (Min) = IO −

= 3 −

:= 2.75 (A)

24

VIN − VO

2L

19 − 5

2 × 15 × 10

ton

×

−6

1

500 × 10

× 0.263

3

Page 25

PC = ID 2 × RDS (ON) × Duty

2

= 3

× 0.05 × 0.263

:= 0.

118 W

MB39A104

PS (ON) =

PS (OFF) =

VD (Max) × ID × tr × fOSC

6

19 × 3 × 100 × 10

=

:= 0.475

W

−9

× 500 × 10

6

VD (Max) × ID (Max) × tf × fOSC

6

19 × 3.25 × 100 × 10−9 × 500 × 10

=

:= 0.515

W

6

3

3

PT = PC + PS (ON) + PS (OFF)

:= 0.118 + 0.475 + 0.515

:= 1.

108 W

The above pow e r dissipation figures for the TPC8102 are satisfied with ample margin at 2.4 W (Ta = +25 °C) .

CH2

Input voltage V

f

OSC = 500 kHz, L = 15 µH, drain-source on resistance RDS (ON) := 50 mΩ, tr = tf := 100 ns.

IN (Max) = 19 V output voltage VO = 3.3 V, drain current ID = 3 A, Oscillation frequency

Drain current (Max) : I

ID (Max) = IO +

= 3 +

VIN − VO

2 × 15 × 10

D (Max)

2L

19 − 3.3

:= 3.18 (A)

Drain current (Min) : ID (Min)

ID (Min) = IO −

= 3 −

VIN − VO

2L

19 − 3.3

2 × 15 × 10

:= 2.82 (A)

ton

ton

×

−6

×

−6

1

500 × 10

1

500 × 10

× 0.174

3

× 0.174

3

25

Page 26

MB39A104

P

C = ID

PS (ON) =

PS (OFF) =

2

× RDS (ON) × Duty

2

= 3

:= 0.

×××× 0.05 × 0.174

078 W

VD (Max) × ID × tr × fOSC

19 × 3 × 100 × 10

=

:= 0.475

D (Max) × ID (Max) × tf × fOSC

V

19 × 3.18 × 100 × 10

=

:= 0.504

W

W

6

−9

× 500 × 10

3

6

6

−9

× 500 × 10

3

6

PT = PC + PS (ON) + PS (OFF)

:= 0.078 + 0.475 + 0.504

:= 1.

057 W

The above pow e r dissipation figures for the TPC8102 are satisfied with ample margin at 2.4 W (Ta = +25 °C) .

• Inductors

In selecting inductors, it is of course essential not to apply more current than the rated capacity of the inductor ,

but also to note that the lower limit for ripple current is a cr itical point that if reached will cause discontinuous

operation and a considerable drop in efficiency. This can be prevented by choosing a higher inductance value,

which will enable continuous operation under light loads. Note that if the inductance value is too high, however,

direct current resistance (DCR) is increased and this will also reduce efficiency. The inductance must be set at

the point where efficiency is greatest.

Note also that the DC superimposition characteristics become worse as the load current value approaches the

rated current value of the inductor , so that the inductance v alue is reduced and ripple current increases, causing

loss of efficiency. The selection of rated current value and inductance value will var y depending on where the

point of peak efficiency lies with respect to load current.

Inductance values are determined by the following formulas.

The L value fo r all load current conditions is set so that the peak to peak value of the ripple current is 1/2 the

load current or less.

Inductance value : L

L ≥

2 (VIN − VO)

I

O

ton

26

Page 27

Example:

CH1

L ≥

2 × (19 − 5)

≥

≥ 4.91 µH

CH2

L ≥

2 × (19 − 3.3)

≥

≥ 3.64 µH

IN − VO)

2 (V

I

O

IO 500 × 10

2 (VIN − VO)

I

O

ton

×

ton

IO 500 × 10

×

MB39A104

1

× 0.263

3

1

× 0.174

3

Inductance values derived from the above formulas are values that provide sufficient margin for continuous

operation at maximum load current, but at which continuous oper ation is not possible at light loads. It is theref ore

necessary to determine the load level at which continuous operation becomes possible. In this application, the

Sumida CDRH104R-150 is used. At 15 µH, the load current value under continuous operating conditions is

determined by the following formula.

Load current value under continuous operating conditions : I

IO ≥

VO

2L

toff

O

Example: Using the CDRH104R-150

15 µH (allowable tolerance ±30%) , rated current = 3.6 A

CH1

O ≥

≥

VO

toff

2L

5

2 × 15 × 10

×

−6

1

500 × 10

× (1 − 0.263)

3

I

≥ 245.7 mA

CH2

IO ≥

VO

2L

≥

2 × 15 × 10

toff

3.3

−6

×

500 × 10

1

× (1 − 0.174)

3

≥ 181.7 mA

27

Page 28

MB39A104

To deter mine whether the current through the inductor is within rated values, it is necessary to determine the

peak value of the ripple current as well as the peak-to-peak values of the ripple current that affect the output

ripple voltage. The peak value and peak-to-peak value of the ripple current can be determined by the following

formulas.

Peak value : I

L ≥ IO +

I

L

VIN − VO

2L

ton

Peak-to-peak value : ∆IL

∆I

L =

VIN − VO

L

ton

Example: Using the CDRH104R-150

15 µH (allowable tolerance ±30%) , rated current = 3.6 A

Peak value:

CH1

I

L ≥ IO +

≥ 3 +

VIN − VO

2L

19 − 5

2 × 15 × 10

ton

−6

×

500 × 10

1

≥ 3.25 A

CH2

IL ≥ IO +

≥ 3 +

VIN − VO

2L

19 − 3.3

2 × 15 × 10

−6

ton

×

500 × 10

1

× 0.263

3

× 0.174

3

≥ 3.18 A

Peak-to-peak value:

CH1

∆IL =

=

= 0.491 A

CH2

∆IL =

=

= 0.364 A

28

VIN − VO

L

19 − 5

15 × 10

VIN − VO

L

19 − 3.3

15 × 10

−6

−6

ton

×

500 × 10

ton

×

500 × 10

1

1

× 0.263

3

× 0.174

3

Page 29

MB39A104

• Flyback diode

The flyback diode is generally used as a Shottky barrier diode (SBD) when the reverse voltage to the diode is

less than 40V. The SBD has the characteristics of higher speed in ter ms of faster reverse recover y time, and

lower forw ard v oltage , and is ideal f or achieving high efficiency . As long as the DC re v erse voltage is sufficiently

higher than the input voltage, the a v erage current flo wing through the diode is within the a v erage output current

level, and peak current is within peak surge current limits, there is no problem. In this application the Rohm

RB053L-30 is used. The diode average current and diode peak current can be calculated by the following

for mul as.

Diode mean current : I

Di ≥ IO × (1 −

I

VO

VIN

Di

)

Diode peak current : IDip

IDip ≥ (IO +

VO

2L

toff)

Example: Using the Rohm RB053L-30

VR (DC reverse voltage) = 30 V, average output voltage = 3.0 A, peak surge current = 70 A,

VF (forward voltage) = 0.42 V, IF = 3.0 A

CH1

I

Di ≥ IO × (1 −

VO

VIN

)

≥ 3 × (1 − 0.263)

≥ 2.21 A

CH2

IDi ≥ IO × (1 −

VO

VIN

)

≥ 3 × (1 − 0.174)

≥ 2.48 A

CH1

IDip ≥ (IO +

≥ 3.24 A

CH2

IDip ≥ (IO +

≥ 3.18 A

VO

2L

VO

2L

toff)

toff)

29

Page 30

MB39A104

• Smoothing Capacitor

The smoothing capacitor is an indispensable element for reducing ripple v oltage in output. In selecting a smoothing capacitor it is essential to consider equivalent series resistance (ESR) and allowable ripple current. Higher

ESR means higher ripple voltage, so that to reduce ripple voltage it is necessary to select a capacitor with low

ESR. However, the use of a capacitor with low ESR can have substantial effects on loop phase characteristics,

and therefore requires attention to system stability. Care should also be taken to use a capacity with sufficient

margin for allow able ripple current. This application uses the (OS-CON

capacitance value, and ripple current can be calculated from the following formulas.

Equivalent Series Resistance : ESR

ESR ≤

O

∆V

∆IL 2πfCL

−

1

TM

) 6SVP82M made by Sanyo . The ESR,

Capacitance value : C

CL

≥

2πf (∆VO − ∆IL × ESR)

∆IL

L

Ripple current : ICLrms

(V

Lrms ≥

IC

IN − VO) ton

2√3

L

Example: Using the 6SVP82M

Rated voltage = 6.3 V, ESR = 50 mΩ, maximum allowable ripple current = 1570 mArms

Equivalent series resistance

CH1

ESR ≤

≤

∆VO

∆IL 2πfCL

0.050

0.491 2π × 500 × 10

−

−

1

1

3

× 82 × 10

−6

≤ 98.0 mΩ

30

Page 31

CH2

O

∆V

ESR ≤

≤

−

∆IL 2πfCL

0.033

0.364 2π × 500 × 10

≤ 86.8 mΩ

Capacitance value

CH1

CL ≥

2πf (∆VO − ∆IL × ESR)

≥

2π × 500 × 10

1

−

1

∆IL

0.491

3

× (0.050 − 0.491 × 0.05)

3

× 82 × 10

MB39A104

−6

≥ 6.14

CH2

CL ≥

2πf (∆VO − ∆IL × ESR)

≥

2π × 500 × 10

≥ 7.83

Ripple current

CH1

ICLrms ≥

≥

≥ 141.7 mArms

CH2

ICLrms ≥

≥

µF

∆IL

0.364

3

× (0.033 − 0.364 × 0.05)

µF

(V

IN − VO) ton

2√3L

(19 − 5) × 0.263

× 15 × 10−6 × 500 × 10

2√3

(V

IN − VO) ton

2√3L

(19 − 3.3) × 0.174

× 15 × 10−6 × 500 × 10

2√3

3

3

≥ 105.1 mArms

31

Page 32

MB39A104

REFERENCE DATA

■

TOTAL Efficiency vs. Input Voltage

100

90

80

70

60

50

40

TOTAL efficiency η (%)

30

10 m 100 m 1 10

Input voltage VIN (V)

Each CH Efficiency vs. Input Voltage

100

90

80

Ta = +25 °C

5 V Output

SW1 = OFF

SW2 = ON

Vin = 7 V

Vin = 10 V

Vin = 12 V

Vin = 19 V

32

70

60

50

40

Each CH efficiency η (%)

30

10 m 100 m 1 10

Input voltage VIN (V)

Ta = +25 °C

3.3 V Output

SW1 = ON

SW2 = OFF

Vin = 7 V

Vin = 10 V

Vin = 12 V

Vin = 19 V

(Continued)

Page 33

(Continued)

MB39A104

Switching Wave Form (CH1)

VG (V)

V

S (V)

VG (V)

15

10

5

0

15

10

5

0

012345678910

Switching Wave Form (CH2)

15

10

5

Ta = +25 °C

VIN = 12 V

CTL = 5 V

O = 5 V

V

RL = 1.67 Ω

t (µs)

Ta = +25 °C

VIN = 12 V

CTL = 5 V

O = 3.3 V

V

RL = 1.1 Ω

V

S (V)

0

15

10

5

0

012345678910

t (µs)

33

Page 34

MB39A104

■ USAGE PRECAUTION

••••

Printed circuit board ground lines should be set up with consideration for common impedance.

••••

Take appropriate static electricity measures.

• Containers for semiconductor materials should hav e anti-static protection or be made of conductive material.

• After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

• Work platforms, tools, and instruments should be properly grounded.

• Working personnel should be grounded with resistance of 250 kΩ to 1 MΩ between body and ground.

••••

Do not apply negative voltages.

The use of negative voltages below –0.3 V may create parasitic transistors on LSI lines, which can cause

abnormal operation.

■ ORDERING INFORMATION

Part number Package Remarks

MB39A104PFV

24-pin plastic SSOP

(FPT-24P-M03)

34

Page 35

■ PACKAGE DIMENSIONS

24-pin plastic SSOP

(FPT-24P-M03)

MB39A104

Note 1) *1 : Resin protrusion. (Each side : +0.15 (.006) MAX) .

Note 2) *2 : These dimensions do not include resin protrusion.

Note 3) Pins width and pins thickness include plating thickness.

Note 4) Pins width do not include tie bar cutting remainder.

1

*

7.75±0.10(.305±.004)

INDEX

112

0.65(.026)

C

2003 FUJITSU LIMITED F24018S-c-4-5

0.24

.009

0.10(.004)

0.10(.004)

+0.08

–0.07

+.003

–.003

0.13(.005)

1324

2

5.60±0.10 7.60±0.20

*

(.220±.004) (.299±.008)

M

0.17±0.03

(.007±.001)

"A"

Details of "A" part

+0.20

–0.10

1.25

+.008

–.004

.049

0.25(.010)

0~8˚

0.50±0.20

(.020±.008)

0.60±0.15

(.024±.006)

(Mounting height)

0.10±0.10

(.004±.004)

(Stand off)

Dimensions in mm (inches)

Note : The values in parentheses are reference values.

35

Page 36

MB39A104

FUJITSU LIMITED

All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with FUJITSU sales

representatives before ordering.

The information, such as descriptions of function and application

circuit examples, in this document are presented solely for the

purpose of reference to show examples of operations and uses of

Fujitsu semiconductor device; Fujitsu does not warrant proper

operation of the device with respect to use based on such

information. When you develop equipment incorporating the

device based on such information, you must assume any

responsibility arising out of such use of the information. Fujitsu

assumes no liability for any damages whatsoever arising out of

the use of the information.

Any information in this document, including descriptions of

function and schematic diagrams, shall not be construed as license

of the use or exercise of any intellectual property right, such as

patent right or copyright, or any other right of Fujitsu or any third

party or does Fujitsu warrant non-infringement of any third-party’s

intellectual property right or other right by using such information.

Fujitsu assumes no liability for any infringement of the intellectual

property rights or other rights of third parties which would result

from the use of information contained herein.

The products described in this document are designed, developed

and manufactured as contemplated for general use, including

without limitation, ordinary industrial use, general office use,

personal use, and household use, but are not designed, developed

and manufactured as contemplated (1) for use accompanying fatal

risks or dangers that, unless extremely high safety is secured, could

have a serious effect to the public, and could lead directly to death,

personal injury, severe physical damage or other loss (i.e., nuclear

reaction control in nuclear facility, aircraft flight control, air traffic

control, mass transport control, medical life support system, missile

launch control in weapon system), or (2) for use requiring

extremely high reliability (i.e., submersible repeater and artificial

satellite).

Please note that Fujitsu will not be liable against you and/or any

third party for any claims or damages arising in connection with

above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You

must protect against injury, damage or loss from such failures by

incorporating safety design measures into your facility and

equipment such as redundancy, fire protection, and prevention of

over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or

technologies subject to certain restrictions on export under the

Foreign Exchange and Foreign Trade Law of Japan, the prior

authorization by Japanese government will be required for export

of those products from Japan.

F0308

FUJITSU LIMITED Printed in Japan

Loading...

Loading...