Page 1

5

J361Y-SB Rev_V3.06(06/16/2005)

91.3H801.001

4

3

http://hobi-elektronika.net

J

2

1

D D

C C

B B

A A

Sheet

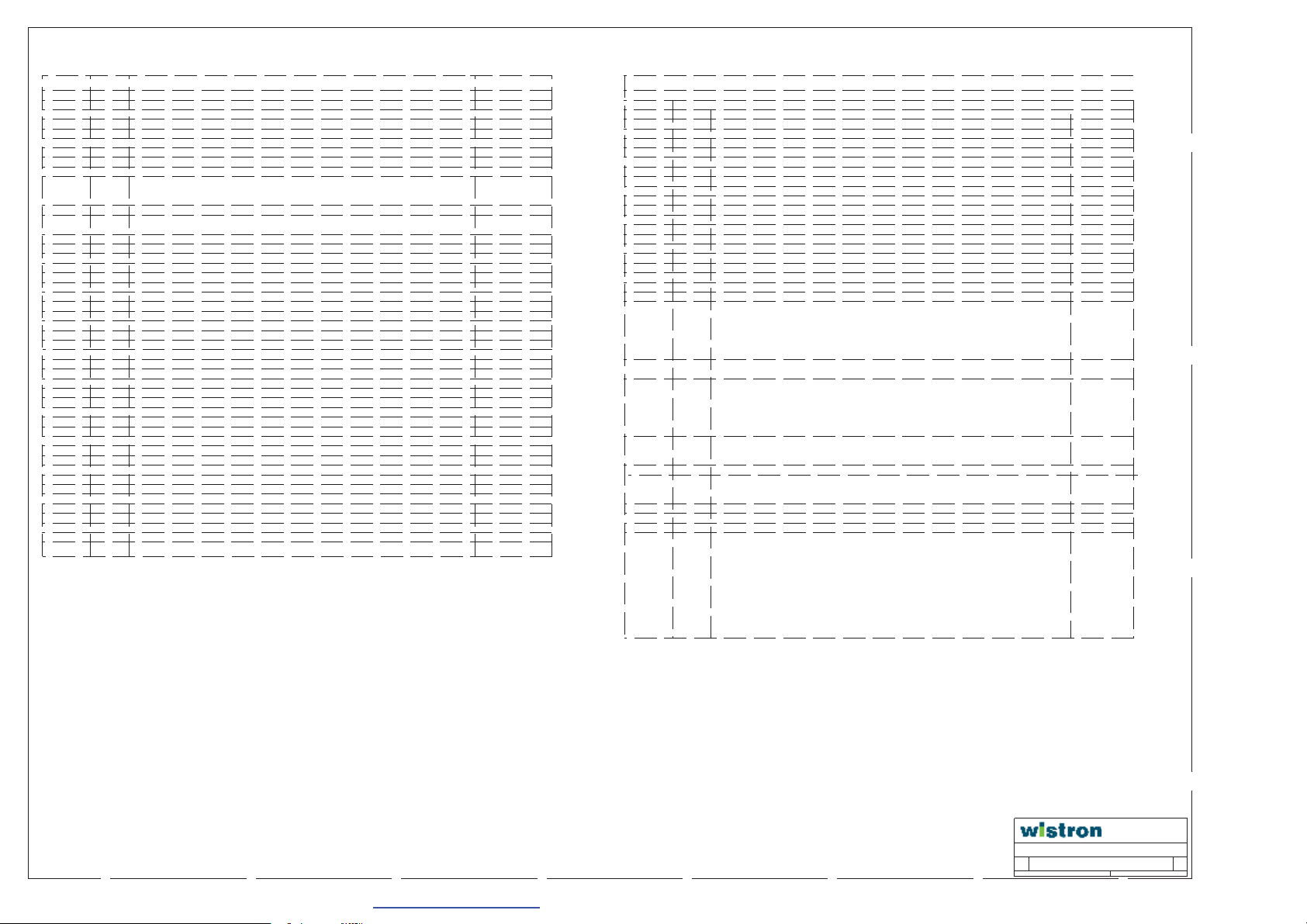

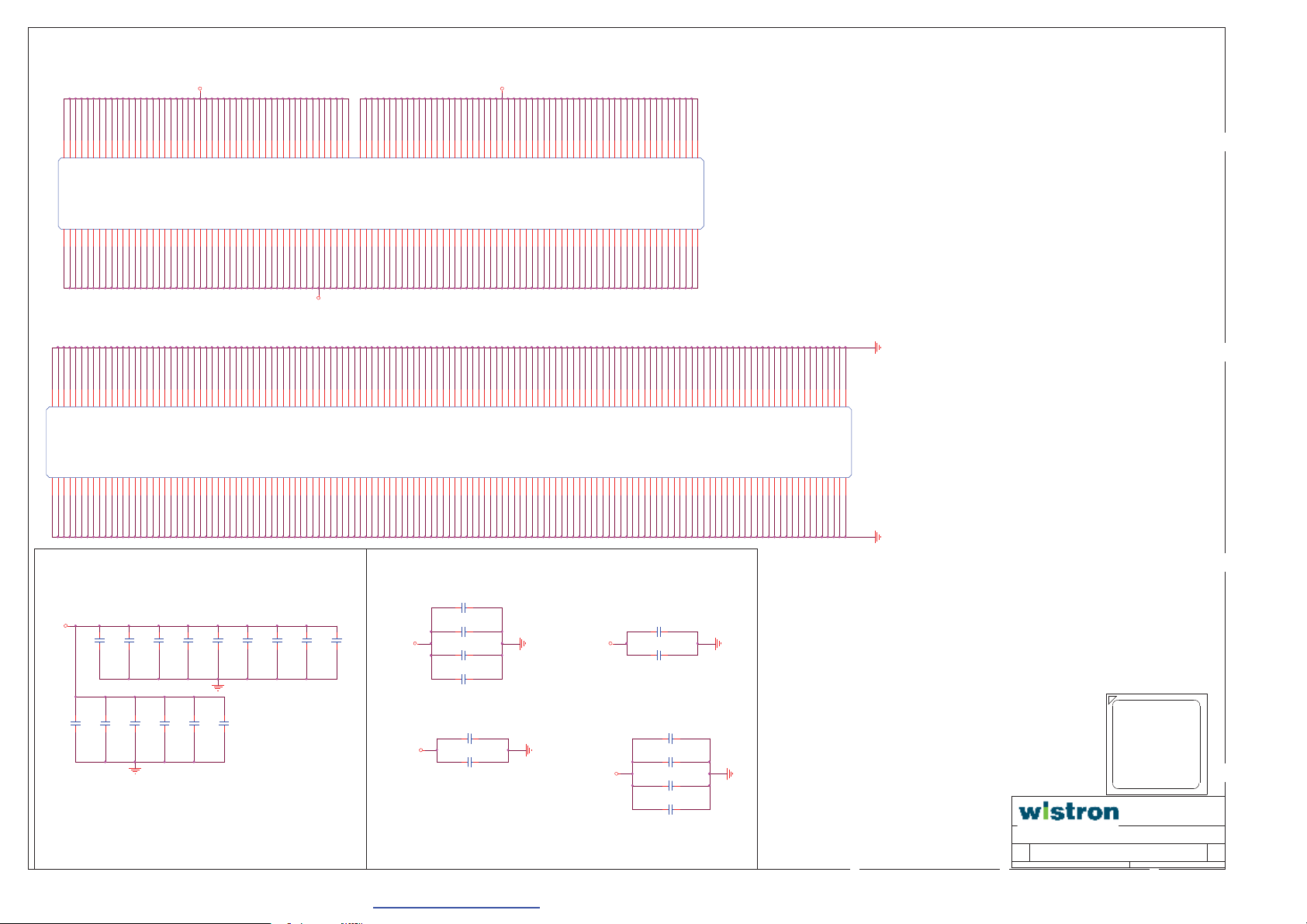

Cover pageSheet 1

Sheet 2

Sheet 3

Sheet 4 GPIO Table

Sheet 5

Sheet 6

Sheet 7

Sheet 8

Sheet 9

Sheet 10

Sheet 11

Sheet 12

Sheet 13

Sheet 14

Sheet 15

Sheet 17 TMDS Transmitter & conn

Sheet 18

Sheet 19

Sheet 21 M1573 PCI/RTC/AC97/LPC/MISC

Sheet 22

Sheet 23

Sheet 24 Clock GEN

Sheet 25

5

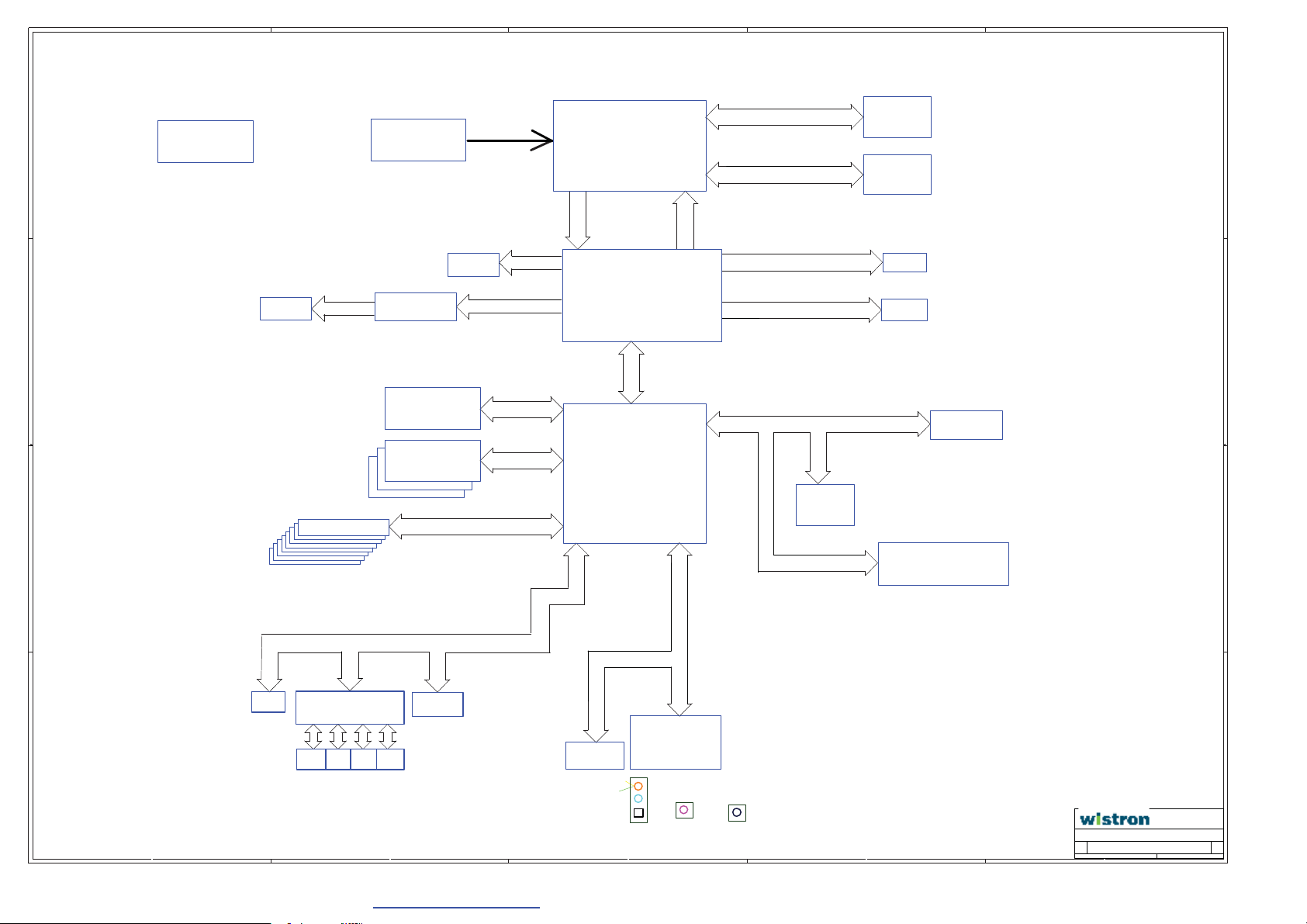

Block Diagram

POWER DELIVERY CHART

Rev Notes

Althon64/64FX HT I/F

Althon64/64FX DDR I/F

Athlon64/64FX Misc

Althon64/64FX PWR & GND

Unbuffered DDR 1,2

SSTL-2 Termination Res

RS482M-HT LINK & DVO I/F

RS482M-DAC/LVDS/MIS/CLK/PM

RS482M-PCIE & A-Link

RS482M-POWER and Ground

LVDS ConnSheet 16

TV OUT Conn

VGA FILTER/CRT CONN

M1573 ALinkSheet 20

M1573 SATA & IDE I/F

M1573 USB/AC97/RESUME

IDE and SATA CONN

4

Sheet

Sheet 26

Sheet 27

Sheet 28

Sheet 29

Sheet 30

Sheet 31

Sheet 32

Sheet 33

Sheet 34

Sheet 35

Sheet 36

Sheet 37

Sheet 38

Sheet 39

Sheet 40

Sheet 41

Sheet 42

Sheet 43

Sheet 44

Sheet 45

Sheet 46

Sheet 47

Sheet 48

Sheet 49

Sheet 50

3

USB CONN

BIOS /Battery RTC

SIO DM1737 & FDD Conn

KB/MS PS2 CONN

COM & PARALLEL PORT

TPM

R5C842-PCI I/F and 1394

R5C842-MDIO I/F and CB I/F

CardBUS Slot and 1394 Conn

MS/SD/xD CARD Conn

PCI Riser Slot

LAN

AUDIO CODEC

AUDIO CONN

Front Board Header & Buzzer

LED/FAN/PWRBTN

USBPOWER&PWRCTL

Dual_5V_3.3V_1.8V & 3.3VSB

VDDIO and DDRVTT Regulator

VCC18_RUN & VCC12_RUN

VCC_Core(ISL6559)

PWR Sequence controller

ATX 24Pin conn

Screw Hole

CLK MAP

2

<Core Design>

Wistron Incorporated

21F, 88, HsinTai WuRd

Title

Cover Page

Size DocumentNumber Rev

Custom

J361Y RS48 2 + M 1 5 7 3

Date: Sheet

Hsichih, Taipei

1

of

150Thursday, June 16, 2005

1A

PDF created with pdfFactory trial version www.pdffactory.com

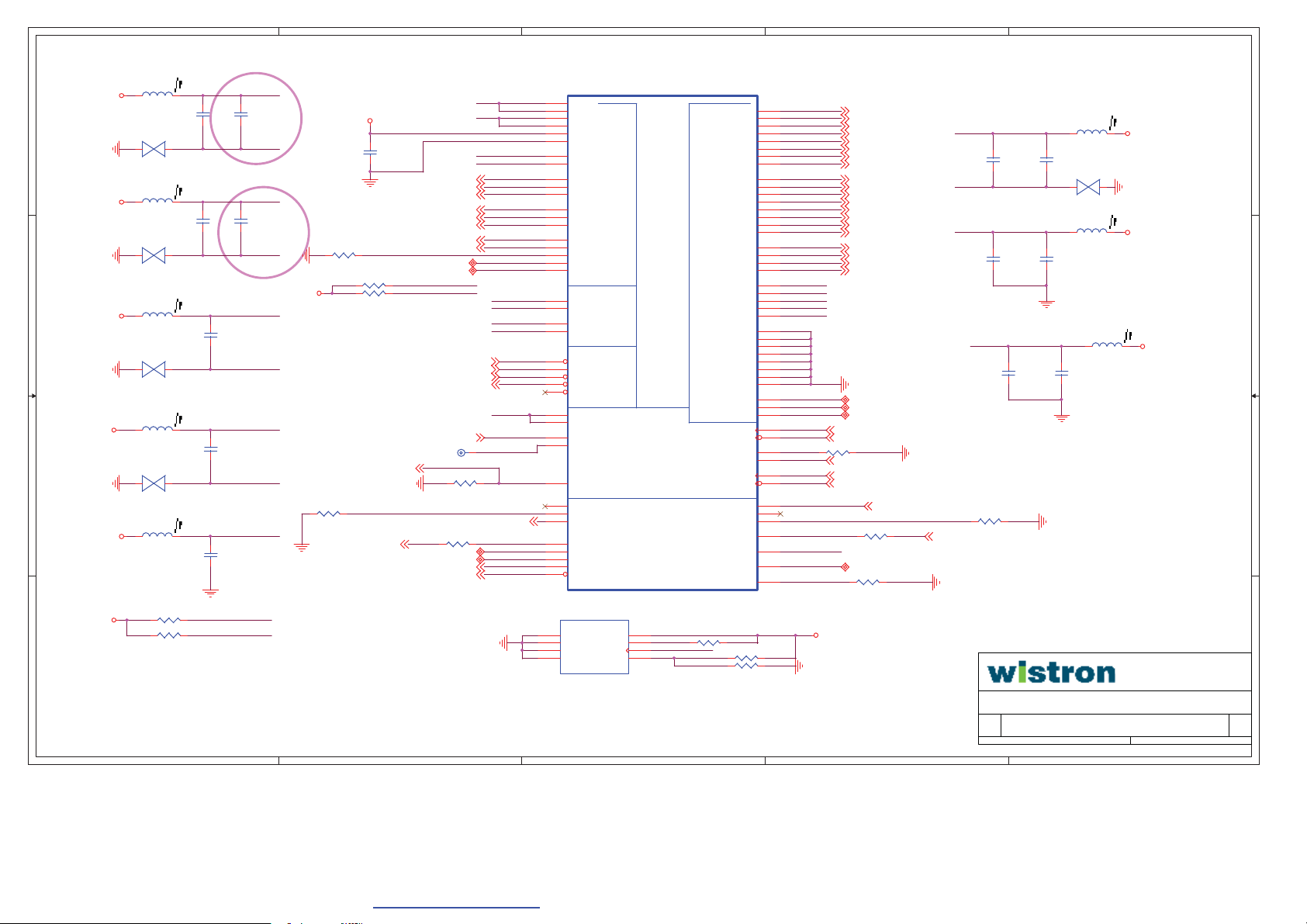

Page 2

5

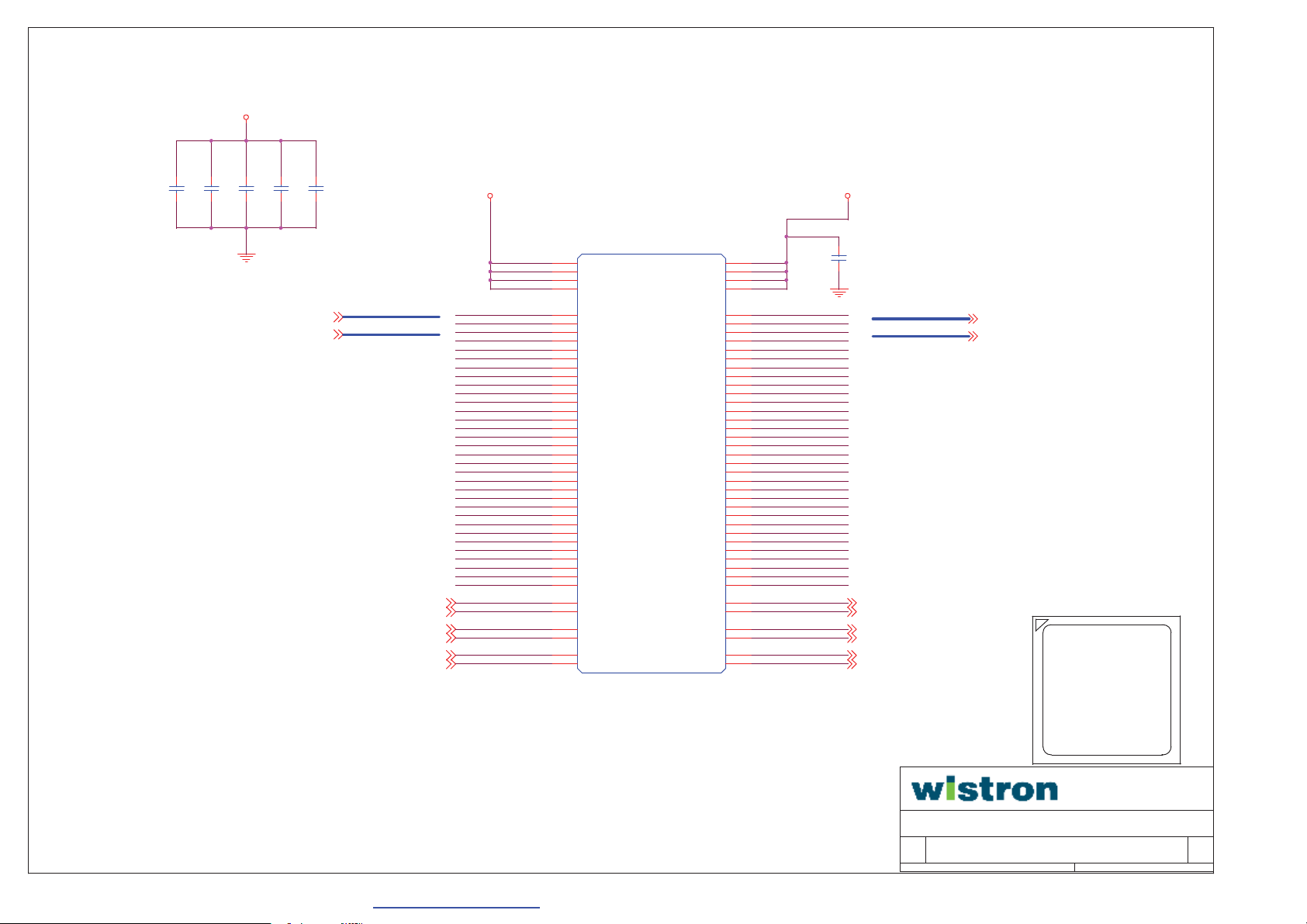

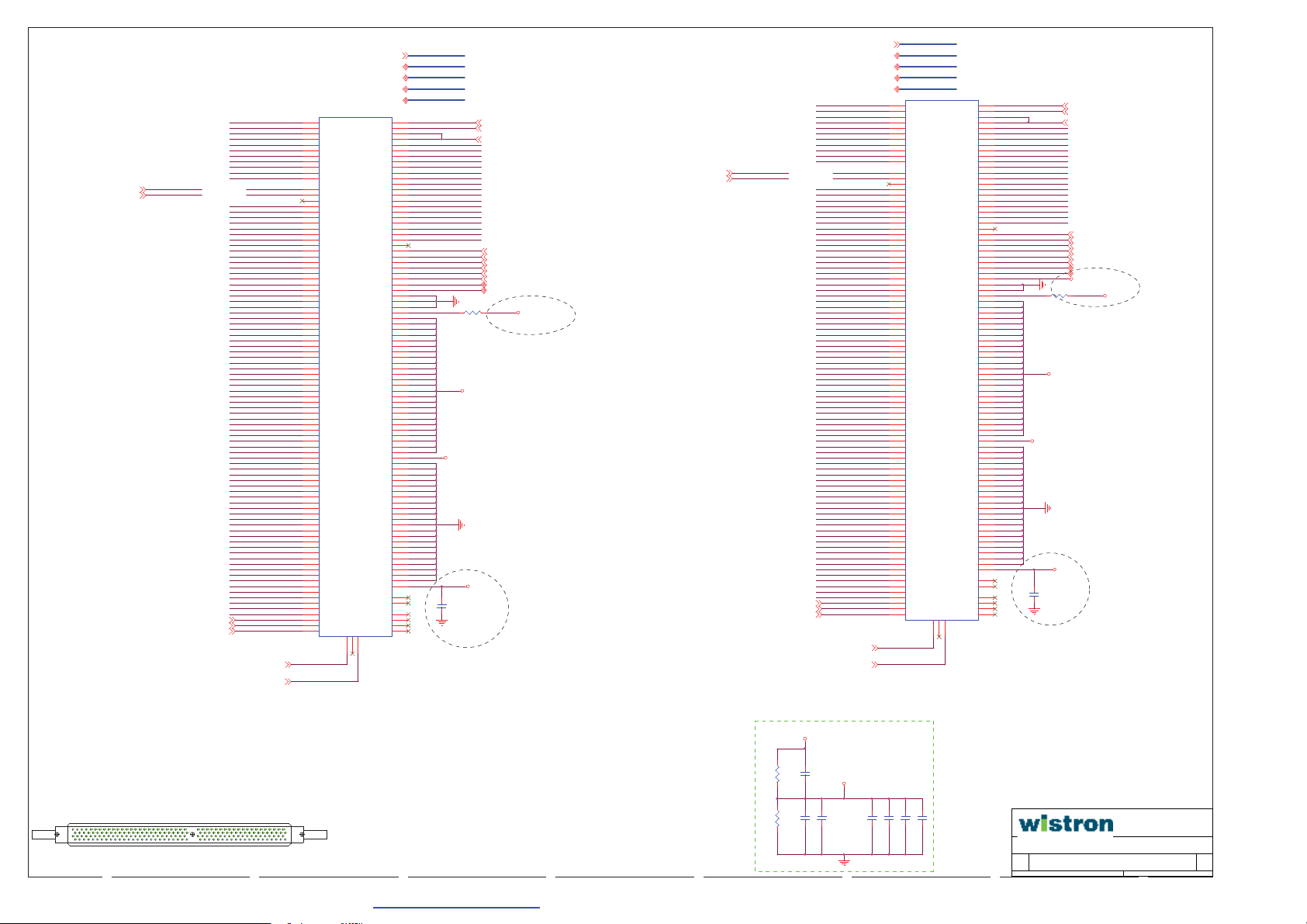

Block Diagram

4

3

2

1

http://hobi-elektronika.net

B

ExternalClock Gen

D D

CLK GEN

ICS951412

VRM ISL6559

4Phase

VCORE

AMD Althon64/64FX

(Socket uF CBGA939)

Processor

DDR266/333/400

DDR266/333/400

HyperTransport

- 16x16/1GHz

OUT

BW:2000MT/s or

RS482M only

LVDS

TMDS

C C

CH7301C-T

Parallel ATA

Devices

12 bits DVO I/F

1 Channel

IDE I/F

4000Mbyte/s

ATI NB RS482/482M(LVDS)

HyperTransportLIN0 CPU I/F

Integrated Graphics -CRT/TV-out/LVDS

ExternalGraphics-DVO

1 16x PCIE I/F

A-Link1X2 Lanes (Up to 4 Lanes)

PCI-E 4X1 Lanes

South Bridge - ULi M1573

IN

A-LinkExpress I/F

1X2 Lanes

Canextendup to

1X4 Lans

RGB

Y/C/COMP S-Video out

andY/Pr/Pb HDTV

PCI2.3 - 33MHz

Serial ATA

Devices

3Channel

SATA 1.0

8Ports

REAR 2*2

B B

Front 1*2

Internal 2*1

USB Port

USB 1.1/2.0 I/F

A-Link1X2 Lanes(Up to 4 Lanes)

SATA 1.0 4 ports

IDE Bus 2-Channel

AC'97/HD Aud i o I/F

USB2.0-8 ports

LPC I/F INT RTC

PCI I/F

AC'97 2.3/HD Audio I/F

Ricoh R5C842

Channel A

-DIMM1

Channel B

-DIMM2

CRT

TV-OUT

PCIRiser

Slot

PCMCIA/PCcard-2 Slots

SD/MMC/MS/MS Pro/xD

1394 *2

BCM4401/5705M/5788M

10/100 and GigaLAN

dual-layout

LPC BUS

TPM

SMSC LPC SIO

DM1737

FLASH

BIOS

AC'97 Codec

ALC655/ALC250

A A

5

FDD

LPT

PS2

KB/MS

Serial

Port*2

Port A : Line_OUT(Orange/Consumer)

Port A : Line_OUT(Lime/Corporate)

4

RiserMR

Slot

Port B : Line_IN(Light Blue)

Port C : SPDIF (Black)

HD Codec

ALC880/ALC260

MIC IN : Pink

Front Audio

Rear

port 1

Audio

port

3

HEADPHONE OUT :

BLACK

Front Audio

port 2

<CoreDesign>

Title

Block Dia gram

Size Document Numbe r Rev

Custom

J361YRS482+M1573

2

Date: Sheet

1

Wistron Inc orporate d

21F, 88, HsinTai WuRd

Hsichih,Taipei

of

250Thursday,June 16, 2005

PDF created with pdfFactory trial version www.pdffactory.com

1A

Page 3

5

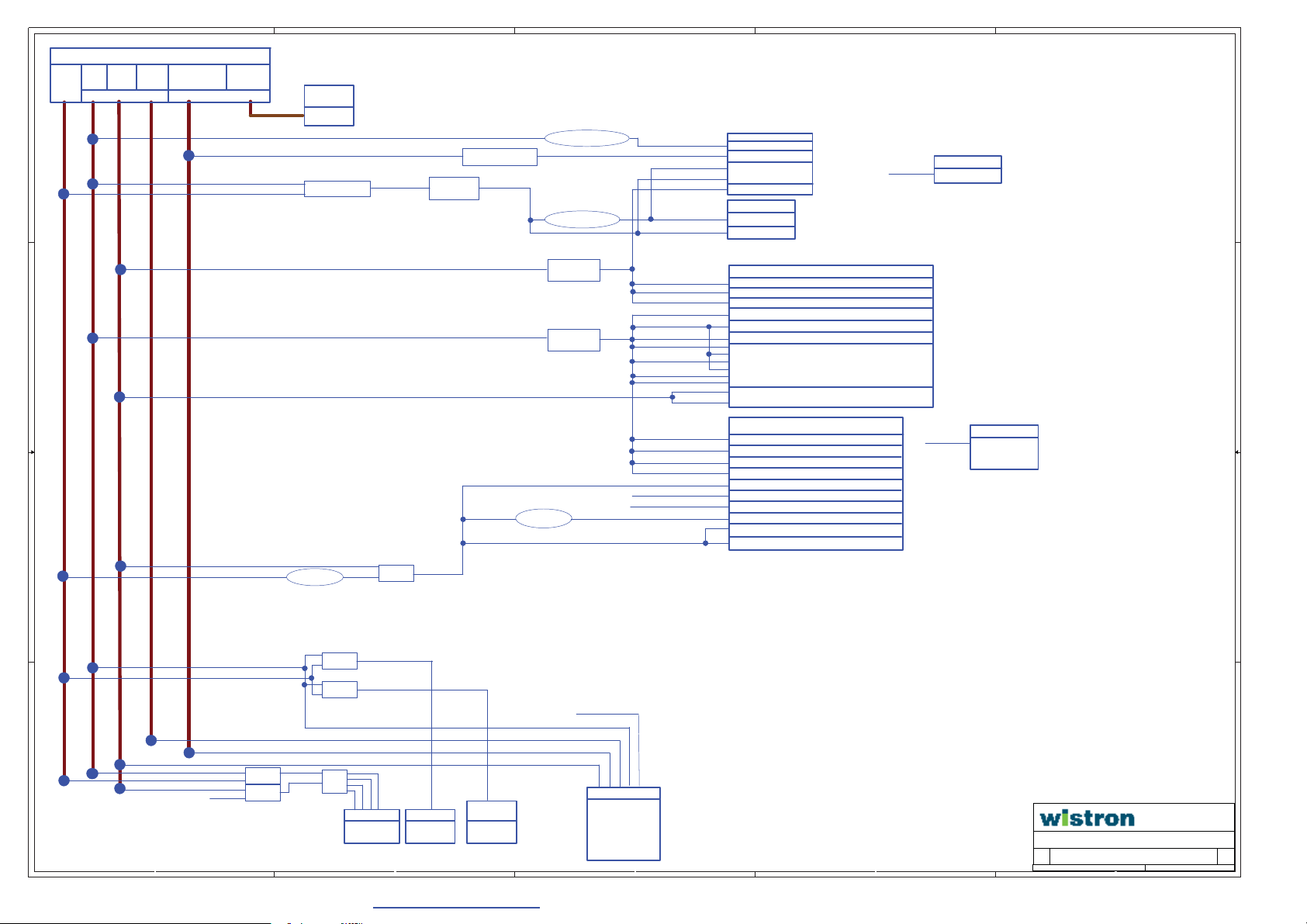

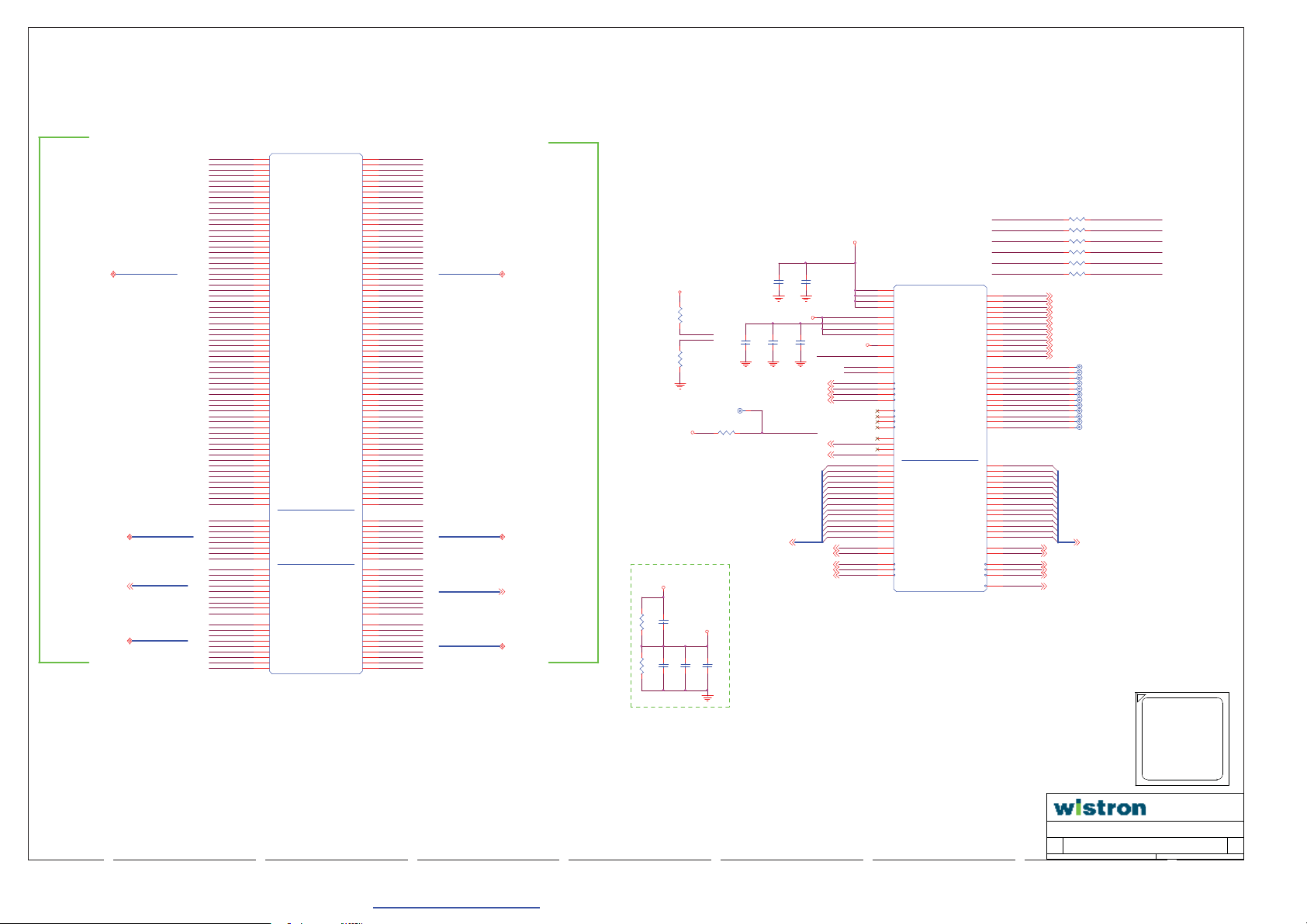

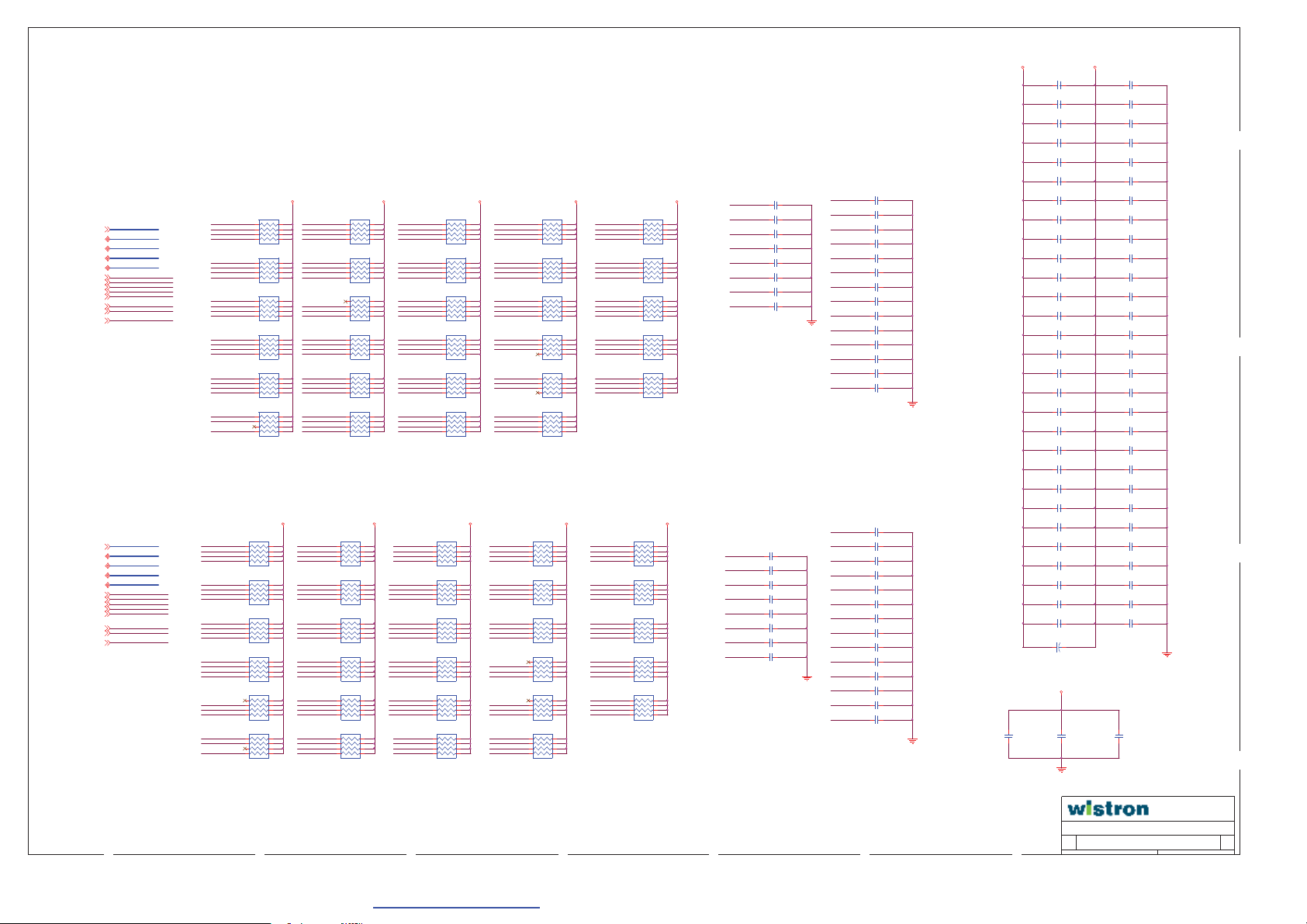

Power Delivery

AcBel Power Supply ACPI4PC49

VCC3_3

VCC5

VCC5SB

+/-5%

+/-5%

10.7A

2.5A

D D

+/-5%

7.46A

Total 54.8W Max

VCC-12V

+/-5%

0.1A

VCC12/+12Vcore

+/-5% 10.7A

Total 180W Max

+12VL

+/-5%

4.0A

VCC12VL (S0, S1)

VCC5 (S0, S1)

VCC5SB

(S0,1,3,5)

6Pins Panel

power conn

VCC12VL

4.0A

+12Vcore (S0,S1)

NMOS PHD45N03LTA

PMOS AP20P02J

4

DDR_VCC5_DUAL

(S0,1,3,5)

3

http://hobi-elektronika.net

P

VDDIO 2.6V SW

REGULATOR

APW7057KC

VCC5 (S0, S1)

33mA

VRM SW REGULATOR

ISL6559

VCC2.5V_SUS (S0,S1,S3)

12.27A

2.5V LDO APL1087

VCC_CORE(S0,S1)

80A

DDRVTT 1.3V

APL5331U5C

VDDA (S0,S1)

DDR_VTT (S0,S1,S3)

VCC2.5V_SUS (S0,S1,S3)

1.25A

VLDT (S0, S1)

DDR_VTT (S0,S1,S3)

VCC2.5V_SUS (S0,S1,S3)

8.52A

0.19A

0.5A

2.31A

ATHLON64 CP U

VDDA 2.5V 33mA

VDDCORE 0.8-1.55V 80A

DDR400 MEM I/F VTT 1.3V

0.19A, VDDIO 2.6V 1.25A

VLDT 1.2V 0.5A

DDR400DIMMs

VTT 1.3V 2.31A,

VDDIO 2.6V 8.52A

2

VCC3_3(S0,S1)

400mA

CLK GEN

ICS953803-LF

CLK_3.3V 400mA

1

VCC3_3 (S0, S1)

C C

B B

A A

5

VCC5 (S0, S1) 2A

VCC5SB (S0,1,3,5)

VCC3_3 (S0, S1) 2A

VCC3_3SB

(S0,1,3,5)

VCC5SB

(S0,1,3,5)

VCC5 (S0, S1)

VCC5SB (S0,1,3,5)

CEM9939A

CEM9939A

VCC3_3SB

APL1085

VCC5_ Dual_842

(S0,1,3, 5)

VCC3_ 3Dual_842

(S0, 1,3,5)

CEM9939A

CEM9939A

R5534V

VCC3_3SB

(S0,1,3,5)

AVPP

BVPP

PCMCIAx2Slot

xVCC Min

2.0A

VCC3_3Dual

CEM9939A

(S0,1,3,5)

VCC5_USB_R

2A

(S0,1,3)

AVCC

BVCC

USB x4 Rear

VCC5_USB_R VCC5_USB_F

2.0A

4

VCC5_USB _F

(S0,1,3)

VCC5 (S0, S1)

2A

VCC3_3 (S0,1)

USB x2 Front

& x2Header

2.0A

VCC12_RUN 1.2V

SW REGULATOR

APW7057KC

VCC18_RUN 1.8V

SW REGULATOR

APW7057KC

VCC 1.8_DUAL

APL1087

VCC12 (S0,1)

VCC3_3(S0,S1) 0.3A

VCC3_3Dual

(S0,1,3,5)

VCC5 (S0, S1)

VCC-12 (S0,1)

PCI Slot Max25W

5V

3.3V

12V

3.3Vaux

-12V

8.25A

VDD_CORE_N B( S0,S1) 5A

4.75A

VDD18 (S0, S1)

AVDDQ(S0,S1)

LPVDD(S0,S1 )

LVDDR18A(S0,S1)

PLLVDD/HTPVDD (S0,S 1)

1.3A

SBVCORE_1D8V(S0, S1)

PCI E_1D8V(S0,S1)

PCIE_VDDA(S0,S1)

SATA_1D8V(S0,S1)

VCC3_3Dual (S0,1,3,5)

VCC_CORE(S0,S1)

VCC3_3(S0,S1) 200mA

3V_DUAL_IO(S0,1,3,5)

5.0A

7.6A

0.5A

0.375A

0.1A

3

VLDT (S0, S1)

VDDR3(S0,S1)

AVDD(S0,S1)

NB ATI-RS480M (Max ?mW)

0.5A

VDDHT 1.2V/0.5AI/O Power for HT I/F

VDD_CORE 1.0~1.2V/5A for NB ASIC core power

2.25AVDDA12(S0, S1)

VDDA12 1.2V/2.25A for PCIEI/Fmain power

2AVDD_DVO (S0, S1)

VDD_DVO 1.8V/2A for DVOI/FIO power

0.2A

VDD_18 1.8V/0.2A for CORE transform power

0.75AVDDA18(S0, S1)

VDDA_18 1.8V/0.75A for PCIEI/F output driver I/O POWER and PLL

AVDDQ1.8V for Band gap ref voltage for DAC

AVDDDI 1.8V Digital power for DAC

LPVDD 1.8V for LVDS PLL

LVDDR18D 1.8Vfor LVDS Digital POWER

LVDDR18A 1.8V for LVDS Analog POWER

PLLVDD/HTPVDD 1.8V for PLL&HT PLL

VDDR3 3.3V for 3.3VI/O POWER

AVDD 2.5V or 3.3V for DACAnalog power

SB ULi-M1573

(Max 3.6W)

0.6A

VDD18M_CORE1.8V/0.6A for main cor e power

0.4A

PCE_VDD/PCE_VTT1.8V/0.4A for PCI-EPHYpower

0.15A

PCE_VDDA 1.8V/0.15A for PCI-E PLL analogpower

0.15A

SATA_18M1.8V/150mA for SATA analog power

VDD33R_RTC 3.3V RESUME power f or RTCPOKcircuit

10mA

VDD_CPU 1.2V/10mA post driver power for CPU I/F

VDD33M_IO3.3V/0.2A for 3.3V Driving I/Fpower

100mAVCC18_DUAL(S0,1,3,5)

VDD18R_CORE 1.8V/0.1A for 1.8V RESUMEpower

100mA

VDD33RUSB 3.3V/0.1A for RESUME power forUSBPHY

10mA

VDD33R_IO 3.3V/ 10mA f or RESUME power for 3.3V driving I/F

Ricoh R5C842

VCC3_3(S0,S1)

2

160mA

Power Supply

Current, operating

Max 160mA

<Core Design>

Title

Power Delivery

Size Document Number Rev

Custom

J361Y RS482+M1573 1A

Date: Sheet

1

Wistron Incorporated

21F, 88, Hsin TaiWu Rd

Hsichih, Taipe i

of

350Thursday, June 16, 2005

PDF created with pdfFactory trial version www.pdffactory.com

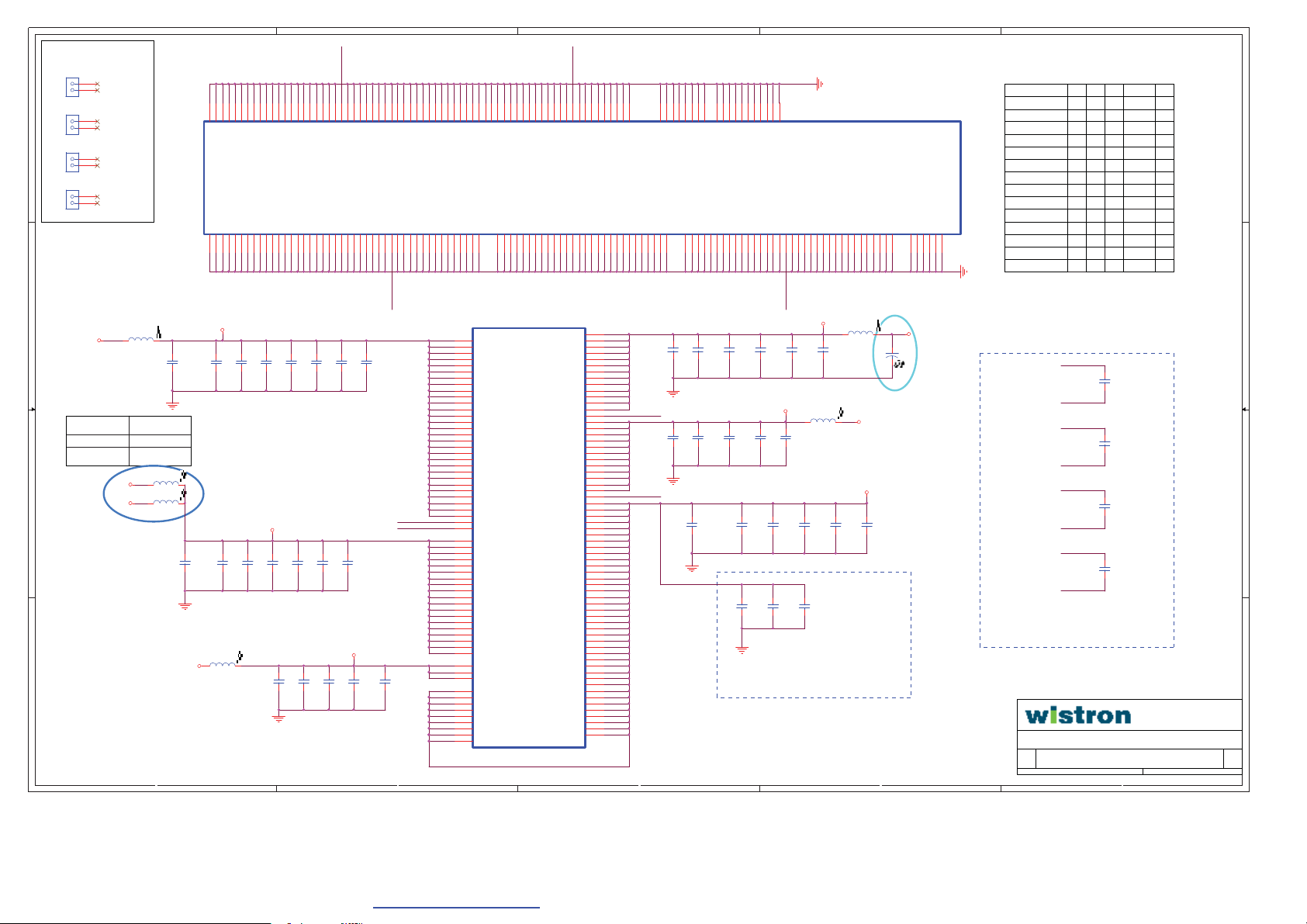

Page 4

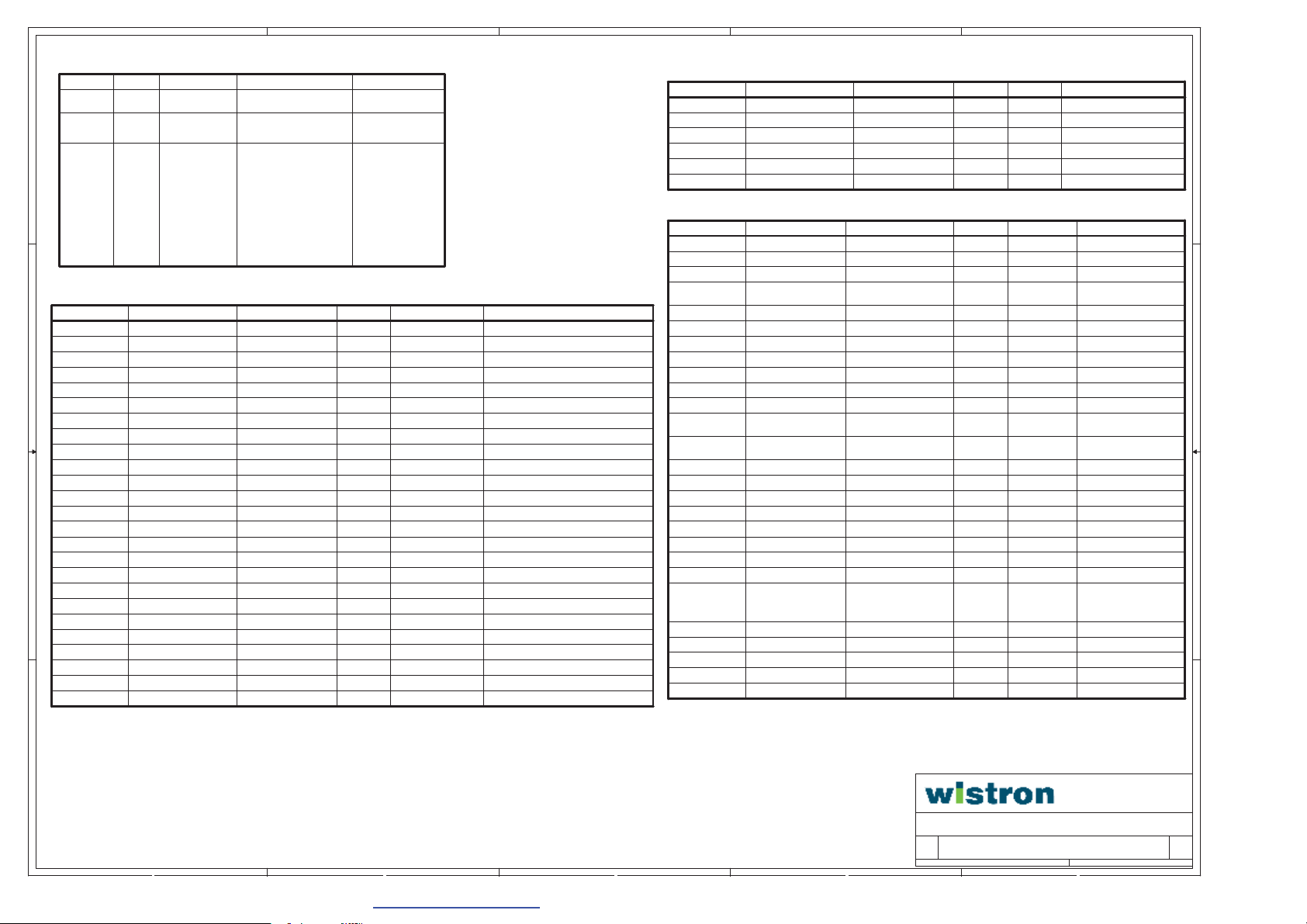

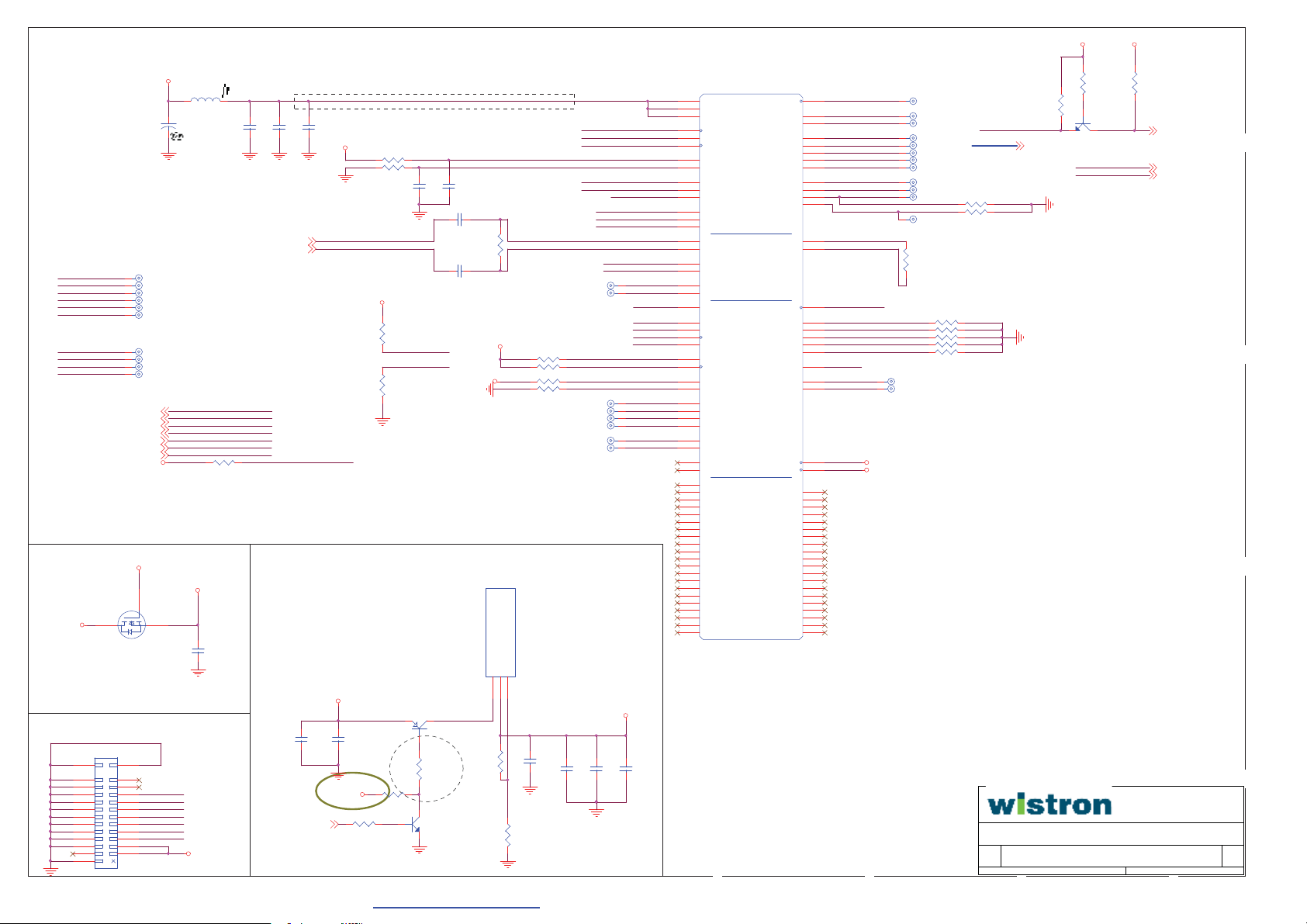

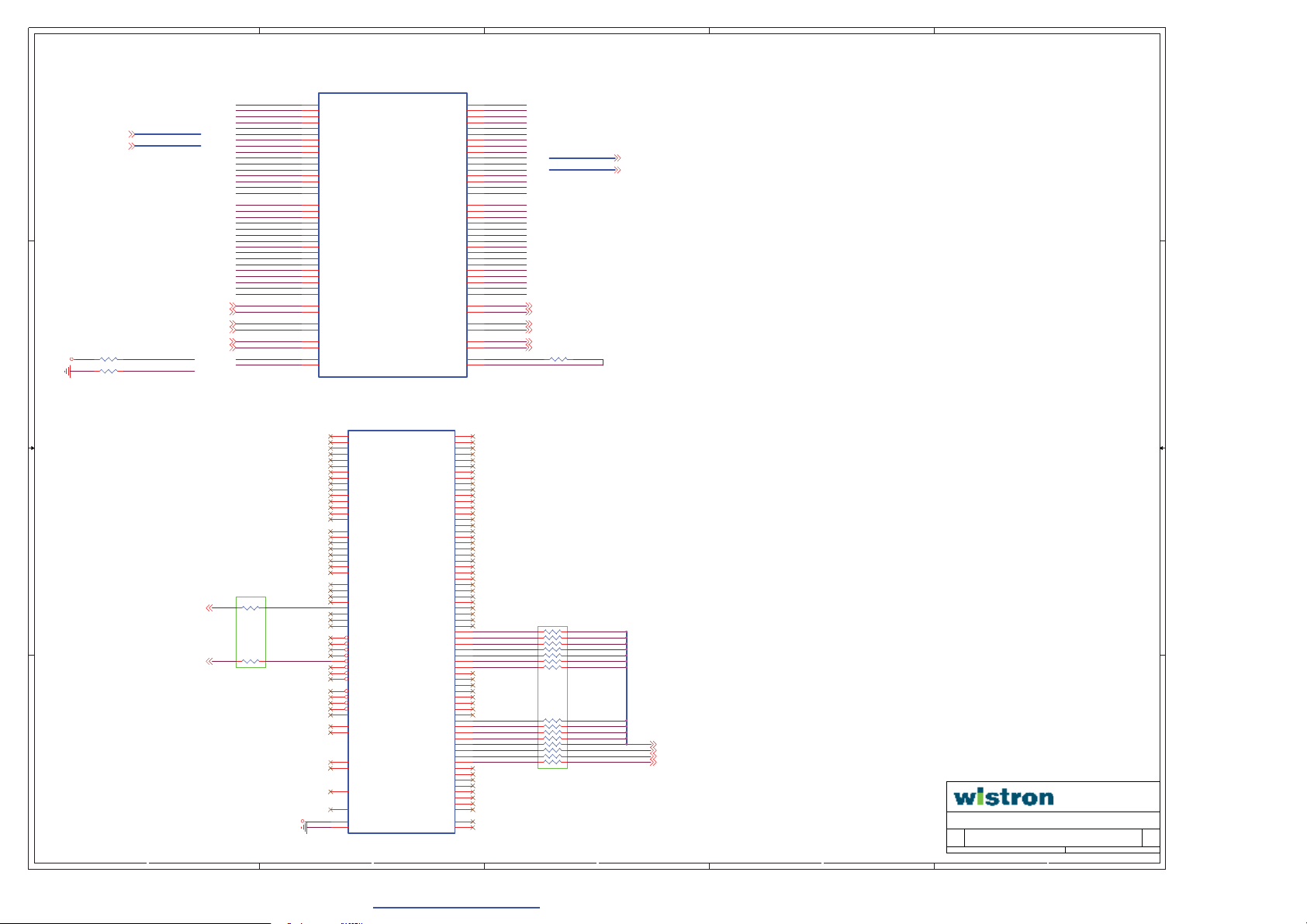

PME event

output

5

PCI

Device

R5C842

PCI

RISER

D D

PCI LAN

IDSEL

AD21

AD19

AD20

AD22

GNTJ/REQJ

PREQJ3/PGNTJ3

PREQJ0/PGNTJ0

PREQJ1/PGNTJ1

PREQJ4/PGNTJ4

IRQ

PIRQJD,A,B,C

PIRQJA,B,C,D

PIRQJB,C,D,A

PIRQJE

SMSC DM1737

GPIO #

GP10

GP11

C C

GP12

GP13

GP14

GP21

GP22

GP27

GP33

GP36

GP37

GP40

GP42

GP43

GP50

B B

GP51

GP52

GP53

GP54

GP55

GP56

GP57

GP60

GP61

Mux Function

RST_IDE*

LAN_DISJPCIRST_OUT1

SLP_S1_S5_L*

SUSLED*PCIRST_OUT4

KBDATA

KBCLK

MSDATA

MSCLK

KBRST*

A20GATE

IO_PMES3#

IO_PMES5#

RI*2

DCD*2

RXD2

TXD2

DSR*2

RTS*2

CTS*2

DTR*2

TVLED*

LCDONJ_SIO

4

Active Status

LOW

LOW

LOW

I/O

O

MAIN (VCC)

AUX (VTR)

O

O

AUX (VTR)

AUX (VTR)

O

O

AUX (VTR)

MAIN (VCC)

I

MAIN (VCC)

I

I

MAIN (VCC)

MAIN (VCC)

IGP32

I

MAIN (VCC)

I

MAIN (VCC)

MAIN (VCC)

I

MAIN (VCC)

O

AUX (VTR)

O

O

AUX (VTR)

MAIN (VCC)

I

MAIN (VCC)

I

MAIN (VCC)

I

I

MAIN (VCC)

I

MAIN (VCC)

I

MAIN (VCC)

MAIN (VCC)

I

I

MAIN (VCC)

AUX (VTR)

O

O

AUX (VTR)

3

2

1

http://hobi-elektronika.net

ATI RS482/482M

GPIO #

DFT_GPIO0

DFT_GPIO1

DFT_GPIO2

DFT_GPIO3

Mux Function

LOAD_ROM_STRAPS#

GPIO Function

TV_SWITCH

D_PLUGDET

DFT_GPIO4

DFT_GPIO5

ULi M1573

GPIO #

RUNGPIO0

LOAD_MEM_STRAPS#

Mux Function

GPIO Function

RUNGPIO1

RUNGPIO2

RUNGPIO3

POWERGPIO Function

Active Status

Low

Low/Default high

RUNGPI18 ACB_BITCLK BOARD_ID_0 I VDD33M_IO

RUNGPI11 VOL_UP# BOARD_ID_1 I VDD33M_IO

RUNGPI12 VOL_DOWN# BOARD_ID_2 I VDD33M_IO

MO_DET

RUNGPI13 VOL_MUTE# BOARD_ID_3 I VDD33M_IO

Low@S0/ S1/ S3 / High@S4/ S5

Low

RUNGPI9 CLKRUN# CRT_TMDS_DISJ O VDD33M_IO HIGH

RUNGPO[13] CPUHI# Blueled* O VDD33M_IO HIGH

RUNGPO[16] IGNNE# Blueled02* O VDD33M_IO HIGH

RUNGPO[19] NMI HDDLED O VDD33M_IO HIGH

RUNGPO[21] SMI# Blueled03* O VDD33M_IO HIGH

LCD_VID0

Low

SATA_GPI1

SATA_GPI2

LCD_VID1 VDD33M_IO

LCD_VID2

SATA_GPI3

PME event output

PME event output

SATA_GPO0

SATA_GPO1

FlashROM_WP

SATA_GPO2

SATA_GPO3

RSMGPIO0

PWRLED*

USBPWR_Ctrl

RSMGPIO1

ACPI_S3

842HWSPNDJ

IO_PMES3#SMBALERT#

High / push-pull

Low/ S5 wake up event

RSMGPIO3

RSMGPI10

SLPBTN# IO_PMES5#

I/O

I

I

O

I

I

I

I/O

I

O

POWER

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

POWER

VDD33M_IOIDE_P

VDD33M_IO

VDD33M_IO

I

VDD33M_IO

I

VDD33M_IOSATA_GPI0

I

I

VDD33M_IO

I

VDD33M_IO

VDD33M_IO

O

O

VDD33M_IO

VDD33M_IO

O

VDD33M_IO

O

VDD33R_IO

O

VDD33R_IO

OACPILED*

O

VDD33R_IO

O

VDD33R_IO

VDD33R_IO

I

IRSMGPIL[0] VDD33R_IO

Active Status

Low

1:D-Video

0:S-Video

0: HDTV connected

1: HDTV unconnected

Low

Active Status

High

LOW

0: MO connected

1: MO

unconnected

LOW

High/Default L OW

LOW

LOW

Consumer:

S3->H, S4/S5->L

Corporate:

S3/S4->H, S5->L

HIGH

S3:HighRSMGPIO2

High

PME event input

PME event input

A A

5

4

3

2

<Core Design>

Wistron Incorporated

21F, 88, HsinTaiWu Rd

Title

GPIO Table

Size Document Number Rev

Custom

J361Y RS482+M1573

Date: Sheet

Hsichih, Taipei

450Thursday,June 16, 2005

1

of

1A

PDF created with pdfFactory trial version www.pdffactory.com

Page 5

8

Rev. Notes

R

7

6

5

4

3

2

1

http://hobi-elektronika.net

Rev Description PageDATE

3/10 SA_V1.0

SA_V1.1 Add Board_ID_[3..0] setting 22

D D

3/15 Modify VDD_DVO power for RS482 revA11 15

SA_V1.2 Change L33 223/15

SA_V1.33/16 Modify DLINE circuit 18

SA_V1.43/16 MoveR664 and R97 to Page17. Delete R665 and R666 13,17,19

Twocopper pure for VTT fill - at least 100mils wide/Change DDR_VTT_CPUas DDR_VTT 7,8

C C

SA_V1.63/21 SWAP USB Port 26

SA_V1.8 Modify LAN Disable circuit 373/22

3/23 Add 6559_Common Ground 46SA_V1.9

SA_V1.10

SA_V1.11 Net Swap3/24

SA_V1.123/25 Add Twocapaci tors for EMI 38

SA_V1.13 Change Q70 to 3904 NPN BJT 42

SA_V1.163/30 Rename Reference and swap nets

3/31 SA_V1.17 Connect H7 to AGND

SA_V1.184/06 Add CLOCK MAP 50

B B

NOTE :

Release Schematic

Add PIRQ#[E:H] pullhigh 36

Add CN41 28

HW strapping setting 13,21,22,23

Modify Front HP OUT Mute circ uit 39

24Modify Net REFCLK0_1 and REFCLK0_2

Change R92 to 2.4K ohm 17

Modify DVO_IDCKN and DVO_IDCKP 17

ModifyTMDSHotPlugcircuit 17

Modify TV-out I2C circuit 18

Modify DVO_VREF circuit 17

Modify VRMCircuit (Vendor suggestion) 46

Change M1573 HW strapping resistors to 1K ohm 21

Change R536 and R538 to 1K ohm and change R554 to 5.1K (Vendor suggestion) 46

Modify SB&NBPOWER Good circuit 47

ModifyTMDSHotplug circuit 15

Delete R669 and R670 18

DeleteTC86 32

Modify DLINE circuit 18

Change M1573 to RevA1D 20-23

Add LAN Disable circuit 37

Delete TC39 for Extra 4 CPU FANSINK screw hole3/19 SA_V1.5 46

Change C763 to a small size 40

Modify FJ's checklist items

SMBCLK and SMBDATA (SIO Page) 28SA_V1.7

Modify SUSLED* circuit 41

Modify NB_RST*circ uit 20

Change PCI RST circuit from VC C3_3D UAL driven to VCC3_3SB

USE CLKRUN# of M1573(RUNGPO9) to disable CRT and TMDS

Modify GPIO arrangement

Add another pair of SM bus dedicate for CLK GEN and DDR

47Connect ASIC8M_CPU_RSTto LDTREST#3/14

14Change R74 and R75 to 8.25K and 82.5 ohm (ATI PA_RS4X0F4.pdf

Rev Description PageDATE

SB_V2.0

0422 Modify All SA P/R rework items and FJ GFX_Feedback

SB_V2.10426 Modify R354 and R744 and FJ GFX Feedback ver.0427 47

0427 Swap ACZ_SDIN0and ACZ_SDIN1 at SB side 23

SB_V2.2 LO_Rcan't be connected with Mute_LO. 39

Add R746/R747/R748 23

Change C267 to 0.018uF and R418 to 60.4 ohm 44

Add R749 27

Modify LAN_RSTJsignal 37

RemoveJP2 and around circuit

Change Pin assignment of CN39

Modify LCD PW RON cir cuit 37

Add USB ESD IC 26

Add COMMON GND fo r SW r egulator 44,45

Change TC35 to 220uF

Modify SUSLED circuit 41

ModifyFAN Tach circuit 41

Modify GPIOassignment forLED function

Modify PCI Riser IDSEL 36

Add FlashRom_write protect functi on

0508 SB_V2.5 Modify USBPWR control circuit 42

0509 SB_ V2.6 Modify VDDA_2.5V_CPU Enable circuit 08

SB_V2.70510 Remove Q73 and ACZ_RST_CRL* 40

0511 SB_V2.8 Add SLP_S4_H to control USB power 23/42

SB_V2.10 USE CRT_TMDS_DISJ to do mute func ti on 40

SB_V2.110512 Modify VLDT_EN circuit 45

0517 SB_V2.13 Change Q105 to FET(2N7002)

0524 R129 unmount, L66 change to 63.R0004.151

0525 R59 R777 change to 0 ohm, Q103 Q15 change to 2N7002 41

Add Two more GPIO pin for IO_PMES3# and IO_PMES5#

Modify SUSLED circuit 41

Modify TVON_Plugcircuit 41

Modify All LED circuit 41

ModifyBIOS write protection circuti 27

Add a pull-up resistor on Mute# 40

Change R557 to 100K ohm

1394 port 0 and port1 swap

Modify All LED circuit 41

Modify USBPOWERcontrollercircuit 42

Add two 1K ohm between VCC5_USB_F"/VCC5USB_R" and GND 42

RemoveD31 and R517. Then change R518 from 1k-ohm to 0ohm and unmount as default.

[ESD for DDC]

Change R775.1 to VCC5 08

Change Q55 to 2N7002 and r emove R768SB_V2.9 41

Change BOM opti on for Audio function 40

Reserve3.3V pull-up forFansink 41

Modify USB power control circuit 42

Unmount R8SB_V2.120513 41

Change Boar d ID

Change C67 to X7R

Change R512 for Consumer/LCDPC ,Change R508 for Corpor ate

Change C88 and C413 to X5R

mount C691 and C692 24

R13 R14 change to 1Kohm , RN1change to 1K ohm 28

U58 U59 U60 change to 83.01293.0AE 26

Consuemr M/B: Board_ID[3..0] = "0001"

Corporate M/B: Board_ID[3..0] = "1000"

Small Qty M/B: Board_ID[3..0] = "0010"

21

40

46Add commonground near VRD low side MOSSB_V2.30505

29

17/19

28/41Modify TVON_PLUSE3.jpg

40

21

16

29

32 26

32 38

A A

PDF created with pdfFactory trial version www.pdffactory.com

8

7

6

<CoreDes ign>

Title

Rev Notes

Size Document Number Rev

Custom

J361Y RS482+M1573

Date: Sheet

5

4

3

2

Wistron Incorporated

21F, 88, Hsin Tai WuRd

Hsichih, Taipei

of

550Thursday,June 16,2005

1

1A

Page 6

8

Processor HyperTransport Interface

7

6

5

4

http://hobi-elektronika.net

P

VLDT

3

2

1

D D

12

12

C170

C179

SC4D7U10V-U

SCD22U10V3KX

C C

12

12

C172

SCD22U10V3KX

L0_CADIN_L[0..15]12

L0_CADIN_H[0..15]12

12

C171

C168

SCD22U10V3KX

SCD22U10V3KX

L0_CADIN_L[0..15]

L0_CADIN_H[0..15]

20/5/5/5/20 1"<x<12"

B B

At least 200mils for pure

and 20mils to pin

VLDT

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H112

L0_CLKIN_L112

L0_CLKIN_H012

L0_CLKIN_L012

L0_CTLIN_H012

L0_CTLIN_L012

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H0

L0_CTLIN_L0

20/5/5/5/20 1"<x<12"

VDD_HT0_IN

U34A

E2

VLDT_06

E1

VLDT_05

F1

VLDT_02

F2

VLDT_01

R5

L0_CADIN_H15

T5

L0_CADIN_L15

P3

L0_CADIN_H14

P4

L0_CADIN_L14

N5

L0_CADIN_H13

P5

L0_CADIN_L13

M3

L0_CADIN_H12

M4

L0_CADIN_L12

K3

L0_CADIN_H11

K4

L0_CADIN_L11

J5

L0_CADIN_H10

K5

L0_CADIN_L10

H3

L0_CADIN_H9

H4

L0_CADIN_L9

G5

L0_CADIN_H8

H5

L0_CADIN_L8

R3

L0_CADIN_H7

R2

L0_CADIN_L7

N1

L0_CADIN_H6

P1

L0_CADIN_L6

N3

L0_CADIN_H5

N2

L0_CADIN_L5

L1

L0_CADIN_H4

M1

L0_CADIN_L4

J1

L0_CADIN_H3

K1

L0_CADIN_L3

J3

L0_CADIN_H2

J2

L0_CADIN_L2

G1

L0_CADIN_H1

H1

L0_CADIN_L1

G3

L0_CADIN_H0

G2

L0_CADIN_L0

L5

L0_CLKIN_H1

M5

L0_CLKIN_L1

L3

L0_CLKIN_H0

L2

L0_CLKIN_L0

R1

L0_CTLIN_H0

T1

L0_CTLIN_L0

SKT-K8-2

VLDT_08

VLDT_07

VLDT_04

VLDT_03

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

At least 100mils to Capacitor

and 20mils to pin

VDD_HT0_OUT

AG4

AG3

AG1

AG2

V4

V3

Y5

W5

Y4

Y3

AB5

AA5

AD5

AC5

AD4

AD3

AF5

AE5

AF4

AF3

V1

U1

W2

W3

Y1

W1

AA2

AA3

AC2

AC3

AD1

AC1

AE2

AE3

AF1

AE1

AB4

AB3

AB1

AA1

U2

U3

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14L0_CADIN_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

VLDT-

12

C202

SC4D7U10V-U

L0_CLKOUT_H1 12

L0_CLKOUT_L1 12

L0_CLKOUT_H0 12

L0_CLKOUT_L0 12

L0_CTLOUT_H0 12

L0_CTLOUT_L0 12

20/5/5/5/20 1"<x<12"

L0_CADOUT_H[0..15]

L0_CADOUT_L[0..15]

20/5/5/5/20 1"<x<12"

L0_CADOUT_H[0..15] 12

L0_CADOUT_L[0..15] 12

A31A1

uPGA939

Top View

<Core Design>

A A

Title

Althon64/64FXHT I/F

Size Docume nt Number Rev

Custom

J361Y RS482+M1573

Date: Sheet

8

7

6

5

4

3

AL1

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

of

650Thursday, June 16, 2005

2

1

1A

PDF created with pdfFactory trial version www.pdffactory.com

Page 7

8

Processor DDR Memory Interface

P

7

6

5

http://hobi-elektronika.net

4

3

2

1

D D

MEM_DATA[63..0]10, 11

MEM_DATA[63..0]

C C

To DIMM Channel-A

MEM_CHECK _LO[7.. 0]10,11

MEM_CHECK _LO[7.. 0]

B B

MEM_DM_LO[8..0]10,11

MEM_DQS_LO[8..0]10, 11

MEM_DM_LO[8..0]

MEM_DQS_LO[8..0]

MEM_DATA63

MEM_DATA62

MEM_DATA61

MEM_DATA60

MEM_DATA59

MEM_DATA58

MEM_DATA57

MEM_DATA56

MEM_DATA55

MEM_DATA54

MEM_DATA53

MEM_DATA52

MEM_DATA51

MEM_DATA50

MEM_DATA49

MEM_DATA48

MEM_DATA47

MEM_DATA46

MEM_DATA45

MEM_DATA44

MEM_DATA43

MEM_DATA42

MEM_DATA41

MEM_DATA40

MEM_DATA39

MEM_DATA38

MEM_DATA37

MEM_DATA36

MEM_DATA35

MEM_DATA34

MEM_DATA33

MEM_DATA32

MEM_DATA31

MEM_DATA30

MEM_DATA29

MEM_DATA28

MEM_DATA27

MEM_DATA26

MEM_DATA25

MEM_DATA24

MEM_DATA23

MEM_DATA22

MEM_DATA21

MEM_DATA20

MEM_DATA19

MEM_DATA18

MEM_DATA17

MEM_DATA16

MEM_DATA15

MEM_DATA14

MEM_DATA13

MEM_DATA12

MEM_DATA11

MEM_DATA10

MEM_DATA9

MEM_DATA8

MEM_DATA7

MEM_DATA6

MEM_DATA5

MEM_DATA4

MEM_DATA3

MEM_DATA2

MEM_DATA1

MEM_DATA0

MEM_CHECK_LO7

MEM_CHECK_LO6

MEM_CHECK_LO5

MEM_CHECK_LO4

MEM_CHECK_LO3

MEM_CHECK_LO2

MEM_CHECK_LO1

MEM_CHECK_LO0

MEM_DM_LO8

MEM_DM_LO7

MEM_DM_LO6

MEM_DM_LO5

MEM_DM_LO4

MEM_DM_LO3

MEM_DM_LO2

MEM_DM_LO1

MEM_DM_LO0

MEM_DQS_LO8

MEM_DQS_LO7

MEM_DQS_LO6

MEM_DQS_LO5

MEM_DQS_LO4

MEM_DQS_LO3

MEM_DQS_LO2

MEM_DQS_LO1

MEM_DQS_LO0

AE16

AG17

AG18

AE18

AG16

AE17

AE20

AE23

AG24

AG19

AE19

AE24

AG25

AE25

AD25

AC25

AF25

AE27

AD29

AB25

AB27

AA28

AC26

AB29

AA27

AF17

AG21

AH27

AA25

AH17

AG20

AG26

AA26

AJ16

AJ18

AJ20

AJ24

AJ26

Y25

Y27

N25

M25

K27

K25

M29

M27

K29

H27

G27

D27

F25

H29

G26

E26

G25

G23

F23

C20

F19

E24

C24

G19

E19

E18

G17

E16

E15

G18

C18

G16

C16

Y29

W27

P27

R25

W26

V25

R28

P29

V29

L26

F27

G20

E17

U26

L25

E27

E20

F17

J27

U34C

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMCHECK 7

MEMCHECK 6

MEMCHECK 5

MEMCHECK 4

MEMCHECK 3

MEMCHECK 2

MEMCHECK 1

MEMCHECK 0

MEMDM_LO8

MEMDM_LO7

MEMDM_LO6

MEMDM_LO5

MEMDM_LO4

MDM_LO3

ME

MEMDM_LO2

MEMDM_LO1

MEMDM_LO0

MEMDQS_LO8

MEMDQS_LO7

MEMDQS_LO6

MEMDQS_LO5

MEMDQS_LO4

MEMDQS_LO3

MEMDQS_LO2

MEMDQS_LO1

MEMDQS_LO0

SKT-K8-2

MEMDATA127

MEMDATA126

MEMDATA125

MEMDATA124

MEMDATA123

MEMDATA122

MEMDATA121

MEMDATA120

MEMDATA119

MEMDATA118

MEMDATA117

MEMDATA116

MEMDATA115

MEMDATA114

MEMDATA113

MEMDATA112

MEMDATA111

MEMDATA110

MEMDATA109

MEMDATA108

MEMDATA107

MEMDATA106

MEMDATA105

MEMDATA104

MEMDATA103

MEMDATA102

MEMDATA101

MEMDATA100

MEMDATA99

MEMDATA98

MEMDATA97

MEMDATA96

MEMDATA95

MEMDATA94

MEMDATA93

MEMDATA92

MEMDATA91

MEMDATA90

MEMDATA89

MEMDATA88

MEMDATA87

MEMDATA86

MEMDATA85

MEMDATA84

MEMDATA83

MEMDATA82

MEMDATA81

MEMDATA80

MEMDATA79

MEMDATA78

MEMDATA77

MEMDATA76

MEMDATA75

MEMDATA74

MEMDATA73

MEMDATA72

MEMDATA71

MEMDATA70

MEMDATA69

MEMDATA68

MEMDATA67

MEMDATA66

MEMDATA65

MEMDATA64

MEMCHECK 15

MEMCHECK 14

MEMCHECK 13

MEMCHECK 12

MEMCHECK 11

MEMCHECK 10

MEMCHECK 9

MEMCHECK 8

MEMDM_UP8

MEMDM_UP7

MEMDM_UP6

MEMDM_UP5

MEMDM_UP4

MEMDM_UP3

MEMDM_UP2

MEMDM_UP1

MEMDM_UP0

MEMDQS_UP8

MEMDQS_UP7

MEMDQS_UP6

MEMDQS_UP5

MEMDQS_UP4

MEMDQS_UP3

MEMDQS_UP2

MEMDQS_UP1

MEMDQS_UP0

MEM_DATA127

AJ15

MEM_DATA126

AL16

MEM_DATA125

AL18

MEM_DATA124

AL19

MEM_DATA123

AL15

MEM_DATA122

AK15

MEM_DATA121

AK17

MEM_DATA120

AJ17

MEM_DATA119

AH19

MEM_DATA118

AL21

MEM_DATA117

AJ23

MEM_DATA116

AL25

MEM_DATA115

AK19

ME

AJ19

MEM_DATA113

AL24

MEM_DATA112

AK25

MEM_DATA111

AJ25

MEM_DATA110

AL26

MEM_DATA109

AG29

MEM_DATA108

AF31

MEM_DATA107

AH25

MEM_DATA106

AL27

MEM_DATA105

AJ31

MEM_DATA104

AG31

MEM_DATA103

AE31

MEM_DATA102

AD31

MEM_DATA101

AB31

MEM_DATA100

AA29

MEM_DATA99

AE29

MEM_DATA98

AC28

MEM_DATA97

AC31

MEM_DATA96

AA30

MEM_DATA95

M31

MEM_DATA94

L30

MEM_DATA93

H31

MEM_DATA92

G31

MEM_DATA91

L31

MEM_DATA90

L29

MEM_DATA89

J28

MEM_DATA88

G30

MEM_DATA87

E30

MEM_DATA86

C31

MEM_DATA85

C27

MEM_DATA84

D25

MEM_DATA83

E31

MEM_DATA82

C30

MEM_DATA81

B27

MEM_DATA80

A27

MEM_DATA79

C23

MEM_DATA78

B23

MEM_DATA77

A20

MEM_DATA76

B19

MEM_DATA75

A25

MEM_DATA74

A24

MEM_DATA73

C19

MEM_DATA72

A19

MEM_DATA71

D17

MEM_DATA70

B17

MEM_DATA69

C15

MEM_DATA68

A15

MEM_DATA67

A18

MEM_DATA66

C17

MEM_DATA65

D15

MEM_DATA64

B15

MEM_CHECK _UP7

AA31

MEM_CHECK _UP6

W29

N31

MEM_CHECK _UP5

MEM_CHECK _UP4

N29

MEM_CHECK_UP3

W28

MEM_CHECK _UP2

W31

MEM_CHECK _UP1

R29

MEM_CHECK_UP0

P31

V31

MEM_DM_UP8

MEM_DM_UP7

AL17

MEM_DM_UP6

AK21

AK27

MEM_DM_UP5

MEM_DM_UP4

AC29

MEM_DM_UP3

J30

MEM_DM_UP2

B29

MEM_DM_UP1

B21

MEM_DM_UP0

A16

U30

MEM_DQS_UP8

MEM_DQS_UP7

AH15

MEM_DQS_UP6

AL20

AJ27

MEM_DQS_UP5

MEM_DQS_UP4

AC30

MEM_DQS_UP3

J29

MEM_DQS_UP2

A28

MEM_DQS_UP1

A21

MEM_DQS_UP0

A17

M_DATA114

MEM_DATA[127..64]

MEM_CHECK _UP[7. .0]

MEM_DM_UP[8..0]

MEM_DQS_UP[8..0]

MEM_DATA[127. .64] 10, 11

MEM_CHECK _UP[7. .0] 10,11

MEM_DM_UP[8. .0] 10,11

MEM_DQS_UP[ 8..0] 10,11

To DIMM Channel-B

MEMZN,MEMZP with

5/10/5,<1000

mils

VCC2.5V_SUS

12

R364

34D8R3F-1

12

R355

34D8R3F-1

DDR_VTT

DDRVREF_CPU

VCC2.5V_SUS

12

C206

R301

12

100R3F

SCD01U16V3KX

12

R313

C214

12

100R3F

SCD01U16V3 KX

SC10 00P50V3KX

Two copper pure for VTT fill - at least 100mils wide

12

12

C231

C231, C229, C228, C234,

C223 are the decoupling

for VTT pins near

Processor

MEMZN

MEMZP

R340 51R3

1 2

20/15/20

DDRVREF_CPU

C205

C213

12

12

(R)

(R)

SCD1U16V3KX

TP70 TPAD28

SC4D7U10V-U

SCD22U10V3 KX

DDR_VTT

12

12

C228

SC4D7U10V-U

MEM_ADDA[13..0]10,11 MEM_ADDB[13. .0] 10,11

12

C234

C223

SCD22U10V3 KX

SCD22U10V3 KX

MEM_CS_1H_L110,11

MEM_CS_1H_L010,11

MEM_CS_1L_L110,11

MEM_CS_1L_L010,11

10/10/10

VTT_DDR_SUS_SENSE

MEM_CKEC10,11

MEM_CKEA10,11

MEM_BANKA110,11

MEM_BANKA010,11

MEM_RASA_L10,11

MEM_CASA_L10,11

MEM_WEA_L10,11

DDR_VTT

C229

DDRVREF_CPU

VTT_DDR_SUS_SE NSE

MEM_CS_1H_L1

MEM_CS_1H_L0

MEM_CS_1L_L1

MEM_CS_1L_L0

MEM_CKEC

MEM_CKEA

MEM_ADDA13

MEM_ADDA12

MEM_ADDA11

MEM_ADDA10

MEM_ADDA9

MEM_ADDA8

MEM_ADDA7

MEM_ADDA6

MEM_ADDA5

MEM_ADDA4

MEM_ADDA3

MEM_ADDA2

MEM_ADDA1

MEM_ADDA0

MEM_BANKA1

M

MEM_RASA_L

MEM_CASA_L

MEM_WEA_L

MEMZN

MEMZP

EM_BANKA0

AG14

AK14

AH14

AF13

AF15

AE15

AG28

AF29

AG27

AE26

AF23

AC27

AD27

AF27

AE28

B14

C14

D14

E14

AJ14

F15

AL29

AJ29

AL28

AJ30

C25

B25

E25

G24

C26

E28

V27

F29

H25

G28

L27

L28

N26

P25

U25

W25

J26

J25

U34B

VTT6

VTT7

VTT8

VTT1

VTT5

VTT4

VTT3

VTT2

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MEMCS_1H_L1

MEMCS_1H_L0

MEMCS_1L_L1

MEMCS_1L_L0

MEMCS_2H_L1

MEMCS_2H_L0

MEMCS_2L_L1

MEMCS_2L_L0

MEMCKED

MEMCKEC

MEMCKEB

MEMCKEA

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMBANKA1

MEMBANKA0

MEMRASA_L

MEMCASA_L

MEMWEA_L

SKT-K8-2

Clock group Layout rule :20/5/5/5/20

(Target Impedance 93 ohm)

MEMCLK_1H_H2

MEMCLK_1H_L2

MEMCLK_1H_H1

MEMCLK_1H_L1

MEMCLK_1H_H0

MEMCLK_1H_L0

MEMCLK_1L_H2

MEMCLK_1L_L2

MEMCLK_1L_H1

MEMCLK_1L_L1

MEMCLK_1L_H0

MEMCLK_1L_L0

MEMCLK_2H_H2

MEMCLK_2H_L2

MEMCLK_2H_H1

MEMCLK_2H_L1

MEMCLK_2H_H0

MEMCLK_2H_L0

MEMCLK_2L_H2

MEMCLK_2L_L2

MEMCLK_2L_H1

MEMCLK_2L_L1

MEMCLK_2L_H0

MEMCLK_2L_L0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMBANKB1

MEMBANKB0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMRESET_L

MEM_CLK_1H_L2

MEM_CLK_1H_L1

MEM_CLK_1H_L0

MEM_CLK_1L_L2

MEM_CLK_1L_L1

MEM_CLK_1L_L0

AL22

AL23

A22

A23

R31

R30

AH23

AG23

D23

E23

R27

R26

AJ21

AH21

C21

D21

T31

U31

AF21

AE21

G21

G22

T27

U27

AK23

A26

A29

W30

C29

E29

D31

G29

F31

J31

K31

N28

N30

U29

Y31

AE30

AG30

AK29

AH31

D19

MEM_CLK_1H_H2

MEM_CLK_1H_L2

MEM_CLK_1H_H1

MEM_CLK_1H_L1

MEM_CLK_1H_H0

MEM_CLK_1H_L0

MEM_CLK_1L_H2

MEM_CLK_1L_L2

MEM_CLK_1L_H1

MEM_CLK_1L_L1

MEM_CLK_1L_H0

MEM_CLK_1L_L0

MEM_CLK_2H_H2

MEM_CLK_2H_L2

MEM_CLK_2H_H1

MEM_CLK_2H_L1

MEM_CLK_2H_H0

MEM_CLK_2H_L0

MEM_CLK_2L_H2

MEM_CLK_2L_L2

MEM_CLK_2L_H1

MEM_CLK_2L_L1

MEM_CLK_2L_H0

MEM_CLK_2L_L0

MEM_ADDB13

MEM_ADDB12

MEM_ADDB11

MEM_ADDB10

MEM_ADDB9

MEM_ADDB8

MEM_ADDB7

MEM_ADDB6

MEM_ADDB5

MEM_ADDB4

MEM_ADDB3

MEM_ADDB2

MEM_ADDB1

MEM_ADDB0

MEM_BANKB1

MEM_BANKB0

MEM_RASB_L

MEM_CASB_L

MEM_WEB_L

MEM_RESET_L

R430 120R3

1 2

R434 120R3

1 2

R484 120R31 2

R439 120R3

1 2

R435 120R3

1 2

R493 120R3

1 2

MEM_CLK_1H_H2 10

MEM_CLK_1H_L2 10

MEM_CLK_1H_H1 10

MEM_CLK_1H_L1 10

MEM_CLK_1H_H0 10

MEM_CLK_1H_L0 10

MEM_CLK_1L_H2 10

MEM_CLK_1L_L2 10

MEM_CLK_1L_H1 10

MEM_CLK_1L_L1 10

MEM_CLK_1L_H0 10

MEM_CLK_1L_L0 10

Unused cloc k pairs

Place tes t points on

thebottom layer

MEM_BANKB1 10,11

MEM_BANKB0 10,11

MEM_RASB_L 10,11

MEM_CASB_L 10,11

MEM_WEB_L 10,11

MEM_RESET_L 10

MEM_CLK_1H_H2

MEM_CLK_1H_H1

MEM_CLK_1H_H0

MEM_CLK_1L_H2

MEM_CLK_1L_H1

MEM_CLK_1L_H0

TP25TPAD28

TP26TPAD28

TP28TPAD28

TP27TPAD28

TP30TPAD28

TP29TPAD28

TP80TPAD28

TP79TPAD28

TP83TPAD28

TP84TPAD28

TP86TPAD28

TP85TPAD28

A1

A31

Data/DM/CHECKgroup Layout rule : (Target Impedance 45 ohm)

Break in/out : 15/5/15

A A

DQS group Layout rule : (Target Impedance 35 ohm)

Motherboard trace routing : 10/10/10

Break in/out : 20/5/20

Motherboard trace routing : 20/15/20

8

7

Address/Command group Layout rule : (Target Impedance 45 ohm)

Break in/out : 15/5/15

Motherboard trace routing : 10/10/10

6

5

4

3

<Core Design>

Titl e

Althon64/64FX DDR I/F

Size DocumentNumber Rev

Custom

J361Y RS482+M1573

Date: Sheet

2

AL1

uPGA939

Top View

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih,Taipei

of

750Thursday, June 16, 2005

1

1A

PDF created with pdfFactory trial version www.pdffactory.com

Page 8

P

Processor MISC Signals

U

VDDA2.5V_CPU

1 2

12

TC27

L32

MLB201209-GP

D D

E100U16VM-L11-GP

8

CORE_SENSE

COREFB_H

COREFB_L

VDDIOFB_H

VDDIOFB_L

VDD_2.5_SUS_SENSE

VDDA

CPU_PWRGD

C C

LDTSTOP_L

LDTREST#

VCC2.5V: for pull-ups., no sequenceissue

B B

VCC2.5V_SUS

PUT IN BOTTOM

COREFB_H46

COREFB_L46

THERMDA_CPU28

THERMDC_CPU28

LDTREST#47

CPU_PWRGD47

LDTSTOP_L13,47

VCC2.5V_SUS

VCC12

1

D

Q60 2N7002-L1

PUT INTOP

G

23

S

TP52TPAD28

TP34TPAD28

TP35TPAD28

TP81TPAD28

TP82TPAD28

TP76TPAD28

TP36TPAD28

TP54TPAD28

TP51TPAD28

TP45TPAD28

COREFB_H

COREFB_L

THERMDA_CPU

THERMDC_CPU

LDTREST#

CPU_PWRGD

LDTSTOP_L

R339 51R3

1 2

VCC2.5V

12

C245

7

Imax: 300mA

Rdc: 50m ohm

100-300nH

12

C183

SCD22U10V3KX

SC3300P16V3KX

Place close

CPU

CPUCLK0_H24

CPUCLK0_L24

VDDA2.5V_CPU: for PLL

12

12

C190

C188

SC4D7U10V-U

VDD_2.5_SUS_SENSE

Width:5mil,

Spacing:10mil,

VLDT

Long:<1000mil

R264 44D2R3F

1 2

R265 44D2R3F

1 2

C177

SC1000P50V3KX

CPUCLK0_H

CPUCLK0_L

20/5/5/5/20

VCC2.5V_SUS

12

R296

820R3

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

12

R290

820R3

layout out with5/5/5

from CPU, thenfan

out to 8/5/8, 20 mils

spacing, < 1000 mils

ASIC8M_VDDA_EN(5V)

High:Enable L:Disable

6

http://hobi-elektronika.net

LAYOUT: Route VDDA trace approx. 50mils

wide (use 2x25 mil traces to exit ballfield) and

500 mils long.

VDDA

L0_REF1

L0_REF0

12

12

C176

SC1000P50V3KX

1 2

SC3900P50V2KX

169R3F

1 2

SC3900P50V2KX

C195

C191

VLDT

10/10/5/10/10

10/10/5/10/10

12

CLKIN_H

R289

CLKIN_L

20/5/5/5/20, length<500 mils

VCC2.5V

R322 680R3

1 2

R323 680R3

1 2

R250 49D9R3F

1 2

R254 49D9R3F

1 2

U24

APL1087

5

COREFB_H

COREFB_L

10/10/10

10/10/10

TP44 TPAD28

TP43 TPAD28

TP39 TPAD28

TP41 TPAD28

TP40 TPAD28

TP42 TPAD28

TP53 TPAD28

TP49 TPAD28

LDTREST#

CPU_PWRGD

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDD_2.5_SUS_SENSE

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

CPU_NC_C5

CPU_NC_A5

P_DBRDY

P_TMS

P_TCK

P_TRST_L

P_TDI

CPU_STRAP_HI_AJ12

CPU_STRAP_HI_AF12

CPU_STRAP_HI_T3

CPU_STRAP_LO_T4

CPU_NC_A4

CPU_NC_D4

CPU_NC_B4

CPU_NC_C4

CPU_NC_C7

CPU_NC_C6

AA24

AE13

AJ12

AF12

AE22

AG22

AH29

AJ22

AJ28

AK10

AK12

AG6

AG7

AH8

AK3

AK4

AK6

AK8

C3

B3

A3

F8

E8

B6

D1

C1

E5

E6

E7

Y24

A8

B8

E11

F11

C5

A5

B11

AF8

AJ9

T3

T4

A4

D4

B4

C4

C7

C6

AL8

AL7

AJ4

AJ5

AJ6

AJ7

AJ8

AL3

AL4

AL5

AL6

4

U34D

VDDA3

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORESENSE

VDDIOFB_H

VDDIOFB_L

VDDIOSENSE

CLKIN_H

CLKIN_L

BYPASSCLK_H

BYPASSCLK_L

PLLCHRZ_H

PLLCHRZ_L

DBRDY

TMS

TCK

TRST_L

TDI

SINGLECHAIN

BURNIN_L

SCANIN_H

SCANIN_L

ANALOG3

ANALOG2

ANALOG1

ANALOG0

DIG_T

ANALOG_T

RSVD_SMBUSC

RSVD_SMBUSD

FREE1

FREE2

FREE3

FREE4

FREE5

FREE6

FREE7

FREE8

FREE9

FREE10

FREE11

FREE12

FREE13

FREE14

FREE15

FREE16

FREE17

FREE18

FREE19

FREE20

FREE21

THERMTRIP_L

FBCLKOUT_H

FBCLKOUT_L

SCANCLK2

SCANCLK1

SCANSHIFTENB

SCANSHIFTEN

SCANOUT_H

SCANOUT_L

PROGEN1_L

PROGEN0_L

SKT-K8-2

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

DBREQ_L

SCANEN

TDO

FREE22

FREE23

FREE24

FREE25

FREE26

FREE27

FREE28

FREE29

FREE30

FREE31

FREE32

FREE33

FREE34

FREE35

FREE36

FREE37

FREE38

FREE39

FREE40

FREE41

3

THERMTRIP_CPU_L

AG10

THERMDA_CPU

AJ2

THERMDC_CPU

AJ1

10/10/10/10/10 place Sensor within 4"

VID4

A13

VID3LDTSTOP_L

A12

VID2

C12

VID1

A11

VID0

A10

CPU_NC_C13

C13

BP3

CPU_NC_E9

E9

BP2

B13

BP1

BP0

CPU_STRAP_LO_B13

C10

CPU_STRAP_LO_C10

2.5V differential output

FBCLKOUT_H

F13

FBCLKOUT_L

E13

P_DBREQ_L

A6

CPU_STRAP_LO_AG9

AG9

CPU_STRAP_LO_AH6

AH6

CPU_STRAP_LO_AF10

AF10

CPU_STRAP_LO_AH10

AH10

CPU_STRAP_LO_AJ10

AJ10

P_TDO

AG8

CPU_NC_V5

V5

CPU_NC_U5

U5

AL14

A14

AL9

AL10

AL11

AL12

C22

C28

D8

D11

D12

D29

E21

E22

G15

N27

T25

T29

U28

C11

AG15

AH12

DDR_VTT

DDR_VTT

TP62TPAD28

TP38TPAD28

TP37TPAD28

THERMTRIP_CPU_L

TP57TPAD28

TP56TPAD28

TP55TPAD28

TP50TPAD28

TP48TPAD28

TP69TPAD28

TP59TPAD28

TP68TPAD28

R329 680R3

1 2

R286 680R3

1 2

TP61TPAD28

R325

Layout rule: 20/8/5/8/20

within 1" Zdiff=80ohm

80D6R2F

0402

1 2

R305 680R3

1 2

R303 680R3

1 2

R309 680R3

1 2

R316 680R3

1 2

R315 680R3

1 2

TP47TPAD28

TP46TPAD28

VID[0..4]

2

VID[0..4] 46

VCC2.5V VCC3_3

12

Place Near CP

R350

1KR3

12

1

Q59

3

2

R348 1KR3

2N3904-L1-U

THERMDA_CPU

THERMDC_CPU

10/10/10/10/10 place Sensor within 4"

12

R341

10KR3

H_THERMTRIP# 20

THERMDA_CPU 28

THERMDC_CPU 28

1

Place Near

M1573

SC4D7U10V-U

VCC5

12

HDT Connector

J4

1

2

3

A A

4

6

8

10

12

14

16

18

20

22

24

26

SMC-CONN26A-FP

8

5

P_DBREQ_L

7

P_DBRDY

9

P_TCK

11

P_TMS

13

P_TDI

15

P_TRST_L

17

P_TDO

19

21

23

(R)

VCC2.5V

12

C147

SC1U16V3KX

SC10U10V5ZY

VCC5

ASIC8M_VDDA_EN47

Modify 0511 /J361Y

Tracking (Item:other

065)

R776 1KR3

7

C149

1 2

Q50

R775 10KR3

1 2

1

2N3906-L-U2

1

12

Q102

3

2N3904-L1-U

2

6

32

RA1

1KR3

6/9

U2_5VIN

100R3F

100R3F

R243

R244

VIN

12

ADJ/GND

VOUT

123

12

C173

VDDA_2.5V_ADJ

SC1U10V3KX

12

12

C181

(R)

SCD1U

SC1U10V3KX

5

VDDA2.5V_CPU

12

C174

SC10U10V5ZY

12

C180

(R)

<Core Design>

Wistron Incorp orated

21F, 88, Hsin Tai WuRd

Title

Althon64/64FX Miscellany

Size Document Number Rev

Custom

J361Y RS482+M1573

Date: Sheet

4

3

2

Hsichih, Taipei

850Thursday, June 16, 2005

1

of

PDF created with pdfFactory trial version www.pdffactory.com

1A

Page 9

8

Processor POWER & Ground

P

VCC_CORE

D D

R11

R13

R15

R17

R19

R21T2T6T8T10

T12

T14

T16

T18

T20U4U7U9U11

U13

U15

U17

U19

U21V6V8

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

AA4

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

VDD24

AB20

AC9

AC11

AC13

AC15

AC17

AC19

AD2

7

6

5

4

3

2

1

http://hobi-elektronika.net

VCC2.5V_SUS

V10

V12

V14

V16

V18

V20W7W9

W11

W13

W15

W17

W19

W21Y2Y6Y8Y10

Y12

Y14

Y16

Y18

Y20

AA23

AB22

AB24

AB30

AC21

AC23

AD20

AD22

AD24

AD30

AF30

AH30

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

B16

B18

B20

B22

B24

B26

B28

B30

D30

F30

H20

H22

H24

H30

J21

J23

K22

K24

K30

L23

M22

M24

M30

N23

P22

P24

P30

R23

T22

T24

T30

U23

V22

V24

V30

W23

Y22

Y30

U34E

DD136

VDD133

VDD134

VDD135

V

VDD137

VDD138

VDD139

VDD140

VDD141

VDD142

VDD143

VDD144

VDD145

VDD146

VDD147

VDD148

VDD149

VDD150

VDD151

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

AD6

AD8

AD10

AD12

AD14

AD16

AD18

AE4

AE7

AE9

AE11

VDD43

AJ11

AK5

AK7

AK9

AK11B5B10

B12

VCC_CORE

VDD152

VDD44

D10G7G9

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDD153

VDD154

VDD155

VDD156

VDD157

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

G11

G13H2H6H8H10

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDD93

VDD94

VDD95

VDD96

VDD97

VDD98

VDD99

VDD100

H12

H14

H16

H18J4J7J9J11

J13

J15

J17

J19K6K8

K10

K12

K14

K16

K18

K20L7L9

L11

L13

L15

L17

L19

L21M2M6M8M10

M12

M14

M16

M18

M20N4N7N9N11

VDD101

N13

N15

N17

N19

N21P6P8

P10

P12

SKT-K8-2

VDDIO52

VDDIO53

VDDIO54

VDDIO55

VDDIO56

VDDIO57

VDDIO58

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

P14

P16

P18

P20R7R9

C C

H23

H26

H28J6J8

J10

J12

J14

J16

J18

J20

J22

J24K2K7K9K11

K13

K15

K17

K19

K21

K23

K26

K28L4L6L8L10

L12

L14

L16

L18

L20

L22

L24M7M9

M11

M13

M15

M17

M19

M21

M23

M26

M28N6N8

N10

N12

N14

N16

N18

N20

N22

N24P2P7P9P11

P13

P15

P17

P19

P21

P23

P26

P28R4R6R8R10

R12

R14

R16

R18

R20

R22

R24T7T9

T11

T13

T15

T17

T19

T21

T23

T26

T28U6U8

U10

U12

U14

U16

U18

U20

U22

U24V2V7V9V11

V13

V15

V17

V19

V21

V23

V26

V28W4W6W8W10

W12

W14

W16

W18

W20

W22

W24Y7Y9

Y11

Y13

Y15

Y17

Y19

Y21

Y23

Y26

Y28

VSS136

VSS1

A7A9AA6

VSS137

VSS2

VSS138

VSS3

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB2

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AB28

AC4

AC6

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC24

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD21

AD23

AD26

AD28

AE6

AE8

AE10

AE12

AE14

AF2

AF6

AF7

AF9

AF11

AF14

AF16

AF20

AF22

AF24

AF26

AF28

AG5

AG11

AG13

AG12

AH1

AH2

AH3

AH4

AH5

AH7

AH9

AH11

AH13

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AJ3

AJ13

AK13

AL13B7B9C2C8C9D2D3D5D6D7D9D13

D16

D18

D20

D22

D24

D26

D28E3E4

E10

E12

G12F5F6F7F9

F10

F12

F14

F16

F18

VSS126VSS127

F22

F24

F26

F28G4G6G8G10

G14H7H9

U34F

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

SKT-K8-2

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

H11

H13

H15

H17

H19

H21

B B

VCC_CORE

VCC_Core decoupling Bottom Layer under

CPU socket

12

12

C641

SC10U10V6KX

12

12

C624

C631

SCD22U10V3KX

SCD22U10V3KX

12

C645

SC10U10V6KX

12

C639

SCD22U10V3KX

12

C617

C636

SC10U10V6KX

SC10U10V6KX

12

12

C614

C606

(R)

SCD22U10V3KX

SCD22U10V3KX

TOP Layer between

CPU and DIMMs

C365

12

12

12

12

C619

C625

C644

SC10U10V6KX

12

C616

(R)

SCD22U10V3KX

(R)

SC10U10V6KX

SC10U10V6KX

12

C623

C637

(R)

SC10U10V6KX

VCC2.5V_SUS VCC2.5V_SUS

(R)

SC10U10V6KX

Bottom Layer between CPU

and DIMMs

VCC2.5V_SUS

C356

C354

C366

C367

C355

A A

8

7

6

VDDIO Decoupling

1 2

SC4D7U10VMX-U

1 2

SC4D7U10VMX-U

1 2

SC4D7U10VMX-U

1 2

SC4D7U10VMX-U

1 2

(R)

SC4D7U10VMX-U

1 2

(R)

SC4D7U10VMX-U

TOP Layer near CPU socket

side

C286

1 2

SCD22U10V3KX

C278

1 2

SCD22U10V3KX

Bottom Layer under CPU

socket

C321

1 2

SCD22U10V3KX

C648

1 2

VCC2.5V_SUS

SCD22U10V3KX

C647

SCD22U10V3KX

C285

SCD22U10V3KX

1 2

1 2

5

A1 A31

uPGA939

Top View

<Core Design>

Title

Althon64/64FX Power a nd Ground

Size Do cument Numb er Rev

Custom

J361Y RS482+M1573

Date: Sheet

4

3

2

AL1

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

950Thursday, June 16, 2005

of

1

1A

PDF created with pdfFactory trial version www.pdffactory.com

Page 10

8

DIMM Slots

D D

MEM_BANKA07,11

MEM_BANKA17,11

C C

B B

MEM_BANKA0

MEM_BANKA1

MEM_RASA_L7,11

MEM_CASA_L7,11

MEM_WEA_ L7,11

7

MEM_ADDA0

MEM_ADDA1MEM_ADDA1

MEM_ADDA2

MEM_ADDA3MEM_ADDA3

MEM_ADDA4

MEM_ADDA5

MEM_ADDA6MEM_ADDA6

MEM_ADDA7MEM_ADDA7

MEM_ADDA8

MEM_ADDA9

MEM_BANKA0

MEM_BANKA1

MEM_ADDA11MEM_ADDA11

MEM_ADDA12

MEM_DAT A0

MEM_DAT A1MEM_DATA1

MEM_DAT A2MEM_DATA2

MEM_DAT A3

MEM_DAT A4

MEM_DAT A5MEM_DATA5

MEM_DAT A6MEM_DATA6

MEM_DAT A7

MEM_DAT A8

MEM_DAT A9

MEM_DAT A10MEM_DATA10

MEM_DAT A11MEM_DATA11

MEM_DAT A12MEM_DATA12

MEM_DAT A13MEM_DATA13

MEM_DAT A14MEM_DATA14

MEM_DAT A15MEM_DATA15

MEM_DAT A16MEM_DATA16

MEM_DAT A17MEM_DATA17

MEM_DAT A18MEM_DATA18

MEM_DAT A19MEM_DATA19

MEM_DAT A20MEM_DATA20

MEM_DAT A21MEM_DATA21

MEM_DAT A22MEM_DATA22

MEM_DAT A23MEM_DATA23

MEM_DAT A24

MEM_DAT A25MEM_DATA25

MEM_DAT A26MEM_DATA26

MEM_DAT A27

MEM_DAT A28

MEM_DAT A29MEM_DATA29

MEM_DAT A30MEM_DATA30

MEM_DAT A31MEM_DATA31

MEM_DAT A32

MEM_DAT A33

MEM_DAT A34MEM_DATA34

MEM_DAT A35MEM_DATA35

MEM_DAT A36MEM_DATA36

MEM_DAT A37

MEM_DAT A38MEM_DATA38

MEM_DAT A39MEM_DATA39

MEM_DAT A40MEM_DATA40

MEM_DAT A41MEM_DATA41

M_DATA42MEM_DATA42

ME

MEM_DAT A43MEM_DATA43

MEM_DAT A44MEM_DATA44

MEM_DAT A45MEM_DATA45

MEM_DAT A46

MEM_DAT A47

MEM_DAT A48

MEM_DAT A49

MEM_DAT A50MEM_DATA50

MEM_DAT A51MEM_DATA51

MEM_DAT A52MEM_DATA52

MEM_DAT A53MEM_DATA53

MEM_DAT A54MEM_DATA54

MEM_DAT A55MEM_DATA55

MEM_DAT A56MEM_DATA56

MEM_DAT A57

MEM_DAT A58MEM_DATA58

MEM_DAT A59MEM_DATA59

MEM_DAT A60MEM_DATA60

MEM_DAT A61MEM_DATA61

MEM_DAT A62

MEM_DAT A62

MEM_DAT A63

MEM_CHECK_ LO0

MEM_CHECK_ LO1

MEM_CHECK_ LO2

MEM_CHECK_ LO3

MEM_CHECK_ LO4

MEM_CHECK_ LO5

MEM_CHECK_ LO6

MEM_CHECK_ LO7

MEM_RESET_L7

MEM_ADDA137,11

MEM_ADDA[13..0]7,11

MEM_DATA[63..0]7,11

MEM_CHECK_LO[7..0]7,11

MEM_DQS_LO[8..0]7,11

MEM_DM_LO[8..0]7,11

CN35

48

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

A10

59

BA0

52

BA1

113

BA2

118 119

A11 DM2

115

A12

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

179

DQ63

44

CB0

45

CB1

49

CB2

51

CB3

134

CB4

135

CB5

142

CB6

144

CB7

154

/RAS

65

/CAS

63

/WE

SKT-DIMM184-U

(22.10244.291)

MEM_RESET_L

MEM_ADDA13

/CS0

/CS1

CKE0

CKE1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM3

DM4

DM5

DM6

DM7

DM8

VDDID

CK1

/CK1

CK0

/CK0

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

WP

VDD

VDD

VDD

VDD

DIMM Slot A

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VSDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VREF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSDQ 62

VSS

VSS

VSS

V33

NC/C S2

NC/C S3

NC

NC

NC

NC

RESET_N

FETEN

A13

10

103

167

6

MEM_ADDA[13. .0]

MEM_DAT A[63..0]

MEM_CHECK_LO[7..0]

MEM_DQS_LO[8..0]

MEM_DM_LO[8..0]

157

158

21

111

5

14

25

36

56

67

78

86

47

97

107

129

149

159

169

177

140

82

16

17

137

138

76

75

92

91

181

182

183

MEMWPA

90

108

120

148

70

85

168

38

7

46

54

96

62

128

104

136

30

143

77

112

156

164

172

180

15

22

1

3

145

18

58

50

100

160

139

132

152

116

11

34

26

66

93

124

74

176178

42

81

89

184

71

163

9

101

102

173

MEM_DQS_LO0MEM_DQ S_LO0

MEM_DQS_LO1MEM_DQ S_LO1

MEM_DQS_LO2MEM_DQ S_LO2

MEM_DQS_LO3MEM_DQ S_LO3

MEM_DQS_LO4MEM_DQ S_LO4

MEM_DQS_LO5MEM_DQ S_LO5

MEM_DQS_LO6MEM_DQ S_LO6MEM_ADDA10MEM_ADDA10

MEM_DQS_LO7MEM_DQ S_LO7

MEM_DQS_LO8

MEM_DM_LO0MEM_DM_LO0

MEM_DM_LO1MEM_DM_LO1

MEM_DM_LO2MEM_DM_LO2

MEM_DM_LO3MEM_DM_LO3

MEM_DM_LO4MEM_DM_LO4

MEM_DM_LO5MEM_DM_LO5

MEM_DM_LO6MEM_DM_LO6

MEM_DM_LO7MEM_DM_LO7

MEM_DM_LO8

MEM_CLK _1L_ H1

MEM_CLK_1L_L1

MEM_CLK _1L_ H0

MEM_CLK_1L_L0

MEM_CLK _1L_ H2

MEM_CLK_1L_L2

SMBCLK

SMBDAT

R569 4K7R3

1 2

DDRVREF

12

CA5

SCD1U

MEM_CS_1L_L0 7,11

MEM_CS_1L_L1 7,11

MEM_CKEA 7,11

MEM_CLK _1L_ H1 7

MEM_CLK_1L_L1 7

MEM_CLK _1L_ H0 7

MEM_CLK_1L_L0 7

MEM_CLK _1L_ H2 7

MEM_CLK_1L_L2 7

SMBCLK 24,28

SMBDAT 24 ,28

VCC2.5V_SUS

VCC3_3

6/14

5

4

http://hobi-elektronika.net

MEM_BANKB0 MEM_BAN KB0

VCC3_3

6/14

MEM_BANKB07,11

MEM_BANKB17,11

3

MEM_ADDB[13. .0]7,11

MEM_DAT A[127..6 4]7,11

MEM_CHECK_UP[7..0]7,11

MEM_DQS_UP[8..0]7,11

MEM_DM_UP[ 8..0 ]7,11

MEM_ADDB0

MEM_ADDB1MEM_ADDB1

MEM_ADDB2

MEM_ADDB3MEM_ADDB3

MEM_ADDB4

MEM_ADDB5

MEM_ADDB6MEM_ADDB6

MEM_ADDB7

MEM_ADDB8

MEM_ADDB9MEM_ADDB9

MEM_ADDB10MEM_ADDB10

MEM_BANKB1MEM_BANKB1

MEM_ADDB11MEM_ADDB11

MEM_ADDB12

MEM_DAT A64

MEM_DAT A65MEM_DATA65

MEM_DAT A66MEM_DATA66

MEM_DAT A67MEM_DATA67

MEM_DAT A68MEM_DATA68

MEM_DAT A69MEM_DATA69

MEM_DAT A70MEM_DATA70

MEM_DAT A71MEM_DATA71

MEM_DAT A72

MEM_DAT A73

MEM_DAT A74

MEM_DAT A75

MEM_DAT A76MEM_DATA76

MEM_DAT A77MEM_DATA77

MEM_DAT A78MEM_DATA78

MEM_DAT A79MEM_DATA79

MEM_DAT A80MEM_DATA80

MEM_DAT A81MEM_DATA81

MEM_DAT A82MEM_DATA82

MEM_DAT A83MEM_DATA83

MEM_DAT A84MEM_DATA84

MEM_DAT A85

MEM_DAT A86

MEM_DAT A87

MEM_DAT A88

MEM_DAT A89

MEM_DAT A90

MEM_DAT A91

MEM_DAT A92

MEM_DAT A93

MEM_DAT A94

MEM_DAT A95

MEM_DAT A96

MEM_DAT A97

MEM_DAT A98

MEM_DAT A99

MEM_DAT A100

MEM_DAT A101

MEM_DAT A102

MEM_DAT A103

MEM_DAT A104

MEM_DAT A105

MEM_DAT A106MEM_DAT A106

MEM_DAT A107MEM_DAT A107

MEM_DAT A108MEM_DAT A108

MEM_DAT A109MEM_DAT A109

M_DAT A110

ME

MEM_DAT A111

MEM_DAT A112MEM_DAT A112

MEM_DAT A113

MEM_DAT A114

MEM_DAT A115MEM_DAT A115

MEM_DAT A116MEM_DAT A116

MEM_DAT A117

MEM_DAT A118MEM_DAT A118

MEM_DAT A119MEM_DAT A119

MEM_DAT A120MEM_DAT A120

MEM_DAT A121MEM_DAT A121

MEM_DAT A122MEM_DAT A122

MEM_DAT A123MEM_DAT A123

MEM_DAT A124MEM_DAT A124

MEM_DAT A125MEM_DAT A125

MEM_DAT A126MEM_DAT A126

MEM_DAT A127

MEM_CHECK_ UP0

MEM_CHECK_ UP1

MEM_CHECK_ UP2

MEM_CHECK_ UP3

MEM_CHECK_ UP4

MEM_CHECK_ UP5

MEM_CHECK_ UP6

MEM_RASB_L7,11

MEM_CASB_L7,11

MEM_WEB_ L7,11

MEM_CHECK_ UP7

MEM_RESET_L7

MEM_ADDB137,11

MEM_ADDB[13. .0]

MEM_DATA[127..64]

MEM_CHECK_ UP[7.. 0]

MEM_DQS_UP[8..0]

MEM_DM_UP[ 8..0 ]

CN38

48

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

A10

59

BA0

52

BA1

113

BA2

118 119

A11 DM2

115

A12

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

179

DQ63

44

CB0

45

CB1

49

CB2

51

CB3

134

CB4

135

CB5

142

CB6

144

CB7

154

/RAS

65

/CAS

63

/WE

RESET_N

SKT-DIMM184-U

(22.10244.291)

MEM_RESET_L

MEM_ADDB13

FETEN

10

103

167

2

157

/CS0

158

/CS1

21

CKE0

111

CKE1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM3

DM4

DM5

DM6

DM7

DM8

VDDID

/CK1

/CK0

/CK2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

DIMM Slot B

VSDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VREF

NC/C S2

NC/C S3

A13

MEM_DQS_UP0

5

MEM_DQS_UP1

14

MEM_DQS_UP2MEM_DQS_UP2

25

MEM_DQS_UP3

36

MEM_DQS_UP4MEM_DQS_UP4

56

MEM_DQS_UP5MEM_DQS_UP5

67

MEM_DQS_UP6MEM_DQS_UP6

78

MEM_DQS_UP7MEM_DQS_UP7

86

MEM_DQS_UP8

47

MEM_DM_UP0

97

MEM_DM_UP1MEM_ DM_UP1

107

MEM_DM_UP2

MEM_DM_UP3

129

MEM_DM_UP4

149

MEM_DM_UP5MEM_ DM_UP5

159

MEM_DM_UP6

169

MEM_DM_UP7MEM_ DM_UP7

177

MEM_DM_UP8

140

82

MEM_CLK_1H_H1

16

CK1

MEM_CLK_1H_L1

17

MEM_CLK_1H_H0

137

CK0

MEM_CLK_1H_L0

138

MEM_CLK_1H_H2

76

CK2

MEM_CLK_1H_L2

75

SMBCLK

92

SCL

SMBDAT

91

SDA

181

SA0

182

SA1

183

SA2

MEMWPB

90

WP

108

120

148

70

85

168

38

7

VDD

46

54

96

62

128

104

136

30

143

77

112

156

164

172

180

15

22

1

3

VSS

145

VSS

18

VSS

58

VSS

50

VSS

100

VSS

160

VSS

139

VSS

132

VSS

152

VSS

116

VSS

11

VSS

34

VSS

26

VSS

66

VSS

93

VSS

124

VSS

74

VSS

176178

VSSDQ 62

42

VSS

81

VSS

89

VSS

184

V33

71

163

9

NC